ホストコントローラ、コンピュータ端末およびカードアクセス方法

【課題】実装スペースおよび消費電力の増大を抑えて、メモリカードの入出力方式に依存した様々なデータレートに適応できるようにする。

【解決手段】ホストコントローラは、メモリカードが装着されるカードスロット9と、送信データをシリアル転送形式に符号化する送信回路40と、受信データをシリアル転送形式から復号化する受信回路50と、カードクロックおよび転送クロックを生成する可変周波数クロック生成器10と、カードクロックをメモリカードに出力するカードクロック出力部20と、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部60と、メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて可変周波数クロック生成器10で生成される転送クロックの周波数を制御する設定レジスタ回路30とを備える。

【解決手段】ホストコントローラは、メモリカードが装着されるカードスロット9と、送信データをシリアル転送形式に符号化する送信回路40と、受信データをシリアル転送形式から復号化する受信回路50と、カードクロックおよび転送クロックを生成する可変周波数クロック生成器10と、カードクロックをメモリカードに出力するカードクロック出力部20と、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部60と、メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて可変周波数クロック生成器10で生成される転送クロックの周波数を制御する設定レジスタ回路30とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えばSDカードやマルチメディアカードのようなメモリカードをアクセスするホストコントローラ、コンピュータ端末、およびカードアクセス方法に関する。

【背景技術】

【0002】

近年では、ノートパソコンや携帯情報端末(PDA: Personal Digital Assistant)のようなコンピュータ端末の普及が著しい。コンピュータ端末の多くは、メモリカードをオプションで利用可能にするホストコントローラをインターフェース回路として備えている(例えば、特許文献1を参照)。一般的なメモリカードは、内部メモリセルアレイに対するデータの読み書きクロック周波数の1倍にこのデータの転送クロック周波数を設定したSDR(Single Data Rate)の入出力方式を採用している。また、最近では、転送クロック周波数の倍率が2倍のDDR(Double Data Rate)やこの倍率が4倍のDDR2(Double Data Rate 2)のメモリカードも登場している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007−34540号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、従来のホストコントローラは、一般的なSDR方式のメモリカードの仕様に合わせて設計されているため、例えばDDR方式のメモリカードとの互換性を得ることはできない。DDR方式に適応するホストコントローラも提案されているが、逆にSDR方式に適応できない。このような事情から、SDR方式用およびDDR方式用のハードウェアを併設した場合には、実装スペースおよび消費電力が増大することになる。

【0005】

本発明の目的は、実装スペースおよび消費電力の増大を抑えて、メモリカードの入出力方式に依存した様々なデータレートに適応できるホストコントローラ、コンピュータ端末、およびカードアクセス方法を提供することにある。

【課題を解決するための手段】

【0006】

本発明の第1観点によれば、メモリカードが装着されるカードスロットと、送信データをシリアル転送形式に符号化する送信回路と、受信データをシリアル転送形式から復号化する受信回路と、カードクロックおよび転送クロックを生成する可変周波数クロック生成器と、カードクロックをメモリカードに出力するカードクロック出力部と、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部と、メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路とを備えるホストコントローラが提供される。

【0007】

本発明の第2観点によれば、メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路と、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、カードクロックをメモリカードに出力するカードクロック出力部、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部、並びにメモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路を含むホストコントローラと、設定情報を設定レジスタ回路に設定すると共に送信データおよび受信データを処理するデータ処理回路とを備えるコンピュータ端末が提供される。

【0008】

本発明の第3観点によれば、メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、カードクロックをメモリカードに出力するカードクロック出力部、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部を備えたホストコントローラを用いるカードアクセス方法であって、メモリカードの入出力方式に関する設定情報を設定レジスタ回路に保持させ、この設定情報に基づいて可変周波数クロック生成器により生成される転送クロックの周波数を制御するカードアクセス方法が提供される。

【発明の効果】

【0009】

これらホストコントローラ、コンピュータ端末、およびカードアクセス方法では、メモリカードの入出力方式に関する設定情報が設定レジスタ回路に保持され、少なくとも可変周波数クロック生成器により生成される転送クロックの周波数がこの設定情報に基づいて制御される。この場合、メモリカードの入出力方式に依存した様々なデータレートに適応でき、かつハードウェア資源の大部分が入出力方式の違いによる不具合を伴わずに共用できるようになる。従って、実装スペースおよび消費電力の増大を抑えられる。

【図面の簡単な説明】

【0010】

【図1】本発明の一実施形態に係るコンピュータ端末の構成例を概略的に示すブロック図である。

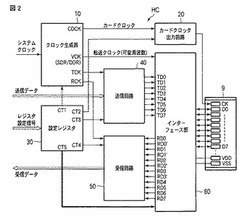

【図2】図1に示すホストコントローラの構成例を概略的に示すブロック図である。

【図3】図2に示す送信回路、受信回路およびインターフェース切換回路の詳細な構成例を示すブロック図である。

【図4】図3に示すインターフェース部の切換動作により構築される4ビットSDRモードインターフェースの例を示す図である。

【図5】図3に示すインターフェース部の切換動作により構築される8ビットSDRモードインターフェースの例を示す図である。

【図6】図3に示すインターフェース部の切換動作により構築される4ビットDDRモードインターフェースの例を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の一実施形態に係るコンピュータ端末について添付図面を参照して説明する。このコンピュータ端末は、例えばメモリカードをオプションで利用可能な携帯情報端末(PDA)である。

【0012】

図1はこのコンピュータ端末の構成例を概略的に示す。このコンピュータ端末は、端末全体を制御するCPU1、CPU1の制御プログラムや設定データを保持するROM2、CPU1への入力データおよびCPU1からの出力データを一時的に保持するRAM3、CPU1で実行すべきアプリケーションプログラム等のソフトウェアを格納する大容量フラッシュメモリ4、および外部入出力用のインターフェース回路5をデータ処理回路として備える。CPU1、ROM2、RAM3、フラッシュメモリ4、およびインターフェス回路5はシステムバスにより相互接続される。インターフェース回路5は、例えば様々なキー入力操作を行うキーボード6、インターネット等にワイヤレスで接続する通信回路7、CPU1の処理結果として得られる画像情報を表示するディスプレイ8、SDカードやマルチメディアカードのようなメモリカードがオプションで装着されるカードスロット9に接続される。インターフェース回路5は上述のメモリカードをアクセスするためにホストコントローラHCを有する。このホストコントローラHCは、メモリカードの入出力方式として代表的な4ビットSDR方式、8ビットSDR方式、および4ビットDDR方式に適応する例である。この例では、これら3方式のいずれかのメモリカードがカードスロット9に接続されると、このメモリカードへのデータ書込みおよびこのメモリカードからのデータ読出しが可能になる。

【0013】

図2はホストコントローラHCの構成例を概略的に示す。ホストコントローラHCは、可変周波数クロック生成器10、カードクロック出力回路20、設定レジスタ回路30、送信回路40、受信回路50、インターフェース部60を含む。 設定レジスタ回路30はデータ処理回路により設定されるメモリカードの入出力方式に関する設定情報を保持する設定レジスタ群を有し、設定情報に基づく制御信号CT1,CT2,CT3,CT4,CT5により可変周波数クロック生成器10、カードクロック出力回路20、設定レジスタ回路30、送信回路40、受信回路50、およびインターフェース部60をそれぞれ制御する。

【0014】

可変周波数クロック生成器10はデータ処理回路から供給されるシステムクロックを基準にして動作し、カードクロック出力回路20に出力されるカードクロックCDCK、インターフェース部60に出力される可変周波数の転送クロックVCK、送信回路40に供給される送信クロックTCK、および受信回路50に出力される受信クロックRCKを生成する。制御信号CT1は変周波数クロック生成器10の制御においてカードクロックCDCKに対する転送クロックVCKの周波数倍率をメモリカードの入出力方式に適合するように変更する。すなわち、メモリカードの入出力方式がSDR方式であれば、転送クロックVCKの周波数がカードクロックCDCKと同じ周波数に可変される。また、メモリカードの入出力方式がDDR方式であれば、転送クロックVCKの周波数がカードクロックCDCKの2倍の周波数に可変される。送信クロックTCKおよび受信クロックRCKはカードクロックCDCKと同じ周波数のクロックである。

【0015】

カードクロック出力回路20はカードクロックCDCKをカードスロット9のクロック端子CKを介してメモリカードに出力する。制御信号CT2はカードクロックCDCKの出力および停止制御を行う。カードクロックCDCKの出力は、メモリカードからの受信データのオーバフローを回避する必要がある場合に一時的に停止される。

【0016】

送信回路40は制御信号CT3によって制御され、データ処理回路からバイト単位または複数バイト単位で供給される送信データを送信クロックTCKに同期してシリアル転送形式に符号化してインターフェース部60のビット入力端子TD0〜TD7に出力する。

インターフェース部60は送信データのビット入力端子TD0〜TD7および受信データのビット出力端子RD0〜RD7,RD0’〜RD3を有し、制御信号CT5によって制御される。この制御の結果、インターフェース部60はビット入力端子TD0〜TD7に送信インターフェースとして内部接続される送信データライン群をメモリカードの入出力方式に適合するように切り換え、このデータライン群からの送信データビットをそれぞれカードスロット9のビット入出力端子DO〜D7のうちの対応部分を介してメモリカードにシリアル転送する。また、インターフェース部60はビット出力端子RD0〜RD7,RD0’〜RD3に受信インターフェースとして内部接続される受信データライン群をメモリカードの入出力方式に適合するように切り換え、メモリカードからカードスロット9のビット入出力端子DO〜D7に介してシリアル転送される受信データをビット出力端子RD0〜RD7,RD0’〜RD3’の対応部分から出力する。受信回路50は制御信号CT4によって制御され、ビット出力端子RD0〜RD7,RD0’〜RD3’の対応部分からの受信データビットを受信クロックRCKに同期してシリアル転送形式から復号化し、バイト単位または複数バイト単位の受信データとしてデータ処理回路に出力する。

【0017】

ちなみに、インターフェース部60はカードスロット9の電源端子VDD,VSSを介してメモリカードに電源電圧を供給する。尚、図2に示すカードスロット9の端子配列は一例であり、装着すべきメモリカードの種類間で互換性の得られる順序に変更してよい。

【0018】

図3は、図2に示す送信回路、受信回路およびインターフェース切換回路の詳細な構成例を示す。

【0019】

送信回路40は送信データを並列−直列変換する並列−直列変換器41、および並列直列変換器41によりビット単位に順次振り分けられる送信データをそれぞれシリアルパケットとして符号化する8個の送信処理部42(TL0〜TL7)を含む。送信処理部TL0〜TL7では、さらに巡回エラーチェック符号(CRC)等がシリアルパケットに付加される。制御信号CT3は並列−直列変換器41に供給され、送信クロックTCKは並列−直列変換器41および送信処理部TL0〜TL7に供給される。

【0020】

受信回路50はそれぞれシリアルパケットとして入力される受信データを復号化する8個の受信処理部52(RL0〜RL7)、および受信処理部TL0〜TL7からビット単位に出力される受信データを直列−並列変換する直列−並列変換器51を含む。受信処理部RL0〜RL7では、巡回エラーチェック符号(CRC)等のチェックも行われる。制御信号CT4は直列−並列変換器51に供給され、受信クロックRCKは直列−並列変換器51および受信処理部RL0〜RL7に供給される。

【0021】

インターフェース部60は送信インターフェース用の切換回路61および受信インターフェース用の切換回路62、および入出力バッファ回路63を含む。入出力バッファ回路63は8個の入出力バッファBF0〜BF7を含む。

【0022】

切換回路61は8個のスイッチSW0〜SW7を含む。切換回路61において、スイッチSW0〜SW3は2入力のスイッチであり、スイッチSW4〜SW7は1入力のスイッチである。送信処理部TL0〜TL7の出力端は切換回路61のスイッチSW0〜SW7に第1入力端にそれぞれ接続され、送信処理部TL4〜TL7の出力端は切換回路61のスイッチSW0〜SW3の第2入力端にも接続される。切換回路61のスイッチSW0〜SW7の出力端は入出力バッファBF0〜BF7にそれぞれ接続され、入出力バッファBF0〜BF7はカードスロット9のビット入出力端子DO〜D7に接続される。

【0023】

切換回路62は8個のスイッチSW0〜SW7を含む。切換回路62において、スイッチSW0〜SW3は2出力のスイッチであり、スイッチSW4〜SW7は1入力のスイッチである。受信処理部RL0〜RL7の入力端は切換回路62のスイッチSW0〜SW7に第1出力端にそれぞれ接続され、受信処理部RL4〜RL7の入力端は切換回路62のスイッチSW0〜SW3の第2出力端にも接続される。スイッチSW0〜SW7の入力端は入出力バッファBF0〜BF7にそれぞれ接続される。制御信号CT5は切換回路61のスイッチSW0〜SW7、切換回路62のスイッチSW0〜SW7、および入出力バッファ回路63に供給され、転送クロックVCKは入出力バッファ回路63に供給される。

【0024】

図4はインターフェース部の切換動作により構築される4ビットSDRモードインターフェースの例を示す。設定情報が4ビットSDRモードを表す場合、クロック生成器10が同一周波数でカードクロックCDCK、転送クロックVCK、送信クロックTCK、および受信クロックRCKを出力する。切換回路61では、スイッチSW0〜SW3が送信回路40の送信処理部TL0〜TL3に接続される4ビット分のデータライン群を選択して、このデータライン群から得られる送信データを入出力バッファBF0〜BF3に転送クロックVCKの立上がりに同期して供給する。これにより、入出力バッファBF0〜BF3は送信データをビット入出力端子DO〜D3を介してメモリカードにシリアル転送する。

【0025】

他方、切換回路62では、スイッチSW0〜SW3が受信回路50の受信処理部RL0〜RL3に接続される4ビット分のデータライン群を選択して、メモリカードからビット入出力端子DO〜D3を介して入出力バッファBF0〜BF3にシリアル転送される受信データを転送クロックVCKの立上がりに同期して受信処理部RL0〜RL3に出力する。

【0026】

図5はインターフェース部の切換動作により構築される8ビットSDRモードインターフェースの例を示す。設定情報が8ビットSDRモードを表す場合、クロック生成器10が同一周波数でカードクロックCDCK、転送クロックVCK、送信クロックTCK、および受信クロックRCKを出力する。

【0027】

切換回路61では、スイッチSW0〜SW7が送信回路40の送信処理部TL0〜TL7に接続される8ビット分のデータライン群を転送クロックVCKの立上がりに同期して選択して、このデータライン群から得られる送信データを入出力バッファBF0〜BF7に供給する。これにより、入出力バッファBF0〜BF7は送信データをビット入出力端子DO〜D7を介してメモリカードにシリアル転送する。

【0028】

他方、切換回路62では、スイッチSW0〜SW7が受信回路50の受信処理部RL0〜RL7に接続される8ビット分のデータライン群を選択して、メモリカードからビット入出力端子DO〜D7を介して入出力バッファBF0〜BF7にシリアル転送される受信データを転送クロックVCKの立上がりに同期して受信処理部RL0〜RL7に出力する。

【0029】

図6はインターフェース部の切換動作により構築される4ビットDDRモードインターフェースの例を示す。設定情報が4ビットDDRモードを表す場合、クロック生成器10が同一周波数でカードクロックCDCK、送信クロックTCK、および受信クロックRCKを出力し、カードクロックCDCKの2倍の周波数で転送クロックVCKを出力する。

【0030】

切換回路61では、スイッチSW0〜SW3が送信回路40の送信処理部TL0〜TL3に接続される4奇数ビット分のデータライン群および送信処理部TL4〜TL7に接続される4偶数ビット分のデータライン群を交互に選択して、このデータライン群から得られる送信データを転送クロックVCKの立上がりに同期して入出力バッファBF0〜BF3に供給する。これにより、入出力バッファBF0〜BF3は送信データをビット入出力端子DO〜D3を介してメモリカードにシリアル転送する。ちなみに、転送クロックVCKの周波数はカードクロックCDCKの2倍であるため、メモリカードはカードクロックのCDCKの立上がりおよび立下りで4奇数ビットのデータおよび4偶数ビットのデータを取得することになる。

【0031】

他方、切換回路62では、スイッチSW0〜SW3が受信回路50の受信処理部RL0〜RL3に接続される4奇数ビット分のデータライン群および受信処理部RL4〜RL7に接続される4偶数ビット分のデータライン群を交互に選択して、メモリカードからビット入出力端子DO〜D3を介して入出力バッファBF0〜BF3にシリアル転送される受信データを転送クロックVCKの立上がりに同期して受信処理部RL0〜RL3,受信処理部RL4〜RL7に交互に出力する。受信回路50では、受信処理部RL0〜RL3で復号化された4奇数ビットのデータおよび受信処理部RL4〜RL7で復号化された4偶数ビットのデータが直列−並列変換器51でそれぞれ直列−並列変換され、バイト単位または複数バイト単位でデータ処理回路に出力される。

【0032】

本実施形態のコンピュータ端末では、メモリカードの入出力方式に関する設定情報が設定レジスタ回路30に保持され、少なくとも可変周波数クロック生成器10により生成される転送クロックVCKの周波数がこの設定情報に基づいて制御される。この場合、メモリカードの入出力方式に依存した様々なデータレートに適応でき、かつハードウェア資源の大部分が入出力方式の違いによる不具合を伴わずに共用できるようになる。従って、実装スペースおよび消費電力の増大を抑えられる。

【0033】

尚、本発明は上述の実施形態に限定されず、その要旨を逸脱しない範囲で様々に変形可能である。

【0034】

上述の実施形態では、クロック生成器10がカードクロックCDCK、可変周波数の転送クロックVCK、送信クロックTCK、および受信クロックRCKを生成するが、カードクロックCDCK、送信クロックTCK、および受信クロックRCKとして同一周波数の固定クロックを生成する第1クロック生成モジュールおよびこの固定クロックの周波数の自然数倍に可変できる周波数の可変クロックを生成する第2クロック生成モジュールを設けてもよい。この場合、固定クロックは第1クロック生成モジュールからカードクロック出力回路20、送信回路40、および受信回路50に供給され、第2クロック生成モジュールからインターフェース部60に供給される。

【0035】

また、このホストコントローラHCは、メモリカードの入出力方式として代表的な4ビットSDR方式、8ビットSDR方式、および4ビットDDR方式に適応する例であるが、カードクロックCDCKに対する転送クロックVCKの周波数倍率を4倍にすることによりさらにDDR2に適合させてもよい。

【0036】

さらに、ここで述べたコンピュータ端末の様々なモジュールは、ソフトウェアアプリケーション、ハードウェアおよび/またはソフトウェアモジュールのような1以上のコンポーネンツで実現可能である。これら様々なモジュールは別々に記載されている一方で、基礎となるロジックやコードの全てあるいは一部に配分されてもよい。

【符号の説明】

【0037】

10…可変周波数クロック生成器、20…カードクロック出力回路、30…設定レジスタ回路、40…送信回路、50…受信回路、60…インターフェース部、61,62…切換回路、63…入出力バッファ回路。

【技術分野】

【0001】

本発明は、例えばSDカードやマルチメディアカードのようなメモリカードをアクセスするホストコントローラ、コンピュータ端末、およびカードアクセス方法に関する。

【背景技術】

【0002】

近年では、ノートパソコンや携帯情報端末(PDA: Personal Digital Assistant)のようなコンピュータ端末の普及が著しい。コンピュータ端末の多くは、メモリカードをオプションで利用可能にするホストコントローラをインターフェース回路として備えている(例えば、特許文献1を参照)。一般的なメモリカードは、内部メモリセルアレイに対するデータの読み書きクロック周波数の1倍にこのデータの転送クロック周波数を設定したSDR(Single Data Rate)の入出力方式を採用している。また、最近では、転送クロック周波数の倍率が2倍のDDR(Double Data Rate)やこの倍率が4倍のDDR2(Double Data Rate 2)のメモリカードも登場している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007−34540号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、従来のホストコントローラは、一般的なSDR方式のメモリカードの仕様に合わせて設計されているため、例えばDDR方式のメモリカードとの互換性を得ることはできない。DDR方式に適応するホストコントローラも提案されているが、逆にSDR方式に適応できない。このような事情から、SDR方式用およびDDR方式用のハードウェアを併設した場合には、実装スペースおよび消費電力が増大することになる。

【0005】

本発明の目的は、実装スペースおよび消費電力の増大を抑えて、メモリカードの入出力方式に依存した様々なデータレートに適応できるホストコントローラ、コンピュータ端末、およびカードアクセス方法を提供することにある。

【課題を解決するための手段】

【0006】

本発明の第1観点によれば、メモリカードが装着されるカードスロットと、送信データをシリアル転送形式に符号化する送信回路と、受信データをシリアル転送形式から復号化する受信回路と、カードクロックおよび転送クロックを生成する可変周波数クロック生成器と、カードクロックをメモリカードに出力するカードクロック出力部と、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部と、メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路とを備えるホストコントローラが提供される。

【0007】

本発明の第2観点によれば、メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路と、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、カードクロックをメモリカードに出力するカードクロック出力部、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部、並びにメモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路を含むホストコントローラと、設定情報を設定レジスタ回路に設定すると共に送信データおよび受信データを処理するデータ処理回路とを備えるコンピュータ端末が提供される。

【0008】

本発明の第3観点によれば、メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、カードクロックをメモリカードに出力するカードクロック出力部、転送クロックに同期して送信回路からの送信データをメモリカードへシリアル転送する送信インターフェースおよび転送クロックに同期してメモリカードからの受信データを受信回路へシリアル転送する受信インターフェースを含むインターフェース部を備えたホストコントローラを用いるカードアクセス方法であって、メモリカードの入出力方式に関する設定情報を設定レジスタ回路に保持させ、この設定情報に基づいて可変周波数クロック生成器により生成される転送クロックの周波数を制御するカードアクセス方法が提供される。

【発明の効果】

【0009】

これらホストコントローラ、コンピュータ端末、およびカードアクセス方法では、メモリカードの入出力方式に関する設定情報が設定レジスタ回路に保持され、少なくとも可変周波数クロック生成器により生成される転送クロックの周波数がこの設定情報に基づいて制御される。この場合、メモリカードの入出力方式に依存した様々なデータレートに適応でき、かつハードウェア資源の大部分が入出力方式の違いによる不具合を伴わずに共用できるようになる。従って、実装スペースおよび消費電力の増大を抑えられる。

【図面の簡単な説明】

【0010】

【図1】本発明の一実施形態に係るコンピュータ端末の構成例を概略的に示すブロック図である。

【図2】図1に示すホストコントローラの構成例を概略的に示すブロック図である。

【図3】図2に示す送信回路、受信回路およびインターフェース切換回路の詳細な構成例を示すブロック図である。

【図4】図3に示すインターフェース部の切換動作により構築される4ビットSDRモードインターフェースの例を示す図である。

【図5】図3に示すインターフェース部の切換動作により構築される8ビットSDRモードインターフェースの例を示す図である。

【図6】図3に示すインターフェース部の切換動作により構築される4ビットDDRモードインターフェースの例を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の一実施形態に係るコンピュータ端末について添付図面を参照して説明する。このコンピュータ端末は、例えばメモリカードをオプションで利用可能な携帯情報端末(PDA)である。

【0012】

図1はこのコンピュータ端末の構成例を概略的に示す。このコンピュータ端末は、端末全体を制御するCPU1、CPU1の制御プログラムや設定データを保持するROM2、CPU1への入力データおよびCPU1からの出力データを一時的に保持するRAM3、CPU1で実行すべきアプリケーションプログラム等のソフトウェアを格納する大容量フラッシュメモリ4、および外部入出力用のインターフェース回路5をデータ処理回路として備える。CPU1、ROM2、RAM3、フラッシュメモリ4、およびインターフェス回路5はシステムバスにより相互接続される。インターフェース回路5は、例えば様々なキー入力操作を行うキーボード6、インターネット等にワイヤレスで接続する通信回路7、CPU1の処理結果として得られる画像情報を表示するディスプレイ8、SDカードやマルチメディアカードのようなメモリカードがオプションで装着されるカードスロット9に接続される。インターフェース回路5は上述のメモリカードをアクセスするためにホストコントローラHCを有する。このホストコントローラHCは、メモリカードの入出力方式として代表的な4ビットSDR方式、8ビットSDR方式、および4ビットDDR方式に適応する例である。この例では、これら3方式のいずれかのメモリカードがカードスロット9に接続されると、このメモリカードへのデータ書込みおよびこのメモリカードからのデータ読出しが可能になる。

【0013】

図2はホストコントローラHCの構成例を概略的に示す。ホストコントローラHCは、可変周波数クロック生成器10、カードクロック出力回路20、設定レジスタ回路30、送信回路40、受信回路50、インターフェース部60を含む。 設定レジスタ回路30はデータ処理回路により設定されるメモリカードの入出力方式に関する設定情報を保持する設定レジスタ群を有し、設定情報に基づく制御信号CT1,CT2,CT3,CT4,CT5により可変周波数クロック生成器10、カードクロック出力回路20、設定レジスタ回路30、送信回路40、受信回路50、およびインターフェース部60をそれぞれ制御する。

【0014】

可変周波数クロック生成器10はデータ処理回路から供給されるシステムクロックを基準にして動作し、カードクロック出力回路20に出力されるカードクロックCDCK、インターフェース部60に出力される可変周波数の転送クロックVCK、送信回路40に供給される送信クロックTCK、および受信回路50に出力される受信クロックRCKを生成する。制御信号CT1は変周波数クロック生成器10の制御においてカードクロックCDCKに対する転送クロックVCKの周波数倍率をメモリカードの入出力方式に適合するように変更する。すなわち、メモリカードの入出力方式がSDR方式であれば、転送クロックVCKの周波数がカードクロックCDCKと同じ周波数に可変される。また、メモリカードの入出力方式がDDR方式であれば、転送クロックVCKの周波数がカードクロックCDCKの2倍の周波数に可変される。送信クロックTCKおよび受信クロックRCKはカードクロックCDCKと同じ周波数のクロックである。

【0015】

カードクロック出力回路20はカードクロックCDCKをカードスロット9のクロック端子CKを介してメモリカードに出力する。制御信号CT2はカードクロックCDCKの出力および停止制御を行う。カードクロックCDCKの出力は、メモリカードからの受信データのオーバフローを回避する必要がある場合に一時的に停止される。

【0016】

送信回路40は制御信号CT3によって制御され、データ処理回路からバイト単位または複数バイト単位で供給される送信データを送信クロックTCKに同期してシリアル転送形式に符号化してインターフェース部60のビット入力端子TD0〜TD7に出力する。

インターフェース部60は送信データのビット入力端子TD0〜TD7および受信データのビット出力端子RD0〜RD7,RD0’〜RD3を有し、制御信号CT5によって制御される。この制御の結果、インターフェース部60はビット入力端子TD0〜TD7に送信インターフェースとして内部接続される送信データライン群をメモリカードの入出力方式に適合するように切り換え、このデータライン群からの送信データビットをそれぞれカードスロット9のビット入出力端子DO〜D7のうちの対応部分を介してメモリカードにシリアル転送する。また、インターフェース部60はビット出力端子RD0〜RD7,RD0’〜RD3に受信インターフェースとして内部接続される受信データライン群をメモリカードの入出力方式に適合するように切り換え、メモリカードからカードスロット9のビット入出力端子DO〜D7に介してシリアル転送される受信データをビット出力端子RD0〜RD7,RD0’〜RD3’の対応部分から出力する。受信回路50は制御信号CT4によって制御され、ビット出力端子RD0〜RD7,RD0’〜RD3’の対応部分からの受信データビットを受信クロックRCKに同期してシリアル転送形式から復号化し、バイト単位または複数バイト単位の受信データとしてデータ処理回路に出力する。

【0017】

ちなみに、インターフェース部60はカードスロット9の電源端子VDD,VSSを介してメモリカードに電源電圧を供給する。尚、図2に示すカードスロット9の端子配列は一例であり、装着すべきメモリカードの種類間で互換性の得られる順序に変更してよい。

【0018】

図3は、図2に示す送信回路、受信回路およびインターフェース切換回路の詳細な構成例を示す。

【0019】

送信回路40は送信データを並列−直列変換する並列−直列変換器41、および並列直列変換器41によりビット単位に順次振り分けられる送信データをそれぞれシリアルパケットとして符号化する8個の送信処理部42(TL0〜TL7)を含む。送信処理部TL0〜TL7では、さらに巡回エラーチェック符号(CRC)等がシリアルパケットに付加される。制御信号CT3は並列−直列変換器41に供給され、送信クロックTCKは並列−直列変換器41および送信処理部TL0〜TL7に供給される。

【0020】

受信回路50はそれぞれシリアルパケットとして入力される受信データを復号化する8個の受信処理部52(RL0〜RL7)、および受信処理部TL0〜TL7からビット単位に出力される受信データを直列−並列変換する直列−並列変換器51を含む。受信処理部RL0〜RL7では、巡回エラーチェック符号(CRC)等のチェックも行われる。制御信号CT4は直列−並列変換器51に供給され、受信クロックRCKは直列−並列変換器51および受信処理部RL0〜RL7に供給される。

【0021】

インターフェース部60は送信インターフェース用の切換回路61および受信インターフェース用の切換回路62、および入出力バッファ回路63を含む。入出力バッファ回路63は8個の入出力バッファBF0〜BF7を含む。

【0022】

切換回路61は8個のスイッチSW0〜SW7を含む。切換回路61において、スイッチSW0〜SW3は2入力のスイッチであり、スイッチSW4〜SW7は1入力のスイッチである。送信処理部TL0〜TL7の出力端は切換回路61のスイッチSW0〜SW7に第1入力端にそれぞれ接続され、送信処理部TL4〜TL7の出力端は切換回路61のスイッチSW0〜SW3の第2入力端にも接続される。切換回路61のスイッチSW0〜SW7の出力端は入出力バッファBF0〜BF7にそれぞれ接続され、入出力バッファBF0〜BF7はカードスロット9のビット入出力端子DO〜D7に接続される。

【0023】

切換回路62は8個のスイッチSW0〜SW7を含む。切換回路62において、スイッチSW0〜SW3は2出力のスイッチであり、スイッチSW4〜SW7は1入力のスイッチである。受信処理部RL0〜RL7の入力端は切換回路62のスイッチSW0〜SW7に第1出力端にそれぞれ接続され、受信処理部RL4〜RL7の入力端は切換回路62のスイッチSW0〜SW3の第2出力端にも接続される。スイッチSW0〜SW7の入力端は入出力バッファBF0〜BF7にそれぞれ接続される。制御信号CT5は切換回路61のスイッチSW0〜SW7、切換回路62のスイッチSW0〜SW7、および入出力バッファ回路63に供給され、転送クロックVCKは入出力バッファ回路63に供給される。

【0024】

図4はインターフェース部の切換動作により構築される4ビットSDRモードインターフェースの例を示す。設定情報が4ビットSDRモードを表す場合、クロック生成器10が同一周波数でカードクロックCDCK、転送クロックVCK、送信クロックTCK、および受信クロックRCKを出力する。切換回路61では、スイッチSW0〜SW3が送信回路40の送信処理部TL0〜TL3に接続される4ビット分のデータライン群を選択して、このデータライン群から得られる送信データを入出力バッファBF0〜BF3に転送クロックVCKの立上がりに同期して供給する。これにより、入出力バッファBF0〜BF3は送信データをビット入出力端子DO〜D3を介してメモリカードにシリアル転送する。

【0025】

他方、切換回路62では、スイッチSW0〜SW3が受信回路50の受信処理部RL0〜RL3に接続される4ビット分のデータライン群を選択して、メモリカードからビット入出力端子DO〜D3を介して入出力バッファBF0〜BF3にシリアル転送される受信データを転送クロックVCKの立上がりに同期して受信処理部RL0〜RL3に出力する。

【0026】

図5はインターフェース部の切換動作により構築される8ビットSDRモードインターフェースの例を示す。設定情報が8ビットSDRモードを表す場合、クロック生成器10が同一周波数でカードクロックCDCK、転送クロックVCK、送信クロックTCK、および受信クロックRCKを出力する。

【0027】

切換回路61では、スイッチSW0〜SW7が送信回路40の送信処理部TL0〜TL7に接続される8ビット分のデータライン群を転送クロックVCKの立上がりに同期して選択して、このデータライン群から得られる送信データを入出力バッファBF0〜BF7に供給する。これにより、入出力バッファBF0〜BF7は送信データをビット入出力端子DO〜D7を介してメモリカードにシリアル転送する。

【0028】

他方、切換回路62では、スイッチSW0〜SW7が受信回路50の受信処理部RL0〜RL7に接続される8ビット分のデータライン群を選択して、メモリカードからビット入出力端子DO〜D7を介して入出力バッファBF0〜BF7にシリアル転送される受信データを転送クロックVCKの立上がりに同期して受信処理部RL0〜RL7に出力する。

【0029】

図6はインターフェース部の切換動作により構築される4ビットDDRモードインターフェースの例を示す。設定情報が4ビットDDRモードを表す場合、クロック生成器10が同一周波数でカードクロックCDCK、送信クロックTCK、および受信クロックRCKを出力し、カードクロックCDCKの2倍の周波数で転送クロックVCKを出力する。

【0030】

切換回路61では、スイッチSW0〜SW3が送信回路40の送信処理部TL0〜TL3に接続される4奇数ビット分のデータライン群および送信処理部TL4〜TL7に接続される4偶数ビット分のデータライン群を交互に選択して、このデータライン群から得られる送信データを転送クロックVCKの立上がりに同期して入出力バッファBF0〜BF3に供給する。これにより、入出力バッファBF0〜BF3は送信データをビット入出力端子DO〜D3を介してメモリカードにシリアル転送する。ちなみに、転送クロックVCKの周波数はカードクロックCDCKの2倍であるため、メモリカードはカードクロックのCDCKの立上がりおよび立下りで4奇数ビットのデータおよび4偶数ビットのデータを取得することになる。

【0031】

他方、切換回路62では、スイッチSW0〜SW3が受信回路50の受信処理部RL0〜RL3に接続される4奇数ビット分のデータライン群および受信処理部RL4〜RL7に接続される4偶数ビット分のデータライン群を交互に選択して、メモリカードからビット入出力端子DO〜D3を介して入出力バッファBF0〜BF3にシリアル転送される受信データを転送クロックVCKの立上がりに同期して受信処理部RL0〜RL3,受信処理部RL4〜RL7に交互に出力する。受信回路50では、受信処理部RL0〜RL3で復号化された4奇数ビットのデータおよび受信処理部RL4〜RL7で復号化された4偶数ビットのデータが直列−並列変換器51でそれぞれ直列−並列変換され、バイト単位または複数バイト単位でデータ処理回路に出力される。

【0032】

本実施形態のコンピュータ端末では、メモリカードの入出力方式に関する設定情報が設定レジスタ回路30に保持され、少なくとも可変周波数クロック生成器10により生成される転送クロックVCKの周波数がこの設定情報に基づいて制御される。この場合、メモリカードの入出力方式に依存した様々なデータレートに適応でき、かつハードウェア資源の大部分が入出力方式の違いによる不具合を伴わずに共用できるようになる。従って、実装スペースおよび消費電力の増大を抑えられる。

【0033】

尚、本発明は上述の実施形態に限定されず、その要旨を逸脱しない範囲で様々に変形可能である。

【0034】

上述の実施形態では、クロック生成器10がカードクロックCDCK、可変周波数の転送クロックVCK、送信クロックTCK、および受信クロックRCKを生成するが、カードクロックCDCK、送信クロックTCK、および受信クロックRCKとして同一周波数の固定クロックを生成する第1クロック生成モジュールおよびこの固定クロックの周波数の自然数倍に可変できる周波数の可変クロックを生成する第2クロック生成モジュールを設けてもよい。この場合、固定クロックは第1クロック生成モジュールからカードクロック出力回路20、送信回路40、および受信回路50に供給され、第2クロック生成モジュールからインターフェース部60に供給される。

【0035】

また、このホストコントローラHCは、メモリカードの入出力方式として代表的な4ビットSDR方式、8ビットSDR方式、および4ビットDDR方式に適応する例であるが、カードクロックCDCKに対する転送クロックVCKの周波数倍率を4倍にすることによりさらにDDR2に適合させてもよい。

【0036】

さらに、ここで述べたコンピュータ端末の様々なモジュールは、ソフトウェアアプリケーション、ハードウェアおよび/またはソフトウェアモジュールのような1以上のコンポーネンツで実現可能である。これら様々なモジュールは別々に記載されている一方で、基礎となるロジックやコードの全てあるいは一部に配分されてもよい。

【符号の説明】

【0037】

10…可変周波数クロック生成器、20…カードクロック出力回路、30…設定レジスタ回路、40…送信回路、50…受信回路、60…インターフェース部、61,62…切換回路、63…入出力バッファ回路。

【特許請求の範囲】

【請求項1】

メモリカードが装着されるカードスロットと、

送信データをシリアル転送形式に符号化する送信回路と、

受信データをシリアル転送形式から復号化する受信回路と、

カードクロックおよび転送クロックを生成する可変周波数クロック生成器と、

前記カードクロックを前記メモリカードに出力するカードクロック出力部と、

前記転送クロックに同期して前記送信回路からの送信データを前記メモリカードへシリアル転送する送信インターフェースおよび前記転送クロックに同期して前記メモリカードからの受信データを前記受信回路へシリアル転送する受信インターフェースを含むインターフェース部と、

前記メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて前記可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路と、を備えることを特徴とするホストコントローラ。

【請求項2】

前記設定レジスタ回路は前記可変周波数クロック生成器の制御において前記カードクロックに対する転送クロックの周波数倍率を前記メモリカードの入出力方式に適合するように変更することを特徴とする請求項1に記載のホストコントローラ。

【請求項3】

前記インターフェース部は前記送信インターフェースとして設けられる送信データライン群、前記受信インターフェースとして設けられる受信データライン群、および前記送信データライン群および前記受信データライン群をそれぞれ切り換える切換回路を含み、前記設定レジスタ回路は前記設定情報に基づいて前記切換回路を制御することを特徴とする請求項2に記載のホストコントローラ。

【請求項4】

前記送信回路は前記送信データを並列−直列変換する並列−直列変換器、および前記並列直列変換器によりビット単位に順次振り分けられる送信データをそれぞれシリアルパケットとして符号化して前記切換回路によって切り換えられた結果の送信データライン群に出力する複数の送信処理部を含み、前記受信回路は前記切換回路によって切換られた結果の受信データライン群からそれぞれシリアルパケットとして入力される前記受信データを復号化する複数の受信処理部、および前記受信処理部からビット単位に出力される受信データを直列−並列変換する直列−並列変換器を含むことを特徴とする請求項3に記載のホストコントローラ。

【請求項5】

前記メモリカードの入出力方式は、少なくともSDR(Single Data Rate)およびDDR(Double Data Rate)から選択されることを特徴とする請求項1に記載のホストコントローラ。

【請求項6】

メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、前記カードクロックを前記メモリカードに出力するカードクロック出力部、前記転送クロックに同期して前記送信回路からの送信データを前記メモリカードへシリアル転送する送信インターフェースおよび前記転送クロックに同期して前記メモリカードからの受信データを前記受信回路へシリアル転送する受信インターフェースを含むインターフェース部、並びに前記メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて前記可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路を含むホストコントローラと、

前記設定情報を前記設定レジスタ回路に設定すると共に送信データおよび受信データを処理するデータ処理回路と、を備えることを特徴とするコンピュータ端末。

【請求項7】

前記設定レジスタ回路は前記可変周波数クロック生成器の制御において前記カードクロックに対する転送クロックの周波数倍率を前記メモリカードの入出力方式に適合するように変更することを特徴とする請求項6に記載のコンピュータ端末。

【請求項8】

前記インターフェース部は前記送信インターフェースとして設けられる送信データライン群、前記受信インターフェースとして設けられる受信データライン群、および前記送信データライン群および前記受信データライン群をそれぞれ切り換える切換回路を含み、前記設定レジスタ回路は前記設定情報に基づいて前記切換回路を制御することを特徴とする請求項7に記載のコンピュータ端末。

【請求項9】

前記送信回路は前記送信データを並列−直列変換する並列−直列変換器、および前記並列直列変換器によりビット単位に順次振り分けられる送信データをそれぞれシリアルパケットとして符号化して前記切換回路によって切り換えられた結果の送信データライン群に出力する複数の送信処理部を含み、前記受信回路は前記切換回路によって切換られた結果の受信データライン群からそれぞれシリアルパケットとして入力される前記受信データを復号化する複数の受信処理部、および前記受信処理部からビット単位に出力される受信データを直列−並列変換する直列−並列変換器を含むことを特徴とする請求項8に記載のコンピュータ端末。

【請求項10】

前記メモリカードの入出力方式は、少なくともSDR(Single Data Rate)およびDDR(Double Data Rate)から選択されることを特徴とする請求項6に記載のコンピュータ端末。

【請求項11】

メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、前記カードクロックを前記メモリカードに出力するカードクロック出力部、前記転送クロックに同期して前記送信回路からの送信データを前記メモリカードへシリアル転送する送信インターフェースおよび前記転送クロックに同期して前記メモリカードからの受信データを前記受信回路へシリアル転送する受信インターフェースを含むインターフェース部を備えたホストコントローラを用いるカードアクセス方法であって、

前記メモリカードの入出力方式に関する設定情報を設定レジスタ回路に保持させ、

この設定情報に基づいて可変周波数クロック生成器により生成される転送クロックの周波数を制御することを特徴とするカードアクセス方法。

【請求項1】

メモリカードが装着されるカードスロットと、

送信データをシリアル転送形式に符号化する送信回路と、

受信データをシリアル転送形式から復号化する受信回路と、

カードクロックおよび転送クロックを生成する可変周波数クロック生成器と、

前記カードクロックを前記メモリカードに出力するカードクロック出力部と、

前記転送クロックに同期して前記送信回路からの送信データを前記メモリカードへシリアル転送する送信インターフェースおよび前記転送クロックに同期して前記メモリカードからの受信データを前記受信回路へシリアル転送する受信インターフェースを含むインターフェース部と、

前記メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて前記可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路と、を備えることを特徴とするホストコントローラ。

【請求項2】

前記設定レジスタ回路は前記可変周波数クロック生成器の制御において前記カードクロックに対する転送クロックの周波数倍率を前記メモリカードの入出力方式に適合するように変更することを特徴とする請求項1に記載のホストコントローラ。

【請求項3】

前記インターフェース部は前記送信インターフェースとして設けられる送信データライン群、前記受信インターフェースとして設けられる受信データライン群、および前記送信データライン群および前記受信データライン群をそれぞれ切り換える切換回路を含み、前記設定レジスタ回路は前記設定情報に基づいて前記切換回路を制御することを特徴とする請求項2に記載のホストコントローラ。

【請求項4】

前記送信回路は前記送信データを並列−直列変換する並列−直列変換器、および前記並列直列変換器によりビット単位に順次振り分けられる送信データをそれぞれシリアルパケットとして符号化して前記切換回路によって切り換えられた結果の送信データライン群に出力する複数の送信処理部を含み、前記受信回路は前記切換回路によって切換られた結果の受信データライン群からそれぞれシリアルパケットとして入力される前記受信データを復号化する複数の受信処理部、および前記受信処理部からビット単位に出力される受信データを直列−並列変換する直列−並列変換器を含むことを特徴とする請求項3に記載のホストコントローラ。

【請求項5】

前記メモリカードの入出力方式は、少なくともSDR(Single Data Rate)およびDDR(Double Data Rate)から選択されることを特徴とする請求項1に記載のホストコントローラ。

【請求項6】

メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、前記カードクロックを前記メモリカードに出力するカードクロック出力部、前記転送クロックに同期して前記送信回路からの送信データを前記メモリカードへシリアル転送する送信インターフェースおよび前記転送クロックに同期して前記メモリカードからの受信データを前記受信回路へシリアル転送する受信インターフェースを含むインターフェース部、並びに前記メモリカードの入出力方式に関する設定情報を保持し、この設定情報に基づいて前記可変周波数クロック生成器で生成される転送クロックの周波数を制御する設定レジスタ回路を含むホストコントローラと、

前記設定情報を前記設定レジスタ回路に設定すると共に送信データおよび受信データを処理するデータ処理回路と、を備えることを特徴とするコンピュータ端末。

【請求項7】

前記設定レジスタ回路は前記可変周波数クロック生成器の制御において前記カードクロックに対する転送クロックの周波数倍率を前記メモリカードの入出力方式に適合するように変更することを特徴とする請求項6に記載のコンピュータ端末。

【請求項8】

前記インターフェース部は前記送信インターフェースとして設けられる送信データライン群、前記受信インターフェースとして設けられる受信データライン群、および前記送信データライン群および前記受信データライン群をそれぞれ切り換える切換回路を含み、前記設定レジスタ回路は前記設定情報に基づいて前記切換回路を制御することを特徴とする請求項7に記載のコンピュータ端末。

【請求項9】

前記送信回路は前記送信データを並列−直列変換する並列−直列変換器、および前記並列直列変換器によりビット単位に順次振り分けられる送信データをそれぞれシリアルパケットとして符号化して前記切換回路によって切り換えられた結果の送信データライン群に出力する複数の送信処理部を含み、前記受信回路は前記切換回路によって切換られた結果の受信データライン群からそれぞれシリアルパケットとして入力される前記受信データを復号化する複数の受信処理部、および前記受信処理部からビット単位に出力される受信データを直列−並列変換する直列−並列変換器を含むことを特徴とする請求項8に記載のコンピュータ端末。

【請求項10】

前記メモリカードの入出力方式は、少なくともSDR(Single Data Rate)およびDDR(Double Data Rate)から選択されることを特徴とする請求項6に記載のコンピュータ端末。

【請求項11】

メモリカードが装着されるカードスロット、送信データをシリアル転送形式に符号化する送信回路、受信データをシリアル転送形式から復号化する受信回路、カードクロックおよび転送クロックを生成する可変周波数クロック生成器、前記カードクロックを前記メモリカードに出力するカードクロック出力部、前記転送クロックに同期して前記送信回路からの送信データを前記メモリカードへシリアル転送する送信インターフェースおよび前記転送クロックに同期して前記メモリカードからの受信データを前記受信回路へシリアル転送する受信インターフェースを含むインターフェース部を備えたホストコントローラを用いるカードアクセス方法であって、

前記メモリカードの入出力方式に関する設定情報を設定レジスタ回路に保持させ、

この設定情報に基づいて可変周波数クロック生成器により生成される転送クロックの周波数を制御することを特徴とするカードアクセス方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2011−13834(P2011−13834A)

【公開日】平成23年1月20日(2011.1.20)

【国際特許分類】

【出願番号】特願2009−156010(P2009−156010)

【出願日】平成21年6月30日(2009.6.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年1月20日(2011.1.20)

【国際特許分類】

【出願日】平成21年6月30日(2009.6.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]