ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムに関する。

【背景技術】

【0002】

近年、集積回路等に用いられているLSI(Large Scale Integrated Circuit)、ディスプレイ等に用いられているAM−TFT(Active Matrix Thin Film Transistor)などのデバイスについて、高集積化及び高密度化が繰り返されている。

前記デバイスの製法の代表例として、フォトリソグラフィー法が挙げられる。前記フォトリソグラフィー法では、アライナーを用いた場合、1μm〜10μmの微細パターンを容易に形成することが可能であり、ステッパーを用いた場合には、1μm以下の微細パターンを容易に形成することが可能である。

しかし、フォトリソグラフィー法では、設備が高価であり、工程数が多く、廃液を処理するなどの手間がかかるという問題がある。

【0003】

一方で、フォトリソグラフィー法以外のより簡便な手法として、低コスト化が可能な微細パターン形成技術が注目されている。これらの中でも、液滴吐出法(インクジェット法)、スクリーン印刷法に代表される印刷法は、少ない工程数、高い材料利用効率、及び低コスト化された設備に基づく、低コストかつ環境負荷が小さい微細パターン形成技術として期待されている。

特に、印刷法を用いたAM−TFTに関する技術は急速な進歩を遂げており、印刷法(反転印刷)を用いて、76ppiの有機TFTを作製する技術(非特許文献1参照)、マイクロコンタクトプリンティング法により200ppiの有機TFTを作製する技術(非特許文献2参照)、UV照射による表面エネルギー制御と液滴吐出法との組み合わせにより200ppiの有機TFTを作製する技術(非特許文献3参照)、などが報告されている。

【0004】

前記印刷法を用いたホール(ビアホール)形成技術としては、例えば、絶縁膜を溶解可能な溶媒を、液滴吐出法を用いて絶縁膜上に局所的に滴下することによって、ホールを形成する技術が提案されている(特許文献1参照)。

しかし、上記技術においては、溶媒に溶解した絶縁膜が残渣として残るという問題がある。更に、微細なホールを形成するためには、液滴吐出法による液滴の吐出量を数10pL以下にする必要があり、常温での蒸発速度が液滴に大きな影響を与え、ホール形成プロセスの再現性が低くなり、歩留まりが低下するという問題がある。

【0005】

また、ホール形成領域に液滴吐出法により撥液材料の液滴を塗布し、撥液領域を形成し、撥液領域以外の領域に絶縁膜材料溶液を塗布することによって、ホールを形成する技術が提案されている(特許文献2参照)。

しかし、上記技術においては、液滴吐出法によって、撥液領域以外にも絶縁膜材料溶液を塗布する必要があり、スループット及び膜厚均一性が低下するという問題がある。

【0006】

更に、ラインパターンで印刷した上で、飛び石状のドットパターンで印刷することにより、20μm〜45μm程度のホール(コンタクトホール)をスクリーン印刷により形成する技術が提案されている(特許文献3参照)。

しかし、前記技術においては、液ダレ等の制御が困難であり、ホール径のバラつきが大きく、ホール形成プロセスの再現性に欠くという問題がある。

【0007】

また、前記問題に加えて、印刷法を用いてホール形成を行う場合、一般的に、層間絶縁膜がμmオーダーの厚みとなって、アスペクト比が高くなり、微細パターン形成が困難となるという問題がある。

【0008】

以上より、印刷法を用いたホール形成方法では、解像度及びプロセス再現性を満足したプロセスは構築されていない。

【0009】

フォトリソグラフィー法及び印刷法以外の方法によるホール形成技術として、レーザードリル法が提案されている。前記レーザードリル法においては、CO2レーザー、YAGレーザーといったレーザー光を利用することにより、プリント配線基板等の多層配線で、露出開口端の最大直径が20μm程度のホールを形成することができる。

例えば、レーザーを照射することにより照射部を脱着もしくは蒸発させる、又はレーザーを照射した後、現像等の照射部を除去することにより、微細パターンを形成する技術が提案されている(特許文献4参照)。

しかしながら、前記技術においては、レーザー装置が高価であり、レーザー照射部を脱着又は蒸発させる場合、AM−TFTのような薄膜に対して、下部電極の形状を維持して、層間絶縁膜のみにホールを形成することができるプロセスマージンが小さいという問題がある。

【0010】

以上より、微細なホール(例えば、ビアホール)を、高い再現性で、効率よく、低コストで容易に形成することが望まれている。

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明は、従来における前記諸問題を解決し、以下の目的を達成することを課題とする。即ち、本発明は、プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムを提供することを目的とする。

【課題を解決するための手段】

【0012】

前記課題を解決するための手段としては、以下の通りである。即ち、

<1> 基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、

前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、

前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、

前記開口部が形成された絶縁膜を熱処理する熱処理工程と、

を含むことを特徴とするホール形成方法である。

<2> ピラー形成液が、樹脂と、溶媒とを含有する前記<1>に記載のホール形成方法である。

<3> ピラー形成液が、無機ナノ粒子と、溶媒とを含有する前記<1>に記載のホール形成方法である。

<4> ピラー形成液の付与が、静電吸引型液滴吐出法により行われる前記<1>から<3>のいずれかに記載のホール形成方法である。

<5> 絶縁膜形成材料を基材全面上に付与する前記<1>から<4>のいずれかに記載のホール形成方法である。

<6> 絶縁膜形成材料を基材上にラインアンドスペース状に付与し、その後絶縁膜形成材料の流動性を利用して基材全面上に付与する前記<1>から<5>のいずれかに記載のホール形成方法である。

<7> 第1の配線と、前記第1の配線を被覆する絶縁膜と、前記絶縁膜上に配置された第2の配線とを有し、前記第1の配線と前記第2の配線とが、前記絶縁膜に形成されたビアホールを介して接続された多層配線であって、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする多層配線である。

<8> 基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも2つ有し、これらのうちの1つの前記電界効果型トランジスタの前記ドレイン電極と、他の前記電界効果型トランジスタの前記ゲート電極とが、前記ゲート絶縁膜に形成されたビアホールを介して接続された回路を少なくとも1つ含む半導体装置であって、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする半導体装置である。

<9> 駆動信号に応じて光出力を制御する光制御素子と、

前記光制御素子を駆動する駆動回路と、を備える表示素子であって、

前記駆動回路が、

基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも2つ有し、これらのうちの1つの前記電界効果型トランジスタの前記ドレイン電極と、他の前記電界効果型トランジスタの前記ゲート電極とが、前記ゲート絶縁膜に形成されたビアホールを介して接続された回路を少なくとも1つ含む駆動回路であって、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする表示素子である。

<10> 駆動信号に応じて光出力を制御する光制御素子と、

前記光制御素子を駆動する駆動回路と、

前記光制御素子と前記駆動回路との間に設けられた層間絶縁膜と、

を備える表示素子であり、

前記駆動回路が、

基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも1つ有する駆動回路であって、

前記駆動回路の前記ドレイン電極と、前記光制御素子に含まれる少なくとも1つの電極とが、

前記層間絶縁膜に形成されたビアホールを介して接続されており、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする表示素子である。

<11> 光制御素子が、有機エレクトロルミネッセンス素子、エレクトロクロミック素子、液晶素子、電気泳動素子、及びエレクトロウェッティング素子の少なくともいずれかを有する前記<9>から<10>のいずれかに記載の表示素子である。

<12> マトリックス状に複数配置された前記<9>から<11>のいずれかに記載の表示素子と、

前記表示素子に電圧を個別に印加するための複数の配線と、

画像データに応じて、前記表示素子に印加された電圧を前記複数の配線を介して個別に制御する表示制御装置と、

を有することを特徴とする画像表示装置である。

<13> 前記<12>に記載の画像表示装置と、

表示する画像情報に基づいて画像データを作成し、該画像データを前記画像表示装置に出力する画像データ出力装置と、を有することを特徴とするシステムである。

【発明の効果】

【0013】

本発明によれば、従来における前記諸問題を解決し、前記目的を達成することができ、プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムを提供することができる。

【図面の簡単な説明】

【0014】

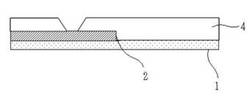

【図1A】図1Aは、本発明の多層配線の製造方法の一例を示す図である(その1)。

【図1B】図1Bは、本発明の多層配線の製造方法の一例を示す図である(その2)。

【図1C】図1Cは、本発明の多層配線の製造方法の一例を示す図である(その3)。

【図1D】図1Dは、本発明の多層配線の製造方法の一例を示す図である(その4)。

【図1E】図1Eは、本発明の多層配線の製造方法の一例を示す図である(その5)。

【図1F】図1Fは、本発明の多層配線の製造方法の一例を示す図である(その6)。

【図1G】図1Gは、本発明の多層配線の製造方法の一例を示す図である(その7)。

【図2A】図2Aは、本発明の半導体装置の製造方法の一例を示す図である(その1)。

【図2B】図2Bは、本発明の半導体装置の製造方法の一例を示す図である(その2)。

【図2C】図2Cは、本発明の半導体装置の製造方法の一例を示す図である(その3)。

【図2D】図2Dは、本発明の半導体装置の製造方法の一例を示す図である(その4)。

【図2E】図2Eは、本発明の半導体装置の製造方法の一例を示す図である(その5)。

【図3】図3は、トップゲート/ボトムコンタクトの半導体装置の一例を示す概略構成図である。

【図4】図4は、トップゲート/トップコンタクトの半導体装置の一例を示す概略構成図である。

【図5】図5は、ボトムゲート/ボトムコンタクトの半導体装置の一例を示す概略構成図である。

【図6】図6は、ボトムゲート/トップコンタクトの半導体装置の一例を示す概略構成図である。

【図7A】図7Aは、本発明の表示素子の製造方法の一例を示す図である(その1)。

【図7B】図7Bは、本発明の表示素子の製造方法の一例を示す図である(その2)。

【図7C】図7Cは、本発明の表示素子の製造方法の一例を示す図である(その3)。

【図7D】図7Dは、本発明の表示素子の製造方法の一例を示す図である(その4)。

【図7E】図7Eは、本発明の表示素子の製造方法の一例を示す図である(その5)。

【図7F】図7Fは、本発明の表示素子の製造方法の一例を示す図である(その6)。

【図7G】図7Gは、本発明の表示素子の製造方法の一例を示す図である(その7)。

【図8A】図8Aは、本発明の表示素子の製造方法の他の一例を示す図である(その1)。

【図8B】図8Bは、本発明の表示素子の製造方法の他の一例を示す図である(その2)。

【図8C】図8Cは、本発明の表示素子の製造方法の他の一例を示す図である(その3)。

【図8D】図8Dは、本発明の表示素子の製造方法の他の一例を示す図である(その4)。

【図8E】図8Eは、本発明の表示素子の製造方法の他の一例を示す図である(その5)。

【図8F】図8Fは、本発明の表示素子の製造方法の他の一例を示す図である(その6)。

【図9】図9は、本発明のシステムとしてのテレビジョン装置の一例を示す概略構成図である。

【図10】図10は、図9における画像表示装置を説明するための図である(その1)。

【図11】図11は、図9における画像表示装置を説明するための図である(その2)。

【図12】図12は、図9における画像表示装置を説明するための図である(その3)。

【図13】図13は、本発明の表示素子を説明するための図である。

【図14】図14は、有機EL素子の一例を示す概略構成図である。

【図15】図15は、表示制御装置を説明するための図である。

【図16】図16は、液晶ディスプレイを説明するための図である。

【図17】図17は、図16における表示素子を説明するための図である。

【図18A】図18Aは、実施例1の多層配線の製造方法を示す図である(その1)。

【図18B】図18Bは、実施例1の多層配線の製造方法を示す図である(その2)。

【図18C】図18Cは、実施例1の多層配線の製造方法を示す図である(その3)。

【図18D】図18Dは、実施例1の多層配線の製造方法を示す図である(その4)。

【図18E】図18Eは、実施例1の多層配線の製造方法を示す図である(その5)。

【図19A】図19Aは、比較例1のγ−ブチロラクトンに浸漬後の開口部の断面形状を示すグラフである。

【図19B】図19Bは、実施例1の絶縁膜の硬化後のビアホールの断面形状を示すグラフである。

【図19C】図19Cは、比較例1のγ−ブチロラクトンに浸漬後の開口部のSEM観察結果を示す図である。

【図19D】図19Dは、実施例1の絶縁膜の硬化後のビアホールのSEM観察結果を示す図である。

【図20】図20は、実施例1の多層配線における上部電極及び下部電極のI−V特性を示すグラフである。

【図21A】図21Aは、実施例17の有機EL表示素子の製造方法を示す図である(その1)。

【図21B】図21Bは、実施例17の有機EL表示素子の製造方法を示す図である(その2)。

【図21C】図21Cは、実施例17の有機EL表示素子の製造方法を示す図である(その3)。

【図21D】図21Dは、実施例17の有機EL表示素子の製造方法を示す図である(その4)。

【図21E】図21Eは、実施例17の有機EL表示素子の製造方法を示す図である(その5)。

【図21F】図21Fは、実施例17の有機EL表示素子の製造方法を示す図である(その6)。

【図22】図22は、静電吸引型液滴吐出装置の概要図の一例を示す図である。

【図23A】図23Aは、ピラーの形成工程の一例を示す図である(その1)。

【図23B】図23Bは、ピラーの形成工程の一例を示す図である(その2)。

【図23C】図23Cは、ピラーの形成工程の一例を示す図である(その3)。

【発明を実施するための形態】

【0015】

(ホール形成方法)

本発明のホール形成方法は、基材上に電子回路を作製するための製造プロセスであって、少なくとも、ピラー形成工程と、絶縁膜形成工程と、ピラー除去工程と、熱処理工程とを含み、更に必要に応じてその他の工程を含んでなる。

【0016】

<ピラー形成工程>

前記ピラー形成工程は、基材上にピラー形成液を付与してピラーを形成する工程である。

【0017】

<<基材>>

前記基材の形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

前記基材の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、ガラス基材、プラスチック基材などが挙げられる。

前記ガラス基材としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、無アルカリガラス、シリカガラスなどが挙げられる。

前記プラスチック基材としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、ポリカーボネート(PC)、ポリイミド(PI)、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)などが挙げられる。

なお、前記基材は、表面の清浄化及び密着性向上の点から、酸素プラズマ、UVオゾン、UV照射洗浄等の前処理が行われることが好ましい。

【0018】

<<ピラー>>

本発明において、前記ピラーとは、平面的でなく立体的に高さ方向に成長した立体構造物をいう。

前記ピラーの形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。前記ピラーの形状としては、例えば、円錐状、円柱状、角柱状などが挙げられる。

【0019】

前記ピラーの最大高さとしては、特に制限はなく、目的に応じて適宜選択することができるが、後述するピラー除去工程において形成される絶縁膜の平均厚みよりも高いことが好ましく、また、前記絶縁膜の平均厚みに対し、5倍以上が好ましく、例えば、0.5μm〜50μmが好ましく、1μm〜30μmがより好ましく、2μm〜10μmが特に好ましい。

前記ピラーの最大高さは、原子間力顕微鏡(AFM)によるピラーの三次元形状測定により得られた高さの最大値である。

【0020】

<<ピラー形成液(第1の形態)>>

前記ピラー形成液は、第1の形態では、樹脂及び溶媒を含有し、更に必要に応じてその他の成分を含有してなる。前記第1の形態のピラー形成液は、導電性溶液、又は高誘電率溶液であることが好ましい。具体的には、導電率が10×10−5S/m以上、又は誘電率が5以上であることが好ましい。

【0021】

−樹脂−

前記樹脂としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、熱硬化性樹脂、UV硬化型樹脂、熱可塑性樹脂などが挙げられる。ただし、前記熱硬化性樹脂、前記UV硬化型樹脂の場合には、ピラー形成後、硬化処理を行ってしまうと、後述するピラー除去工程で不具合が生じてしまうため、硬化処理を行わないで次工程に進むことが好ましい。

前記樹脂としては、例えば、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリエステル樹脂、ポリビニルフェノール樹脂、ポリビニルアルコール樹脂、ポリ酢酸ビニル樹脂、ポリスルホン樹脂、フッ素樹脂、これらの樹脂の共重合樹脂、又はポリマーアロイ、これらのプレポリマーなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。これらの中でも、熱可塑性アクリル樹脂、熱硬化性ポリイミド樹脂が特に好ましい。

前記樹脂の前記第1の形態のピラー形成液における含有量は、特に制限はなく、目的に応じて適宜選択することができるが、5質量%〜50質量%が好ましい。

【0022】

−溶媒−

前記溶媒としては、特に制限はなく、目的に応じて適宜選択することができるが、誘電率の高い極性溶媒であることが好ましい。前記誘電率としては、5以上であることが好ましく、10以上であることがより好ましい。

前記誘電率が高い極性溶媒としては、例えば、メタノール、エタノール、イソプロピルアルコール、n−ブタノール、n−ヘキサノール、n−オクタノール、エチレングリコール、ジエチレングリコール、プロピレングリコール、1,3−ブチレングリコール、ベンジルアルコール、2−メトキシエタノール、2−エトキシエタノール、2−ブトキシエタノール、ジプロピレングリコールモノメチルエーテル、アセトン、メチルエチルケトン、メチルイソブチルケトン、メチルn−ブチルケトン、メチルn−アミルケトン、アセトフェノン、シクロヘキサノン、γ−ブチロラクトン、炭酸プロピレン、ホルムアミド、N,N−ジメチルホルムアミド、N,N−ジメチルアセトアミド、1,3−ジメチル−2−イミダゾリジノン、N,N’−ジメチルプロピレンウレア、2−ピロリジノン、N−メチルピロリドン、ニトロメタン、ニトロベンゼン、メチルスルホキシドなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0023】

−その他の成分−

前記その他の成分としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、分散剤、安定化剤、硬化剤などが挙げられる。

【0024】

前記ピラー形成液としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、γ−ブチロラクトンで希釈した熱可塑性アクリル樹脂溶液(商品名:KH−CT−865、日立化成工業株式会社製)、γ−ブチロラクトンを溶媒とした熱硬化性ポリイミド樹脂(商品名:HPC−5030、日立化成工業株式会社製)、γ−ブチロラクトンで希釈した熱硬化性ポリイミド溶液(商品名:ユピコートFS−100L、宇部興産社製)などが挙げられる。

【0025】

<<ピラー形成液(第2の形態)>>

前記ピラー形成液は、第2の形態では、無機ナノ粒子と、溶媒とを含有し、更に必要に応じてその他の成分を含有してなる。前記第2の形態のピラー形成液は、導電性溶液、又は高誘電率溶液であることが好ましい。具体的には、導電率が10×10−5S/m以上、又は誘電率が5以上であることが好ましい。

【0026】

−無機ナノ粒子−

前記無機ナノ粒子としては、例えば、銀(Ag)、金(Au)、銅(Cu)等の金属ナノ粒子;ITO(Indium−Tin Oxide)、酸化スズ、酸化アンチモンドープ酸化スズ等の酸化物ナノ粒子などが挙げられる。これらの中でも、銀ナノ粒子、金ナノ粒子が特に好ましい。

前記無機ナノ粒子の平均粒径としては、特に制限はなく、目的に応じて適宜選択することができるが、5nm〜50nmが好ましい。

前記無機ナノ粒子としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、銀ナノ粒子(商品名:NPS−J、ハリマ化成社製、平均粒径12nm)、金ナノ粒子(商品名:NPG−J、ハリマ化成社製、平均粒径7nm)などが挙げられる。

【0027】

前記無機ナノ粒子の前記第2の形態のピラー形成液における含有量は、特に制限はなく、目的に応じて適宜選択することができるが、10質量%〜70質量%が好ましい。

【0028】

−溶媒−

前記溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、極性溶媒、無極性溶媒、フッ素系溶媒などが挙げられる。前記極性溶媒、前記無極性溶媒、及び前記フッ素系溶媒としては、後述する絶縁膜形成材料の溶媒と同様のものを用いることができる。

【0029】

−その他の成分−

前記その他の成分としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、分散剤、安定化剤などが挙げられる。

【0030】

<絶縁膜形成工程>

前記絶縁膜形成工程は、前記ピラーが形成された基材上に絶縁膜を形成する工程である。

前記絶縁膜形成工程においては、形成したピラーの形状を維持しながら絶縁膜形成材料を付与して絶縁膜を形成することが好ましい。

【0031】

<<絶縁膜形成材料>>

前記絶縁膜形成材料としては、有機絶縁材料、無機酸化物絶縁材料、及び有機無機ハイブリッド材料のいずれかを含有し、溶媒、更に必要に応じてその他の成分を含有してなる。

【0032】

−有機絶縁材料−

前記有機絶縁材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、熱硬化型樹脂、UV硬化型樹脂、熱可塑性樹脂等の樹脂などが挙げられる。

前記樹脂としては、例えば、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリエステル樹脂、ポリビニルフェノール樹脂、ポリビニルアルコール樹脂、ポリ酢酸ビニル樹脂、ポリスルホン樹脂、フッ素樹脂、シリコーン樹脂、これらの樹脂の共重合樹脂、又はポリマーアロイ、これらのプレポリマーなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。これらの中でも、熱可塑性フッ素樹脂、熱硬化性ポリイミド樹脂、熱硬化性アクリル樹脂、熱硬化性エポキシ樹脂、熱硬化性フェノール樹脂、熱硬化性シリコーン樹脂が特に好ましい。

【0033】

−無機酸化物絶縁材料−

前記無機酸化物絶縁材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、金属アルコキシド、有機金属錯体等から形成されるSiO2、Al2O3、などが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

前記無機酸化物絶縁材料としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、メチルイソブチルケトンを溶媒としたスピンオングラス材料(商品名:FOX(R)−16、東レ・ダウコーニング社製)などが挙げられる。

【0034】

−有機無機ハイブリッド材料−

前記有機無機ハイブリッド材料としては、特に制限はなく、目的に応じて適宜選択することができる。前記有機無機ハイブリッド材料とは、有機成分と無機成分とがナノレベルで混合された材料である。例えば、(1)ヒドロキシル基(−OH基)又はアルコキシ基(−OR基)を含有したアクリル樹脂又はエポキシ樹脂等とアルコキシシランとが混合された材料、(2)ヒドロキシル基(−OH基)を含有したシリコーン樹脂とアルコキシシランとが混合された材料、(3)ヒドロシリル基(−SiH)を含有したシリコーン樹脂とビニル基(−CH=CH2)を含有したアクリル樹脂又はエポキシ樹脂等とが混合された材料などが挙げられる。前記有機無機ハイブリッド材料の中でも、シリコーン樹脂を利用した材料を、ポリジメチルシロキサン(PDMS)系有機無機ハイブリッド材料と呼ぶ。

前記有機無機ハイブリッド材料としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、荒川化学社製コンポセラン、JSR社製グラスカなどが挙げられる。

【0035】

−溶媒−

前記絶縁膜形成材料は、前記ピラー形成工程で形成されたピラーを溶解しないことが必要である。即ち、前記絶縁膜形成材料の溶媒と、ピラー形成液の溶媒との組み合わせが重要となる。ただし、ピラー材料として無機ナノ粒子を用いた場合はこの限りではなく、絶縁膜形成材料に溶解されることは無いため、任意の絶縁膜形成材料を使用することができる。

【0036】

一方、前記ピラー材料として樹脂を用いた場合には、前記絶縁膜形成材料の溶媒と、ピラー形成液の溶媒の組み合わせを考慮する必要があり、前記ピラー形成液の溶媒が互いに相溶しない極性溶媒、無極性溶媒、及びフッ素系溶媒の3種の溶媒群から選ばれるいずれかの1種の溶媒であり、前記絶縁膜形成材料の溶媒が前記ピラー形成液の溶媒を含む溶媒群以外の2種の溶媒群から選ばれること、又は無溶媒であることが好ましい。

【0037】

前記極性溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、メタノール、エタノール、イソプロピルアルコール、n−ブタノール、n−ヘキサノール、n−オクタノール、エチレングリコール、ジエチレングリコール、プロピレングリコール、1,3−ブチレングリコール、ベンジルアルコール、2−メトキシエタノール、2−エトキシエタノール、2−ブトキシエタノール、ジプロピレングリコールモノメチルエーテル、アセトン、メチルエチルケトン、メチルイソブチルケトン、メチルn−ブチルケトン、メチルn−アミルケトン、アセトフェノン、シクロヘキサノン、γ−ブチロラクトン、炭酸プロピレン、ホルムアミド、N,N−ジメチルホルムアミド、N,N−ジメチルアセトアミド、1,3−ジメチル−2−イミダゾリジノン、N,N’−ジメチルプロピレンウレア、2−ピロリジノン、N−メチルピロリドン、ニトロメタン、ニトロベンゼン、メチルスルホキシドなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0038】

前記無極性溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、オクタン、ノナン、デカン、ウンデカン、ドデカン、トリデカン、テトラデカン、シクロヘキサン、3−メチルシクロヘキサン、ベンゼン、トルエン、キシレン、メシチレン、テトラリンなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0039】

前記フッ素系溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、テトラデカフルオロヘキサン、パーフルオロヘプタン、オクタデカフルオロオクタン、パーフルオロノナン、ヘキサフルオロベンゼン、オクタフルオロトルエン、オクタフルオロシクロペンテン、ヘプタコサフルオロトリブチルアミン、パーフルオロトリエチルアミン、パーフルオロトリブチルアミン、パーフルオロトリアミルアミン、パーフルオロ(1,3−ジメチルシクロヘキサン)、パーフルオロメチルシクロヘキサン、オクタデカフルオロデカヒドロナフタレン、パーフルオロ−2−メチルペンタンなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0040】

前記極性溶媒に可溶なピラー材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ポリイミド、ポリアミド、ポリエステル、ポリビニルフェノール、ポリビニルアルコール、ポリ酢酸ビニル、ポリスルホン、フッ素樹脂、前記樹脂の共重合樹脂又はポリマーアロイ、ポリジメチルシロキサン(PDMS)等の有機絶縁膜、金属アルコキシドや有機金属錯体等から形成されるSiO2、Al2O3等の無機酸化物絶縁膜、更にはそれらが混合された有機無機ハイブリッド膜などが挙げられる。

前記無極性溶媒に可溶なピラー材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、アクリル樹脂、ポリジメチルシロキサン(PDMS)、ポリスチレンなどが挙げられる。

前記フッ素系溶媒に可溶なピラー材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、フッ素樹脂などが挙げられる。

【0041】

前記樹脂を用いたピラー形成液の溶媒と前記絶縁膜形成材料の溶媒の組み合わせとしては、以下のものが好適に挙げられる。

(1)前記ピラー形成液の溶媒(γ−ブチロラクトン)と前記絶縁膜形成材料の溶媒(パーフルオロトリブチルアミン)

(2)前記ピラー形成液の溶媒(γ−ブチロラクトン)と前記絶縁膜形成材料の溶媒(n−テトラデカン、シクロへキサン、トルエン、キシレン)

【0042】

−その他の成分−

前記その他の成分としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、分散剤、安定化剤、硬化剤などが挙げられる。

【0043】

前記絶縁膜の形成方法としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、塗布対象面であるピラーが形成された基材上の全面に前記絶縁膜形成材料を塗布する塗布法などが挙げられる。

前記塗布法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、スピンコート法、ダイコート法、スリットコート法、スクリーン印刷法、ディスペンサー法、液滴吐出法、ノズルコーティング法などが挙げられる。これらの中でも、スループット及び膜厚の均一性の点で、全面塗布であるスピンコート法、ダイコート法、スリットコート法が特に好ましい。

また、スループットの観点から、ノズルコーティング法が好ましい。前記ノズルコーティング法は、前記絶縁膜形成材料を基材上にラインアンドスペース状に高速塗布する手法であり、塗布後の絶縁膜形成材料の流動性を利用して前記ピラー以外の基板全面を塗布することが可能である。

【0044】

前記絶縁膜の材質、形状、構造、大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

前記絶縁膜の膜厚としては、特に制限はなく、目的に応じて適宜選択することができるが、0.1μm〜20μmが好ましく、0.2μm〜10μmがより好ましく、0.4μm〜5μmが特に好ましい。

前記絶縁膜の膜厚は、例えば、触針式段差計などにより測定することができる。

【0045】

<ピラー除去工程>

前記ピラー除去工程は、前記ピラーを除去し、絶縁膜に開口部を形成する工程である。

前記絶縁膜形成工程後、ピラーが樹脂によって完全に被覆されていると、ピラーの除去が困難となるため、前記ピラー除去工程の前にAr、O2等のガスを用いたプラズマエッチングによりピラー上の樹脂をアッシングしてもよい。

【0046】

前記ピラーの除去方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(1)ピラーを溶解可能な溶液を用いて、ディップ等のプロセスによりピラーを溶解させて除去する方法、(2)熱処理によってピラーを気化させて除去する方法などが挙げられる。

前記(1)のピラーを溶解可能な溶液としては、ピラー材料が樹脂の場合は、前記ピラー形成液(インク)の溶媒、又はピラー形成液(インク)の溶媒と同等の極性を持つ溶媒を用いることができ、例えば、アセトン、γ−ブチロラクトン、N−メチルピロリドンなどが挙げられる。

前記ピラー材料が無機ナノ粒子の場合は、例えば、硝酸、塩酸、硫酸、リン酸、ホウ酸、酢酸等の酸が適宜混合されたエッチング液を用いることができる。

前記ピラー材料として、銀ナノ粒子を用いた場合には、エッチング液としては、例えば、リン酸、硝酸、酢酸などを用いることが好ましい。

【0047】

前記開口部としては、絶縁膜に形成され、下部電極部分へ貫通した孔である限り、特に制限はなく、目的に応じて適宜選択することができる。

前記開口部の形状としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、円形、四角形などが好ましい。また、前記開口部の形状が逆テーパー形状のとき、後述する熱処理工程により、テーパー形状を制御することが可能で、例えば、順テーパー形状に変形させることができる。

【0048】

前記開口部の露出開口端の最大直径としては、特に制限はなく、目的に応じて適宜選択することができるが、40μm以下が好ましく、20μm以下がより好ましい。前記最大直径が前記より好ましい範囲内であると、高密度の電子デバイス等で利用可能となる点で有利である。

前記開口部の露出開口端間の最大直径は、例えば、光学顕微鏡を用いて測定することができる。

【0049】

<熱処理工程>

前記熱処理工程は、前記開口部が形成された絶縁膜を熱処理する工程である。

前記熱処理工程により、絶縁膜の開口部がテーパー状に整形される。

【0050】

−熱処理−

前記絶縁膜を熱処理することによって、開口部周縁の突起部において絶縁膜軟化による形状変化が起こる(熱ダレ)。この熱ダレにより、なだらかな傾斜の順テーパー状ホールを形成して、前記順テーパー状ホールに導電性材料を充填しやすくできる。

前記絶縁膜が熱可塑性材料からなる場合、前記絶縁膜のガラス転移点等に起因する軟化温度を超えた温度をかけることにより容易に軟化現象が見られ、熱ダレ現象を起こすことが可能である。

また、前記絶縁膜が熱硬化性材料からなる場合、前記絶縁膜形成材料の硬化開始温度以下の温度領域においては温度上昇に伴う絶縁膜の粘度低下の現象が起きる。その温度領域を利用して、熱ダレ現象を起こすことが可能である。具体的には、(1)前記絶縁膜形成材料を硬化させる前に、硬化開始温度以下の温度で熱処理することで熱変形させる方法、(2)前記絶縁膜形成材料の処理温度の室温から硬化温度までの昇温速度を、特定の昇温速度、例えば、1℃/分間の速度で制御し、硬化温度に達するまでの間に熱変形させる方法などが挙げられる。

また、前記絶縁膜がUV硬化性材料の場合においても、絶縁膜材料の硬化前の段階で所望の温度で熱処理を行うことで、熱ダレ現象を起こすことが可能である。

【0051】

前記熱処理における加熱温度としては、特に制限はなく、前記絶縁膜形成材料の分子構造、分子量等によって決定される粘度特性に応じて適宜選択することができるが、100℃以上500℃以下が好ましく、120℃以上450℃以下がより好ましい。前記加熱温度が、100℃未満であると、電子デバイス等で使用した場合、水分が残存し、絶縁性に不具合が生じることがあり、500℃を超えると、高温であることから他の材料への影響が大きくなり、使用可能な材料が大きく制限されてしまうことがある。

なお、前記熱硬化性材料の熱硬化、前記熱可塑性材料の熱処理による溶媒除去等が必要な場合、前記熱処理にて同時に行ってもよく、別途行ってもよい。

【0052】

前記開口部が熱処理により成形されたホールの形状としては、特に制限はなく、目的に応じて適宜選択することができるが、ホールに導電性材料を充填しやすくできる点で、順テーパー形状であることが好ましい。

【0053】

前記ホールのテーパー角としては、特に制限はなく、目的に応じて適宜選択することができるが、60°以下であることが好ましく、45°以下であることがより好ましい。また、前記ホールのテーパー角は、順テーパー形状が好ましいため、前記ホールのテーパー角は、正の値となる。

ここで、前記ホールのテーパー角とは、開口部を有するホールの内壁面が、前記ホールの開口端から前記ホールの底面に向かって前記ホールの最大開口径が小さくなるように傾斜したテーパー面と水平な底面とのなす角を意味する。

前記テーパー角が、60°を超えると、電子デバイス等で使用した場合、上部電極の断線、又は、ホール充填時の気泡の混入といった不具合が見られることがある。

【0054】

ここで、前記ホールのテーパー角は、例えば、1断面のプロファイルをAFM(Atomic Force Microscope;原子間力顕微鏡)(Pacific Nanotechnology社製)にて解析することにより、測定することができる。

【0055】

<その他の工程>

前記その他の工程としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、後述する多層配線の製造方法で説明する、基材配置工程、第1の配線形成工程、第2の配線形成工程などが挙げられる。

【0056】

本発明のホール形成方法は、フォトリソグラフィー法に対してプロセスが簡便であり、絶縁膜をスピンコートなどの全面塗布によって形成することが可能であるため、高スループットなプロセスであり、コストダウンが可能である。また、静電吸引型液滴吐出法によりアスペクト比の高いピラーを形成することによって、膜厚1.5μmの層間絶縁膜に対して最大直径15μmの微細な順テーパー状ホールを形成することができる。

【0057】

ここで、本発明のホール形成方法について、図面を用いて詳細に説明する。

本発明のホール形成方法において、開口部は、例えば、図1A〜図1Fに示すように、ピラー形成工程において、基材(第1の配線2)1上のホール(ビアホール)形成領域2にピラー3を形成し(図1C)、絶縁膜形成工程において、ピラー3が形成された基材(第1の配線2)上に絶縁膜4を形成し(図1D)、ピラー除去工程において、ピラー3を除去することにより形成される(図1E)。

次に、熱処理工程において、開口部周縁の突起部において絶縁膜軟化による形状変化が起こる(熱ダレ)。その熱ダレにより、テーパー形状を制御することが可能であり、例えば、順テーパー状ホールが形成される(図1F)。

【0058】

ここで、前記ピラー形成工程に用いる静電気吸引型液滴吐出法について、特許第3975272号公報、特許第4590493号公報を参照し、図面に基づき説明する。

ピラー形成液(インク)が充填され、かつ内側に電極が設けられたノズル及び基板間に所望の電圧を印加することにより吐出する静電吸引型液滴吐出法において、前記ノズル内径を少なくとも8μm以下、ノズル−基板間距離を少なくとも100μm以下とすることにより、ノズル−基板間の電界よりも強い局所的な電界集中をノズル先端に発生させ、液滴をノズルから分離・吐出させる吐出方法である。

前記方法によれば、前記ノズル径が小さくなるほど吐出に必要な臨界電圧を小さくすることが可能であり、更にノズルから分離した液滴は空気抵抗に耐え得る高い運動エネルギーを付与されるため、径の小さい液滴でも基板に着弾させることができる。

前記静電吸引型液滴吐出法を用いることで、前記ピラーを形成することが可能である。

【0059】

本発明における静電吸引型液滴吐出法によるピラー形成の原理及び方法について説明する。

前記静電吸引型液滴吐出法は、上述したように、内径が8μm以下のノズルを用いて液滴吐出することが可能であり、現在実用化されているインクジェット方式(ピエゾ方式、サーマル方式)では困難であった1pL以下の微小液滴の吐出が可能である。前記微細液滴は表面張力の作用、比表面積の高さなどにより、極めて蒸発速度が早いため、速乾性がある。また、加えられた電界は、先行して基材に付着した液滴が固化して形成された構造物の先端部に作用し、電界集中が起きる。このような微小液滴の速乾性、電界集中により、ピラーを作製することが可能となる。

【0060】

以下に、ピラーの形成方法について更に詳細に説明する。まず、静電吸引型液滴吐出装置の概要図の一例を図22に示す。

【0061】

この図22の静電吸引型液滴吐出装置は、ノズル1001、ピラー形成液(インク)1002、基板1003、ステージ1004、電極1005、高電圧アンプ1006、ファンクションジェネレータ1007、及びコントローラ(PC)1008によって構成されている。

ここで、前記電極1005が、前記ノズル1001の内部に挿入されてピラー形成液(インク)1002と接している図を示している。その構造は、特に制限はなく、目的に応じて適宜選択することができ、例えば、少なくともピラー形成液(インク)1002と電極1005が接触していることが好ましい。

前記ノズル1001としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、ガラス等の絶縁性材料で形成されることが好ましい。前記ノズル1001の内径としては、特に制限はなく、目的に応じて適宜選択することができ、8μm以下が好ましい。前記ノズル1001と基板1003の間の距離は、100μm以下が好ましい。前記ステージ1004は、アースに接続されており、前記電極1005に対して高電圧アンプ1006、ファンクションジェネレータ1007、コントローラ(PC)1008を用いて所望の電圧を印加することにより、前記ピラー形成液(インク)1002は、前記ノズル1001から分離・吐出され、前記基板1003に着弾する。

【0062】

前記電極1005に印加する電圧の波形については、特に制限はなく、目的に応じて適宜選択することができ、例えば、方形波、サイン波、三角波等を含む任意の交流で与えてもよいし、直流でもよく、また、交流波と直流を組み合わせた波形でもよい。周波数、電圧絶対値についても、特に制限はなく、目的に応じて適宜選択することができ、例えば、ピラー形成液(インク)1002に対して最適な値を用いることができる。

【0063】

前記ピラー形成液(インク)1002は、特に制限はなく、目的に応じて適宜選択することができるが、例えば、導電性溶液、又は高誘電率溶液であることが好ましい。具体的には、導電率が10×10−5S/m以上、又は誘電率が5以上であることが好ましい。

【0064】

前記静電吸引型液滴吐出装置を用いて基板1003上にピラーを形成する過程の一例について、図23A〜図23Cを用いて説明するが、これらの過程に限定されることはない。

図23A〜図23Cでは、どの場合においても、まず、初期段階にドット形状の初期構造体1011が形成される。その後、ピラー形成液(インク)を吐出し続けることによって、図23Aでは、初期構造体1011全体に濡れ広がりながら高さ方向に成長し、ドット形状を有するピラー1012が形成される。図23Bでは、前記初期構造体1011の頂点付近に電界が集中することにより急激に高さ方向に構造体が成長し、図23Aと比較してシャープな形状を有するピラー1013が形成される。更に、図23Cでは、前記初期構造体の上に第2の構造体1014が形成され、更に前記第2の構造体1014の頂点付近に電界が集中することにより、シャープな形状を有するピラー1015が形成される。吐出する時間については、特に制限はなく、目的に応じて適宜選択することができ、任意の時間を選択することができる。また、一度にピラーを形成する必要はなく、複数の吐出に分けて形成してもよい。

これらの過程により形成されたピラーを用いることにより、アスペクト比の高いホール(ビアホール)を得ることが可能となる。

【0065】

(多層配線及び多層配線の製造方法)

以下、本発明の多層配線を、製造方法を通じて説明する。

本発明の多層配線の製造方法は、少なくとも、基材配置工程と、第1の配線形成工程と、ピラー形成工程と、絶縁膜形成工程と、ピラー除去工程と、熱処理工程と、第2の配線形成工程とを含んでなり、必要に応じて、その他の工程を含む。

該方法により、図1Gに示すような、基材1上に形成された第1の配線2が、絶縁膜4に形成されたビアホールを介して、第2の配線5と導通した多層配線が製造される。

【0066】

<基材配置工程>

前記基材配置工程は、基材を配置する工程である(図1A)。

【0067】

−基材−

前記基材は、前述したホール形成方法で説明した基材と同様である。

【0068】

<第1の配線形成工程>

前記第1の配線形成工程は、基材上に第1の配線を形成する工程である。例えば、図1Bに示すように、例えば、基材1上に第1の配線2が形成される。

【0069】

−第1の配線−

前記第1の配線の形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

前記第1の配線の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、Mo、Al、Ag、Cu等の金属乃至合金;ITO、ATO等の透明導電性酸化物;ポリエチレンジオキシチオフェン(PEDOT)、ポリアニリン(PANI)等の有機導電体などが挙げられる。

前記第1の配線の形成方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)スパッタ法、ディップコーティング法等による成膜後、フォトリソグラフィーによってパターニングする方法、(ii)インクジェット、ナノインプリント、グラビア等の印刷プロセスによって、所望の形状を直接成膜する方法などが挙げられる。

【0070】

<ピラー形成工程>

前記ピラー形成工程は、第1の配線上のビアホール形成領域に、ピラーを形成する工程である。図1Cに示すように、例えば、第1の配線2上にピラー3が形成される。

【0071】

−ピラー−

前記ピラーは、前述したホール形成方法で説明したピラーと同様である。

【0072】

<絶縁膜形成工程>

前記絶縁膜形成工程は、ピラーが形成された第1の配線上に絶縁膜を形成する工程である。図1Dに示すように、例えば、ピラー3が形成された第1の配線2上に絶縁膜4が形成される。

【0073】

−絶縁膜−

前記絶縁膜は、前述したホール形成方法で説明した絶縁膜と同様である。

【0074】

<ピラー除去工程>

前記ピラー除去工程は、ピラーを除去する工程である。図1Eに示すように、例えば、絶縁膜4に、周縁に突起部7が形成された開口部が形成される。

【0075】

<熱処理工程>

前記熱処理工程は、絶縁膜を熱処理する工程である。熱処理によって、図1Fに示すように、開口部周縁の突起部の熱ダレにより、テーパー形状を制御することが可能で、例えば、順テーパー状ホールが形成される。

前記熱処理の方法としては、特に制限はなく、目的に応じて適宜選択することができる。

前記絶縁膜の材質が、硬化温度が軟化温度より高い樹脂である場合、ビアホールのテーパー形状が、逆テーパーからなだらかな順テーパーへと変形する。これにより、後述する第2の配線形成工程において、第2の配線の断線及びビアホール内への気泡の侵入などを回避することができ、信頼性を向上させることができる。

なお、熱硬化性樹脂の熱硬化や、熱可塑性樹脂の熱処理による溶媒除去等、別の目的での熱処理が必要な場合、前記熱処理にて同時に行ってもよく、別途行ってもよい。

【0076】

<第2の配線形成工程>

前記第2の配線形成工程は、第1の配線及び絶縁膜上に第2の配線を形成する工程である。図1Gに示すように、例えば、第1の配線2及び絶縁膜4上に第2の配線5が形成される。

前記第2の配線の形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

前記第2の配線の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、Mo、Al、Ag、Cu等の金属乃至合金;ITO、ATO等の透明導電性酸化物;ポリエチレンジオキシチオフェン(PEDOT)、ポリアニリン(PANI)等の有機導電体などが挙げられる。

前記第2の配線の形成方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)スパッタ法、ディップコーティング法等による成膜後、フォトリソグラフィーによってパターニングする方法、(ii)インクジェット、ナノインプリント、グラビア等の印刷プロセスによって、所望の形状を直接成膜する方法などが挙げられる。

【0077】

(半導体装置及び半導体装置の製造方法)

本発明の半導体装置は、

基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも2つ有し、これらのうちの一の前記電界効果型トランジスタの前記ドレイン電極と、他の前記電界効果型トランジスタの前記ゲート電極とが、前記ゲート絶縁膜に形成されたビアホールを介して接続された回路を少なくとも1つ含む半導体装置であって、

前記ビアホールが本発明の前記ホール形成方法により形成されたことを特徴とする。

【0078】

以下、本発明の半導体装置を、半導体装置の製造方法を通じて説明する。

本発明の半導体装置の製造方法は、少なくとも、基材配置工程と、第1の電極形成工程と、半導体層形成工程と、ピラー形成工程と、絶縁膜形成工程と、ピラー除去工程と、熱処理工程と、第2の電極形成工程とを含み、更に必要に応じて、その他の工程を含んでなる。

【0079】

前記半導体装置の製造方法により、例えば、図2Eに示すように、基材11上に形成された第1のドレイン電極13が、半導体層16,17と、ゲート電極20,21との間に設けられたゲート絶縁膜18に形成されたビアホールを介して、第2のゲート電極21と導通した半導体装置10が製造される。半導体装置10は、電界効果型トランジスタを2つ含んでなり、2トランジスタ1キャパシタ構造である。図2Eにおいては、便宜上、第2のソース電極14と、第2のゲート電極21との間にキャパシタが形成されているが、実際にはキャパシタ形成箇所は限定されず、適宜必要な容量のキャパシタを必要な箇所に設計しつつ形成することができる。

前記半導体装置としての電界効果型トランジスタとしては、特に制限はなく、目的に応じて適宜選択することができ、例えば、トップゲート/ボトムコンタクト型(図3)、トップゲート/トップコンタクト型(図4)、ボトムゲート/ボトムコンタクト型(図5)、ボトムゲート/トップコンタクト型(図6)などが挙げられる。

なお、図3〜図6中、22は基材、23はソース電極、24はドレイン電極、25は半導体層、26はゲート絶縁膜、27はゲート電極をそれぞれ表す。

【0080】

<基材配置工程>

前記基材配置工程は、基材を配置する工程である(図2A参照)。

前記基材としては、前述した多層配線の基材と同様である。

【0081】

<第1の電極形成工程>

前記第1の電極形成工程は、基材上に第1の電極を形成する工程である(図2A参照)。例えば、図2Aに示すように、基材11上に、第1のソース電極12、第1のドレイン電極13、第2のソース電極14、及び第2のドレイン電極15が形成される。

ソース電極12,14、及びドレイン電極13,15は、電流を取り出すためのものである。

【0082】

−第1の電極−

前記第1の電極の形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

【0083】

前記第1の電極の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、Mo、Al、Ag、Cu等の金属乃至合金;ITO、ATO等の透明導電性酸化物;ポリエチレンジオキシチオフェン(PEDOT)、ポリアニリン(PANI)等の有機導電体などが挙げられる。

【0084】

前記第1の電極の形成プロセスとしては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)スパッタ法、ディップコーティング法等による成膜後、フォトリソグラフィーによってパターニングする方法、(ii)インクジェット、ナノインプリント、グラビア等の印刷プロセスによって、所望の形状を直接成膜する方法などが挙げられる。

【0085】

<半導体層形成工程>

前記半導体層形成工程は、基材及び第1の電極上に、第1及び第2の半導体層を形成する工程である(図2A参照)。例えば、図2Aに示すように、基材11及び第1のソース電極12/ドレイン電極13上に第1の半導体層16が形成され、基材11及び第2のソース電極14/ドレイン電極15上に第2の半導体層17が形成される。

【0086】

−半導体層−

前記半導体層の形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

【0087】

前記半導体層の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、多結晶シリコン(p−Si)、アモルファスシリコン(a−Si)、In−Ga−Zn−O等の酸化物半導体;ペンタセン等の有機半導体などが挙げられる。

【0088】

前記半導体層の形成方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、スパッタ法、パルスレーザーデポジッション(PLD)法、CVD法、ALD法等の真空プロセス;ディップコーティング、インクジェット、ナノインプリント等の印刷法などが挙げられる。

【0089】

<ピラー形成工程>

前記ピラー形成工程は、第1の電極上のビアホール形成領域に、ピラーを形成する工程である(図2A参照)。例えば、図2Aに示すように、第1のドレイン電極13上のビアホール形成領域にピラー19が形成される。

前記ピラーは、前述した多層配線のピラーと同様である。

【0090】

<絶縁膜形成工程>

前記絶縁膜形成工程は、ピラーが形成された第1の電極上に絶縁膜を形成する工程である(図2B参照)。例えば、図2Bに示すように、ピラー19が形成された第1のドレイン電極13上にゲート絶縁膜18が形成される。

前記絶縁膜は、前述した多層配線の絶縁膜と同様である。

【0091】

<ピラー除去工程>

前記ピラー除去工程は、ピラーを除去して、絶縁膜に開口部を形成する工程である(図2C参照)。例えば、図2Cに示すように、第1のドレイン電極13上に形成されたゲート絶縁膜18に開口部が形成される。

【0092】

前記ピラーの除去方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)溶媒浸漬によってピラーを溶解させる方法、(ii)熱処理によってピラーを気化させる方法などが挙げられる。ここで、前記ピラーを除去するためには、絶縁膜に被覆されていないピラー領域が必要である。

【0093】

前記ピラーを除去した後、残渣が発生した場合、UV−O3処理及びプラズマ処理のいずれかによるアッシングによって残渣の除去が可能である。前記プラズマ処理の使用ガスとしては、特に制限はなく、目的に応じて適宜選択することができ、例えば、O2、Ar、CF4、CHF3などが挙げられる。

【0094】

<熱処理工程>

前記熱処理工程は、絶縁膜を熱処理する工程である(図2D参照)。熱処理によって、開口部周縁の突起部の熱ダレによりテーパー形状を制御することが可能であり、例えば、図2Dに示すように、順テーパー状ホールが形成される。

なお、熱硬化性樹脂の熱硬化や、熱可塑性樹脂の熱処理による溶媒除去等、別の目的での熱処理が必要な場合、前記熱処理にて同時に行ってもよく、別途行ってもよい。

【0095】

<第2の電極形成工程>

前記第2の電極形成工程は、絶縁膜上に第2の電極を形成する工程である(図2E参照)。例えば、図2Eに示すように、ゲート絶縁膜18上に第2の電極20,21が形成される。

【0096】

−第2の電極−

前記第2の電極としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、第1のゲート電極20(図2E)、第2のゲート電極21(図2E)などが挙げられる。前記第1及び第2のゲート電極20,21は、ゲート電圧を印加する。

前記第2の電極の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、Mo、Al、Ag、Cu等の金属乃至合金;ITO、ATO等の透明導電性酸化物;ポリエチレンジオキシチオフェン(PEDOT)、ポリアニリン(PANI)等の有機導電体などが挙げられる。

前記第2の電極の形成プロセスとしては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)スパッタ法、ディップコーティング法等による成膜後、フォトリソグラフィーによってパターニングする方法、(ii)インクジェット、ナノインプリント、グラビア等の印刷プロセスによって、所望の形状を直接成膜する方法などが挙げられる。

【0097】

(表示素子)

本発明の表示素子は、少なくとも、光制御素子と、前記光制御素子を駆動する駆動回路とを有してなり、更に必要に応じて、その他の部材を有してなる。

【0098】

<光制御素子>

前記光制御素子としては、駆動信号に応じて光出力を制御する素子である限り、特に制限はなく、目的に応じて適宜選択することができ、例えば、有機エレクトロルミネッセンス(EL)素子、エレクトロクロミック(EC)素子、液晶素子、電気泳動素子、エレクトロウェッティング素子などが挙げられる。

【0099】

<駆動回路>

前記駆動回路としては、前記ホール形成方法によって形成されたビアホールを有する限り、特に制限はなく、目的に応じて適宜選択することができる。

【0100】

<その他の部材>

前記その他の部材としては、特に制限はなく、目的に応じて適宜選択することができる。

【0101】

(表示素子及び表示素子の製造方法)

本発明の第1の表示素子は、

駆動信号に応じて光出力を制御する光制御素子と、

前記光制御素子を駆動する駆動回路と、を備える表示素子であって、

前記駆動回路は、

基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも2つ有し、これらのうちの一の前記電界効果型トランジスタの前記ドレイン電極と、他の前記電界効果型トランジスタの前記ゲート電極とが、前記ゲート絶縁膜に形成されたビアホールを介して接続された回路を少なくとも1つ含む駆動回路であって、

前記ビアホールが本発明の前記ホール形成方法により形成されたことを特徴とする。

前記第1の表示素子は、例えば、図7Gに示すように、半導体装置10と、有機EL素子350を組み合わせることにより、表示素子30を作製することができる。

【0102】

本発明の第1の表示素子の製造方法について説明する。

本発明の第1の表示素子の製造方法は、

少なくとも、基材配置工程と、第1の電極形成工程と、半導体層形成工程と、第1のピラー形成工程と、第1の絶縁膜形成工程と、第1のピラー除去工程と、第1の熱処理工程と、第2の電極形成工程と、表示層形成工程と、第3の電極形成工程とを含み、更に必要に応じて、その他の工程を含んでなる。

該方法により、図7Gに示すような、基材31上に形成された第1のドレイン電極33が、ゲート絶縁膜38に形成されたビアホールを介して、第2のゲート電極42と導通し、基材31上に形成された第2のドレイン電極35が、ゲート絶縁膜38に形成されたビアホールを介して、画素電極43と導通し、前記画素電極43上に有機EL層、上部電極が形成された、低コストの表示素子30が製造される。

表示素子30の駆動回路は、少なくとも2つ以上の電界効果型トランジスタを有しており、2トランジスタ1キャパシタ構造、5トランジスタ2キャパシタ構造等の複数の電界効果型トランジスタ/キャパシタを有する駆動回路が適宜利用できる。

また、表示層については、有機EL層、エレクトロクロミック層、電気泳動層、エレクトロウェッティング層等を適宜利用することができる。

また、図7E〜図7Gにおいては、便宜上、第2のソース電極34と第2のゲート電極42との間や、第2のドレイン電極35と画素電極43との間にキャパシタが形成されているように見えるが、実際にはキャパシタ形成箇所は限定されず、適宜必要な容量のキャパシタを必要な箇所に設計しつつ形成することができる。

【0103】

<基材配置工程>

前記基材配置工程は、基材を配置する工程である(図7A参照)。

前記基材は、前述した多層配線の基材と同様である。

【0104】

<第1の電極形成工程>

前記第1の電極形成工程は、基材上に第1の電極を形成する工程である(図7A参照)。例えば、図7Aに示すように、基材31上に、第1のソース電極32/ドレイン電極33、及び、第2のソース電極34/ドレイン電極35が形成される。

前記第1の電極の材質、形状、構造、大きさ、及び形成方法は、前述した半導体装置の第1の電極と同様である。

【0105】

<半導体層形成工程>

前記半導体層形成工程は、基材及び第1の電極上に、半導体層を形成する工程である(図7A参照)。例えば、図7Aに示すように、基材31、第1のソース電極32、及び第1のドレイン電極33上に第1の半導体層36が形成され、基材31、第2のソース電極34、及び第2のドレイン電極35上に第2の半導体層37が形成される。

前記半導体層の材質、形状、構造、大きさ、及び形成方法は、前述した半導体装置の半導体層と同様である。

【0106】

<ピラー形成工程>

前記ピラー形成工程は、第1の電極上のビアホール形成領域に、ピラーを形成する工程である(図7A参照)。例えば、図7Aに示すように、第1のドレイン電極33上のビアホール形成領域にピラー39が形成され、第2のドレイン電極35上のビアホール形成領域にピラー40が形成される。

【0107】

<絶縁膜形成工程>

前記第1の絶縁膜形成工程は、基材、半導体層及び第1の電極上に第1の絶縁膜を形成する工程である(図7B参照)。例えば、図7Bに示すように、基材31、半導体層36,37、ソース電極32,34、及びドレイン電極33,35上に、ゲート絶縁膜38が形成される。

【0108】

<第1のピラー除去工程>

前記ピラー除去工程は、ピラーを除去して、絶縁膜に開口部を形成する工程である(図7C参照)。例えば、図7Cに示すように、ゲート絶縁膜38に開口部が形成される。

【0109】

<第1の熱処理工程>

前記第1の熱処理工程は、第1の絶縁膜を熱処理する工程である(図7C参照)。熱処理によって、開口部周縁の突起部の熱ダレにより、テーパー形状を制御することが可能であり、例えば、図7Dに示すように、順テーパー状ホールが形成される。

なお、熱硬化性樹脂の熱硬化や、熱可塑性樹脂の熱処理による溶媒除去等、別の目的での熱処理が必要な場合、前記熱処理にて同時に行ってもよく、別途行ってもよい。

【0110】

<第2の電極形成工程>

前記第2の電極形成工程は、第1の絶縁膜上に第2の電極を形成する工程である(図7E参照)。例えば、図7Eに示すように、ゲート絶縁膜38上に第1及び第2のゲート電極41,42、更には画素電極43が形成される。

前記第2の電極の材質、形状、構造、大きさ、及び形成方法は、前述した多層配線の第2の電極と同様である。

【0111】

<隔壁形成工程>

前記隔壁形成工程は、画素電極43上に表示のための開口部以外の領域に、隔壁44を形成する工程である。

様々な材料、プロセス、パターニング方法が利用可能である。前記材料としては、例えば、SiO2等の既に広く量産に利用されている材料;ポリイミド(PI)、アクリル樹脂、フッ素系樹脂等の有機材料などが利用できる。前記プロセスとしては、例えば、スパッタ法、化学気相蒸着(CVD)等の真空成膜法やスピンコート法、ダイコート等の溶液プロセスによる成膜後、フォトリソグラフィーによるパターンニング、インクジェット、ノズルプリンター等の印刷プロセスによって、所望の形状を直接成膜することも可能である。

【0112】

<表示層形成工程>

前記表示層形成工程は、画素電極43上に、表示層45を形成する工程である(図7G参照)。

前記表示層としては、有機EL層、エレクトロクロミック層、電気泳動層、エレクトロウェッティング層等を適宜利用することができ、プロセスについても、特に制限はなく、目的に応じて適宜選択できる。

【0113】

<第3の電極形成工程>

前記第3の電極形成工程は、前記表示層45上に、上部電極46を形成する工程である(図7G参照)。

前記第3の電極の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、Mo、Al、Ag、Cu等の金属乃至合金;ITO、ATO等の透明導電性酸化物;ポリエチレンジオキシチオフェン(PEDOT)、ポリアニリン(PANI)等の有機導電体などが挙げられる。

前記第3の電極の形成プロセスとしては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)真空蒸着法、スパッタ法、ディップコーティング法等による成膜後、必要に応じてフォトリソグラフィーによってパターニングする方法、(ii)インクジェット、ナノインプリント、グラビア等の印刷プロセスによって、所望の形状を直接成膜する方法などが挙げられる。

これらの工程により、低コストで表示素子30を作製することができる。

【0114】

(第2の表示素子)

本発明の第2の表示素子は、

駆動信号に応じて光出力を制御する光制御素子と、

前記光制御素子を駆動する駆動回路と、

前記光制御素子と前記駆動回路との間に設けられた層間絶縁膜と、

を備える表示素子であり、

前記駆動回路が、

基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも1つ有する駆動回路であって、

前記駆動回路の前記ドレイン電極と、前記光制御素子に含まれる少なくとも1つの電極とが、

層間絶縁膜に形成されたビアホールを介して接続されており、

前記ビアホールが本発明の前記ホール形成方法により形成されたことを特徴とする。

【0115】

本発明の第2の表示素子の製造方法について説明する。

本発明の第2の表示素子の製造方法は、少なくとも、基材配置工程と、第1の電極形成工程と、第1の絶縁膜形成工程と、第2の電極形成工程と、半導体層形成工程と、ピラー形成工程と、第2の絶縁膜形成工程と、ピラー除去工程と、熱処理工程と、第3の電極形成工程と、表示層形成工程と、第四の電極形成工程とを含んでなり、必要に応じて、その他の工程を含む。

該方法により、図8Fに示すような、ゲート絶縁膜53上に形成されたドレイン電極55が、層間絶縁膜57に形成されたビアホールを介して、画素電極59と導通し、更に表示層60、上部電極61が形成された低コストの表示素子50が製造される。

表示素子50に含まれる駆動回路は、電界効果型トランジスタの数が1つであってもよく、2トランジスタ1キャパシタ構造、5トランジスタ2キャパシタ等の複数の電界効果型トランジスタ/キャパシタを有する半導体装置を有するものであってもよい。また、表示素子は、有機エレクトロルミネッセンス(EL)素子、エレクトロクロミック素子、液晶素子、エレクトロウェッティング素子等のその他の表示素子であってもよい。

【0116】

<基材配置工程>

前記基材配置工程は、基材を配置する工程である(図8A参照)。

前記基材は、前述した多層配線の基材と同様である。

【0117】

<第1の電極形成工程>

前記第1の電極形成工程は、基材上に第1の電極を形成する工程である(図8A参照)。例えば、図8Aに示すように、基材51上にゲート電極52が形成される。

前記第1の電極の材質、形状、構造、大きさ、及び形成方法は、前述した半導体装置の第1の電極と同様である。

【0118】

<第1の絶縁膜形成工程>

前記第1の絶縁膜形成工程は、基材及び第1の電極上に第1の絶縁膜を形成する工程である(図8A参照)。例えば、図8Aに示すように、基材51及びゲート電極52上にゲート絶縁膜53が形成される。

前記第1の絶縁膜は、様々な材料、プロセス、パターニング方法が利用可能である。前記材料としては、例えば、SiO2、SiNx等の既に広く量産に利用されている材料;La2O3、HfO2等の高誘電率材料;ポリイミド(PI)、フッ素系樹脂等の有機材料などが利用できる。前記プロセスとしては、スパッタ法、化学気相蒸着(CVD)法、原子層蒸着(ALD)等の真空成膜法やスピンコート、ダイコート等の溶液プロセスによる成膜後、フォトリソグラフィーによるパターンニング、インクジェット、ノズルプリンター等の印刷プロセスによって、所望の形状を直接成膜することも可能である。

【0119】

<第2の電極形成工程>

前記第2の電極形成工程は、第1の絶縁膜上に第2の電極を形成する工程である(図8A参照)。例えば、図8Aに示すように、ゲート絶縁膜53上にソース電極54、ドレイン電極55が形成される。

前記第2の電極の材質、形状、構造、大きさ、及び形成方法は、前述した半導体装置の第2の電極と同様である。

【0120】

<半導体層形成工程>

前記半導体層形成工程は、第2の電極及び第1の絶縁膜上に、半導体層を形成する工程である(図8A参照)。例えば、図8Aに示すように、ゲート絶縁膜53及びソース電極54、ドレイン電極55上に半導体層56が形成される。

前記半導体層は、前述した半導体装置における半導体層と同様である。

【0121】

また、前記半導体層上に保護層を形成してもよい。

前記保護層の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、SiO2、SiNx、Al2O3、フッ素系ポリマーなどが挙げられる。

前記保護層の形成方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、CVD法、スパッタ法などが挙げられる。

【0122】

<ピラー形成工程>

前記ピラー形成工程は、第2の電極上のビアホール形成領域に、ピラーを形成する工程である(図8A参照)。例えば、図8Aに示すように、ドレイン電極55上のビアホール形成領域にピラー58が形成される。

【0123】

−ピラー−

前記ピラーは、前述した多層配線におけるピラーと同様である。

【0124】

<第2の絶縁膜形成工程>

前記第2の絶縁膜形成工程は、ピラーが形成された第2の電極上に第2の絶縁膜を形成する工程である(図8B参照)。例えば、図8Bに示すように、ピラー58が形成されたドレイン電極55上に層間絶縁膜57が形成される。

前記第2の絶縁膜は、前述した多層配線の絶縁膜と同様である。

【0125】

<ピラー除去工程>

前記ピラー除去工程は、ピラーを除去して、絶縁膜に開口部を形成する工程である(図8C参照)。例えば、図8Cに示すように、ドレイン電極55上に形成された第2の絶縁膜57にビアホールが形成される。

【0126】

<熱処理工程>

前記熱処理工程は、第2の絶縁膜を熱処理する工程である(図8D参照)。熱処理によって、開口部周縁の突起部の熱ダレにより、テーパー形状を制御することが可能であり、例えば、図8Dに示すように、順テーパー状ホールが形成される。

なお、熱硬化性樹脂の熱硬化や、熱可塑性樹脂の熱処理による溶媒除去等、別の目的での熱処理が必要な場合、前記熱処理にて同時に行ってもよく、別途行ってもよい。

【0127】

<第3の電極形成工程>

前記第3の電極形成工程は、第2の電極及び第2の絶縁膜上に第3の電極を形成する工程である(図8E参照)。例えば、図8Eに示すように、ドレイン電極55及び第2の絶縁膜57上に画素電極59が形成される。

【0128】

−第3の電極−

前記第3の電極の形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

【0129】

前記第3の電極の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、Mo、Al、Ag、Cu等の金属乃至合金;ITO、ATO等の透明導電性酸化物;ポリエチレンジオキシチオフェン(PEDOT)、ポリアニリン(PANI)等の有機導電体などが挙げられる。

【0130】

前記第3の電極の形成方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)スパッタ法、ディップコーティング法等による成膜後、フォトリソグラフィーによってパターニングする方法、(ii)インクジェット、ナノインプリント、グラビア等の印刷プロセスによって、所望の形状を直接成膜する方法などが挙げられる。

【0131】

<表示層形成工程>

前記表示層形成工程は、第3の電極上に、表示層60を形成する工程である(図8F)。

前記表示層としては、有機EL層、エレクトロクロミック層、電気泳動層、エレクトロウェッティング層等を適宜利用することができ、プロセスについても、特に制限はなく、目的に応じて適宜選択できる。

【0132】

<第4の電極形成工程>

前記第4の電極形成工程は、前記表示層60上に、上部電極61を形成する工程である(図8F)。

前記第4の電極の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、Mo、Al、Ag、Cu等の金属乃至合金、ITO、ATO等の透明導電性酸化物、ポリエチレンジオキシチオフェン(PEDOT)、ポリアニリン(PANI)等の有機導電体などが挙げられる。

前記第4の電極の形成プロセスとしては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(i)真空蒸着法、スパッタ法、ディップコーティング法等による成膜後、必要に応じてフォトリソグラフィーによってパターニングする方法、(ii)インクジェット、ナノインプリント、グラビア等の印刷プロセスによって、所望の形状を直接成膜する方法、などが挙げられる。

これらの工程により、低コストで表示素子50を作製することができる。

【0133】

(システム)

本発明のシステムは、少なくとも、本発明の画像表示装置と、画像データ出力装置とを有する。

前記画像データ出力装置は、表示する画像情報に基づいて画像データを作成し、該画像データを前記画像表示装置に出力する。

【0134】

(画像表示装置)

本発明の画像表示装置は、少なくとも、表示素子と、配線と、表示制御装置とを有してなり、更に必要に応じて、その他の部材を有してなる。

【0135】

<表示素子>

前記表示素子としては、マトリックス状に配置された本発明の表示素子である限り、特に制限はなく、目的に応じて適宜選択することができる。

【0136】

<配線>

前記配線は、前記表示素子における各電界効果型トランジスタにゲート電圧を個別に印加可能である限り、特に制限はなく、目的に応じて適宜選択することができる。

【0137】

<表示制御装置>

前記表示制御装置としては、画像データに応じて、各電界効果型トランジスタのゲート電圧を複数の配線を介して個別に制御可能である限り、特に制限はなく、目的に応じて適宜選択することができる。

【0138】

<その他の部材>

前記その他の部材としては、特に制限はなく、目的に応じて適宜選択することができる。

【0139】

本発明のシステムとしてのテレビジョン装置を、図9を用いて説明する。

図9は、本発明のシステムとしてのテレビジョン装置の一例を示す概略構成図である。なお、図9における接続線は、代表的な信号や情報の流れを示すものであり、各ブロックの接続関係の全てを表すものではない。

【0140】

図9において、テレビジョン装置100は、主制御装置101、チューナ103、ADコンバータ(ADC)104、復調回路105、TS(Transport Stream)デコーダ106、音声デコーダ111、DAコンバータ(DAC)112、音声出力回路113、スピーカ114、映像デコーダ121、映像・OSD合成回路122、映像出力回路123、画像表示装置124、OSD描画回路125、メモリ131、操作装置132、ドライブインターフェース(ドライブIF)141、ハードディスク装置142、光ディスク装置143、IR受光器151、及び通信制御装置152を備える。

映像デコーダ121と、映像・OSD合成回路122と、映像出力回路123と、OSD描画回路125とが、画像データ出力装置を構成する。

【0141】

主制御装置101は、CPUと、フラッシュROMと、RAMと、その他の部材とから構成され、テレビジョン装置100の全体を制御する。

前記フラッシュROMには、前記CPUにて解読可能なコードで記述されたプログラム、及び前記CPUでの処理に用いられる各種データなどが格納されている。

また、RAMは、作業用のメモリである。

【0142】

チューナ103は、アンテナ210で受信された放送波の中から、予め設定されているチャンネルの放送を選局する。

【0143】

ADC104は、チューナ103の出力信号(アナログ情報)をデジタル情報に変換する。

【0144】

復調回路105は、ADC104からのデジタル情報を復調する。

【0145】

TSデコーダ106は、復調回路105の出力信号をTSデコードし、音声情報及び映像情報を分離する。

【0146】

音声デコーダ111は、TSデコーダ106からの音声情報をデコードする。

【0147】

DAコンバータ(DAC)112は、音声デコーダ111の出力信号をアナログ信号に変換する。

【0148】

音声出力回路113は、DAコンバータ(DAC)112の出力信号をスピーカ114に出力する。

【0149】

映像デコーダ121は、TSデコーダ106からの映像情報をデコードする。

【0150】

映像・OSD合成回路122は、映像デコーダ121の出力信号とOSD描画回路125の出力信号を合成する。

【0151】

映像出力回路123は、映像・OSD合成回路122の出力信号を画像表示装置124に出力する。

【0152】

OSD描画回路125は、画像表示装置124の画面に文字や図形を表示するためのキャラクタ・ジェネレータを備えており、操作装置132、IR受光器151からの指示に応じて表示情報が含まれる信号を生成する。

【0153】

メモリ131には、AV(Audio−Visual)データ等が一時的に蓄積される。

【0154】

操作装置132は、例えば、コントロールパネルなどの入力媒体(図示省略)を備え、ユーザから入力された各種情報を主制御装置101に通知する。

【0155】

ドライブIF141は、双方向の通信インターフェースであり、一例としてATAPI(AT Attachment Packet Interface)に準拠している。

【0156】

ハードディスク装置142は、ハードディスクと、該ハードディスクを駆動するための駆動装置などから構成されている。駆動装置は、ハードディスクにデータを記録するとともに、ハードディスクに記録されているデータを再生する。

【0157】

光ディスク装置143は、光ディスク(例えば、DVDなど)にデータを記録するとともに、光ディスクに記録されているデータを再生する。

【0158】

IR受光器151は、リモコン送信機220からの光信号を受信し、主制御装置101に通知する。

【0159】

通信制御装置152は、インターネットとの通信を制御する。インターネットを介して各種情報を取得することができる。

【0160】

図10は、本発明の画像表示装置の一例を示す概略構成図である。

図10において、画像表示装置124は、表示器300と、表示制御装置400とを有する。

表示器300は、図11に示されるように、複数(ここでは、n×m個)の表示素子302がマトリックス状に配置されたディスプレイ310を有する。

また、ディスプレイ310は、図12に示されるように、X軸方向に沿って等間隔に配置されているn本の走査線(X0、X1、X2、X3、・・・、Xn−2、Xn−1)と、Y軸方向に沿って等間隔に配置されているm本のデータ線(Y0、Y1、Y2、Y3、・・・、Ym−1)、Y軸方向に沿って等間隔に配置されているm本の電流供給線(Y0i、Y1i、Y2i、Y3i、・・・・・、Ym−1i)とを有する。

よって、走査線とデータ線とによって、表示素子を特定することができる。

【0161】

以下、本発明の表示素子を、図13を用いて説明する。

図13は、本発明の表示素子の一例を示す概略構成図である。

図13において、表示素子としてのディスプレイ310は、いわゆるアクティブマトリックス方式の有機ELディスプレイであり、光制御素子としての有機EL(エレクトロルミネッセンス)素子350と、有機EL素子350を発光させるためのドライブ回路(駆動回路)320とを有する。

【0162】

図14は、有機EL素子の一例を示す概略構成図である。

図14において、有機EL素子350は、陰極312と、陽極314と、有機EL薄膜層340とを有する。

【0163】

陰極312の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、アルミニウム(Al)、マグネシウム(Mg)−銀(Ag)合金、アルミニウム(Al)−リチウム(Li)合金、ITO(Indium Tin Oxide)などが挙げられる。なお、マグネシウム(Mg)−銀(Ag)合金は、半透明電極である。

【0164】

陽極314の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、ITO(Indium Tin Oxide)、IZO(Indium Zinc Oxide)、銀(Ag)−ネオジウム(Nd)合金などが挙げられる。なお、銀(Ag)−ネオジウム(Nd)合金を用いた場合は、高反射率電極となる。

【0165】

有機EL薄膜層340は、電子輸送層342と、発光層344と、正孔輸送層346とを有する。電子輸送層342は、陰極312に接続され、正孔輸送層346は、陽極314に接続されている。陽極314と陰極312との間に所定の電圧を印加すると、発光層344が発光する。

【0166】

ここで、電子輸送層342と発光層344が1つの層を形成してもよく、また、電子輸送層342と陰極312との間に電子注入層が設けられてもよく、更に、正孔輸送層346と陽極314との間に正孔注入層346が設けられてもよい。

【0167】

また、基材側から光を取り出すいわゆる「ボトムエミッション」の場合について説明したが、基材と反対側から光を取り出す「トップエミッション」であってもよい。

【0168】

ドライブ回路320は、2つの電界効果型トランジスタ321及び322(図13)と、コンデンサ323(図13)とを有する。

【0169】

電界効果型トランジスタ321(図13)は、スイッチ素子として動作する。ゲート電極G(図13)は、所定の走査線に接続され、ソース電極S(図13)は、所定のデータ線に接続されている。また、ドレイン電極D(図13)は、コンデンサ323(図13)の一方の端子に接続されている。

【0170】

電界効果型トランジスタ322(図13)は、有機EL素子350に大きな電流を供給する。電界効果型トランジスタ322(図13)のゲート電極Gは、電界効果型トランジスタ321のドレイン電極Dと接続されている。そして、電界効果型トランジスタ322(図13)がドレイン電極Dは、有機EL素子350の陽極314に接続され、ソース電極Sは、所定の電流供給線に接続されている。

【0171】

そこで、電界効果型トランジスタ321が「オン」状態になると、電界効果型トランジスタ322によって、有機EL素子350は駆動される。

【0172】

コンデンサ323は、電界効果型トランジスタ321の状態、即ちデータを記憶する。コンデンサ323の他方の端子は、所定の電流供給線に接続されている。

【0173】

図15は、本発明の画像表示装置の他の一例を示す概略構成図である。

図15において、画像表示装置は、表示素子302と、配線(走査線、データ線)と、表示制御装置400とを有する。

表示制御装置400は、画像データ処理回路402と、走査線駆動回路404と、データ線駆動回路406とを有する。

画像データ処理回路402は、映像出力回路123の出力信号に基づいて、ディスプレイ310における複数の表示素子302の輝度を判断する。

走査線駆動回路404は、画像データ処理回路402の指示に応じてn本の走査線に個別に電圧を印加する。

データ線駆動回路406は、画像データ処理回路402の指示に応じてm本のデータ線に個別に電圧を印加する。

【0174】

以上の説明から明らかなように、本実施形態に係るテレビジョン装置100では、映像デコーダ121と映像・OSD合成回路122と映像出力回路123とOSD描画回路125とによって画像データ作成装置が構成されている。

【0175】

本実施の形態での有機EL素子350と、ドライブ回路(駆動回路)320によって構成された表示素子302として、前記表示素子30、又は前記表示素子50を利用することによって、低コストで画像表示装置を提供することが可能となる。

また、上記実施形態では、光制御素子が有機EL素子の場合について説明したが、これに限定されるものではなく、例えば、光制御素子がエレクトロクロミック素子であってもよい。この場合は、上記ディスプレイ310は、エレクトロクロミックディスプレイとなる。

また、前記光制御素子が液晶素子であってもよく、この場合ディスプレイ310は、液晶ディスプレイとなり、図16に示されるように、表示素子302´に対する電流供給線は不要となる。また、図17に示されるように、ドライブ回路320´は、後述する電界効果型トランジスタ321及び322、と同様の電界効果型トランジスタ324及びキャパシタ325により構成することができる。電界効果型トランジスタ324において、ゲート電極Gが所定の走査線に接続され、ソース電極Sが所定のデータ線に接続されている。また、ドレイン電極Dが、キャパシタ325及び液晶素子370の画素電極に接続されている。

この場合、ドライブ回路320´と液晶素子370によって構成された表示素子302として、前記表示素子50を利用することができ、低コストで液晶表示素子を提供することができる。

また、前記光制御素子は、電気泳動素子、エレクトロウェッティング素子であってもよい。

【0176】

以上、本発明のシステムがテレビジョン装置である場合について説明したが、これに限定されるものではなく、画像及び情報を表示する装置として画像表示装置124を備えていればよい。例えば、コンピュータ(パソコンを含む)と画像表示装置124とが接続されたコンピュータシステムであってもよい。

【実施例】

【0177】

以下、本発明の実施例を説明するが、本発明は、これらの実施例に何ら限定されるものではない。

【0178】

(実施例1)

図18A〜図18Eに示すように、フォトリソグラフィー法によって、ガラス基板71上に、下部電極の配線パターン72を形成した。

【0179】

具体的には、まず、厚み0.7mmのガラス基板に、常温下のDCスパッタリング(装置名:i−Miller、芝浦メカトロニクス社製)により、ITO(スズドープ酸化インジウム)からなる導電性酸化物薄膜を、厚みが200nmとなるように成膜した後、250℃で30分間の熱処理を行った。

【0180】

−下部電極の形成−

次に、ITOからなる導電性酸化物薄膜上に、フォトレジストをスピンコート(装置名:1X−DX2、ミカサ社製)にて塗布後、90℃で30分間のプリベークを行った。続いて、フォトマスクを用いて、g、h、及びi混合UV光を150mJ/cm2で露光し、東京応化株式会社製の現像液NMD−W2.38を用いて現像した後、120℃で30分間のポストベークを行い、フォトレジストのパターンを形成した。その後、RIE(Reactive Ion Etching)によりレジストパターンが形成されていない領域のITO膜を除去し、その後、レジストパターンを除去することにより、ITO膜からなる下部電極72を形成した(図18A)。

【0181】

−ピラーの形成−

ピラー形成液として、γ−ブチロラクトンによって希釈した熱可塑性アクリル樹脂溶液(商品名:KH−CT−865、日立化成工業株式会社製)を用意した。ピラー形成液中の熱可塑性アクリル樹脂の含有量は25質量%であった。

下部電極72上に、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法(吐出条件:電圧220V、周波数100Hz)により、ピラー形成液(インク)を吐出させて最大直径15μm、最大高さ7μmのピラー73を形成した。ピラー73を形成後、65℃で30分間の条件で乾燥させた(図18B)。

【0182】

−絶縁膜の形成−

絶縁膜形成材料として、フッ素系溶媒パーフルオロトリブチルアミンを溶媒とした熱可塑性フッ素系樹脂(旭硝子株式会社製、サイトップ、(C6F10O)n(n=約80,000))を用意した。絶縁膜形成材料中の熱可塑性フッ素系樹脂の含有量は9質量%であった。

下部電極72及びピラー73が形成されたガラス基板71に絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜74を成膜した(図18C)。

【0183】

−ピラー除去−

次に、絶縁膜74を成膜したガラス基板71をγ−ブチロラクトンに室温で5分間浸漬することにより、ピラー73を溶解させて、ピラー73を除去し、周縁に突起部が形成された開口部を形成した(図18D)。

【0184】

−熱処理−

次に、絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から230℃まで1℃/分間の昇温速度で加熱し、その後230℃で1時間の熱処理を行うことで、絶縁膜の突起部が消失して、順テーパー状ホールが形成された。

【0185】

次に、残渣を除去するために、Arプラズマを用いてアッシング処理を行った。アッシング処理の条件は、Ar流量50sccm、圧力35Pa、パワー500W、処理時間30秒間とした。

【0186】

最後に、アルミニウムを蒸着源として、メタルマスクを用いた抵抗加熱真空蒸着装置(装置名:EBX−60D、アルバック社製)を用いて抵抗加熱真空蒸着法によって上部電極75を形成し、多層配線70を形成した(図18E)。蒸着の背圧は3×10−6Torrであった。

【0187】

<絶縁膜の平均厚みに対するピラーの最大高さと、ビアホール形成の可否との関係>

実施例1において、下記表1に示すように、ピラーの最大高さ及び絶縁膜の平均厚みを変化させた以外は、実施例1と同様にして、多層配線を作製した。表1に絶縁膜の平均厚みに対するピラーの最大高さと、ビアホール形成の可否との関係を示す。

【0188】

−ピラーの最大高さ−

前記ピラーの最大高さは、原子間力顕微鏡(AFM、Pacific Nanotechnology社製)によりピラーの三次元形状を測定することにより求めた。

【0189】

−絶縁膜の平均厚み−

前記絶縁膜の平均厚みは、触針式段差計(Alpha−Step IQ、KLA Tencor Japan社製)により測定した。

【0190】

−ビアホール形成の可否の評価−

ピラー除去前後のAFM(Pacific Nanotechnology社製)を用いた1断面のプロファイルの計測により、下記基準でビアホール形成の可否を評価した。

〔評価基準〕

○:ピラー部が凸状から凹状へ変化した(ビアホール形成可)

×:ピラー部が凸状のままであった(ビアホール形成否)

【0191】

【表1】

表1の結果から、ピラーの最大高さが絶縁膜の平均厚みの5倍以上の高さである場合は、ビアホールが形成でき、ピラーの最大高さが絶縁膜の平均厚みの5倍未満の高さである場合は、ピラーが絶縁膜に埋め込まれてしまい、γ−ブチロラクトンの浸漬によるピラー除去によってビアホールが形成できないことが分かった。

【0192】

(比較例1)

実施例1において、ピラー除去後の熱処理工程(230℃で1時間の熱処理)を行わなかった以外は、実施例1と同様にして、多層配線を形成した。

【0193】

ここで、図19Aは、比較例1でのγ−ブチロラクトンの浸漬後に形成された開口部の断面形状を示す。図19Bは、実施例1での絶縁膜74の熱処理後のビアホールの断面形状を示す。図19Cは、比較例1でのγ−ブチロラクトンの浸漬後に形成された開口部のSEM観察結果を示す。図19Dは、実施例1での絶縁膜74の熱処理後のビアホールのSEM観察結果を示す。なお、前記断面形状はAFM(Pacific Nanotechnology社製)解析より測定した。

図19Aにおいて、ビアホールのエッジ部(周縁)の厚みが極端に厚くなっている。また、図19CのSEM観察より、図19Aのビアホールは逆テーパー状となっていることが分かった。

【0194】

一方、図19Bでは、ビアホールのテーパーは、なだらかな順テーパーとなっていることが分かった。これは、絶縁膜74が230℃で1時間の熱処理によって形状が変化したことにより、順テーパー形状となったと考えられる。図19Bのテーパー角は、約10°であった。よって、上部電極75を形成する工程において、上部電極75の断線や、ビアホール内への気泡の侵入などを回避することができた。

【0195】

また、図20に、下部電極72と上部電極75とのI−V特性を示す。ビアホールの数は、1個、4個、及び9個とした。いずれの場合もオーミックコンタクトをとっており、ビアホールを介して下部電極72と上部電極75が導通していることが分かった。

【0196】

(実施例2)

実施例1において、「絶縁膜の形成」、及び「熱処理」を下記のように変更した以外は、実施例1と同様にして、実施例2の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、キシレンを溶媒とした熱硬化性シリコーン樹脂(商品名:KR−271、信越化学工業社製)を用意した。絶縁膜形成材料中の熱硬化性シリコーン樹脂の含有量は50質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0197】

−熱処理−

絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から200℃まで1℃/分間の昇温速度で加熱し、その後200℃で1時間の熱処理を行うことで、絶縁膜の突起部が消失して、順テーパー状ホールが形成された。

【0198】

(実施例3)

実施例1において、「絶縁膜の形成」を下記のように変更した以外は、実施例1と同様にして、実施例3の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、シクロヘキサンを溶媒とした熱硬化性PDMS(ポリジメチルシロキサン)系有機無機ハイブリッド材料を用意した。絶縁膜形成材料中の熱硬化性PDMS系有機無機ハイブリッド材料の含有量は50質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0199】

(実施例4)

実施例1において、「ピラーの形成」を下記のように代えた以外は、実施例1と同様にして、実施例4の多層配線を作製した。

−ピラーの形成−

ピラー形成液として、γ−ブチロラクトンによって希釈した熱硬化性ポリイミド樹脂溶液(商品名:ユピコートFS−100L、宇部興産社製)を用意した。ピラー形成液中の熱硬化性ポリイミドの含有量は30質量%であった。

下部電極上に、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法(吐出条件:電圧220V、周波数100Hz)により、ピラー形成液(インク)を吐出させて最大直径15μm、最大高さ7μmのピラーを形成した。ピラーを形成後、65℃で30分間の条件で乾燥させた。

【0200】

(実施例5)

実施例2において、「ピラーの形成」を下記のように代えた以外は、実施例2と同様にして、実施例5の多層配線を作製した。

−ピラーの形成−

ピラー形成液として、γ−ブチロラクトンによって希釈した熱硬化性ポリイミド樹脂溶液(商品名:ユピコートFS−100L、宇部興産社製)を用意した。ピラー形成液中の熱硬化性ポリイミドの含有量は30質量%であった。

下部電極上に、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法(吐出条件:電圧220V、周波数100Hz)により、ピラー形成液(インク)を吐出させて最大直径15μm、最大高さ7μmのピラーを形成した。ピラーを形成後、65℃で30分間の条件で乾燥させた。

【0201】

(実施例6)

実施例3において、「ピラーの形成」を下記のように代えた以外は、実施例3と同様にして、実施例6の多層配線を作製した。

−ピラーの形成−

ピラー形成液として、γ−ブチロラクトンによって希釈した熱硬化性ポリイミド樹脂溶液(商品名:ユピコートFS−100L、宇部興産社製)を用意した。ピラー形成液中の熱硬化性ポリイミドの含有量は30質量%であった。

下部電極上に、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法(吐出条件:電圧220V、周波数100Hz)により、ピラー形成液(インク)を吐出させて最大直径15μm、最大高さ7μmのピラーを形成した。ピラーを形成後、65℃で30分間の条件で乾燥させた。

【0202】

(実施例7)

実施例1において、「ピラーの形成」、「絶縁膜の形成」、「ピラー除去」、及び「熱処理」を下記のように代えた以外は、実施例1と同様にして、実施例7の多層配線を作製した。

−ピラーの形成−

ピラー形成液として、n−テトラデカンを溶媒とした銀ナノ粒子(商品名:NPS−J、ハリマ化成社製、平均粒径12nm)を用意した。ピラー形成液中の銀ナノ粒子の含有量は65質量%であった。

下部電極上に、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法(吐出条件:電圧400V、周波数50Hz)により、ピラー形成液(インク)を吐出させて、180℃で30分間の条件で熱処理して、最大直径15μm、最大高さ10μmのピラーを形成した。

【0203】

−絶縁膜の形成−

絶縁膜形成材料として、γ−ブチロラクトンを主溶媒とした熱硬化性ポリイミド樹脂(商品名:DL−1000、東レ株式会社製)を用意した。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成液をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0204】

−ピラー除去−

絶縁膜を形成したガラス基板を、Agエッチング液(商品名:SEA−1、関東化学社製)を用いて、室温で5分間浸漬することにより、ピラーを除去し、周縁に突起部が形成された開口部を形成した。

【0205】

−熱処理−

絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から230℃まで1℃/分間の昇温速度で加熱し、その後230℃で1時間の熱処理を行うことで、絶縁膜の突起部が消失して、順テーパー状ホールが形成された。

【0206】

(実施例8)

実施例7において、「絶縁膜の形成」を下記のように代えた以外は、実施例7と同様にして、実施例8の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、γ−ブチロラクトンを溶媒とした熱硬化性アクリル樹脂を用意した。絶縁膜形成材料中の熱硬化性アクリル樹脂の含有量は30質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0207】

(実施例9)

実施例7において、「絶縁膜の形成」を下記のように代えた以外は、実施例7と同様にして、実施例9の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、γ−ブチロラクトンを溶媒とした熱硬化性エポキシ樹脂を用意した。絶縁膜形成材料中の熱硬化性エポキシ樹脂の含有量は30質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0208】

(実施例10)

実施例7において、「絶縁膜の形成」を下記のように代えた以外は、実施例7と同様にして、実施例10の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、パーフルオロトリブチルアミンを溶媒とした熱可塑性フッ素樹脂(商品名:サイトップ、(C6F10O)n(n=約80,000)、旭硝子株式会社製)を用意した。絶縁膜形成材料中の熱可塑性フッ素樹脂の含有量は9質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0209】

(実施例11)

実施例7において、「絶縁膜の形成」及び「熱処理」を下記のように代えた以外は、実施例7と同様にして、実施例11の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、キシレンを溶媒とした熱硬化性シリコーン樹脂(商品名:KR−271、信越化学工業株式会社製)を用意した。絶縁膜形成材料中の熱硬化性シリコーン樹脂の含有量は50質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0210】

−熱処理−

絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から200℃まで1℃/分間の昇温速度で加熱し、その後200℃で1時間の熱処理を行うことで、絶縁膜の突起部が消失して、順テーパー状ホールが形成された。

【0211】

(実施例12)

実施例7において、「絶縁膜の形成」及び「熱処理」を下記のように代えた以外は、実施例7と同様にして、実施例12の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、シクロヘキサンを溶媒とした熱硬化性PDMS(ポリジメチルシロキサン)系有機無機ハイブリッド材料を用意した。絶縁膜形成材料中の熱硬化性PDMS系有機無機ハイブリッド材料の含有量は50質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0212】

−熱処理−

絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から200℃まで1℃/分間の昇温速度で加熱し、その後200℃で1時間の熱処理を行うことで、絶縁膜の突起部が消失して、順テーパー状ホールが形成された。

【0213】

(実施例13)

実施例7において、「絶縁膜の形成」及び「熱処理」を下記のように代えた以外は、実施例7と同様にして、実施例13の多層配線を作製した。

−絶縁膜の形成−

絶縁膜形成材料として、アルコールを溶媒とした有機無機ハイブリッド材料(商品名:グラスカ、JSR社製)を用意した。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み1μmの絶縁膜を形成した。

【0214】

(実施例14)

実施例7において、「ピラーの形成」、「絶縁膜の形成」、「ピラー除去」、及び「熱処理」を下記のように代えた以外は、実施例7と同様にして、実施例14の多層配線を作製した。

−ピラーの形成−

ピラー形成液として、n−テトラデカンを溶媒とした銀ナノ粒子(商品名:NPS−J、ハリマ化成社製、平均粒径12nm)を用意した。ピラー形成液中の銀ナノ粒子の含有量は65質量%であった。

下部電極上に、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法(吐出条件:電圧400V、周波数50Hz)により、ピラー形成液(インク)を吐出させて、180℃で30分間の条件で熱処理して、最大直径15μm、高さ5μmのピラーを形成した。

【0215】

−絶縁膜の形成−

絶縁膜形成材料として、メチルイソブチルケトンを溶媒としたスピンオングラス材料(商品名:FOX(R)−16、東レ・ダウコーニング社製)を用意した。絶縁膜形成材料中のスピンオングラス材料の含有量は20質量%であった。

下部電極及びピラーが形成されたガラス基板上に、絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、平均厚み500nmの絶縁膜を形成した。

【0216】

−熱処理−

絶縁膜に開口部が形成されたガラス基板を、電気炉(KDF008H、デンケン社製)を用い、室温から450℃まで5℃/分間の昇温速度で加熱し、その後450℃で1時間の熱処理を行うことで、絶縁膜の突起部が消失して、順テーパー状ホールが形成された。

【0217】

次に、実施例1〜14及び比較例1で作製した多層配線について、以下のようにして、「ビアホールの最大直径の測定」、「ビアホールのテーパー角の測定」、「ビアホールへの導電性材料のステップカバレッジの測定」、「多層配線の導通性の評価」、及び「プロセス再現性の評価」を行った。結果を表3に示す。

【0218】

<ビアホールの最大直径の測定>

ビアホールにおける開口部の露出開口端の最大直径を光学顕微鏡によって測長した。

【0219】

<ビアホールのテーパー角の測定>

ビアホールのテーパー角を、AFM(Pacific Nanotechnology社製)により測定した。

【0220】

<ビアホールへの導電性材料のステップカバレッジの評価>

ビアホールへの導電性材料のステップカバレッジを、断面SEM写真観察により、下記基準で評価した。

〔評価基準〕

○:断線等が見られず、下部電極と上部電極が接続されていることを確認できた場合 ×:断線等の不具合が確認された場合

【0221】

<導通性の評価>

導通性について、上部−下部電極間に、±0.1Vの電圧を印加し、Agilent社製4156Cにより電流値を計測し、下記基準で評価した。

〔評価基準〕

○:オーミックコンタクトの特性が確認できた場合

×:上記以外の場合

【0222】

<プロセス再現性の評価>

5回同様の実験を行い、前記プロセス再現性を評価した。毎回ホールが形成され、又はホール最大直径が30μm以内となった場合「○」、それ以外を「×」と判定した。

【0223】

【表2】

【0224】

【表3】

【0225】

(実施例15)

図2A〜図2Eに基づいて、実施例15の詳細について説明する。

まず、厚み0.7mmのガラス基板11に対し、UVオゾン洗浄の前処理を行った。UVオゾン洗浄については、UVランプとしての低圧水銀ランプを用いて、90℃で10分間の処理条件で行った。

【0226】

次に、ガラス基板11上に、第1のソース電極12、第1のドレイン電極13、第2のソース電極14、及び第2のドレイン電極15を形成した(図2A)。

具体的には、常温下のDCスパッタリング(装置名:i−Miller、芝浦メカトロニクス社製)により、ITOからなる導電性酸化物薄膜を、ガラス基板11に、厚みが100nmとなるように成膜した。

【0227】

次に、ITOからなる導電性酸化物皮膜上に、フォトレジストをスピンコート(装置名:1X−DX2、ミカサ社製)にて塗布後、90℃で30分間のプリベークを行った。続いてフォトマスクを用いてg、h、及びi混合UV光を150mJ/cm2で露光し、東京応化株式会社製現像液NMD−W2.38を用いて現像した後、120℃で30分間のポストベークを行い、フォトレジストのパターンを形成した。その後、RIE(Reactive Ion Etching)によりレジストパターンが形成されていない領域のITO膜を除去し、その後、レジストパターンを除去した(図2A)。更に、250℃で30分間の熱処理を行った。このようにして、第1のソース電極12、第1のドレイン電極13、第2のソース電極14、及び第2のドレイン電極15を形成した。

【0228】

次に、第1及び第2の半導体層16,17を形成した(図2A)。

具体的には、DCスパッタリング法により、In−Ga−Zn−O酸化物膜を、厚みが約100nmとなるように成膜し、その後、In−Ga−Zn−O酸化物膜上に、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、レジストパターンを形成し、更に、RIEにより、レジストパターンの形成されていない領域のIn−Ga−Zn−O酸化物膜を除去し、その後、レジストパターンも除去することにより、第1及び第2の半導体層16,17を形成した。

次に、第1のドレイン電極13上に、ビアホールが形成されたゲート絶縁膜18を形成した(図2B〜図2D)。

【0229】

−ピラーの形成−

ピラー形成液として、γ−ブチロラクトンによって希釈した熱可塑性アクリル樹脂溶液(商品名:KH−CT−865、日立化成工業株式会社製)を用意した。ピラー形成液中の熱可塑性アクリル樹脂の含有量は25質量%であった。

具体的には、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法により、ピラー形成液(インク)を吐出させて最大直径15μm、最大高さ5μmのピラー19を形成した(図2A)。ピラー19形成後、65℃で30分間の条件で乾燥させた。

【0230】

−絶縁膜の形成−

絶縁膜形成材料として、フッ素系溶媒パーフルオロトリブチルアミンを溶媒とした熱可塑性フッ素系樹脂(旭硝子株式会社製、サイトップ、(C6F10O)n(n=約80,000))を用意した。絶縁膜形成材料中の熱可塑性フッ素系樹脂の含有量は9質量%であった。

ピラー19が形成されたガラス基板11に絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)によって塗布し、65℃で30分間の条件で乾燥させ、厚み500nmのゲート絶縁膜18を成膜した(図2B)。

【0231】

−ピラー除去−

次に、ゲート絶縁膜18を成膜したガラス基板11を、γ−ブチロラクトンに室温で5分間浸漬することにより、ピラー19を溶解させて、ピラー19を除去し、周縁に突起部が形成された開口部を形成した(図2C)。

【0232】

−熱処理−

絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から230℃まで1℃/分間の昇温速度で加熱し、その後230℃で1時間の熱処理を行うことで、絶縁膜の突起部が消失して、順テーパー状ホールが形成された(図2D)。

【0233】

次に、残渣を除去するために、Arプラズマを用いてアッシング処理を行った。アッシング処理の条件は、Ar流量50sccm、圧力35Pa、パワー500W、処理時間30秒間とした。

【0234】

次に、第1及び第2のゲート電極20,21を形成し、半導体装置10を形成した(図2E)。

具体的には、常温下のDCスパッタリング法によって、ゲート絶縁膜18を硬化させたガラス基板11にモリブデン(Mo)を100nm成膜した後、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、レジストパターンを形成し、更に、RIE(Reactive Ion Etching)によりレジストパターンの形成されていない領域のMo膜を除去し、その後、レジストパターンを除去した。

以上の工程により、第1のドレイン電極13と、第2のゲート電極21とが、ビアホールを介して接続されており、更に、第2のゲート電極と第2のソース電極間にキャパシタが形成された、2トランジスタ1キャパシタ構造の半導体装置を得た。

【0235】

次に、実施例15の2トランジスタ1キャパシタ構造の半導体装置について、実施例1と同様にして、「ビアホールの最大直径の測定」、「ビアホールのテーパー角の測定」、「ビアホールへの導電性材料のステップカバレッジの測定」、「多層配線の導通性の評価」、及び「プロセス再現性の評価」を行った。結果を表4に示す。

【0236】

(実施例16)

図7A〜図7Gに基づいて、実施例16の詳細を説明する。

【0237】

まず、厚み0.7mmのガラス基板31に対し、UVオゾン洗浄の前処理を行った。UVオゾン洗浄は、UVランプとしての低圧水銀ランプを用いて、90℃で10分間の処理条件で行った。

【0238】

次に、ガラス基板31上に、第1のソース電極32、第1のドレイン電極33、第2のソース電極34、及び第2のドレイン電極35を形成した(図7A)。

具体的には、常温下のDCスパッタリング(装置名:i−Miller、芝浦メカトロニクス社製)により、ITOからなる導電性酸化物薄膜を、ガラス基板31に、厚みが100nmとなるように成膜した。

【0239】

次に、ITOからなる導電性酸化物皮膜上に、フォトレジストをスピンコートにて塗布後、90℃で30分間のプリベークを行った。続いて、フォトマスクを用いてg、h、及びi混合UV光を150mJ/cm2で露光し、東京応化社製現像液NMD−W2.38を用いて現像した後、120℃で30分間のポストベークを行い、フォトレジストのパターンを形成した。その後、RIE(Reactive Ion Etching)によりレジストパターンが形成されていない領域のITO膜を除去し、その後、レジストパターンを除去した(図7A)。更に、250℃で30分間の熱処理を行った。このようにして、第1のソース電極32、第1のドレイン電極33、第2のソース電極34、及び第2のドレイン電極35を形成した。

【0240】

次に、第1及び第2の半導体層36,37を形成した(図7A)。

具体的には、DCスパッタリング法により、In−Ga−Zn−O酸化物膜を、厚みが約100nmとなるように成膜し、その後、In−Ga−Zn−O酸化物膜上に、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、レジストパターンを形成し、更に、RIEにより、レジストパターンの形成されていない領域のIn−Ga−Zn−O酸化物膜を除去し、その後、レジストパターンも除去することにより、第1及び第2の半導体層36,37を形成した(図7A)。

次に、第1、第2のドレイン電極33、35上に、ビアホールが形成されたゲート絶縁膜18を形成した(図7B〜図7D)。

【0241】

−ピラーの形成−

ピラー形成液としては、γ−ブチロラクトンによって希釈した熱可塑性アクリル樹脂(商品名:KH−CT−865、日立化成工業株式会社製)を用意した。ピラー形成液中の熱可塑性アクリル樹脂の含有量は25質量%であった。

具体的には、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法により、ピラー形成液(インク)を吐出させて第1、第2のドレイン電極33、35上に、最大直径15μm、最大高さ5μmのピラー39、40を形成した(図7A)。ピラー39を形成後、65℃で30分間の条件で乾燥させた。

【0242】

−絶縁膜の形成−

絶縁膜形成材料として、フッ素系溶媒パーフルオロトリブチルアミンを溶媒とした熱可塑性フッ素系樹脂(旭硝子株式会社製、サイトップ、(C6F10O)n(n=約80,000))を用意した。絶縁膜形成材料中の熱可塑性フッ素系樹脂の含有量は9質量%であった。

ピラー19が形成されたガラス基板11に絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)によって塗布し、65℃で30分間の条件で乾燥させ、厚み500nmのゲート絶縁膜18を成膜した(図7B)。

【0243】

−ピラーの除去−

次に、ゲート絶縁膜18を成膜したガラス基板11を、γ−ブチロラクトンに室温で5分間浸漬することにより、ピラー39、40を溶解させて、ピラー39、40を除去し、周縁に突起部が形成された開口部を形成した(図7C)。

【0244】

−熱処理−

絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から230℃まで1℃/分間の昇温速度で加熱し、その後230℃で1時間の熱処理によりゲート絶縁膜38を硬化させることで、突起部が消失して、順テーパー状ホールが形成された(図7D)。

【0245】

次に、残渣を除去するために、Arプラズマを用いてアッシング処理を行った。アッシング処理の条件は、Ar流量50sccm、圧力35Pa、パワー500W、処理時間30秒間とした。

【0246】

次に、第1及び第2のゲート電極41,42、画素電極(陽極)43を形成した(図7E)。

具体的には、常温下のDCスパッタリング法によって、ゲート絶縁膜38を硬化させたガラス基板31にITOからなる導電性酸化物薄膜を100nm成膜した後、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、レジストパターンを形成し、更に、RIE(Reactive Ion Etching)によりレジストパターンの形成されていない領域のITO膜を除去し、その後、レジストパターンを除去した。

次に、隔壁44を形成した。具体的にはポジ型感光性ポリイミド樹脂を用いて、スピンコートにより塗布し、プリベーク、露光装置による露光、現像により、所望のパターンを得た後、230℃でのポストベークすることにより、隔壁44を形成した(図7F)。

次に、高分子有機発光材料を用いて、液滴吐出法により、隔壁44の開口領域に表示層としての有機EL層45を形成した。

次に、上部電極(陰極)46を形成した。具体的には、MgAgを真空蒸着することにより、上部電極(陰極)46を形成した(図7G)。

以上より、有機EL表示素子30を形成し、コストダウンが可能となった。

【0247】

次に、実施例16の有機EL表示素子について、実施例1と同様にして、「ビアホールの最大直径の測定」、「ビアホールのテーパー角の測定」、「ビアホールへの導電性材料のステップカバレッジの測定」、「多層配線の導通性の評価」、及び「プロセス再現性の評価」を行った。結果を表4に示す。

【0248】

(実施例17)

図21A〜図21Fに基づいて、実施例17の詳細を説明する。

【0249】

まず、厚み0.7mmのガラス基板81に対し、UVオゾン洗浄の前処理を行った。UVオゾン洗浄については、UVランプ:低圧水銀ランプ、処理条件:90℃で10分間とした。

【0250】

次に、ガラス基板81上に、第1及び第2のゲート電極82、83を形成した。具体的には、ガラス基板81上に、DCスパッタリング(装置名:i−Miller、芝浦メカトロニクス社製)により透明導電膜であるITO膜を厚さが約100nmとなるよう成膜した。この後、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、形成される第1及び第2のゲート電極82、83のパターンと同様のレジストパターンを形成し、更に、RIE(Reactive Ion Etching)により、レジストパターンの形成されていない領域のITO膜を除去した。この後、レジストパターンも除去することにより、第1及び第2のゲート電極82、83を形成した(図21A参照)。

【0251】

次に、ゲート絶縁層84を形成した。具体的には、第1及び第2のゲート電極82、83及びガラス基板81上に、RFスパッタリングによりSiO2膜を約300nm成膜した。この後、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、形成されるゲート絶縁層84のパターンと同様のレジストパターンを形成し、更に、RIE(Reactive Ion Etching)により、レジストパターンの形成されていない領域のSiO2膜を除去し、この後、レジストパターンも除去することによりゲート絶縁層84を形成した(図21A参照)。

【0252】

次に、第1及び第2のソース電極85、86及び第1及び第2のドレイン電極87、88を形成した。具体的には、ゲート絶縁層84上にDCスパッタリングにより透明導電膜であるITO膜を膜厚が約100nmとなるように成膜し、この後、ITO膜上に、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、形成される第1及び第2のソース電極85、86及び第1及び第2のドレイン電極87、88のパターンと同様のレジストパターンを形成し、更に、RIEにより、レジストパターンの形成されていない領域のITO膜を除去した。この後、レジストパターンも除去することにより、ITO膜からなる第1及び第2のソース電極85、86並びに第1及び第2のドレイン電極87、88を形成した(図21A参照)。

【0253】

次に、第1及び第2の半導体層89、90を形成した。具体的には、DCスパッタリングにより、Mg−In系酸化物膜を膜厚が約100nmとなるように成膜し、この後、Mg−In系酸化物膜上に、フォトレジストを塗布し、プリベーク、露光装置による露光、現像により、形成される第1及び第2の半導体層89、90のパターンと同様のレジストパターンを形成し、更に、RIEにより、レジストパターンの形成されていない領域のMg−In系酸化物膜を除去した。この後、レジストパターンも除去することにより、第1及び第2の半導体層89、90を形成した。これにより、第1のソース電極85と第1のドレイン電極87との間にチャネルが形成されるように第1の半導体層89が、第2のソース電極86と第2のドレイン電極88との間にチャネルが形成されるように第2の半導体層90が形成された(図21A参照)。

次に、ドレイン電極88上にビアホールを有した層間絶縁膜92を形成した(図21B〜図21E)。

【0254】

−ピラーの形成−

ピラー形成液として、γ−ブチロラクトンによって希釈した熱可塑性アクリル樹脂溶液(商品名:KH−CT−865、日立化成工業株式会社製)を用意した。ピラー形成液中の熱可塑性アクリル樹脂の含有量は25質量%であった。

具体的には、インクジェット装置(商品名:スーパーインクジェット装置、SIJテクノロジ社製)を用いて、液滴吐出法により、ピラー形成液(インク)を吐出させて最大直径15μm、最大高さ10μmのピラー91を形成した(図21B)。ピラー91を形成後、65℃で30分間の条件で乾燥させた(図21B)。

【0255】

−絶縁膜の形成−

次に、絶縁膜形成材料としてフッ素系樹脂(旭硝子株式会社製、サイトップ、(C6F10O)n(n=約80,000))を用意した。絶縁膜形成材料中の熱可塑性フッ素系樹脂の含有量は9質量%であった。

ピラー91が形成されたガラス基板81に絶縁膜形成材料をスピンコート(装置名:1X−DX2、ミカサ社製)により塗布し、65℃で30分間の条件で乾燥させ、厚み1.5μmの層間絶縁膜92を成膜した(図21C)。

【0256】

−ピラーの除去−

次に、層間絶縁膜92が成膜されたガラス基板81を、γ−ブチロラクトンに室温で5分間浸漬することにより、ピラー91を溶解させて、ピラー91を除去し、周縁に突起部が形成された開口部を形成した(図21D)。

【0257】

−熱処理−

層間絶縁膜に開口部が形成されたガラス基板を、オーブン(DTS82、ヤマト科学社製)を用いて、室温から230℃まで1℃/分間の昇温速度で加熱し、その後230℃で1時間の熱処理により層間絶縁膜92を硬化させることで、突起部が消失して、順テーパー状ホールが形成された(図21E)。

【0258】

次に、残渣を除去するために、Arプラズマを用いてアッシング処理を行った。アッシング処理の条件は、Ar流量50sccm、圧力35Pa、パワー500W、処理時間30秒とした。

【0259】

次に、DCスパッタリング法によりITO薄膜を成膜後、フォトレジストをスピンコート(装置名:1X−DX2、ミカサ社製)にて塗布後、90℃で30分間のプリベークを行った。続いて、フォトマスクを用いてg、h、及びi混合UV光を150mJ/cm2露光し、東京応化株式会社製の現像液NMD−W2.38を用いて現像した後、120℃で30分間のポストベークを行い、フォトレジストのパターンを形成した。

更に、RIE(Reactive Ion Etching)により、レジストパターンの形成されていない領域のITO薄膜を除去し、その後、レジストパターンも除去することにより、陽極94を形成した(図21F)。

【0260】

次に、隔壁93を形成した。具体的には、ポジ型感光性ポリイミド樹脂を用いて、スピンコートにより塗布し、プリベーク、露光装置による露光、現像により、所望のパターンを得た後、230℃でのポストベークすることにより、隔壁93を形成した(図21F)。

【0261】

次に、高分子有機発光材料を用いて、液滴吐出法により、隔壁93の開口領域に有機EL層95を形成した(図21F)。

【0262】

次に、陰極96を形成した。具体的には、MgAgを真空蒸着することにより、陰極96を形成した(図21F)。

以上より、有機EL表示素子80を形成し、コストダウンが可能となった。

【0263】

次に、実施例17の有機EL表示素子について、実施例1と同様にして、「ビアホールの最大直径の測定」、「ビアホールのテーパー角の測定」、「ビアホールへの導電性材料のステップカバレッジの測定」、「多層配線の導通性の評価」、及び「プロセス再現性の評価」を行った。結果を表4に示す。

【0264】

【表4】

【産業上の利用可能性】

【0265】

本発明のホール形成方法、並びに、該ホール方法を用いて形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムは、携帯電話、携帯型音楽再生装置、携帯型動画再生装置、電子BOOK、PDA(Personal Digital Assistant)等の携帯情報機器、スチルカメラ、ビデオカメラ等の撮像機器における表示手段として好適に利用可能である。

【0266】

また、本発明のホール形成方法、並びに、該ホール形成方法を用いて形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムは、車、航空機、電車、船舶等の移動体システムにおける各種情報の表示手段として好適に利用可能である。更に、計測装置、分析装置、医療機器、広告媒体における各種情報の表示手段に画像表示装置を用いることができる。

なお、本発明のホール形成方法、並びに、該ホール方法を用いて形成した多層配線、半導体装置は、表示素子以外のもの(例えば、ICカード、IDタグなど)にも用いることができる。

【0267】

更に、本発明のホール形成方法、並びに、該ホール形成方法を用いて形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムは、計測装置、分析装置、医療機器、広告媒体における各種情報の表示手段として好適に利用可能である。

【符号の説明】

【0268】

1 基材

2 第1の配線

3 ピラー

4 絶縁膜

5 第2の配線

7 突起部

22 基材

23 ソース電極

24 ドレイン電極

25 半導体層

26 ゲート絶縁膜

27 ゲート電極

372 液晶素子の対向電極(コモン電極)

374 コンデンサの対向電極(コモン電極)

【先行技術文献】

【特許文献】

【0269】

【特許文献1】特表2003−518755号公報

【特許文献2】特開2009−21552号公報

【特許文献3】特開2007−95783号公報

【特許文献4】特開2005−50558号公報

【非特許文献】

【0270】

【非特許文献1】T.Okubo,et al.:IDW ’07,(2007),pp.463−464.

【非特許文献2】K.Yase,et al.:IDW ’09,(2009),pp.717−720.

【非特許文献3】K.Suzuki,et al.:IDW ’09,(2009),pp.1581−1584.

【技術分野】

【0001】

本発明は、ホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムに関する。

【背景技術】

【0002】

近年、集積回路等に用いられているLSI(Large Scale Integrated Circuit)、ディスプレイ等に用いられているAM−TFT(Active Matrix Thin Film Transistor)などのデバイスについて、高集積化及び高密度化が繰り返されている。

前記デバイスの製法の代表例として、フォトリソグラフィー法が挙げられる。前記フォトリソグラフィー法では、アライナーを用いた場合、1μm〜10μmの微細パターンを容易に形成することが可能であり、ステッパーを用いた場合には、1μm以下の微細パターンを容易に形成することが可能である。

しかし、フォトリソグラフィー法では、設備が高価であり、工程数が多く、廃液を処理するなどの手間がかかるという問題がある。

【0003】

一方で、フォトリソグラフィー法以外のより簡便な手法として、低コスト化が可能な微細パターン形成技術が注目されている。これらの中でも、液滴吐出法(インクジェット法)、スクリーン印刷法に代表される印刷法は、少ない工程数、高い材料利用効率、及び低コスト化された設備に基づく、低コストかつ環境負荷が小さい微細パターン形成技術として期待されている。

特に、印刷法を用いたAM−TFTに関する技術は急速な進歩を遂げており、印刷法(反転印刷)を用いて、76ppiの有機TFTを作製する技術(非特許文献1参照)、マイクロコンタクトプリンティング法により200ppiの有機TFTを作製する技術(非特許文献2参照)、UV照射による表面エネルギー制御と液滴吐出法との組み合わせにより200ppiの有機TFTを作製する技術(非特許文献3参照)、などが報告されている。

【0004】

前記印刷法を用いたホール(ビアホール)形成技術としては、例えば、絶縁膜を溶解可能な溶媒を、液滴吐出法を用いて絶縁膜上に局所的に滴下することによって、ホールを形成する技術が提案されている(特許文献1参照)。

しかし、上記技術においては、溶媒に溶解した絶縁膜が残渣として残るという問題がある。更に、微細なホールを形成するためには、液滴吐出法による液滴の吐出量を数10pL以下にする必要があり、常温での蒸発速度が液滴に大きな影響を与え、ホール形成プロセスの再現性が低くなり、歩留まりが低下するという問題がある。

【0005】

また、ホール形成領域に液滴吐出法により撥液材料の液滴を塗布し、撥液領域を形成し、撥液領域以外の領域に絶縁膜材料溶液を塗布することによって、ホールを形成する技術が提案されている(特許文献2参照)。

しかし、上記技術においては、液滴吐出法によって、撥液領域以外にも絶縁膜材料溶液を塗布する必要があり、スループット及び膜厚均一性が低下するという問題がある。

【0006】

更に、ラインパターンで印刷した上で、飛び石状のドットパターンで印刷することにより、20μm〜45μm程度のホール(コンタクトホール)をスクリーン印刷により形成する技術が提案されている(特許文献3参照)。

しかし、前記技術においては、液ダレ等の制御が困難であり、ホール径のバラつきが大きく、ホール形成プロセスの再現性に欠くという問題がある。

【0007】

また、前記問題に加えて、印刷法を用いてホール形成を行う場合、一般的に、層間絶縁膜がμmオーダーの厚みとなって、アスペクト比が高くなり、微細パターン形成が困難となるという問題がある。

【0008】

以上より、印刷法を用いたホール形成方法では、解像度及びプロセス再現性を満足したプロセスは構築されていない。

【0009】

フォトリソグラフィー法及び印刷法以外の方法によるホール形成技術として、レーザードリル法が提案されている。前記レーザードリル法においては、CO2レーザー、YAGレーザーといったレーザー光を利用することにより、プリント配線基板等の多層配線で、露出開口端の最大直径が20μm程度のホールを形成することができる。

例えば、レーザーを照射することにより照射部を脱着もしくは蒸発させる、又はレーザーを照射した後、現像等の照射部を除去することにより、微細パターンを形成する技術が提案されている(特許文献4参照)。

しかしながら、前記技術においては、レーザー装置が高価であり、レーザー照射部を脱着又は蒸発させる場合、AM−TFTのような薄膜に対して、下部電極の形状を維持して、層間絶縁膜のみにホールを形成することができるプロセスマージンが小さいという問題がある。

【0010】

以上より、微細なホール(例えば、ビアホール)を、高い再現性で、効率よく、低コストで容易に形成することが望まれている。

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明は、従来における前記諸問題を解決し、以下の目的を達成することを課題とする。即ち、本発明は、プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムを提供することを目的とする。

【課題を解決するための手段】

【0012】

前記課題を解決するための手段としては、以下の通りである。即ち、

<1> 基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、

前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、

前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、

前記開口部が形成された絶縁膜を熱処理する熱処理工程と、

を含むことを特徴とするホール形成方法である。

<2> ピラー形成液が、樹脂と、溶媒とを含有する前記<1>に記載のホール形成方法である。

<3> ピラー形成液が、無機ナノ粒子と、溶媒とを含有する前記<1>に記載のホール形成方法である。

<4> ピラー形成液の付与が、静電吸引型液滴吐出法により行われる前記<1>から<3>のいずれかに記載のホール形成方法である。

<5> 絶縁膜形成材料を基材全面上に付与する前記<1>から<4>のいずれかに記載のホール形成方法である。

<6> 絶縁膜形成材料を基材上にラインアンドスペース状に付与し、その後絶縁膜形成材料の流動性を利用して基材全面上に付与する前記<1>から<5>のいずれかに記載のホール形成方法である。

<7> 第1の配線と、前記第1の配線を被覆する絶縁膜と、前記絶縁膜上に配置された第2の配線とを有し、前記第1の配線と前記第2の配線とが、前記絶縁膜に形成されたビアホールを介して接続された多層配線であって、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする多層配線である。

<8> 基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも2つ有し、これらのうちの1つの前記電界効果型トランジスタの前記ドレイン電極と、他の前記電界効果型トランジスタの前記ゲート電極とが、前記ゲート絶縁膜に形成されたビアホールを介して接続された回路を少なくとも1つ含む半導体装置であって、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする半導体装置である。

<9> 駆動信号に応じて光出力を制御する光制御素子と、

前記光制御素子を駆動する駆動回路と、を備える表示素子であって、

前記駆動回路が、

基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも2つ有し、これらのうちの1つの前記電界効果型トランジスタの前記ドレイン電極と、他の前記電界効果型トランジスタの前記ゲート電極とが、前記ゲート絶縁膜に形成されたビアホールを介して接続された回路を少なくとも1つ含む駆動回路であって、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする表示素子である。

<10> 駆動信号に応じて光出力を制御する光制御素子と、

前記光制御素子を駆動する駆動回路と、

前記光制御素子と前記駆動回路との間に設けられた層間絶縁膜と、

を備える表示素子であり、

前記駆動回路が、

基板と、

ゲート電圧を印加するためのゲート電極と、

電流を取り出すためのソース電極及びドレイン電極と、

少なくとも前記ソース電極及び前記ドレイン電極との間に形成された半導体層と、

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁膜と、

を有する電界効果型トランジスタを少なくとも1つ有する駆動回路であって、

前記駆動回路の前記ドレイン電極と、前記光制御素子に含まれる少なくとも1つの電極とが、

前記層間絶縁膜に形成されたビアホールを介して接続されており、

前記ビアホールが、前記<1>から<6>のいずれかに記載のホール形成方法により形成されたことを特徴とする表示素子である。

<11> 光制御素子が、有機エレクトロルミネッセンス素子、エレクトロクロミック素子、液晶素子、電気泳動素子、及びエレクトロウェッティング素子の少なくともいずれかを有する前記<9>から<10>のいずれかに記載の表示素子である。

<12> マトリックス状に複数配置された前記<9>から<11>のいずれかに記載の表示素子と、

前記表示素子に電圧を個別に印加するための複数の配線と、

画像データに応じて、前記表示素子に印加された電圧を前記複数の配線を介して個別に制御する表示制御装置と、

を有することを特徴とする画像表示装置である。

<13> 前記<12>に記載の画像表示装置と、

表示する画像情報に基づいて画像データを作成し、該画像データを前記画像表示装置に出力する画像データ出力装置と、を有することを特徴とするシステムである。

【発明の効果】

【0013】

本発明によれば、従来における前記諸問題を解決し、前記目的を達成することができ、プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムを提供することができる。

【図面の簡単な説明】

【0014】

【図1A】図1Aは、本発明の多層配線の製造方法の一例を示す図である(その1)。

【図1B】図1Bは、本発明の多層配線の製造方法の一例を示す図である(その2)。

【図1C】図1Cは、本発明の多層配線の製造方法の一例を示す図である(その3)。

【図1D】図1Dは、本発明の多層配線の製造方法の一例を示す図である(その4)。

【図1E】図1Eは、本発明の多層配線の製造方法の一例を示す図である(その5)。

【図1F】図1Fは、本発明の多層配線の製造方法の一例を示す図である(その6)。

【図1G】図1Gは、本発明の多層配線の製造方法の一例を示す図である(その7)。

【図2A】図2Aは、本発明の半導体装置の製造方法の一例を示す図である(その1)。

【図2B】図2Bは、本発明の半導体装置の製造方法の一例を示す図である(その2)。

【図2C】図2Cは、本発明の半導体装置の製造方法の一例を示す図である(その3)。

【図2D】図2Dは、本発明の半導体装置の製造方法の一例を示す図である(その4)。

【図2E】図2Eは、本発明の半導体装置の製造方法の一例を示す図である(その5)。

【図3】図3は、トップゲート/ボトムコンタクトの半導体装置の一例を示す概略構成図である。

【図4】図4は、トップゲート/トップコンタクトの半導体装置の一例を示す概略構成図である。

【図5】図5は、ボトムゲート/ボトムコンタクトの半導体装置の一例を示す概略構成図である。

【図6】図6は、ボトムゲート/トップコンタクトの半導体装置の一例を示す概略構成図である。

【図7A】図7Aは、本発明の表示素子の製造方法の一例を示す図である(その1)。

【図7B】図7Bは、本発明の表示素子の製造方法の一例を示す図である(その2)。

【図7C】図7Cは、本発明の表示素子の製造方法の一例を示す図である(その3)。

【図7D】図7Dは、本発明の表示素子の製造方法の一例を示す図である(その4)。

【図7E】図7Eは、本発明の表示素子の製造方法の一例を示す図である(その5)。

【図7F】図7Fは、本発明の表示素子の製造方法の一例を示す図である(その6)。

【図7G】図7Gは、本発明の表示素子の製造方法の一例を示す図である(その7)。

【図8A】図8Aは、本発明の表示素子の製造方法の他の一例を示す図である(その1)。

【図8B】図8Bは、本発明の表示素子の製造方法の他の一例を示す図である(その2)。

【図8C】図8Cは、本発明の表示素子の製造方法の他の一例を示す図である(その3)。

【図8D】図8Dは、本発明の表示素子の製造方法の他の一例を示す図である(その4)。

【図8E】図8Eは、本発明の表示素子の製造方法の他の一例を示す図である(その5)。

【図8F】図8Fは、本発明の表示素子の製造方法の他の一例を示す図である(その6)。

【図9】図9は、本発明のシステムとしてのテレビジョン装置の一例を示す概略構成図である。

【図10】図10は、図9における画像表示装置を説明するための図である(その1)。

【図11】図11は、図9における画像表示装置を説明するための図である(その2)。

【図12】図12は、図9における画像表示装置を説明するための図である(その3)。

【図13】図13は、本発明の表示素子を説明するための図である。

【図14】図14は、有機EL素子の一例を示す概略構成図である。

【図15】図15は、表示制御装置を説明するための図である。

【図16】図16は、液晶ディスプレイを説明するための図である。

【図17】図17は、図16における表示素子を説明するための図である。

【図18A】図18Aは、実施例1の多層配線の製造方法を示す図である(その1)。

【図18B】図18Bは、実施例1の多層配線の製造方法を示す図である(その2)。

【図18C】図18Cは、実施例1の多層配線の製造方法を示す図である(その3)。

【図18D】図18Dは、実施例1の多層配線の製造方法を示す図である(その4)。

【図18E】図18Eは、実施例1の多層配線の製造方法を示す図である(その5)。

【図19A】図19Aは、比較例1のγ−ブチロラクトンに浸漬後の開口部の断面形状を示すグラフである。

【図19B】図19Bは、実施例1の絶縁膜の硬化後のビアホールの断面形状を示すグラフである。

【図19C】図19Cは、比較例1のγ−ブチロラクトンに浸漬後の開口部のSEM観察結果を示す図である。

【図19D】図19Dは、実施例1の絶縁膜の硬化後のビアホールのSEM観察結果を示す図である。

【図20】図20は、実施例1の多層配線における上部電極及び下部電極のI−V特性を示すグラフである。

【図21A】図21Aは、実施例17の有機EL表示素子の製造方法を示す図である(その1)。

【図21B】図21Bは、実施例17の有機EL表示素子の製造方法を示す図である(その2)。

【図21C】図21Cは、実施例17の有機EL表示素子の製造方法を示す図である(その3)。

【図21D】図21Dは、実施例17の有機EL表示素子の製造方法を示す図である(その4)。

【図21E】図21Eは、実施例17の有機EL表示素子の製造方法を示す図である(その5)。

【図21F】図21Fは、実施例17の有機EL表示素子の製造方法を示す図である(その6)。

【図22】図22は、静電吸引型液滴吐出装置の概要図の一例を示す図である。

【図23A】図23Aは、ピラーの形成工程の一例を示す図である(その1)。

【図23B】図23Bは、ピラーの形成工程の一例を示す図である(その2)。

【図23C】図23Cは、ピラーの形成工程の一例を示す図である(その3)。

【発明を実施するための形態】

【0015】

(ホール形成方法)

本発明のホール形成方法は、基材上に電子回路を作製するための製造プロセスであって、少なくとも、ピラー形成工程と、絶縁膜形成工程と、ピラー除去工程と、熱処理工程とを含み、更に必要に応じてその他の工程を含んでなる。

【0016】

<ピラー形成工程>

前記ピラー形成工程は、基材上にピラー形成液を付与してピラーを形成する工程である。

【0017】

<<基材>>

前記基材の形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

前記基材の材質としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、ガラス基材、プラスチック基材などが挙げられる。

前記ガラス基材としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、無アルカリガラス、シリカガラスなどが挙げられる。

前記プラスチック基材としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、ポリカーボネート(PC)、ポリイミド(PI)、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)などが挙げられる。

なお、前記基材は、表面の清浄化及び密着性向上の点から、酸素プラズマ、UVオゾン、UV照射洗浄等の前処理が行われることが好ましい。

【0018】

<<ピラー>>

本発明において、前記ピラーとは、平面的でなく立体的に高さ方向に成長した立体構造物をいう。

前記ピラーの形状、構造、及び大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。前記ピラーの形状としては、例えば、円錐状、円柱状、角柱状などが挙げられる。

【0019】

前記ピラーの最大高さとしては、特に制限はなく、目的に応じて適宜選択することができるが、後述するピラー除去工程において形成される絶縁膜の平均厚みよりも高いことが好ましく、また、前記絶縁膜の平均厚みに対し、5倍以上が好ましく、例えば、0.5μm〜50μmが好ましく、1μm〜30μmがより好ましく、2μm〜10μmが特に好ましい。

前記ピラーの最大高さは、原子間力顕微鏡(AFM)によるピラーの三次元形状測定により得られた高さの最大値である。

【0020】

<<ピラー形成液(第1の形態)>>

前記ピラー形成液は、第1の形態では、樹脂及び溶媒を含有し、更に必要に応じてその他の成分を含有してなる。前記第1の形態のピラー形成液は、導電性溶液、又は高誘電率溶液であることが好ましい。具体的には、導電率が10×10−5S/m以上、又は誘電率が5以上であることが好ましい。

【0021】

−樹脂−

前記樹脂としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、熱硬化性樹脂、UV硬化型樹脂、熱可塑性樹脂などが挙げられる。ただし、前記熱硬化性樹脂、前記UV硬化型樹脂の場合には、ピラー形成後、硬化処理を行ってしまうと、後述するピラー除去工程で不具合が生じてしまうため、硬化処理を行わないで次工程に進むことが好ましい。

前記樹脂としては、例えば、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリエステル樹脂、ポリビニルフェノール樹脂、ポリビニルアルコール樹脂、ポリ酢酸ビニル樹脂、ポリスルホン樹脂、フッ素樹脂、これらの樹脂の共重合樹脂、又はポリマーアロイ、これらのプレポリマーなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。これらの中でも、熱可塑性アクリル樹脂、熱硬化性ポリイミド樹脂が特に好ましい。

前記樹脂の前記第1の形態のピラー形成液における含有量は、特に制限はなく、目的に応じて適宜選択することができるが、5質量%〜50質量%が好ましい。

【0022】

−溶媒−

前記溶媒としては、特に制限はなく、目的に応じて適宜選択することができるが、誘電率の高い極性溶媒であることが好ましい。前記誘電率としては、5以上であることが好ましく、10以上であることがより好ましい。

前記誘電率が高い極性溶媒としては、例えば、メタノール、エタノール、イソプロピルアルコール、n−ブタノール、n−ヘキサノール、n−オクタノール、エチレングリコール、ジエチレングリコール、プロピレングリコール、1,3−ブチレングリコール、ベンジルアルコール、2−メトキシエタノール、2−エトキシエタノール、2−ブトキシエタノール、ジプロピレングリコールモノメチルエーテル、アセトン、メチルエチルケトン、メチルイソブチルケトン、メチルn−ブチルケトン、メチルn−アミルケトン、アセトフェノン、シクロヘキサノン、γ−ブチロラクトン、炭酸プロピレン、ホルムアミド、N,N−ジメチルホルムアミド、N,N−ジメチルアセトアミド、1,3−ジメチル−2−イミダゾリジノン、N,N’−ジメチルプロピレンウレア、2−ピロリジノン、N−メチルピロリドン、ニトロメタン、ニトロベンゼン、メチルスルホキシドなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0023】

−その他の成分−

前記その他の成分としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、分散剤、安定化剤、硬化剤などが挙げられる。

【0024】

前記ピラー形成液としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、γ−ブチロラクトンで希釈した熱可塑性アクリル樹脂溶液(商品名:KH−CT−865、日立化成工業株式会社製)、γ−ブチロラクトンを溶媒とした熱硬化性ポリイミド樹脂(商品名:HPC−5030、日立化成工業株式会社製)、γ−ブチロラクトンで希釈した熱硬化性ポリイミド溶液(商品名:ユピコートFS−100L、宇部興産社製)などが挙げられる。

【0025】

<<ピラー形成液(第2の形態)>>

前記ピラー形成液は、第2の形態では、無機ナノ粒子と、溶媒とを含有し、更に必要に応じてその他の成分を含有してなる。前記第2の形態のピラー形成液は、導電性溶液、又は高誘電率溶液であることが好ましい。具体的には、導電率が10×10−5S/m以上、又は誘電率が5以上であることが好ましい。

【0026】

−無機ナノ粒子−

前記無機ナノ粒子としては、例えば、銀(Ag)、金(Au)、銅(Cu)等の金属ナノ粒子;ITO(Indium−Tin Oxide)、酸化スズ、酸化アンチモンドープ酸化スズ等の酸化物ナノ粒子などが挙げられる。これらの中でも、銀ナノ粒子、金ナノ粒子が特に好ましい。

前記無機ナノ粒子の平均粒径としては、特に制限はなく、目的に応じて適宜選択することができるが、5nm〜50nmが好ましい。

前記無機ナノ粒子としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、銀ナノ粒子(商品名:NPS−J、ハリマ化成社製、平均粒径12nm)、金ナノ粒子(商品名:NPG−J、ハリマ化成社製、平均粒径7nm)などが挙げられる。

【0027】

前記無機ナノ粒子の前記第2の形態のピラー形成液における含有量は、特に制限はなく、目的に応じて適宜選択することができるが、10質量%〜70質量%が好ましい。

【0028】

−溶媒−

前記溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、極性溶媒、無極性溶媒、フッ素系溶媒などが挙げられる。前記極性溶媒、前記無極性溶媒、及び前記フッ素系溶媒としては、後述する絶縁膜形成材料の溶媒と同様のものを用いることができる。

【0029】

−その他の成分−

前記その他の成分としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、分散剤、安定化剤などが挙げられる。

【0030】

<絶縁膜形成工程>

前記絶縁膜形成工程は、前記ピラーが形成された基材上に絶縁膜を形成する工程である。

前記絶縁膜形成工程においては、形成したピラーの形状を維持しながら絶縁膜形成材料を付与して絶縁膜を形成することが好ましい。

【0031】

<<絶縁膜形成材料>>

前記絶縁膜形成材料としては、有機絶縁材料、無機酸化物絶縁材料、及び有機無機ハイブリッド材料のいずれかを含有し、溶媒、更に必要に応じてその他の成分を含有してなる。

【0032】

−有機絶縁材料−

前記有機絶縁材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、熱硬化型樹脂、UV硬化型樹脂、熱可塑性樹脂等の樹脂などが挙げられる。

前記樹脂としては、例えば、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリエステル樹脂、ポリビニルフェノール樹脂、ポリビニルアルコール樹脂、ポリ酢酸ビニル樹脂、ポリスルホン樹脂、フッ素樹脂、シリコーン樹脂、これらの樹脂の共重合樹脂、又はポリマーアロイ、これらのプレポリマーなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。これらの中でも、熱可塑性フッ素樹脂、熱硬化性ポリイミド樹脂、熱硬化性アクリル樹脂、熱硬化性エポキシ樹脂、熱硬化性フェノール樹脂、熱硬化性シリコーン樹脂が特に好ましい。

【0033】

−無機酸化物絶縁材料−

前記無機酸化物絶縁材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、金属アルコキシド、有機金属錯体等から形成されるSiO2、Al2O3、などが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

前記無機酸化物絶縁材料としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、メチルイソブチルケトンを溶媒としたスピンオングラス材料(商品名:FOX(R)−16、東レ・ダウコーニング社製)などが挙げられる。

【0034】

−有機無機ハイブリッド材料−

前記有機無機ハイブリッド材料としては、特に制限はなく、目的に応じて適宜選択することができる。前記有機無機ハイブリッド材料とは、有機成分と無機成分とがナノレベルで混合された材料である。例えば、(1)ヒドロキシル基(−OH基)又はアルコキシ基(−OR基)を含有したアクリル樹脂又はエポキシ樹脂等とアルコキシシランとが混合された材料、(2)ヒドロキシル基(−OH基)を含有したシリコーン樹脂とアルコキシシランとが混合された材料、(3)ヒドロシリル基(−SiH)を含有したシリコーン樹脂とビニル基(−CH=CH2)を含有したアクリル樹脂又はエポキシ樹脂等とが混合された材料などが挙げられる。前記有機無機ハイブリッド材料の中でも、シリコーン樹脂を利用した材料を、ポリジメチルシロキサン(PDMS)系有機無機ハイブリッド材料と呼ぶ。

前記有機無機ハイブリッド材料としては、特に制限はなく、適宜調製したものを使用してもよいし、市販品を使用してもよい。前記市販品としては、例えば、荒川化学社製コンポセラン、JSR社製グラスカなどが挙げられる。

【0035】

−溶媒−

前記絶縁膜形成材料は、前記ピラー形成工程で形成されたピラーを溶解しないことが必要である。即ち、前記絶縁膜形成材料の溶媒と、ピラー形成液の溶媒との組み合わせが重要となる。ただし、ピラー材料として無機ナノ粒子を用いた場合はこの限りではなく、絶縁膜形成材料に溶解されることは無いため、任意の絶縁膜形成材料を使用することができる。

【0036】

一方、前記ピラー材料として樹脂を用いた場合には、前記絶縁膜形成材料の溶媒と、ピラー形成液の溶媒の組み合わせを考慮する必要があり、前記ピラー形成液の溶媒が互いに相溶しない極性溶媒、無極性溶媒、及びフッ素系溶媒の3種の溶媒群から選ばれるいずれかの1種の溶媒であり、前記絶縁膜形成材料の溶媒が前記ピラー形成液の溶媒を含む溶媒群以外の2種の溶媒群から選ばれること、又は無溶媒であることが好ましい。

【0037】

前記極性溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、メタノール、エタノール、イソプロピルアルコール、n−ブタノール、n−ヘキサノール、n−オクタノール、エチレングリコール、ジエチレングリコール、プロピレングリコール、1,3−ブチレングリコール、ベンジルアルコール、2−メトキシエタノール、2−エトキシエタノール、2−ブトキシエタノール、ジプロピレングリコールモノメチルエーテル、アセトン、メチルエチルケトン、メチルイソブチルケトン、メチルn−ブチルケトン、メチルn−アミルケトン、アセトフェノン、シクロヘキサノン、γ−ブチロラクトン、炭酸プロピレン、ホルムアミド、N,N−ジメチルホルムアミド、N,N−ジメチルアセトアミド、1,3−ジメチル−2−イミダゾリジノン、N,N’−ジメチルプロピレンウレア、2−ピロリジノン、N−メチルピロリドン、ニトロメタン、ニトロベンゼン、メチルスルホキシドなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0038】

前記無極性溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、オクタン、ノナン、デカン、ウンデカン、ドデカン、トリデカン、テトラデカン、シクロヘキサン、3−メチルシクロヘキサン、ベンゼン、トルエン、キシレン、メシチレン、テトラリンなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0039】

前記フッ素系溶媒としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、テトラデカフルオロヘキサン、パーフルオロヘプタン、オクタデカフルオロオクタン、パーフルオロノナン、ヘキサフルオロベンゼン、オクタフルオロトルエン、オクタフルオロシクロペンテン、ヘプタコサフルオロトリブチルアミン、パーフルオロトリエチルアミン、パーフルオロトリブチルアミン、パーフルオロトリアミルアミン、パーフルオロ(1,3−ジメチルシクロヘキサン)、パーフルオロメチルシクロヘキサン、オクタデカフルオロデカヒドロナフタレン、パーフルオロ−2−メチルペンタンなどが挙げられる。これらは、1種単独で使用してもよいし、2種以上を併用してもよい。

【0040】

前記極性溶媒に可溶なピラー材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ポリイミド、ポリアミド、ポリエステル、ポリビニルフェノール、ポリビニルアルコール、ポリ酢酸ビニル、ポリスルホン、フッ素樹脂、前記樹脂の共重合樹脂又はポリマーアロイ、ポリジメチルシロキサン(PDMS)等の有機絶縁膜、金属アルコキシドや有機金属錯体等から形成されるSiO2、Al2O3等の無機酸化物絶縁膜、更にはそれらが混合された有機無機ハイブリッド膜などが挙げられる。

前記無極性溶媒に可溶なピラー材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、アクリル樹脂、ポリジメチルシロキサン(PDMS)、ポリスチレンなどが挙げられる。

前記フッ素系溶媒に可溶なピラー材料としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、フッ素樹脂などが挙げられる。

【0041】

前記樹脂を用いたピラー形成液の溶媒と前記絶縁膜形成材料の溶媒の組み合わせとしては、以下のものが好適に挙げられる。

(1)前記ピラー形成液の溶媒(γ−ブチロラクトン)と前記絶縁膜形成材料の溶媒(パーフルオロトリブチルアミン)

(2)前記ピラー形成液の溶媒(γ−ブチロラクトン)と前記絶縁膜形成材料の溶媒(n−テトラデカン、シクロへキサン、トルエン、キシレン)

【0042】

−その他の成分−

前記その他の成分としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、分散剤、安定化剤、硬化剤などが挙げられる。

【0043】

前記絶縁膜の形成方法としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、塗布対象面であるピラーが形成された基材上の全面に前記絶縁膜形成材料を塗布する塗布法などが挙げられる。

前記塗布法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、スピンコート法、ダイコート法、スリットコート法、スクリーン印刷法、ディスペンサー法、液滴吐出法、ノズルコーティング法などが挙げられる。これらの中でも、スループット及び膜厚の均一性の点で、全面塗布であるスピンコート法、ダイコート法、スリットコート法が特に好ましい。

また、スループットの観点から、ノズルコーティング法が好ましい。前記ノズルコーティング法は、前記絶縁膜形成材料を基材上にラインアンドスペース状に高速塗布する手法であり、塗布後の絶縁膜形成材料の流動性を利用して前記ピラー以外の基板全面を塗布することが可能である。

【0044】

前記絶縁膜の材質、形状、構造、大きさとしては、特に制限はなく、目的に応じて適宜選択することができる。

前記絶縁膜の膜厚としては、特に制限はなく、目的に応じて適宜選択することができるが、0.1μm〜20μmが好ましく、0.2μm〜10μmがより好ましく、0.4μm〜5μmが特に好ましい。

前記絶縁膜の膜厚は、例えば、触針式段差計などにより測定することができる。

【0045】

<ピラー除去工程>

前記ピラー除去工程は、前記ピラーを除去し、絶縁膜に開口部を形成する工程である。

前記絶縁膜形成工程後、ピラーが樹脂によって完全に被覆されていると、ピラーの除去が困難となるため、前記ピラー除去工程の前にAr、O2等のガスを用いたプラズマエッチングによりピラー上の樹脂をアッシングしてもよい。

【0046】

前記ピラーの除去方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、(1)ピラーを溶解可能な溶液を用いて、ディップ等のプロセスによりピラーを溶解させて除去する方法、(2)熱処理によってピラーを気化させて除去する方法などが挙げられる。

前記(1)のピラーを溶解可能な溶液としては、ピラー材料が樹脂の場合は、前記ピラー形成液(インク)の溶媒、又はピラー形成液(インク)の溶媒と同等の極性を持つ溶媒を用いることができ、例えば、アセトン、γ−ブチロラクトン、N−メチルピロリドンなどが挙げられる。

前記ピラー材料が無機ナノ粒子の場合は、例えば、硝酸、塩酸、硫酸、リン酸、ホウ酸、酢酸等の酸が適宜混合されたエッチング液を用いることができる。

前記ピラー材料として、銀ナノ粒子を用いた場合には、エッチング液としては、例えば、リン酸、硝酸、酢酸などを用いることが好ましい。

【0047】

前記開口部としては、絶縁膜に形成され、下部電極部分へ貫通した孔である限り、特に制限はなく、目的に応じて適宜選択することができる。

前記開口部の形状としては、特に制限はなく、目的に応じて適宜選択することができるが、例えば、円形、四角形などが好ましい。また、前記開口部の形状が逆テーパー形状のとき、後述する熱処理工程により、テーパー形状を制御することが可能で、例えば、順テーパー形状に変形させることができる。

【0048】

前記開口部の露出開口端の最大直径としては、特に制限はなく、目的に応じて適宜選択することができるが、40μm以下が好ましく、20μm以下がより好ましい。前記最大直径が前記より好ましい範囲内であると、高密度の電子デバイス等で利用可能となる点で有利である。

前記開口部の露出開口端間の最大直径は、例えば、光学顕微鏡を用いて測定することができる。

【0049】

<熱処理工程>

前記熱処理工程は、前記開口部が形成された絶縁膜を熱処理する工程である。

前記熱処理工程により、絶縁膜の開口部がテーパー状に整形される。

【0050】

−熱処理−

前記絶縁膜を熱処理することによって、開口部周縁の突起部において絶縁膜軟化による形状変化が起こる(熱ダレ)。この熱ダレにより、なだらかな傾斜の順テーパー状ホールを形成して、前記順テーパー状ホールに導電性材料を充填しやすくできる。

前記絶縁膜が熱可塑性材料からなる場合、前記絶縁膜のガラス転移点等に起因する軟化温度を超えた温度をかけることにより容易に軟化現象が見られ、熱ダレ現象を起こすことが可能である。

また、前記絶縁膜が熱硬化性材料からなる場合、前記絶縁膜形成材料の硬化開始温度以下の温度領域においては温度上昇に伴う絶縁膜の粘度低下の現象が起きる。その温度領域を利用して、熱ダレ現象を起こすことが可能である。具体的には、(1)前記絶縁膜形成材料を硬化させる前に、硬化開始温度以下の温度で熱処理することで熱変形させる方法、(2)前記絶縁膜形成材料の処理温度の室温から硬化温度までの昇温速度を、特定の昇温速度、例えば、1℃/分間の速度で制御し、硬化温度に達するまでの間に熱変形させる方法などが挙げられる。