ポインタのリンクのチェック回路

【課題】本発明は、パケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできるポインタのリンクのチェック回路を提供することを目的とする。

【解決手段】第1のデータから演算した演算結果を第1のデータのポインタにより示される次の第2のデータに対応させて記憶する記憶手段40と、記憶手段から読み出した第1のデータから演算した演算結果と該読み出した前記第1のデータのポインタにより示される次のデータに対応させて記憶された演算結果を比較する比較手段46とを有する。

【解決手段】第1のデータから演算した演算結果を第1のデータのポインタにより示される次の第2のデータに対応させて記憶する記憶手段40と、記憶手段から読み出した第1のデータから演算した演算結果と該読み出した前記第1のデータのポインタにより示される次のデータに対応させて記憶された演算結果を比較する比較手段46とを有する。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、ポインタのリンクのチェック回路に関し、特に、記憶装置上でアドレスのリンクチェーンを展開することにより形成されるリンクドリストの連続性チェックを行うポインタのリンクのチェック回路に関する。

【0002】

【従来の技術】

近年、パーソナル・コンピュータ等の情報関連機器、通信設備の普及、発展が目覚しく、様々な機器設備にて記憶装置上でアドレスのリンクチェーンを展開してリスト構造を形成するリンクドリストが用いられている。

【0003】

特に通信事業者向けの通信設備では、通信サービス品質(QOS)の提供等の顧客サービス向上のために、記憶装置の故障や周辺環境の影響による記憶装置の誤動作を早期に発見し、問題解決を確実とすることが要求されている。

【0004】

図1は、従来のリンクドリストを用いた記憶装置の一例のブロック構成図を示す。この記憶装置は例えば通信ネットワークのノード装置の入力バッファ等に適用される。

【0005】

同図中、FCS演算回路10は、パケット入力に対してFCS(Frame Check Sequence)演算を行い、生成したFCS値をパケットに付加する。ここでFCS演算とは、パリティ演算やCRC演算等を用いたデータの誤り検出アルゴリズムを指している。固定長分割回路12は、FCS値を含む入力パケットを固定長に分割する。ポインタ付与回路14は、固定長分割された個々のデータに対しポインタ値を付与する。

【0006】

ポインタ保持回路16は、ポインタ付与回路14の出力するポインタ値を一時的に保持する。パリティ演算回路18は、固定長分割された個々のデータ及びポインタ付与回路14の出力するポインタ値に対し故障検出用のパリティ演算を行う。

【0007】

記憶装置20は例えばRAMで構成され、固定長分割された個々のデータと、ポインタ付与回路14の出力するポインタ値と、パリティ演算回路18の出力するパリティ値とが、ポインタ保持回路16からのポインタ値(前回の書き込み時に生成された値)で指示されるアドレスに書き込まれる。上記のデータ分割と記憶装置の記録の様子を図2に示す。

【0008】

記憶装置20から読み出されたポインタ値は次の読み出しアドレスとして記憶装置20に供給される。また、読み出された個々のデータはパケット組立回路22でパケットに組み立てられる。組み立てられたパケットはFCS演算回路22に供給されてFCS演算が行われ、得られたFCS値とパケットに含まれるFCS値との一致比較によりパケットが正常に再現されたかを確認したのち、パケットに含まれるFCS値を削除して出力される。また、パリティ演算回路26は、記憶装置20から読み出された個々のデータ及び読み出されたポインタ値のパリティ演算を行って、記憶装置20から読み出されたパリティ値との一致比較により個々のデータ及びポインタ値の正常性、すなわち記憶装置20の故障の有無を確認している。

【0009】

以上の手順により、記憶装置20に書き込まれるデータの一部であるポインタ値のリンクを利用してデータの連続性を保持することにより、記憶装置20上に連続した未使用領域が無くてもデータを書き込みでき、読み出し時にデータの連続性を復元するとともに、データの連続性が正しく復元されたかを、FCS演算により確認する。また、記憶装置20から読み出された個々のデータは後続の回路に向けて出力される。

【0010】

なお、セルバッファメモリにおけるデータの連続性をチェックするために、シーケンス番号生成カウンタでシーケンス番号を発生して、セルデータをセルバッファメモリに書き込む際にシーケンス番号をアドレス監視テーブルに書き込み、セルデータをセルバッファメモリから読み出される際にアドレス監視テーブルから読み出されるシーケンス番号をシーケンス番号確認カウンタでシーケンス番号の連続性を確認する方法が例えば、特許文献1に記載されている。

【0011】

【特許文献1】

特開平10−126416号公報

【0012】

【発明が解決しようとする課題】

しかしながら、従来の回路構成ではポインタのリンクチェックをFCS演算に頼っているため、パケット単位のFCS演算回路10と、記憶装置20の読み出し後にパケットを組み立てる回路22と、パケットが正しく組み立てられたかをFCS演算により確認するFCS演算回路24が必須であり、パケット組み立て後、FCS演算を行うために、パケットデータ毎の処理遅延が大きくなるという問題があった。

【0013】

また、FCS演算回路10,24におけるFCS演算アルゴリズムとしてパリティ演算を用いた場合、記憶装置20の書き込み側アドレス、または、読み出し側アドレスのビット誤りによりパケットデータの一部が前後入れ替わった場合にも、これを検出することができないという問題があった。

【0014】

本発明は、上記の点に鑑みなされたものであり、パケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできるポインタのリンクのチェック回路を提供することを目的とする。

【0015】

【課題を解決するための手段】

請求項1に記載の発明は、第1のデータから演算した演算結果を該第1のデータのポインタにより示される次の第2のデータに対応させて記憶する記憶手段と、

該記憶手段から読み出した前記第1のデータから演算した演算結果と該読み出した前記第1のデータのポインタにより示される次の第2のデータに対応させて記憶された演算結果を比較する比較手段と、を有することにより、

回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【0016】

請求項2に記載の発明は、次に書き込むデータの書き込み先を示す第1ポインタと、前に書き込んだデータの書き込み先を示す第2ポインタとをデータに対応付けて記憶する記憶手段と、

該記憶手段からデータを読み出す際に用いたポインタと、該データに対応付けて記憶された第1ポインタにより示されるデータに対応して記憶された第2ポインタとを比較する比較手段と、を有することにより、

回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【0017】

【発明の実施の形態】

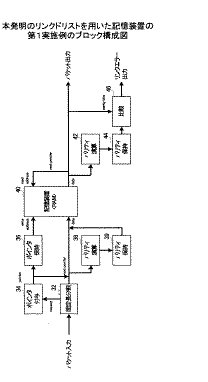

図3は、本発明のリンクドリストを用いた記憶装置の第1実施例のブロック構成図を示す。この記憶装置は例えば通信ネットワークのノード装置の入力バッファ等に適用される。

【0018】

同図中、固定長分割回路32は、パケット入力を固定長に分割する。ポインタ付与回路34は、固定長分割された個々のデータに対しポインタ値を付与する。ポインタ保持回路36は、ポインタ付与回路34の出力するポインタ値を一時的に保持する。

【0019】

パリティ演算回路38は、固定長分割された個々のデータ及びポインタ付与回路34の出力するポインタ値に対し故障検出及び連続性検出用のパリティ演算を行う。ここで得られたパリティはパリティ保持回路39で一時的に保持されたのち記憶装置40に供給される。

【0020】

記憶装置40は例えばRAMで構成され、固定長分割された個々のデータと、ポインタ付与回路34の出力するポインタ値(次の書き込みに使用される値)と、パリティ保持回路39の出力するパリティ値(前回の書き込み時に生成された値)とが、ポインタ保持回路36からのポインタ値(前回の書き込み時に生成された値)で指示されるアドレスに書き込まれる。つまり、個々のデータ及びポインタ値に対してパリティ値はずらして記憶装置40に書き込まれる。

【0021】

上記のデータ分割と記憶装置の記録の様子を図4に示す。図4において、パケットデータはデータA,B,C,Dに4分割され、記憶装置40のアドレス#0に、データAと次の書き込みに使用される次ポインタ値#2と前回の書き込み時に生成されたパリティ値が書き込まれる。また、アドレス#2に、データBと次の書き込みに使用される次ポインタ値#5と前回の書き込み時に生成されたパリティ値#0が書き込まれる。同様に、アドレス#5に、データCと次の書き込みに使用される次ポインタ値#4と前回の書き込み時に生成されたパリティ値#2が書き込まれ、アドレス#4に、データDと次の書き込みに使用される次ポインタ値#6と前回の書き込み時に生成されたパリティ値#5が書き込まれる。

【0022】

記憶装置40から前回読み出された次ポインタ値が読みだしアドレスとして記憶装置40に与えられており、これにより記憶装置40から読み出された次ポインタ値が次の読み出しアドレスとして記憶装置40に供給される。

【0023】

また、パリティ演算回路42は、記憶装置40から読み出された個々のデータ及び読み出された次ポインタ値のパリティ演算を行う。得られたパリティ値はパリティ保持回路44で一時的に保持されたのち比較回路46に供給される。比較回路46は記憶装置40から読み出されたパリティ値とパリティ保持回路44で一時的に保持されたパリティ値(前回の書き込み時に生成された値)との一致比較を行う。

【0024】

例えば、記憶装置40のアドレス#0から読み出されたデータA及び次ポインタ値#2をパリティ演算回路42で演算して得られたパリティ値#0がパリティ保持回路44から比較回路46に供給されるタイミングで、記憶装置40のアドレス#2からパリティ値#0が読み出されて比較回路46に供給され、両パリティ値の一致比較が行われる。

【0025】

これにより、個々のデータ及びポインタ値の正常性、すなわち記憶装置40の故障の有無を確認すると共に、前回読み出されたパリティ値(前回の書き込み時に生成された値)と今回読み出された個々のデータ及びポインタ値の連続性を確認している。

【0026】

つまり、個々のデータ及びポインタ値に対してパリティ値はずらして記憶装置に書き込まれているため、上記比較回路46で不一致の場合には、記憶装置40から読み出された個々のデータ及びポインタ値が異常であるか、または、今回読み出された個々のデータ及びポインタ値と前回読み出されたパリティ値との間に連続性がないということであり、このような誤りがあった場合にはリンクエラー信号を出力する。また、記憶装置40から読み出された個々のデータは後続の回路に向けて出力される。

【0027】

この実施例では、パケット組み立て後FCS演算を行う必要がないため、データの処理遅延を削減することができ、回路規模を削減することができる。また、記憶装置40の書き込み側アドレス、または、読み出し側アドレスのビット誤りによりパケットデータの一部が前後入れ替わった場合にも、これを検出することができる。

【0028】

なお、上記実施例ではパリティ演算回路38,42を用いているが、データの正当性を確認できる誤り検出符号であれば何でもよく、例えばCRC演算でも同じ効果を得ることができる。また、記憶装置40に書き込む個々のデータとパリティ演算結果のずれは1アドレスで説明したが、2アドレス以上ずれていても同じ効果を得ることができる。

【0029】

図5は、本発明のリンクドリストを用いた記憶装置の第2実施例のブロック構成図を示す。この記憶装置は例えば通信ネットワークのノード装置の入力バッファ等に適用される。同図中、図3と同一部分には同一符号を付す。

【0030】

図5において、固定長分割回路32は、パケット入力を固定長に分割する。ポインタ付与回路34は、固定長分割された個々のデータに対しポインタ値を付与する。ポインタ保持回路36は、ポインタ付与回路34の出力するポインタ値を一時的に保持する。ポインタ保持回路50は、ポインタ保持回路36の出力するポインタ値を更に一時的に保持されて記憶装置40に供給される。

【0031】

パリティ演算回路38は、固定長分割された個々のデータ及びポインタ付与回路34の出力するポインタ値に対し故障検出及び連続性検出用のパリティ演算を行う。ここで得られたパリティは記憶装置40に供給される。

【0032】

記憶装置40は例えばRAMで構成され、固定長分割された個々のデータと、ポインタ付与回路34の出力する次ポインタ値(次の書き込みに使用される値)と、ポインタ保持回路50の出力する前ポインタ値(前回の書き込みに使用された値)と、パリティ保持回路39の出力するパリティ値(今回の値)とが、ポインタ保持回路36からの現ポインタ値(前回の書き込み時に生成された値)で指示されるアドレスに書き込まれる。つまり、個々のデータ及び次ポインタ値に対して前ポインタ値がずらして記憶装置40に書き込まれる。

【0033】

上記のデータ分割と記憶装置の記録の様子を図6に示す。図6において、パケットデータはデータA,B,C,Dに4分割され、記憶装置40のアドレス#0に、データAと次の書き込みに使用される次ポインタ値#2と前回の書き込みに使用された前ポインタ値と今回のパリティ値#0が書き込まれる。また、アドレス#2に、データBと次の書き込みに使用される次ポインタ値#5と前回の書き込みに使用された前ポインタ値#0と今回のパリティ値#2が書き込まれる。同様に、アドレス#5に、データCと次の書き込みに使用される次ポインタ値#4と前回の書き込みに使用された前ポインタ値#2と今回のパリティ値#5が書き込まれ、アドレス#4に、データDと次の書き込みに使用される次ポインタ値#6と前回の書き込みに使用された前ポインタ値#5と今回のパリティ値#4が書き込まれる。

【0034】

記憶装置40からは前回読み出された次ポインタ値が読みだしアドレスとして与えられており、これにより読み出された次ポインタ値は次の読み出しアドレスとして記憶装置40に供給されると共に、ポインタ保持回路52で一時的に保持されたのち比較回路54に供給される。

【0035】

また、記憶装置40から読み出された前ポインタ値が比較回路54に供給され、比較回路54は記憶装置40から読み出された前ポインタ値とポインタ保持回路52で保持された次ポインタ値との一致比較を行い、今回読み出された個々のデータの連続性を確認して、エラーがあった場合にはリンクエラー信号を出力する。

【0036】

例えば、記憶装置40のアドレス#2を読み出す際にポインタ保持回路52に保持されたアドレス#2が比較回路54に供給されるタイミングに、記憶装置40のアドレス#5から前ポインタ値#2が読み出されて比較回路54に供給され、両ポインタ値の一致比較が行われる。

【0037】

また、パリティ演算回路42は、記憶装置40から読み出された個々のデータ及び読み出された次ポインタ値のパリティ演算を行って個々のデータ及びポインタ値の正常性、すなわち記憶装置40の故障の有無を確認して、エラーがあった場合にはパリティエラー信号を出力する。また、記憶装置40から読み出された個々のデータは後続の回路に向けて出力される。

【0038】

この実施例では、パケット組み立て後FCS演算を行う必要がないため、データの処理遅延を削減することができ、回路規模を削減することができる。また、記憶装置40の書き込み側アドレス、または、読み出し側アドレスのビット誤りによりパケットデータの一部が前後入れ替わった場合にも、これを検出することができる。

【0039】

なお、上記実施例では前ポインタ値そのものを記憶装置40に書き込んでいるが、ポインタ保持回路50,52にパリティ演算機能やCRC演算機能を付け、その演算結果を記憶装置40に書き込んでも同じ効果が得られる。

【0040】

なお、記憶装置40が請求項記載の記憶手段に対応し、比較回路46,54が比較手段に対応する。

【0041】

【発明の効果】

上述の如く、請求項1に記載の発明によれば、回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【0042】

また、請求項2に記載の発明によれば、回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【図面の簡単な説明】

【図1】従来のリンクドリストを用いた記憶装置の一例のブロック構成図である。

【図2】従来の構成におけるデータ分割と記憶装置の記録の様子を示す図である。

【図3】本発明のリンクドリストを用いた記憶装置の第1実施例のブロック構成図である。

【図4】第1実施例の構成におけるデータ分割と記憶装置の記録の様子を示す図である。

【図5】本発明のリンクドリストを用いた記憶装置の第2実施例のブロック構成図である。

【図6】第2実施例の構成におけるデータ分割と記憶装置の記録の様子を示す図である。

【符号の説明】

32 固定長分割回路

34 ポインタ付与回路

36 ポインタ保持回路

38,42 パリティ演算回路

39 パリティ保持回路

40 記憶装置

44 パリティ保持回路

46,54 比較回路

50,52 ポインタ保持回路

【0001】

【発明の属する技術分野】

本発明は、ポインタのリンクのチェック回路に関し、特に、記憶装置上でアドレスのリンクチェーンを展開することにより形成されるリンクドリストの連続性チェックを行うポインタのリンクのチェック回路に関する。

【0002】

【従来の技術】

近年、パーソナル・コンピュータ等の情報関連機器、通信設備の普及、発展が目覚しく、様々な機器設備にて記憶装置上でアドレスのリンクチェーンを展開してリスト構造を形成するリンクドリストが用いられている。

【0003】

特に通信事業者向けの通信設備では、通信サービス品質(QOS)の提供等の顧客サービス向上のために、記憶装置の故障や周辺環境の影響による記憶装置の誤動作を早期に発見し、問題解決を確実とすることが要求されている。

【0004】

図1は、従来のリンクドリストを用いた記憶装置の一例のブロック構成図を示す。この記憶装置は例えば通信ネットワークのノード装置の入力バッファ等に適用される。

【0005】

同図中、FCS演算回路10は、パケット入力に対してFCS(Frame Check Sequence)演算を行い、生成したFCS値をパケットに付加する。ここでFCS演算とは、パリティ演算やCRC演算等を用いたデータの誤り検出アルゴリズムを指している。固定長分割回路12は、FCS値を含む入力パケットを固定長に分割する。ポインタ付与回路14は、固定長分割された個々のデータに対しポインタ値を付与する。

【0006】

ポインタ保持回路16は、ポインタ付与回路14の出力するポインタ値を一時的に保持する。パリティ演算回路18は、固定長分割された個々のデータ及びポインタ付与回路14の出力するポインタ値に対し故障検出用のパリティ演算を行う。

【0007】

記憶装置20は例えばRAMで構成され、固定長分割された個々のデータと、ポインタ付与回路14の出力するポインタ値と、パリティ演算回路18の出力するパリティ値とが、ポインタ保持回路16からのポインタ値(前回の書き込み時に生成された値)で指示されるアドレスに書き込まれる。上記のデータ分割と記憶装置の記録の様子を図2に示す。

【0008】

記憶装置20から読み出されたポインタ値は次の読み出しアドレスとして記憶装置20に供給される。また、読み出された個々のデータはパケット組立回路22でパケットに組み立てられる。組み立てられたパケットはFCS演算回路22に供給されてFCS演算が行われ、得られたFCS値とパケットに含まれるFCS値との一致比較によりパケットが正常に再現されたかを確認したのち、パケットに含まれるFCS値を削除して出力される。また、パリティ演算回路26は、記憶装置20から読み出された個々のデータ及び読み出されたポインタ値のパリティ演算を行って、記憶装置20から読み出されたパリティ値との一致比較により個々のデータ及びポインタ値の正常性、すなわち記憶装置20の故障の有無を確認している。

【0009】

以上の手順により、記憶装置20に書き込まれるデータの一部であるポインタ値のリンクを利用してデータの連続性を保持することにより、記憶装置20上に連続した未使用領域が無くてもデータを書き込みでき、読み出し時にデータの連続性を復元するとともに、データの連続性が正しく復元されたかを、FCS演算により確認する。また、記憶装置20から読み出された個々のデータは後続の回路に向けて出力される。

【0010】

なお、セルバッファメモリにおけるデータの連続性をチェックするために、シーケンス番号生成カウンタでシーケンス番号を発生して、セルデータをセルバッファメモリに書き込む際にシーケンス番号をアドレス監視テーブルに書き込み、セルデータをセルバッファメモリから読み出される際にアドレス監視テーブルから読み出されるシーケンス番号をシーケンス番号確認カウンタでシーケンス番号の連続性を確認する方法が例えば、特許文献1に記載されている。

【0011】

【特許文献1】

特開平10−126416号公報

【0012】

【発明が解決しようとする課題】

しかしながら、従来の回路構成ではポインタのリンクチェックをFCS演算に頼っているため、パケット単位のFCS演算回路10と、記憶装置20の読み出し後にパケットを組み立てる回路22と、パケットが正しく組み立てられたかをFCS演算により確認するFCS演算回路24が必須であり、パケット組み立て後、FCS演算を行うために、パケットデータ毎の処理遅延が大きくなるという問題があった。

【0013】

また、FCS演算回路10,24におけるFCS演算アルゴリズムとしてパリティ演算を用いた場合、記憶装置20の書き込み側アドレス、または、読み出し側アドレスのビット誤りによりパケットデータの一部が前後入れ替わった場合にも、これを検出することができないという問題があった。

【0014】

本発明は、上記の点に鑑みなされたものであり、パケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできるポインタのリンクのチェック回路を提供することを目的とする。

【0015】

【課題を解決するための手段】

請求項1に記載の発明は、第1のデータから演算した演算結果を該第1のデータのポインタにより示される次の第2のデータに対応させて記憶する記憶手段と、

該記憶手段から読み出した前記第1のデータから演算した演算結果と該読み出した前記第1のデータのポインタにより示される次の第2のデータに対応させて記憶された演算結果を比較する比較手段と、を有することにより、

回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【0016】

請求項2に記載の発明は、次に書き込むデータの書き込み先を示す第1ポインタと、前に書き込んだデータの書き込み先を示す第2ポインタとをデータに対応付けて記憶する記憶手段と、

該記憶手段からデータを読み出す際に用いたポインタと、該データに対応付けて記憶された第1ポインタにより示されるデータに対応して記憶された第2ポインタとを比較する比較手段と、を有することにより、

回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【0017】

【発明の実施の形態】

図3は、本発明のリンクドリストを用いた記憶装置の第1実施例のブロック構成図を示す。この記憶装置は例えば通信ネットワークのノード装置の入力バッファ等に適用される。

【0018】

同図中、固定長分割回路32は、パケット入力を固定長に分割する。ポインタ付与回路34は、固定長分割された個々のデータに対しポインタ値を付与する。ポインタ保持回路36は、ポインタ付与回路34の出力するポインタ値を一時的に保持する。

【0019】

パリティ演算回路38は、固定長分割された個々のデータ及びポインタ付与回路34の出力するポインタ値に対し故障検出及び連続性検出用のパリティ演算を行う。ここで得られたパリティはパリティ保持回路39で一時的に保持されたのち記憶装置40に供給される。

【0020】

記憶装置40は例えばRAMで構成され、固定長分割された個々のデータと、ポインタ付与回路34の出力するポインタ値(次の書き込みに使用される値)と、パリティ保持回路39の出力するパリティ値(前回の書き込み時に生成された値)とが、ポインタ保持回路36からのポインタ値(前回の書き込み時に生成された値)で指示されるアドレスに書き込まれる。つまり、個々のデータ及びポインタ値に対してパリティ値はずらして記憶装置40に書き込まれる。

【0021】

上記のデータ分割と記憶装置の記録の様子を図4に示す。図4において、パケットデータはデータA,B,C,Dに4分割され、記憶装置40のアドレス#0に、データAと次の書き込みに使用される次ポインタ値#2と前回の書き込み時に生成されたパリティ値が書き込まれる。また、アドレス#2に、データBと次の書き込みに使用される次ポインタ値#5と前回の書き込み時に生成されたパリティ値#0が書き込まれる。同様に、アドレス#5に、データCと次の書き込みに使用される次ポインタ値#4と前回の書き込み時に生成されたパリティ値#2が書き込まれ、アドレス#4に、データDと次の書き込みに使用される次ポインタ値#6と前回の書き込み時に生成されたパリティ値#5が書き込まれる。

【0022】

記憶装置40から前回読み出された次ポインタ値が読みだしアドレスとして記憶装置40に与えられており、これにより記憶装置40から読み出された次ポインタ値が次の読み出しアドレスとして記憶装置40に供給される。

【0023】

また、パリティ演算回路42は、記憶装置40から読み出された個々のデータ及び読み出された次ポインタ値のパリティ演算を行う。得られたパリティ値はパリティ保持回路44で一時的に保持されたのち比較回路46に供給される。比較回路46は記憶装置40から読み出されたパリティ値とパリティ保持回路44で一時的に保持されたパリティ値(前回の書き込み時に生成された値)との一致比較を行う。

【0024】

例えば、記憶装置40のアドレス#0から読み出されたデータA及び次ポインタ値#2をパリティ演算回路42で演算して得られたパリティ値#0がパリティ保持回路44から比較回路46に供給されるタイミングで、記憶装置40のアドレス#2からパリティ値#0が読み出されて比較回路46に供給され、両パリティ値の一致比較が行われる。

【0025】

これにより、個々のデータ及びポインタ値の正常性、すなわち記憶装置40の故障の有無を確認すると共に、前回読み出されたパリティ値(前回の書き込み時に生成された値)と今回読み出された個々のデータ及びポインタ値の連続性を確認している。

【0026】

つまり、個々のデータ及びポインタ値に対してパリティ値はずらして記憶装置に書き込まれているため、上記比較回路46で不一致の場合には、記憶装置40から読み出された個々のデータ及びポインタ値が異常であるか、または、今回読み出された個々のデータ及びポインタ値と前回読み出されたパリティ値との間に連続性がないということであり、このような誤りがあった場合にはリンクエラー信号を出力する。また、記憶装置40から読み出された個々のデータは後続の回路に向けて出力される。

【0027】

この実施例では、パケット組み立て後FCS演算を行う必要がないため、データの処理遅延を削減することができ、回路規模を削減することができる。また、記憶装置40の書き込み側アドレス、または、読み出し側アドレスのビット誤りによりパケットデータの一部が前後入れ替わった場合にも、これを検出することができる。

【0028】

なお、上記実施例ではパリティ演算回路38,42を用いているが、データの正当性を確認できる誤り検出符号であれば何でもよく、例えばCRC演算でも同じ効果を得ることができる。また、記憶装置40に書き込む個々のデータとパリティ演算結果のずれは1アドレスで説明したが、2アドレス以上ずれていても同じ効果を得ることができる。

【0029】

図5は、本発明のリンクドリストを用いた記憶装置の第2実施例のブロック構成図を示す。この記憶装置は例えば通信ネットワークのノード装置の入力バッファ等に適用される。同図中、図3と同一部分には同一符号を付す。

【0030】

図5において、固定長分割回路32は、パケット入力を固定長に分割する。ポインタ付与回路34は、固定長分割された個々のデータに対しポインタ値を付与する。ポインタ保持回路36は、ポインタ付与回路34の出力するポインタ値を一時的に保持する。ポインタ保持回路50は、ポインタ保持回路36の出力するポインタ値を更に一時的に保持されて記憶装置40に供給される。

【0031】

パリティ演算回路38は、固定長分割された個々のデータ及びポインタ付与回路34の出力するポインタ値に対し故障検出及び連続性検出用のパリティ演算を行う。ここで得られたパリティは記憶装置40に供給される。

【0032】

記憶装置40は例えばRAMで構成され、固定長分割された個々のデータと、ポインタ付与回路34の出力する次ポインタ値(次の書き込みに使用される値)と、ポインタ保持回路50の出力する前ポインタ値(前回の書き込みに使用された値)と、パリティ保持回路39の出力するパリティ値(今回の値)とが、ポインタ保持回路36からの現ポインタ値(前回の書き込み時に生成された値)で指示されるアドレスに書き込まれる。つまり、個々のデータ及び次ポインタ値に対して前ポインタ値がずらして記憶装置40に書き込まれる。

【0033】

上記のデータ分割と記憶装置の記録の様子を図6に示す。図6において、パケットデータはデータA,B,C,Dに4分割され、記憶装置40のアドレス#0に、データAと次の書き込みに使用される次ポインタ値#2と前回の書き込みに使用された前ポインタ値と今回のパリティ値#0が書き込まれる。また、アドレス#2に、データBと次の書き込みに使用される次ポインタ値#5と前回の書き込みに使用された前ポインタ値#0と今回のパリティ値#2が書き込まれる。同様に、アドレス#5に、データCと次の書き込みに使用される次ポインタ値#4と前回の書き込みに使用された前ポインタ値#2と今回のパリティ値#5が書き込まれ、アドレス#4に、データDと次の書き込みに使用される次ポインタ値#6と前回の書き込みに使用された前ポインタ値#5と今回のパリティ値#4が書き込まれる。

【0034】

記憶装置40からは前回読み出された次ポインタ値が読みだしアドレスとして与えられており、これにより読み出された次ポインタ値は次の読み出しアドレスとして記憶装置40に供給されると共に、ポインタ保持回路52で一時的に保持されたのち比較回路54に供給される。

【0035】

また、記憶装置40から読み出された前ポインタ値が比較回路54に供給され、比較回路54は記憶装置40から読み出された前ポインタ値とポインタ保持回路52で保持された次ポインタ値との一致比較を行い、今回読み出された個々のデータの連続性を確認して、エラーがあった場合にはリンクエラー信号を出力する。

【0036】

例えば、記憶装置40のアドレス#2を読み出す際にポインタ保持回路52に保持されたアドレス#2が比較回路54に供給されるタイミングに、記憶装置40のアドレス#5から前ポインタ値#2が読み出されて比較回路54に供給され、両ポインタ値の一致比較が行われる。

【0037】

また、パリティ演算回路42は、記憶装置40から読み出された個々のデータ及び読み出された次ポインタ値のパリティ演算を行って個々のデータ及びポインタ値の正常性、すなわち記憶装置40の故障の有無を確認して、エラーがあった場合にはパリティエラー信号を出力する。また、記憶装置40から読み出された個々のデータは後続の回路に向けて出力される。

【0038】

この実施例では、パケット組み立て後FCS演算を行う必要がないため、データの処理遅延を削減することができ、回路規模を削減することができる。また、記憶装置40の書き込み側アドレス、または、読み出し側アドレスのビット誤りによりパケットデータの一部が前後入れ替わった場合にも、これを検出することができる。

【0039】

なお、上記実施例では前ポインタ値そのものを記憶装置40に書き込んでいるが、ポインタ保持回路50,52にパリティ演算機能やCRC演算機能を付け、その演算結果を記憶装置40に書き込んでも同じ効果が得られる。

【0040】

なお、記憶装置40が請求項記載の記憶手段に対応し、比較回路46,54が比較手段に対応する。

【0041】

【発明の効果】

上述の如く、請求項1に記載の発明によれば、回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【0042】

また、請求項2に記載の発明によれば、回路規模を小さくするとともにパケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできる。

【図面の簡単な説明】

【図1】従来のリンクドリストを用いた記憶装置の一例のブロック構成図である。

【図2】従来の構成におけるデータ分割と記憶装置の記録の様子を示す図である。

【図3】本発明のリンクドリストを用いた記憶装置の第1実施例のブロック構成図である。

【図4】第1実施例の構成におけるデータ分割と記憶装置の記録の様子を示す図である。

【図5】本発明のリンクドリストを用いた記憶装置の第2実施例のブロック構成図である。

【図6】第2実施例の構成におけるデータ分割と記憶装置の記録の様子を示す図である。

【符号の説明】

32 固定長分割回路

34 ポインタ付与回路

36 ポインタ保持回路

38,42 パリティ演算回路

39 パリティ保持回路

40 記憶装置

44 パリティ保持回路

46,54 比較回路

50,52 ポインタ保持回路

【特許請求の範囲】

【請求項1】

ポインタのリンクのチェック回路において、

第1のデータから演算した演算結果を該第1のデータのポインタにより示される次の第2のデータに対応させて記憶する記憶手段と、

該記憶手段から読み出した前記第1のデータから演算した演算結果と該読み出した前記第1のデータのポインタにより示される次の第2のデータに対応させて記憶された演算結果を比較する比較手段と、を有することを特徴とするポインタのリンクのチェック回路。

【請求項2】

ポインタのリンクのチェック回路において、

次に書き込むデータの書き込み先を示す第1ポインタと、前に書き込んだデータの書き込み先を示す第2ポインタとをデータに対応付けて記憶する記憶手段と、

該記憶手段からデータを読み出す際に用いたポインタと、該データに対応付けて記憶された第1ポインタにより示されるデータに対応して記憶された第2ポインタとを比較する比較手段と、を有することを特徴とするポインタのリンクのチェック回路。

【請求項1】

ポインタのリンクのチェック回路において、

第1のデータから演算した演算結果を該第1のデータのポインタにより示される次の第2のデータに対応させて記憶する記憶手段と、

該記憶手段から読み出した前記第1のデータから演算した演算結果と該読み出した前記第1のデータのポインタにより示される次の第2のデータに対応させて記憶された演算結果を比較する比較手段と、を有することを特徴とするポインタのリンクのチェック回路。

【請求項2】

ポインタのリンクのチェック回路において、

次に書き込むデータの書き込み先を示す第1ポインタと、前に書き込んだデータの書き込み先を示す第2ポインタとをデータに対応付けて記憶する記憶手段と、

該記憶手段からデータを読み出す際に用いたポインタと、該データに対応付けて記憶された第1ポインタにより示されるデータに対応して記憶された第2ポインタとを比較する比較手段と、を有することを特徴とするポインタのリンクのチェック回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2004−348451(P2004−348451A)

【公開日】平成16年12月9日(2004.12.9)

【国際特許分類】

【出願番号】特願2003−144965(P2003−144965)

【出願日】平成15年5月22日(2003.5.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成16年12月9日(2004.12.9)

【国際特許分類】

【出願日】平成15年5月22日(2003.5.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]