ポイントツーポイント相互接続システム上のセキュアな環境初期化命令の実行

【課題】トラステッドなシステムにおいて、共通の市販のオペレーティングシステムおよびアプリケーションソフトウェアでの同時利用ができるようにする。

【解決手段】セキュアなエンター命令を実行する第1のプロセッサ202と、チップセット240と、第1のプロセッサ202をチップセット240に連結するポイントツーポイントファブリック230と、ポイントツーポイントファブリック230によりチップセット240に連結される第2のプロセッサ212、222と、を含むシステムにおいて、チップセット240はセキュアなエンター命令の実行中に、第2のプロセッサ212、222を休止状態に入らせ、チップセット240が、第2のプロセッサ212、222に休止状態に入らせる信号を送信した後、第2のプロセッサ212、222は、第2のプロセッサ212、222が休止状態に入ったことを知らせる信号をチップセット240に送信する。

【解決手段】セキュアなエンター命令を実行する第1のプロセッサ202と、チップセット240と、第1のプロセッサ202をチップセット240に連結するポイントツーポイントファブリック230と、ポイントツーポイントファブリック230によりチップセット240に連結される第2のプロセッサ212、222と、を含むシステムにおいて、チップセット240はセキュアなエンター命令の実行中に、第2のプロセッサ212、222を休止状態に入らせ、チップセット240が、第2のプロセッサ212、222に休止状態に入らせる信号を送信した後、第2のプロセッサ212、222は、第2のプロセッサ212、222が休止状態に入ったことを知らせる信号をチップセット240に送信する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概してマイクロプロセッサシステムに関しており、より具体的には、トラステッドな、あるいはセキュアな環境で動作できるマイクロプロセッサシステムに関する。

【背景技術】

【0002】

ローカルあるいは遠隔マイクロコンピュータで金融および個人的な取引を行う数の増加が、「トラステッドな」、あるいは「セキュアな」マイクロプロセッサ環境の構築の原動力となってきた。これら環境が解決しようとする課題は、プライバシー欠如、あるいはデータ破損あるいは乱用である。ユーザは自分のプライベートなデータを公にしたくないし、自分のデータを変更されたり、あるいは不適切な処理に利用されたくない。これらの例には、過失による医療記録の流出、あるいはオンライン銀行あるいはその他の保管所からの電子資金盗用が含まれる。同様に、コンテンツプロバイダは、デジタルコンテンツ(例えば、音楽、その他の音声、ビデオ、あるいは他の種類のデータ一般)が許可なくコピーされるのを防ぎたいと思っている。

【0003】

既存のトラステッドなシステムには、完結した一式のトラステッドなソフトウェアが利用されているものがある。この方法は実装が比較的簡単であるが、共通の市販のオペレーティングシステムおよびアプリケーションソフトウェアでの同時利用ができないという不利な点がある。この不利な点により、このようなトラステッドなシステムは受容が限られる。

【0004】

他の方策では、システムが、互いにバスを介して接続されたプロセッサを内蔵することが要求される。

【図面の簡単な説明】

【0005】

本願を、同様の参照番号が同様の部材を示す添付図面において、限定ではなく例示により示す。

【0006】

【図1】マイクロプロセッサシステムで実行される例示的なソフトウェア環境を示す図である。

【0007】

【図2】本発明の一実施形態による、ある例示的なトラステッドな、あるいはセキュアなソフトウェアモジュールおよび例示的なシステム環境を示す図である。

【0008】

【図3】本発明の一実施形態による例示的なトラステッドな、あるいはセキュアなソフトウェア環境を示す図である。

【0009】

【図4】本発明の方法の一実施形態による、ソフトウェアおよびその他の処理ブロックのフローチャートである。

【発明を実施するための最良の形態】

【0010】

以下の記載では、マイクロプロセッサシステムにおけるトラステッドなセキュアな環境を初期化する技法を記載する。以下の記載において、論理実装、ソフトウェアモジュール割り当て、暗号化技法、バス信号化技法、および動作の詳細などの幾多もの特定の詳細を述べて、本発明のより完全な理解を助ける。しかし、本発明がこのような特定の詳細なしに実施できることは当業者であれば理解する。他の場合においては、本発明を曖昧にしないように、制御構造、ゲートレベル回路、および完全なソフトウェア命令列は詳細に示していない。当業者であれば、含めた記載を読めば、必要以上の実験なしに、適切な機能を実装することができる。発明はマイクロプロセッサシステムの形で開示される。しかし、本発明は、デジタル信号プロセッサ、ミニコンピュータ、あるいはメインフレームコンピュータでも実施することができる。

【0011】

図1を参照すると、マイクロプロセッサシステムで実行される例示的ソフトウェア環境を示す図が示されている。図1に示すソフトウェアはトラステッドでない(アントラステッド)。高優先度レベルで動作する際、オペレーティングシステム150のサイズおよび定期的な更新により、任意のトラステッドな分析を適時に実施することが非常に難しくなる。オペレーティングシステムの多くが、優先度が最大レベルである優先度リングゼロ(0)に在る。アプリケーション152、154、156は、これよりずっと低い優先度を持ち、典型的に優先度リング3に在る。異なる優先度リングが在ること、およびオペレーティングシステム150およびアプリケーション152、154、156をこれら異なる優先度リングに分類することで、オペレーティングシステム150が提供する機能の信頼性に関する決定に基づき、トラステッドなモードで図1のソフトウェアの動作を行うことができるように一見思われる。しかし実際上は、このような信頼性に関する決定はしばしば実用的ではない。この課題を生じる要素には、オペレーティングシステム150のサイズ(コードのライン数)、オペレーティングシステム150が幾らもの更新(新たなコードモジュールおよびパッチ)を受信する可能性があるという事実、およびオペレーティングシステム150が、オペレーティングシステムの開発業者以外の者が供給するデバイスドライバなどのコードモジュールを含みうるという事実、などがある。オペレーティングシステム150は、Microsoft(登録商標)、Windows(登録商標)、Linux、あるいはSolaris(登録商標)などの一般的なもの、あるいは任意の他の適切な既知の、あるいは入手可能なオペレーティングシステムであってよい。特定の種類のあるいは名称のアプリケーションあるいはオペレーティングシステムの運用は重要ではない。

【0012】

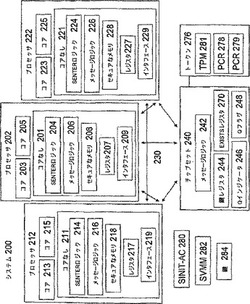

図2を参照すると、ある例示的なトラステッドな、あるいはセキュアなソフトウェアモジュールおよび例示的なシステム環境200が示されている。図2の実施形態においては、プロセッサ202、プロセッサ212、プロセッサ222、およびオプションとして他のプロセッサ(不図示)を別個のハードウェア資源として示している。図2は三つのプロセッサを示しているが、本発明の実施形態は任意の数のプロセッサを含みえ、これは単一のプロセッサをも含みうる。

【0013】

システム200はさらに、下に示す任意の他のシステムあるいは他のロジックとともに、入力/出力(I/O)コントローラあるいはハブを含みうるチップセット240を含む。他の実施形態は、図2に示す部材の代わりに、あるいはそれに加えて、他の部材を含みえ、これら任意の数のプロセッサあるいは他の部材は、それらの互いに対する配置などで異なっていてよい。

【0014】

プロセッサ202、212、222は、コア203、205、213、215、223、および225など、一以上の実行コアを含みうる。幾らかの実施形態においては、プロセッサあるいはコアを、一以上の物理的プロセッサあるいはコア上で動作する別個のハードウェア実行スレッドで置き換えてもよい。これらスレッドは、追加的な物理的プロセッサの属性の多くを所有する。多数の物理的プロセッサおよびプロセッサ上の多数のスレッドを任意に組み合わせて説明する便宜上の一般的表現として「論理プロセッサ」という用語を利用して、一つの物理的プロセッサあるいは一以上の物理的プロセッサで動作するスレッドを記載する。故に、一つのシングルスレッドプロセッサは論理プロセッサとして考えられ、マルチスレッドあるいはマルチコアプロセッサは多数の論理プロセッサとして考えられうる。

【0015】

プロセッサ202、212、222はさらに、コアなしロジック201、211、および221などの「コアなし」ロジックを含みえ、ここで「コアなし」ロジックは、実行コアのうちのいずれからも別離されるロジックである。コアなしロジックは、そこにあるプロセッサに関する情報を記憶するのに利用されうるレジスタ207、217、227などの、レジスタ、あるいは任意のほかの記憶位置を含みうる。これらレジスタあるいは記憶位置はプログラムできる、あるいはハードコードされえ、このような情報は、対応するプロセッサに含まれる数のコアおよび/または論理プロセッサを含みうる。レジスタ207、217、227は、電源投入時のリセット中に更新される標準グローバルメモリマップレジスタ(standard global memory mapped register)であってよい。

【0016】

プロセッサ202、212、222はさらに、セキュアなあるいはトラステッドな動作を支援する特別な回路あるいは論理部材を含みうる。例えば、プロセッサ202は、安全入力(SENTER)ロジック204を含むことで、トラステッドな動作を始めうる特別なSENTER命令の実行を支援しうる。プロセッサ202はさらに、特別なSENTER動作を支援すべくプロセッサおよび他の部材間の特別な相互接続メッセージを支援すべく相互接続メッセージロジック206を含みうる。特別な相互接続メッセージは、システムの安全性あるいは信頼性を様々な理由から増加させうる。プロセッサ202、212、222、あるいはチップセット240などの回路部材は、それらが本開示の実施形態の適切な論理部材を含む場合にのみ、このようなメッセージを発行しうる、あるいはそれに対して応答しうる。従って、特別な相互接続メッセージの交換を成功させることで、適切なシステム構成の確保を助けうる。特別な相互接続メッセージはさらに、プラットフォーム構成レジスタ278のリセットなどの、通常は禁止されているべきアクティビティを許可しうる。潜在的に敵意のある信用のおかれないコードがある相互接続処理上でスパイをする能力は、特別な相互接続メッセージを、特別な安全命令に対して発行することで、削減されうる。SENTERロジック204、相互接続メッセージロジック206、および本発明の実施形態で利用される任意の他のロジックは、ロジック回路、マイクロコード、およびファームウェアを含む任意の既知の方策により実装されうる。

【0017】

さらに、プロセッサ202は、セキュアな初期化動作を支援すべくセキュアなメモリ208を含みうる。一実施形態においては、セキュアなメモリ208は、特別なモードで動作してもよいプロセッサ202の内部キャッシュであってよい。代替実施形態においては、セキュアなメモリ208は特別なメモリであってよい。プロセッサ212およびプロセッサ222などの他のプロセッサはさらに、SENTERロジック214、224、バスメッセージロジック216、226、およびセキュアなメモリ218、228を含みうる。

【0018】

「チップセット」は、接続プロセッサ(一または複数)用のメモリおよび/またはI/O動作を支援する一群の回路およびロジックとして定義されうる。一つのチップセットの個々の部材は、単一のチップ、一対のチップ上にまとめられてよく、あるいは多数のプロセッサを含む多数のチップ間で分散されてもよい。図2の実施形態においてチップセット240は、プロセッサ202、212、222のI/O動作を支援する回路およびロジックを含みうるが、ここで各プロセッサはメモリ動作を支援する回路およびロジックを含む。その代わりに、チップセット240はさらに、プロセッサ202、212、222のメモリ動作を支援する回路およびロジックを含みうる。チップセット240の機能は、代替実施形態においては、一以上の物理デバイス間に割り当てられうる。

【0019】

チップセット240はさらに、特別なSENTER動作を支援するPTPファブリック230上の特別な相互メッセージを支援すべく、自身の相互接続メッセージロジック242を含みうる。これら特別な相互接続メッセージには、鍵レジスタ244の内容をプロセッサ202、212、あるいは222に対して転送することで、プロセッサに対して、特別な「QUIESCE」インジケータ246を設定あるいはクリアして、チップセット240に、システム200をquieseあるいはde−quieseさせる、あるいはプロセッサにより特別な「QUIESCED」フラグ248を検査させることを許可することを含みうる。バスメッセージロジック242のさらなる特徴は、「EXISTS」レジスタ270内のシステム200のプロセッサの存在あるいは参加をレジスタすることであってよい。

【0020】

プロセッサ202、212、222は互いに、チップセット240に対して、および任意の他の部材あるいはエージェントに対して、ポイントツーポイント(PTP)相互接続ファブリック230により接続されてよい。プロセッサ202、212、および222、およびチップセット240は、PTPファブリック230に接続すべく、および互いに対しておよびシステム200に存在あるいは参加する任意の他のエージェントに対してメッセージを送受信すべく、それぞれインタフェースユニット209、219、229、および239の各々を含んでよい。インタフェースユニット209、219、229、および239の各々は、任意の数の他の部材と通信する任意の数の一方向性および/または双方向性ポートを含みうる。通信は、任意のあるいは全てのリンク層、プロトコル層、ルーティング層、搬送層、物理層、および任意の他の同様の層によりフレームされたメッセージおよび/またはデータを表す信号を含むパケットがエージェント間で(ポイントツーポイント)送信される層型のポイントツーポイント相互接続アーキテクチャによりPTPファブリック230を介して行われる。故に、インタフェースユニット209、219、229、および239の各々は、各層に対応する信号を生成する回路あるいはロジックを含みうる。パケットはさらに、検知あるいはエラー訂正用の、重複するあるいは他の情報を含みうる。

【0021】

トークン276は、一以上のプラットフォーム構成レジスタ(PCR)278、279を含み、チップセット230に接続されてよい。一実施形態においては、トークン276は、特別な安全フィーチャを含みえ、一実施形態では、TCPA(www.trustedpc.comから入手可能)発行の2001年12月1日付けのバージョン1.1a、Trusted Computing Platform Alliance(TCPA)Main Specificationに開示されている、トラステッドなプラットフォームモジュール(TPM)281を含みうる。

【0022】

システム環境200で識別される二つのソフトウェア部材は、Secure Virtual Machine Monitor(SVMM)282モジュールおよびSecure Initialization Authenticated Code(SINIT−AC)280モジュールである。SVMM282モジュールは、システムディスクあるいは他の大容量記憶装置に記憶でき、必要に応じて他の場所に移動あるいはコピーされうる。一実施形態においては、セキュアな起動プロセス開始の前に、SVMM282を、システム200内の一以上のメモリページに移動あるいはコピーしてよい。セキュアなエンタープロセスに続いて、SVMM282がシステム内で最も優先度の高いコードとして動作し得る仮想マシン環境が作成され得、作成された仮想マシン内のオペレーティングシステムあるいはアプリケーションによりあるシステム資源への直接アクセスが許可あるいは否認するのに利用され得る。

【0023】

セキュアなエンタープロセスが必要とするアクションの幾らかは、簡単なハードウェア実装の範囲を超える場合があり、代わりに実行が暗に信用されうるソフトウェアモジュールを利用することができるという利点がある。一実施形態においては、これらアクションはAuthenticated(SINIT)Codeとして実行されうる。一例示的アクションは、セキュアな環境の正しいインタスタンス化を支援する構成を確保すべく、システム構成の重要な部分を表す様々な制御を必要としうる。第2の例示的アクションは、SVMM282モジュールの識別情報を算出およびレジスタして、それへのシステム制御を転送することを含む。ここで、「レジスタ」とは、SVMM282の信頼尺度を、例えばPCR278あるいはPCR279などのレジスタあるいは他の記憶位置に配置することを意味する。この第2のアクションがとられると、SVMM282の信頼性が潜在的なシステムユーザにより調査されうる。

【0024】

SINITコードは、プロセッサあるいはチップセットの製造業者により作成されうる。この理由から、SINITコードはチップセット240のセキュアな起動の支援を信頼される。SINITコードを分配すべく、一実施形態においては、公知の暗号ハッシュが全SINITコードからなっており、これにより「ダイジェスト」として知られている値を生成する。一実施形態においては、ダイジェストは160ビット値を生成する。ダイジェストは、その後、秘密鍵により暗号化され、一実施形態においてはプロセッサの製造業者により保持され、デジタル署名を形成しうる。SINITコードは対応するデジタル署名により束ねられると、この組み合わせがSINIT認証コード(SINIT−AC)280として言及されうる。以下に記載するようにSINIT−AC280のコピーは後に有効性を確認される(validate)。

【0025】

SINIT−AC280は、システムディスクあるいは他の大容量記憶装置あるいは固定媒体に記憶され得、必要に応じて他の位置に移動あるいはコピーされ得る。一実施形態においては、セキュアな起動プロセスの開始前に、SINIT−AC280をシステム200の一以上のメモリページに移動あるいはコピーして、SINIT−ACのメモリレジデントコピーを形成しうる。

【0026】

オペレーティングシステムなどのシステム200上で動く任意の優先ソフトウェアは、論理プロセッサ上のセキュアな起動プロセスを開始してよく、これは開始論理プロセッサ(initiating logical processor)(ILP)と称される。本例のプロセッサ202はILPであるが、PTPファブリック230上の任意のプロセッサもILPである場合がある。SINIT−AC280のメモリレジデントコピーもSVMM282のメモリレジデントコピーもいずれも、今回信頼性があるとして考慮され得ない。

【0027】

ILP(プロセッサ202)はセキュアな起動プロセスを開始すべく特別な命令を実行する。この特別な命令はセキュアなエンター(SENTER)命令として証され得、SENTERロジック204により支援され得る。SENTER命令は第1にシステム200の全ての論理プロセッサがチップセット240(例えばEXISTSレジスタ270)に登録されているかを検証する。各プロセッサおよび、PTPファブリック230に接続される他のエージェントは、レジスタ207、217、および227などのレジスタあるいは他の記憶位置を含み、自身の含む論理プロセッサの数を示す。これらレジスタは読み出されて、システムトポロジーが正確にチップセット240で表されているかを検証する。

【0028】

この検証の後、SENTER命令はQUIESCEインジケータ246に書き込み、チップセット240に対してシステム200を休止させる(quiesce)。チップセット240はPTPファブリック230上でハンドシェイク列を開始して、一つのプロセッサ(休止状態マスター)を除く、PTPファブリック230上の全てのプロセッサおよび他のエージェントに休止状態に入らせる。本実施形態においては、プロセッサ202がILPであるとともに休止状態マスターである。休止列は「STOP_REQ」信号をマスターでないプロセッサに対して各々送信して、各マスターでないプロセッサのイベント処理を終了させ、それらのバッファをドレインさせ、「STOP_ACK」信号をチップセット240に戻してそれらが休止状態に入ったことを承認させる。休止状態は、命令を何ら実行せず、PTPファブリック230上に処理を何ら生成しない状態のことである。チップセット240がチップセット240に登録されている全ての論理プロセッサを代表してSTOP_ACK信号を各エージェントから受信した後、QUIESCEDフラグ248が設定されてよい。マスターのプロセッサは、セキュアな初期化認証モジュールを実行する前に休止状態に入ったことを検証すべくチップセット内のインジケータレジスタを読み出してよい。また、セキュアな仮想マシン監視モジュールを実行する前に休止状態に入ったことを検証すべくチップセット内のインジケータレジスタを読み出してよい。

【0029】

システムが休止した後、SENTER命令が安全モジュールを安全に実行しうることを以下に記す。この目的上、PTPファブリック230は依然機能的であり、TPM281は依然休止状態マスターに対して入手できる。安全モジュールの実行が完了すると、休止状態マスターはQUIESCEインジケータ246をクリアして、チップセット240に対してシステム200を休止状態から抜けさせる。

【0030】

安全モジュールを実行すべく、ILP(プロセッサ202)は、SINIT‐AC280に含まれるSINITコードを認証およびその後実行する目的から第1にSINIT−AC280および鍵284の写し両方をセキュアなメモリ208に移動しうる。一実施形態においては、このセキュアなメモリ208は、ILP(プロセッサ202)の内部キャッシュであってよく、特別なモードで動作していてよい。鍵284はSINIT−AC280モジュールに含まれるデジタル署名を暗号化するのに利用される秘密鍵に対応する公開鍵を表しており、デジタル署名を検証してSINITコードを認証するのに利用される。一実施形態においては、鍵284は、場合としてはSENTERロジック204の一部としてプロセッサに予め記憶されている場合もある。別の実施形態においては、鍵284はチップセット240の読み出し専用鍵レジスタ244に記憶され、ILPより読み出されてよい。また別の実施形態においては、プロセッサあるいはチップセットの鍵レジスタ244は、実際に鍵284の暗号化ダイジェストを保持していてよく、ここで鍵284そのものがSINIT−AC280モジュールに含まれている。この最後の実施形態においては、ILPは鍵レジスタ244からダイジェストを読み出し、SINIT−AC280に埋め込まれた鍵284の等価暗号化ハッシュ(equivalent cryptographic hash)を算出して、二つのダイジェストを比較し、供給された鍵284が実際にトラステッドか確かめる。

【0031】

SINIT−ACのコピーおよび公開鍵のコピーはセキュアなメモリ208内に存在してよい。ILPは公開鍵のコピーを利用してSINIT−ACのコピーに含まれるデジタル署名を復号することでSINIT−ACの写しが有効性を確認される。この復号により、暗号化ハッシュダイジェストの原本を生成する。新たに算出されたダイジェストがこの原ダイジェストに整合している場合、SINIT−ACのコピーおよびそれに含まれるSINITコードはトラステッドであると考えられる。

【0032】

ILPは、以下に概略を示すように、セキュアなトークン276内のプラットフォーム構成レジスタ272に対してSINIT−ACモジュールの暗号化ダイジェスト値を書き込むことで、SINIT−ACモジュールの唯一の識別情報を登録する。SENTER命令のILP実行は、ILPのセキュアなメモリ208内に保持されるSINITコードのトラステッドなコピーに実行制御を転送することで終了しうる。トラステッドなSINITコードはシステムテストおよび構成アクションを実行して、上述のレジスタの定義に則りSVMMのメモリレジデントコピーを登録してよい。

【0033】

SVMMのメモリレジデントコピーの登録は、幾らかの方法で行うことができる。一実施形態においては、ILP上で動くSENTER命令は、安全トークン276内のPCR278にSINIT−ACの算出されたダイジェストを書き込む。次に、トラステッドなSINITコードは、メモリレジデントSVMMの算出されたダイジェストを、同じPCR278あるいは安全トークン276内の別のPCR279に書き込むことができる。SVMMダイジェストが同じPCR278に書き込まれる場合、安全トークン276は、新たな値(SVMMダイジェスト)で原コンテンツ(SINITダイジェスト)をハッシュして、結果をPCR278に書き込む。第1(初期化)のPCR278への書き込みがSENTER命令に限定される実施形態においては、結果であるダイジェストはシステムの信頼ルート(a root of trust)として利用されうる。

【0034】

トラステッドなSINITコードはその実行を完了して、SVMMの識別情報をPCRに登録すると、SINITコードはILP実行制御をSVMMに転送しうる。典型的な実施形態においては、ILPにより実行される第1のSVMM命令は、SVMMの初期化ルーチンを表しうる。システム200は、以下の図3の説明で概略を示すように、目下実行しているSVMMのコピーの監督下で、トラステッドなモードで動作することができる。ここからは、システム全体は、以下の図3の説明で概略を示すように、トラステッドなモードで動作することができる。

【0035】

図3を参照すると、本発明の一実施形態による例示的なトラステッドなあるいはセキュアなソフトウェア環境が示されている。図3の実施形態においては、トラステッドなソフトウェアおよびトラステッドでないソフトウェアは、同時にロードされて同時に単一のコンピュータシステム上で実行されうる。SVMM350は、一以上のトラステッドでないオペレーティングシステム340およびトラステッドでないアプリケーション310〜330からハードウェア資源380への直接アクセスを選択的に許可あるいは禁止する。この文脈において、「トラステッドでない」とは、必ずしもオペレーティングシステムあるいはアプリケーションが故意に不正を行っていることを意味するとは限らず、相互作用するコードのサイズおよび種類により、ソフトウェアが所望の通りに行動すること、およびこの実行に干渉するウィルスあるいは他の異質のコードがないこと、を確実にアサートすることが実際的でないことを意味する。典型的な実施形態においては、トラステッドでないコードは、今日のパーソナルコンピュータで見られる通常のオペレーティングシステムおよびアプリケーションからなる場合がある。

【0036】

SVMM350はさらに、一以上のトラステッドなあるいはセキュアなカーネル360から、および一以上のトラステッドなアプリケーション370から、ハードウェア資源380への直接アクセスを選択的に許可あるいは禁止する。このようなトラステッドな、あるいはセキュアなカーネル360およびトラステッドなアプリケーション370は、トラステッドな分析をそれに対して行う能力を支援すべく寸法および機能が限られうる。トラステッドなアプリケーション370は、セキュアな環境下で実行可能な任意のソフトウェアコード、プログラム、ルーチン、あるいは一式のルーチンでありうる。故に、トラステッドなアプリケーション370は、様々なアプリケーション、あるいはコード列でありえ、あるいはJavaアプレットのような比較的小さいアプリケーションでありえる。

【0037】

システム資源保護あるいは優先度を変更しうるオペレーティングシステム340あるいはカーネル360により通常実行される命令あるいは動作は、SVMM350によりトラップ、選択的に許可、部分的に許可、あるいは拒絶されうる。一例として、典型的な実施形態においては、このかわりに、通常オペレーティングシステム340あるいはカーネル360により実行されるプロセッサのページテーブルの変更命令が、SVMM350によりトラップされえ、これにより、要求が仮想マシンのドメイン外でページ優先度を変更しようと試みなかったことを確かめうる。

【0038】

図4を参照すると、本発明の一実施形態における方法400におけるソフトウェアおよび他のプロセスブロックのフローチャートが示されている。

【0039】

方法400のブロック410において論理プロセッサは、後続のSENTER命令によりアクセス可能なSINIT−ACおよびSVMMモジュールのコピーを作成する。本例においては、ILPはSINIT−ACおよびSVMMコードを大容量記憶装置から物理メモリにロードする。代替的実施形態においては、ILPだけでなくて任意の論理プロセッサがこれを行ってよい。プロセッサは、ブロック412で示されるように、SENTER命令を実行することでILPとなる。

【0040】

ブロック420においては、SENTER命令は、システム200内の全ての論理プロセッサがチップセット240に(例えばEXISTSレジスタ270に)登録されているか検証する。チップセットは、ポイントツーポイントファブリックに連結されるプロセッサを含むエージェントのリストを維持する。ブロック422において、SENTER命令は、QUIESCEインジケータ246に書き込んで、チップセット240にシステム200を休止させる。ブロック424において、チップセット240は、「STOP_REQ」信号を各マスターでないプロセッサに送り、各マスターでないプロセッサにそれらの処理を終了させ、それらのバッファをドレインさせ、「STOP_ACK」信号をチップセット240に戻してそれらが休止状態に入ったことを通知する。ブロック426において、QUIESCEDフラグ248を設定して、チップセット240がSTOP_ACK信号を、チップセット240に登録されている全ての論理プロセッサを代表して、全てのエージェントから受信したことを示す。

【0041】

ブロック430において、ILPはチップセットの公開鍵およびSINIT−ACのメモリレジデントコピーを、安全に実行すべく自身のセキュアなメモリに移動する。ブロック432において、ILPは鍵を使ってSINIT−ACのセキュアなメモリレジデントコピーの有効性を確認して実行する。SINIT−ACの実行により、システム構成およびSVMMコピーのテストを行ってよく、その後SVMMの識別情報を登録して、最後にブロック434にてSVMMの実行を開始する。ブロック436において、休止状態のマスターはWUIESCEインジケータ246をクリアして、ブロック438でチップセット240に対してシステム200を休止状態から復帰させる。

【0042】

以下に本発明の実施形態の一例を示す。

[実施形態1]

システムであって、

セキュアなエンター命令を実行する第1のプロセッサと、

前記セキュアなエンター命令の実行中に、前記システムを休止状態に入らせるチップセットと、を含むシステム。

[実施形態2]

前記第1のプロセッサを前記チップセットに連結するポイントツーポイントファブリックをさらに含む、実施形態1に記載のシステム。

[実施形態3]

前記ポイントツーポイントファブリックにより前記チップセットに連結される第2のプロセッサをさらに含み、

前記チップセットは、前記セキュアなエンター命令の実行中に、さらに前記第2のプロセッサを前記休止状態に入らせる、実施形態2に記載のシステム。

[実施形態4]

前記チップセットは、さらに前記システムを、前記第1のプロセッサおよび前記チップセットだけが前記ポイントツーポイントファブリックを介して通信する前記休止状態に入らせる、実施形態2に記載のシステム。

[実施形態5]

トラステッドなプラットフォームモジュールをさらに含み、

前記トラステッドなプラットフォームモジュールは前記休止状態中に前記第1のプロセッサにアクセス可能である、実施形態1に記載のシステム。

[実施形態6]

前記第1のプロセッサは、セキュアな初期化認証コードモジュールをさらに実行する、実施形態1に記載のシステム。

[実施形態7]

前記第1のプロセッサは、セキュアな仮想マシン監視モジュールをさらに実行する、実施形態1に記載のシステム。

[実施形態8]

前記チップセットは、前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なインジケータを含む、実施形態1に記載のシステム。

[実施形態9]

前記チップセットは、

前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なインジケータと、

前記システムの各プロセッサの識別情報を示す第1の記憶位置と、を含み、

前記第2のプロセッサは、前記第2のプロセッサが前記ポイントツーポイントファブリックに接続されていることを示す第2の記憶位置を含み、

前記第1のプロセッサは、前記チップセットに前記システムを前記休止状態に入らせるべく前記インジケータにアクセスする前に前記第2のプロセッサの識別情報(identity)が前記第1の記憶位置に示されていることを検証するロジックを含む、実施形態3に記載のシステム。

[実施形態10]

ポイントツーポイントファブリックを介してチップセットに連結される第1のプロセッサ上で、セキュアなエンター命令の実行を開始することと、

セキュアなエンター命令の実行中に、前記チップセットに、前記ポイントツーポイントファブリックに連結される第2のプロセッサを休止状態に入らせることと、を含む方法。

[実施形態11]

前記チップセットが、前記ポイントツーポイントファブリックに連結されるエージェントのリストを維持することをさらに含む、実施形態10に記載の方法。

[実施形態12]

前記第2のプロセッサを介して前記ポイントツーポイントファブリックに連結されるエージェントの数を識別する、前記第2のプロセッサ内の記憶位置を読み出すことをさらに含む、実施形態11に記載の方法。

[実施形態13]

前記休止状態中に前記第1のプロセッサが、トラステッドなプラットフォームモジュールにアクセスすることをさらに含む、実施形態10に記載の方法。

[実施形態14]

セキュアな初期化認証モジュールを実行することをさらに含む、実施形態13に記載の方法。

[実施形態15]

前記セキュアな初期化認証モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータを読み出すことをさらに含む、実施形態14に記載の方法。

[実施形態16]

セキュアな仮想マシン監視モジュールを実行することをさらに含む、実施形態13に記載の方法。

[実施形態17]

前記セキュアな仮想マシン監視モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータを読み出すことをさらに含む、実施形態16に記載の方法。

[実施形態18]

前記休止状態に入る前に、前記第2のプロセッサに、自身のイベント処理を終了させ、自身のバッファをドレインさせることをさらに含む、実施形態10に記載の方法。

[実施形態19]

前記休止状態に入ったことを通知すべく前記チップセットに信号を送る前記第2のプロセッサをさらに含む、実施形態18に記載の方法。

[実施形態20]

セキュアな動作の初期化を呼び出すべく第1の命令を実行するセキュアなエンターロジックと、

チップセットに対して、ポイントツーポイントファブリックを介して前記チップセットに連結されるエージェントを休止状態に入らせる相互接続メッセージロジック(interconnection messaging logic)と、を含むプロセッサ。

前述の記載において、本発明を特定の例示的実施形態により記載してきた。しかし、添付請求項に示す本発明の幅広い精神および範囲から逸脱しない範囲で、様々な変形例および変更例を考えられることが明らかである。故に、明細書および図面は、限定的な意味ではなくて例示的な意味で捉えられるべきである。

【技術分野】

【0001】

本発明は、概してマイクロプロセッサシステムに関しており、より具体的には、トラステッドな、あるいはセキュアな環境で動作できるマイクロプロセッサシステムに関する。

【背景技術】

【0002】

ローカルあるいは遠隔マイクロコンピュータで金融および個人的な取引を行う数の増加が、「トラステッドな」、あるいは「セキュアな」マイクロプロセッサ環境の構築の原動力となってきた。これら環境が解決しようとする課題は、プライバシー欠如、あるいはデータ破損あるいは乱用である。ユーザは自分のプライベートなデータを公にしたくないし、自分のデータを変更されたり、あるいは不適切な処理に利用されたくない。これらの例には、過失による医療記録の流出、あるいはオンライン銀行あるいはその他の保管所からの電子資金盗用が含まれる。同様に、コンテンツプロバイダは、デジタルコンテンツ(例えば、音楽、その他の音声、ビデオ、あるいは他の種類のデータ一般)が許可なくコピーされるのを防ぎたいと思っている。

【0003】

既存のトラステッドなシステムには、完結した一式のトラステッドなソフトウェアが利用されているものがある。この方法は実装が比較的簡単であるが、共通の市販のオペレーティングシステムおよびアプリケーションソフトウェアでの同時利用ができないという不利な点がある。この不利な点により、このようなトラステッドなシステムは受容が限られる。

【0004】

他の方策では、システムが、互いにバスを介して接続されたプロセッサを内蔵することが要求される。

【図面の簡単な説明】

【0005】

本願を、同様の参照番号が同様の部材を示す添付図面において、限定ではなく例示により示す。

【0006】

【図1】マイクロプロセッサシステムで実行される例示的なソフトウェア環境を示す図である。

【0007】

【図2】本発明の一実施形態による、ある例示的なトラステッドな、あるいはセキュアなソフトウェアモジュールおよび例示的なシステム環境を示す図である。

【0008】

【図3】本発明の一実施形態による例示的なトラステッドな、あるいはセキュアなソフトウェア環境を示す図である。

【0009】

【図4】本発明の方法の一実施形態による、ソフトウェアおよびその他の処理ブロックのフローチャートである。

【発明を実施するための最良の形態】

【0010】

以下の記載では、マイクロプロセッサシステムにおけるトラステッドなセキュアな環境を初期化する技法を記載する。以下の記載において、論理実装、ソフトウェアモジュール割り当て、暗号化技法、バス信号化技法、および動作の詳細などの幾多もの特定の詳細を述べて、本発明のより完全な理解を助ける。しかし、本発明がこのような特定の詳細なしに実施できることは当業者であれば理解する。他の場合においては、本発明を曖昧にしないように、制御構造、ゲートレベル回路、および完全なソフトウェア命令列は詳細に示していない。当業者であれば、含めた記載を読めば、必要以上の実験なしに、適切な機能を実装することができる。発明はマイクロプロセッサシステムの形で開示される。しかし、本発明は、デジタル信号プロセッサ、ミニコンピュータ、あるいはメインフレームコンピュータでも実施することができる。

【0011】

図1を参照すると、マイクロプロセッサシステムで実行される例示的ソフトウェア環境を示す図が示されている。図1に示すソフトウェアはトラステッドでない(アントラステッド)。高優先度レベルで動作する際、オペレーティングシステム150のサイズおよび定期的な更新により、任意のトラステッドな分析を適時に実施することが非常に難しくなる。オペレーティングシステムの多くが、優先度が最大レベルである優先度リングゼロ(0)に在る。アプリケーション152、154、156は、これよりずっと低い優先度を持ち、典型的に優先度リング3に在る。異なる優先度リングが在ること、およびオペレーティングシステム150およびアプリケーション152、154、156をこれら異なる優先度リングに分類することで、オペレーティングシステム150が提供する機能の信頼性に関する決定に基づき、トラステッドなモードで図1のソフトウェアの動作を行うことができるように一見思われる。しかし実際上は、このような信頼性に関する決定はしばしば実用的ではない。この課題を生じる要素には、オペレーティングシステム150のサイズ(コードのライン数)、オペレーティングシステム150が幾らもの更新(新たなコードモジュールおよびパッチ)を受信する可能性があるという事実、およびオペレーティングシステム150が、オペレーティングシステムの開発業者以外の者が供給するデバイスドライバなどのコードモジュールを含みうるという事実、などがある。オペレーティングシステム150は、Microsoft(登録商標)、Windows(登録商標)、Linux、あるいはSolaris(登録商標)などの一般的なもの、あるいは任意の他の適切な既知の、あるいは入手可能なオペレーティングシステムであってよい。特定の種類のあるいは名称のアプリケーションあるいはオペレーティングシステムの運用は重要ではない。

【0012】

図2を参照すると、ある例示的なトラステッドな、あるいはセキュアなソフトウェアモジュールおよび例示的なシステム環境200が示されている。図2の実施形態においては、プロセッサ202、プロセッサ212、プロセッサ222、およびオプションとして他のプロセッサ(不図示)を別個のハードウェア資源として示している。図2は三つのプロセッサを示しているが、本発明の実施形態は任意の数のプロセッサを含みえ、これは単一のプロセッサをも含みうる。

【0013】

システム200はさらに、下に示す任意の他のシステムあるいは他のロジックとともに、入力/出力(I/O)コントローラあるいはハブを含みうるチップセット240を含む。他の実施形態は、図2に示す部材の代わりに、あるいはそれに加えて、他の部材を含みえ、これら任意の数のプロセッサあるいは他の部材は、それらの互いに対する配置などで異なっていてよい。

【0014】

プロセッサ202、212、222は、コア203、205、213、215、223、および225など、一以上の実行コアを含みうる。幾らかの実施形態においては、プロセッサあるいはコアを、一以上の物理的プロセッサあるいはコア上で動作する別個のハードウェア実行スレッドで置き換えてもよい。これらスレッドは、追加的な物理的プロセッサの属性の多くを所有する。多数の物理的プロセッサおよびプロセッサ上の多数のスレッドを任意に組み合わせて説明する便宜上の一般的表現として「論理プロセッサ」という用語を利用して、一つの物理的プロセッサあるいは一以上の物理的プロセッサで動作するスレッドを記載する。故に、一つのシングルスレッドプロセッサは論理プロセッサとして考えられ、マルチスレッドあるいはマルチコアプロセッサは多数の論理プロセッサとして考えられうる。

【0015】

プロセッサ202、212、222はさらに、コアなしロジック201、211、および221などの「コアなし」ロジックを含みえ、ここで「コアなし」ロジックは、実行コアのうちのいずれからも別離されるロジックである。コアなしロジックは、そこにあるプロセッサに関する情報を記憶するのに利用されうるレジスタ207、217、227などの、レジスタ、あるいは任意のほかの記憶位置を含みうる。これらレジスタあるいは記憶位置はプログラムできる、あるいはハードコードされえ、このような情報は、対応するプロセッサに含まれる数のコアおよび/または論理プロセッサを含みうる。レジスタ207、217、227は、電源投入時のリセット中に更新される標準グローバルメモリマップレジスタ(standard global memory mapped register)であってよい。

【0016】

プロセッサ202、212、222はさらに、セキュアなあるいはトラステッドな動作を支援する特別な回路あるいは論理部材を含みうる。例えば、プロセッサ202は、安全入力(SENTER)ロジック204を含むことで、トラステッドな動作を始めうる特別なSENTER命令の実行を支援しうる。プロセッサ202はさらに、特別なSENTER動作を支援すべくプロセッサおよび他の部材間の特別な相互接続メッセージを支援すべく相互接続メッセージロジック206を含みうる。特別な相互接続メッセージは、システムの安全性あるいは信頼性を様々な理由から増加させうる。プロセッサ202、212、222、あるいはチップセット240などの回路部材は、それらが本開示の実施形態の適切な論理部材を含む場合にのみ、このようなメッセージを発行しうる、あるいはそれに対して応答しうる。従って、特別な相互接続メッセージの交換を成功させることで、適切なシステム構成の確保を助けうる。特別な相互接続メッセージはさらに、プラットフォーム構成レジスタ278のリセットなどの、通常は禁止されているべきアクティビティを許可しうる。潜在的に敵意のある信用のおかれないコードがある相互接続処理上でスパイをする能力は、特別な相互接続メッセージを、特別な安全命令に対して発行することで、削減されうる。SENTERロジック204、相互接続メッセージロジック206、および本発明の実施形態で利用される任意の他のロジックは、ロジック回路、マイクロコード、およびファームウェアを含む任意の既知の方策により実装されうる。

【0017】

さらに、プロセッサ202は、セキュアな初期化動作を支援すべくセキュアなメモリ208を含みうる。一実施形態においては、セキュアなメモリ208は、特別なモードで動作してもよいプロセッサ202の内部キャッシュであってよい。代替実施形態においては、セキュアなメモリ208は特別なメモリであってよい。プロセッサ212およびプロセッサ222などの他のプロセッサはさらに、SENTERロジック214、224、バスメッセージロジック216、226、およびセキュアなメモリ218、228を含みうる。

【0018】

「チップセット」は、接続プロセッサ(一または複数)用のメモリおよび/またはI/O動作を支援する一群の回路およびロジックとして定義されうる。一つのチップセットの個々の部材は、単一のチップ、一対のチップ上にまとめられてよく、あるいは多数のプロセッサを含む多数のチップ間で分散されてもよい。図2の実施形態においてチップセット240は、プロセッサ202、212、222のI/O動作を支援する回路およびロジックを含みうるが、ここで各プロセッサはメモリ動作を支援する回路およびロジックを含む。その代わりに、チップセット240はさらに、プロセッサ202、212、222のメモリ動作を支援する回路およびロジックを含みうる。チップセット240の機能は、代替実施形態においては、一以上の物理デバイス間に割り当てられうる。

【0019】

チップセット240はさらに、特別なSENTER動作を支援するPTPファブリック230上の特別な相互メッセージを支援すべく、自身の相互接続メッセージロジック242を含みうる。これら特別な相互接続メッセージには、鍵レジスタ244の内容をプロセッサ202、212、あるいは222に対して転送することで、プロセッサに対して、特別な「QUIESCE」インジケータ246を設定あるいはクリアして、チップセット240に、システム200をquieseあるいはde−quieseさせる、あるいはプロセッサにより特別な「QUIESCED」フラグ248を検査させることを許可することを含みうる。バスメッセージロジック242のさらなる特徴は、「EXISTS」レジスタ270内のシステム200のプロセッサの存在あるいは参加をレジスタすることであってよい。

【0020】

プロセッサ202、212、222は互いに、チップセット240に対して、および任意の他の部材あるいはエージェントに対して、ポイントツーポイント(PTP)相互接続ファブリック230により接続されてよい。プロセッサ202、212、および222、およびチップセット240は、PTPファブリック230に接続すべく、および互いに対しておよびシステム200に存在あるいは参加する任意の他のエージェントに対してメッセージを送受信すべく、それぞれインタフェースユニット209、219、229、および239の各々を含んでよい。インタフェースユニット209、219、229、および239の各々は、任意の数の他の部材と通信する任意の数の一方向性および/または双方向性ポートを含みうる。通信は、任意のあるいは全てのリンク層、プロトコル層、ルーティング層、搬送層、物理層、および任意の他の同様の層によりフレームされたメッセージおよび/またはデータを表す信号を含むパケットがエージェント間で(ポイントツーポイント)送信される層型のポイントツーポイント相互接続アーキテクチャによりPTPファブリック230を介して行われる。故に、インタフェースユニット209、219、229、および239の各々は、各層に対応する信号を生成する回路あるいはロジックを含みうる。パケットはさらに、検知あるいはエラー訂正用の、重複するあるいは他の情報を含みうる。

【0021】

トークン276は、一以上のプラットフォーム構成レジスタ(PCR)278、279を含み、チップセット230に接続されてよい。一実施形態においては、トークン276は、特別な安全フィーチャを含みえ、一実施形態では、TCPA(www.trustedpc.comから入手可能)発行の2001年12月1日付けのバージョン1.1a、Trusted Computing Platform Alliance(TCPA)Main Specificationに開示されている、トラステッドなプラットフォームモジュール(TPM)281を含みうる。

【0022】

システム環境200で識別される二つのソフトウェア部材は、Secure Virtual Machine Monitor(SVMM)282モジュールおよびSecure Initialization Authenticated Code(SINIT−AC)280モジュールである。SVMM282モジュールは、システムディスクあるいは他の大容量記憶装置に記憶でき、必要に応じて他の場所に移動あるいはコピーされうる。一実施形態においては、セキュアな起動プロセス開始の前に、SVMM282を、システム200内の一以上のメモリページに移動あるいはコピーしてよい。セキュアなエンタープロセスに続いて、SVMM282がシステム内で最も優先度の高いコードとして動作し得る仮想マシン環境が作成され得、作成された仮想マシン内のオペレーティングシステムあるいはアプリケーションによりあるシステム資源への直接アクセスが許可あるいは否認するのに利用され得る。

【0023】

セキュアなエンタープロセスが必要とするアクションの幾らかは、簡単なハードウェア実装の範囲を超える場合があり、代わりに実行が暗に信用されうるソフトウェアモジュールを利用することができるという利点がある。一実施形態においては、これらアクションはAuthenticated(SINIT)Codeとして実行されうる。一例示的アクションは、セキュアな環境の正しいインタスタンス化を支援する構成を確保すべく、システム構成の重要な部分を表す様々な制御を必要としうる。第2の例示的アクションは、SVMM282モジュールの識別情報を算出およびレジスタして、それへのシステム制御を転送することを含む。ここで、「レジスタ」とは、SVMM282の信頼尺度を、例えばPCR278あるいはPCR279などのレジスタあるいは他の記憶位置に配置することを意味する。この第2のアクションがとられると、SVMM282の信頼性が潜在的なシステムユーザにより調査されうる。

【0024】

SINITコードは、プロセッサあるいはチップセットの製造業者により作成されうる。この理由から、SINITコードはチップセット240のセキュアな起動の支援を信頼される。SINITコードを分配すべく、一実施形態においては、公知の暗号ハッシュが全SINITコードからなっており、これにより「ダイジェスト」として知られている値を生成する。一実施形態においては、ダイジェストは160ビット値を生成する。ダイジェストは、その後、秘密鍵により暗号化され、一実施形態においてはプロセッサの製造業者により保持され、デジタル署名を形成しうる。SINITコードは対応するデジタル署名により束ねられると、この組み合わせがSINIT認証コード(SINIT−AC)280として言及されうる。以下に記載するようにSINIT−AC280のコピーは後に有効性を確認される(validate)。

【0025】

SINIT−AC280は、システムディスクあるいは他の大容量記憶装置あるいは固定媒体に記憶され得、必要に応じて他の位置に移動あるいはコピーされ得る。一実施形態においては、セキュアな起動プロセスの開始前に、SINIT−AC280をシステム200の一以上のメモリページに移動あるいはコピーして、SINIT−ACのメモリレジデントコピーを形成しうる。

【0026】

オペレーティングシステムなどのシステム200上で動く任意の優先ソフトウェアは、論理プロセッサ上のセキュアな起動プロセスを開始してよく、これは開始論理プロセッサ(initiating logical processor)(ILP)と称される。本例のプロセッサ202はILPであるが、PTPファブリック230上の任意のプロセッサもILPである場合がある。SINIT−AC280のメモリレジデントコピーもSVMM282のメモリレジデントコピーもいずれも、今回信頼性があるとして考慮され得ない。

【0027】

ILP(プロセッサ202)はセキュアな起動プロセスを開始すべく特別な命令を実行する。この特別な命令はセキュアなエンター(SENTER)命令として証され得、SENTERロジック204により支援され得る。SENTER命令は第1にシステム200の全ての論理プロセッサがチップセット240(例えばEXISTSレジスタ270)に登録されているかを検証する。各プロセッサおよび、PTPファブリック230に接続される他のエージェントは、レジスタ207、217、および227などのレジスタあるいは他の記憶位置を含み、自身の含む論理プロセッサの数を示す。これらレジスタは読み出されて、システムトポロジーが正確にチップセット240で表されているかを検証する。

【0028】

この検証の後、SENTER命令はQUIESCEインジケータ246に書き込み、チップセット240に対してシステム200を休止させる(quiesce)。チップセット240はPTPファブリック230上でハンドシェイク列を開始して、一つのプロセッサ(休止状態マスター)を除く、PTPファブリック230上の全てのプロセッサおよび他のエージェントに休止状態に入らせる。本実施形態においては、プロセッサ202がILPであるとともに休止状態マスターである。休止列は「STOP_REQ」信号をマスターでないプロセッサに対して各々送信して、各マスターでないプロセッサのイベント処理を終了させ、それらのバッファをドレインさせ、「STOP_ACK」信号をチップセット240に戻してそれらが休止状態に入ったことを承認させる。休止状態は、命令を何ら実行せず、PTPファブリック230上に処理を何ら生成しない状態のことである。チップセット240がチップセット240に登録されている全ての論理プロセッサを代表してSTOP_ACK信号を各エージェントから受信した後、QUIESCEDフラグ248が設定されてよい。マスターのプロセッサは、セキュアな初期化認証モジュールを実行する前に休止状態に入ったことを検証すべくチップセット内のインジケータレジスタを読み出してよい。また、セキュアな仮想マシン監視モジュールを実行する前に休止状態に入ったことを検証すべくチップセット内のインジケータレジスタを読み出してよい。

【0029】

システムが休止した後、SENTER命令が安全モジュールを安全に実行しうることを以下に記す。この目的上、PTPファブリック230は依然機能的であり、TPM281は依然休止状態マスターに対して入手できる。安全モジュールの実行が完了すると、休止状態マスターはQUIESCEインジケータ246をクリアして、チップセット240に対してシステム200を休止状態から抜けさせる。

【0030】

安全モジュールを実行すべく、ILP(プロセッサ202)は、SINIT‐AC280に含まれるSINITコードを認証およびその後実行する目的から第1にSINIT−AC280および鍵284の写し両方をセキュアなメモリ208に移動しうる。一実施形態においては、このセキュアなメモリ208は、ILP(プロセッサ202)の内部キャッシュであってよく、特別なモードで動作していてよい。鍵284はSINIT−AC280モジュールに含まれるデジタル署名を暗号化するのに利用される秘密鍵に対応する公開鍵を表しており、デジタル署名を検証してSINITコードを認証するのに利用される。一実施形態においては、鍵284は、場合としてはSENTERロジック204の一部としてプロセッサに予め記憶されている場合もある。別の実施形態においては、鍵284はチップセット240の読み出し専用鍵レジスタ244に記憶され、ILPより読み出されてよい。また別の実施形態においては、プロセッサあるいはチップセットの鍵レジスタ244は、実際に鍵284の暗号化ダイジェストを保持していてよく、ここで鍵284そのものがSINIT−AC280モジュールに含まれている。この最後の実施形態においては、ILPは鍵レジスタ244からダイジェストを読み出し、SINIT−AC280に埋め込まれた鍵284の等価暗号化ハッシュ(equivalent cryptographic hash)を算出して、二つのダイジェストを比較し、供給された鍵284が実際にトラステッドか確かめる。

【0031】

SINIT−ACのコピーおよび公開鍵のコピーはセキュアなメモリ208内に存在してよい。ILPは公開鍵のコピーを利用してSINIT−ACのコピーに含まれるデジタル署名を復号することでSINIT−ACの写しが有効性を確認される。この復号により、暗号化ハッシュダイジェストの原本を生成する。新たに算出されたダイジェストがこの原ダイジェストに整合している場合、SINIT−ACのコピーおよびそれに含まれるSINITコードはトラステッドであると考えられる。

【0032】

ILPは、以下に概略を示すように、セキュアなトークン276内のプラットフォーム構成レジスタ272に対してSINIT−ACモジュールの暗号化ダイジェスト値を書き込むことで、SINIT−ACモジュールの唯一の識別情報を登録する。SENTER命令のILP実行は、ILPのセキュアなメモリ208内に保持されるSINITコードのトラステッドなコピーに実行制御を転送することで終了しうる。トラステッドなSINITコードはシステムテストおよび構成アクションを実行して、上述のレジスタの定義に則りSVMMのメモリレジデントコピーを登録してよい。

【0033】

SVMMのメモリレジデントコピーの登録は、幾らかの方法で行うことができる。一実施形態においては、ILP上で動くSENTER命令は、安全トークン276内のPCR278にSINIT−ACの算出されたダイジェストを書き込む。次に、トラステッドなSINITコードは、メモリレジデントSVMMの算出されたダイジェストを、同じPCR278あるいは安全トークン276内の別のPCR279に書き込むことができる。SVMMダイジェストが同じPCR278に書き込まれる場合、安全トークン276は、新たな値(SVMMダイジェスト)で原コンテンツ(SINITダイジェスト)をハッシュして、結果をPCR278に書き込む。第1(初期化)のPCR278への書き込みがSENTER命令に限定される実施形態においては、結果であるダイジェストはシステムの信頼ルート(a root of trust)として利用されうる。

【0034】

トラステッドなSINITコードはその実行を完了して、SVMMの識別情報をPCRに登録すると、SINITコードはILP実行制御をSVMMに転送しうる。典型的な実施形態においては、ILPにより実行される第1のSVMM命令は、SVMMの初期化ルーチンを表しうる。システム200は、以下の図3の説明で概略を示すように、目下実行しているSVMMのコピーの監督下で、トラステッドなモードで動作することができる。ここからは、システム全体は、以下の図3の説明で概略を示すように、トラステッドなモードで動作することができる。

【0035】

図3を参照すると、本発明の一実施形態による例示的なトラステッドなあるいはセキュアなソフトウェア環境が示されている。図3の実施形態においては、トラステッドなソフトウェアおよびトラステッドでないソフトウェアは、同時にロードされて同時に単一のコンピュータシステム上で実行されうる。SVMM350は、一以上のトラステッドでないオペレーティングシステム340およびトラステッドでないアプリケーション310〜330からハードウェア資源380への直接アクセスを選択的に許可あるいは禁止する。この文脈において、「トラステッドでない」とは、必ずしもオペレーティングシステムあるいはアプリケーションが故意に不正を行っていることを意味するとは限らず、相互作用するコードのサイズおよび種類により、ソフトウェアが所望の通りに行動すること、およびこの実行に干渉するウィルスあるいは他の異質のコードがないこと、を確実にアサートすることが実際的でないことを意味する。典型的な実施形態においては、トラステッドでないコードは、今日のパーソナルコンピュータで見られる通常のオペレーティングシステムおよびアプリケーションからなる場合がある。

【0036】

SVMM350はさらに、一以上のトラステッドなあるいはセキュアなカーネル360から、および一以上のトラステッドなアプリケーション370から、ハードウェア資源380への直接アクセスを選択的に許可あるいは禁止する。このようなトラステッドな、あるいはセキュアなカーネル360およびトラステッドなアプリケーション370は、トラステッドな分析をそれに対して行う能力を支援すべく寸法および機能が限られうる。トラステッドなアプリケーション370は、セキュアな環境下で実行可能な任意のソフトウェアコード、プログラム、ルーチン、あるいは一式のルーチンでありうる。故に、トラステッドなアプリケーション370は、様々なアプリケーション、あるいはコード列でありえ、あるいはJavaアプレットのような比較的小さいアプリケーションでありえる。

【0037】

システム資源保護あるいは優先度を変更しうるオペレーティングシステム340あるいはカーネル360により通常実行される命令あるいは動作は、SVMM350によりトラップ、選択的に許可、部分的に許可、あるいは拒絶されうる。一例として、典型的な実施形態においては、このかわりに、通常オペレーティングシステム340あるいはカーネル360により実行されるプロセッサのページテーブルの変更命令が、SVMM350によりトラップされえ、これにより、要求が仮想マシンのドメイン外でページ優先度を変更しようと試みなかったことを確かめうる。

【0038】

図4を参照すると、本発明の一実施形態における方法400におけるソフトウェアおよび他のプロセスブロックのフローチャートが示されている。

【0039】

方法400のブロック410において論理プロセッサは、後続のSENTER命令によりアクセス可能なSINIT−ACおよびSVMMモジュールのコピーを作成する。本例においては、ILPはSINIT−ACおよびSVMMコードを大容量記憶装置から物理メモリにロードする。代替的実施形態においては、ILPだけでなくて任意の論理プロセッサがこれを行ってよい。プロセッサは、ブロック412で示されるように、SENTER命令を実行することでILPとなる。

【0040】

ブロック420においては、SENTER命令は、システム200内の全ての論理プロセッサがチップセット240に(例えばEXISTSレジスタ270に)登録されているか検証する。チップセットは、ポイントツーポイントファブリックに連結されるプロセッサを含むエージェントのリストを維持する。ブロック422において、SENTER命令は、QUIESCEインジケータ246に書き込んで、チップセット240にシステム200を休止させる。ブロック424において、チップセット240は、「STOP_REQ」信号を各マスターでないプロセッサに送り、各マスターでないプロセッサにそれらの処理を終了させ、それらのバッファをドレインさせ、「STOP_ACK」信号をチップセット240に戻してそれらが休止状態に入ったことを通知する。ブロック426において、QUIESCEDフラグ248を設定して、チップセット240がSTOP_ACK信号を、チップセット240に登録されている全ての論理プロセッサを代表して、全てのエージェントから受信したことを示す。

【0041】

ブロック430において、ILPはチップセットの公開鍵およびSINIT−ACのメモリレジデントコピーを、安全に実行すべく自身のセキュアなメモリに移動する。ブロック432において、ILPは鍵を使ってSINIT−ACのセキュアなメモリレジデントコピーの有効性を確認して実行する。SINIT−ACの実行により、システム構成およびSVMMコピーのテストを行ってよく、その後SVMMの識別情報を登録して、最後にブロック434にてSVMMの実行を開始する。ブロック436において、休止状態のマスターはWUIESCEインジケータ246をクリアして、ブロック438でチップセット240に対してシステム200を休止状態から復帰させる。

【0042】

以下に本発明の実施形態の一例を示す。

[実施形態1]

システムであって、

セキュアなエンター命令を実行する第1のプロセッサと、

前記セキュアなエンター命令の実行中に、前記システムを休止状態に入らせるチップセットと、を含むシステム。

[実施形態2]

前記第1のプロセッサを前記チップセットに連結するポイントツーポイントファブリックをさらに含む、実施形態1に記載のシステム。

[実施形態3]

前記ポイントツーポイントファブリックにより前記チップセットに連結される第2のプロセッサをさらに含み、

前記チップセットは、前記セキュアなエンター命令の実行中に、さらに前記第2のプロセッサを前記休止状態に入らせる、実施形態2に記載のシステム。

[実施形態4]

前記チップセットは、さらに前記システムを、前記第1のプロセッサおよび前記チップセットだけが前記ポイントツーポイントファブリックを介して通信する前記休止状態に入らせる、実施形態2に記載のシステム。

[実施形態5]

トラステッドなプラットフォームモジュールをさらに含み、

前記トラステッドなプラットフォームモジュールは前記休止状態中に前記第1のプロセッサにアクセス可能である、実施形態1に記載のシステム。

[実施形態6]

前記第1のプロセッサは、セキュアな初期化認証コードモジュールをさらに実行する、実施形態1に記載のシステム。

[実施形態7]

前記第1のプロセッサは、セキュアな仮想マシン監視モジュールをさらに実行する、実施形態1に記載のシステム。

[実施形態8]

前記チップセットは、前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なインジケータを含む、実施形態1に記載のシステム。

[実施形態9]

前記チップセットは、

前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なインジケータと、

前記システムの各プロセッサの識別情報を示す第1の記憶位置と、を含み、

前記第2のプロセッサは、前記第2のプロセッサが前記ポイントツーポイントファブリックに接続されていることを示す第2の記憶位置を含み、

前記第1のプロセッサは、前記チップセットに前記システムを前記休止状態に入らせるべく前記インジケータにアクセスする前に前記第2のプロセッサの識別情報(identity)が前記第1の記憶位置に示されていることを検証するロジックを含む、実施形態3に記載のシステム。

[実施形態10]

ポイントツーポイントファブリックを介してチップセットに連結される第1のプロセッサ上で、セキュアなエンター命令の実行を開始することと、

セキュアなエンター命令の実行中に、前記チップセットに、前記ポイントツーポイントファブリックに連結される第2のプロセッサを休止状態に入らせることと、を含む方法。

[実施形態11]

前記チップセットが、前記ポイントツーポイントファブリックに連結されるエージェントのリストを維持することをさらに含む、実施形態10に記載の方法。

[実施形態12]

前記第2のプロセッサを介して前記ポイントツーポイントファブリックに連結されるエージェントの数を識別する、前記第2のプロセッサ内の記憶位置を読み出すことをさらに含む、実施形態11に記載の方法。

[実施形態13]

前記休止状態中に前記第1のプロセッサが、トラステッドなプラットフォームモジュールにアクセスすることをさらに含む、実施形態10に記載の方法。

[実施形態14]

セキュアな初期化認証モジュールを実行することをさらに含む、実施形態13に記載の方法。

[実施形態15]

前記セキュアな初期化認証モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータを読み出すことをさらに含む、実施形態14に記載の方法。

[実施形態16]

セキュアな仮想マシン監視モジュールを実行することをさらに含む、実施形態13に記載の方法。

[実施形態17]

前記セキュアな仮想マシン監視モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータを読み出すことをさらに含む、実施形態16に記載の方法。

[実施形態18]

前記休止状態に入る前に、前記第2のプロセッサに、自身のイベント処理を終了させ、自身のバッファをドレインさせることをさらに含む、実施形態10に記載の方法。

[実施形態19]

前記休止状態に入ったことを通知すべく前記チップセットに信号を送る前記第2のプロセッサをさらに含む、実施形態18に記載の方法。

[実施形態20]

セキュアな動作の初期化を呼び出すべく第1の命令を実行するセキュアなエンターロジックと、

チップセットに対して、ポイントツーポイントファブリックを介して前記チップセットに連結されるエージェントを休止状態に入らせる相互接続メッセージロジック(interconnection messaging logic)と、を含むプロセッサ。

前述の記載において、本発明を特定の例示的実施形態により記載してきた。しかし、添付請求項に示す本発明の幅広い精神および範囲から逸脱しない範囲で、様々な変形例および変更例を考えられることが明らかである。故に、明細書および図面は、限定的な意味ではなくて例示的な意味で捉えられるべきである。

【特許請求の範囲】

【請求項1】

システムであって、

セキュアな起動プロセスを開始するセキュアなエンター命令を実行する第1のプロセッサと、

チップセットと、

前記第1のプロセッサを前記チップセットに連結するポイントツーポイントファブリックと、

前記ポイントツーポイントファブリックにより前記チップセットに連結される第2のプロセッサと、を含み、

前記チップセットは前記セキュアなエンター命令の実行中に、前記第2のプロセッサを休止状態に入らせ、

前記チップセットが、前記第2のプロセッサに休止状態に入らせる信号を送信した後、前記第2のプロセッサは、前記第2のプロセッサが休止状態に入ったことを知らせる信号を前記チップセットに送信する

システム。

【請求項2】

前記チップセットは、さらに前記システムを、前記第1のプロセッサおよび前記チップセットだけが前記ポイントツーポイントファブリックを介して通信する前記休止状態に入らせる、請求項1に記載のシステム。

【請求項3】

トラステッドなプラットフォームモジュールをさらに含み、

前記トラステッドなプラットフォームモジュールは前記休止状態中に前記第1のプロセッサにアクセス可能である、請求項1又は2に記載のシステム。

【請求項4】

前記第1のプロセッサは、セキュアな起動プロセスを実行するSINITコード及び前記SINITコードのデジタル署名を含むセキュアな初期化認証コードモジュールをさらに実行する、請求項1から3のいずれか1項に記載のシステム。

【請求項5】

前記第1のプロセッサは、前記セキュアな起動プロセスに続いて仮想マシン環境を作成し、前記仮想マシン環境において前記システム内で最も優先度の高いレベルで動作するセキュアな仮想マシン監視モジュールをさらに実行する、請求項1から4のいずれか1項に記載のシステム。

【請求項6】

前記チップセットは、前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なレジスタを含む、請求項1から5のいずれか1項に記載のシステム。

【請求項7】

前記チップセットは、

前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なインジケータレジスタと、

前記システムの各プロセッサの識別情報を示す第1のレジスタと、を含み、

前記第2のプロセッサは、前記第2のプロセッサが前記ポイントツーポイントファブリックに接続されていることを示す第2のレジスタを含み、

前記第1のプロセッサは、前記チップセットに前記システムを前記休止状態に入らせるべく前記インジケータレジスタにアクセスする前に前記第2のプロセッサの識別情報(identity)が前記第1のレジスタに示されていることを検証するロジックを含む、請求項1から6のいずれか1項に記載のシステム。

【請求項8】

ポイントツーポイントファブリックを介してチップセットに連結される第1のプロセッサ上で、セキュアな起動プロセスを開始するセキュアなエンター命令の実行を開始することと、

前記セキュアなエンター命令の実行中に、前記チップセットに、前記ポイントツーポイントファブリックに連結される第2のプロセッサを休止状態に入らせることと、を含み、

前記チップセットが、前記第2のプロセッサに休止状態に入らせる信号を送信した後、

前記第2のプロセッサは、前記第2のプロセッサが休止状態に入ったことを知らせる信号を前記チップセットに送信する

方法。

【請求項9】

前記チップセットが、前記ポイントツーポイントファブリックに連結されるプロセッサを含むエージェントのリストを維持することをさらに含む、請求項8に記載の方法。

【請求項10】

前記第2のプロセッサを介して前記ポイントツーポイントファブリックに連結される前記エージェントの数を識別する、前記第2のプロセッサ内のレジスタを読み出すことをさらに含む、請求項9に記載の方法。

【請求項11】

前記休止状態中に前記第1のプロセッサが、トラステッドなプラットフォームモジュールにアクセスすることをさらに含む、請求項8から10のいずれか1項に記載の方法。

【請求項12】

セキュアな起動プロセスを実行するSINITコード及び前記SINITコードのデジタル署名を含むセキュアな初期化認証モジュール

を実行することをさらに含む、請求項11に記載の方法。

【請求項13】

前記第1のプロセッサが、前記セキュアな初期化認証モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータレジスタを読み出すことをさらに含む、請求項12に記載の方法。

【請求項14】

前記第1のプロセッサが、前記セキュアな起動プロセスに続いて、仮想マシン環境を作成し、前記仮想マシン環境において最も優先度の高いレベルで動作するセキュアな仮想マシン監視モジュールを実行することをさらに含む、請求項11又は12に記載の方法。

【請求項15】

前記セキュアな仮想マシン監視モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータレジスタを読み出すことをさらに含む、請求項14に記載の方法。

【請求項16】

前記休止状態に入る前に、前記第2のプロセッサに、実行しているイベント処理を終了させ、前記第2のプロセッサのバッファをドレインさせることをさらに含む、請求項8から15のいずれか1項に記載の方法。

【請求項17】

前記休止状態に入ったことを通知すべく前記チップセットに信号を送る前記第2のプロセッサをさらに含む、請求項16に記載の方法。

【請求項18】

セキュアな起動プロセスを開始する第1の命令を実行するセキュアなエンターロジックと、

チップセットに対して、ポイントツーポイントファブリックを介して前記チップセットに連結される他のプロセッサを休止状態に入らせる相互接続メッセージロジック(interconnection messaging logic)と、を含み、

前記チップセットに、前記他のプロセッサに休止状態に入らせる信号を送信させた後、前記他のプロセッサに、前記他のプロセッサが休止状態に入ったことを知らせる信号を前記チップセットに送信させる

プロセッサ。

【請求項1】

システムであって、

セキュアな起動プロセスを開始するセキュアなエンター命令を実行する第1のプロセッサと、

チップセットと、

前記第1のプロセッサを前記チップセットに連結するポイントツーポイントファブリックと、

前記ポイントツーポイントファブリックにより前記チップセットに連結される第2のプロセッサと、を含み、

前記チップセットは前記セキュアなエンター命令の実行中に、前記第2のプロセッサを休止状態に入らせ、

前記チップセットが、前記第2のプロセッサに休止状態に入らせる信号を送信した後、前記第2のプロセッサは、前記第2のプロセッサが休止状態に入ったことを知らせる信号を前記チップセットに送信する

システム。

【請求項2】

前記チップセットは、さらに前記システムを、前記第1のプロセッサおよび前記チップセットだけが前記ポイントツーポイントファブリックを介して通信する前記休止状態に入らせる、請求項1に記載のシステム。

【請求項3】

トラステッドなプラットフォームモジュールをさらに含み、

前記トラステッドなプラットフォームモジュールは前記休止状態中に前記第1のプロセッサにアクセス可能である、請求項1又は2に記載のシステム。

【請求項4】

前記第1のプロセッサは、セキュアな起動プロセスを実行するSINITコード及び前記SINITコードのデジタル署名を含むセキュアな初期化認証コードモジュールをさらに実行する、請求項1から3のいずれか1項に記載のシステム。

【請求項5】

前記第1のプロセッサは、前記セキュアな起動プロセスに続いて仮想マシン環境を作成し、前記仮想マシン環境において前記システム内で最も優先度の高いレベルで動作するセキュアな仮想マシン監視モジュールをさらに実行する、請求項1から4のいずれか1項に記載のシステム。

【請求項6】

前記チップセットは、前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なレジスタを含む、請求項1から5のいずれか1項に記載のシステム。

【請求項7】

前記チップセットは、

前記チップセットが前記システムを前記休止状態に入らせるべく前記第1のプロセッサにアクセス可能なインジケータレジスタと、

前記システムの各プロセッサの識別情報を示す第1のレジスタと、を含み、

前記第2のプロセッサは、前記第2のプロセッサが前記ポイントツーポイントファブリックに接続されていることを示す第2のレジスタを含み、

前記第1のプロセッサは、前記チップセットに前記システムを前記休止状態に入らせるべく前記インジケータレジスタにアクセスする前に前記第2のプロセッサの識別情報(identity)が前記第1のレジスタに示されていることを検証するロジックを含む、請求項1から6のいずれか1項に記載のシステム。

【請求項8】

ポイントツーポイントファブリックを介してチップセットに連結される第1のプロセッサ上で、セキュアな起動プロセスを開始するセキュアなエンター命令の実行を開始することと、

前記セキュアなエンター命令の実行中に、前記チップセットに、前記ポイントツーポイントファブリックに連結される第2のプロセッサを休止状態に入らせることと、を含み、

前記チップセットが、前記第2のプロセッサに休止状態に入らせる信号を送信した後、

前記第2のプロセッサは、前記第2のプロセッサが休止状態に入ったことを知らせる信号を前記チップセットに送信する

方法。

【請求項9】

前記チップセットが、前記ポイントツーポイントファブリックに連結されるプロセッサを含むエージェントのリストを維持することをさらに含む、請求項8に記載の方法。

【請求項10】

前記第2のプロセッサを介して前記ポイントツーポイントファブリックに連結される前記エージェントの数を識別する、前記第2のプロセッサ内のレジスタを読み出すことをさらに含む、請求項9に記載の方法。

【請求項11】

前記休止状態中に前記第1のプロセッサが、トラステッドなプラットフォームモジュールにアクセスすることをさらに含む、請求項8から10のいずれか1項に記載の方法。

【請求項12】

セキュアな起動プロセスを実行するSINITコード及び前記SINITコードのデジタル署名を含むセキュアな初期化認証モジュール

を実行することをさらに含む、請求項11に記載の方法。

【請求項13】

前記第1のプロセッサが、前記セキュアな初期化認証モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータレジスタを読み出すことをさらに含む、請求項12に記載の方法。

【請求項14】

前記第1のプロセッサが、前記セキュアな起動プロセスに続いて、仮想マシン環境を作成し、前記仮想マシン環境において最も優先度の高いレベルで動作するセキュアな仮想マシン監視モジュールを実行することをさらに含む、請求項11又は12に記載の方法。

【請求項15】

前記セキュアな仮想マシン監視モジュールを実行する前に前記休止状態に入ったことを検証すべく前記チップセット内のインジケータレジスタを読み出すことをさらに含む、請求項14に記載の方法。

【請求項16】

前記休止状態に入る前に、前記第2のプロセッサに、実行しているイベント処理を終了させ、前記第2のプロセッサのバッファをドレインさせることをさらに含む、請求項8から15のいずれか1項に記載の方法。

【請求項17】

前記休止状態に入ったことを通知すべく前記チップセットに信号を送る前記第2のプロセッサをさらに含む、請求項16に記載の方法。

【請求項18】

セキュアな起動プロセスを開始する第1の命令を実行するセキュアなエンターロジックと、

チップセットに対して、ポイントツーポイントファブリックを介して前記チップセットに連結される他のプロセッサを休止状態に入らせる相互接続メッセージロジック(interconnection messaging logic)と、を含み、

前記チップセットに、前記他のプロセッサに休止状態に入らせる信号を送信させた後、前記他のプロセッサに、前記他のプロセッサが休止状態に入ったことを知らせる信号を前記チップセットに送信させる

プロセッサ。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−89147(P2012−89147A)

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願番号】特願2011−259595(P2011−259595)

【出願日】平成23年11月28日(2011.11.28)

【分割の表示】特願2009−506817(P2009−506817)の分割

【原出願日】平成19年5月25日(2007.5.25)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.JAVA

2.Linux

【出願人】(591003943)インテル・コーポレーション (1,101)

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願日】平成23年11月28日(2011.11.28)

【分割の表示】特願2009−506817(P2009−506817)の分割

【原出願日】平成19年5月25日(2007.5.25)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.JAVA

2.Linux

【出願人】(591003943)インテル・コーポレーション (1,101)

[ Back to top ]