ポストニップ絶縁破壊により荷電均一性を改善する電極埋込型バイアスド荷電ローラ

【課題】荷電均一性に優れ、摩耗が少なく、より安価なBCRシステムを提供する。

【解決手段】バイアスド荷電ローラ(BCR)1を、絶縁基板層10の上に多数の電極8を配置しその上を半導体層9により覆った構成とする。電極8に対しては、例えばプリニップ領域6(及びニップ内領域3)に属する電極群と、ポストニップ領域7に属する電極群とが、異なるバイアス電圧でバイアスされるよう、電源14及び15からバイアス電圧VPRE-NIP及びVPOST-NIPを印加する。電極の配置乃至寸法形状や電圧設定等によってニップ内領域3、プリニップ領域6及びポストニップ領域7におけるフォトレセプタ表面2への荷電態様が最適化される。電極8は、絶縁基板層10内や半導体層9内に配置してもよい。

【解決手段】バイアスド荷電ローラ(BCR)1を、絶縁基板層10の上に多数の電極8を配置しその上を半導体層9により覆った構成とする。電極8に対しては、例えばプリニップ領域6(及びニップ内領域3)に属する電極群と、ポストニップ領域7に属する電極群とが、異なるバイアス電圧でバイアスされるよう、電源14及び15からバイアス電圧VPRE-NIP及びVPOST-NIPを印加する。電極の配置乃至寸法形状や電圧設定等によってニップ内領域3、プリニップ領域6及びポストニップ領域7におけるフォトレセプタ表面2への荷電態様が最適化される。電極8は、絶縁基板層10内や半導体層9内に配置してもよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、高速電子写真印刷用のバイアスド荷電ローラ(BCR:biased charge roller)に関し、より詳細には、電荷保持面上における電荷の堆積を制御するためローラ表面下に整列して埋め込まれた縦長電極群を有するBCRに関する。

【背景技術】

【0002】

通常、静電画像化印刷プロセスは幾つかの個別段階から構成されており、各段階は一般に(1)荷電、(2)画像化、(3)露出、(4)現像、(5)転写、(6)融着及び(7)清掃と呼ばれている。荷電段階においては、電荷保持面例えばフォトレセプタ表面上に電荷を均一に堆積させることによって、この電荷保持面を静電的に感受性とする。画像化段階においては原画像を取得する。露出段階においては、静電感受的となっているフォトレセプタ表面上に取得した画像を投影し露出することにより、原画像に対応する静電潜像をフォトレセプタ表面上に記録する。現像段階においては、荷電トナー粒子をこの静電潜像に接触させることにより当該静電潜像を現像する。このとき、CAD(charged area development)を用いるのであればフォトレセプタ表面上の荷電領域へと荷電トナー粒子が引き寄せられ、またより一般的なDAD(discharged area development)を用いるのであればフォトレセプタ表面上の非荷電領域へと荷電トナー粒子が引き寄せられて、静電潜像に対応する像が現れる。転写段階を単一ステップにて行う際には、当該転写段階において、トナー粒子が静電的に吸着しているフォトレセプタ表面を、紙その他の基板により提供される画像受容面に接触させる。このとき、トナー粒子に対し静電界が作用するためトナー粒子は画像受容面に吸い寄せられて付着する。即ち、フォトレセプタ表面から画像受容面上へとトナー粒子が転写される。融着段階においては、溶融乃至加圧によりトナー粒子が画像受容面に融着する。清掃段階においては、清掃装置によってフォトレセプタ表面上から残存トナー粒子を取り除く。これによって、一連のプロセスが完了する。

【0003】

フォトレセプタ表面に荷電する装置としては接触式荷電装置が知られている。接触式荷電装置は、フォトレセプタ等の画像担持部材の荷電対象面に接触する荷電用導電部材を有しており、この荷電用導電部材に適当な電圧を印加すれば当該荷電対象面を所定電位VOPCまで荷電することができる。荷電用導電部材をローラ状の形状乃至構造としたものを荷電ローラと呼び、電源からバイアス電圧の供給を受ける荷電ローラをバイアスド荷電ローラ即ちBCRと呼び、当該バイアス電圧がDC電圧又はAC電圧である場合そのBCRをそれぞれDCBCR又はACBCRと呼び、ACBCRの中でもバイアス電圧がDC/AC重畳電圧(DCシフトAC電圧)であるものをDCシフトACBCRと呼ぶ。DCシフトACBCRにおけるDC/AC重畳電圧はDC電圧VDCにAC電圧を重畳させた電圧であり、このAC電圧のピークトゥピーク振幅VACは空気絶縁破壊しきい値電圧VTHの2倍以上とする必要がある。即ち、一般に荷電ローラとフォトレセプタとの間には、その接触部の上流側及び下流側それぞれに空隙(後述のプリニップ空隙及びポストニップ空隙)が発生する。荷電ローラに対し十分な電圧が印加されるとこれらの空隙にて空気絶縁破壊が生じ、フォトレセプタ外表面はこの空気絶縁破壊に伴い荷電される。注記すべきことに、荷電用導電部材として十分な導電性を有する荷電ローラを使用する場合、空気絶縁破壊しきい値電圧VTHは、次の式

(数1)

DOPC(μm)=dOPC/k(但しdOPCはフォトレセプタ厚、kは定数(フォトレセプタ誘電率))

により与えられるフォトレセプタ誘電体厚DOPCを用い、次の式

(数2)

VTH〜312+87.96(DOPC)1/2+6.2DOPC

によって与えることができる。例えば、DOPC=7.6μmのフォトレセプタであればこの式からVTH=600VとなるためVAC>1200Vとしなければならない。特に、従来方式によるDCシフトACBCRを用いる場合、DC電圧VDCによってフォトレセプタ荷電電圧乃至電位VOPCがVOPC=VDCと決まる。フォトレセプタ荷電電圧VOPCが決まれば、

(数3)

VOPC=σDOPC/ε0、σ=Q/A

の関係からフォトレセプタの表面に堆積する電荷量Q及びその密度(単位面積当たり電荷量)σが決まる(但しε0は自由空間誘電率、Aはフォトレセプタ表面積)。なお、荷電用導電部材が荷電ロールとして構成されている接触式荷電装置については、この参照を以て本願に繰り入れられるところの特許文献11並びに特許文献1乃至4を参照されたい。

【0004】

接触式荷電装置を用いる際に大切なのは、その荷電用導電部材を、電荷保持面例えばフォトレセプタ表面に対し、その長手方向に沿い均等に接触させることである。従って、接触式荷電装置における荷電用導電部材例えば荷電ローラは、通常、その形状を適合させやすく柔らかい素材により形成し、フォトレセプタ等の光導電性部材乃至光導電性ドラムに対する接触状態を良好に保持できるようにする。印刷装置においては、普通、このようにしてフォトレセプタ等に接触している荷電ローラに対し、AC電圧やDC電圧を印加する。

【0005】

電荷保持面と荷電ローラ表面との接触部近傍は、ニップ内領域、プリニップ領域及びポストニップ領域という三種類の領域に区分することができる。これらのうちニップ内領域即ち前述の接触部は、電荷保持面と荷電ローラ表面とが直接接触する点を含む領域である。また、プリニップ領域はニップ内領域から見て上流側の領域、ポストニップ領域はニップ内領域から見て下流側の領域である。プリニップ領域は電荷保持面と荷電ローラ表面とが接触しつつある領域でありポストニップ領域は離れていく領域であるため、プリニップ領域及びポストニップ領域においては電荷保持面と荷電ローラ表面とが直接接触せず、従って前述の通り両者の間に空隙が発生する。これをプリニップ空隙及びポストニップ空隙と呼び、当該空隙における空気絶縁破壊をそれぞれプリニップ絶縁破壊又はポストニップ絶縁破壊と呼ぶ。

【0006】

先に述べたように、荷電段階において目的としているのは、電荷保持面例えばフォトレセプタ表面上に電荷を均一に堆積させること、即ち荷電均一性である。しかしながら、荷電方式として仮にDCバイアス荷電方式を使用することとすると、周知の通り、荷電均一性が貧弱なものになる。これは、既に判明している通りポストニップ絶縁破壊の方がプリニップ絶縁破壊に比べ電荷保持面例えばフォトレセプタ表面をより均一に荷電できるのに、DCバイアス荷電方式ではプリニップ絶縁破壊によりポストニップ絶縁破壊が抑制されてしまうためである。そのため、従来から、DCバイアス荷電方式よりもACバイアス荷電方式の方が一般に用いられている。ACバイアス荷電方式では、DCシフトAC高電圧電源を用いてポストニップ絶縁破壊を発生させ、それにより荷電均一性を(DCバイアス荷電方式に比べ)良好としている。しかしながら、ACバイアス荷電方式には、コストが高いことやフォトレセプタが摩耗しやすいことを含め幾つかの欠点がある。

【0007】

即ち、DCシフトACBCRは、小型電子写真エンジンにて広く用いられているバイアス荷電手段の一つであり、これを用いた場合、プリニップ空隙でもポストニップ空隙でも空気絶縁破壊が生じる。そのため、この種のBCRを用いれば、荷電均一性をより良好にすることができ、またオゾンもほとんど発生しなくなる。しかしながら、荷電ローラに高電圧のAC電圧分も印加されるため、摩耗の程度が大きく、高コストとなりやすく、帯状欠陥(banding)が発生することがあり、プロセス速度が制限される、といった問題点をはらんでいる。

【0008】

第1に、ACBCRを用いた場合、AC電圧分によりフォトレセプタ表面上に正電荷及び負電荷が堆積する。そのうち正電荷はフォトレセプタを形成しているポリマを弱体化させる。清掃装置のブレード(刃)が当たるとこの弱体化しているポリマはすり減り、その結果、摩耗の程度が甚だしくなり寿命が短縮される。既に判明していることであるが、BCRによる正電荷堆積を防ぐことができれば、フォトレセプタの寿命は2倍に延長されるであろう。

【0009】

第2に、従来方式によるBCRにおいては、DC電源だけでなく一般に高価な高電圧AC電源も必要となる。また、かかるAC電圧を印加するとフォトレセプタにて可聴領域の雑音が発生する。この雑音の量を減らすため雑音低減手段を設けるには、そのための費用が必要となる。

【0010】

第3に、AC電圧を使用すると空間的帯状欠陥が発生する。この帯状欠陥のプロセス方向間隔Xは、プロセス速度をVPROCESS、AC電圧の周波数をfとすると、

(数4)

X=VPROCESS/f

で表すことができる。従って、周波数fが低ければ間隔Xが大きくなるため看者はこの帯状欠陥を知覚できない。しかし、周波数fが低いままでプロセス速度VPROCESSを高めるとこの帯状欠陥が高周波の空間的帯状欠陥となり看取されやすくなるため、プロセス速度をVPROCESSを高めるには併せてAC電圧の周波数fを高めねばならない。AC電圧一定のまま周波数fを高めるとAC電流が1/fに比例して減少するため、十分なAC電流を得るにはAC電源それ自体を能力の高い大型のもの(従って一般に高価なもの)にすることを余儀なくされる。そのため、周波数fひいてはプロセス速度VPROCESSを高めるには自ずから限界がある。

【0011】

ところで、DCバイアス荷電方式を用いることができない又は用いるのが好ましくない第1の理由は、ポストニップ絶縁破壊が生じないため十分な荷電均一性が得られないことである。即ち、十分高い負DC電圧をBCRのシャフトに印加すると、プリニップ領域内電界がパッシェン曲線を上回ってプリニップ絶縁破壊が発生するが、その後各空隙における電界が落ち込んでパッシェン曲線を下回るまでは負電荷がフォトレセプタ表面上に堆積され、負電荷が堆積しているとポストニップ領域では空気絶縁破壊が生じないため荷電が不均一になる。もっとも、荷電緩和時間がニップ内滞在時間(dwell time in nip)と概略等しくなるようBCRエラストマの比抵抗が精密に調整されていれば、ポストニップ領域内電界がプリニップ領域内電界を上回り荷電がより均一になるが、そのようにするのは普通は現実的でない。それは、比抵抗について非常にタイトな調整乃至管理が必要になるためである。加えて、この電界最適化(field tailoring)方式に従い比抵抗を調整するとDCBCRの感度が増すため、荷電を均一にしようとしているにもかかわらずゴースト欠陥が発生する。ゴースト欠陥とは、フォトレセプタ表面上に均一に堆積されるはずの電荷が、前回サイクルにてフォトレセプタ表面上に形成された静電潜像(例えば放電パターン)に応じて堆積してしまうことを、指している。従って、ゴースト欠陥が発生すると前回サイクルでの静電潜像がゴースト画像となって印刷物上に現れてしまう。

【0012】

【特許文献1】米国特許第4851960号明細書

【特許文献2】米国特許第5164779号明細書

【特許文献3】米国特許第5613173号明細書

【特許文献4】米国特許第2912586号明細書

【特許文献5】米国特許第6360065号明細書

【特許文献6】米国特許第3043684号明細書

【特許文献7】米国特許第3398336号明細書

【特許文献8】米国特許第3684364号明細書

【特許文献9】米国特許第3702482号明細書

【特許文献10】米国特許第6006447号明細書

【特許文献11】米国特許第4387980号明細書

【特許文献12】米国特許第5634179号明細書

【特許文献13】米国特許第2807233号明細書

【特許文献14】米国特許第3781105号明細書

【特許文献15】米国特許第3830589号明細書

【特許文献16】米国特許第3832055号明細書

【特許文献17】米国特許第3936174号明細書

【特許文献18】米国特許第3832053号明細書

【特許文献19】米国特許第5276490号明細書

【特許文献20】米国特許第5303013号明細書

【特許文献21】米国特許第5583623号明細書

【特許文献22】米国特許第5697034号明細書

【特許文献23】米国特許第6075965号明細書

【特許文献24】米国特許第6203743号明細書

【特許文献25】欧州特許公報第0642063号(A1)

【特許文献26】欧州特許公報第0642063号(B1)

【発明の開示】

【0013】

ここに、本願にて説明する電極付きDCBCRによれば、ACBCRにて生じる問題を発生させることなく、また上述の電界最適化方式を使用したDCBCRにて生じる問題も発生させることなく、ポストニップ領域における荷電を可能にしまたより良好な荷電均一性を実現することができる。

【0014】

本発明に係るBCRは、フォトレセプタ表面上に電荷を均一に堆積させ当該表面を静電的に感受性とするための部材乃至装置であり、荷電が均一であること、摩耗及びコストを実質的に減らせること等を含め、幾つかの利点を有するものである。

【0015】

本発明においては、前掲の従来技術に鑑み、荷電均一性に優れ摩耗が少なくより安価なBCRシステムを提供することを、目的としている。

【0016】

本発明においては、BCR内に電極群を埋め込むことによってこの目的を達成しまたその他の利点を実現している。埋め込んだ電極群に対しては、例えば、荷電ニップ領域内に入り又は荷電ニップ領域外に出て行く電界を簡単に且つ精密に制御でき上述の画像欠陥を防止できるよう、バイアスを印加する。

【0017】

電極群は、例えばBCR基板上に埋め込み、BCRの表面上に蓄積される電荷を緩和できるよう半導体層で覆うこととする。この半導体層は、形状を適合させやすく(形状加工乃至形成しやすく)柔らかい層としてもよいし、逆に形状を適合させにくく(形状加工乃至形成しにくく)硬い層にしてもよい。

【0018】

埋め込んだ電極群に対するバイアスの加え方には、幾つかの異なるやり方がある。例えば、プリニップ領域にある電極(群)及びニップ内領域にある電極(群)は接地しポストニップ領域にある電極(群)にはバイアスを印加する、というやり方がある。また、これらの領域全てにおいてバイアスを印加する、というやり方もあるし、各領域内でバイアスを変化(分布)させる、というやり方もある。更に、広範囲に分布する電極群に対し、それらを覆う半導体層に沿った電極間電圧降下乃至電位差が生じるようバイアスを印加し、それにより電界最適化効果を得る、というやり方もある。ニップ内領域から大きく離れている電極群については、BCR表面に蓄積される電荷が緩和されるようバイアスしてもよいし接地してもよい。電極に対するバイアス印加は、電極1個毎に行ってもよいし、1個又は複数個の電極を含む幾つかのグループ毎に行ってもよい。各電極又はそのグループに対するバイアスは異なるバイアスとすることもできるし、幾つかの電極又はそのグループについて互いに同じバイアスとすることもできる。グループ分けの仕方としては、例えば、プリニップ前領域内電極(群)、プリニップ領域内電極(群)、ニップ内領域内電極(群)、ポストニップ領域内電極(群)及びポストニップ後領域内電極(群)というやり方があるが、無論他のやり方でグループ分けを行ってもよい。印加するバイアスはDCバイアスでもよいし、ACバイアスでもよいし、DCシフトACバイアスでもよい。電源(群)の動作モードは定電圧モードでも定電流モードでもよい。

【発明を実施するための最良の形態】

【0019】

本発明の好適な実施形態に係るBCRは、絶縁基板(層)と、BCRの表面上に蓄積される電荷を緩和できるよう絶縁基板(層)を覆う半導体層と、を備える電荷保持面荷電用BCRにおいて、絶縁基板(層)の上若しくは内部又は絶縁基板(層)を覆う半導体層の内部のうち少なくとも何れかに配置された多数の電極を備え、絶縁基板(層)をBCR内部に埋め込まれた電極群もろとも半導体層により覆った電荷保持面荷電用電極付きBCRであり、接触式BCRとしても間隙付き(即ち非接触式)BCRとしても実現できる。その半導体層は、接触式か否かを問わず、形状を適合させやすく柔らかい層としてもよいし(但し接触式の場合はフォトレセプタ等との間で良好な接触状態を保持する上でこちらの方が望ましい)、逆に形状を適合させにくく硬い層にしてもよい(但し硬い層は接触式より非接触式に適している)。形状を適合させやすい半導体層は例えばエラストマによって実現できる。更に、本発明の好適な実施形態における電極群は、ニップ内領域内電界だけでなくプリニップ領域内電界やポストニップ領域内電界も制御できるよう、また幾つかの異なるやり方で、バイアスすることができる。

【0020】

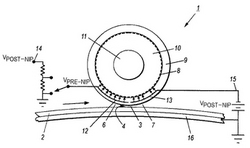

図1に、本発明の一実施形態に係る電極付きBCRシステムの軸断面を示す。この図に示すBCR1は、フォトレセプタ接地面16を取り巻いているフォトレセプタ表面2に隣り合うよう、位置決めされている。BCR1とフォトレセプタ表面2は、ニップ内領域3において最接近している。即ち、接触式の場合は図2に示すクロスプロセス方向に沿ってフォトレセプタ表面2に均等に接触するよう、また非接触式の場合はクロスプロセス方向に沿ってフォトレセプタ表面2に対し均等な間隔を呈するよう、BCR1が配置される。

【0021】

また、ニップ内領域3の上流側にはプリニップ領域6が、下流側にはこれに相応してポストニップ領域7がある。プリニップ領域6及びポストニップ領域7においては、BCR1とフォトレセプタ表面2との間に、空隙が生じている。なお、フォトレセプタは例えばベルト或いはドラム等、様々な構成とすることができる。

【0022】

BCR1は、通流用縦長電極8、半導体層9、絶縁基板層10及びシャフト11を備え、シャフト11の軸を中心に回転させることが可能なロール状の部材である。シャフト11は、絶縁基板層10を支持できる素材である限り、どのような素材からも形成でき、導体でも非導体でもよく、例えばスチールシャフトとして構成することができる。シャフト11はBCR1の絶縁基板たる絶縁基板層10によって概ね覆われており、この絶縁基板層10上には多数の電極8が整列して配置されており、絶縁基板層10及び電極8は半導体層9により概ね覆われている。このように本実施形態では電極8は絶縁基板層10と半導体層9との間に配置されているが、全ての又は一部の電極8を絶縁基板層10又は半導体層9の内部に多数整列して埋め込んでもよい。何れにせよ、電極8は回転可能なBCR1即ち可動部分に組み込まれているため、固定部分に配置されている部材例えば固定された電源14及び15に対して電極8を電気的に接続するには、可動部分と固定部分とを電気的に接続するための部材が必要である。本実施形態においては、それぞれ1個又は複数個の電極8を含む複数個の電極群に対してそれぞれ異なるバイアスを印加するための経路を、当該部材によって提供している。その種の部材として本実施形態にて設けられているのは、具体的には、電圧VPRE-NIPを供給する電源14に接続されている固定式プリニップ接触子12、並びに電圧VPOST-NIPを供給する電源15に接続されている固定式ポストニップ接触子13である。これらの接触子12及び13は、BCR1の回転に伴いプリニップ領域6に入ってきた電極8が固定式プリニップ接触子12に電気的に接触し、その後ニップ内領域3に入ってきた電極8が引き続き固定式プリニップ接触子12に電気的に接触し、更にその後ポストニップ領域7に入ってきた電極8が固定式ポストニップ接触子13に接触するよう、設けられている。従って、プリニップ領域6に属する電極8の集まり即ちプリニップ領域内電極群、並びにニップ内領域3にある電極8の集まり即ちニップ内領域内電極群に対しては電圧VPRE-NIPによって電荷が供給され、ポストニップ領域7に属する電極8の集まり即ちポストニップ領域内電極群に対しては電圧VPOST-NIPによって電荷が供給される。なお、ここではプリニップ領域内電極群とニップ内領域内電極群とに同じ電圧VNIPを印加する例を示しているが、異なる電圧を印加するように固定部分の構造等を定めることもできる。更に、電圧VPRE-NIPと電圧VPOST-NIPは異なる電圧とすることができる。例えばこの図の例では、電源14は電圧VPOST-NIPを分圧して得られる電圧を電圧VPRE-NIPとして供給している。また、電圧VPRE-NIP及び電圧VPOST-NIPを随時切り替えることもできる。例えばこの図の例では、電源14は電圧VPRE-NIPを接地電位に切り替えられるよう構成されている。更に、この図に示した例は、多数の電極8をプリニップ領域内電極群、ニップ内領域内電極群及びポストニップ領域内電極群にグループ分けしてバイアス電圧を印加する例であるが、電極8のグループ分けの仕方及び固定部分と可動部分との接続関係乃至接続方式は、より複雑なものにすることもできる。例えば、プリニップ前領域内電極群、プリニップ領域内電極群、ニップ内領域内電極群、ポストニップ領域内電極群及びポストニップ後領域内電極群という5種類のグループそれぞれを個別にバイアスできるよう、別個の固定式接触子を設けてもよい。プリニップ前領域とはプリニップ領域6より更に上流側の、またポストニップ後領域とはポストニップ領域7より更に下流側の、領域を指している。

【0023】

本実施形態におけるBCR1の頂面を図2に、またそのIII−III断面を図3に、それぞれ示す。これらの図に示すように、シャフト11は絶縁基板層10により、また絶縁基板層10の表面は半導体層9により、概ね覆われている。電極8は、図1に示したように絶縁基板層10と半導体層9の間に配置することもできるが、図4に示すように半導体層9内に埋め込むこともできる。図4に示す例では、多数の電極8を1個おきに半導体層9内に埋め込み、残りを絶縁基板層10と半導体層9の間に配置している。但し、製造の容易さを考えると、電極8は、図1に示したように絶縁基板層10上に配置する方がよい。

【0024】

例えばポリアミド(polyamide)等の絶縁素材により形成された絶縁外皮である絶縁基板層10は、例えば約0.1〜約20mmの厚みでシャフト11を概ね覆っている。シャフト11の直径が例えば約6〜約10mmであるなら、絶縁基板層10の厚みは約5〜約10mmとし、その周りの半導体層9、例えばBCR1の表面上に蓄積される電荷を緩和できるエラストマの厚みは約0.2〜約1mmとする。なお、ここで示した数値は一例に過ぎず、設計次第で様々な直径乃至厚みとすることができる。

【0025】

各電極8の長さ(図2中のクロスプロセス方向に沿った寸法)はBCR1(或いはそのシャフト11や絶縁基板層10や半導体層9)のほぼ全長に亘る長さとするのが望ましいが、当該全長とは異なる長さの電極8を用いることや、電極8同士の間でその長さを規則的パターンに従い変えることも可能である。また、各電極8の幅(図2中のプロセス方向即ちBCR1の回転方向に沿った寸法)は、例えば約0.05〜約3mmの範囲に属する幅とすればよく、好ましくは約0.2〜約0.7mmの範囲内とする。更に、各電極8の厚み(図3中の半径方向即ちBCR1の表面に直交する方向に沿った寸法)は、好ましくは例えば約50μm未満とする。そして、電極8同士の間隔は、絶縁基板層10の表面に沿い隣り合う電極8同士の間に平均して約0.05〜約3mmの範囲に属する間隙が生じるよう、より好ましくは約0.2〜約0.7mmの範囲に属する間隙が生じるよう、規則的なパターンに従って定めるのが望ましい。何れにせよ、電極8の寸法及び間隔は、発生する電界を十分精密且つ確実に制御できる程度に電極8同士が近づくよう、それでいて電極8同士の間に流れる電流を十分制限できる程度に電極8同士が離れるよう、定めるべきである。勿論、ここで示した数値は一例に過ぎず、電極8の寸法は設計次第で様々な寸法とすることができる。

【0026】

電極8のプロセス方向位置にずれが生じないよう電極8を配置した配置パターンを図5に、また電極8のプロセス方向占有範囲に重複が生じるよう電極8を配置した配置パターンを図6に、それぞれ示す。何れの配置パターンにおいても、電極8は絶縁基板層10の表面上に配置されている。また、先に図2に示した通り、クロスプロセス方向に沿い、絶縁基板層10を半導体層9から突出して延ばし、シャフト11を絶縁基板層10から突出して延ばすのが望ましい。各電極8の長さを例えば絶縁基板層10のほぼ全長に亘る長さ等とすれば、電極8の一部分を必要長だけ露出させることができる。

【0027】

図1に示した電源14及び15は高電圧バイアス電源であり、それぞれ固定式プリニップ接触子12又は固定式ポストニップ接触子13、例えば導電ブラシ等の固定電極を介し、電極8の露出部分に接触する。なお、図2等においては固定式プリニップ接触子12及び固定式ポストニップ接触子13は省略してある。電源14及び15は、例えば、プログラムされている制御ルーチンをコンピュータ等の装置にて実行することにより、制御される。電極8用の電源は図示の如く複数個としてもよいし、1個としてもよい。また、その電源(群)から電極8に供給するバイアスは、DCバイアスでもよいし、ACバイアスでもよいし、DCシフトACバイアスでもよいし、その組合せでもよい。電源(群)の動作モードは、定電圧モードでもよいし、定電流モードでもよいし、その組合せでもよい。

【0028】

本実施形態に係るBCR1を間隙付き(即ち非接触式)BCRとして構成する場合、図1、図5及び図6に示すように、ニップ内領域3において、荷電部材表面即ち半導体層9の表面とフォトレセプタ表面2との間に空隙4が発生する。先に数2に示した空気絶縁破壊しきい値電圧VTHは、この空隙4の大きさ(半導体層9の表面とフォトレセプタ表面2との間隔)dAIRが

(数5)

dAIR≦dTH=7.09(DOPC)1/2

という条件を満たしているときには、空隙dAIRに依存しない。例えば、DOPC=7.6μmであるときは空隙しきい値dTH=20μmになるため、dAIR≦20μmなら空気絶縁破壊しきい値電圧VTHは空隙dAIRに依存しない。逆に、空隙dAIRが空隙しきい値dTHを上回っていると、空気絶縁破壊しきい値電圧VTHが空隙dAIRに依存することとなる。そのため、図2に示したクロスプロセス方向に沿って空隙dAIRに不均等さがあると、それによってクロスプロセス方向に沿い荷電不均一性が発生することとなり得る。この現象は、特に、純粋なDCBCR(即ちAC電圧VAC=0のBCR)のうちVDC<0であるときVOPC=VDC+VTHになるものにおいて、生じ得る。従って、本発明を非接触式BCRとして構成する際、クロスプロセス方向荷電不均一性を抑えるには、dAIR≦dTHとするのが望ましい。しかし、本発明は、dAIR>dTHの非接触式BCRとして実施することもできる。その場合には、空気絶縁破壊しきい値電圧VTHが高めになるためDC電圧VDCを高めに設定して所要フォトレセプタ荷電電圧VOPCを得るようにするのが望ましく、また空隙dAIRがクロスプロセス方向に沿ってさほど変化しないよう空隙dAIRについての精度を注意深く制御してクロスプロセス方向荷電不均一性を抑えるのが望ましい。

【0029】

ここに、例えばVTH=600Vの純粋DCBCRにおいてフォトレセプタ(OPC)の荷電電圧乃至電位VOPCを−500Vにするには、従来であれば、VOPC=VDC+VTHの式よりVDC=−1100Vとする必要があった。しかしながら、そのように定めたDC電圧VDCをプリニップ領域にて使用すると、プリニップ絶縁破壊によりポストニップ絶縁破壊が抑制されてしまうため荷電均一性が低くなる。そこで、本発明に従い純粋DCBCRを実現する際には、電極群を1個ずつ又は複数個単位で領域別に分け、電極毎或いは電極グループ毎に一般に異なるDC電圧を印加する(但し同電圧が印加される電極又はそのグループがあってもよい)ことによって、荷電均一性を改善する。グループ分けの仕方には色々なものがあり得、例えば、多数の電極8のうちプリニップ領域6に属するもの、ニップ内領域3に属するもの及びポストニップ領域7に属するものをそれぞれひとまとめにして扱い(順にプリニップ領域内電極群、ニップ内領域内電極群及びポストニップ領域内電極群)、プリニップ領域6だけでなくポストニップ領域7でも空気絶縁破壊が生じるよう、それぞれに対して一般に異なるDC電圧VPRE-NIP、VNIP又はVPOST-NIPを印加するやり方がある。具体的には、図1に示すように2個の直流電源14及び15を用いて純粋DCBCRを構成するのであれば、電極8を、次の式

(数6)

|VPOST-NIP|>(|VPRE-NIP|=|VNIP|)>VTH

により定まる電圧VPRE-NIP、VNIP及びVPOST-NIPによりバイアスすればよい。例えば、VTH=600VでVOPC=−500Vを実現するには、VOPC=VDC+VTHの式に倣いVOPC=VPOST-NIP+VTHの式を用いてVPOST-NIP=−1100Vと決め、DC電圧VNIP及びVPRE-NIPをそれより低く且つ空気絶縁破壊しきい値電圧VTHより高い値例えばVPRE-NIP=VNIP=−850Vとすればよい。このようにすれば、プリニップ絶縁破壊だけでなくポストニップ絶縁破壊も発生し、ポストニップ絶縁破壊によって荷電均一性が顕著に改善される。実際、プリニップ絶縁破壊及びポストニップ絶縁破壊の協働によって荷電均一性が全体的に最適化される。更に、プリニップ絶縁破壊を発生させているため、荷電緩和時間がニップ内滞在時間と概略等しくなるようタイトな比抵抗調整乃至管理を行う必要がなくなり、従ってゴースト欠陥も生じにくくなる。言い換えれば、ニップ内領域3内に入り又はニップ内領域3外に出て行く電界を簡単に且つ精密に制御できるよう、埋め込んだ電極群に対しバイアスを印加しているため、画像欠陥を防止できる。無論、ACバイアスに起因する問題も生じ得ない。また、この構成においては、プロセス方向に並んでいる電極8と電極8との間に半導体層9が介在しているため半導体層9の比抵抗と電圧値の設定とによって電極8同士の間の電流を抑えることができ、また半導体エラストマ等の半導体層9の比抵抗が採り得る範囲も広くなっている。ここで、DOPC=7.6μmでありVTH=600Vである負荷電の例にてDCバイアスが負電圧であるときVOPC=VPOST-NIP+VTHという関係がフォトレセプタ荷電電圧VOPCとDC電圧VPOST-NIPとの間に成り立つことを図7に、またVTH=600Vの純粋DCBCR実施形態にて所要フォトレセプタ荷電電圧VOPCを得る際のDC電圧VPRE-NIP、VNIP及びVPOST-NIPの設定の仕方の例を図8〜図11に、それぞれ示す。これらのうち、図8及び図11に示した例はそれぞれ数6が成り立つよう3個の領域全てでバイアスを印加する例である。図8に示した例ではフォトレセプタ表面2への荷電のうち50%がプリニップ領域6にて、残りの50%がポストニップ領域7にて行われるようバイアス電圧等が設定されているのに対し、図10に示した例ではフォトレセプタ表面2への荷電のうち80%がプリニップ領域6にて、残りの20%がポストニップ領域7にて行われるようバイアス電圧等が設定されている。また、図9に示した例は

(数7)

|VPOST-NIP|>(|VPRE-NIP|=|VNIP|=VTH)

が成り立つよう、即ちフォトレセプタ表面2への荷電が全てポストニップ領域7にて行われるよう3個の領域全てで、バイアスを印加する例である。更に、図10に示した例は

(数8)

|VPOST-NIP|>VTH>(|VPRE-NIP|=|VNIP|)

が成り立つよう、即ちフォトレセプタ表面2への荷電が全てポストニップ領域7にて行われるようバイアスを印加する例、特にプリニップ領域内電極群及びニップ内領域内電極群は接地してポストニップ領域内電極群にのみバイアスを印加する例である(但しプリニップ領域内電極群及びニップ内領域内電極群にバイアスを印加しつつ数8を満足させることもできる)。これらの図から理解できるように、本発明によれば、様々な荷電態様を容易に且つ精密に実現できる。更に、DC電圧VPRE-NIP及びVNIPと電圧VPOST-NIPとの差が小さいため、図9に示した例の方が図10に示した例に比べて電極8同士の間の電流が小さくなる。

【0030】

また、図5及び図6においては、隣り合う電極8同士が半径方向に沿ってずれた位置にある。更に、図6においてはプロセス方向に沿い電極8同士が重複しているが(重複部分17)、図5においては重複部分17の幅が0である。

【0031】

半導体層9は、一方では、電極8同士の間の電流を制限できるよう十分な比抵抗を有していなければならず、他方では、BCR1の表面に発生し堆積した電荷を迅速且つ確実に緩和できるよう十分な導電性を有していなければならない。

【0032】

また、BCR1の全周及び全長のどこでも概ね均一なニップ内領域3を形成できるようにするには、十分な可撓性を有する可撓性エラストマにより半導体層9を形成するのが望ましい。半導体層9乃至これを構成する可撓性エラストマのショアO硬度は、例えば約0〜約100の範囲内であることが望ましく、約15〜約80の範囲内であれば更に望ましい。半導体層9として好適に使用できる可撓性エラストマとしては、例えば、ウレタンラバー(urethane rubber)、エピクロロヒドリンエラストマ(epichlorohydrin elastomer)、EPDM(エチレン−プロピエン−ジエン三元共重合体)ラバー(EPDM rubber)、スチレンブタジエンラバー(styrene butadiene rubber)、フルオロエラストマ(fluoro-elastomer)、シリコーンラバー(silicone rubber)等がある。また、エラストマの比抵抗を変化させ又は調整したいのであれば、素材中に各種のイオン種や導電性フィラをドーピングする等、様々な手法を採ることができる。そして、半導体層9の厚みは如何様にも設定できるが、例えば約0.02〜約10mm、より好ましくは約0.2〜約1mmの範囲内とする。無論、硬く形状的に適合させにくい層を半導体層9として形成することもできる。

【0033】

半導体層9の素材選択、特性調整、形成等に際しては、その緩和時間tRELAXが

(数9)

tRELAX<〜0.2×(WELECTRODE/VPROCESS)(但しWELECTRODEは埋め込まれている電極8(1個分)の幅、VPROCESSは電子写真プロセスにおけるプロセス速度)

の条件を満たすようにするのが望ましい。この条件を満たすためには、半導体層9として用いるエラストマの比抵抗ρは、理論的には、

(数10)

ρ<tRELAXDOPC/(dε0)(但しDOPCはフォトレセプタ誘電体厚、dはエラストマ厚、ε0は自由空間誘電率)

という条件を満たしていなければならない。また、プロセス速度VPROCESSは普通は約100mm/s(毎分約25ページ)から約250mm/s(毎分約60ページ)であるが、本発明はプロセス速度VPROCESSがこれより高い(例えば300mm/s超の)又は低いマシンにおいても実施することができる。プロセス速度VPROCESSの値域は、例えば約25〜約1250mm/sといったところであろう。また、電極幅WELECTRODEは、例えば約0.05〜約6mm、好ましくは約0.5〜約3mmの範囲内とする(ニップ内領域3の幅が約0〜6mmの場合)。

【0034】

更に、フォトレセプタ側に小規模欠陥があるときに、BCR1とフォトレセプタ接地面16との短絡即ちバイアスリークによって誘電体絶縁破壊が生じないようにするには、誘電体絶縁破壊電界EBREAK即ち誘電体絶縁破壊が発生する電界の値ができるだけ大きい素材及び態様を以て半導体層9を形成すると共に、半導体層9の厚みdを十分に厚くする必要がある。誘電体絶縁破壊電界EBREAKは1V/μmを超える電界とする必要があり、半導体層9として使用するエラストマが薄い場合は100V/μmを超える電界とすることが必要となることもあろう。例えば誘電体絶縁破壊電界EBREAKが5V/μmのエラストマにより半導体層9を形成した場合、電極8に印加される電圧のピーク値が1100Vに達し得る用途においては、誘電体絶縁破壊を防ぐのにd>0.2mmであることが必要である。他方、プリニップ領域6及びポストニップ領域7における電界制御を(好適に)実行可能にするには、半導体層9の厚みdを十分薄くしなければならない。以上の条件を考慮すると、半導体層9の比抵抗ρは例えば約104〜約1013Ω・cmの範囲内とするのが望ましいが、これより高い又は低い比抵抗ρを有する層を半導体層9として用いてもかまわない。

【0035】

各領域において印加する電圧は、その電子写真プロセスに対してどのような結果乃至成果が望まれているかに応じ、定めればよい。電圧VPRE-NIP、VNIP及びVPOST-NIPは、トナーの荷電が正か負かにもよるが、最も狭く見ても−10000〜+10000Vの範囲に属する値を採り得る。先により詳細に述べた通り、最終的に得られるフォトレセプタ荷電電圧VOPCはポストニップ領域7内で印加されているDC電圧VPOST-NIPに依存しており、負荷電であればVOPC=VPOST-NIP+VTHの式により、正荷電であればVOPC=VPOST-NIP−VTHの式により、その値が定まる。例えば、VTH=600Vである場合にフォトレセプタを+500Vまで正荷電するには、ポストニップ領域7内で印加するDCバイアス電圧VPOST-NIPを+1100Vに設定する必要がある。

【0036】

電源14及び15から取り出すことができる最大電流IMAXは、例えば約2〜約3mAの範囲に属する値とし、より好ましくは例えば約10若しくは20mA又はそれ以上とする。なお、電源14及び15から大電流が引き出されるのは、隣り合っている電極8同士でそのバイアス電位が著しく異なるときや、光導電体に恒久的に発生し接地に対して非常に低い抵抗値を示す小さなスポット即ちピンホール欠陥がフォトレセプタ(ドラム又はベルト)にて生じていてBCR1がフォトレセプタ接地面16と短絡しているときである。

【0037】

本発明を実施するに当たっては、例えばDOPC=7.6μm(即ちVTH=600V)とし、負荷電のためバイアス電圧VPRE-NIP及びVNIPを共に約−850Vとしバイアス電圧VPOST-NIPを約−1100Vとする(これによりフォトレセプタ荷電電圧VOPCは−500Vとなる;図8参照)。また、プロセス速度VPROCESSは例えば約100mm/sとする。荷電緩和時間tRELAXはこのプロセス速度VPROCESSと電極幅WELECTRODEから決まる。更に、最大電流IMAXは約1mA、誘電体絶縁破壊電界EBREAKは約5V/μmとする。そして、電極8同士の間隔は約0.5mm、半導体層9の厚みdは約0.3〜約0.5mmと設定する。このように厳しく設定した場合でも、半導体層9の比抵抗ρが採り得る範囲は、好ましくも、約3×106〜5×108Ω・cmという比較的広い範囲となる。比抵抗ρの値域がこのように比較的広いため、この範囲内の比抵抗ρを実現でき電荷を緩和できるエラストマは多く、これは本発明の実施に際して有利な事項である。なお、先に述べたように電荷を迅速に緩和できるよう半導体層9の導電性を十分にしておかねばならないため、半導体層9が採り得る比抵抗ρの最大値は緩和時間tRELAXにより概ね決まる。他方、電極8同士の間の電流を制限できるようにしておかねばならないため、半導体層9が採り得る比抵抗ρの最小値は、電源14及び15から流すことができる最大電流IMAXの値、即ち(1)バイアスリーク状況下で接地へと電流が流れた場合でも(2)加わっているバイアス電圧値が異なる電極8同士の間で電流が流れた場合でも超えてはならないとされている電流IMAXの値により、決定される。

【0038】

比抵抗ρが上掲の好ましい範囲内に属している場合、半導体層9上の電荷はプロセス速度VPROCESSに対する電極幅WELECTRODEの比WELECTRODE/VPROCESSに比して短い時間(緩和時間tRELAX)内で緩和する。このように緩和時間tRELAXが短いためニップ内領域3において電荷を接地面に逃がすことは概ね不要であるが、半導体層9の表面上に電荷が積もり積もって過剰になることを防ぐには、ニップ内領域3内で適当なバイアスを印加すること或いは接地することが望ましいとも言える。

【0039】

また、BCR1の汚れを最小限まで抑えるには、例えば、ブレードタイプ、パッドタイプ、ブラシタイプ等のクリーナを、BCR1に設けるとよい。もしクリーナを設けるのであれば、その位置は、プリニップ領域6やポストニップ領域7の外側とする。

【0040】

本発明の好適な実施形態に係る電極付きBCRは、これまでBCRが用いられてきたどのような電子写真システムにおいても、用いることができる。また、本発明の好適な実施形態に係る電極付きBCRによれば、システムにおけるバイアスの加え方及び値を必要乃至所望に応じて変化させることができる。例えば、図10に示した例ではプリニップ領域内電極群及びニップ内領域内電極群を全て接地しポストニップ領域内電極群に高電圧バイアスを印加しているが、図8、図9及び図11に示した例ではプリニップ領域内電極群及びニップ内領域内電極群にもバイアスを印加している。更に、本発明によれば、これに限られるものではないが、次に述べる例を含め幾つかの異なるやり方によって、埋め込んだ電極群に対しバイアスを加えることができる。

【0041】

まず、BCR1のプリニップ領域6、ニップ内領域3及びポストニップ領域7それぞれにて印加するバイアス電圧は、互いに異なるものとすることができ、また随時変えることができる。更に、BCR1のプリニップ領域6、ニップ内領域3及びポストニップ領域7それぞれの内部において、固定部分の構造等を工夫することによってバイアス電圧値を変える(分布させる)ことも可能である。電極8に対するバイアス印加は、電極8の1個毎に行ってもよいし、1個又は複数個の電極8を含む幾つかのグループ毎に行ってもよい。各電極8又はそのグループに対するバイアス電圧は異なる電圧とすることもできるし、幾つかの電極8又はそのグループについて互いに同じバイアス電圧とすることもできる。更に、広範囲に分布する電極群に対し、バイアスされている電極8間でそれらを覆う半導体層9の表面に沿った電極間電圧降下乃至電位差が生じるようバイアス電圧を印加し、それにより、バイアスされている電極8間の電位差が半導体層9の表面に沿って滑らかに変化していくように(電界分布が最適化されるように)、することもできる。グループ分けの仕方としては、例えば、プリニップ前領域内電極群、プリニップ領域内電極群、ニップ内領域内電極群、ポストニップ領域内電極群及びポストニップ後領域内電極群という分け方もある。無論、他のやり方でグループ分けを行ってもよい。ニップ内領域3から大きく離れている電極群については、BCR1の表面に蓄積される電荷が緩和されるようバイアスしてもよいし接地してもよい。印加するバイアスはDCバイアスでもよいし、ACバイアスでもよいし、DCシフトACバイアスでもよい(先にDCバイアスの例について説明を行ったがACバイアス乃至DCシフトACバイアスでも本発明は効果がある)。電源(群)の動作モードは定電圧モードでも定電流モードでもよい。

【0042】

本発明に係るBCRシステムの各構成部材の配置や素材に関しては、本発明の技術的範囲から逸脱することなく、様々に変えまた置換することができる。例えば、図1に示すように電極8同士が密接して配置されている場合、電源14及び15から流れ出す電流が大きくなり得るため、電源14及び15から引き出すことができる電流についての制限(最大電流IMAXによる制限)を緩くする必要がある。即ち、電極間隔ΔxELECTRODEと最大電流IMAXの間には

(数11)

IMAXΔxELECTRODE=k(但しkは定数)

という関係があり、電極間隔ΔxELECTRODEを縮めたらそれに反比例して最大電流IMAXを大きくしなければならない。なお、定数kは、半導体層9として使用するエラストマの厚みd、その最小所望比抵抗及びそのクロスプロセス方向長さと、隣り合っている電極8同士の間に発生し得る最大の電位差とにより、定まる。

【0043】

更に、電極間隔ΔxELECTRODEは例えば0.1mm未満とする。また、電極8の配置パターンは、荷電領域における高い均一性を保証できるよう様々に設定することができる。例えば、図4に示したように、BCR1の断面上で電極8の配置箇所を結ぶと2本の曲線となり、各曲線上における電極8の位置が互い違いになり、且つ一方の曲線に属する電極8と他方の曲線に属する電極8とが部分的に重なり合うよう(或いはそれに近い状態となるよう)、電極8を配置することができる。また、図6に示したようにプロセス方向に沿い電極8同士が重なり合うよう電極8を配置することもできるし、図5に示したようにプロセス方向における電極8同士の重複部分17の幅が0になるよう電極8を配置することもできる。図5に示したように配置すれば製造が比較的容易になる。また、図5の実施形態においても図6の実施形態においても、隣り合う電極8同士の半径方向間隔は、0.1〜1mmの範囲に属する値とするのが望ましいが、この範囲外の値とすることもできる。また、図5の実施形態においても図6の実施形態においても電極8は絶縁基板層10上に配置されているが、電極8は絶縁基板層10や半導体層9の内部に埋め込むこともできる。

【0044】

更に、半導体層9として使用するエラストマの厚みd及び比抵抗ρは最適化可能である。例えば、エラストマは半導体とするのが望ましいが、エラストマの導電性が十分良好であれば、ある電圧でバイアスされている電極8とその隣にあり同じ電圧でバイアスされている電極8とにより挟まれる領域における電位分布は均一分布に近い分布になる。

【図面の簡単な説明】

【0045】

【図1】本発明の一実施形態に係る電極付きBCR(バイアスド荷電ローラ)システムの軸断面図である。

【図2】本実施形態における電極付きBCRの頂面図である。

【図3】図2に示した電極付きBCRのIII−III断面図である。

【図4】本実施形態における電極付きBCRの部分拡大断面をフォトレセプタ表面の一部と共に示す図である。

【図5】本発明の他の実施形態における電極付きBCRの部分拡大断面をフォトレセプタ表面の一部と共に示す図である。

【図6】本発明の更に他の実施形態における電極付きBCRの部分拡大断面をフォトレセプタ表面の一部と共に示す図である。

【図7】ポストニップ領域におけるバイアス電圧とフォトレセプタ荷電電圧との関係を示す図である。

【図8】プリニップ領域及びポストニップ領域における荷電の仕方の例を示す図であ る。

【図9】プリニップ領域及びポストニップ領域における荷電の仕方の他の例を示す図である。

【図10】プリニップ領域及びポストニップ領域における荷電の仕方の更に他の例を示す図である。

【図11】プリニップ領域及びポストニップ領域における荷電の仕方の更なる例を示す図である。

【技術分野】

【0001】

本発明は、高速電子写真印刷用のバイアスド荷電ローラ(BCR:biased charge roller)に関し、より詳細には、電荷保持面上における電荷の堆積を制御するためローラ表面下に整列して埋め込まれた縦長電極群を有するBCRに関する。

【背景技術】

【0002】

通常、静電画像化印刷プロセスは幾つかの個別段階から構成されており、各段階は一般に(1)荷電、(2)画像化、(3)露出、(4)現像、(5)転写、(6)融着及び(7)清掃と呼ばれている。荷電段階においては、電荷保持面例えばフォトレセプタ表面上に電荷を均一に堆積させることによって、この電荷保持面を静電的に感受性とする。画像化段階においては原画像を取得する。露出段階においては、静電感受的となっているフォトレセプタ表面上に取得した画像を投影し露出することにより、原画像に対応する静電潜像をフォトレセプタ表面上に記録する。現像段階においては、荷電トナー粒子をこの静電潜像に接触させることにより当該静電潜像を現像する。このとき、CAD(charged area development)を用いるのであればフォトレセプタ表面上の荷電領域へと荷電トナー粒子が引き寄せられ、またより一般的なDAD(discharged area development)を用いるのであればフォトレセプタ表面上の非荷電領域へと荷電トナー粒子が引き寄せられて、静電潜像に対応する像が現れる。転写段階を単一ステップにて行う際には、当該転写段階において、トナー粒子が静電的に吸着しているフォトレセプタ表面を、紙その他の基板により提供される画像受容面に接触させる。このとき、トナー粒子に対し静電界が作用するためトナー粒子は画像受容面に吸い寄せられて付着する。即ち、フォトレセプタ表面から画像受容面上へとトナー粒子が転写される。融着段階においては、溶融乃至加圧によりトナー粒子が画像受容面に融着する。清掃段階においては、清掃装置によってフォトレセプタ表面上から残存トナー粒子を取り除く。これによって、一連のプロセスが完了する。

【0003】

フォトレセプタ表面に荷電する装置としては接触式荷電装置が知られている。接触式荷電装置は、フォトレセプタ等の画像担持部材の荷電対象面に接触する荷電用導電部材を有しており、この荷電用導電部材に適当な電圧を印加すれば当該荷電対象面を所定電位VOPCまで荷電することができる。荷電用導電部材をローラ状の形状乃至構造としたものを荷電ローラと呼び、電源からバイアス電圧の供給を受ける荷電ローラをバイアスド荷電ローラ即ちBCRと呼び、当該バイアス電圧がDC電圧又はAC電圧である場合そのBCRをそれぞれDCBCR又はACBCRと呼び、ACBCRの中でもバイアス電圧がDC/AC重畳電圧(DCシフトAC電圧)であるものをDCシフトACBCRと呼ぶ。DCシフトACBCRにおけるDC/AC重畳電圧はDC電圧VDCにAC電圧を重畳させた電圧であり、このAC電圧のピークトゥピーク振幅VACは空気絶縁破壊しきい値電圧VTHの2倍以上とする必要がある。即ち、一般に荷電ローラとフォトレセプタとの間には、その接触部の上流側及び下流側それぞれに空隙(後述のプリニップ空隙及びポストニップ空隙)が発生する。荷電ローラに対し十分な電圧が印加されるとこれらの空隙にて空気絶縁破壊が生じ、フォトレセプタ外表面はこの空気絶縁破壊に伴い荷電される。注記すべきことに、荷電用導電部材として十分な導電性を有する荷電ローラを使用する場合、空気絶縁破壊しきい値電圧VTHは、次の式

(数1)

DOPC(μm)=dOPC/k(但しdOPCはフォトレセプタ厚、kは定数(フォトレセプタ誘電率))

により与えられるフォトレセプタ誘電体厚DOPCを用い、次の式

(数2)

VTH〜312+87.96(DOPC)1/2+6.2DOPC

によって与えることができる。例えば、DOPC=7.6μmのフォトレセプタであればこの式からVTH=600VとなるためVAC>1200Vとしなければならない。特に、従来方式によるDCシフトACBCRを用いる場合、DC電圧VDCによってフォトレセプタ荷電電圧乃至電位VOPCがVOPC=VDCと決まる。フォトレセプタ荷電電圧VOPCが決まれば、

(数3)

VOPC=σDOPC/ε0、σ=Q/A

の関係からフォトレセプタの表面に堆積する電荷量Q及びその密度(単位面積当たり電荷量)σが決まる(但しε0は自由空間誘電率、Aはフォトレセプタ表面積)。なお、荷電用導電部材が荷電ロールとして構成されている接触式荷電装置については、この参照を以て本願に繰り入れられるところの特許文献11並びに特許文献1乃至4を参照されたい。

【0004】

接触式荷電装置を用いる際に大切なのは、その荷電用導電部材を、電荷保持面例えばフォトレセプタ表面に対し、その長手方向に沿い均等に接触させることである。従って、接触式荷電装置における荷電用導電部材例えば荷電ローラは、通常、その形状を適合させやすく柔らかい素材により形成し、フォトレセプタ等の光導電性部材乃至光導電性ドラムに対する接触状態を良好に保持できるようにする。印刷装置においては、普通、このようにしてフォトレセプタ等に接触している荷電ローラに対し、AC電圧やDC電圧を印加する。

【0005】

電荷保持面と荷電ローラ表面との接触部近傍は、ニップ内領域、プリニップ領域及びポストニップ領域という三種類の領域に区分することができる。これらのうちニップ内領域即ち前述の接触部は、電荷保持面と荷電ローラ表面とが直接接触する点を含む領域である。また、プリニップ領域はニップ内領域から見て上流側の領域、ポストニップ領域はニップ内領域から見て下流側の領域である。プリニップ領域は電荷保持面と荷電ローラ表面とが接触しつつある領域でありポストニップ領域は離れていく領域であるため、プリニップ領域及びポストニップ領域においては電荷保持面と荷電ローラ表面とが直接接触せず、従って前述の通り両者の間に空隙が発生する。これをプリニップ空隙及びポストニップ空隙と呼び、当該空隙における空気絶縁破壊をそれぞれプリニップ絶縁破壊又はポストニップ絶縁破壊と呼ぶ。

【0006】

先に述べたように、荷電段階において目的としているのは、電荷保持面例えばフォトレセプタ表面上に電荷を均一に堆積させること、即ち荷電均一性である。しかしながら、荷電方式として仮にDCバイアス荷電方式を使用することとすると、周知の通り、荷電均一性が貧弱なものになる。これは、既に判明している通りポストニップ絶縁破壊の方がプリニップ絶縁破壊に比べ電荷保持面例えばフォトレセプタ表面をより均一に荷電できるのに、DCバイアス荷電方式ではプリニップ絶縁破壊によりポストニップ絶縁破壊が抑制されてしまうためである。そのため、従来から、DCバイアス荷電方式よりもACバイアス荷電方式の方が一般に用いられている。ACバイアス荷電方式では、DCシフトAC高電圧電源を用いてポストニップ絶縁破壊を発生させ、それにより荷電均一性を(DCバイアス荷電方式に比べ)良好としている。しかしながら、ACバイアス荷電方式には、コストが高いことやフォトレセプタが摩耗しやすいことを含め幾つかの欠点がある。

【0007】

即ち、DCシフトACBCRは、小型電子写真エンジンにて広く用いられているバイアス荷電手段の一つであり、これを用いた場合、プリニップ空隙でもポストニップ空隙でも空気絶縁破壊が生じる。そのため、この種のBCRを用いれば、荷電均一性をより良好にすることができ、またオゾンもほとんど発生しなくなる。しかしながら、荷電ローラに高電圧のAC電圧分も印加されるため、摩耗の程度が大きく、高コストとなりやすく、帯状欠陥(banding)が発生することがあり、プロセス速度が制限される、といった問題点をはらんでいる。

【0008】

第1に、ACBCRを用いた場合、AC電圧分によりフォトレセプタ表面上に正電荷及び負電荷が堆積する。そのうち正電荷はフォトレセプタを形成しているポリマを弱体化させる。清掃装置のブレード(刃)が当たるとこの弱体化しているポリマはすり減り、その結果、摩耗の程度が甚だしくなり寿命が短縮される。既に判明していることであるが、BCRによる正電荷堆積を防ぐことができれば、フォトレセプタの寿命は2倍に延長されるであろう。

【0009】

第2に、従来方式によるBCRにおいては、DC電源だけでなく一般に高価な高電圧AC電源も必要となる。また、かかるAC電圧を印加するとフォトレセプタにて可聴領域の雑音が発生する。この雑音の量を減らすため雑音低減手段を設けるには、そのための費用が必要となる。

【0010】

第3に、AC電圧を使用すると空間的帯状欠陥が発生する。この帯状欠陥のプロセス方向間隔Xは、プロセス速度をVPROCESS、AC電圧の周波数をfとすると、

(数4)

X=VPROCESS/f

で表すことができる。従って、周波数fが低ければ間隔Xが大きくなるため看者はこの帯状欠陥を知覚できない。しかし、周波数fが低いままでプロセス速度VPROCESSを高めるとこの帯状欠陥が高周波の空間的帯状欠陥となり看取されやすくなるため、プロセス速度をVPROCESSを高めるには併せてAC電圧の周波数fを高めねばならない。AC電圧一定のまま周波数fを高めるとAC電流が1/fに比例して減少するため、十分なAC電流を得るにはAC電源それ自体を能力の高い大型のもの(従って一般に高価なもの)にすることを余儀なくされる。そのため、周波数fひいてはプロセス速度VPROCESSを高めるには自ずから限界がある。

【0011】

ところで、DCバイアス荷電方式を用いることができない又は用いるのが好ましくない第1の理由は、ポストニップ絶縁破壊が生じないため十分な荷電均一性が得られないことである。即ち、十分高い負DC電圧をBCRのシャフトに印加すると、プリニップ領域内電界がパッシェン曲線を上回ってプリニップ絶縁破壊が発生するが、その後各空隙における電界が落ち込んでパッシェン曲線を下回るまでは負電荷がフォトレセプタ表面上に堆積され、負電荷が堆積しているとポストニップ領域では空気絶縁破壊が生じないため荷電が不均一になる。もっとも、荷電緩和時間がニップ内滞在時間(dwell time in nip)と概略等しくなるようBCRエラストマの比抵抗が精密に調整されていれば、ポストニップ領域内電界がプリニップ領域内電界を上回り荷電がより均一になるが、そのようにするのは普通は現実的でない。それは、比抵抗について非常にタイトな調整乃至管理が必要になるためである。加えて、この電界最適化(field tailoring)方式に従い比抵抗を調整するとDCBCRの感度が増すため、荷電を均一にしようとしているにもかかわらずゴースト欠陥が発生する。ゴースト欠陥とは、フォトレセプタ表面上に均一に堆積されるはずの電荷が、前回サイクルにてフォトレセプタ表面上に形成された静電潜像(例えば放電パターン)に応じて堆積してしまうことを、指している。従って、ゴースト欠陥が発生すると前回サイクルでの静電潜像がゴースト画像となって印刷物上に現れてしまう。

【0012】

【特許文献1】米国特許第4851960号明細書

【特許文献2】米国特許第5164779号明細書

【特許文献3】米国特許第5613173号明細書

【特許文献4】米国特許第2912586号明細書

【特許文献5】米国特許第6360065号明細書

【特許文献6】米国特許第3043684号明細書

【特許文献7】米国特許第3398336号明細書

【特許文献8】米国特許第3684364号明細書

【特許文献9】米国特許第3702482号明細書

【特許文献10】米国特許第6006447号明細書

【特許文献11】米国特許第4387980号明細書

【特許文献12】米国特許第5634179号明細書

【特許文献13】米国特許第2807233号明細書

【特許文献14】米国特許第3781105号明細書

【特許文献15】米国特許第3830589号明細書

【特許文献16】米国特許第3832055号明細書

【特許文献17】米国特許第3936174号明細書

【特許文献18】米国特許第3832053号明細書

【特許文献19】米国特許第5276490号明細書

【特許文献20】米国特許第5303013号明細書

【特許文献21】米国特許第5583623号明細書

【特許文献22】米国特許第5697034号明細書

【特許文献23】米国特許第6075965号明細書

【特許文献24】米国特許第6203743号明細書

【特許文献25】欧州特許公報第0642063号(A1)

【特許文献26】欧州特許公報第0642063号(B1)

【発明の開示】

【0013】

ここに、本願にて説明する電極付きDCBCRによれば、ACBCRにて生じる問題を発生させることなく、また上述の電界最適化方式を使用したDCBCRにて生じる問題も発生させることなく、ポストニップ領域における荷電を可能にしまたより良好な荷電均一性を実現することができる。

【0014】

本発明に係るBCRは、フォトレセプタ表面上に電荷を均一に堆積させ当該表面を静電的に感受性とするための部材乃至装置であり、荷電が均一であること、摩耗及びコストを実質的に減らせること等を含め、幾つかの利点を有するものである。

【0015】

本発明においては、前掲の従来技術に鑑み、荷電均一性に優れ摩耗が少なくより安価なBCRシステムを提供することを、目的としている。

【0016】

本発明においては、BCR内に電極群を埋め込むことによってこの目的を達成しまたその他の利点を実現している。埋め込んだ電極群に対しては、例えば、荷電ニップ領域内に入り又は荷電ニップ領域外に出て行く電界を簡単に且つ精密に制御でき上述の画像欠陥を防止できるよう、バイアスを印加する。

【0017】

電極群は、例えばBCR基板上に埋め込み、BCRの表面上に蓄積される電荷を緩和できるよう半導体層で覆うこととする。この半導体層は、形状を適合させやすく(形状加工乃至形成しやすく)柔らかい層としてもよいし、逆に形状を適合させにくく(形状加工乃至形成しにくく)硬い層にしてもよい。

【0018】

埋め込んだ電極群に対するバイアスの加え方には、幾つかの異なるやり方がある。例えば、プリニップ領域にある電極(群)及びニップ内領域にある電極(群)は接地しポストニップ領域にある電極(群)にはバイアスを印加する、というやり方がある。また、これらの領域全てにおいてバイアスを印加する、というやり方もあるし、各領域内でバイアスを変化(分布)させる、というやり方もある。更に、広範囲に分布する電極群に対し、それらを覆う半導体層に沿った電極間電圧降下乃至電位差が生じるようバイアスを印加し、それにより電界最適化効果を得る、というやり方もある。ニップ内領域から大きく離れている電極群については、BCR表面に蓄積される電荷が緩和されるようバイアスしてもよいし接地してもよい。電極に対するバイアス印加は、電極1個毎に行ってもよいし、1個又は複数個の電極を含む幾つかのグループ毎に行ってもよい。各電極又はそのグループに対するバイアスは異なるバイアスとすることもできるし、幾つかの電極又はそのグループについて互いに同じバイアスとすることもできる。グループ分けの仕方としては、例えば、プリニップ前領域内電極(群)、プリニップ領域内電極(群)、ニップ内領域内電極(群)、ポストニップ領域内電極(群)及びポストニップ後領域内電極(群)というやり方があるが、無論他のやり方でグループ分けを行ってもよい。印加するバイアスはDCバイアスでもよいし、ACバイアスでもよいし、DCシフトACバイアスでもよい。電源(群)の動作モードは定電圧モードでも定電流モードでもよい。

【発明を実施するための最良の形態】

【0019】

本発明の好適な実施形態に係るBCRは、絶縁基板(層)と、BCRの表面上に蓄積される電荷を緩和できるよう絶縁基板(層)を覆う半導体層と、を備える電荷保持面荷電用BCRにおいて、絶縁基板(層)の上若しくは内部又は絶縁基板(層)を覆う半導体層の内部のうち少なくとも何れかに配置された多数の電極を備え、絶縁基板(層)をBCR内部に埋め込まれた電極群もろとも半導体層により覆った電荷保持面荷電用電極付きBCRであり、接触式BCRとしても間隙付き(即ち非接触式)BCRとしても実現できる。その半導体層は、接触式か否かを問わず、形状を適合させやすく柔らかい層としてもよいし(但し接触式の場合はフォトレセプタ等との間で良好な接触状態を保持する上でこちらの方が望ましい)、逆に形状を適合させにくく硬い層にしてもよい(但し硬い層は接触式より非接触式に適している)。形状を適合させやすい半導体層は例えばエラストマによって実現できる。更に、本発明の好適な実施形態における電極群は、ニップ内領域内電界だけでなくプリニップ領域内電界やポストニップ領域内電界も制御できるよう、また幾つかの異なるやり方で、バイアスすることができる。

【0020】

図1に、本発明の一実施形態に係る電極付きBCRシステムの軸断面を示す。この図に示すBCR1は、フォトレセプタ接地面16を取り巻いているフォトレセプタ表面2に隣り合うよう、位置決めされている。BCR1とフォトレセプタ表面2は、ニップ内領域3において最接近している。即ち、接触式の場合は図2に示すクロスプロセス方向に沿ってフォトレセプタ表面2に均等に接触するよう、また非接触式の場合はクロスプロセス方向に沿ってフォトレセプタ表面2に対し均等な間隔を呈するよう、BCR1が配置される。

【0021】

また、ニップ内領域3の上流側にはプリニップ領域6が、下流側にはこれに相応してポストニップ領域7がある。プリニップ領域6及びポストニップ領域7においては、BCR1とフォトレセプタ表面2との間に、空隙が生じている。なお、フォトレセプタは例えばベルト或いはドラム等、様々な構成とすることができる。

【0022】

BCR1は、通流用縦長電極8、半導体層9、絶縁基板層10及びシャフト11を備え、シャフト11の軸を中心に回転させることが可能なロール状の部材である。シャフト11は、絶縁基板層10を支持できる素材である限り、どのような素材からも形成でき、導体でも非導体でもよく、例えばスチールシャフトとして構成することができる。シャフト11はBCR1の絶縁基板たる絶縁基板層10によって概ね覆われており、この絶縁基板層10上には多数の電極8が整列して配置されており、絶縁基板層10及び電極8は半導体層9により概ね覆われている。このように本実施形態では電極8は絶縁基板層10と半導体層9との間に配置されているが、全ての又は一部の電極8を絶縁基板層10又は半導体層9の内部に多数整列して埋め込んでもよい。何れにせよ、電極8は回転可能なBCR1即ち可動部分に組み込まれているため、固定部分に配置されている部材例えば固定された電源14及び15に対して電極8を電気的に接続するには、可動部分と固定部分とを電気的に接続するための部材が必要である。本実施形態においては、それぞれ1個又は複数個の電極8を含む複数個の電極群に対してそれぞれ異なるバイアスを印加するための経路を、当該部材によって提供している。その種の部材として本実施形態にて設けられているのは、具体的には、電圧VPRE-NIPを供給する電源14に接続されている固定式プリニップ接触子12、並びに電圧VPOST-NIPを供給する電源15に接続されている固定式ポストニップ接触子13である。これらの接触子12及び13は、BCR1の回転に伴いプリニップ領域6に入ってきた電極8が固定式プリニップ接触子12に電気的に接触し、その後ニップ内領域3に入ってきた電極8が引き続き固定式プリニップ接触子12に電気的に接触し、更にその後ポストニップ領域7に入ってきた電極8が固定式ポストニップ接触子13に接触するよう、設けられている。従って、プリニップ領域6に属する電極8の集まり即ちプリニップ領域内電極群、並びにニップ内領域3にある電極8の集まり即ちニップ内領域内電極群に対しては電圧VPRE-NIPによって電荷が供給され、ポストニップ領域7に属する電極8の集まり即ちポストニップ領域内電極群に対しては電圧VPOST-NIPによって電荷が供給される。なお、ここではプリニップ領域内電極群とニップ内領域内電極群とに同じ電圧VNIPを印加する例を示しているが、異なる電圧を印加するように固定部分の構造等を定めることもできる。更に、電圧VPRE-NIPと電圧VPOST-NIPは異なる電圧とすることができる。例えばこの図の例では、電源14は電圧VPOST-NIPを分圧して得られる電圧を電圧VPRE-NIPとして供給している。また、電圧VPRE-NIP及び電圧VPOST-NIPを随時切り替えることもできる。例えばこの図の例では、電源14は電圧VPRE-NIPを接地電位に切り替えられるよう構成されている。更に、この図に示した例は、多数の電極8をプリニップ領域内電極群、ニップ内領域内電極群及びポストニップ領域内電極群にグループ分けしてバイアス電圧を印加する例であるが、電極8のグループ分けの仕方及び固定部分と可動部分との接続関係乃至接続方式は、より複雑なものにすることもできる。例えば、プリニップ前領域内電極群、プリニップ領域内電極群、ニップ内領域内電極群、ポストニップ領域内電極群及びポストニップ後領域内電極群という5種類のグループそれぞれを個別にバイアスできるよう、別個の固定式接触子を設けてもよい。プリニップ前領域とはプリニップ領域6より更に上流側の、またポストニップ後領域とはポストニップ領域7より更に下流側の、領域を指している。

【0023】

本実施形態におけるBCR1の頂面を図2に、またそのIII−III断面を図3に、それぞれ示す。これらの図に示すように、シャフト11は絶縁基板層10により、また絶縁基板層10の表面は半導体層9により、概ね覆われている。電極8は、図1に示したように絶縁基板層10と半導体層9の間に配置することもできるが、図4に示すように半導体層9内に埋め込むこともできる。図4に示す例では、多数の電極8を1個おきに半導体層9内に埋め込み、残りを絶縁基板層10と半導体層9の間に配置している。但し、製造の容易さを考えると、電極8は、図1に示したように絶縁基板層10上に配置する方がよい。

【0024】

例えばポリアミド(polyamide)等の絶縁素材により形成された絶縁外皮である絶縁基板層10は、例えば約0.1〜約20mmの厚みでシャフト11を概ね覆っている。シャフト11の直径が例えば約6〜約10mmであるなら、絶縁基板層10の厚みは約5〜約10mmとし、その周りの半導体層9、例えばBCR1の表面上に蓄積される電荷を緩和できるエラストマの厚みは約0.2〜約1mmとする。なお、ここで示した数値は一例に過ぎず、設計次第で様々な直径乃至厚みとすることができる。

【0025】

各電極8の長さ(図2中のクロスプロセス方向に沿った寸法)はBCR1(或いはそのシャフト11や絶縁基板層10や半導体層9)のほぼ全長に亘る長さとするのが望ましいが、当該全長とは異なる長さの電極8を用いることや、電極8同士の間でその長さを規則的パターンに従い変えることも可能である。また、各電極8の幅(図2中のプロセス方向即ちBCR1の回転方向に沿った寸法)は、例えば約0.05〜約3mmの範囲に属する幅とすればよく、好ましくは約0.2〜約0.7mmの範囲内とする。更に、各電極8の厚み(図3中の半径方向即ちBCR1の表面に直交する方向に沿った寸法)は、好ましくは例えば約50μm未満とする。そして、電極8同士の間隔は、絶縁基板層10の表面に沿い隣り合う電極8同士の間に平均して約0.05〜約3mmの範囲に属する間隙が生じるよう、より好ましくは約0.2〜約0.7mmの範囲に属する間隙が生じるよう、規則的なパターンに従って定めるのが望ましい。何れにせよ、電極8の寸法及び間隔は、発生する電界を十分精密且つ確実に制御できる程度に電極8同士が近づくよう、それでいて電極8同士の間に流れる電流を十分制限できる程度に電極8同士が離れるよう、定めるべきである。勿論、ここで示した数値は一例に過ぎず、電極8の寸法は設計次第で様々な寸法とすることができる。

【0026】

電極8のプロセス方向位置にずれが生じないよう電極8を配置した配置パターンを図5に、また電極8のプロセス方向占有範囲に重複が生じるよう電極8を配置した配置パターンを図6に、それぞれ示す。何れの配置パターンにおいても、電極8は絶縁基板層10の表面上に配置されている。また、先に図2に示した通り、クロスプロセス方向に沿い、絶縁基板層10を半導体層9から突出して延ばし、シャフト11を絶縁基板層10から突出して延ばすのが望ましい。各電極8の長さを例えば絶縁基板層10のほぼ全長に亘る長さ等とすれば、電極8の一部分を必要長だけ露出させることができる。

【0027】

図1に示した電源14及び15は高電圧バイアス電源であり、それぞれ固定式プリニップ接触子12又は固定式ポストニップ接触子13、例えば導電ブラシ等の固定電極を介し、電極8の露出部分に接触する。なお、図2等においては固定式プリニップ接触子12及び固定式ポストニップ接触子13は省略してある。電源14及び15は、例えば、プログラムされている制御ルーチンをコンピュータ等の装置にて実行することにより、制御される。電極8用の電源は図示の如く複数個としてもよいし、1個としてもよい。また、その電源(群)から電極8に供給するバイアスは、DCバイアスでもよいし、ACバイアスでもよいし、DCシフトACバイアスでもよいし、その組合せでもよい。電源(群)の動作モードは、定電圧モードでもよいし、定電流モードでもよいし、その組合せでもよい。

【0028】

本実施形態に係るBCR1を間隙付き(即ち非接触式)BCRとして構成する場合、図1、図5及び図6に示すように、ニップ内領域3において、荷電部材表面即ち半導体層9の表面とフォトレセプタ表面2との間に空隙4が発生する。先に数2に示した空気絶縁破壊しきい値電圧VTHは、この空隙4の大きさ(半導体層9の表面とフォトレセプタ表面2との間隔)dAIRが

(数5)

dAIR≦dTH=7.09(DOPC)1/2

という条件を満たしているときには、空隙dAIRに依存しない。例えば、DOPC=7.6μmであるときは空隙しきい値dTH=20μmになるため、dAIR≦20μmなら空気絶縁破壊しきい値電圧VTHは空隙dAIRに依存しない。逆に、空隙dAIRが空隙しきい値dTHを上回っていると、空気絶縁破壊しきい値電圧VTHが空隙dAIRに依存することとなる。そのため、図2に示したクロスプロセス方向に沿って空隙dAIRに不均等さがあると、それによってクロスプロセス方向に沿い荷電不均一性が発生することとなり得る。この現象は、特に、純粋なDCBCR(即ちAC電圧VAC=0のBCR)のうちVDC<0であるときVOPC=VDC+VTHになるものにおいて、生じ得る。従って、本発明を非接触式BCRとして構成する際、クロスプロセス方向荷電不均一性を抑えるには、dAIR≦dTHとするのが望ましい。しかし、本発明は、dAIR>dTHの非接触式BCRとして実施することもできる。その場合には、空気絶縁破壊しきい値電圧VTHが高めになるためDC電圧VDCを高めに設定して所要フォトレセプタ荷電電圧VOPCを得るようにするのが望ましく、また空隙dAIRがクロスプロセス方向に沿ってさほど変化しないよう空隙dAIRについての精度を注意深く制御してクロスプロセス方向荷電不均一性を抑えるのが望ましい。

【0029】

ここに、例えばVTH=600Vの純粋DCBCRにおいてフォトレセプタ(OPC)の荷電電圧乃至電位VOPCを−500Vにするには、従来であれば、VOPC=VDC+VTHの式よりVDC=−1100Vとする必要があった。しかしながら、そのように定めたDC電圧VDCをプリニップ領域にて使用すると、プリニップ絶縁破壊によりポストニップ絶縁破壊が抑制されてしまうため荷電均一性が低くなる。そこで、本発明に従い純粋DCBCRを実現する際には、電極群を1個ずつ又は複数個単位で領域別に分け、電極毎或いは電極グループ毎に一般に異なるDC電圧を印加する(但し同電圧が印加される電極又はそのグループがあってもよい)ことによって、荷電均一性を改善する。グループ分けの仕方には色々なものがあり得、例えば、多数の電極8のうちプリニップ領域6に属するもの、ニップ内領域3に属するもの及びポストニップ領域7に属するものをそれぞれひとまとめにして扱い(順にプリニップ領域内電極群、ニップ内領域内電極群及びポストニップ領域内電極群)、プリニップ領域6だけでなくポストニップ領域7でも空気絶縁破壊が生じるよう、それぞれに対して一般に異なるDC電圧VPRE-NIP、VNIP又はVPOST-NIPを印加するやり方がある。具体的には、図1に示すように2個の直流電源14及び15を用いて純粋DCBCRを構成するのであれば、電極8を、次の式

(数6)

|VPOST-NIP|>(|VPRE-NIP|=|VNIP|)>VTH

により定まる電圧VPRE-NIP、VNIP及びVPOST-NIPによりバイアスすればよい。例えば、VTH=600VでVOPC=−500Vを実現するには、VOPC=VDC+VTHの式に倣いVOPC=VPOST-NIP+VTHの式を用いてVPOST-NIP=−1100Vと決め、DC電圧VNIP及びVPRE-NIPをそれより低く且つ空気絶縁破壊しきい値電圧VTHより高い値例えばVPRE-NIP=VNIP=−850Vとすればよい。このようにすれば、プリニップ絶縁破壊だけでなくポストニップ絶縁破壊も発生し、ポストニップ絶縁破壊によって荷電均一性が顕著に改善される。実際、プリニップ絶縁破壊及びポストニップ絶縁破壊の協働によって荷電均一性が全体的に最適化される。更に、プリニップ絶縁破壊を発生させているため、荷電緩和時間がニップ内滞在時間と概略等しくなるようタイトな比抵抗調整乃至管理を行う必要がなくなり、従ってゴースト欠陥も生じにくくなる。言い換えれば、ニップ内領域3内に入り又はニップ内領域3外に出て行く電界を簡単に且つ精密に制御できるよう、埋め込んだ電極群に対しバイアスを印加しているため、画像欠陥を防止できる。無論、ACバイアスに起因する問題も生じ得ない。また、この構成においては、プロセス方向に並んでいる電極8と電極8との間に半導体層9が介在しているため半導体層9の比抵抗と電圧値の設定とによって電極8同士の間の電流を抑えることができ、また半導体エラストマ等の半導体層9の比抵抗が採り得る範囲も広くなっている。ここで、DOPC=7.6μmでありVTH=600Vである負荷電の例にてDCバイアスが負電圧であるときVOPC=VPOST-NIP+VTHという関係がフォトレセプタ荷電電圧VOPCとDC電圧VPOST-NIPとの間に成り立つことを図7に、またVTH=600Vの純粋DCBCR実施形態にて所要フォトレセプタ荷電電圧VOPCを得る際のDC電圧VPRE-NIP、VNIP及びVPOST-NIPの設定の仕方の例を図8〜図11に、それぞれ示す。これらのうち、図8及び図11に示した例はそれぞれ数6が成り立つよう3個の領域全てでバイアスを印加する例である。図8に示した例ではフォトレセプタ表面2への荷電のうち50%がプリニップ領域6にて、残りの50%がポストニップ領域7にて行われるようバイアス電圧等が設定されているのに対し、図10に示した例ではフォトレセプタ表面2への荷電のうち80%がプリニップ領域6にて、残りの20%がポストニップ領域7にて行われるようバイアス電圧等が設定されている。また、図9に示した例は

(数7)

|VPOST-NIP|>(|VPRE-NIP|=|VNIP|=VTH)

が成り立つよう、即ちフォトレセプタ表面2への荷電が全てポストニップ領域7にて行われるよう3個の領域全てで、バイアスを印加する例である。更に、図10に示した例は

(数8)

|VPOST-NIP|>VTH>(|VPRE-NIP|=|VNIP|)

が成り立つよう、即ちフォトレセプタ表面2への荷電が全てポストニップ領域7にて行われるようバイアスを印加する例、特にプリニップ領域内電極群及びニップ内領域内電極群は接地してポストニップ領域内電極群にのみバイアスを印加する例である(但しプリニップ領域内電極群及びニップ内領域内電極群にバイアスを印加しつつ数8を満足させることもできる)。これらの図から理解できるように、本発明によれば、様々な荷電態様を容易に且つ精密に実現できる。更に、DC電圧VPRE-NIP及びVNIPと電圧VPOST-NIPとの差が小さいため、図9に示した例の方が図10に示した例に比べて電極8同士の間の電流が小さくなる。

【0030】

また、図5及び図6においては、隣り合う電極8同士が半径方向に沿ってずれた位置にある。更に、図6においてはプロセス方向に沿い電極8同士が重複しているが(重複部分17)、図5においては重複部分17の幅が0である。

【0031】

半導体層9は、一方では、電極8同士の間の電流を制限できるよう十分な比抵抗を有していなければならず、他方では、BCR1の表面に発生し堆積した電荷を迅速且つ確実に緩和できるよう十分な導電性を有していなければならない。

【0032】

また、BCR1の全周及び全長のどこでも概ね均一なニップ内領域3を形成できるようにするには、十分な可撓性を有する可撓性エラストマにより半導体層9を形成するのが望ましい。半導体層9乃至これを構成する可撓性エラストマのショアO硬度は、例えば約0〜約100の範囲内であることが望ましく、約15〜約80の範囲内であれば更に望ましい。半導体層9として好適に使用できる可撓性エラストマとしては、例えば、ウレタンラバー(urethane rubber)、エピクロロヒドリンエラストマ(epichlorohydrin elastomer)、EPDM(エチレン−プロピエン−ジエン三元共重合体)ラバー(EPDM rubber)、スチレンブタジエンラバー(styrene butadiene rubber)、フルオロエラストマ(fluoro-elastomer)、シリコーンラバー(silicone rubber)等がある。また、エラストマの比抵抗を変化させ又は調整したいのであれば、素材中に各種のイオン種や導電性フィラをドーピングする等、様々な手法を採ることができる。そして、半導体層9の厚みは如何様にも設定できるが、例えば約0.02〜約10mm、より好ましくは約0.2〜約1mmの範囲内とする。無論、硬く形状的に適合させにくい層を半導体層9として形成することもできる。

【0033】

半導体層9の素材選択、特性調整、形成等に際しては、その緩和時間tRELAXが

(数9)

tRELAX<〜0.2×(WELECTRODE/VPROCESS)(但しWELECTRODEは埋め込まれている電極8(1個分)の幅、VPROCESSは電子写真プロセスにおけるプロセス速度)

の条件を満たすようにするのが望ましい。この条件を満たすためには、半導体層9として用いるエラストマの比抵抗ρは、理論的には、

(数10)

ρ<tRELAXDOPC/(dε0)(但しDOPCはフォトレセプタ誘電体厚、dはエラストマ厚、ε0は自由空間誘電率)

という条件を満たしていなければならない。また、プロセス速度VPROCESSは普通は約100mm/s(毎分約25ページ)から約250mm/s(毎分約60ページ)であるが、本発明はプロセス速度VPROCESSがこれより高い(例えば300mm/s超の)又は低いマシンにおいても実施することができる。プロセス速度VPROCESSの値域は、例えば約25〜約1250mm/sといったところであろう。また、電極幅WELECTRODEは、例えば約0.05〜約6mm、好ましくは約0.5〜約3mmの範囲内とする(ニップ内領域3の幅が約0〜6mmの場合)。

【0034】

更に、フォトレセプタ側に小規模欠陥があるときに、BCR1とフォトレセプタ接地面16との短絡即ちバイアスリークによって誘電体絶縁破壊が生じないようにするには、誘電体絶縁破壊電界EBREAK即ち誘電体絶縁破壊が発生する電界の値ができるだけ大きい素材及び態様を以て半導体層9を形成すると共に、半導体層9の厚みdを十分に厚くする必要がある。誘電体絶縁破壊電界EBREAKは1V/μmを超える電界とする必要があり、半導体層9として使用するエラストマが薄い場合は100V/μmを超える電界とすることが必要となることもあろう。例えば誘電体絶縁破壊電界EBREAKが5V/μmのエラストマにより半導体層9を形成した場合、電極8に印加される電圧のピーク値が1100Vに達し得る用途においては、誘電体絶縁破壊を防ぐのにd>0.2mmであることが必要である。他方、プリニップ領域6及びポストニップ領域7における電界制御を(好適に)実行可能にするには、半導体層9の厚みdを十分薄くしなければならない。以上の条件を考慮すると、半導体層9の比抵抗ρは例えば約104〜約1013Ω・cmの範囲内とするのが望ましいが、これより高い又は低い比抵抗ρを有する層を半導体層9として用いてもかまわない。

【0035】

各領域において印加する電圧は、その電子写真プロセスに対してどのような結果乃至成果が望まれているかに応じ、定めればよい。電圧VPRE-NIP、VNIP及びVPOST-NIPは、トナーの荷電が正か負かにもよるが、最も狭く見ても−10000〜+10000Vの範囲に属する値を採り得る。先により詳細に述べた通り、最終的に得られるフォトレセプタ荷電電圧VOPCはポストニップ領域7内で印加されているDC電圧VPOST-NIPに依存しており、負荷電であればVOPC=VPOST-NIP+VTHの式により、正荷電であればVOPC=VPOST-NIP−VTHの式により、その値が定まる。例えば、VTH=600Vである場合にフォトレセプタを+500Vまで正荷電するには、ポストニップ領域7内で印加するDCバイアス電圧VPOST-NIPを+1100Vに設定する必要がある。

【0036】

電源14及び15から取り出すことができる最大電流IMAXは、例えば約2〜約3mAの範囲に属する値とし、より好ましくは例えば約10若しくは20mA又はそれ以上とする。なお、電源14及び15から大電流が引き出されるのは、隣り合っている電極8同士でそのバイアス電位が著しく異なるときや、光導電体に恒久的に発生し接地に対して非常に低い抵抗値を示す小さなスポット即ちピンホール欠陥がフォトレセプタ(ドラム又はベルト)にて生じていてBCR1がフォトレセプタ接地面16と短絡しているときである。

【0037】

本発明を実施するに当たっては、例えばDOPC=7.6μm(即ちVTH=600V)とし、負荷電のためバイアス電圧VPRE-NIP及びVNIPを共に約−850Vとしバイアス電圧VPOST-NIPを約−1100Vとする(これによりフォトレセプタ荷電電圧VOPCは−500Vとなる;図8参照)。また、プロセス速度VPROCESSは例えば約100mm/sとする。荷電緩和時間tRELAXはこのプロセス速度VPROCESSと電極幅WELECTRODEから決まる。更に、最大電流IMAXは約1mA、誘電体絶縁破壊電界EBREAKは約5V/μmとする。そして、電極8同士の間隔は約0.5mm、半導体層9の厚みdは約0.3〜約0.5mmと設定する。このように厳しく設定した場合でも、半導体層9の比抵抗ρが採り得る範囲は、好ましくも、約3×106〜5×108Ω・cmという比較的広い範囲となる。比抵抗ρの値域がこのように比較的広いため、この範囲内の比抵抗ρを実現でき電荷を緩和できるエラストマは多く、これは本発明の実施に際して有利な事項である。なお、先に述べたように電荷を迅速に緩和できるよう半導体層9の導電性を十分にしておかねばならないため、半導体層9が採り得る比抵抗ρの最大値は緩和時間tRELAXにより概ね決まる。他方、電極8同士の間の電流を制限できるようにしておかねばならないため、半導体層9が採り得る比抵抗ρの最小値は、電源14及び15から流すことができる最大電流IMAXの値、即ち(1)バイアスリーク状況下で接地へと電流が流れた場合でも(2)加わっているバイアス電圧値が異なる電極8同士の間で電流が流れた場合でも超えてはならないとされている電流IMAXの値により、決定される。

【0038】

比抵抗ρが上掲の好ましい範囲内に属している場合、半導体層9上の電荷はプロセス速度VPROCESSに対する電極幅WELECTRODEの比WELECTRODE/VPROCESSに比して短い時間(緩和時間tRELAX)内で緩和する。このように緩和時間tRELAXが短いためニップ内領域3において電荷を接地面に逃がすことは概ね不要であるが、半導体層9の表面上に電荷が積もり積もって過剰になることを防ぐには、ニップ内領域3内で適当なバイアスを印加すること或いは接地することが望ましいとも言える。

【0039】

また、BCR1の汚れを最小限まで抑えるには、例えば、ブレードタイプ、パッドタイプ、ブラシタイプ等のクリーナを、BCR1に設けるとよい。もしクリーナを設けるのであれば、その位置は、プリニップ領域6やポストニップ領域7の外側とする。

【0040】

本発明の好適な実施形態に係る電極付きBCRは、これまでBCRが用いられてきたどのような電子写真システムにおいても、用いることができる。また、本発明の好適な実施形態に係る電極付きBCRによれば、システムにおけるバイアスの加え方及び値を必要乃至所望に応じて変化させることができる。例えば、図10に示した例ではプリニップ領域内電極群及びニップ内領域内電極群を全て接地しポストニップ領域内電極群に高電圧バイアスを印加しているが、図8、図9及び図11に示した例ではプリニップ領域内電極群及びニップ内領域内電極群にもバイアスを印加している。更に、本発明によれば、これに限られるものではないが、次に述べる例を含め幾つかの異なるやり方によって、埋め込んだ電極群に対しバイアスを加えることができる。

【0041】

まず、BCR1のプリニップ領域6、ニップ内領域3及びポストニップ領域7それぞれにて印加するバイアス電圧は、互いに異なるものとすることができ、また随時変えることができる。更に、BCR1のプリニップ領域6、ニップ内領域3及びポストニップ領域7それぞれの内部において、固定部分の構造等を工夫することによってバイアス電圧値を変える(分布させる)ことも可能である。電極8に対するバイアス印加は、電極8の1個毎に行ってもよいし、1個又は複数個の電極8を含む幾つかのグループ毎に行ってもよい。各電極8又はそのグループに対するバイアス電圧は異なる電圧とすることもできるし、幾つかの電極8又はそのグループについて互いに同じバイアス電圧とすることもできる。更に、広範囲に分布する電極群に対し、バイアスされている電極8間でそれらを覆う半導体層9の表面に沿った電極間電圧降下乃至電位差が生じるようバイアス電圧を印加し、それにより、バイアスされている電極8間の電位差が半導体層9の表面に沿って滑らかに変化していくように(電界分布が最適化されるように)、することもできる。グループ分けの仕方としては、例えば、プリニップ前領域内電極群、プリニップ領域内電極群、ニップ内領域内電極群、ポストニップ領域内電極群及びポストニップ後領域内電極群という分け方もある。無論、他のやり方でグループ分けを行ってもよい。ニップ内領域3から大きく離れている電極群については、BCR1の表面に蓄積される電荷が緩和されるようバイアスしてもよいし接地してもよい。印加するバイアスはDCバイアスでもよいし、ACバイアスでもよいし、DCシフトACバイアスでもよい(先にDCバイアスの例について説明を行ったがACバイアス乃至DCシフトACバイアスでも本発明は効果がある)。電源(群)の動作モードは定電圧モードでも定電流モードでもよい。

【0042】

本発明に係るBCRシステムの各構成部材の配置や素材に関しては、本発明の技術的範囲から逸脱することなく、様々に変えまた置換することができる。例えば、図1に示すように電極8同士が密接して配置されている場合、電源14及び15から流れ出す電流が大きくなり得るため、電源14及び15から引き出すことができる電流についての制限(最大電流IMAXによる制限)を緩くする必要がある。即ち、電極間隔ΔxELECTRODEと最大電流IMAXの間には

(数11)

IMAXΔxELECTRODE=k(但しkは定数)

という関係があり、電極間隔ΔxELECTRODEを縮めたらそれに反比例して最大電流IMAXを大きくしなければならない。なお、定数kは、半導体層9として使用するエラストマの厚みd、その最小所望比抵抗及びそのクロスプロセス方向長さと、隣り合っている電極8同士の間に発生し得る最大の電位差とにより、定まる。

【0043】

更に、電極間隔ΔxELECTRODEは例えば0.1mm未満とする。また、電極8の配置パターンは、荷電領域における高い均一性を保証できるよう様々に設定することができる。例えば、図4に示したように、BCR1の断面上で電極8の配置箇所を結ぶと2本の曲線となり、各曲線上における電極8の位置が互い違いになり、且つ一方の曲線に属する電極8と他方の曲線に属する電極8とが部分的に重なり合うよう(或いはそれに近い状態となるよう)、電極8を配置することができる。また、図6に示したようにプロセス方向に沿い電極8同士が重なり合うよう電極8を配置することもできるし、図5に示したようにプロセス方向における電極8同士の重複部分17の幅が0になるよう電極8を配置することもできる。図5に示したように配置すれば製造が比較的容易になる。また、図5の実施形態においても図6の実施形態においても、隣り合う電極8同士の半径方向間隔は、0.1〜1mmの範囲に属する値とするのが望ましいが、この範囲外の値とすることもできる。また、図5の実施形態においても図6の実施形態においても電極8は絶縁基板層10上に配置されているが、電極8は絶縁基板層10や半導体層9の内部に埋め込むこともできる。

【0044】

更に、半導体層9として使用するエラストマの厚みd及び比抵抗ρは最適化可能である。例えば、エラストマは半導体とするのが望ましいが、エラストマの導電性が十分良好であれば、ある電圧でバイアスされている電極8とその隣にあり同じ電圧でバイアスされている電極8とにより挟まれる領域における電位分布は均一分布に近い分布になる。

【図面の簡単な説明】

【0045】

【図1】本発明の一実施形態に係る電極付きBCR(バイアスド荷電ローラ)システムの軸断面図である。

【図2】本実施形態における電極付きBCRの頂面図である。

【図3】図2に示した電極付きBCRのIII−III断面図である。

【図4】本実施形態における電極付きBCRの部分拡大断面をフォトレセプタ表面の一部と共に示す図である。

【図5】本発明の他の実施形態における電極付きBCRの部分拡大断面をフォトレセプタ表面の一部と共に示す図である。

【図6】本発明の更に他の実施形態における電極付きBCRの部分拡大断面をフォトレセプタ表面の一部と共に示す図である。

【図7】ポストニップ領域におけるバイアス電圧とフォトレセプタ荷電電圧との関係を示す図である。

【図8】プリニップ領域及びポストニップ領域における荷電の仕方の例を示す図であ る。

【図9】プリニップ領域及びポストニップ領域における荷電の仕方の他の例を示す図である。

【図10】プリニップ領域及びポストニップ領域における荷電の仕方の更に他の例を示す図である。

【図11】プリニップ領域及びポストニップ領域における荷電の仕方の更なる例を示す図である。

【特許請求の範囲】

【請求項1】

絶縁基板と、

絶縁基板上の半導体層と、

少なくとも絶縁基板内、半導体層内、又は絶縁基板と半導体層の間に配置された複数の電極と、

を備える電荷保持面荷電用電極付きバイアスド荷電ローラ。

【請求項1】

絶縁基板と、

絶縁基板上の半導体層と、

少なくとも絶縁基板内、半導体層内、又は絶縁基板と半導体層の間に配置された複数の電極と、

を備える電荷保持面荷電用電極付きバイアスド荷電ローラ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2006−11455(P2006−11455A)

【公開日】平成18年1月12日(2006.1.12)

【国際特許分類】

【出願番号】特願2005−186327(P2005−186327)

【出願日】平成17年6月27日(2005.6.27)

【出願人】(596170170)ゼロックス コーポレイション (1,961)

【氏名又は名称原語表記】XEROX CORPORATION

【Fターム(参考)】

【公開日】平成18年1月12日(2006.1.12)

【国際特許分類】

【出願日】平成17年6月27日(2005.6.27)

【出願人】(596170170)ゼロックス コーポレイション (1,961)

【氏名又は名称原語表記】XEROX CORPORATION

【Fターム(参考)】

[ Back to top ]