ポストフィルタリングを利用した小数遅延フィルタに基づくビーム形成装置及び方法

【課題】 補間工程で小数遅延フィルタを用いることによりビーム形成の精度を向上させると共に、ポストフィルタリング技術を用いることでハードウェアの複雑化を低減するビーム形成装置を提供する。

【解決手段】 本発明のビーム形成装置は、各チャンネルについて小数部分が遅延したブロックデータを合算し、この合算データから小数部分の遅延値を得る、小数遅延フィルタを備えたポストフィルタリング手段を含む。このポストフィルタリング手段は、各チャンネル毎に同じ係数を付与されたブロックデータを集めて、同時にフィルタリング工程を実行する。

【解決手段】 本発明のビーム形成装置は、各チャンネルについて小数部分が遅延したブロックデータを合算し、この合算データから小数部分の遅延値を得る、小数遅延フィルタを備えたポストフィルタリング手段を含む。このポストフィルタリング手段は、各チャンネル毎に同じ係数を付与されたブロックデータを集めて、同時にフィルタリング工程を実行する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、超音波映像装置のためのビーム形成装置に関する。特に、従来の補間(interpolation)フィルタ又はIQ(In-phase and quadrature)位相回転器よりもハードウェアの複雑化を低減する必要があるポストフィルタリングを使用する小数遅延(Fractional Delay)フィルタを備えることにより、広い周波数スペクトルで遅延サンプルを適切に発生することができるビーム形成装置に関する。

【背景技術】

【0002】

従来の遅延-合算ビーム形成装置(delay-sum beamformer)は、(精密な遅延制御のために16f0を超えて)データ伝送率を効果的に増大するために4重の補間フィルタを用いている。このためには、位相誤差がなく振幅誤差が少ない遅延サンプルを生成する有限インパルス応答(Finite Impulse Response)フィルタが理想的である。しかしながら、補間フィルタは複数の乗算器を必要とする。一方、位相回転ビーム形成装置は、IQ復調のために2つのFIR低域フィルタ(FIR LPF)と、チャンネル毎にIQ信号の位相回転のために4つの実数乗算器とを必要とする。

【0003】

しかしながら、これらのビーム形成装置は、高画質の映像を形成するために開発されたものであるため、電力消費、製造コスト、サイズなどを考慮して設計しなければならない携帯型の超音波スキャナには適していない。

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明は、上記の課題を解決するためになされたもので、小数遅延フィルタを用いるポストフィルタリング技術を採用することによってハードウェアの複雑化を減少させる、超音波映像装置のためのビーム形成装置及びビーム形成方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明は、各チャンネルからサンプリングされたデータを保存するメモリと、該データの遅延値の整数部分に基づいてブロックデータを発生するための手段とを含む、超音波映像装置のための多チャンネルビーム形成装置であって、各チャンネルについて小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得る小数遅延フィルタを含むポストフィルタリング手段を備え、該ポストフィルタリング手段は、同じ係数を付されたチャンネルのブロックデータを結合して同時にフィルタリング工程を行うことを特徴とする。

【0006】

本発明の装置において、前記ポストフィルタリング手段は、各チャンネル別ブロックアドレスをn個出力するためにチャンネル別に設けられる複数の1対nデマルチプレクサと、各チャンネルのデマルチプレクサから出力されるすべての信号を加算し、各チャンネル別に設けられる複数のブロック加算器と、各ブロック加算器から出力されるn個の出力を各チャンネル別に小数遅延する複数の小数遅延フィルタと、各チャンネル別小数遅延フィルタの出力を合算する加算器とを含むことが好ましい。

【0007】

或いは、前記ポストフィルタリング手段は、各チャンネル別ブロックアドレスをn個出力するためにチャンネル別に設けられる複数の1対nデマルチプレクサと、各チャンネルのデマルチプレクサから出力されるすべての信号を加算するために各チャンネル別に設けられる複数のブロック加算器と、各ブロック加算器から出力されるn個の出力信号を所定の変数と乗算する複数のチャンネル別乗算器と、前記乗算器の出力を合算する加算器とを含むことが好ましい。

【0008】

本発明の装置は更に、前記デマルチプレクサから出力される信号を乗算して、対応するブロック加算器に対して出力する複数のマルチプレクサを備えることが好ましい。

【0009】

本発明の方法は、各チャンネルからサンプリングされたデータを保存するメモリと、該メモリに保存されたデータの遅延値の整数部分を使ってブロックデータを生成させる手段とを含む超音波映像処理装置用の多チャンネルビーム形成方法であって、小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得ることを含むポストフィルタリングを備え、該ポストフィルタリングは、同じ係数を付されたブロックデータを結合して同時にフィルタリングすることを特徴とする。

【0010】

本発明の方法において、前記ポストフィルタリングは、各チャンネルを異なるアドレスを持つn個の信号に多重化すること、前記多重化信号をアドレスにより結合すること、結合した信号について小数部分のフィルタリングを行うこと、及び小数フィルタリングした信号を合算することを含むことが好ましい。

【0011】

或いは、前記ポストフィルタリングは、各チャンネルを異なるアドレスを持つn個の信号に多重化すること、前記多重化信号をアドレスにより結合すること、前記結合した信号を各変数と乗算すること、及び前記乗算して得られた信号を合算することを含むことが好ましい。

【0012】

本発明の方法は更に、デマルチプレクシングにより出力された信号を多重化し、アドレスにより結合される信号を出力することを備えることが好ましい。

【発明を実施するための最良の形態】

【0013】

本発明のビーム形成装置は、個々のチャンネルに異なる遅延値を加えるために受信信号を量子化してこれを保存するためのメモリを備えている。このメモリから、ブロックデータを得るために遅延値の整数部分のみ読み出される。一方、ビーム形成の正確度を高めるためには、それぞれのチャンネルにより細密な遅延値を与えなければならず、このために遅延値の小数部分(小数値)を計算する、遅延値の小数部分を使ってこれに相応する受信値を得るために小数遅延フィルタを利用する。使われる小数遅延フィルタのタップ数は、ビーム形成装置が得ようとする性能によって可変することができ、得ようとする遅延値の正確度によってフィルタのセット数が決定される。小数遅延フィルタのセット(係数)は、遅延値の小数部によって決定されるが、本発明では、このとき、同じ係数を使うチャンネル同士で集めてあらかじめ加算した後、最後に一回のみフィルタリングを取る構造を提案し、これをポストフィルタリング(post-filtering)と名付けた。このようなポストフィルタリング技法は、ビーム形成装置のチャンネル数と関係なく一回のフィルタリングのみでビーム形成をできるようにすることで、ハードウェア複雑度を大きく減らしうる。

【0014】

本発明では、同一の小数遅延が与えられなければならないすべてのチャンネルはブロック合算によって集合され、この合算データは該当のFDフィルタ(すなわち、0,0.25,0.5,0.75サンプル遅延に対する4個のFDフィルタのうちの1つ)に供給される。したがって、4個の四タップFDフィルタの対称特性を用いる6個の乗算器でビーム形成装置を構成できる。

【0015】

実験結果によれば、本発明のFDビーム形成装置は、一層単純化されたハードウェア構成で、64タップフィルタを有する遅延合算ビーム形成装置とほぼ同一の映像品質を達成できる。

【0016】

フィルタ設計及び最適なハードウェア構造

本発明の実施形態のFDビーム形成装置は、補間フィルタでなくFDフィルタを用いる点を除いて、補間ビーム形成装置と同一の構造を有する。一般に、補間ビーム形成装置は4重補間フィルタを使うので、補間フィルタをFDフィルタに置き換えるために、FDフィルタはプログラム可能な小数遅延値Dを生成する必要がある。小数遅延値の理想的な応答は、次式1によって得られる。

【0017】

【数1】

【0018】

D= 0,0.25,0.5,0.75

本実施形態のビーム形成装置は、FDフィルタを用いて、2段階の最小二乗評価(LSE)法によりサイズとグループ遅延応答とを向上させている。まず、二乗誤差を最小化するFDフィルタ係数は、次式2によって計算される、式2では、限定された周波数スペクトルは、απからβπの範囲にある。この式によって計算された係数は、フィルタ応答特性を向上させるために使われる最適化プログラムのための初期パラメータとして使用される。

【0019】

【数2】

【0020】

例えば、5MHzの映像周波数に対するFDフィルタ係数は、D=0のとき(0,0,1,0)、D=0.25のとき(−0.0677,0.8320,0.2788,−0.0498)、D=0.5のとき(−0.0788,0.5742,0.5742,−0.0788)、D=0.75のとき(−0.0498,0.2788,0.8320,−0.0677)である。D=0.75のときのフィルタ係数は、D=0.25のときの値を時間的に逆順にしたものであり、D=0.5に対する係数は、対称的に並んでいる。他の映像周波数に対するフィルタ係数は、同一の対称特性を示す。

【0021】

位相回転器及び二個の補間フィルタに対するFDフィルタの性能を評価するために、基準信号xref(n)(各映像形成周波数160 MHzである場合に6dB帯域幅の60%を有するガウス信号をサンプリングして得る)に対してコンピュータシミュレーションを行った。各基準信号は、40MHzのサンプリング周波数に減じて、すべてのシミュレーション方法に対する入力データとして使用した。

【0022】

図1は、限定された周波数スペクトルにおいて種々のビーム形成技術の信号対雑音比(SNR)を示すグラフである。SNRは、次式3で定義される。式3において、xd(n) は、各方式の4重補間の結果を表わす。小型携帯型スキャナ用ビーム形成装置を設計するために、8ビットの符号含み整数形式(8-bit signed integer format)が基準信号を表わすために使用され、すべてのフィルタ係数は、固定点演算のための符号含み12ビット数(signed 12-bit numbers)に量子化される。

【0023】

【数3】

【0024】

LSEによるFDフィルタは、位相回転器(△)及び16タップ補間フィルタ(・)に比べて、大部分の映像形成周波数(2、3.5、5、7.5、10 MHz)で高いSNRを与える。また、LSEに基づくFDフィルタは、7.5及び10 MHzの周波数では、64タップ補間フィルタに比べて、それぞれ2.75dB及び10.93dBほどSNRが低い。既存の映像形成周波数帯域で動作する商用製品には位相回転器が成功裏に使われているので、4タップFDフィルタは、少なくとも10MHzまでは効率的な映像形成手段になりうる。

【0025】

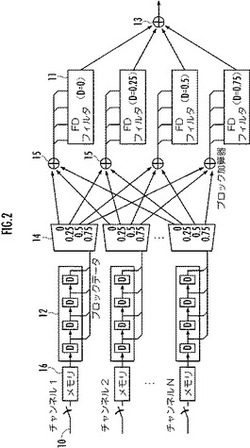

図2は、本発明の実施形態によるビーム形成装置の構成を示すブロック図である。この実施形態では、ビーム形成装置は、ポストフィルタリング技術を採用することによってハードウェアの複雑化を減少させている。図2において、すべてのチャンネル10を通って入力された同じ遅延のブロックデータ12は、ブロック加算器15によって合算される。各ブロックデータ12は、(FDフィルタにより遅延されたサンプルとして出力される)4個の連続的なデータサンプルからなる。

【0026】

図2は、タップ数が4で補間比が4のFDフィルタ11を用いたビーム形成装置の構成を示している。各チャンネル上でサンプリングされたデータはメモリ16に格納され、各チャンネルに付与される遅延値の整数部分に基づいて、ブロックデータ12として更新されるかどうかが決定される。遅延値の同じ小数部分が付与されたチャンネル上のブロックデータ12は合算され、同時にフィルタを通って互いに結合されてビームを形成することになる。FDフィルタのタップ数が4、ブロックデータ12の数が4、そして補間比が4であるので、遅延値は、小数部分が0,0.25,0.5,0.75のように表わされる。

【0027】

このビーム形成装置は、各チャンネル毎に1対4デマルチプレクサ14を含むことによって、4個のブロックアドレス(それぞれ4個の別アドレスを含む)中の一つにブロックデータ12を印加する。そして、各ブロック加算器15から出力される4個の出力サンプルは、対応するFDフィルタ11に印加される。最後に、4個のFDフィルタ11の出力を加算器13で結合するようにしたので、各FDフィルタ11は、各チャンネルごとに独立してFDフィルタを配置している場合と同様の出力を生成することができる。すなわち、本発明のFDビーム形成装置は、4個のFDフィルタを備えていればよい。

【0028】

本発明のビーム形成装置は、FDフィルタの特性を活用することで、ハードウェア構造をさらに単純化して設計することができる。これは、ビーム形成装置を次のように構成することで達成される。まず、遅延なし(D=0)の入力サンプルはバイパスして通過させる。D=0.25及び0.75に対しては、0.75のフィルタ係数は0.25のフィルタ係数を時間的に逆にすることで得られるから、4個の乗算器で4タップFDフィルタを具現できる。更に、D=0.5のときの入力サンプリングは、係数値が対称であるから、2個の乗算器のみで処理できる。

【0029】

図3は、本発明の別の実施形態によるビーム形成装置の構成を示すブロック図である。図3において、チャンネルブロック29は、本発明のポストフィルタリング構造において1つのチャンネルに対するハードウェアを表わしている。チャンネルブロックは、ビーム形成装置のチャンネル数に応じて反復的に使用される。各ブロックは、データパス30を通じて直列加算されて、FDフィルタ23に入力される。例えば、D=0.25と0.75は順序が反対で、同じ係数を使うので、図3のチャンネルブロック29の構造では一つのフィルタのみ必要である。D=0.5のフィルタ係数は、時間的に対称に配列されるので、チャンネルブロック29の構造では2個の乗算器のみ用いられる。D=0の場合は、係数に拘らずサンプルの加算のみ必要である。

【0030】

図3のビーム形成装置は、図2のFDビーム形成装置の各チャンネルのFDフィルタを1対4デマルチプレクサ21に置き換えると共に6個の乗算器23を用いて構成されている。乗算器23の被乗数であるFDフィルタ係数は、超音波の中心周波数及び帯域幅の変更に従って修正されなければならない。このため、乗算器23で用いられる被乗数を保存するためにレジスタが必要である。このレジスタの値は、超音波の中心周波数が変わるときだけ、更新される。

【0031】

メモリ24は、整数部分の遅延値を与えるための遅延メモリであり、遅延計算器25は、目標により異なって適用される超音波の遅延値を計算する。遅延計算器25の小数部分の解像度は、遅延値の精度に応じて決定される。図3の例では、解像度を4倍に増加させるので、小数部分は2ビットになる。すなわち、遅延計算器25は、概略的な遅延制御用に整数部分を与え、細密な遅延制御用に内部サンプル遅延を規定する2ビットの小数部分を与える。

【0032】

図3において、メモリ24から出力される入力サンプル信号は、従来のビーム形成装置と同様に概略的な遅延値を用いて、動的フォーカシング用レジスタ27内でシフトされる。精密な遅延値は、2つの小数遅延ビットを各チャンネルのデマルチプレクサ21の選択ラインに連結することにより、動的に制御されうる。動的フォーカシング用レジスタ27は、本発明のポストフィルタリングのために使用されるブロックデータを保存するためのレジスタである。このレジスタの数は、FDフィルタのタップ数によって決定される。この実施形態では、図3に示すように4−タップFDフィルタで4個のレジスタが使われる。レジスタのイネーブル信号は、遅延計算器25で計算された遅延値によって決定される。より詳細には、遅延値の整数部分が変わるときのみ、レジスタが可能化されて、その値が変わる。デマルチプレクサ21とマルチプレクサ28は協働して、遅延計算器25で計算された遅延値の小数部分に従って、各レジスタ内に保存された値を加算器31に送るように動作する。

【0033】

シミュレーション結果

本発明の効果を検証するために、従来の64チャンネル超音波スキャナの各チャンネルでのアナログ/デジタル変換器(ADC)の出力端からサンプルRFデータを測定した。商用ファントム(ATS tissue phantom、Model 539 )を、128個の線形配列素子(中心周波数6.2MHz、伝達焦点設定3cm)によってスキャンした。図4(a)は、本実施形態のビーム形成装置を用いて得られたファントムのワイヤ標的(wire target)を示し、図4(b)は、64タップフィルタを用いて得られたファントムのワイヤ標的を示している。図4(a)及び(b)に示されるように、これら二つの映像は近似している。

【0034】

図4の(c)(d)では、ファントムの他の範囲でも同一の結果を得ることができた。表1に、画像の左側のホール(黒点)40の周辺で測定されたCNR値を示す。一方、ホール40の周辺よりも明るく面積の大きいターゲット領域(cyst area)41でのCNR値は、(c)ビーム形成装置の場合7.90dB、(d)補間ビーム形成装置の場合7.98dBであった。このシミュレーション結果は、4タップFDフィルタと64タップ補間フィルタとの間のSNR比較結果に適合している。

【0035】

[表1]

深 さ FDビーム形成装置 補間ビーム形成装置

2cm 7.7 dB 7.73dB

3cm 10.47dB 10.46dB

4cm 9.50dB 9.48dB

5cm 3.63dB 3.22dB

ハードウェアの複雑さを比較するために、本発明の4タップFDビーム形成装置と、16タップ及び64タップフィルタを使う二個の補間ビーム形成装置とを、VHDLによって設計した。メモリを除いたVHDL設計のビーム形成装置の複雑度を、Xilinxフィールド・プログラマブル・ゲート・アレイ(FPGA)でのゲート数として測定した。各設計案の最大クロック周波数は、55MHzであった。入力サンプルとFDフィルタ係数は、8ビット及び12ビットの固定点の数にそれぞれ量子化された。一方、補間フィルタには、3回以下のシフト及び加算演算によって最適化された係数を適用した。3つのビーム形成装置を同じ遅延算出器で設計した。

【0036】

64タップ補間フィルタを用いる64チャンネルビーム形成装置には、64×25,933個の補間用ゲート、11,089個の内部チャンネル合算用ゲート、83,100個の遅延計算器用ゲートを必要として、計1,753,901個のゲートが追加された。同様に、16タップ補間フィルタを使う64チャンネルビーム形成装置は、527,789個のゲートを使っている。一方、本発明のビーム形成装置は、デマルチプレクサ及び各チャンネル別関連制御ロジック用ゲート1,028個、内部チャンネル合算用ゲート68,515個、6個の乗算器及びその後端の加算器用ゲート26,133個を使っている。したがって、本発明のFDビーム形成装置を構成するためには、243,540個のゲートが必要である。この結果から、本発明のハードウェア複雑度は、従来の64タップ補間ビーム形成装置の14%、16タップ補間ビーム形成装置の46%に過ぎない。

【0037】

以上、本発明の実施形態について説明したが、本発明はその技術思想の範囲内で適宜改変可能である。

【0038】

上述のように、本発明のビーム形成装置は、ビーム形成装置のチャンネル数に拘らず、ビーム形成のために一のフィルタリング工程しか必要としない小数遅延フィルタを使用するポストフィルタリング技術で実現される。

【0039】

上記のとおり、本発明のビーム形成装置は、ビーム形成装置のチャンネル数に拘らず、一つのフィルタリング工程でビーム形成ができるという効果を奏する。本発明のビーム形成装置は、FDフィルタを使用するポストフィルタリング技術で実現されるので、ハードウェアの複雑化を著しく減らす。シミュレーション結果によれば、FDフィルタに基づくビーム形成装置は、ハードウェアの複雑化を最小限に抑えながら、64タップフィルタを使用する遅延合算ビーム形成装置で得られる品質とほぼ同一の高品質映像を得ることができる。

【図面の簡単な説明】

【0040】

【図1】限定された周波数スペクトルで、異なるビーム形成技術の信号対ノイズ比(SNR)を示すグラフである。

【図2】本発明の実施形態によるビーム形成装置の構成を示すブロック図である。

【図3】本発明のもう1つの実施形態によるビーム形成装置の構成を示すブロック図である。

【図4】(a)〜(d)は、本発明のビーム形成装置と従来のビーム形成装置の性能比較のシミュレーション結果を示すグラフである。

【符号の説明】

【0041】

10…チャンネル、11…FDフィルタ、12…ブロックデータ、13…加算器、14…デマルチプレクサ、15…ブロック加算器、16…メモリ、21…デマルチプレクサ、23…乗算器、24…メモリ、25…遅延計算器、27…動的フォーカシング用レジスタ、28…デマルチプレクサ、29…チャンネルブロック、30…データパス、31…加算器。

【技術分野】

【0001】

本発明は、超音波映像装置のためのビーム形成装置に関する。特に、従来の補間(interpolation)フィルタ又はIQ(In-phase and quadrature)位相回転器よりもハードウェアの複雑化を低減する必要があるポストフィルタリングを使用する小数遅延(Fractional Delay)フィルタを備えることにより、広い周波数スペクトルで遅延サンプルを適切に発生することができるビーム形成装置に関する。

【背景技術】

【0002】

従来の遅延-合算ビーム形成装置(delay-sum beamformer)は、(精密な遅延制御のために16f0を超えて)データ伝送率を効果的に増大するために4重の補間フィルタを用いている。このためには、位相誤差がなく振幅誤差が少ない遅延サンプルを生成する有限インパルス応答(Finite Impulse Response)フィルタが理想的である。しかしながら、補間フィルタは複数の乗算器を必要とする。一方、位相回転ビーム形成装置は、IQ復調のために2つのFIR低域フィルタ(FIR LPF)と、チャンネル毎にIQ信号の位相回転のために4つの実数乗算器とを必要とする。

【0003】

しかしながら、これらのビーム形成装置は、高画質の映像を形成するために開発されたものであるため、電力消費、製造コスト、サイズなどを考慮して設計しなければならない携帯型の超音波スキャナには適していない。

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明は、上記の課題を解決するためになされたもので、小数遅延フィルタを用いるポストフィルタリング技術を採用することによってハードウェアの複雑化を減少させる、超音波映像装置のためのビーム形成装置及びビーム形成方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明は、各チャンネルからサンプリングされたデータを保存するメモリと、該データの遅延値の整数部分に基づいてブロックデータを発生するための手段とを含む、超音波映像装置のための多チャンネルビーム形成装置であって、各チャンネルについて小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得る小数遅延フィルタを含むポストフィルタリング手段を備え、該ポストフィルタリング手段は、同じ係数を付されたチャンネルのブロックデータを結合して同時にフィルタリング工程を行うことを特徴とする。

【0006】

本発明の装置において、前記ポストフィルタリング手段は、各チャンネル別ブロックアドレスをn個出力するためにチャンネル別に設けられる複数の1対nデマルチプレクサと、各チャンネルのデマルチプレクサから出力されるすべての信号を加算し、各チャンネル別に設けられる複数のブロック加算器と、各ブロック加算器から出力されるn個の出力を各チャンネル別に小数遅延する複数の小数遅延フィルタと、各チャンネル別小数遅延フィルタの出力を合算する加算器とを含むことが好ましい。

【0007】

或いは、前記ポストフィルタリング手段は、各チャンネル別ブロックアドレスをn個出力するためにチャンネル別に設けられる複数の1対nデマルチプレクサと、各チャンネルのデマルチプレクサから出力されるすべての信号を加算するために各チャンネル別に設けられる複数のブロック加算器と、各ブロック加算器から出力されるn個の出力信号を所定の変数と乗算する複数のチャンネル別乗算器と、前記乗算器の出力を合算する加算器とを含むことが好ましい。

【0008】

本発明の装置は更に、前記デマルチプレクサから出力される信号を乗算して、対応するブロック加算器に対して出力する複数のマルチプレクサを備えることが好ましい。

【0009】

本発明の方法は、各チャンネルからサンプリングされたデータを保存するメモリと、該メモリに保存されたデータの遅延値の整数部分を使ってブロックデータを生成させる手段とを含む超音波映像処理装置用の多チャンネルビーム形成方法であって、小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得ることを含むポストフィルタリングを備え、該ポストフィルタリングは、同じ係数を付されたブロックデータを結合して同時にフィルタリングすることを特徴とする。

【0010】

本発明の方法において、前記ポストフィルタリングは、各チャンネルを異なるアドレスを持つn個の信号に多重化すること、前記多重化信号をアドレスにより結合すること、結合した信号について小数部分のフィルタリングを行うこと、及び小数フィルタリングした信号を合算することを含むことが好ましい。

【0011】

或いは、前記ポストフィルタリングは、各チャンネルを異なるアドレスを持つn個の信号に多重化すること、前記多重化信号をアドレスにより結合すること、前記結合した信号を各変数と乗算すること、及び前記乗算して得られた信号を合算することを含むことが好ましい。

【0012】

本発明の方法は更に、デマルチプレクシングにより出力された信号を多重化し、アドレスにより結合される信号を出力することを備えることが好ましい。

【発明を実施するための最良の形態】

【0013】

本発明のビーム形成装置は、個々のチャンネルに異なる遅延値を加えるために受信信号を量子化してこれを保存するためのメモリを備えている。このメモリから、ブロックデータを得るために遅延値の整数部分のみ読み出される。一方、ビーム形成の正確度を高めるためには、それぞれのチャンネルにより細密な遅延値を与えなければならず、このために遅延値の小数部分(小数値)を計算する、遅延値の小数部分を使ってこれに相応する受信値を得るために小数遅延フィルタを利用する。使われる小数遅延フィルタのタップ数は、ビーム形成装置が得ようとする性能によって可変することができ、得ようとする遅延値の正確度によってフィルタのセット数が決定される。小数遅延フィルタのセット(係数)は、遅延値の小数部によって決定されるが、本発明では、このとき、同じ係数を使うチャンネル同士で集めてあらかじめ加算した後、最後に一回のみフィルタリングを取る構造を提案し、これをポストフィルタリング(post-filtering)と名付けた。このようなポストフィルタリング技法は、ビーム形成装置のチャンネル数と関係なく一回のフィルタリングのみでビーム形成をできるようにすることで、ハードウェア複雑度を大きく減らしうる。

【0014】

本発明では、同一の小数遅延が与えられなければならないすべてのチャンネルはブロック合算によって集合され、この合算データは該当のFDフィルタ(すなわち、0,0.25,0.5,0.75サンプル遅延に対する4個のFDフィルタのうちの1つ)に供給される。したがって、4個の四タップFDフィルタの対称特性を用いる6個の乗算器でビーム形成装置を構成できる。

【0015】

実験結果によれば、本発明のFDビーム形成装置は、一層単純化されたハードウェア構成で、64タップフィルタを有する遅延合算ビーム形成装置とほぼ同一の映像品質を達成できる。

【0016】

フィルタ設計及び最適なハードウェア構造

本発明の実施形態のFDビーム形成装置は、補間フィルタでなくFDフィルタを用いる点を除いて、補間ビーム形成装置と同一の構造を有する。一般に、補間ビーム形成装置は4重補間フィルタを使うので、補間フィルタをFDフィルタに置き換えるために、FDフィルタはプログラム可能な小数遅延値Dを生成する必要がある。小数遅延値の理想的な応答は、次式1によって得られる。

【0017】

【数1】

【0018】

D= 0,0.25,0.5,0.75

本実施形態のビーム形成装置は、FDフィルタを用いて、2段階の最小二乗評価(LSE)法によりサイズとグループ遅延応答とを向上させている。まず、二乗誤差を最小化するFDフィルタ係数は、次式2によって計算される、式2では、限定された周波数スペクトルは、απからβπの範囲にある。この式によって計算された係数は、フィルタ応答特性を向上させるために使われる最適化プログラムのための初期パラメータとして使用される。

【0019】

【数2】

【0020】

例えば、5MHzの映像周波数に対するFDフィルタ係数は、D=0のとき(0,0,1,0)、D=0.25のとき(−0.0677,0.8320,0.2788,−0.0498)、D=0.5のとき(−0.0788,0.5742,0.5742,−0.0788)、D=0.75のとき(−0.0498,0.2788,0.8320,−0.0677)である。D=0.75のときのフィルタ係数は、D=0.25のときの値を時間的に逆順にしたものであり、D=0.5に対する係数は、対称的に並んでいる。他の映像周波数に対するフィルタ係数は、同一の対称特性を示す。

【0021】

位相回転器及び二個の補間フィルタに対するFDフィルタの性能を評価するために、基準信号xref(n)(各映像形成周波数160 MHzである場合に6dB帯域幅の60%を有するガウス信号をサンプリングして得る)に対してコンピュータシミュレーションを行った。各基準信号は、40MHzのサンプリング周波数に減じて、すべてのシミュレーション方法に対する入力データとして使用した。

【0022】

図1は、限定された周波数スペクトルにおいて種々のビーム形成技術の信号対雑音比(SNR)を示すグラフである。SNRは、次式3で定義される。式3において、xd(n) は、各方式の4重補間の結果を表わす。小型携帯型スキャナ用ビーム形成装置を設計するために、8ビットの符号含み整数形式(8-bit signed integer format)が基準信号を表わすために使用され、すべてのフィルタ係数は、固定点演算のための符号含み12ビット数(signed 12-bit numbers)に量子化される。

【0023】

【数3】

【0024】

LSEによるFDフィルタは、位相回転器(△)及び16タップ補間フィルタ(・)に比べて、大部分の映像形成周波数(2、3.5、5、7.5、10 MHz)で高いSNRを与える。また、LSEに基づくFDフィルタは、7.5及び10 MHzの周波数では、64タップ補間フィルタに比べて、それぞれ2.75dB及び10.93dBほどSNRが低い。既存の映像形成周波数帯域で動作する商用製品には位相回転器が成功裏に使われているので、4タップFDフィルタは、少なくとも10MHzまでは効率的な映像形成手段になりうる。

【0025】

図2は、本発明の実施形態によるビーム形成装置の構成を示すブロック図である。この実施形態では、ビーム形成装置は、ポストフィルタリング技術を採用することによってハードウェアの複雑化を減少させている。図2において、すべてのチャンネル10を通って入力された同じ遅延のブロックデータ12は、ブロック加算器15によって合算される。各ブロックデータ12は、(FDフィルタにより遅延されたサンプルとして出力される)4個の連続的なデータサンプルからなる。

【0026】

図2は、タップ数が4で補間比が4のFDフィルタ11を用いたビーム形成装置の構成を示している。各チャンネル上でサンプリングされたデータはメモリ16に格納され、各チャンネルに付与される遅延値の整数部分に基づいて、ブロックデータ12として更新されるかどうかが決定される。遅延値の同じ小数部分が付与されたチャンネル上のブロックデータ12は合算され、同時にフィルタを通って互いに結合されてビームを形成することになる。FDフィルタのタップ数が4、ブロックデータ12の数が4、そして補間比が4であるので、遅延値は、小数部分が0,0.25,0.5,0.75のように表わされる。

【0027】

このビーム形成装置は、各チャンネル毎に1対4デマルチプレクサ14を含むことによって、4個のブロックアドレス(それぞれ4個の別アドレスを含む)中の一つにブロックデータ12を印加する。そして、各ブロック加算器15から出力される4個の出力サンプルは、対応するFDフィルタ11に印加される。最後に、4個のFDフィルタ11の出力を加算器13で結合するようにしたので、各FDフィルタ11は、各チャンネルごとに独立してFDフィルタを配置している場合と同様の出力を生成することができる。すなわち、本発明のFDビーム形成装置は、4個のFDフィルタを備えていればよい。

【0028】

本発明のビーム形成装置は、FDフィルタの特性を活用することで、ハードウェア構造をさらに単純化して設計することができる。これは、ビーム形成装置を次のように構成することで達成される。まず、遅延なし(D=0)の入力サンプルはバイパスして通過させる。D=0.25及び0.75に対しては、0.75のフィルタ係数は0.25のフィルタ係数を時間的に逆にすることで得られるから、4個の乗算器で4タップFDフィルタを具現できる。更に、D=0.5のときの入力サンプリングは、係数値が対称であるから、2個の乗算器のみで処理できる。

【0029】

図3は、本発明の別の実施形態によるビーム形成装置の構成を示すブロック図である。図3において、チャンネルブロック29は、本発明のポストフィルタリング構造において1つのチャンネルに対するハードウェアを表わしている。チャンネルブロックは、ビーム形成装置のチャンネル数に応じて反復的に使用される。各ブロックは、データパス30を通じて直列加算されて、FDフィルタ23に入力される。例えば、D=0.25と0.75は順序が反対で、同じ係数を使うので、図3のチャンネルブロック29の構造では一つのフィルタのみ必要である。D=0.5のフィルタ係数は、時間的に対称に配列されるので、チャンネルブロック29の構造では2個の乗算器のみ用いられる。D=0の場合は、係数に拘らずサンプルの加算のみ必要である。

【0030】

図3のビーム形成装置は、図2のFDビーム形成装置の各チャンネルのFDフィルタを1対4デマルチプレクサ21に置き換えると共に6個の乗算器23を用いて構成されている。乗算器23の被乗数であるFDフィルタ係数は、超音波の中心周波数及び帯域幅の変更に従って修正されなければならない。このため、乗算器23で用いられる被乗数を保存するためにレジスタが必要である。このレジスタの値は、超音波の中心周波数が変わるときだけ、更新される。

【0031】

メモリ24は、整数部分の遅延値を与えるための遅延メモリであり、遅延計算器25は、目標により異なって適用される超音波の遅延値を計算する。遅延計算器25の小数部分の解像度は、遅延値の精度に応じて決定される。図3の例では、解像度を4倍に増加させるので、小数部分は2ビットになる。すなわち、遅延計算器25は、概略的な遅延制御用に整数部分を与え、細密な遅延制御用に内部サンプル遅延を規定する2ビットの小数部分を与える。

【0032】

図3において、メモリ24から出力される入力サンプル信号は、従来のビーム形成装置と同様に概略的な遅延値を用いて、動的フォーカシング用レジスタ27内でシフトされる。精密な遅延値は、2つの小数遅延ビットを各チャンネルのデマルチプレクサ21の選択ラインに連結することにより、動的に制御されうる。動的フォーカシング用レジスタ27は、本発明のポストフィルタリングのために使用されるブロックデータを保存するためのレジスタである。このレジスタの数は、FDフィルタのタップ数によって決定される。この実施形態では、図3に示すように4−タップFDフィルタで4個のレジスタが使われる。レジスタのイネーブル信号は、遅延計算器25で計算された遅延値によって決定される。より詳細には、遅延値の整数部分が変わるときのみ、レジスタが可能化されて、その値が変わる。デマルチプレクサ21とマルチプレクサ28は協働して、遅延計算器25で計算された遅延値の小数部分に従って、各レジスタ内に保存された値を加算器31に送るように動作する。

【0033】

シミュレーション結果

本発明の効果を検証するために、従来の64チャンネル超音波スキャナの各チャンネルでのアナログ/デジタル変換器(ADC)の出力端からサンプルRFデータを測定した。商用ファントム(ATS tissue phantom、Model 539 )を、128個の線形配列素子(中心周波数6.2MHz、伝達焦点設定3cm)によってスキャンした。図4(a)は、本実施形態のビーム形成装置を用いて得られたファントムのワイヤ標的(wire target)を示し、図4(b)は、64タップフィルタを用いて得られたファントムのワイヤ標的を示している。図4(a)及び(b)に示されるように、これら二つの映像は近似している。

【0034】

図4の(c)(d)では、ファントムの他の範囲でも同一の結果を得ることができた。表1に、画像の左側のホール(黒点)40の周辺で測定されたCNR値を示す。一方、ホール40の周辺よりも明るく面積の大きいターゲット領域(cyst area)41でのCNR値は、(c)ビーム形成装置の場合7.90dB、(d)補間ビーム形成装置の場合7.98dBであった。このシミュレーション結果は、4タップFDフィルタと64タップ補間フィルタとの間のSNR比較結果に適合している。

【0035】

[表1]

深 さ FDビーム形成装置 補間ビーム形成装置

2cm 7.7 dB 7.73dB

3cm 10.47dB 10.46dB

4cm 9.50dB 9.48dB

5cm 3.63dB 3.22dB

ハードウェアの複雑さを比較するために、本発明の4タップFDビーム形成装置と、16タップ及び64タップフィルタを使う二個の補間ビーム形成装置とを、VHDLによって設計した。メモリを除いたVHDL設計のビーム形成装置の複雑度を、Xilinxフィールド・プログラマブル・ゲート・アレイ(FPGA)でのゲート数として測定した。各設計案の最大クロック周波数は、55MHzであった。入力サンプルとFDフィルタ係数は、8ビット及び12ビットの固定点の数にそれぞれ量子化された。一方、補間フィルタには、3回以下のシフト及び加算演算によって最適化された係数を適用した。3つのビーム形成装置を同じ遅延算出器で設計した。

【0036】

64タップ補間フィルタを用いる64チャンネルビーム形成装置には、64×25,933個の補間用ゲート、11,089個の内部チャンネル合算用ゲート、83,100個の遅延計算器用ゲートを必要として、計1,753,901個のゲートが追加された。同様に、16タップ補間フィルタを使う64チャンネルビーム形成装置は、527,789個のゲートを使っている。一方、本発明のビーム形成装置は、デマルチプレクサ及び各チャンネル別関連制御ロジック用ゲート1,028個、内部チャンネル合算用ゲート68,515個、6個の乗算器及びその後端の加算器用ゲート26,133個を使っている。したがって、本発明のFDビーム形成装置を構成するためには、243,540個のゲートが必要である。この結果から、本発明のハードウェア複雑度は、従来の64タップ補間ビーム形成装置の14%、16タップ補間ビーム形成装置の46%に過ぎない。

【0037】

以上、本発明の実施形態について説明したが、本発明はその技術思想の範囲内で適宜改変可能である。

【0038】

上述のように、本発明のビーム形成装置は、ビーム形成装置のチャンネル数に拘らず、ビーム形成のために一のフィルタリング工程しか必要としない小数遅延フィルタを使用するポストフィルタリング技術で実現される。

【0039】

上記のとおり、本発明のビーム形成装置は、ビーム形成装置のチャンネル数に拘らず、一つのフィルタリング工程でビーム形成ができるという効果を奏する。本発明のビーム形成装置は、FDフィルタを使用するポストフィルタリング技術で実現されるので、ハードウェアの複雑化を著しく減らす。シミュレーション結果によれば、FDフィルタに基づくビーム形成装置は、ハードウェアの複雑化を最小限に抑えながら、64タップフィルタを使用する遅延合算ビーム形成装置で得られる品質とほぼ同一の高品質映像を得ることができる。

【図面の簡単な説明】

【0040】

【図1】限定された周波数スペクトルで、異なるビーム形成技術の信号対ノイズ比(SNR)を示すグラフである。

【図2】本発明の実施形態によるビーム形成装置の構成を示すブロック図である。

【図3】本発明のもう1つの実施形態によるビーム形成装置の構成を示すブロック図である。

【図4】(a)〜(d)は、本発明のビーム形成装置と従来のビーム形成装置の性能比較のシミュレーション結果を示すグラフである。

【符号の説明】

【0041】

10…チャンネル、11…FDフィルタ、12…ブロックデータ、13…加算器、14…デマルチプレクサ、15…ブロック加算器、16…メモリ、21…デマルチプレクサ、23…乗算器、24…メモリ、25…遅延計算器、27…動的フォーカシング用レジスタ、28…デマルチプレクサ、29…チャンネルブロック、30…データパス、31…加算器。

【特許請求の範囲】

【請求項1】

各チャンネルからサンプリングされたデータを保存するためのメモリと、該データの遅延値の整数部分に基づいてブロックデータを発生するための手段とを含む、超音波映像装置のための多チャンネルビーム形成装置において、

各チャンネルについて小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得る小数遅延フィルタを含むポストフィルタリング手段を備え、該ポストフィルタリング手段は、同じ係数を付されたチャンネルのブロックデータを結合して同時にフィルタリング工程を行うことを特徴とする多チャンネルビーム形成装置。

【請求項2】

請求項1記載の多チャンネルビーム形成装置において、

前記ポストフィルタリング手段は、

各チャンネル別ブロックアドレスをn個出力するためにチャンネル毎に設けられた複数の1対nデマルチプレクサと、

前記デマルチプレクサから出力される全ての信号を加算するためにチャンネル毎に設けられた複数のブロック加算器と、

各ブロック加算器から出力されるn個の信号を小数遅延するための複数の小数遅延フィルタと、

各小数遅延フィルタの出力信号を合算する加算器と

を含むことを特徴とする多チャンネルビーム形成装置。

【請求項3】

請求項1記載の多チャンネルビーム形成装置において、

前記ポストフィルタリング手段は、

各チャンネル別ブロックアドレスをn個出力するためにチャンネル毎に設けられた複数の1対nデマルチプレクサと、

前記デマルチプレクサから出力される信号を結合するための複数のブロック加算器と、

各ブロック加算器から出力されるn個の信号を所定の変数と乗算する複数の乗算器と、

前記乗算器から出力される信号を合算する合算器と

を備えることを特徴とする多チャンネルビーム形成装置。

【請求項4】

請求項3記載の多チャンネルビーム形成装置において、更に、

前記デマルチプレクサから出力される信号を乗算して、対応するブロック加算器に対して出力する複数のマルチプレクサ

を備えることを特徴とする多チャンネルビーム形成装置。

【請求項5】

各チャンネルからサンプリングされたデータを保存するメモリと、メモリに保存されたデータの遅延値の整数部分を使ってブロックデータを生成させる手段とを有する多チャンネルビーム形成装置を含む超音波映像処理装置用のビーム形成方法において、

小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得ることを含むポストフィルタリングを備え、該ポストフィルタリングは、同じ係数を付されたブロックデータを結合して同時にフィルタリングすることを特徴とするビーム形成方法。

【請求項6】

請求項5記載のビーム形成方法において、

前記ポストフィルタリングは、

各チャンネルを異なるアドレスを持つn個の信号に多重化すること、

前記多重化信号をアドレスにより結合すること、

結合した信号について小数部分のフィルタリングを行うこと、及び

小数フィルタリングした信号を合算すること

を備えることを特徴とするビーム形成方法。

【請求項7】

請求項5記載のビーム形成方法において、

前記ポストフィルタリングは、

各チャンネルを異なるアドレスを持つn個の信号に多重化すること、

前記多重化信号をアドレスにより結合すること、

前記結合した信号を各変数と乗算すること、及び

前記乗算して得られた信号を合算すること

を備えることを特徴とするビーム形成方法。

【請求項8】

請求項5記載のビーム形成方法において、更に、

デマルチプレクシングにより出力された信号を多重化し、アドレスにより結合される信号を出力することを備えることを特徴とするビーム形成方法。

【請求項1】

各チャンネルからサンプリングされたデータを保存するためのメモリと、該データの遅延値の整数部分に基づいてブロックデータを発生するための手段とを含む、超音波映像装置のための多チャンネルビーム形成装置において、

各チャンネルについて小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得る小数遅延フィルタを含むポストフィルタリング手段を備え、該ポストフィルタリング手段は、同じ係数を付されたチャンネルのブロックデータを結合して同時にフィルタリング工程を行うことを特徴とする多チャンネルビーム形成装置。

【請求項2】

請求項1記載の多チャンネルビーム形成装置において、

前記ポストフィルタリング手段は、

各チャンネル別ブロックアドレスをn個出力するためにチャンネル毎に設けられた複数の1対nデマルチプレクサと、

前記デマルチプレクサから出力される全ての信号を加算するためにチャンネル毎に設けられた複数のブロック加算器と、

各ブロック加算器から出力されるn個の信号を小数遅延するための複数の小数遅延フィルタと、

各小数遅延フィルタの出力信号を合算する加算器と

を含むことを特徴とする多チャンネルビーム形成装置。

【請求項3】

請求項1記載の多チャンネルビーム形成装置において、

前記ポストフィルタリング手段は、

各チャンネル別ブロックアドレスをn個出力するためにチャンネル毎に設けられた複数の1対nデマルチプレクサと、

前記デマルチプレクサから出力される信号を結合するための複数のブロック加算器と、

各ブロック加算器から出力されるn個の信号を所定の変数と乗算する複数の乗算器と、

前記乗算器から出力される信号を合算する合算器と

を備えることを特徴とする多チャンネルビーム形成装置。

【請求項4】

請求項3記載の多チャンネルビーム形成装置において、更に、

前記デマルチプレクサから出力される信号を乗算して、対応するブロック加算器に対して出力する複数のマルチプレクサ

を備えることを特徴とする多チャンネルビーム形成装置。

【請求項5】

各チャンネルからサンプリングされたデータを保存するメモリと、メモリに保存されたデータの遅延値の整数部分を使ってブロックデータを生成させる手段とを有する多チャンネルビーム形成装置を含む超音波映像処理装置用のビーム形成方法において、

小数遅延が同じブロックデータを結合し、結合されたデータから小数部分の遅延値を得ることを含むポストフィルタリングを備え、該ポストフィルタリングは、同じ係数を付されたブロックデータを結合して同時にフィルタリングすることを特徴とするビーム形成方法。

【請求項6】

請求項5記載のビーム形成方法において、

前記ポストフィルタリングは、

各チャンネルを異なるアドレスを持つn個の信号に多重化すること、

前記多重化信号をアドレスにより結合すること、

結合した信号について小数部分のフィルタリングを行うこと、及び

小数フィルタリングした信号を合算すること

を備えることを特徴とするビーム形成方法。

【請求項7】

請求項5記載のビーム形成方法において、

前記ポストフィルタリングは、

各チャンネルを異なるアドレスを持つn個の信号に多重化すること、

前記多重化信号をアドレスにより結合すること、

前記結合した信号を各変数と乗算すること、及び

前記乗算して得られた信号を合算すること

を備えることを特徴とするビーム形成方法。

【請求項8】

請求項5記載のビーム形成方法において、更に、

デマルチプレクシングにより出力された信号を多重化し、アドレスにより結合される信号を出力することを備えることを特徴とするビーム形成方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2008−149139(P2008−149139A)

【公開日】平成20年7月3日(2008.7.3)

【国際特許分類】

【出願番号】特願2007−321918(P2007−321918)

【出願日】平成19年12月13日(2007.12.13)

【出願人】(505162227)西江大学校 産学協力団 (11)

【Fターム(参考)】

【公開日】平成20年7月3日(2008.7.3)

【国際特許分類】

【出願日】平成19年12月13日(2007.12.13)

【出願人】(505162227)西江大学校 産学協力団 (11)

【Fターム(参考)】

[ Back to top ]