マイクロコントローラー

【課題】誤動作を確実に防止する。

【解決手段】クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、第2クロック信号の異常を検出する異常検出回路と、第1クロック信号と第2クロック信号のいずれかを選択して演算回路に供給する選択回路であって、電源起動時には第1クロック信号を選択し、異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて第1クロック信号から第2クロック信号に切り換え、異常検出回路で異常が検出された場合には、ファームウェアの設定に関わらずに、第1クロック信号から第2クロック信号への切り換えを行わない選択回路と、異常検出回路で異常が検出された場合に、第1クロック信号から第2クロック信号への切り換えが行われなかったことを演算回路に知らせるステータスレジスタと、を備える。

【解決手段】クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、第2クロック信号の異常を検出する異常検出回路と、第1クロック信号と第2クロック信号のいずれかを選択して演算回路に供給する選択回路であって、電源起動時には第1クロック信号を選択し、異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて第1クロック信号から第2クロック信号に切り換え、異常検出回路で異常が検出された場合には、ファームウェアの設定に関わらずに、第1クロック信号から第2クロック信号への切り換えを行わない選択回路と、異常検出回路で異常が検出された場合に、第1クロック信号から第2クロック信号への切り換えが行われなかったことを演算回路に知らせるステータスレジスタと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロコントローラーに関する。

【背景技術】

【0002】

マイクロコントローラーは、クロック信号が供給されて動作する演算回路を備えている。また、このようなマイクロコントローラーとして、メインクロックと予備クロックの2つのクロック信号を用意し、メインクロックが何らかの原因で停止した場合、予備クロックに切り換えて動作を継続させるようにしたものが提案されている(例えば特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平7−182065号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上述したマイクロコントローラーでは、メインクロックが停止した場合に予備クロックを用いていたが、例えば装置開発時などにおいて、設定ミス等によりメインクロックが異常(例えば演算回路が動作しないような周波数)になる場合がある。この場合、メインクロックを使用すると、マイクロコントローラーが誤動作するおそれがあった。

そこで、本発明は、誤動作を確実に防止することを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するための主たる発明は、クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、前記第2クロック信号の異常を検出する異常検出回路と、前記第1クロック信号と前記第2クロック信号のいずれかを選択して前記演算回路に供給する選択回路であって、電源起動時には前記第1クロック信号を選択し、前記異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて前記第1クロック信号から前記第2クロック信号に切り換え、前記異常検出回路で異常が検出された場合には、前記ファームウェアの設定に関わらずに、前記第1クロック信号から前記第2クロック信号への切り換えを行わない選択回路と、前記異常検出回路で異常が検出された場合に、前記第1クロック信号から前記第2クロック信号への切り換えが行われなかったことを前記演算回路に知らせるステータスレジスタと、を備えたことを特徴とするマイクロコントローラーである。

【0006】

本発明の他の特徴については、本明細書及び添付図面の記載により明らかにする。

【図面の簡単な説明】

【0007】

【図1】プリンター1のブロック図である。

【図2】プリンター1の装置本体2の概略断面図である。

【図3】4パスで印刷するケースにおいて各パスで形成されるラスタラインを示した模式図である。

【図4】ヘッドの移動を説明するための模式図である。

【図5】サブ基板300の構成の一例を示すブロック図である。

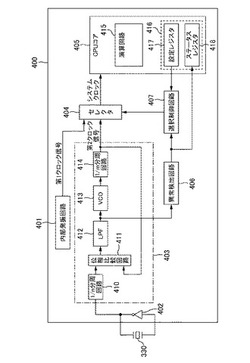

【図6】第1実施形態におけるマイクロコントローラー400の構成を示すブロック図である。

【図7】第1実施形態における異常検出回路406を示すブロック図である。

【図8】プリンター1の起動時におけるマイクロコントローラー400の動作を示すフロー図である。

【図9】第2実施形態におけるマイクロコントローラー400の構成を示すブロック図である。

【図10】第2実施形態における異常検出回路406´を示すブロック図である。

【発明を実施するための形態】

【0008】

本明細書及び添付図面の記載により、少なくとも、以下の事項が明らかとなる。

【0009】

クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、前記第2クロック信号の異常を検出する異常検出回路と、前記第1クロック信号と前記第2クロック信号のいずれかを選択して前記演算回路に供給する選択回路であって、電源起動時には前記第1クロック信号を選択し、前記異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて前記第1クロック信号から前記第2クロック信号に切り換え、前記異常検出回路で異常が検出された場合には、前記ファームウェアの設定に関わらずに、前記第1クロック信号から前記第2クロック信号への切り換えを行わない選択回路と、前記異常検出回路で異常が検出された場合に、前記第1クロック信号から前記第2クロック信号への切り換えが行われなかったことを前記演算回路に知らせるステータスレジスタと、を備えたことを特徴とするマイクロコントローラーが明らかとなる。

このようなマイクロコントローラーによれは、PLL回路から出力される第2クロック信号が異常となる場合には、演算回路に第2クロック信号が供給されなくなるので、演算回路による誤動作を確実に防止することができる。

【0010】

かかるマイクロコントローラーであって、前記異常検出回路は、前記PLL回路の電圧制御発振器への入力電圧をモニターすることによって前記第2クロック信号の異常の有無を検出してもよい。

このようなマイクロコントローラーによれば、第2クロック信号の異常を確実に検出することができる。

【0011】

かかるマイクロコントローラーであって、前記異常検出回路は、前記第2クロック信号が入力されるモニター用ロジック回路を有し、前記モニター用ロジック回路が正常に動作するか否かに基づいて前記第2クロック信号の異常の有無を検出してもよい。

このようなマイクロコントローラーによれば、第2クロック信号の異常を確実に検出することができる。

【0012】

かかるマイクロコントローラーであって、当該マイクロコントローラーのプログラミング処理中に発生したエラーをデバッグすることを示すデバッグフラグがオン状態の場合のみ、前記異常検出回路を有効にすることが望ましい。

このようなマイクロコントローラーによれば、デバック効率の向上を図ることができる。

【0013】

かかるマイクロコントローラーであって、被印刷媒体に画像を形成する画像形成装置に設けられていることが望ましい。

【0014】

かかるマイクロコントローラーであって、前記画像形成装置は、メイン基板と、前記メイン基板とは所定距離離れた位置であり、前記画像形成装置の取替え可能な消耗品とは前記所定距離未満の近い位置に配置されたサブ基板と、を有し、前記サブ基板に設けられていることが望ましい。

このようなマイクロコントローラーによれば、メイン基板と消耗品との間の信号の伝達の正確化を図ることができる。

【0015】

かかるマイクロコントローラーであって、前記メイン基板からの指示に応じて、前記消耗品に設けられた記憶素子に対してデータの読み書きをさせることが望ましい。

このようなマイクロコントローラーによれば、記憶素子のデータの読み書きを確実に行うことができる。

【0016】

以下の実施形態では、マイクロコントローラーとしてラテラル方式のインクジェットプリンター(以下、プリンター1ともいう)に設けられたものを例に挙げて説明する。なお、プリンター1は、産業用の大型プリンターである。

【0017】

===第1実施形態===

まず、図1及び図2を用いてプリンター1の構成例について説明する。図1は、プリンター1のブロック図である。図2は、プリンター1の装置本体2の概略断面図である。

なお、以下の説明において、「上下方向」、「前後方向」をいう場合は、図2に矢印で示した方向を基準として示すものとする。また、「左右方向」をいう場合は、図2において紙面に直交する方向を示すものとする。

また、本実施形態においては、プリンター1が画像を記録する媒体としてロール紙S(連続紙)を用いて説明する。

本実施形態に係るプリンター1は、図1に示すように、装置本体2と、装置本体2の右隣に配置されたインクカートリッジホルダーユニット3とを備えている。

【0018】

≪装置本体側の構成例について≫

図1及び図2に示すように、プリンター1の装置本体2は、搬送ユニット20と、及び、該搬送ユニット20がロール紙Sを搬送する搬送経路に沿って、給送ユニット10と、プラテン29と、巻き取りユニット70と、を有し、さらに、ヘッドユニット30と、キャリッジユニット40と、これらのユニット等を制御しプリンター1としての動作を司るコントローラー60と、検出器群50と、電源ユニット80とを有している。

【0019】

給送ユニット10は、ロール紙Sを搬送ユニット20に給送するものである。この給送ユニット10は、ロール紙Sが巻かれ回転可能に支持される巻軸18と、巻軸18から繰り出されたロール紙Sを巻き掛けて搬送ユニット20に導くための中継ローラー19と、を有している。

【0020】

搬送ユニット20は、給送ユニット10により送られたロール紙Sを、予め設定された搬送経路に沿って搬送するものである。この搬送ユニット20は、図2に示すように、中継ローラー19に対して水平後方に位置する中継ローラー21と、中継ローラー21から見て後斜め下方に位置する中継ローラー22と、中継ローラー22から見て後斜め上方(ロール紙Sが搬送される方向において、プラテン29から見て上流側)に位置する第一搬送ローラー23と、第一搬送ローラー23から見て後方(ロール紙Sが搬送される方向において、プラテン29から見て下流側)に位置する第二搬送ローラー24と、第二搬送ローラー24から見て鉛直下方に位置する反転ローラー25と、反転ローラー25から見て後方に位置する中継ローラー26と、中継ローラー26から見て上方に位置する送り出しローラー27と、を有している。

【0021】

中継ローラー21は、中継ローラー19から送られたロール紙Sを、前方から巻き掛けて下方に向かって弛ませるローラーである。

中継ローラー22は、中継ローラー21から送られたロール紙Sを、前方から巻き掛けて後斜め上方に向かって搬送するローラーである。

【0022】

第一搬送ローラー23は、不図示のモーターにより駆動される第一駆動ローラー23aと、該第一駆動ローラー23aに対してロール紙Sを挟んで対向するように配置された第一従動ローラー23bとを有している。この第一搬送ローラー23は、下方に弛ませたロール紙Sを上方に引き上げ、プラテン29に対向する印刷領域Rへ搬送するローラーである。第一搬送ローラー23は、印刷領域R上のロール紙Sの部位に対して画像記録がなされている期間、一時的に搬送を停止させるようになっている。なお、コントローラー60の駆動制御により、第一駆動ローラー23aの回転駆動に伴って第一従動ローラー23bが回転することによって、プラテン29上に位置させるロール紙Sの搬送量(ロール紙の部位の長さ)が調整される。

【0023】

搬送ユニット20は、上述したとおり、中継ローラー21、22と第一搬送ローラー23との間に巻き掛けたロール紙Sの部位を下方に弛ませて搬送する機構を有している。このロール紙Sの弛みは、コントローラー60により、不図示の弛み検出用センサーからの検出信号に基づき監視される。具体的には、中継ローラー21、22と第一搬送ローラー23との間において弛ませたロール紙Sの部位を、弛み検出用センサーが検出した場合には、該部位に適切な大きさの張力が与えられていることになるため、搬送ユニット20はロール紙Sを弛ませた状態で搬送することが可能となる。一方、弛み検出用センサーが弛ませたロール紙Sの部位検出しない場合は、該部位に過剰な大きさの張力が与えられていることになるため、搬送ユニット20によるロール紙Sの搬送が一時的に停止され、張力が適切な大きさに調整される。

【0024】

第二搬送ローラー24は、不図示のモーターにより駆動される第二駆動ローラー24aと、該第二駆動ローラー24aに対してロール紙Sを挟んで対向するように配置された第二従動ローラー24bとを有している。この第二搬送ローラー24は、ヘッドユニット30により画像が記録された後のロール紙Sの部位を、プラテン29の支持面に沿って水平後方向に搬送した後に鉛直下方に搬送するローラーである。これにより、ロール紙Sの搬送方向が転換されることになる。なお、コントローラー60の駆動制御により、第二駆動ローラー24aの回転駆動に伴って第二従動ローラー24bが回転することによって、プラテン29上に位置するロール紙Sの部位に対して付与される所定の張力が調整される。

【0025】

反転ローラー25は、第二搬送ローラー24から送られたロール紙Sを、前側上方から巻き掛けて後斜め上方に向かって搬送するローラーである。

中継ローラー26は、反転ローラー25から送られたロール紙Sを、前側下方から巻き掛けて上方に向かって搬送するローラーである。

送り出しローラー27は、中継ローラー26から送られたロール紙Sを、前側下方から巻き掛けて巻き取りユニット70に送り出すようになっている。

【0026】

このように、ロール紙Sが各ローラーを順次経由して移動することにより、ロール紙Sを搬送するための搬送経路が形成されることになる。なお、ロール紙Sは、搬送ユニット20により、印刷領域Rと対応した領域単位で間欠的にその搬送経路に沿って搬送される(すなわち、印刷領域R上のロール紙Sの部位に1ページ分の画像記録が成される毎に、間欠的な当該搬送が行なわれる)。

【0027】

プラテン29は、搬送経路上の印刷領域Rに位置するロール紙Sの部位を支持するものである。このプラテン29は、図2に示すように、搬送経路上の印刷領域Rに対応させて設けられ、かつ、第一搬送ローラー23と第二搬送ローラー24との間の搬送経路に沿った領域に配置されている。

【0028】

ヘッドユニット30は、搬送ユニット20により搬送経路上の印刷領域Rに(プラテン29上に)送り込まれたロール紙Sの部位に、液体の一例としてのインクを吐出するためのものである。このヘッドユニット30は、ヘッド31と、バルブユニット34と、クリーニングユニット35とを有している。

【0029】

ヘッド31は、その下面に、列方向にノズルが並んだノズル列を有している。本実施形態においては、イエロー(Y)、マゼンタ(M)、シアン(C)、ブラック(K)等の色ごとにそれぞれ複数のノズル♯1〜♯Nからなるノズル列を有している。各ノズル列の各ノズル♯1〜♯Nは、ロール紙Sの搬送方向に交差する交差方向(つまり、当該交差方向が前述した列方向である)に直線状に配列されている。各ノズル列は、当該搬送方向に沿って相互に間隔をあけて平行に配置されている。

【0030】

各ノズル♯1〜♯Nには、インク滴を吐出するための駆動素子としてピエゾ素子(不図示)が設けられている。ピエゾ素子は、その両端に設けられた電極間に所定時間幅の電圧を印加すると、電圧の印加時間に応じて伸張し、インクの流路の側壁を変形させる。これによって、インクの流路の体積がピエゾ素子の伸縮に応じて収縮し、この収縮分に相当するインクが、インク滴となって各色の各ノズル♯1〜♯Nから吐出される。

【0031】

また、ヘッド31は、後述するように、前記搬送方向(すなわち、前記前後方向)と前記列方向(すなわち、前記左右方向)に往復移動することができるようになっている。

【0032】

バルブユニット34は、インクを一時貯留するためのものであり、後述するインクカートリッジホルダーユニット3のカートリッジホルダー部310に装着されたインクカートリッジからインクが供給される。また、バルブユニット34は、不図示のインク供給チューブを介してヘッド31に接続されている。このため、ヘッド31は、バルブユニット34から供給されたインクをノズルからプラテン29上に搬送されて停止された状態のロール紙Sの部位に向けて吐出することにより、画像記録を行なうことができる。

【0033】

クリーニングユニット35は、ヘッド31をクリーニングするためのものである。このクリーニングユニット35は、ホームポジション(以下、HPと呼ぶ。図2参照)に設けられており、キャップと、吸引ポンプ等とを有している。ヘッド31(キャリッジ42)が搬送方向(前後方向)に移動してHPに位置すると、ヘッド31の下面(ノズル面)に不図示のキャップが密着するようになっている。このようにキャップが密着した状態で吸引ポンプが作動すると、ヘッド31内のインクが、増粘したインクや紙粉と共に吸引される。このようにして、目詰まりしたノズルが不吐出状態から回復することによってヘッドのクリーニングが完了する。

【0034】

キャリッジユニット40は、ヘッド31を移動させるためのものである。このキャリッジユニット40は、搬送方向(前後方向)に延びるキャリッジガイドレール41と(図2に二点鎖線で示す)、キャリッジガイドレール41に沿って搬送方向(前後方向)へ往復移動可能に支持されたキャリッジ42と、不図示のモーターとを有する。

【0035】

キャリッジ42は、不図示のモーターの駆動により、ヘッド31と一体となって搬送方向(前後方向)へ移動するよう構成されている。また、キャリッジ42には、列方向(左右方向)に延びる不図示のヘッドガイドレールが設けられており、ヘッド31は、前記モーターの駆動により、当該ヘッドガイドレールに沿って列方向(左右方向)へ移動するよう構成されている。

【0036】

巻き取りユニット70は、搬送ユニット20により送られたロール紙S(画像記録済みのロール紙)を巻き取るためのものである。この巻き取りユニット70は、送り出しローラー27から送られたロール紙Sを、前側上方から巻き掛けて後斜め下方へ搬送するための中継ローラー71と、回転可能に支持され中継ローラー71から送られたロール紙Sを巻き取る巻き取り駆動軸72と、を有している。

【0037】

コントローラー60は、プリンター1の制御を行なうための制御ユニットである。このコントローラー60は、図1に示すように、インターフェース部61A、61Bと、CPU62と、メモリー63と、ユニット制御回路64と、を有している。インターフェース部61Aは、外部装置であるホストコンピューター110とプリンター1との間でデータの送受信を行なうためのものである。インターフェース部61Bは、インクカートリッジホルダーユニット3のサブ基板300との間でデータの送受信を行なうためのものである。CPU62は、プリンター1全体の制御を行なうための演算処理装置である。メモリー63は、CPU62のプログラムを格納する領域や作業領域等を確保するためのものである。CPU62は、メモリー63に格納されているプログラムに従ってユニット制御回路64により各ユニットを制御する。なお、コントローラー60は、メイン基板200上に設けられている。

【0038】

検出器群50は、プリンター1内の状況を監視するものであり、例えば、搬送ローラーに取り付けられて媒体の搬送などの制御に利用されるロータリー式エンコーダー、搬送される媒体の有無を検出する用紙検出センサー、キャリッジ42(又はヘッド31)の搬送方向(前後方向)の位置を検出するためのリニア式エンコーダーなどがある。

【0039】

電源ユニット80は、装置本体2に固設されている。そして、不図示の電気コード等を介してコンセント等に接続されている。なお、電源ユニット80は、電源のオンオフ操作を行う電源スイッチ81を備えている。この電源スイッチ81がオン状態になることにより、プリンター1に電力が供給される。

【0040】

≪プリンター1の動作例について≫

上述した通り、本実施形態に係るプリンター1には、列方向(左右方向)にノズルが並んだノズル列を有するヘッド31が設けられている。そして、コントローラー60が、当該ヘッド31を搬送方向(前後方向)に移動させながら、ノズルからインクを吐出させ、搬送方向(前後方向)に沿ったラスタラインを形成することにより、印刷領域R上のロール紙Sの部位に1ページ分の画像記録を行なう。

【0041】

ここで、本実施形態に係るコントローラー60は、複数パス(2パス、4パス等)の印刷を実行する。すなわち、列方向における画像の解像度を高くするために、パス毎に列方向におけるヘッド31の位置を少しずつ変えて印刷を行なう。本実施形態では4パスの印刷を実行することとする。また、画像形成方法としては、例えば、公知のインターレース(マイクロウィーブ)印刷が実行される。

【0042】

これについて、図3を用いてより具体的に説明する。図3は、4パスで印刷するケースにおいて各パスで形成されるラスタラインを示した模式図である。

【0043】

図3の左側にはヘッド31のノズル列(ノズル)が表されており、当該ヘッド31(ノズル列)が搬送方向に移動しながらノズルからインクが吐出されることにより、ラスタラインが形成される。図に表されているヘッド31(ノズル列)の列方向における位置は、1パス目のときの位置であり、かかる位置を維持したままヘッド31(ノズル列)が搬送方向に移動すると、1パス目の印刷が実行され、図に表された5つのラスタライン(図の右端にパス1と書かれているラスタラインL1)が形成される。

【0044】

そして、次に、ヘッド31(ノズル列)が列方向に移動して、移動後の位置を維持したままヘッド31(ノズル列)が搬送方向に移動すると、2パス目の印刷が実行され、図に表された4つのラスタライン(右端にパス2と書かれているラスタラインL2)が形成される。なお、インターレース(マイクロウィーブ)印刷が採用されているため、前記ラスタラインL1に隣接するラスタラインL2は、ラスタラインL1を形成するインクが吐出されたノズルとは異なるノズルから吐出されたインクにより形成されることとなる。そのため、ヘッド31(ノズル列)の列方向への移動距離は、ノズル間距離(例えば、1/180インチ)の1/4分(1/180×1/4=1/720インチ)ではなく、これより大きな距離となる。

【0045】

以下、同様の動作が行なわれることにより、3パス目、4パス目の印刷が実行されて、図に表された残りのラスタライン(右端にパス3と書かれているラスタラインL3及びパス4と書かれているラスタラインL4)が形成される。このように、4パスでラスタラインが形成されることにより、列方向における画像の解像度を4倍(=720÷180)の解像度とすることが可能となる。

【0046】

なお、本実施形態においては、所謂双方向印刷が行なわれる。すなわち、1パス、3パス目の印刷が行なわれるときのヘッド31(ノズル列)の移動方向と2パス、4パス、目の印刷が行なわれるときのヘッド31(ノズル列)の移動方向は互いに逆方向となる(後に、詳述する)。

【0047】

以下では、プリンター1の動作例としてプリンター1の画像形成動作(換言すれば、インク吐出動作)を説明するが、上述した4パスで印刷する図4のケースを例に挙げて説明する(以下の説明で、図3も随時参照する)。

【0048】

<プリンター1の画像形成動作例について>

ここでは、プリンター1の印刷動作例について、図3、図4を用いて説明する。図4は、ヘッドの移動を説明するための模式図である。印刷動作を説明する前に、先ず、図4(の見方)について説明する。

【0049】

図4には、印刷処理(すなわち、画像形成に係る一連の処理)が行なわれている間に、ヘッドがどのように移動するかが示されている。ここでは、説明を分かり易くするために、ヘッド31(およびノズル列)の数は、複数個ではなく1つであることとして、説明を行なう。

【0050】

ヘッド31は、便宜上、丸印で表され(図には、大きな丸と小さな丸があるが、双方の区別に意味は無い)、ヘッドの移動が矢印で表されている。ここで、図中前後方向に向いた矢印は、搬送方向におけるヘッドの移動を表し、左右方向に向いた矢印は、列方向におけるヘッドの移動を表している。また、各矢印には、S1〜S10の符号が付けられているが、これは、以降の印刷処理の説明で用いられるステップ番号である。

【0051】

また、パス1乃至パス4が付されているステップ番号があるが、これらのステップ番号はインクが吐出されることにより画像形成動作が実行されるステップを表している。

【0052】

以下、図3、図4を参照しつつ、印刷処理について説明する。なお、当該印刷処理は、主としてコントローラー60により実現される。特に、本実施形態においては、メモリー63に格納されたプログラムをCPU62が処理することにより実現される。そして、このプログラムは、以下に説明する各種の動作を行なうためのコードから構成されている。

【0053】

前述した間欠的なロール紙Sの搬送が行なわれてロール紙Sが停止すると、印刷領域R上のロール紙Sの部位に1ページ分の画像形成を行なうための印刷処理が開始される。

【0054】

先ず、コントローラー60は、キャリッジ42(すなわち各ヘッド)をHP位置から往方向(ロール紙Sが搬送される方向において、上流側から下流側へ向かう方向)へ移動させる(ステップS1)。

【0055】

コントローラー60は、ヘッド31の往方向への移動を継続しつつ、ヘッドにインクを吐出させて、1パス目の印刷を実行する(ステップS2)。そして、このことにより、図6に示されたラスタラインL1(パス1のラスタライン)が形成される。

【0056】

ヘッドが第一折り返し位置へ至ると、コントローラー60は、ヘッドを列方向へ移動させる(ステップS3)。本実施形態においては、前記距離dだけヘッドを移動させる。

【0057】

その後、コントローラー60は、ヘッドを復方向(ロール紙Sが搬送される方向において、下流側から上流側へ向かう方向)へ移動させながら、ヘッドにインクを吐出させて、2パス目の印刷を実行する(ステップS4)。そして、このことにより、図3に示されたラスタラインL2(パス2のラスタライン)が形成される。

【0058】

ヘッドが第二折り返し位置へ至ると、コントローラー60は、ヘッドを列方向へ移動させる(ステップS5)。本実施形態においては、前記距離dだけヘッドを移動させる。

【0059】

次に、コントローラー60は、ステップS2乃至ステップS4の処理と同じ処理をさらになう(ステップS6乃至ステップS8)。この処理において、3パス目の印刷(ステップS6)により図6に示されたラスタラインL3(パス3のラスタライン)が、4パス目の印刷(ステップS8)により図6に示されたラスタラインL4(パス4のラスタライン)が、それぞれ形成される。コントローラー60は、ヘッドの列方向における位置を元に戻す(ステップS9)。すなわち、ステップS3、S5、S7でヘッドが移動した方向とは逆方向に、距離3dだけヘッドを移動させる。

【0060】

そして、コントローラー60は、ヘッドをHP位置へ移動させることにより(ステップS10)、1ページ分の画像形成を行なうための印刷処理を終了させる。なお、本実施形態では、1ページ分の画像形成を4パスで行うこととしたがこれには限られない。例えば2パスで1ページ分の画像形成を行うようにしてもよい。また、本実施形態ではインターレース(マイクロウィーブ)印刷を行うこととしたがこれには限られない。例えばバンド印刷を行ってもよい。

【0061】

≪インクカートリッジホルダーユニットの構成例について≫

図1に示すように、インクカートリッジホルダーユニット3は、サブ基板300とカートリッジホルダー部310を備えている。

【0062】

<カートリッジホルダー部について>

カートリッジホルダー部310には、インクが収容されたインクカートリッジを着脱可能に装着するためのカートリッジホルダーH1〜H4が設けられている。なお、インク、及び、インクが収容されたインクカートリッジは、プリンター1の消耗品に相当する。このカートリッジホルダーH1〜H4には、各種類(色)のインクのインクカートリッジがそれぞれ着脱可能に装着される。なお、カートリッジホルダーH1〜H4は、ヘッド31の各色のノズル列と対応している。そして、カートリッジホルダーH1〜H4に装着された各インクカートリッジのインクは不図示のインク供給チューブを通じてバルブユニット34に供給され、さらに不図示のインク供給チューブを介してヘッド31に供給される。例えば、カートリッジホルダーH1がヘッド31のシアンのノズル列に対応している場合、カートリッジホルダーH1にシアンのインクカートリッジが装着されることによって、シアンのノズル列にシアンのインクが供給されることになる。

【0063】

こうして、ヘッド31は各カートリッジホルダーから供給されたインクを吐出する。本実施形態では、前述したようにイエロー(Y)、マゼンタ(M)、シアン(C)、ブラック(K)の4色のインクを使用して画像を印刷する。すなわちカートリッジホルダーH1〜H4には、上記4色のインクカートリッジの何れかが装着される。

【0064】

なお、インクカートリッジ(不図示)は、内部にインクを収容するカートリッジ本体、カートリッジ本体に備えつけられた基板、当該基板に設けられた記憶素子(CSICともいう)を備えている。CSICは、インクカートリッジをカートリッジホルダー部310のカートリッジホルダーH1〜H4に装着したときに、プリンター1(コントローラー60)との間で各種のデータを授受するための素子であり、不揮発性メモリー(例えばフラッシュメモリー)など、データの格納可能な素子により構成される。CSICには、例えば、当該カートリッジに収容されているインクの色、濃度、粘性などの特性を示す情報や、各種の印刷制御プログラムなどが記憶されている。また、インクカートリッジには、この記憶素子と電気的に接続された複数の接続端子が露出して形成されている。

【0065】

これに対して、カートリッジホルダー部310のカートリッジホルダーH1〜H4には、インクカートリッジを装着したときにインクカートリッジの複数の接続端子とそれぞれ電気的に接続するための複数の接続端子(不図示)が形成されている。

【0066】

インクカートリッジがカートリッジホルダー部310のカートリッジホルダーH1〜H4に装着されると、インクカートリッジからプリンターの装置本体2のヘッド31へのインクの供給が可能になる。また、インクカートリッジがカートリッジホルダーH1〜H4に装着されるとインクカートリッジの複数の接続端子と、カートリッジホルダーH1〜H4の複数の接続端子とがそれぞれ電気的に接続して、サブ基板300を介して、プリンター1のメイン基板200(コントローラー60)とインクカートリッジの記憶素子との間においてデータの授受が可能となる。

【0067】

このように、インクカートリッジホルダーユニット3のカートリッジホルダー部310にインクカートリッジが装着されることにより、メイン基板200(コントローラー60)は、サブ基板300を介してインクカートリッジの記憶素子からのデータの読み出しや、インクカートリッジの記憶素子へのデータの書き込みを行うことができる。

【0068】

<サブ基板について>

本実施形態のプリンター1のような大型のプリンターの場合、メイン基板200とカートリッジホルダー部310の位置がかなり離れていることがある。この場合、仮に、メイン基板200とカートリッジホルダー部310とを直接電気的に接続すると、信号の伝送距離が非常に長くなってしまう。このため、例えば、信号がなまってしまい、正確な通信が行えなくなるおそれがある。そこで本実施形態では、メイン基板200とカートリッジホルダー部310との間にサブ基板300を設けている。そして、メイン基板200からサブ基板300を介して、カートリッジの記憶素子(CSIC)の読み取りや書き込みを行うようにしている。このようにサブ基板300を設けることによって、メイン基板200とインクカートリッジのCSIC間の信号の伝達の安定化を図っている。

【0069】

図5はサブ基板300の構成の一例を示すブロック図である。

図5に示すサブ基板300は、マイクロコントローラー400を備えている。またサブ基板300は、メイン基板200及びカートリッジホルダー部310と通信するための不図示のインターフェース部などを有している。本実施形態ではサブ基板300は、インクカートリッジホルダーユニット3に設けられている。言い換えると、メイン基板200とは一定距離離れた位置であり、カートリッジホルダー部310(言い換えるとインクカートリッジ)とは近い(上記一定距離より短い)位置に設けられている。

【0070】

≪マイクロコントローラーの構成について≫

図6は、第1実施形態におけるマイクロコントローラー400の構成の一例を示すブロック図である。

図6に示すように、第1実施形態のマイクロコントローラー400は、内部発振回路401と、インバーター402と、PLL回路403と、セレクタ404と、CPUコア405と、異常検出回路406と、選択制御回路407とを備えている。

【0071】

内部発振回路401は、不図示の内部発振器により所定周波数のクロック信号(以下、第1クロック信号とよぶ)を生成して出力する。

インバーター402は、サブ基板300(マイクロコントローラー400の外部)に設けられた外部発振素子330とともに基準クロックを生成する発振回路を構成している。なお、外部発振素子330には、例えば水晶発振子が用いられる。

【0072】

PLL(Phase Locked Loop)回路403は、外部発振素子330の発振クロック(基準クロック)に基づいてクロック信号(以下、第2クロック信号とよぶ)を生成する。なお、PLL回路403の詳細については後述する。

【0073】

セレクタ404は、内部発振回路401から出力される第1クロック信号、及び、PLL回路403から出力される第2クロック信号の何れかを選択し、システムクロックとしてCPUコア405に供給する。

【0074】

CPUコア405は、プログラムによって様々な数値計算や情報処理、機器制御などを行うものであり、論理演算や制御を行う演算回路415と、プログラムやデータ等を記憶する記憶回路416(例えば、フラッシュメモリーやRAM)を有している。また、記憶回路416は、設定レジスタ417、及び、ステータスレジスタ418を有している。

【0075】

異常検出回路406は、PLL回路403で生成される第2クロック信号の異常(クロック周波数の異常など)の有無を検出するためのものである。なお、異常検出回路406の詳細については後述する。

【0076】

選択制御回路407は、異常検出回路406の検出結果及び設定レジスタ417の設定に基づいて、セレクタ404の選択を制御する(換言すると、クロック信号の切り換えを制御する)ためのものである。なお、本実施形態において、セレクタ404と選択制御回路407は、選択回路に相当する。

【0077】

<PLL回路について>

図6に示すように、PLL回路403は、1/n分周回路410と、位相比較回路411と、ローパスフィルター(以下、LPFともいう)412と、電圧制御発振器(以下、VCOともいう)413と、1/m分周回路414とを有している。

【0078】

1/n分周回路410は、外部発振素子330の発振クロック(基準クロック)を1/n分周した周波数信号(第3クロック信号とよぶ)を生成し、位相比較回路411に出力する。例えば、n=10の場合、入力周波数が10MHzのとき出力周波数は1MHzになる。

【0079】

位相比較回路411は、1/n分周回路410の出力である第3クロック信号と、PLL回路403(より具体的には、後述する1/m分周回路414)の出力である第2クロック信号を位相比較し、その位相差を電圧(または電流)の形で出力する。

【0080】

LPF412は、例えば、抵抗とコンデンサとを有するRC積分回路であり、位相比較回路411の出力電圧の交流成分(高周波成分)をコンデンサで除去することにより平滑化する。

【0081】

VCO(Voltage Controlled Oscillator)413は、入力電圧に応じた周波数信号(パルス信号)を出力するものである。例えば、入力電圧が高いほど、高い周波数の信号を出力し、入力電圧が低いほど低い周波数の信号を出力する。このように、VCO413は、LPF412からの電圧に対応する発振周波数の周波数信号を生成して、1/m分周回路414に出力する。尚、VCO413としては、不図示の水晶発振器やリチウムタンタレート(LiTaO3)を用いた発振器等を適用することが可能である。

【0082】

1/m分周回路414は、1/n分周回路410と同様の構成の回路であり、VCO413の出力信号を1/m分周したクロック信号(第2クロック信号)を生成し、セレクタ404及び位相比較回路411に出力する。

【0083】

次にPLL回路403の動作について説明する。外部から入力される基準信号に基づいた1/n分周回路410の出力(第3クロック信号)と1/m分周回路414の出力(第2クロック信号)との比較信号との位相比較が位相比較回路411で行なわれる。そして、位相比較回路411は、この位相差成分をパルス状の位相差信号として出力する。

【0084】

次に、この位相差信号は、LPF412により高周波成分が遮断されてVCO413に入力される。VCO413は入力電圧に応じた周波数信号(パルス信号)を出力し、その周波数信号は1/m分周回路414で分周されて第2クロック信号として出力されるとともに、位相比較回路411にフィードバック(帰還ループ)される。

【0085】

このように、PLL回路403は、外部の基準クロックに基づいて第2クロック信号を生成する。なお、第2クロック信号は、1/n分周回路410及び1/m分周回路414の設定(すなわち「n」と「m」の値の設定)によって、必要な周波数に定めることが可能である。本実施形態では、このPLL回路403で生成される第2クロック信号をメインクロックとして使用することとしている。

【0086】

<異常検出回路について>

図7は第1実施形態における異常検出回路406の一例を示すブロック図である。

第1実施形態の異常検出回路406は、上限電圧コンパレーター421と、下限電圧コンパレーター422と、論理和回路(OR回路)423とを有している。

【0087】

上限電圧コンパレーター421の非反転入力(+端子:不図示)には、VCO413への入力電圧が印加され、反転入力(−端子:不図示)には上限電圧が印加される。そして、上限電圧コンパレーター421は、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも高ければハイレベル(以下、Hレベルともいう)の電圧を出力する。言い換えると、VCO413への入力電圧が上限電圧よりも高ければHレベルの電圧を出力する。一方、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも低ければローレベル(以下、Lレベルともいう)の電圧を出力する。

【0088】

下限電圧コンパレーター422の非反転入力(+端子:不図示)には、下限電圧が印加され、反転入力(−端子:不図示)にはVCO413への入力電圧が印加される。そして、下限電圧コンパレーター422は、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも高ければHレベルの電圧を出力する。言い換えると、VCO413への入力電圧が下限電圧よりも低ければHレベルの電圧を出力する。一方、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも低ければLレベルの電圧を出力する。

【0089】

論理和回路423は、上限電圧コンパレーター421と下限電圧コンパレーター422の出力の少なくとも一つがHレベルであればHレベルを出力し、上限電圧コンパレーター421と下限電圧コンパレーター422の出力が共にLレベルであればLレベルを出力する。

【0090】

以上の構成により、異常検出回路406の出力がHレベルのときには、上限電圧と下限電圧の少なくとも一方に異常が発生していることになる。一方、異常検出回路406の出力がLレベルのときには上限電圧と下限電圧の何れにも異常が発生していないことになる。このように第1実施形態の異常検出回路406は、VCO413への入力電圧をモニターしている。そして、その出力レベルがHレベルかLレベルかによって、第2クロック信号に異常が発生しているか否かを判断することができる。

【0091】

<選択制御回路について>

セレクタ404には、内部発振回路401から出力されるクロック信号(第1クロック信号)と、PLL回路403から出力されるクロック信号(第2クロック信号)の2つのクロック信号が入力される。そしてセレクタ404は、その2つのクロック信号の何れかを選択して、CPUコア405のシステムクロックとして出力する。

【0092】

前述したように、選択制御回路407は、セレクタ404のクロック信号の選択を制御するためのものである。

本実施形態の選択制御回路407は、電源起動時(すなわち電源スイッチ81がオン状態となったとき)にはセレクタ404が第1クロック信号を選択するように制御する。

【0093】

その後、異常検出回路406の出力がLレベルのとき(すなわち異常が発生していないと検出されたとき)には、選択制御回路407は、ファームウェアの設定(設定レジスタ417の設定)に応じたタイミングで、セレクタ404が第2クロック信号を選択するようにセレクタ404の選択の切り換えを行う。

【0094】

一方、異常検出回路406の出力がHレベルのとき(すなわち異常が発生していると検出されたき)には、選択制御回路407は、ファームウェアの設定(設定レジスタ417の設定)にかかわらず、セレクタ404の選択の切り換えを行わないようにする。すなわち、セレクタ404は第1クロック信号を選択したままであり、第2クロック信号への切り換えは行わない。

【0095】

また、このとき、ステータスレジスタ418は、異常検出回路406の出力がHレベルであることを記憶し、演算回路415に対して、セレクタ404によるシステムクロックの切り換えが行われなかったことを知らせる。これにより、演算回路415は、例えば、クロック信号が切り換わらない場合に応じた対応を行う。

【0096】

<起動時の動作について>

本実施形態のマイクロコントローラー400には、プログラミングデバッグを行っているか否かを示すフラグ(以下、デバッグフラグとよぶ)が用意されている。そして、異常検出回路406は、デバッグフラグが立っている場合(オン状態の場合)のみに有効になるように設定されている。なお、デバッグとは、コンピュータープログラム中のバグ・欠陥などのエラーを発見及び修正し、動作を仕様通りのものとするための作業である。例えば、装置(プリンター1)の開発時に、1/n分周回路410と1/m分周回路における分周の比(nとmの値)を間違うと、異常に低い周波数になったり、異常に高い周波数になったりしてVCO413が発振しなかったり、あるいはPLL回路403の後段の演算回路415が正常に動作しなかったりする。この状態でセレクタ404の選択をPLL回路403の出力側に切り換えるとデバッグがハングした状態となり、以後、デバッグ作業ができなくなるおそれがある。また、この設定(nとmの値の設定)ミスに気づくのに時間を要し、デバッグ効率を落とすおそれもある。本実施形態では、デバッグ時にステータスレジスタ418を確認することにより、第2クロック信号の異常を気付きやすくすることができ、デバッグの効率を向上させることができる。

【0097】

図8は、プリンター1の起動時におけるマイクロコントローラー400の動作の一例を示すフロー図である。

まず、電源がON(すなわち電源スイッチ81がオン状態)になると(S101)、マイクロコントローラー400の選択制御回路407は、セレクタ404に第1クロック信号を選択させる(S102)。すなわち、システムクロックとして第1クロック信号がセレクタ404からCPUコア405に供給される。

【0098】

次にマイクロコンコントローラー400は、デバッグフラグが立っているか否かを判断する(S103)。デバッグフラグが立っていない場合(S103でNO)、マイクロコントローラー400は、異常検出回路406を無効にし(S104)、選択制御回路407は、ファームウェアの設定(具体的には設定レジスタ417の設定)に応じてセレクタ404の選択を第1クロック信号から第2クロック信号に切り換えさせる(S105)

一方、ステップS103でデバッグフラグが立っていると判断した場合(S103でYES)、マイクロコントローラー400は、異常検出回路406を有効にし(S106)、異常が検出されたか否かの判断を行う(S107)。異常が検出されなければ(S107でNO)、具体的には異常検出回路406の出力がLレベルである場合は、ステップS105を実行する。

【0099】

異常が検出された場合(S107でYES)、具体的には異常検出回路406の出力がHレベルである場合は、選択制御回路407は、ファームウェアの設定にかかわらず、セレクタ404に第1クロック信号から第2クロック信号への切り換えを実行させない(S108)。また、CPUコア405のステータスレジスタ418には、異常検出回路406の出力がHレベルであること(すなわち第2クロック信号に異常が検出されたこと)が記憶される(S109)。このステータスレジスタ418の情報により、演算回路415は、第1クロック信号から第2クロック信号に切り換えられていないことを認識する。そして、演算回路415は、例えば、クロック信号が切り換わらない場合に応じた対応を行う。

【0100】

上述したように、本実施形態では、異常検出回路406はプログラミングデバッグ時のみに有効になるようにしている。この異常検出回路406によってデバッグ時の異常の原因が特定しやすくなり、デバック効率を向上させることができる。

【0101】

以上説明したように、本実施形態のマイクロコントローラー400は、クロック信号が供給されて動作するCPUコア405の演算回路415と、第1クロック信号を生成する内部発振回路401と、基準クロックに基づいて第2クロック信号を生成するPLL回路403と、第2クロック信号の異常を検出する異常検出回路406と、第1クロック信号と第2クロック信号のいずれかを選択してCPUコア405にシステムクロックとして供給する選択回路(セレクタ404及び選択制御回路407)を備えている。

【0102】

そして、選択回路は、電源起動時にはシステムクロックとして第1クロック信号を選択し、異常検出回路406で異常が検出されない場合には、ファームウェアの設定に応じて第1クロック信号から第2クロック信号に切り換えている。一方、異常検出回路406で異常が検出された場合には、ファームウェアの設定に関わらずに、第1クロック信号から第2クロック信号への切り換えを行わないようにしている。また、ステータスレジスタ418は、異常検出回路406で異常が検出されたことを示す情報(言い換えると、クロック信号の切り換えが行われなかったことを示す情報)を記憶し、演算回路415に知らせている。

【0103】

こうすることにより、例えば、プログラミングデバッグ時などにおいてnの値、及び、mの値の設定ミスにより第2クロック信号が異常周波数となった場合においても、第1クロック信号から第2クロック信号への切り換えが行われないので、誤動作を確実に防止することができる。また、ステータスレジスタ418を確認することにより第2クロック信号が異常になっていることを認識できる。このため、デバッグ時の異常の原因が特定しやすくなり、デバック効率を向上させることができる。

【0104】

===第2実施形態===

図9は、第2実施形態におけるマイクロコントローラー400の構成を示すブロック図である。なお、図8において、第1実施形態(図6)と同じ構成の部分には同一符号を付し説明を省略する。第2実施形態のマイクロコントローラー400は、異常検出回路406´を有している。異常検出回路406´には、1/m分周回路414の出力(すなわちク第2ロック信号)が入力されている。

【0105】

図10は、第2実施形態における異常検出回路406´の構成の一例を示すブロック図である。

図に示すように、異常検出回路406´は、Dフロップフロップ(D-FF)431、遅延回路432、トグル動作確認回路433を有している。なお、これらの回路は、第2クロック信号のモニター用ロジック回路を構成している。

【0106】

Dフリップフロップ431のD入力には、遅延回路432の出力が入力される。またCKには、1/m分周回路414の出力(すなわち第2クロック信号)が入力される。第2クロック信号が立ち上がったときに、D入力が「Hレベル」ならば、Q出力は「Hレベル」となり、/Qは「Lレベル」となる。一方、第2クロック信号が立ち上がったときに、D入力が「Lレベル」ならば、Q出力は「Lレベル」となり、/Qは1「Hレベル」となる

遅延回路432は、入力される信号の波形を変えずに伝達に所定時間の遅れ(遅延)を作る回路である。

【0107】

トグル動作確認回路433には、内部発振回路401の出力(すなわち第1クロック信号)と、遅延回路432の出力が入力される。そして、トグル動作確認回路433は、遅延回路432の出力が第1クロック信号の周期で、HレベルとLレベルに切り換わっているか(トグル動作をしているか)を検出する。例えば、第2クロック信号として、Hレベル又はLレベルの一方が連続して続くようになると、CPUコア405のシステムクロックとして機能しないことになる。よって、Hレベル又はLレベルが所定回数連続することによって、第2クロック信号が異常であることを検出することができる。トグル動作確認回路433は、第1クロック信号の周期で遅延回路432の出力がHレベルあるいはLレベルが連続して続く場合は異常を示す信号(例えばHレベルの信号)を出力する。一方、HレベルとLレベルに切り換わっている場合(すばわちトグル動作を確認した場合)は異常が検出されなかったことを示す信号(例えばLレベルの信号)を出力する。このトグル動作確認回路433の出力が異常検出回路406´の出力になる。

【0108】

なお、プリンター1の起動時の動作については第1実施形態(図8)と同様であるので説明を省略する。

【0109】

===その他の実施の形態===

一実施形態としてのプリンター等を説明したが、上記の実施形態は、本発明の理解を容易にするためのものであり、本発明を限定して解釈するためのものではない。本発明は、その趣旨を逸脱することなく、変更、改良され得ると共に、本発明にはその等価物が含まれることは言うまでもない。特に、以下に述べる実施形態であっても、本発明に含まれるものである。

【0110】

<プリンターについて>

前述の実施形態では、ラテラル式のプリンターであったが、これには限らない。例えば、被印刷媒体を搬送方向に搬送する搬送動作と、ヘッドを移動方向(搬送方向と交差する方向)に移動しつつ、ヘッドのノズルからインクを吐出して被印刷媒体にドットを形成するドット形成動作とを繰り返して画像を形成するプリンター(いわゆるシリアルプリンター)であってもよい。また、例えば、被印刷媒体を搬送方向に搬送しつつ搬送経路上に設けられたヘッドからUVインクを吐出して画像を形成するプリンター(いわゆるラインプリンター)であってもよい。

【0111】

<ノズルについて>

前述の実施形態では、圧電素子(ピエゾ素子)を用いてインクを吐出していた。しかし、液体を吐出する方式は、これに限られるものではない。例えば、熱によりノズル内に泡を発生させる方式など、他の方式を用いてもよい。

【0112】

<サブ基板について>

前述の実施形態では、1つのサブ基板が4つのインクカートリッジ(言い換えるとCSIC)と対応していたが、これには限らない。例えば3つ以下のインクカートリッジと対応していてもよいし、5つ以上のインクカートリッジと対応していてもよい。また、サブ基板(マイクロコントローラー400)の数が2つ以上であってもよい。

【0113】

<異常検出回路について>

異常検出回路406(406´)の構成は、前述した実施形態には限られず、第2クロック信号の異常を検出することが出来れば、他の構成のものを用いてもよい。

【符号の説明】

【0114】

1 プリンター、2 装置本体、3 インクカートリッジホルダーユニット、

10 給送ユニット、18 巻軸、19 中継ローラー、

20 搬送ユニット、21 中継ローラー、22 中継ローラー、

23 第一搬送ローラー、23a 第一駆動ローラー、23b 第一従動ローラー、

24 第二搬送ローラー、24a 第二駆動ローラー、24b 第二従動ローラー、

25 反転ローラー、26 中継ローラー、27 送り出しローラー、29 プラテン、

30 ヘッドユニット、31 ヘッド、34 バルブユニット、

35 クリーニングユニット、40 キャリッジユニット、41 ガイドレール、

42 キャリッジ、50 検出器群、60 コントローラー、

61 インターフェース部、62 CPU、63 メモリー、64 ユニット制御回路、

70 巻き取りユニット、71 中継ローラー、72 巻き取り駆動軸、

80 電源ユニット、81 電源スイッチ、

110 ホストコンピューター、200 メイン基板、300 サブ基板、

310 カートリッジホルダー部、330 外部発振素子、

400 マイクロコントローラー、401 内部発振回路、402 インバーター、

403 PLL回路、404 セレクタ、405 CPUコア、406 異常検出回路、

407 選択制御回路、410 1/n分周回路、411 位相比較回路、

412 LPF、413 VCO、414 1/m分周回路、

415 演算回路、416 記憶回路、417 設定レジスタ、

418 ステータスレジスタ、421 上限電圧コンパレーター、

422 下限電圧コンパレーター、423 論理和回路、431 Dフリップフロップ、

432 遅延回路、433 トグル動作確認回路

【技術分野】

【0001】

本発明は、マイクロコントローラーに関する。

【背景技術】

【0002】

マイクロコントローラーは、クロック信号が供給されて動作する演算回路を備えている。また、このようなマイクロコントローラーとして、メインクロックと予備クロックの2つのクロック信号を用意し、メインクロックが何らかの原因で停止した場合、予備クロックに切り換えて動作を継続させるようにしたものが提案されている(例えば特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平7−182065号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上述したマイクロコントローラーでは、メインクロックが停止した場合に予備クロックを用いていたが、例えば装置開発時などにおいて、設定ミス等によりメインクロックが異常(例えば演算回路が動作しないような周波数)になる場合がある。この場合、メインクロックを使用すると、マイクロコントローラーが誤動作するおそれがあった。

そこで、本発明は、誤動作を確実に防止することを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するための主たる発明は、クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、前記第2クロック信号の異常を検出する異常検出回路と、前記第1クロック信号と前記第2クロック信号のいずれかを選択して前記演算回路に供給する選択回路であって、電源起動時には前記第1クロック信号を選択し、前記異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて前記第1クロック信号から前記第2クロック信号に切り換え、前記異常検出回路で異常が検出された場合には、前記ファームウェアの設定に関わらずに、前記第1クロック信号から前記第2クロック信号への切り換えを行わない選択回路と、前記異常検出回路で異常が検出された場合に、前記第1クロック信号から前記第2クロック信号への切り換えが行われなかったことを前記演算回路に知らせるステータスレジスタと、を備えたことを特徴とするマイクロコントローラーである。

【0006】

本発明の他の特徴については、本明細書及び添付図面の記載により明らかにする。

【図面の簡単な説明】

【0007】

【図1】プリンター1のブロック図である。

【図2】プリンター1の装置本体2の概略断面図である。

【図3】4パスで印刷するケースにおいて各パスで形成されるラスタラインを示した模式図である。

【図4】ヘッドの移動を説明するための模式図である。

【図5】サブ基板300の構成の一例を示すブロック図である。

【図6】第1実施形態におけるマイクロコントローラー400の構成を示すブロック図である。

【図7】第1実施形態における異常検出回路406を示すブロック図である。

【図8】プリンター1の起動時におけるマイクロコントローラー400の動作を示すフロー図である。

【図9】第2実施形態におけるマイクロコントローラー400の構成を示すブロック図である。

【図10】第2実施形態における異常検出回路406´を示すブロック図である。

【発明を実施するための形態】

【0008】

本明細書及び添付図面の記載により、少なくとも、以下の事項が明らかとなる。

【0009】

クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、前記第2クロック信号の異常を検出する異常検出回路と、前記第1クロック信号と前記第2クロック信号のいずれかを選択して前記演算回路に供給する選択回路であって、電源起動時には前記第1クロック信号を選択し、前記異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて前記第1クロック信号から前記第2クロック信号に切り換え、前記異常検出回路で異常が検出された場合には、前記ファームウェアの設定に関わらずに、前記第1クロック信号から前記第2クロック信号への切り換えを行わない選択回路と、前記異常検出回路で異常が検出された場合に、前記第1クロック信号から前記第2クロック信号への切り換えが行われなかったことを前記演算回路に知らせるステータスレジスタと、を備えたことを特徴とするマイクロコントローラーが明らかとなる。

このようなマイクロコントローラーによれは、PLL回路から出力される第2クロック信号が異常となる場合には、演算回路に第2クロック信号が供給されなくなるので、演算回路による誤動作を確実に防止することができる。

【0010】

かかるマイクロコントローラーであって、前記異常検出回路は、前記PLL回路の電圧制御発振器への入力電圧をモニターすることによって前記第2クロック信号の異常の有無を検出してもよい。

このようなマイクロコントローラーによれば、第2クロック信号の異常を確実に検出することができる。

【0011】

かかるマイクロコントローラーであって、前記異常検出回路は、前記第2クロック信号が入力されるモニター用ロジック回路を有し、前記モニター用ロジック回路が正常に動作するか否かに基づいて前記第2クロック信号の異常の有無を検出してもよい。

このようなマイクロコントローラーによれば、第2クロック信号の異常を確実に検出することができる。

【0012】

かかるマイクロコントローラーであって、当該マイクロコントローラーのプログラミング処理中に発生したエラーをデバッグすることを示すデバッグフラグがオン状態の場合のみ、前記異常検出回路を有効にすることが望ましい。

このようなマイクロコントローラーによれば、デバック効率の向上を図ることができる。

【0013】

かかるマイクロコントローラーであって、被印刷媒体に画像を形成する画像形成装置に設けられていることが望ましい。

【0014】

かかるマイクロコントローラーであって、前記画像形成装置は、メイン基板と、前記メイン基板とは所定距離離れた位置であり、前記画像形成装置の取替え可能な消耗品とは前記所定距離未満の近い位置に配置されたサブ基板と、を有し、前記サブ基板に設けられていることが望ましい。

このようなマイクロコントローラーによれば、メイン基板と消耗品との間の信号の伝達の正確化を図ることができる。

【0015】

かかるマイクロコントローラーであって、前記メイン基板からの指示に応じて、前記消耗品に設けられた記憶素子に対してデータの読み書きをさせることが望ましい。

このようなマイクロコントローラーによれば、記憶素子のデータの読み書きを確実に行うことができる。

【0016】

以下の実施形態では、マイクロコントローラーとしてラテラル方式のインクジェットプリンター(以下、プリンター1ともいう)に設けられたものを例に挙げて説明する。なお、プリンター1は、産業用の大型プリンターである。

【0017】

===第1実施形態===

まず、図1及び図2を用いてプリンター1の構成例について説明する。図1は、プリンター1のブロック図である。図2は、プリンター1の装置本体2の概略断面図である。

なお、以下の説明において、「上下方向」、「前後方向」をいう場合は、図2に矢印で示した方向を基準として示すものとする。また、「左右方向」をいう場合は、図2において紙面に直交する方向を示すものとする。

また、本実施形態においては、プリンター1が画像を記録する媒体としてロール紙S(連続紙)を用いて説明する。

本実施形態に係るプリンター1は、図1に示すように、装置本体2と、装置本体2の右隣に配置されたインクカートリッジホルダーユニット3とを備えている。

【0018】

≪装置本体側の構成例について≫

図1及び図2に示すように、プリンター1の装置本体2は、搬送ユニット20と、及び、該搬送ユニット20がロール紙Sを搬送する搬送経路に沿って、給送ユニット10と、プラテン29と、巻き取りユニット70と、を有し、さらに、ヘッドユニット30と、キャリッジユニット40と、これらのユニット等を制御しプリンター1としての動作を司るコントローラー60と、検出器群50と、電源ユニット80とを有している。

【0019】

給送ユニット10は、ロール紙Sを搬送ユニット20に給送するものである。この給送ユニット10は、ロール紙Sが巻かれ回転可能に支持される巻軸18と、巻軸18から繰り出されたロール紙Sを巻き掛けて搬送ユニット20に導くための中継ローラー19と、を有している。

【0020】

搬送ユニット20は、給送ユニット10により送られたロール紙Sを、予め設定された搬送経路に沿って搬送するものである。この搬送ユニット20は、図2に示すように、中継ローラー19に対して水平後方に位置する中継ローラー21と、中継ローラー21から見て後斜め下方に位置する中継ローラー22と、中継ローラー22から見て後斜め上方(ロール紙Sが搬送される方向において、プラテン29から見て上流側)に位置する第一搬送ローラー23と、第一搬送ローラー23から見て後方(ロール紙Sが搬送される方向において、プラテン29から見て下流側)に位置する第二搬送ローラー24と、第二搬送ローラー24から見て鉛直下方に位置する反転ローラー25と、反転ローラー25から見て後方に位置する中継ローラー26と、中継ローラー26から見て上方に位置する送り出しローラー27と、を有している。

【0021】

中継ローラー21は、中継ローラー19から送られたロール紙Sを、前方から巻き掛けて下方に向かって弛ませるローラーである。

中継ローラー22は、中継ローラー21から送られたロール紙Sを、前方から巻き掛けて後斜め上方に向かって搬送するローラーである。

【0022】

第一搬送ローラー23は、不図示のモーターにより駆動される第一駆動ローラー23aと、該第一駆動ローラー23aに対してロール紙Sを挟んで対向するように配置された第一従動ローラー23bとを有している。この第一搬送ローラー23は、下方に弛ませたロール紙Sを上方に引き上げ、プラテン29に対向する印刷領域Rへ搬送するローラーである。第一搬送ローラー23は、印刷領域R上のロール紙Sの部位に対して画像記録がなされている期間、一時的に搬送を停止させるようになっている。なお、コントローラー60の駆動制御により、第一駆動ローラー23aの回転駆動に伴って第一従動ローラー23bが回転することによって、プラテン29上に位置させるロール紙Sの搬送量(ロール紙の部位の長さ)が調整される。

【0023】

搬送ユニット20は、上述したとおり、中継ローラー21、22と第一搬送ローラー23との間に巻き掛けたロール紙Sの部位を下方に弛ませて搬送する機構を有している。このロール紙Sの弛みは、コントローラー60により、不図示の弛み検出用センサーからの検出信号に基づき監視される。具体的には、中継ローラー21、22と第一搬送ローラー23との間において弛ませたロール紙Sの部位を、弛み検出用センサーが検出した場合には、該部位に適切な大きさの張力が与えられていることになるため、搬送ユニット20はロール紙Sを弛ませた状態で搬送することが可能となる。一方、弛み検出用センサーが弛ませたロール紙Sの部位検出しない場合は、該部位に過剰な大きさの張力が与えられていることになるため、搬送ユニット20によるロール紙Sの搬送が一時的に停止され、張力が適切な大きさに調整される。

【0024】

第二搬送ローラー24は、不図示のモーターにより駆動される第二駆動ローラー24aと、該第二駆動ローラー24aに対してロール紙Sを挟んで対向するように配置された第二従動ローラー24bとを有している。この第二搬送ローラー24は、ヘッドユニット30により画像が記録された後のロール紙Sの部位を、プラテン29の支持面に沿って水平後方向に搬送した後に鉛直下方に搬送するローラーである。これにより、ロール紙Sの搬送方向が転換されることになる。なお、コントローラー60の駆動制御により、第二駆動ローラー24aの回転駆動に伴って第二従動ローラー24bが回転することによって、プラテン29上に位置するロール紙Sの部位に対して付与される所定の張力が調整される。

【0025】

反転ローラー25は、第二搬送ローラー24から送られたロール紙Sを、前側上方から巻き掛けて後斜め上方に向かって搬送するローラーである。

中継ローラー26は、反転ローラー25から送られたロール紙Sを、前側下方から巻き掛けて上方に向かって搬送するローラーである。

送り出しローラー27は、中継ローラー26から送られたロール紙Sを、前側下方から巻き掛けて巻き取りユニット70に送り出すようになっている。

【0026】

このように、ロール紙Sが各ローラーを順次経由して移動することにより、ロール紙Sを搬送するための搬送経路が形成されることになる。なお、ロール紙Sは、搬送ユニット20により、印刷領域Rと対応した領域単位で間欠的にその搬送経路に沿って搬送される(すなわち、印刷領域R上のロール紙Sの部位に1ページ分の画像記録が成される毎に、間欠的な当該搬送が行なわれる)。

【0027】

プラテン29は、搬送経路上の印刷領域Rに位置するロール紙Sの部位を支持するものである。このプラテン29は、図2に示すように、搬送経路上の印刷領域Rに対応させて設けられ、かつ、第一搬送ローラー23と第二搬送ローラー24との間の搬送経路に沿った領域に配置されている。

【0028】

ヘッドユニット30は、搬送ユニット20により搬送経路上の印刷領域Rに(プラテン29上に)送り込まれたロール紙Sの部位に、液体の一例としてのインクを吐出するためのものである。このヘッドユニット30は、ヘッド31と、バルブユニット34と、クリーニングユニット35とを有している。

【0029】

ヘッド31は、その下面に、列方向にノズルが並んだノズル列を有している。本実施形態においては、イエロー(Y)、マゼンタ(M)、シアン(C)、ブラック(K)等の色ごとにそれぞれ複数のノズル♯1〜♯Nからなるノズル列を有している。各ノズル列の各ノズル♯1〜♯Nは、ロール紙Sの搬送方向に交差する交差方向(つまり、当該交差方向が前述した列方向である)に直線状に配列されている。各ノズル列は、当該搬送方向に沿って相互に間隔をあけて平行に配置されている。

【0030】

各ノズル♯1〜♯Nには、インク滴を吐出するための駆動素子としてピエゾ素子(不図示)が設けられている。ピエゾ素子は、その両端に設けられた電極間に所定時間幅の電圧を印加すると、電圧の印加時間に応じて伸張し、インクの流路の側壁を変形させる。これによって、インクの流路の体積がピエゾ素子の伸縮に応じて収縮し、この収縮分に相当するインクが、インク滴となって各色の各ノズル♯1〜♯Nから吐出される。

【0031】

また、ヘッド31は、後述するように、前記搬送方向(すなわち、前記前後方向)と前記列方向(すなわち、前記左右方向)に往復移動することができるようになっている。

【0032】

バルブユニット34は、インクを一時貯留するためのものであり、後述するインクカートリッジホルダーユニット3のカートリッジホルダー部310に装着されたインクカートリッジからインクが供給される。また、バルブユニット34は、不図示のインク供給チューブを介してヘッド31に接続されている。このため、ヘッド31は、バルブユニット34から供給されたインクをノズルからプラテン29上に搬送されて停止された状態のロール紙Sの部位に向けて吐出することにより、画像記録を行なうことができる。

【0033】

クリーニングユニット35は、ヘッド31をクリーニングするためのものである。このクリーニングユニット35は、ホームポジション(以下、HPと呼ぶ。図2参照)に設けられており、キャップと、吸引ポンプ等とを有している。ヘッド31(キャリッジ42)が搬送方向(前後方向)に移動してHPに位置すると、ヘッド31の下面(ノズル面)に不図示のキャップが密着するようになっている。このようにキャップが密着した状態で吸引ポンプが作動すると、ヘッド31内のインクが、増粘したインクや紙粉と共に吸引される。このようにして、目詰まりしたノズルが不吐出状態から回復することによってヘッドのクリーニングが完了する。

【0034】

キャリッジユニット40は、ヘッド31を移動させるためのものである。このキャリッジユニット40は、搬送方向(前後方向)に延びるキャリッジガイドレール41と(図2に二点鎖線で示す)、キャリッジガイドレール41に沿って搬送方向(前後方向)へ往復移動可能に支持されたキャリッジ42と、不図示のモーターとを有する。

【0035】

キャリッジ42は、不図示のモーターの駆動により、ヘッド31と一体となって搬送方向(前後方向)へ移動するよう構成されている。また、キャリッジ42には、列方向(左右方向)に延びる不図示のヘッドガイドレールが設けられており、ヘッド31は、前記モーターの駆動により、当該ヘッドガイドレールに沿って列方向(左右方向)へ移動するよう構成されている。

【0036】

巻き取りユニット70は、搬送ユニット20により送られたロール紙S(画像記録済みのロール紙)を巻き取るためのものである。この巻き取りユニット70は、送り出しローラー27から送られたロール紙Sを、前側上方から巻き掛けて後斜め下方へ搬送するための中継ローラー71と、回転可能に支持され中継ローラー71から送られたロール紙Sを巻き取る巻き取り駆動軸72と、を有している。

【0037】

コントローラー60は、プリンター1の制御を行なうための制御ユニットである。このコントローラー60は、図1に示すように、インターフェース部61A、61Bと、CPU62と、メモリー63と、ユニット制御回路64と、を有している。インターフェース部61Aは、外部装置であるホストコンピューター110とプリンター1との間でデータの送受信を行なうためのものである。インターフェース部61Bは、インクカートリッジホルダーユニット3のサブ基板300との間でデータの送受信を行なうためのものである。CPU62は、プリンター1全体の制御を行なうための演算処理装置である。メモリー63は、CPU62のプログラムを格納する領域や作業領域等を確保するためのものである。CPU62は、メモリー63に格納されているプログラムに従ってユニット制御回路64により各ユニットを制御する。なお、コントローラー60は、メイン基板200上に設けられている。

【0038】

検出器群50は、プリンター1内の状況を監視するものであり、例えば、搬送ローラーに取り付けられて媒体の搬送などの制御に利用されるロータリー式エンコーダー、搬送される媒体の有無を検出する用紙検出センサー、キャリッジ42(又はヘッド31)の搬送方向(前後方向)の位置を検出するためのリニア式エンコーダーなどがある。

【0039】

電源ユニット80は、装置本体2に固設されている。そして、不図示の電気コード等を介してコンセント等に接続されている。なお、電源ユニット80は、電源のオンオフ操作を行う電源スイッチ81を備えている。この電源スイッチ81がオン状態になることにより、プリンター1に電力が供給される。

【0040】

≪プリンター1の動作例について≫

上述した通り、本実施形態に係るプリンター1には、列方向(左右方向)にノズルが並んだノズル列を有するヘッド31が設けられている。そして、コントローラー60が、当該ヘッド31を搬送方向(前後方向)に移動させながら、ノズルからインクを吐出させ、搬送方向(前後方向)に沿ったラスタラインを形成することにより、印刷領域R上のロール紙Sの部位に1ページ分の画像記録を行なう。

【0041】

ここで、本実施形態に係るコントローラー60は、複数パス(2パス、4パス等)の印刷を実行する。すなわち、列方向における画像の解像度を高くするために、パス毎に列方向におけるヘッド31の位置を少しずつ変えて印刷を行なう。本実施形態では4パスの印刷を実行することとする。また、画像形成方法としては、例えば、公知のインターレース(マイクロウィーブ)印刷が実行される。

【0042】

これについて、図3を用いてより具体的に説明する。図3は、4パスで印刷するケースにおいて各パスで形成されるラスタラインを示した模式図である。

【0043】

図3の左側にはヘッド31のノズル列(ノズル)が表されており、当該ヘッド31(ノズル列)が搬送方向に移動しながらノズルからインクが吐出されることにより、ラスタラインが形成される。図に表されているヘッド31(ノズル列)の列方向における位置は、1パス目のときの位置であり、かかる位置を維持したままヘッド31(ノズル列)が搬送方向に移動すると、1パス目の印刷が実行され、図に表された5つのラスタライン(図の右端にパス1と書かれているラスタラインL1)が形成される。

【0044】

そして、次に、ヘッド31(ノズル列)が列方向に移動して、移動後の位置を維持したままヘッド31(ノズル列)が搬送方向に移動すると、2パス目の印刷が実行され、図に表された4つのラスタライン(右端にパス2と書かれているラスタラインL2)が形成される。なお、インターレース(マイクロウィーブ)印刷が採用されているため、前記ラスタラインL1に隣接するラスタラインL2は、ラスタラインL1を形成するインクが吐出されたノズルとは異なるノズルから吐出されたインクにより形成されることとなる。そのため、ヘッド31(ノズル列)の列方向への移動距離は、ノズル間距離(例えば、1/180インチ)の1/4分(1/180×1/4=1/720インチ)ではなく、これより大きな距離となる。

【0045】

以下、同様の動作が行なわれることにより、3パス目、4パス目の印刷が実行されて、図に表された残りのラスタライン(右端にパス3と書かれているラスタラインL3及びパス4と書かれているラスタラインL4)が形成される。このように、4パスでラスタラインが形成されることにより、列方向における画像の解像度を4倍(=720÷180)の解像度とすることが可能となる。

【0046】

なお、本実施形態においては、所謂双方向印刷が行なわれる。すなわち、1パス、3パス目の印刷が行なわれるときのヘッド31(ノズル列)の移動方向と2パス、4パス、目の印刷が行なわれるときのヘッド31(ノズル列)の移動方向は互いに逆方向となる(後に、詳述する)。

【0047】

以下では、プリンター1の動作例としてプリンター1の画像形成動作(換言すれば、インク吐出動作)を説明するが、上述した4パスで印刷する図4のケースを例に挙げて説明する(以下の説明で、図3も随時参照する)。

【0048】

<プリンター1の画像形成動作例について>

ここでは、プリンター1の印刷動作例について、図3、図4を用いて説明する。図4は、ヘッドの移動を説明するための模式図である。印刷動作を説明する前に、先ず、図4(の見方)について説明する。

【0049】

図4には、印刷処理(すなわち、画像形成に係る一連の処理)が行なわれている間に、ヘッドがどのように移動するかが示されている。ここでは、説明を分かり易くするために、ヘッド31(およびノズル列)の数は、複数個ではなく1つであることとして、説明を行なう。

【0050】

ヘッド31は、便宜上、丸印で表され(図には、大きな丸と小さな丸があるが、双方の区別に意味は無い)、ヘッドの移動が矢印で表されている。ここで、図中前後方向に向いた矢印は、搬送方向におけるヘッドの移動を表し、左右方向に向いた矢印は、列方向におけるヘッドの移動を表している。また、各矢印には、S1〜S10の符号が付けられているが、これは、以降の印刷処理の説明で用いられるステップ番号である。

【0051】

また、パス1乃至パス4が付されているステップ番号があるが、これらのステップ番号はインクが吐出されることにより画像形成動作が実行されるステップを表している。

【0052】

以下、図3、図4を参照しつつ、印刷処理について説明する。なお、当該印刷処理は、主としてコントローラー60により実現される。特に、本実施形態においては、メモリー63に格納されたプログラムをCPU62が処理することにより実現される。そして、このプログラムは、以下に説明する各種の動作を行なうためのコードから構成されている。

【0053】

前述した間欠的なロール紙Sの搬送が行なわれてロール紙Sが停止すると、印刷領域R上のロール紙Sの部位に1ページ分の画像形成を行なうための印刷処理が開始される。

【0054】

先ず、コントローラー60は、キャリッジ42(すなわち各ヘッド)をHP位置から往方向(ロール紙Sが搬送される方向において、上流側から下流側へ向かう方向)へ移動させる(ステップS1)。

【0055】

コントローラー60は、ヘッド31の往方向への移動を継続しつつ、ヘッドにインクを吐出させて、1パス目の印刷を実行する(ステップS2)。そして、このことにより、図6に示されたラスタラインL1(パス1のラスタライン)が形成される。

【0056】

ヘッドが第一折り返し位置へ至ると、コントローラー60は、ヘッドを列方向へ移動させる(ステップS3)。本実施形態においては、前記距離dだけヘッドを移動させる。

【0057】

その後、コントローラー60は、ヘッドを復方向(ロール紙Sが搬送される方向において、下流側から上流側へ向かう方向)へ移動させながら、ヘッドにインクを吐出させて、2パス目の印刷を実行する(ステップS4)。そして、このことにより、図3に示されたラスタラインL2(パス2のラスタライン)が形成される。

【0058】

ヘッドが第二折り返し位置へ至ると、コントローラー60は、ヘッドを列方向へ移動させる(ステップS5)。本実施形態においては、前記距離dだけヘッドを移動させる。

【0059】

次に、コントローラー60は、ステップS2乃至ステップS4の処理と同じ処理をさらになう(ステップS6乃至ステップS8)。この処理において、3パス目の印刷(ステップS6)により図6に示されたラスタラインL3(パス3のラスタライン)が、4パス目の印刷(ステップS8)により図6に示されたラスタラインL4(パス4のラスタライン)が、それぞれ形成される。コントローラー60は、ヘッドの列方向における位置を元に戻す(ステップS9)。すなわち、ステップS3、S5、S7でヘッドが移動した方向とは逆方向に、距離3dだけヘッドを移動させる。

【0060】

そして、コントローラー60は、ヘッドをHP位置へ移動させることにより(ステップS10)、1ページ分の画像形成を行なうための印刷処理を終了させる。なお、本実施形態では、1ページ分の画像形成を4パスで行うこととしたがこれには限られない。例えば2パスで1ページ分の画像形成を行うようにしてもよい。また、本実施形態ではインターレース(マイクロウィーブ)印刷を行うこととしたがこれには限られない。例えばバンド印刷を行ってもよい。

【0061】

≪インクカートリッジホルダーユニットの構成例について≫

図1に示すように、インクカートリッジホルダーユニット3は、サブ基板300とカートリッジホルダー部310を備えている。

【0062】

<カートリッジホルダー部について>

カートリッジホルダー部310には、インクが収容されたインクカートリッジを着脱可能に装着するためのカートリッジホルダーH1〜H4が設けられている。なお、インク、及び、インクが収容されたインクカートリッジは、プリンター1の消耗品に相当する。このカートリッジホルダーH1〜H4には、各種類(色)のインクのインクカートリッジがそれぞれ着脱可能に装着される。なお、カートリッジホルダーH1〜H4は、ヘッド31の各色のノズル列と対応している。そして、カートリッジホルダーH1〜H4に装着された各インクカートリッジのインクは不図示のインク供給チューブを通じてバルブユニット34に供給され、さらに不図示のインク供給チューブを介してヘッド31に供給される。例えば、カートリッジホルダーH1がヘッド31のシアンのノズル列に対応している場合、カートリッジホルダーH1にシアンのインクカートリッジが装着されることによって、シアンのノズル列にシアンのインクが供給されることになる。

【0063】

こうして、ヘッド31は各カートリッジホルダーから供給されたインクを吐出する。本実施形態では、前述したようにイエロー(Y)、マゼンタ(M)、シアン(C)、ブラック(K)の4色のインクを使用して画像を印刷する。すなわちカートリッジホルダーH1〜H4には、上記4色のインクカートリッジの何れかが装着される。

【0064】

なお、インクカートリッジ(不図示)は、内部にインクを収容するカートリッジ本体、カートリッジ本体に備えつけられた基板、当該基板に設けられた記憶素子(CSICともいう)を備えている。CSICは、インクカートリッジをカートリッジホルダー部310のカートリッジホルダーH1〜H4に装着したときに、プリンター1(コントローラー60)との間で各種のデータを授受するための素子であり、不揮発性メモリー(例えばフラッシュメモリー)など、データの格納可能な素子により構成される。CSICには、例えば、当該カートリッジに収容されているインクの色、濃度、粘性などの特性を示す情報や、各種の印刷制御プログラムなどが記憶されている。また、インクカートリッジには、この記憶素子と電気的に接続された複数の接続端子が露出して形成されている。

【0065】

これに対して、カートリッジホルダー部310のカートリッジホルダーH1〜H4には、インクカートリッジを装着したときにインクカートリッジの複数の接続端子とそれぞれ電気的に接続するための複数の接続端子(不図示)が形成されている。

【0066】

インクカートリッジがカートリッジホルダー部310のカートリッジホルダーH1〜H4に装着されると、インクカートリッジからプリンターの装置本体2のヘッド31へのインクの供給が可能になる。また、インクカートリッジがカートリッジホルダーH1〜H4に装着されるとインクカートリッジの複数の接続端子と、カートリッジホルダーH1〜H4の複数の接続端子とがそれぞれ電気的に接続して、サブ基板300を介して、プリンター1のメイン基板200(コントローラー60)とインクカートリッジの記憶素子との間においてデータの授受が可能となる。

【0067】

このように、インクカートリッジホルダーユニット3のカートリッジホルダー部310にインクカートリッジが装着されることにより、メイン基板200(コントローラー60)は、サブ基板300を介してインクカートリッジの記憶素子からのデータの読み出しや、インクカートリッジの記憶素子へのデータの書き込みを行うことができる。

【0068】

<サブ基板について>

本実施形態のプリンター1のような大型のプリンターの場合、メイン基板200とカートリッジホルダー部310の位置がかなり離れていることがある。この場合、仮に、メイン基板200とカートリッジホルダー部310とを直接電気的に接続すると、信号の伝送距離が非常に長くなってしまう。このため、例えば、信号がなまってしまい、正確な通信が行えなくなるおそれがある。そこで本実施形態では、メイン基板200とカートリッジホルダー部310との間にサブ基板300を設けている。そして、メイン基板200からサブ基板300を介して、カートリッジの記憶素子(CSIC)の読み取りや書き込みを行うようにしている。このようにサブ基板300を設けることによって、メイン基板200とインクカートリッジのCSIC間の信号の伝達の安定化を図っている。

【0069】

図5はサブ基板300の構成の一例を示すブロック図である。

図5に示すサブ基板300は、マイクロコントローラー400を備えている。またサブ基板300は、メイン基板200及びカートリッジホルダー部310と通信するための不図示のインターフェース部などを有している。本実施形態ではサブ基板300は、インクカートリッジホルダーユニット3に設けられている。言い換えると、メイン基板200とは一定距離離れた位置であり、カートリッジホルダー部310(言い換えるとインクカートリッジ)とは近い(上記一定距離より短い)位置に設けられている。

【0070】

≪マイクロコントローラーの構成について≫

図6は、第1実施形態におけるマイクロコントローラー400の構成の一例を示すブロック図である。

図6に示すように、第1実施形態のマイクロコントローラー400は、内部発振回路401と、インバーター402と、PLL回路403と、セレクタ404と、CPUコア405と、異常検出回路406と、選択制御回路407とを備えている。

【0071】

内部発振回路401は、不図示の内部発振器により所定周波数のクロック信号(以下、第1クロック信号とよぶ)を生成して出力する。

インバーター402は、サブ基板300(マイクロコントローラー400の外部)に設けられた外部発振素子330とともに基準クロックを生成する発振回路を構成している。なお、外部発振素子330には、例えば水晶発振子が用いられる。

【0072】

PLL(Phase Locked Loop)回路403は、外部発振素子330の発振クロック(基準クロック)に基づいてクロック信号(以下、第2クロック信号とよぶ)を生成する。なお、PLL回路403の詳細については後述する。

【0073】

セレクタ404は、内部発振回路401から出力される第1クロック信号、及び、PLL回路403から出力される第2クロック信号の何れかを選択し、システムクロックとしてCPUコア405に供給する。

【0074】

CPUコア405は、プログラムによって様々な数値計算や情報処理、機器制御などを行うものであり、論理演算や制御を行う演算回路415と、プログラムやデータ等を記憶する記憶回路416(例えば、フラッシュメモリーやRAM)を有している。また、記憶回路416は、設定レジスタ417、及び、ステータスレジスタ418を有している。

【0075】

異常検出回路406は、PLL回路403で生成される第2クロック信号の異常(クロック周波数の異常など)の有無を検出するためのものである。なお、異常検出回路406の詳細については後述する。

【0076】

選択制御回路407は、異常検出回路406の検出結果及び設定レジスタ417の設定に基づいて、セレクタ404の選択を制御する(換言すると、クロック信号の切り換えを制御する)ためのものである。なお、本実施形態において、セレクタ404と選択制御回路407は、選択回路に相当する。

【0077】

<PLL回路について>

図6に示すように、PLL回路403は、1/n分周回路410と、位相比較回路411と、ローパスフィルター(以下、LPFともいう)412と、電圧制御発振器(以下、VCOともいう)413と、1/m分周回路414とを有している。

【0078】

1/n分周回路410は、外部発振素子330の発振クロック(基準クロック)を1/n分周した周波数信号(第3クロック信号とよぶ)を生成し、位相比較回路411に出力する。例えば、n=10の場合、入力周波数が10MHzのとき出力周波数は1MHzになる。

【0079】

位相比較回路411は、1/n分周回路410の出力である第3クロック信号と、PLL回路403(より具体的には、後述する1/m分周回路414)の出力である第2クロック信号を位相比較し、その位相差を電圧(または電流)の形で出力する。

【0080】

LPF412は、例えば、抵抗とコンデンサとを有するRC積分回路であり、位相比較回路411の出力電圧の交流成分(高周波成分)をコンデンサで除去することにより平滑化する。

【0081】

VCO(Voltage Controlled Oscillator)413は、入力電圧に応じた周波数信号(パルス信号)を出力するものである。例えば、入力電圧が高いほど、高い周波数の信号を出力し、入力電圧が低いほど低い周波数の信号を出力する。このように、VCO413は、LPF412からの電圧に対応する発振周波数の周波数信号を生成して、1/m分周回路414に出力する。尚、VCO413としては、不図示の水晶発振器やリチウムタンタレート(LiTaO3)を用いた発振器等を適用することが可能である。

【0082】

1/m分周回路414は、1/n分周回路410と同様の構成の回路であり、VCO413の出力信号を1/m分周したクロック信号(第2クロック信号)を生成し、セレクタ404及び位相比較回路411に出力する。

【0083】

次にPLL回路403の動作について説明する。外部から入力される基準信号に基づいた1/n分周回路410の出力(第3クロック信号)と1/m分周回路414の出力(第2クロック信号)との比較信号との位相比較が位相比較回路411で行なわれる。そして、位相比較回路411は、この位相差成分をパルス状の位相差信号として出力する。

【0084】

次に、この位相差信号は、LPF412により高周波成分が遮断されてVCO413に入力される。VCO413は入力電圧に応じた周波数信号(パルス信号)を出力し、その周波数信号は1/m分周回路414で分周されて第2クロック信号として出力されるとともに、位相比較回路411にフィードバック(帰還ループ)される。

【0085】

このように、PLL回路403は、外部の基準クロックに基づいて第2クロック信号を生成する。なお、第2クロック信号は、1/n分周回路410及び1/m分周回路414の設定(すなわち「n」と「m」の値の設定)によって、必要な周波数に定めることが可能である。本実施形態では、このPLL回路403で生成される第2クロック信号をメインクロックとして使用することとしている。

【0086】

<異常検出回路について>

図7は第1実施形態における異常検出回路406の一例を示すブロック図である。

第1実施形態の異常検出回路406は、上限電圧コンパレーター421と、下限電圧コンパレーター422と、論理和回路(OR回路)423とを有している。

【0087】

上限電圧コンパレーター421の非反転入力(+端子:不図示)には、VCO413への入力電圧が印加され、反転入力(−端子:不図示)には上限電圧が印加される。そして、上限電圧コンパレーター421は、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも高ければハイレベル(以下、Hレベルともいう)の電圧を出力する。言い換えると、VCO413への入力電圧が上限電圧よりも高ければHレベルの電圧を出力する。一方、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも低ければローレベル(以下、Lレベルともいう)の電圧を出力する。

【0088】

下限電圧コンパレーター422の非反転入力(+端子:不図示)には、下限電圧が印加され、反転入力(−端子:不図示)にはVCO413への入力電圧が印加される。そして、下限電圧コンパレーター422は、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも高ければHレベルの電圧を出力する。言い換えると、VCO413への入力電圧が下限電圧よりも低ければHレベルの電圧を出力する。一方、非反転入力(+端子)の電圧が反転入力(−端子)の電圧よりも低ければLレベルの電圧を出力する。

【0089】

論理和回路423は、上限電圧コンパレーター421と下限電圧コンパレーター422の出力の少なくとも一つがHレベルであればHレベルを出力し、上限電圧コンパレーター421と下限電圧コンパレーター422の出力が共にLレベルであればLレベルを出力する。

【0090】

以上の構成により、異常検出回路406の出力がHレベルのときには、上限電圧と下限電圧の少なくとも一方に異常が発生していることになる。一方、異常検出回路406の出力がLレベルのときには上限電圧と下限電圧の何れにも異常が発生していないことになる。このように第1実施形態の異常検出回路406は、VCO413への入力電圧をモニターしている。そして、その出力レベルがHレベルかLレベルかによって、第2クロック信号に異常が発生しているか否かを判断することができる。

【0091】

<選択制御回路について>

セレクタ404には、内部発振回路401から出力されるクロック信号(第1クロック信号)と、PLL回路403から出力されるクロック信号(第2クロック信号)の2つのクロック信号が入力される。そしてセレクタ404は、その2つのクロック信号の何れかを選択して、CPUコア405のシステムクロックとして出力する。

【0092】

前述したように、選択制御回路407は、セレクタ404のクロック信号の選択を制御するためのものである。

本実施形態の選択制御回路407は、電源起動時(すなわち電源スイッチ81がオン状態となったとき)にはセレクタ404が第1クロック信号を選択するように制御する。

【0093】

その後、異常検出回路406の出力がLレベルのとき(すなわち異常が発生していないと検出されたとき)には、選択制御回路407は、ファームウェアの設定(設定レジスタ417の設定)に応じたタイミングで、セレクタ404が第2クロック信号を選択するようにセレクタ404の選択の切り換えを行う。

【0094】

一方、異常検出回路406の出力がHレベルのとき(すなわち異常が発生していると検出されたき)には、選択制御回路407は、ファームウェアの設定(設定レジスタ417の設定)にかかわらず、セレクタ404の選択の切り換えを行わないようにする。すなわち、セレクタ404は第1クロック信号を選択したままであり、第2クロック信号への切り換えは行わない。

【0095】

また、このとき、ステータスレジスタ418は、異常検出回路406の出力がHレベルであることを記憶し、演算回路415に対して、セレクタ404によるシステムクロックの切り換えが行われなかったことを知らせる。これにより、演算回路415は、例えば、クロック信号が切り換わらない場合に応じた対応を行う。

【0096】

<起動時の動作について>

本実施形態のマイクロコントローラー400には、プログラミングデバッグを行っているか否かを示すフラグ(以下、デバッグフラグとよぶ)が用意されている。そして、異常検出回路406は、デバッグフラグが立っている場合(オン状態の場合)のみに有効になるように設定されている。なお、デバッグとは、コンピュータープログラム中のバグ・欠陥などのエラーを発見及び修正し、動作を仕様通りのものとするための作業である。例えば、装置(プリンター1)の開発時に、1/n分周回路410と1/m分周回路における分周の比(nとmの値)を間違うと、異常に低い周波数になったり、異常に高い周波数になったりしてVCO413が発振しなかったり、あるいはPLL回路403の後段の演算回路415が正常に動作しなかったりする。この状態でセレクタ404の選択をPLL回路403の出力側に切り換えるとデバッグがハングした状態となり、以後、デバッグ作業ができなくなるおそれがある。また、この設定(nとmの値の設定)ミスに気づくのに時間を要し、デバッグ効率を落とすおそれもある。本実施形態では、デバッグ時にステータスレジスタ418を確認することにより、第2クロック信号の異常を気付きやすくすることができ、デバッグの効率を向上させることができる。

【0097】

図8は、プリンター1の起動時におけるマイクロコントローラー400の動作の一例を示すフロー図である。

まず、電源がON(すなわち電源スイッチ81がオン状態)になると(S101)、マイクロコントローラー400の選択制御回路407は、セレクタ404に第1クロック信号を選択させる(S102)。すなわち、システムクロックとして第1クロック信号がセレクタ404からCPUコア405に供給される。

【0098】

次にマイクロコンコントローラー400は、デバッグフラグが立っているか否かを判断する(S103)。デバッグフラグが立っていない場合(S103でNO)、マイクロコントローラー400は、異常検出回路406を無効にし(S104)、選択制御回路407は、ファームウェアの設定(具体的には設定レジスタ417の設定)に応じてセレクタ404の選択を第1クロック信号から第2クロック信号に切り換えさせる(S105)

一方、ステップS103でデバッグフラグが立っていると判断した場合(S103でYES)、マイクロコントローラー400は、異常検出回路406を有効にし(S106)、異常が検出されたか否かの判断を行う(S107)。異常が検出されなければ(S107でNO)、具体的には異常検出回路406の出力がLレベルである場合は、ステップS105を実行する。

【0099】

異常が検出された場合(S107でYES)、具体的には異常検出回路406の出力がHレベルである場合は、選択制御回路407は、ファームウェアの設定にかかわらず、セレクタ404に第1クロック信号から第2クロック信号への切り換えを実行させない(S108)。また、CPUコア405のステータスレジスタ418には、異常検出回路406の出力がHレベルであること(すなわち第2クロック信号に異常が検出されたこと)が記憶される(S109)。このステータスレジスタ418の情報により、演算回路415は、第1クロック信号から第2クロック信号に切り換えられていないことを認識する。そして、演算回路415は、例えば、クロック信号が切り換わらない場合に応じた対応を行う。

【0100】

上述したように、本実施形態では、異常検出回路406はプログラミングデバッグ時のみに有効になるようにしている。この異常検出回路406によってデバッグ時の異常の原因が特定しやすくなり、デバック効率を向上させることができる。

【0101】

以上説明したように、本実施形態のマイクロコントローラー400は、クロック信号が供給されて動作するCPUコア405の演算回路415と、第1クロック信号を生成する内部発振回路401と、基準クロックに基づいて第2クロック信号を生成するPLL回路403と、第2クロック信号の異常を検出する異常検出回路406と、第1クロック信号と第2クロック信号のいずれかを選択してCPUコア405にシステムクロックとして供給する選択回路(セレクタ404及び選択制御回路407)を備えている。

【0102】

そして、選択回路は、電源起動時にはシステムクロックとして第1クロック信号を選択し、異常検出回路406で異常が検出されない場合には、ファームウェアの設定に応じて第1クロック信号から第2クロック信号に切り換えている。一方、異常検出回路406で異常が検出された場合には、ファームウェアの設定に関わらずに、第1クロック信号から第2クロック信号への切り換えを行わないようにしている。また、ステータスレジスタ418は、異常検出回路406で異常が検出されたことを示す情報(言い換えると、クロック信号の切り換えが行われなかったことを示す情報)を記憶し、演算回路415に知らせている。

【0103】

こうすることにより、例えば、プログラミングデバッグ時などにおいてnの値、及び、mの値の設定ミスにより第2クロック信号が異常周波数となった場合においても、第1クロック信号から第2クロック信号への切り換えが行われないので、誤動作を確実に防止することができる。また、ステータスレジスタ418を確認することにより第2クロック信号が異常になっていることを認識できる。このため、デバッグ時の異常の原因が特定しやすくなり、デバック効率を向上させることができる。

【0104】

===第2実施形態===

図9は、第2実施形態におけるマイクロコントローラー400の構成を示すブロック図である。なお、図8において、第1実施形態(図6)と同じ構成の部分には同一符号を付し説明を省略する。第2実施形態のマイクロコントローラー400は、異常検出回路406´を有している。異常検出回路406´には、1/m分周回路414の出力(すなわちク第2ロック信号)が入力されている。

【0105】

図10は、第2実施形態における異常検出回路406´の構成の一例を示すブロック図である。

図に示すように、異常検出回路406´は、Dフロップフロップ(D-FF)431、遅延回路432、トグル動作確認回路433を有している。なお、これらの回路は、第2クロック信号のモニター用ロジック回路を構成している。

【0106】

Dフリップフロップ431のD入力には、遅延回路432の出力が入力される。またCKには、1/m分周回路414の出力(すなわち第2クロック信号)が入力される。第2クロック信号が立ち上がったときに、D入力が「Hレベル」ならば、Q出力は「Hレベル」となり、/Qは「Lレベル」となる。一方、第2クロック信号が立ち上がったときに、D入力が「Lレベル」ならば、Q出力は「Lレベル」となり、/Qは1「Hレベル」となる

遅延回路432は、入力される信号の波形を変えずに伝達に所定時間の遅れ(遅延)を作る回路である。

【0107】

トグル動作確認回路433には、内部発振回路401の出力(すなわち第1クロック信号)と、遅延回路432の出力が入力される。そして、トグル動作確認回路433は、遅延回路432の出力が第1クロック信号の周期で、HレベルとLレベルに切り換わっているか(トグル動作をしているか)を検出する。例えば、第2クロック信号として、Hレベル又はLレベルの一方が連続して続くようになると、CPUコア405のシステムクロックとして機能しないことになる。よって、Hレベル又はLレベルが所定回数連続することによって、第2クロック信号が異常であることを検出することができる。トグル動作確認回路433は、第1クロック信号の周期で遅延回路432の出力がHレベルあるいはLレベルが連続して続く場合は異常を示す信号(例えばHレベルの信号)を出力する。一方、HレベルとLレベルに切り換わっている場合(すばわちトグル動作を確認した場合)は異常が検出されなかったことを示す信号(例えばLレベルの信号)を出力する。このトグル動作確認回路433の出力が異常検出回路406´の出力になる。

【0108】

なお、プリンター1の起動時の動作については第1実施形態(図8)と同様であるので説明を省略する。

【0109】

===その他の実施の形態===

一実施形態としてのプリンター等を説明したが、上記の実施形態は、本発明の理解を容易にするためのものであり、本発明を限定して解釈するためのものではない。本発明は、その趣旨を逸脱することなく、変更、改良され得ると共に、本発明にはその等価物が含まれることは言うまでもない。特に、以下に述べる実施形態であっても、本発明に含まれるものである。

【0110】

<プリンターについて>

前述の実施形態では、ラテラル式のプリンターであったが、これには限らない。例えば、被印刷媒体を搬送方向に搬送する搬送動作と、ヘッドを移動方向(搬送方向と交差する方向)に移動しつつ、ヘッドのノズルからインクを吐出して被印刷媒体にドットを形成するドット形成動作とを繰り返して画像を形成するプリンター(いわゆるシリアルプリンター)であってもよい。また、例えば、被印刷媒体を搬送方向に搬送しつつ搬送経路上に設けられたヘッドからUVインクを吐出して画像を形成するプリンター(いわゆるラインプリンター)であってもよい。

【0111】

<ノズルについて>

前述の実施形態では、圧電素子(ピエゾ素子)を用いてインクを吐出していた。しかし、液体を吐出する方式は、これに限られるものではない。例えば、熱によりノズル内に泡を発生させる方式など、他の方式を用いてもよい。

【0112】

<サブ基板について>

前述の実施形態では、1つのサブ基板が4つのインクカートリッジ(言い換えるとCSIC)と対応していたが、これには限らない。例えば3つ以下のインクカートリッジと対応していてもよいし、5つ以上のインクカートリッジと対応していてもよい。また、サブ基板(マイクロコントローラー400)の数が2つ以上であってもよい。

【0113】

<異常検出回路について>

異常検出回路406(406´)の構成は、前述した実施形態には限られず、第2クロック信号の異常を検出することが出来れば、他の構成のものを用いてもよい。

【符号の説明】

【0114】

1 プリンター、2 装置本体、3 インクカートリッジホルダーユニット、

10 給送ユニット、18 巻軸、19 中継ローラー、

20 搬送ユニット、21 中継ローラー、22 中継ローラー、

23 第一搬送ローラー、23a 第一駆動ローラー、23b 第一従動ローラー、

24 第二搬送ローラー、24a 第二駆動ローラー、24b 第二従動ローラー、

25 反転ローラー、26 中継ローラー、27 送り出しローラー、29 プラテン、

30 ヘッドユニット、31 ヘッド、34 バルブユニット、

35 クリーニングユニット、40 キャリッジユニット、41 ガイドレール、

42 キャリッジ、50 検出器群、60 コントローラー、

61 インターフェース部、62 CPU、63 メモリー、64 ユニット制御回路、

70 巻き取りユニット、71 中継ローラー、72 巻き取り駆動軸、

80 電源ユニット、81 電源スイッチ、

110 ホストコンピューター、200 メイン基板、300 サブ基板、

310 カートリッジホルダー部、330 外部発振素子、

400 マイクロコントローラー、401 内部発振回路、402 インバーター、

403 PLL回路、404 セレクタ、405 CPUコア、406 異常検出回路、

407 選択制御回路、410 1/n分周回路、411 位相比較回路、

412 LPF、413 VCO、414 1/m分周回路、

415 演算回路、416 記憶回路、417 設定レジスタ、

418 ステータスレジスタ、421 上限電圧コンパレーター、

422 下限電圧コンパレーター、423 論理和回路、431 Dフリップフロップ、

432 遅延回路、433 トグル動作確認回路

【特許請求の範囲】

【請求項1】

クロック信号が供給されて動作する演算回路と、

第1クロック信号を生成する発振回路と、

基準クロックに基づいて第2クロック信号を生成するPLL回路と、

前記第2クロック信号の異常を検出する異常検出回路と、

前記第1クロック信号と前記第2クロック信号のいずれかを選択して前記演算回路に供給する選択回路であって、

電源起動時には前記第1クロック信号を選択し、

前記異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて前記第1クロック信号から前記第2クロック信号に切り換え、

前記異常検出回路で異常が検出された場合には、前記ファームウェアの設定に関わらずに、前記第1クロック信号から前記第2クロック信号への切り換えを行わない選択回路と、

前記異常検出回路で異常が検出された場合に、前記第1クロック信号から前記第2クロック信号への切り換えが行われなかったことを前記演算回路に知らせるステータスレジスタと、

を備えたことを特徴とするマイクロコントローラー。

【請求項2】

請求項1に記載のマイクロコントローラーであって、

前記異常検出回路は、前記PLL回路の電圧制御発振器への入力電圧をモニターすることによって前記第2クロック信号の異常の有無を検出する、

ことを特徴とするマイクロコントローラー。

【請求項3】

請求項1に記載のマイクロコントローラーであって、

前記異常検出回路は、前記第2クロック信号が入力されるモニター用ロジック回路を有し、前記モニター用ロジック回路が正常に動作するか否かに基づいて前記第2クロック信号の異常の有無を検出する、

ことを特徴とするマイクロコントローラー。

【請求項4】

請求項1〜3の何れかに記載のマイクロコントローラーであって、

当該マイクロコントローラーのプログラミング処理中に発生したエラーをデバッグすることを示すデバッグフラグがオン状態の場合のみ、前記異常検出回路を有効にする、

ことを特徴とするマイクロコントローラー。

【請求項5】

請求項1〜4の何れかに記載のマイクロコントローラーであって、

被印刷媒体に画像を形成する画像形成装置に設けられている、

ことを特徴とするマイクロコントローラー。

【請求項6】

請求項5に記載のマイクロコントローラーであって、

前記画像形成装置は、

メイン基板と、

前記メイン基板とは所定距離離れた位置であり、前記画像形成装置の取替え可能な消耗品とは前記所定距離未満の近い位置に配置されたサブ基板と、

を有し、

前記サブ基板に設けられていることを特徴とするマイクロコントローラー。

【請求項7】

請求項6に記載のマイクロコントローラーであって、

前記メイン基板からの指示に応じて、前記消耗品に設けられた記憶素子に対してデータの読み書きをさせる、

ことを特徴とするマイクロコンコントローラー。

【請求項1】

クロック信号が供給されて動作する演算回路と、

第1クロック信号を生成する発振回路と、

基準クロックに基づいて第2クロック信号を生成するPLL回路と、

前記第2クロック信号の異常を検出する異常検出回路と、

前記第1クロック信号と前記第2クロック信号のいずれかを選択して前記演算回路に供給する選択回路であって、

電源起動時には前記第1クロック信号を選択し、

前記異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて前記第1クロック信号から前記第2クロック信号に切り換え、

前記異常検出回路で異常が検出された場合には、前記ファームウェアの設定に関わらずに、前記第1クロック信号から前記第2クロック信号への切り換えを行わない選択回路と、

前記異常検出回路で異常が検出された場合に、前記第1クロック信号から前記第2クロック信号への切り換えが行われなかったことを前記演算回路に知らせるステータスレジスタと、

を備えたことを特徴とするマイクロコントローラー。

【請求項2】

請求項1に記載のマイクロコントローラーであって、

前記異常検出回路は、前記PLL回路の電圧制御発振器への入力電圧をモニターすることによって前記第2クロック信号の異常の有無を検出する、

ことを特徴とするマイクロコントローラー。

【請求項3】

請求項1に記載のマイクロコントローラーであって、

前記異常検出回路は、前記第2クロック信号が入力されるモニター用ロジック回路を有し、前記モニター用ロジック回路が正常に動作するか否かに基づいて前記第2クロック信号の異常の有無を検出する、

ことを特徴とするマイクロコントローラー。

【請求項4】

請求項1〜3の何れかに記載のマイクロコントローラーであって、

当該マイクロコントローラーのプログラミング処理中に発生したエラーをデバッグすることを示すデバッグフラグがオン状態の場合のみ、前記異常検出回路を有効にする、

ことを特徴とするマイクロコントローラー。

【請求項5】

請求項1〜4の何れかに記載のマイクロコントローラーであって、

被印刷媒体に画像を形成する画像形成装置に設けられている、

ことを特徴とするマイクロコントローラー。

【請求項6】

請求項5に記載のマイクロコントローラーであって、

前記画像形成装置は、

メイン基板と、

前記メイン基板とは所定距離離れた位置であり、前記画像形成装置の取替え可能な消耗品とは前記所定距離未満の近い位置に配置されたサブ基板と、

を有し、

前記サブ基板に設けられていることを特徴とするマイクロコントローラー。

【請求項7】

請求項6に記載のマイクロコントローラーであって、

前記メイン基板からの指示に応じて、前記消耗品に設けられた記憶素子に対してデータの読み書きをさせる、

ことを特徴とするマイクロコンコントローラー。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−114589(P2013−114589A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−262479(P2011−262479)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]