マイクロコンピュータおよびデータ処理装置

【課題】マイクロコンピュータにおいて、半導体素子としてのデッドコピーを防止し、また、プログラムやデータなどのメモリの内容を読み取ることができないように秘匿する。

【解決手段】マイクロコンピュータのプログラムおよびデータを、半導体チップが製造された結果である物理的特性に基づいて生成された識別情報を暗号鍵として暗号化する。マイクロコンピュータは、物理的特性に基づいて識別情報を生成する手段とその識別手段を暗号鍵としてプログラムやデータを暗号化する暗号エンジンを備えるものであって、暗号化に用いた暗号鍵の値の読み出しが禁止されている。

【解決手段】マイクロコンピュータのプログラムおよびデータを、半導体チップが製造された結果である物理的特性に基づいて生成された識別情報を暗号鍵として暗号化する。マイクロコンピュータは、物理的特性に基づいて識別情報を生成する手段とその識別手段を暗号鍵としてプログラムやデータを暗号化する暗号エンジンを備えるものであって、暗号化に用いた暗号鍵の値の読み出しが禁止されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロコンピュータおよびそれを含むデータ処理装置に関し、特にそのプログラム及びデータを秘匿するために有効な技術に関する。

【背景技術】

【0002】

半導体集積回路の模倣、即ち回路などのレイアウト情報のデッドコピーは、半導体メーカーのみならずユーザにとっても重大な問題である。特にマイクロコンピュータでは、回路の情報の他、メモリに格納されたプログラムの秘匿が重要である。

【0003】

従来、メモリに格納するプログラムやデータを暗号化して秘匿する技術が採用されているが、その場合には、暗号鍵の管理が問題となる。暗号鍵を半導体上に記憶すると、暗号鍵を含めてデッドコピーされた場合にプログラムによるマイコン動作の模倣を許してしまう。暗号鍵を製品上に記憶せず製造工程で管理することで、秘匿性は向上するが、製造工程からの情報漏洩があれば模倣を許してしまうという問題がある。

【0004】

一方、半導体のデッドコピーを防止するために有効な技術として、半導体の物理的特性に基づいて固有の識別情報を生成する技術が提案されている(特許文献1乃至3)。半導体が製造された結果であるトランジスタの電流や寄生容量などの物理的特性に基づいて識別情報を生成するので、回路パターンをデッドコピーしても、製造バラツキによって生成される識別情報が異なることとなり、実質的に固有の識別情報を生成することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−147088号公報

【特許文献2】特開2010−226603号公報

【特許文献3】特開2005−244356号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1乃至3には、この識別情報を使って認証を行ったり、通信における情報の暗号化の暗号鍵として利用する応用技術が開示されている。しかし、マイクロコンピュータのデッドコピーを防止し、そのプログラムおよびデータを秘匿するために、このような識別情報を利用する応用技術については開示されていない。

【0007】

本発明の目的は、マイクロコンピュータにおいて、半導体素子としてのデッドコピーを防止し、またメモリの内容を読み取ることができないように秘匿する技術を提供することである。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、CPUとメモリインターフェースとデバッグインターフェースと暗号エンジンと暗号鍵生成回路とを含んで単一半導体チップ上に形成されたマイクロコンピュータであって、暗号鍵生成回路は、半導体の物理的な特性に基づいて乱数IDを生成して暗号エンジンに入力し、暗号エンジンはその乱数IDを暗号鍵として入力されたデータを暗号化し復号する機能を備え、乱数IDの読み出しが禁止されている。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、本願発明に係るマイクロコンピュータによれば、半導体素子としてのデッドコピーを防止し、またメモリの内容を読み取ることができないように秘匿することができる。

【図面の簡単な説明】

【0013】

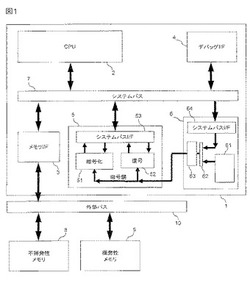

【図1】図1は、本発明の一実施形態に係るマイクロコンピュータと、それを含むデータ処理装置の構成を示すブロック図である。

【図2】図2は、図1に示したデータ処理装置において、プログラムダウンロードを行う場合のデータの流れを説明する図である。

【図3】図3は、図1に示したデータ処理装置において、データリードを行う場合のデータの流れを説明する図である。

【図4】図4は、図1に示したデータ処理装置において、データライトを行う場合のデータの流れを説明する図である。

【図5】図5は、本発明の別の実施形態に係るマイクロコンピュータであって、個別IDを格納した記憶素子をさらに含むものと、それを含むデータ処理装置の構成を示すブロック図である。

【発明を実施するための形態】

【0014】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0015】

〔1〕<暗号鍵読み出し禁止>

本発明の代表的な実施の形態に係るマイクロコンピュータ(1)は、CPU(2)とメモリインターフェース(3)とデバッグインターフェース(4)と暗号エンジン(5)と暗号鍵生成回路(6)とを含んで単一半導体チップ上に形成されたマイクロコンピュータであって、以下のように構成されている。

【0016】

前記CPUと前記メモリインターフェースと前記デバッグインターフェースと前記暗号エンジンと前記暗号鍵生成回路とがシステムバス(7)に接続されている。

【0017】

前記暗号鍵生成回路は、前記半導体集の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力する。

【0018】

前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記システムバスを介して入力されたデータを暗号化して前記システムバスを介して出力する暗号化処理機能と、前記システムバスを介して入力されたデータを復号して前記システムバスを介して出力する復号処理機能とを備える。

【0019】

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記デバッグインターフェースからの読み出しが禁止されている。

【0020】

これによれば、CPUで実行されるプログラムが、半導体の物理的な特性に基づいて生成された乱数IDを暗号鍵として用いて暗号化してメモリに格納されているので、マイクロコンピュータがデッドコピーされたときであっても、模倣品で生成される乱数ID即ち暗号鍵は、真正品で暗号化に用いられた暗号鍵の値と異なるものとなる。したがって、模倣品ではプログラムを復号して実行することができないため、マイクロプロセッサのデッドコピーを防止することができる。

【0021】

またこれによれば、本実施形態のマイクロコンピュータは、真正品で生成された乱数IDの読み出しが、CPUとデバッグインターフェースからのアクセスが禁じられているので、不正コピーに関与した者のみならず設計者や製造者でさえも暗号鍵の値を知ることができない。したがって、メモリに格納されたプログラムおよびデータを復号することはできないため、メモリの内容を読み取ることができないように秘匿することができる。

【0022】

〔2〕<デバッグ時、暗号鍵に代わる値の設定>

項1記載のマイクロコンピュータにおいて、前記暗号エンジンは、前記暗号鍵生成回路の出力する前記乱数IDに代えて、前記デバッグインターフェースから前記システムバスを介して入力される値を暗号鍵として、暗号化処理を行う前記暗号化処理機能と復号処理を行う前記復号処理機能を備える。

【0023】

これにより、チップデバッグのときに、暗号エンジンに任意の暗号鍵を与えることができるので、暗号エンジンがいかなる暗号鍵の値が入力されても正しく機能することを確認し、また暗号エンジンおよびシステム全体をデバッグすることができる。また、出荷前テストときには、任意の数の暗号鍵の値を入力することができ、暗号エンジンを構成する素子の故障(欠陥)検出率を十分高めることができる。

【0024】

〔3〕<システム:暗号化と復号を伴うメモリアクセス>

本発明の代表的な実施の形態に係るデータ処理装置は、項1又は2記載のマイクロコンピュータと、前記メモリインターフェースに接続され、前記マイクロコンピュータによってアクセスされるメモリ(8、9)とを含んで構成され、前記メモリは、前記暗号エンジンによって前記暗号化処理を施されたデータを格納し、前記マイクロコンピュータは、前記暗号化されたデータを前記メモリから読み出し、前記暗号エンジンによって復号する。

【0025】

これにより、マイクロコンピュータは、アクセス可能なメモリを拡張したデータ処理装置を提供することができる。

【0026】

〔4〕<オンチップメモリ>

項3記載のデータ処理装置であって、前記メモリが前記マイクロコンピュータと同一の半導体チップに形成されている。

【0027】

これにより、メモリとマイクロコンピュータの間の信号を外部で観測することができなくなり、メモリに格納されたプログラムやデータがより安全に秘匿される。

【0028】

〔5〕<プログラムのダウンロードと復号>

項3または4記載のデータ処理装置は、前記デバッグインターフェースから入力されたプログラムを前記暗号エンジンに転送し、前記暗号エンジンは、前記プログラムに暗号化処理を施し、暗号化されたプログラムを前記メモリインターフェースを介して前記メモリに格納する、プログラムダウンロード機能を備える。また、データ処理装置は、その暗号化され前記メモリに格納されたプログラムを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力する機能を備える。

【0029】

これにより、マイクロコンピュータが製造された後、即ち、暗号鍵生成回路が生成する乱数ID(暗号鍵の値)が確定した後で、マイクロコンピュータ内の暗号エンジンを用いて、プログラムを暗号化するので、暗号鍵の値は、不正にコピーをする者にはもちろん設計者や製造者にさえも知られることはなく、よってメモリに格納されたプログラムが安全に秘匿される。

【0030】

〔6〕<CPUのメモリアクセス時の暗号処理>

項3または4記載のデータ処理装置は、前記CPUがライトコマンドを与えられたとき、書き込みデータを、前記暗号エンジンに転送し、前記暗号エンジンは、前記書き込みデータに暗号化処理を施し、暗号化された書き込みデータを前記メモリインターフェースを介して前記メモリに格納する、データライト動作を実行する機能を備える。また、そのデータ処理装置は、前記CPUがリードコマンドを与えられたとき、暗号化され前記メモリに格納されたデータを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力するデータリード動作を実行する機能を備える。

【0031】

これにより、メモリ(8、9)に格納されるデータが暗号化され、安全に秘匿される。

【0032】

〔7〕<個別IDの付加>

項1もしくは項2記載のマイクロコンピュータ、または、項3、4、5もしくは6記載のデータ処理装置において、前記システムバス上に、前記CPUおよびまたは前記デバッグインターフェースから読み出し可能に構成された記憶手段に個別ID(11)を格納した。

【0033】

これにより、例えば、個別ID(11)を暗号の共有鍵とし、前記乱数IDを秘密鍵として使う通信に応用することができる。上述してきたとおり、前記乱数IDは、マイクロコンピュータから読み出す手段がないので、秘密鍵を盗まれて通信が傍受される危険がなく、よって通信の内容が安全に秘匿される。

【0034】

〔8〕<上位概念>

単一半導体チップ上に形成されたマイクロコンピュータであって、CPU(2)と前記マイクロコンピュータ(1)の外部との間で入出力動作を行う外部インターフェース(3、4)と暗号エンジン(5)と暗号鍵生成回路(6)とを含む。

【0035】

前記暗号鍵生成回路は、前記半導体の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力し、前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記外部インターフェースから入力されたデータを暗号化する暗号化処理機能と、前記暗号化されたデータを復号する復号処理機能とを備えている。

【0036】

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記外部インターフェースからの外部出力が禁止されている。

【0037】

これにより、マイクロコンピュータにおいて、半導体素子としてのデッドコピーを防止し、またメモリの内容を読み取ることができないように秘匿することができる。

【0038】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0039】

図1は、本発明の一実施形態に係るマイクロコンピュータと、それを含むデータ処理装置の構成を示すブロック図である。

【0040】

本発明の代表的な実施の形態に係るマイクロコンピュータ1は、CPU2と、マイクロコンピュータの外部との間で入出力動作を行う外部インターフェースとして代表的に示されたメモリインターフェース3及びデバッグインターフェース4と、暗号エンジン5と暗号鍵生成回路6と、を含んで単一半導体チップ上に形成されたマイクロコンピュータである。CPU2とメモリインターフェース3とデバッグインターフェース4と暗号エンジン5と暗号鍵生成回路6とがシステムバス7に接続されている。暗号鍵生成回路6は、半導体の物理的な特性に基づいて乱数IDを生成して暗号エンジン5に入力する。暗号エンジンは、暗号化処理機能51と復号処理機能52とを備え、入力された前記乱数IDを暗号鍵として、前記システムバスを介して入力されたデータを暗号化してシステムバスを介して出力し、システムバスを介して入力されたデータを復号してシステムバスを介して出力する。マイクロコンピュータ1において、暗号鍵生成回路が出力する乱数IDに対するCPU2の制御に基づく読み出しと、デバッグインターフェース3に代表される外部インターフェースからの読み出しが禁止されている。

【0041】

CPU2は、中央処理装置(Central Processing Unit)であって、プログラムをデコードして演算処理やメモリアクセスを実行する。マイクロコンピュータ内外のメモリやレジスタ、その他機能ブロックのデータ入出力ポートには、CPUのメモリ空間のアドレスが割り付けられており、CPUはそのアドレスを指定して、それらにアクセスする。

【0042】

メモリインターフェース3は、システムバスとその外側のメモリを互いに接続するインターフェースである。システムバス7に直接接続されたメモリ以外に、メモリインターフェースを介してメモリを接続することができる。接続するメモリには上記メモリ空間内の別のアドレスが割り付けられており、CPUからはそのアドレスを指定してアクセスすることができる。メモリは、NANDフラッシュメモリ、NORフラッシュメモリなどの汎用フラッシュデバイスを含む不揮発性メモリ、もしくは、SDRAM、各種DDR型SDRAM、SRAMなどの揮発性メモリ、またはそれらを複数接続したメモリ群で構成することができ、複数接続する場合には、一般には、メモリインターフェース3に接続した外部バス10が用いられる。

【0043】

デバッグインターフェース4は、プログラムデバッグの際に、例えばデバッガを外付けして、デバッグプログラムを供給し、マイクロコンピュータ内外のメモリやレジスタ、その他機能ブロックのデータ入出力ポートの値を読み出し、あるいは、必要に応じて書き込むこともできるように構成されている。デバッグを行うときには、CPU2がデバッグインターフェースの指示に従って動作するいわゆるエミュレーション動作をする。デバッグインターフェース4から直接にレジスタ、その他機能ブロックのデータ入出力ポートへのアクセス手段を設けてもよい。

【0044】

半導体の出荷前の良品選別試験は、半導体の入出力端子にテストパターンを与えて、半導体を構成するトランジスタなどの素子の良否を判定して、欠陥のある半導体を不良品として排除するものである。回路ブロックごとの欠陥(不良)検出率を選別試験として十分な高さまで高めるためには、試験対象の回路ブロックに任意の値を入力し、その出力を読み出すことが有効であり、前記デバッグインターフェースを使った動作が使われることも多い。

【0045】

暗号エンジン5は、暗号化機能51と復号機能52を備えており、入力された暗号鍵を使ってデータを暗号化し、または復号する。暗号化または復号の対象となるデータは、システムバス7から暗号エンジン5内のシステムバスインターフェース53を介して与えられ、処理の結果はシステムバスインターフェース53を介してシステムバス7に出力される。

【0046】

暗号鍵生成回路6は、乱数ID生成回路61を含んで構成されており、乱数ID生成回路61は、半導体集積回路であるマイクロコンピュータ1を製造した結果である物理的な特性に基づいて乱数IDを生成する回路である。例えば、特許文献1または2記載の技術を採用することができる。生成された乱数IDは、セレクタ62とレジスタ63を介して暗号鍵として暗号エンジン5に入力されている。レジスタ63の出力は、暗号エンジン5にのみ接続されていて、システムバス7への出力回路を備えていない。一般には、前記したようにチップデバッグやシステムデバッグ、あるいは、出荷前の良品選別試験の際に、レジスタの値を読み出すことが求められるが、本願発明においては、この値は暗号の秘匿性を確保するために、絶対に知られてはならない値であるので、読み出し手段を備えていない。

【0047】

これにより、マイクロコンピュータ1は、CPU2で実行されるプログラムを暗号化してメモリに格納しておけば、デッドコピーされた場合にそのプログラムを実行することができず、また、オフラインでもそのプログラムを復号することができない。その理由は以下の通りである。半導体の物理的な特性に基づいて生成された乱数IDを用いているので、回路が同一であっても物理的特性の製造バラツキによって、その乱数IDは異なる。プログラムを暗号化するための暗号鍵にその乱数IDを用いているので、真正なチップで生成された暗号鍵とデッドコピーされたチップで復号に用いる暗号鍵は異なるものとなる。したがって、暗号化したときのマイクロコンピュータでなければ、メモリに格納されたプログラムを正しく復号することができず、よってデッドコピーされたマイクロコンピュータではデッドコピーされたプログラムを実行することができない。

【0048】

また、暗号鍵である乱数IDを読み出すことができないので、不正コピーを目的とする者のみならず正当なユーザやマイクロコンピュータの設計者や製造者自身でさえも、暗号鍵の値を知ることができない。したがって、暗号化されたメモリの内容を読み取ったとしても、正しく復号することはできず、よって、メモリの内容を読み取ることができないように秘匿することができる。

【0049】

上記実施形態には、デバッグ時、暗号鍵に代わる値の設定を可能とする回路を付加することができる。図1は既にその回路手段を含めたブロック図であるので、これを参照して説明する。

【0050】

前記マイクロコンピュータにおいてさらに、暗号エンジン5は、暗号鍵生成回路6の出力する乱数IDに代えて、デバッグインターフェース4からシステムバスを介して入力される値を暗号鍵として、暗号化処理を行う暗号化処理機能と復号処理を行う復号処理機能を備える。

【0051】

暗号鍵生成回路6のセレクタ62は、乱数ID生成回路61とシステムバス7からシステムバスインターフェース64を介して入力される信号とを切り替え、その出力をレジスタ63へ書き込む。通常動作では、レジスタ63には乱数ID生成回路61で生成された乱数IDが書き込まれ、暗号エンジンへ暗号鍵として接続しているが、システムバス側が選択されることにより、任意の値を暗号鍵として暗号エンジン5に入力することができる。

【0052】

これにより、チップデバッグのときに、暗号エンジンに任意の暗号鍵を与えることができるので、暗号エンジンがいかなる暗号鍵の値が入力されても正しく機能することを確認し、また暗号エンジンおよびシステム全体をデバッグすることができる。また、出荷前テストのときには、任意の数の暗号鍵の値を入力することができ、よって暗号エンジンを構成する素子の故障(欠陥)検出率を十分高めることができる。

【0053】

以上の実施形態では、乱数IDの読み出しは、CPUからだけでなくデバッグインターフェースからのアクセスであっても禁止する構成とした。しかし、デバッグの際にデバッグインターフェースからの乱数IDの読み出しを許す構成とし、量産品ではデバッグインターフェースを物理的に使用できないようにすることもできる。具体的その方法としては、例えば、外部ピンへのワイヤボンディングを行わない、デバッグインターフェースへの制御信号を、量産時に切断するなどの手段があげられる。

【0054】

マイクロコンピュータ1に、メモリインターフェース3に接続した外部バス10に不揮発性メモリ8と揮発性メモリ9とを接続したデータ処理装置の実施の形態について説明する。図1はそのブロック構成を示しているので、図1を参照する。不揮発性メモリは、例えば、NANDフラッシュメモリ、NORフラッシュメモリなどの汎用フラッシュデバイスである。揮発性メモリは、例えばSDRAM、各種DDR型SDRAM、SRAMなどである。不揮発性メモリ8と揮発性メモリ9は、暗号エンジン5によって暗号化処理を施されたデータを格納し、マイクロコンピュータ1は、暗号化されたデータをそれらメモリ8、9から読み出し、暗号エンジン5によって復号する。

【0055】

これにより、不揮発性メモリ8と揮発性メモリ9に格納されたプログラムやデータが秘匿される。

【0056】

不揮発性メモリ8と揮発性メモリ9は、いずれか1個であってもよい。その場合には外部バスはメモリインターフェースといずれか1個のメモリの間を直結する信号線であってよい。また、不揮発性メモリ8と揮発性メモリ9は、一方または両方の複数の組み合わせであってもよい。

【0057】

さらに、上記のようなメモリまたはメモリ群をマイクロコンピュータ1と同一の半導体チップに形成してもよい。これにより、メモリとマイクロコンピュータの間の信号を観測することが困難になり、メモリに格納されたプログラムやデータがより安全に秘匿される。

【0058】

「メモリインターフェース」の語は、同一半導体チップの内部と外部のインターフェースであることを指すものとは限らず、階層化されたバスの間をブリッジするものであって、どのような回路ブロックをCPUと同一のチップ内に形成するかは、これとは独立の設計パラメータである。メモリインターフェースをさらに付加して、バスを多段に階層化することも、本発明の技術思想に反するものではなく自由に採用することができる。

【0059】

プログラムのダウンロードについて説明する。本発明のマイクロコンピュータは、暗号化したプログラムを格納したROMを予め作成して接続するようなシステムには適さない。暗号鍵の値は、マイクロコンピュータを製造した時点でその個体固有に確定し、それを読み出さないで暗号化することによって、プログラムやデータの秘匿を担保しているからである。したがって、マイクロコンピュータを製造した後で、プログラムをダウンロードする必要がある。

【0060】

図2は、本発明の一実施形態に係るマイクロコンピュータを搭載したデータ処理装置において、プログラムダウンロードを行う場合の、データの流れを説明する図である。開発後のプログラムをデバッグインターフェース4から入力し、プログラムを暗号エンジン5に転送する(S1)。暗号エンジンは、転送されたプログラムに対し、物理的な特性に基づいて生成された乱数IDを暗号鍵として暗号化処理を施し、暗号化されたプログラムをメモリインターフェース3に転送する(S2)。メモリインターフェース3は暗号化されたプログラムを不揮発性メモリ8に格納する(S3)。S1は暗号化されていないプログラムデータであり、S2およびS3は暗号化された後のプログラムデータである。

【0061】

これにより、マイクロコンピュータが製造された後、即ち、暗号鍵生成回路が生成する乱数ID(暗号鍵の値)が確定した後で、マイクロコンピュータ内の暗号エンジンを用いて、プログラムを暗号化するので、暗号鍵の値は、不正にコピーをする者にはもちろん設計者や製造者にさえも知られることはなく、よってメモリに格納されたプログラムが安全に秘匿される。

【0062】

暗号化されたプログラムの不揮発性メモリからの読み出し方法を説明する。

【0063】

図3は、本発明の一実施形態に係るマイクロコンピュータを搭載したデータ処理装置において、データリードを行う場合の、データの流れを説明する図である。

【0064】

CPU2がリードコマンドを暗号エンジン5とメモリインターフェース3に送信する(S4)。メモリインターフェース3は、不揮発メモリ8または揮発性メモリ9から、暗号化されて格納されているプログラムを読み出す(S5)。メモリインターフェース3は、読み出したプログラムを暗号エンジン5に転送する(S6)。暗号エンジン5は乱数IDを暗号鍵としてプログラムを復号する。暗号エンジン5は、復号したプログラムをCPU2へ転送する(S7)。

【0065】

本発明のデータ処理装置においては、プログラムだけでなくデータも暗号化してメモリに格納することができる。メモリに格納されるデータには、秘匿を必要とする情報が含まれている場合があるので、これを同様の暗号化で秘匿するための技術である。

【0066】

暗号化されプログラムの不揮発性メモリへの書き込み方法を説明する。

【0067】

図4は、本発明の一実施形態に係るマイクロコンピュータを搭載したデータ処理装置において、データライトを行う場合の、データの流れを説明する図である。

【0068】

CPU2がライトコマンドを暗号エンジン5とメモリインターフェース3に送信する(S8)。CPU2はさらに暗号化すべきデータを暗号エンジン5に転送する(S9)。暗号エンジンは、転送されたデータに対し、物理的な特性に基づいて生成された乱数IDを暗号鍵として暗号化処理を施し、暗号化されたデータをメモリインターフェース3に転送する(S10)。メモリインターフェース3は暗号化されたデータを不揮発性メモリ8または揮発性メモリ9に書き込む(S11)。S9は暗号化されていないデータであり、S10およびS11は暗号化された後のデータである。

【0069】

これにより、メモリ8、9に格納されるデータが暗号化され、安全に秘匿される。

【0070】

本実施形態における「データ」は、ユーザデータなどプログラムが実行することによって参照あるいは操作されるデータには限られず、プログラムコードであってもよい。

【0071】

「ライトコマンド」、「リードコマンド」は、単一のライト命令、リード命令、あるいはストア命令、ロード命令などで、上記シーケンスをマイクロ命令で順次実行してもよいし、一連のシーケンスを実行するマクロ命令であってもよい。また、暗号化または復号を伴わないライトコマンドとリードコマンドを、さらに備えてもよい。

【0072】

本発明のマイクロコンピュータとデータ処理装置を、暗号化通信に利用する実施の形態について図5を参照して説明する。図5は、以上で説明してきたマイクロコンピュータ、または、データ処理装置に、さらに、システムバス7上に、CPUおよびまたはデバッグインターフェースから読み出し可能に構成された記憶手段に個別ID11を格納し、ネットワークインターフェース12を備えたものである。

【0073】

暗号鍵生成回路で生成される乱数IDを、これまでに説明した通りプログラムやデータの暗号化のための暗号鍵として使うとともに、伝送するデータを暗号化するための秘密鍵としても使用し、個別ID11を暗号の共有鍵として使用して行う通信に応用することができる。

【0074】

詳細には、送信する内容は、暗号鍵生成回路6の出力を秘密鍵、個別ID11を共有鍵として使用して暗号化し、ネットワークインターフェース12を介して送信し、ネットワークインターフェース12を介して受信した暗号文を、個別ID11を共有鍵として復号して読み取るものである。

【0075】

暗号鍵生成回路6の出力は上述してきたとおりの乱数IDで、マイクロコンピュータから読み出す手段がないので、本実施形態においては秘密鍵を盗まれて通信が傍受される危険がなく、よって通信の内容が安全に秘匿される。

【0076】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0077】

例えば、外部インターフェースとして、メモリインターフェースとデバッグインターフェースを示したが、この他、パラレルインターフェース、シリアルインターフェースなどであってもよいし、マイクロコンピュータは、メモリインターフェースとデバッグインターフェース以外の外部インターフェースをさらに備えてもよい。

【0078】

CPUの制御に基づく読み出しには、CPU以外をバスマスタとして機能する場合を含む。例えば、CPUがパラメータを設定し、動作を起動するDMAコントローラがこれに相当する。

【0079】

マイクロコンピュータは、揮発性、不揮発性を問わないメモリ、その他の回路ブロックを備えていてもよい。このとき、メモリには暗号化されたデータを格納する動作も、暗号化しないデータを格納する動作も、適宜選択して採用することができる。

【符号の説明】

【0080】

1 マイクロコンピュータ

2 CPU

3 メモリインターフェース

4 デバッグインターフェース

5 暗号エンジン

51 暗号化機能

52 復号機能

6 暗号鍵生成回路

61 乱数ID生成回路

62 セレクタ

63 レジスタ

7 システムバス

8 不揮発性メモリ

9 揮発性メモリ

10 外部バス

11 個別IDを格納する記憶素子

12 ネットワークインターフェース

S1〜S11 暗号化または復号を行う信号の流れ

【技術分野】

【0001】

本発明は、マイクロコンピュータおよびそれを含むデータ処理装置に関し、特にそのプログラム及びデータを秘匿するために有効な技術に関する。

【背景技術】

【0002】

半導体集積回路の模倣、即ち回路などのレイアウト情報のデッドコピーは、半導体メーカーのみならずユーザにとっても重大な問題である。特にマイクロコンピュータでは、回路の情報の他、メモリに格納されたプログラムの秘匿が重要である。

【0003】

従来、メモリに格納するプログラムやデータを暗号化して秘匿する技術が採用されているが、その場合には、暗号鍵の管理が問題となる。暗号鍵を半導体上に記憶すると、暗号鍵を含めてデッドコピーされた場合にプログラムによるマイコン動作の模倣を許してしまう。暗号鍵を製品上に記憶せず製造工程で管理することで、秘匿性は向上するが、製造工程からの情報漏洩があれば模倣を許してしまうという問題がある。

【0004】

一方、半導体のデッドコピーを防止するために有効な技術として、半導体の物理的特性に基づいて固有の識別情報を生成する技術が提案されている(特許文献1乃至3)。半導体が製造された結果であるトランジスタの電流や寄生容量などの物理的特性に基づいて識別情報を生成するので、回路パターンをデッドコピーしても、製造バラツキによって生成される識別情報が異なることとなり、実質的に固有の識別情報を生成することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−147088号公報

【特許文献2】特開2010−226603号公報

【特許文献3】特開2005−244356号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1乃至3には、この識別情報を使って認証を行ったり、通信における情報の暗号化の暗号鍵として利用する応用技術が開示されている。しかし、マイクロコンピュータのデッドコピーを防止し、そのプログラムおよびデータを秘匿するために、このような識別情報を利用する応用技術については開示されていない。

【0007】

本発明の目的は、マイクロコンピュータにおいて、半導体素子としてのデッドコピーを防止し、またメモリの内容を読み取ることができないように秘匿する技術を提供することである。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、CPUとメモリインターフェースとデバッグインターフェースと暗号エンジンと暗号鍵生成回路とを含んで単一半導体チップ上に形成されたマイクロコンピュータであって、暗号鍵生成回路は、半導体の物理的な特性に基づいて乱数IDを生成して暗号エンジンに入力し、暗号エンジンはその乱数IDを暗号鍵として入力されたデータを暗号化し復号する機能を備え、乱数IDの読み出しが禁止されている。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、本願発明に係るマイクロコンピュータによれば、半導体素子としてのデッドコピーを防止し、またメモリの内容を読み取ることができないように秘匿することができる。

【図面の簡単な説明】

【0013】

【図1】図1は、本発明の一実施形態に係るマイクロコンピュータと、それを含むデータ処理装置の構成を示すブロック図である。

【図2】図2は、図1に示したデータ処理装置において、プログラムダウンロードを行う場合のデータの流れを説明する図である。

【図3】図3は、図1に示したデータ処理装置において、データリードを行う場合のデータの流れを説明する図である。

【図4】図4は、図1に示したデータ処理装置において、データライトを行う場合のデータの流れを説明する図である。

【図5】図5は、本発明の別の実施形態に係るマイクロコンピュータであって、個別IDを格納した記憶素子をさらに含むものと、それを含むデータ処理装置の構成を示すブロック図である。

【発明を実施するための形態】

【0014】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0015】

〔1〕<暗号鍵読み出し禁止>

本発明の代表的な実施の形態に係るマイクロコンピュータ(1)は、CPU(2)とメモリインターフェース(3)とデバッグインターフェース(4)と暗号エンジン(5)と暗号鍵生成回路(6)とを含んで単一半導体チップ上に形成されたマイクロコンピュータであって、以下のように構成されている。

【0016】

前記CPUと前記メモリインターフェースと前記デバッグインターフェースと前記暗号エンジンと前記暗号鍵生成回路とがシステムバス(7)に接続されている。

【0017】

前記暗号鍵生成回路は、前記半導体集の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力する。

【0018】

前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記システムバスを介して入力されたデータを暗号化して前記システムバスを介して出力する暗号化処理機能と、前記システムバスを介して入力されたデータを復号して前記システムバスを介して出力する復号処理機能とを備える。

【0019】

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記デバッグインターフェースからの読み出しが禁止されている。

【0020】

これによれば、CPUで実行されるプログラムが、半導体の物理的な特性に基づいて生成された乱数IDを暗号鍵として用いて暗号化してメモリに格納されているので、マイクロコンピュータがデッドコピーされたときであっても、模倣品で生成される乱数ID即ち暗号鍵は、真正品で暗号化に用いられた暗号鍵の値と異なるものとなる。したがって、模倣品ではプログラムを復号して実行することができないため、マイクロプロセッサのデッドコピーを防止することができる。

【0021】

またこれによれば、本実施形態のマイクロコンピュータは、真正品で生成された乱数IDの読み出しが、CPUとデバッグインターフェースからのアクセスが禁じられているので、不正コピーに関与した者のみならず設計者や製造者でさえも暗号鍵の値を知ることができない。したがって、メモリに格納されたプログラムおよびデータを復号することはできないため、メモリの内容を読み取ることができないように秘匿することができる。

【0022】

〔2〕<デバッグ時、暗号鍵に代わる値の設定>

項1記載のマイクロコンピュータにおいて、前記暗号エンジンは、前記暗号鍵生成回路の出力する前記乱数IDに代えて、前記デバッグインターフェースから前記システムバスを介して入力される値を暗号鍵として、暗号化処理を行う前記暗号化処理機能と復号処理を行う前記復号処理機能を備える。

【0023】

これにより、チップデバッグのときに、暗号エンジンに任意の暗号鍵を与えることができるので、暗号エンジンがいかなる暗号鍵の値が入力されても正しく機能することを確認し、また暗号エンジンおよびシステム全体をデバッグすることができる。また、出荷前テストときには、任意の数の暗号鍵の値を入力することができ、暗号エンジンを構成する素子の故障(欠陥)検出率を十分高めることができる。

【0024】

〔3〕<システム:暗号化と復号を伴うメモリアクセス>

本発明の代表的な実施の形態に係るデータ処理装置は、項1又は2記載のマイクロコンピュータと、前記メモリインターフェースに接続され、前記マイクロコンピュータによってアクセスされるメモリ(8、9)とを含んで構成され、前記メモリは、前記暗号エンジンによって前記暗号化処理を施されたデータを格納し、前記マイクロコンピュータは、前記暗号化されたデータを前記メモリから読み出し、前記暗号エンジンによって復号する。

【0025】

これにより、マイクロコンピュータは、アクセス可能なメモリを拡張したデータ処理装置を提供することができる。

【0026】

〔4〕<オンチップメモリ>

項3記載のデータ処理装置であって、前記メモリが前記マイクロコンピュータと同一の半導体チップに形成されている。

【0027】

これにより、メモリとマイクロコンピュータの間の信号を外部で観測することができなくなり、メモリに格納されたプログラムやデータがより安全に秘匿される。

【0028】

〔5〕<プログラムのダウンロードと復号>

項3または4記載のデータ処理装置は、前記デバッグインターフェースから入力されたプログラムを前記暗号エンジンに転送し、前記暗号エンジンは、前記プログラムに暗号化処理を施し、暗号化されたプログラムを前記メモリインターフェースを介して前記メモリに格納する、プログラムダウンロード機能を備える。また、データ処理装置は、その暗号化され前記メモリに格納されたプログラムを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力する機能を備える。

【0029】

これにより、マイクロコンピュータが製造された後、即ち、暗号鍵生成回路が生成する乱数ID(暗号鍵の値)が確定した後で、マイクロコンピュータ内の暗号エンジンを用いて、プログラムを暗号化するので、暗号鍵の値は、不正にコピーをする者にはもちろん設計者や製造者にさえも知られることはなく、よってメモリに格納されたプログラムが安全に秘匿される。

【0030】

〔6〕<CPUのメモリアクセス時の暗号処理>

項3または4記載のデータ処理装置は、前記CPUがライトコマンドを与えられたとき、書き込みデータを、前記暗号エンジンに転送し、前記暗号エンジンは、前記書き込みデータに暗号化処理を施し、暗号化された書き込みデータを前記メモリインターフェースを介して前記メモリに格納する、データライト動作を実行する機能を備える。また、そのデータ処理装置は、前記CPUがリードコマンドを与えられたとき、暗号化され前記メモリに格納されたデータを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力するデータリード動作を実行する機能を備える。

【0031】

これにより、メモリ(8、9)に格納されるデータが暗号化され、安全に秘匿される。

【0032】

〔7〕<個別IDの付加>

項1もしくは項2記載のマイクロコンピュータ、または、項3、4、5もしくは6記載のデータ処理装置において、前記システムバス上に、前記CPUおよびまたは前記デバッグインターフェースから読み出し可能に構成された記憶手段に個別ID(11)を格納した。

【0033】

これにより、例えば、個別ID(11)を暗号の共有鍵とし、前記乱数IDを秘密鍵として使う通信に応用することができる。上述してきたとおり、前記乱数IDは、マイクロコンピュータから読み出す手段がないので、秘密鍵を盗まれて通信が傍受される危険がなく、よって通信の内容が安全に秘匿される。

【0034】

〔8〕<上位概念>

単一半導体チップ上に形成されたマイクロコンピュータであって、CPU(2)と前記マイクロコンピュータ(1)の外部との間で入出力動作を行う外部インターフェース(3、4)と暗号エンジン(5)と暗号鍵生成回路(6)とを含む。

【0035】

前記暗号鍵生成回路は、前記半導体の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力し、前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記外部インターフェースから入力されたデータを暗号化する暗号化処理機能と、前記暗号化されたデータを復号する復号処理機能とを備えている。

【0036】

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記外部インターフェースからの外部出力が禁止されている。

【0037】

これにより、マイクロコンピュータにおいて、半導体素子としてのデッドコピーを防止し、またメモリの内容を読み取ることができないように秘匿することができる。

【0038】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0039】

図1は、本発明の一実施形態に係るマイクロコンピュータと、それを含むデータ処理装置の構成を示すブロック図である。

【0040】

本発明の代表的な実施の形態に係るマイクロコンピュータ1は、CPU2と、マイクロコンピュータの外部との間で入出力動作を行う外部インターフェースとして代表的に示されたメモリインターフェース3及びデバッグインターフェース4と、暗号エンジン5と暗号鍵生成回路6と、を含んで単一半導体チップ上に形成されたマイクロコンピュータである。CPU2とメモリインターフェース3とデバッグインターフェース4と暗号エンジン5と暗号鍵生成回路6とがシステムバス7に接続されている。暗号鍵生成回路6は、半導体の物理的な特性に基づいて乱数IDを生成して暗号エンジン5に入力する。暗号エンジンは、暗号化処理機能51と復号処理機能52とを備え、入力された前記乱数IDを暗号鍵として、前記システムバスを介して入力されたデータを暗号化してシステムバスを介して出力し、システムバスを介して入力されたデータを復号してシステムバスを介して出力する。マイクロコンピュータ1において、暗号鍵生成回路が出力する乱数IDに対するCPU2の制御に基づく読み出しと、デバッグインターフェース3に代表される外部インターフェースからの読み出しが禁止されている。

【0041】

CPU2は、中央処理装置(Central Processing Unit)であって、プログラムをデコードして演算処理やメモリアクセスを実行する。マイクロコンピュータ内外のメモリやレジスタ、その他機能ブロックのデータ入出力ポートには、CPUのメモリ空間のアドレスが割り付けられており、CPUはそのアドレスを指定して、それらにアクセスする。

【0042】

メモリインターフェース3は、システムバスとその外側のメモリを互いに接続するインターフェースである。システムバス7に直接接続されたメモリ以外に、メモリインターフェースを介してメモリを接続することができる。接続するメモリには上記メモリ空間内の別のアドレスが割り付けられており、CPUからはそのアドレスを指定してアクセスすることができる。メモリは、NANDフラッシュメモリ、NORフラッシュメモリなどの汎用フラッシュデバイスを含む不揮発性メモリ、もしくは、SDRAM、各種DDR型SDRAM、SRAMなどの揮発性メモリ、またはそれらを複数接続したメモリ群で構成することができ、複数接続する場合には、一般には、メモリインターフェース3に接続した外部バス10が用いられる。

【0043】

デバッグインターフェース4は、プログラムデバッグの際に、例えばデバッガを外付けして、デバッグプログラムを供給し、マイクロコンピュータ内外のメモリやレジスタ、その他機能ブロックのデータ入出力ポートの値を読み出し、あるいは、必要に応じて書き込むこともできるように構成されている。デバッグを行うときには、CPU2がデバッグインターフェースの指示に従って動作するいわゆるエミュレーション動作をする。デバッグインターフェース4から直接にレジスタ、その他機能ブロックのデータ入出力ポートへのアクセス手段を設けてもよい。

【0044】

半導体の出荷前の良品選別試験は、半導体の入出力端子にテストパターンを与えて、半導体を構成するトランジスタなどの素子の良否を判定して、欠陥のある半導体を不良品として排除するものである。回路ブロックごとの欠陥(不良)検出率を選別試験として十分な高さまで高めるためには、試験対象の回路ブロックに任意の値を入力し、その出力を読み出すことが有効であり、前記デバッグインターフェースを使った動作が使われることも多い。

【0045】

暗号エンジン5は、暗号化機能51と復号機能52を備えており、入力された暗号鍵を使ってデータを暗号化し、または復号する。暗号化または復号の対象となるデータは、システムバス7から暗号エンジン5内のシステムバスインターフェース53を介して与えられ、処理の結果はシステムバスインターフェース53を介してシステムバス7に出力される。

【0046】

暗号鍵生成回路6は、乱数ID生成回路61を含んで構成されており、乱数ID生成回路61は、半導体集積回路であるマイクロコンピュータ1を製造した結果である物理的な特性に基づいて乱数IDを生成する回路である。例えば、特許文献1または2記載の技術を採用することができる。生成された乱数IDは、セレクタ62とレジスタ63を介して暗号鍵として暗号エンジン5に入力されている。レジスタ63の出力は、暗号エンジン5にのみ接続されていて、システムバス7への出力回路を備えていない。一般には、前記したようにチップデバッグやシステムデバッグ、あるいは、出荷前の良品選別試験の際に、レジスタの値を読み出すことが求められるが、本願発明においては、この値は暗号の秘匿性を確保するために、絶対に知られてはならない値であるので、読み出し手段を備えていない。

【0047】

これにより、マイクロコンピュータ1は、CPU2で実行されるプログラムを暗号化してメモリに格納しておけば、デッドコピーされた場合にそのプログラムを実行することができず、また、オフラインでもそのプログラムを復号することができない。その理由は以下の通りである。半導体の物理的な特性に基づいて生成された乱数IDを用いているので、回路が同一であっても物理的特性の製造バラツキによって、その乱数IDは異なる。プログラムを暗号化するための暗号鍵にその乱数IDを用いているので、真正なチップで生成された暗号鍵とデッドコピーされたチップで復号に用いる暗号鍵は異なるものとなる。したがって、暗号化したときのマイクロコンピュータでなければ、メモリに格納されたプログラムを正しく復号することができず、よってデッドコピーされたマイクロコンピュータではデッドコピーされたプログラムを実行することができない。

【0048】

また、暗号鍵である乱数IDを読み出すことができないので、不正コピーを目的とする者のみならず正当なユーザやマイクロコンピュータの設計者や製造者自身でさえも、暗号鍵の値を知ることができない。したがって、暗号化されたメモリの内容を読み取ったとしても、正しく復号することはできず、よって、メモリの内容を読み取ることができないように秘匿することができる。

【0049】

上記実施形態には、デバッグ時、暗号鍵に代わる値の設定を可能とする回路を付加することができる。図1は既にその回路手段を含めたブロック図であるので、これを参照して説明する。

【0050】

前記マイクロコンピュータにおいてさらに、暗号エンジン5は、暗号鍵生成回路6の出力する乱数IDに代えて、デバッグインターフェース4からシステムバスを介して入力される値を暗号鍵として、暗号化処理を行う暗号化処理機能と復号処理を行う復号処理機能を備える。

【0051】

暗号鍵生成回路6のセレクタ62は、乱数ID生成回路61とシステムバス7からシステムバスインターフェース64を介して入力される信号とを切り替え、その出力をレジスタ63へ書き込む。通常動作では、レジスタ63には乱数ID生成回路61で生成された乱数IDが書き込まれ、暗号エンジンへ暗号鍵として接続しているが、システムバス側が選択されることにより、任意の値を暗号鍵として暗号エンジン5に入力することができる。

【0052】

これにより、チップデバッグのときに、暗号エンジンに任意の暗号鍵を与えることができるので、暗号エンジンがいかなる暗号鍵の値が入力されても正しく機能することを確認し、また暗号エンジンおよびシステム全体をデバッグすることができる。また、出荷前テストのときには、任意の数の暗号鍵の値を入力することができ、よって暗号エンジンを構成する素子の故障(欠陥)検出率を十分高めることができる。

【0053】

以上の実施形態では、乱数IDの読み出しは、CPUからだけでなくデバッグインターフェースからのアクセスであっても禁止する構成とした。しかし、デバッグの際にデバッグインターフェースからの乱数IDの読み出しを許す構成とし、量産品ではデバッグインターフェースを物理的に使用できないようにすることもできる。具体的その方法としては、例えば、外部ピンへのワイヤボンディングを行わない、デバッグインターフェースへの制御信号を、量産時に切断するなどの手段があげられる。

【0054】

マイクロコンピュータ1に、メモリインターフェース3に接続した外部バス10に不揮発性メモリ8と揮発性メモリ9とを接続したデータ処理装置の実施の形態について説明する。図1はそのブロック構成を示しているので、図1を参照する。不揮発性メモリは、例えば、NANDフラッシュメモリ、NORフラッシュメモリなどの汎用フラッシュデバイスである。揮発性メモリは、例えばSDRAM、各種DDR型SDRAM、SRAMなどである。不揮発性メモリ8と揮発性メモリ9は、暗号エンジン5によって暗号化処理を施されたデータを格納し、マイクロコンピュータ1は、暗号化されたデータをそれらメモリ8、9から読み出し、暗号エンジン5によって復号する。

【0055】

これにより、不揮発性メモリ8と揮発性メモリ9に格納されたプログラムやデータが秘匿される。

【0056】

不揮発性メモリ8と揮発性メモリ9は、いずれか1個であってもよい。その場合には外部バスはメモリインターフェースといずれか1個のメモリの間を直結する信号線であってよい。また、不揮発性メモリ8と揮発性メモリ9は、一方または両方の複数の組み合わせであってもよい。

【0057】

さらに、上記のようなメモリまたはメモリ群をマイクロコンピュータ1と同一の半導体チップに形成してもよい。これにより、メモリとマイクロコンピュータの間の信号を観測することが困難になり、メモリに格納されたプログラムやデータがより安全に秘匿される。

【0058】

「メモリインターフェース」の語は、同一半導体チップの内部と外部のインターフェースであることを指すものとは限らず、階層化されたバスの間をブリッジするものであって、どのような回路ブロックをCPUと同一のチップ内に形成するかは、これとは独立の設計パラメータである。メモリインターフェースをさらに付加して、バスを多段に階層化することも、本発明の技術思想に反するものではなく自由に採用することができる。

【0059】

プログラムのダウンロードについて説明する。本発明のマイクロコンピュータは、暗号化したプログラムを格納したROMを予め作成して接続するようなシステムには適さない。暗号鍵の値は、マイクロコンピュータを製造した時点でその個体固有に確定し、それを読み出さないで暗号化することによって、プログラムやデータの秘匿を担保しているからである。したがって、マイクロコンピュータを製造した後で、プログラムをダウンロードする必要がある。

【0060】

図2は、本発明の一実施形態に係るマイクロコンピュータを搭載したデータ処理装置において、プログラムダウンロードを行う場合の、データの流れを説明する図である。開発後のプログラムをデバッグインターフェース4から入力し、プログラムを暗号エンジン5に転送する(S1)。暗号エンジンは、転送されたプログラムに対し、物理的な特性に基づいて生成された乱数IDを暗号鍵として暗号化処理を施し、暗号化されたプログラムをメモリインターフェース3に転送する(S2)。メモリインターフェース3は暗号化されたプログラムを不揮発性メモリ8に格納する(S3)。S1は暗号化されていないプログラムデータであり、S2およびS3は暗号化された後のプログラムデータである。

【0061】

これにより、マイクロコンピュータが製造された後、即ち、暗号鍵生成回路が生成する乱数ID(暗号鍵の値)が確定した後で、マイクロコンピュータ内の暗号エンジンを用いて、プログラムを暗号化するので、暗号鍵の値は、不正にコピーをする者にはもちろん設計者や製造者にさえも知られることはなく、よってメモリに格納されたプログラムが安全に秘匿される。

【0062】

暗号化されたプログラムの不揮発性メモリからの読み出し方法を説明する。

【0063】

図3は、本発明の一実施形態に係るマイクロコンピュータを搭載したデータ処理装置において、データリードを行う場合の、データの流れを説明する図である。

【0064】

CPU2がリードコマンドを暗号エンジン5とメモリインターフェース3に送信する(S4)。メモリインターフェース3は、不揮発メモリ8または揮発性メモリ9から、暗号化されて格納されているプログラムを読み出す(S5)。メモリインターフェース3は、読み出したプログラムを暗号エンジン5に転送する(S6)。暗号エンジン5は乱数IDを暗号鍵としてプログラムを復号する。暗号エンジン5は、復号したプログラムをCPU2へ転送する(S7)。

【0065】

本発明のデータ処理装置においては、プログラムだけでなくデータも暗号化してメモリに格納することができる。メモリに格納されるデータには、秘匿を必要とする情報が含まれている場合があるので、これを同様の暗号化で秘匿するための技術である。

【0066】

暗号化されプログラムの不揮発性メモリへの書き込み方法を説明する。

【0067】

図4は、本発明の一実施形態に係るマイクロコンピュータを搭載したデータ処理装置において、データライトを行う場合の、データの流れを説明する図である。

【0068】

CPU2がライトコマンドを暗号エンジン5とメモリインターフェース3に送信する(S8)。CPU2はさらに暗号化すべきデータを暗号エンジン5に転送する(S9)。暗号エンジンは、転送されたデータに対し、物理的な特性に基づいて生成された乱数IDを暗号鍵として暗号化処理を施し、暗号化されたデータをメモリインターフェース3に転送する(S10)。メモリインターフェース3は暗号化されたデータを不揮発性メモリ8または揮発性メモリ9に書き込む(S11)。S9は暗号化されていないデータであり、S10およびS11は暗号化された後のデータである。

【0069】

これにより、メモリ8、9に格納されるデータが暗号化され、安全に秘匿される。

【0070】

本実施形態における「データ」は、ユーザデータなどプログラムが実行することによって参照あるいは操作されるデータには限られず、プログラムコードであってもよい。

【0071】

「ライトコマンド」、「リードコマンド」は、単一のライト命令、リード命令、あるいはストア命令、ロード命令などで、上記シーケンスをマイクロ命令で順次実行してもよいし、一連のシーケンスを実行するマクロ命令であってもよい。また、暗号化または復号を伴わないライトコマンドとリードコマンドを、さらに備えてもよい。

【0072】

本発明のマイクロコンピュータとデータ処理装置を、暗号化通信に利用する実施の形態について図5を参照して説明する。図5は、以上で説明してきたマイクロコンピュータ、または、データ処理装置に、さらに、システムバス7上に、CPUおよびまたはデバッグインターフェースから読み出し可能に構成された記憶手段に個別ID11を格納し、ネットワークインターフェース12を備えたものである。

【0073】

暗号鍵生成回路で生成される乱数IDを、これまでに説明した通りプログラムやデータの暗号化のための暗号鍵として使うとともに、伝送するデータを暗号化するための秘密鍵としても使用し、個別ID11を暗号の共有鍵として使用して行う通信に応用することができる。

【0074】

詳細には、送信する内容は、暗号鍵生成回路6の出力を秘密鍵、個別ID11を共有鍵として使用して暗号化し、ネットワークインターフェース12を介して送信し、ネットワークインターフェース12を介して受信した暗号文を、個別ID11を共有鍵として復号して読み取るものである。

【0075】

暗号鍵生成回路6の出力は上述してきたとおりの乱数IDで、マイクロコンピュータから読み出す手段がないので、本実施形態においては秘密鍵を盗まれて通信が傍受される危険がなく、よって通信の内容が安全に秘匿される。

【0076】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0077】

例えば、外部インターフェースとして、メモリインターフェースとデバッグインターフェースを示したが、この他、パラレルインターフェース、シリアルインターフェースなどであってもよいし、マイクロコンピュータは、メモリインターフェースとデバッグインターフェース以外の外部インターフェースをさらに備えてもよい。

【0078】

CPUの制御に基づく読み出しには、CPU以外をバスマスタとして機能する場合を含む。例えば、CPUがパラメータを設定し、動作を起動するDMAコントローラがこれに相当する。

【0079】

マイクロコンピュータは、揮発性、不揮発性を問わないメモリ、その他の回路ブロックを備えていてもよい。このとき、メモリには暗号化されたデータを格納する動作も、暗号化しないデータを格納する動作も、適宜選択して採用することができる。

【符号の説明】

【0080】

1 マイクロコンピュータ

2 CPU

3 メモリインターフェース

4 デバッグインターフェース

5 暗号エンジン

51 暗号化機能

52 復号機能

6 暗号鍵生成回路

61 乱数ID生成回路

62 セレクタ

63 レジスタ

7 システムバス

8 不揮発性メモリ

9 揮発性メモリ

10 外部バス

11 個別IDを格納する記憶素子

12 ネットワークインターフェース

S1〜S11 暗号化または復号を行う信号の流れ

【特許請求の範囲】

【請求項1】

CPUとメモリインターフェースとデバッグインターフェースと暗号エンジンと暗号鍵生成回路とを含んで単一半導体チップ上に形成されたマイクロコンピュータであって、

前記CPUと前記メモリインターフェースと前記デバッグインターフェースと前記暗号エンジンと前記暗号鍵生成回路とがシステムバスに接続されており、

前記暗号鍵生成回路は、前記半導体の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力し、

前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記システムバスを介して入力されたデータを暗号化して前記システムバスを介して出力する暗号化処理機能と、前記システムバスを介して入力されたデータを復号して前記システムバスを介して出力する復号処理機能とを備え、

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記デバッグインターフェースからの読み出しが禁止されている、

マイクロコンピュータ。

【請求項2】

前記暗号エンジンは、前記暗号鍵生成回路の出力する前記乱数IDに代えて、前記デバッグインターフェースから前記システムバスを介して入力される値を暗号鍵として、暗号化処理を行う前記暗号化処理機能と復号処理を行う前記復号処理機能を備える、

請求項1記載のマイクロコンピュータ。

【請求項3】

請求項1記載のマイクロコンピュータと、前記メモリインターフェースに接続され、前記マイクロコンピュータによってアクセスされるメモリとを含んで構成され、

前記メモリは、前記暗号エンジンによって前記暗号化処理を施されたデータを格納し、

前記マイクロコンピュータは、前記暗号化されたデータを前記メモリから読み出し、前記暗号エンジンによって復号する、

データ処理装置。

【請求項4】

前記メモリが前記マイクロコンピュータと同一の半導体チップに形成されている、

請求項3記載のデータ処理装置。

【請求項5】

前記デバッグインターフェースから入力されたプログラムを前記暗号エンジンに転送し、前記暗号エンジンは、前記プログラムに暗号化処理を施し、暗号化されたプログラムを前記メモリインターフェースを介して前記メモリに格納する、プログラムダウンロード機能を備え、

暗号化され前記メモリに格納されたプログラムを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力する機能を備える、

請求項3記載のデータ処理装置。

【請求項6】

前記CPUがライトコマンドを与えられたとき、書き込みデータを、前記暗号エンジンに転送し、前記暗号エンジンは、前記書き込みデータに暗号化処理を施し、暗号化された書き込みデータを前記メモリインターフェースを介して前記メモリに格納する、データライト動作を実行する機能を備え、

前記CPUがリードコマンドを与えられたとき、暗号化され前記メモリに格納されたデータを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力するデータリード動作を実行する機能を備える、

請求項3記載のデータ処理装置。

【請求項7】

前記システムバス上に、前記CPUおよびまたは前記デバッグインターフェースから読み出し可能に構成され、個別IDを格納した記憶装置を有する、

請求項3記載のデータ処理装置。

【請求項8】

単一半導体チップ上に形成されたマイクロコンピュータであって、

CPUと前記マイクロコンピュータの外部との間で入出力動作を行う外部インターフェースと暗号エンジンと暗号鍵生成回路とを含み、

前記暗号鍵生成回路は、前記半導体の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力し、

前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記外部インターフェースから入力されたデータを暗号化する暗号化処理機能と、前記暗号化されたデータを復号する復号処理機能とを備え、

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記外部インターフェースからの外部出力が禁止されている、

マイクロコンピュータ。

【請求項1】

CPUとメモリインターフェースとデバッグインターフェースと暗号エンジンと暗号鍵生成回路とを含んで単一半導体チップ上に形成されたマイクロコンピュータであって、

前記CPUと前記メモリインターフェースと前記デバッグインターフェースと前記暗号エンジンと前記暗号鍵生成回路とがシステムバスに接続されており、

前記暗号鍵生成回路は、前記半導体の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力し、

前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記システムバスを介して入力されたデータを暗号化して前記システムバスを介して出力する暗号化処理機能と、前記システムバスを介して入力されたデータを復号して前記システムバスを介して出力する復号処理機能とを備え、

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記デバッグインターフェースからの読み出しが禁止されている、

マイクロコンピュータ。

【請求項2】

前記暗号エンジンは、前記暗号鍵生成回路の出力する前記乱数IDに代えて、前記デバッグインターフェースから前記システムバスを介して入力される値を暗号鍵として、暗号化処理を行う前記暗号化処理機能と復号処理を行う前記復号処理機能を備える、

請求項1記載のマイクロコンピュータ。

【請求項3】

請求項1記載のマイクロコンピュータと、前記メモリインターフェースに接続され、前記マイクロコンピュータによってアクセスされるメモリとを含んで構成され、

前記メモリは、前記暗号エンジンによって前記暗号化処理を施されたデータを格納し、

前記マイクロコンピュータは、前記暗号化されたデータを前記メモリから読み出し、前記暗号エンジンによって復号する、

データ処理装置。

【請求項4】

前記メモリが前記マイクロコンピュータと同一の半導体チップに形成されている、

請求項3記載のデータ処理装置。

【請求項5】

前記デバッグインターフェースから入力されたプログラムを前記暗号エンジンに転送し、前記暗号エンジンは、前記プログラムに暗号化処理を施し、暗号化されたプログラムを前記メモリインターフェースを介して前記メモリに格納する、プログラムダウンロード機能を備え、

暗号化され前記メモリに格納されたプログラムを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力する機能を備える、

請求項3記載のデータ処理装置。

【請求項6】

前記CPUがライトコマンドを与えられたとき、書き込みデータを、前記暗号エンジンに転送し、前記暗号エンジンは、前記書き込みデータに暗号化処理を施し、暗号化された書き込みデータを前記メモリインターフェースを介して前記メモリに格納する、データライト動作を実行する機能を備え、

前記CPUがリードコマンドを与えられたとき、暗号化され前記メモリに格納されたデータを前記メモリインターフェースを介して読み出し、前記暗号エンジンによって復号処理を施して前記CPUに入力するデータリード動作を実行する機能を備える、

請求項3記載のデータ処理装置。

【請求項7】

前記システムバス上に、前記CPUおよびまたは前記デバッグインターフェースから読み出し可能に構成され、個別IDを格納した記憶装置を有する、

請求項3記載のデータ処理装置。

【請求項8】

単一半導体チップ上に形成されたマイクロコンピュータであって、

CPUと前記マイクロコンピュータの外部との間で入出力動作を行う外部インターフェースと暗号エンジンと暗号鍵生成回路とを含み、

前記暗号鍵生成回路は、前記半導体の物理的な特性に基づいて乱数IDを生成して前記暗号エンジンに入力し、

前記暗号エンジンは、入力された前記乱数IDを暗号鍵として、前記外部インターフェースから入力されたデータを暗号化する暗号化処理機能と、前記暗号化されたデータを復号する復号処理機能とを備え、

前記暗号鍵生成回路が出力する前記乱数IDに対する前記CPUの制御に基づく読み出しと前記外部インターフェースからの外部出力が禁止されている、

マイクロコンピュータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−101442(P2013−101442A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−244072(P2011−244072)

【出願日】平成23年11月8日(2011.11.8)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月8日(2011.11.8)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]