マイクロコンピュータ及びメモリアクセスの制御方法

【課題】メモリアクセス制御の信頼性を向上させる。

【解決手段】マイクロコンピュータ1は、CPU10、CPU10で実行されるプログラムによるメモリ空間へのアクセス許可を示すメモリ保護情報を格納する保護設定レジスタ群11、保護設定レジスタ群11の設定内容を参照して、CPU10によるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御装置12、及び、CPU10が出力するリセット要求信号に基づいて、保護設定レジスタ群11に格納されたメモリ保護情報を一括して無効化するリセット装置16を備える。

【解決手段】マイクロコンピュータ1は、CPU10、CPU10で実行されるプログラムによるメモリ空間へのアクセス許可を示すメモリ保護情報を格納する保護設定レジスタ群11、保護設定レジスタ群11の設定内容を参照して、CPU10によるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御装置12、及び、CPU10が出力するリセット要求信号に基づいて、保護設定レジスタ群11に格納されたメモリ保護情報を一括して無効化するリセット装置16を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CPUによるメモリアクセスを許可するか否かを決定するメモリアクセス制御機構を備えたマイクロコンピュータに関する。

【背景技術】

【0002】

自動車、航空機等の輸送機械や、携帯電話機、交換機等の通信機器に組み込まれ、これらの機械、機器の制御を行うマイクロコンピュータは組み込みシステムと呼ばれている。組み込みシステムは、処理時間の向上、リアルタイム性の確保、プログラムのソフトウェア部品化による生産性向上等を実現するため、一般にマルチプログラミング環境を備えている。マルチプログラミング環境とは、複数のアプリケーションプログラムを定期的に切り替えて実行したり、あるイベントの発生に応じて実行するアプリケーションプログラムを切り替えたりすることによって、複数のアプリケーションプログラムがあたかも並列実行されているような環境を意味する。このようなマルチプログラミング環境は、CPUと、CPUで実行されるアプリケーションプログラムのスケジューリングを担うシステムプログラムによって実現される。なお、以下では、マルチプログラミング環境で並列実行されるプログラム単位をタスクと呼ぶこととする。

【0003】

従来、組み込みシステムにおいては、各々のタスクがアクセス可能なメモリ空間を制限する、いわゆるメモリ保護機能は重要視されていなかった。しかしながら、近年、Java(登録商標)プログラムをダウンロードして実行することが可能な携帯電話機など、信頼性が保証されていないプログラムを実行する組み込みシステムが登場している。このようなシステムでは、信頼性の保証されていないプログラムからシステムプログラムや他のアプリケーションプログラムを保護することが不可欠である。また、アプリケーションプログラム単位やこれを構成するソフトウェア部品単位で、アプリケーションプログラムが使用するメモリ空間を予め分離することで、ソフトウェア開発工程におけるデバッグを容易にしたいという要求もある。このような背景から、マイクロコンピュータにおけるメモリ保護機能の重要性が増大している。

【0004】

マイクロコンピュータにおけるメモリ保護、つまりメモリアクセスの制御は、メモリ空間のうちアクセスを許可する領域又はアクセスを禁止する領域をメモリ保護情報として定めておき、CPUによるメモリアクセス要求をメモリ保護情報と照合することによって行われる。具体的には、メモリアクセス要求に含まれるメモリアドレスがアクセス許可領域に含まれる場合にメモリアクセスを許可し、アクセス禁止領域に含まれる場合にメモリアクセスを禁止する。また、アプリケーションプログラム単位又はタスク単位で、プログラム実行時に使用するメモリ領域を分離する場合には、実行されるプログラムの切り替えに応じて、アクセスを許可するメモリ領域を変更する必要がある。このため、CPUで実行されるプログラムの切り替え時には、メモリ保護情報の書換えが行われる。このようなメモリ保護機能を備えたマイクロコンピュータは、例えば、非特許文献1及び2に開示されている。

【0005】

非特許文献1に開示されたマイクロコンピュータは、メモリ保護ユニットを備えている。さらに、メモリ保護ユニットは、メモリアクセスを許可する領域を定めるための16個の保護設定レジスタを備えている。各々の保護設定レジスタには、アクセスを許可する領域のベースアドレス、アクセス許可領域のサイズ、及び当該保護設定レジスタによる設定内容の有効又は無効を示す有効ビットが格納される。メモリ保護ユニットは、CPUがアクセスを要求するメモリ領域のメモリアドレスと有効ビットが有効状態に設定された保護設定レジスタによって規定されたアクセス許可領域とを比較する。CPUがアクセスを要求するメモリアドレスが、有効ビットが有効状態に設定された保護設定レジスタによって規定されたアクセス許可領域に含まれるか否かによって、メモリアクセスの許可又は不許可を決定する。

【0006】

一方、非特許文献2に開示されたマイクロコンピュータは、データ領域に対して4通り、及び命令領域に対して4通りのアクセス許可領域を定めることが可能な複数の保護設定レジスタを備えている。各々の保護設定レジスタには、アクセス許可領域の下限アドレス並びに上限アドレス、及び当該保護設定レジスタによる設定内容の保護モードを定めている。保護モードとは、ライトアクセスの許可/不許可、リードアクセスの許可/不許可、実行の許可/不許可を示す情報であり、非特許文献1に開示されたマイクロコンピュータにおける有効ビットに相当するものである。

【先行技術文献】

【非特許文献】

【0007】

【非特許文献1】"ARM1156T2F-S Technical Reference Manual Rev.r0p0"、[online]、2005年10月25日、ARM Ltd.、[2006年4月11日検索]、インターネット<URL:http://www.arm.com/pdfs/DDI0290C_arm1156t2fs_r0p0_trm.pdf>、Chapter3 p.61-69及びChapter5 p.7

【非特許文献2】"TriCore. 1 32-Bit Unified Processor Core Volume 1: V1.3 Core Architecture"、[online]、2005年10月、Infineon Technologies、[2006年4月11日検索]、インターネット<URL:http://www.infineon.com/upload/Document/TriCore_1_um_vol1_Core_Architecture.pdf>、Chapter8 p.4-10及びChapter8 p.13

【発明の概要】

【発明が解決しようとする課題】

【0008】

非特許文献1及び2に開示されたマイクロコンピュータは、CPUで実行されるプログラムの切り替えに応じて保護設定レジスタの内容を順次更新することにより、新たに実行されるプログラムに対するメモリ保護情報を設定する。具体的には、保護設定レジスタの有効ビットを無効状態に設定する処理、保護設定レジスタに許可領域を設定する処理、及び許可領域を定めた保護設定レジスタの有効ビットを有効状態に設定する処理を、全ての保護設定レジスタに対して順次行うことによって、新たなに実行されるプログラムに対するアクセス許可領域を設定する。

【0009】

上述したように、非特許文献1及び2に開示されたマイクロコンピュータは、実行するプログラムの切り替え時に保護設定レジスタを順次書換えていく。このため、保護設定レジスタの書換え漏れを生じ易いという問題がある。

【課題を解決するための手段】

【0010】

本発明の第1の態様にかかるマイクロコンピュータは、CPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御装置と、前記CPUが出力するリセット要求信号に基づいて、前記複数の保護情報格納部に格納されたメモリ保護情報を一括して無効化するリセット装置と、を備える。

【0011】

このような構成により、CPUが出力するリセット要求信号に基づいて動作するリセット装置によって、保護情報格納部に格納されたメモリ保護情報を一括して無効化することができる。プログラムの切り替え時の保護情報格納部の更新に先立ってリセット装置を動作させることとすれば、保護情報格納部の書換えもれによって、過去のメモリ保護情報が残存することを防止し、メモリアクセス制御の信頼性を向上させることができる。

【0012】

また、本発明の第2の態様にかかるマイクロコンピュータは、複数のプログラムを切り替えて実行するCPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、 前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部と、前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラム対するメモリ保護情報を一括して無効化する無効化手段と、前記無効化手段による一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって、前記複数の保護情報格納部を更新する更新手段と、を備える。

【0013】

このように、CPUで新たに実行されるプログラムに応じてメモリ保護情報を更新する処理に先立って、過去のメモリ保護情報を一括して無効化することにより、保護情報格納部の書換えもれによって、過去のメモリ保護情報が残存することを防止し、メモリアクセス制御の信頼性を向上させることができる。

【0014】

また、本発明の第3の態様は、マイクロコンピュータのメモリアクセス制御方法であって、 前記マイクロコンピュータは、CPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部とを備え、前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラムに対するメモリ保護情報を一括して無効化し、前記メモリ保護情報の一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって前記複数の保護情報格納部を更新する。

【0015】

このように、CPUで新たに実行されるプログラムに応じてメモリ保護情報を更新する処理に先立って、過去のメモリ保護情報を一括して無効化することにより、保護情報格納部の書換えもれによって、過去のメモリ保護情報が残存することを防止し、メモリアクセス制御の信頼性を向上させることができる。

【発明の効果】

【0016】

本発明により、メモリアクセス制御の信頼性を向上させることが可能なコンピュータ、及びメモリアクセスの制御方法を提供できる。

【図面の簡単な説明】

【0017】

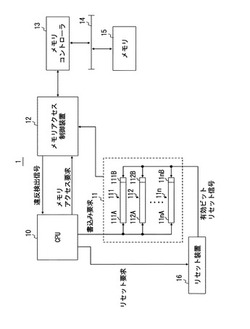

【図1】発明の実施の形態1にかかるマイクロコンピュータの構成図である。

【図2】メモリマップの具体例を示す図である。

【図3】保護設定レジスタ群の設定例を示す図である。

【図4】発明の実施の形態1にかかるマイクロコンピュータが行うメモリ保護情報の更新処理を示すフローチャートである。

【図5】発明の実施の形態2にかかるマイクロコンピュータの構成図である。

【図6】発明の実施の形態2にかかるマイクロコンピュータが行うメモリ保護情報の更新処理を示すフローチャートである。

【図7】発明の実施の形態3にかかるマイクロコンピュータの構成図である。

【図8】発明の実施の形態3にかかるマイクロコンピュータが行うメモリ保護情報の更新処理を示すフローチャートである。

【図9】発明の実施の形態4にかかるマイクロコンピュータの構成図である。

【発明を実施するための最良の形態】

【0018】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。各図面において、同一要素には同一の符号が付されており、説明の明確化のため、必要に応じて重複説明は省略する。

【0019】

発明の実施の形態1.

本実施の形態にかかるマイクロコンピュータ1の構成を図1に示す。図1において、CPU(Central Processing Unit)10は、メモリ15から命令を読み出し、読み出した命令をデコードし、命令に応じた処理、例えば、算術演算及び論理演算等の演算処理や、メモリ15に対するリードアクセス及びライトアクセスを実行する。

【0020】

保護設定レジスタ群11は、メモリ15の保護設定を格納する保護設定格納部である。保護設定レジスタ群11は、n個の保護設定レジスタ111〜11nを有する。本実施の形態では、1つの保護設定レジスタによって1つのアクセス許可領域を指定するものとする。具体的に述べると、保護設定レジスタ111〜11nはそれぞれ、アクセスを許可する領域を指定するための領域指定部と、各保護設定レジスタによる設定内容の有効又は無効を示す有効ビットを格納する有効ビット格納部とを有している。例えば、保護設定レジスタ111は、領域指定部111A、及び有効ビット格納部111Bを有する。なお、領域指定部111A〜11nAによる許可領域の指定は、アクセスを許可する領域のベースアドレス及びアクセス許可領域のサイズを指定することによって行っても良いし、アクセスを許可する領域の下限アドレスと上限アドレスを指定することによって行っても良い。また、有効ビット格納部111B〜11nBはそれぞれ、1ビットの格納領域とし、例えば格納値"0"のとき無効状態を示し、格納値"1"のとき有効状態を示すものとすればよい。保護設定レジスタ群11の書換えは、CPU10が出力する書込み要求に基づいて行われる。

【0021】

メモリアクセス制御装置12は、CPU10が生成するメモリ15に対するメモリアクセス要求を入力する。CPU10が生成するメモリアクセス要求には、リード/ライト種別、アクセス先を指定するためのメモリアドレス、さらにライトアクセスの場合には書込みデータが含まれる。アクセス先を指定するメモリアドレスは、例えば、ベースアドレスと、転送を要求するデータサイズによって指定される。

【0022】

メモリアクセス要求を受信したメモリアクセス制御装置12は、CPU10がアクセスを要求するメモリアドレスと保護設定レジスタ群11が備える各保護設定レジスタ111〜11nの設定内容とを比較することによって、メモリアクセス要求を許可する否かを決定する。具体的には、CPU10がアクセスを要求するメモリアドレスが、保護設定レジスタ111〜11nのうち有効ビットが有効状態に設定された保護設定レジスタによって規定されたアクセス許可領域に含まれる場合に、メモリアクセス制御装置12はメモリアクセスを許可する。一方、CPU10がアクセスを要求するメモリアドレスが許可領域に含まれない場合には、メモリアクセス制御装置12はメモリアクセスを許可せず、不正メモリアクセスの発生を示す違反検出信号をCPU10に対して出力する。なお、図面が複雑となるため、図1では、保護設定レジスタ111〜11nの各々とメモリアクセス制御装置12との接続関係の記載を省略し、これらの接続関係を保護設定レジスタ群11とメモリアクセス制御装置12との接続線によって示している。

【0023】

メモリコントローラ13は、メモリアクセス制御装置12によって許可されたメモリアクセス要求を入力し、メモリアクセス要求によって指定されたアドレスに対応するメモリ15にアクセスする。リードアクセスであればメモリ15から読み出したデータをCPU10に転送し、ライトアクセスであればメモリ15に対するデータ書込みを行う。

【0024】

メモリ15は、メモリバス14を介してメモリコントローラ13と接続されている。メモリ15は、CPU10に読み出されて実行されるシステムプログラムやアプリケーションプログラムの格納領域、及びシステムプログラムやアプリケーションプログラムによって使用されるデータの格納領域として使用される。つまり、メモリ15は、RAM、ROM、フラッシュメモリ等の組合せである。また、メモリバス14は、アドレスバス及びデータバスの総称である。

【0025】

リセット装置16は、CPU10が出力するリセット要求信号に応じて、n個の保護設定レジスタ111〜11nの有効ビット格納部111B〜11nBを無効状態に設定する。本実施の形態では、有効ビット格納部111B〜11nBを有効状態に設定することによってメモリアクセスが許可されるため、有効ビット格納部111B〜11nBを無効状態に設定することは、メモリ15の全ての領域に対するアクセスが禁止された状態を意味する。

【0026】

CPU10で実行されるプログラムを切り替える処理は、システムプログラムによって行われる。例えば、アプリケーションプログラムAからアプリケーションプログラムBに切り替える際には、切り替え処理を担うシステムプログラムが起床され、システムプログラムをCPU10で実行することにより、新たに実行されるプログラムBに応じて保護設定レジスタ群11の設定内容が更新される。

【0027】

保護設定レジスタ群11の設定内容の更新の具体例を、図2及び図3を用いて説明する。図2は、メモリ15がROM及びRAMである場合のメモリマップの具体例を示している。図2(a)はROMのメモリマップ例を示しており、00000〜00FFF番地にシステムプログラムが格納され、01000〜01FFF番地にアプリケーションプログラムAが格納され、02000〜02FFF番地にアプリケーションプログラムBが格納されているものとする。また、図2(b)はRAMのメモリマップ例を示しており、10000〜10FFF番地がシステムプログラムのワーク領域として使用され、12000〜120FF番地及び14000〜141FF番地がアプリケーションプログラムAのワーク領域として使用され、13000〜130FF番地がアプリケーションプログラムBのワーク領域として使用されるものとする。

【0028】

アプリケーションプログラムAに対応する保護設定レジスタ群11の設定内容を図3(a)に示す。図3(a)では、保護設定レジスタ111がROMのアプリケーションプログラムAの格納領域へのアクセス許可を規定し、保護設定レジスタ112及び保護設定レジスタ113がRAMのワーク領域へのアクセス許可を規定している。一方、アプリケーションプログラムBに対応する保護設定レジスタ群11の設定内容を図3(b)に示す。図3(b)では、保護設定レジスタ111がROMのアプリケーションプログラムBの格納領域へのアクセス許可を規定し、保護設定レジスタ112がRAMのワーク領域へのアクセス許可を規定している。

【0029】

アプリケーションプログラムAからアプリケーションプログラムBに実行プログラムを切り替える際には、保護設定レジスタ113の有効ビット格納部113Bを、無効状態を示す値"0"に書換える必要がある。このとき、マイクロコンピュータ1では、リセット装置16によって保護設定レジスタ群11の設定内容を一括して無効化した後に、新たに実行するアプリケーションプログラムBに対するメモリ保護情報、つまりアクセス許可領域の設定を書込むように動作する。以下では、マイクロコンピュータ1が行うメモリ保護情報の更新処理を図4のフローチャートを用いて詳細に説明する。

【0030】

ステップS101では、システムプログラムによって、新たに実行されるプログラムに関するプログラム情報が取得される。ここでプログラム情報とは、CPU10で実行されるプログラムに使用を許可するメモリ領域を指定する情報である。ステップS102では、CPU10から送信されたリセット要求信号を受信したリセット装置16が、有効ビットリセット信号を保護設定レジスタ111〜11nに送信し、有効ビット格納部111B〜11nBを一括して無効状態にリセットする。

【0031】

ステップS103〜S107では、システムプログラムによって、新たに実行されるプログラムに合わせたメモリ保護設定が行われる。なお、ここでは、メモリ15対するメモリ空間がn個の領域に分割され、各領域に対するアクセス許可を設定するものとして説明する。具体的には、ステップS103では、変数Kの値を1に設定する。ステップS104では、ステップS101で取得した新たな実行プログラムに関する保護情報を参照し、K番目の領域Kに対するアクセスを許可するか否かを判定する。領域Kがメモリアクセスを許可する領域である場合は、保護設定レジスタ111〜11nのいずれかに、領域Kを保護領域として設定し、設定した保護設定レジスタの有効ビットを有効状態にセットする(ステップS105)。

【0032】

ステップS106では変数Kの値をインクリメントし、変数Kの値がnより小さい場合は、ステップS104に戻ってS104以降の処理を繰り返す(ステップS107)。一方、n個の領域全てに対する処理した場合は、メモリ保護情報の更新処理を終了する。

【0033】

上述したように、従来のマイクロコンピュータは、実行するプログラムの切り替え時に保護設定レジスタを順次書換えていく。このため、保護設定レジスタの書換え漏れを生じ易いという問題がある。例えば、メモリアクセスを許可する領域をメモリ保護設定レジスタに設定する場合において、以前のプログラムに対する設定が、プログラムの切り替え後に残存していると、アクセスを許可すべきでないメモリ領域へのアクセスが可能となり、不正なメモリアクセスを検出できない状況を招く。また、メモリアクセスを禁止する領域をメモリ保護設定レジスタに設定する場合において、以前のプログラムに対する設定が、プログラムの切り替え後に残存していると、アクセス可能であるべきメモリ領域にアクセスできないことにより、アプリケーションプログラムの実行に不具合をもたらす可能性がある。

【0034】

これに対して、本実施の形態にかかるマイクロコンピュータ1は、保護設定レジスタ群11によって規定される過去の実行プログラムのメモリ保護情報を全て無効とした後、新たな実行プログラムに対するメモリ保護情報の設定を行うこととしている。これにより、以前のプログラムに対するメモリ保護情報がプログラムの切り替え後に残存することを防止し、メモリ保護の信頼性を向上させることができる。

【0035】

発明の実施の形態2.

本実施の形態にかかるマイクロコンピュータ2の構成を図5に示す。マイクロコンピュータ2は、特権ビット格納部21及び書込み禁止装置22を備える点が、発明の実施の形態1にかかるマイクロコンピュータ1と相違している。

【0036】

特権ビット格納部21は、リセット装置16の起動及び保護設定レジスタ群11の更新が可能であるか否かを示す特権ビットを格納する。例えば、特権ビットを1ビットデータとし、リセット装置16の起動及び保護設定レジスタ群11の更新が可能な特権モードを値"1"とし、逆に、リセット装置16の起動及び保護設定レジスタ群11の更新が不可能な非特権モードを値"0"とすればよい。特権ビット格納部21の値は、CPU20において実行されるシステムプログラムによって書換え可能であり、アプリケーションプログラムによる書換えは不可能とする。

【0037】

書込み禁止装置22は、リセット装置16に対するリセット要求及び保護設定レジスタ群11に対する書込み要求をCPU20から入力し、特権ビット格納部21に格納された値が特権モードを示す場合に限り、リセット要求及び書込み要求をリセット装置16又は保護設定レジスタ群11に転送する。

【0038】

なお、CPU20は、特権ビット格納部21の書換えを行うことを除いて、発明の実施の形態1のCPU10と同様である。

【0039】

特権ビット格納部21、書込み禁止装置22及びCPU20を除く他の構成要素は、発明の実施の形態1のマイクロコンピュータ1が有する構成要素と同一であるため、詳細な説明を省略する。

【0040】

次に、マイクロコンピュータ2が行うメモリ保護情報の更新処理を図6のフローチャートを用いて説明する。なお、図6において、図4のフローチャートと同様のステップについては、図4と同一の符号を付している。

【0041】

ステップS201では、システムプログラムの命令によって特権ビット格納部21の特権ビットを更新し、特権モードに遷移する。ステップS202では、システムプログラムの命令に応じて、CPU20からリセット装置16に対して有効ビット格納部111B〜11nBのリセット要求が出力される。ステップS202では、書込み禁止装置22が特権ビット格納部21を参照し、特権モードを示す値(ここでは値"1"とする)が設定されている場合に限り、リセット装置16に対してリセット要求を転送する(ステップS203)。書込み禁止装置22からリセット要求を受信したリセット装置16は、有効ビットリセット信号を保護設定レジスタ111〜11nに送信し、有効ビット格納部111B〜11nBを一括して無効状態にリセットする(ステップS102)。

【0042】

続く、ステップS103〜S107までの保護設定レジスタ群11の書換え処理では、ステップS204が本実施の形態に特有の処理である。ステップS204では、書込み禁止装置22が特権ビット格納部21を参照し、特権モードを示す値(ここでは値"1"とする)が設定されている場合に限り、CPU20から入力した書込み要求を保護設定レジスタ群11に転送する。最後のステップS205では、非特権モードを示す状態に特権ビット格納部22を書換えることによって、非特権モードに遷移する。

【0043】

発明の実施の形態1にかかるマイクロコンピュータ1は、保護設定レジスタ群11に対する書込み要求を拒絶する条件が考慮されていないため、アプリケーションプログラムによって生成された書込み要求によって保護設定レジスタ群11が書換えられる可能性がある。これに対して、本実施の形態のマイクロコンピュータ2では、特権モードに遷移していない状態で発行された書込み要求は書込み禁止装置22によって拒絶され、かつ、特権モードのへの遷移はシステムプログラムによって特権ビット格納部21を書換えることによって行われる。このため、非特権モードで動作するアプリケーションプログラムによる書込み要求では、保護設定レジスタ群11の書換えは発生しない。これにより、悪意のあるアプリケーションプログラムによるメモリ保護設定の変更を防止することができる。

【0044】

発明の実施の形態3.

本実施の形態にかかるマイクロコンピュータ3の構成を図7に示す。マイクロコンピュータ3は、書込み禁止ビット格納部31及び書込み禁止装置32を備える点が、発明の実施の形態2にかかるマイクロコンピュータ2と相違している。

【0045】

書込み禁止ビット格納部31は、保護設定レジスタ群11に対する書込みが可能であるか否かを示す書込み禁止ビットを格納する。例えば、書込み禁止ビットを1ビットデータとし、保護設定レジスタ群11に対する書込みが禁止された禁止状態を値"1"とし、逆に、保護設定レジスタ群11に対する書込みが可能な許可状態を値"0"とすればよい。後述するように、保護設定レジスタ群11に対する書込みを禁止する状態の設定は、CPU20において実行されるシステムプログラムによって行われる。また、保護設定レジスタ群11に対する書込みを許可する状態の設定は、リセット装置36によって行われる。

【0046】

書込み禁止装置32は、保護設定レジスタ群11に対する書込み要求書込み禁止装置22から入力し、書込み禁止ビット格納部31に格納された値が書込み許可を示す場合に限り、書込み要求をリセット装置16又は保護設定レジスタ群11に転送する。

【0047】

なお、CPU30は、書込み禁止ビット格納部31の書換えを行うことを除いて、発明の実施の形態2のCPU20と同様である。また、リセット装置36は、書込み禁止ビット格納部31の書換えを行うことを除いて、発明の実施の形態1のリセット装置16と同様である。

【0048】

書込み禁止ビット格納部31、書込み禁止装置32、CPU30及びリセット装置36を除く他の構成要素は、上述したマイクロコンピュータ1又は2が有する構成要素と同一であるため、詳細な説明を省略する。

【0049】

次に、マイクロコンピュータ3が行うメモリ保護情報の更新処理を図8のフローチャートを用いて説明する。なお、図8において、図4又は図6のフローチャートと同様のステップについては、図4又は図6と同一の符号を付している。

【0050】

ステップS301では、システムプログラムの命令によって、書込み禁止ビット格納部31が書込み禁止状態を示す値(ここでは値"1"とする)に設定される。ステップS302では、リセット装置36によって有効ビット格納部111B〜11nBが一括して無効状態にリセットされたことに合わせて、書込み禁止ビット格納部31の値が書込み許可を示す値(ここでは値"0"とする)にリセットされる(ステップS102及びS302)。なお、書込み禁止ビット格納部31のリセットは、有効ビット格納部111B〜11nBをリセットするための有効ビットリセット信号を書込み禁ビット格納部31に入力することによって行えば良い。

【0051】

続く、ステップS103〜S107までの保護設定レジスタ群11の書換え処理では、ステップS303が本実施の形態に特有の処理である。ステップS303では、書込み禁止装置32が書込み禁止ビット格納部31を参照し、保護設定レジスタ群11に対する書込みが可能な許可状態である場合に限り、書込み禁止装置22から入力した書込み要求を保護設定レジスタ群11に転送する。

【0052】

発明の実施の形態1又は2にかかるマイクロコンピュータ1及び2は、リセット装置16によって有効ビット格納部111B〜11nBが全て無効状態とされたことを、保護設定レジスタ群11に対する書込みを許可する条件としていない。このため、プログラム切り替え時の保護設定レジスタ群11の更新において、無効状態とすべき保護設定レジスタに対する設定漏れが発生する可能性がある。

【0053】

これに対して、マイクロコンピュータ3では、書込み禁止ビット格納部31に格納された値が書込み禁止を示している状態で、保護設定レジスタ群11に対する書込み要求が発行された場合、当該書込み要求は書込み禁止装置32によって拒絶される。さらに、マイクロコンピュータ3において、書込み禁止ビット格納部31の値が書込み許可状態となる条件は、リセット装置36によって有効ビット格納部111B〜11nBを全て無効状態とするリセット動作が行われていることである。このため、マイクロコンピュータ3では、有効ビット格納部111B〜11nBを全て無効状態とされていない状態において、保護設定レジスタ群11の書換えが行われることがなく、無効状態とすべき保護設定レジスタに対する設定漏れが発生することを防止できる。

【0054】

発明の実施の形態4.

本実施の形態にかかるマイクロコンピュータ4の構成を図4に示す。マイクロコンピュータ4は、有効ビット格納部111B〜11nBだけでなく、領域指定部111A〜11nAを含む保護設定レジスタ111〜11n全体を、リセット装置46によるリセット対象とすることが特徴である。領域指定部111A〜11nAのリセットは、予め定められた無効値に設定することによって行えば良い。無効値は、メモリ空間のどの領域とも対応しない値を選択すれば良く、例えば、領域指定部111A〜11nAをオールゼロ又はオール1に設定すれば良い。また、領域指定部111A〜11nAがアクセス許可領域のサイズ情報を含む場合は、アクセス許可領域のサイズをゼロに設定しても良い。

【0055】

なお、リセット装置46を除く他の構成要素は、上述したマイクロコンピュータ3が有する構成要素と同一であるため、詳細な説明を省略する。

【0056】

上述したマイクロコンピュータ1乃至3は、リセット装置によるリセット範囲を有効ビット格納部111B〜11nBのみとしている。このため、CPU10乃至30から出力される書込み要求に基づいて有効ビット格納部111B〜11nBが有効状態に更新されたにも関わらず、対応する領域指定部111A〜11nAの値が設定されなかった場合に、誤ったメモリ保護情報が有効となる可能性がある。

【0057】

これに対して、マイクロコンピュータ4では、有効ビット格納部111B〜11nBだけでなく、領域指定部111A〜11nAを含む保護設定レジスタ111〜11n全体を、リセット装置46によるリセット対象としている。このため、仮に、領域指定部111A〜11nAが更新されずに有効ビット格納部111B〜11nBが有効とされる状況が発生しても、この場合の領域指定部111A〜11nAの値は無効な値である。従って、不正なメモリアクセスが許可されることを防止することができる。

【0058】

その他の実施の形態.

上述した発明の実施の形態1乃至4において、リセット装置16、36及び46が行う処理は、CPU10、20又は30と、CPU10、20又は30で実行されるプログラムとによって実現することも可能である。具体的には、実行プログラムの切り替え処理における保護設定レジスタ111〜11nの書換えを行う前に、CPU10に保護設定レジスタ111〜11nを無効化する処理をさせるためのプログラムを実行すればよい。

【0059】

しかしながら、マイクロコンピュータ1のように、CPU10と独立したリセット装置16を設け、CPU10が出力するリセット要求信号に応じてリセット装置16が保護設定レジスタ群11を無効状態に設定する構成が望ましい。このような構成によって、少ない命令の実行、具合的にはリセット要求信号を送信するための1つの命令を実行することで、誤ったメモリ保護設定を排除することができる。

【0060】

また、上述した発明の実施の形態1乃至4では、CPU10で実行されるプログラムによるメモリアクセスを許可する領域を保護設定レジスタ111〜11nに設定することとした。しかしながら、保護設定レジスタ111〜11nには、アクセスを禁止する領域を設定してもよいし、許可領域及び禁止領域を設定してもよい。

【0061】

また、上述した発明の実施の形態1乃至4では、保護設定レジスタ111〜11nの設定内容が有効であるか否かを有効ビット格納部111B〜11nBによって示す構成を説明した。しかしながら、保護設定レジスタ111〜11nの設定内容が有効であるか否かを定めるための構成は、当該構成に限定されない。例えば、非特許文献2に記載されているように、ライトアクセスの許可/不許可、リードアクセスの許可/不許可、実行の許可/不許可を示す識別子によって、保護設定レジスタ111〜11nの設定内容が有効であるか否かを定めても良い。この場合は、ライトアクセス、リードアクセス及び実行を共に不許可に設定することが、保護設定レジスタ111〜11nの設定内容を無効状態に設定することに相当する。

【0062】

また、上述した発明の実施の形態1乃至4では、保護設定レジスタ111〜11nのそれぞれが、領域指定部111A〜11nA、及び有効ビット格納部111B〜11nBを備えることとした。しかしながら、メモリ保護情報を格納する領域と、当該保持後情報の有効性を規定する情報を格納する領域とは、物理的に独立した記憶装置に格納しても良い。

【0063】

また、上述した発明の実施の形態1乃至4において、リセット装置16、36又は46の制御対象である保護設定レジスタ111〜11nによってアクセス制御を行うメモリ空間は、メモリ15の全てに対応するメモリ空間に限られない。例えば、システムプログラムの格納領域など、アプリケーションプログラムによるアクセスを一律に禁止する領域をメモリ15に規定する場合には、このような一律に禁止される領域を除外した領域を、保護設定レジスタ111〜11nによるアクセス制御の対象とすれば良い。

【0064】

また、上述した発明の実施の形態1乃至4において、メモリ15は、マイクロコンピュータ1乃至4の外部に設けられていても良い。また、メモリアクセス制御装置12にメモリコントローラ13を介してメモリ15が接続された構成は一例である。例えば、DMA転送を行う場合には、メモリアクセス制御装置12とメモリ16は、DMA転送を制御するDMAコントローラを介して接続されても良い。

【0065】

さらに、本発明は上述した実施の形態のみに限定されるものではなく、既に述べた本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

【符号の説明】

【0066】

1、2、3、4 マイクロコンピュータ

10、20、30 CPU(Central Processing Unit)

11 保護設定レジスタ群

111〜11n 保護設定レジスタ

111A〜11nA 領域指定部

111B〜11nB 有効ビット格納部

12 メモリアクセス制御装置

13 メモリコントローラ

14 メモリバス

15 メモリ

16、36、46 リセット装置

21 特権ビット格納部

22 書込み禁止装置

31 書込み禁止ビット格納部

32 書込み禁止装置

【技術分野】

【0001】

本発明は、CPUによるメモリアクセスを許可するか否かを決定するメモリアクセス制御機構を備えたマイクロコンピュータに関する。

【背景技術】

【0002】

自動車、航空機等の輸送機械や、携帯電話機、交換機等の通信機器に組み込まれ、これらの機械、機器の制御を行うマイクロコンピュータは組み込みシステムと呼ばれている。組み込みシステムは、処理時間の向上、リアルタイム性の確保、プログラムのソフトウェア部品化による生産性向上等を実現するため、一般にマルチプログラミング環境を備えている。マルチプログラミング環境とは、複数のアプリケーションプログラムを定期的に切り替えて実行したり、あるイベントの発生に応じて実行するアプリケーションプログラムを切り替えたりすることによって、複数のアプリケーションプログラムがあたかも並列実行されているような環境を意味する。このようなマルチプログラミング環境は、CPUと、CPUで実行されるアプリケーションプログラムのスケジューリングを担うシステムプログラムによって実現される。なお、以下では、マルチプログラミング環境で並列実行されるプログラム単位をタスクと呼ぶこととする。

【0003】

従来、組み込みシステムにおいては、各々のタスクがアクセス可能なメモリ空間を制限する、いわゆるメモリ保護機能は重要視されていなかった。しかしながら、近年、Java(登録商標)プログラムをダウンロードして実行することが可能な携帯電話機など、信頼性が保証されていないプログラムを実行する組み込みシステムが登場している。このようなシステムでは、信頼性の保証されていないプログラムからシステムプログラムや他のアプリケーションプログラムを保護することが不可欠である。また、アプリケーションプログラム単位やこれを構成するソフトウェア部品単位で、アプリケーションプログラムが使用するメモリ空間を予め分離することで、ソフトウェア開発工程におけるデバッグを容易にしたいという要求もある。このような背景から、マイクロコンピュータにおけるメモリ保護機能の重要性が増大している。

【0004】

マイクロコンピュータにおけるメモリ保護、つまりメモリアクセスの制御は、メモリ空間のうちアクセスを許可する領域又はアクセスを禁止する領域をメモリ保護情報として定めておき、CPUによるメモリアクセス要求をメモリ保護情報と照合することによって行われる。具体的には、メモリアクセス要求に含まれるメモリアドレスがアクセス許可領域に含まれる場合にメモリアクセスを許可し、アクセス禁止領域に含まれる場合にメモリアクセスを禁止する。また、アプリケーションプログラム単位又はタスク単位で、プログラム実行時に使用するメモリ領域を分離する場合には、実行されるプログラムの切り替えに応じて、アクセスを許可するメモリ領域を変更する必要がある。このため、CPUで実行されるプログラムの切り替え時には、メモリ保護情報の書換えが行われる。このようなメモリ保護機能を備えたマイクロコンピュータは、例えば、非特許文献1及び2に開示されている。

【0005】

非特許文献1に開示されたマイクロコンピュータは、メモリ保護ユニットを備えている。さらに、メモリ保護ユニットは、メモリアクセスを許可する領域を定めるための16個の保護設定レジスタを備えている。各々の保護設定レジスタには、アクセスを許可する領域のベースアドレス、アクセス許可領域のサイズ、及び当該保護設定レジスタによる設定内容の有効又は無効を示す有効ビットが格納される。メモリ保護ユニットは、CPUがアクセスを要求するメモリ領域のメモリアドレスと有効ビットが有効状態に設定された保護設定レジスタによって規定されたアクセス許可領域とを比較する。CPUがアクセスを要求するメモリアドレスが、有効ビットが有効状態に設定された保護設定レジスタによって規定されたアクセス許可領域に含まれるか否かによって、メモリアクセスの許可又は不許可を決定する。

【0006】

一方、非特許文献2に開示されたマイクロコンピュータは、データ領域に対して4通り、及び命令領域に対して4通りのアクセス許可領域を定めることが可能な複数の保護設定レジスタを備えている。各々の保護設定レジスタには、アクセス許可領域の下限アドレス並びに上限アドレス、及び当該保護設定レジスタによる設定内容の保護モードを定めている。保護モードとは、ライトアクセスの許可/不許可、リードアクセスの許可/不許可、実行の許可/不許可を示す情報であり、非特許文献1に開示されたマイクロコンピュータにおける有効ビットに相当するものである。

【先行技術文献】

【非特許文献】

【0007】

【非特許文献1】"ARM1156T2F-S Technical Reference Manual Rev.r0p0"、[online]、2005年10月25日、ARM Ltd.、[2006年4月11日検索]、インターネット<URL:http://www.arm.com/pdfs/DDI0290C_arm1156t2fs_r0p0_trm.pdf>、Chapter3 p.61-69及びChapter5 p.7

【非特許文献2】"TriCore. 1 32-Bit Unified Processor Core Volume 1: V1.3 Core Architecture"、[online]、2005年10月、Infineon Technologies、[2006年4月11日検索]、インターネット<URL:http://www.infineon.com/upload/Document/TriCore_1_um_vol1_Core_Architecture.pdf>、Chapter8 p.4-10及びChapter8 p.13

【発明の概要】

【発明が解決しようとする課題】

【0008】

非特許文献1及び2に開示されたマイクロコンピュータは、CPUで実行されるプログラムの切り替えに応じて保護設定レジスタの内容を順次更新することにより、新たに実行されるプログラムに対するメモリ保護情報を設定する。具体的には、保護設定レジスタの有効ビットを無効状態に設定する処理、保護設定レジスタに許可領域を設定する処理、及び許可領域を定めた保護設定レジスタの有効ビットを有効状態に設定する処理を、全ての保護設定レジスタに対して順次行うことによって、新たなに実行されるプログラムに対するアクセス許可領域を設定する。

【0009】

上述したように、非特許文献1及び2に開示されたマイクロコンピュータは、実行するプログラムの切り替え時に保護設定レジスタを順次書換えていく。このため、保護設定レジスタの書換え漏れを生じ易いという問題がある。

【課題を解決するための手段】

【0010】

本発明の第1の態様にかかるマイクロコンピュータは、CPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御装置と、前記CPUが出力するリセット要求信号に基づいて、前記複数の保護情報格納部に格納されたメモリ保護情報を一括して無効化するリセット装置と、を備える。

【0011】

このような構成により、CPUが出力するリセット要求信号に基づいて動作するリセット装置によって、保護情報格納部に格納されたメモリ保護情報を一括して無効化することができる。プログラムの切り替え時の保護情報格納部の更新に先立ってリセット装置を動作させることとすれば、保護情報格納部の書換えもれによって、過去のメモリ保護情報が残存することを防止し、メモリアクセス制御の信頼性を向上させることができる。

【0012】

また、本発明の第2の態様にかかるマイクロコンピュータは、複数のプログラムを切り替えて実行するCPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、 前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部と、前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラム対するメモリ保護情報を一括して無効化する無効化手段と、前記無効化手段による一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって、前記複数の保護情報格納部を更新する更新手段と、を備える。

【0013】

このように、CPUで新たに実行されるプログラムに応じてメモリ保護情報を更新する処理に先立って、過去のメモリ保護情報を一括して無効化することにより、保護情報格納部の書換えもれによって、過去のメモリ保護情報が残存することを防止し、メモリアクセス制御の信頼性を向上させることができる。

【0014】

また、本発明の第3の態様は、マイクロコンピュータのメモリアクセス制御方法であって、 前記マイクロコンピュータは、CPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部とを備え、前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラムに対するメモリ保護情報を一括して無効化し、前記メモリ保護情報の一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって前記複数の保護情報格納部を更新する。

【0015】

このように、CPUで新たに実行されるプログラムに応じてメモリ保護情報を更新する処理に先立って、過去のメモリ保護情報を一括して無効化することにより、保護情報格納部の書換えもれによって、過去のメモリ保護情報が残存することを防止し、メモリアクセス制御の信頼性を向上させることができる。

【発明の効果】

【0016】

本発明により、メモリアクセス制御の信頼性を向上させることが可能なコンピュータ、及びメモリアクセスの制御方法を提供できる。

【図面の簡単な説明】

【0017】

【図1】発明の実施の形態1にかかるマイクロコンピュータの構成図である。

【図2】メモリマップの具体例を示す図である。

【図3】保護設定レジスタ群の設定例を示す図である。

【図4】発明の実施の形態1にかかるマイクロコンピュータが行うメモリ保護情報の更新処理を示すフローチャートである。

【図5】発明の実施の形態2にかかるマイクロコンピュータの構成図である。

【図6】発明の実施の形態2にかかるマイクロコンピュータが行うメモリ保護情報の更新処理を示すフローチャートである。

【図7】発明の実施の形態3にかかるマイクロコンピュータの構成図である。

【図8】発明の実施の形態3にかかるマイクロコンピュータが行うメモリ保護情報の更新処理を示すフローチャートである。

【図9】発明の実施の形態4にかかるマイクロコンピュータの構成図である。

【発明を実施するための最良の形態】

【0018】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。各図面において、同一要素には同一の符号が付されており、説明の明確化のため、必要に応じて重複説明は省略する。

【0019】

発明の実施の形態1.

本実施の形態にかかるマイクロコンピュータ1の構成を図1に示す。図1において、CPU(Central Processing Unit)10は、メモリ15から命令を読み出し、読み出した命令をデコードし、命令に応じた処理、例えば、算術演算及び論理演算等の演算処理や、メモリ15に対するリードアクセス及びライトアクセスを実行する。

【0020】

保護設定レジスタ群11は、メモリ15の保護設定を格納する保護設定格納部である。保護設定レジスタ群11は、n個の保護設定レジスタ111〜11nを有する。本実施の形態では、1つの保護設定レジスタによって1つのアクセス許可領域を指定するものとする。具体的に述べると、保護設定レジスタ111〜11nはそれぞれ、アクセスを許可する領域を指定するための領域指定部と、各保護設定レジスタによる設定内容の有効又は無効を示す有効ビットを格納する有効ビット格納部とを有している。例えば、保護設定レジスタ111は、領域指定部111A、及び有効ビット格納部111Bを有する。なお、領域指定部111A〜11nAによる許可領域の指定は、アクセスを許可する領域のベースアドレス及びアクセス許可領域のサイズを指定することによって行っても良いし、アクセスを許可する領域の下限アドレスと上限アドレスを指定することによって行っても良い。また、有効ビット格納部111B〜11nBはそれぞれ、1ビットの格納領域とし、例えば格納値"0"のとき無効状態を示し、格納値"1"のとき有効状態を示すものとすればよい。保護設定レジスタ群11の書換えは、CPU10が出力する書込み要求に基づいて行われる。

【0021】

メモリアクセス制御装置12は、CPU10が生成するメモリ15に対するメモリアクセス要求を入力する。CPU10が生成するメモリアクセス要求には、リード/ライト種別、アクセス先を指定するためのメモリアドレス、さらにライトアクセスの場合には書込みデータが含まれる。アクセス先を指定するメモリアドレスは、例えば、ベースアドレスと、転送を要求するデータサイズによって指定される。

【0022】

メモリアクセス要求を受信したメモリアクセス制御装置12は、CPU10がアクセスを要求するメモリアドレスと保護設定レジスタ群11が備える各保護設定レジスタ111〜11nの設定内容とを比較することによって、メモリアクセス要求を許可する否かを決定する。具体的には、CPU10がアクセスを要求するメモリアドレスが、保護設定レジスタ111〜11nのうち有効ビットが有効状態に設定された保護設定レジスタによって規定されたアクセス許可領域に含まれる場合に、メモリアクセス制御装置12はメモリアクセスを許可する。一方、CPU10がアクセスを要求するメモリアドレスが許可領域に含まれない場合には、メモリアクセス制御装置12はメモリアクセスを許可せず、不正メモリアクセスの発生を示す違反検出信号をCPU10に対して出力する。なお、図面が複雑となるため、図1では、保護設定レジスタ111〜11nの各々とメモリアクセス制御装置12との接続関係の記載を省略し、これらの接続関係を保護設定レジスタ群11とメモリアクセス制御装置12との接続線によって示している。

【0023】

メモリコントローラ13は、メモリアクセス制御装置12によって許可されたメモリアクセス要求を入力し、メモリアクセス要求によって指定されたアドレスに対応するメモリ15にアクセスする。リードアクセスであればメモリ15から読み出したデータをCPU10に転送し、ライトアクセスであればメモリ15に対するデータ書込みを行う。

【0024】

メモリ15は、メモリバス14を介してメモリコントローラ13と接続されている。メモリ15は、CPU10に読み出されて実行されるシステムプログラムやアプリケーションプログラムの格納領域、及びシステムプログラムやアプリケーションプログラムによって使用されるデータの格納領域として使用される。つまり、メモリ15は、RAM、ROM、フラッシュメモリ等の組合せである。また、メモリバス14は、アドレスバス及びデータバスの総称である。

【0025】

リセット装置16は、CPU10が出力するリセット要求信号に応じて、n個の保護設定レジスタ111〜11nの有効ビット格納部111B〜11nBを無効状態に設定する。本実施の形態では、有効ビット格納部111B〜11nBを有効状態に設定することによってメモリアクセスが許可されるため、有効ビット格納部111B〜11nBを無効状態に設定することは、メモリ15の全ての領域に対するアクセスが禁止された状態を意味する。

【0026】

CPU10で実行されるプログラムを切り替える処理は、システムプログラムによって行われる。例えば、アプリケーションプログラムAからアプリケーションプログラムBに切り替える際には、切り替え処理を担うシステムプログラムが起床され、システムプログラムをCPU10で実行することにより、新たに実行されるプログラムBに応じて保護設定レジスタ群11の設定内容が更新される。

【0027】

保護設定レジスタ群11の設定内容の更新の具体例を、図2及び図3を用いて説明する。図2は、メモリ15がROM及びRAMである場合のメモリマップの具体例を示している。図2(a)はROMのメモリマップ例を示しており、00000〜00FFF番地にシステムプログラムが格納され、01000〜01FFF番地にアプリケーションプログラムAが格納され、02000〜02FFF番地にアプリケーションプログラムBが格納されているものとする。また、図2(b)はRAMのメモリマップ例を示しており、10000〜10FFF番地がシステムプログラムのワーク領域として使用され、12000〜120FF番地及び14000〜141FF番地がアプリケーションプログラムAのワーク領域として使用され、13000〜130FF番地がアプリケーションプログラムBのワーク領域として使用されるものとする。

【0028】

アプリケーションプログラムAに対応する保護設定レジスタ群11の設定内容を図3(a)に示す。図3(a)では、保護設定レジスタ111がROMのアプリケーションプログラムAの格納領域へのアクセス許可を規定し、保護設定レジスタ112及び保護設定レジスタ113がRAMのワーク領域へのアクセス許可を規定している。一方、アプリケーションプログラムBに対応する保護設定レジスタ群11の設定内容を図3(b)に示す。図3(b)では、保護設定レジスタ111がROMのアプリケーションプログラムBの格納領域へのアクセス許可を規定し、保護設定レジスタ112がRAMのワーク領域へのアクセス許可を規定している。

【0029】

アプリケーションプログラムAからアプリケーションプログラムBに実行プログラムを切り替える際には、保護設定レジスタ113の有効ビット格納部113Bを、無効状態を示す値"0"に書換える必要がある。このとき、マイクロコンピュータ1では、リセット装置16によって保護設定レジスタ群11の設定内容を一括して無効化した後に、新たに実行するアプリケーションプログラムBに対するメモリ保護情報、つまりアクセス許可領域の設定を書込むように動作する。以下では、マイクロコンピュータ1が行うメモリ保護情報の更新処理を図4のフローチャートを用いて詳細に説明する。

【0030】

ステップS101では、システムプログラムによって、新たに実行されるプログラムに関するプログラム情報が取得される。ここでプログラム情報とは、CPU10で実行されるプログラムに使用を許可するメモリ領域を指定する情報である。ステップS102では、CPU10から送信されたリセット要求信号を受信したリセット装置16が、有効ビットリセット信号を保護設定レジスタ111〜11nに送信し、有効ビット格納部111B〜11nBを一括して無効状態にリセットする。

【0031】

ステップS103〜S107では、システムプログラムによって、新たに実行されるプログラムに合わせたメモリ保護設定が行われる。なお、ここでは、メモリ15対するメモリ空間がn個の領域に分割され、各領域に対するアクセス許可を設定するものとして説明する。具体的には、ステップS103では、変数Kの値を1に設定する。ステップS104では、ステップS101で取得した新たな実行プログラムに関する保護情報を参照し、K番目の領域Kに対するアクセスを許可するか否かを判定する。領域Kがメモリアクセスを許可する領域である場合は、保護設定レジスタ111〜11nのいずれかに、領域Kを保護領域として設定し、設定した保護設定レジスタの有効ビットを有効状態にセットする(ステップS105)。

【0032】

ステップS106では変数Kの値をインクリメントし、変数Kの値がnより小さい場合は、ステップS104に戻ってS104以降の処理を繰り返す(ステップS107)。一方、n個の領域全てに対する処理した場合は、メモリ保護情報の更新処理を終了する。

【0033】

上述したように、従来のマイクロコンピュータは、実行するプログラムの切り替え時に保護設定レジスタを順次書換えていく。このため、保護設定レジスタの書換え漏れを生じ易いという問題がある。例えば、メモリアクセスを許可する領域をメモリ保護設定レジスタに設定する場合において、以前のプログラムに対する設定が、プログラムの切り替え後に残存していると、アクセスを許可すべきでないメモリ領域へのアクセスが可能となり、不正なメモリアクセスを検出できない状況を招く。また、メモリアクセスを禁止する領域をメモリ保護設定レジスタに設定する場合において、以前のプログラムに対する設定が、プログラムの切り替え後に残存していると、アクセス可能であるべきメモリ領域にアクセスできないことにより、アプリケーションプログラムの実行に不具合をもたらす可能性がある。

【0034】

これに対して、本実施の形態にかかるマイクロコンピュータ1は、保護設定レジスタ群11によって規定される過去の実行プログラムのメモリ保護情報を全て無効とした後、新たな実行プログラムに対するメモリ保護情報の設定を行うこととしている。これにより、以前のプログラムに対するメモリ保護情報がプログラムの切り替え後に残存することを防止し、メモリ保護の信頼性を向上させることができる。

【0035】

発明の実施の形態2.

本実施の形態にかかるマイクロコンピュータ2の構成を図5に示す。マイクロコンピュータ2は、特権ビット格納部21及び書込み禁止装置22を備える点が、発明の実施の形態1にかかるマイクロコンピュータ1と相違している。

【0036】

特権ビット格納部21は、リセット装置16の起動及び保護設定レジスタ群11の更新が可能であるか否かを示す特権ビットを格納する。例えば、特権ビットを1ビットデータとし、リセット装置16の起動及び保護設定レジスタ群11の更新が可能な特権モードを値"1"とし、逆に、リセット装置16の起動及び保護設定レジスタ群11の更新が不可能な非特権モードを値"0"とすればよい。特権ビット格納部21の値は、CPU20において実行されるシステムプログラムによって書換え可能であり、アプリケーションプログラムによる書換えは不可能とする。

【0037】

書込み禁止装置22は、リセット装置16に対するリセット要求及び保護設定レジスタ群11に対する書込み要求をCPU20から入力し、特権ビット格納部21に格納された値が特権モードを示す場合に限り、リセット要求及び書込み要求をリセット装置16又は保護設定レジスタ群11に転送する。

【0038】

なお、CPU20は、特権ビット格納部21の書換えを行うことを除いて、発明の実施の形態1のCPU10と同様である。

【0039】

特権ビット格納部21、書込み禁止装置22及びCPU20を除く他の構成要素は、発明の実施の形態1のマイクロコンピュータ1が有する構成要素と同一であるため、詳細な説明を省略する。

【0040】

次に、マイクロコンピュータ2が行うメモリ保護情報の更新処理を図6のフローチャートを用いて説明する。なお、図6において、図4のフローチャートと同様のステップについては、図4と同一の符号を付している。

【0041】

ステップS201では、システムプログラムの命令によって特権ビット格納部21の特権ビットを更新し、特権モードに遷移する。ステップS202では、システムプログラムの命令に応じて、CPU20からリセット装置16に対して有効ビット格納部111B〜11nBのリセット要求が出力される。ステップS202では、書込み禁止装置22が特権ビット格納部21を参照し、特権モードを示す値(ここでは値"1"とする)が設定されている場合に限り、リセット装置16に対してリセット要求を転送する(ステップS203)。書込み禁止装置22からリセット要求を受信したリセット装置16は、有効ビットリセット信号を保護設定レジスタ111〜11nに送信し、有効ビット格納部111B〜11nBを一括して無効状態にリセットする(ステップS102)。

【0042】

続く、ステップS103〜S107までの保護設定レジスタ群11の書換え処理では、ステップS204が本実施の形態に特有の処理である。ステップS204では、書込み禁止装置22が特権ビット格納部21を参照し、特権モードを示す値(ここでは値"1"とする)が設定されている場合に限り、CPU20から入力した書込み要求を保護設定レジスタ群11に転送する。最後のステップS205では、非特権モードを示す状態に特権ビット格納部22を書換えることによって、非特権モードに遷移する。

【0043】

発明の実施の形態1にかかるマイクロコンピュータ1は、保護設定レジスタ群11に対する書込み要求を拒絶する条件が考慮されていないため、アプリケーションプログラムによって生成された書込み要求によって保護設定レジスタ群11が書換えられる可能性がある。これに対して、本実施の形態のマイクロコンピュータ2では、特権モードに遷移していない状態で発行された書込み要求は書込み禁止装置22によって拒絶され、かつ、特権モードのへの遷移はシステムプログラムによって特権ビット格納部21を書換えることによって行われる。このため、非特権モードで動作するアプリケーションプログラムによる書込み要求では、保護設定レジスタ群11の書換えは発生しない。これにより、悪意のあるアプリケーションプログラムによるメモリ保護設定の変更を防止することができる。

【0044】

発明の実施の形態3.

本実施の形態にかかるマイクロコンピュータ3の構成を図7に示す。マイクロコンピュータ3は、書込み禁止ビット格納部31及び書込み禁止装置32を備える点が、発明の実施の形態2にかかるマイクロコンピュータ2と相違している。

【0045】

書込み禁止ビット格納部31は、保護設定レジスタ群11に対する書込みが可能であるか否かを示す書込み禁止ビットを格納する。例えば、書込み禁止ビットを1ビットデータとし、保護設定レジスタ群11に対する書込みが禁止された禁止状態を値"1"とし、逆に、保護設定レジスタ群11に対する書込みが可能な許可状態を値"0"とすればよい。後述するように、保護設定レジスタ群11に対する書込みを禁止する状態の設定は、CPU20において実行されるシステムプログラムによって行われる。また、保護設定レジスタ群11に対する書込みを許可する状態の設定は、リセット装置36によって行われる。

【0046】

書込み禁止装置32は、保護設定レジスタ群11に対する書込み要求書込み禁止装置22から入力し、書込み禁止ビット格納部31に格納された値が書込み許可を示す場合に限り、書込み要求をリセット装置16又は保護設定レジスタ群11に転送する。

【0047】

なお、CPU30は、書込み禁止ビット格納部31の書換えを行うことを除いて、発明の実施の形態2のCPU20と同様である。また、リセット装置36は、書込み禁止ビット格納部31の書換えを行うことを除いて、発明の実施の形態1のリセット装置16と同様である。

【0048】

書込み禁止ビット格納部31、書込み禁止装置32、CPU30及びリセット装置36を除く他の構成要素は、上述したマイクロコンピュータ1又は2が有する構成要素と同一であるため、詳細な説明を省略する。

【0049】

次に、マイクロコンピュータ3が行うメモリ保護情報の更新処理を図8のフローチャートを用いて説明する。なお、図8において、図4又は図6のフローチャートと同様のステップについては、図4又は図6と同一の符号を付している。

【0050】

ステップS301では、システムプログラムの命令によって、書込み禁止ビット格納部31が書込み禁止状態を示す値(ここでは値"1"とする)に設定される。ステップS302では、リセット装置36によって有効ビット格納部111B〜11nBが一括して無効状態にリセットされたことに合わせて、書込み禁止ビット格納部31の値が書込み許可を示す値(ここでは値"0"とする)にリセットされる(ステップS102及びS302)。なお、書込み禁止ビット格納部31のリセットは、有効ビット格納部111B〜11nBをリセットするための有効ビットリセット信号を書込み禁ビット格納部31に入力することによって行えば良い。

【0051】

続く、ステップS103〜S107までの保護設定レジスタ群11の書換え処理では、ステップS303が本実施の形態に特有の処理である。ステップS303では、書込み禁止装置32が書込み禁止ビット格納部31を参照し、保護設定レジスタ群11に対する書込みが可能な許可状態である場合に限り、書込み禁止装置22から入力した書込み要求を保護設定レジスタ群11に転送する。

【0052】

発明の実施の形態1又は2にかかるマイクロコンピュータ1及び2は、リセット装置16によって有効ビット格納部111B〜11nBが全て無効状態とされたことを、保護設定レジスタ群11に対する書込みを許可する条件としていない。このため、プログラム切り替え時の保護設定レジスタ群11の更新において、無効状態とすべき保護設定レジスタに対する設定漏れが発生する可能性がある。

【0053】

これに対して、マイクロコンピュータ3では、書込み禁止ビット格納部31に格納された値が書込み禁止を示している状態で、保護設定レジスタ群11に対する書込み要求が発行された場合、当該書込み要求は書込み禁止装置32によって拒絶される。さらに、マイクロコンピュータ3において、書込み禁止ビット格納部31の値が書込み許可状態となる条件は、リセット装置36によって有効ビット格納部111B〜11nBを全て無効状態とするリセット動作が行われていることである。このため、マイクロコンピュータ3では、有効ビット格納部111B〜11nBを全て無効状態とされていない状態において、保護設定レジスタ群11の書換えが行われることがなく、無効状態とすべき保護設定レジスタに対する設定漏れが発生することを防止できる。

【0054】

発明の実施の形態4.

本実施の形態にかかるマイクロコンピュータ4の構成を図4に示す。マイクロコンピュータ4は、有効ビット格納部111B〜11nBだけでなく、領域指定部111A〜11nAを含む保護設定レジスタ111〜11n全体を、リセット装置46によるリセット対象とすることが特徴である。領域指定部111A〜11nAのリセットは、予め定められた無効値に設定することによって行えば良い。無効値は、メモリ空間のどの領域とも対応しない値を選択すれば良く、例えば、領域指定部111A〜11nAをオールゼロ又はオール1に設定すれば良い。また、領域指定部111A〜11nAがアクセス許可領域のサイズ情報を含む場合は、アクセス許可領域のサイズをゼロに設定しても良い。

【0055】

なお、リセット装置46を除く他の構成要素は、上述したマイクロコンピュータ3が有する構成要素と同一であるため、詳細な説明を省略する。

【0056】

上述したマイクロコンピュータ1乃至3は、リセット装置によるリセット範囲を有効ビット格納部111B〜11nBのみとしている。このため、CPU10乃至30から出力される書込み要求に基づいて有効ビット格納部111B〜11nBが有効状態に更新されたにも関わらず、対応する領域指定部111A〜11nAの値が設定されなかった場合に、誤ったメモリ保護情報が有効となる可能性がある。

【0057】

これに対して、マイクロコンピュータ4では、有効ビット格納部111B〜11nBだけでなく、領域指定部111A〜11nAを含む保護設定レジスタ111〜11n全体を、リセット装置46によるリセット対象としている。このため、仮に、領域指定部111A〜11nAが更新されずに有効ビット格納部111B〜11nBが有効とされる状況が発生しても、この場合の領域指定部111A〜11nAの値は無効な値である。従って、不正なメモリアクセスが許可されることを防止することができる。

【0058】

その他の実施の形態.

上述した発明の実施の形態1乃至4において、リセット装置16、36及び46が行う処理は、CPU10、20又は30と、CPU10、20又は30で実行されるプログラムとによって実現することも可能である。具体的には、実行プログラムの切り替え処理における保護設定レジスタ111〜11nの書換えを行う前に、CPU10に保護設定レジスタ111〜11nを無効化する処理をさせるためのプログラムを実行すればよい。

【0059】

しかしながら、マイクロコンピュータ1のように、CPU10と独立したリセット装置16を設け、CPU10が出力するリセット要求信号に応じてリセット装置16が保護設定レジスタ群11を無効状態に設定する構成が望ましい。このような構成によって、少ない命令の実行、具合的にはリセット要求信号を送信するための1つの命令を実行することで、誤ったメモリ保護設定を排除することができる。

【0060】

また、上述した発明の実施の形態1乃至4では、CPU10で実行されるプログラムによるメモリアクセスを許可する領域を保護設定レジスタ111〜11nに設定することとした。しかしながら、保護設定レジスタ111〜11nには、アクセスを禁止する領域を設定してもよいし、許可領域及び禁止領域を設定してもよい。

【0061】

また、上述した発明の実施の形態1乃至4では、保護設定レジスタ111〜11nの設定内容が有効であるか否かを有効ビット格納部111B〜11nBによって示す構成を説明した。しかしながら、保護設定レジスタ111〜11nの設定内容が有効であるか否かを定めるための構成は、当該構成に限定されない。例えば、非特許文献2に記載されているように、ライトアクセスの許可/不許可、リードアクセスの許可/不許可、実行の許可/不許可を示す識別子によって、保護設定レジスタ111〜11nの設定内容が有効であるか否かを定めても良い。この場合は、ライトアクセス、リードアクセス及び実行を共に不許可に設定することが、保護設定レジスタ111〜11nの設定内容を無効状態に設定することに相当する。

【0062】

また、上述した発明の実施の形態1乃至4では、保護設定レジスタ111〜11nのそれぞれが、領域指定部111A〜11nA、及び有効ビット格納部111B〜11nBを備えることとした。しかしながら、メモリ保護情報を格納する領域と、当該保持後情報の有効性を規定する情報を格納する領域とは、物理的に独立した記憶装置に格納しても良い。

【0063】

また、上述した発明の実施の形態1乃至4において、リセット装置16、36又は46の制御対象である保護設定レジスタ111〜11nによってアクセス制御を行うメモリ空間は、メモリ15の全てに対応するメモリ空間に限られない。例えば、システムプログラムの格納領域など、アプリケーションプログラムによるアクセスを一律に禁止する領域をメモリ15に規定する場合には、このような一律に禁止される領域を除外した領域を、保護設定レジスタ111〜11nによるアクセス制御の対象とすれば良い。

【0064】

また、上述した発明の実施の形態1乃至4において、メモリ15は、マイクロコンピュータ1乃至4の外部に設けられていても良い。また、メモリアクセス制御装置12にメモリコントローラ13を介してメモリ15が接続された構成は一例である。例えば、DMA転送を行う場合には、メモリアクセス制御装置12とメモリ16は、DMA転送を制御するDMAコントローラを介して接続されても良い。

【0065】

さらに、本発明は上述した実施の形態のみに限定されるものではなく、既に述べた本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

【符号の説明】

【0066】

1、2、3、4 マイクロコンピュータ

10、20、30 CPU(Central Processing Unit)

11 保護設定レジスタ群

111〜11n 保護設定レジスタ

111A〜11nA 領域指定部

111B〜11nB 有効ビット格納部

12 メモリアクセス制御装置

13 メモリコントローラ

14 メモリバス

15 メモリ

16、36、46 リセット装置

21 特権ビット格納部

22 書込み禁止装置

31 書込み禁止ビット格納部

32 書込み禁止装置

【特許請求の範囲】

【請求項1】

CPUと、

前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、

前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御装置と、

前記CPUが出力するリセット要求信号に基づいて、前記複数の保護情報格納部に格納されたメモリ保護情報を一括して無効化するリセット装置と、

を備えるマイクロコンピュータ。

【請求項2】

前記保護情報格納部は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記リセット装置は、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項1に記載のマイクロコンピュータ。

【請求項3】

前記保護情報格納部は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記リセット装置は、前記領域指定部の設定内容を消去し、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項1に記載のマイクロコンピュータ。

【請求項4】

複数のプログラムを切り替えて実行するCPUと、

前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、

前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部と、

前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラム対するメモリ保護情報を一括して無効化する無効化手段と、

前記無効化手段による一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって、前記複数の保護情報格納部を更新する更新手段と、

を備えるマイクロコンピュータ。

【請求項5】

前記無効化手段による前記複数の保護情報格納部の設定内容の無効化が行われていない場合に前記更新手段による前記複数の保護情報格納部の更新を禁止する判定部を更に備える請求項4に記載のマイクロコンピュータ。

【請求項6】

前記CPUは、前記CPUで実行されるプログラムの切り替えに応じてリセット要求信号を出力し、

前記無効化手段は、前記リセット要求信号に応じて前記複数の保護情報格納部に格納された前記メモリ保護情報を無効化するリセット装置である請求項4に記載のマイクロコンピュータ。

【請求項7】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記無効化手段は、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項4に記載のマイクロコンピュータ。

【請求項8】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記無効化手段は、前記領域指定部の設定内容を消去し、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項4に記載のマイクロコンピュータ。

【請求項9】

マイクロコンピュータのメモリアクセス制御方法であって、

前記マイクロコンピュータは、CPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部とを備え、

前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラムに対するメモリ保護情報を一括して無効化し、

前記メモリ保護情報の一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって前記複数の保護情報格納部を更新する、方法。

【請求項10】

前記マイクロコンピュータは、前記CPUが出力するリセット要求信号に応じて前記複数の保護情報格納部に格納されたメモリ保護情報を無効化するリセット装置をさらに備えており、

前記メモリ保護情報の無効化は、前記CPUで実行するプログラムの切り替えに応じて前記リセット要求信号を前記リセット装置に送信することにより実行される請求項9に記載の方法。

【請求項11】

前記複数の保護情報格納部の更新の前に、前記メモリ保護情報の無効化が行われたか否かを判定し、前記メモリ保護情報の無効化が未完了の場合に、前記複数の保護情報格納部の更新を禁止する請求項9に記載の方法。

【請求項12】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備えており、

前記メモリ保護情報の無効化は、前記格納部に格納された識別情報を更新することにより行われる請求項9に記載の方法。

【請求項13】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記メモリ保護情報の無効化は、前記領域指定部の設定内容を消去し、前記格納部に格納された識別情報を更新することにより行われる請求項9に記載の方法。

【請求項1】

CPUと、

前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、

前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御装置と、

前記CPUが出力するリセット要求信号に基づいて、前記複数の保護情報格納部に格納されたメモリ保護情報を一括して無効化するリセット装置と、

を備えるマイクロコンピュータ。

【請求項2】

前記保護情報格納部は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記リセット装置は、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項1に記載のマイクロコンピュータ。

【請求項3】

前記保護情報格納部は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記リセット装置は、前記領域指定部の設定内容を消去し、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項1に記載のマイクロコンピュータ。

【請求項4】

複数のプログラムを切り替えて実行するCPUと、

前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、

前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部と、

前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラム対するメモリ保護情報を一括して無効化する無効化手段と、

前記無効化手段による一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって、前記複数の保護情報格納部を更新する更新手段と、

を備えるマイクロコンピュータ。

【請求項5】

前記無効化手段による前記複数の保護情報格納部の設定内容の無効化が行われていない場合に前記更新手段による前記複数の保護情報格納部の更新を禁止する判定部を更に備える請求項4に記載のマイクロコンピュータ。

【請求項6】

前記CPUは、前記CPUで実行されるプログラムの切り替えに応じてリセット要求信号を出力し、

前記無効化手段は、前記リセット要求信号に応じて前記複数の保護情報格納部に格納された前記メモリ保護情報を無効化するリセット装置である請求項4に記載のマイクロコンピュータ。

【請求項7】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記無効化手段は、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項4に記載のマイクロコンピュータ。

【請求項8】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記無効化手段は、前記領域指定部の設定内容を消去し、前記格納部に格納された識別情報を更新することによって、前記保護情報格納部に格納されたメモリ保護情報を無効化する請求項4に記載のマイクロコンピュータ。

【請求項9】

マイクロコンピュータのメモリアクセス制御方法であって、

前記マイクロコンピュータは、CPUと、前記CPUで実行されるプログラムによるメモリ空間へのアクセス許可又は禁止の状態を指定するメモリ保護情報を格納する複数の保護情報格納部と、前記メモリ保護情報に基づいて、前記CPUによるメモリアクセス要求を許可するか否かを判定するメモリアクセス制御部とを備え、

前記CPUで実行するプログラムの切り替えに応じて、前記複数の保護情報格納部に保持された切り替え前の実行プログラムに対するメモリ保護情報を一括して無効化し、

前記メモリ保護情報の一括無効化後に、前記CPUにおいて新たに実行されるプログラムに対応するメモリ保護情報によって前記複数の保護情報格納部を更新する、方法。

【請求項10】

前記マイクロコンピュータは、前記CPUが出力するリセット要求信号に応じて前記複数の保護情報格納部に格納されたメモリ保護情報を無効化するリセット装置をさらに備えており、

前記メモリ保護情報の無効化は、前記CPUで実行するプログラムの切り替えに応じて前記リセット要求信号を前記リセット装置に送信することにより実行される請求項9に記載の方法。

【請求項11】

前記複数の保護情報格納部の更新の前に、前記メモリ保護情報の無効化が行われたか否かを判定し、前記メモリ保護情報の無効化が未完了の場合に、前記複数の保護情報格納部の更新を禁止する請求項9に記載の方法。

【請求項12】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備えており、

前記メモリ保護情報の無効化は、前記格納部に格納された識別情報を更新することにより行われる請求項9に記載の方法。

【請求項13】

前記複数の保護情報格納部の各々は、保護対象とするメモリ空間を指定する領域指定部と、前記領域指定部の設定内容が有効であるか否かを示す識別情報を格納する格納部とを備え、

前記メモリ保護情報の無効化は、前記領域指定部の設定内容を消去し、前記格納部に格納された識別情報を更新することにより行われる請求項9に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−222055(P2011−222055A)

【公開日】平成23年11月4日(2011.11.4)

【国際特許分類】

【出願番号】特願2011−176745(P2011−176745)

【出願日】平成23年8月12日(2011.8.12)

【分割の表示】特願2006−116954(P2006−116954)の分割

【原出願日】平成18年4月20日(2006.4.20)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年11月4日(2011.11.4)

【国際特許分類】

【出願日】平成23年8月12日(2011.8.12)

【分割の表示】特願2006−116954(P2006−116954)の分割

【原出願日】平成18年4月20日(2006.4.20)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]