マイクロプロセッサ

【課題】使い勝手を良くしたマイクロプロセッサを提供する。

【解決手段】パーソナルコンピュータ等に内蔵されるマイクロプロセッサに、ウェイトコントロールレジスタWCR1及びWCR2等のコントロールレジスタを含みかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラBSCを設ける。バスステートコントローラBSCには、シンクロナスDRAM接続時におけるPCカードの起動信号(−OE、−WE)のセットアップ時間を制御するための制御レジスタ(PCR)が設けられる。

【解決手段】パーソナルコンピュータ等に内蔵されるマイクロプロセッサに、ウェイトコントロールレジスタWCR1及びWCR2等のコントロールレジスタを含みかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラBSCを設ける。バスステートコントローラBSCには、シンクロナスDRAM接続時におけるPCカードの起動信号(−OE、−WE)のセットアップ時間を制御するための制御レジスタ(PCR)が設けられる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明はマイクロプロセッサに関し、例えば、その外部バスインターフェイスに利用して特に有効な技術に関するものである。

【背景技術】

【0002】

シンクロナスDRAM(ダイナミック型ランダムアクセスメモリ)等の各種半導体メモリを直結しうる外部バスを具備するマイクロプロセッサ(マイクロコントローラ)が、例えば、日経マグロウヒル社発行の1994年2月14日付『日経エレクトロニクス』第79頁ないし第91頁に記載されている。

【0003】

一方、メモリカード及びI/Oカード等のPCカードがあり、マイクロプロセッサ等にPCカードを結合するためのインターフェイス条件が日本電子工業振興協会(JEIDA)及びPCMCIA(Personal Computer Memory Card International AssocIation)により標準化されている。PCカードインターフェイスには、ガイドラインVer.4.1の『6.電気・インターフェイス仕様』で規定される68ピンのICメモリカードインターフェイス及びI/Oカードインターフェイスが含まれる。また、このようなPCカードインターフェイスに対処するため、82365SL等の専用IC(集積回路)チップが用意されている。

【非特許文献1】日経マグロウヒル社発行1994年2月14日付『日経エレクトロニクス』第79頁ないし第91頁

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来のマイクロプロセッサ等において、PCカードを結合するためのバスは、半導体メモリ等を結合するためのバスとは別個に設けられるとともに、PCカードは上記専用ICチップを介してバスに結合され、そのインターフェイス制御はこれらの専用ICチップによって行われる。このため、パーソナルコンピュータや携帯情報端末等にPCカードインターフェイスを組み込もうとした場合、バス構成が複雑となり設計工数が増大するとともに、マイクロプロセッサの外付け部品が増大する。この結果、パーソナルコンピュータ及び携帯情報端末等の開発期間が増大し、その低コスト化が阻害されるものとなる。

【0005】

この発明の目的は、使い勝手を良くしたマイクロプロセッサを提供することにある。この発明の他の目的は、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し外付け部品数を削減して、その低コスト化を図ることにある。この発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0006】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。すなわち、パーソナルコンピュータ及び携帯情報端末等に内蔵されるマイクロプロセッサに、外部バスに結合されかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラを設ける。このバスステートコントローラBSCには、シンクロナスDRAM接続時におけるPCカードの起動信号(−OE、−WE)のセットアップ時間を制御するための制御レジスタ(PCR)が設けられる。

【0007】

また、外部バスのアドレス空間を所定数のエリアに分割し、各エリアに各種半導体メモリ又はPCカードを固定的に割り当てるとともに、I/Oカードが入出力装置として機能する場合の物理アドレスとメモリとして機能する場合の物理アドレスとを独立に割り当て、マイクロプロセッサに、その内部における論理アドレスを外部バスにおける物理アドレスに変換するためのメモリ管理ユニットを設ける。

【発明の効果】

【0008】

上記した手段によれば、以下の理由により、上記目的が達成される。その物理アドレスによる制約を受けることなくしかもインターフェイス制御のための外付け部品を削減しつつ、各種半導体メモリとメモリカード及びI/Oカード等のPCカードとを直接かつ同時にマイクロプロセッサの外部バスに結合することができる。この結果、マイクロプロセッサの使い勝手を改善できるとともに、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し外付け部品数を削減して、その低コスト化を図ることができる。

【0009】

また、バスステートコントローラBSCには、シンクロナスDRAM接続時におけるPCカードの起動信号(−OE、−WE)のセットアップ時間を制御するための制御レジスタ(PCR)が設けられるので、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間などを制御することが出来る。その結果、PCカードとシンクロナスDRAMとを本発明のマイクロプロセッサMPUに同時に結合させても、本発明のマイクロプロセッサMPUは、不都合なくPCカードとシンクロナスDRAMに対するアクセスを行うことが出来る。

【発明を実施するための最良の形態】

【0010】

図1には、この発明に係るマイクロプロセッサMPUを含むパーソナルコンピュータの一実施例のシステム構成図が示されている。同図において、パーソナルコンピュータは、マイクロプロセッサMPUを搭載したマザーボードMBDをその基本構成要素とする。マザーボードMBDには、特に制限されないが、PCカードスロットPCSL1及びPCSL2を介して2種のPCカードつまりメモリカードMEMC及びI/OカードIOCがそれぞれ結合され、コネクタLCDCON及びKBDCONを介してマンマシンインターフェイスとなる液晶ディスプレイLCD及びキーボードKBDがそれぞれ結合される。

【0011】

メモリカードMEMCは、SRAM(スタティック型RAM),EPROM(電気的に情報の書き込み可能なリードオンリメモリ),EEPROM(電気的に情報の消去・書き込み可能なリードオンリメモリ)あるいはフラッシュEEPROM等から構成され、データ記憶用のカードとされる。一方、I/OカードIOCは、ファクシミリやデータ転送のためのモデム,LANに利用される制御回路,グローバルポジショニングシステム(GPS)に利用される制御回路あるいはスモールコンピュータシステムインターフェイスコントローラ等とされる。

【0012】

マザーボードMBDのマイクロプロセッサMPUには、特に制限されないが、外部バスE−BUSを介して6種の半導体メモリつまりROM,バーストROM(BROM),SRAM,PSRAM(疑似SRAM),DRAM(ダイナミック型RAM)及びシンクロナスDRAM(SDRAM)が結合される。この外部バスE−BUSには、さらにPCカードバッファBUF1及びBUF2ならびにディスプレイコントローラLCDC及びキーボードコントローラKBDCが結合される。このうち、PCカードバッファBUF1及びBUF2には、上記PCカードスロットPCSL1及びPCSL2つまりメモリカードMEMC及びI/OカードIOCがそれぞれ結合され、ディスプレイコントローラLCDC及びキーボードコントローラKBDCには、コネクタLCDCON及びKBDCONつまり液晶ディスプレイLCD及びキーボードKBDがそれぞれ結合される。マザーボードMBDに搭載された各種半導体メモリ,PCカードバッファ及びコントローラには、電源ユニットPOWUから所定の動作電源が供給される。

【0013】

マイクロプロセッサMPUは、ROM又はバーストROMから読み出されるプログラムに従ってステップ動作し、所定の論理演算処理を実行するとともに、パーソナルコンピュータの各部を制御・統括する。また、PCカードバッファBUF1及びBUF2は、PCカードスロットPCSL1又はPCSL2に装着されたメモリカードMEMC又はI/OカードIOCとの間のインターフェイス整合を行い、ディスプレイコントローラLCDC及びキーボードコントローラKBDCは、コネクタLCDCON又はKBDCONを介して結合された液晶ディスプレイLCD又はキーボードKBDを制御する。

【0014】

この実施例において、マイクロプロセッサMPUは、後述するように、外部バスE−BUSに結合されたROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリとメモリカードMEMC及びI/OカードIOC等のPCカードとに対するインターフェイスを並行制御しうるバスステートコントローラBSCを備える。また、外部バスE−BUSのアドレス空間は所定数のエリアに分割され、これらのエリアに半導体メモリ又はPCカードが固定的に割り当てられるとともに、I/OカードがI/Oカードとして機能する場合の物理アドレスが、メモリカードとして機能する場合の物理アドレスとは独立に割り当てられる。

【0015】

このため、マイクロプロセッサMPUは、さらにその内部における論理アドレスを外部バスにおける物理アドレスに変換するメモリ管理ユニットMMUを備える。これらの結果、その物理アドレスによる制約を受けることなくしかもインターフェイス制御のための外付け部品を削減しつつ、各種半導体メモリとPCカードつまりメモリカードMEMC及びI/OカードIOCとを直接かつ同時に外部バスE−BUSに結合でき、これによってマイクロプロセッサMPUの使い勝手を改善できるとともに、パーソナルコンピュータの設計工数を削減し外付け部品数を削減して、その低コスト化を図ることができるものである。

【0016】

図2には、図1のパーソナルコンピュータの三つの実施例の外観構成図が示されている。まず、図2の(a)において、パーソナルコンピュータは、いわゆるノート型とされ、PCカードスロットMSLOT(PCSL1,PCSL2)に装着されたメモリカードMEMC又はI/OカードIOCからなるファイルFfileを内蔵するとともに、入出力装置としてキーボードKB(KBD)及び液晶ディスプレイDP(LCD)を備える。このうち、液晶ディスプレイは内側に折り畳むことができ、これによって携帯に便利な形態とされる。

【0017】

図2の(b)において、パーソナルコンピュータは、いわゆるデスクトップ型とされ、フレキシブルディスクドライブFDDと、図示されないPCカードスロットに装置されたメモリカードMEMC又はI/OカードIOCからなるファイルFfileとを備える。また、入出力装置としてキーボードKB及び液晶ディスプレイDPを備え、フレキシブルディスクドライブFDDには所定のフレキシブルディスクFDが挿入される。これにより、パーソナルコンピュータは、フレキシブルディスクFDによるソフトウェアとしての記憶領域と、ファイルFfileによるハードウェアとしての記憶領域とを併せ持つものとなる。

【0018】

図2の(c)において、パーソナルコンピュータは、いわゆるペンポータブル型とされ、メモリカードMEMC又はI/OカードIOCからなるファイルカードFfileCARDを装着しうる二つのPCカードスロットを備える。また、入出力装置として感圧シート付液晶ディスプレイDP及び入力ペンPENを備え、手書き文字による入力を可能とする。

【0019】

これらの実施例において、パーソナルコンピュータのマザーボードMBDを構成するマイクロプロセッサMPUは、前述のように、各種の半導体メモリとメモリカードMEMC及びI/OカードIOCからなるPCカードとを直接かつ同時に結合しうるインターフェイスを有する。この結果、マザーボードMBDひいてはパーソナルコンピュータの構成が簡素化され、その小型化,軽量化,薄型化が図られて携帯に便利な形態を採りうるとともに、後述するバースト機能等により大容量の情報を高速に入出力することが可能となり、パーソナルコンピュータとしての処理能力が高めるられるものとなる。

【0020】

図3には、図1のパーソナルコンピュータに含まれるマイクロプロセッサMPUの一実施例のブロック図が示され、図4には、マイクロプロセッサMPUの半導体基板(半導体チップ)上でのレイアウトの一実施例が示されている。すなわち、マイクロプロセッサMPUは公知の半導体製造方法によって単結晶シリコンのような半導体基板に形成される。

【0021】

図3において、マイクロプロセッサMPUは、演算器ALUを含むストアドプログラム方式の中央処理ユニットCPUをその基本構成要素とする。この中央処理ユニットCPUには、システムバスS−BUS(第1内部バス)を介して乗算器MULT,メモリ管理ユニットMMUならびにキャッシュメモリCACHEが結合され、メモリ管理ユニットMMUにはアドレス変換バッファTLBが結合される。メモリ管理ユニットMMU及びキャッシュメモリCACHEは、さらにその他方においてキャッシュバスC−BUS(第2内部バス)に結合され、このキャッシュバスC−BUSにはバスステートコントローラBSCが結合される。

【0022】

バスステートコントローラBSCは、その他方において周辺バスP−BUSに結合されるとともに、図示されないバスインターフェイス部及びバスコネクタを介して外部バスE−BUSに結合される。このうち、周辺バスP−BUS(第3内部バス)には、リフレッシュコントローラREFC,ダイレクトメモリアクセスコントローラDMAC,タイマ回路TIM,シリアルコミュニケーションインターフェイスSCI,ディジタル/アナログ変換回路D/A及びアナログ/ディジタル変換回路A/D等の周辺装置コントローラが結合され、外部バスE−BUSには、前記各種の半導体メモリやPCカードを結合するためのPCカードバッファBUF1及びBUF2ならびにディスプレイコントローラLCDC及びキーボードコントローラKBDCが結合される。

【0023】

バスステートコントローラBSC,リフレッシュコントローラREFC,ダイレクトメモリアクセスコントローラDMAC,タイマ回路TIM,シリアルコミュニケーションインターフェイスSCI,ディジタル/アナログ変換回路D/A及びアナログ/ディジタル変換回路A/Dは、さらに割り込みコントローラINTCに結合され、この割り込みコントローラは割り込み要求信号IRQを介して中央処理ユニットCPUに結合される。

【0024】

同図には図示されないが、システムバスS−BUS、キャッシュバスC−BUSおよび周辺バスP−BUSのそれぞれは、アドレス信号を伝送するための内部アドレスバス、データを伝送するための内部データバスおよび、制御信号を伝送するための内部制御バスをそれぞれ含むものとみなされる。一方、外部バスE−BUSは、アドレス信号を伝送するための外部アドレスバス、データを伝送するための外部データバスおよび、制御信号を伝送するための外部制御バスをそれぞれ含むものとみなされる。

【0025】

上記中央処理ユニットCPUは、クロックパルス発生回路CPGから供給される所定のシステムクロック信号に従って同期動作し、キャッシュメモリCACHEから読み出される制御プログラムに従って所定の演算処理を実行するとともに、マイクロプロセッサMPUの各部を制御・統括する。このとき、演算器ALUは所定の算術論理演算を実行し、乗算器MULTはディジタル信号処理等に有効な乗算処理又は積和処理を実行する。

【0026】

上記メモリ管理ユニットMMUは、メモリアクセスに際してマイクロプロセッサMPUの内部つまり中央処理ユニットCPU等から出力される論理アドレスを、アドレス変換バッファ(address translation look-aside buffer )TLBを参照して物理アドレスに変換し、バスステートコントローラBSCを介してマイクロプロセッサMPUの外部つまり外部バスE−BUSに伝達する。キャッシュメモリCACHEは、高速アクセス可能な半導体メモリからなり、外部のROM又はバーストROM等に格納された制御プログラム又はデータ等を所定のブロック単位で読み出し保持して、中央処理ユニットCPUの高速動作に寄与する。

【0027】

一方、バスステートコントローラBSCは、周辺バスP−BUSに結合される各周辺装置コントローラのバスアクセスを管理し、その動作を制御・統括するとともに、外部バスE−BUSに結合される各種の半導体メモリ及びPCカードならびに各種入出力コントローラの動作を制御・統括する。

【0028】

この実施例において、外部バスE−BUSの物理アドレス空間は、特に制限されないが、8つのエリアに分割され、このうち7つのエリアは、所定の組み合わせをもって各種半導体メモリ及びPCカードに固定的に割り当てられる。また、バスステートコントローラBSCは、外部バスE−BUSの各エリアに割り当てられた各種半導体メモリ及びPCカードに対する制御信号のタイミングをそれぞれ所定の条件でかつ並行して制御・管理する機能を有し、これらのタイミング条件を選択的に指定するための各種コントロールレジスタを備える。

【0029】

この結果、外部バスE−BUSには、前記のように、ROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等を含む各種半導体メモリと、メモリカードMEMC及びI/OカードIOCを含むPCカードとを直接かつ同時に結合しうるものとなる。外部バスE−BUSの信号構成ならびにバスステートコントローラBSCの具体的構成については、後で詳細に説明する。

【0030】

次に、周辺装置コントローラの一つであるリフレッシュコントローラREFCは、外部バスE−BUSに結合されたDRAM及びSDRAMのリフレッシュ動作を制御し、ダイレクトメモリアクセスコントローラDMACは、例えば外部バスE−BUSに結合されたROM又はバーストROMとキャッシュメモリCACHE等との間の高速データ転送をサポートする。

【0031】

タイマ回路TIMは、中央処理ユニットCPUに必要な時間管理をサポートとし、シリアルコミュニケーションインターフェイスSCIは、外部の通信制御装置等との間のシリアルデータ転送をサポートする。一方、アナログ/ディジタル変換回路A/Dは、外部のセンサ等から入力されるアナログ信号を所定のディジタル信号に変換し、ディジタル/アナログ変換回路D/Aは、逆に中央処理ユニットCPUから出力されるディジタル信号を所定のアナログ信号に変換して外部出力する。割り込みコントローラINTCは、バスステートコントローラBSCや各周辺装置コントローラの割り込み要求を所定の優先順位で択一的に受理し、割り込み要求信号IRQとして中央処理ユニットCPUに伝達する。

【0032】

この実施例において、マイクロプロセッサMPUを構成する各部は、図4に例示されるように、所定のレイアウト条件をもって1個の半導体基板上に配置される。また、マイクロプロセッサMPUの各部はいわゆるモジュール化され、ユーザ仕様に基づいて選択的に形成され、選択的に有効とされる。

【0033】

図4において、バスコントローラは図3のバスステートコントローラBSCに対応し、Timerはタイマ回路TIMに対応する。また、クロックパルス発生回路CPGにより形成されるシステムクロックは、所定のクロックドライバDriverを介してマイクロプロセッサMPUの各部に分配・供給される。

【0034】

図5には、図3のマイクロプロセッサMPUの外部バスE−BUSにおける物理アドレスの割り当てを説明するための一実施例のアドレスマップが示され、図6には、そのエリア5及びエリア6における物理アドレスの割り当てを説明するための一実施例の部分的なアドレスマップが示されている。まず図5において、この実施例のマイクロプロセッサMPUの外部バスE−BUSの物理アドレス空間は、特に制限されないが、8つのエリア0〜エリア7に分割され、このうちのエリア0〜6の7つが外部バスE−BUSに結合された各種半導体メモリ及びPCカードによって使用可能とされる。

【0035】

このうち、エリア0は、SRAM及びROMを含む通常メモリかバーストROMに対して選択的に割り当てられ、エリア1及びエリア4は通常メモリに選択的に割り当てられる。また、エリア2は、通常メモリ,SDRAM又はDRAMに対して選択的に割り当てられ、エリア3は、通常メモリ,SDRAM,DRAM又はPSRAMに選択的に割り当てられる。一方、エリア5は、通常メモリ又はバーストROMかメモリカードMEMCに選択的に割り当てられ、エリア6は、通常メモリ又はバーストROMかメモリカードMEMC又はI/OカードIOCに選択的に割り当てられる。なお、本明細書において、通常メモリとは、SRAMやROMのように行及び列アドレスが同時に供給されてアクセスされるアドレスノンマルチプレクス型のメモリを意味し、DRAMやSDRAMのように行及び列アドレスが時分割的に供給されてアクセスされるアドレスマルチプレクス型のメモリとは区別される。

【0036】

なお、エリア7は、マイクロプロセッサMPUの内部装置のアドレス、たとえば、CPUの内部レジスタのアドレスや上記周辺装置コントローラ内のレジスタのアドレス、に割り当てられ、外部装置では使用できない。また、エリア0〜エリア6にいずれの半導体メモリ又はPCカードが結合されるかは、後述するバスステートコントローラBSCのバスコントロールレジスタBCR1によって選択的に指定される。

【0037】

この実施例において、マイクロプロセッサMPUのシステムバスS−BUS、キャッシュバスC−BUSおよび周辺バスP−BUSの内部アドレスバスは、32ビットのアドレス信号A0〜A31を転送可能な信号線を含み、マイクロプロセッサMPUの内部における論理アドレスは、これらアドレス信号A0〜A31により択一的に指定されるいわゆる4GB(ギガバイト)のアドレス空間からなる。一方、マイクロプロセッサMPUの外部つまり外部バスE−BUSにおける物理アドレスは、上位3ビットを除く29ビットのアドレス信号A0〜A28により択一的に指定されるが、アドレス信号A0〜A31の上位3ビット、つまり、アドレス信号A26〜A28は、エリア0ないしエリア6を択一的に指定するためのチップセレクト信号−CS0〜−CS6を作成するために供され、下位26ビットのアドレス信号A0〜A25は、各エリア内のアドレスを択一的に指定するために供される。すなわち、外部バスE−BUSにおける外部アドレスバスは、アドレス信号A0〜A25を転送可能な信号線を含む。

【0038】

これにより、エリア0には、16進数表示でH’00000000ないしH’03FFFFFFの物理アドレスが割り当てられ、エリア1には、H’04000000ないし07FFFFFFの物理アドレスが割り当てられる。また、エリア2ないしエリア4には、H’08000000ないしH’0BFFFFFF,H’0C000000ないしH’0FFFFFFFならびにH’10000000ないしH’13FFFFFFの物理アドレスがそれぞれ割り当てられ、エリア5及びエリア6には、H’14000000ないしH’17FFFFFFならびにH’18000000ないしH’1BFFFFFFの物理アドレスがそれぞれ割り当てられる。この結果、各エリアは、いわゆる64MB(メガバイト)の物理アドレス空間を持つものとなる。なお、エリア0〜エリア6の物理アドレスにそれぞれH’20000000×n(n=1〜6)を加えた物理アドレスは、各エリアのシャドウ空間とされ、この乗数nは、論理アドレスの上位3ビットつまりアドレス信号A29〜A31により選択的に指定される。

【0039】

メモリカードMEMC及びI/OカードIOCに割り当てられるエリア5及びエリア6の物理アドレスは、図6に示されるように、さらにそれぞれ二つに分割される。このうち、エリア5では、アドレスH’14000000〜H’15FFFFFFからなる下位の領域が、メモリカードMEMCのためのコモンメモリ又はアトリビュートメモリ領域として割り当てられ、アドレスH’16000000〜H’17FFFFFFからなる上位の領域は、使用禁止領域とされる。また、エリア6では、アドレスH’18000000〜H’19FFFFFFからなる下位の領域が、メモリカードMEMCあるいはI/OカードIOCがメモリとして機能する場合のコモンメモリ又はアトリビュートメモリ領域として割り当てられ、アドレスH’1A000000〜H’1BFFFFFFからなる上位の領域は、I/OカードIOCが入出力装置として機能する場合のI/O領域とされる。この結果、エリア5及びエリア6におけるコモンメモリ又はアトリビュートメモリ領域は、いわゆる32MBのアドレス空間となる。

【0040】

特に制限されないが、エリア6の二分された領域つまりI/OカードIOCがメモリ又は入出力装置のいずれで機能するかは、アドレス信号A25によって選択的に指定され、32MBのアドレス空間は、残り25ビットのアドレス信号A0〜A24により択一的に指定される。周知のように、PCMCIA規格では、PCカードとして最大64MBのアドレス空間を持つことが許されるが、この場合、後述するように、さらに最上位ビットのアドレス信号A25がマイクロプロセッサMPUの出力ポートを介して別経路で出力される。このように、エリア6の物理アドレス空間を二分しアドレスA25により選択的に指定できるようにすることで、エリア6に結合されたI/OカードIOCのメモリ又は入出力装置としての機能をソフトウェアによりダイナミックに切り替えることが可能となり、マイクロプロセッサMPUの利便性が高められる結果となる。

【0041】

上記のようにマイクロプロセッサMPUの物理アドレス空間が8つのエリアに分割され、このうちの7つがマイクロプロセッサMPUの外部バスE−BUSに結合される各種半導体メモリ又はPCカードに固定的に割り当てられる。このことは、ユーザから見た場合、ソフトウェアにおける論理アドレスの配分に制約を与える原因となるように見える。しかし、この実施例では、前述のように、マイクロプロセッサMPUにメモリ管理ユニットMMUが設けられ、その内部における論理アドレスと外部バスE−BUSにおける物理アドレスとの対応は、アドレス変換バッファTLBの書き換え、すなわち、外部バスE−BUSに結合される外部メモリ、たとえば、DRAMなどに記憶されるアドレス変換テーブルのアドレス変換対の内容の書換によって容易に変更可能とされる。このため、ユーザは外部バスE−BUSの物理アドレスによる制約から解放され、自由な論理アドレス空間を有するソフトウェアを構築しうるものとなる。

【0042】

図7及び図8には、図3のマイクロプロセッサMPUの外部バスE−BUSの接続形態を説明するための一実施例の接続図が示されている。また、図9には、図7及び図8の外部バスE−BUSとPCカードが結合される場合の一実施例のインターフェイス構成図が示され、図10及び図11には、図7及び図8の外部バスE−BUSの一実施例の信号構成図が示されている。なお、図7及び図8では、エリア0〜エリア4に結合可能な半導体メモリを適当に割り当てているが、実際にはエリアによって結合可能な組み合わせが制限されるケースもある。図10及び図11は、図7ないし図9の説明の過程で適宜参照されたい。

【0043】

図7において、外部バスE−BUSは、マイクロプロセッサMPUから見てアドレス出力バスとなる26ビットの外部アドレスバスEBA0〜EBA25と、入出力バスとなる32ビットの外部データバスEBD0〜EBD31とを備える。このうち、アドレスバスEBA0〜EBA25を介して伝達されるアドレス信号A0〜A25は、各種半導体メモリ及びPCカードが結合されるすべてのエリアに共通に供給されるが、外部データバスEBD0〜EBD31は、外部バスE−BUSに結合される半導体メモリ及びPCカードのバスサイズに応じて選択的な接続形態を採る。なお、DRAM及びSDRAMにおいては、行及び列アドレスが時分割的にアドレスバス上の同一ラインに供給されるため、DRAM及びSDRAMの各アドレス入力端子は、外部アドレスバスEBA0〜EBA25のうちの所定数のラインに結合されることになる。

【0044】

すなわち、この実施例のマイクロプロセッサMPUでは、後述するバスステートコントローラBSCのバスコントロールレジスタBCR2により、エリア0〜エリア6のバスサイズをエリアごとに指定することができる。このうち、エリア0では、バイト(8ビット),ワード(16ビット),ロングワード(32ビット)のバスサイズを任意に選択できるが、エリア1ないしエリア6では、各エリアがSRAM,ROM又はバーストROMに割り当てられる場合には、バイト,ワード又はロングワードを任意に選択できるが、SDRAM,DRAM又はPSRAMに割り当てられる場合には、メモリコントロールレジスタMCR1との組み合わせによってワード又はロングワードの選択に制限される。さらに、エリア2及びエリア3がDRAMに割り当てられる場合、そのバスサイズはワードのみに制限され、エリア5及びエリア6がPCカードに割り当てられる場合には、バイト又ワードのいずれかが選択される。

【0045】

これにより、下位16ビットのデータバスEBD0〜EBD15は、エリア0〜エリア6に割り当てられたすべての半導体メモリ及びPCカードに結合されるが、上位16ビットのデータバスEBD16〜EBD23ならびにEBD24〜EBD31は、各エリアのバスサイズに応じてそれぞれ選択的に結合されるものとなる。なお、8ビットのデータバスEBD16〜EBD23は、後で例示するように、エリアのバスサイズが16ビット以下であることを条件に、汎用のポートPORT0〜PORT7としても使用できる。ただし、この場合にはバスステートコントローラBSC2のポート機能イネーブルビットが論理“1”にセットされる。

【0046】

外部バスE−BUSは、外部バスE−BUS上のデータが有効であることを示すバススタート信号−BS(ここで、それが有効とされるとき選択的にロウレベルとされるいわゆる反転信号等については、その名称の先頭に−を付加する。以下同様)を伝達するための制御信号線を外部制御バスEBCとして備える。この信号−BSは、バスステートコントローラBSCによって各種半導体メモリ及びPCカードに必要な起動信号に変換される。このため、バススタート信号−BSは、ディスプレイコントローラLCDC及びキーボードコントローラKBDC等のバス管理機能を持つI/Oコントローラには供給されるが、バス管理機能を持たない半導体メモリ及びPCカードには供給されない。

【0047】

一方、外部バスE−BUSの外部制御バスEBCは、エリア0ないしエリア6を択一的に指定するためのチップセレクト信号−CS0〜−CS6を伝達するための制御信号線と、エリア0のバスサイズやエンディアンの指定に供されるモード信号MD3〜MD5を伝達するための制御信号線を備える。このうち、チップセレクト信号−CS5及び−CS6は、エリア5及びエリア6のPCカードに対するカードイネーブル信号−CE1つまり−CE1A及び−CE1Bとしてそれぞれ併用される。また、モード信号MD3及びMD4は、これらのPCカードに対するカードイネーブル信号−CE2つまり−CE2A及び−CE2Bとしてそれぞれ併用され、モード信号MD5は、エリア3に結合される2セット目のDRAMに対するロウアドレスストローブ信号−RAS2として併用される。

【0048】

外部バスE−BUSの外部制御バスEBCは、さらに各種半導体メモリ及びPCカードに対する起動制御信号となるロウアドレスストローブ信号−RASを伝達するための制御信号線と、カラムアドレスストローブ信号−CASLL,−CASLH,−CASHL及び−CASHHのそれぞれを伝達するための制御信号線と、ライトイネーブル信号−WE0〜−WE3ならびにリード・ライトステータス信号RD/−WR,リードコントロール信号−RD,I/Oクロック信号CKIO及びクロックイネーブル信号CKEのそれぞれを伝達するための制御信号線を備える。なお、I/Oクロック信号CKIOは、マイクロプロセッサMPUに入力されるシステムクロックあるいは、SDRAM接続時に、上記SDRAMへ供給される動作クロック信号を示し、上記マイクロプロセッサMPUは、I/Oクロック信号CKIOに基づいて、各種出力信号のタイミング管理を行う。

【0049】

このうち、ロウアドレスストローブ信号−RASは、DRAM及びSDRAMに対するロウアドレスストローブ信号−RASとして供給されるともに、エリア3のPSRAMに対するチップイネーブル信号−CEとしても併用される。また、カラムアドレスストローブ信号−CASLL,−CASLH,−CASHL及び−CASHHは、32ビットバスサイズのDRAMに対して、データバスD0〜D7,D8〜D15,D16〜D23ならびにD24〜D31に対応したカラムアドレスストローブ信号として供給されるが、このうち、カラムアドレスストローブ信号−CASLLは、SDRAMに対するカラムアドレスストローブ信号−CASあるいはPSRAMに対する出力イネーブル信号−OEとして併用され、カラムアドレスストローブ信号−CASHL及び−CASHHは、2セット目のDRAMに対するバイト対応のカラムアドレスストローブ信号−CAS2L及び−CAS2Hとしてそれぞれ併用される。

【0050】

ライトイネーブル信号−WE0〜−WE3は、32ビットバスサイズのSRAM及びPSRAMあるいはSDRAMに対して、データバスEBD0〜EBD7,EBD8〜EBD15,EBD16〜EBD23ならびにEBD24〜EBD31にそれぞれ対応したライトイネーブル信号あるいはデータコントロール信号DQMLL,DQMLU,DQMUL及びDQMUUとして供給されるが、このうち、ライトイネーブル信号−WE2は、エリア6のI/OカードIOCに対するI/Oリードコントロール信号−ICIORDとして併用され、ライトイネーブル信号−WE3は、I/Oライトコントロール信号−ICIOWRとして併用される。

【0051】

リード・ライトステータス信号RD/−WRは、DRAM及びSDRAMに対するライトイネーブル信号−WEとして供給されるとともに、図示されないI/Oコントローラに対するリード・ライト信号R/−Wとして併用される。また、リードコントロール信号−RDは、ROM及びSRAMならびにメモリカードMEMC及びI/OカードIOCに対する出力イネーブル信号−OEとして供給され、I/Oクロック信号CKIOとクロックイネーブル信号CKEは、SDRAMに対して供給される。

【0052】

この実施例において、外部バスE−BUSは、PCカード専用の外部入力バスとしてライトプロテクト信号WPを伝達するための制御信号線を備え、バスコントロール用の信号としてウェイトコントロール信号−WAIT,バスリクエスト信号−BREQ及びバスアクノリジ信号BACKのそれぞれを伝達するための制御信号線を備える。このうち、ライトプロテクト信号WPは、書き込み禁止を必要とするメモリカードMEMCから選択的に入力されるとともに、I/OカードIOCのバスサイズが16ビットであることをマイクロプロセッサMPUに知らせるための16ビットI/Oポート信号−IOIS16としても併用される。

【0053】

ウェイトコントロール信号−WAITは、マイクロプロセッサMPUのサイクル待ち合わせを必要とするPCカード及びI/Oコントローラ等から必要に応じて選択的に入力される。さらに、バスリクエスト信号−BREQは、外部バスE−BUSを専有したいバスマスタから必要に応じて選択的に入力され、バスアクノリジ信号BACKは、これらのバスマスタに対するバス使用許可信号としてマイクロプロセッサMPUから出力される。マイクロプロセッサMPUから出力されライトイネーブル信号−WE1は、ライトイネーブル信号−WE/−PGMとしてPCカードに伝達される。なお、図8に示される各種半導体メモリ及びPCカードは、バスマスタとしての機能を有しない。

【0054】

外部バスE−BUSには含まれないが、メモリカードMEMC及びI/OカードIOCは、PCカードスロットPCSL1及びPCSL2にPCカードが装着されたことを示すカード検出信号−CD1及び−CD2のそれぞれを伝達するための制御信号線と、リセット信号RESETを伝達するための制御信号線とに結合される。これらの制御信号は、マザーボードMBDに設けられたボードコントローラBCで検知され、ボード制御に供される。マザーボードMBDは、さらに動作電源となる電源電圧VCC及び接地電位GNDを入力するための端子を備え、この電源電圧及び接地電位を各種半導体メモリ,PCカード,I/OコントローラならびにマイクロプロセッサMPUに1対の電源供給線を介して分配する。

【0055】

メモリカードMEMC又はI/OカードIOC等のPCカードは、前述のように、PCカードバッファBUF1又はBUF2を介して外部バスE−BUSに結合され、アドレス信号A25は、エリア6のI/OカードIOCがメモリ又は入出力装置のいずれで機能するかを識別するために供される。したがって、メモリカードMEMC及びI/OカードIOCが64MBのアドレス領域を有する場合には、図9に示されるように、マイクロプロセッサMPUのポートPORTを介して、最上位のアドレス選択に供されるアドレス信号A25が改めて出力される。このポートPORTには、リセット信号RESETとアトリビュートメモリ空間選択信号−REGが含まれる。

【0056】

マザーボードMBDは、割り込みレベルIRL0〜IRL3を設定するためのエンコーダENCODRとを備える。これらの信号が、PCMCIA標準に準拠したものであることは言うまでもない。図9に示されるように、PCカードバッファBUF1又はBUF2は、外部データバスEBD0〜EBD7に設けられる双方向バッファB1と、外部データバスEBD8〜EBD15に設けられる双方向バッファB2とを含む。上記双方向バッファB1およびB2は、リード・ライトステータス信号RD/−WRによってデータの伝送方向(DIR)がそれぞれ制御され、カードイネーブル信号−CE1B及び−CE2Bによってそのゲートティング動作(G)がそれぞれ制御される。

【0057】

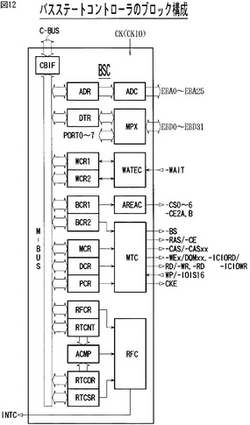

図12には、図3のマイクロプロセッサMPUに含まれるバスステートコントローラBSCの一実施例のブロック図が示されている。同図において、バスステートコントローラBSCは、マイクロプロセッサMPUのキャッシュバスC−BUSに結合されるキャッシュバスインターフェイス部CBIFと、バスステートコントローラBSC内のモジュールバスM−BUSを介してキャッシュバスインターフェイス部CBIFに結合されるアドレスレジスタADR,データレジスタDTR,ウェイトコントロールレジスタWCR1及びWCR2,バスコントロールレジスタBCR1及びBCR2,メモリコントロールレジスタMCR,DRAMコントロールレジスタDCR,PCMCIAコントロールレジスタPCR,リフレッシュカウントレジスタRFCR,リフレッシュタイマカウントレジスタRTCNT,リフレッシュタイムコンスタントレジスタRTCOR及びリフレッシュタイマコントロールステータスレジスタRTCSRとを備える。

【0058】

これらのレジスタの内容は、マイクロプロセッサMPUの中央処理ユニットCPUつまりはそのソフトウェアによって任意に書き換えることができる。すなわち、中央処理ユニットCPUは、キャッシュバスC−BUS、キャッシュバスインターフェイス部CBIF及びモジュールバスM−BUSを介して、各レジスタ(ADR,DTR,WCR1,WCR2,BCR1,BCR2,MCR,DCR,PCMCIA,PCR,RFCR,RTCNT,RTCORおよびRTCSR)の内容の書き込み、あるいは変更を実施できる。

【0059】

上記バスステートコントローラBSCには、動作タイミングを決定するための動作クロックとして、図4に記載されるクロックパルスジェネレータCPGから発生される動作クロックCKがクロックドライバDriverから供給される。このクロック信号CKは、中央処理装置CPUの動作クロックと同一の周波数を有するクロックとされるとともに、上記マイクロプロプロセッサMPUの外部へシステムクロックとしてシステムクロック入出力端子CKIOから出力される。後述されるように、上記システムクロック入出力端子CKIOから出力されるシステムクロックは、シンクロナスDRAMの動作クロックとして利用される。

【0060】

アドレスレジスタADRは、アドレス制御部ADCに結合される。また、データレジスタDTRの出力端子は、マルチプレクサMPXの一方の入力端子に結合され、このマルチプレクサMPXの他方の入力端子は、ポートPORT0〜PORT7に結合される。一方、ウェイトコントロールレジスタWCR1及びWCR2は、ウェイト制御部WATECに結合され、バスコントロールレジスタBCR1は、エリア制御部AREACに結合される。

【0061】

バスコントロールレジスタBCR2ならびにメモリコントロールレジスタMCR,DRAMコントロールレジスタDCR及びPCMCIAコントロールレジスタPCRは、メモリタイミング制御部MTCに結合され、リフレッシュカウントレジスタRFCR,リフレッシュタイマカウントレジスタRTCNT,リフレッシュタイムコンスタントレジスタRTCORならびにリフレッシュタイマコントロールステータスレジスタRTCSRは、リフレッシュ制御部RFCに結合される。

【0062】

アドレス制御部ADCの出力端子は、外部バスE−BUSのアドレスバスEBA0〜EBA25にそれぞれ結合され、マルチプレクサMPXの出力端子はデータバスEBD0〜EBD31にそれぞれ結合される。また、ウェイト制御部WATECの出力信号はウェイトコントロール信号−WAITとなり、エリア制御部AREACの出力信号はチップセレクト信号−CS0〜−CS6ならびにカードイネーブル信号−CE2A及び−CE2Bとなる。

【0063】

メモリタイミング制御部MTCの出力信号は、バススタート信号−BS,ロウアドレスストローブ信号−RAS/チップイネーブル信号−CE,カラムアドレスストローブ信号−CAS/−CASxx(ここで、例えば四つのカラムアドレスストローブ信号−CASLL,−CASLH,−CASHL及び−CASHHを総称して−CASxxのようにxxを付して表す。以下同様),ライトイネーブル信号−WEx/データコントロール信号DQMxx,I/Oリードコントロール信号−ICIORD/I/Oライトコントロール信号−ICIOWR,リード・ライトステータス信号RD/−WR,リードコントロール信号−RD,ライトプロテクト信号WP/16ビットI/Oポート信号−IOIS16ならびにクロックイネーブル信号CKEとなる。

【0064】

アドレス制御部ADCは、キャッシュバスC−BUSのアドレスバスを介して伝達されるアドレス信号A0〜A25を外部バスE−BUSのアドレスバスEBA0〜EBA25に伝達するとともに、一連のアドレスを連続アクセスするためのバーストモードにおいてアドレス信号の所定ビットを自律的に更新するアドレス生成機能を有する。

【0065】

マルチプレクサMPXは、キャッシュバスC−BUS及び外部バスE−BUSのデータバスEBD0〜EBD31を結合するとともに、データバスの所定ビットつまりデータバスEBD16〜EBD23がポートPORT0〜PORT7として使用される場合の切り替え制御を行う。このように、バスステートコントローラBSCにアドレス制御部ADCを設け、バーストモードのためのアドレス生成機能を持たせることで、マイクロプロセッサの外付け部品を増やすことなく、バーストモードを有する半導体メモリ及びPCカードの接続を可能とし、その連続アクセスを高速化することができるものとなる。

【0066】

ウェイト制御部WATECは、外部バスE−BUSのウェイト信号−WAITを介して行われるPCカード又はI/Oコントローラからのサイクル待ち合わせ要求をマイクロプロセッサMPUに伝達する。また、ウェイトコントロールレジスタWCR1及びWCR2に書き込まれた各定数をもとに、リードアクセスからライトアクセスに切り替わった場合のアイドルサイクルの挿入や、各エリアに対するウェイトステート挿入を選択的に実行する。

【0067】

エリア制御部AREACは、バスステートコントロールレジスタラBSC1に書き込まれたエリア0〜エリア6の割り当て等に関する属性とキャッシュバスC−BUSのアドレスバスA26〜A28を介して供給されるエリア選択信号とをもとに、チップセレクト−CS0〜−CS6ならびにカードイネーブル信号−CE2A及び−CE2Bを選択的に形成する。

【0068】

メモリタイミング制御部MTCは、バスコントロールレジスタBCR2に書き込まれたエリア0〜エリア6のバスサイズ等に関する属性やメモリコントロールレジスタMCR,DRAMコントロールレジスタDCR及びPCMCIAコントロールレジスタPCRに書き込まれた定数とをもとに、各種半導体メモリ及びPCカードの動作制御に必要となる起動制御信号等を所定のタイミング条件で選択的に形成する。さらに、リフレッシュ制御部RFCは、リフレッシュカウンタのオーバーフロー割り込み機能を利用して、DRAM及びSDRAM等のリフレッシュ動作を制御する。

【0069】

図13には、図12のバスステートコントローラBSCの一実施例の状態遷移図が示されている。また、図14には、図12のバスステートコントローラBSCの一実施例のステート構成図が示され、図15には、その状態遷移に関する一実施例の遷移条件図が示されている。さらに、図16ないし図18には、図3のマイクロプロセッサMPUのウェイトを伴わないメモリカードMEMCアクセス時,ウェイトを伴うメモリカードMEMCアクセス時ならびにバーストモードを用いたメモリカードMEMCアクセス時の一実施例の信号波形図がそれぞれ示され、図19及び図20には、図3のマイクロプロセッサMPUのウェイトを伴わないI/OカードIOCアクセス時ならびにウェイトを伴うI/OカードIOCアクセス時の一実施例の信号波形図がそれぞれ示されている。

【0070】

以下、図13に沿ってバスステートコントローラBSCの状態遷移に関する具体的な説明を進めるが、図14ないし図20はこれらの説明の過程で随時参照されたい。なお、図13ないし図15に示されるステートは、SRAM,バーストROM及びPCカードの制御に関する部分的なものであり、バスステートコントローラBSCは、他の半導体メモリ等の制御に関する他の多数のステートを有する。

【0071】

図16ないし図20には、参考のため、メモリカードMEMC及びI/OカードIOCに供給されないI/Oクロック信号CKIO,バススタート信号−BS及びリード・ライトステータス信号RD/−WRが併せて示されている。なお、システムクロックあるいは中央処理装置の動作クロックとされるI/Oクロック信号CKIOは、図16ないし図20に示される各種のタイミング信号を作成するための基準クロック信号としての意味を有する。

【0072】

図13において、この実施例のバスステートコントローラBSCは、いわゆるステートマシンとされ、SRAM及びバーストROMならびにメモリカードMEMC及びI/OカードIOCの制御に関する10個のステートST1〜ST10を有する。このうち、ステートST1は、図14に示されるように、IDLEステートであって、マイクロプロセッサMPUの待機状態に対応する。

【0073】

ステートST2〜ST4は、PCMCIA TED1ないしPCMCIA TED3ステートであり、PCMCIAつまりメモリカードMEMC及びI/OカードIOCの起動制御信号となるライトイネーブル信号−WE1及び出力イネーブル信号−OEのアドレス信号A0〜A25に対するセットアップ時間を1サイクル分だけ遅延させるためのものである。

【0074】

ステートST5,ST6及びST7は、それぞれアクセス開始サイクルに対応するNORM T1ステート,ウェイトサイクルに対応するNORM TWステートならびにアクセス終結サイクルに対応するNORM T2ステートであって、ステートST8〜ST10は、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのアドレス信号A0〜A25に対するホールド時間を1サイクル分だけ遅延させるためのPCMCIA TEH1ステート,PCMCIA TEH2ならびにPCMCIA TEH3ステートである。なお、ステートST1〜ST10は、図14の右端欄に示される形で、図16ないし図20の各サイクルと対応する。

【0075】

バスステートコントローラBSCがステートST1のIDLEつまり待機状態にあるとき、外部バスE−BUSが空き状態でメモリつまり外部バスE−BUSに対するアクセス要求が発生しかつPCMCIAコントロールレジスタPCRのセットアップ遅延に関する定数TEDが1〜3である遷移条件(1) が成立すると、バスステートコントローラBSCは、ステートST2に遷移し、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間の遅延サイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、まずTpcm0サイクル又はTpci0サイクルによりバススタート信号−BSつまりはライトイネーブル信号−WE1及び出力イネーブル信号−OE(リードコントロール信号−RD)のセットアップ時間がI/Oクロック信号CKIOの1サイクル分だけ遅延される。

【0076】

ステートST2によるセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが2又は3である遷移条件(4) が成立すると、バスステートコントローラBSCは、ステートST3に遷移し、再びライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間の遅延サイクルに入る。

【0077】

このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、Tpcm0wサイクル又はTpci0wサイクルによりバススタート信号−BSつまりはライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間がさらにI/Oクロック信号CKIOの1サイクル分だけ遅延される。さらに、ステートST3によるセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが2である遷移条件(3) が成立すると、バスステートコントローラBSCは、ステートST5に遷移し、アクセス開始サイクルに入る。

【0078】

このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、Tpcm1サイクル又はTpci1サイクルによりバススタート信号−BSつまりは出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)がロウレベルの有効レベルとされ、アドレス信号A0〜A25により指定されたアドレスに対する実質的なデータの読み出し又は書き込みが実行される。

【0079】

ステートST2においてセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが1である遷移条件(2) が成立すると、バスステートコントローラBSCは、そのままステートST5に遷移し、アクセス開始サイクルに入る。また、ステートST3においてセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが3である遷移条件(5) が成立すると、バスステートコントローラBSCは、ステートST4に遷移し、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間をさらに1サイクル分だけ遅延させる。そして、ステートST4におけるセットアップ時間の1サイクル遅延の終了つまり遷移条件(6) を受けてステートST5に遷移する。

【0080】

一方、ステートST1の待機状態において、外部バスE−BUSが空き状態でメモリアクセス要求が発生しかつPCMCIAコントロールレジスタPCRの定数TEDが0である遷移条件(7) が成立すると、バスステートコントローラBSCは、直接ステートST5に遷移し、アクセス開始サイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図16及び図19に例示されるように、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ遅延のためのサイクルを挟むことなくTpcm1サイクル又はTpci1サイクルが実行され、データの読み出し又は書き込みが行われる。

【0081】

次に、ステートST5によるアクセス開始サイクルが終了し、ウェイトコントロールレジスタWCR2の定数WAITが例えば1である遷移条件(9) が成立すると、バスステートコントローラBSCは、ステートST6に遷移し、ウェイトサイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、二つのTpcm1w又はTpci1wによる1回分のウェイトステートが挿入され、出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)のハイレベルへの立ち上がりつまりデータの読み出し又は書き込み動作の終了が遅らされる。この間、ウェイトコントロール信号−WAITは、I/Oクロック信号CKIOの次の立ち上がりエッジを包含する所定のタイミングでロウレベルとされ、その次の立ち上がりエッジを包含する所定のタイミングでハイレベルに戻される。

【0082】

ステートST6によるウェイトサイクルが終了し遷移条件(12)が成立すると、バスステートコントローラBSCは、ステートST7に遷移し、アクセス終結サイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図16ないし図20に例示されるように、Tpcm2サイクル又はTpci2サイクルによって出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)がハイレベルの無効レベルに戻され、指定されたアドレスに対するデータの読み出し又は書き込み動作が終結する。なお、ステートST6において、ウェイトコントロールレジスタWCR2の定数WAITが2以上とされ引き続きウェイトが必要な遷移条件(10)が成立すると、バスステートコントローラBSCは再度ステートST6によるウェイトサイクルを挿入する。

【0083】

ステートST7によるアクセス終結サイクルが終了すると、バスステートコントローラBSCは、バーストモード又は全サイクルの終結状態とPCMCIAコントロールレジスタPCRの定数TED及びTEHつまりセットアップ時間及びホールド時間の遅延条件とに応じて選択的にステートST1,ST2,ST5又はST6に遷移する。すなわち、バスステートコントローラBSCは、ステートST7のアクセス終結サイクル時にバーストモードが未終了である遷移条件(12)が成立した場合、ステートST6に戻り、バーストモードが終了するまでこれを繰り返す。このとき、メモリカードMEMC及びI/OカードIOCでは、図18に例示されるように、バススタート信号−BS及び出力イネーブル信号−OE等がバースト回数だけ断続して形成されるとともに、バスステートコントローラBSCのアドレス制御部ADCにより下位4ビットのアドレス信号A0〜A3が順次生成され、一連のアドレスに対する連続アクセスが行われる。

【0084】

一方、ステートST7のアクセス終結サイクル時、例えばバスサイズが小さいためにバイト又はワード単位の分割アクセスが行われその全サイクルが未終了であって、かつセットアップ時間及びホールド時間の遅延が必要ない遷移条件(13)が成立した場合、バスステートコントローラBSCは、ステートST5に戻り、アクセスを繰り返す。このとき、セットアップ時間の遅延が必要な遷移条件(14)が成立すると、バスステートコントローラBSCは、ステートST2に遷移し、またホールド時間の遅延が必要な遷移条件(16)ないし(18)が成立すると、その遅延サイクル数に応じてステートST8,ST9又はST10に遷移する。

【0085】

エリア5及びエリア6におけるメモリカードMEMC及びI/OカードIOCのバーストモードは、キャッシュファイルの際の16バイトのアクセスをバーストROMのページモードと同様な形で実現するためのものである。このとき、バーストモードのデータ転送回数は、バスコントロールレジスタBCR1により設定可能とされ、4回,8回又は16回連続アクセスを任意に選択できる。バーストモードによる読み出し時の先頭アクセスサイクルでは、読み出し要求発生の原因となったデータのアクセスが行われ、残りのサイクルでは、当該データを含む16バイトバウンダリのデータがラップアラウンドでアクセスされる。バーストモードによる書き込み時は、16バイトバウンダリのデータに対応して先頭から順次書き込みが行われる。先頭アクセス時及び2回目以降のアクセス時のウェイトステートの挿入回数は、前述のように、ウェイトコントロールレジスタWCR2の定数WAITによって選択的に設定可能とされる。

【0086】

ステートST7のアクセス終結サイクル時に全サイクルの終了が確認されかつホールド時間の遅延が必要ない遷移条件(15)が成立した場合、バスステートコントローラBSCは、ステートST1に戻る。また、このとき、PCMCIAコントロールレジスタPCRの定数TEHが1以上とされホールド時間の遅延が必要な遷移条件(16)ないし(18)が成立した場合、バスステートコントローラBSCはその遅延サイクル数つまりPCMCIAコントロールレジスタPCRの定数TEHの値に応じて選択的にステートST8,ST9又はST10に遷移する。

【0087】

バスステートコントローラBSCが遷移条件(16)の成立を受けてステートST8の遅延サイクルに遷移したとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、Tpcm2wサイクル又はTpci2wサイクルが挿入され、出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)の立ち上がりからアドレス信号A0〜A25の次の遷移までのホールド時間が1サイクル分だけ遅延される。また、バスステートコントローラBSCが遷移条件(17)の成立を受けてステートST9の遅延サイクルに遷移すると、Tpcm2wサイクル又はTpci2wサイクルが2回挿入されてそのホールド時間が2サイクル分遅延され、バスステートコントローラBSCが遷移条件(18)の成立を受けてステートST9の遅延サイクルに遷移した場合には、Tpcm2wサイクル又はTpci2wサイクルが3回挿入されてそのホールド時間が3サイクル分遅延される。

【0088】

ステートST8では、その遅延サイクル終了に際してステートST7と同様な終結条件の選択が行われ、バスステートコントローラBSCは、全サイクルの終結状態とPCMCIAコントロールレジスタPCRの定数TEDつまりセットアップ時間の遅延条件とに応じて選択的にステートST1,ST2又はST5に遷移する。すなわち、バスステートコントローラBSCは、ステートST8の遅延サイクル終了時に全サイクルが未終了でありかつセットアップ時間の遅延が必要ない遷移条件(22)の成立を受けてステートST5に、またセットアップ時間の遅延が必要な遷移条件(21)の成立を受けてステートST2にそれぞれ戻り、アクセスを繰り返す。そして、ステートST8で全サイクルの終了が確認され遷移条件(23)が成立すると、ステートST1に戻って待機状態となる。

【0089】

このように、各種半導体メモリやPCカードに対応しうる複雑な機能を有するバスステートコントローラBSCをステートマシンとし、その遷移条件を各コントロールレジスタの定数書き換えにより選択的に設定できるようにすることで、外部バスE−BUSのエリア0ないしエリア6におけるインターフェイス条件を各エリアに結合された半導体メモリ又はPCカードのそれに効率良く適合させることができるとともに、バスステートコントローラBSC自体の論理構成を簡素化し、そのシステム柔軟性を高めることができるものとなる。

【0090】

図21は、シンクロナスDRAMとPCカード(MEMC/(IOC))とを本発明のマイクロプロセッサMPUに接続した場合の接続例を示している。PCカード(MEMC/(IOC))とマイクロプロセッサMPUとの接続に関しては、図9において詳細に説明されているので、図21には、その1部分についてのみ図示される。また、PCカード(MEMC/(IOC))とマイクロプロセッサMPUとの接続に関しての説明は、図9において詳細に説明されているので、この図では行われない。

【0091】

図21に示されるように、SDRAM1およびSDRAM2のそれぞれは、256K×16ビットのメモリ構成にされる。SDRAM1は、マイクロプロセッサMPUから出力されるアドレス信号A11−A2を受けるように結合されたアドレス端子A9−A0と、マイクロプロセッサMPUのシステムクロック入出力端子CKIOに結合されたクロック端子CKLと、マイクロプロセッサMPUのクロックイネーブル信号端子CKEに結合されたクロックイネーブル信号端子CKEと、マイクロプロセッサMPUのチップセレクト信号端子−CS3に結合されたチップセレクト信号端子−CSと、マイクロプロセッサMPUのロウアドレスストローブ信号端子−RAS/−CEに結合されたロウアドレスストローブ信号端子−RASと、マイクロプロセッサMPUのカラムアドレスストローブ信号端子−CAS/−OEに結合されたカラムアドレスストローブ信号端子−CASと、マイクロプロセッサMPUのリード・ライトステータス信号端子RD/−WRに結合されたライトイネーブル信号端子−WEと、マイクロプロセッサMPUのデータ入出力端子D31−D16にそれぞれ結合されたデータ入出力端子I/O15−I/O0、マイクロプロセッサMPUのデータコントロール信号端子DQMUU及びDQMULにそれぞれ結合されたデータコントロール信号端子DQMU及びDQMLをと有する。

【0092】

SDRAM2は、マイクロプロセッサMPUから出力されるアドレス信号A11−A2を受けるように結合されたアドレス端子A9−A0と、マイクロプロセッサMPUのシステムクロック入出力端子CKIOに結合されたクロック端子CKLと、マイクロプロセッサMPUのクロックイネーブル信号端子CKEに結合されたクロックイネーブル信号端子CKEと、マイクロプロセッサMPUのチップセレクト信号端子−CS3に結合されたチップセレクト信号端子−CSと、マイクロプロセッサMPUのロウアドレスストローブ信号端子−RAS/−CEに結合されたロウアドレスストローブ信号端子−RASと、マイクロプロセッサMPUのカラムアドレスストローブ信号端子−CAS/−OEに結合されたカラムアドレスストローブ信号端子−CASと、マイクロプロセッサMPUのリード・ライトステータス信号端子RD/−WRに結合されたライトイネーブル信号端子−WEと、マイクロプロセッサMPUのデータ入出力端子D15−D0にそれぞれ結合されたデータ入出力端子I/O15−I/O0、マイクロプロセッサMPUのデータコントロール信号端子DQMLU及びDQMLLにそれぞれ結合されたデータコントロール信号端子DQMU及びDQMLをと有する。

【0093】

図21に示されるように、マイクロプロセッサMPUと高速なアドレスアクセス時間を有するシンクロナスDRAM(SDRAM1,SDRAM2)とを結合することによって、32ビット幅のメモリとして上記シンクロナスDRAM(SDRAM1,SDRAM2)を利用することが出来る。マイクロプロセッサMPUのシステムクロック入出力端子CKIOから出力されるシステムクロック信号は、中央処理装置CPUの動作クロックと同一の周波数を有するクロック信号であり、かつ、バスステートコントローラBSCにも供給される。

【0094】

図22は、図21に示される上記シンクロナスDRAM(SDRAM1,SDRAM2)のバーストリード動作を説明するためのバスサイクル波形図を示している。なお、同図では省略されているが、クロックイネーブル信号CKEはハイレベルにされている。クロックイネーブル信号CKEは、上記シンクロナスDRAMにリフレッシュ動作させるとき、選択的に、ロウレベルにされる。バススタート信号−BSは、バスサイクルをモニタするためのストローブ信号であり、上記シンクロナスDRAMには接続されない。

【0095】

最初のサイクルTrでは、上記シンクロナスDRAMが割り当てられた空間に対応した信号−CS3がロウレベルにされ、ロウアドレスストローブ信号−RASがロウレベルにされて、上記シンクロナスDRAMにロウアドレスが取り込まれる。次のサイクルTc では、カラムアドレスストローブ信号−CASがロウレベルにされて、上記シンクロナスDRAMにカラムアドレスが取り込まれる。このように中央処理装置CPU側からのクロック信号CKIOの立ち上がりエッジに同期して出力される信号−CS2、−RASや−CAS及びアドレス信号に対して、上記シンクロナスDRAMにおいてクロック信号CKIOの立ち上がりエッジに同期して上記各信号が取り込まれる。すなわち、上記シンクロナスDRAMの読み出し動作ないし図示されない各種動作は、クロック信号CKIOに基づき制御される。

【0096】

3番目のサイクルTd1では、−CASがハイレベルにリセットされる。そして、3番目以降Td 1〜Td 4の4サイクルにわたって上記シンクロナスDRAMからデータD31〜D0が、1D−4Dとして示すように、連続して読み出される。このようなバーストリードによって、4バイト×4サイクル=16バイトのデータを読み出すことができる。上記のようなタイミングでの制御信号の発生は、前記バスステートコントローラBCSにより形成される。

【0097】

図23には、上記シンクロナスDRAM(以下、単にSDRAMという)の一実施例のブロック図が示されている。同図に示されたSDRAMは、特に制限されないが、公知の半導体集積回路の製造技術によって単結晶シリコンのような1つの半導体基板上に形成される。

【0098】

この実施例のSDRAMは、メモリバンクA(BANKA)を構成するメモリアレイ200Aと、メモリバンク(BANKB)を構成するメモリアレイ200Bを備える。それぞれのメモリアレイ200Aと200Bは、マトリクス配置されたダイナミック型メモリセルを備え、図に従えば同一列に配置されたメモリセルの選択端子は列毎のワード線(図示せず)に結合され、同一行に配置されたメモリセルのデータ入出力端子は行毎に相補データ線(図示せず)に結合される。

【0099】

上記メモリアレイ200Aの図示しないワード線はロウデコーダ201Aによるロウアドレス信号のデコード結果に従って1本が選択レベルに駆動される。メモリアレイ200Aの図示しない相補データ線はセンスアンプ及びカラム選択回路202Aに結合される。センスアンプ及びカラム選択回路202Aにおけるセンスアンプは、メモリセルからのデータ読出しによって夫々の相補データ線に現れる微小電位差を検出して増幅する増幅回路である。それにおけるカラムスイッチ回路は、相補データ線を各別に選択して相補共通データ線204に導通させるためのスイッチ回路である。カラムスイッチ回路はカラムデコーダ203Aによるカラムアドレス信号のデコード結果に従って選択動作される。

【0100】

メモリアレイ200B側にも同様にロウデコーダ201B,センスアンプ及びカラム選択回路202B,カラムデコーダ203Bが設けられる。上記相補共通データ線204は入力バッファ210の出力端子及び出力バッファ211の入力端子に接続される。入力バッファ210の入力端子及び出力バッファ211の出力端子は16ビットのデータ入出力端子I/O0〜I/O15に接続される。

【0101】

アドレス入力端子A0〜A9から供給されるロウアドレス信号とカラムアドレス信号はカラムアドレスバッファ205とロウアドレスバッファ206にアドレスマルチプレクス形式で取り込まれる。供給されたアドレス信号はそれぞれのバッファが保持する。ロウアドレスバッファ206はリフレッシュ動作モードにおいてはリフレッシュカウンタ208から出力されるリフレッシュアドレス信号をロウアドレス信号として取り込む。カラムアドレスバッファ205の出力はカラムアドレスカウンタ207のプリセットデータとして供給され、カラムアドレスカウンタ207はコマンドなどで指定される動作モードに応じて、上記プリセットデータとしてのカラムアドレス信号、又はそのカラムアドレス信号を順次インクリメントした値を、カラムデコーダ203A,203Bに向けて出力する。

【0102】

コントローラ212は、特に制限されないが、クロック信号CKIOが入力される入力端子CLKと、クロックイネーブル信号CKEが入力される入力端子と、チップセレクト信号−CSが入力される入力端子と、カラムアドレスストローブ信号−CASが入力される入力端子、ロウアドレスストローブ信号−RASが入力される入力端子と、及びライトイネーブル信号−WEが入力される入力端子と、データコントロール信号DQMU,DQMLが入力される入力端子とに結合される。コントローラ212は、上記各入力端子から供給される外部制御信号とアドレス入力端子A0〜A9からの制御データとが供給され、これらの信号のレベルの変化やタイミングなどに基づいてSDRAMの動作モード及び上記回路ブロックの動作を制御するための内部タイミング信号を形成するもので、そのためのコントロールロジック(図示せず)とモードレジスタ30を備える。

【0103】

クロック信号CKIOはSDRAMのマクタクロックとされ、その他の外部入力信号は当該クロック信号CKIOの立ち上がりエッジに同期して有意とされる。チップセレクト信号−CSはそのロウレベルによってコマンド入力サイクルの開始を指示する。チップセレクト信号−CSがハイレベルのとき(チップ非選択状態)やその他の入力は意味を持たない。但し、メモリバンクの選択状態やバースト動作などの内部動作はチップ非選択状態への変化によって影響されない。−RAS,−CAS,−WEの各信号は通常のDRAMにおける対応信号とは機能が相違され、コマンドサイクルを定義するときに有意の信号とされる。

【0104】

上記ロウアドレス信号は、クロック信号CKIOの立ち上がりエッジに同期するロウアドレスストローブ・バンクアクティブコマンドサイクルにおけるA0〜A8のレベルによって定義される。A9からの入力は、上記ロウアドレスストローブ・バンクアクティブコマンドサイクルにおいてバンク選択信号とみなされる。即ち、A9の入力がロウレベルの時はメモリバンクBANKAが選択され、ハイレベルの時はメモリバンクBANKBが選択される。メモリバンクの選択制御は、特に制限されないが、選択メモリバンク側のロウデコーダのみの活性化、非選択メモリバンク側のカラムスイッチ回路の全非選択、選択メモリバンク側のみの入力バッファ210及び出力バッファ211への接続などの処理によって行うことができる。

【0105】

プリチャージコマンドサイクルにおけるA8の入力は相補データ線などに対するプリチャージ動作の態様を指示し、そのハイレベルはプリチャージの対象が双方のメモリバンクであることを指示し、そのロウレベルは、A9で指示されている一方のメモリバンクがプリチャージの対象であることを指示する。上記カラムアドレス信号は、クロック信号CKIOの立ち上がりエッジに同期するリード又はライトコマンド(カラムアドレス・リードコマンド、カラムアドレス・ライトコマンド)サイクルにおけるA0〜A7のレベルによって定義される。そして、この様にして定義されたカラムアドレスはバーストアクセスのスタートアドレスとされる。

【0106】

このように、シンクロナスDRAMの動作は、クロック信号CKIOに基づいて制御されている。一方、PCカードとしてのメモリカードMEMCないしI/OカードIOCの動作制御も、バスステートコントローラBSCの動作説明から理解されるように、クロック信号CKIOに基づいて制御されている。したがって、シンクロナスDRAMを高速に動作させながら、PCカード(メモリカードMEMC、I/OカードIOC)の動作制御させる場合、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間などが、PCカードの規格を満足できない場合が発生する。

【0107】

そのため、バスステートコントローラBSCの動作説明ないし図17及び図20から理解されるように、バスステートコントローラBSCにPCMCIAコントロールレジスタPCRが設けられ、PCMCIAコントロールレジスタPCRのセットアップ遅延の関する定数TEDないしホールド遅延に関する定数TEHに基づいて、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間やホールド時間などが制御される。

【0108】

このように、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間などを制御することが出来るので、PCカードとシンクロナスDRAMとを本発明のマイクロプロセッサMPUに同時に結合させても、本発明のマイクロプロセッサMPUは、不都合なくPCカードとシンクロナスDRAMに対するアクセスを行うことが出来る。

【0109】

以上の実施例により得られる作用効果は、下記の通りである。すなわち、

(1)パーソナルコンピュータ等に内蔵されるマイクロプロセッサに、外部バスに結合されかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラを設けることで、インターフェイス制御のための外付け部品を削減しつつ、各種の半導体メモリ及びPCカードを直接かつ同時にマイクロプロセッサの外部バスに結合することができるという効果が得られる。

【0110】

(2)上記(1)項において、外部バスのアドレス空間を所定数のエリアに分割し、これらのエリアに各種半導体メモリ又はPCカードを固定的に割り当てるとともに、マイクロプロセッサにその内部における論理アドレスを外部バスにおける物理アドレスに変換するメモリ管理ユニットを設けることで、外部バスE−BUSの物理アドレスによる制約からユーザを解放し、自由な論理アドレス空間を有するソフトウェアを構築できるという効果が得られる。

【0111】

(3)上記(1)項及び(2)項において、I/Oカードの物理アドレス空間をさらに二分し、I/Oカードがメモリとして機能する場合の物理アドレスと入出力装置として機能する場合の物理アドレスとを独立に割り当てるとともに、これらのアドレス空間をアドレス信号の所定ビットにより選択的に指定できるようにすることで、I/Oカードのメモリ又は入出力装置としての機能をソフトウェアによりダイナミックに切り替えることができるという効果が得られる。

【0112】

(4)上記(1)項ないし(3)項において、バスステートコントローラをステートマシンとし、各エリアに割り当てられた半導体メモリ又はPCカードの種類及びその動作条件等をソフトウェアによって容易に設定しうるコントロールレジスタを設けることで、各エリアにおけるインターフェイス条件を対応する半導体メモリ又はPCカードのインターフェイス条件に効率良く適合させることができるとともに、バスステートコントローラ自体の論理構成を簡素化し、そのシステムの柔軟性を高めることができる

【0113】

(5)上記(1)項ないし(4)項において、バスステートコントローラに、バーストモードのためのアドレス生成機能を持たせることで、マイクロプロセッサの外付け部品を増やすことなく、バーストモードを有する半導体メモリ及びPCカードを結合し、そのアクセスを高速化できるという効果が得られる。

【0114】

(6)上記(1)項ないし(5)項により、マイクロプロセッサの使い勝手を改善できるとともに、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し外付け部品数を削減して、その低コスト化を図ることができるという効果が得られる。

【0115】

以上、本発明者によってなされた発明を実施例に基づき具体的に説明したが、この発明は、上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。例えば、図1において、マイクロプロセッサMPUつまりマザーボードMBDの外部バスE−BUSに結合される半導体メモリ及びPCカードの種類及び数ならびにその組み合わせは、種々の実施形態を採りうる。また、パーソナルコンピュータは、各種の入出力装置を備えることができるし、そのブロック構成や接続形態も任意である。図2において、パーソナルコンピュータの外観構成は、これらの実施例による制約を受けない。図3において、マイクロプロセッサMPUは任意のブロック構成を採りうるし、そのバス形態も任意である。図4において、示されるマイクロプロセッサMPUの基板配置は本の一例であって、本発明に制約を与えない。

【0116】

図5及び図6において、外部バスE−BUSの物理アドレス空間は、任意数のエリアに分割できるし、その各種半導体メモリ及びPCカードに対する割り当ても任意に設定できる。図7ないし図11において、外部バスE−BUSの信号構成や各信号の有効レベル及び機能ならびに各種半導体メモリ及びPCカードとの組み合わせ等は、これらの実施例による制約を受けない。

【0117】

図12において、バスステートコントローラBSCのブロック構成は、設けられるレジスタの種類及び組み合わせを含めて任意である。図13ないし図15において、バスステートコントローラBSCのステートマシンとしての論理構成ならびに各ステートの機能及び遷移条件等は、種々の実施形態を採りうる。図16ないし図20において、各アクセスモードにおけるアドレス信号及び起動制御信号等の論理レベル及び時間関係等は、この実施例により制約されない。

【0118】

以上の説明では、主として本発明者によってなされた発明をその背景となった利用分野であるパーソナルコンピュータを構成するマイクロプロセッサに適用した場合について説明したが、それに限定されるものではなく、例えば、各種の携帯情報端末及びコンピュータを構成する同様なマイクロプロセッサにも適用できる。この発明は、少なくとも外部バスを有するマイクロプロセッサならびにこのようなマイクロプロセッサを含む装置又はシステムに広く適用できる。

【0119】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。すなわち、パーソナルコンピュータ及び携帯情報端末等に内蔵されるマイクロプロセッサに、その外部バスに結合されかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラを設けることで、インターフェイス制御のための外付け部品を削減しつつ、各種半導体メモリ及びPCカードとを直接かつ同時にマイクロプロセッサに結合できる。

【0120】

マイクロプロセッサの外部バスのアドレス空間を所定数のエリアに分割し、各エリアに各種半導体メモリ又はPCカードを固定的に割り当てるとともに、マイクロプロセッサにその内部における論理アドレスを外部バスにおける物理アドレスに変換するメモリ管理ユニットを設けることで、マイクロプロセッサの外部バスの物理アドレスによる制約からユーザを解放し、自由な論理アドレス空間を有するソフトウェアを構築することができる。

【0121】

I/Oカードの物理アドレス空間をさらに二分割し、I/Oカードがメモリとして機能する場合の物理アドレスと入出力装置として機能する場合のそれとを独立に割り当てるとともに、これらのアドレス空間をアドレス信号の所定ビットにより選択できるようにすることで、I/Oカードのメモリ又は入出力装置としての機能をソフトウェアによりダイナミックに切り替えることができる。

【0122】

バスステートコントローラをステートマシンとし、各エリアに割り当てられた半導体メモリ又はPCカードの種類及びその動作条件等をソフトウェアにより容易に設定しうるコントロールレジスタを設けることで、各エリアにおけるインターフェイス条件を対応する半導体メモリ又はPCカードのインターフェイス条件に効率良く適合させることができるとともに、バスステートコントローラ自体の論理構成を簡素化し、そのシステムの柔軟性を高めることができる。

【0123】

バスステートコントローラに、一連のアドレスを連続アクセスするバーストモードのためのアドレス生成機能を持たせることで、マイクロプロセッサの外付け部品を増やすことなく、バーストモードを有する半導体メモリ及びPCカードをマイクロプロセッサに結合し、そのアクセスを高速化できる。

【0124】

以上の結果、マイクロプロセッサの使い勝手を改善できるとともに、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し、その外付け部品数を削減して、パーソナルコンピュータ等の低コスト化を図ることができる。

【図面の簡単な説明】

【0125】

【図1】この発明に係るマイクロプロセッサを含むパーソナルコンピュータの一実施例を示すシステム構成図である。

【図2】図1のパーソナルコンピュータの一実施例を示す外観構成図である。

【図3】図1のパーソナルコンピュータに含まれるマイクロプロセッサの一実施例を示すブロック図である。

【図4】図3のマイクロプロセッサの一実施例を示す基板配置図である。

【図5】図3のマイクロプロセッサの外部バスのアドレス空間を説明するための一実施例を示すアドレスマップ図である。

【図6】図3のマイクロプロセッサの外部バスのエリア5及びエリア6におけるアドレス空間を説明するための一実施例を示すアドレスマップ図である。

【図7】図3のマイクロプロセッサの外部バスの接続形態を説明するための一実施例を示す部分的な接続図である。

【図8】図3のマイクロプロセッサの外部バスの接続形態を説明するための一実施例を示す他の部分的な接続図である。

【図9】図7及び図8の外部バスにPCカードが結合される場合の一実施例を示す部分的なインターフェイス構成図である。

【図10】図7及び図8の外部バスの一実施例を示す部分的な信号構成図である。

【図11】図7及び図8の外部バスの一実施例を示す他の部分的な信号構成図である。

【図12】図3のマイクロプロセッサに含まれるバスステートコントローラの一実施例を示すブロック図である。

【図13】図12のバスステートコントローラの一実施例を示す状態遷移図である。

【図14】図13のバスステートコントローラの一実施例を示すステート構成図である。

【図15】図13のバスステートコントローラの状態遷移を説明するための一実施例を示す遷移条件図である。

【図16】図3のマイクロプロセッサのウェイトを伴わないメモリカードアクセス時の一実施例を示す信号波形図である。

【図17】図3のマイクロプロセッサのウェイトを伴うメモリカードアクセス時の一実施例を示す信号波形図である。

【図18】図3のマイクロプロセッサのバーストモードを用いたメモリカードアクセス時の一実施例を示す信号波形図である。

【図19】図3のマイクロプロセッサのウェイトを伴わないI/Oカードアクセス時の一実施例を示す信号波形図である。

【図20】図3のマイクロプロセッサのウェイトを伴うI/Oカードアクセス時の一実施例を示す信号波形図である。

【図21】図3のマイクロプロセッサにPCカードとシンクロナスDRAMとが結合される場合の一実施例を部分的に示すインターフェイス構成図である。

【図22】シンクロナスDRAMアクセス時の一実施例を示す信号波形図である。

【図23】シンクロナスDRAMの一実施例を示すブロック図である。

【符号の説明】

【0126】

MBD…マザーボード、POWU…電源ユニット、MPU…マイクロプロセッサ、E−BUS…外部バス、ROM…リードオンリメモリ、BROM…バーストROM、SRAM…スタティック型RAM、PSRAM…疑似SRAM、DRAM…ダイナミック型RAM、SDRAM…シンクロナスDRAM、BUF1〜BUF2…PCカードバッファ、PCSL1〜PCSL2…PCカードスロット、MEMC…メモリカード、IOC…I/Oカード、LCDC…ディスプレイコントローラ、LCDCON…ディスプレイ用コネクタ、LCD(DP)…液晶ディスプレイ、KBDC…キーボードコントローラ、KBDCON…キーボード用コネクタ、KBD(KB)…キーボード、

MSLOT…PCカードスロット、Ffile…ファイル、FDD…フレキシブルディスクドライブ、PEN…入力ペン。

CPU…中央処理ユニット、ALU…演算器、MULT…乗算器、MMU…メモリ管理ユニット、TLB…アドレス変換テーブル、CACHE(Cache)…キャッシュメモリ、BSC…バスステートコントローラ、REFC…リフレッシュコントローラ、DMAC…ダイレクトメモリアクセスコントローラ、TIM(Timer)…タイマ回路、SCI…シリアルコミュニケーションインターフェイス、D/A(D/Aconverter)ディジタル/アナログ変換回路、A/D(A/Dconverter)…アナログ/ディジタル変換回路、INTC…割り込みコントローラ、CPG…クロック発生回路、S−BUS…システムバス、C−BUS…キャッシュバス、P−BUS…周辺バス、

ENCODR…エンコーダ、OG…オアゲート、PORT…ポート、

CBIF…キャッシュバスインターフェイス部、M−BUS…BSCモジュールバス、ADR…アドレスレジスタ、ADC…アドレス制御部、DTR…データレジスタ、MPX…マルチプレクサ、WCR1〜WCR2…ウェイトコントロールレジスタ、WATEC…ウェイト制御部、BCR1〜BCR2…バスコントロールレジスタ、AREAC…エリア制御部、MCR…メモリコントロールレジスタ、DCR…DRAMコントロールレジスタ、PCR…PCMCIAコントロールレジスタ、MTC…メモリタイミング制御部、RFCR…リフレッシュカウントレジスタ、RTCNT…リフレッシュタイマカウントレジスタ、RTCOR…リフレッシュタイムコンスタントレジスタ、RTCSR…リフレッシュタイマコントロールステータスレジスタ、RFC…リフレッシュ制御部、ST1〜ST10…ステート、

22…SDRAM、30…モードレジスタ、200A,200B…メモリアレイ、201A,201B…ロウデコーダ、202A,202B…センスアンプ及びカラム選択回路、203A,203B…カラムデコーダ、205…カラムアドレスバッファ、206…ロウアドレスバッファ、207…カラムアドレスカウンタ、208…リフレッシュカウンタ、210…入力バッファ、211…出力バッファ、212…コントローラ。

【技術分野】

【0001】

この発明はマイクロプロセッサに関し、例えば、その外部バスインターフェイスに利用して特に有効な技術に関するものである。

【背景技術】

【0002】

シンクロナスDRAM(ダイナミック型ランダムアクセスメモリ)等の各種半導体メモリを直結しうる外部バスを具備するマイクロプロセッサ(マイクロコントローラ)が、例えば、日経マグロウヒル社発行の1994年2月14日付『日経エレクトロニクス』第79頁ないし第91頁に記載されている。

【0003】

一方、メモリカード及びI/Oカード等のPCカードがあり、マイクロプロセッサ等にPCカードを結合するためのインターフェイス条件が日本電子工業振興協会(JEIDA)及びPCMCIA(Personal Computer Memory Card International AssocIation)により標準化されている。PCカードインターフェイスには、ガイドラインVer.4.1の『6.電気・インターフェイス仕様』で規定される68ピンのICメモリカードインターフェイス及びI/Oカードインターフェイスが含まれる。また、このようなPCカードインターフェイスに対処するため、82365SL等の専用IC(集積回路)チップが用意されている。

【非特許文献1】日経マグロウヒル社発行1994年2月14日付『日経エレクトロニクス』第79頁ないし第91頁

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来のマイクロプロセッサ等において、PCカードを結合するためのバスは、半導体メモリ等を結合するためのバスとは別個に設けられるとともに、PCカードは上記専用ICチップを介してバスに結合され、そのインターフェイス制御はこれらの専用ICチップによって行われる。このため、パーソナルコンピュータや携帯情報端末等にPCカードインターフェイスを組み込もうとした場合、バス構成が複雑となり設計工数が増大するとともに、マイクロプロセッサの外付け部品が増大する。この結果、パーソナルコンピュータ及び携帯情報端末等の開発期間が増大し、その低コスト化が阻害されるものとなる。

【0005】

この発明の目的は、使い勝手を良くしたマイクロプロセッサを提供することにある。この発明の他の目的は、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し外付け部品数を削減して、その低コスト化を図ることにある。この発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0006】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。すなわち、パーソナルコンピュータ及び携帯情報端末等に内蔵されるマイクロプロセッサに、外部バスに結合されかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラを設ける。このバスステートコントローラBSCには、シンクロナスDRAM接続時におけるPCカードの起動信号(−OE、−WE)のセットアップ時間を制御するための制御レジスタ(PCR)が設けられる。

【0007】

また、外部バスのアドレス空間を所定数のエリアに分割し、各エリアに各種半導体メモリ又はPCカードを固定的に割り当てるとともに、I/Oカードが入出力装置として機能する場合の物理アドレスとメモリとして機能する場合の物理アドレスとを独立に割り当て、マイクロプロセッサに、その内部における論理アドレスを外部バスにおける物理アドレスに変換するためのメモリ管理ユニットを設ける。

【発明の効果】

【0008】

上記した手段によれば、以下の理由により、上記目的が達成される。その物理アドレスによる制約を受けることなくしかもインターフェイス制御のための外付け部品を削減しつつ、各種半導体メモリとメモリカード及びI/Oカード等のPCカードとを直接かつ同時にマイクロプロセッサの外部バスに結合することができる。この結果、マイクロプロセッサの使い勝手を改善できるとともに、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し外付け部品数を削減して、その低コスト化を図ることができる。

【0009】

また、バスステートコントローラBSCには、シンクロナスDRAM接続時におけるPCカードの起動信号(−OE、−WE)のセットアップ時間を制御するための制御レジスタ(PCR)が設けられるので、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間などを制御することが出来る。その結果、PCカードとシンクロナスDRAMとを本発明のマイクロプロセッサMPUに同時に結合させても、本発明のマイクロプロセッサMPUは、不都合なくPCカードとシンクロナスDRAMに対するアクセスを行うことが出来る。

【発明を実施するための最良の形態】

【0010】

図1には、この発明に係るマイクロプロセッサMPUを含むパーソナルコンピュータの一実施例のシステム構成図が示されている。同図において、パーソナルコンピュータは、マイクロプロセッサMPUを搭載したマザーボードMBDをその基本構成要素とする。マザーボードMBDには、特に制限されないが、PCカードスロットPCSL1及びPCSL2を介して2種のPCカードつまりメモリカードMEMC及びI/OカードIOCがそれぞれ結合され、コネクタLCDCON及びKBDCONを介してマンマシンインターフェイスとなる液晶ディスプレイLCD及びキーボードKBDがそれぞれ結合される。

【0011】

メモリカードMEMCは、SRAM(スタティック型RAM),EPROM(電気的に情報の書き込み可能なリードオンリメモリ),EEPROM(電気的に情報の消去・書き込み可能なリードオンリメモリ)あるいはフラッシュEEPROM等から構成され、データ記憶用のカードとされる。一方、I/OカードIOCは、ファクシミリやデータ転送のためのモデム,LANに利用される制御回路,グローバルポジショニングシステム(GPS)に利用される制御回路あるいはスモールコンピュータシステムインターフェイスコントローラ等とされる。

【0012】

マザーボードMBDのマイクロプロセッサMPUには、特に制限されないが、外部バスE−BUSを介して6種の半導体メモリつまりROM,バーストROM(BROM),SRAM,PSRAM(疑似SRAM),DRAM(ダイナミック型RAM)及びシンクロナスDRAM(SDRAM)が結合される。この外部バスE−BUSには、さらにPCカードバッファBUF1及びBUF2ならびにディスプレイコントローラLCDC及びキーボードコントローラKBDCが結合される。このうち、PCカードバッファBUF1及びBUF2には、上記PCカードスロットPCSL1及びPCSL2つまりメモリカードMEMC及びI/OカードIOCがそれぞれ結合され、ディスプレイコントローラLCDC及びキーボードコントローラKBDCには、コネクタLCDCON及びKBDCONつまり液晶ディスプレイLCD及びキーボードKBDがそれぞれ結合される。マザーボードMBDに搭載された各種半導体メモリ,PCカードバッファ及びコントローラには、電源ユニットPOWUから所定の動作電源が供給される。

【0013】

マイクロプロセッサMPUは、ROM又はバーストROMから読み出されるプログラムに従ってステップ動作し、所定の論理演算処理を実行するとともに、パーソナルコンピュータの各部を制御・統括する。また、PCカードバッファBUF1及びBUF2は、PCカードスロットPCSL1又はPCSL2に装着されたメモリカードMEMC又はI/OカードIOCとの間のインターフェイス整合を行い、ディスプレイコントローラLCDC及びキーボードコントローラKBDCは、コネクタLCDCON又はKBDCONを介して結合された液晶ディスプレイLCD又はキーボードKBDを制御する。

【0014】

この実施例において、マイクロプロセッサMPUは、後述するように、外部バスE−BUSに結合されたROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリとメモリカードMEMC及びI/OカードIOC等のPCカードとに対するインターフェイスを並行制御しうるバスステートコントローラBSCを備える。また、外部バスE−BUSのアドレス空間は所定数のエリアに分割され、これらのエリアに半導体メモリ又はPCカードが固定的に割り当てられるとともに、I/OカードがI/Oカードとして機能する場合の物理アドレスが、メモリカードとして機能する場合の物理アドレスとは独立に割り当てられる。

【0015】

このため、マイクロプロセッサMPUは、さらにその内部における論理アドレスを外部バスにおける物理アドレスに変換するメモリ管理ユニットMMUを備える。これらの結果、その物理アドレスによる制約を受けることなくしかもインターフェイス制御のための外付け部品を削減しつつ、各種半導体メモリとPCカードつまりメモリカードMEMC及びI/OカードIOCとを直接かつ同時に外部バスE−BUSに結合でき、これによってマイクロプロセッサMPUの使い勝手を改善できるとともに、パーソナルコンピュータの設計工数を削減し外付け部品数を削減して、その低コスト化を図ることができるものである。

【0016】

図2には、図1のパーソナルコンピュータの三つの実施例の外観構成図が示されている。まず、図2の(a)において、パーソナルコンピュータは、いわゆるノート型とされ、PCカードスロットMSLOT(PCSL1,PCSL2)に装着されたメモリカードMEMC又はI/OカードIOCからなるファイルFfileを内蔵するとともに、入出力装置としてキーボードKB(KBD)及び液晶ディスプレイDP(LCD)を備える。このうち、液晶ディスプレイは内側に折り畳むことができ、これによって携帯に便利な形態とされる。

【0017】

図2の(b)において、パーソナルコンピュータは、いわゆるデスクトップ型とされ、フレキシブルディスクドライブFDDと、図示されないPCカードスロットに装置されたメモリカードMEMC又はI/OカードIOCからなるファイルFfileとを備える。また、入出力装置としてキーボードKB及び液晶ディスプレイDPを備え、フレキシブルディスクドライブFDDには所定のフレキシブルディスクFDが挿入される。これにより、パーソナルコンピュータは、フレキシブルディスクFDによるソフトウェアとしての記憶領域と、ファイルFfileによるハードウェアとしての記憶領域とを併せ持つものとなる。

【0018】

図2の(c)において、パーソナルコンピュータは、いわゆるペンポータブル型とされ、メモリカードMEMC又はI/OカードIOCからなるファイルカードFfileCARDを装着しうる二つのPCカードスロットを備える。また、入出力装置として感圧シート付液晶ディスプレイDP及び入力ペンPENを備え、手書き文字による入力を可能とする。

【0019】

これらの実施例において、パーソナルコンピュータのマザーボードMBDを構成するマイクロプロセッサMPUは、前述のように、各種の半導体メモリとメモリカードMEMC及びI/OカードIOCからなるPCカードとを直接かつ同時に結合しうるインターフェイスを有する。この結果、マザーボードMBDひいてはパーソナルコンピュータの構成が簡素化され、その小型化,軽量化,薄型化が図られて携帯に便利な形態を採りうるとともに、後述するバースト機能等により大容量の情報を高速に入出力することが可能となり、パーソナルコンピュータとしての処理能力が高めるられるものとなる。

【0020】

図3には、図1のパーソナルコンピュータに含まれるマイクロプロセッサMPUの一実施例のブロック図が示され、図4には、マイクロプロセッサMPUの半導体基板(半導体チップ)上でのレイアウトの一実施例が示されている。すなわち、マイクロプロセッサMPUは公知の半導体製造方法によって単結晶シリコンのような半導体基板に形成される。

【0021】

図3において、マイクロプロセッサMPUは、演算器ALUを含むストアドプログラム方式の中央処理ユニットCPUをその基本構成要素とする。この中央処理ユニットCPUには、システムバスS−BUS(第1内部バス)を介して乗算器MULT,メモリ管理ユニットMMUならびにキャッシュメモリCACHEが結合され、メモリ管理ユニットMMUにはアドレス変換バッファTLBが結合される。メモリ管理ユニットMMU及びキャッシュメモリCACHEは、さらにその他方においてキャッシュバスC−BUS(第2内部バス)に結合され、このキャッシュバスC−BUSにはバスステートコントローラBSCが結合される。

【0022】

バスステートコントローラBSCは、その他方において周辺バスP−BUSに結合されるとともに、図示されないバスインターフェイス部及びバスコネクタを介して外部バスE−BUSに結合される。このうち、周辺バスP−BUS(第3内部バス)には、リフレッシュコントローラREFC,ダイレクトメモリアクセスコントローラDMAC,タイマ回路TIM,シリアルコミュニケーションインターフェイスSCI,ディジタル/アナログ変換回路D/A及びアナログ/ディジタル変換回路A/D等の周辺装置コントローラが結合され、外部バスE−BUSには、前記各種の半導体メモリやPCカードを結合するためのPCカードバッファBUF1及びBUF2ならびにディスプレイコントローラLCDC及びキーボードコントローラKBDCが結合される。

【0023】

バスステートコントローラBSC,リフレッシュコントローラREFC,ダイレクトメモリアクセスコントローラDMAC,タイマ回路TIM,シリアルコミュニケーションインターフェイスSCI,ディジタル/アナログ変換回路D/A及びアナログ/ディジタル変換回路A/Dは、さらに割り込みコントローラINTCに結合され、この割り込みコントローラは割り込み要求信号IRQを介して中央処理ユニットCPUに結合される。

【0024】

同図には図示されないが、システムバスS−BUS、キャッシュバスC−BUSおよび周辺バスP−BUSのそれぞれは、アドレス信号を伝送するための内部アドレスバス、データを伝送するための内部データバスおよび、制御信号を伝送するための内部制御バスをそれぞれ含むものとみなされる。一方、外部バスE−BUSは、アドレス信号を伝送するための外部アドレスバス、データを伝送するための外部データバスおよび、制御信号を伝送するための外部制御バスをそれぞれ含むものとみなされる。

【0025】

上記中央処理ユニットCPUは、クロックパルス発生回路CPGから供給される所定のシステムクロック信号に従って同期動作し、キャッシュメモリCACHEから読み出される制御プログラムに従って所定の演算処理を実行するとともに、マイクロプロセッサMPUの各部を制御・統括する。このとき、演算器ALUは所定の算術論理演算を実行し、乗算器MULTはディジタル信号処理等に有効な乗算処理又は積和処理を実行する。

【0026】

上記メモリ管理ユニットMMUは、メモリアクセスに際してマイクロプロセッサMPUの内部つまり中央処理ユニットCPU等から出力される論理アドレスを、アドレス変換バッファ(address translation look-aside buffer )TLBを参照して物理アドレスに変換し、バスステートコントローラBSCを介してマイクロプロセッサMPUの外部つまり外部バスE−BUSに伝達する。キャッシュメモリCACHEは、高速アクセス可能な半導体メモリからなり、外部のROM又はバーストROM等に格納された制御プログラム又はデータ等を所定のブロック単位で読み出し保持して、中央処理ユニットCPUの高速動作に寄与する。

【0027】

一方、バスステートコントローラBSCは、周辺バスP−BUSに結合される各周辺装置コントローラのバスアクセスを管理し、その動作を制御・統括するとともに、外部バスE−BUSに結合される各種の半導体メモリ及びPCカードならびに各種入出力コントローラの動作を制御・統括する。

【0028】

この実施例において、外部バスE−BUSの物理アドレス空間は、特に制限されないが、8つのエリアに分割され、このうち7つのエリアは、所定の組み合わせをもって各種半導体メモリ及びPCカードに固定的に割り当てられる。また、バスステートコントローラBSCは、外部バスE−BUSの各エリアに割り当てられた各種半導体メモリ及びPCカードに対する制御信号のタイミングをそれぞれ所定の条件でかつ並行して制御・管理する機能を有し、これらのタイミング条件を選択的に指定するための各種コントロールレジスタを備える。

【0029】

この結果、外部バスE−BUSには、前記のように、ROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等を含む各種半導体メモリと、メモリカードMEMC及びI/OカードIOCを含むPCカードとを直接かつ同時に結合しうるものとなる。外部バスE−BUSの信号構成ならびにバスステートコントローラBSCの具体的構成については、後で詳細に説明する。

【0030】

次に、周辺装置コントローラの一つであるリフレッシュコントローラREFCは、外部バスE−BUSに結合されたDRAM及びSDRAMのリフレッシュ動作を制御し、ダイレクトメモリアクセスコントローラDMACは、例えば外部バスE−BUSに結合されたROM又はバーストROMとキャッシュメモリCACHE等との間の高速データ転送をサポートする。

【0031】

タイマ回路TIMは、中央処理ユニットCPUに必要な時間管理をサポートとし、シリアルコミュニケーションインターフェイスSCIは、外部の通信制御装置等との間のシリアルデータ転送をサポートする。一方、アナログ/ディジタル変換回路A/Dは、外部のセンサ等から入力されるアナログ信号を所定のディジタル信号に変換し、ディジタル/アナログ変換回路D/Aは、逆に中央処理ユニットCPUから出力されるディジタル信号を所定のアナログ信号に変換して外部出力する。割り込みコントローラINTCは、バスステートコントローラBSCや各周辺装置コントローラの割り込み要求を所定の優先順位で択一的に受理し、割り込み要求信号IRQとして中央処理ユニットCPUに伝達する。

【0032】

この実施例において、マイクロプロセッサMPUを構成する各部は、図4に例示されるように、所定のレイアウト条件をもって1個の半導体基板上に配置される。また、マイクロプロセッサMPUの各部はいわゆるモジュール化され、ユーザ仕様に基づいて選択的に形成され、選択的に有効とされる。

【0033】

図4において、バスコントローラは図3のバスステートコントローラBSCに対応し、Timerはタイマ回路TIMに対応する。また、クロックパルス発生回路CPGにより形成されるシステムクロックは、所定のクロックドライバDriverを介してマイクロプロセッサMPUの各部に分配・供給される。

【0034】

図5には、図3のマイクロプロセッサMPUの外部バスE−BUSにおける物理アドレスの割り当てを説明するための一実施例のアドレスマップが示され、図6には、そのエリア5及びエリア6における物理アドレスの割り当てを説明するための一実施例の部分的なアドレスマップが示されている。まず図5において、この実施例のマイクロプロセッサMPUの外部バスE−BUSの物理アドレス空間は、特に制限されないが、8つのエリア0〜エリア7に分割され、このうちのエリア0〜6の7つが外部バスE−BUSに結合された各種半導体メモリ及びPCカードによって使用可能とされる。

【0035】

このうち、エリア0は、SRAM及びROMを含む通常メモリかバーストROMに対して選択的に割り当てられ、エリア1及びエリア4は通常メモリに選択的に割り当てられる。また、エリア2は、通常メモリ,SDRAM又はDRAMに対して選択的に割り当てられ、エリア3は、通常メモリ,SDRAM,DRAM又はPSRAMに選択的に割り当てられる。一方、エリア5は、通常メモリ又はバーストROMかメモリカードMEMCに選択的に割り当てられ、エリア6は、通常メモリ又はバーストROMかメモリカードMEMC又はI/OカードIOCに選択的に割り当てられる。なお、本明細書において、通常メモリとは、SRAMやROMのように行及び列アドレスが同時に供給されてアクセスされるアドレスノンマルチプレクス型のメモリを意味し、DRAMやSDRAMのように行及び列アドレスが時分割的に供給されてアクセスされるアドレスマルチプレクス型のメモリとは区別される。

【0036】

なお、エリア7は、マイクロプロセッサMPUの内部装置のアドレス、たとえば、CPUの内部レジスタのアドレスや上記周辺装置コントローラ内のレジスタのアドレス、に割り当てられ、外部装置では使用できない。また、エリア0〜エリア6にいずれの半導体メモリ又はPCカードが結合されるかは、後述するバスステートコントローラBSCのバスコントロールレジスタBCR1によって選択的に指定される。

【0037】

この実施例において、マイクロプロセッサMPUのシステムバスS−BUS、キャッシュバスC−BUSおよび周辺バスP−BUSの内部アドレスバスは、32ビットのアドレス信号A0〜A31を転送可能な信号線を含み、マイクロプロセッサMPUの内部における論理アドレスは、これらアドレス信号A0〜A31により択一的に指定されるいわゆる4GB(ギガバイト)のアドレス空間からなる。一方、マイクロプロセッサMPUの外部つまり外部バスE−BUSにおける物理アドレスは、上位3ビットを除く29ビットのアドレス信号A0〜A28により択一的に指定されるが、アドレス信号A0〜A31の上位3ビット、つまり、アドレス信号A26〜A28は、エリア0ないしエリア6を択一的に指定するためのチップセレクト信号−CS0〜−CS6を作成するために供され、下位26ビットのアドレス信号A0〜A25は、各エリア内のアドレスを択一的に指定するために供される。すなわち、外部バスE−BUSにおける外部アドレスバスは、アドレス信号A0〜A25を転送可能な信号線を含む。

【0038】

これにより、エリア0には、16進数表示でH’00000000ないしH’03FFFFFFの物理アドレスが割り当てられ、エリア1には、H’04000000ないし07FFFFFFの物理アドレスが割り当てられる。また、エリア2ないしエリア4には、H’08000000ないしH’0BFFFFFF,H’0C000000ないしH’0FFFFFFFならびにH’10000000ないしH’13FFFFFFの物理アドレスがそれぞれ割り当てられ、エリア5及びエリア6には、H’14000000ないしH’17FFFFFFならびにH’18000000ないしH’1BFFFFFFの物理アドレスがそれぞれ割り当てられる。この結果、各エリアは、いわゆる64MB(メガバイト)の物理アドレス空間を持つものとなる。なお、エリア0〜エリア6の物理アドレスにそれぞれH’20000000×n(n=1〜6)を加えた物理アドレスは、各エリアのシャドウ空間とされ、この乗数nは、論理アドレスの上位3ビットつまりアドレス信号A29〜A31により選択的に指定される。

【0039】

メモリカードMEMC及びI/OカードIOCに割り当てられるエリア5及びエリア6の物理アドレスは、図6に示されるように、さらにそれぞれ二つに分割される。このうち、エリア5では、アドレスH’14000000〜H’15FFFFFFからなる下位の領域が、メモリカードMEMCのためのコモンメモリ又はアトリビュートメモリ領域として割り当てられ、アドレスH’16000000〜H’17FFFFFFからなる上位の領域は、使用禁止領域とされる。また、エリア6では、アドレスH’18000000〜H’19FFFFFFからなる下位の領域が、メモリカードMEMCあるいはI/OカードIOCがメモリとして機能する場合のコモンメモリ又はアトリビュートメモリ領域として割り当てられ、アドレスH’1A000000〜H’1BFFFFFFからなる上位の領域は、I/OカードIOCが入出力装置として機能する場合のI/O領域とされる。この結果、エリア5及びエリア6におけるコモンメモリ又はアトリビュートメモリ領域は、いわゆる32MBのアドレス空間となる。

【0040】

特に制限されないが、エリア6の二分された領域つまりI/OカードIOCがメモリ又は入出力装置のいずれで機能するかは、アドレス信号A25によって選択的に指定され、32MBのアドレス空間は、残り25ビットのアドレス信号A0〜A24により択一的に指定される。周知のように、PCMCIA規格では、PCカードとして最大64MBのアドレス空間を持つことが許されるが、この場合、後述するように、さらに最上位ビットのアドレス信号A25がマイクロプロセッサMPUの出力ポートを介して別経路で出力される。このように、エリア6の物理アドレス空間を二分しアドレスA25により選択的に指定できるようにすることで、エリア6に結合されたI/OカードIOCのメモリ又は入出力装置としての機能をソフトウェアによりダイナミックに切り替えることが可能となり、マイクロプロセッサMPUの利便性が高められる結果となる。

【0041】

上記のようにマイクロプロセッサMPUの物理アドレス空間が8つのエリアに分割され、このうちの7つがマイクロプロセッサMPUの外部バスE−BUSに結合される各種半導体メモリ又はPCカードに固定的に割り当てられる。このことは、ユーザから見た場合、ソフトウェアにおける論理アドレスの配分に制約を与える原因となるように見える。しかし、この実施例では、前述のように、マイクロプロセッサMPUにメモリ管理ユニットMMUが設けられ、その内部における論理アドレスと外部バスE−BUSにおける物理アドレスとの対応は、アドレス変換バッファTLBの書き換え、すなわち、外部バスE−BUSに結合される外部メモリ、たとえば、DRAMなどに記憶されるアドレス変換テーブルのアドレス変換対の内容の書換によって容易に変更可能とされる。このため、ユーザは外部バスE−BUSの物理アドレスによる制約から解放され、自由な論理アドレス空間を有するソフトウェアを構築しうるものとなる。

【0042】

図7及び図8には、図3のマイクロプロセッサMPUの外部バスE−BUSの接続形態を説明するための一実施例の接続図が示されている。また、図9には、図7及び図8の外部バスE−BUSとPCカードが結合される場合の一実施例のインターフェイス構成図が示され、図10及び図11には、図7及び図8の外部バスE−BUSの一実施例の信号構成図が示されている。なお、図7及び図8では、エリア0〜エリア4に結合可能な半導体メモリを適当に割り当てているが、実際にはエリアによって結合可能な組み合わせが制限されるケースもある。図10及び図11は、図7ないし図9の説明の過程で適宜参照されたい。

【0043】

図7において、外部バスE−BUSは、マイクロプロセッサMPUから見てアドレス出力バスとなる26ビットの外部アドレスバスEBA0〜EBA25と、入出力バスとなる32ビットの外部データバスEBD0〜EBD31とを備える。このうち、アドレスバスEBA0〜EBA25を介して伝達されるアドレス信号A0〜A25は、各種半導体メモリ及びPCカードが結合されるすべてのエリアに共通に供給されるが、外部データバスEBD0〜EBD31は、外部バスE−BUSに結合される半導体メモリ及びPCカードのバスサイズに応じて選択的な接続形態を採る。なお、DRAM及びSDRAMにおいては、行及び列アドレスが時分割的にアドレスバス上の同一ラインに供給されるため、DRAM及びSDRAMの各アドレス入力端子は、外部アドレスバスEBA0〜EBA25のうちの所定数のラインに結合されることになる。

【0044】

すなわち、この実施例のマイクロプロセッサMPUでは、後述するバスステートコントローラBSCのバスコントロールレジスタBCR2により、エリア0〜エリア6のバスサイズをエリアごとに指定することができる。このうち、エリア0では、バイト(8ビット),ワード(16ビット),ロングワード(32ビット)のバスサイズを任意に選択できるが、エリア1ないしエリア6では、各エリアがSRAM,ROM又はバーストROMに割り当てられる場合には、バイト,ワード又はロングワードを任意に選択できるが、SDRAM,DRAM又はPSRAMに割り当てられる場合には、メモリコントロールレジスタMCR1との組み合わせによってワード又はロングワードの選択に制限される。さらに、エリア2及びエリア3がDRAMに割り当てられる場合、そのバスサイズはワードのみに制限され、エリア5及びエリア6がPCカードに割り当てられる場合には、バイト又ワードのいずれかが選択される。

【0045】

これにより、下位16ビットのデータバスEBD0〜EBD15は、エリア0〜エリア6に割り当てられたすべての半導体メモリ及びPCカードに結合されるが、上位16ビットのデータバスEBD16〜EBD23ならびにEBD24〜EBD31は、各エリアのバスサイズに応じてそれぞれ選択的に結合されるものとなる。なお、8ビットのデータバスEBD16〜EBD23は、後で例示するように、エリアのバスサイズが16ビット以下であることを条件に、汎用のポートPORT0〜PORT7としても使用できる。ただし、この場合にはバスステートコントローラBSC2のポート機能イネーブルビットが論理“1”にセットされる。

【0046】

外部バスE−BUSは、外部バスE−BUS上のデータが有効であることを示すバススタート信号−BS(ここで、それが有効とされるとき選択的にロウレベルとされるいわゆる反転信号等については、その名称の先頭に−を付加する。以下同様)を伝達するための制御信号線を外部制御バスEBCとして備える。この信号−BSは、バスステートコントローラBSCによって各種半導体メモリ及びPCカードに必要な起動信号に変換される。このため、バススタート信号−BSは、ディスプレイコントローラLCDC及びキーボードコントローラKBDC等のバス管理機能を持つI/Oコントローラには供給されるが、バス管理機能を持たない半導体メモリ及びPCカードには供給されない。

【0047】

一方、外部バスE−BUSの外部制御バスEBCは、エリア0ないしエリア6を択一的に指定するためのチップセレクト信号−CS0〜−CS6を伝達するための制御信号線と、エリア0のバスサイズやエンディアンの指定に供されるモード信号MD3〜MD5を伝達するための制御信号線を備える。このうち、チップセレクト信号−CS5及び−CS6は、エリア5及びエリア6のPCカードに対するカードイネーブル信号−CE1つまり−CE1A及び−CE1Bとしてそれぞれ併用される。また、モード信号MD3及びMD4は、これらのPCカードに対するカードイネーブル信号−CE2つまり−CE2A及び−CE2Bとしてそれぞれ併用され、モード信号MD5は、エリア3に結合される2セット目のDRAMに対するロウアドレスストローブ信号−RAS2として併用される。

【0048】

外部バスE−BUSの外部制御バスEBCは、さらに各種半導体メモリ及びPCカードに対する起動制御信号となるロウアドレスストローブ信号−RASを伝達するための制御信号線と、カラムアドレスストローブ信号−CASLL,−CASLH,−CASHL及び−CASHHのそれぞれを伝達するための制御信号線と、ライトイネーブル信号−WE0〜−WE3ならびにリード・ライトステータス信号RD/−WR,リードコントロール信号−RD,I/Oクロック信号CKIO及びクロックイネーブル信号CKEのそれぞれを伝達するための制御信号線を備える。なお、I/Oクロック信号CKIOは、マイクロプロセッサMPUに入力されるシステムクロックあるいは、SDRAM接続時に、上記SDRAMへ供給される動作クロック信号を示し、上記マイクロプロセッサMPUは、I/Oクロック信号CKIOに基づいて、各種出力信号のタイミング管理を行う。

【0049】

このうち、ロウアドレスストローブ信号−RASは、DRAM及びSDRAMに対するロウアドレスストローブ信号−RASとして供給されるともに、エリア3のPSRAMに対するチップイネーブル信号−CEとしても併用される。また、カラムアドレスストローブ信号−CASLL,−CASLH,−CASHL及び−CASHHは、32ビットバスサイズのDRAMに対して、データバスD0〜D7,D8〜D15,D16〜D23ならびにD24〜D31に対応したカラムアドレスストローブ信号として供給されるが、このうち、カラムアドレスストローブ信号−CASLLは、SDRAMに対するカラムアドレスストローブ信号−CASあるいはPSRAMに対する出力イネーブル信号−OEとして併用され、カラムアドレスストローブ信号−CASHL及び−CASHHは、2セット目のDRAMに対するバイト対応のカラムアドレスストローブ信号−CAS2L及び−CAS2Hとしてそれぞれ併用される。

【0050】

ライトイネーブル信号−WE0〜−WE3は、32ビットバスサイズのSRAM及びPSRAMあるいはSDRAMに対して、データバスEBD0〜EBD7,EBD8〜EBD15,EBD16〜EBD23ならびにEBD24〜EBD31にそれぞれ対応したライトイネーブル信号あるいはデータコントロール信号DQMLL,DQMLU,DQMUL及びDQMUUとして供給されるが、このうち、ライトイネーブル信号−WE2は、エリア6のI/OカードIOCに対するI/Oリードコントロール信号−ICIORDとして併用され、ライトイネーブル信号−WE3は、I/Oライトコントロール信号−ICIOWRとして併用される。

【0051】

リード・ライトステータス信号RD/−WRは、DRAM及びSDRAMに対するライトイネーブル信号−WEとして供給されるとともに、図示されないI/Oコントローラに対するリード・ライト信号R/−Wとして併用される。また、リードコントロール信号−RDは、ROM及びSRAMならびにメモリカードMEMC及びI/OカードIOCに対する出力イネーブル信号−OEとして供給され、I/Oクロック信号CKIOとクロックイネーブル信号CKEは、SDRAMに対して供給される。

【0052】

この実施例において、外部バスE−BUSは、PCカード専用の外部入力バスとしてライトプロテクト信号WPを伝達するための制御信号線を備え、バスコントロール用の信号としてウェイトコントロール信号−WAIT,バスリクエスト信号−BREQ及びバスアクノリジ信号BACKのそれぞれを伝達するための制御信号線を備える。このうち、ライトプロテクト信号WPは、書き込み禁止を必要とするメモリカードMEMCから選択的に入力されるとともに、I/OカードIOCのバスサイズが16ビットであることをマイクロプロセッサMPUに知らせるための16ビットI/Oポート信号−IOIS16としても併用される。

【0053】

ウェイトコントロール信号−WAITは、マイクロプロセッサMPUのサイクル待ち合わせを必要とするPCカード及びI/Oコントローラ等から必要に応じて選択的に入力される。さらに、バスリクエスト信号−BREQは、外部バスE−BUSを専有したいバスマスタから必要に応じて選択的に入力され、バスアクノリジ信号BACKは、これらのバスマスタに対するバス使用許可信号としてマイクロプロセッサMPUから出力される。マイクロプロセッサMPUから出力されライトイネーブル信号−WE1は、ライトイネーブル信号−WE/−PGMとしてPCカードに伝達される。なお、図8に示される各種半導体メモリ及びPCカードは、バスマスタとしての機能を有しない。

【0054】

外部バスE−BUSには含まれないが、メモリカードMEMC及びI/OカードIOCは、PCカードスロットPCSL1及びPCSL2にPCカードが装着されたことを示すカード検出信号−CD1及び−CD2のそれぞれを伝達するための制御信号線と、リセット信号RESETを伝達するための制御信号線とに結合される。これらの制御信号は、マザーボードMBDに設けられたボードコントローラBCで検知され、ボード制御に供される。マザーボードMBDは、さらに動作電源となる電源電圧VCC及び接地電位GNDを入力するための端子を備え、この電源電圧及び接地電位を各種半導体メモリ,PCカード,I/OコントローラならびにマイクロプロセッサMPUに1対の電源供給線を介して分配する。

【0055】

メモリカードMEMC又はI/OカードIOC等のPCカードは、前述のように、PCカードバッファBUF1又はBUF2を介して外部バスE−BUSに結合され、アドレス信号A25は、エリア6のI/OカードIOCがメモリ又は入出力装置のいずれで機能するかを識別するために供される。したがって、メモリカードMEMC及びI/OカードIOCが64MBのアドレス領域を有する場合には、図9に示されるように、マイクロプロセッサMPUのポートPORTを介して、最上位のアドレス選択に供されるアドレス信号A25が改めて出力される。このポートPORTには、リセット信号RESETとアトリビュートメモリ空間選択信号−REGが含まれる。

【0056】

マザーボードMBDは、割り込みレベルIRL0〜IRL3を設定するためのエンコーダENCODRとを備える。これらの信号が、PCMCIA標準に準拠したものであることは言うまでもない。図9に示されるように、PCカードバッファBUF1又はBUF2は、外部データバスEBD0〜EBD7に設けられる双方向バッファB1と、外部データバスEBD8〜EBD15に設けられる双方向バッファB2とを含む。上記双方向バッファB1およびB2は、リード・ライトステータス信号RD/−WRによってデータの伝送方向(DIR)がそれぞれ制御され、カードイネーブル信号−CE1B及び−CE2Bによってそのゲートティング動作(G)がそれぞれ制御される。

【0057】

図12には、図3のマイクロプロセッサMPUに含まれるバスステートコントローラBSCの一実施例のブロック図が示されている。同図において、バスステートコントローラBSCは、マイクロプロセッサMPUのキャッシュバスC−BUSに結合されるキャッシュバスインターフェイス部CBIFと、バスステートコントローラBSC内のモジュールバスM−BUSを介してキャッシュバスインターフェイス部CBIFに結合されるアドレスレジスタADR,データレジスタDTR,ウェイトコントロールレジスタWCR1及びWCR2,バスコントロールレジスタBCR1及びBCR2,メモリコントロールレジスタMCR,DRAMコントロールレジスタDCR,PCMCIAコントロールレジスタPCR,リフレッシュカウントレジスタRFCR,リフレッシュタイマカウントレジスタRTCNT,リフレッシュタイムコンスタントレジスタRTCOR及びリフレッシュタイマコントロールステータスレジスタRTCSRとを備える。

【0058】

これらのレジスタの内容は、マイクロプロセッサMPUの中央処理ユニットCPUつまりはそのソフトウェアによって任意に書き換えることができる。すなわち、中央処理ユニットCPUは、キャッシュバスC−BUS、キャッシュバスインターフェイス部CBIF及びモジュールバスM−BUSを介して、各レジスタ(ADR,DTR,WCR1,WCR2,BCR1,BCR2,MCR,DCR,PCMCIA,PCR,RFCR,RTCNT,RTCORおよびRTCSR)の内容の書き込み、あるいは変更を実施できる。

【0059】

上記バスステートコントローラBSCには、動作タイミングを決定するための動作クロックとして、図4に記載されるクロックパルスジェネレータCPGから発生される動作クロックCKがクロックドライバDriverから供給される。このクロック信号CKは、中央処理装置CPUの動作クロックと同一の周波数を有するクロックとされるとともに、上記マイクロプロプロセッサMPUの外部へシステムクロックとしてシステムクロック入出力端子CKIOから出力される。後述されるように、上記システムクロック入出力端子CKIOから出力されるシステムクロックは、シンクロナスDRAMの動作クロックとして利用される。

【0060】

アドレスレジスタADRは、アドレス制御部ADCに結合される。また、データレジスタDTRの出力端子は、マルチプレクサMPXの一方の入力端子に結合され、このマルチプレクサMPXの他方の入力端子は、ポートPORT0〜PORT7に結合される。一方、ウェイトコントロールレジスタWCR1及びWCR2は、ウェイト制御部WATECに結合され、バスコントロールレジスタBCR1は、エリア制御部AREACに結合される。

【0061】

バスコントロールレジスタBCR2ならびにメモリコントロールレジスタMCR,DRAMコントロールレジスタDCR及びPCMCIAコントロールレジスタPCRは、メモリタイミング制御部MTCに結合され、リフレッシュカウントレジスタRFCR,リフレッシュタイマカウントレジスタRTCNT,リフレッシュタイムコンスタントレジスタRTCORならびにリフレッシュタイマコントロールステータスレジスタRTCSRは、リフレッシュ制御部RFCに結合される。

【0062】

アドレス制御部ADCの出力端子は、外部バスE−BUSのアドレスバスEBA0〜EBA25にそれぞれ結合され、マルチプレクサMPXの出力端子はデータバスEBD0〜EBD31にそれぞれ結合される。また、ウェイト制御部WATECの出力信号はウェイトコントロール信号−WAITとなり、エリア制御部AREACの出力信号はチップセレクト信号−CS0〜−CS6ならびにカードイネーブル信号−CE2A及び−CE2Bとなる。

【0063】

メモリタイミング制御部MTCの出力信号は、バススタート信号−BS,ロウアドレスストローブ信号−RAS/チップイネーブル信号−CE,カラムアドレスストローブ信号−CAS/−CASxx(ここで、例えば四つのカラムアドレスストローブ信号−CASLL,−CASLH,−CASHL及び−CASHHを総称して−CASxxのようにxxを付して表す。以下同様),ライトイネーブル信号−WEx/データコントロール信号DQMxx,I/Oリードコントロール信号−ICIORD/I/Oライトコントロール信号−ICIOWR,リード・ライトステータス信号RD/−WR,リードコントロール信号−RD,ライトプロテクト信号WP/16ビットI/Oポート信号−IOIS16ならびにクロックイネーブル信号CKEとなる。

【0064】

アドレス制御部ADCは、キャッシュバスC−BUSのアドレスバスを介して伝達されるアドレス信号A0〜A25を外部バスE−BUSのアドレスバスEBA0〜EBA25に伝達するとともに、一連のアドレスを連続アクセスするためのバーストモードにおいてアドレス信号の所定ビットを自律的に更新するアドレス生成機能を有する。

【0065】

マルチプレクサMPXは、キャッシュバスC−BUS及び外部バスE−BUSのデータバスEBD0〜EBD31を結合するとともに、データバスの所定ビットつまりデータバスEBD16〜EBD23がポートPORT0〜PORT7として使用される場合の切り替え制御を行う。このように、バスステートコントローラBSCにアドレス制御部ADCを設け、バーストモードのためのアドレス生成機能を持たせることで、マイクロプロセッサの外付け部品を増やすことなく、バーストモードを有する半導体メモリ及びPCカードの接続を可能とし、その連続アクセスを高速化することができるものとなる。

【0066】

ウェイト制御部WATECは、外部バスE−BUSのウェイト信号−WAITを介して行われるPCカード又はI/Oコントローラからのサイクル待ち合わせ要求をマイクロプロセッサMPUに伝達する。また、ウェイトコントロールレジスタWCR1及びWCR2に書き込まれた各定数をもとに、リードアクセスからライトアクセスに切り替わった場合のアイドルサイクルの挿入や、各エリアに対するウェイトステート挿入を選択的に実行する。

【0067】

エリア制御部AREACは、バスステートコントロールレジスタラBSC1に書き込まれたエリア0〜エリア6の割り当て等に関する属性とキャッシュバスC−BUSのアドレスバスA26〜A28を介して供給されるエリア選択信号とをもとに、チップセレクト−CS0〜−CS6ならびにカードイネーブル信号−CE2A及び−CE2Bを選択的に形成する。

【0068】

メモリタイミング制御部MTCは、バスコントロールレジスタBCR2に書き込まれたエリア0〜エリア6のバスサイズ等に関する属性やメモリコントロールレジスタMCR,DRAMコントロールレジスタDCR及びPCMCIAコントロールレジスタPCRに書き込まれた定数とをもとに、各種半導体メモリ及びPCカードの動作制御に必要となる起動制御信号等を所定のタイミング条件で選択的に形成する。さらに、リフレッシュ制御部RFCは、リフレッシュカウンタのオーバーフロー割り込み機能を利用して、DRAM及びSDRAM等のリフレッシュ動作を制御する。

【0069】

図13には、図12のバスステートコントローラBSCの一実施例の状態遷移図が示されている。また、図14には、図12のバスステートコントローラBSCの一実施例のステート構成図が示され、図15には、その状態遷移に関する一実施例の遷移条件図が示されている。さらに、図16ないし図18には、図3のマイクロプロセッサMPUのウェイトを伴わないメモリカードMEMCアクセス時,ウェイトを伴うメモリカードMEMCアクセス時ならびにバーストモードを用いたメモリカードMEMCアクセス時の一実施例の信号波形図がそれぞれ示され、図19及び図20には、図3のマイクロプロセッサMPUのウェイトを伴わないI/OカードIOCアクセス時ならびにウェイトを伴うI/OカードIOCアクセス時の一実施例の信号波形図がそれぞれ示されている。

【0070】

以下、図13に沿ってバスステートコントローラBSCの状態遷移に関する具体的な説明を進めるが、図14ないし図20はこれらの説明の過程で随時参照されたい。なお、図13ないし図15に示されるステートは、SRAM,バーストROM及びPCカードの制御に関する部分的なものであり、バスステートコントローラBSCは、他の半導体メモリ等の制御に関する他の多数のステートを有する。

【0071】

図16ないし図20には、参考のため、メモリカードMEMC及びI/OカードIOCに供給されないI/Oクロック信号CKIO,バススタート信号−BS及びリード・ライトステータス信号RD/−WRが併せて示されている。なお、システムクロックあるいは中央処理装置の動作クロックとされるI/Oクロック信号CKIOは、図16ないし図20に示される各種のタイミング信号を作成するための基準クロック信号としての意味を有する。

【0072】

図13において、この実施例のバスステートコントローラBSCは、いわゆるステートマシンとされ、SRAM及びバーストROMならびにメモリカードMEMC及びI/OカードIOCの制御に関する10個のステートST1〜ST10を有する。このうち、ステートST1は、図14に示されるように、IDLEステートであって、マイクロプロセッサMPUの待機状態に対応する。

【0073】

ステートST2〜ST4は、PCMCIA TED1ないしPCMCIA TED3ステートであり、PCMCIAつまりメモリカードMEMC及びI/OカードIOCの起動制御信号となるライトイネーブル信号−WE1及び出力イネーブル信号−OEのアドレス信号A0〜A25に対するセットアップ時間を1サイクル分だけ遅延させるためのものである。

【0074】

ステートST5,ST6及びST7は、それぞれアクセス開始サイクルに対応するNORM T1ステート,ウェイトサイクルに対応するNORM TWステートならびにアクセス終結サイクルに対応するNORM T2ステートであって、ステートST8〜ST10は、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのアドレス信号A0〜A25に対するホールド時間を1サイクル分だけ遅延させるためのPCMCIA TEH1ステート,PCMCIA TEH2ならびにPCMCIA TEH3ステートである。なお、ステートST1〜ST10は、図14の右端欄に示される形で、図16ないし図20の各サイクルと対応する。

【0075】

バスステートコントローラBSCがステートST1のIDLEつまり待機状態にあるとき、外部バスE−BUSが空き状態でメモリつまり外部バスE−BUSに対するアクセス要求が発生しかつPCMCIAコントロールレジスタPCRのセットアップ遅延に関する定数TEDが1〜3である遷移条件(1) が成立すると、バスステートコントローラBSCは、ステートST2に遷移し、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間の遅延サイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、まずTpcm0サイクル又はTpci0サイクルによりバススタート信号−BSつまりはライトイネーブル信号−WE1及び出力イネーブル信号−OE(リードコントロール信号−RD)のセットアップ時間がI/Oクロック信号CKIOの1サイクル分だけ遅延される。

【0076】

ステートST2によるセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが2又は3である遷移条件(4) が成立すると、バスステートコントローラBSCは、ステートST3に遷移し、再びライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間の遅延サイクルに入る。

【0077】

このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、Tpcm0wサイクル又はTpci0wサイクルによりバススタート信号−BSつまりはライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間がさらにI/Oクロック信号CKIOの1サイクル分だけ遅延される。さらに、ステートST3によるセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが2である遷移条件(3) が成立すると、バスステートコントローラBSCは、ステートST5に遷移し、アクセス開始サイクルに入る。

【0078】

このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、Tpcm1サイクル又はTpci1サイクルによりバススタート信号−BSつまりは出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)がロウレベルの有効レベルとされ、アドレス信号A0〜A25により指定されたアドレスに対する実質的なデータの読み出し又は書き込みが実行される。

【0079】

ステートST2においてセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが1である遷移条件(2) が成立すると、バスステートコントローラBSCは、そのままステートST5に遷移し、アクセス開始サイクルに入る。また、ステートST3においてセットアップ時間の1サイクル遅延が終了しかつPCMCIAコントロールレジスタPCRの定数TEDが3である遷移条件(5) が成立すると、バスステートコントローラBSCは、ステートST4に遷移し、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ時間をさらに1サイクル分だけ遅延させる。そして、ステートST4におけるセットアップ時間の1サイクル遅延の終了つまり遷移条件(6) を受けてステートST5に遷移する。

【0080】

一方、ステートST1の待機状態において、外部バスE−BUSが空き状態でメモリアクセス要求が発生しかつPCMCIAコントロールレジスタPCRの定数TEDが0である遷移条件(7) が成立すると、バスステートコントローラBSCは、直接ステートST5に遷移し、アクセス開始サイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図16及び図19に例示されるように、ライトイネーブル信号−WE1及び出力イネーブル信号−OEのセットアップ遅延のためのサイクルを挟むことなくTpcm1サイクル又はTpci1サイクルが実行され、データの読み出し又は書き込みが行われる。

【0081】

次に、ステートST5によるアクセス開始サイクルが終了し、ウェイトコントロールレジスタWCR2の定数WAITが例えば1である遷移条件(9) が成立すると、バスステートコントローラBSCは、ステートST6に遷移し、ウェイトサイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、二つのTpcm1w又はTpci1wによる1回分のウェイトステートが挿入され、出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)のハイレベルへの立ち上がりつまりデータの読み出し又は書き込み動作の終了が遅らされる。この間、ウェイトコントロール信号−WAITは、I/Oクロック信号CKIOの次の立ち上がりエッジを包含する所定のタイミングでロウレベルとされ、その次の立ち上がりエッジを包含する所定のタイミングでハイレベルに戻される。

【0082】

ステートST6によるウェイトサイクルが終了し遷移条件(12)が成立すると、バスステートコントローラBSCは、ステートST7に遷移し、アクセス終結サイクルに入る。このとき、メモリカードMEMC及びI/OカードIOCでは、図16ないし図20に例示されるように、Tpcm2サイクル又はTpci2サイクルによって出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)がハイレベルの無効レベルに戻され、指定されたアドレスに対するデータの読み出し又は書き込み動作が終結する。なお、ステートST6において、ウェイトコントロールレジスタWCR2の定数WAITが2以上とされ引き続きウェイトが必要な遷移条件(10)が成立すると、バスステートコントローラBSCは再度ステートST6によるウェイトサイクルを挿入する。

【0083】

ステートST7によるアクセス終結サイクルが終了すると、バスステートコントローラBSCは、バーストモード又は全サイクルの終結状態とPCMCIAコントロールレジスタPCRの定数TED及びTEHつまりセットアップ時間及びホールド時間の遅延条件とに応じて選択的にステートST1,ST2,ST5又はST6に遷移する。すなわち、バスステートコントローラBSCは、ステートST7のアクセス終結サイクル時にバーストモードが未終了である遷移条件(12)が成立した場合、ステートST6に戻り、バーストモードが終了するまでこれを繰り返す。このとき、メモリカードMEMC及びI/OカードIOCでは、図18に例示されるように、バススタート信号−BS及び出力イネーブル信号−OE等がバースト回数だけ断続して形成されるとともに、バスステートコントローラBSCのアドレス制御部ADCにより下位4ビットのアドレス信号A0〜A3が順次生成され、一連のアドレスに対する連続アクセスが行われる。

【0084】

一方、ステートST7のアクセス終結サイクル時、例えばバスサイズが小さいためにバイト又はワード単位の分割アクセスが行われその全サイクルが未終了であって、かつセットアップ時間及びホールド時間の遅延が必要ない遷移条件(13)が成立した場合、バスステートコントローラBSCは、ステートST5に戻り、アクセスを繰り返す。このとき、セットアップ時間の遅延が必要な遷移条件(14)が成立すると、バスステートコントローラBSCは、ステートST2に遷移し、またホールド時間の遅延が必要な遷移条件(16)ないし(18)が成立すると、その遅延サイクル数に応じてステートST8,ST9又はST10に遷移する。

【0085】

エリア5及びエリア6におけるメモリカードMEMC及びI/OカードIOCのバーストモードは、キャッシュファイルの際の16バイトのアクセスをバーストROMのページモードと同様な形で実現するためのものである。このとき、バーストモードのデータ転送回数は、バスコントロールレジスタBCR1により設定可能とされ、4回,8回又は16回連続アクセスを任意に選択できる。バーストモードによる読み出し時の先頭アクセスサイクルでは、読み出し要求発生の原因となったデータのアクセスが行われ、残りのサイクルでは、当該データを含む16バイトバウンダリのデータがラップアラウンドでアクセスされる。バーストモードによる書き込み時は、16バイトバウンダリのデータに対応して先頭から順次書き込みが行われる。先頭アクセス時及び2回目以降のアクセス時のウェイトステートの挿入回数は、前述のように、ウェイトコントロールレジスタWCR2の定数WAITによって選択的に設定可能とされる。

【0086】

ステートST7のアクセス終結サイクル時に全サイクルの終了が確認されかつホールド時間の遅延が必要ない遷移条件(15)が成立した場合、バスステートコントローラBSCは、ステートST1に戻る。また、このとき、PCMCIAコントロールレジスタPCRの定数TEHが1以上とされホールド時間の遅延が必要な遷移条件(16)ないし(18)が成立した場合、バスステートコントローラBSCはその遅延サイクル数つまりPCMCIAコントロールレジスタPCRの定数TEHの値に応じて選択的にステートST8,ST9又はST10に遷移する。

【0087】

バスステートコントローラBSCが遷移条件(16)の成立を受けてステートST8の遅延サイクルに遷移したとき、メモリカードMEMC及びI/OカードIOCでは、図17及び図20に例示されるように、Tpcm2wサイクル又はTpci2wサイクルが挿入され、出力イネーブル信号−OE(I/Oリードコントロール信号−ICIORD)又はライトイネーブル信号−WE1(I/Oライトコントロール信号−ICIOWR)の立ち上がりからアドレス信号A0〜A25の次の遷移までのホールド時間が1サイクル分だけ遅延される。また、バスステートコントローラBSCが遷移条件(17)の成立を受けてステートST9の遅延サイクルに遷移すると、Tpcm2wサイクル又はTpci2wサイクルが2回挿入されてそのホールド時間が2サイクル分遅延され、バスステートコントローラBSCが遷移条件(18)の成立を受けてステートST9の遅延サイクルに遷移した場合には、Tpcm2wサイクル又はTpci2wサイクルが3回挿入されてそのホールド時間が3サイクル分遅延される。

【0088】

ステートST8では、その遅延サイクル終了に際してステートST7と同様な終結条件の選択が行われ、バスステートコントローラBSCは、全サイクルの終結状態とPCMCIAコントロールレジスタPCRの定数TEDつまりセットアップ時間の遅延条件とに応じて選択的にステートST1,ST2又はST5に遷移する。すなわち、バスステートコントローラBSCは、ステートST8の遅延サイクル終了時に全サイクルが未終了でありかつセットアップ時間の遅延が必要ない遷移条件(22)の成立を受けてステートST5に、またセットアップ時間の遅延が必要な遷移条件(21)の成立を受けてステートST2にそれぞれ戻り、アクセスを繰り返す。そして、ステートST8で全サイクルの終了が確認され遷移条件(23)が成立すると、ステートST1に戻って待機状態となる。

【0089】

このように、各種半導体メモリやPCカードに対応しうる複雑な機能を有するバスステートコントローラBSCをステートマシンとし、その遷移条件を各コントロールレジスタの定数書き換えにより選択的に設定できるようにすることで、外部バスE−BUSのエリア0ないしエリア6におけるインターフェイス条件を各エリアに結合された半導体メモリ又はPCカードのそれに効率良く適合させることができるとともに、バスステートコントローラBSC自体の論理構成を簡素化し、そのシステム柔軟性を高めることができるものとなる。

【0090】

図21は、シンクロナスDRAMとPCカード(MEMC/(IOC))とを本発明のマイクロプロセッサMPUに接続した場合の接続例を示している。PCカード(MEMC/(IOC))とマイクロプロセッサMPUとの接続に関しては、図9において詳細に説明されているので、図21には、その1部分についてのみ図示される。また、PCカード(MEMC/(IOC))とマイクロプロセッサMPUとの接続に関しての説明は、図9において詳細に説明されているので、この図では行われない。

【0091】

図21に示されるように、SDRAM1およびSDRAM2のそれぞれは、256K×16ビットのメモリ構成にされる。SDRAM1は、マイクロプロセッサMPUから出力されるアドレス信号A11−A2を受けるように結合されたアドレス端子A9−A0と、マイクロプロセッサMPUのシステムクロック入出力端子CKIOに結合されたクロック端子CKLと、マイクロプロセッサMPUのクロックイネーブル信号端子CKEに結合されたクロックイネーブル信号端子CKEと、マイクロプロセッサMPUのチップセレクト信号端子−CS3に結合されたチップセレクト信号端子−CSと、マイクロプロセッサMPUのロウアドレスストローブ信号端子−RAS/−CEに結合されたロウアドレスストローブ信号端子−RASと、マイクロプロセッサMPUのカラムアドレスストローブ信号端子−CAS/−OEに結合されたカラムアドレスストローブ信号端子−CASと、マイクロプロセッサMPUのリード・ライトステータス信号端子RD/−WRに結合されたライトイネーブル信号端子−WEと、マイクロプロセッサMPUのデータ入出力端子D31−D16にそれぞれ結合されたデータ入出力端子I/O15−I/O0、マイクロプロセッサMPUのデータコントロール信号端子DQMUU及びDQMULにそれぞれ結合されたデータコントロール信号端子DQMU及びDQMLをと有する。

【0092】

SDRAM2は、マイクロプロセッサMPUから出力されるアドレス信号A11−A2を受けるように結合されたアドレス端子A9−A0と、マイクロプロセッサMPUのシステムクロック入出力端子CKIOに結合されたクロック端子CKLと、マイクロプロセッサMPUのクロックイネーブル信号端子CKEに結合されたクロックイネーブル信号端子CKEと、マイクロプロセッサMPUのチップセレクト信号端子−CS3に結合されたチップセレクト信号端子−CSと、マイクロプロセッサMPUのロウアドレスストローブ信号端子−RAS/−CEに結合されたロウアドレスストローブ信号端子−RASと、マイクロプロセッサMPUのカラムアドレスストローブ信号端子−CAS/−OEに結合されたカラムアドレスストローブ信号端子−CASと、マイクロプロセッサMPUのリード・ライトステータス信号端子RD/−WRに結合されたライトイネーブル信号端子−WEと、マイクロプロセッサMPUのデータ入出力端子D15−D0にそれぞれ結合されたデータ入出力端子I/O15−I/O0、マイクロプロセッサMPUのデータコントロール信号端子DQMLU及びDQMLLにそれぞれ結合されたデータコントロール信号端子DQMU及びDQMLをと有する。

【0093】

図21に示されるように、マイクロプロセッサMPUと高速なアドレスアクセス時間を有するシンクロナスDRAM(SDRAM1,SDRAM2)とを結合することによって、32ビット幅のメモリとして上記シンクロナスDRAM(SDRAM1,SDRAM2)を利用することが出来る。マイクロプロセッサMPUのシステムクロック入出力端子CKIOから出力されるシステムクロック信号は、中央処理装置CPUの動作クロックと同一の周波数を有するクロック信号であり、かつ、バスステートコントローラBSCにも供給される。

【0094】

図22は、図21に示される上記シンクロナスDRAM(SDRAM1,SDRAM2)のバーストリード動作を説明するためのバスサイクル波形図を示している。なお、同図では省略されているが、クロックイネーブル信号CKEはハイレベルにされている。クロックイネーブル信号CKEは、上記シンクロナスDRAMにリフレッシュ動作させるとき、選択的に、ロウレベルにされる。バススタート信号−BSは、バスサイクルをモニタするためのストローブ信号であり、上記シンクロナスDRAMには接続されない。

【0095】

最初のサイクルTrでは、上記シンクロナスDRAMが割り当てられた空間に対応した信号−CS3がロウレベルにされ、ロウアドレスストローブ信号−RASがロウレベルにされて、上記シンクロナスDRAMにロウアドレスが取り込まれる。次のサイクルTc では、カラムアドレスストローブ信号−CASがロウレベルにされて、上記シンクロナスDRAMにカラムアドレスが取り込まれる。このように中央処理装置CPU側からのクロック信号CKIOの立ち上がりエッジに同期して出力される信号−CS2、−RASや−CAS及びアドレス信号に対して、上記シンクロナスDRAMにおいてクロック信号CKIOの立ち上がりエッジに同期して上記各信号が取り込まれる。すなわち、上記シンクロナスDRAMの読み出し動作ないし図示されない各種動作は、クロック信号CKIOに基づき制御される。

【0096】

3番目のサイクルTd1では、−CASがハイレベルにリセットされる。そして、3番目以降Td 1〜Td 4の4サイクルにわたって上記シンクロナスDRAMからデータD31〜D0が、1D−4Dとして示すように、連続して読み出される。このようなバーストリードによって、4バイト×4サイクル=16バイトのデータを読み出すことができる。上記のようなタイミングでの制御信号の発生は、前記バスステートコントローラBCSにより形成される。

【0097】

図23には、上記シンクロナスDRAM(以下、単にSDRAMという)の一実施例のブロック図が示されている。同図に示されたSDRAMは、特に制限されないが、公知の半導体集積回路の製造技術によって単結晶シリコンのような1つの半導体基板上に形成される。

【0098】

この実施例のSDRAMは、メモリバンクA(BANKA)を構成するメモリアレイ200Aと、メモリバンク(BANKB)を構成するメモリアレイ200Bを備える。それぞれのメモリアレイ200Aと200Bは、マトリクス配置されたダイナミック型メモリセルを備え、図に従えば同一列に配置されたメモリセルの選択端子は列毎のワード線(図示せず)に結合され、同一行に配置されたメモリセルのデータ入出力端子は行毎に相補データ線(図示せず)に結合される。

【0099】

上記メモリアレイ200Aの図示しないワード線はロウデコーダ201Aによるロウアドレス信号のデコード結果に従って1本が選択レベルに駆動される。メモリアレイ200Aの図示しない相補データ線はセンスアンプ及びカラム選択回路202Aに結合される。センスアンプ及びカラム選択回路202Aにおけるセンスアンプは、メモリセルからのデータ読出しによって夫々の相補データ線に現れる微小電位差を検出して増幅する増幅回路である。それにおけるカラムスイッチ回路は、相補データ線を各別に選択して相補共通データ線204に導通させるためのスイッチ回路である。カラムスイッチ回路はカラムデコーダ203Aによるカラムアドレス信号のデコード結果に従って選択動作される。

【0100】

メモリアレイ200B側にも同様にロウデコーダ201B,センスアンプ及びカラム選択回路202B,カラムデコーダ203Bが設けられる。上記相補共通データ線204は入力バッファ210の出力端子及び出力バッファ211の入力端子に接続される。入力バッファ210の入力端子及び出力バッファ211の出力端子は16ビットのデータ入出力端子I/O0〜I/O15に接続される。

【0101】

アドレス入力端子A0〜A9から供給されるロウアドレス信号とカラムアドレス信号はカラムアドレスバッファ205とロウアドレスバッファ206にアドレスマルチプレクス形式で取り込まれる。供給されたアドレス信号はそれぞれのバッファが保持する。ロウアドレスバッファ206はリフレッシュ動作モードにおいてはリフレッシュカウンタ208から出力されるリフレッシュアドレス信号をロウアドレス信号として取り込む。カラムアドレスバッファ205の出力はカラムアドレスカウンタ207のプリセットデータとして供給され、カラムアドレスカウンタ207はコマンドなどで指定される動作モードに応じて、上記プリセットデータとしてのカラムアドレス信号、又はそのカラムアドレス信号を順次インクリメントした値を、カラムデコーダ203A,203Bに向けて出力する。

【0102】

コントローラ212は、特に制限されないが、クロック信号CKIOが入力される入力端子CLKと、クロックイネーブル信号CKEが入力される入力端子と、チップセレクト信号−CSが入力される入力端子と、カラムアドレスストローブ信号−CASが入力される入力端子、ロウアドレスストローブ信号−RASが入力される入力端子と、及びライトイネーブル信号−WEが入力される入力端子と、データコントロール信号DQMU,DQMLが入力される入力端子とに結合される。コントローラ212は、上記各入力端子から供給される外部制御信号とアドレス入力端子A0〜A9からの制御データとが供給され、これらの信号のレベルの変化やタイミングなどに基づいてSDRAMの動作モード及び上記回路ブロックの動作を制御するための内部タイミング信号を形成するもので、そのためのコントロールロジック(図示せず)とモードレジスタ30を備える。

【0103】

クロック信号CKIOはSDRAMのマクタクロックとされ、その他の外部入力信号は当該クロック信号CKIOの立ち上がりエッジに同期して有意とされる。チップセレクト信号−CSはそのロウレベルによってコマンド入力サイクルの開始を指示する。チップセレクト信号−CSがハイレベルのとき(チップ非選択状態)やその他の入力は意味を持たない。但し、メモリバンクの選択状態やバースト動作などの内部動作はチップ非選択状態への変化によって影響されない。−RAS,−CAS,−WEの各信号は通常のDRAMにおける対応信号とは機能が相違され、コマンドサイクルを定義するときに有意の信号とされる。

【0104】

上記ロウアドレス信号は、クロック信号CKIOの立ち上がりエッジに同期するロウアドレスストローブ・バンクアクティブコマンドサイクルにおけるA0〜A8のレベルによって定義される。A9からの入力は、上記ロウアドレスストローブ・バンクアクティブコマンドサイクルにおいてバンク選択信号とみなされる。即ち、A9の入力がロウレベルの時はメモリバンクBANKAが選択され、ハイレベルの時はメモリバンクBANKBが選択される。メモリバンクの選択制御は、特に制限されないが、選択メモリバンク側のロウデコーダのみの活性化、非選択メモリバンク側のカラムスイッチ回路の全非選択、選択メモリバンク側のみの入力バッファ210及び出力バッファ211への接続などの処理によって行うことができる。

【0105】

プリチャージコマンドサイクルにおけるA8の入力は相補データ線などに対するプリチャージ動作の態様を指示し、そのハイレベルはプリチャージの対象が双方のメモリバンクであることを指示し、そのロウレベルは、A9で指示されている一方のメモリバンクがプリチャージの対象であることを指示する。上記カラムアドレス信号は、クロック信号CKIOの立ち上がりエッジに同期するリード又はライトコマンド(カラムアドレス・リードコマンド、カラムアドレス・ライトコマンド)サイクルにおけるA0〜A7のレベルによって定義される。そして、この様にして定義されたカラムアドレスはバーストアクセスのスタートアドレスとされる。

【0106】

このように、シンクロナスDRAMの動作は、クロック信号CKIOに基づいて制御されている。一方、PCカードとしてのメモリカードMEMCないしI/OカードIOCの動作制御も、バスステートコントローラBSCの動作説明から理解されるように、クロック信号CKIOに基づいて制御されている。したがって、シンクロナスDRAMを高速に動作させながら、PCカード(メモリカードMEMC、I/OカードIOC)の動作制御させる場合、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間などが、PCカードの規格を満足できない場合が発生する。

【0107】

そのため、バスステートコントローラBSCの動作説明ないし図17及び図20から理解されるように、バスステートコントローラBSCにPCMCIAコントロールレジスタPCRが設けられ、PCMCIAコントロールレジスタPCRのセットアップ遅延の関する定数TEDないしホールド遅延に関する定数TEHに基づいて、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間やホールド時間などが制御される。

【0108】

このように、PCカードの起動信号としての出力イネーブル信号−OEないしライトイネーブル信号−WEのクロック信号CKIOの立ち下がりあるいはアドレス信号に対するセットアップ時間などを制御することが出来るので、PCカードとシンクロナスDRAMとを本発明のマイクロプロセッサMPUに同時に結合させても、本発明のマイクロプロセッサMPUは、不都合なくPCカードとシンクロナスDRAMに対するアクセスを行うことが出来る。

【0109】

以上の実施例により得られる作用効果は、下記の通りである。すなわち、

(1)パーソナルコンピュータ等に内蔵されるマイクロプロセッサに、外部バスに結合されかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラを設けることで、インターフェイス制御のための外付け部品を削減しつつ、各種の半導体メモリ及びPCカードを直接かつ同時にマイクロプロセッサの外部バスに結合することができるという効果が得られる。

【0110】

(2)上記(1)項において、外部バスのアドレス空間を所定数のエリアに分割し、これらのエリアに各種半導体メモリ又はPCカードを固定的に割り当てるとともに、マイクロプロセッサにその内部における論理アドレスを外部バスにおける物理アドレスに変換するメモリ管理ユニットを設けることで、外部バスE−BUSの物理アドレスによる制約からユーザを解放し、自由な論理アドレス空間を有するソフトウェアを構築できるという効果が得られる。

【0111】

(3)上記(1)項及び(2)項において、I/Oカードの物理アドレス空間をさらに二分し、I/Oカードがメモリとして機能する場合の物理アドレスと入出力装置として機能する場合の物理アドレスとを独立に割り当てるとともに、これらのアドレス空間をアドレス信号の所定ビットにより選択的に指定できるようにすることで、I/Oカードのメモリ又は入出力装置としての機能をソフトウェアによりダイナミックに切り替えることができるという効果が得られる。

【0112】

(4)上記(1)項ないし(3)項において、バスステートコントローラをステートマシンとし、各エリアに割り当てられた半導体メモリ又はPCカードの種類及びその動作条件等をソフトウェアによって容易に設定しうるコントロールレジスタを設けることで、各エリアにおけるインターフェイス条件を対応する半導体メモリ又はPCカードのインターフェイス条件に効率良く適合させることができるとともに、バスステートコントローラ自体の論理構成を簡素化し、そのシステムの柔軟性を高めることができる

【0113】

(5)上記(1)項ないし(4)項において、バスステートコントローラに、バーストモードのためのアドレス生成機能を持たせることで、マイクロプロセッサの外付け部品を増やすことなく、バーストモードを有する半導体メモリ及びPCカードを結合し、そのアクセスを高速化できるという効果が得られる。

【0114】

(6)上記(1)項ないし(5)項により、マイクロプロセッサの使い勝手を改善できるとともに、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し外付け部品数を削減して、その低コスト化を図ることができるという効果が得られる。

【0115】

以上、本発明者によってなされた発明を実施例に基づき具体的に説明したが、この発明は、上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。例えば、図1において、マイクロプロセッサMPUつまりマザーボードMBDの外部バスE−BUSに結合される半導体メモリ及びPCカードの種類及び数ならびにその組み合わせは、種々の実施形態を採りうる。また、パーソナルコンピュータは、各種の入出力装置を備えることができるし、そのブロック構成や接続形態も任意である。図2において、パーソナルコンピュータの外観構成は、これらの実施例による制約を受けない。図3において、マイクロプロセッサMPUは任意のブロック構成を採りうるし、そのバス形態も任意である。図4において、示されるマイクロプロセッサMPUの基板配置は本の一例であって、本発明に制約を与えない。

【0116】

図5及び図6において、外部バスE−BUSの物理アドレス空間は、任意数のエリアに分割できるし、その各種半導体メモリ及びPCカードに対する割り当ても任意に設定できる。図7ないし図11において、外部バスE−BUSの信号構成や各信号の有効レベル及び機能ならびに各種半導体メモリ及びPCカードとの組み合わせ等は、これらの実施例による制約を受けない。

【0117】

図12において、バスステートコントローラBSCのブロック構成は、設けられるレジスタの種類及び組み合わせを含めて任意である。図13ないし図15において、バスステートコントローラBSCのステートマシンとしての論理構成ならびに各ステートの機能及び遷移条件等は、種々の実施形態を採りうる。図16ないし図20において、各アクセスモードにおけるアドレス信号及び起動制御信号等の論理レベル及び時間関係等は、この実施例により制約されない。

【0118】

以上の説明では、主として本発明者によってなされた発明をその背景となった利用分野であるパーソナルコンピュータを構成するマイクロプロセッサに適用した場合について説明したが、それに限定されるものではなく、例えば、各種の携帯情報端末及びコンピュータを構成する同様なマイクロプロセッサにも適用できる。この発明は、少なくとも外部バスを有するマイクロプロセッサならびにこのようなマイクロプロセッサを含む装置又はシステムに広く適用できる。

【0119】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。すなわち、パーソナルコンピュータ及び携帯情報端末等に内蔵されるマイクロプロセッサに、その外部バスに結合されかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラを設けることで、インターフェイス制御のための外付け部品を削減しつつ、各種半導体メモリ及びPCカードとを直接かつ同時にマイクロプロセッサに結合できる。

【0120】

マイクロプロセッサの外部バスのアドレス空間を所定数のエリアに分割し、各エリアに各種半導体メモリ又はPCカードを固定的に割り当てるとともに、マイクロプロセッサにその内部における論理アドレスを外部バスにおける物理アドレスに変換するメモリ管理ユニットを設けることで、マイクロプロセッサの外部バスの物理アドレスによる制約からユーザを解放し、自由な論理アドレス空間を有するソフトウェアを構築することができる。

【0121】

I/Oカードの物理アドレス空間をさらに二分割し、I/Oカードがメモリとして機能する場合の物理アドレスと入出力装置として機能する場合のそれとを独立に割り当てるとともに、これらのアドレス空間をアドレス信号の所定ビットにより選択できるようにすることで、I/Oカードのメモリ又は入出力装置としての機能をソフトウェアによりダイナミックに切り替えることができる。

【0122】

バスステートコントローラをステートマシンとし、各エリアに割り当てられた半導体メモリ又はPCカードの種類及びその動作条件等をソフトウェアにより容易に設定しうるコントロールレジスタを設けることで、各エリアにおけるインターフェイス条件を対応する半導体メモリ又はPCカードのインターフェイス条件に効率良く適合させることができるとともに、バスステートコントローラ自体の論理構成を簡素化し、そのシステムの柔軟性を高めることができる。

【0123】

バスステートコントローラに、一連のアドレスを連続アクセスするバーストモードのためのアドレス生成機能を持たせることで、マイクロプロセッサの外付け部品を増やすことなく、バーストモードを有する半導体メモリ及びPCカードをマイクロプロセッサに結合し、そのアクセスを高速化できる。

【0124】

以上の結果、マイクロプロセッサの使い勝手を改善できるとともに、マイクロプロセッサを内蔵しかつPCカードインターフェイスを有するパーソナルコンピュータ等の設計工数を削減し、その外付け部品数を削減して、パーソナルコンピュータ等の低コスト化を図ることができる。

【図面の簡単な説明】

【0125】

【図1】この発明に係るマイクロプロセッサを含むパーソナルコンピュータの一実施例を示すシステム構成図である。

【図2】図1のパーソナルコンピュータの一実施例を示す外観構成図である。

【図3】図1のパーソナルコンピュータに含まれるマイクロプロセッサの一実施例を示すブロック図である。

【図4】図3のマイクロプロセッサの一実施例を示す基板配置図である。

【図5】図3のマイクロプロセッサの外部バスのアドレス空間を説明するための一実施例を示すアドレスマップ図である。

【図6】図3のマイクロプロセッサの外部バスのエリア5及びエリア6におけるアドレス空間を説明するための一実施例を示すアドレスマップ図である。

【図7】図3のマイクロプロセッサの外部バスの接続形態を説明するための一実施例を示す部分的な接続図である。

【図8】図3のマイクロプロセッサの外部バスの接続形態を説明するための一実施例を示す他の部分的な接続図である。

【図9】図7及び図8の外部バスにPCカードが結合される場合の一実施例を示す部分的なインターフェイス構成図である。

【図10】図7及び図8の外部バスの一実施例を示す部分的な信号構成図である。

【図11】図7及び図8の外部バスの一実施例を示す他の部分的な信号構成図である。

【図12】図3のマイクロプロセッサに含まれるバスステートコントローラの一実施例を示すブロック図である。

【図13】図12のバスステートコントローラの一実施例を示す状態遷移図である。

【図14】図13のバスステートコントローラの一実施例を示すステート構成図である。

【図15】図13のバスステートコントローラの状態遷移を説明するための一実施例を示す遷移条件図である。

【図16】図3のマイクロプロセッサのウェイトを伴わないメモリカードアクセス時の一実施例を示す信号波形図である。

【図17】図3のマイクロプロセッサのウェイトを伴うメモリカードアクセス時の一実施例を示す信号波形図である。

【図18】図3のマイクロプロセッサのバーストモードを用いたメモリカードアクセス時の一実施例を示す信号波形図である。

【図19】図3のマイクロプロセッサのウェイトを伴わないI/Oカードアクセス時の一実施例を示す信号波形図である。

【図20】図3のマイクロプロセッサのウェイトを伴うI/Oカードアクセス時の一実施例を示す信号波形図である。

【図21】図3のマイクロプロセッサにPCカードとシンクロナスDRAMとが結合される場合の一実施例を部分的に示すインターフェイス構成図である。

【図22】シンクロナスDRAMアクセス時の一実施例を示す信号波形図である。

【図23】シンクロナスDRAMの一実施例を示すブロック図である。

【符号の説明】

【0126】

MBD…マザーボード、POWU…電源ユニット、MPU…マイクロプロセッサ、E−BUS…外部バス、ROM…リードオンリメモリ、BROM…バーストROM、SRAM…スタティック型RAM、PSRAM…疑似SRAM、DRAM…ダイナミック型RAM、SDRAM…シンクロナスDRAM、BUF1〜BUF2…PCカードバッファ、PCSL1〜PCSL2…PCカードスロット、MEMC…メモリカード、IOC…I/Oカード、LCDC…ディスプレイコントローラ、LCDCON…ディスプレイ用コネクタ、LCD(DP)…液晶ディスプレイ、KBDC…キーボードコントローラ、KBDCON…キーボード用コネクタ、KBD(KB)…キーボード、

MSLOT…PCカードスロット、Ffile…ファイル、FDD…フレキシブルディスクドライブ、PEN…入力ペン。

CPU…中央処理ユニット、ALU…演算器、MULT…乗算器、MMU…メモリ管理ユニット、TLB…アドレス変換テーブル、CACHE(Cache)…キャッシュメモリ、BSC…バスステートコントローラ、REFC…リフレッシュコントローラ、DMAC…ダイレクトメモリアクセスコントローラ、TIM(Timer)…タイマ回路、SCI…シリアルコミュニケーションインターフェイス、D/A(D/Aconverter)ディジタル/アナログ変換回路、A/D(A/Dconverter)…アナログ/ディジタル変換回路、INTC…割り込みコントローラ、CPG…クロック発生回路、S−BUS…システムバス、C−BUS…キャッシュバス、P−BUS…周辺バス、

ENCODR…エンコーダ、OG…オアゲート、PORT…ポート、

CBIF…キャッシュバスインターフェイス部、M−BUS…BSCモジュールバス、ADR…アドレスレジスタ、ADC…アドレス制御部、DTR…データレジスタ、MPX…マルチプレクサ、WCR1〜WCR2…ウェイトコントロールレジスタ、WATEC…ウェイト制御部、BCR1〜BCR2…バスコントロールレジスタ、AREAC…エリア制御部、MCR…メモリコントロールレジスタ、DCR…DRAMコントロールレジスタ、PCR…PCMCIAコントロールレジスタ、MTC…メモリタイミング制御部、RFCR…リフレッシュカウントレジスタ、RTCNT…リフレッシュタイマカウントレジスタ、RTCOR…リフレッシュタイムコンスタントレジスタ、RTCSR…リフレッシュタイマコントロールステータスレジスタ、RFC…リフレッシュ制御部、ST1〜ST10…ステート、

22…SDRAM、30…モードレジスタ、200A,200B…メモリアレイ、201A,201B…ロウデコーダ、202A,202B…センスアンプ及びカラム選択回路、203A,203B…カラムデコーダ、205…カラムアドレスバッファ、206…ロウアドレスバッファ、207…カラムアドレスカウンタ、208…リフレッシュカウンタ、210…入力バッファ、211…出力バッファ、212…コントローラ。

【特許請求の範囲】

【請求項1】

半導体メモリ及びPCカードを直接結合可能にするインターフェイス回路を具備することを特徴とするマイクロプロセッサ。

【請求項2】

上記インターフェイス回路は、上記マイクロプロセッサの外部バスへ出力されるべき複数の制御信号を作成し、

上記半導体メモリは、ROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAMを含み、

上記PCカードは、メモリカード及びI/Oカードを含むものであることを特徴とする請求項1のマイクロプロセッサ。

【請求項3】

上記外部バスのアドレス空間は、複数のエリアに分割され、 上記複数のエリアのそれぞれは、所定の半導体メモリ又はPCカードに固定的に割り当てられ、

上記マイクロプロセッサは、その内部における論理アドレスを上記外部バスにおける物理アドレスに変換するメモリ管理ユニットを具備するものであることを特徴とする請求項2のマイクロプロセッサ。

【請求項4】

上記外部バスには、上記複数種の半導体メモリの一部又は全部とメモリカード及びI/Oカードとを同時に結合することができるものであることを特徴とする請求項2又は請求項3のマイクロプロセッサ。

【請求項5】

上記I/Oカードは、メモリとしての機能を有し、その入出力装置として機能する場合の物理アドレスは、メモリとして機能する場合の物理アドレスとは独立に割り当てられるものであることを特徴とする請求項2,請求項3又は請求項4のマイクロプロセッサ。

【請求項6】

上記マイクロプロセッサは、さらに、