マルチキャリア送信機

【課題】回路規模の縮減及び消費電力の低減を図るとともに、ダイナミックレンジの広いALC制御を可能とし、さらに低コスト化を図るマルチキャリア送信機の提供。

【解決手段】第1、第2の局部発振器からの第1、第2の高周波信号でそれぞれデータ変調して第1、第2の変調波を生成する第1、第2の変調器と、第1、第2の変調波を利得可変に増幅する第1、第2の可変利得増幅部と、2つの変調波を合成する合成部と、合成部の出力を分配しその一方をアンテナに供給する分配部と、分配された出力の他方を入力としALC制御のために抽出された第1、第2の変調波を第3の局部発振器からの高周波信号で第1、第2の中間周波数に周波数変換する周波数変換部と、送信出力制御信号と第1、第2の中間周波数を入力して比較演算処理し、第1、第2の制御電圧を可変利得増幅器に出力するALC回路と、備え、第1、第2の変調波の出力レベルを一定に保つ。

【解決手段】第1、第2の局部発振器からの第1、第2の高周波信号でそれぞれデータ変調して第1、第2の変調波を生成する第1、第2の変調器と、第1、第2の変調波を利得可変に増幅する第1、第2の可変利得増幅部と、2つの変調波を合成する合成部と、合成部の出力を分配しその一方をアンテナに供給する分配部と、分配された出力の他方を入力としALC制御のために抽出された第1、第2の変調波を第3の局部発振器からの高周波信号で第1、第2の中間周波数に周波数変換する周波数変換部と、送信出力制御信号と第1、第2の中間周波数を入力して比較演算処理し、第1、第2の制御電圧を可変利得増幅器に出力するALC回路と、備え、第1、第2の変調波の出力レベルを一定に保つ。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、マルチキャリア送信機に関し、特に、省スペース、低消費電力化を図るマルチキャリア送信機に関する。

【0002】

【従来の技術】図9に、TDMA(時分割多元アクセス)方式の従来のマルチキャリア送信機の構成の一例をプロック図にて示す。図9を参照すると、局部発振器2、5からの出力される異なった高周波信号a、bは、変調器3、6にてデ−タ変調され変調波a、bが生成される。次に変調波a、bは制御電圧59、60に応じた利得に増幅する可変利得増幅部4、7、分配部37、38及び合成部8を経由しアンテナ10から出力される。

【0003】ALC(自動レベル制御)制御のため、検波部39、40は、分配部37、38からの変調波c、dを入力し、変調波c、dの電力レベルに応じた直流電圧43、44を出力し、直流電圧43、44はA/Dコンバータ41、42によりデジタルデータ45、46に変換される。

【0004】デジタルデータ45、46はCPU47、48に入力され、 CPU(中央処理装置)47、48は、上位装置により送出される送信出力制御信号49、50を変換し送信出力制御信号データ53、54として記憶するROM(読み出し専用メモリ)51、52と、送信出力制御信号49、50を認識し、ROM51、52から送信出力制御信号データ53、54を読み出し、入力されたデジタルデータ45、46と送信出力制御信号データ53、54を常時監視し同一になるように比較演算処理を行い制御電圧データ55、56を生成、出力する。より詳細には、CPU47、48はデジタルデータ45、46入力し、ROM17にあらかじめ記憶されている送信出力制御信号データ53、54を読み出すことにより変調波c、dの電力レベルを検出し、上位装置から送出される送信出力制御信号49、50により、その送信出力制御信号データ53、54とデジタルデータ45、46を常時監視し、同一になるように比較演算処理を行い、制御電圧データ55、56を生成、出力する。

【0005】制御電圧データ55、56は、D/Aコンバータ57、58によって制御電圧59、60に変換する。周波数ごとにALC制御ループを有している。

【0006】

【発明が解決しようとする課題】しかし、図9に示した従来のマルチキャリア送信機は、次のような問題点があった。

【0007】第1の問題点は、回路のスペースの大型化及び消費電力が増大する、ということである。

【0008】その理由は、検波用の伝送路を共有せず、ALC制御ループを個別化した回路にて構成しているためである。

【0009】第2の問題点は、ダイナミックレンジの広いALC制御を行うことが困難である、ということである。

【0010】その理由は、中間周波数を用いてLOG−LINERアンプにて検波しないためである。

【0011】第の3問題点は、回路を構成するときにその価格が高価なものとなる、ということである。

【0012】その理由は、出力電力が低い場合に、ゼロバイアスダイオードを用いたり、検波ダイオードを駆動する駆動増幅部を用いる必要があるためである。

【0013】したがって、本発明は、上記問題点に鑑みてなされたものであって、その目的は、回路規模の縮減及び消費電力の低減を図るとともに、ダイナミックレンジの広いALC制御を可能とし、さらに低コスト化を図るマルチキャリア送信機を提供することにある。

【0014】

【課題を解決するための手段】前記目的を達成する本発明によるTDMA(時分割多元アクセス)方式のマルチキャリア送信機は、自動電力制御(ALC;Auto Level Control;自動レベル制御)ループを共有化することにより、省スペース、消費電力を低減させるようにしたものである。

【0015】

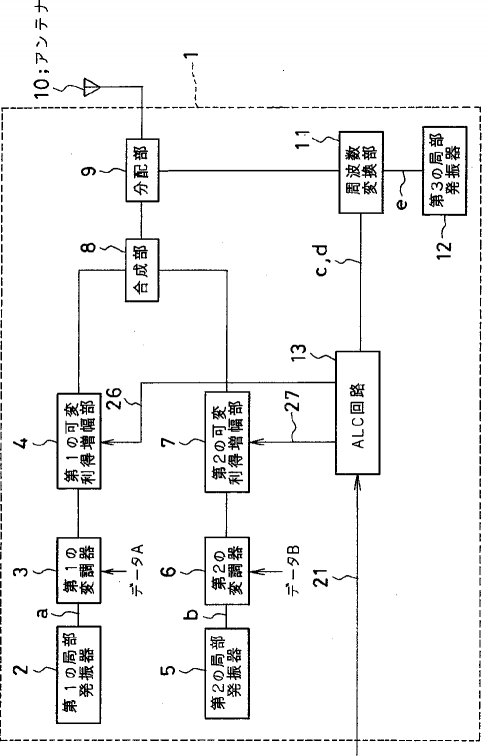

【発明の実施の形態】本発明の実施の形態について図面を参照して以下に説明する。図1は、本発明の実施の形態の構成を示す図である。図1を参照すると、本発明の実施の形態において、第1及び第2の局部発振器2、5から出力される異なった第1及び第2の高周波信号a、bは、第1及び第2の変調器3、6にてそれぞれデータ変調され第1及び第2の変調波a、bが生成される。次に、第1及び第2の変調波は、第1及び第2の制御電圧26、27に応じた利得に増幅する第1及び第2の可変利得増幅部4、7、2つの変調波を合成する合成部8、分配部9を経由して、一方はアンテナ10、他方は、ALC制御のため周波数変換部11へ出力される。

【0016】ALC制御のために抽出された第1及び第2の変調波a、bは、周波数変換部11において第3の局部発振器12からの第3の高周波信号cで第1及び第2の中間周波数c、dに周波数変換される。

【0017】ALC回路13は、送信出力制御信号21と第1及び第2の中間周波数c、dを入力して比較演算処理し、第1及び第2の制御電圧26、27を出力し、第1及び第2の変調波a、bの出力レベルを一定に保つことができる。

【0018】このように異なった高周波信号の2波の出力制御を独立のALC回路ループで行っている。

【0019】

【実施例】上記した本発明の実施の形態についてさらに詳細に説明すべく、本発明の実施例について図面を参照して以下に説明する。

【0020】図1を参照すると、本実施例のマルチキャリア送信機1は、異なった高周波信号a、bを出力する第1及び第2の局部発振器2、5と、高周波信号a、bにデ−タ変調をかけ第1及び第2の変調波a、bを生成する第1及び第2の変調器3、6と、変調波a、bを第1及び第2の制御電圧26、27に応じた利得に増幅する第1及び第2の可変利得増幅部4、7と、変調波a、bを合成する合成部8と、変調波a、bを一方はアンテナ10へ、他方は、第3の局部発振器12からの第3の高周波信号eで第1及び第2の中間周波数c、dに周波数変換する周波数変換部11に分配する分配部9と、中間周波数c、d及び送信出力制御信号21を入力し、制御電圧26、27を所定の値になるように比較演算処理するALC機能を具備したALC回路13を備える。

【0021】図2は、図1に示したALC回路13の構成の一例を示す図である。

【0022】図2を参照すると、ALC回路13は、中心周波数が中間周波数cかつ帯域が変調波の帯域であるバンドパスフィルタ特性を具備し、中間周波数cの電力レベルに対応した直流電圧15を出力する第1のLOG(対数)−LINER(線形)アンプ部14と、中心周波数が中間周波数dかつ帯域が変調波の帯域であるバンドパスフィルタ特性を具備し、中間周波数dの電力レベルに対応した直流電圧29を出力する第2のLOG(対数)−LINER(線形)アンプ部28と、直流電圧15、29に対応したデジタルデータ22、31に変換する第1及び第2のA/Dコンバータ16、30と、あらかじめ中間周波数c、dの入力電力レベル−デジタルデータ22、31の特性を記憶するROM17と、上位装置から送出される送信出力制御信号21を認識して、ROM17から送信出力制御信号データ23を読み出し、中間周波数cに対応したデジタルデータ22と送信出力制御信号データ23、中間周波数dに対応したデジタルデータ31と送信出力制御信号データ23との比較演算処理をそれぞれ独立に行い、制御電圧データ19、20を生成、出力するマイクロプロセッサ(CPU)18と、制御電圧データ19、20に対応した制御電圧26、27に変換する第1及び第2のD/Aコンバータ24、25と、を備えて構成される。

【0023】例えば、温度変動等により第1の可変利得増幅部4の増幅度が変化した場合(増大した場合)の変調波aの信号の流れは、周波数変換部11において周波数変換された中間周波数cの電力レベルが増大し、比例して直流電圧15も増大する。

【0024】第1のA/Dコンバータ16で変換されたデジタルデータ22は、変動前の送信出力制御信号データ23の値と異なるため、同一になるようにCPU18が比較演算処理を行い、前の値より小さい制御電圧データ19に可変し、制御電圧26は変化する。従って、第1の可変利得増幅部4の利得は減少され、出力電力は変動前の値に戻る。このようにALC制御を行っている。

【0025】一方、変調波bの信号の流れは、第2の局部発振器5、第2の変調器6、第2の可変利得増幅部7、中間周波数d、第2のLOG−LINERアンプ部28、直流電圧29、第2のA/Dコンバータ30、デジタルデータ31、制御電圧データ20、第2のD/Aコンバータ25、制御電圧27により、同様に動作する。また、ループの反応速度は、各スロットタイミングに対応しており、スロットごとのALC制御も可能である。

【0026】次に、図1に示した本実施例の動作について、図3に示す可変利得増幅部4、5の制御電圧−出力電力の関係、図4に示すマルチキャリア送信機1の運用状況のタイムチャート、図5に示すLOG−LINERアンプ部14、28での中間周波数c、dの電力レベル−直流電圧15、29の関係、図6に示すD/Aコンバータ16、30の入力データ−出力電圧の関係、図7に示すA/Dコンバータ24、25の入力電圧−出力デ−タの関係を参照して説明する。

【0027】以下、アクセス方式としてTDMA−FDD方式(PDCハーフレート)を採用しているマルチキャリア送信機に本発明を適用した一実施例を図面を参照しながら詳説する。

【0028】初めに、キャリア1のみ送信する場合(TS#0)。

【0029】局部発振器2から出力される高周波信号a(810MHz)は、変調器3にてデータ変調され変調波a(810MHz)を生成する。次に、その変調波aは、制御電圧26に応じた利得に増幅する可変利得増幅部4、合成部8、及び分配部11を経由してアンテナ10から出力される。一方、ALC制御は、分配部9から周波数変換部11側へ分配された変調波a(810MHz、−10dBm)が高周波信号e(800MHz)によって、周波数変換部11で中間周波数c(810MHz−800MH=10MHz、−20dBm)に周波数変換される。このときの電力レベルの変換ロスは、−10dBである。

【0030】その中間周波数cは、ALC回路13の、中心周波数が10MHzかつ帯域が21kHzのフィルタ特性を具備したLOG−LINERアンプ部14において、中間周波数cの電力レベル(−20[dBm])に対応した直流電圧15(1.4[V])に変換され、A/Dコンバータにおいて、その直流電圧15(1.4[V])に対応したデジタルデータ22(1Ch)に変換される。

【0031】マイクロプロセッサ(CPU)18は、入力したデジタルデータ22からROM17にあらかじめ記憶されている送信出力制御信号データ23(=中間周波数cの電力レベル−直流電圧の相対するデジタルデータ22と同様)[1Ch]を読み出すことにより、中間周波数cの電力レベルを−20[dBm]、つまり変調波aの電力レベルを−10[dBm]と判断し、上位装置から送出される送信出力制御信号21(028h)により、その送信出力制御信号データ23(1Ch)とデジタルデータ22(1Ch)を常時監視して同一になるように、比較演算処理を行い、変調波aの電力レベルが−10[dBm]となるように、制御電圧データ19(=可変利得増幅器4の出力電力に対応したデジタルデータ22と同様)[28h]を生成、出力する。

【0032】その制御電圧データ19(28h)は、D/Aコンバータ24においてに制御電圧26(2[V])に変換し、可変利得増幅器4に供給される。

【0033】例えば、温度変動等により可変利得増幅部4の出力電力が−10dBmから−9dBmに変化した場合(増大した場合)、中間周波数c(10MHz)の電力レベルも−20dBmから−19dBmに増大し、直流電圧15も1.4Vから1.5Vに増大する。

【0034】第1のA/Dコンバータ16で変換されたデジタルデータ22(1Eh)は、変動前の送信出力制御信号データ23の値(1Ch)と異なるため、同一になるように、CPU18が演算処理を行い、制御電圧データ19を(28h)から(26h)へ可変する。つまり、出力電力が−10dBmから−9dBmに増大した場合は、制御電圧データ19に対応した前の値より小さい制御電圧26(2Vから1.9V)に変換する。このため、可変利得増幅部4の利得は減少され、出力電力は変動前の値、つまり−9dBmから−10dBmに戻る。

【0035】以上のようにALC制御を行っている。本動作は、他のタイムスロット(TS#1〜TS#5)についても同様に独立して制御している。

【0036】次に、キャリア2のみ送信する場合(TS#1)。

【0037】局部発振器5から出力される高周波信号b(820MHz)は、変調器6にてデータ変調され変調波b(820MHz)を生成する。次に、その変調波bは制御電圧27に応じた利得に増幅する可変利得増幅部7、合成部8、分配部11を経由してアンテナ10から出力される。一方、ALC制御は分配部9から周波数変換部11側へ分配された変調波b(820MHz、−14dBm)が高周波信号e(800MHz)によって、中間周波数d(820MHz−800MH=20MHz、−24dBm)に周波数変換される。このときの電力レベルの変換ロスは、−10dBである。

【0038】その中間周波数dは、ALC回路13の中心周波数が20MHzかつ帯域が21kHzのフィルタ特性を具備したLOG−LINERアンプ部28において、中間周波数dの電力レベル(−24[dBm])に対応した直流電圧29(1.2[V])に変換し、第2のA/Dコンバータ30においてその直流電圧15(1.2[V])に対応したデジタルデータ22(18h)に変換される。

【0039】以後、キャリア2の信号の流れは、可変利得増幅部7、中間周波数d、LOG−LINERアンプ部28、直流電圧29、A/Dコンバータ30、デジタルデータ31、制御電圧データ20、D/Aコンバータ25、制御電圧27によってALC制御ループを構築する。

【0040】最後に、キャリア1及びキャリア2を同時に送信する場合(TS#5)。上述したように、キャリア1のループで変調波a(810MHz)、キャリア2のループ変調波b(820MHz)を同時に出力することになる。

【0041】従って、周波数変換部11には、同一タイミングで変調波a、bは入力され、中間周波数c(10Mhz)、d(20Mhz)に変換され、ALC回路13に入力される。このとき、分配部9から周波数変換部11を経由してALC回路13までの伝送路においては、変調波a、bあるいは中間周波数c、dが多重された形となっている。

【0042】よって、2つの中間周波数c、dを入力したALC回路13では、キャリア1のループにて中間周波数cを、キャリア2のループにて中間周波数dを同一タイミングで処理することが可能となり、2つのALC制御ループを構築することができる。

【0043】従って、キャリア1の出力電力とキャリア2の出力電力が異なったALC制御も可能となる。

【0044】次に、本発明の他の実施例について図面を参照して詳細に説明する。

【0045】図8は、本発明の第二の実施例の構成を示す図である。図8において、第1、第2の変調器3、6と、第1、第2の可変利得増幅器4、7の間にそれぞれ、局部発振部32からの高周波信号fを入力し、周波数変換する周波数変換部33、34が設けられている。また、分配部9からの変調波c、dを周波数変換部11で周波数変換する際、局部発振器32からの高周波信号fを入力している。

【0046】マルチキャリア送信機1の送信周波数が、変調器3、6の変調可能な周波数よりも高い場合、直接変調をかけられないという問題がある。この実施例は、変調波c、dが、周波数変換部において局部発振器32からの高周波信号fで周波数変換を行うことにより、高い周波数の変調波を出力できる。

【0047】この実施例は、変調器3、6の変調可能な周波数を超える周波数を出力できるという新たな効果を有する。

【発明の効果】以上説明したように、本発明によれば下記記載の効果を奏する。

【0048】本発明の第一の効果は、回路の省スペース、低消費電力が可能となる、ということである。

【0049】その理由は、本発明においては、高周波信号から中間周波数までの伝送路を共有して、ALC制御ループを共有化したためである。

【0050】本発明の第二の効果は、ダイナミックレンジの広いALC制御を可能とする、ということである。

【0051】その理由は、本発明においては、中間周波数を用いてLOG−LINERアンプにて検波しているためである。

【0052】本発明の第3の効果は、回路を構成する際に価格を低減する、ということである。

【0053】その理由は、本発明においては、出力電力が低い場合に、ゼロバイアスダイオードを用いたり、検波電圧を駆動する増幅部を用いる必要が無いためである。

【図面の簡単な説明】

【図1】本発明の一実施例の構成を示す図である。

【図2】本発明の一実施例におけるALC回路の構成を示す図である。

【図3】可変利得増幅部における制御電圧−出力電圧の関係を示す図である。

【図4】本発明の一実施例におけるマリチキャリア送信機の運用状況のタイムチャートである。

【図5】対数・直線増幅器の入出力特性(中間周波数の電力−出力電圧)を示す図である。

【図6】本発明の一実施例におけるALC回路のD/Aコンバータの入力データ−出力電圧の一例を示す図である。

【図7】本発明の一実施例におけるALC回路のA/Dコンバータの入力電圧−出力データの一例を示す図である。

【図8】本発明の第二の実施例の構成を示す図である。

【図9】従来のマルチキャリア送信機の構成を示す図である。

【符号の説明】

1 マルチキャリア送信機

2 第1の局部発信器

3 第1の変調器

4 第1の可変利得増幅器

5 第2の局部発信器

6 第2の変調器

7 第2の可変利得増幅器

8 合成器

9 分配器

10 アンテナ

11 周波数変換部

12 第3の局部発信器

13 ALC回路

14 第1のLOG−LINEARアンプ部

16 第1のA/Dコンバータ

17 ROM

18 CPU

21 送信制御信号

24 第1のD/Aコンバータ

25 第2のD/Aコンバータ

28 第2のLOG−LINEARアンプ部

30 第2のA/Dコンバータ

32 第4の局部発信器

33 第2の周波数変換部

34 第3の周波数変換部

35 第5の局部発信器

36 第6の局部発信器

【0001】

【発明の属する技術分野】本発明は、マルチキャリア送信機に関し、特に、省スペース、低消費電力化を図るマルチキャリア送信機に関する。

【0002】

【従来の技術】図9に、TDMA(時分割多元アクセス)方式の従来のマルチキャリア送信機の構成の一例をプロック図にて示す。図9を参照すると、局部発振器2、5からの出力される異なった高周波信号a、bは、変調器3、6にてデ−タ変調され変調波a、bが生成される。次に変調波a、bは制御電圧59、60に応じた利得に増幅する可変利得増幅部4、7、分配部37、38及び合成部8を経由しアンテナ10から出力される。

【0003】ALC(自動レベル制御)制御のため、検波部39、40は、分配部37、38からの変調波c、dを入力し、変調波c、dの電力レベルに応じた直流電圧43、44を出力し、直流電圧43、44はA/Dコンバータ41、42によりデジタルデータ45、46に変換される。

【0004】デジタルデータ45、46はCPU47、48に入力され、 CPU(中央処理装置)47、48は、上位装置により送出される送信出力制御信号49、50を変換し送信出力制御信号データ53、54として記憶するROM(読み出し専用メモリ)51、52と、送信出力制御信号49、50を認識し、ROM51、52から送信出力制御信号データ53、54を読み出し、入力されたデジタルデータ45、46と送信出力制御信号データ53、54を常時監視し同一になるように比較演算処理を行い制御電圧データ55、56を生成、出力する。より詳細には、CPU47、48はデジタルデータ45、46入力し、ROM17にあらかじめ記憶されている送信出力制御信号データ53、54を読み出すことにより変調波c、dの電力レベルを検出し、上位装置から送出される送信出力制御信号49、50により、その送信出力制御信号データ53、54とデジタルデータ45、46を常時監視し、同一になるように比較演算処理を行い、制御電圧データ55、56を生成、出力する。

【0005】制御電圧データ55、56は、D/Aコンバータ57、58によって制御電圧59、60に変換する。周波数ごとにALC制御ループを有している。

【0006】

【発明が解決しようとする課題】しかし、図9に示した従来のマルチキャリア送信機は、次のような問題点があった。

【0007】第1の問題点は、回路のスペースの大型化及び消費電力が増大する、ということである。

【0008】その理由は、検波用の伝送路を共有せず、ALC制御ループを個別化した回路にて構成しているためである。

【0009】第2の問題点は、ダイナミックレンジの広いALC制御を行うことが困難である、ということである。

【0010】その理由は、中間周波数を用いてLOG−LINERアンプにて検波しないためである。

【0011】第の3問題点は、回路を構成するときにその価格が高価なものとなる、ということである。

【0012】その理由は、出力電力が低い場合に、ゼロバイアスダイオードを用いたり、検波ダイオードを駆動する駆動増幅部を用いる必要があるためである。

【0013】したがって、本発明は、上記問題点に鑑みてなされたものであって、その目的は、回路規模の縮減及び消費電力の低減を図るとともに、ダイナミックレンジの広いALC制御を可能とし、さらに低コスト化を図るマルチキャリア送信機を提供することにある。

【0014】

【課題を解決するための手段】前記目的を達成する本発明によるTDMA(時分割多元アクセス)方式のマルチキャリア送信機は、自動電力制御(ALC;Auto Level Control;自動レベル制御)ループを共有化することにより、省スペース、消費電力を低減させるようにしたものである。

【0015】

【発明の実施の形態】本発明の実施の形態について図面を参照して以下に説明する。図1は、本発明の実施の形態の構成を示す図である。図1を参照すると、本発明の実施の形態において、第1及び第2の局部発振器2、5から出力される異なった第1及び第2の高周波信号a、bは、第1及び第2の変調器3、6にてそれぞれデータ変調され第1及び第2の変調波a、bが生成される。次に、第1及び第2の変調波は、第1及び第2の制御電圧26、27に応じた利得に増幅する第1及び第2の可変利得増幅部4、7、2つの変調波を合成する合成部8、分配部9を経由して、一方はアンテナ10、他方は、ALC制御のため周波数変換部11へ出力される。

【0016】ALC制御のために抽出された第1及び第2の変調波a、bは、周波数変換部11において第3の局部発振器12からの第3の高周波信号cで第1及び第2の中間周波数c、dに周波数変換される。

【0017】ALC回路13は、送信出力制御信号21と第1及び第2の中間周波数c、dを入力して比較演算処理し、第1及び第2の制御電圧26、27を出力し、第1及び第2の変調波a、bの出力レベルを一定に保つことができる。

【0018】このように異なった高周波信号の2波の出力制御を独立のALC回路ループで行っている。

【0019】

【実施例】上記した本発明の実施の形態についてさらに詳細に説明すべく、本発明の実施例について図面を参照して以下に説明する。

【0020】図1を参照すると、本実施例のマルチキャリア送信機1は、異なった高周波信号a、bを出力する第1及び第2の局部発振器2、5と、高周波信号a、bにデ−タ変調をかけ第1及び第2の変調波a、bを生成する第1及び第2の変調器3、6と、変調波a、bを第1及び第2の制御電圧26、27に応じた利得に増幅する第1及び第2の可変利得増幅部4、7と、変調波a、bを合成する合成部8と、変調波a、bを一方はアンテナ10へ、他方は、第3の局部発振器12からの第3の高周波信号eで第1及び第2の中間周波数c、dに周波数変換する周波数変換部11に分配する分配部9と、中間周波数c、d及び送信出力制御信号21を入力し、制御電圧26、27を所定の値になるように比較演算処理するALC機能を具備したALC回路13を備える。

【0021】図2は、図1に示したALC回路13の構成の一例を示す図である。

【0022】図2を参照すると、ALC回路13は、中心周波数が中間周波数cかつ帯域が変調波の帯域であるバンドパスフィルタ特性を具備し、中間周波数cの電力レベルに対応した直流電圧15を出力する第1のLOG(対数)−LINER(線形)アンプ部14と、中心周波数が中間周波数dかつ帯域が変調波の帯域であるバンドパスフィルタ特性を具備し、中間周波数dの電力レベルに対応した直流電圧29を出力する第2のLOG(対数)−LINER(線形)アンプ部28と、直流電圧15、29に対応したデジタルデータ22、31に変換する第1及び第2のA/Dコンバータ16、30と、あらかじめ中間周波数c、dの入力電力レベル−デジタルデータ22、31の特性を記憶するROM17と、上位装置から送出される送信出力制御信号21を認識して、ROM17から送信出力制御信号データ23を読み出し、中間周波数cに対応したデジタルデータ22と送信出力制御信号データ23、中間周波数dに対応したデジタルデータ31と送信出力制御信号データ23との比較演算処理をそれぞれ独立に行い、制御電圧データ19、20を生成、出力するマイクロプロセッサ(CPU)18と、制御電圧データ19、20に対応した制御電圧26、27に変換する第1及び第2のD/Aコンバータ24、25と、を備えて構成される。

【0023】例えば、温度変動等により第1の可変利得増幅部4の増幅度が変化した場合(増大した場合)の変調波aの信号の流れは、周波数変換部11において周波数変換された中間周波数cの電力レベルが増大し、比例して直流電圧15も増大する。

【0024】第1のA/Dコンバータ16で変換されたデジタルデータ22は、変動前の送信出力制御信号データ23の値と異なるため、同一になるようにCPU18が比較演算処理を行い、前の値より小さい制御電圧データ19に可変し、制御電圧26は変化する。従って、第1の可変利得増幅部4の利得は減少され、出力電力は変動前の値に戻る。このようにALC制御を行っている。

【0025】一方、変調波bの信号の流れは、第2の局部発振器5、第2の変調器6、第2の可変利得増幅部7、中間周波数d、第2のLOG−LINERアンプ部28、直流電圧29、第2のA/Dコンバータ30、デジタルデータ31、制御電圧データ20、第2のD/Aコンバータ25、制御電圧27により、同様に動作する。また、ループの反応速度は、各スロットタイミングに対応しており、スロットごとのALC制御も可能である。

【0026】次に、図1に示した本実施例の動作について、図3に示す可変利得増幅部4、5の制御電圧−出力電力の関係、図4に示すマルチキャリア送信機1の運用状況のタイムチャート、図5に示すLOG−LINERアンプ部14、28での中間周波数c、dの電力レベル−直流電圧15、29の関係、図6に示すD/Aコンバータ16、30の入力データ−出力電圧の関係、図7に示すA/Dコンバータ24、25の入力電圧−出力デ−タの関係を参照して説明する。

【0027】以下、アクセス方式としてTDMA−FDD方式(PDCハーフレート)を採用しているマルチキャリア送信機に本発明を適用した一実施例を図面を参照しながら詳説する。

【0028】初めに、キャリア1のみ送信する場合(TS#0)。

【0029】局部発振器2から出力される高周波信号a(810MHz)は、変調器3にてデータ変調され変調波a(810MHz)を生成する。次に、その変調波aは、制御電圧26に応じた利得に増幅する可変利得増幅部4、合成部8、及び分配部11を経由してアンテナ10から出力される。一方、ALC制御は、分配部9から周波数変換部11側へ分配された変調波a(810MHz、−10dBm)が高周波信号e(800MHz)によって、周波数変換部11で中間周波数c(810MHz−800MH=10MHz、−20dBm)に周波数変換される。このときの電力レベルの変換ロスは、−10dBである。

【0030】その中間周波数cは、ALC回路13の、中心周波数が10MHzかつ帯域が21kHzのフィルタ特性を具備したLOG−LINERアンプ部14において、中間周波数cの電力レベル(−20[dBm])に対応した直流電圧15(1.4[V])に変換され、A/Dコンバータにおいて、その直流電圧15(1.4[V])に対応したデジタルデータ22(1Ch)に変換される。

【0031】マイクロプロセッサ(CPU)18は、入力したデジタルデータ22からROM17にあらかじめ記憶されている送信出力制御信号データ23(=中間周波数cの電力レベル−直流電圧の相対するデジタルデータ22と同様)[1Ch]を読み出すことにより、中間周波数cの電力レベルを−20[dBm]、つまり変調波aの電力レベルを−10[dBm]と判断し、上位装置から送出される送信出力制御信号21(028h)により、その送信出力制御信号データ23(1Ch)とデジタルデータ22(1Ch)を常時監視して同一になるように、比較演算処理を行い、変調波aの電力レベルが−10[dBm]となるように、制御電圧データ19(=可変利得増幅器4の出力電力に対応したデジタルデータ22と同様)[28h]を生成、出力する。

【0032】その制御電圧データ19(28h)は、D/Aコンバータ24においてに制御電圧26(2[V])に変換し、可変利得増幅器4に供給される。

【0033】例えば、温度変動等により可変利得増幅部4の出力電力が−10dBmから−9dBmに変化した場合(増大した場合)、中間周波数c(10MHz)の電力レベルも−20dBmから−19dBmに増大し、直流電圧15も1.4Vから1.5Vに増大する。

【0034】第1のA/Dコンバータ16で変換されたデジタルデータ22(1Eh)は、変動前の送信出力制御信号データ23の値(1Ch)と異なるため、同一になるように、CPU18が演算処理を行い、制御電圧データ19を(28h)から(26h)へ可変する。つまり、出力電力が−10dBmから−9dBmに増大した場合は、制御電圧データ19に対応した前の値より小さい制御電圧26(2Vから1.9V)に変換する。このため、可変利得増幅部4の利得は減少され、出力電力は変動前の値、つまり−9dBmから−10dBmに戻る。

【0035】以上のようにALC制御を行っている。本動作は、他のタイムスロット(TS#1〜TS#5)についても同様に独立して制御している。

【0036】次に、キャリア2のみ送信する場合(TS#1)。

【0037】局部発振器5から出力される高周波信号b(820MHz)は、変調器6にてデータ変調され変調波b(820MHz)を生成する。次に、その変調波bは制御電圧27に応じた利得に増幅する可変利得増幅部7、合成部8、分配部11を経由してアンテナ10から出力される。一方、ALC制御は分配部9から周波数変換部11側へ分配された変調波b(820MHz、−14dBm)が高周波信号e(800MHz)によって、中間周波数d(820MHz−800MH=20MHz、−24dBm)に周波数変換される。このときの電力レベルの変換ロスは、−10dBである。

【0038】その中間周波数dは、ALC回路13の中心周波数が20MHzかつ帯域が21kHzのフィルタ特性を具備したLOG−LINERアンプ部28において、中間周波数dの電力レベル(−24[dBm])に対応した直流電圧29(1.2[V])に変換し、第2のA/Dコンバータ30においてその直流電圧15(1.2[V])に対応したデジタルデータ22(18h)に変換される。

【0039】以後、キャリア2の信号の流れは、可変利得増幅部7、中間周波数d、LOG−LINERアンプ部28、直流電圧29、A/Dコンバータ30、デジタルデータ31、制御電圧データ20、D/Aコンバータ25、制御電圧27によってALC制御ループを構築する。

【0040】最後に、キャリア1及びキャリア2を同時に送信する場合(TS#5)。上述したように、キャリア1のループで変調波a(810MHz)、キャリア2のループ変調波b(820MHz)を同時に出力することになる。

【0041】従って、周波数変換部11には、同一タイミングで変調波a、bは入力され、中間周波数c(10Mhz)、d(20Mhz)に変換され、ALC回路13に入力される。このとき、分配部9から周波数変換部11を経由してALC回路13までの伝送路においては、変調波a、bあるいは中間周波数c、dが多重された形となっている。

【0042】よって、2つの中間周波数c、dを入力したALC回路13では、キャリア1のループにて中間周波数cを、キャリア2のループにて中間周波数dを同一タイミングで処理することが可能となり、2つのALC制御ループを構築することができる。

【0043】従って、キャリア1の出力電力とキャリア2の出力電力が異なったALC制御も可能となる。

【0044】次に、本発明の他の実施例について図面を参照して詳細に説明する。

【0045】図8は、本発明の第二の実施例の構成を示す図である。図8において、第1、第2の変調器3、6と、第1、第2の可変利得増幅器4、7の間にそれぞれ、局部発振部32からの高周波信号fを入力し、周波数変換する周波数変換部33、34が設けられている。また、分配部9からの変調波c、dを周波数変換部11で周波数変換する際、局部発振器32からの高周波信号fを入力している。

【0046】マルチキャリア送信機1の送信周波数が、変調器3、6の変調可能な周波数よりも高い場合、直接変調をかけられないという問題がある。この実施例は、変調波c、dが、周波数変換部において局部発振器32からの高周波信号fで周波数変換を行うことにより、高い周波数の変調波を出力できる。

【0047】この実施例は、変調器3、6の変調可能な周波数を超える周波数を出力できるという新たな効果を有する。

【発明の効果】以上説明したように、本発明によれば下記記載の効果を奏する。

【0048】本発明の第一の効果は、回路の省スペース、低消費電力が可能となる、ということである。

【0049】その理由は、本発明においては、高周波信号から中間周波数までの伝送路を共有して、ALC制御ループを共有化したためである。

【0050】本発明の第二の効果は、ダイナミックレンジの広いALC制御を可能とする、ということである。

【0051】その理由は、本発明においては、中間周波数を用いてLOG−LINERアンプにて検波しているためである。

【0052】本発明の第3の効果は、回路を構成する際に価格を低減する、ということである。

【0053】その理由は、本発明においては、出力電力が低い場合に、ゼロバイアスダイオードを用いたり、検波電圧を駆動する増幅部を用いる必要が無いためである。

【図面の簡単な説明】

【図1】本発明の一実施例の構成を示す図である。

【図2】本発明の一実施例におけるALC回路の構成を示す図である。

【図3】可変利得増幅部における制御電圧−出力電圧の関係を示す図である。

【図4】本発明の一実施例におけるマリチキャリア送信機の運用状況のタイムチャートである。

【図5】対数・直線増幅器の入出力特性(中間周波数の電力−出力電圧)を示す図である。

【図6】本発明の一実施例におけるALC回路のD/Aコンバータの入力データ−出力電圧の一例を示す図である。

【図7】本発明の一実施例におけるALC回路のA/Dコンバータの入力電圧−出力データの一例を示す図である。

【図8】本発明の第二の実施例の構成を示す図である。

【図9】従来のマルチキャリア送信機の構成を示す図である。

【符号の説明】

1 マルチキャリア送信機

2 第1の局部発信器

3 第1の変調器

4 第1の可変利得増幅器

5 第2の局部発信器

6 第2の変調器

7 第2の可変利得増幅器

8 合成器

9 分配器

10 アンテナ

11 周波数変換部

12 第3の局部発信器

13 ALC回路

14 第1のLOG−LINEARアンプ部

16 第1のA/Dコンバータ

17 ROM

18 CPU

21 送信制御信号

24 第1のD/Aコンバータ

25 第2のD/Aコンバータ

28 第2のLOG−LINEARアンプ部

30 第2のA/Dコンバータ

32 第4の局部発信器

33 第2の周波数変換部

34 第3の周波数変換部

35 第5の局部発信器

36 第6の局部発信器

【特許請求の範囲】

【請求項1】第1及び第2の局部発振器から出力される異なった第1及び第2の高周波信号でそれぞれ第1及び第2のデータを変調して第1及び第2の変調波を生成する第1及び第2の変調器と、前記第1及び第2の変調波をそれぞれ利得可変に増幅する第1及び第2の可変利得増幅部と、前記第1及び第2の可変利得増幅部から出力された2つの変調波を合成する合成部と、前記合成部の出力を分配し、その一方をアンテナに供給する分配部と、前記分配部で分配された出力の他方を入力とし、ALC制御のために抽出された第1及び第2の変調波を第3の局部発振器からの第3の高周波信号で第1及び第2の中間周波数に周波数変換する周波数変換部と、送信出力制御信号と第1及び第2の中間周波数を入力して比較演算処理し、第1及び第2の制御電圧を前記可変利得増幅器に出力するALC回路と、備え、前記ALC回路が、入力した第1及び第2の中間周波数を、それぞれ検波する第1及び第2の対数−線形増幅器(LOG−LINEARアンプ)と、前記第1及び第2の対数−線形増幅器の出力をそれぞれ第1及び第2のデジタルデータに変換する第1及び第2のA/D変換器と、前記第1及び第2のA/D変換器からの前記第1及び第2の中間周波数の前記のデジタルデータと、送信出力制御信号データとの比較演算処理をそれぞれ独立に行い、第1及び第2の制御電圧データを生成出力するCPUと、前記第1及び第2の制御電圧データに対応した前記第1及び第2の制御電圧に変換する第1及び第2のD/A変換器と、を備え、前記第1及び第2の変調波の出力レベルを一定に保つ、ことを特徴とするマルチキャリア送信機。

【請求項2】前記第1及び第2の中間周波数の入力電力レベルとデジタルデータの特性を記憶する記憶部を備え、前記CPUが、上位装置から送出される送信出力制御信号を認識して、前記記憶部から送信出力制御信号データを読み出し、前記第1のA/D変換器からの前記第1の中間周波数に対応した第1のデジタルデータと送信出力制御信号データ、前記第2のA/D変換器からの前記第2の中間周波数に対応した第2のデジタルデータと送信出力制御信号データとの比較演算処理をそれぞれ独立に行い、前記第1、第2の制御電圧データを生成、出力することを特徴とする請求項1記載のマルチキャリア送信機。

【請求項3】前記第1及び第2の変調器と前記第1及び第2の可変利得増幅部の間にそれぞれ、第3の局部発信器からの高周波信号を入力として周波数変換する第2、第3の周波数変換部を備え、前記分配部からの第1、第2の変調波を前記第一の周波数変換部において前記第3の局部発信器からの高周波信号で中間周波数に周波数変換する、ことを特徴とする請求項1記載のマルチキャリア送信機。

【請求項1】第1及び第2の局部発振器から出力される異なった第1及び第2の高周波信号でそれぞれ第1及び第2のデータを変調して第1及び第2の変調波を生成する第1及び第2の変調器と、前記第1及び第2の変調波をそれぞれ利得可変に増幅する第1及び第2の可変利得増幅部と、前記第1及び第2の可変利得増幅部から出力された2つの変調波を合成する合成部と、前記合成部の出力を分配し、その一方をアンテナに供給する分配部と、前記分配部で分配された出力の他方を入力とし、ALC制御のために抽出された第1及び第2の変調波を第3の局部発振器からの第3の高周波信号で第1及び第2の中間周波数に周波数変換する周波数変換部と、送信出力制御信号と第1及び第2の中間周波数を入力して比較演算処理し、第1及び第2の制御電圧を前記可変利得増幅器に出力するALC回路と、備え、前記ALC回路が、入力した第1及び第2の中間周波数を、それぞれ検波する第1及び第2の対数−線形増幅器(LOG−LINEARアンプ)と、前記第1及び第2の対数−線形増幅器の出力をそれぞれ第1及び第2のデジタルデータに変換する第1及び第2のA/D変換器と、前記第1及び第2のA/D変換器からの前記第1及び第2の中間周波数の前記のデジタルデータと、送信出力制御信号データとの比較演算処理をそれぞれ独立に行い、第1及び第2の制御電圧データを生成出力するCPUと、前記第1及び第2の制御電圧データに対応した前記第1及び第2の制御電圧に変換する第1及び第2のD/A変換器と、を備え、前記第1及び第2の変調波の出力レベルを一定に保つ、ことを特徴とするマルチキャリア送信機。

【請求項2】前記第1及び第2の中間周波数の入力電力レベルとデジタルデータの特性を記憶する記憶部を備え、前記CPUが、上位装置から送出される送信出力制御信号を認識して、前記記憶部から送信出力制御信号データを読み出し、前記第1のA/D変換器からの前記第1の中間周波数に対応した第1のデジタルデータと送信出力制御信号データ、前記第2のA/D変換器からの前記第2の中間周波数に対応した第2のデジタルデータと送信出力制御信号データとの比較演算処理をそれぞれ独立に行い、前記第1、第2の制御電圧データを生成、出力することを特徴とする請求項1記載のマルチキャリア送信機。

【請求項3】前記第1及び第2の変調器と前記第1及び第2の可変利得増幅部の間にそれぞれ、第3の局部発信器からの高周波信号を入力として周波数変換する第2、第3の周波数変換部を備え、前記分配部からの第1、第2の変調波を前記第一の周波数変換部において前記第3の局部発信器からの高周波信号で中間周波数に周波数変換する、ことを特徴とする請求項1記載のマルチキャリア送信機。

【図2】

【図3】

【図6】

【図7】

【図1】

【図4】

【図5】

【図8】

【図9】

【図3】

【図6】

【図7】

【図1】

【図4】

【図5】

【図8】

【図9】

【特許番号】第2908403号

【登録日】平成11年(1999)4月2日

【発行日】平成11年(1999)6月21日

【国際特許分類】

【出願番号】特願平10−14929

【出願日】平成10年(1998)1月9日

【審査請求日】平成10年(1998)1月9日

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【参考文献】

【文献】特開 平3−265314(JP,A)

【文献】特開 平5−268178(JP,A)

【文献】特開 平6−132835(JP,A)

【文献】特開 平7−264146(JP,A)

【文献】特開 昭61−56531(JP,A)

【文献】特開 昭63−138807(JP,A)

【文献】特開 平8−274734(JP,A)

【文献】特開 平9−116359(JP,A)

【文献】特開 平8−213919(JP,A)

【文献】特開 平10−41857(JP,A)

【文献】特開 平10−173609(JP,A)

【登録日】平成11年(1999)4月2日

【発行日】平成11年(1999)6月21日

【国際特許分類】

【出願日】平成10年(1998)1月9日

【審査請求日】平成10年(1998)1月9日

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【参考文献】

【文献】特開 平3−265314(JP,A)

【文献】特開 平5−268178(JP,A)

【文献】特開 平6−132835(JP,A)

【文献】特開 平7−264146(JP,A)

【文献】特開 昭61−56531(JP,A)

【文献】特開 昭63−138807(JP,A)

【文献】特開 平8−274734(JP,A)

【文献】特開 平9−116359(JP,A)

【文献】特開 平8−213919(JP,A)

【文献】特開 平10−41857(JP,A)

【文献】特開 平10−173609(JP,A)

[ Back to top ]