マルチプロセッサシステム、ノードコントローラ、障害回復方式

【課題】ノードコントローラの障害によるシステム停止時間を短縮することが可能なマルチプロセッサシステムを提供することにある。

【解決手段】第一ノードコントローラと第二ノードコントローラは、リクエストに含まれるアクセス先のメモリアドレスに基づいて、リクエストの送信先の識別子を決定する第一、及び第二リクエスト制御部と、第一リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第一レジスタと、第二リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第二レジスタと、リクエストを受信すると、リクエストの送信先の識別子と、第一、及び第二レジスタに設定された識別子に基づいて、第一、第二リクエスト制御部のいずれかにリクエストの出力先を決定する第一ルーティングテーブルと、第一、第二リクエスト制御部の決定した送信先の識別子に基づいて、送信先の識別子に対応する信号線を選択して、リクエストを送信する第二ルーティングテーブルと、を備える。

【解決手段】第一ノードコントローラと第二ノードコントローラは、リクエストに含まれるアクセス先のメモリアドレスに基づいて、リクエストの送信先の識別子を決定する第一、及び第二リクエスト制御部と、第一リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第一レジスタと、第二リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第二レジスタと、リクエストを受信すると、リクエストの送信先の識別子と、第一、及び第二レジスタに設定された識別子に基づいて、第一、第二リクエスト制御部のいずれかにリクエストの出力先を決定する第一ルーティングテーブルと、第一、第二リクエスト制御部の決定した送信先の識別子に基づいて、送信先の識別子に対応する信号線を選択して、リクエストを送信する第二ルーティングテーブルと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マルチプロセッサシステムに関する。

【背景技術】

【0002】

マルチプロセッサシステムにおいて、ノードコントローラは、一般に冗長化されている。そのため、ノードコントローラの障害時には、障害の発生していないノードコントローラの動作により、システムの動作を継続する。従来、ノードコントローラ障害時におけるシステム性能の低下を抑えるために、各ノードのアドレスデコーダや、ルーティングテーブル等の設定を多数変更する必要が生じていた。そのため、システムの動作を回復するまでに長い時間を要し、特にシステムをリブートせずに動作を継続する場合には、設定変更に要する時間がオペレーションシステムの制約を満たすことができないことがあった。マルチプロセッサシステムにおける障害対策に関する技術が以下の通り公開されている。

【0003】

特許文献1は、障害による縮退運転時にも、アプリケーションが特別な処理を行う必要の無いマルチプロセッサシステムを開示している。特許文献1のマルチプロセッサシステムは、それぞれ個別の連続した識別情報が付与された複数のプロセッサを、通信経路情報を有する通信ノード要素を介して接続している。通信ノード要素は、故障が検出されたプロセッサへの通信経路を正常なプロセッサへの通信経路となるように変更して、見掛け上、複数のプロセッサの識別情報が連続し、かつ、総数が一定となるようにしている。そのため、特許文献1のマルチプロセッサシステムによれば、システムの縮退運転時に、アプリケーションがプロセッサの連続性や総数を意識した処理を行う必要が無くなる。

【0004】

特許文献2は、二重化された通信制御装置を接続して構成された二重化されたリングのそれぞれの異なる通信制御装置に障害が発生しても、障害が発生した通信制御装置に接続するプロセッサ間の通信を可能とするマルチプロセッサ間通信制御システムにおけるフレーム中継通信処理方式を開示している。特許文献2のフレーム中継通信処理方式は、各系の通信制御システムで異なるプロセッサに対応する通信制御装置の障害が発生して該プロセッサ間の各系内の通信システムによる直接通信が不可能となると、障害の発生した通信制御装置に対応する一方のプロセッサから他方のプロセッサへの通信は、正常な通信制御装置の一方の系から、両系の通信制御装置が正常であるプロセッサを介して他方の系へフレームを中継して行うことを特徴とする。特許文献2のフレーム中継通信処理方式によれば、二重化された通信制御装置のそれぞれにより構成されたリング等のネットワークにおける二重障害の場合に、両系が共に正常である通信制御装置を持つプロセッサでフレームを中継して送受することにより、障害の通信制御装置を持ったプロセッサ間の通信ダウンを防止することができる。

【0005】

特許文献3は、共通バスや、チャネル制御装置等の障害が発生しても系切替を行うことなく同じ通信バスを介する通信を維持することができる系間交絡通信制御方式を開示している。特許文献3の系間交絡通信制御方式は、0系と1系の各通信制御装置において、それぞれの共通バスインターフェース装置を二重化して、それぞれの一方の共通バスインターフェース装置は自系のリングバスインターフェース装置を介して自系のリングバスに接続し、他方は他系のリングバスインターフェース装置を介して他系のリングバスに接続し、各系のリングバスインターフェース装置は、通常は自系の共通バスに接続した共通バスインターフェース装置を選択し、自系の共通バスの障害等の場合には他系の共通バスに接続する共通バスインターフェース装置を選択して自系のリングバスを介する通信を行う。特許文献3の系間交絡通信制御方式によれば、現用系の共通バスに障害が発生しても、通信バスに接続された装置が正常である限り、他系との系間交絡通信を行うことにより、通信バスの系切替えを行うことなく通信を継続することができる。

【0006】

特許文献4は、充分な障害回避対策が計られてシステム全体の稼働率を向上し得る分散メモリ型マルチプロセッサシステムを開示している。特許文献4の分散メモリ型マルチプロセッサシステムは、プロセッサ及びローカルメモリ間をローカルネットワークで接続して成るプロセッサ構成装置の複数のものの間同士を互いに通信可能なようにグローバルネットワークで接続して成る分散メモリ型マルチプロセッサシステムにおいて、複数のプロセッサ構成装置は、それぞれプロセッサに接続された入出力機能を有するI/Oプロセッサと、I/Oプロセッサに接続された所定数のチャネル装置と、I/Oプロセッサ及びバスに接続された縮退運転用のリクエスト送出装置とを備える。特許文献4の分散メモリ型マルチプロセッサシステムによれば、プロセッサ構成装置及びグローバルネットワーク間に故障が発生した場合、プロセッサ構成装置内のハードウェア自体に故障がなければ、故障の発生したプロセッサ構成装置を縮退させることなく、データ転送速度は、低下するものの充分な障害回避対策が計られてシステム全体の稼働率を向上されることができるようになる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平4−321138号公報

【特許文献2】特開平5−158840号公報

【特許文献3】特開平5−175980号公報

【特許文献4】特開平11−053331号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、ノードコントローラの障害によるシステム停止時間を短縮することが可能なマルチプロセッサシステムを提供することにある。

【課題を解決するための手段】

【0009】

本発明のマルチプロセッサシステムは、複数のノードを備え、複数のノードの各々は、複数のプロセッサと、複数のプロセッサに対応して接続された複数のメモリと、複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備し、各ノードの複数のプロセッサと、第一ノードコントローラと、第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、第一ノードコントローラと第二ノードコントローラは、リクエストに含まれるアクセス先のメモリアドレスに基づいて、リクエストの送信先の識別子を決定する第一リクエスト制御部、及び第二リクエスト制御部と、第一リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第一レジスタと、第二リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第二レジスタと、リクエストを受信すると、リクエストの送信先の識別子と、第一レジスタ、及び第二レジスタに設定された識別子に基づいて、第一リクエスト制御部か第二リクエスト制御部のいずれかにリクエストの出力先を決定する第一ルーティングテーブルと、第一リクエスト制御部、あるいは第二リクエスト制御部の決定した送信先の識別子に基づいて、送信先の識別子に対応する信号線を選択して、リクエストを送信する第二ルーティングテーブルと、を備える。

【0010】

本発明のノードコントローラは、上述のマルチプロセッサシステムで使用される。

【0011】

本発明のマルチプロセッサシステムの障害回復方式は、複数のノードを備え、複数のノードの各々は、複数のプロセッサと、複数のプロセッサに対応して接続された複数のメモリと、複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備するマルチプロセッサシステムにおいて、各ノードの複数のプロセッサと、第一ノードコントローラと、第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、第一ノードコントローラと第二ノードコントローラは、リクエストに含まれるアクセス先のメモリアドレスに基づいて、リクエストの送信先の識別子を決定するステップと、第一リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を第一レジスタへ記憶するステップと、第二リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を第二レジスタへ記憶するステップと、リクエストを入力すると、リクエストの送信先の識別子と、第一レジスタ、及び第二レジスタに設定された識別子に基づいて、第一リクエスト制御部か第二リクエスト制御部のいずれかにリクエストの出力先を決定するステップと、第一リクエスト制御部、あるいは第二リクエスト制御部の決定した送信先の識別子に基づいて、送信先の識別子に対応する信号線を選択して、リクエストを送信するステップとを具備する。

【発明の効果】

【0012】

本発明によれば、ノードコントローラの障害によるシステム停止時間を短縮することが可能なマルチプロセッサシステムを提供することができる。

【図面の簡単な説明】

【0013】

【図1】本実施形態のマルチプロセッサシステムにおけるノード100の構成を示す図である。

【図2】本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を示す図である。

【図3】本実施形態におけるプロセッサ101の構成を示す図である。

【図4】本実施形態におけるルーティングテーブル404を示す図である。

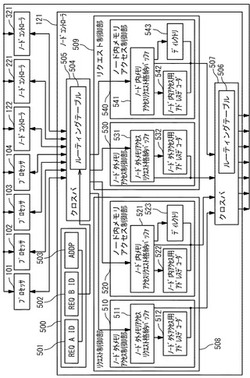

【図5】本実施形態におけるノードコントローラ121の構成を示す図である。

【図6】本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作フローである。

【図7A】本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作フローである。

【図7B】本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作フローである。

【図8A】本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。

【図8B】本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。

【図8C】本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。

【図9】本実施形態におけるノード100内の接続構成の変形例を示す図である。

【図10】本実施形態におけるノード100内の接続構成の変形例を示す図である。

【発明を実施するための形態】

【0014】

添付図面を参照して、本発明の実施形態によるマルチプロセッサシステムを以下に説明する。

【0015】

はじめに、図1を用いて本実施形態のマルチプロセッサシステムにおけるノード100の構成の説明を行う。図1は、本実施形態のマルチプロセッサシステムにおけるノード100の構成を示す図である。本実施形態のノード100は、プロセッサ101、102、103、104と、メモリ111、112、113、114と、ノードコントローラ121と、122とを備える。なお、本実施形態においてノード100は、4つのプロセッサとメモリとを備えているが、プロセッサ及びメモリの数量は限定せず、これより多くても良いし、あるいはこれより少なくても良い。なお、本実施形態において、プロセッサ101〜104、及びノードコントローラ121、122は、一意のIDを付与されている。プロセッサ101〜104は、それぞれノード100内のプロセッサ101〜104、及びノードコントローラ121、122のID情報のみを記憶している。ノードコントローラ121、122は、ノード100内のプロセッサ101〜104、及びノードコントローラ121、122のID情報のみでなく、後述する他ノードのノードコントローラのID情報を記憶している。そのため、プロセッサ101〜104は、ノード100外のプロセッサやノードコントローラへアクセスするときには、ノードコントローラ121、122へリクエストを送信して、ノードコントローラ121、122にリクエストを転送させることでノード100外へのアクセスを実現する。

【0016】

プロセッサ101は、信号線165によりメモリ111と接続される。プロセッサ102は、信号線166によりメモリ112と接続される。プロセッサ103は、信号線167によりメモリ113と接続される。プロセッサ104は、信号線168によりメモリ114と接続される。また、プロセッサ101は、信号線151によりノードコントローラ121と接続され、信号線152によりノードコントローラ122と接続される。さらに、プロセッサ101は、信号線153〜155により、それぞれプロセッサ102〜104と接続される。プロセッサ102は、信号線156によりノードコントローラ121と接続され、信号線157によりノードコントローラ122と接続される。さらに、プロセッサ102は、信号線153、158、159により、それぞれプロセッサ101、103、104と接続される。プロセッサ103は、信号線160によりノードコントローラ121と接続され、信号線161により、ノードコントローラ122と接続される。さらに、プロセッサ103は、信号線154、158、162により、それぞれプロセッサ101、102、104と接続される。プロセッサ104は、信号線163によりノードコントローラ121と接続され、信号線164によりノードコントローラ122と接続される。さらに、プロセッサ104は、信号線155、159、162により、それぞれプロセッサ101、102、103と接続される。

【0017】

プロセッサ101〜104は、それぞれ対応して接続されるメモリ111〜114のデータをキャッシュする。なお、プロセッサ101〜104は、それぞれ対応して接続されるメモリ111〜114以外の、ノード100内の他のメモリ111〜114のデータをキャッシュすることもできる。さらに、プロセッサ101〜104は、後述する図1に図示されないノード100の外部のノードの備えるメモリのデータもキャッシュすることが可能である。

【0018】

メモリ111〜114は、それぞれプロセッサ101〜104からキャッシュライン単位でアクセスされる。1キャッシュラインのビット幅は、例えば、64バイト(byte)で一定である。プロセッサ101〜104は、メモリアクセスの際に指定されるアドレスにより、キャッシュラインの位置を決定する。なお、メモリ111〜114は、後述する図1に図示されない外部のノードの備えるプロセッサからもデータをキャッシュされる。

【0019】

ノードコントローラ121、122は、ノード100の内部のプロセッサ101〜104がノード100の外部へアクセスする際、あるいは、ノード100の外部のプロセッサがノード100の内部へアクセスする際に、アクセス先を決定する。ノードコントローラ121とノードコントローラ122とは、信号線169により互いに接続される。ノードコントローラ121とノードコントローラ122とは、同様の機能を備えており、冗長構成となっている。

【0020】

以上が、本実施形態のマルチプロセッサシステムにおけるノード100の構成の説明である。なお、プロセッサ101と、ノードコントローラ121、122については、後に、さらに詳述する。

【0021】

次に、図2を用いて、本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を説明する。図2は、本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を示す図である。本実施形態のマルチプロセッサシステムは、ノード100と同様の構成を備えるノード200と、ノード300とを備える。ノード200は、プロセッサ201〜204と、メモリ211〜214と、ノードコントローラ221、222とを備える。また、ノード300は、プロセッサ301〜304と、メモリ311〜314と、ノードコントローラ321と322とを備える。ノード200とノード300とにおける各構成要素の接続関係は、ノード100と同様であるので説明を省略する。ノードコントローラ121と、221と、321とは、信号線20、21、22を用いて互いに1対1で接続される。また、ノードコントローラ122と、222と、322とは、信号線10、11、12を用いて互いに1対1で接続される。互いに接続されていないノードコントローラ間のおけるアクセスは、各ノード100、200、300内のノードコントローラ間を接続する信号線161、261、361を使用する。例えば、ノードコントローラ121からノードコントローラ222へのアクセスする場合、信号線161と、ノードコントローラ122と、信号線12とを経由してアクセスするか、あるいは、信号線22と、ノードコントローラ221と、信号線261とを経由してアクセスすることができる。

【0022】

以上が、本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を説明である。なお、ノード200とノード300とは、前述したノード100と同様の構成であるため、重ねての説明は省略する。

【0023】

次に、図3を用いて本実施形態におけるプロセッサ101の構成の説明を行う。図3は、本実施形態におけるプロセッサ101の構成を示す図である。尚、ノード100の備える他のプロセッサ102〜104、ノード200の備えるプロセッサ201〜204、及びノード300の備えるプロセッサ301〜304も同様の構成であるため重ねての説明は省略する。

【0024】

プロセッサ101は、リクエスト処理部401と、キャッシュ制御部402と、アドレスデコーダ403と、ルーティングテーブル404と、キャッシュ405と、クロスバ406とを備える。

【0025】

リクエスト処理部401は、命令を生成する。リクエスト処理部401は、キャッシュ制御部402と接続される。リクエスト処理部401は、メモリを読込むリードアクセス命令や、メモリへ書き込むライトアクセス命令などを生成する。リクエスト処理部401は、プロセッサ101上で動作するプロセスからの命令により、各命令を生成する。リクエスト制御部401は、生成した命令をキャッシュ制御部402へ出力する。

【0026】

キャッシュ405は、メモリのデータを一時的に格納する。キャッシュ405は、キャッシュ制御部402と接続される。キャッシュ405は、MESI(Modified,ExClusive,Shared,Invalid)のような一般的なキャッシュプロトコルを採用したキャッシュメモリである。キャッシュ405により、プロセッサ101は、一時的にメモリ111のデータをプロセッサ101内に格納することができる。

【0027】

キャッシュ制御部402は、キャッシュ405へのアクセスを制御する。キャッシュ制御部402は、リクエスト処理部401と、アドレスデコーダ403と、キャッシュ405と、クロスバ406と接続される。キャッシュ制御部402は、リクエスト処理部401から命令を入力すると、命令に記述されているアクセス先のアドレスに基づいて、アクセス先のキャッシュラインに対するアクセス権を保持しているか否かを判定する。キャッシュ制御部402は、リードアクセス時に、アクセス先のアドレスのキャッシュラインに対するアクセス権を保持している場合、キャッシュ405の当該キャッシュラインからデータを取り出して、リクエスト処理部401へ出力する。一方、キャッシュ制御部402は、リードアクセス時に、アクセス先のアドレスのキャッシュラインに対するアクセス権を保持していない場合、リードリクエストを生成して、アドレスデコーダ403へ出力する。また、キャッシュ制御部402は、ライトアクセス時には、キャッシュ405の当該キャッシュラインからデータを取り出して、データをマージする。キャッシュ制御部402は、リクエスト制御部401から入力するリクエスト、あるいは、クロスバ406を介してノード100外のプロセッサから入力するリクエストに基づいて、必要に応じてキャッシュ405のデータをメモリへ書き戻すライトリクエストを生成して、データと共にライトリクエストをアドレスデコーダ403へ出力する。また、キャッシュ制御部402は、クロスバ406を介してノード100外のプロセッサからキャッシュ405のキャッシュラインに対するアクセス権を入力すると、当該プロセッサの当該キャッシュラインに対するアクセス権の有無を保持する。キャッシュ制御部402は、当該プロセッサからのクロスバ406を介したアクセスに応じて、キャッシュ405へデータを格納し、あるいは、リクエスト処理部401へデータを出力する。

【0028】

アドレスデコーダ403は、リクエストに含まれるアクセス先のアドレスに基づいて、プロセッサ、あるいはノードコントローラのIDを特定する。アドレスデコーダ403は、キャッシュ制御部402と、ルーティングテーブル404と接続される。アドレスデコーダ403は、ノード100内のメモリ112〜114、ノード200の備えるメモリ211〜214、及びノード300の備えるメモリ311〜314にそれぞれ割り当てられたアドレス範囲を示すレジスタを備える。アドレスデコーダ403は、キャッシュ制御部402から入力するリクエストに含まれるアドレスに基づいて、当該アドレスの属するアドレス範囲を備えるメモリを特定して、当該メモリに対応するプロセッサ、あるいはノードコントローラのIDを特定する。アドレスデコーダ403は、プロセッサ、あるいはノードコントローラのIDを、リクエストと共にルーティングテーブル404へ出力する。

【0029】

ルーティングテーブル404は、リクエストを出力する信号線を決定する。ルーティングテーブル404は、アドレスデコーダ403と、クロスバ406と接続される。ルーティングテーブル404は、プロセッサ、及びノードコントローラの各IDに対応する信号線を記憶している。ルーティングテーブル404は、アドレスデコーダ403から入力するIDに基づいて、リクエストを出力する信号線を決定する。

【0030】

図4は、本実施形態におけるルーティングテーブル404を示す図である。ルーティングテーブル404は、プロセッサ、あるいはノードコントローラのIDと、出力先の信号線と、IDに対応するプロセッサ、あるいはノードコントローラの名称とを対応させて記録している。本実施形態において、プロセッサ及びノードコントローラへ付与されるIDは、5ビットである。IDの上位2ビット(第1ビット、第2ビット)は、ノード番号を示す。例えば、「00」でノード100を、「01」でノード200を、「10」でノード300を、それぞれ示す。その下位のビット(第3ビット)は、プロセッサであるかノードコントローラであるかを示す。例えば、「0」でプロセッサを、「1」でノードコントローラを、それぞれ示す。IDの下位2ビット(第4ビット、第5ビット)は、各プロセッサおよびノードコントローラに付与される番号を示す。ノード100を例に示すと、「00000」でプロセッサ101を、「00001」でプロセッサ102を、「00010」でプロセッサ103を、「00011」でプロセッサ104を示す。また、「00100」でノードコントローラ121を、「00101」でノードコントローラ122を示す。例えば、アドレスデコーダ403は、プロセッサ102のアドレス範囲を示すあるリクエストを入力するとID「00001」と決定する。ルーティングテーブル404は、ID「00001」に基づいて、当該リクエストの出力先信号線を「信号線153」と決定する。同様に、プロセッサ103に対応するID「00010」であれば、出力先を「信号線154」と、プロセッサ104に対応するID「00011」であれば、出力先を「信号線155」と決定する。なお、図4に示すIDは、一例でありこの例に限定はしない。

【0031】

クロスバ406は、信号線151〜155、165へ、リクエストやリプライを出力する。クロスバ406は、キャッシュ制御部402と、ルーティングテーブル404と接続される。さらに、クロスバ406は、信号線151〜155、165を介して、メモリ111、プロセッサ102〜104、ノードコントローラ121、122と接続される。クロスバ406は、ルーティングテーブル404の決定した信号線へ、リクエスト処理部401の生成したリクエストを出力する。また、クロスバ406は、信号線151〜155、165から入力するリクエストや、リクエストに対するリプライをキャッシュ制御部402へ出力する。また、クロスバ406は、キャッシュ制御部402から入力するキャッシュ405のリプライを信号線151〜155、165へ出力する。さらに、クロスバ406は、他のプロセッサから入力したリクエストがプロセッサ101へのアクセスでない場合、当該リクエストに含まれるIDをルーティングテーブル404へ出力して、ルーティングテーブル404により出力すべき信号線決定し、当該出力すべき信号線へ当該リクエストを転送する。

【0032】

以上が、本実施形態におけるプロセッサ101の構成の説明である。

【0033】

次に、図5を用いて、本実施形態におけるノードコントローラ121、122の説明を行う。なお、ノードコントローラ121とノードコントローラ122とは、同様の構成であるため、ノードコントローラ121の説明のみを行い、ノードコントローラ122の説明を省略する。また、ノード200の備えるノードコントローラ221、222、及びノード300の備えるノードコントローラ321、322も、それぞれ同様の構成であるため説明を省略する。図5は、本実施形態におけるノードコントローラ121の構成を示す図である。本実施形態におけるノードコントローラ121は、リクエスト振り分け情報レジスタ部500と、ルーティングテーブル504、506と、クロスバ505、507と、リクエスト制御部508、509とを備える。

【0034】

リクエスト振り分け情報レジスタ部500は、レジスタ501、502、503を備える。レジスタ501、502、503は、それぞれ、ルーティングテーブル504と接続される。レジスタ501、502、503は、ノードコントローラ121が受信したリクエストを、リクエスト制御部508とリクエスト制御部509のいずれに振り分けるかを決定するためのレジスタである。レジスタ501は、リクエスト制御部508へ振り分けを行うべき送信先IDを設定している。つまり、例えば、リクエストの送信先IDがレジスタ501に設定されているIDであった場合、当該リクエストは、リクエスト制御部508へ転送される。同様に、レジスタ502は、リクエスト制御部509へ振り分け行うべき送信先IDを設定している。例えば、リクエストの送信先IDがレジスタ502に設定されているIDであった場合、当該リクエストは、リクエスト制御部509へ転送される。レジスタ501、502に設定されたIDは、リクエストの出力先を決定するための情報として、ルーティングテーブル504へ出力される。また、レジスタ503は、アドレスインタリーブを行うビット位置を設定している。レジスタ503に設定されたビット位置は、アドレスインタリーブの振り分けを行うために、ルーティングテーブル504へ出力される。本実施形態において、レジスタ501、502は、5ビットのレジスタであり、レジスタ503は、6ビットのレジスタである。なお、レジスタ501、502、503のビット数は、これに限定しない。レジスタ501、502、503のビット数は、プロセッサや、ノードコントローラへ付与されるIDに応じて変化する。

【0035】

ルーティングテーブル504は、前述したプロセッサ101の備えるルーティングテーブル404と同様の構成を備える。ルーティングテーブル504は、レジスタ501、502、503と、クロスバ505と接続される。ルーティングテーブル504は、プロセッサ101〜104や、ノードコントローラ122、221、321から入力するリクエストを、リクエスト振り分け情報レジスタ部500のレジスタ501〜503に設定された情報と、ルーティングテーブル504に設定された図4に示すようなルーティング情報とに基づいて、出力先を決定する。ルーティングテーブル504は、ノードコントローラ121と接続するプロセッサ101〜104や、ノードコントローラ122、221、321から入力するリクエストに含まれる送信先IDを取り出して、リクエスト振り分け情報レジスタ部500のレジスタ501、502に設定されたIDと比較を行う。ルーティングテーブル504は、リクエストの送信先IDがレジスタ501、あるいはレジスタ502のいずれかに設定されたIDと一致する場合、一致したIDに対応するリクエスト制御部へ当該リクエストを出力する。また、ルーティングテーブル504は、リクエストの送信先IDがレジスタ501、及びレジスタ502に設定されたいずれのIDとも一致する場合、レジスタ503に設定されたアドレスインタリーブを行うビット位置のアドレスを比較して、出力するリクエスト制御部を決定する。さらに、ルーティングテーブル504は、リクエストの送信先IDがレジスタ501、及びレジスタ502に設定されたいずれのIDとも一致しない場合、当該リクエストは別ノードへのアクセスするリクエストであると判定して、送信先IDに基づいて図4に示すようなルーティング情報を参照して、ノードコントローラ121と接続されるプロセッサ101〜104や、ノードコントローラ122、221、321への信号線を決定する。

【0036】

例えば、リクエストに含まれる送信先IDが「00100」であり、レジスタ501とレジスタ502とが共に「00100」を設定している場合、ルーティングテーブル504は、レジスタ503に設定されたビット位置を参照する。ここで、例えば、レジスタ503が「000111」を設定している場合、アドレスの「ビット7」を比較して、当該リクエストを出力するリクエスト制御部を決定する。また、リクエストに含まれる送信先IDが「00100」であり、レジスタ501が「00100」を設定し、レジスタ502が「00101」を設定している場合、ルーティングテーブル504は、当該リクエストの出力先をリクエスト制御部508と決定する。一方、ルーティングテーブル504のテーブルの状態が図4で示した状態であるときに、リクエストに含まれる送信先IDが「00001」であって、レジスタ501が「00100」を設定し、レジスタ502が「00101」を設定している場合、ルーティングテーブル504は、送信先IDがレジスタ501及びレジスタ502のいずれのIDとも一致しないと判定する。ルーティングテーブル504は、ルーティング情報を参照して、当該リクエストの送信先IDに対応するプロセッサ102への信号線153を、当該リクエストの出力先と決定する。

【0037】

クロスバ505、507は、入力したリクエストを、それぞれのルーティングテーブル504、506の決定した信号線へ出力する。クロスバ505は、ルーティングテーブル504と、リクエスト制御部508、509と接続される。さらに、クロスバ505は、信号線を介して、ノード100内のプロセッサ101〜104、ノードコントローラ122、及び、ノード200の221、ノード300の321とそれぞれ接続される。また、クロスバ507は、ルーティングテーブル506と、リクエスト制御部508、509と接続される。さらに、クロスバ505は、信号線を介して、ノード100内のプロセッサ101〜104、ノードコントローラ122、及び、ノード200の221、ノード300の321とそれぞれ接続される。

【0038】

リクエスト制御部508は、ノード外メモリアクセス制御部510と、ノード内メモリアクセス制御部520とを備える。また、リクエスト制御部509は、ノード外メモリアクセス制御部530と、ノード内メモリアクセス制御部540とを備える。リクエスト制御部509は、リクエスト制御部508と同様の構成であるので重ねての説明は省略する。

【0039】

ノード外メモリアクセス制御部510は、ノード外メモリアクセスリクエスト格納バッファ511と、ノード外アクセス用アドレスレコーダ512とを備える。ノード外メモリアクセスリクエスト格納バッファ511は、クロスバ505、507と、ノード外アクセス用アドレスデコーダ512と接続される。ノード外アクセス用アドレスレコーダ512は、さらに、クロスバ507と接続される。ノード外メモリアクセスリクエスト格納バッファ511は、ノード100の内部のプロセッサ101〜104が、ノード100の外部に存在するメモリへアクセスを行うためのリクエストを格納する。ノード外アクセス用アドレスレコーダ512は、ノード外メモリアクセスリクエスト格納バッファ511から入力するリクエストに含まれたアドレスに基づいて、出力先のノードコントローラのIDを割り出す。また、ノード外アクセス用アドレスレコーダ512で割り出されたIDは、クロスバ505がリクエストを受信したときに、当該リクエストの転送先をルーティングテーブル504で参照することを可能にするために、ルーティングテーブル504へリクエストと共に送信される。

【0040】

ノード外メモリアクセス制御部510は、ノード外メモリアクセスリクエスト格納バッファへ格納したリクエストからアドレスを抜き出して、ノード外アクセス用デコーダ512へ出力する。ノード外アクセス用アドレスデコーダ512は、ノード外メモリアクセスリクエスト格納バッファ511から入力するリクエストに含まれたアドレスに基づいて、出力先のノードコントローラのIDを割り出す。ノード外メモリアクセス制御部510は、ノード外アクセス用アドレスデコーダ512の割り出したIDと、ノード外メモリアクセスリクエスト格納バッファへ格納したリクエストとを、クロスバ507へ出力する。

【0041】

ノード内メモリアクセス制御部520は、ノード内メモリアクセスリクエスト格納バッファ521と、ノード内アクセス用アドレスデコーダ522と、ディレクトリ523とを備える。ノード内メモリアクセスリクエスト格納バッファ521は、クロスバ505、507と、ノード内アクセス用アドレスデコーダ522と、ディレクトリ523と接続される。ノード内アクセス用アドレスデコーダ522と、ディレクトリ523とは、さらに、クロスバ507と接続される。ノード内メモリアクセスリスト格納バッファ521は、ノード100の外部のプロセッサからノード100の備えるメモリ111〜114へアクセスを行うためのリクエストを格納する。ノード内アクセス用アドレスデコーダ522は、ノード内メモリアクセスリクエスト格納バッファ521から入力するアドレスに基づいて、当該リクエストの出力先のプロセッサのIDを割り出す。また、ノード内アクセス用アドレスレコーダ522で割り出されたIDは、クロスバ505がリクエストを受信したときに、当該リクエストの転送先をルーティングテーブル504で参照することを可能にするために、ルーティングテーブル504へリクエストと共に送信される。ディレクトリ523は、ノード100内のメモリ111〜114のライン毎にステータス情報を管理する。ステータス情報は、メモリ111〜114に格納されたデータが他ノードのプロセッサにキャッシュされているか否かを示す情報と、キャッシュされている場合、キャッシュしているプロセッサのIDとキャッシュされているメモリ111〜114のアドレス情報とを対応させて記録している。ディレクトリ523は、ノード100外のプロセッサがキャッシュするノード100内のメモリ111〜114のキャッシュラインのアドレス情報を、全て記録している。

【0042】

ノード内メモリアクセス制御部520は、ノード内メモリアクセスリクエスト格納バッファ521に格納したリクエストからアドレスを抜き出して、ノード内アクセス用アドレスデコーダ522と、ディレクトリ523とへ出力する。ノード内アクセス用アドレスデコーダ522は、ノード内メモリアクセスリクエスト格納バッファ521から入力するアドレスに基づいて、当該リクエストの出先のプロセッサのIDを割り出す。ノード内メモリアクセス制御部520は、ノード内アクセス用アドレスデコーダ522の割り出したプロセッサのIDと、ノード内メモリアクセスリクエスト格納バッファ521に格納したリクエストとを、クロスバ507へ出力する。ディレクトリ523は、アクセス元のプロセッサのIDと、アクセス先のプロセッサのID、及びキャッシュされるメモリ111〜114のアドレス情報とを記憶する。また、ノード内メモリアクセス制御部520は、ディレクトリ523に記録されたメモリ111〜114のデータをキャッシュしているプロセッサに対して、当該キャッシュラインのアクセス権の返却を要求するスヌープを作成して、クロスバ507へ出力する。

【0043】

ルーティングテーブル506は、ノード外メモリアクセス制御部510から出力されるリクエストを出力する信号線を、ノード外アクセス用アドレスデコーダ512から出力される転送先のIDに基づいて決定する。また、ルーティングテーブル506は、ノード内メモリアクセス制御部520から出力されるリクエストを出力する信号線を、ノード内アクセス用アドレスデコーダ522から出力される転送先のIDに基づいて決定する。ルーティングテーブル506は、クロスバ507と接続される。ルーティングテーブル506は、決定した信号線をクロスバ507へ通知する。

【0044】

以上が、本実施形態におけるマルチプロセッサシステムの構成の説明である。

【0045】

[動作方法の説明]

次に、本実施形態のマルチプロセッサシステムにおける動作方法の説明を行う。まず、図6を用いて、本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作方法を説明する。図6は、本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作フローである。本説明において、ノード100のノードコントローラ122に故障が発生した場合を用いて説明する。

【0046】

(ステップS601)

ノードコントローラ122に障害が発生する。ノードコントローラ122は、システムファームウェアへ障害を通知する。ここで、システムファームウェハは、マルチプロセッサ上で動作を行うソフトウェアであり、マルチプロセッサシステムを制御している。

【0047】

(ステップS602)

システムファームウェアは、ノードコントローラ122の障害を検知すると、ノード100、200、300の各プロセッサからのリクエスト出力を抑止する。

【0048】

(ステップS603)

システムファームウェアは、ノード100外のプロセッサに、キャッシュラインのアクセス権を返却させる。システムファームウェアは、ノードコントローラ121のディレクトリ523、543と、ノードコントローラ122のディレクトリ523、543(以下、区別のために、ディレクトリ523B、ディレクトリ543Bと表記する。)とに記録された、ノード100外のプロセッサによるノード100内のメモリ111〜114のキャッシュ状況に基づいて、ノード100外のプロセッサにキャッシュしているデータをメモリ111〜114へ書き戻させて、ノード100外のプロセッサにメモリ111〜114のキャッシュラインのアクセス権を返却させる。これによって、ノード100内のメモリ111〜114のデータを最新の状態に更新することができ、コヒーレンシを保証することができる。なお、ノードコントローラ121のディレクトリ523、543と、ノードコントローラ122のディレクトリ523B、543Bとは、各ノード間のコヒーレンシを保証するために、ノード100外のプロセッサによるキャッシュ状況を記録している。そのため、ノード100内のプロセッサがメモリ111〜114のデータをキャッシュしていたとしても問題とはならない。

【0049】

(ステップS604)

ノードコントローラ121は、振り分け制御レジスタ部500のレジスタ502に設定されたIDを、ノードコントローラ122のIDへ変更する。これによって、ノードコントローラ122宛てのリクエストは、リクエスト制御部509へ転送されることになる。つまり、ノードコントローラ121宛てのリクエストは、リクエスト制御部508へ、ノードコントローラ122宛てのリクエストは、リクエスト制御部509へ出力されることになる。なお、本実施形態では、レジスタ502に設定されたIDを変更しているが、レジスタ501に設定されたIDをノードコントローラ122のIDへ変更することも可能である。この場合は、ノードコントローラ122宛てのリクエストは、リクエスト制御部508へ転送されることになる。

【0050】

(ステップS605)

ノードコントローラ121は、ノードコントローラ121のリクエスト制御部509の備えるノード内アクセスアドレスデコーダ542がデコードを行うアドレス範囲を、ノードコントローラ122が対応していたアドレス範囲まで含むように変更する。リクエスト制御部509は、ノードコントローラ122宛てのリクエストを振り分けられるため、ノード内アクセスアドレスデコーダ542をノードコントローラ122のアドレス対応範囲まで適応させるためである。これによって、リクエスト制御部509にノードコントローラ122宛てのリクエストが転送されたとしても、ノード内アクセスアドレスデコーダ542は、ノードコントローラ122対応していたアドレス範囲に基づいて送信先のIDを決定することができる。なお、ノード外アクセス用アドレスデコーダ532は、ノードコントローラ121とノードコントローラ122で同様であるので、特に対応するための処理を行う必要はない。

【0051】

(ステップS606)

システムファームウェアは、ノードコントローラ121、122以外のノードコントローラ221、222、321、322の備えるルーティングテーブルを、縮退したノードコントローラ122を経由しないルーティング経路となるように設定を変更する。例えば、ノードコントローラ222からノードコントローラ121へアクセスする場合に、ノードコントローラ222から、ノードコントローラ122を経由して、ノードコントローラ121へ、という経路設定であるならば、ノードコントローラ222から、ノードコントローラ221を経由して、ノードコントローラ121へという経路設定へ変更する。

【0052】

また、ノードコントローラ122のIDへのアクセスがノードコントローラ121へ転送されるように、ルーティングテーブルの設定を変更する。このように設定することで、ノードコントローラ122宛てのリクエストは、ノードコントローラ121へ転送されることになる。ノードコントローラ121は、ノードコントローラ122宛てのリクエストを、リクエスト制御部509において処理するように設定されている。そのため、ノードコントローラ121は、ノードコントローラ122宛てのリクエストを受信して処理を行うことになる。

【0053】

(ステップS607)

ノード100内のプロセッサ101〜104は、ノードコントローラ122へのアクセスがノードコントローラ121へのアクセスとなるように、ルーティングテーブルの設定を変更する。すなわち、ノードコントローラ122のIDに対応する信号線を、ノードコントローラ121と接続された信号線へ変更する。このようにすることで、ノードコントローラ122宛てのリクエストは、ノードコントローラ121接続された信号線へ出力されて、ノードコントローラ121のリクエスト制御部509で処理されることになる。

【0054】

(ステップS608)

システムファームウェアは、ノード100、200、300に対するリクエストの出力抑止を解除する。その後、マルチプロセッサシステムが再開する。

【0055】

以上が、本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作方法の説明である。このように、本実施形態のマルチプロセッサシステムでは、冗長化されたノードコントローラ122の障害時において、ノードコントローラ121は、内部のレジスタ502にノードコントローラ122のIDを設定することで、ノードコントローラ122宛てのリクエスト等を処理することが可能となる。そのため、ノード100内のプロセッサ101〜104や、他のノード200、300のノードコントローラ221、222、321、322の備えるルーティングテーブルの設定を、ノードコントローラ122宛てのリクエストがノードコントローラ121宛てに送信されるように変更するのみで、システムを再開することができる。そのため、リクエストの送信先ID自体を書き換えるために、各ノードのアドレスデコーダを書き換える場合に比べて、短時間でシステムを再開することができる。

【0056】

次に、図7A、及び図7Bを用いて、本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作方法を説明する。図7A、及び図7Bは、本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作フローである。以下の説明では、ノード100のプロセッサ101から、ノード200のメモリ214へのリードリクエストが発行された場合を説明する。つまり、ノード100内のプロセッサ101が、ノード100外のメモリ214へアクセスする場合を説明する。

【0057】

(ステップS701)

キャッシュ制御部402は、ノード200のメモリ214へのリードリクエスト(以下、本説明においてリクエストと呼ぶ。)を生成する。プロセッサ101は、プロセッサ101上で動作するプロセスから要求を入力する。プロセッサ101のリクエスト処理部401は、ノード200のメモリ214に記録されたデータをキャッシュするための命令を生成する。キャッシュ制御部402は、リクエスト処理部401の生成した命令に基づいて、ノード200のメモリ214に記録されたデータをキャッシュするためのリードリクエストを生成する。

【0058】

(ステップS702)

プロセッサ101は、リクエストの送信先IDを決定する。プロセッサ101は、アドレスデコーダ403を参照して、キャッシュ制御部402の生成したリードリクエストに含まれるアクセス先のアドレスに基づいて、当該リードリクエストを送信する送信先IDを決定する。なお、本説明では、アクセス先のアドレスがノード200内のメモリ241上であるため、プロセッサ101は、送信先IDをノードコントローラ121のIDに決定する。

【0059】

(ステップS703)

プロセッサ101は、リクエストを出力する信号線を決定する。プロセッサ101は、ルーティングテーブル404を参照して、アドレスデコーダ403の決定した送信先IDに基づいて、出力する信号線を決定する。クロスバ406は、ルーティングテーブル404の決定した信号線へ、リクエストを出力する。本説明では、送信先IDがノードコントローラ121のIDであるため、プロセッサ101は、出力する信号線を信号線151と決定する。

【0060】

(ステップS704)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。ノードコントローラ121は、プロセッサ101からリクエストを、クロスバ505に受信する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報と、リクエスト振り分け情報レジスタ部500のレジスタ501〜503に設定された情報とを参照して、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。

【0061】

ルーティングテーブル504は、リクエスト振り分け情報レジスタ部500からレジスタ501、502に設定されたIDを取得できる。ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ501と一致する場合、リクエスト制御部508へ当該リクエストを出力する。一方、ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ502と一致する場合、リクエスト制御部509へ当該リクエストを出力する。また、ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ501、502のいずれとも一致する場合、レジスタ503に設定された値に基づいてアドレスインタリーブを行って、当該リクエストをリクエスト制御部508、509のいずれに出力するかを決定する。さらに、ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ501、502のいずれとも一致しない場合、当該リクエストは、他のノードコントローラ、あるいはプロセッサ宛であると判定して、ルーティングテーブル504に設定されたルーティング情報を参照して出力先を決定する。クロスバ505は、ルーティングテーブル504によって決定された出力先へ、リクエストを出力する。なお、本説明において、ノードコントローラ121は、当該リクエストの出力先として、リクエスト制御部508のノード外メモリアクセス制御部510と決定する。

【0062】

(ステップS705)

ノードコントローラ121は、リクエストの送信先IDを決定する。リクエスト制御部508のノード外メモリアクセス制御部510は、クロスバ504からリクエストを入力する。ノード外メモリアクセス制御部510は、当該リクエストを、ノード外メモリアクセスリクエスト格納バッファ511へ格納する。ノード外メモリアクセス制御部510は、リクエストをクロスバ507へ出力する。また、同時に、ノード外メモリアクセス制御部510は、ノード外アクセス用アドレスデコーダ512を参照して、リクエストに含まれるアクセス先のアドレスに基づいて、リクエストの転送先をノードコントローラ222と決定して、ノードコントローラ222の送信先IDをクロスバ507へ出力する。なお、本説明では、ノードコントローラ222は、アクセス先のアドレスがノード200のメモリ214であるため、ノード200のノードコントローラ221のIDを送信先IDと決定する。

【0063】

(ステップS706)

ノードコントローラ121は、送信先IDに基づいて、リクエストを出力する信号線を決定する。クロスバ507は、ノード外アクセス用アドレスデコーダ512から送信先IDを入力する。また、クロスバ507は、ノード外メモリアクセスリクエスト格納バッファ511からリクエストを入力する。ノードコントローラ121は、ルーティングテーブル506に設定されたルーティング情報を参照して、送信先IDに基づいて、リクエストを出力する信号線を決定する。クロスバ507は、決定した信号線22へリクエストを出力する。なお、本説明において、送信先IDがノードコントローラ221のIDであるため、ルーティングテーブル506は、リクエストの出力先を出力線22と決定する。クロスバ507は、リクエスト22を出力線22へ出力する。

【0064】

(ステップS707)

ノード200において処理が行われて、メモリ214からリプライデータを受信する。ノード200のノードコントローラ221は、ノード100のノードコントローラ121からリクエストを受信する。この後の動作は、別ノードでの動作のため説明を省略する。すなわち、この後、リクエストは、ノード200内のノードコントローラ222へ転送される。ノードコントローラ222は、メモリ214のデータのキャッシュ状況の確認をおこなう。リクエストはプロセッサ204へ送信されて、プロセッサ204からメモリ214へアクセスが行われる。メモリ214のアクセス先のアドレスのデータが、リプライデータとして送信時の経路を経由して、ノードコントローラ121へ送信される。

【0065】

(ステップS708)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリプライデータを出力するかを決定する。ノードコントローラ121は、メモリ214からのリプライデータをクロスバ505に入力する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報と、リクエスト振り分け情報レジスタ部500の各レジスタに設定された情報とを参照して、リクエスト制御部508、509のいずれにリプライデータを出力するかを決定する。この処理は、ステップS704で説明を行った処理と同様であるので、重ねての説明を省略する。なお、本説明において、ノードコントローラ121は、リプライデータの出力先をリクエスト制御部508のノード外メモリアクセス制御部510と決定する。クロスバ505は、ルーティングテーブル504により決定した出力先へリプライデータを出力する。

【0066】

(ステップS709)

ノード外メモリアクセス制御部510は、格納していたリクエストからリクエスト元のIDを取得する。ノード外メモリアクセス制御部510は、クロスバ505からリプライデータを入力すると、ノード外メモリアクセスリクエスト格納バッファ511へ格納していたリクエストに基づいて、当該リプライデータのリクエスト元のプロセッサ101のIDを決定する。ノード外メモリアクセス制御部510は、クロスバ507へ、プロセッサ11のIDと共にリプライデータを出力する。

【0067】

(ステップS710)

ノードコントローラ121は、リプライデータを出力する信号線を決定する。クロスバ507は、ノード外メモリアクセス制御部510からリプライデータを入力する。ノードコントローラ121は、ルーティングテーブル506に設定されたルーティング情報を参照して、リクエスト元のIDに基づいてリプライデータを出力する信号線を決定する。クロスバ505は、ルーティングテーブル506により決定された信号線へリプライデータを出力する。なお、本説明において、ノードコントローラ121は、リプライデータの信号線を、リクエスト元のプロセッサ101のIDに対応する信号線151と決定する。クロスバ505は、リプライデータを信号線151へ出力する

【0068】

(ステップS711)

プロセッサ101は、リプライデータをキャッシュ405へ保存すると共に、リクエスト処理部401へリプライデータを出力する。プロセッサ101のクロスバ406は、信号線151からリプライデータを受信する。クロスバ406は、リプライデータをキャッシュ制御部402へ出力する。キャッシュ制御部402は、リプライデータをキャッシュ405へ保存すると共に、リプライデータをリクエスト処理部401へ出力する。これにより、リードリクエスト処理は完了する。

【0069】

以上が、本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作方法の説明である。

【0070】

次に、図8A〜図8Cを用いて、本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作方法を説明する。図8A〜図8Cは、本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。以下の説明では、ノード200のプロセッサ204から、ノード100のメモリ105へのリードリクエストが発行された場合を説明する。つまり、ノード100外のプロセッサ204が、ノード100内のメモリ105へアクセスする場合を説明する。

【0071】

(ステップS801)

ノードコントローラ121は、ノード200のプロセッサ204からリクエストを受信する。ノード200のプロセッサ204は、ノード100のメモリ111へのリードリクエスト(以下、本説明でリクエストと呼ぶ。)を発行する。この動作は、ステップS701からステップS703においてプロセッサ101が行った処理と同様であるので説明を省略する。プロセッサ204の出力したリクエストは、ノードコントローラ221を介して、ノード100へ転送される。ノードコントローラ121は、ノードコントローラ221からプロセッサ204の発行したリクエストを、クロスバ505に受信する。

【0072】

(ステップS802)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報とリクエスト振り分け情報レジスタ部500のレジスタ501〜503に設定された情報とに基づいて、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。なお、本ステップにおける動作は、ステップS704と同様であるので重ねての説明を省略する。本説明において、ノードコントローラ121は、リクエストの出力先として、リクエスト制御部508のノード内メモリアクセス制御部520と決定する。クロスバ505は、リクエストをリクエスト制御部のノード内メモリアクセス制御部520へ出力する。

【0073】

(ステップS803)

ノード内メモリアクセス制御部520は、メモリ111のデータキャッシュ状況を確認する。ノード内メモリアクセス制御部520は、クロスバ505からリクエストを入力すると、リクエストをノード内メモリアクセスリクエスト格納バッファ521へ格納する。ノード内メモリアクセス制御部520は、ディレクトリ523を参照して、リクエストに含まれるアクセス先アドレスのデータキャッシュ状況を確認する。なお、本説明において、ノード内メモリアクセス制御部520は、ディレクトリ523を参照して、メモリ111のデータキャッシュ状況を確認する。

【0074】

(ステップS804)

ノード内メモリアクセス制御部520は、リクエストに含まれるメモリ111のアクセス先アドレスのデータが、他のプロセッサにキャッシュされているか否かを判定する。他のプロセッサにキャッシュされていない場合、ステップS805へ進む。一方、他のプロセッサにキャッシュされている場合、ステップS807へ進む。

【0075】

(ステップS805)

ノード内メモリアクセス制御部520は、リクエストの送信先IDを決定する。ノード内メモリアクセス制御部520は、リクエストに含まれるメモリ111のアクセス先アドレスのデータが他のプロセッサにキャッシュされていない場合、リクエストをクロスバ507へ出力する。同時に、ノード内メモリアクセス制御部520は、ノード内アクセス用アドレスデコーダ522を参照して、リクエストに含まれるアクセス先のアドレスに基づいて、送信先IDを決定する。ノード内メモリアクセス制御部520は、送信先IDをクロスバ507へ出力する。なお、本説明において、当該リクエストはメモリ111へのリードアクセスであるため、ノード内メモリアクセス制御部520は、送信先IDをプロセッサ101のIDと決定する。

【0076】

(ステップS806)

ノードコントローラ121は、リクエストを出力する信号線を決定する。クロスバ507は、ノード内メモリアクセス制御部520からリクエストと送信式IDを入力する。ノードコントローラ121は、ルーティングテーブル506を参照して、リクエストを出力する信号線を決定する。クロスバ507は、ルーティングテーブル506により決定された出力先の信号線へリクエストを出力する。なお、本説明において、ノードコントローラ121は、プロセッサ101と接続された信号線151を、リクエストを出力する信号線と決定する。クロスバ507は、信号線151へリクエストを出力する。

【0077】

(ステップS807)

ノード内メモリアクセス制御部520は、メモリ111のアクセス権の返却を要求するスヌープを生成する。ノード内メモリアクセス制御部520は、リクエストに含まれるメモリ111のアクセス先アドレスのデータが他のプロセッサにキャッシュされている場合、メモリ111のアクセス権の返却を要求するスヌープを生成する。

【0078】

(ステップS808)

ノード内メモリアクセス制御部520は、スヌープを行うプロセッサの送信先IDを決定する。ノード内メモリアクセス制御部520は、ディレクトリ523を参照して、アクセス先アドレスのデータをキャッシュしているプロセッサのIDを決定する。ノード内メモリアクセス制御部520は、スヌープと送信先IDとをクロスバ507へ出力する。

【0079】

(ステップS809)

ノードコントローラ121は、スヌープを出力する信号線を決定する。クロスバ507は、ノード内メモリアクセス制御部520からスヌープと送信先IDとを入力する。ノードコントローラ121は、ルーティングテーブル506を参照して、送信先IDに基づいて、スヌープを出力する信号線を決定する。クロスバ507は、ルーティングテーブル506により決定された信号線へ、スヌープを出力する。

【0080】

(ステップS810)

ノード内メモリアクセス制御部520は、スヌープの結果に基づいて、所定の処理を行う。ノード内メモリアクセス制御部520は、スヌープのリプライを受信すると、必要に応じて、所定の処理を行う。ここで、所定の処理とは、メモリ111に対するライトリクエストの生成や、データの送受信や、ディレクトリ523の更新等である。このように、ノード内メモリアクセス制御部520は、スヌープのリプライに応じて、様々な処理を行うことになるが、これらは従来技術によるため、詳細な説明を省略する。なお、ノードコントローラ121は、この後、ステップS805、及びステップS806と同様の処理を実行する。すなわち、ノード内メモリアクセス制御部520は、リクエストの送信先IDを決定する(ステップS805)。ノードコントローラ121は、リクエストを出力する信号線を決定して、クロスバ507は、信号線151へリクエストを出力する(ステップS806)。その後、ステップS811へ進む。

【0081】

(ステップS811)

ノードコントローラ121は、メモリ111からリプライデータを受信する。プロセッサ101は、クロスバ507から出力されたリクエストを受信する。プロセッサ101は、メモリ111へリクエストを転送する。プロセッサ101は、メモリ111からアクセス先アドレスのデータを取得して、当該データを含めたリプライデータをノードコントローラ121へ出力する。

【0082】

(ステップS812)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。ノードコントローラ121は、プロセッサ101から、リプライデータをクロスバ505へ入力する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報と、リクエスト振り分け情報レジスタ部500の各レジスタの情報とを参照して、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。クロスバ505は、ルーティングテーブル504により決定した出力先へリプライデータを出力する。なお、本ステップにおける動作は、ステップS704と同様であるので重ねての説明を省略する。なお、本説明において、ノードコントローラ121は、リプライデータの出力先を、リクエスト制御部508のノード内メモリアクセス制御部520と決定する。クロスバ505は、ノード内メモリアクセス制御部520へリプライデータを出力する。

【0083】

(ステップS813)

ノード内メモリアクセス制御部520は、格納していたリクエストからリクエスト元のIDを取得する。ノード内メモリアクセス制御部510は、クロスバ505からリプライデータを入力すると、ノード内メモリアクセスリクエスト格納バッファ521へ格納していたリクエストに基づいて、リクエスト元のプロセッサのIDに基づいて、当該リプライデータの送信先IDを決定する。ノード外メモリアクセス制御部510は、クロスバ507へ、送信先IDと共にリプライデータを出力する。なお、本説明において、ノード内メモリアクセス制御部510は、リクエスト元のプロセッサIDに基づいて、当該リプライデータの送信先IDを、ノードコントローラ221と決定する。

【0084】

(ステップS814)

ノードコントローラ121は、リプライデータを出力する信号線を決定する。クロスバ507は、ノード内メモリアクセス制御部520からリプライデータと送信先IDを入力する。ノードコントローラ121は、ルーティングテーブル506を参照して、送信先IDに基づいて、リプライデータを出力する信号線を決定する。本説明において、ノードコントローラ121は、リプライデータの信号線を、ノードコントローラ221のIDに対応する信号線22と決定する。クロスバ505は、リプライデータを信号線22へ出力する

【0085】

(ステップS815)

ノード内メモリアクセス制御部520は、リクエスト元のプロセッサ204の情報をディレクトリ523へ記録する。ノード内メモリアクセス制御部520は、キャッシュラインのアクセス権を渡したプロセッサ204の情報をディレクトリへ記録する。これにより、プロセッサ204からのリクエストに対するノードコントローラ121の処理は完了する。なお、プロセッサ204は、ノードコントローラ221を介してリプライデータを受信して、プロセッサ204のキャッシュにデータを記録すると共に、リクエスト処理部へデータを出力して、リードリクエストを完了する。

【0086】

以上が、本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作方法の説明である。

【0087】

ここまで、本実施形態の説明を行ってきた、本発明によれば、各ノードのノードコントローラは、データの処理を行う2つのリクエスト制御部に対応して、いずれのリクエスト制御部にデータを転送するかを決定するためのIDを格納する2つのレジスタを備えている。片系のノードコントローラの故障時には、正常なノードコントローラの1つのレジスタへ、故障により縮退したノードコントローラのIDを設定する。また、当該ノード外の各ノードコントローラとノード内の各プロセッサのルーティングテーブルとに設定されたデータを、故障したノードコントローラ宛のリクエストを正常なノードコントローラ宛へ転送するように変更を行う。これによって、正常なノードコントローラは、故障したノードコントローラ宛のリクエストを受信して、1つのリクエスト制御部で処理を行うことが可能となる。このように、実際には故障しているノードコントローラ宛のリクエストを正常なノードコントローラで処理を行うことができるため、他ノードの各ノードコントローラや、各プロセッサにおいて、アドレスデコーダの設定変更を行う必要がない。そのため、故障発生時にマルチプロセッサシステムの停止時間を短時間にすることができる。

【0088】

なお、ノード100内(他のノード内も含む。)における各ノードコントローラと各プロセッサの接続は、図1で説明を行った接続構成に限定しない。図9、及び図10は、本実施形態におけるノード100内の接続構成の変形例を示す図である。例えば、図9に示すように、信号線601〜609による接続のように各プロセッサ同士を1対1に接続しない接続構成でも良いし、図10に示すようなバス700による接続のようなバス型の接続構成でもよい。

【0089】

また、ノードコントローラ121(他のノードコントローラを含む。)は、4つのアドレスデコーダ(512、522、532、542)を備えている。これは、ノード外アクセス用アドレスデコーダ512、532が、ノードコントローラ221、222、321、322までを対象としたアドレスデコーダであり、ノード内アクセス用アドレスデコーダ522、542が、ノード100内のプロセッサ101〜104を対象としたアドレスデコーダであるためである。しかし、ノード外アクセス用アドレスデコーダ512、532が、ノード100外のノード200、300の備えるプロセッサ201〜204、301〜304までを対象とするアドレスデコーダであるなら、ノード内へアクセスするときには、ノードコントローラ121から出力する出力先のプロセッサのIDが判明しているので、ノード内アクセス用アドレスデコーダ522、542を備えない構成とすることも可能である。

【0090】

以上、実施形態を参照して本発明を説明したが、本発明は上記実施形態に限定されるものではない。本発明の構成や詳細には、本発明の範囲内で当業者が理解し得る様々な変更を行うことが可能である。

【符号の説明】

【0091】

10〜12 信号線

20〜22 信号線

100 ノード

101〜104 プロセッサ

111〜114 メモリ

121、122 ノードコントローラ

151〜169 信号線

200 ノード

201〜204 プロセッサ

211〜214 メモリ

221、222 ノードコントローラ

269 信号線

300 ノード

301〜304 プロセッサ

311〜314 メモリ

321、322 ノードコントローラ

369 信号線

401 リクエスト処理部

402 キャッシュ制御部

403 アドレスデコーダ

404 ルーティングテーブル

405 キャッシュ

406 クロスバ

500 リクエスト振り分け情報レジスタ部

501 レジスタ

502 レジスタ

503 レジスタ

504 ルーティングテーブル

505 クロスバ

506 ルーティングテーブル

507 クロスバ

508 リクエスト制御部

509 リクエスト制御部

510 ノード外メモリアクセス制御部

511 ノード外メモリアクセスリクエスト格納バッファ

512 ノード外アクセス用アドレスデコーダ

520 ノード内メモリアクセス制御部

521 ノード内メモリアクセスリクエスト格納バッファ

522 ノード内アクセス用アドレスデコーダ

523 ディレクトリ

530 ノード外メモリアクセス制御部

531 ノード外メモリアクセスリクエスト格納バッファ

532 ノード外アクセス用アドレスデコーダ

540 ノード内メモリアクセス制御部

541 ノード内メモリアクセスリクエスト格納バッファ

542 ノード内アクセス用アドレスデコーダ

543 ディレクトリ

601〜609 信号線

700 バス

【技術分野】

【0001】

本発明は、マルチプロセッサシステムに関する。

【背景技術】

【0002】

マルチプロセッサシステムにおいて、ノードコントローラは、一般に冗長化されている。そのため、ノードコントローラの障害時には、障害の発生していないノードコントローラの動作により、システムの動作を継続する。従来、ノードコントローラ障害時におけるシステム性能の低下を抑えるために、各ノードのアドレスデコーダや、ルーティングテーブル等の設定を多数変更する必要が生じていた。そのため、システムの動作を回復するまでに長い時間を要し、特にシステムをリブートせずに動作を継続する場合には、設定変更に要する時間がオペレーションシステムの制約を満たすことができないことがあった。マルチプロセッサシステムにおける障害対策に関する技術が以下の通り公開されている。

【0003】

特許文献1は、障害による縮退運転時にも、アプリケーションが特別な処理を行う必要の無いマルチプロセッサシステムを開示している。特許文献1のマルチプロセッサシステムは、それぞれ個別の連続した識別情報が付与された複数のプロセッサを、通信経路情報を有する通信ノード要素を介して接続している。通信ノード要素は、故障が検出されたプロセッサへの通信経路を正常なプロセッサへの通信経路となるように変更して、見掛け上、複数のプロセッサの識別情報が連続し、かつ、総数が一定となるようにしている。そのため、特許文献1のマルチプロセッサシステムによれば、システムの縮退運転時に、アプリケーションがプロセッサの連続性や総数を意識した処理を行う必要が無くなる。

【0004】

特許文献2は、二重化された通信制御装置を接続して構成された二重化されたリングのそれぞれの異なる通信制御装置に障害が発生しても、障害が発生した通信制御装置に接続するプロセッサ間の通信を可能とするマルチプロセッサ間通信制御システムにおけるフレーム中継通信処理方式を開示している。特許文献2のフレーム中継通信処理方式は、各系の通信制御システムで異なるプロセッサに対応する通信制御装置の障害が発生して該プロセッサ間の各系内の通信システムによる直接通信が不可能となると、障害の発生した通信制御装置に対応する一方のプロセッサから他方のプロセッサへの通信は、正常な通信制御装置の一方の系から、両系の通信制御装置が正常であるプロセッサを介して他方の系へフレームを中継して行うことを特徴とする。特許文献2のフレーム中継通信処理方式によれば、二重化された通信制御装置のそれぞれにより構成されたリング等のネットワークにおける二重障害の場合に、両系が共に正常である通信制御装置を持つプロセッサでフレームを中継して送受することにより、障害の通信制御装置を持ったプロセッサ間の通信ダウンを防止することができる。

【0005】

特許文献3は、共通バスや、チャネル制御装置等の障害が発生しても系切替を行うことなく同じ通信バスを介する通信を維持することができる系間交絡通信制御方式を開示している。特許文献3の系間交絡通信制御方式は、0系と1系の各通信制御装置において、それぞれの共通バスインターフェース装置を二重化して、それぞれの一方の共通バスインターフェース装置は自系のリングバスインターフェース装置を介して自系のリングバスに接続し、他方は他系のリングバスインターフェース装置を介して他系のリングバスに接続し、各系のリングバスインターフェース装置は、通常は自系の共通バスに接続した共通バスインターフェース装置を選択し、自系の共通バスの障害等の場合には他系の共通バスに接続する共通バスインターフェース装置を選択して自系のリングバスを介する通信を行う。特許文献3の系間交絡通信制御方式によれば、現用系の共通バスに障害が発生しても、通信バスに接続された装置が正常である限り、他系との系間交絡通信を行うことにより、通信バスの系切替えを行うことなく通信を継続することができる。

【0006】

特許文献4は、充分な障害回避対策が計られてシステム全体の稼働率を向上し得る分散メモリ型マルチプロセッサシステムを開示している。特許文献4の分散メモリ型マルチプロセッサシステムは、プロセッサ及びローカルメモリ間をローカルネットワークで接続して成るプロセッサ構成装置の複数のものの間同士を互いに通信可能なようにグローバルネットワークで接続して成る分散メモリ型マルチプロセッサシステムにおいて、複数のプロセッサ構成装置は、それぞれプロセッサに接続された入出力機能を有するI/Oプロセッサと、I/Oプロセッサに接続された所定数のチャネル装置と、I/Oプロセッサ及びバスに接続された縮退運転用のリクエスト送出装置とを備える。特許文献4の分散メモリ型マルチプロセッサシステムによれば、プロセッサ構成装置及びグローバルネットワーク間に故障が発生した場合、プロセッサ構成装置内のハードウェア自体に故障がなければ、故障の発生したプロセッサ構成装置を縮退させることなく、データ転送速度は、低下するものの充分な障害回避対策が計られてシステム全体の稼働率を向上されることができるようになる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平4−321138号公報

【特許文献2】特開平5−158840号公報

【特許文献3】特開平5−175980号公報

【特許文献4】特開平11−053331号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、ノードコントローラの障害によるシステム停止時間を短縮することが可能なマルチプロセッサシステムを提供することにある。

【課題を解決するための手段】

【0009】

本発明のマルチプロセッサシステムは、複数のノードを備え、複数のノードの各々は、複数のプロセッサと、複数のプロセッサに対応して接続された複数のメモリと、複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備し、各ノードの複数のプロセッサと、第一ノードコントローラと、第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、第一ノードコントローラと第二ノードコントローラは、リクエストに含まれるアクセス先のメモリアドレスに基づいて、リクエストの送信先の識別子を決定する第一リクエスト制御部、及び第二リクエスト制御部と、第一リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第一レジスタと、第二リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第二レジスタと、リクエストを受信すると、リクエストの送信先の識別子と、第一レジスタ、及び第二レジスタに設定された識別子に基づいて、第一リクエスト制御部か第二リクエスト制御部のいずれかにリクエストの出力先を決定する第一ルーティングテーブルと、第一リクエスト制御部、あるいは第二リクエスト制御部の決定した送信先の識別子に基づいて、送信先の識別子に対応する信号線を選択して、リクエストを送信する第二ルーティングテーブルと、を備える。

【0010】

本発明のノードコントローラは、上述のマルチプロセッサシステムで使用される。

【0011】

本発明のマルチプロセッサシステムの障害回復方式は、複数のノードを備え、複数のノードの各々は、複数のプロセッサと、複数のプロセッサに対応して接続された複数のメモリと、複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備するマルチプロセッサシステムにおいて、各ノードの複数のプロセッサと、第一ノードコントローラと、第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、第一ノードコントローラと第二ノードコントローラは、リクエストに含まれるアクセス先のメモリアドレスに基づいて、リクエストの送信先の識別子を決定するステップと、第一リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を第一レジスタへ記憶するステップと、第二リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を第二レジスタへ記憶するステップと、リクエストを入力すると、リクエストの送信先の識別子と、第一レジスタ、及び第二レジスタに設定された識別子に基づいて、第一リクエスト制御部か第二リクエスト制御部のいずれかにリクエストの出力先を決定するステップと、第一リクエスト制御部、あるいは第二リクエスト制御部の決定した送信先の識別子に基づいて、送信先の識別子に対応する信号線を選択して、リクエストを送信するステップとを具備する。

【発明の効果】

【0012】

本発明によれば、ノードコントローラの障害によるシステム停止時間を短縮することが可能なマルチプロセッサシステムを提供することができる。

【図面の簡単な説明】

【0013】

【図1】本実施形態のマルチプロセッサシステムにおけるノード100の構成を示す図である。

【図2】本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を示す図である。

【図3】本実施形態におけるプロセッサ101の構成を示す図である。

【図4】本実施形態におけるルーティングテーブル404を示す図である。

【図5】本実施形態におけるノードコントローラ121の構成を示す図である。

【図6】本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作フローである。

【図7A】本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作フローである。

【図7B】本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作フローである。

【図8A】本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。

【図8B】本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。

【図8C】本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。

【図9】本実施形態におけるノード100内の接続構成の変形例を示す図である。

【図10】本実施形態におけるノード100内の接続構成の変形例を示す図である。

【発明を実施するための形態】

【0014】

添付図面を参照して、本発明の実施形態によるマルチプロセッサシステムを以下に説明する。

【0015】

はじめに、図1を用いて本実施形態のマルチプロセッサシステムにおけるノード100の構成の説明を行う。図1は、本実施形態のマルチプロセッサシステムにおけるノード100の構成を示す図である。本実施形態のノード100は、プロセッサ101、102、103、104と、メモリ111、112、113、114と、ノードコントローラ121と、122とを備える。なお、本実施形態においてノード100は、4つのプロセッサとメモリとを備えているが、プロセッサ及びメモリの数量は限定せず、これより多くても良いし、あるいはこれより少なくても良い。なお、本実施形態において、プロセッサ101〜104、及びノードコントローラ121、122は、一意のIDを付与されている。プロセッサ101〜104は、それぞれノード100内のプロセッサ101〜104、及びノードコントローラ121、122のID情報のみを記憶している。ノードコントローラ121、122は、ノード100内のプロセッサ101〜104、及びノードコントローラ121、122のID情報のみでなく、後述する他ノードのノードコントローラのID情報を記憶している。そのため、プロセッサ101〜104は、ノード100外のプロセッサやノードコントローラへアクセスするときには、ノードコントローラ121、122へリクエストを送信して、ノードコントローラ121、122にリクエストを転送させることでノード100外へのアクセスを実現する。

【0016】

プロセッサ101は、信号線165によりメモリ111と接続される。プロセッサ102は、信号線166によりメモリ112と接続される。プロセッサ103は、信号線167によりメモリ113と接続される。プロセッサ104は、信号線168によりメモリ114と接続される。また、プロセッサ101は、信号線151によりノードコントローラ121と接続され、信号線152によりノードコントローラ122と接続される。さらに、プロセッサ101は、信号線153〜155により、それぞれプロセッサ102〜104と接続される。プロセッサ102は、信号線156によりノードコントローラ121と接続され、信号線157によりノードコントローラ122と接続される。さらに、プロセッサ102は、信号線153、158、159により、それぞれプロセッサ101、103、104と接続される。プロセッサ103は、信号線160によりノードコントローラ121と接続され、信号線161により、ノードコントローラ122と接続される。さらに、プロセッサ103は、信号線154、158、162により、それぞれプロセッサ101、102、104と接続される。プロセッサ104は、信号線163によりノードコントローラ121と接続され、信号線164によりノードコントローラ122と接続される。さらに、プロセッサ104は、信号線155、159、162により、それぞれプロセッサ101、102、103と接続される。

【0017】

プロセッサ101〜104は、それぞれ対応して接続されるメモリ111〜114のデータをキャッシュする。なお、プロセッサ101〜104は、それぞれ対応して接続されるメモリ111〜114以外の、ノード100内の他のメモリ111〜114のデータをキャッシュすることもできる。さらに、プロセッサ101〜104は、後述する図1に図示されないノード100の外部のノードの備えるメモリのデータもキャッシュすることが可能である。

【0018】

メモリ111〜114は、それぞれプロセッサ101〜104からキャッシュライン単位でアクセスされる。1キャッシュラインのビット幅は、例えば、64バイト(byte)で一定である。プロセッサ101〜104は、メモリアクセスの際に指定されるアドレスにより、キャッシュラインの位置を決定する。なお、メモリ111〜114は、後述する図1に図示されない外部のノードの備えるプロセッサからもデータをキャッシュされる。

【0019】

ノードコントローラ121、122は、ノード100の内部のプロセッサ101〜104がノード100の外部へアクセスする際、あるいは、ノード100の外部のプロセッサがノード100の内部へアクセスする際に、アクセス先を決定する。ノードコントローラ121とノードコントローラ122とは、信号線169により互いに接続される。ノードコントローラ121とノードコントローラ122とは、同様の機能を備えており、冗長構成となっている。

【0020】

以上が、本実施形態のマルチプロセッサシステムにおけるノード100の構成の説明である。なお、プロセッサ101と、ノードコントローラ121、122については、後に、さらに詳述する。

【0021】

次に、図2を用いて、本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を説明する。図2は、本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を示す図である。本実施形態のマルチプロセッサシステムは、ノード100と同様の構成を備えるノード200と、ノード300とを備える。ノード200は、プロセッサ201〜204と、メモリ211〜214と、ノードコントローラ221、222とを備える。また、ノード300は、プロセッサ301〜304と、メモリ311〜314と、ノードコントローラ321と322とを備える。ノード200とノード300とにおける各構成要素の接続関係は、ノード100と同様であるので説明を省略する。ノードコントローラ121と、221と、321とは、信号線20、21、22を用いて互いに1対1で接続される。また、ノードコントローラ122と、222と、322とは、信号線10、11、12を用いて互いに1対1で接続される。互いに接続されていないノードコントローラ間のおけるアクセスは、各ノード100、200、300内のノードコントローラ間を接続する信号線161、261、361を使用する。例えば、ノードコントローラ121からノードコントローラ222へのアクセスする場合、信号線161と、ノードコントローラ122と、信号線12とを経由してアクセスするか、あるいは、信号線22と、ノードコントローラ221と、信号線261とを経由してアクセスすることができる。

【0022】

以上が、本実施形態のマルチプロセッサシステムにおけるノード間の接続関係を説明である。なお、ノード200とノード300とは、前述したノード100と同様の構成であるため、重ねての説明は省略する。

【0023】

次に、図3を用いて本実施形態におけるプロセッサ101の構成の説明を行う。図3は、本実施形態におけるプロセッサ101の構成を示す図である。尚、ノード100の備える他のプロセッサ102〜104、ノード200の備えるプロセッサ201〜204、及びノード300の備えるプロセッサ301〜304も同様の構成であるため重ねての説明は省略する。

【0024】

プロセッサ101は、リクエスト処理部401と、キャッシュ制御部402と、アドレスデコーダ403と、ルーティングテーブル404と、キャッシュ405と、クロスバ406とを備える。

【0025】

リクエスト処理部401は、命令を生成する。リクエスト処理部401は、キャッシュ制御部402と接続される。リクエスト処理部401は、メモリを読込むリードアクセス命令や、メモリへ書き込むライトアクセス命令などを生成する。リクエスト処理部401は、プロセッサ101上で動作するプロセスからの命令により、各命令を生成する。リクエスト制御部401は、生成した命令をキャッシュ制御部402へ出力する。

【0026】

キャッシュ405は、メモリのデータを一時的に格納する。キャッシュ405は、キャッシュ制御部402と接続される。キャッシュ405は、MESI(Modified,ExClusive,Shared,Invalid)のような一般的なキャッシュプロトコルを採用したキャッシュメモリである。キャッシュ405により、プロセッサ101は、一時的にメモリ111のデータをプロセッサ101内に格納することができる。

【0027】

キャッシュ制御部402は、キャッシュ405へのアクセスを制御する。キャッシュ制御部402は、リクエスト処理部401と、アドレスデコーダ403と、キャッシュ405と、クロスバ406と接続される。キャッシュ制御部402は、リクエスト処理部401から命令を入力すると、命令に記述されているアクセス先のアドレスに基づいて、アクセス先のキャッシュラインに対するアクセス権を保持しているか否かを判定する。キャッシュ制御部402は、リードアクセス時に、アクセス先のアドレスのキャッシュラインに対するアクセス権を保持している場合、キャッシュ405の当該キャッシュラインからデータを取り出して、リクエスト処理部401へ出力する。一方、キャッシュ制御部402は、リードアクセス時に、アクセス先のアドレスのキャッシュラインに対するアクセス権を保持していない場合、リードリクエストを生成して、アドレスデコーダ403へ出力する。また、キャッシュ制御部402は、ライトアクセス時には、キャッシュ405の当該キャッシュラインからデータを取り出して、データをマージする。キャッシュ制御部402は、リクエスト制御部401から入力するリクエスト、あるいは、クロスバ406を介してノード100外のプロセッサから入力するリクエストに基づいて、必要に応じてキャッシュ405のデータをメモリへ書き戻すライトリクエストを生成して、データと共にライトリクエストをアドレスデコーダ403へ出力する。また、キャッシュ制御部402は、クロスバ406を介してノード100外のプロセッサからキャッシュ405のキャッシュラインに対するアクセス権を入力すると、当該プロセッサの当該キャッシュラインに対するアクセス権の有無を保持する。キャッシュ制御部402は、当該プロセッサからのクロスバ406を介したアクセスに応じて、キャッシュ405へデータを格納し、あるいは、リクエスト処理部401へデータを出力する。

【0028】

アドレスデコーダ403は、リクエストに含まれるアクセス先のアドレスに基づいて、プロセッサ、あるいはノードコントローラのIDを特定する。アドレスデコーダ403は、キャッシュ制御部402と、ルーティングテーブル404と接続される。アドレスデコーダ403は、ノード100内のメモリ112〜114、ノード200の備えるメモリ211〜214、及びノード300の備えるメモリ311〜314にそれぞれ割り当てられたアドレス範囲を示すレジスタを備える。アドレスデコーダ403は、キャッシュ制御部402から入力するリクエストに含まれるアドレスに基づいて、当該アドレスの属するアドレス範囲を備えるメモリを特定して、当該メモリに対応するプロセッサ、あるいはノードコントローラのIDを特定する。アドレスデコーダ403は、プロセッサ、あるいはノードコントローラのIDを、リクエストと共にルーティングテーブル404へ出力する。

【0029】

ルーティングテーブル404は、リクエストを出力する信号線を決定する。ルーティングテーブル404は、アドレスデコーダ403と、クロスバ406と接続される。ルーティングテーブル404は、プロセッサ、及びノードコントローラの各IDに対応する信号線を記憶している。ルーティングテーブル404は、アドレスデコーダ403から入力するIDに基づいて、リクエストを出力する信号線を決定する。

【0030】

図4は、本実施形態におけるルーティングテーブル404を示す図である。ルーティングテーブル404は、プロセッサ、あるいはノードコントローラのIDと、出力先の信号線と、IDに対応するプロセッサ、あるいはノードコントローラの名称とを対応させて記録している。本実施形態において、プロセッサ及びノードコントローラへ付与されるIDは、5ビットである。IDの上位2ビット(第1ビット、第2ビット)は、ノード番号を示す。例えば、「00」でノード100を、「01」でノード200を、「10」でノード300を、それぞれ示す。その下位のビット(第3ビット)は、プロセッサであるかノードコントローラであるかを示す。例えば、「0」でプロセッサを、「1」でノードコントローラを、それぞれ示す。IDの下位2ビット(第4ビット、第5ビット)は、各プロセッサおよびノードコントローラに付与される番号を示す。ノード100を例に示すと、「00000」でプロセッサ101を、「00001」でプロセッサ102を、「00010」でプロセッサ103を、「00011」でプロセッサ104を示す。また、「00100」でノードコントローラ121を、「00101」でノードコントローラ122を示す。例えば、アドレスデコーダ403は、プロセッサ102のアドレス範囲を示すあるリクエストを入力するとID「00001」と決定する。ルーティングテーブル404は、ID「00001」に基づいて、当該リクエストの出力先信号線を「信号線153」と決定する。同様に、プロセッサ103に対応するID「00010」であれば、出力先を「信号線154」と、プロセッサ104に対応するID「00011」であれば、出力先を「信号線155」と決定する。なお、図4に示すIDは、一例でありこの例に限定はしない。

【0031】

クロスバ406は、信号線151〜155、165へ、リクエストやリプライを出力する。クロスバ406は、キャッシュ制御部402と、ルーティングテーブル404と接続される。さらに、クロスバ406は、信号線151〜155、165を介して、メモリ111、プロセッサ102〜104、ノードコントローラ121、122と接続される。クロスバ406は、ルーティングテーブル404の決定した信号線へ、リクエスト処理部401の生成したリクエストを出力する。また、クロスバ406は、信号線151〜155、165から入力するリクエストや、リクエストに対するリプライをキャッシュ制御部402へ出力する。また、クロスバ406は、キャッシュ制御部402から入力するキャッシュ405のリプライを信号線151〜155、165へ出力する。さらに、クロスバ406は、他のプロセッサから入力したリクエストがプロセッサ101へのアクセスでない場合、当該リクエストに含まれるIDをルーティングテーブル404へ出力して、ルーティングテーブル404により出力すべき信号線決定し、当該出力すべき信号線へ当該リクエストを転送する。

【0032】

以上が、本実施形態におけるプロセッサ101の構成の説明である。

【0033】

次に、図5を用いて、本実施形態におけるノードコントローラ121、122の説明を行う。なお、ノードコントローラ121とノードコントローラ122とは、同様の構成であるため、ノードコントローラ121の説明のみを行い、ノードコントローラ122の説明を省略する。また、ノード200の備えるノードコントローラ221、222、及びノード300の備えるノードコントローラ321、322も、それぞれ同様の構成であるため説明を省略する。図5は、本実施形態におけるノードコントローラ121の構成を示す図である。本実施形態におけるノードコントローラ121は、リクエスト振り分け情報レジスタ部500と、ルーティングテーブル504、506と、クロスバ505、507と、リクエスト制御部508、509とを備える。

【0034】

リクエスト振り分け情報レジスタ部500は、レジスタ501、502、503を備える。レジスタ501、502、503は、それぞれ、ルーティングテーブル504と接続される。レジスタ501、502、503は、ノードコントローラ121が受信したリクエストを、リクエスト制御部508とリクエスト制御部509のいずれに振り分けるかを決定するためのレジスタである。レジスタ501は、リクエスト制御部508へ振り分けを行うべき送信先IDを設定している。つまり、例えば、リクエストの送信先IDがレジスタ501に設定されているIDであった場合、当該リクエストは、リクエスト制御部508へ転送される。同様に、レジスタ502は、リクエスト制御部509へ振り分け行うべき送信先IDを設定している。例えば、リクエストの送信先IDがレジスタ502に設定されているIDであった場合、当該リクエストは、リクエスト制御部509へ転送される。レジスタ501、502に設定されたIDは、リクエストの出力先を決定するための情報として、ルーティングテーブル504へ出力される。また、レジスタ503は、アドレスインタリーブを行うビット位置を設定している。レジスタ503に設定されたビット位置は、アドレスインタリーブの振り分けを行うために、ルーティングテーブル504へ出力される。本実施形態において、レジスタ501、502は、5ビットのレジスタであり、レジスタ503は、6ビットのレジスタである。なお、レジスタ501、502、503のビット数は、これに限定しない。レジスタ501、502、503のビット数は、プロセッサや、ノードコントローラへ付与されるIDに応じて変化する。

【0035】

ルーティングテーブル504は、前述したプロセッサ101の備えるルーティングテーブル404と同様の構成を備える。ルーティングテーブル504は、レジスタ501、502、503と、クロスバ505と接続される。ルーティングテーブル504は、プロセッサ101〜104や、ノードコントローラ122、221、321から入力するリクエストを、リクエスト振り分け情報レジスタ部500のレジスタ501〜503に設定された情報と、ルーティングテーブル504に設定された図4に示すようなルーティング情報とに基づいて、出力先を決定する。ルーティングテーブル504は、ノードコントローラ121と接続するプロセッサ101〜104や、ノードコントローラ122、221、321から入力するリクエストに含まれる送信先IDを取り出して、リクエスト振り分け情報レジスタ部500のレジスタ501、502に設定されたIDと比較を行う。ルーティングテーブル504は、リクエストの送信先IDがレジスタ501、あるいはレジスタ502のいずれかに設定されたIDと一致する場合、一致したIDに対応するリクエスト制御部へ当該リクエストを出力する。また、ルーティングテーブル504は、リクエストの送信先IDがレジスタ501、及びレジスタ502に設定されたいずれのIDとも一致する場合、レジスタ503に設定されたアドレスインタリーブを行うビット位置のアドレスを比較して、出力するリクエスト制御部を決定する。さらに、ルーティングテーブル504は、リクエストの送信先IDがレジスタ501、及びレジスタ502に設定されたいずれのIDとも一致しない場合、当該リクエストは別ノードへのアクセスするリクエストであると判定して、送信先IDに基づいて図4に示すようなルーティング情報を参照して、ノードコントローラ121と接続されるプロセッサ101〜104や、ノードコントローラ122、221、321への信号線を決定する。

【0036】

例えば、リクエストに含まれる送信先IDが「00100」であり、レジスタ501とレジスタ502とが共に「00100」を設定している場合、ルーティングテーブル504は、レジスタ503に設定されたビット位置を参照する。ここで、例えば、レジスタ503が「000111」を設定している場合、アドレスの「ビット7」を比較して、当該リクエストを出力するリクエスト制御部を決定する。また、リクエストに含まれる送信先IDが「00100」であり、レジスタ501が「00100」を設定し、レジスタ502が「00101」を設定している場合、ルーティングテーブル504は、当該リクエストの出力先をリクエスト制御部508と決定する。一方、ルーティングテーブル504のテーブルの状態が図4で示した状態であるときに、リクエストに含まれる送信先IDが「00001」であって、レジスタ501が「00100」を設定し、レジスタ502が「00101」を設定している場合、ルーティングテーブル504は、送信先IDがレジスタ501及びレジスタ502のいずれのIDとも一致しないと判定する。ルーティングテーブル504は、ルーティング情報を参照して、当該リクエストの送信先IDに対応するプロセッサ102への信号線153を、当該リクエストの出力先と決定する。

【0037】

クロスバ505、507は、入力したリクエストを、それぞれのルーティングテーブル504、506の決定した信号線へ出力する。クロスバ505は、ルーティングテーブル504と、リクエスト制御部508、509と接続される。さらに、クロスバ505は、信号線を介して、ノード100内のプロセッサ101〜104、ノードコントローラ122、及び、ノード200の221、ノード300の321とそれぞれ接続される。また、クロスバ507は、ルーティングテーブル506と、リクエスト制御部508、509と接続される。さらに、クロスバ505は、信号線を介して、ノード100内のプロセッサ101〜104、ノードコントローラ122、及び、ノード200の221、ノード300の321とそれぞれ接続される。

【0038】

リクエスト制御部508は、ノード外メモリアクセス制御部510と、ノード内メモリアクセス制御部520とを備える。また、リクエスト制御部509は、ノード外メモリアクセス制御部530と、ノード内メモリアクセス制御部540とを備える。リクエスト制御部509は、リクエスト制御部508と同様の構成であるので重ねての説明は省略する。

【0039】

ノード外メモリアクセス制御部510は、ノード外メモリアクセスリクエスト格納バッファ511と、ノード外アクセス用アドレスレコーダ512とを備える。ノード外メモリアクセスリクエスト格納バッファ511は、クロスバ505、507と、ノード外アクセス用アドレスデコーダ512と接続される。ノード外アクセス用アドレスレコーダ512は、さらに、クロスバ507と接続される。ノード外メモリアクセスリクエスト格納バッファ511は、ノード100の内部のプロセッサ101〜104が、ノード100の外部に存在するメモリへアクセスを行うためのリクエストを格納する。ノード外アクセス用アドレスレコーダ512は、ノード外メモリアクセスリクエスト格納バッファ511から入力するリクエストに含まれたアドレスに基づいて、出力先のノードコントローラのIDを割り出す。また、ノード外アクセス用アドレスレコーダ512で割り出されたIDは、クロスバ505がリクエストを受信したときに、当該リクエストの転送先をルーティングテーブル504で参照することを可能にするために、ルーティングテーブル504へリクエストと共に送信される。

【0040】

ノード外メモリアクセス制御部510は、ノード外メモリアクセスリクエスト格納バッファへ格納したリクエストからアドレスを抜き出して、ノード外アクセス用デコーダ512へ出力する。ノード外アクセス用アドレスデコーダ512は、ノード外メモリアクセスリクエスト格納バッファ511から入力するリクエストに含まれたアドレスに基づいて、出力先のノードコントローラのIDを割り出す。ノード外メモリアクセス制御部510は、ノード外アクセス用アドレスデコーダ512の割り出したIDと、ノード外メモリアクセスリクエスト格納バッファへ格納したリクエストとを、クロスバ507へ出力する。

【0041】

ノード内メモリアクセス制御部520は、ノード内メモリアクセスリクエスト格納バッファ521と、ノード内アクセス用アドレスデコーダ522と、ディレクトリ523とを備える。ノード内メモリアクセスリクエスト格納バッファ521は、クロスバ505、507と、ノード内アクセス用アドレスデコーダ522と、ディレクトリ523と接続される。ノード内アクセス用アドレスデコーダ522と、ディレクトリ523とは、さらに、クロスバ507と接続される。ノード内メモリアクセスリスト格納バッファ521は、ノード100の外部のプロセッサからノード100の備えるメモリ111〜114へアクセスを行うためのリクエストを格納する。ノード内アクセス用アドレスデコーダ522は、ノード内メモリアクセスリクエスト格納バッファ521から入力するアドレスに基づいて、当該リクエストの出力先のプロセッサのIDを割り出す。また、ノード内アクセス用アドレスレコーダ522で割り出されたIDは、クロスバ505がリクエストを受信したときに、当該リクエストの転送先をルーティングテーブル504で参照することを可能にするために、ルーティングテーブル504へリクエストと共に送信される。ディレクトリ523は、ノード100内のメモリ111〜114のライン毎にステータス情報を管理する。ステータス情報は、メモリ111〜114に格納されたデータが他ノードのプロセッサにキャッシュされているか否かを示す情報と、キャッシュされている場合、キャッシュしているプロセッサのIDとキャッシュされているメモリ111〜114のアドレス情報とを対応させて記録している。ディレクトリ523は、ノード100外のプロセッサがキャッシュするノード100内のメモリ111〜114のキャッシュラインのアドレス情報を、全て記録している。

【0042】

ノード内メモリアクセス制御部520は、ノード内メモリアクセスリクエスト格納バッファ521に格納したリクエストからアドレスを抜き出して、ノード内アクセス用アドレスデコーダ522と、ディレクトリ523とへ出力する。ノード内アクセス用アドレスデコーダ522は、ノード内メモリアクセスリクエスト格納バッファ521から入力するアドレスに基づいて、当該リクエストの出先のプロセッサのIDを割り出す。ノード内メモリアクセス制御部520は、ノード内アクセス用アドレスデコーダ522の割り出したプロセッサのIDと、ノード内メモリアクセスリクエスト格納バッファ521に格納したリクエストとを、クロスバ507へ出力する。ディレクトリ523は、アクセス元のプロセッサのIDと、アクセス先のプロセッサのID、及びキャッシュされるメモリ111〜114のアドレス情報とを記憶する。また、ノード内メモリアクセス制御部520は、ディレクトリ523に記録されたメモリ111〜114のデータをキャッシュしているプロセッサに対して、当該キャッシュラインのアクセス権の返却を要求するスヌープを作成して、クロスバ507へ出力する。

【0043】

ルーティングテーブル506は、ノード外メモリアクセス制御部510から出力されるリクエストを出力する信号線を、ノード外アクセス用アドレスデコーダ512から出力される転送先のIDに基づいて決定する。また、ルーティングテーブル506は、ノード内メモリアクセス制御部520から出力されるリクエストを出力する信号線を、ノード内アクセス用アドレスデコーダ522から出力される転送先のIDに基づいて決定する。ルーティングテーブル506は、クロスバ507と接続される。ルーティングテーブル506は、決定した信号線をクロスバ507へ通知する。

【0044】

以上が、本実施形態におけるマルチプロセッサシステムの構成の説明である。

【0045】

[動作方法の説明]

次に、本実施形態のマルチプロセッサシステムにおける動作方法の説明を行う。まず、図6を用いて、本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作方法を説明する。図6は、本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作フローである。本説明において、ノード100のノードコントローラ122に故障が発生した場合を用いて説明する。

【0046】

(ステップS601)

ノードコントローラ122に障害が発生する。ノードコントローラ122は、システムファームウェアへ障害を通知する。ここで、システムファームウェハは、マルチプロセッサ上で動作を行うソフトウェアであり、マルチプロセッサシステムを制御している。

【0047】

(ステップS602)

システムファームウェアは、ノードコントローラ122の障害を検知すると、ノード100、200、300の各プロセッサからのリクエスト出力を抑止する。

【0048】

(ステップS603)

システムファームウェアは、ノード100外のプロセッサに、キャッシュラインのアクセス権を返却させる。システムファームウェアは、ノードコントローラ121のディレクトリ523、543と、ノードコントローラ122のディレクトリ523、543(以下、区別のために、ディレクトリ523B、ディレクトリ543Bと表記する。)とに記録された、ノード100外のプロセッサによるノード100内のメモリ111〜114のキャッシュ状況に基づいて、ノード100外のプロセッサにキャッシュしているデータをメモリ111〜114へ書き戻させて、ノード100外のプロセッサにメモリ111〜114のキャッシュラインのアクセス権を返却させる。これによって、ノード100内のメモリ111〜114のデータを最新の状態に更新することができ、コヒーレンシを保証することができる。なお、ノードコントローラ121のディレクトリ523、543と、ノードコントローラ122のディレクトリ523B、543Bとは、各ノード間のコヒーレンシを保証するために、ノード100外のプロセッサによるキャッシュ状況を記録している。そのため、ノード100内のプロセッサがメモリ111〜114のデータをキャッシュしていたとしても問題とはならない。

【0049】

(ステップS604)

ノードコントローラ121は、振り分け制御レジスタ部500のレジスタ502に設定されたIDを、ノードコントローラ122のIDへ変更する。これによって、ノードコントローラ122宛てのリクエストは、リクエスト制御部509へ転送されることになる。つまり、ノードコントローラ121宛てのリクエストは、リクエスト制御部508へ、ノードコントローラ122宛てのリクエストは、リクエスト制御部509へ出力されることになる。なお、本実施形態では、レジスタ502に設定されたIDを変更しているが、レジスタ501に設定されたIDをノードコントローラ122のIDへ変更することも可能である。この場合は、ノードコントローラ122宛てのリクエストは、リクエスト制御部508へ転送されることになる。

【0050】

(ステップS605)

ノードコントローラ121は、ノードコントローラ121のリクエスト制御部509の備えるノード内アクセスアドレスデコーダ542がデコードを行うアドレス範囲を、ノードコントローラ122が対応していたアドレス範囲まで含むように変更する。リクエスト制御部509は、ノードコントローラ122宛てのリクエストを振り分けられるため、ノード内アクセスアドレスデコーダ542をノードコントローラ122のアドレス対応範囲まで適応させるためである。これによって、リクエスト制御部509にノードコントローラ122宛てのリクエストが転送されたとしても、ノード内アクセスアドレスデコーダ542は、ノードコントローラ122対応していたアドレス範囲に基づいて送信先のIDを決定することができる。なお、ノード外アクセス用アドレスデコーダ532は、ノードコントローラ121とノードコントローラ122で同様であるので、特に対応するための処理を行う必要はない。

【0051】

(ステップS606)

システムファームウェアは、ノードコントローラ121、122以外のノードコントローラ221、222、321、322の備えるルーティングテーブルを、縮退したノードコントローラ122を経由しないルーティング経路となるように設定を変更する。例えば、ノードコントローラ222からノードコントローラ121へアクセスする場合に、ノードコントローラ222から、ノードコントローラ122を経由して、ノードコントローラ121へ、という経路設定であるならば、ノードコントローラ222から、ノードコントローラ221を経由して、ノードコントローラ121へという経路設定へ変更する。

【0052】

また、ノードコントローラ122のIDへのアクセスがノードコントローラ121へ転送されるように、ルーティングテーブルの設定を変更する。このように設定することで、ノードコントローラ122宛てのリクエストは、ノードコントローラ121へ転送されることになる。ノードコントローラ121は、ノードコントローラ122宛てのリクエストを、リクエスト制御部509において処理するように設定されている。そのため、ノードコントローラ121は、ノードコントローラ122宛てのリクエストを受信して処理を行うことになる。

【0053】

(ステップS607)

ノード100内のプロセッサ101〜104は、ノードコントローラ122へのアクセスがノードコントローラ121へのアクセスとなるように、ルーティングテーブルの設定を変更する。すなわち、ノードコントローラ122のIDに対応する信号線を、ノードコントローラ121と接続された信号線へ変更する。このようにすることで、ノードコントローラ122宛てのリクエストは、ノードコントローラ121接続された信号線へ出力されて、ノードコントローラ121のリクエスト制御部509で処理されることになる。

【0054】

(ステップS608)

システムファームウェアは、ノード100、200、300に対するリクエストの出力抑止を解除する。その後、マルチプロセッサシステムが再開する。

【0055】

以上が、本実施形態のマルチプロセッサシステムにおけるノードコントローラ故障時の動作方法の説明である。このように、本実施形態のマルチプロセッサシステムでは、冗長化されたノードコントローラ122の障害時において、ノードコントローラ121は、内部のレジスタ502にノードコントローラ122のIDを設定することで、ノードコントローラ122宛てのリクエスト等を処理することが可能となる。そのため、ノード100内のプロセッサ101〜104や、他のノード200、300のノードコントローラ221、222、321、322の備えるルーティングテーブルの設定を、ノードコントローラ122宛てのリクエストがノードコントローラ121宛てに送信されるように変更するのみで、システムを再開することができる。そのため、リクエストの送信先ID自体を書き換えるために、各ノードのアドレスデコーダを書き換える場合に比べて、短時間でシステムを再開することができる。

【0056】

次に、図7A、及び図7Bを用いて、本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作方法を説明する。図7A、及び図7Bは、本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作フローである。以下の説明では、ノード100のプロセッサ101から、ノード200のメモリ214へのリードリクエストが発行された場合を説明する。つまり、ノード100内のプロセッサ101が、ノード100外のメモリ214へアクセスする場合を説明する。

【0057】

(ステップS701)

キャッシュ制御部402は、ノード200のメモリ214へのリードリクエスト(以下、本説明においてリクエストと呼ぶ。)を生成する。プロセッサ101は、プロセッサ101上で動作するプロセスから要求を入力する。プロセッサ101のリクエスト処理部401は、ノード200のメモリ214に記録されたデータをキャッシュするための命令を生成する。キャッシュ制御部402は、リクエスト処理部401の生成した命令に基づいて、ノード200のメモリ214に記録されたデータをキャッシュするためのリードリクエストを生成する。

【0058】

(ステップS702)

プロセッサ101は、リクエストの送信先IDを決定する。プロセッサ101は、アドレスデコーダ403を参照して、キャッシュ制御部402の生成したリードリクエストに含まれるアクセス先のアドレスに基づいて、当該リードリクエストを送信する送信先IDを決定する。なお、本説明では、アクセス先のアドレスがノード200内のメモリ241上であるため、プロセッサ101は、送信先IDをノードコントローラ121のIDに決定する。

【0059】

(ステップS703)

プロセッサ101は、リクエストを出力する信号線を決定する。プロセッサ101は、ルーティングテーブル404を参照して、アドレスデコーダ403の決定した送信先IDに基づいて、出力する信号線を決定する。クロスバ406は、ルーティングテーブル404の決定した信号線へ、リクエストを出力する。本説明では、送信先IDがノードコントローラ121のIDであるため、プロセッサ101は、出力する信号線を信号線151と決定する。

【0060】

(ステップS704)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。ノードコントローラ121は、プロセッサ101からリクエストを、クロスバ505に受信する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報と、リクエスト振り分け情報レジスタ部500のレジスタ501〜503に設定された情報とを参照して、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。

【0061】

ルーティングテーブル504は、リクエスト振り分け情報レジスタ部500からレジスタ501、502に設定されたIDを取得できる。ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ501と一致する場合、リクエスト制御部508へ当該リクエストを出力する。一方、ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ502と一致する場合、リクエスト制御部509へ当該リクエストを出力する。また、ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ501、502のいずれとも一致する場合、レジスタ503に設定された値に基づいてアドレスインタリーブを行って、当該リクエストをリクエスト制御部508、509のいずれに出力するかを決定する。さらに、ノードコントローラ121は、リクエストに含まれた送信先IDがレジスタ501、502のいずれとも一致しない場合、当該リクエストは、他のノードコントローラ、あるいはプロセッサ宛であると判定して、ルーティングテーブル504に設定されたルーティング情報を参照して出力先を決定する。クロスバ505は、ルーティングテーブル504によって決定された出力先へ、リクエストを出力する。なお、本説明において、ノードコントローラ121は、当該リクエストの出力先として、リクエスト制御部508のノード外メモリアクセス制御部510と決定する。

【0062】

(ステップS705)

ノードコントローラ121は、リクエストの送信先IDを決定する。リクエスト制御部508のノード外メモリアクセス制御部510は、クロスバ504からリクエストを入力する。ノード外メモリアクセス制御部510は、当該リクエストを、ノード外メモリアクセスリクエスト格納バッファ511へ格納する。ノード外メモリアクセス制御部510は、リクエストをクロスバ507へ出力する。また、同時に、ノード外メモリアクセス制御部510は、ノード外アクセス用アドレスデコーダ512を参照して、リクエストに含まれるアクセス先のアドレスに基づいて、リクエストの転送先をノードコントローラ222と決定して、ノードコントローラ222の送信先IDをクロスバ507へ出力する。なお、本説明では、ノードコントローラ222は、アクセス先のアドレスがノード200のメモリ214であるため、ノード200のノードコントローラ221のIDを送信先IDと決定する。

【0063】

(ステップS706)

ノードコントローラ121は、送信先IDに基づいて、リクエストを出力する信号線を決定する。クロスバ507は、ノード外アクセス用アドレスデコーダ512から送信先IDを入力する。また、クロスバ507は、ノード外メモリアクセスリクエスト格納バッファ511からリクエストを入力する。ノードコントローラ121は、ルーティングテーブル506に設定されたルーティング情報を参照して、送信先IDに基づいて、リクエストを出力する信号線を決定する。クロスバ507は、決定した信号線22へリクエストを出力する。なお、本説明において、送信先IDがノードコントローラ221のIDであるため、ルーティングテーブル506は、リクエストの出力先を出力線22と決定する。クロスバ507は、リクエスト22を出力線22へ出力する。

【0064】

(ステップS707)

ノード200において処理が行われて、メモリ214からリプライデータを受信する。ノード200のノードコントローラ221は、ノード100のノードコントローラ121からリクエストを受信する。この後の動作は、別ノードでの動作のため説明を省略する。すなわち、この後、リクエストは、ノード200内のノードコントローラ222へ転送される。ノードコントローラ222は、メモリ214のデータのキャッシュ状況の確認をおこなう。リクエストはプロセッサ204へ送信されて、プロセッサ204からメモリ214へアクセスが行われる。メモリ214のアクセス先のアドレスのデータが、リプライデータとして送信時の経路を経由して、ノードコントローラ121へ送信される。

【0065】

(ステップS708)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリプライデータを出力するかを決定する。ノードコントローラ121は、メモリ214からのリプライデータをクロスバ505に入力する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報と、リクエスト振り分け情報レジスタ部500の各レジスタに設定された情報とを参照して、リクエスト制御部508、509のいずれにリプライデータを出力するかを決定する。この処理は、ステップS704で説明を行った処理と同様であるので、重ねての説明を省略する。なお、本説明において、ノードコントローラ121は、リプライデータの出力先をリクエスト制御部508のノード外メモリアクセス制御部510と決定する。クロスバ505は、ルーティングテーブル504により決定した出力先へリプライデータを出力する。

【0066】

(ステップS709)

ノード外メモリアクセス制御部510は、格納していたリクエストからリクエスト元のIDを取得する。ノード外メモリアクセス制御部510は、クロスバ505からリプライデータを入力すると、ノード外メモリアクセスリクエスト格納バッファ511へ格納していたリクエストに基づいて、当該リプライデータのリクエスト元のプロセッサ101のIDを決定する。ノード外メモリアクセス制御部510は、クロスバ507へ、プロセッサ11のIDと共にリプライデータを出力する。

【0067】

(ステップS710)

ノードコントローラ121は、リプライデータを出力する信号線を決定する。クロスバ507は、ノード外メモリアクセス制御部510からリプライデータを入力する。ノードコントローラ121は、ルーティングテーブル506に設定されたルーティング情報を参照して、リクエスト元のIDに基づいてリプライデータを出力する信号線を決定する。クロスバ505は、ルーティングテーブル506により決定された信号線へリプライデータを出力する。なお、本説明において、ノードコントローラ121は、リプライデータの信号線を、リクエスト元のプロセッサ101のIDに対応する信号線151と決定する。クロスバ505は、リプライデータを信号線151へ出力する

【0068】

(ステップS711)

プロセッサ101は、リプライデータをキャッシュ405へ保存すると共に、リクエスト処理部401へリプライデータを出力する。プロセッサ101のクロスバ406は、信号線151からリプライデータを受信する。クロスバ406は、リプライデータをキャッシュ制御部402へ出力する。キャッシュ制御部402は、リプライデータをキャッシュ405へ保存すると共に、リプライデータをリクエスト処理部401へ出力する。これにより、リードリクエスト処理は完了する。

【0069】

以上が、本実施形態のマルチプロセッサシステムにおけるノード内からリクエストを受信した場合のノードコントローラの動作方法の説明である。

【0070】

次に、図8A〜図8Cを用いて、本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作方法を説明する。図8A〜図8Cは、本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作フローである。以下の説明では、ノード200のプロセッサ204から、ノード100のメモリ105へのリードリクエストが発行された場合を説明する。つまり、ノード100外のプロセッサ204が、ノード100内のメモリ105へアクセスする場合を説明する。

【0071】

(ステップS801)

ノードコントローラ121は、ノード200のプロセッサ204からリクエストを受信する。ノード200のプロセッサ204は、ノード100のメモリ111へのリードリクエスト(以下、本説明でリクエストと呼ぶ。)を発行する。この動作は、ステップS701からステップS703においてプロセッサ101が行った処理と同様であるので説明を省略する。プロセッサ204の出力したリクエストは、ノードコントローラ221を介して、ノード100へ転送される。ノードコントローラ121は、ノードコントローラ221からプロセッサ204の発行したリクエストを、クロスバ505に受信する。

【0072】

(ステップS802)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報とリクエスト振り分け情報レジスタ部500のレジスタ501〜503に設定された情報とに基づいて、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。なお、本ステップにおける動作は、ステップS704と同様であるので重ねての説明を省略する。本説明において、ノードコントローラ121は、リクエストの出力先として、リクエスト制御部508のノード内メモリアクセス制御部520と決定する。クロスバ505は、リクエストをリクエスト制御部のノード内メモリアクセス制御部520へ出力する。

【0073】

(ステップS803)

ノード内メモリアクセス制御部520は、メモリ111のデータキャッシュ状況を確認する。ノード内メモリアクセス制御部520は、クロスバ505からリクエストを入力すると、リクエストをノード内メモリアクセスリクエスト格納バッファ521へ格納する。ノード内メモリアクセス制御部520は、ディレクトリ523を参照して、リクエストに含まれるアクセス先アドレスのデータキャッシュ状況を確認する。なお、本説明において、ノード内メモリアクセス制御部520は、ディレクトリ523を参照して、メモリ111のデータキャッシュ状況を確認する。

【0074】

(ステップS804)

ノード内メモリアクセス制御部520は、リクエストに含まれるメモリ111のアクセス先アドレスのデータが、他のプロセッサにキャッシュされているか否かを判定する。他のプロセッサにキャッシュされていない場合、ステップS805へ進む。一方、他のプロセッサにキャッシュされている場合、ステップS807へ進む。

【0075】

(ステップS805)

ノード内メモリアクセス制御部520は、リクエストの送信先IDを決定する。ノード内メモリアクセス制御部520は、リクエストに含まれるメモリ111のアクセス先アドレスのデータが他のプロセッサにキャッシュされていない場合、リクエストをクロスバ507へ出力する。同時に、ノード内メモリアクセス制御部520は、ノード内アクセス用アドレスデコーダ522を参照して、リクエストに含まれるアクセス先のアドレスに基づいて、送信先IDを決定する。ノード内メモリアクセス制御部520は、送信先IDをクロスバ507へ出力する。なお、本説明において、当該リクエストはメモリ111へのリードアクセスであるため、ノード内メモリアクセス制御部520は、送信先IDをプロセッサ101のIDと決定する。

【0076】

(ステップS806)

ノードコントローラ121は、リクエストを出力する信号線を決定する。クロスバ507は、ノード内メモリアクセス制御部520からリクエストと送信式IDを入力する。ノードコントローラ121は、ルーティングテーブル506を参照して、リクエストを出力する信号線を決定する。クロスバ507は、ルーティングテーブル506により決定された出力先の信号線へリクエストを出力する。なお、本説明において、ノードコントローラ121は、プロセッサ101と接続された信号線151を、リクエストを出力する信号線と決定する。クロスバ507は、信号線151へリクエストを出力する。

【0077】

(ステップS807)

ノード内メモリアクセス制御部520は、メモリ111のアクセス権の返却を要求するスヌープを生成する。ノード内メモリアクセス制御部520は、リクエストに含まれるメモリ111のアクセス先アドレスのデータが他のプロセッサにキャッシュされている場合、メモリ111のアクセス権の返却を要求するスヌープを生成する。

【0078】

(ステップS808)

ノード内メモリアクセス制御部520は、スヌープを行うプロセッサの送信先IDを決定する。ノード内メモリアクセス制御部520は、ディレクトリ523を参照して、アクセス先アドレスのデータをキャッシュしているプロセッサのIDを決定する。ノード内メモリアクセス制御部520は、スヌープと送信先IDとをクロスバ507へ出力する。

【0079】

(ステップS809)

ノードコントローラ121は、スヌープを出力する信号線を決定する。クロスバ507は、ノード内メモリアクセス制御部520からスヌープと送信先IDとを入力する。ノードコントローラ121は、ルーティングテーブル506を参照して、送信先IDに基づいて、スヌープを出力する信号線を決定する。クロスバ507は、ルーティングテーブル506により決定された信号線へ、スヌープを出力する。

【0080】

(ステップS810)

ノード内メモリアクセス制御部520は、スヌープの結果に基づいて、所定の処理を行う。ノード内メモリアクセス制御部520は、スヌープのリプライを受信すると、必要に応じて、所定の処理を行う。ここで、所定の処理とは、メモリ111に対するライトリクエストの生成や、データの送受信や、ディレクトリ523の更新等である。このように、ノード内メモリアクセス制御部520は、スヌープのリプライに応じて、様々な処理を行うことになるが、これらは従来技術によるため、詳細な説明を省略する。なお、ノードコントローラ121は、この後、ステップS805、及びステップS806と同様の処理を実行する。すなわち、ノード内メモリアクセス制御部520は、リクエストの送信先IDを決定する(ステップS805)。ノードコントローラ121は、リクエストを出力する信号線を決定して、クロスバ507は、信号線151へリクエストを出力する(ステップS806)。その後、ステップS811へ進む。

【0081】

(ステップS811)

ノードコントローラ121は、メモリ111からリプライデータを受信する。プロセッサ101は、クロスバ507から出力されたリクエストを受信する。プロセッサ101は、メモリ111へリクエストを転送する。プロセッサ101は、メモリ111からアクセス先アドレスのデータを取得して、当該データを含めたリプライデータをノードコントローラ121へ出力する。

【0082】

(ステップS812)

ノードコントローラ121は、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。ノードコントローラ121は、プロセッサ101から、リプライデータをクロスバ505へ入力する。ノードコントローラ121は、ルーティングテーブル504に設定されたルーティング情報と、リクエスト振り分け情報レジスタ部500の各レジスタの情報とを参照して、リクエスト制御部508、509のいずれにリクエストを出力するかを決定する。クロスバ505は、ルーティングテーブル504により決定した出力先へリプライデータを出力する。なお、本ステップにおける動作は、ステップS704と同様であるので重ねての説明を省略する。なお、本説明において、ノードコントローラ121は、リプライデータの出力先を、リクエスト制御部508のノード内メモリアクセス制御部520と決定する。クロスバ505は、ノード内メモリアクセス制御部520へリプライデータを出力する。

【0083】

(ステップS813)

ノード内メモリアクセス制御部520は、格納していたリクエストからリクエスト元のIDを取得する。ノード内メモリアクセス制御部510は、クロスバ505からリプライデータを入力すると、ノード内メモリアクセスリクエスト格納バッファ521へ格納していたリクエストに基づいて、リクエスト元のプロセッサのIDに基づいて、当該リプライデータの送信先IDを決定する。ノード外メモリアクセス制御部510は、クロスバ507へ、送信先IDと共にリプライデータを出力する。なお、本説明において、ノード内メモリアクセス制御部510は、リクエスト元のプロセッサIDに基づいて、当該リプライデータの送信先IDを、ノードコントローラ221と決定する。

【0084】

(ステップS814)

ノードコントローラ121は、リプライデータを出力する信号線を決定する。クロスバ507は、ノード内メモリアクセス制御部520からリプライデータと送信先IDを入力する。ノードコントローラ121は、ルーティングテーブル506を参照して、送信先IDに基づいて、リプライデータを出力する信号線を決定する。本説明において、ノードコントローラ121は、リプライデータの信号線を、ノードコントローラ221のIDに対応する信号線22と決定する。クロスバ505は、リプライデータを信号線22へ出力する

【0085】

(ステップS815)

ノード内メモリアクセス制御部520は、リクエスト元のプロセッサ204の情報をディレクトリ523へ記録する。ノード内メモリアクセス制御部520は、キャッシュラインのアクセス権を渡したプロセッサ204の情報をディレクトリへ記録する。これにより、プロセッサ204からのリクエストに対するノードコントローラ121の処理は完了する。なお、プロセッサ204は、ノードコントローラ221を介してリプライデータを受信して、プロセッサ204のキャッシュにデータを記録すると共に、リクエスト処理部へデータを出力して、リードリクエストを完了する。

【0086】

以上が、本実施形態のマルチプロセッサシステムにおけるノード外からリクエストを受信した場合のノードコントローラの動作方法の説明である。

【0087】

ここまで、本実施形態の説明を行ってきた、本発明によれば、各ノードのノードコントローラは、データの処理を行う2つのリクエスト制御部に対応して、いずれのリクエスト制御部にデータを転送するかを決定するためのIDを格納する2つのレジスタを備えている。片系のノードコントローラの故障時には、正常なノードコントローラの1つのレジスタへ、故障により縮退したノードコントローラのIDを設定する。また、当該ノード外の各ノードコントローラとノード内の各プロセッサのルーティングテーブルとに設定されたデータを、故障したノードコントローラ宛のリクエストを正常なノードコントローラ宛へ転送するように変更を行う。これによって、正常なノードコントローラは、故障したノードコントローラ宛のリクエストを受信して、1つのリクエスト制御部で処理を行うことが可能となる。このように、実際には故障しているノードコントローラ宛のリクエストを正常なノードコントローラで処理を行うことができるため、他ノードの各ノードコントローラや、各プロセッサにおいて、アドレスデコーダの設定変更を行う必要がない。そのため、故障発生時にマルチプロセッサシステムの停止時間を短時間にすることができる。

【0088】

なお、ノード100内(他のノード内も含む。)における各ノードコントローラと各プロセッサの接続は、図1で説明を行った接続構成に限定しない。図9、及び図10は、本実施形態におけるノード100内の接続構成の変形例を示す図である。例えば、図9に示すように、信号線601〜609による接続のように各プロセッサ同士を1対1に接続しない接続構成でも良いし、図10に示すようなバス700による接続のようなバス型の接続構成でもよい。

【0089】

また、ノードコントローラ121(他のノードコントローラを含む。)は、4つのアドレスデコーダ(512、522、532、542)を備えている。これは、ノード外アクセス用アドレスデコーダ512、532が、ノードコントローラ221、222、321、322までを対象としたアドレスデコーダであり、ノード内アクセス用アドレスデコーダ522、542が、ノード100内のプロセッサ101〜104を対象としたアドレスデコーダであるためである。しかし、ノード外アクセス用アドレスデコーダ512、532が、ノード100外のノード200、300の備えるプロセッサ201〜204、301〜304までを対象とするアドレスデコーダであるなら、ノード内へアクセスするときには、ノードコントローラ121から出力する出力先のプロセッサのIDが判明しているので、ノード内アクセス用アドレスデコーダ522、542を備えない構成とすることも可能である。

【0090】

以上、実施形態を参照して本発明を説明したが、本発明は上記実施形態に限定されるものではない。本発明の構成や詳細には、本発明の範囲内で当業者が理解し得る様々な変更を行うことが可能である。

【符号の説明】

【0091】

10〜12 信号線

20〜22 信号線

100 ノード

101〜104 プロセッサ

111〜114 メモリ

121、122 ノードコントローラ

151〜169 信号線

200 ノード

201〜204 プロセッサ

211〜214 メモリ

221、222 ノードコントローラ

269 信号線

300 ノード

301〜304 プロセッサ

311〜314 メモリ

321、322 ノードコントローラ

369 信号線

401 リクエスト処理部

402 キャッシュ制御部

403 アドレスデコーダ

404 ルーティングテーブル

405 キャッシュ

406 クロスバ

500 リクエスト振り分け情報レジスタ部

501 レジスタ

502 レジスタ

503 レジスタ

504 ルーティングテーブル

505 クロスバ

506 ルーティングテーブル

507 クロスバ

508 リクエスト制御部

509 リクエスト制御部

510 ノード外メモリアクセス制御部

511 ノード外メモリアクセスリクエスト格納バッファ

512 ノード外アクセス用アドレスデコーダ

520 ノード内メモリアクセス制御部

521 ノード内メモリアクセスリクエスト格納バッファ

522 ノード内アクセス用アドレスデコーダ

523 ディレクトリ

530 ノード外メモリアクセス制御部

531 ノード外メモリアクセスリクエスト格納バッファ

532 ノード外アクセス用アドレスデコーダ

540 ノード内メモリアクセス制御部

541 ノード内メモリアクセスリクエスト格納バッファ

542 ノード内アクセス用アドレスデコーダ

543 ディレクトリ

601〜609 信号線

700 バス

【特許請求の範囲】

【請求項1】

複数のノードを備え、

前記複数のノードの各々は、複数のプロセッサと、前記複数のプロセッサに対応して接続された複数のメモリと、前記複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備し、

前記各ノードの複数のプロセッサと、前記第一ノードコントローラと、前記第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、

前記第一ノードコントローラと第二ノードコントローラは、

リクエストに含まれるアクセス先のメモリアドレスに基づいて、前記リクエストの送信先の識別子を決定する第一リクエスト制御部、及び第二リクエスト制御部と、

前記第一リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を記憶する第一レジスタと、

前記第二リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を記憶する第二レジスタと、

前記リクエストを受信すると、前記リクエストの送信先の識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子に基づいて、前記第一リクエスト制御部か前記第二リクエスト制御部のいずれかに前記リクエストの出力先を決定する第一ルーティングテーブルと、

前記第一リクエスト制御部、あるいは前記第二リクエスト制御部の決定した前記送信先の識別子に基づいて、前記送信先の識別子に対応する信号線を選択して、前記リクエストを送信する第二ルーティングテーブルと

を備えるマルチプロセッサシステム。

【請求項2】

請求項1に記載のマルチプロセッサシステムであって、

前記第一ルーティングテーブルは、前記リクエストに含まれる当該リクエストの送信先を示す識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子とが一致するかを判定して、前記リクエストの送信先を示す識別子と前記第一レジスタに設定された識別子とが一致する場合、前記第一レジスタに対応する前記第一リクエスト制御部を、前記リクエストの出力先と決定し、前記リクエストの送信先を示す識別子と前記第二レジスタに設定された識別子とが一致する場合、前記第二レジスタに対応する前記第二リクエスト制御部を、前記リクエストの出力先と決定する

マルチプロセッサシステム。

【請求項3】

請求項2に記載のマルチプロセッサシステムであって、

前記各ノードの前記第一ノードコントローラは、前記第二ノードコントローラに障害が発生すると、前記第二レジスタへ、前記第二ノードコントローラの識別子を設定する

マルチプロセッサシステム。

【請求項4】

請求項3に記載のマルチプロセッサシステムであって、

前記各ノードの備える前記複数のプロセッサの各々は、前記リクエストの送信先の識別子を決定するプロセッサルーティングテーブルを備え、

前記複数のノードのうち前記障害の発生した障害ノードの前記各プロセッサは、前記障害ノードの前記第二コントローラ宛の前記リクエストを前記障害ノードの前記第一コントローラ宛へ出力するように前記プロセッサルーティングテーブルの設定を変更し、

前記複数のノードのうち前記障害ノード以外のノードの備える前記第一ノードコントローラ、及び前記第二ノードコントローラは、前記障害ノードの前記第二コントローラ宛の前記リクエストを、前記障害ノードの前記第一ノードコントローラ宛へ出力するように前記第二ルーティングテーブルの設定を変更する

マルチプロセッサシステム。

【請求項5】

請求項4に記載のマルチプロセッサシステムであって、

第一リクエスト制御部と第二リクエスト制御部とは、それぞれ、前記リクエストに含まれるアクセス先のメモリアドレスに基づいて前記リクエストの送信先の識別子を決定するアドレスデコーダを備え、

前記障害ノードの前記第一リクエスト制御部は、前記第一リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を、前記第二リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を含むように設定を変更する

マルチプロセッサシステム。

【請求項6】

請求項2から請求項5までのいずれかに記載のマルチプロセッサシステムであって、

前記リクエストの送信先の識別子において参照するべきビットのビット位置を記録した第三レジスタをさらに備え、

前記ルーティングテーブルは、前記リクエストの含む送信先の識別子が、前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致する場合、前記第三レジスタに設定された前記ビット位置基づいて前記リクエストの出力先を前記第一リクエスト制御部か前記第二リクエスト制御部かのいずれかに決定する

マルチプロセッサシステム。

【請求項7】

請求項6に記載のマルチプロセッサシステムであって、

前記ルーティングテーブルは、前記リクエストの含む送信先の識別子が、前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致しない場合、前記ルーティングテーブルに記録されたデータを参照して転送先を決定する

マルチプロセッサシステム。

【請求項8】

請求項1〜請求項7までのいずれかに記載のマルチプロセッサシステムで使用されるノードコントローラ。

【請求項9】

複数のノードを備え、

前記複数のノードの各々は、複数のプロセッサと、前記複数のプロセッサに対応して接続された複数のメモリと、前記複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備するマルチプロセッサシステムにおいて、

前記各ノードの複数のプロセッサと、前記第一ノードコントローラと、前記第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、

前記第一ノードコントローラと第二ノードコントローラは、

リクエストに含まれるアクセス先のメモリアドレスに基づいて、前記リクエストの送信先の識別子を決定するステップと、

前記第一リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を第一レジスタへ記憶するステップと、

前記第二リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を第二レジスタへ記憶するステップと、

前記リクエストを入力すると、前記リクエストの送信先の識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子に基づいて、前記第一リクエスト制御部か前記第二リクエスト制御部のいずれかに前記リクエストの出力先を決定するステップと、

前記第一リクエスト制御部、あるいは前記第二リクエスト制御部の決定した前記送信先の識別子に基づいて、前記送信先の識別子に対応する信号線を選択して、前記リクエストを送信するステップと

を備えるマルチプロセッサシステムの障害回復方式。

【請求項10】

請求項9に記載のマルチプロセッサシステムの障害回復方式であって、前記リクエストの出力先を決定するステップは、

前記リクエストに含まれる当該リクエストの送信先を示す識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子とが一致するかを判定するステップと、

前記リクエストの送信先を示す識別子と前記第一レジスタに設定された識別子とが一致する場合、前記第一レジスタに対応する前記第一リクエスト制御部を、前記リクエストの出力先と決定するステップと、

前記リクエストの送信先を示す識別子と前記第二レジスタに設定された識別子とが一致する場合、前記第二レジスタに対応する前記第二リクエスト制御部を、前記リクエストの出力先と決定するステップと

を含むマルチプロセッサシステムの障害回復方式。

【請求項11】

請求項10に記載のマルチプロセッサシステムの障害回復方式であって、

前記第二ノードコントローラに障害が発生すると、前記第一ノードコントローラの前記第二レジスタへ、前記第二ノードコントローラの識別子を設定するステップ

をさらに備えるマルチプロセッサシステムの障害回復方式。

【請求項12】

請求項11に記載のマルチプロセッサシステムの障害回復方式であって、

前記各ノードの備える前記複数のプロセッサの各々は、前記リクエストの送信先の識別子を決定するプロセッサルーティングテーブルを備え、

前記複数のノードのうち前記障害の発生した障害ノードの前記第二コントローラ宛ての前記リクエストを前記障害ノードの前記第一コントローラ宛へ出力するように前記プロセッサルーティングテーブルの設定を変更するステップと、

前記障害ノードの前記第二コントローラ宛の前記リクエストを、前記障害ノードの前記第一ノードコントローラ宛へ出力するように前記第二ルーティングテーブルの設定を変更するステップと

をさらに備えるマルチプロセッサシステムの障害回復方式。

【請求項13】

請求項12に記載のマルチプロセッサシステムの障害回復方式であって、

第一リクエスト制御部と第二リクエスト制御部とは、それぞれ、前記リクエストに含まれるアクセス先のメモリアドレスに基づいて前記リクエストの送信先の識別子を決定するアドレスデコーダを備え、

前記第一リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を、前記第二リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を含むように設定を変更するステップ

をさらに備えるマルチプロセッサシステムの障害回復方式。

【請求項14】

請求項10から請求項13までのいずれかに記載のマルチプロセッサシステムの障害回復方式であって、

前記リクエストの送信先の識別子において参照するべきビットのビット位置を記録した第三レジスタをさらに備え、

前記リクエストの出力先を決定するステップは、

前記リクエストの含む送信先の識別子が、前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致する場合、前記第三レジスタに設定された前記ビット位置基づいて前記リクエストの出力先を前記第一リクエスト制御部か前記第二リクエスト制御部かのいずれかに決定するステップ

を含むマルチプロセッサシステムの障害回復方式。

【請求項15】

請求項14に記載のマルチプロセッサシステムの障害回復方式であって、前記リクエストの出力先を決定するステップは、

前記リクエストの含む送信先の識別子が前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致しない場合、前記ルーティングテーブルに記録されたデータを参照して転送先を決定するステップ

を含むマルチプロセッサシステム障害回復方式。

【請求項1】

複数のノードを備え、

前記複数のノードの各々は、複数のプロセッサと、前記複数のプロセッサに対応して接続された複数のメモリと、前記複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備し、

前記各ノードの複数のプロセッサと、前記第一ノードコントローラと、前記第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、

前記第一ノードコントローラと第二ノードコントローラは、

リクエストに含まれるアクセス先のメモリアドレスに基づいて、前記リクエストの送信先の識別子を決定する第一リクエスト制御部、及び第二リクエスト制御部と、

前記第一リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を記憶する第一レジスタと、

前記第二リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を記憶する第二レジスタと、

前記リクエストを受信すると、前記リクエストの送信先の識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子に基づいて、前記第一リクエスト制御部か前記第二リクエスト制御部のいずれかに前記リクエストの出力先を決定する第一ルーティングテーブルと、

前記第一リクエスト制御部、あるいは前記第二リクエスト制御部の決定した前記送信先の識別子に基づいて、前記送信先の識別子に対応する信号線を選択して、前記リクエストを送信する第二ルーティングテーブルと

を備えるマルチプロセッサシステム。

【請求項2】

請求項1に記載のマルチプロセッサシステムであって、

前記第一ルーティングテーブルは、前記リクエストに含まれる当該リクエストの送信先を示す識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子とが一致するかを判定して、前記リクエストの送信先を示す識別子と前記第一レジスタに設定された識別子とが一致する場合、前記第一レジスタに対応する前記第一リクエスト制御部を、前記リクエストの出力先と決定し、前記リクエストの送信先を示す識別子と前記第二レジスタに設定された識別子とが一致する場合、前記第二レジスタに対応する前記第二リクエスト制御部を、前記リクエストの出力先と決定する

マルチプロセッサシステム。

【請求項3】

請求項2に記載のマルチプロセッサシステムであって、

前記各ノードの前記第一ノードコントローラは、前記第二ノードコントローラに障害が発生すると、前記第二レジスタへ、前記第二ノードコントローラの識別子を設定する

マルチプロセッサシステム。

【請求項4】

請求項3に記載のマルチプロセッサシステムであって、

前記各ノードの備える前記複数のプロセッサの各々は、前記リクエストの送信先の識別子を決定するプロセッサルーティングテーブルを備え、

前記複数のノードのうち前記障害の発生した障害ノードの前記各プロセッサは、前記障害ノードの前記第二コントローラ宛の前記リクエストを前記障害ノードの前記第一コントローラ宛へ出力するように前記プロセッサルーティングテーブルの設定を変更し、

前記複数のノードのうち前記障害ノード以外のノードの備える前記第一ノードコントローラ、及び前記第二ノードコントローラは、前記障害ノードの前記第二コントローラ宛の前記リクエストを、前記障害ノードの前記第一ノードコントローラ宛へ出力するように前記第二ルーティングテーブルの設定を変更する

マルチプロセッサシステム。

【請求項5】

請求項4に記載のマルチプロセッサシステムであって、

第一リクエスト制御部と第二リクエスト制御部とは、それぞれ、前記リクエストに含まれるアクセス先のメモリアドレスに基づいて前記リクエストの送信先の識別子を決定するアドレスデコーダを備え、

前記障害ノードの前記第一リクエスト制御部は、前記第一リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を、前記第二リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を含むように設定を変更する

マルチプロセッサシステム。

【請求項6】

請求項2から請求項5までのいずれかに記載のマルチプロセッサシステムであって、

前記リクエストの送信先の識別子において参照するべきビットのビット位置を記録した第三レジスタをさらに備え、

前記ルーティングテーブルは、前記リクエストの含む送信先の識別子が、前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致する場合、前記第三レジスタに設定された前記ビット位置基づいて前記リクエストの出力先を前記第一リクエスト制御部か前記第二リクエスト制御部かのいずれかに決定する

マルチプロセッサシステム。

【請求項7】

請求項6に記載のマルチプロセッサシステムであって、

前記ルーティングテーブルは、前記リクエストの含む送信先の識別子が、前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致しない場合、前記ルーティングテーブルに記録されたデータを参照して転送先を決定する

マルチプロセッサシステム。

【請求項8】

請求項1〜請求項7までのいずれかに記載のマルチプロセッサシステムで使用されるノードコントローラ。

【請求項9】

複数のノードを備え、

前記複数のノードの各々は、複数のプロセッサと、前記複数のプロセッサに対応して接続された複数のメモリと、前記複数のプロセッサと接続され互いに冗長関係にある第一ノードコントローラと第二ノードコントローラとを具備するマルチプロセッサシステムにおいて、

前記各ノードの複数のプロセッサと、前記第一ノードコントローラと、前記第二ノードコントローラとは、それぞれ一意に定められた識別子を付与されており、

前記第一ノードコントローラと第二ノードコントローラは、

リクエストに含まれるアクセス先のメモリアドレスに基づいて、前記リクエストの送信先の識別子を決定するステップと、

前記第一リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を第一レジスタへ記憶するステップと、

前記第二リクエスト制御部へ前記リクエストを出力すべき前記リクエストの送信先の識別子を第二レジスタへ記憶するステップと、

前記リクエストを入力すると、前記リクエストの送信先の識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子に基づいて、前記第一リクエスト制御部か前記第二リクエスト制御部のいずれかに前記リクエストの出力先を決定するステップと、

前記第一リクエスト制御部、あるいは前記第二リクエスト制御部の決定した前記送信先の識別子に基づいて、前記送信先の識別子に対応する信号線を選択して、前記リクエストを送信するステップと

を備えるマルチプロセッサシステムの障害回復方式。

【請求項10】

請求項9に記載のマルチプロセッサシステムの障害回復方式であって、前記リクエストの出力先を決定するステップは、

前記リクエストに含まれる当該リクエストの送信先を示す識別子と、前記第一レジスタ、及び前記第二レジスタに設定された識別子とが一致するかを判定するステップと、

前記リクエストの送信先を示す識別子と前記第一レジスタに設定された識別子とが一致する場合、前記第一レジスタに対応する前記第一リクエスト制御部を、前記リクエストの出力先と決定するステップと、

前記リクエストの送信先を示す識別子と前記第二レジスタに設定された識別子とが一致する場合、前記第二レジスタに対応する前記第二リクエスト制御部を、前記リクエストの出力先と決定するステップと

を含むマルチプロセッサシステムの障害回復方式。

【請求項11】

請求項10に記載のマルチプロセッサシステムの障害回復方式であって、

前記第二ノードコントローラに障害が発生すると、前記第一ノードコントローラの前記第二レジスタへ、前記第二ノードコントローラの識別子を設定するステップ

をさらに備えるマルチプロセッサシステムの障害回復方式。

【請求項12】

請求項11に記載のマルチプロセッサシステムの障害回復方式であって、

前記各ノードの備える前記複数のプロセッサの各々は、前記リクエストの送信先の識別子を決定するプロセッサルーティングテーブルを備え、

前記複数のノードのうち前記障害の発生した障害ノードの前記第二コントローラ宛ての前記リクエストを前記障害ノードの前記第一コントローラ宛へ出力するように前記プロセッサルーティングテーブルの設定を変更するステップと、

前記障害ノードの前記第二コントローラ宛の前記リクエストを、前記障害ノードの前記第一ノードコントローラ宛へ出力するように前記第二ルーティングテーブルの設定を変更するステップと

をさらに備えるマルチプロセッサシステムの障害回復方式。

【請求項13】

請求項12に記載のマルチプロセッサシステムの障害回復方式であって、

第一リクエスト制御部と第二リクエスト制御部とは、それぞれ、前記リクエストに含まれるアクセス先のメモリアドレスに基づいて前記リクエストの送信先の識別子を決定するアドレスデコーダを備え、

前記第一リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を、前記第二リクエスト制御部の備えるアドレスデコーダの前記メモリアドレスの範囲を含むように設定を変更するステップ

をさらに備えるマルチプロセッサシステムの障害回復方式。

【請求項14】

請求項10から請求項13までのいずれかに記載のマルチプロセッサシステムの障害回復方式であって、

前記リクエストの送信先の識別子において参照するべきビットのビット位置を記録した第三レジスタをさらに備え、

前記リクエストの出力先を決定するステップは、

前記リクエストの含む送信先の識別子が、前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致する場合、前記第三レジスタに設定された前記ビット位置基づいて前記リクエストの出力先を前記第一リクエスト制御部か前記第二リクエスト制御部かのいずれかに決定するステップ

を含むマルチプロセッサシステムの障害回復方式。

【請求項15】

請求項14に記載のマルチプロセッサシステムの障害回復方式であって、前記リクエストの出力先を決定するステップは、

前記リクエストの含む送信先の識別子が前記第一レジスタに設定された識別子と前記第二レジスタに設定された識別子とのいずれにも一致しない場合、前記ルーティングテーブルに記録されたデータを参照して転送先を決定するステップ

を含むマルチプロセッサシステム障害回復方式。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【公開番号】特開2010−231723(P2010−231723A)

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願番号】特願2009−81353(P2009−81353)

【出願日】平成21年3月30日(2009.3.30)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願日】平成21年3月30日(2009.3.30)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]