マルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラム

【課題】安定性やセキュリティレベルを考慮して実行する処理内容に応じて実行環境を柔軟に構築する。

【解決手段】マルチプロセッサシステムは、CPU割当ての決定に際し、CPU割当てを判断する実行環境主制御手段10と、実行環境主制御手段10の指示に従って、実行環境の起動・停止・切替を制御し、実行環境主制御手段10との同期をとる実行環境副制御手段20a〜20nと、CPU4−0〜CPU4−n又は実行環境毎の共有資源の管理情報や参照拒否情報を入力し、実行環境主制御手段10と実行環境副制御手段20a〜20n又は、実行環境副制御手段20a〜20nをそれぞれ分離する実行環境管理手段30とを含む。

【解決手段】マルチプロセッサシステムは、CPU割当ての決定に際し、CPU割当てを判断する実行環境主制御手段10と、実行環境主制御手段10の指示に従って、実行環境の起動・停止・切替を制御し、実行環境主制御手段10との同期をとる実行環境副制御手段20a〜20nと、CPU4−0〜CPU4−n又は実行環境毎の共有資源の管理情報や参照拒否情報を入力し、実行環境主制御手段10と実行環境副制御手段20a〜20n又は、実行環境副制御手段20a〜20nをそれぞれ分離する実行環境管理手段30とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マルチプロセッサシステムに関し、特に、セキュリティレベルを考慮して処理単位の実行環境を構築することを可能にするマルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラムに関するものである。

【背景技術】

【0002】

マルチプロセッサ上でマルチプロセッサ用のOSを動作させるマルチプロセッサシステムである、例えば、対称型マルチプロセッサ(SMP:Symmetric Multiple Processor)上で対照型マルチプロセッサOS(SMP OS)を実行するマルチプロセッサシステムにおいては、複数のCPUが互いに同等な立場でアプリケーションの処理を分担するといった構成がとられており、SMP OSの元でCPUの負荷状態に応じて実行する処理とCPUの組み合わせからなる実行環境の構成変更を行うことにより、効率的な処理を実現している。

【0003】

このようなマルチプロセッサシステムとしては、例えば、関連文献1(特開2002−278778号公報)に開示されるシステムが存在する。

【0004】

関連文献1のマルチプロセッサシステムでは、ある一定時間内に実行された全プロセス(処理)について、プロセスを特定の1個のCPUで実行すべきか否か決定し、プロセスを特定の1個のCPUで実行すべきであると決定されたプロセス数の、全プロセス数に対する割合が閾値を上回った場合、全てのプロセスについて全スレッドを特定の1個のCPUで実行すべきであると決定し、これにより、オーバーヘッドの原因である、スレッドの実行における順番の管理、各CPUが内蔵するキャッシュメモリと主記憶の同期合わせ、主記憶や入出力のための排他利用管理処理を解消するものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−278778号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した関連のマルチプロセッサシステムにおいては、以下に述べるような問題点があった。

【0007】

まず、関連文献1等に記載されるシステムでは、複数のCPUが互いに同等な立場でアプリケーションの複数の処理を分担し、CPUの負荷状態を条件として実行環境(CPUと処理の組み合わせ)の構成変更を行うだけであるので、処理毎に安定性やセキュリティレベルを変えた実行環境を構築することができないといった問題があった。

【0008】

例えば、アプリケーションの本来的な処理(基本処理)と、基本処理に伴って実行され、任意に追加又は削除される付随的な処理(追加処理)を実行する場合、基本処理を実行する実行環境と、追加処理を実行する実行環境とを安定性やセキュリティレベルを考慮して(基本処理の実行環境の安定性及びセキュリティレベルを高くして)構築するといったことが不可能であった。

【0009】

具体的には、安定性の要求度合いが異なる複数の処理を同時に実行する場合、高い安定性が要求される処理とそれ以外の処理とを異なる実行環境の下で実行するといった環境の構築ができないという不都合があった。

【0010】

なお、SMP OSを搭載するマルチプロセッサシステム以外のシステムにおいても上述した課題を同様に抱えている。

【0011】

本発明の目的は、上記課題を解決するためになされたものであり、安定性やセキュリティレベルを考慮して実行する処理内容に応じて実行環境を柔軟に構築することができるマルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラムを提案することにある。

【0012】

また、本発明の他の目的は、各処理内容に応じた実行環境の切り替え(構成変更)を高速に実現することを可能にするマルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラムを提案することにある。

【課題を解決するための手段】

【0013】

上記課題を解決するため本発明は、複数のCPUと、前記CPU上で実行される複数のOSを搭載し、前記CPUと前記OSを組み合わせた少なくとも一つの実行環境を、システム上で実行する処理に応じて形成する。

【発明の効果】

【0014】

本発明によれば、システム上で実行する処理毎に安定性やセキュリティレベルを変えた実行環境を構築することができるという効果が達成される。

【0015】

その理由は、複数のCPUと、当該CPU上で実行される複数のOSを搭載し、当該CPUと当該OSを組み合わせた少なくとも一つの実行環境を、システム上で実行する処理に応じて形成することで、処理に応じた多様な実行環境を形成することができるためのである。

【図面の簡単な説明】

【0016】

【図1】図1は、本発明のマルチプロセッサシステムの概略を説明する遷移図である。

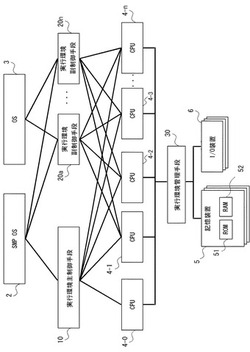

【図2】図2は、本発明の第1の実施の形態によるマルチプロセッサシステムの構成を示すブロック図である。

【図3】図3は、本発明の特徴的な構成である実行環境主制御手段、実行環境副制御手段、実行環境管理手段の相互関係の概略を示す図である。

【図4】図4は、第1の実施の形態による記憶装置の論理アドレスを説明する図である。

【図5】図5は、第1の実施の形態によるRAM上のCPUベースの実行環境情報を説明する図である。

【図6】図6は、第1の実施の形態によるRAM上の実行環境ベースの実行環境情報を説明する図である。

【図7】図7は、第1の実施の形態によるCPUのコンテキストの構成を示す図である。

【図8】図8は、第1の実施の形態による実行環境主制御手段の構成を示すブロック図である。

【図9】図9は、第1の実施の形態による実行環境副制御手段の構成を示すブロック図である。

【図10】図10は、第1の実施の形態による実行環境主制御手段と実行環境副制御手段との接続関係を示すブロック図である。

【図11】図11は、第1の実施の形態による実行環境管理手段の構成をCPUベースで説明するブロック図である。

【図12】図12は、第1の実施の形態によるCPU管理データの構成を説明する図である。

【図13】図13は、第1の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図14】図14は、第1の実施の形態による実行環境管理手段のアクセス許可機能を説明する図である。

【図15】図15は、第1の実施の形態による実行環境管理手段のアクセス拒否機能を説明する図である。

【図16】図16は、第1の実施の形態による実行環境管理手段の構成を実行環境ベースで説明するブロック図である。

【図17】図17は、第1の実施の形態による実行環境管理データ記憶装置の実行環境対応情報を説明する図である。

【図18】図18は、第1の実施の形態による実行環境管理データの構成を説明する図である。

【図19】図19は、第1の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図20】図20は、第1の実施の形態による実行環境管理手段のアクセス許可機能を説明する図である。

【図21】図21は、第1の実施の形態による実行環境管理手段のアクセス拒否機能を説明する図である。

【図22】図22は、第2の実施の形態による切替え後のマルチプロセッサシステムの構成を示すブロック図である。

【図23】図23は、本実施の形態によるマルチプロセッサシステムのハードウェア構成を示すブロック図である。

【図24】図24は、第1の実施の形態による実行環境停止処理を共有メモリベース同期に基づいて説明する図である。

【図25】図25は、第1の実施の形態による実行環境停止処理を割込みベース同期に基づいて説明する図である。

【図26】図26は、第1の実施の形態による実行環境停止処理をバリア同期に基づいて説明する図である。

【図27】図27は、第1の実施の形態による実行環境切替え処理を共有メモリベース同期に基づいて説明する図である。

【図28】図28は、第1の実施の形態による実行環境切替え処理を割込みベース同期に基づいて説明する図である。

【図29】図29は、第1の実施の形態による実行環境切替え処理をバリア同期に基づいて説明する図である。

【図30】図30は、第1の実施の形態によるマルチプロセッサシステムのCPU4−0の動作概略を説明する図である。

【図31】図31は、第1の実施の形態によるマルチプロセッサシステムのCPU4−1〜4−nの動作概略を説明する図である。

【図32】図32は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図33】図33は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図34】図34は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図35】図35は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図36】図36は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図37】図37は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図38】図38は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図39】図39は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図40】図40は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図41】図41は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図42】図42は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図43】図43は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図44】図44は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図45】図45は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図46】図46は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図47】図47は、第1の実施の形態による実行環境主制御手段の主実行環境内CPU停止処理(自動切換え機能無し)を説明する図である。

【図48】図48は、第1の実施の形態による実行環境主制御手段の主実行環境内CPU停止処理及びコンテキスト保存処理(自動切換え機能無し)を説明する図である。

【図49】図49は、第1の実施の形態による実行環境主制御手段の主実行環境内切替処理(自動切換え機能無し)を説明する図である。

【図50】図50は、第1の実施の形態による実行環境主制御手段の初期状態の主実行環境内のCPU追加処理(自動切換え機能無し)を説明する図である。

【図51】図51は、第1の実施の形態による実行環境主制御手段のコンテキスト設定付き主実行環境内のCPU追加処理(自動切換え機能無し)を説明する図である。

【図52】図52は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上のOS停止処理(自動切換え機能無し)を説明する図である。

【図53】図53は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上のOS停止処理及びコンテキスト保存処理(自動切換え機能無し)を説明する図である。

【図54】図54は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上の実行環境切替処理(自動切換え機能無し)を説明する図である。

【図55】図55は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の初期状態の別CPU上のOS起動処理(自動切換え機能無し)を説明する図である。

【図56】図56は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段のコンテキスト設定付き別CPU上のOS起動処理(自動切換え機能無し)を説明する図である。

【図57】図57は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の実行環境副制御手段からの切替処理(自動切換え機能無し)を説明する図である。

【図58】図58は、第1の実施の形態による実行環境主制御手段の別CPU上の実行環境副制御手段停止処理(自動切換え機能無し)を説明する図である。

【図59】図59は、第1の実施の形態による実行環境主制御手段の別CPU上の実行環境副制御手段起動処理(自動切換え機能無し)を説明する図である。

【図60】図60は、本発明の第2の実施の形態による実行環境管理手段の構成をCPUベースで説明するブロック図である。

【図61】図61は、第2の実施の形態による自動CPU切替データの構成を説明する図である。

【図62】図62は、第2の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図63】図63は、第2の実施の形態による実行環境管理手段のリード(R)アクセスでの自動切替機能を説明する図である。

【図64】図64は、第2の実施の形態による実行環境管理手段のライト(W)アクセスでの自動切替機能を説明する図である。

【図65】図65は、第2の実施の形態による切替え後のCPU管理データの構成を説明する図である。

【図66】図66は、第2の実施の形態による実行環境管理手段の構成を実行環境ベースで説明するブロック図である。

【図67】図67は、第2の実施の形態による自動実行環境切替データの構成を説明する図である。

【図68】図68は、第2の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図69】図69は、第2の実施の形態による実行環境管理手段のリード(R)アクセスでの自動切替機能を説明する図である。

【図70】図70は、第2の実施の形態による実行環境管理手段のライト(W)アクセスでの自動切替機能を説明する図である。

【図71】図71は、第2の実施の形態による実行環境切替え機能(自動切換え機能有り)を説明する図である。

【図72】図72は、第2の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上の実行環境切替処理(自動切換え機能有り)を説明する図である。

【図73】図73は、第2の実施の形態による切替え後のマルチプロセッサシステムの構成を示すブロック図である。

【図74】図74は、本発明の第3の実施の形態による実行環境副制御手段の構成を示すブロック図である。

【図75】図75は、第3の実施の形態による実行環境副制御手段の同一信頼度実行環境切替処理(自動切換え機能無し)を説明する図である。

【図76】図76は、第3の実施の形態による実行環境主制御手段及び実行環境副制御手段の同一実行環境スケジュール手段からの切替処理(自動切換え機能無し)を説明する図である。

【図77】図77は、本発明の第4の実施の形態によるマルチプロセッサシステムの構成を示すブロック図である。

【図78】図78は、本発明の第5の実施の形態のマルチプロセッサシステムにおける一部の構成を示すブロック図である。

【図79】図79は、本発明の第5の実施の形態のマルチプロセッサシステムにおける一部の構成を示すブロック図である。

【図80】図80は、本発明の第6の実施の形態のマルチプロセッサシステムの構成を示すブロック図である。

【図81】図81は、本発明の実施例1のマルチプロセッサシステムの具体的動作例を示すフローチャートである。

【図82】図82は、本発明の一実施例による実行順序検査付き実行環境管理手段の構成を示す図である。

【図83】図83は、本発明の一実施例による実行順序検査記憶手段の構成を示す図である。

【図84】図84は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図85】図85は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図86】図86は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図87】図87は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図88】図88は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図89】図89は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図90】図90は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【発明を実施するための形態】

【0017】

まず、図1に本発明によるマルチプロセッサシステムによる実行環境の切り替え(状態遷移)の仕組みを示す。

【0018】

図1を参照すると、本発明のマルチプロセッサシステムによれば、実行環境主制御手段10を備えるSMP OS2がCPU4−0及びCPU4−1上でアプリケーション(AP)8において基本的な処理である基本処理110を実行させる基本処理用実行環境100−0のみの状態(構成)と、実行環境主制御手段10を備えるSMP OS2がCPU4−0上で基本処理110を実行させる基本処理用実行環境100−0及び実行環境副制御手段20を備えるOS3がCPU4−1上で新たなアプリケーション8における追加処理120を実行させる追加処理用実行環境100−1からなる状態(構成)との間で、各CPUの負荷、処理の安定性やセキュリティレベルに応じて構成状態を遷移させることを可能にする。

【0019】

なお、本実施の形態において、各基本処理110は、アプリケーション8において本来的(必須)に備えられる処理であり、信頼度(セキュリティレベル)が最も高い。各追加処理120は、アプリケーション8において基本処理110に付随して又は単独で追加又は削除される処理であり、信頼度(セキュリティレベル)は基本処理に比べると低いものである。このように各追加処理は、処理内容の違い、安定性やセキュリティなどの違いによって基本処理110と区別される。なお、セキュリティレベル(信頼度)とは、処理ごとに、あるセキュリティポリシーに従って段階ごとに付与されるものをいう。

【0020】

すなわち、図1は、基本処理のみ行う基本処理用実行環境100−0を構築した構成状態(状態A)と、基本処理を行う基本処理用実行環境100−0と追加処理を行う追加処理用実行環境100−1の複数の実行環境を構築した構成状態(状態B)との間の状態遷移を示している。

【0021】

なお、図1に示す状態遷移は、本発明によるマルチプロセッサシステムによる状態遷移のあくまで一例であって図示の内容に限定されないことは言うまでもない。

【0022】

(第1の実施の形態)

本発明の第1の実施の形態を図を用いて詳細に説明する。

【0023】

(第1の実施の形態の構成)

図2は、本発明の第1の実施の形態によるマルチプロセッサシステムの構成を示すブロック図である。

【0024】

図2を参照すると、本実施の形態によるマルチプロセッサシステムは、SMP OS2と、OS3と、実行環境主制御手段10と、実行環境副制御手段20a〜20nと、CPU4−0〜4−nと、実行環境管理手段30と、記憶装置5と、I/O(In/Out:入出力)装置6とを備える。SMP OS2は実行環境主制御手段10及び実行環境副制御手段20a〜20nに接続し、OS3は実行環境副制御手段20a〜20nに接続し、実行環境主制御手段10はCPU4−0〜4−nに接続し、実行環境副制御手段20a〜20nはCPU4−1〜4−nに接続し、CPU4−0〜4−n、共有資源である記憶装置5及びI/O装置6は実行環境管理手段30に接続する。

【0025】

すなわち、本実施の形態によるマルチプロセッサシステムは、実行環境主制御手段10が各CPU4−0〜4−nを直接制御する。

【0026】

図3は、本願発明の特徴的な構成である実行環境主制御手段10、実行環境副制御手段20a〜20n、実行環境管理手段30の相互関係の概略を示す図である。

【0027】

実行環境主制御手段10は、基本処理用実行環境を実行する機能と、追加処理用実行環境を制御する機能と、CPU4と実行環境の管理情報を実行環境管理手段30に対して設定する機能と、実行環境管理情報又はコンテキスト情報(コンテキスト90)を実行環境副制御手段20との間でやりとりする機能と、実行環境管理手段30よって実行環境同士が干渉されることを防止する機能とを有する。

【0028】

具体的には、実行環境主制御手段10は、入力情報として、アプリケーションやOS3からの起動/切替通知や、タイマや割込みといったイベント通知や、実行環境副制御手段20からの切替通知を入力し、基本処理110用のSMP OS2又はOS3と共に動作し、又は、実行環境のCPU割当てを決定し、又は、実行環境の起動・停止・切替を制御し、又は、実行環境副制御手段20及び実行環境管理手段30と連携して正しい制御を保障し、場合により出力情報として、実行環境副制御手段20に対して実行環境制御情報及びコンテキスト情報(コンテキスト90)を出力する。

【0029】

例えば、実行環境主制御手段10は、CPU割当ての決定に際し、追加処理の信頼度(セキュリティレベル)や、CPUの信頼度(セキュリティレベル)や性能の違い、基本処理と追加処理の関連性や適合性等に基づいてCPU割当てを判断する。

【0030】

すなわち、実行環境主制御手段10は、AP8やOS3からの起動/切替通知として、例えば、実行環境100−1を起動してほしいとの要求を受けると該当する実行環境100−1を起動し、例えば、実行環境100−3はもう必要ないとの通知を受けると、該当する実行環境100−3を停止し、例えば、実行環境100−2におけるあるアプリケーションと通信したいとの要求を受けると、該当する実行環境100−2が動作中なら何もせず、停止中なら該当する実行環境100−2を起動する。なお、起動する場合、CPU以上の実行環境が動作することになるならば、最も動作時間の長い実行環境と切替えて実行環境100−2を起動することが望ましい。

【0031】

さらに、実行環境主制御手段10は、自発的要求として、例えば、タイマ割込みを受けた際にCPU以上の実行環境動作中の場合、停止中の実行環境のうち、実行時間の少ない実行環境(実行時間の少ない実行環境を選択するポリシは任意)へ動作中の実行環境を切替え、例えば、所定の外部割込みがきたら実行環境100−4を起動又は停止する場合、所定の外部割込みがきたら該当する実行環境100−4を起動又は停止する。なお、起動する場合、CPU以上の実行環境が動作中ならば、当該実行環境と切替えて実行環境100−4を起動することが望ましい。

【0032】

実行環境副制御手段20は、実行環境主制御手段10からの通知によって、追加処理用実行環境を制御する機能を有する。

【0033】

具体的には、実行環境副制御手段20は、入力情報として、実行環境主制御手段10からの実行環境制御情報及びコンテキスト情報(コンテキスト90)を入力し、実行環境主制御手段10の指示に従って、実行環境の起動・停止・切替を制御し、実行環境主制御手段10との同期をとる。実行環境主制御手段10との同期をとることによって切替前後の実行環境の分離が可能となる。また、実行環境副制御手段20は、場合により出力情報として、実行環境主制御手段10に対してエラー情報を出力する。

【0034】

実行環境管理手段30は、実行環境主制御手段10と実行環境副制御手段20a〜20n又は、実行環境副制御手段20a〜20nをそれぞれ分離する機能を有する。具体的には、実行環境管理手段30は、入力情報として、CPU4又は実行環境毎の共有資源(記憶装置5、I/O装置6)の管理情報や参照拒否情報を入力し、入力情報に基づいて各CPUからの参照に対し、何もしないか、又は拒絶してエラー情報を返す。

【0035】

共有資源は、各処理ごとに、例えばアドレスに従って割り当てられており、基本処理110用領域、追加処理120用実行環境100用領域、共有領域、実行環境情報領域ごとに予め決められたアドレスを有していてもよい。図4は、共有資源である記憶装置の論理アドレスを説明する図である。

【0036】

図4を参照すると、記憶装置5のROM51は、アドレス0x00000000〜0x007FFFFFの基本処理110用領域と、アドレス0x00800000〜0x00FFFFFFの追加処理用実行環境100−1用領域と、アドレス0x01000000〜0x017FFFFFの追加処理120用実行環境100−2用領域と、アドレス0x01800000〜0x02000000の追加処理120用実行環境100−3用領域とを有し、また、記憶装置5のRAM52は、アドレス0x30000000〜0x30FFFFFFの基本処理110用領域と、アドレス0x31000000〜0x31FFFFFFの追加処理120用実行環境100−1用領域と、アドレス0x32000000〜0x32FFFFFFの追加処理120用実行環境100−2用領域と、アドレス0x33000000〜0x33FFFFFFの追加処理120用実行環境100−3用領域と、アドレス0x34000000〜0x34FFFFFFの共有領域と、アドレス0x35000000〜0x36000000の実行環境情報領域とを有する。

【0037】

図5及び図6は、RAM上の実行環境情報を説明する図である。

【0038】

図5は、RAM上のCPUベースの実行環境情報を説明する図であり、図5(a)〜図5(d)を参照すると、CPUベースの実行環境情報は、各実行環境100−0〜100−3を構成するCPU用のコンテキスト及びCPU管理データによって実行環境毎の動作状態を格納する。

【0039】

図6は、RAM上の実行環境ベースの実行環境情報を説明する図であり、図6(a)〜図6(d)を参照すると、実行環境ベースの実行環境情報は、各実行環境100−0〜100−3を構成するCPU用のコンテキスト及び各実行環境用の実行環境情報によって実行環境毎の動作状態を格納する。

【0040】

図7は、CPU4−kのコンテキストの構成を示す図である。図7を参照すると、CPU4−kのコンテキスト90は、レジスタ#0〜レジスタ#14、レジスタ#15(PC)、プロセッサ状態レジスタ及びプロセッサ制御レジスタを備え、例えば、動作中のCPU4−kのある指定された瞬間の記憶状態の全てが格納されている。

【0041】

ここで、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の構成を図を用いてさらに詳細に説明する。

【0042】

図8は、本実施の形態による実行環境主制御手段10の構成を示すブロック図である。

【0043】

図8を参照すると、本実施の形態による実行環境主制御手段10は、AP8/OS3及びRAMに接続する実行環境スケジュール手段13と、OS3、OS副連携手段21(後述)及び実行環境スケジュール手段13に接続するOS主連携手段11と、OS副連携手段21、実行環境副管理同期手段22、実行環境管理手段30及び実行環境スケジュール手段13に接続する実行環境主管理同期手段12とを備える。

【0044】

実行環境スケジュール手段13は、入力情報として、例えば、AP8/OS3から何らかの要求を受けると、RAM52上の実行環境情報を参照し、参照した実行環境情報に基づいて、OS主連携手段11に対し、実行環境スケジュール手段13自身が属する実行環境・そのCPU・そのOSの起動・停止・追加・切り替え等の制御命令や、実行環境スケジュール手段13自身が属さない実行環境・そのCPU・そのOSの起動・停止・追加・切り替え等の制御命令を通知する機能と、OS主連携手段11に対し、次に切り替わるべきコンテキストや前回のコンテキストの情報を通知する機能と、実行環境主管理同期手段12に対し、当該制御命令によってCPUなどが追加等された後の実行環境スケジュール手段13の設定情報を通知する機能と、RAM52上の実行環境情報を更新する機能等を有する。

【0045】

OS主連携手段11は、実行環境スケジュール手段13から受けた制御命令を実行する機能及び当該制御命令をOS副連携手段21(後述)に通知する機能と、OS3対して前回のコンテキストや切り替え先のコンテキストの情報を設定する機能と、動作中のOS3のコンテキストを取得して実行環境スケジュール手段13に対して渡す機能と、OS副連携手段21(後述)から受けた制御命令を実行する機能等を有する。

【0046】

実行環境主管理同期手段12は、実行環境スケジュール手段13が通知された設定情報を実行環境スケジュール手段13に対して設定する機能と、当該設定が終了したことを実行環境スケジュール手段13やOS主連携手段11に対して通知する機能と、実行環境副管理同期手段22(後述)との間で処理の同期をとる機能等を有する。

【0047】

図9は、本実施の形態による実行環境副制御手段20の構成を示すブロック図である。

【0048】

図9を参照すると、本実施の形態による実行環境副制御手段20は、OS3及びOS主連携手段11に接続するOS副連携手段21と、実行環境主管理同期手段12及びOS副連携手段21に接続する実行環境副管理同期手段22とを備える。

【0049】

OS副連携手段21は、OS主連携手段11から受けた制御命令を実行する機能と、命令が実行されたことを実行環境副管理同期手段22に通知する機能と、OS副連携手段21自身が属する実行環境のOSのコンテキストの情報を取得してOS主連携手段11に対して送付する機能と、OS主連携手段11から送付された前回のコンテキストや切り替え先のコンテキストの情報をOS副連携手段21自身が属する実行環境のOS3に対して設定する機能と、入力情報として、例えば、OS副連携手段21自身が属する実行環境のOS3から受けた何らかの要求をOS主連携手段11に対して通知する機能等を有する。

【0050】

実行環境副管理同期手段22は、命令が実行されたことをOS副連携手段21から通知されると、当該命令が実行されたことを実行環境主管理同期手段11に通知する等によって、実行環境主管理同期手段11との間で処理の同期をとる機能等を有する。

【0051】

図10は、本発明の第1の実施の形態による実行環境主制御手段10と実行環境副制御手段20との接続関係を示すブロック図である。

【0052】

ここで、本実施の形態による実行環境管理手段30の構成を、(a)CPUベース、(b)実行環境ベースによってさらに詳細に説明する。

【0053】

((a)CPUベースの場合)

図11〜図15は、本実施の形態による実行環境管理手段30の構成をCPUベースで説明する図である。

【0054】

図11は、本実施の形態による実行環境管理手段30の構成をCPUベースで説明するブロック図である。図11を参照すると、実行環境管理手段30は、システムバス及び周辺バスに接続するCPUフィルタ手段31と、システムバス及びCPUフィルタ手段31に接続するCPU管理データ記憶装置32とを備える。

【0055】

CPUフィルタ手段31は、システムバスを介してあるCPU4からのアクセス要求を受けると、CPU管理データ記憶装置32から読み出したCPU管理データ321(後述)に基づいて、当該アクセス要求の拒否を判定する機能を有する。

【0056】

CPU管理データ記憶装置32は、CPU管理データ321を格納し、CPU管理データ321の更新要求を実行する機能を有する。

【0057】

図12は、本実施の形態によるCPU管理データ321の構成を説明する図である。図12を参照すると、CPU管理データ321は、CPU4−0〜4−4毎に、割当てられた記憶装置5領域の始点・終点と、リード処理(R)及びライト処理(W)のうち許可される処理を示す許可ビットとが記載されたエントリによって構成されている。

次いで、本実施の形態のCPUベースにおける実行環境管理手段30の機能を説明する。

【0058】

(データ更新機能)

図13は、本実施の形態による実行環境管理手段30のデータ更新機能を説明する図である。図13を参照すると、実行環境管理手段30のデータ更新機能は、ステップS1において、CPU管理データ321を更新する。なお、基本的には、基本処理実行中のCPUのみがCPU管理データ321に触ることができる。ただし、所定のエントリに関しては、追加処理実行中のCPUがCPU管理データ321に触ってもよい。

【0059】

(アクセス許可機能)

図14は、本実施の形態による実行環境管理手段30のアクセス許可機能を説明する図である。図14を参照すると、実行環境管理手段30のアクセス許可機能は、CPUフィルタ手段31が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、CPU管理データ321を読み出し、ステップS3において、前記読み出したCPU管理データ321に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを許可する。

【0060】

(アクセス拒否機能)

図15は、本実施の形態による実行環境管理手段30のアクセス拒否機能を説明する図である。図15を参照すると、実行環境管理手段30のアクセス拒否機能は、CPUフィルタ手段31が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、CPU管理データ321を読み出し、ステップS3において、前記読み出したCPU管理データ321に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを拒否する。タイミング制約が厳しい場合には、この回路で拒否するのではなく、あえてアクセスアドレスをシステムに存在しないアドレスに変換して、そして、別の回路でそのような拒否をさせてもよい。

【0061】

((b)実行環境ベースの場合)

図16〜図21は、本実施の形態による実行環境管理手段30の構成を実行環境ベースで説明する図である。

図16は、本実施の形態による実行環境管理手段30の構成を実行環境ベースで説明するブロック図である。図16を参照すると、実行環境管理手段30は、システムバス及び周辺バスに接続する実行環境フィルタ手段35と、システムバス及び実行環境フィルタ手段35に接続する実行環境管理データ記憶装置36とを備える。

【0062】

実行環境フィルタ手段35は、システムバスを介してあるCPU4からのアクセス要求を受けると、実行環境管理データ記憶装置36から読み出した実行環境管理データ361及び実行環境対応情報362(後述)に基づいて、当該アクセス要求の拒否を判定する機能を有する。

【0063】

実行環境管理データ記憶装置36は、実行環境管理データ361及び実行環境対応情報362を格納し、実行環境管理データ361及び実行環境対応情報362の更新要求を実行する機能を有する。

【0064】

図17は、本実施の形態による実行環境管理データ記憶装置36の実行環境対応情報362を説明する図である。図17を参照すると、実行環境対応情報362は、CPU4−0〜4−4毎に、実行環境番号で示される実行環境100−0〜100−4が対応付けられている。より詳細には、CPU4−0、4−1に実行環境100−0が対応付けられ、CPU4−2に実行環境100−1が対応付けられ、CPU4−3に実行環境100−2が対応付けられ、CPU4−3に実行環境100−3が対応付けられている。

【0065】

図18は、本実施の形態による実行環境管理データ361の構成を説明する図である。図18を参照すると、実行環境管理データ361は、実行環境番号を示す実行環境100−0〜100−4毎に、割当てられた記憶装置5領域の始点・終点と、リード処理(R)及びライト処理(W)のうち許可される処理を示す許可ビットとが記載されたエントリによって構成されている。

【0066】

次いで、本実施の形態の実行環境ベースにおける実行環境管理手段30の機能を説明する。

【0067】

(データ更新機能)

図19は、本実施の形態による実行環境管理手段30のデータ更新機能を説明する図である。図19を参照すると、実行環境管理手段30のデータ更新機能は、ステップS1において、実行環境管理データ361を更新する。なお、基本的には、基本処理実行中のCPUのみが実行環境管理データ361に触れる。ただし、所定のエントリに関しては、追加処理実行中のCPU4が実行環境管理データ361に触ってもよい。

【0068】

(アクセス許可機能)

図20は、本実施の形態による実行環境管理手段30のアクセス許可機能を説明する図である。図20を参照すると、実行環境管理手段30のアクセス許可機能は、実行環境フィルタ手段35が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、実行環境管理データ361を読み出し、ステップS3において、前記読み出した実行環境管理データ361に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを許可する。

【0069】

(アクセス拒否機能)

図21は、本実施の形態による実行環境管理手段30のアクセス拒否機能を説明する図である。図21を参照すると、実行環境管理手段30のアクセス拒否機能は、実行環境フィルタ手段35が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、実行環境管理データ361を読み出し、ステップS3において、前記読み出した実行環境管理データ361に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを拒否する。タイミング制約が厳しい場合には、この回路で拒否するのではなく、あえてアクセスアドレスをシステムに存在しないアドレスに変換して、そして、別の回路でそのような拒否をさせてもよい。

【0070】

本実施の形態のCPUベース又は実行環境ベースによる切り替え後のマルチプロセッサシステムの構成を図22に示す。

【0071】

ここで、マルチプロセッサシステムのハードウェア構成の説明をする。

【0072】

図23は、本実施の形態によるマルチプロセッサシステムのハードウェア構成を示すブロック図である。

【0073】

図23を参照すると、本発明によるマルチプロセッサシステムは、一般的なコンピュータ装置と同様のハードウェア構成によって実現することができ、CPU(Central Processing Unit)501、RAM(Random Access Memory)等のメインメモリであり、データの作業領域やデータの一時退避領域に用いられる主記憶部502、インターネット等を介してデータの送受信を行う通信制御部503、周辺機器と接続してデータの送受信を行うインタフェース部504、ROM(Read Only Memory)、磁気ディスク、半導体メモリ等の不揮発性メモリから構成されるハードディスク装置である補助記憶部505、本情報処理装置の上記各構成要素を相互に接続するシステムバス506等を備えている。

【0074】

本発明によるマルチプロセッサシステムは、その動作を、マルチプロセッサシステム内部にそのような機能を実現するプログラムを組み込んだ、LSI(Large Scale Integration)等のハードウェア部品からなる回路部品を実装してハードウェア的に実現することは勿論として、上記した各構成要素の各機能を提供するプログラムを、コンピュータ処理装置上のCPU501で実行することにより、ソフトウェア的に実現することができる。

【0075】

すなわち、CPU501(CPU4、CPU4−0〜4−n、CPU4−k)は、補助記憶部505(記憶装置5)に格納されているプログラムを、主記憶部501(記憶装置5)にロードして実行し、マルチプロセッサシステムの動作を制御することにより、上述した各機能をソフトウェア的に実現する。

【0076】

(第1の実施の形態の動作)

図24〜図59は、本発明の第1の実施の形態によるマルチプロセッサシステムの動作を説明する図である。

【0077】

まず、本実施の形態による実行環境停止処理及び実行環境切替え処理を、(a)共有メモリベース同期、(b)割込みベース同期、(c)バリア同期に基づいて詳細に説明する。

【0078】

(実行環境停止処理)

実行停止処理は、実行環境副管理同期手段22が属する実行環境を停止する処理である。

【0079】

((a)共有メモリベース同期)

図24は、本実施の形態による実行環境停止処理を共有メモリベース同期に基づいて説明する図である。

【0080】

図24を参照すると、実行環境副管理同期手段22が共有メモリである記憶装置5にある値(例えば“A”)を書く(ステップS101)。実行環境主管理同期手段12は、実行環境副管理同期手段22によって共有メモリに値が書かれると、共有メモリの値が“A”であるか否かを判定し(ステップS102)、共有メモリの値が“A”である場合に実行環境管理手段30を設定して(ステップS105)処理を継続し(ステップS106)、実行環境副管理同期手段22が属する実行環境が停止する(ステップS107)。実行環境主管理同期手段12は、共有メモリの値が“A”でない場合において、共有メモリの値が“A”でない場合が閾値回数以上判定されたときに(ステップS103)相手を強制的にリセットし(ステップS104)、閾値回数に達しないときに(ステップS103)共有メモリの値が“A”であるか否かを再度判定する(ステップS102)。なお、実行環境副管理同期手段22がループしていてもよい。

【0081】

((b)割込みベース同期)

図25は、本実施の形態による実行環境停止処理を割込みベース同期に基づいて説明する図である。

【0082】

図25を参照すると、実行環境副管理同期手段22が割込み要求を送信すると(ステップS201)、実行環境主管理同期手段12は、割込み要求の受信の有無を判定し(ステップS202)、割込み要求を受信した場合に実行環境管理手段30を設定して(ステップS205)処理を継続し(ステップS206)、実行環境副管理同期手段22が属する実行環境が停止する(ステップS207)。実行環境主管理同期手段12は、割込み要求を受信していない場合において、受信していない状態が閾値時間以上経過したときに(ステップS203)相手を強制的にリセットし(ステップS204)、閾値時間に達しないときに(ステップS203)割込み要求の受信の有無を再度判定する(ステップS202)。なお、実行環境副管理同期手段22がループしていてもよい。

【0083】

((c)バリア同期)

図26は、本実施の形態による実行環境停止処理をバリア同期に基づいて説明する図である。

【0084】

図26を参照すると、実行環境副管理同期手段22は、実行環境主管理同期手段12とバリア同期を行い(ステップS301)、バリア同期が達成されたか否かを判定し(ステップS302)、達成されていなければ再度判定し、達成されていれば実行環境を停止する(ステップS303)。実行環境主管理同期手段12は、実行環境副管理同期手段22とバリア同期を行い(ステップS311)、バリア同期が達成されたか否かを判定し(ステップS312)、達成されていれば実行環境管理手段30を設定し(ステップS313)、処理を継続する(ステップS314)。実行環境副管理同期手段22は、達成されていなければ、達成されていない状態が閾値時間以上経過しているか否かを判定し(ステップS315)、閾値時間以上経過しているときに相手を強制的にリセットし(ステップS316)、閾値時間に達しないときはバリア同期が達成されたか否かを再度判定する(ステップS312)。

【0085】

(実行環境切替え処理)

実行環境切替え処理は、実行環境主制御手段10または実行環境副制御手段20が属する実行環境を切り替える処理である。

【0086】

((a)共有メモリベース同期)

図27は、本実施の形態による実行環境切替え処理を共有メモリベース同期に基づいて説明する図である。

【0087】

図27を参照すると、実行環境副管理同期手段22が共有メモリにある値(例えば“A”)を書く(ステップS401)。実行環境主管理同期手段12は、実行環境副管理同期手段22によって共有メモリに値が書かれると、共有メモリの値が“A”であるか否かを判定し(ステップS402)、共有メモリの値が“A”でない場合において、共有メモリの値が“A”でない場合が閾値回数以上判定されたときに(ステップS403)相手を強制的にリセットし(ステップS404)、閾値回数に達しないときに共有メモリの値が“A”であるか否かを再度判定し(ステップS402)、共有メモリの値が“A”である場合に実行環境管理手段30を設定し(ステップS405)、共有メモリにある値(例えば“B”)を書いて(ステップS406)処理を継続する(ステップS407)。実行環境副管理同期手段22は、実行環境主管理同期手段12によって共有メモリに値が書かれると、共有メモリの値が“B”であるか否かを判定し(ステップS408)、共有メモリの値が“B”でない場合に共有メモリの値が“B”であるか否かを再度判定し(ステップS408)、共有メモリの値が“B”である場合に実行環境を切り替える(ステップS409)。なお、実行環境副管理同期手段22が先にループしていてもよい。

【0088】

((b)割込みベース同期)

図28は、本実施の形態による実行環境切替え処理を割込みベース同期に基づいて説明する図である。

【0089】

図28を参照すると、実行環境副管理同期手段22が割込み要求を送信すると(ステップS501)、実行環境主管理同期手段12は、割込み要求の受信の有無を判定し(ステップS502)、割込み要求を受信していない場合において、閾値時間以上のときに(ステップS503)相手を強制的にリセットし(ステップS504)、閾値時間に達しないときに割込み要求の受信の有無を再度判定し(ステップS502)、割込み要求を受信した場合に実行環境管理手段30を設定して(ステップS505)割込み要求を送信して(ステップS506)処理を継続する(ステップS507)。実行環境副管理同期手段22は、割込み要求の受信の有無を判定し(ステップS508)、割込み要求を受信していない場合に割込み要求の受信の有無を再度判定し(ステップS508)、割込み要求を受信した場合に実行環境を切り替える(ステップS509)。なお、実行環境副管理同期手段22が先にループしていてもよい。

【0090】

((c)バリア同期)

図29は、本実施の形態による実行環境切替え処理をバリア同期に基づいて説明する図である。

【0091】

図29を参照すると、実行環境副管理同期手段22は、実行環境主管理同期手段12とバリア同期を行い(ステップS601)、バリア同期が達成されたか否かを判定し(ステップS602)、達成されていなければ再度判定し(ステップS602)、達成されていれば再度実行環境主管理同期手段12とバリア同期を行い(ステップS603)、バリア同期が達成されたか否かを判定し(ステップS604)、達成されていなければ再度判定し(ステップS604)、達成されていれば実行環境を停止する(ステップS605)。実行環境主管理同期手段12は、実行環境副管理同期手段22とバリア同期を行い(ステップS611)、バリア同期が達成されたか否かを判定し(ステップS612)、達成されていなければ、達成されていない状態が閾値時間以上経過しているか否かを判定し(ステップS613)、閾値時間以上経過しているときに相手を強制的にリセットし(ステップS614)、閾値時間に達していなければバリア同期が達成されたか否かを再度判定する(ステップS612)。実行環境主管理同期手段12は、ステップS612においてバリア同期が達成されていれば、実行環境管理手段30を設定して(ステップS615)再度実行環境副管理同期手段22とバリア同期を行い(ステップS616)、バリア同期が達成されたか否かを判定し(ステップS617)、達成されていなければ、達成されていない状態が閾値時間以上経過しているか否かを判定し(ステップS618)、閾値時間以上経過しているときに相手を強制的にリセットし(ステップS614)、閾値時間に達していなければバリア同期が達成されたか否かを再度判定して(ステップS617)処理を継続する(ステップS619)。

【0092】

次いで、本実施の形態によるマルチプロセッサシステムの動作を、実行環境主制御手段10の動作を中心に詳細に説明する。なお、本実施の形態による実行環境主制御手段10は、少なくともCPU4−0を含む実行環境100−0上において動作する。

【0093】

図30は、本実施の形態によるマルチプロセッサシステムのCPU4−0の動作概略を説明する図であり、図31は、本実施の形態によるマルチプロセッサシステムのCPU4−1〜4−nの動作概略を説明する図である。

【0094】

図30を参照すると、CPU4−0は、初期状態における起動処理によって実行環境主制御手段10が起動する。また、CPU4−0は、実行環境主制御手段10のレジューム処理によってSMP OS2が起動し、サスペンド処理によってSMP OS2が停止する。また、CPU4−0は、SMP OS2又は実行環境主制御手段10の停止処理によって初期状態に戻る。

【0095】

図31を参照すると、CPU4−1〜4−nは、初期状態における実行環境主制御手段10起動処理によって実行環境主制御手段10が起動し、初期状態における実行環境副制御手段起動処理によって実行環境副制御手段20が起動し、切替え処理によって実行環境主制御手段10と実行環境副制御手段20とは切替え可能である。実行環境主制御手段10は、SMP OS2に対してレジューム処理及びサスペンド処理を行実行環境制御副主手段は、SMP OS2及びシングルOS7に対してレジューム処理及びサスペンド処理を行う。また、CPU4−1〜4−nは、SMP OS2、シングルOS7、実行環境主制御手段10もしくは実行環境副制御手段20の停止処理によって初期状態に戻る。

【0096】

また、図32〜図46は、本実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【0097】

(主実行環境内CPU停止処理(自動切換え機能無し))

図47は、本実施の形態による実行環境主制御手段10の主実行環境内CPU停止処理(自動切換え機能無し)を説明する図である。

【0098】

図47を参照すると、本実施の形態による実行環境主制御手段10の主実行環境内CPU停止処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して当該実行環境内のCPU停止要求を通知し、また、実行環境主管理同期手段12に対してCPU停止後の実行環境管理手段30の設定情報を通知する。

【0099】

次いで、OS主連携手段11が、ステップS4において、OS3に対して上記CPUの停止を要求し、ステップS5において、OS3から、上記CPUの停止完了の通知を受理し(これは、電源管理におけるCPUシャットダウン処理に近い)、ステップS6において、実行環境主管理同期手段12に対して上記CPUの停止が完了したことを通知する。

【0100】

次いで、実行環境主管理同期手段12が、ステップS7において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS8において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

次いで、実行環境スケジュール手段13が、ステップS9において、実行環境情報521を更新し、ステップS10において、AP8/OS3に当該要求の完了を通知する。

【0101】

(主実行環境内CPU停止処理及びコンテキスト保存処理(自動切換え機能無し))

図48は、本実施の形態による実行環境主制御手段10の主実行環境内CPU停止処理及びコンテキスト保存処理(自動切換え機能無し)を説明する図である。

【0102】

図48を参照すると、本実施の形態による実行環境主制御手段10の主実行環境内CPU停止処理及びコンテキスト保存処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して当該実行環境内のCPU停止及びコンテキスト保存要求を通知し、また、実行環境主管理同期手段12に対してCPU停止後の実行環境管理手段30の設定情報を通知する。

【0103】

次いで、OS主連携手段11が、ステップS4において、OS3に対して上記CPUの停止及びコンテキスト保存を要求し、ステップS5において、OS3から、上記CPUの停止完了の通知及び上記OS3のコンテキスト90を受理し(これは、電源管理におけるCPUサスペンド処理に近い)、ステップS6において、実行環境スケジュール手段13に対して上記OS3のコンテキスト90を渡し、ステップS7において、実行環境主管理同期手段12に対して上記CPUの停止が完了したことを通知する。

【0104】

次いで、実行環境主管理同期手段12が、ステップS8において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS9において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0105】

次いで、実行環境スケジュール手段13が、ステップS10において、実行環境情報521を更新し、ステップS11において、AP8/OS3に当該要求の完了を通知する。

【0106】

上記主実行環境内CPU停止処理及びコンテキスト保存処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0107】

図32は、全てのCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させる状態であって、上記主実行環境内CPU停止処理前の状態を示し、図33は、1つのCPUを除いた残りの全てのCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させる状態であって、上記主実行環境内CPU停止処理後の状態を示す。すなわち、図32に示される状態が、上記主実行環境内CPU停止処理によって、主実行環境内で所定のCPUが停止した図33に示される状態に遷移する。

【0108】

(主実行環境内切替処理(自動切換え機能無し))

図49は、本実施の形態による実行環境主制御手段10の主実行環境内切替処理(自動切換え機能無し)を説明する図である。

【0109】

図49を参照すると、本実施の形態による実行環境主制御手段10の主実行環境内切替処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して当該実行環境内の実行環境切替要求及び切替先のコンテキスト90を通知し、また、実行環境主管理同期手段12に対して切替後の実行環境管理手段30の設定情報を通知する。

【0110】

次いで、OS主連携手段11が、ステップS4において、OS3から、動作中のOS3のコンテキスト90を受理し、ステップS5において、実行環境スケジュール手段13に対して上記OS3のコンテキスト90を渡し、ステップS6において、実行環境主管理同期手段12に対して上記コンテキスト保存の完了を通知する。

【0111】

次いで、実行環境主管理同期手段12が、ステップS7において、実行環境管理手段30に対して切替後の実行環境管理手段30の設定情報を設定し、ステップS8において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0112】

次いで、実行環境スケジュール手段13が、ステップS9において、実行環境情報521を更新し、ステップS10において、AP8/OS3に当該要求の完了を通知する。

【0113】

次いで、ステップS11において、実行環境主管理同期手段12が、OS主連携手段11に対して当該処理の完了を通知し、ステップS12において、OS主連携手段11が、先に受理した切替先のコンテキスト90を設定する。

【0114】

上記主実行環境内切替処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0115】

図32は、全てのCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させる状態であって、上記主実行環境内切替処理前の状態を示し、図34は、1つのCPUを除いた残りの全てのCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りの1つのCPUによって構成される実行環境においてOS3が追加処理120を実行させる状態であって、上記主実行環境内切替処理後の状態を示す。すなわち、図32に示される状態が、上記主実行環境内切替処理によって、主実行環境内で切替えが行われた図34に示される状態に遷移する。

【0116】

また、同様にすれば、図35に示される複数のCPUによって構成される1つの実行環境においてSMP OS2が基本処理110を実行させる状態が、上記実行環境内切替処理によって、図36に示される1つのCPUによって構成される1つの実行環境においてSMP OS2が基本処理110を実行させ、残りのCPUの内複数のCPUによって構成される1つの実行環境においてSMP OS2が追加処理120を実行させる状態に遷移する。

【0117】

さらに、同様にすれば、図37に示される複数のCPUによって構成される1つの実行環境においてSMP OS2が基本処理110を実行させ、残りの全てのCPUによって構成される実行環境においてSMP OS2が追加処理120を実行させる状態が、上記実行環境内切替処理によって、図38に示される複数のCPUによって構成される1つの実行環境においてSMP OS2が基本処理110を実行させ、残りのCPUの内1つのCPUによって構成される1つの実行環境においてSMP OS2が追加処理120を実行させ、残りの各CPUによって構成される各実行環境においてOS3が追加処理120を実行させる状態に遷移する。

【0118】

(初期状態の主実行環境内のCPU追加処理(自動切換え機能無し))

図50は、本実施の形態による実行環境主制御手段10の初期状態の主実行環境内のCPU追加処理(自動切換え機能無し)を説明する図である。

【0119】

図50を参照すると、本実施の形態による実行環境主制御手段10の初期状態の主実行環境内のCPU追加処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して当該実行環境外のCPU追加要求を通知し、また、実行環境主管理同期手段12に対してCPU追加後の実行環境管理手段30の設定情報を通知する。

【0120】

次いで、OS主連携手段11が、ステップS4において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS5において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0121】

次いで、実行環境スケジュール手段13が、ステップS6において、実行環境情報521を更新し、ステップS7において、AP8/OS3に当該要求の完了を通知する。

【0122】

次いで、ステップS8において、実行環境主管理同期手段12が、OS主連携手段11に対して実行環境管理手段30の設定の完了を通知する。

【0123】

次いで、OS主連携手段11が、ステップS9において、OS3に対して上記CPUの追加を要求し、ステップS10において、OS3から、上記CPUの追加完了の通知を受理する(これは、電源管理におけるCPUパワーアップ処理に近い)。

【0124】

(コンテキスト設定処理付き主実行環境内のCPU追加処理(自動切換え機能無し))

図51は、本実施の形態による実行環境主制御手段10のコンテキスト設定処理付き主実行環境内のCPU追加処理(自動切換え機能無し)を説明する図である。

【0125】

図51を参照すると、本実施の形態による実行環境主制御手段10のコンテキスト設定処理付き主実行環境内のCPU追加処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して当該実行環境外のCPU追加要求及び前回のコンテキスト90を通知し、また、実行環境主管理同期手段12に対してCPU追加後の実行環境管理手段30の設定情報を通知する。

【0126】

次いで、実行環境主管理同期手段12が、ステップS4において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS5において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0127】

次いで、実行環境スケジュール手段13が、ステップS6において、実行環境情報521を更新し、ステップS7において、AP8/OS3に当該要求の完了を通知する。

【0128】

次いで、実行環境主管理同期手段12が、ステップS8において、OS主連携手段11に対して実行環境管理手段30の設定の完了を通知する。

【0129】

次いで、OS主連携手段11が、ステップS9において、OS3に対して上記CPUの追加及び前回のコンテキスト設定を要求し、ステップS10において、OS3から、上記CPUの追加完了の通知を受理する(これは、電源管理におけるCPUレジューム処理に近い)。

【0130】

次いで、本実施の形態による実行環境主制御手段10が実行環境副制御手段20と連携して行う動作を詳細に説明する。

【0131】

上記コンテキスト設定処理付き主実行環境内のCPU追加処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0132】

図39は、1つのCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りのCPUが停止している状態であって、上記CPU追加処理前の状態を示し、図40は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りのCPUが停止している状態であって、上記CPU追加処理後の状態を示す。すなわち、図39に示される状態が、上記CPU追加処理によって、主実行環境内のCPUが追加された図40に示される状態に遷移する。

【0133】

(別CPU上のOS停止処理(自動切換え機能無し))

図52は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上のOS停止処理(自動切換え機能無し)を説明する図である。

【0134】

図52を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上のOS停止処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して別CPU上実行環境のOS停止要求を通知し、また、実行環境主管理同期手段12に対してOS停止後の実行環境管理手段30の設定情報を通知する。

【0135】

次いで、OS主連携手段11が、ステップS4において、別CPU上のOS副連携手段21に対してOS停止要求を通知し、ステップS5において、実行環境主管理同期手段12に対して上記CPUの停止完了待ちを通知する。

【0136】

次いで、上記通知を受けたOS副連携手段21が、ステップS6において、OS3に対して上記CPUの停止を要求し、ステップS7において、OS3から、上記CPUの停止完了の通知を受理し(これは、電源管理におけるCPUシャットダウン処理に近い)、ステップS8において、実行環境副管理同期手段22に対してOS停止完了を通知する。

【0137】

次いで、実行環境副管理同期手段22が、ステップS9において、実行環境主管理同期手段12に対して上記CPUの停止が完了したことを通知する。

【0138】

次いで、実行環境主管理同期手段12が、ステップS10において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS11において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0139】

次いで、実行環境スケジュール手段13が、ステップS12において、実行環境情報521を更新し、ステップS13において、AP8/OS3に当該要求の完了を通知する。

【0140】

次いで、実行環境主管理同期手段12が、ステップS8において、OS主連携手段11に対して実行環境管理手段30の設定の完了を通知する。

【0141】

次いで、OS主連携手段11が、ステップS9において、OS3に対して上記CPUの追加及び前回のコンテキスト設定を要求し、ステップS10において、OS3から、上記CPUの追加完了の通知を受理する(これは、電源管理におけるCPUレジューム処理に近い)。

【0142】

(別CPU上のOS停止処理及びコンテキスト保存処理(自動切換え機能無し))

図53は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上のOS停止処理及びコンテキスト保存処理(自動切換え機能無し)を説明する図である。

【0143】

図53を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上のOS停止処理及びコンテキスト保存処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して別CPU上実行環境のOS停止要求を通知し、また、実行環境主管理同期手段12に対してOS停止後の実行環境管理手段30の設定情報を通知する。

【0144】

次いで、OS主連携手段11が、ステップS4において、別CPU上のOS副連携手段21に対してOS停止要求を通知し、ステップS5において、実行環境主管理同期手段12に対して上記CPUの停止完了待ちを通知する。

【0145】

次いで、上記通知を受けたOS副連携手段21が、ステップS6において、OS3に対して上記CPUの停止及びコンテキスト保存を要求し、ステップS7において、OS3から、上記CPUの停止完了の通知及び上記OS3のコンテキスト90を受理し(これは、電源管理におけるCPUサスペンド処理に近い)、ステップS8において、OS主連携手段11に対して上記OS3のコンテキスト90を送付する。

【0146】

次いで、OS主連携手段11が、ステップS9において、実行環境スケジュール手段13に対して上記OS3のコンテキスト90を渡す。

【0147】

次いで、OS副連携手段21が、ステップS10において、実行環境副管理同期手段22に対してOS停止完了を通知する。

【0148】

次いで、実行環境副管理同期手段22が、ステップS11において、実行環境主管理同期手段12に対して上記CPUの停止が完了したことを通知する。

【0149】

次いで、実行環境主管理同期手段12が、ステップS12において、実行環境管理手段30に対して上記OS停止後の実行環境管理手段30の設定情報を設定し、ステップS13において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0150】

次いで、実行環境スケジュール手段13が、ステップS14において、実行環境情報521を更新し、ステップS15において、AP8/OS3に当該要求の完了を通知する。

【0151】

上記別CPU上のOS停止処理及びコンテキスト保存処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0152】

図35は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、1つのCPUによって構成される他の1つの実行環境においてOSが追加処理120を実行させる状態であって、上記OS停止処理前の状態を示し、図41は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、1つのCPUによって構成される他の1つの実行環境において追加処理120を実行させるOSが停止した状態であって、上記OS停止処理後の状態を示す。すなわち、図35に示される状態が、上記OS停止処理によって、上記別CPU上のOS3が停止した図41に示される状態に遷移する。

【0153】

(別CPU上の実行環境切替処理(自動切換え機能無し))

図54は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上の実行環境切替処理(自動切換え機能無し)を説明する図である。

【0154】

図54を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上の実行環境切替処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して別CPU上実行環境の実行環境切替要求及び切替先のコンテキスト90を通知し、また、実行環境主管理同期手段12に対して切替後の実行環境管理手段30の設定情報を通知する。

【0155】

次いで、OS主連携手段11が、ステップS4において、別CPU上のOS副連携手段21に対して実行環境切替要求及び切替先のコンテキスト90を通知し、ステップS5において、実行環境主管理同期手段12に対して上記実行環境切替完了待ちを通知する。

【0156】

次いで、上記通知を受けたOS副連携手段21が、ステップS6において、動作中のOS3のコンテキスト90を受理し、ステップS7において、OS主連携手段11に対して上記OS3のコンテキスト90を送付する。

【0157】

次いで、OS主連携手段11が、ステップS8において、実行環境スケジュール手段13に対して上記OS3のコンテキスト90を渡す。

【0158】

次いで、OS副連携手段21が、ステップS9において、実行環境副管理同期手段22に対してコンテキスト抽出完了を通知する。

【0159】

次いで、実行環境副管理同期手段22が、ステップS10において、実行環境主管理同期手段12に対して上記コンテキスト抽出が完了したことを通知する。

【0160】

次いで、実行環境主管理同期手段12が、ステップS11において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS12において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0161】

次いで、実行環境スケジュール手段13が、ステップS13において、実行環境情報521を更新し、ステップS14において、AP8/OS3に当該要求の完了を通知する。

【0162】

次いで、実行環境主管理同期手段12が、ステップS15において、実行環境副管理同期手段22に対して実行環境管理手段30の設定が完了したことを通知する。

【0163】

次いで、実行環境副管理同期手段22が、ステップS16において、OS副連携手段21に対して上記設定完了を通知する。

【0164】

次いで、OS副連携手段21が、ステップS17において、先に受理した切替先のコンテキスト90を設定する。

【0165】

図54に示す切替処理を行う際に、まず、図53に示す別CPU上のOS停止処理及びコンテキスト保存処理を行い、そして、当該別CPUのリセットないし電源オフをする。次に、リセット解除ないし電源オンによって、当該別CPUをクリアな状態から再起動させることで、別CPU上でOS副連携手段をまっさらな状態から起動する。その後、図56に示されるコンテキスト設定処理付き別CPU上のOS起動処理を行うことで、たとえ当該別CPU上のOS副連携手段が、ウィルス等に汚染されて正常な動作をしなくなっていたとしても、リセット及び電源オフを経由することによって、再度正しい状態なOS副連携手段を起動することができるので、遷移時間は長くかかるものの、非常に安定・安全な、別CPU上での実行環境切替処理が実現できる。

【0166】

上記別CPU上の実行環境切替処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0167】

図42は、1つのCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りの各CPUによって構成される各実行環境において各OSがそれぞれ追加処理120を実行させる状態であって、上記実行環境切替処理前の状態を示し、図43は、1つのCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りの各CPUの内複数のCPUによって構成される1つの実行環境においてSMP OSが追加処理120を実行させ、残りの各CPUによって構成される各実行環境において各OSがそれぞれ追加処理120を実行させる状態であって、上記実行環境切替処理後の状態を示す。すなわち、図42に示される状態が、上記実行環境切替処理によって、別CPU上の実行環境で切替えが行われた図43に示される状態に遷移する。

【0168】

さらに、同様にして、上記図43に示される状態が、上記実行環境切替処理によって、1つのCPUによって構成される1つの実行環境においてSMP OS2が基本処理110を実行させ、残りの各CPUの内複数のCPUによって構成される1つの実行環境においてSMP OS2が追加処理120を実行させ、残りの全てのCPUによって構成される1つの実行環境においてSMP OS2が追加処理120を実行させる図44に示される状態に遷移する。

【0169】

(初期状態の別CPU上のOS起動処理(自動切換え機能無し))

図55は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の初期状態の別CPU上のOS起動処理(自動切換え機能無し)を説明する図である。

【0170】

図55を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の初期状態の別CPU上のOS起動処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して当該別CPU上のCPU起動要求を通知し、また、実行環境主管理同期手段12に対してCPU起動後の実行環境管理手段30の設定情報を通知する。

【0171】

次いで、実行環境主管理同期手段12が、ステップS4において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS5において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0172】

次いで、実行環境スケジュール手段13が、ステップS6において、実行環境情報521を更新し、ステップS7において、AP8/OS3に当該要求の完了を通知する。

【0173】

次いで、実行環境主管理同期手段12が、ステップS8において、OS主連携手段11に対して上記設定完了を通知する。

【0174】

次いで、OS主連携手段11が、ステップS9において、別CPU上のOS副連携手段21に対してCPU起動を要求する。

【0175】

次いで、OS副連携手段21が、ステップS10において、上記CPUの起動を行う(これは、電源管理におけるCPUパワーアップ処理に近い)。

【0176】

(コンテキスト設定処理付き別CPU上のOS起動処理(自動切換え機能無し))

図56は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20のコンテキスト設定処理付き別CPU上のOS起動処理(自動切換え機能無し)を説明する図である。

【0177】

図56を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20のコンテキスト設定処理付き別CPU上のOS起動処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して当該実行環境外のCPU追加要求及び前回のコンテキスト90を通知し、また、実行環境主管理同期手段12に対してCPU追加後の実行環境管理手段30の設定情報を通知する。

【0178】

次いで、実行環境主管理同期手段12が、ステップS4において、実行環境管理手段30に対して上記CPU停止後の実行環境管理手段30の設定情報を設定し、ステップS5において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0179】

次いで、実行環境スケジュール手段13が、ステップS6において、実行環境情報521を更新し、ステップS7において、AP8/OS3に当該要求の完了を通知する。

【0180】

次いで、実行環境主管理同期手段12が、ステップS8において、OS主連携手段11に対して実行環境管理手段30の設定の完了を通知する。

【0181】

次いで、OS主連携手段11が、ステップS9において、別CPU上のOS副連携手段21に対してCPU起動及び前回のコンテキスト設定を要求する。

【0182】

次いで、OS副連携手段21が、ステップS10において、上記CPUの起動及びコンテキスト設定を行う(これは、電源管理におけるCPUレジューム処理に近い)。

【0183】

上記コンテキスト設定処理付き別CPU上のOS起動処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0184】

図41は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、1つのCPUによって構成される他の1つの実行環境において追加処理120を実行させるOSが停止した状態であって、上記OS起動処理前の状態を示し、図35は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、1つのCPUによって構成される他の1つの実行環境においてOSが追加処理120を実行させる状態であって、上記OS起動処理後の状態を示す。すなわち、図41に示される状態が、上記OS起動処理によって、別CPU上のOS3が起動された図35に示される状態に遷移する。

【0185】

(実行環境副制御手段20からの切替処理(自動切換え機能無し))

図57は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の実行環境副制御手段からの切替処理(自動切換え機能無し)を説明する図である。

【0186】

図57を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の実行環境副制御手段20からの切替処理(自動切換え機能無し)は、OS副連携手段21が、ステップS1において、OS3から当該要求を受理し、ステップS2において、OS主連携手段11に対して当該要求を通知する。

【0187】

次いで、OS主連携手段11が、ステップS3において、実行環境スケジュール手段13に対して当該要求を通知する。

【0188】

(別CPU上の実行環境副制御手段停止処理(自動切換え機能無し))

図58は、本実施の形態による実行環境主制御手段10の別CPU上の実行環境副制御手段停止処理(自動切換え機能無し)を説明する図である。

【0189】

図58を参照すると、本実施の形態による実行環境主制御手段10の別CPU上の実行環境副制御手段停止処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して別CPU上実行環境の実行環境副制御手段停止要求を通知し、また、実行環境主管理同期手段12に対して実行環境副制御手段停止後の実行環境管理手段30の設定情報を通知する。

【0190】

次いで、OS主連携手段11が、ステップS4において、実行環境主管理同期手段12に対して上記実行環境副制御手段停止後の実行環境管理手段30の設定を要求する。

【0191】

次いで、実行環境主管理同期手段12が、ステップS5において、実行環境管理手段30に対して上記実行環境副制御手段停止後の実行環境管理手段30の設定情報を設定し、ステップS6において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0192】

次いで、実行環境スケジュール手段13が、ステップS7において、実行環境情報521を更新し、ステップS8において、AP8/OS3に当該要求の完了を通知する。

次いで、ステップS9において、実行環境主管理同期手段12がOS主連携手段11に対して実行環境管理手段30の設定の完了を通知し、OS主連携手段11が当該CPUを停止する。

【0193】

上記別CPU上の実行環境副制御手段停止処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0194】

図41は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りの各CPUによって構成される各実行環境において実行環境副制御手段が設定された状態であって、上記実行環境副制御手段停止処理前の状態を示し、図45は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りのCPUの内1つのCPUによって構成される1つの実行環境において設定されていた実行環境副制御手段が停止した状態であって、上記実行環境副制御手段停止処理後の状態を示す。すなわち、図41に示される状態が、上記実行環境副制御手段停止処理によって、上記別CPU上の実行環境副制御手段20が停止した図45に示される状態に遷移する。

【0195】

さらに、同様にして、上記図45に示される状態が、上記実行環境副制御手段停止処理によって、複数のCPUによって構成される1つの実行環境においてSMP OS2が基本処理110を実行させ、残りの各CPUによって構成される各実行環境の全てにおいて実行環境副制御手段20が停止した図46に示される状態に遷移する。

【0196】

(別CPU上の実行環境副制御手段起動処理(自動切換え機能無し))

図59は、本実施の形態による実行環境主制御手段10の別CPU上の実行環境副制御手段起動処理(自動切換え機能無し)を説明する図である。

【0197】

図59を参照すると、本実施の形態による実行環境主制御手段10の別CPU上の実行環境副制御手段起動処理(自動切換え機能無し)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して別CPU上実行環境の実行環境副制御手段起動要求を通知し、また、実行環境主管理同期手段12に対して実行環境副制御手段起動後の実行環境管理手段30の設定情報を通知する。

【0198】

次いで、OS主連携手段11が、ステップS4において、実行環境主管理同期手段12に対して上記実行環境副制御手段起動後の実行環境管理手段30の設定を要求する。

【0199】

次いで、実行環境主管理同期手段12が、ステップS5において、実行環境管理手段30に対して上記実行環境副制御手段起動後の実行環境管理手段30の設定情報を設定し、ステップS6において、実行環境スケジュール手段13に対して当該処理の完了を通知する。

【0200】

次いで、実行環境スケジュール手段13が、ステップS7において、実行環境情報521を更新し、ステップS8において、AP8/OS3に当該要求の完了を通知する。

【0201】

次いで、ステップS9において、実行環境主管理同期手段12がOS主連携手段11に対して実行環境管理手段30の設定の完了を通知し、OS主連携手段11が当該CPU上の停止状態を解除する。

【0202】

上記別CPU上の実行環境副制御手段起動処理(自動切換え機能無し)によるマルチプロセッサシステムの状態の遷移を説明する。

【0203】

図45は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りのCPUの内1つのCPU以外の各CPUによって構成される各実行環境において実行環境副制御手段が設定された状態であって、上記実行環境副制御手段起動処理前の状態を示し、図41は、複数のCPUによって構成される1つの実行環境においてSMP OSが基本処理110を実行させ、残りの各CPUによって構成される各実行環境において実行環境副制御手段が設定された状態であって、上記実行環境副制御手段起動処理後の状態を示す。すなわち、図45に示される状態が、上記実行環境副制御手段起動処理によって、上記別CPU上の実行環境副制御手段20が起動した図41に示される状態に遷移する。

【0204】

(第1の実施の形態の効果)

本実施の形態によれば、マルチプロセッサシステム上で実行する処理毎に安定性やセキュリティレベルを変えた実行環境100を構築することができる。

【0205】

例えば、アプリケーション8の本来的な処理(基本処理110)と、基本処理110に伴って実行され、任意に追加又は削除される付随的な処理(追加処理120)を実行する場合、基本処理110を実行する実行環境100−0と、追加処理120を実行する実行環境100−nとを安定性やセキュリティレベルを考慮して(基本処理110の実行環境100−0の安定性及びセキュリティレベルを高くして)マルチプロセッサシステムを構築することができる。

【0206】

その理由は、複数のCPU4と、当該CPU4上で実行される複数のOS3を搭載し、当該CPU4と当該OS3を組み合わせた少なくとも一つの実行環境100を、マルチプロセッサシステム上で実行する処理に応じて形成するからである。

【0207】

また、本実施の形態によれば、処理の高速化を図ることができる。

【0208】

その理由は、実行環境主制御手段10、実行環境副制御手段20及び実行環境管理手段30が連携して動作することにより仮想マシンを設ける必要がないため、アプリケーション8がCPU4上で直接動作するからである。

【0209】

また、本実施の形態によれば、CPUの処理負荷を軽減することができる。

【0210】

その理由は、マルチプロセッサシステム上で実行する処理に応じてCPU4とOS3を組み合わせた実行環境を多様に形成できるからである。

【0211】

また、本実施の形態によれば、SMP OS環境においても追加処理向け実行環境の生成が可能となるので、基本処理の安定性やセキュリティレベルが向上し、また、追加処理120向け実行環境100がCPU4上で直接動作するので、基本処理110及び追加処理120を非常に高速で処理できる。

【0212】

(第2の実施の形態)

(第2の実施の形態の構成)

本発明の第2の実施の形態による実行環境管理手段30の構成を、(a)CPUベース、(b)実行環境ベースによって詳細に説明する。本実施の形態による実行環境管理手段30は、CPU4又は実行環境100を自動で切替える自動切替機能を有する点で第1の実施の形態と相違する。従って、第1の実施の形態との相違点を中心に説明する。

【0213】

((a)CPUベースの場合)

図60〜図64は、本実施の形態による実行環境管理手段30の構成をCPUベースで説明する図である。

【0214】

図60は、本実施の形態による実行環境管理手段30の構成をCPUベースで説明するブロック図である。図60を参照すると、本実施の形態による実行環境管理手段30は、周辺バス及びCPU管理データ記憶装置32に接続する自動CPU切替手段33と、システムバス、CPU管理データ記憶装置32及び自動CPU切替手段33に接続する自動CPU切替データ記憶装置34とをさらに備える点で、第1の実施の形態における実行環境管理手段30の構成と相違する。従って、第1の実施の形態との相違点を中心に説明する。

【0215】

自動CPU切替手段33は、CPUフィルタ手段31がシステムバスを介してあるCPU4からのアクセス要求を受けると、自動CPU切替データ記憶装置34から読み出した自動CPU切替データ341(後述)に基づいて、当該アクセス要求が切替制御を要求する条件である切替トリガであるか否かを判定する機能と、自動CPU切替データ341のトリガ条件に相当するエントリを更新する機能等を有する。

【0216】

自動CPU切替データ記憶装置34は、自動CPU切替データ341を格納し、自動CPU切替データ341の更新要求を実行する機能を有する。

【0217】

図61は、本実施の形態による自動CPU切替データの構成を説明する図である。図61を参照すると、自動CPU切替データ341は、CPU4−0〜4−4毎に、トリガ条件と、切替後に割当てられるメモリ領域の始点・終点と、リード処理(R)及びライト処理(W)のうち切替後に許可される処理を示す許可ビットとが記載されたエントリによって構成されている。

【0218】

次いで、本実施の形態のCPUベースにおける実行環境管理手段30の機能を説明する。

【0219】

(データ更新機能)

図62は、本実施の形態による実行環境管理手段30のデータ更新機能を説明する図である。図62を参照すると、実行環境管理手段30のデータ更新機能は、ステップS1において、CPU管理データ321を更新する。なお、基本的には、基本処理実行中のCPUのみがCPU管理データ321に触ることができる。ただし、所定のエントリに関しては、追加処理実行中のCPUがCPU管理データ321に触ってもよい。

【0220】

(リード(R)アクセスでの自動切替機能)

図63は、本実施の形態による実行環境管理手段30のリード(R)アクセスでの自動切替機能を説明する図である。

【0221】

図63を参照すると、本実施の形態による実行環境管理手段30のリードアクセスでの自動切替機能は、CPUフィルタ手段31が、ステップS1において、任意のCPUからのリードアクセスを受理し、ステップS2において、CPU管理データ321を読み出す。また、ステップS2において、自動CPU切替手段33が自動CPU切替データ341を読み出す。

【0222】

次いで、ステップS3において、CPUフィルタ手段31が、前記読み出したCPU管理データ321に基づいて、当該受理したリードアクセスの許否を判定し、当該受理したリードアクセスを許可し、また、自動CPU切替手段33が、当該受理したリードアクセスが切替トリガであることを認知する。

【0223】

次いで、ステップS4において、CPUフィルタ手段31が前記リードアクセスの応答を受理し、また、自動CPU切替手段33が前記リードアクセスの完了を認知する。

次いで、ステップS5において、CPUフィルタ手段31が前記リードアクセスの応答をCPUに返し、ステップS6において、自動CPU切替手段33がCPU管理データ321のトリガ条件に相当するエントリを更新する。

【0224】

(ライト(W)アクセスでの自動切替機能)

図64は、本実施の形態による実行環境管理手段30のライト(W)アクセスでの自動切替機能を説明する図である。

【0225】

図64を参照すると、本実施の形態による実行環境管理手段30のライトアクセスでの自動切替機能は、CPUフィルタ手段31が、ステップS1において、任意のCPUからのライトアクセスを受理し、ステップS2において、CPU管理データ321を読み出す。また、ステップS2において、自動CPU切替手段33が自動CPU切替データ341を読み出す。

【0226】

次いで、ステップS3において、CPUフィルタ手段31が、前記読み出したCPU管理データ記憶装置32に基づいて、当該受理したライトアクセスの許否を判定し、当該受理したライトアクセスを許可し、また、自動CPU切替手段33が、当該受理したライトアクセスが切替トリガであることを認知する。

次いで、ステップS4において、自動CPU切替手段33が、CPU管理データ321のトリガ条件に相当するエントリを更新する。

本実施の形態による切替え後のCPU管理データ記憶装置32の構成を図65に示す。

【0227】

((b)実行環境ベースの場合)

図66〜図71は、本実施の形態による実行環境管理手段30の構成を実行環境ベースで説明する図である。

【0228】

図66は、本実施の形態による実行環境管理手段30の構成を実行環境ベースで説明するブロック図である。図66を参照すると、本実施の形態による実行環境管理手段30は、周辺バス及び実行環境管理データ記憶装置36に接続する自動実行環境切替手段37と、システムバス、実行環境管理データ記憶装置36及び自動実行環境切替手段37に接続する自動実行環境切替データ記憶装置38とをさらに備える点で、第1の実施の形態における実行環境管理手段30の構成と相違する。従って、第1の実施の形態との相違点を中心に説明する。

【0229】

自動実行環境切替手段37は、実行環境フィルタ手段35がシステムバスを介してあるCPU4からのアクセス要求を受けると、自動実行環境切替データ記憶装置38から読み出した自動実行環境切替データ381(後述)に基づいて、当該アクセス要求が切替制御を要求する条件である切替トリガであるか否かを判定する機能と、自動実行環境切替データ381のトリガ条件に相当するエントリを更新する機能等を有する。

【0230】

自動実行環境切替データ記憶装置38は、自動実行環境切替データ381を格納し、自動実行環境切替データ381の更新要求を実行する機能を有する。

【0231】

図67は、本実施の形態による自動実行環境切替データ381の構成を説明する図である。図67を参照すると、本実施の形態による自動実行環境切替データ381は、CPU4−0〜4−4毎に、トリガ条件と、実行環境番号によって示される実行環境とが対応付けて記載されたエントリによって構成されている。より詳細には、CPU4−0〜4−2には実行環境100−0が対応付けられ、CPU4−3には実行環境が対応付けられておらず、CPU4−4には実行環境100−2が対応付けられている。

【0232】

次いで、本実施の形態の実行環境ベースにおける実行環境管理手段30の機能を説明する。

【0233】

(データ更新機能)

図68は、本実施の形態による実行環境管理手段30のデータ更新機能を説明する図である。

【0234】

図68を参照すると、本実施の形態による実行環境管理手段30のデータ更新機能は、ステップS1において、自動実行環境切替データ381を更新する。なお、基本的には、基本処理実行中のCPUのみが自動実行環境切替データ381に触ることができる。ただし、所定のエントリに関しては、追加処理実行中のCPUが自動実行環境切替データ381に触ってもよい。

【0235】

(リード(R)アクセスでの自動切替機能)

図69は、本実施の形態による実行環境管理手段30のリード(R)アクセスでの自動切替機能を説明する図である。

【0236】

図69を参照すると、本実施の形態による実行環境管理手段30のリードアクセスでの自動切替機能は、実行環境フィルタ手段35が、ステップS1において、任意のCPUからのリードアクセスを受理し、ステップS2において、実行環境管理データ361を読み出す。また、ステップS2において、自動実行環境切替手段37が自動実行環境切替データ381を読み出す。

【0237】

次いで、ステップS3において、実行環境フィルタ手段35が、前記読み出した実行環境管理データ361に基づいて、当該受理したリードアクセスの許否を判定し、当該受理したリードアクセスを許可し、また、自動実行環境切替手段37が、当該受理したリードアクセスが切替トリガであることを認知する。

【0238】

次いで、ステップS4において、実行環境フィルタ手段35が前記リードアクセスの応答を受理し、また、自動実行環境切替手段37が前記リードアクセスの完了を認知する。

【0239】

次いで、ステップS5において、実行環境フィルタ手段35が前記リードアクセスの応答をCPUに返し、ステップS6において、自動実行環境切替手段37が実行環境管理データ361のトリガ条件に相当するエントリを更新する。

【0240】

(ライト(W)アクセスでの自動切替機能)

図70は、本実施の形態による実行環境管理手段30のライト(W)アクセスでの自動切替機能を説明する図である。

【0241】

図70を参照すると、本実施の形態による実行環境管理手段30のライトアクセスでの自動切替機能は、実行環境フィルタ手段35が、ステップS1において、任意のCPUからのライトアクセスを受理し、ステップS2において、実行環境管理データ361を読み出す。また、ステップS2において、自動実行環境切替手段37が自動実行環境切替データ381を読み出す。

【0242】

次いで、ステップS3において、実行環境フィルタ手段35が、前記読み出した実行環境管理データ361に基づいて、当該受理したライトアクセスの許否を判定し、当該受理したライトアクセスを許可し、また、自動実行環境切替手段37が、当該受理したライトアクセスが切替トリガであることを認知する。

【0243】

次いで、ステップS4において、自動実行環境切替手段37が、実行環境管理データ361のトリガ条件に相当するエントリを更新する。

【0244】

図71は、本実施の形態による実行環境切替え機能(自動切換え機能有り)を説明する図である。

【0245】

図71を参照すると、実行環境管理手段30に自動切換え機能を有する本実施の形態において、実行環境主制御手段10と実行環境副制御手段20とは互いに同期をとることなく、実行環境主制御手段10が処理を継続させ、実行環境副制御手段20が実行環境を切替える。

【0246】

(第2の実施の形態の動作)

本実施の形態による実行環境主制御手段10が実行環境副制御手段20と連携して行う動作を詳細に説明する。

【0247】

(別CPU上の実行環境切替処理(自動切換え機能有り))

図72は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上の実行環境切替処理(自動切換え機能有り)を説明する図である。

【0248】

図72を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の別CPU上の実行環境切替処理(自動切換え機能有り)は、実行環境スケジュール手段13が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS主連携手段11に対して別CPU上実行環境の実行環境切替要求及び切替先のコンテキスト90を通知し、また、実行環境主管理同期手段12に対してCPU停止後の実行環境管理手段30の設定情報を通知する。

【0249】

次いで、OS主連携手段11が、ステップS4において、別CPU上のOS副連携手段21に対して実行環境切替要求及び切替先のコンテキスト90を通知する。

【0250】

次いで、上記通知を受けたOS副連携手段21が、ステップS5において、OS3から、動作中のOS3のコンテキスト90を受理し、ステップS6において、OS主連携手段11に対して上記OS3のコンテキスト90を送付する。

【0251】

次いで、OS主連携手段11が、ステップS7において、実行環境スケジュール手段13に対して上記OS3のコンテキスト90を渡す。

【0252】

次いで、実行環境スケジュール手段13が、ステップS8において、実行環境情報521を更新し、ステップS9において、AP8/OS3に当該要求の完了を通知する。

【0253】

次いで、OS副連携手段21が、ステップS10において、先に受理した切替先のコンテキスト90を設定する。

【0254】

本実施の形態による切替え後のマルチプロセッサシステムの構成を図734に示す。

【0255】

なお、本実施の形態における切替トリガは、システムバスを介して受信したあるCPU4からのアクセス要求がトリガ条件を満たすか否かによって判定されるが、これは、アクセス要求に限定されず、所定の時間の経過や所定の閾値以上のCPU負荷等によってトリガ条件が満たされ、対応する所定の切替制御を自動的に要求するものであってもよい。

【0256】

(第2の実施の形態の効果)

本実施の形態によれば、実行環境管理手段30は、CPUフィルタ手段31がシステムバスを介してあるCPU4からのアクセス要求を受けると、自動CPU切替データ記憶装置34から読み出した自動CPU切替データ341(後述)に基づいて、当該アクセス要求が切替制御を要求する条件である切替トリガであるか否かを判定し、切替トリガである場合には自動的に切替制御を要求する自動CPU切替手段33を備えるため、実行環境主制御手段10の処理負担を軽減することができる。

【0257】

また、本実施の形態によれば、アクセス要求に限定されず、所定の時間の経過や所定の閾値以上のCPU負荷等によってトリガ条件が満たされ、対応する所定の切替制御を自動的に要求するため、より多様な切替制御が可能となる。

【0258】

(第3の実施の形態)

(第3の実施の形態の構成)

図74は、本発明の第3の実施の形態による実行環境副制御手段20の構成を示すブロック図である。図74を参照すると、本実施の形態による実行環境副制御手段20は、実行環境スケジュール手段13と同様の機能(スケジュール機能)を有し、AP8/OS3、RAM、OS副連携手段21及び実行環境副管理同期手段22に接続する同一実行環境スケジュール手段23をさらに備える点で、第1の実施の形態における実行環境副制御手段20の構成と相違する。従って、第1の実施の形態との相違点を中心に説明する。

【0259】

(第3の実施の形態の動作)

(同一信頼度(セキュリティレベル)実行環境切替処理(自動切換え機能無し))

図75は、本実施の形態による実行環境副制御手段20の同一信頼度実行環境切替処理(自動切換え機能無し)を説明する図である。

【0260】

図75を参照すると、本実施の形態による実行環境副制御手段20の同一信頼度実行環境切替処理(自動切換え機能無し)は、同一実行環境スケジュール手段23が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、OS副連携手段21に対して当該実行環境内の実行環境切替要求及び切替先のコンテキスト90を通知し、また、実行環境副管理同期手段22に対して切替後の実行環境管理手段30の設定情報を通知する。

【0261】

次いで、OS副連携手段21が、ステップS4において、OS3から、動作中のOS3のコンテキスト90を受理し、ステップS5において、同一実行環境スケジュール手段23に対して上記OS3のコンテキスト90を渡し、ステップS6において、実行環境副管理同期手段22に対して上記コンテキスト90保存の完了を通知する。

【0262】

次いで、実行環境副管理同期手段22が、ステップS7において、実行環境管理手段30に対して切替後の実行環境管理手段30の設定情報を設定し、ステップS8において、同一実行環境スケジュール手段23に対して当該処理の完了を通知する。

【0263】

次いで、同一実行環境スケジュール手段23が、ステップS9において、実行環境情報521を更新し、ステップS10において、AP8/OS3に当該要求の完了を通知する。

【0264】

次いで、ステップS11において、実行環境副管理同期手段22が、OS副連携手段21に対して当該処理の完了を通知し、ステップS12において、OS副連携手段21が、先に受理した切替先のコンテキスト90を設定する。

【0265】

また、図76は、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の同一実行環境スケジュール手段からの切替処理(自動切換え機能無し)を説明する図である。

【0266】

図76を参照すると、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の同一実行環境スケジュール手段23からの切替処理(自動切換え機能無し)は、同一実行環境スケジュール手段23が、ステップS1において、AP8/OS3から当該要求を受理し、ステップS2において、RAM52上の実行環境情報521を読み出し、ステップS3において、自身にてスケジューリングできないと判断し、該要求をOS副連携手段21に対して通知する。

【0267】

次いで、ステップS4において、OS副連携手段21がOS主連携手段11に対して当該要求を通知し、ステップS5において、OS主連携手段11が実行環境スケジュール手段13に対して当該要求を通知する。

【0268】

次いで、実行環境副管理同期手段22が、ステップS7において、実行環境管理手段30に対して切替後の実行環境管理手段30の設定情報を設定し、ステップS8において、同一実行環境スケジュール手段23に対して当該処理の完了を通知する。

【0269】

次いで、同一実行環境スケジュール手段23が、ステップS9において、実行環境情報521を更新し、ステップS10において、AP8/OS3に当該要求の完了を通知する。

【0270】

次いで、ステップS11において、実行環境副管理同期手段22が、OS副連携手段21に対して当該処理の完了を通知し、ステップS12において、OS副連携手段21が、先に受理した切替先のコンテキスト90を設定する。

【0271】

(第3の実施の形態の効果)

本実施の形態によれば、実行環境副制御手段20が、実行環境スケジュール手段13と同様の機能(スケジュール機能)を有する同一実行環境スケジュール手段23を備えるので、実行環境スケジュール手段13を備える実行環境主制御手段10だけでなく、実行環境副制御手段20においても、他の実行環境副制御手段20に対する実行環境の切り替え制御命令を単独で生成できる。

【0272】

また、本実施の形態によれば、実行環境副制御手段20においても、他の実行環境副制御手段20に対する実行環境の切り替え制御命令を単独で生成できるので、実行環境主制御手段10の処理負担を軽減し、処理の高速化、さらには、実行環境主制御手段10の安定性及びセキュリティレベルの向上を図ることができる。

【0273】

(第4の実施の形態)

図77は、本発明の第4の実施の形態によるマルチプロセッサシステムの構成を示すブロック図である。

【0274】

図77を参照すると、本実施の形態によるマルチプロセッサシステムの構成は、実行環境副制御手段20がCPU4−1〜4−nだけでなくCPU4−0にも接続する点で、図2に示す第1の実施の形態によるマルチプロセッサシステムの構成と相違する。従って、本実施の形態によるマルチプロセッサシステムは、実行環境主制御手段10が動作するCPU4を固定するのではなく、当該CPUを実行環境主制御手段10によって追加されたCPU4のいずれのCPU4へも移動可能とする点で第1の実施の形態と相違する。

【0275】

(第5の実施の形態)

図78及び図79は、本発明の第5の実施の形態のマルチプロセッサシステムにおける一部の構成を示すブロック図である。

【0276】

図78及び図79を参照すると、本実施の形態のマルチプロセッサシステムは、CPU4が、ユーザ・スーパバイザ41モードと、ユーザ・スーパバイザより優先度の高いハイパーバイザ42モードと、記憶装置管理ユニット43を備える点で上記第1〜第4の実施の形態と相違する。

【0277】

本実施の形態によれば、図78に示すような、SMP OS2がCPU4上で実行環境主制御手段10によって制御されて基本処理110を実行させる状態が、図79に示すような、OS3がCPU4上で実行環境副制御手段20によって制御されてそれぞれ追加処理120を実行させる状態に遷移可能である。

【0278】

(第6の実施の形態)

図80は、本発明の第6の実施の形態のマルチプロセッサシステムの構成を示すブロック図である。

【0279】

図80を参照すると、本実施の形態のマルチプロセッサシステムは、上記第1〜第5の何れかの実施の形態のマルチプロセッサシステム300−1〜300−nを並列して複数備えた構成に、実行環境管理手段30、記憶装置5及びI/O装置6からなる構成を階層的に備える点で、上記第1〜第5の実施の形態と相違する。

【0280】

本実施の形態によれば、上記第1〜第5の何れかの実施の形態のマルチプロセッサシステムを並列して複数備えた構成に、実行環境管理手段30、記憶装置5及びI/O装置6からなる構成を階層的に備えるので、より多様な実行環境の分離、切り替え、拡大、縮退等が可能になるため、基本処理110や追加処理120のセキュリティレベルやCPU負荷並びにOS3の種類等に応じてより詳細に実行環境を制御することができる。

【0281】

(実施例1)

本発明の実施例1は、第1の実施の形態のマルチプロセッサシステムの具体的動作例である。本実施例を、上記図34、図37及び図81を用いて説明する。図81は、本実施例のマルチプロセッサシステムの具体的動作例を示すフローチャートである。

【0282】

ステップS901において、基本処理用のSMP OS2が、1つの実行環境を構成する5つのCPU上で動作している。

【0283】

ステップS902において、ユーザがゲームを実行したいとのイベントを入力する。

【0284】

ステップS903において、そのイベントに対応して、ゲーム実行環境の起動を実行環境主制御手段10に対して通知する。

【0285】

ステップS904において、実行環境主制御手段10は、ゲーム実行環境が一度実行済みか否かを判定する。もしゲーム実行環境が一度実行済みの場合、ステップS909へ。

【0286】

ステップS905において、実行環境主制御手段10は、ゲーム実行環境が実行済みでない場合、5つのCPUのうち、1つのCPUをゲーム実行環境に割当てることを決定する。

【0287】

ステップS906において、実行環境主制御手段10は、主実行環境内CPU停止処理により、そのCPUを停止する。

【0288】

ステップS907において、実行環境主制御手段10は、別CPU上の実行環境副制御手段起動処理により、実行環境副制御手段20を起動する。

【0289】

ステップS908において、実行環境主制御手段10は、別CPU上のOS起動処理(初期状態)により、ゲーム実行環境を起動し、処理を終了する。

【0290】

ステップS909において、実行環境主制御手段10は、主実行環境内の切替処理により、ゲーム実行環境を起動し、処理を終了する。

【0291】

図82は、本発明の一実施例による実行順序検査付き実行環境管理手段50の構成を示す図である。図82を参照すると、実行環境管理手段30と並列に、実行順序検査手段51と、実行順序検査記憶手段52とを備える。すなわち、実行順序検査付き実行環境管理手段50は、図3等に示される実行環境管理手段30へ置換可能であり、さらに、これにより、以下で述べる実行順序検査機能を利用することができるため、より高い安全性を実現可能である。

【0292】

実行順序検査手段51は、実行順序検査記憶手段52の情報に基づいて、観測対象のCPUが正しい順序で命令をフェッチしているか、すなわち、正しい実行順序を保持しているかどうかを検査する機能を有する。これにより、実行環境副制御手段を実行するCPUの動作を、実行環境主制御手段を実行するCPUから監視することが可能となる。また、この実行順序検査手段51は、観測対象のCPUが指定された範囲の命令をフェッチしている状態にあるかないかといった状態をも保持している。この状態は、実行環境主制御手段を実行するCPUから読出し、ないし、状態リセットが可能である。

【0293】

図83は、本発明の一実施例による実行順序検査記憶装置52の構成を示す図である。図83を参照すると、実行順序検査記憶装置52は、どのCPUを観測対象とし、かつ、その観測範囲が記述される。ここで、Startとは、観測対象のCPUが最初の命令フェッチを許可する物理アドレスを意味し、そして、Endとは物理アドレスを表し、StartからEndまでの間の範囲での、最初の命令フェッチを許可しないことを意味している。すなわち、図では、観測対象のCPU#3は、0x0e000000と0x0e001000で挟まれた物理アドレスにおいて、0x0e000000からのみ命令をフェッチすることが可能であることを意味している。それ以外のアドレスに関する命令フェッチにおいては、CPUに対して何の影響も及ぼさない。なお、この実行順序検査記憶装置52は、実行環境主制御手段を実行するCPUからのみ書き換えが可能である。

【0294】

図84は、図82の実行順序検査付き実行環境管理手段50の動作の一例を説明するための図である。図84において、矢印脇のSと数字からなる符合は、ステップ番号を表している。この例では、観測対象のCPUが、一番最初に、実行順序検査記憶装置52で許可された物理アドレスの先頭(以降では物理アドレスAと呼ぶ)の命令をフェッチする場合について説明する。

【0295】

ステップS1: 観測対象のCPUが物理アドレスAの命令をフェッチ要求をだし、実行順序検査手段51と実行環境管理手段50が受理する。

【0296】

ステップS2: 実行順序検査手段51は、実行順序検査記憶装置52の情報を読出し、当該物理アドレスAの命令フェッチが許可されていることを判断し、その結果、その動作を中断する。

【0297】

図85は、図82の実行順序検査付き実行環境管理手段50の動作の一例を説明するための図である。図85において、矢印脇のSと数字からなる符合は、ステップ番号を表している。この例では、図84での命令フェッチの後、観測対象のCPUが、引き続いて、実行順序検査記憶装置52で記述された範囲の物理アドレス(以降では物理アドレスBと呼ぶ)の命令をフェッチする場合について説明する。

【0298】

ステップS1: 観測対象のCPUが物理アドレスBの命令をフェッチ要求をだし、実行順序検査手段51と実行環境管理手段50が受理する。

【0299】

ステップS2: 実行順序検査手段51は、実行順序検査記憶装置52の情報を読出し、既に物理アドレスAの命令フェッチが許可されていることから、当該物理アドレスBの命令フェッチも許可されることを判断し、その結果、その動作を中断する。

【0300】

図86は、図82の実行順序検査付き実行環境管理手段50の動作の一例を説明するための図である。図86において、矢印脇のSと数字からなる符合は、ステップ番号を表している。この例では、観測対象のCPUが、一番最初に、実行順序検査記憶装置52で記述された範囲の物理アドレス(以降では物理アドレスBと呼ぶ)の命令をフェッチする場合について説明する。

【0301】

ステップS1: 観測対象のCPUが物理アドレスBの命令をフェッチ要求をだし、実行順序検査手段51と実行環境管理手段50が受理する。

【0302】

ステップS2: 実行順序検査手段51は、実行順序検査記憶装置52の情報を読出し、物理アドレスAの命令フェッチが行われていないことから、当該物理アドレスBの命令フェッチを許可しない。

【0303】

ステップS3: 実行順序検査手段51は、実行環境管理手段30へ命令フェッチを許可しないことを通知する。

【0304】

ステップS4: 実行環境管理手段30はアクセス処理を中断し、当該CPUへエラーを返す。

【0305】

図87は、図82の実行順序検査付き実行環境管理手段50の動作の一例を説明するための図である。図87において、矢印脇のSと数字からなる符合は、ステップ番号を表している。この例では、実行環境主制御手段を実行するCPUから実行順序検査記憶装置52を書き換える場合について説明する。

【0306】

ステップS1: 実行環境主制御手段を実行するCPUが実行順序検査記憶装置52を更新する。

【0307】

図88は、図82の実行順序検査付き実行環境管理手段50の動作の一例を説明するための図である。図88において、矢印脇のSと数字からなる符合は、ステップ番号を表している。この例では、実行環境主制御手段を実行するCPUから実行順序検査手段51の状態を読み出す場合について説明する。

【0308】

ステップS1: 実行環境主制御手段を実行するCPUは、実行順序検査手段51の状態を読み出す。もし該当するエントリのCPUが指定された範囲内の命令をフェッチしていれば、検査状態にあることを返し、逆に、フェッチしていなければ、検査状態にないことを返す。

【0309】

これにより、観測対象のCPUがどの範囲の命令を現在実行しているかを、実行環境主制御手段を実行するCPUから把握することができるので、実行環境主制御手段と実行環境副制御手段との同期等のシステム状態の変更の際に、ウィルスの侵入などを防ぐため、信頼できないコードの排除を実現することが可能である。

【0310】

図89は、図82の実行順序検査付き実行環境管理手段50の動作の一例を説明するための図である。図89において、矢印脇のSと数字からなる符合は、ステップ番号を表している。この例では、実行環境主制御手段を実行するCPUから実行順序検査手段51の状態をクリアする場合について説明する。

【0311】

ステップS1: 実行環境主制御手段を実行するCPUは、実行順序検査手段51の状態をクリアする。これ以降、観測対象のCPUは指定された物理アドレスの先頭からのみしか再度アクセスが許可されなくなる。

【0312】

これにより、実行環境主制御手段を実行するCPUから、任意の時点で、観測対象のCPUの動作を再び観測可能にできる。

【0313】

図90は、図82の実行順序検査付き実行環境管理手段50の動作の一例を説明するための図である。図90において、矢印脇のSと数字からなる符合は、ステップ番号を表している。この例では、実行順序検査手段51と実行環境管理手段30が協調した動作をする場合について説明する。

【0314】

ステップS1: 観測対象のCPUがある物理アドレスの命令をフェッチ要求をだし、実行順序検査手段51と実行環境管理手段50が受理する。

【0315】

ステップS2: 実行順序検査手段51は、実行順序検査記憶装置52の情報を読出し、その物理アドレスの命令フェッチを許可する。

【0316】

ステップS3: 実行環境管理手段30は、ある物理アドレスへのデータアクセスを受理する。

【0317】

実行順序検査手段51は、実行環境管理手段30へ命令フェッチを許可しないことを通知する。

【0318】

ステップS4: 実行環境管理手段30は、当該アクセスが当該CPUの検査状態によって許可・不許可が判断されるアクセスと判断し、その結果、実行順序検査手段51から現在当該アクセスを発行したCPUの検査状態について情報を取得する。

【0319】

ステップS5: 実行環境管理手段30は、当該アクセスが検査状態のCPUからアクセスが許可されていない領域と判断し、その結果、当該CPUへエラーを返す。

【0320】

ここで、当該CPUだけでなく、実行環境主制御手段を実行するCPUへもエラー通知をすることで、エラーを起こした当該CPUのリセット等のリカバリーを行ってもよい。

【0321】

以上、実行順序検査手段51と実行環境管理手段30との協調によって、データアクセスのみに依存していた安全性について、観測対象のCPUのプログラムの実行状況に応じて、そのデータアクセスを柔軟に制限することができるので、さらなる高い安全性を実現できる。

【0322】

以上好ましい実施の形態及び実施例をあげて本発明を説明したが、本発明は必ずしも、上記実施の形態及び実施例に限定されるものでなく、その技術的思想の範囲内において様々に変形して実施することができる。

【0323】

この出願は、2006年11月2日に出願された日本出願特願2006−299019号と2007年9月25日に出願された日本出願特願2007−247491号を基礎とする優先権を主張し、その開示の全てをここに取り込む。

【符号の説明】

【0324】

2:SMP OS

3、3A〜3n:OS

4、4−0〜4−n、4−k:CPU

41:ユーザ・スーパバイザ

42:ハイパーバイザ

43:記憶装置管理ユニット

5:記憶装置

51:ROM

52:RAM

521:

6:I/O装置

7:シングルOS

8:アプリケーション

10:実行環境主制御手段

11:OS主連携手段

12:実行環境主管理同期手段

13:実行環境スケジュール手段

20:実行環境副制御手段

21:OS副連携手段

22:実行環境管理同期副手段

23:同一実行環境スケジュール手段

30:実行環境管理手段

31:CPUフィルタ手段

32:CPU管理データ記憶装置

321:CPU管理データ

33:自動CPU切替手段

34:自動CPU切替データ記憶装置

341:自動CPU切替データ

35:実行環境フィルタ手段

36:実行環境管理データ記憶装置

361:実行環境管理データ

362:実行環境対応情報

37:自動実行環境切替手段

38:自動実行環境切替データ

90:コンテキスト

100、100−1〜100−n:実行環境

110:基本処理

120:追加処理

300−1〜300−n:マルチプロセッサシステム

501:CPU

502:主記憶部

503:通信制御部

504:インタフェース部

505:補助記憶部

506:システムバス

50:実行順序検査付き実行環境管理手段

51:実行順序検査手段

52:実行順序検査記憶装置

【技術分野】

【0001】

本発明は、マルチプロセッサシステムに関し、特に、セキュリティレベルを考慮して処理単位の実行環境を構築することを可能にするマルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラムに関するものである。

【背景技術】

【0002】

マルチプロセッサ上でマルチプロセッサ用のOSを動作させるマルチプロセッサシステムである、例えば、対称型マルチプロセッサ(SMP:Symmetric Multiple Processor)上で対照型マルチプロセッサOS(SMP OS)を実行するマルチプロセッサシステムにおいては、複数のCPUが互いに同等な立場でアプリケーションの処理を分担するといった構成がとられており、SMP OSの元でCPUの負荷状態に応じて実行する処理とCPUの組み合わせからなる実行環境の構成変更を行うことにより、効率的な処理を実現している。

【0003】

このようなマルチプロセッサシステムとしては、例えば、関連文献1(特開2002−278778号公報)に開示されるシステムが存在する。

【0004】

関連文献1のマルチプロセッサシステムでは、ある一定時間内に実行された全プロセス(処理)について、プロセスを特定の1個のCPUで実行すべきか否か決定し、プロセスを特定の1個のCPUで実行すべきであると決定されたプロセス数の、全プロセス数に対する割合が閾値を上回った場合、全てのプロセスについて全スレッドを特定の1個のCPUで実行すべきであると決定し、これにより、オーバーヘッドの原因である、スレッドの実行における順番の管理、各CPUが内蔵するキャッシュメモリと主記憶の同期合わせ、主記憶や入出力のための排他利用管理処理を解消するものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−278778号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した関連のマルチプロセッサシステムにおいては、以下に述べるような問題点があった。

【0007】

まず、関連文献1等に記載されるシステムでは、複数のCPUが互いに同等な立場でアプリケーションの複数の処理を分担し、CPUの負荷状態を条件として実行環境(CPUと処理の組み合わせ)の構成変更を行うだけであるので、処理毎に安定性やセキュリティレベルを変えた実行環境を構築することができないといった問題があった。

【0008】

例えば、アプリケーションの本来的な処理(基本処理)と、基本処理に伴って実行され、任意に追加又は削除される付随的な処理(追加処理)を実行する場合、基本処理を実行する実行環境と、追加処理を実行する実行環境とを安定性やセキュリティレベルを考慮して(基本処理の実行環境の安定性及びセキュリティレベルを高くして)構築するといったことが不可能であった。

【0009】

具体的には、安定性の要求度合いが異なる複数の処理を同時に実行する場合、高い安定性が要求される処理とそれ以外の処理とを異なる実行環境の下で実行するといった環境の構築ができないという不都合があった。

【0010】

なお、SMP OSを搭載するマルチプロセッサシステム以外のシステムにおいても上述した課題を同様に抱えている。

【0011】

本発明の目的は、上記課題を解決するためになされたものであり、安定性やセキュリティレベルを考慮して実行する処理内容に応じて実行環境を柔軟に構築することができるマルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラムを提案することにある。

【0012】

また、本発明の他の目的は、各処理内容に応じた実行環境の切り替え(構成変更)を高速に実現することを可能にするマルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラムを提案することにある。

【課題を解決するための手段】

【0013】

上記課題を解決するため本発明は、複数のCPUと、前記CPU上で実行される複数のOSを搭載し、前記CPUと前記OSを組み合わせた少なくとも一つの実行環境を、システム上で実行する処理に応じて形成する。

【発明の効果】

【0014】

本発明によれば、システム上で実行する処理毎に安定性やセキュリティレベルを変えた実行環境を構築することができるという効果が達成される。

【0015】

その理由は、複数のCPUと、当該CPU上で実行される複数のOSを搭載し、当該CPUと当該OSを組み合わせた少なくとも一つの実行環境を、システム上で実行する処理に応じて形成することで、処理に応じた多様な実行環境を形成することができるためのである。

【図面の簡単な説明】

【0016】

【図1】図1は、本発明のマルチプロセッサシステムの概略を説明する遷移図である。

【図2】図2は、本発明の第1の実施の形態によるマルチプロセッサシステムの構成を示すブロック図である。

【図3】図3は、本発明の特徴的な構成である実行環境主制御手段、実行環境副制御手段、実行環境管理手段の相互関係の概略を示す図である。

【図4】図4は、第1の実施の形態による記憶装置の論理アドレスを説明する図である。

【図5】図5は、第1の実施の形態によるRAM上のCPUベースの実行環境情報を説明する図である。

【図6】図6は、第1の実施の形態によるRAM上の実行環境ベースの実行環境情報を説明する図である。

【図7】図7は、第1の実施の形態によるCPUのコンテキストの構成を示す図である。

【図8】図8は、第1の実施の形態による実行環境主制御手段の構成を示すブロック図である。

【図9】図9は、第1の実施の形態による実行環境副制御手段の構成を示すブロック図である。

【図10】図10は、第1の実施の形態による実行環境主制御手段と実行環境副制御手段との接続関係を示すブロック図である。

【図11】図11は、第1の実施の形態による実行環境管理手段の構成をCPUベースで説明するブロック図である。

【図12】図12は、第1の実施の形態によるCPU管理データの構成を説明する図である。

【図13】図13は、第1の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図14】図14は、第1の実施の形態による実行環境管理手段のアクセス許可機能を説明する図である。

【図15】図15は、第1の実施の形態による実行環境管理手段のアクセス拒否機能を説明する図である。

【図16】図16は、第1の実施の形態による実行環境管理手段の構成を実行環境ベースで説明するブロック図である。

【図17】図17は、第1の実施の形態による実行環境管理データ記憶装置の実行環境対応情報を説明する図である。

【図18】図18は、第1の実施の形態による実行環境管理データの構成を説明する図である。

【図19】図19は、第1の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図20】図20は、第1の実施の形態による実行環境管理手段のアクセス許可機能を説明する図である。

【図21】図21は、第1の実施の形態による実行環境管理手段のアクセス拒否機能を説明する図である。

【図22】図22は、第2の実施の形態による切替え後のマルチプロセッサシステムの構成を示すブロック図である。

【図23】図23は、本実施の形態によるマルチプロセッサシステムのハードウェア構成を示すブロック図である。

【図24】図24は、第1の実施の形態による実行環境停止処理を共有メモリベース同期に基づいて説明する図である。

【図25】図25は、第1の実施の形態による実行環境停止処理を割込みベース同期に基づいて説明する図である。

【図26】図26は、第1の実施の形態による実行環境停止処理をバリア同期に基づいて説明する図である。

【図27】図27は、第1の実施の形態による実行環境切替え処理を共有メモリベース同期に基づいて説明する図である。

【図28】図28は、第1の実施の形態による実行環境切替え処理を割込みベース同期に基づいて説明する図である。

【図29】図29は、第1の実施の形態による実行環境切替え処理をバリア同期に基づいて説明する図である。

【図30】図30は、第1の実施の形態によるマルチプロセッサシステムのCPU4−0の動作概略を説明する図である。

【図31】図31は、第1の実施の形態によるマルチプロセッサシステムのCPU4−1〜4−nの動作概略を説明する図である。

【図32】図32は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図33】図33は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図34】図34は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図35】図35は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図36】図36は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図37】図37は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図38】図38は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図39】図39は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図40】図40は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図41】図41は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図42】図42は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図43】図43は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図44】図44は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図45】図45は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図46】図46は、第1の実施の形態によるマルチプロセッサシステムの状態の遷移を説明する図である。

【図47】図47は、第1の実施の形態による実行環境主制御手段の主実行環境内CPU停止処理(自動切換え機能無し)を説明する図である。

【図48】図48は、第1の実施の形態による実行環境主制御手段の主実行環境内CPU停止処理及びコンテキスト保存処理(自動切換え機能無し)を説明する図である。

【図49】図49は、第1の実施の形態による実行環境主制御手段の主実行環境内切替処理(自動切換え機能無し)を説明する図である。

【図50】図50は、第1の実施の形態による実行環境主制御手段の初期状態の主実行環境内のCPU追加処理(自動切換え機能無し)を説明する図である。

【図51】図51は、第1の実施の形態による実行環境主制御手段のコンテキスト設定付き主実行環境内のCPU追加処理(自動切換え機能無し)を説明する図である。

【図52】図52は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上のOS停止処理(自動切換え機能無し)を説明する図である。

【図53】図53は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上のOS停止処理及びコンテキスト保存処理(自動切換え機能無し)を説明する図である。

【図54】図54は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上の実行環境切替処理(自動切換え機能無し)を説明する図である。

【図55】図55は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の初期状態の別CPU上のOS起動処理(自動切換え機能無し)を説明する図である。

【図56】図56は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段のコンテキスト設定付き別CPU上のOS起動処理(自動切換え機能無し)を説明する図である。

【図57】図57は、第1の実施の形態による実行環境主制御手段及び実行環境副制御手段の実行環境副制御手段からの切替処理(自動切換え機能無し)を説明する図である。

【図58】図58は、第1の実施の形態による実行環境主制御手段の別CPU上の実行環境副制御手段停止処理(自動切換え機能無し)を説明する図である。

【図59】図59は、第1の実施の形態による実行環境主制御手段の別CPU上の実行環境副制御手段起動処理(自動切換え機能無し)を説明する図である。

【図60】図60は、本発明の第2の実施の形態による実行環境管理手段の構成をCPUベースで説明するブロック図である。

【図61】図61は、第2の実施の形態による自動CPU切替データの構成を説明する図である。

【図62】図62は、第2の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図63】図63は、第2の実施の形態による実行環境管理手段のリード(R)アクセスでの自動切替機能を説明する図である。

【図64】図64は、第2の実施の形態による実行環境管理手段のライト(W)アクセスでの自動切替機能を説明する図である。

【図65】図65は、第2の実施の形態による切替え後のCPU管理データの構成を説明する図である。

【図66】図66は、第2の実施の形態による実行環境管理手段の構成を実行環境ベースで説明するブロック図である。

【図67】図67は、第2の実施の形態による自動実行環境切替データの構成を説明する図である。

【図68】図68は、第2の実施の形態による実行環境管理手段のデータ更新機能を説明する図である。

【図69】図69は、第2の実施の形態による実行環境管理手段のリード(R)アクセスでの自動切替機能を説明する図である。

【図70】図70は、第2の実施の形態による実行環境管理手段のライト(W)アクセスでの自動切替機能を説明する図である。

【図71】図71は、第2の実施の形態による実行環境切替え機能(自動切換え機能有り)を説明する図である。

【図72】図72は、第2の実施の形態による実行環境主制御手段及び実行環境副制御手段の別CPU上の実行環境切替処理(自動切換え機能有り)を説明する図である。

【図73】図73は、第2の実施の形態による切替え後のマルチプロセッサシステムの構成を示すブロック図である。

【図74】図74は、本発明の第3の実施の形態による実行環境副制御手段の構成を示すブロック図である。

【図75】図75は、第3の実施の形態による実行環境副制御手段の同一信頼度実行環境切替処理(自動切換え機能無し)を説明する図である。

【図76】図76は、第3の実施の形態による実行環境主制御手段及び実行環境副制御手段の同一実行環境スケジュール手段からの切替処理(自動切換え機能無し)を説明する図である。

【図77】図77は、本発明の第4の実施の形態によるマルチプロセッサシステムの構成を示すブロック図である。

【図78】図78は、本発明の第5の実施の形態のマルチプロセッサシステムにおける一部の構成を示すブロック図である。

【図79】図79は、本発明の第5の実施の形態のマルチプロセッサシステムにおける一部の構成を示すブロック図である。

【図80】図80は、本発明の第6の実施の形態のマルチプロセッサシステムの構成を示すブロック図である。

【図81】図81は、本発明の実施例1のマルチプロセッサシステムの具体的動作例を示すフローチャートである。

【図82】図82は、本発明の一実施例による実行順序検査付き実行環境管理手段の構成を示す図である。

【図83】図83は、本発明の一実施例による実行順序検査記憶手段の構成を示す図である。

【図84】図84は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図85】図85は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図86】図86は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図87】図87は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図88】図88は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図89】図89は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【図90】図90は、本発明の一実施例による実行順序検査付き実行環境管理手段の動作を説明する図である。

【発明を実施するための形態】

【0017】

まず、図1に本発明によるマルチプロセッサシステムによる実行環境の切り替え(状態遷移)の仕組みを示す。

【0018】

図1を参照すると、本発明のマルチプロセッサシステムによれば、実行環境主制御手段10を備えるSMP OS2がCPU4−0及びCPU4−1上でアプリケーション(AP)8において基本的な処理である基本処理110を実行させる基本処理用実行環境100−0のみの状態(構成)と、実行環境主制御手段10を備えるSMP OS2がCPU4−0上で基本処理110を実行させる基本処理用実行環境100−0及び実行環境副制御手段20を備えるOS3がCPU4−1上で新たなアプリケーション8における追加処理120を実行させる追加処理用実行環境100−1からなる状態(構成)との間で、各CPUの負荷、処理の安定性やセキュリティレベルに応じて構成状態を遷移させることを可能にする。

【0019】

なお、本実施の形態において、各基本処理110は、アプリケーション8において本来的(必須)に備えられる処理であり、信頼度(セキュリティレベル)が最も高い。各追加処理120は、アプリケーション8において基本処理110に付随して又は単独で追加又は削除される処理であり、信頼度(セキュリティレベル)は基本処理に比べると低いものである。このように各追加処理は、処理内容の違い、安定性やセキュリティなどの違いによって基本処理110と区別される。なお、セキュリティレベル(信頼度)とは、処理ごとに、あるセキュリティポリシーに従って段階ごとに付与されるものをいう。

【0020】

すなわち、図1は、基本処理のみ行う基本処理用実行環境100−0を構築した構成状態(状態A)と、基本処理を行う基本処理用実行環境100−0と追加処理を行う追加処理用実行環境100−1の複数の実行環境を構築した構成状態(状態B)との間の状態遷移を示している。

【0021】

なお、図1に示す状態遷移は、本発明によるマルチプロセッサシステムによる状態遷移のあくまで一例であって図示の内容に限定されないことは言うまでもない。

【0022】

(第1の実施の形態)

本発明の第1の実施の形態を図を用いて詳細に説明する。

【0023】

(第1の実施の形態の構成)

図2は、本発明の第1の実施の形態によるマルチプロセッサシステムの構成を示すブロック図である。

【0024】

図2を参照すると、本実施の形態によるマルチプロセッサシステムは、SMP OS2と、OS3と、実行環境主制御手段10と、実行環境副制御手段20a〜20nと、CPU4−0〜4−nと、実行環境管理手段30と、記憶装置5と、I/O(In/Out:入出力)装置6とを備える。SMP OS2は実行環境主制御手段10及び実行環境副制御手段20a〜20nに接続し、OS3は実行環境副制御手段20a〜20nに接続し、実行環境主制御手段10はCPU4−0〜4−nに接続し、実行環境副制御手段20a〜20nはCPU4−1〜4−nに接続し、CPU4−0〜4−n、共有資源である記憶装置5及びI/O装置6は実行環境管理手段30に接続する。

【0025】

すなわち、本実施の形態によるマルチプロセッサシステムは、実行環境主制御手段10が各CPU4−0〜4−nを直接制御する。

【0026】

図3は、本願発明の特徴的な構成である実行環境主制御手段10、実行環境副制御手段20a〜20n、実行環境管理手段30の相互関係の概略を示す図である。

【0027】

実行環境主制御手段10は、基本処理用実行環境を実行する機能と、追加処理用実行環境を制御する機能と、CPU4と実行環境の管理情報を実行環境管理手段30に対して設定する機能と、実行環境管理情報又はコンテキスト情報(コンテキスト90)を実行環境副制御手段20との間でやりとりする機能と、実行環境管理手段30よって実行環境同士が干渉されることを防止する機能とを有する。

【0028】

具体的には、実行環境主制御手段10は、入力情報として、アプリケーションやOS3からの起動/切替通知や、タイマや割込みといったイベント通知や、実行環境副制御手段20からの切替通知を入力し、基本処理110用のSMP OS2又はOS3と共に動作し、又は、実行環境のCPU割当てを決定し、又は、実行環境の起動・停止・切替を制御し、又は、実行環境副制御手段20及び実行環境管理手段30と連携して正しい制御を保障し、場合により出力情報として、実行環境副制御手段20に対して実行環境制御情報及びコンテキスト情報(コンテキスト90)を出力する。

【0029】

例えば、実行環境主制御手段10は、CPU割当ての決定に際し、追加処理の信頼度(セキュリティレベル)や、CPUの信頼度(セキュリティレベル)や性能の違い、基本処理と追加処理の関連性や適合性等に基づいてCPU割当てを判断する。

【0030】

すなわち、実行環境主制御手段10は、AP8やOS3からの起動/切替通知として、例えば、実行環境100−1を起動してほしいとの要求を受けると該当する実行環境100−1を起動し、例えば、実行環境100−3はもう必要ないとの通知を受けると、該当する実行環境100−3を停止し、例えば、実行環境100−2におけるあるアプリケーションと通信したいとの要求を受けると、該当する実行環境100−2が動作中なら何もせず、停止中なら該当する実行環境100−2を起動する。なお、起動する場合、CPU以上の実行環境が動作することになるならば、最も動作時間の長い実行環境と切替えて実行環境100−2を起動することが望ましい。

【0031】

さらに、実行環境主制御手段10は、自発的要求として、例えば、タイマ割込みを受けた際にCPU以上の実行環境動作中の場合、停止中の実行環境のうち、実行時間の少ない実行環境(実行時間の少ない実行環境を選択するポリシは任意)へ動作中の実行環境を切替え、例えば、所定の外部割込みがきたら実行環境100−4を起動又は停止する場合、所定の外部割込みがきたら該当する実行環境100−4を起動又は停止する。なお、起動する場合、CPU以上の実行環境が動作中ならば、当該実行環境と切替えて実行環境100−4を起動することが望ましい。

【0032】

実行環境副制御手段20は、実行環境主制御手段10からの通知によって、追加処理用実行環境を制御する機能を有する。

【0033】

具体的には、実行環境副制御手段20は、入力情報として、実行環境主制御手段10からの実行環境制御情報及びコンテキスト情報(コンテキスト90)を入力し、実行環境主制御手段10の指示に従って、実行環境の起動・停止・切替を制御し、実行環境主制御手段10との同期をとる。実行環境主制御手段10との同期をとることによって切替前後の実行環境の分離が可能となる。また、実行環境副制御手段20は、場合により出力情報として、実行環境主制御手段10に対してエラー情報を出力する。

【0034】

実行環境管理手段30は、実行環境主制御手段10と実行環境副制御手段20a〜20n又は、実行環境副制御手段20a〜20nをそれぞれ分離する機能を有する。具体的には、実行環境管理手段30は、入力情報として、CPU4又は実行環境毎の共有資源(記憶装置5、I/O装置6)の管理情報や参照拒否情報を入力し、入力情報に基づいて各CPUからの参照に対し、何もしないか、又は拒絶してエラー情報を返す。

【0035】

共有資源は、各処理ごとに、例えばアドレスに従って割り当てられており、基本処理110用領域、追加処理120用実行環境100用領域、共有領域、実行環境情報領域ごとに予め決められたアドレスを有していてもよい。図4は、共有資源である記憶装置の論理アドレスを説明する図である。

【0036】

図4を参照すると、記憶装置5のROM51は、アドレス0x00000000〜0x007FFFFFの基本処理110用領域と、アドレス0x00800000〜0x00FFFFFFの追加処理用実行環境100−1用領域と、アドレス0x01000000〜0x017FFFFFの追加処理120用実行環境100−2用領域と、アドレス0x01800000〜0x02000000の追加処理120用実行環境100−3用領域とを有し、また、記憶装置5のRAM52は、アドレス0x30000000〜0x30FFFFFFの基本処理110用領域と、アドレス0x31000000〜0x31FFFFFFの追加処理120用実行環境100−1用領域と、アドレス0x32000000〜0x32FFFFFFの追加処理120用実行環境100−2用領域と、アドレス0x33000000〜0x33FFFFFFの追加処理120用実行環境100−3用領域と、アドレス0x34000000〜0x34FFFFFFの共有領域と、アドレス0x35000000〜0x36000000の実行環境情報領域とを有する。

【0037】

図5及び図6は、RAM上の実行環境情報を説明する図である。

【0038】

図5は、RAM上のCPUベースの実行環境情報を説明する図であり、図5(a)〜図5(d)を参照すると、CPUベースの実行環境情報は、各実行環境100−0〜100−3を構成するCPU用のコンテキスト及びCPU管理データによって実行環境毎の動作状態を格納する。

【0039】

図6は、RAM上の実行環境ベースの実行環境情報を説明する図であり、図6(a)〜図6(d)を参照すると、実行環境ベースの実行環境情報は、各実行環境100−0〜100−3を構成するCPU用のコンテキスト及び各実行環境用の実行環境情報によって実行環境毎の動作状態を格納する。

【0040】

図7は、CPU4−kのコンテキストの構成を示す図である。図7を参照すると、CPU4−kのコンテキスト90は、レジスタ#0〜レジスタ#14、レジスタ#15(PC)、プロセッサ状態レジスタ及びプロセッサ制御レジスタを備え、例えば、動作中のCPU4−kのある指定された瞬間の記憶状態の全てが格納されている。

【0041】

ここで、本実施の形態による実行環境主制御手段10及び実行環境副制御手段20の構成を図を用いてさらに詳細に説明する。

【0042】

図8は、本実施の形態による実行環境主制御手段10の構成を示すブロック図である。

【0043】

図8を参照すると、本実施の形態による実行環境主制御手段10は、AP8/OS3及びRAMに接続する実行環境スケジュール手段13と、OS3、OS副連携手段21(後述)及び実行環境スケジュール手段13に接続するOS主連携手段11と、OS副連携手段21、実行環境副管理同期手段22、実行環境管理手段30及び実行環境スケジュール手段13に接続する実行環境主管理同期手段12とを備える。

【0044】

実行環境スケジュール手段13は、入力情報として、例えば、AP8/OS3から何らかの要求を受けると、RAM52上の実行環境情報を参照し、参照した実行環境情報に基づいて、OS主連携手段11に対し、実行環境スケジュール手段13自身が属する実行環境・そのCPU・そのOSの起動・停止・追加・切り替え等の制御命令や、実行環境スケジュール手段13自身が属さない実行環境・そのCPU・そのOSの起動・停止・追加・切り替え等の制御命令を通知する機能と、OS主連携手段11に対し、次に切り替わるべきコンテキストや前回のコンテキストの情報を通知する機能と、実行環境主管理同期手段12に対し、当該制御命令によってCPUなどが追加等された後の実行環境スケジュール手段13の設定情報を通知する機能と、RAM52上の実行環境情報を更新する機能等を有する。

【0045】

OS主連携手段11は、実行環境スケジュール手段13から受けた制御命令を実行する機能及び当該制御命令をOS副連携手段21(後述)に通知する機能と、OS3対して前回のコンテキストや切り替え先のコンテキストの情報を設定する機能と、動作中のOS3のコンテキストを取得して実行環境スケジュール手段13に対して渡す機能と、OS副連携手段21(後述)から受けた制御命令を実行する機能等を有する。

【0046】

実行環境主管理同期手段12は、実行環境スケジュール手段13が通知された設定情報を実行環境スケジュール手段13に対して設定する機能と、当該設定が終了したことを実行環境スケジュール手段13やOS主連携手段11に対して通知する機能と、実行環境副管理同期手段22(後述)との間で処理の同期をとる機能等を有する。

【0047】

図9は、本実施の形態による実行環境副制御手段20の構成を示すブロック図である。

【0048】

図9を参照すると、本実施の形態による実行環境副制御手段20は、OS3及びOS主連携手段11に接続するOS副連携手段21と、実行環境主管理同期手段12及びOS副連携手段21に接続する実行環境副管理同期手段22とを備える。

【0049】

OS副連携手段21は、OS主連携手段11から受けた制御命令を実行する機能と、命令が実行されたことを実行環境副管理同期手段22に通知する機能と、OS副連携手段21自身が属する実行環境のOSのコンテキストの情報を取得してOS主連携手段11に対して送付する機能と、OS主連携手段11から送付された前回のコンテキストや切り替え先のコンテキストの情報をOS副連携手段21自身が属する実行環境のOS3に対して設定する機能と、入力情報として、例えば、OS副連携手段21自身が属する実行環境のOS3から受けた何らかの要求をOS主連携手段11に対して通知する機能等を有する。

【0050】

実行環境副管理同期手段22は、命令が実行されたことをOS副連携手段21から通知されると、当該命令が実行されたことを実行環境主管理同期手段11に通知する等によって、実行環境主管理同期手段11との間で処理の同期をとる機能等を有する。

【0051】

図10は、本発明の第1の実施の形態による実行環境主制御手段10と実行環境副制御手段20との接続関係を示すブロック図である。

【0052】

ここで、本実施の形態による実行環境管理手段30の構成を、(a)CPUベース、(b)実行環境ベースによってさらに詳細に説明する。

【0053】

((a)CPUベースの場合)

図11〜図15は、本実施の形態による実行環境管理手段30の構成をCPUベースで説明する図である。

【0054】

図11は、本実施の形態による実行環境管理手段30の構成をCPUベースで説明するブロック図である。図11を参照すると、実行環境管理手段30は、システムバス及び周辺バスに接続するCPUフィルタ手段31と、システムバス及びCPUフィルタ手段31に接続するCPU管理データ記憶装置32とを備える。

【0055】

CPUフィルタ手段31は、システムバスを介してあるCPU4からのアクセス要求を受けると、CPU管理データ記憶装置32から読み出したCPU管理データ321(後述)に基づいて、当該アクセス要求の拒否を判定する機能を有する。

【0056】

CPU管理データ記憶装置32は、CPU管理データ321を格納し、CPU管理データ321の更新要求を実行する機能を有する。

【0057】

図12は、本実施の形態によるCPU管理データ321の構成を説明する図である。図12を参照すると、CPU管理データ321は、CPU4−0〜4−4毎に、割当てられた記憶装置5領域の始点・終点と、リード処理(R)及びライト処理(W)のうち許可される処理を示す許可ビットとが記載されたエントリによって構成されている。

次いで、本実施の形態のCPUベースにおける実行環境管理手段30の機能を説明する。

【0058】

(データ更新機能)

図13は、本実施の形態による実行環境管理手段30のデータ更新機能を説明する図である。図13を参照すると、実行環境管理手段30のデータ更新機能は、ステップS1において、CPU管理データ321を更新する。なお、基本的には、基本処理実行中のCPUのみがCPU管理データ321に触ることができる。ただし、所定のエントリに関しては、追加処理実行中のCPUがCPU管理データ321に触ってもよい。

【0059】

(アクセス許可機能)

図14は、本実施の形態による実行環境管理手段30のアクセス許可機能を説明する図である。図14を参照すると、実行環境管理手段30のアクセス許可機能は、CPUフィルタ手段31が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、CPU管理データ321を読み出し、ステップS3において、前記読み出したCPU管理データ321に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを許可する。

【0060】

(アクセス拒否機能)

図15は、本実施の形態による実行環境管理手段30のアクセス拒否機能を説明する図である。図15を参照すると、実行環境管理手段30のアクセス拒否機能は、CPUフィルタ手段31が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、CPU管理データ321を読み出し、ステップS3において、前記読み出したCPU管理データ321に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを拒否する。タイミング制約が厳しい場合には、この回路で拒否するのではなく、あえてアクセスアドレスをシステムに存在しないアドレスに変換して、そして、別の回路でそのような拒否をさせてもよい。

【0061】

((b)実行環境ベースの場合)

図16〜図21は、本実施の形態による実行環境管理手段30の構成を実行環境ベースで説明する図である。

図16は、本実施の形態による実行環境管理手段30の構成を実行環境ベースで説明するブロック図である。図16を参照すると、実行環境管理手段30は、システムバス及び周辺バスに接続する実行環境フィルタ手段35と、システムバス及び実行環境フィルタ手段35に接続する実行環境管理データ記憶装置36とを備える。

【0062】

実行環境フィルタ手段35は、システムバスを介してあるCPU4からのアクセス要求を受けると、実行環境管理データ記憶装置36から読み出した実行環境管理データ361及び実行環境対応情報362(後述)に基づいて、当該アクセス要求の拒否を判定する機能を有する。

【0063】

実行環境管理データ記憶装置36は、実行環境管理データ361及び実行環境対応情報362を格納し、実行環境管理データ361及び実行環境対応情報362の更新要求を実行する機能を有する。

【0064】

図17は、本実施の形態による実行環境管理データ記憶装置36の実行環境対応情報362を説明する図である。図17を参照すると、実行環境対応情報362は、CPU4−0〜4−4毎に、実行環境番号で示される実行環境100−0〜100−4が対応付けられている。より詳細には、CPU4−0、4−1に実行環境100−0が対応付けられ、CPU4−2に実行環境100−1が対応付けられ、CPU4−3に実行環境100−2が対応付けられ、CPU4−3に実行環境100−3が対応付けられている。

【0065】

図18は、本実施の形態による実行環境管理データ361の構成を説明する図である。図18を参照すると、実行環境管理データ361は、実行環境番号を示す実行環境100−0〜100−4毎に、割当てられた記憶装置5領域の始点・終点と、リード処理(R)及びライト処理(W)のうち許可される処理を示す許可ビットとが記載されたエントリによって構成されている。

【0066】

次いで、本実施の形態の実行環境ベースにおける実行環境管理手段30の機能を説明する。

【0067】

(データ更新機能)

図19は、本実施の形態による実行環境管理手段30のデータ更新機能を説明する図である。図19を参照すると、実行環境管理手段30のデータ更新機能は、ステップS1において、実行環境管理データ361を更新する。なお、基本的には、基本処理実行中のCPUのみが実行環境管理データ361に触れる。ただし、所定のエントリに関しては、追加処理実行中のCPU4が実行環境管理データ361に触ってもよい。

【0068】

(アクセス許可機能)

図20は、本実施の形態による実行環境管理手段30のアクセス許可機能を説明する図である。図20を参照すると、実行環境管理手段30のアクセス許可機能は、実行環境フィルタ手段35が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、実行環境管理データ361を読み出し、ステップS3において、前記読み出した実行環境管理データ361に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを許可する。

【0069】

(アクセス拒否機能)

図21は、本実施の形態による実行環境管理手段30のアクセス拒否機能を説明する図である。図21を参照すると、実行環境管理手段30のアクセス拒否機能は、実行環境フィルタ手段35が、ステップS1において、任意のCPUからのアクセスを受理し、ステップS2において、実行環境管理データ361を読み出し、ステップS3において、前記読み出した実行環境管理データ361に基づいて、当該受理したアクセスの許否を判定し、当該受理したアクセスを拒否する。タイミング制約が厳しい場合には、この回路で拒否するのではなく、あえてアクセスアドレスをシステムに存在しないアドレスに変換して、そして、別の回路でそのような拒否をさせてもよい。

【0070】

本実施の形態のCPUベース又は実行環境ベースによる切り替え後のマルチプロセッサシステムの構成を図22に示す。

【0071】

ここで、マルチプロセッサシステムのハードウェア構成の説明をする。

【0072】

図23は、本実施の形態によるマルチプロセッサシステムのハードウェア構成を示すブロック図である。

【0073】

図23を参照すると、本発明によるマルチプロセッサシステムは、一般的なコンピュータ装置と同様のハードウェア構成によって実現することができ、CPU(Central Processing Unit)501、RAM(Random Access Memory)等のメインメモリであり、データの作業領域やデータの一時退避領域に用いられる主記憶部502、インターネット等を介してデータの送受信を行う通信制御部503、周辺機器と接続してデータの送受信を行うインタフェース部504、ROM(Read Only Memory)、磁気ディスク、半導体メモリ等の不揮発性メモリから構成されるハードディスク装置である補助記憶部505、本情報処理装置の上記各構成要素を相互に接続するシステムバス506等を備えている。

【0074】

本発明によるマルチプロセッサシステムは、その動作を、マルチプロセッサシステム内部にそのような機能を実現するプログラムを組み込んだ、LSI(Large Scale Integration)等のハードウェア部品からなる回路部品を実装してハードウェア的に実現することは勿論として、上記した各構成要素の各機能を提供するプログラムを、コンピュータ処理装置上のCPU501で実行することにより、ソフトウェア的に実現することができる。

【0075】

すなわち、CPU501(CPU4、CPU4−0〜4−n、CPU4−k)は、補助記憶部505(記憶装置5)に格納されているプログラムを、主記憶部501(記憶装置5)にロードして実行し、マルチプロセッサシステムの動作を制御することにより、上述した各機能をソフトウェア的に実現する。

【0076】

(第1の実施の形態の動作)

図24〜図59は、本発明の第1の実施の形態によるマルチプロセッサシステムの動作を説明する図である。

【0077】

まず、本実施の形態による実行環境停止処理及び実行環境切替え処理を、(a)共有メモリベース同期、(b)割込みベース同期、(c)バリア同期に基づいて詳細に説明する。

【0078】

(実行環境停止処理)

実行停止処理は、実行環境副管理同期手段22が属する実行環境を停止する処理である。

【0079】

((a)共有メモリベース同期)

図24は、本実施の形態による実行環境停止処理を共有メモリベース同期に基づいて説明する図である。

【0080】

図24を参照すると、実行環境副管理同期手段22が共有メモリである記憶装置5にある値(例えば“A”)を書く(ステップS101)。実行環境主管理同期手段12は、実行環境副管理同期手段22によって共有メモリに値が書かれると、共有メモリの値が“A”であるか否かを判定し(ステップS102)、共有メモリの値が“A”である場合に実行環境管理手段30を設定して(ステップS105)処理を継続し(ステップS106)、実行環境副管理同期手段22が属する実行環境が停止する(ステップS107)。実行環境主管理同期手段12は、共有メモリの値が“A”でない場合において、共有メモリの値が“A”でない場合が閾値回数以上判定されたときに(ステップS103)相手を強制的にリセットし(ステップS104)、閾値回数に達しないときに(ステップS103)共有メモリの値が“A”であるか否かを再度判定する(ステップS102)。なお、実行環境副管理同期手段22がループしていてもよい。

【0081】

((b)割込みベース同期)

図25は、本実施の形態による実行環境停止処理を割込みベース同期に基づいて説明する図である。

【0082】

図25を参照すると、実行環境副管理同期手段22が割込み要求を送信すると(ステップS201)、実行環境主管理同期手段12は、割込み要求の受信の有無を判定し(ステップS202)、割込み要求を受信した場合に実行環境管理手段30を設定して(ステップS205)処理を継続し(ステップS206)、実行環境副管理同期手段22が属する実行環境が停止する(ステップS207)。実行環境主管理同期手段12は、割込み要求を受信していない場合において、受信していない状態が閾値時間以上経過したときに(ステップS203)相手を強制的にリセットし(ステップS204)、閾値時間に達しないときに(ステップS203)割込み要求の受信の有無を再度判定する(ステップS202)。なお、実行環境副管理同期手段22がループしていてもよい。

【0083】

((c)バリア同期)

図26は、本実施の形態による実行環境停止処理をバリア同期に基づいて説明する図である。

【0084】

図26を参照すると、実行環境副管理同期手段22は、実行環境主管理同期手段12とバリア同期を行い(ステップS301)、バリア同期が達成されたか否かを判定し(ステップS302)、達成されていなければ再度判定し、達成されていれば実行環境を停止する(ステップS303)。実行環境主管理同期手段12は、実行環境副管理同期手段22とバリア同期を行い(ステップS311)、バリア同期が達成されたか否かを判定し(ステップS312)、達成されていれば実行環境管理手段30を設定し(ステップS313)、処理を継続する(ステップS314)。実行環境副管理同期手段22は、達成されていなければ、達成されていない状態が閾値時間以上経過しているか否かを判定し(ステップS315)、閾値時間以上経過しているときに相手を強制的にリセットし(ステップS316)、閾値時間に達しないときはバリア同期が達成されたか否かを再度判定する(ステップS312)。

【0085】

(実行環境切替え処理)

実行環境切替え処理は、実行環境主制御手段10または実行環境副制御手段20が属する実行環境を切り替える処理である。

【0086】

((a)共有メモリベース同期)

図27は、本実施の形態による実行環境切替え処理を共有メモリベース同期に基づいて説明する図である。

【0087】

図27を参照すると、実行環境副管理同期手段22が共有メモリにある値(例えば“A”)を書く(ステップS401)。実行環境主管理同期手段12は、実行環境副管理同期手段22によって共有メモリに値が書かれると、共有メモリの値が“A”であるか否かを判定し(ステップS402)、共有メモリの値が“A”でない場合において、共有メモリの値が“A”でない場合が閾値回数以上判定されたときに(ステップS403)相手を強制的にリセットし(ステップS404)、閾値回数に達しないときに共有メモリの値が“A”であるか否かを再度判定し(ステップS402)、共有メモリの値が“A”である場合に実行環境管理手段30を設定し(ステップS405)、共有メモリにある値(例えば“B”)を書いて(ステップS406)処理を継続する(ステップS407)。実行環境副管理同期手段22は、実行環境主管理同期手段12によって共有メモリに値が書かれると、共有メモリの値が“B”であるか否かを判定し(ステップS408)、共有メモリの値が“B”でない場合に共有メモリの値が“B”であるか否かを再度判定し(ステップS408)、共有メモリの値が“B”である場合に実行環境を切り替える(ステップS409)。なお、実行環境副管理同期手段22が先にループしていてもよい。

【0088】

((b)割込みベース同期)

図28は、本実施の形態による実行環境切替え処理を割込みベース同期に基づいて説明する図である。

【0089】

図28を参照すると、実行環境副管理同期手段22が割込み要求を送信すると(ステップS501)、実行環境主管理同期手段12は、割込み要求の受信の有無を判定し(ステップS502)、割込み要求を受信していない場合において、閾値時間以上のときに(ステップS503)相手を強制的にリセットし(ステップS504)、閾値時間に達しないときに割込み要求の受信の有無を再度判定し(ステップS502)、割込み要求を受信した場合に実行環境管理手段30を設定して(ステップS505)割込み要求を送信して(ステップS506)処理を継続する(ステップS507)。実行環境副管理同期手段22は、割込み要求の受信の有無を判定し(ステップS508)、割込み要求を受信していない場合に割込み要求の受信の有無を再度判定し(ステップS508)、割込み要求を受信した場合に実行環境を切り替える(ステップS509)。なお、実行環境副管理同期手段22が先にループしていてもよい。

【0090】

((c)バリア同期)

図29は、本実施の形態による実行環境切替え処理をバリア同期に基づいて説明する図である。

【0091】