マルチプロセッサシステム及びその動作方法

【課題】マルチプロセッサシステムにおいて、コヒーレンシの保障と処理速度の向上を両立させる。

【解決手段】複数のセルC1〜Cnは、リクエストセルCRと、ホームセルCHと、オーナーセルCOとを含む。ホームセルCHのメインメモリ5に記憶された対象データの最新版は、オーナーセルCOのキャッシュメモリ7に格納されている。リクエストセルCRは、その対象データに対するリードリクエストをホームセルCHに発行する。ホームセルCHは、そのリードリクエストに応答して、スヌープリクエストをオーナーセルCOに発行する。オーナーセルCOは、そのスヌープリクエストに応答して最新データをリクエストセルCRに直接送信する。ホームセルCHは、オーナーセルCOからのリプライライトバックをリクエストセルCRからのリクエストライトバックよりも後に受信した場合、そのリプライライトバックを破棄する。

【解決手段】複数のセルC1〜Cnは、リクエストセルCRと、ホームセルCHと、オーナーセルCOとを含む。ホームセルCHのメインメモリ5に記憶された対象データの最新版は、オーナーセルCOのキャッシュメモリ7に格納されている。リクエストセルCRは、その対象データに対するリードリクエストをホームセルCHに発行する。ホームセルCHは、そのリードリクエストに応答して、スヌープリクエストをオーナーセルCOに発行する。オーナーセルCOは、そのスヌープリクエストに応答して最新データをリクエストセルCRに直接送信する。ホームセルCHは、オーナーセルCOからのリプライライトバックをリクエストセルCRからのリクエストライトバックよりも後に受信した場合、そのリプライライトバックを破棄する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のセルにより構成される分散共有メモリ型のマルチプロセッサシステムに関する。特に、本発明は、複数のセルを備える分散共有メモリ型マルチプロセッサシステムにおけるコヒーレンシ技術に関する。

【背景技術】

【0002】

コンピュータシステムの分野において、多数のプロセッサによって構成される「マルチプロセッサシステム(Multiprocessor System)」が従来知られている。マルチプロセッサシステムの中でも、複数のセル(あるいは複数のノード)によって構成され、その複数のセル間がバスやスイッチにより結合されたものが知られている。複数のセルはそれぞれ独立にプロセッサとメインメモリを有し、全てのメインメモリによって論理的に「共有メモリ」が構成される(例えば、特許文献1、特許文献2、特許文献3、特許文献4、及び特許文献5を参照)。メモリが分散的に配置され、且つ複数のプロセッサにより共有されるため、そのようなマルチプロセッサシステムは、「分散共有メモリ型(DSM: Distributed Shared Memory)マルチプロセッサシステム」や「分散共有メモリ型アーキテクチャ」と呼ばれることもある。

【0003】

図1は、分散共有メモリ型マルチプロセッサシステム1の構成を示すブロック図である。図1に示されたマルチプロセッサシステム1は、複数のセルC1〜Cn(nはセル数を示す整数)と、それら複数のセルC1〜Cn間を互いに結合するクロスバースイッチ9から構成されている。複数のセルC1〜Cnは同一の機能を有している。各々のセルCj(jは1以上n以下の整数)は、少なくとも1つのCPU(マイクロプロセッサ)2−j−1〜2−j−m(mは各セル内のCPU数を示す整数)と、メインメモリ(ローカルメモリ)5−jを備えている。それらCPU2の各々は、少なくとも1つのキャッシュメモリ(ストアインキャッシュ)7を搭載している。分散的に設けられたメインメモリ5−1〜5−nの全てによって共有メモリが構成され、その共有メモリは全てのCPU2によって参照される。

【0004】

このような分散共有メモリ型マルチプロセッサシステム1においては、CPU2のそれぞれがキャッシュ7を駆使しながら、メインメモリ5−1〜5−nに格納されたデータにアクセスし、またその更新を行う。データ更新にライトバック(Write Back)方式が用いられる場合、更新されたデータがキャッシュ7に滞留し、メインメモリ5−jには最新のデータが存在しない可能性もある。この時、複数のCPU2が同一の記憶領域を参照/更新しようとすると、データの不整合により正しい結果が得られなくなる。従って、マルチプロセッサシステムにおいては、各CPU2が最新のデータにアクセスできるように、データの一貫性(「キャッシュコヒーレンシ:Cache Coherency」と参照される)を保障ことが重要である。ここで、各セルCj内のキャッシュ7間のコヒーレンシを保つだけでなく、複数のセルC1〜Cn間のコヒーレンシも保つ必要があることに留意されるべきである。

【0005】

キャッシュコヒーレンシの方式としては、「ディレクトリ方式(Directory-based Cache Coherency Protocol)」と「スヌープ方式(Snooping Cache Coherency Protocol)」が知られている。

【0006】

ディレクトリ方式によれば、メインメモリに格納されたデータに関するキャッシングの状態を管理するテーブル(ディレクトリ)が設けられる。あるCPUがあるデータにアクセスする際、まず、そのディレクトリに格納されたキャッシング状態に関する情報が調べられる。所望の最新データがメインメモリではなく、あるキャッシュにのみ存在することが判明した場合、CPUはそのキャッシュに対してそのデータのアクセスを行う。

【0007】

一方、スヌープ方式によれば、あるCPUがあるアクセスアドレスのデータにアクセスする際、全てのキャッシュは、そのアクセスアドレスのデータのコピーを保有しているか否かを調べる。そして、各キャッシュは、必要なときに最新のデータを取得できるように自身の状態(キャッシュステータス)を変更する。例えば、MESIプロトコルによれば、「I(Invalid;無効)」、「S(Shared;最新データがメインメモリと複数のキャッシュに存在する)」、「E(Exclusive;最新データがメインメモリと自キャッシュに存在する)」、「M(Modified);最新データが自キャッシュにのみ存在する」の4つのキャッシュステータスが提供される。

【0008】

図1に示されたセルC1〜Cnのそれぞれには、上述のキャッシュコヒーレンシを実現するために、キャッシュコヒーレンシ回路3−1〜3−n及びディレクトリ4−1〜4−nが設けられている。ディレクトリ4−jは、DRAM等により実現される記憶領域であり、その中には、自セルCjのメインメモリ5−jに格納されたデータに関するキャッシングの状態を管理するための情報が格納される。より具体的には、ディレクトリ4−jには、自セルCjのメインメモリ5−jに格納されたデータに関して最新データをキャッシングしているセルを示すテーブルが格納される。最新データをキャッシングしているセルは、自セルである場合もあるし、他のセルである場合もある。キャッシュコヒーレンシ回路3は、ディレクトリ4を参照することにより、セルC1〜Cn間のコヒーレンシを保障するように構成されている。尚、各セル内のキャッシュコヒーレンシは、例えばスヌープ方式により実現される。

【0009】

【特許文献1】特開2000−67024号公報

【特許文献2】特開2000−259596号公報

【特許文献3】特開平6−110844号公報

【特許文献4】特開平11−219343号公報

【特許文献5】特開2003−216597号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

あるデータに対するリードリクエストを発行する発行元であるCPU2を搭載するセルは、以下「リクエストセルCR」と参照される。そのアクセス対象であるデータが格納されたメインメモリ5を搭載するセルは、以下「ホームセルCH」と参照される。また、そのアクセス対象であるデータの最新版(最新データ)をキャッシングしているキャッシュ7を有するセルは、以下「オーナーセルCO」と参照される。本願発明者は、ディレクトリ4を用いるマルチプロセッサシステム1において、それらリクエストセルCR、ホームセルCH、及びオーナーセルCOがそれぞれ異なる状態が発生することに着目した。

【0011】

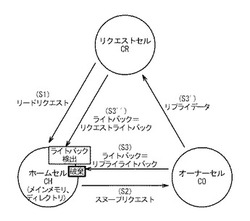

そのような状態における従来のマルチプロセッサシステムの動作例を、図2を参照して説明する。まず、リクエストセルCRのCPU2は、アクセス対象データが格納されたメインメモリ5を有するホームセルCHに、リードリクエストを発行する(ステップS1)。ホームセルCHは、リードリクエストに応答して、自身のディレクトリ4を検索(索引)する。ディレクトリ4に格納された情報より、ホームセルCHは、対象データの最新版がオーナーセルCOのキャッシュ7に格納されていることを知る。そこで、ホームセルCHは、オーナーセルCOにスヌープリクエストを発行する(ステップS2)。

【0012】

オーナーセルCOは、スヌープリクエストに応答して、キャッシュ7から最新データを読み出す。そして、オーナーセルCOは、その最新データをホームセルCHのメインメモリ5に書き戻すために、ホームセルCHに対してライトバックを発行する(ステップS3)。オーナーセルCOがスヌープリクエストに応答して発行するライトバックは、以下、「リプライライトバック」と参照される。このリプライライトバックと同時に、オーナーセルCOは、読み出された最新データをリプライデータとしてリクエストセルCRに直接送信する(ステップS3’)。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOP(ステップS1,S2,S3’)で実現することができる(セル間のレイテンシを1HOPとする)。

【0013】

リードリクエストを発行したリクエストセルCRのCPU2は、受け取ったリプライデータを自身のキャッシュ7に格納する。その後、そのキャッシュ7のリプライデータがリプレースされた場合などにおいて、リクエストセルCRからホームセルCHに対するライトバックが発生する可能性がある(ステップS3’’)。CPU2がキャッシュ7のリプレース等により発行するライトバックは、以下、「リクエストライトバック」と参照される。ここで、上記リプライライトバック(ステップS3)とリクエストライトバック(ステップS3’’)は異なるパスで行われるため、それらの順序は必ずしも一意に定まらない。もし、ステップS3がステップS3’’よりも“後に”行われると、ホームセルCHのメインメモリ5において、リクエストセルCRによって更新された最新のデータが、オーナーセルCOからの古いデータによって上書きされてしまう。すなわち、ステップS3とステップS3’’が異なる場合、コヒーレンシを必ずしも保障できなくなるという問題がある。

【0014】

このような問題を解決するための動作例を、図3を参照して説明する。まず、リクエストセルCRがホームセルCHにリードリクエストを発行する(ステップS1)。次に、ホームセルCHがオーナーセルCOにスヌープリクエストを発行する(ステップS2)。スヌープリクエストに応答して、オーナーセルCOは、キャッシュ7から最新データを読み出し、ホームセルCHに対してリプライライトバックを発行する(ステップS3)。ここで、オーナーセルCOは、リクエストセルCRに対して最新データを直接は送信しない。次に、ホームセルCHは、リプライライトバックに応答して、最新データで自身のメインメモリ5を更新する。その後、ホームセルCHは、その最新データをリプライデータとしてリクエストセルCRに送信する(ステップS4)。

【0015】

このような処理によって、図2に示されたステップS3とステップS3’’の関係の発生が防止され、セル間のコヒーレンシを保障することが可能となる。しかしながら、図3に示された処理の場合、リードリクエストの発行からリプライデータの受け取りまでのレイテンシは4HOP(ステップS1,S2,S3,S4)となってしまう。このことは、処理速度の低下を意味する。本来、マルチプロセッサシステムにおいて複数のプロセッサが用いられるのは、処理速度を向上させるためであり、上述のような処理速度の低下は重要な問題である。

【0016】

従って、本発明の目的は、コヒーレンシの保障と処理速度の向上を両立させることである。すなわち、本発明の目的は、セル間のコヒーレンシを保障しつつ、リードリクエストに関するレイテンシを3HOP以内に抑えることができる技術を提供することにある。

【課題を解決するための手段】

【0017】

以下に、[発明を実施するための最良の形態]で使用される番号・符号を用いて、[課題を解決するための手段]を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0018】

本発明に係るマルチプロセッサシステム(1)は、同一の機能を有する複数のセル(C1〜Cn)と、それら複数のセル(C1〜Cn)間を接続するネットワーク(9)とを備える。各セル(Cj)は、プロセッサ(2)、ディレクトリ(4)、キャッシュメモリ(7)、及びメインメモリ(5)を備える。複数のセル(C1〜Cn)は、リクエストセル(CR)と、ホームセル(CH)と、オーナーセル(CO)とを含む。ホームセル(CH)のメインメモリ(5)に記憶された対象データの最新版は、オーナーセル(CO)のキャッシュメモリ(7)に格納されている。

【0019】

リクエストセル(CR)は、その対象データに対するリードリクエストをホームセル(CH)に発行する。ホームセル(CH)は、そのリードリクエストに応答して、スヌープリクエストをオーナーセル(CO)に発行する。オーナーセル(CO)は、そのスヌープリクエストに応答して、最新データをリクエストセル(CR)に直接送信する。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。

【0020】

また、オーナーセル(CO)は、スヌープリクエストに応答して、リプライライトバックをホームセル(CH)に送信する。リクエストセル(CR)は、ホームセル(CH)中の上記対象データと同じアドレスに対してリクエストライトバックを発行する。そのリクエストライトバックは、リクエストセル(CR)に含まれるキャッシュ(7)のステータスとホームセル(CH)のディレクトリ(4)のステータスとを整合させるためのディレクトリ更新情報を含む。ホームセル(CH)は、オーナーセル(CO)からのリプライライトバックをリクエストセル(CR)からのリクエストライトバックよりも後に受信した場合、そのリプライライトバックを破棄し、また、ディレクトリ更新情報に基づいてディレクトリ(4)のステータスを更新する。

【0021】

このような構成により、リクエストセル(CR)からのリクエストライトバックによって更新されたデータが、オーナーセル(CO)からのリプライライトバックによる古いデータで上書きされることが防止される。従って、リクエストライトバックとリプライライトバックの経路が異なっていても、コヒーレンシを保障することが可能となる。言い換えれば、オーナーセル(CO)がリプライデータを直接リクエストセル(CR)に送信しても、セル間のコヒーレンシが保たれる。

【発明の効果】

【0022】

本発明に係るマルチプロセッサシステムによれば、リクエストセルCR、ホームセルCH、及びオーナーセルCOがそれぞれ異なる場合においても、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPにすることが可能である。且つ、セル間のコヒーレンシを保障することも可能である。すなわち、コヒーレンシの保障とレイテンシの短縮(処理速度の向上)との両立が実現される。

【発明を実施するための最良の形態】

【0023】

添付図面を参照して、本発明の実施の形態に係るマルチプロセッサシステムを説明する。

【0024】

1.概念

図4を参照して、本実施の形態に係るマルチプロセッサシステムの動作を説明する。図4において、リクエストセルCRは、リードリクエストを発行する発行元であるCPUを搭載している。ホームセルCHは、そのアクセス対象であるデータが格納されたメインメモリを有している。オーナーセルCOは、そのアクセス対象であるデータの最新版(最新データ)をキャッシングしているキャッシュを有している。ここでは、リクエストセルCR、ホームセルCH、及びオーナーセルCOがそれぞれ異なる場合を考える。

【0025】

まず、リクエストセルCRのCPUは、アクセス対象データを有するホームセルCHに、リードリクエストを発行する(ステップS1)。ホームセルCHは、リードリクエストに応答して、自身のディレクトリを検索(索引)する。ディレクトリに格納された情報により、ホームセルCHは、対象データの最新版がオーナーセルCOのキャッシュに格納されていることを知る。よって、ホームセルCHは、オーナーセルCOにスヌープリクエストを発行する(ステップS2)。

【0026】

オーナーセルCOは、スヌープリクエストに応答して、キャッシュから最新データを読み出す。そして、オーナーセルCOは、その最新データをホームセルCHのメインメモリに書き戻すために、ホームセルCHに対してリプライライトバックを発行する(ステップS3)。このリプライライトバックと同時に、オーナーセルCOは、読み出された最新データをリプライデータとしてリクエストセルCRに直接送信する(ステップS3’)。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOP(ステップS1,S2,S3’)で実現することができる。

【0027】

リードリクエストを発行したリクエストセルCRのCPUは、受け取ったリプライデータを自身のキャッシュに格納する。その後、そのキャッシュのデータがリプレースされた場合などにおいて、リクエストセルCRは、ホームセルCHに対してリクエストライトバックを発行する(ステップS3’’)。ここで、上記リプライライトバック(ステップS3)とリクエストライトバック(ステップS3’’)は異なるパスで行われるため、それらの順序は必ずしも一意に定まらない。

【0028】

本発明に係るセルは、受け取ったリードリクエストを所定のテーブルに登録しておく機能を有している。また、本発明に係るセルは、登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、検出フラグを有効にする機能を有している。更に、本発明に係るセルは、そのリクエストライトバック(ステップS3’’)よりも後にリプライライトバック(ステップS3)を受け取った場合、上記検出フラグを参照することによって、受け取ったリプライライトバックを“破棄(discard)”する機能を備えている。言い換えれば、本発明に係るセルは、スヌープリクエストの発行(ステップS2)からリプライライトバック(ステップS3)までの期間にリクエストライトバック(ステップS3’’)を検出した場合、リプライライトバックを破棄する機能を備えている。

【0029】

これにより、ホームセルCHにおいて、リクエストセルCRからのリクエストライトバックによって更新されたデータが、オーナーセルCOからのリプライライトバックによる古いデータで上書きされることが防止される。従って、ステップS3とステップS3’’が異なっていても、コヒーレンシを保障することが可能となる。言い換えれば、オーナーセルCOがリプライデータを直接リクエストセルCRに送信しても(ステップS3’)、セル間のコヒーレンシが保たれる。逆に言えば、コヒーレンシを保障しつつ、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。すなわち、コヒーレンシの保障とレイテンシの短縮(処理速度の向上)との両立が実現される。

【0030】

2.構成

2−1.全体構成

本実施の形態に係る処理を実現するための具体的な構成例を以下に説明する。本実施の形態に係るマルチプロセッサシステムは分散共有メモリ型のマルチプロセッサシステムであり、その全体的な構成は図1に示された構成と同様である。すなわち、本実施の形態に係る分散共有メモリ型マルチプロセッサシステム1は、複数のセル(ノード)C1〜Cn(nはセル数を示す整数)と、それら複数のセルC1〜Cn間を互いに結合するクロスバースイッチ9を備えている。複数のセルC1〜Cnは、共有バスやデータリンク等のネットワークにより互いに結合されていてもよい。

【0031】

複数のセルC1〜Cnは同一の機能を有している。各々のセルCj(jは1以上n以下の整数)は、少なくとも1つのCPU(マイクロプロセッサ)2−j−1〜2−j−m(mは各セル内のCPU数を示す整数)と、メインメモリ(ローカルメモリ)5−jを備えている。それらCPU2の各々は、少なくとも1つのキャッシュメモリ(ストアインキャッシュ)7を搭載している。分散的に設けられたメインメモリ5−1〜5−nの全てによって共有メモリが構成され、その共有メモリは全てのCPU2によって参照される。

【0032】

1つのセルが複数のCPU2、すなわち複数のキャッシュ7を有している場合、セル内のローカルなキャッシュコヒーレンシは、例えば「スヌープ方式」により実現される。この場合、各CPU2に搭載されるキャッシュ7は、例えばMESIプロトコルに基づいてキャッシュステータスを管理する。MESIプロトコルによれば、「M(Modified)」、「E(Exclusive)」、「S(Shared)」、及び「I(Invalid)またはU(Uncached)」の4つのキャッシュステータスが提供される。

【0033】

M(Modified):当該キャッシュ中のデータは、当該キャッシュ内にのみ存在し、且つ、メインメモリ内のデータとは同一でない。つまり、最新データが自キャッシュにのみ存在する。

E(Exclusive):当該キャッシュ中のデータは、複数のキャッシュのうち当該キャッシュ内にのみ存在し、且つ、メインメモリ内のデータと同一である。つまり、最新データは、自キャッシュとメインメモリに存在する。

S(Shared):当該キャッシュ中のデータは、自キャッシュ及び他のCPUのキャッシュに存在し、且つ、メインメモリ内のデータと同一である。つまり、最新データは、複数のキャッシュとメインメモリに存在する。

I(Invalid)、U(Uncached):当該キャッシュ中のデータは、無効である。つまり、最新データは、自キャッシュに存在せずメインメモリに存在する。

【0034】

尚、本発明に適用されるキャッシュプロトコルは、上記MESIプロトコルに限られない。キャッシュステータスM(Modified)を提供するプロトコルであれば、如何なるキャッシュプロトコルでも適用され得る。

【0035】

また、セル内のキャッシュコヒーレンシだけでなく、図1に示された複数のセルC1〜Cn間のキャッシュコヒーレンシも保つ必要がある。本実施の形態によれば、複数のセルC1〜Cnの間のキャッシュコヒーレンシは、「ディレクトリ方式」に基づいて制御される。そのため、セルC1〜Cnのそれぞれには、キャッシュコヒーレンシ回路3−1〜3−n及びディレクトリ4−1〜4−nが設けられている。

【0036】

ディレクトリ4−jは、DRAM等により実現される記憶領域である。ディレクトリ4−jには、自セルCjのメインメモリ5−jに格納されたデータに関するキャッシングの状態を管理するための情報が格納される。より具体的には、ディレクトリ4−jには、自セルCjのメインメモリ5−jに格納された全データのステータスと、そのデータの最新版をキャッシングしているセル(すなわちオーナーセルCO)を示すテーブルが格納される。最新データをキャッシングしているオーナーセルCOは、自セルである場合もあるし、他のセルである場合もある。

【0037】

ディレクトリ4−jに格納される情報の一例が、図5に示されている。図5に示されるように、メインメモリ5−jのデータアドレス毎に、そのステータス(P,S,U)及びオーナーセル情報が対応付けられている。例えば、データアドレスA0に関するステータスは「P(Private)」である。ステータス「P」は、最新データが唯一のセルのキャッシュ7に登録されている可能性を示している。そのキャッシュ7のキャッシュステータスとしては、「M」,「E」,「S」,及び「I」の全てが許容される。また、オーナーセル情報としてはオーナーセルCOのセル番号が登録される。

【0038】

また、データアドレスA1に関するステータスは「S」である。ステータス「S(Shared)」は、最新データが複数のセルのキャッシュ7に登録されている可能性を示している。それらキャッシュ7のキャッシュステータスとしては、「S」及び「I」が許容される。この場合、オーナーセル情報としては、セルC1〜Cnに対応するビットマップが登録される。例として、セル数が3個であり(n=3)、セルC1及びC2のキャッシュ7に最新データが格納されている場合を考える。この場合、3ビットのビットマップのうちセルC1とセルC2に対応するビットが“1”にセットされ、セルC3に対応するビットは“0”にセットされる;(セルC3,セルC2,セルC1)=(0,1,1)。このようなビットマップによりオーナー情報が管理される。

【0039】

また、データアドレスA2に関するステータスは「U(Uncached)」である。ステータス「U」は、メインメモリ5−j中のデータが最新データであることを示す。この場合、オーナーセル情報としては特に何も登録されない(N/A:NotAvailable)。以上に示されたステータスP,S,Uは、メインメモリ5−jに関するキャッシュステータスと言うこともできる。

【0040】

このようなディレクトリ4−jを参照することによって、本実施の形態に係るキャッシュコヒーレンシ回路3−jは、セルC1〜Cn間のコヒーレンシ制御を行う。つまり、キャッシュコヒーレンシ回路3−jは、ディレクトリ4−jを用い、ディレクトリ方式に基づいてキャッシュコヒーレンシを保障する。以下に説明されるように、本発明は特に、このキャッシュコヒーレンシ回路3−jに特徴を有している。

【0041】

2−2.キャッシュコヒーレンシ回路

図6は、本実施の形態に係るセルCjのキャッシュコヒーレンシ回路3−jの構成を示すブロック図である。セルCjにおいて、キャッシュコヒーレンシ回路3−jは、複数のCPU2−j−1〜2−j−m、ディレクトリ4−j、及びメインメモリ5−jに接続されている。また、キャッシュコヒーレンシ回路3−jは、クロスバースイッチ9を介して他のセルと通信可能に接続されている。図6に示されるように、キャッシュコヒーレンシ回路3−jは、CPUリクエスト制御部10、クロスバーリクエスト制御部20、メインパイプ部30、ディレクトリアクセス制御部40、メインメモリアクセス制御部50、及びリプライデータ制御部60を有している。それらユニットは、互いにデータやリクエストをやりとりできるように構成されている。

【0042】

リクエストとしては、「リードリクエスト」、「スヌープリクエスト」、「リプライライトバック」、及び「リクエストライトバック」が挙げられる。

【0043】

リードリクエストには、リード対象アドレス及び当該リードリクエストの発行元が含まれる。本例において、リード対象アドレスは、ホームセルCHのメインメモリ5中のアドレスであり、発行元は、リクエストセルCRのCPU2である。つまり、リードリクエストには、少なくともリクエストセルCRとホームセルCHに関する情報が含まれていると言える。

【0044】

スヌープリクエストには、リードリクエストの情報がコピーされ、リード対象アドレス及びリードリクエストの発行元が含まれる。

【0045】

リプライライトバックには、スヌープリクエストの情報がコピーされ、リード対象アドレス及びリードリクエストの発行元が含まれる。更に、リプライライトバックには、ライトバックデータが含まれる。リード対象アドレスは、そのライトバックデータが書き戻されるライトバック対象アドレスでもある。

【0046】

リクエストライトバックには、ライトバックデータ、ライトバック対象アドレス、当該リクエストライトバックの発行元、及びディレクトリ更新情報が含まれる。本例において、ライトバック対象アドレスは、ホームセルCHのメインメモリ5中のアドレスであり、発行元は、リクエストセルCRのCPU2である。ディレクトリ更新情報は、リクエストセルCRに含まれるキャッシュ7のキャッシュステータスとホームセルCHのディレクトリ4のステータスとを整合させるための情報である。ディレクトリ更新情報には、ホームセルCHのディレクトリ4のステータスをどのように更新すればよいか示されている。

【0047】

CPUリクエスト制御部10は、CPU2からのリクエストを処理する機能を有する。より具体的には、CPUリクエスト制御部10は、CPU2が発行するリードリクエストを受信し、そのリードリクエストに含まれるリード対象アドレスに応じて、自セルのメインパイプ部30又はホームセルCHにリードリクエストを転送する。また、CPUリクエスト制御部10は、CPU2が発行するライトバックを受信し、そのライトバックに含まれるライトバック対象アドレスに応じて、自セルのメインパイプ部30又はホームセルCHにライトバックを転送する。

【0048】

更に、CPUリクエスト制御部10は、CPU2に対するスヌープリクエストを処理する機能を有する。より具体的には、CPUリクエスト制御部10は、クロスバースイッチ9又はディレクトリアクセス制御部40から受け取るスヌープリクエストを、CPU2に転送する。そして、CPUリクエスト制御部10は、スヌープ処理によってCPU2のキャッシュ7から得られるリプライデータを、リクエストセルCRに直接送信する。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシが短縮される。

【0049】

クロスバーリクエスト制御部20は、クロスバースイッチ9から受け取るリクエストを処理する機能を有する。より具体的には、クロスバーリクエスト制御部20は、クロスバースイッチ9より受信するリードリクエスト、リプライライトバック、及びリクエストライトバックをメインパイプ部30に転送する。

【0050】

メインパイプ部30は、CPUリクエスト制御部10とクロスバーリクエスト制御部20から受信したリクエストを調停し、また、ディレクトリアクセス制御部40及びメインメモリアクセス制御部50に対するリクエストを制御する機能を備える。メインパイプ部30の詳細な機能は、後の第2−3節において詳しく説明される。

【0051】

ディレクトリアクセス制御部40は、ディレクトリ4に対するアクセスを制御する。具体的には、ディレクトリアクセス制御部40は、メインパイプ部30から受信するリクエスト(リードリクエスト,リクエストライトバック,リプライライトバック)に応答して、ディレクトリ4の索引(検索)を行う。読み出されたディレクトリ4のステータスによっては、ディレクトリアクセス制御部40は、スヌープリクエストをオーナーセルCO又は自セルのCPUリクエスト制御部10に発行する。

【0052】

また、ディレクトリアクセス制御部40は、メインパイプ部30から受信するリクエストに応答して、ディレクトリ4の更新を行う。ディレクトリ4の更新方法は、読み出されるディレクトリ4の状態に応じて異なり、それは所定のルールにより規定されている(図9参照)。ただし、リプライライトバックの場合、ディレクトリ4の更新がその所定のルールと違う方式で行われることがある。そのような場合、ディレクトリアクセス制御部40は、メインパイプ部30から「更新リクエスト」を受け取る。そして、ディレクトリアクセス制御部40は、その更新リクエストが指示するように、ディレクトリ4の更新を行う。

【0053】

メインメモリアクセス制御部50は、メインメモリ5に対するアクセスを制御する。具体的には、メインメモリアクセス制御部50は、メインパイプ部30から受信したリードリクエストに応答して、メインメモリ5から対象データを読み出す。そして、メインメモリアクセス制御部50は、読み出されたデータ(読み出しデータ)をリプライデータとしてリクエストセルCR又は自セルのリプライデータ制御部60に送信する。また、メインメモリアクセス制御部50は、メインパイプ部30から受信したリプライライトバック又はリクエストライトバックに応答して、ライトバックデータをメインメモリ5に書き込む。

【0054】

リプライデータ制御部60は、メインメモリアクセス制御部50あるいはクロスバースイッチ9から受け取るリプライデータを、CPU2に転送する機能を有している。

【0055】

2−3.メインパイプ部

図7は、本実施の形態に係るメインパイプ部30の構成を示すブロック図である。図7に示されるように、メインパイプ部30は、スヌープ管理テーブル31、ライトバック検出回路32、キャンセル判定回路33、ディスカード判定回路34、及び調停制御回路35を有している。

【0056】

調停制御回路35は、CPUリクエスト制御部10からのリクエストとクロスバーリクエスト制御部20からのリクエストとの調停を行う。調停を獲得したリクエストは、スヌープ管理テーブル31、ライトバック検出回路32、キャンセル判定回路33、及びディスカード判定回路34へ転送される。

【0057】

スヌープ管理テーブル31は情報が格納されるテーブルであり、そこには複数のエントリが格納される。各エントリは、バリッドビット311、アドレス情報312、セル情報313、及びライトバック検出情報314から構成される。図8には、あるセルにおけるスヌープ管理テーブル31の一例が示されている。バリッド(V)ビット311は、当該エントリが有効エントリ(“1”)か空きエントリ(“0”)かを示す。

【0058】

アドレス情報312としては、リードリクエストが示すリード対象アドレス(例:A0,A1)が格納される。セル情報(リクエストセル情報)313としては、そのリードリクエストを発行した発行元のセル(例:C1,C3)の番号が格納される。このように、本発明に係るセルは、受け取ったリードリクエストを記憶しておく機能を有している。尚、後述されるように、複数のエントリに対応する複数のリード対象アドレス(A0,A1)は、それぞれ異なるように制御される。つまり、アドレス情報312に含まれる“あるリード対象アドレス”の数は、0個か1個である。あるリード対象アドレスに対するリードリクエストが既に登録されている場合、同じリード対象アドレスに対するリードリクエストは登録待機状態になる。

【0059】

ライトバック検出情報314は、検出フラグとディレクトリ更新情報を含む。検出フラグやディレクトリ更新情報は、登録されたアドレス情報312及びセル情報313と対応付けられている。検出フラグは、リクエストセルCRからのライトバック、すなわちリクエストライトバックが検出されたか否かを示すフラグである。検出フラグが有効(“1”)のとき、当該リード対象アドレス(A0)に対するリクエストライトバックが検出されている。一方、ディレクトリ更新情報は、ディレクトリ4がどのステータスに更新されるかを示す情報であり、検出フラグが“1”に設定される時に同時に設定される。後述されるように、このディレクトリ更新情報は、更新リクエストの生成時に用いられる。

【0060】

図7に戻り、ライトバック検出回路32は、アドレス情報比較器321、セル情報比較器322、及びAND323を有している。このライトバック検出回路32は、調停制御回路35から転送されたリクエストを受け取る。そして、ライトバック検出回路32は、上記スヌープ管理テーブル31を参照することによって、アドレス情報312が示すリード対象アドレスの各々に対する「リクエストライトバック」を検出する。

【0061】

具体的には、アドレス情報比較器321は、ライトバック(リプライライトバック又はリクエストライトバック)が示すライトバック対象アドレスと、上記スヌープ管理テーブル31中のアドレス情報312が示すリード対象アドレスとの比較を行う。そして、アドレス情報比較器321は、全てのエントリに関して一致(“1”)/不一致(“0”)を示すビットマップデータ(ビット数=総エントリ数)を出力する。尚、Vビット311が無効であるエントリは、自動的に不一致(“0”)と判定される。そのビットマップデータにおいて、全てのビットは“0”、あるいは、1つのビットだけが“1”である。ビットマップデータのうち“1”に対応するエントリは、以下「一致エントリ」と参照される。

【0062】

一方、セル情報比較器322は、リクエストライトバックを受けとった時に、そのリクエストライトバックが示す発行元の番号と、上記スヌープ管理テーブル31中のセル情報313が示すリクエストセルCRの番号との比較を行う。そして、セル情報比較器322は、全てのエントリに関して一致(“1”)/不一致(“0”)を示すビットマップデータを出力する。尚、Vビット311が無効であるエントリは、自動的に不一致(“0”)と判定される。

【0063】

AND323は、アドレス情報比較器321からのビットマップデータとセル情報比較器322からのビットマップデータとの論理積を出力する。出力されるビットマップデータにおいて、全てのビットは“0”、あるいは、1つのビットだけが“1”である。そして、ライトバック検出回路32は、そのビットマップデータのうち“1”に対応するエントリ(一致エントリ)のライトバック検出情報314を変更する。具体的には、ライトバック検出回路32は、検出フラグを無効(“0”)から有効(“1”)に変更し、また、ディレクトリ変更情報をリクエストライトバックが示すディレクトリ更新情報に設定する。つまり、ディレクトリ更新情報は、有効化された検出フラグと対応づけられてスヌープ管理テーブル31に格納される。

【0064】

AND323の出力に“1”が含まれていることは、「あるリクエストセルCRがあるアドレスに対してリードリクエストを発行し、更に、同じリクエストセルCRが同じアドレスに対してリクエストライトバックを発行したこと」を意味する。つまり、ライトバック検出回路32は、スヌープ管理テーブル31に登録されたリードリクエストと関連したリクエストライトバックを検出するための回路であると言える。ライトバック検出回路32は、そのようなリクエストライトバックを検出した場合、当該一致エントリの検出フラグを“1”にセットする。このように、本発明に係るセルは、登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、検出フラグを有効にする機能を有している。スヌープ管理テーブル31に予め格納されるリードリクエストに関する情報(アドレス情報312,セル情報313)は、後に受け取るかもしれないリクエストライトバックを検出するための情報であると言える。

【0065】

また、ライトバック検出回路32は、リプライライトバックを受け取った場合、アドレス情報比較器321から出力されるアドレス一致エントリ(ビットマップデータ)をキャンセル判定回路33及びディスカード判定回路34に出力する。また、ライトバック検出回路32は、リプライライトバックを受け取った場合、そのアドレス一致エントリに関するVビット311を無効化(“0”)する。つまり、ライトバック検出回路32は、リプライライトバックに応答して、そのリプライライトバックに関連するエントリを初期化する。

【0066】

次に、キャンセル判定回路33について説明する。上述の通り、スヌープ管理テーブル31において、あるリード対象アドレスに対するリードリクエストが既に登録されている場合、同じリード対象アドレスに対するリードリクエストは登録待機状態に設定される。そのためにキャンセル判定回路33が設けられている。キャンセル判定回路33は、調停制御回路35からのリードリクエスト、及び上記ライトバック検出回路32のアドレス情報比較器321からの出力を受け取る。アドレス情報比較器321からアドレス一致エントリが出力された場合、すなわち、スヌープ管理テーブル31に既に登録されているリード対象アドレスと同一アドレスへのリードリクエストが検出された場合、キャンセル判定回路33は、CPUリクエスト制御部10又はクロスバーリクエスト制御部20に対して、リードリクエストの再発行を要求する。そして、スヌープ管理テーブル31に空きエントリができるまで、同じ動作が繰り返される。これにより、そのリードリクエストは、登録待機状態となる。

【0067】

ディスカード判定回路34は、調停制御回路35から転送されたリクエスト(リードリクエスト,リクエストライトバック,リプライライトバック)を受け取る。受け取ったリクエストがリードリクエストの場合、ディスカード判定回路34は、そのリードリクエストをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。また、そのリクエストがリクエストライトバックの場合、ディスカード判定回路34は、そのリクエストライトバックをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。

【0068】

また、受け取ったリクエストがリプライライトバックの場合、ディスカード判定回路34は、アドレス情報比較器321からの出力(ビットマップデータ)を受け取り、そのビットマップデータが示すアドレス一致エントリのライトバック検出情報314を参照する。参照されたライトバック検出情報314の検出フラグが“0”の場合、ディスカード判定回路34は、リプライライトバックをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。一方、検出フラグが“1”の場合、それはリクエストライトバックの後にリプライライトバックが入力されたことを意味する。この場合、ディスカード判定回路34は、受け取ったリプライライトバックを破棄(ディスカード)する。よって、リプライライトバックは、メインメモリアクセス制御部50には出力されない。ただし、ディスカード判定回路34は、ディレクトリ4のステータスを更新するための「更新リクエスト」をディレクトリアクセス制御部40に発行する。その更新リクエストの指示内容は、参照されたライトバック検出情報314中の「ディレクトリ更新情報」によって決定される。

【0069】

以上に説明されたように、本実施の形態に係るメインパイプ部30は、(1)リクエストセルCRからのリードリクエストを登録する機能、(2)登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、その検出を記憶しておく機能、及び(3)ディレクトリアクセス制御部40及びメインメモリアクセス制御部50に対するリクエストを制御する機能;具体的には、リクエストライトバックよりも後にリプライライトバックを受け取った場合、そのリプライライトバックを破棄し、ディレクトリ4を更新する機能、を備えている。上記(1)の機能は、スヌープ管理テーブル31により提供される。上記(2)の機能は、ライトバック検出回路32及びスヌープ管理テーブル31により提供される。上記(3)の機能は、ディスカード判定回路34及びスヌープ管理テーブル31により提供される。これにより、上述の図4に示された動作が実現される。

【0070】

尚、図9には、各リクエストに対するディレクトリ4の索引時のステータス及び更新後のステータスが要約的に示されている。図9に示された要約は、以下の動作例の説明において適宜参照される。

【0071】

3.システムの動作例

既出の図6、図7、図9、及び以下に示される図面を参照しながら、本実施の形態に係るマルチプロセッサシステム1の動作例を説明する。本動作例において、リクエストセルCR、ホームセルCH、及びオーナーセルCOは互いに異なっているとする。例えば、リクエストセルCRはセルC1、ホームセルCHはセルC2、オーナーセルCOはセルC3である。つまり、リクエストセルC1のCPU2(例えばCPU2−1−1)による読み出し対象のアドレスは、ホームセルC2に搭載されたメインメモリ5−2中のアドレスであり、そのアドレスに対応した最新データは、オーナーセルC3に搭載されたCPU2(例えばCPU2−3−1)中のキャッシュ7に格納されている。

【0072】

図10は、本動作例における処理フローを概念的に示している。また、図11は、リクエストセルC1のCPU2−1−1のキャッシュステータス、ホームセルC2のキャッシュコヒーレンシ回路3−2のスヌープ管理テーブル31及びディレクトリ4−2の内容、及びオーナーセルC3のCPU2−3−1のキャッシュステータスの遷移を示している。初期状態において、リクエストセルC1のCPU2−1−1のキャッシュステータスは“I(Invalid)”、オーナーセルC3のCPU2−3−1のキャッシュステータスは“M(Modified)”である。また、ホームセルC2のディレクトリ4−2において、リード対象アドレスA0に対するステータスは“P”、オーナーセル情報は“セルC3”をそれぞれ示すとする。

【0073】

ステップS11:リクエストセルC1:リードリクエストの発行

まず、リクエストセルC1のCPU2−1−1が、ホームセルC2のメインメモリ5−2中のアドレスA0に対して「リードリクエスト」を発行する。このリードリクエストには、リード対象アドレスA0及び発行元(CPU2−1−1)が含まれている。CPU2−1−1がリードリクエストを発行すると、リクエストセルC1のCPU2−1−1〜CPU2−1−mのそれぞれにおいてスヌープ処理が実行される。具体的には、CPU2−1−1〜CPU2−1−mのそれぞれのキャッシュ7が、自身がリード対象アドレスA0のデータを格納しているかどうか調べる。

【0074】

キャッシュヒットが無い場合、リードリクエストは、リクエストセルC1のキャッシュコヒーレンシ回路3−1に送信される。キャッシュコヒーレンシ回路3−1のCPUリクエスト制御部10は、CPU2−1−1からのリードリクエストを受け取る。そのCPUリクエスト制御部10は、リードリクエストに含まれるリード対象アドレスA0に基づいて、アクセス対象となるホームセルC2を判別する。ホームセルC2は、リード対象アドレスA0により一意に決定される。そして、CPUリクエスト制御部10は、クロスバースイッチ9を介してホームセルC2にリードリクエストを送信する。

【0075】

ステップS12:ホームセルC2:スヌープ管理テーブル31の更新

ホームセルC2のキャッシュコヒーレンシ回路3−2のクロスバーリクエスト制御部20は、リクエストセルC1からクロスバースイッチ9を通してリードリクエストを受け取る。そして、クロスバーリクエスト制御部20は、受け取ったリードリクエストをメインパイプ部30に転送する。メインパイプ部30の調停制御回路35は、そのリードリクエストとCPUリクエスト制御部10からのリクエストとの調停を行う。

【0076】

クロスバーリクエスト制御部20からのリードリクエストが調停を獲得すると、そのリードリクエストは、スヌープ管理テーブル31、ライトバック検出回路32、キャンセル判定回路33、及びディスカード判定回路34に転送される。そして、メインパイプ部30は、スヌープ管理テーブル31の空きエントリに、そのリードリクエストを登録する。この場合、図11に示されるように、リードリクエストが登録されるエントリに関して、Vビット311は“0”から“1”に変更され、アドレス情報312としてリード対象アドレスA0が登録され、セル情報313としてリクエストセルC1の番号が登録され、ライトバック検出情報314の検出フラグは“0”にセットされる。

【0077】

尚、スヌープ管理テーブル31の有効エントリ(Vビット311が“1”のエントリ)に同一アドレスA0に対するリードリクエストが既に存在する場合、アドレス情報比較器321(図7参照)は、アドレス一致エントリを検出する。アドレス一致エントリが検出されると、キャンセル判定回路33は、クロスバーリクエスト制御部20にリードリクエストの再発行を要求する。その結果、そのリードリクエストは登録待ち状態になる。これにより、スヌープ管理テーブル31に同一アドレスに対する複数のリードリクエストが格納されることが防止される。

【0078】

続いて、メインパイプ部30(ディスカード判定回路34)は、ディレクトリアクセス制御部40及びメインメモリアクセス制御部50にリードリクエストを送信する。

【0079】

ステップS13:ホームセルC2:ディレクトリアクセス

ホームセルC2のディレクトリアクセス制御部40は、受け取ったリードリクエストに応答して、まずディレクトリ4−2の索引を行う。図11に示されるように、ディレクトリ4−2において、リード対象アドレスA0に対するステータスは“P”、オーナーセル情報は“セルC3”である。この場合、ディレクトリアクセス制御部40は、クロスバースイッチ9を通してオーナーセルC3に「スヌープリクエスト」を発行する。このスヌープリクエストには、リードリクエストの情報がコピーされ、リード対象アドレスA0及び当該リードリクエストの発行元(リクエストセルC1のCPU2−1−1)が含まれる。

【0080】

また、ディレクトリアクセス制御部40は、リードリクエストに応答して、ディレクトリ4−2の更新を行う。図9を参照して、リードリクエストに対する索引時にステータスが“P”である場合、ステータスは更新されない(NC:No Change)。更に、ディレクトリアクセス制御部40は、メインメモリアクセス制御部50に、ステータス情報“P”とオーナーセル情報“C3”を出力する。

【0081】

ステップS14:ホームセルC2:メモリアクセス

一方、ホームセルC2のメインメモリアクセス制御部50は、受け取ったリードリクエストに応答して、メインメモリ5−2中のリード対象アドレスA0からデータを読み出す。そして、メインメモリアクセス制御部50は、読み出されたデータに、ディレクトリアクセス制御部40から受け取ったステータス情報“P”とオーナーセル情報“C3”を付与することによって、リプライデータDRを生成する。メモリアクセス制御部50は、そのリプライデータDRを、クロスバースイッチ9を介してリクエストセルC1に送信する。

【0082】

ステップS15:リクエストセルC1:リプライデータDRの受信

リクエストセルC1のリプライデータ制御部60は、クロスバースイッチ9からリプライデータDRを受け取る。そのリプライデータDRには、ステータスが“P”であることと、オーナーセルがセルC3であることが示されている。この場合、リプライデータ制御部60は、オーナーセルC3からのリプライデータを待ち合わせる。

【0083】

ステップS16:オーナーセルC3:スヌープ処理、リプライライトバックの発行

オーナーセルC3のCPUリクエスト制御部10は、ホームセルC2が発行したスヌープリクエストを受け取る。そして、CPUリクエスト制御部10は、自セルC3のCPU2−3−1〜2−3−mにスヌープリクエストを発行する。CPU2−3−1〜2−3−mのそれぞれのキャッシュ7は、スヌープ処理を実行する。その結果、キャッシュステータスが“M”であるCPU2−3−1は、「リプライライトバック」をCPUリクエスト制御部10に発行する。リプライライトバックには、スヌープリクエストの情報がコピーされ、リード対象アドレスA0及びリードリクエストの発行元(リクエストセルC1)が含まれる。更に、リプライライトバックには、キャッシュ7から読み出されたデータ(ライトバックデータ)が含まれる。リード対象アドレスA0は、そのライトバックデータが書き戻されるライトバック対象アドレスA0でもある。また、リプライライトバックの発行に応答して、CPU2−3−1のキャッシュ7のキャッシュステータスは、“M”から“I”に変更される。

【0084】

オーナーセルC3のCPUリクエスト制御部10は、CPU2−3−1からリプライライトバックを受け取ると、そのリプライライトバックをクロスバースイッチ9を介してホームセルC2に送信する(ステップS16−1)。ホームセルC2は、ライトバック対象アドレスA0により一意に決定される。

【0085】

更に、オーナーセルC3のCPUリクエスト制御部10は、キャッシュ7から読み出されたデータ(リプライデータDR’)をリクエストセルC1へ直接送信する(ステップS16−2)。その送信先(リクエストセルC1)は、スヌープリクエストあるいはリプライライトバックに含まれるリードリクエストの発行元情報により決定することができる。

【0086】

ステップS17:リクエストセルC1:リプライデータDR’の受信

リクエストセルC1のリプライデータ制御部60は、オーナーセルC3からクロスバースイッチ9を通してリプライデータDR’を直接受け取る。この時、リプライデータ制御部60は、上記ステップS15で受け取ったリプライデータDRを破棄する。そして、リプライデータ制御部60は、オーナーセルC3から受け取ったリプライデータDR’を、リードリクエストの発行元であるCPU2−1−1に送信する。CPU2−1−1は、リプライデータDR’を受け取ると、そのリプライデータDR’を自身のキャッシュ7に登録する。この時、CPU2−1−1のキャッシュ7のキャッシュステータスは、“I”から“E”に変更される。以上に説明されたように、リードリクエストの発行からリプライデータDR’の受け取りまでが3HOPで実現される。

【0087】

ステップS18:リクエストセルC1:リクエストライトバックの発行

ステップS17の後、CPU2−1−1は、キャッシュ7に格納されたデータを新たなデータで書き換える、すなわち、キャッシュ7に格納されたデータを更新する。この時、そのキャッシュ7のステータスは、“E”から“M”に一旦変更される。更に、CPU2−1−1は、キャッシュ7のデータ更新に応答して、「リクエストライトバック」をCPUリクエスト制御部10に発行する。リクエストライトバックの発行に応答して、CPU2−1−1のキャッシュ7のキャッシュステータスは、“M”から“I”に変更される。このリクエストライトバックには、キャッシュ7に格納された最新データ(ライトバックデータ)、ライトバック対象アドレスA0、発行元情報(リクエストセルC1のCPU2−1−1)、及びディレクトリ更新情報が含まれている。キャッシュステータスが“I”に変更されている場合、ディレクトリ更新情報は「U更新」に設定される。

【0088】

参考のため、CPU2−1−1のキャッシュ7のステータスが“E”から“M”に変更された後、別のCPU2−1−2がそのデータに対するリードリクエストを発行した場合を考える。この場合、スヌープ処理により、CPU2−1−1のキャッシュ7に格納されたデータが、CPU2−1−2のキャッシュ7に移動する。CPU2−1−1に関するキャッシュステータスは“M”から“I”に変更される一方、CPU2−1−2に関するキャッシュステータスは“I”から“E”に変更される。この場合、セルC1におけるキャッシュステータスに“E”が含まれているため、CPU2−1−1が発行するリクエストライトバックのディレクトリ更新情報は「NC更新」に設定されるとよい。

【0089】

キャッシュコヒーレンシ回路3−1のCPUリクエスト制御部10は、CPU2−1−1からリクエストライトバック(U更新)を受け取ると、ライトバック対象アドレスA0に基づいて、アクセス先となるホームセルC2を判別する。そして、CPUリクエスト制御部10は、そのリクエストライトバックをクロスバースイッチ9を介してホームセルC2に送信する。

【0090】

ステップS19:ホームセルC2:リクエストライトバックの検出

ホームセルC2のキャッシュコヒーレンシ回路3−2のクロスバーリクエスト制御部20は、リクエストセルC1からリクエストライトバックを受け取る。そして、クロスバーリクエスト制御部20は、受け取ったリクエストライトバックをメインパイプ部30に転送する。メインパイプ部30の調停制御回路35は、そのリクエストライトバックとCPUリクエスト制御部10からのリクエストとの調停を行う。

【0091】

クロスバーリクエスト制御部20からのリクエストライトバックが調停を獲得すると、そのリクエストライトバックは、ライトバック検出回路32及びディスカード判定回路34に転送される。ライトバック検出回路32において、アドレス情報比較器321は、図11に示されたスヌープ管理テーブル31のアドレス情報312(“A0”)と、リクエストライトバックが示すライトバック対象アドレスA0とが一致していることを検出する。また、セル情報比較器322は、図11に示されたスヌープ管理テーブル31のセル情報313(“C1”)と、リクエストライトバックが示す発行元情報(“C1”)とが一致していることを検出する。そして、AND323の演算により、一致エントリが検出される。この場合、ライトバック検出回路32は、スヌープ管理テーブル31中の当該一致エントリのライトバック検出情報314を更新する。具体的には、当該一致エントリの検出フラグが“1”にセットされる。また、リクエストライトバックに含まれるディレクトリ更新情報(U更新)に応じて、当該一致エントリのディレクトリ更新情報は「U」にセットされる。

【0092】

以上に説明されたように、ホームセルC2において、アドレスA0に対するリクエストライトバックが検出されたことが記憶される。また、スヌープ管理テーブル31の更新が行われる。続いて、メインパイプ部30(ディスカード判定回路34)は、ディレクトリアクセス制御部40及びメインメモリアクセス制御部50にリクエストライトバックを送信する。

【0093】

ステップS20:ホームセルC2:ディレクトリアクセス、メモリアクセス

ホームセルC2のメインメモリアクセス制御部50は、受け取ったリクエストライトバックに応答して、メインメモリ5−2中のライトバック対象アドレスA0に、ライトバックデータを書き戻す。

【0094】

また、ディレクトリアクセス制御部40は、受け取ったリクエストライトバックに応答して、ディレクトリ4−2の索引・更新を行う。図11に示されるように、ディレクトリ4−2において、オーナーセル情報は“セルC3”である。つまり、ディレクトリ4−2の索引の結果、リクエストライトバックが示す発行元情報(リクエストセルC1)はディレクトリ4−2中のオーナーセル情報(オーナーセルC3)と異なっていることが分かる。この場合、図9を参照して、ディレクトリアクセス制御部40は、ディレクトリ4−2のステータス及びオーナーセル情報を更新しない(NC:No Change)。

【0095】

ステップS21:ホームセルC2:リプライライトバックの破棄

ホームセルC2は、ステップS19による「リクエストライトバック」よりも後に、上記ステップS16−1による「リプライライトバック」を受け取るとする。ホームセルC2のキャッシュコヒーレンシ回路3−2のクロスバーリクエスト制御部20は、オーナーセルC3からリプライライトバックを受け取る。そして、クロスバーリクエスト制御部20は、受け取ったリプライライトバックをメインパイプ部30に転送する。メインパイプ部30の調停制御回路35は、そのリプライライトバックとCPUリクエスト制御部10からのリクエストとの調停を行う。

【0096】

クロスバーリクエスト制御部20からのリプライライトバックが調停を獲得すると、そのリプライライトバックは、ライトバック検出回路32及びディスカード判定回路34に転送される。ライトバック検出回路32において、アドレス情報比較器321は、リプライライトバックが示すライトバック対象アドレスA0とスヌープ管理テーブル31のアドレス情報312との比較を行う。そして、ライトバック検出回路32は、ライトバック対象アドレスA0と一致するアドレス一致エントリを、ディスカード判定回路34に通知する。

【0097】

ディスカード判定回路34は、リプライライトバックを受け取った場合、スヌープ管理テーブル31中の当該アドレス一致エントリのライトバック検出情報314を読み出す。図11に示されるように、当該アドレス一致エントリの検出フラグは“1”にセットされている。これは、リクエストライトバックが既に行われていることを意味する。これにより、ディスカード判定回路34は、リプライライトバックよりも前にリクエストライトバックが行われたことを認識する。この場合、ディスカード判定回路34は、リプライライトバックを破棄(ディスカード)し、メインメモリアクセス制御部50に対してリプライライトバックを出力しない。その結果、リクエストセルCRからのリクエストライトバックによって更新されたデータが、オーナーセルCOからのリプライライトバックによる古いデータで上書きされることが防止される。

【0098】

ステップS22:ホームセルC2:ディレクトリの更新

また、ディスカード判定回路34は、ライトバック検出情報314を参照した際、当該アドレス一致エントリのディレクトリ更新情報が「U」にセットされていることを検知する(図11参照)。この場合、ディスカード判定回路34は、ディレクトリアクセス制御部40に「更新リクエスト(U更新)」を発行する。ディレクトリアクセス制御部40は、受け取った更新リクエストに応答して、ディレクトリ4−2の更新を行う。図9に示された規定によるとリプライライトバックの場合は「NC」であるが、今回の場合、「更新リクエスト(U更新)」が優先される。よって、ディレクトリアクセス制御部40は、更新リクエストに応じて、ディレクトリ4−2のステータスを“P”から“U”に変更し、オーナーセル情報を消去する。図11に示されるように、セルC1のキャッシュステータス(“I”)、セルC2のディレクトリ4−2のステータス(“U”)、及びセルC3のキャッシュステータス(“I”)の間に不整合が無いことが分かる。すなわち、セル間のコヒーレンシが保たれている。

【0099】

尚、リプライライトバックを受け取った場合、ライトバック検出回路32は、アドレス情報比較器321からの出力に基づいて、スヌープ管理テーブル31中のアドレス一致エントリを初期化する。具体的には、ライトバック検出回路32は、そのアドレス一致エントリに関するVビット311を“0”に戻す。これにより、一連の処理が終わる。

【0100】

また、ホームセルC2がリプライライトバックをリクエストライトバックよりも前に受け取った場合の処理は、次の通りである。ライトバック検出情報314の検出フラグは“0”のままなので、ディスカード判定回路34は、リプライライトバックをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。これにより、通常通りライトバックが行われ、ライトバックデータがアドレスA0に書き戻される。また、図9に示されたルールに従い、ディレクトリ4−2のステータスは“P”のまま維持され、オーナーセル情報は「セルC3」から「セルC1(リクエストセル)」に変更される。セルC1は、リプライライトバックに含まれる「リクエストセルの発行元情報」により指定される。また、リプライライトバックによって、当該エントリは初期化される。従って、その後にリクエストライトバックが受信されても、ライトバック検出情報314の検出フラグは有効化されない。リクエストライトバックがそのまま実行されるのみである。

【0101】

4.まとめ

以上に説明されたように、本発明によれば、リクエストセルCRとホームセルCHとオーナーセルCOがそれぞれ異なる状態においても、コヒーレンシの保障とレイテンシの短縮が実現される。

【0102】

リクエストセルCRからオーナーセルCOのキャッシュ7に対するアクセスが発生した場合、オーナーセルCOは、メインメモリ5へのライトバックと同時に、リクエストセルCRに最新データを返却する。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。

【0103】

また、セルCjに搭載されるキャッシュコヒーレンシ回路3−jにスヌープ管理テーブル31、ライトバック検出回路32、及びディスカード判定回路34を設けることにより、各セルCjには次の機能が提供される:(1)リクエストセルCRからのリードリクエストを登録する機能、(2)登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、検出フラグを有効にする機能、(3)そのリクエストライトバックよりも後にリプライライトバックを受け取った場合、上記検出フラグを参照することによって、受け取ったリプライライトバックを破棄する機能、及び(4)リプライライトバックの破棄と共に、ディレクトリを更新する機能。これらの機能により、リクエストセルCRからのリクエストライトバックによって更新されたデータが、オーナーセルCOからのリプライライトバックによる古いデータで上書きされることが防止される。従って、リクエストライトバックとリプライライトバックの経路が異なっていても、コヒーレンシを保障することが可能となる。言い換えれば、オーナーセルCOがリプライデータDR’を直接リクエストセルCRに送信しても、セル間のコヒーレンシが保たれる。

【0104】

以上に説明されたように、本発明によれば、コヒーレンシを保障しつつ、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。すなわち、コヒーレンシの保障とレイテンシの短縮(処理速度の向上)との両立が実現される。本発明は、リクエストセルCRとホームセルCH間の距離(HOP数)と、ホームセルCHとオーナーセルCO間の距離が遠くなるような、大規模なマルチプロセッサシステムにおいては、さらに効果が大きくなる。

【図面の簡単な説明】

【0105】

【図1】図1は、分散共有メモリ型マルチプロセッサシステムの構成を示すブロック図である。

【図2】図2は、従来のマルチプロセッサシステムの動作を示す概念図である。

【図3】図3は、従来のマルチプロセッサシステムの動作を示す概念図である。

【図4】図4は、本発明に係るマルチプロセッサシステムの動作を示す概念図である。

【図5】図5は、本発明の実施の形態に係るディレクトリに格納される情報の一例を示すテーブルである。

【図6】図6は、本実施の形態に係るキャッシュコヒーレンシ回路の構成を示すブロック図である。

【図7】図7は、本実施の形態に係るメインパイプ部の構成を示すブロック図である。

【図8】図8は、本実施の形態に係るスヌープ管理テーブルの一例を示すテーブルである。

【図9】図9は、本実施の形態に係るディレクトリの更新方法を要約的に示すテーブルである。

【図10】図10は、本実施の形態に係るマルチプロセッサシステムの動作フローの一例を示す図である。

【図11】図11は、キャッシュステータス、スヌープ管理テーブル、及びディレクトリに格納される情報の遷移を示すテーブルである。

【符号の説明】

【0106】

1 分散共有メモリ型マルチプロセッサシステム

2 CPU

3 キャッシュコヒーレンシ回路

4 ディレクトリ

5 メインメモリ

7 キャッシュ

9 クロスバースイッチ

C セル

CR リクエストセル

CH ホームセル

CO オーナーセル

10 CPUリクエスト制御部

20 クロスバーリクエスト制御部

30 メインパイプ部

31 スヌープ管理テーブル

311 Vビット

312 アドレス情報

313 セル情報

314 ライトバック検出情報

32 ライトバック検出回路

321 アドレス情報比較器

322 セル情報比較器

323 AND

33 キャンセル判定回路

34 ディスカード判定回路

35 調停制御回路

40 ディレクトリアクセス制御部

50 メインメモリアクセス制御部

60 リプライデータ制御部

【技術分野】

【0001】

本発明は、複数のセルにより構成される分散共有メモリ型のマルチプロセッサシステムに関する。特に、本発明は、複数のセルを備える分散共有メモリ型マルチプロセッサシステムにおけるコヒーレンシ技術に関する。

【背景技術】

【0002】

コンピュータシステムの分野において、多数のプロセッサによって構成される「マルチプロセッサシステム(Multiprocessor System)」が従来知られている。マルチプロセッサシステムの中でも、複数のセル(あるいは複数のノード)によって構成され、その複数のセル間がバスやスイッチにより結合されたものが知られている。複数のセルはそれぞれ独立にプロセッサとメインメモリを有し、全てのメインメモリによって論理的に「共有メモリ」が構成される(例えば、特許文献1、特許文献2、特許文献3、特許文献4、及び特許文献5を参照)。メモリが分散的に配置され、且つ複数のプロセッサにより共有されるため、そのようなマルチプロセッサシステムは、「分散共有メモリ型(DSM: Distributed Shared Memory)マルチプロセッサシステム」や「分散共有メモリ型アーキテクチャ」と呼ばれることもある。

【0003】

図1は、分散共有メモリ型マルチプロセッサシステム1の構成を示すブロック図である。図1に示されたマルチプロセッサシステム1は、複数のセルC1〜Cn(nはセル数を示す整数)と、それら複数のセルC1〜Cn間を互いに結合するクロスバースイッチ9から構成されている。複数のセルC1〜Cnは同一の機能を有している。各々のセルCj(jは1以上n以下の整数)は、少なくとも1つのCPU(マイクロプロセッサ)2−j−1〜2−j−m(mは各セル内のCPU数を示す整数)と、メインメモリ(ローカルメモリ)5−jを備えている。それらCPU2の各々は、少なくとも1つのキャッシュメモリ(ストアインキャッシュ)7を搭載している。分散的に設けられたメインメモリ5−1〜5−nの全てによって共有メモリが構成され、その共有メモリは全てのCPU2によって参照される。

【0004】

このような分散共有メモリ型マルチプロセッサシステム1においては、CPU2のそれぞれがキャッシュ7を駆使しながら、メインメモリ5−1〜5−nに格納されたデータにアクセスし、またその更新を行う。データ更新にライトバック(Write Back)方式が用いられる場合、更新されたデータがキャッシュ7に滞留し、メインメモリ5−jには最新のデータが存在しない可能性もある。この時、複数のCPU2が同一の記憶領域を参照/更新しようとすると、データの不整合により正しい結果が得られなくなる。従って、マルチプロセッサシステムにおいては、各CPU2が最新のデータにアクセスできるように、データの一貫性(「キャッシュコヒーレンシ:Cache Coherency」と参照される)を保障ことが重要である。ここで、各セルCj内のキャッシュ7間のコヒーレンシを保つだけでなく、複数のセルC1〜Cn間のコヒーレンシも保つ必要があることに留意されるべきである。

【0005】

キャッシュコヒーレンシの方式としては、「ディレクトリ方式(Directory-based Cache Coherency Protocol)」と「スヌープ方式(Snooping Cache Coherency Protocol)」が知られている。

【0006】

ディレクトリ方式によれば、メインメモリに格納されたデータに関するキャッシングの状態を管理するテーブル(ディレクトリ)が設けられる。あるCPUがあるデータにアクセスする際、まず、そのディレクトリに格納されたキャッシング状態に関する情報が調べられる。所望の最新データがメインメモリではなく、あるキャッシュにのみ存在することが判明した場合、CPUはそのキャッシュに対してそのデータのアクセスを行う。

【0007】

一方、スヌープ方式によれば、あるCPUがあるアクセスアドレスのデータにアクセスする際、全てのキャッシュは、そのアクセスアドレスのデータのコピーを保有しているか否かを調べる。そして、各キャッシュは、必要なときに最新のデータを取得できるように自身の状態(キャッシュステータス)を変更する。例えば、MESIプロトコルによれば、「I(Invalid;無効)」、「S(Shared;最新データがメインメモリと複数のキャッシュに存在する)」、「E(Exclusive;最新データがメインメモリと自キャッシュに存在する)」、「M(Modified);最新データが自キャッシュにのみ存在する」の4つのキャッシュステータスが提供される。

【0008】

図1に示されたセルC1〜Cnのそれぞれには、上述のキャッシュコヒーレンシを実現するために、キャッシュコヒーレンシ回路3−1〜3−n及びディレクトリ4−1〜4−nが設けられている。ディレクトリ4−jは、DRAM等により実現される記憶領域であり、その中には、自セルCjのメインメモリ5−jに格納されたデータに関するキャッシングの状態を管理するための情報が格納される。より具体的には、ディレクトリ4−jには、自セルCjのメインメモリ5−jに格納されたデータに関して最新データをキャッシングしているセルを示すテーブルが格納される。最新データをキャッシングしているセルは、自セルである場合もあるし、他のセルである場合もある。キャッシュコヒーレンシ回路3は、ディレクトリ4を参照することにより、セルC1〜Cn間のコヒーレンシを保障するように構成されている。尚、各セル内のキャッシュコヒーレンシは、例えばスヌープ方式により実現される。

【0009】

【特許文献1】特開2000−67024号公報

【特許文献2】特開2000−259596号公報

【特許文献3】特開平6−110844号公報

【特許文献4】特開平11−219343号公報

【特許文献5】特開2003−216597号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

あるデータに対するリードリクエストを発行する発行元であるCPU2を搭載するセルは、以下「リクエストセルCR」と参照される。そのアクセス対象であるデータが格納されたメインメモリ5を搭載するセルは、以下「ホームセルCH」と参照される。また、そのアクセス対象であるデータの最新版(最新データ)をキャッシングしているキャッシュ7を有するセルは、以下「オーナーセルCO」と参照される。本願発明者は、ディレクトリ4を用いるマルチプロセッサシステム1において、それらリクエストセルCR、ホームセルCH、及びオーナーセルCOがそれぞれ異なる状態が発生することに着目した。

【0011】

そのような状態における従来のマルチプロセッサシステムの動作例を、図2を参照して説明する。まず、リクエストセルCRのCPU2は、アクセス対象データが格納されたメインメモリ5を有するホームセルCHに、リードリクエストを発行する(ステップS1)。ホームセルCHは、リードリクエストに応答して、自身のディレクトリ4を検索(索引)する。ディレクトリ4に格納された情報より、ホームセルCHは、対象データの最新版がオーナーセルCOのキャッシュ7に格納されていることを知る。そこで、ホームセルCHは、オーナーセルCOにスヌープリクエストを発行する(ステップS2)。

【0012】

オーナーセルCOは、スヌープリクエストに応答して、キャッシュ7から最新データを読み出す。そして、オーナーセルCOは、その最新データをホームセルCHのメインメモリ5に書き戻すために、ホームセルCHに対してライトバックを発行する(ステップS3)。オーナーセルCOがスヌープリクエストに応答して発行するライトバックは、以下、「リプライライトバック」と参照される。このリプライライトバックと同時に、オーナーセルCOは、読み出された最新データをリプライデータとしてリクエストセルCRに直接送信する(ステップS3’)。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOP(ステップS1,S2,S3’)で実現することができる(セル間のレイテンシを1HOPとする)。

【0013】

リードリクエストを発行したリクエストセルCRのCPU2は、受け取ったリプライデータを自身のキャッシュ7に格納する。その後、そのキャッシュ7のリプライデータがリプレースされた場合などにおいて、リクエストセルCRからホームセルCHに対するライトバックが発生する可能性がある(ステップS3’’)。CPU2がキャッシュ7のリプレース等により発行するライトバックは、以下、「リクエストライトバック」と参照される。ここで、上記リプライライトバック(ステップS3)とリクエストライトバック(ステップS3’’)は異なるパスで行われるため、それらの順序は必ずしも一意に定まらない。もし、ステップS3がステップS3’’よりも“後に”行われると、ホームセルCHのメインメモリ5において、リクエストセルCRによって更新された最新のデータが、オーナーセルCOからの古いデータによって上書きされてしまう。すなわち、ステップS3とステップS3’’が異なる場合、コヒーレンシを必ずしも保障できなくなるという問題がある。

【0014】

このような問題を解決するための動作例を、図3を参照して説明する。まず、リクエストセルCRがホームセルCHにリードリクエストを発行する(ステップS1)。次に、ホームセルCHがオーナーセルCOにスヌープリクエストを発行する(ステップS2)。スヌープリクエストに応答して、オーナーセルCOは、キャッシュ7から最新データを読み出し、ホームセルCHに対してリプライライトバックを発行する(ステップS3)。ここで、オーナーセルCOは、リクエストセルCRに対して最新データを直接は送信しない。次に、ホームセルCHは、リプライライトバックに応答して、最新データで自身のメインメモリ5を更新する。その後、ホームセルCHは、その最新データをリプライデータとしてリクエストセルCRに送信する(ステップS4)。

【0015】

このような処理によって、図2に示されたステップS3とステップS3’’の関係の発生が防止され、セル間のコヒーレンシを保障することが可能となる。しかしながら、図3に示された処理の場合、リードリクエストの発行からリプライデータの受け取りまでのレイテンシは4HOP(ステップS1,S2,S3,S4)となってしまう。このことは、処理速度の低下を意味する。本来、マルチプロセッサシステムにおいて複数のプロセッサが用いられるのは、処理速度を向上させるためであり、上述のような処理速度の低下は重要な問題である。

【0016】

従って、本発明の目的は、コヒーレンシの保障と処理速度の向上を両立させることである。すなわち、本発明の目的は、セル間のコヒーレンシを保障しつつ、リードリクエストに関するレイテンシを3HOP以内に抑えることができる技術を提供することにある。

【課題を解決するための手段】

【0017】

以下に、[発明を実施するための最良の形態]で使用される番号・符号を用いて、[課題を解決するための手段]を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0018】

本発明に係るマルチプロセッサシステム(1)は、同一の機能を有する複数のセル(C1〜Cn)と、それら複数のセル(C1〜Cn)間を接続するネットワーク(9)とを備える。各セル(Cj)は、プロセッサ(2)、ディレクトリ(4)、キャッシュメモリ(7)、及びメインメモリ(5)を備える。複数のセル(C1〜Cn)は、リクエストセル(CR)と、ホームセル(CH)と、オーナーセル(CO)とを含む。ホームセル(CH)のメインメモリ(5)に記憶された対象データの最新版は、オーナーセル(CO)のキャッシュメモリ(7)に格納されている。

【0019】

リクエストセル(CR)は、その対象データに対するリードリクエストをホームセル(CH)に発行する。ホームセル(CH)は、そのリードリクエストに応答して、スヌープリクエストをオーナーセル(CO)に発行する。オーナーセル(CO)は、そのスヌープリクエストに応答して、最新データをリクエストセル(CR)に直接送信する。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。

【0020】

また、オーナーセル(CO)は、スヌープリクエストに応答して、リプライライトバックをホームセル(CH)に送信する。リクエストセル(CR)は、ホームセル(CH)中の上記対象データと同じアドレスに対してリクエストライトバックを発行する。そのリクエストライトバックは、リクエストセル(CR)に含まれるキャッシュ(7)のステータスとホームセル(CH)のディレクトリ(4)のステータスとを整合させるためのディレクトリ更新情報を含む。ホームセル(CH)は、オーナーセル(CO)からのリプライライトバックをリクエストセル(CR)からのリクエストライトバックよりも後に受信した場合、そのリプライライトバックを破棄し、また、ディレクトリ更新情報に基づいてディレクトリ(4)のステータスを更新する。

【0021】

このような構成により、リクエストセル(CR)からのリクエストライトバックによって更新されたデータが、オーナーセル(CO)からのリプライライトバックによる古いデータで上書きされることが防止される。従って、リクエストライトバックとリプライライトバックの経路が異なっていても、コヒーレンシを保障することが可能となる。言い換えれば、オーナーセル(CO)がリプライデータを直接リクエストセル(CR)に送信しても、セル間のコヒーレンシが保たれる。

【発明の効果】

【0022】

本発明に係るマルチプロセッサシステムによれば、リクエストセルCR、ホームセルCH、及びオーナーセルCOがそれぞれ異なる場合においても、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPにすることが可能である。且つ、セル間のコヒーレンシを保障することも可能である。すなわち、コヒーレンシの保障とレイテンシの短縮(処理速度の向上)との両立が実現される。

【発明を実施するための最良の形態】

【0023】

添付図面を参照して、本発明の実施の形態に係るマルチプロセッサシステムを説明する。

【0024】

1.概念

図4を参照して、本実施の形態に係るマルチプロセッサシステムの動作を説明する。図4において、リクエストセルCRは、リードリクエストを発行する発行元であるCPUを搭載している。ホームセルCHは、そのアクセス対象であるデータが格納されたメインメモリを有している。オーナーセルCOは、そのアクセス対象であるデータの最新版(最新データ)をキャッシングしているキャッシュを有している。ここでは、リクエストセルCR、ホームセルCH、及びオーナーセルCOがそれぞれ異なる場合を考える。

【0025】

まず、リクエストセルCRのCPUは、アクセス対象データを有するホームセルCHに、リードリクエストを発行する(ステップS1)。ホームセルCHは、リードリクエストに応答して、自身のディレクトリを検索(索引)する。ディレクトリに格納された情報により、ホームセルCHは、対象データの最新版がオーナーセルCOのキャッシュに格納されていることを知る。よって、ホームセルCHは、オーナーセルCOにスヌープリクエストを発行する(ステップS2)。

【0026】

オーナーセルCOは、スヌープリクエストに応答して、キャッシュから最新データを読み出す。そして、オーナーセルCOは、その最新データをホームセルCHのメインメモリに書き戻すために、ホームセルCHに対してリプライライトバックを発行する(ステップS3)。このリプライライトバックと同時に、オーナーセルCOは、読み出された最新データをリプライデータとしてリクエストセルCRに直接送信する(ステップS3’)。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOP(ステップS1,S2,S3’)で実現することができる。

【0027】

リードリクエストを発行したリクエストセルCRのCPUは、受け取ったリプライデータを自身のキャッシュに格納する。その後、そのキャッシュのデータがリプレースされた場合などにおいて、リクエストセルCRは、ホームセルCHに対してリクエストライトバックを発行する(ステップS3’’)。ここで、上記リプライライトバック(ステップS3)とリクエストライトバック(ステップS3’’)は異なるパスで行われるため、それらの順序は必ずしも一意に定まらない。

【0028】

本発明に係るセルは、受け取ったリードリクエストを所定のテーブルに登録しておく機能を有している。また、本発明に係るセルは、登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、検出フラグを有効にする機能を有している。更に、本発明に係るセルは、そのリクエストライトバック(ステップS3’’)よりも後にリプライライトバック(ステップS3)を受け取った場合、上記検出フラグを参照することによって、受け取ったリプライライトバックを“破棄(discard)”する機能を備えている。言い換えれば、本発明に係るセルは、スヌープリクエストの発行(ステップS2)からリプライライトバック(ステップS3)までの期間にリクエストライトバック(ステップS3’’)を検出した場合、リプライライトバックを破棄する機能を備えている。

【0029】

これにより、ホームセルCHにおいて、リクエストセルCRからのリクエストライトバックによって更新されたデータが、オーナーセルCOからのリプライライトバックによる古いデータで上書きされることが防止される。従って、ステップS3とステップS3’’が異なっていても、コヒーレンシを保障することが可能となる。言い換えれば、オーナーセルCOがリプライデータを直接リクエストセルCRに送信しても(ステップS3’)、セル間のコヒーレンシが保たれる。逆に言えば、コヒーレンシを保障しつつ、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。すなわち、コヒーレンシの保障とレイテンシの短縮(処理速度の向上)との両立が実現される。

【0030】

2.構成

2−1.全体構成

本実施の形態に係る処理を実現するための具体的な構成例を以下に説明する。本実施の形態に係るマルチプロセッサシステムは分散共有メモリ型のマルチプロセッサシステムであり、その全体的な構成は図1に示された構成と同様である。すなわち、本実施の形態に係る分散共有メモリ型マルチプロセッサシステム1は、複数のセル(ノード)C1〜Cn(nはセル数を示す整数)と、それら複数のセルC1〜Cn間を互いに結合するクロスバースイッチ9を備えている。複数のセルC1〜Cnは、共有バスやデータリンク等のネットワークにより互いに結合されていてもよい。

【0031】

複数のセルC1〜Cnは同一の機能を有している。各々のセルCj(jは1以上n以下の整数)は、少なくとも1つのCPU(マイクロプロセッサ)2−j−1〜2−j−m(mは各セル内のCPU数を示す整数)と、メインメモリ(ローカルメモリ)5−jを備えている。それらCPU2の各々は、少なくとも1つのキャッシュメモリ(ストアインキャッシュ)7を搭載している。分散的に設けられたメインメモリ5−1〜5−nの全てによって共有メモリが構成され、その共有メモリは全てのCPU2によって参照される。

【0032】

1つのセルが複数のCPU2、すなわち複数のキャッシュ7を有している場合、セル内のローカルなキャッシュコヒーレンシは、例えば「スヌープ方式」により実現される。この場合、各CPU2に搭載されるキャッシュ7は、例えばMESIプロトコルに基づいてキャッシュステータスを管理する。MESIプロトコルによれば、「M(Modified)」、「E(Exclusive)」、「S(Shared)」、及び「I(Invalid)またはU(Uncached)」の4つのキャッシュステータスが提供される。

【0033】

M(Modified):当該キャッシュ中のデータは、当該キャッシュ内にのみ存在し、且つ、メインメモリ内のデータとは同一でない。つまり、最新データが自キャッシュにのみ存在する。

E(Exclusive):当該キャッシュ中のデータは、複数のキャッシュのうち当該キャッシュ内にのみ存在し、且つ、メインメモリ内のデータと同一である。つまり、最新データは、自キャッシュとメインメモリに存在する。

S(Shared):当該キャッシュ中のデータは、自キャッシュ及び他のCPUのキャッシュに存在し、且つ、メインメモリ内のデータと同一である。つまり、最新データは、複数のキャッシュとメインメモリに存在する。

I(Invalid)、U(Uncached):当該キャッシュ中のデータは、無効である。つまり、最新データは、自キャッシュに存在せずメインメモリに存在する。

【0034】

尚、本発明に適用されるキャッシュプロトコルは、上記MESIプロトコルに限られない。キャッシュステータスM(Modified)を提供するプロトコルであれば、如何なるキャッシュプロトコルでも適用され得る。

【0035】

また、セル内のキャッシュコヒーレンシだけでなく、図1に示された複数のセルC1〜Cn間のキャッシュコヒーレンシも保つ必要がある。本実施の形態によれば、複数のセルC1〜Cnの間のキャッシュコヒーレンシは、「ディレクトリ方式」に基づいて制御される。そのため、セルC1〜Cnのそれぞれには、キャッシュコヒーレンシ回路3−1〜3−n及びディレクトリ4−1〜4−nが設けられている。

【0036】

ディレクトリ4−jは、DRAM等により実現される記憶領域である。ディレクトリ4−jには、自セルCjのメインメモリ5−jに格納されたデータに関するキャッシングの状態を管理するための情報が格納される。より具体的には、ディレクトリ4−jには、自セルCjのメインメモリ5−jに格納された全データのステータスと、そのデータの最新版をキャッシングしているセル(すなわちオーナーセルCO)を示すテーブルが格納される。最新データをキャッシングしているオーナーセルCOは、自セルである場合もあるし、他のセルである場合もある。

【0037】

ディレクトリ4−jに格納される情報の一例が、図5に示されている。図5に示されるように、メインメモリ5−jのデータアドレス毎に、そのステータス(P,S,U)及びオーナーセル情報が対応付けられている。例えば、データアドレスA0に関するステータスは「P(Private)」である。ステータス「P」は、最新データが唯一のセルのキャッシュ7に登録されている可能性を示している。そのキャッシュ7のキャッシュステータスとしては、「M」,「E」,「S」,及び「I」の全てが許容される。また、オーナーセル情報としてはオーナーセルCOのセル番号が登録される。

【0038】

また、データアドレスA1に関するステータスは「S」である。ステータス「S(Shared)」は、最新データが複数のセルのキャッシュ7に登録されている可能性を示している。それらキャッシュ7のキャッシュステータスとしては、「S」及び「I」が許容される。この場合、オーナーセル情報としては、セルC1〜Cnに対応するビットマップが登録される。例として、セル数が3個であり(n=3)、セルC1及びC2のキャッシュ7に最新データが格納されている場合を考える。この場合、3ビットのビットマップのうちセルC1とセルC2に対応するビットが“1”にセットされ、セルC3に対応するビットは“0”にセットされる;(セルC3,セルC2,セルC1)=(0,1,1)。このようなビットマップによりオーナー情報が管理される。

【0039】

また、データアドレスA2に関するステータスは「U(Uncached)」である。ステータス「U」は、メインメモリ5−j中のデータが最新データであることを示す。この場合、オーナーセル情報としては特に何も登録されない(N/A:NotAvailable)。以上に示されたステータスP,S,Uは、メインメモリ5−jに関するキャッシュステータスと言うこともできる。

【0040】

このようなディレクトリ4−jを参照することによって、本実施の形態に係るキャッシュコヒーレンシ回路3−jは、セルC1〜Cn間のコヒーレンシ制御を行う。つまり、キャッシュコヒーレンシ回路3−jは、ディレクトリ4−jを用い、ディレクトリ方式に基づいてキャッシュコヒーレンシを保障する。以下に説明されるように、本発明は特に、このキャッシュコヒーレンシ回路3−jに特徴を有している。

【0041】

2−2.キャッシュコヒーレンシ回路

図6は、本実施の形態に係るセルCjのキャッシュコヒーレンシ回路3−jの構成を示すブロック図である。セルCjにおいて、キャッシュコヒーレンシ回路3−jは、複数のCPU2−j−1〜2−j−m、ディレクトリ4−j、及びメインメモリ5−jに接続されている。また、キャッシュコヒーレンシ回路3−jは、クロスバースイッチ9を介して他のセルと通信可能に接続されている。図6に示されるように、キャッシュコヒーレンシ回路3−jは、CPUリクエスト制御部10、クロスバーリクエスト制御部20、メインパイプ部30、ディレクトリアクセス制御部40、メインメモリアクセス制御部50、及びリプライデータ制御部60を有している。それらユニットは、互いにデータやリクエストをやりとりできるように構成されている。

【0042】

リクエストとしては、「リードリクエスト」、「スヌープリクエスト」、「リプライライトバック」、及び「リクエストライトバック」が挙げられる。

【0043】

リードリクエストには、リード対象アドレス及び当該リードリクエストの発行元が含まれる。本例において、リード対象アドレスは、ホームセルCHのメインメモリ5中のアドレスであり、発行元は、リクエストセルCRのCPU2である。つまり、リードリクエストには、少なくともリクエストセルCRとホームセルCHに関する情報が含まれていると言える。

【0044】

スヌープリクエストには、リードリクエストの情報がコピーされ、リード対象アドレス及びリードリクエストの発行元が含まれる。

【0045】

リプライライトバックには、スヌープリクエストの情報がコピーされ、リード対象アドレス及びリードリクエストの発行元が含まれる。更に、リプライライトバックには、ライトバックデータが含まれる。リード対象アドレスは、そのライトバックデータが書き戻されるライトバック対象アドレスでもある。

【0046】

リクエストライトバックには、ライトバックデータ、ライトバック対象アドレス、当該リクエストライトバックの発行元、及びディレクトリ更新情報が含まれる。本例において、ライトバック対象アドレスは、ホームセルCHのメインメモリ5中のアドレスであり、発行元は、リクエストセルCRのCPU2である。ディレクトリ更新情報は、リクエストセルCRに含まれるキャッシュ7のキャッシュステータスとホームセルCHのディレクトリ4のステータスとを整合させるための情報である。ディレクトリ更新情報には、ホームセルCHのディレクトリ4のステータスをどのように更新すればよいか示されている。

【0047】

CPUリクエスト制御部10は、CPU2からのリクエストを処理する機能を有する。より具体的には、CPUリクエスト制御部10は、CPU2が発行するリードリクエストを受信し、そのリードリクエストに含まれるリード対象アドレスに応じて、自セルのメインパイプ部30又はホームセルCHにリードリクエストを転送する。また、CPUリクエスト制御部10は、CPU2が発行するライトバックを受信し、そのライトバックに含まれるライトバック対象アドレスに応じて、自セルのメインパイプ部30又はホームセルCHにライトバックを転送する。

【0048】

更に、CPUリクエスト制御部10は、CPU2に対するスヌープリクエストを処理する機能を有する。より具体的には、CPUリクエスト制御部10は、クロスバースイッチ9又はディレクトリアクセス制御部40から受け取るスヌープリクエストを、CPU2に転送する。そして、CPUリクエスト制御部10は、スヌープ処理によってCPU2のキャッシュ7から得られるリプライデータを、リクエストセルCRに直接送信する。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシが短縮される。

【0049】

クロスバーリクエスト制御部20は、クロスバースイッチ9から受け取るリクエストを処理する機能を有する。より具体的には、クロスバーリクエスト制御部20は、クロスバースイッチ9より受信するリードリクエスト、リプライライトバック、及びリクエストライトバックをメインパイプ部30に転送する。

【0050】

メインパイプ部30は、CPUリクエスト制御部10とクロスバーリクエスト制御部20から受信したリクエストを調停し、また、ディレクトリアクセス制御部40及びメインメモリアクセス制御部50に対するリクエストを制御する機能を備える。メインパイプ部30の詳細な機能は、後の第2−3節において詳しく説明される。

【0051】

ディレクトリアクセス制御部40は、ディレクトリ4に対するアクセスを制御する。具体的には、ディレクトリアクセス制御部40は、メインパイプ部30から受信するリクエスト(リードリクエスト,リクエストライトバック,リプライライトバック)に応答して、ディレクトリ4の索引(検索)を行う。読み出されたディレクトリ4のステータスによっては、ディレクトリアクセス制御部40は、スヌープリクエストをオーナーセルCO又は自セルのCPUリクエスト制御部10に発行する。

【0052】

また、ディレクトリアクセス制御部40は、メインパイプ部30から受信するリクエストに応答して、ディレクトリ4の更新を行う。ディレクトリ4の更新方法は、読み出されるディレクトリ4の状態に応じて異なり、それは所定のルールにより規定されている(図9参照)。ただし、リプライライトバックの場合、ディレクトリ4の更新がその所定のルールと違う方式で行われることがある。そのような場合、ディレクトリアクセス制御部40は、メインパイプ部30から「更新リクエスト」を受け取る。そして、ディレクトリアクセス制御部40は、その更新リクエストが指示するように、ディレクトリ4の更新を行う。

【0053】

メインメモリアクセス制御部50は、メインメモリ5に対するアクセスを制御する。具体的には、メインメモリアクセス制御部50は、メインパイプ部30から受信したリードリクエストに応答して、メインメモリ5から対象データを読み出す。そして、メインメモリアクセス制御部50は、読み出されたデータ(読み出しデータ)をリプライデータとしてリクエストセルCR又は自セルのリプライデータ制御部60に送信する。また、メインメモリアクセス制御部50は、メインパイプ部30から受信したリプライライトバック又はリクエストライトバックに応答して、ライトバックデータをメインメモリ5に書き込む。

【0054】

リプライデータ制御部60は、メインメモリアクセス制御部50あるいはクロスバースイッチ9から受け取るリプライデータを、CPU2に転送する機能を有している。

【0055】

2−3.メインパイプ部

図7は、本実施の形態に係るメインパイプ部30の構成を示すブロック図である。図7に示されるように、メインパイプ部30は、スヌープ管理テーブル31、ライトバック検出回路32、キャンセル判定回路33、ディスカード判定回路34、及び調停制御回路35を有している。

【0056】

調停制御回路35は、CPUリクエスト制御部10からのリクエストとクロスバーリクエスト制御部20からのリクエストとの調停を行う。調停を獲得したリクエストは、スヌープ管理テーブル31、ライトバック検出回路32、キャンセル判定回路33、及びディスカード判定回路34へ転送される。

【0057】

スヌープ管理テーブル31は情報が格納されるテーブルであり、そこには複数のエントリが格納される。各エントリは、バリッドビット311、アドレス情報312、セル情報313、及びライトバック検出情報314から構成される。図8には、あるセルにおけるスヌープ管理テーブル31の一例が示されている。バリッド(V)ビット311は、当該エントリが有効エントリ(“1”)か空きエントリ(“0”)かを示す。

【0058】

アドレス情報312としては、リードリクエストが示すリード対象アドレス(例:A0,A1)が格納される。セル情報(リクエストセル情報)313としては、そのリードリクエストを発行した発行元のセル(例:C1,C3)の番号が格納される。このように、本発明に係るセルは、受け取ったリードリクエストを記憶しておく機能を有している。尚、後述されるように、複数のエントリに対応する複数のリード対象アドレス(A0,A1)は、それぞれ異なるように制御される。つまり、アドレス情報312に含まれる“あるリード対象アドレス”の数は、0個か1個である。あるリード対象アドレスに対するリードリクエストが既に登録されている場合、同じリード対象アドレスに対するリードリクエストは登録待機状態になる。

【0059】

ライトバック検出情報314は、検出フラグとディレクトリ更新情報を含む。検出フラグやディレクトリ更新情報は、登録されたアドレス情報312及びセル情報313と対応付けられている。検出フラグは、リクエストセルCRからのライトバック、すなわちリクエストライトバックが検出されたか否かを示すフラグである。検出フラグが有効(“1”)のとき、当該リード対象アドレス(A0)に対するリクエストライトバックが検出されている。一方、ディレクトリ更新情報は、ディレクトリ4がどのステータスに更新されるかを示す情報であり、検出フラグが“1”に設定される時に同時に設定される。後述されるように、このディレクトリ更新情報は、更新リクエストの生成時に用いられる。

【0060】

図7に戻り、ライトバック検出回路32は、アドレス情報比較器321、セル情報比較器322、及びAND323を有している。このライトバック検出回路32は、調停制御回路35から転送されたリクエストを受け取る。そして、ライトバック検出回路32は、上記スヌープ管理テーブル31を参照することによって、アドレス情報312が示すリード対象アドレスの各々に対する「リクエストライトバック」を検出する。

【0061】

具体的には、アドレス情報比較器321は、ライトバック(リプライライトバック又はリクエストライトバック)が示すライトバック対象アドレスと、上記スヌープ管理テーブル31中のアドレス情報312が示すリード対象アドレスとの比較を行う。そして、アドレス情報比較器321は、全てのエントリに関して一致(“1”)/不一致(“0”)を示すビットマップデータ(ビット数=総エントリ数)を出力する。尚、Vビット311が無効であるエントリは、自動的に不一致(“0”)と判定される。そのビットマップデータにおいて、全てのビットは“0”、あるいは、1つのビットだけが“1”である。ビットマップデータのうち“1”に対応するエントリは、以下「一致エントリ」と参照される。

【0062】

一方、セル情報比較器322は、リクエストライトバックを受けとった時に、そのリクエストライトバックが示す発行元の番号と、上記スヌープ管理テーブル31中のセル情報313が示すリクエストセルCRの番号との比較を行う。そして、セル情報比較器322は、全てのエントリに関して一致(“1”)/不一致(“0”)を示すビットマップデータを出力する。尚、Vビット311が無効であるエントリは、自動的に不一致(“0”)と判定される。

【0063】

AND323は、アドレス情報比較器321からのビットマップデータとセル情報比較器322からのビットマップデータとの論理積を出力する。出力されるビットマップデータにおいて、全てのビットは“0”、あるいは、1つのビットだけが“1”である。そして、ライトバック検出回路32は、そのビットマップデータのうち“1”に対応するエントリ(一致エントリ)のライトバック検出情報314を変更する。具体的には、ライトバック検出回路32は、検出フラグを無効(“0”)から有効(“1”)に変更し、また、ディレクトリ変更情報をリクエストライトバックが示すディレクトリ更新情報に設定する。つまり、ディレクトリ更新情報は、有効化された検出フラグと対応づけられてスヌープ管理テーブル31に格納される。

【0064】

AND323の出力に“1”が含まれていることは、「あるリクエストセルCRがあるアドレスに対してリードリクエストを発行し、更に、同じリクエストセルCRが同じアドレスに対してリクエストライトバックを発行したこと」を意味する。つまり、ライトバック検出回路32は、スヌープ管理テーブル31に登録されたリードリクエストと関連したリクエストライトバックを検出するための回路であると言える。ライトバック検出回路32は、そのようなリクエストライトバックを検出した場合、当該一致エントリの検出フラグを“1”にセットする。このように、本発明に係るセルは、登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、検出フラグを有効にする機能を有している。スヌープ管理テーブル31に予め格納されるリードリクエストに関する情報(アドレス情報312,セル情報313)は、後に受け取るかもしれないリクエストライトバックを検出するための情報であると言える。

【0065】

また、ライトバック検出回路32は、リプライライトバックを受け取った場合、アドレス情報比較器321から出力されるアドレス一致エントリ(ビットマップデータ)をキャンセル判定回路33及びディスカード判定回路34に出力する。また、ライトバック検出回路32は、リプライライトバックを受け取った場合、そのアドレス一致エントリに関するVビット311を無効化(“0”)する。つまり、ライトバック検出回路32は、リプライライトバックに応答して、そのリプライライトバックに関連するエントリを初期化する。

【0066】

次に、キャンセル判定回路33について説明する。上述の通り、スヌープ管理テーブル31において、あるリード対象アドレスに対するリードリクエストが既に登録されている場合、同じリード対象アドレスに対するリードリクエストは登録待機状態に設定される。そのためにキャンセル判定回路33が設けられている。キャンセル判定回路33は、調停制御回路35からのリードリクエスト、及び上記ライトバック検出回路32のアドレス情報比較器321からの出力を受け取る。アドレス情報比較器321からアドレス一致エントリが出力された場合、すなわち、スヌープ管理テーブル31に既に登録されているリード対象アドレスと同一アドレスへのリードリクエストが検出された場合、キャンセル判定回路33は、CPUリクエスト制御部10又はクロスバーリクエスト制御部20に対して、リードリクエストの再発行を要求する。そして、スヌープ管理テーブル31に空きエントリができるまで、同じ動作が繰り返される。これにより、そのリードリクエストは、登録待機状態となる。

【0067】

ディスカード判定回路34は、調停制御回路35から転送されたリクエスト(リードリクエスト,リクエストライトバック,リプライライトバック)を受け取る。受け取ったリクエストがリードリクエストの場合、ディスカード判定回路34は、そのリードリクエストをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。また、そのリクエストがリクエストライトバックの場合、ディスカード判定回路34は、そのリクエストライトバックをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。

【0068】

また、受け取ったリクエストがリプライライトバックの場合、ディスカード判定回路34は、アドレス情報比較器321からの出力(ビットマップデータ)を受け取り、そのビットマップデータが示すアドレス一致エントリのライトバック検出情報314を参照する。参照されたライトバック検出情報314の検出フラグが“0”の場合、ディスカード判定回路34は、リプライライトバックをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。一方、検出フラグが“1”の場合、それはリクエストライトバックの後にリプライライトバックが入力されたことを意味する。この場合、ディスカード判定回路34は、受け取ったリプライライトバックを破棄(ディスカード)する。よって、リプライライトバックは、メインメモリアクセス制御部50には出力されない。ただし、ディスカード判定回路34は、ディレクトリ4のステータスを更新するための「更新リクエスト」をディレクトリアクセス制御部40に発行する。その更新リクエストの指示内容は、参照されたライトバック検出情報314中の「ディレクトリ更新情報」によって決定される。

【0069】

以上に説明されたように、本実施の形態に係るメインパイプ部30は、(1)リクエストセルCRからのリードリクエストを登録する機能、(2)登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、その検出を記憶しておく機能、及び(3)ディレクトリアクセス制御部40及びメインメモリアクセス制御部50に対するリクエストを制御する機能;具体的には、リクエストライトバックよりも後にリプライライトバックを受け取った場合、そのリプライライトバックを破棄し、ディレクトリ4を更新する機能、を備えている。上記(1)の機能は、スヌープ管理テーブル31により提供される。上記(2)の機能は、ライトバック検出回路32及びスヌープ管理テーブル31により提供される。上記(3)の機能は、ディスカード判定回路34及びスヌープ管理テーブル31により提供される。これにより、上述の図4に示された動作が実現される。

【0070】

尚、図9には、各リクエストに対するディレクトリ4の索引時のステータス及び更新後のステータスが要約的に示されている。図9に示された要約は、以下の動作例の説明において適宜参照される。

【0071】

3.システムの動作例

既出の図6、図7、図9、及び以下に示される図面を参照しながら、本実施の形態に係るマルチプロセッサシステム1の動作例を説明する。本動作例において、リクエストセルCR、ホームセルCH、及びオーナーセルCOは互いに異なっているとする。例えば、リクエストセルCRはセルC1、ホームセルCHはセルC2、オーナーセルCOはセルC3である。つまり、リクエストセルC1のCPU2(例えばCPU2−1−1)による読み出し対象のアドレスは、ホームセルC2に搭載されたメインメモリ5−2中のアドレスであり、そのアドレスに対応した最新データは、オーナーセルC3に搭載されたCPU2(例えばCPU2−3−1)中のキャッシュ7に格納されている。

【0072】

図10は、本動作例における処理フローを概念的に示している。また、図11は、リクエストセルC1のCPU2−1−1のキャッシュステータス、ホームセルC2のキャッシュコヒーレンシ回路3−2のスヌープ管理テーブル31及びディレクトリ4−2の内容、及びオーナーセルC3のCPU2−3−1のキャッシュステータスの遷移を示している。初期状態において、リクエストセルC1のCPU2−1−1のキャッシュステータスは“I(Invalid)”、オーナーセルC3のCPU2−3−1のキャッシュステータスは“M(Modified)”である。また、ホームセルC2のディレクトリ4−2において、リード対象アドレスA0に対するステータスは“P”、オーナーセル情報は“セルC3”をそれぞれ示すとする。

【0073】

ステップS11:リクエストセルC1:リードリクエストの発行

まず、リクエストセルC1のCPU2−1−1が、ホームセルC2のメインメモリ5−2中のアドレスA0に対して「リードリクエスト」を発行する。このリードリクエストには、リード対象アドレスA0及び発行元(CPU2−1−1)が含まれている。CPU2−1−1がリードリクエストを発行すると、リクエストセルC1のCPU2−1−1〜CPU2−1−mのそれぞれにおいてスヌープ処理が実行される。具体的には、CPU2−1−1〜CPU2−1−mのそれぞれのキャッシュ7が、自身がリード対象アドレスA0のデータを格納しているかどうか調べる。

【0074】

キャッシュヒットが無い場合、リードリクエストは、リクエストセルC1のキャッシュコヒーレンシ回路3−1に送信される。キャッシュコヒーレンシ回路3−1のCPUリクエスト制御部10は、CPU2−1−1からのリードリクエストを受け取る。そのCPUリクエスト制御部10は、リードリクエストに含まれるリード対象アドレスA0に基づいて、アクセス対象となるホームセルC2を判別する。ホームセルC2は、リード対象アドレスA0により一意に決定される。そして、CPUリクエスト制御部10は、クロスバースイッチ9を介してホームセルC2にリードリクエストを送信する。

【0075】

ステップS12:ホームセルC2:スヌープ管理テーブル31の更新

ホームセルC2のキャッシュコヒーレンシ回路3−2のクロスバーリクエスト制御部20は、リクエストセルC1からクロスバースイッチ9を通してリードリクエストを受け取る。そして、クロスバーリクエスト制御部20は、受け取ったリードリクエストをメインパイプ部30に転送する。メインパイプ部30の調停制御回路35は、そのリードリクエストとCPUリクエスト制御部10からのリクエストとの調停を行う。

【0076】

クロスバーリクエスト制御部20からのリードリクエストが調停を獲得すると、そのリードリクエストは、スヌープ管理テーブル31、ライトバック検出回路32、キャンセル判定回路33、及びディスカード判定回路34に転送される。そして、メインパイプ部30は、スヌープ管理テーブル31の空きエントリに、そのリードリクエストを登録する。この場合、図11に示されるように、リードリクエストが登録されるエントリに関して、Vビット311は“0”から“1”に変更され、アドレス情報312としてリード対象アドレスA0が登録され、セル情報313としてリクエストセルC1の番号が登録され、ライトバック検出情報314の検出フラグは“0”にセットされる。

【0077】

尚、スヌープ管理テーブル31の有効エントリ(Vビット311が“1”のエントリ)に同一アドレスA0に対するリードリクエストが既に存在する場合、アドレス情報比較器321(図7参照)は、アドレス一致エントリを検出する。アドレス一致エントリが検出されると、キャンセル判定回路33は、クロスバーリクエスト制御部20にリードリクエストの再発行を要求する。その結果、そのリードリクエストは登録待ち状態になる。これにより、スヌープ管理テーブル31に同一アドレスに対する複数のリードリクエストが格納されることが防止される。

【0078】

続いて、メインパイプ部30(ディスカード判定回路34)は、ディレクトリアクセス制御部40及びメインメモリアクセス制御部50にリードリクエストを送信する。

【0079】

ステップS13:ホームセルC2:ディレクトリアクセス

ホームセルC2のディレクトリアクセス制御部40は、受け取ったリードリクエストに応答して、まずディレクトリ4−2の索引を行う。図11に示されるように、ディレクトリ4−2において、リード対象アドレスA0に対するステータスは“P”、オーナーセル情報は“セルC3”である。この場合、ディレクトリアクセス制御部40は、クロスバースイッチ9を通してオーナーセルC3に「スヌープリクエスト」を発行する。このスヌープリクエストには、リードリクエストの情報がコピーされ、リード対象アドレスA0及び当該リードリクエストの発行元(リクエストセルC1のCPU2−1−1)が含まれる。

【0080】

また、ディレクトリアクセス制御部40は、リードリクエストに応答して、ディレクトリ4−2の更新を行う。図9を参照して、リードリクエストに対する索引時にステータスが“P”である場合、ステータスは更新されない(NC:No Change)。更に、ディレクトリアクセス制御部40は、メインメモリアクセス制御部50に、ステータス情報“P”とオーナーセル情報“C3”を出力する。

【0081】

ステップS14:ホームセルC2:メモリアクセス

一方、ホームセルC2のメインメモリアクセス制御部50は、受け取ったリードリクエストに応答して、メインメモリ5−2中のリード対象アドレスA0からデータを読み出す。そして、メインメモリアクセス制御部50は、読み出されたデータに、ディレクトリアクセス制御部40から受け取ったステータス情報“P”とオーナーセル情報“C3”を付与することによって、リプライデータDRを生成する。メモリアクセス制御部50は、そのリプライデータDRを、クロスバースイッチ9を介してリクエストセルC1に送信する。

【0082】

ステップS15:リクエストセルC1:リプライデータDRの受信

リクエストセルC1のリプライデータ制御部60は、クロスバースイッチ9からリプライデータDRを受け取る。そのリプライデータDRには、ステータスが“P”であることと、オーナーセルがセルC3であることが示されている。この場合、リプライデータ制御部60は、オーナーセルC3からのリプライデータを待ち合わせる。

【0083】

ステップS16:オーナーセルC3:スヌープ処理、リプライライトバックの発行

オーナーセルC3のCPUリクエスト制御部10は、ホームセルC2が発行したスヌープリクエストを受け取る。そして、CPUリクエスト制御部10は、自セルC3のCPU2−3−1〜2−3−mにスヌープリクエストを発行する。CPU2−3−1〜2−3−mのそれぞれのキャッシュ7は、スヌープ処理を実行する。その結果、キャッシュステータスが“M”であるCPU2−3−1は、「リプライライトバック」をCPUリクエスト制御部10に発行する。リプライライトバックには、スヌープリクエストの情報がコピーされ、リード対象アドレスA0及びリードリクエストの発行元(リクエストセルC1)が含まれる。更に、リプライライトバックには、キャッシュ7から読み出されたデータ(ライトバックデータ)が含まれる。リード対象アドレスA0は、そのライトバックデータが書き戻されるライトバック対象アドレスA0でもある。また、リプライライトバックの発行に応答して、CPU2−3−1のキャッシュ7のキャッシュステータスは、“M”から“I”に変更される。

【0084】

オーナーセルC3のCPUリクエスト制御部10は、CPU2−3−1からリプライライトバックを受け取ると、そのリプライライトバックをクロスバースイッチ9を介してホームセルC2に送信する(ステップS16−1)。ホームセルC2は、ライトバック対象アドレスA0により一意に決定される。

【0085】

更に、オーナーセルC3のCPUリクエスト制御部10は、キャッシュ7から読み出されたデータ(リプライデータDR’)をリクエストセルC1へ直接送信する(ステップS16−2)。その送信先(リクエストセルC1)は、スヌープリクエストあるいはリプライライトバックに含まれるリードリクエストの発行元情報により決定することができる。

【0086】

ステップS17:リクエストセルC1:リプライデータDR’の受信

リクエストセルC1のリプライデータ制御部60は、オーナーセルC3からクロスバースイッチ9を通してリプライデータDR’を直接受け取る。この時、リプライデータ制御部60は、上記ステップS15で受け取ったリプライデータDRを破棄する。そして、リプライデータ制御部60は、オーナーセルC3から受け取ったリプライデータDR’を、リードリクエストの発行元であるCPU2−1−1に送信する。CPU2−1−1は、リプライデータDR’を受け取ると、そのリプライデータDR’を自身のキャッシュ7に登録する。この時、CPU2−1−1のキャッシュ7のキャッシュステータスは、“I”から“E”に変更される。以上に説明されたように、リードリクエストの発行からリプライデータDR’の受け取りまでが3HOPで実現される。

【0087】

ステップS18:リクエストセルC1:リクエストライトバックの発行

ステップS17の後、CPU2−1−1は、キャッシュ7に格納されたデータを新たなデータで書き換える、すなわち、キャッシュ7に格納されたデータを更新する。この時、そのキャッシュ7のステータスは、“E”から“M”に一旦変更される。更に、CPU2−1−1は、キャッシュ7のデータ更新に応答して、「リクエストライトバック」をCPUリクエスト制御部10に発行する。リクエストライトバックの発行に応答して、CPU2−1−1のキャッシュ7のキャッシュステータスは、“M”から“I”に変更される。このリクエストライトバックには、キャッシュ7に格納された最新データ(ライトバックデータ)、ライトバック対象アドレスA0、発行元情報(リクエストセルC1のCPU2−1−1)、及びディレクトリ更新情報が含まれている。キャッシュステータスが“I”に変更されている場合、ディレクトリ更新情報は「U更新」に設定される。

【0088】

参考のため、CPU2−1−1のキャッシュ7のステータスが“E”から“M”に変更された後、別のCPU2−1−2がそのデータに対するリードリクエストを発行した場合を考える。この場合、スヌープ処理により、CPU2−1−1のキャッシュ7に格納されたデータが、CPU2−1−2のキャッシュ7に移動する。CPU2−1−1に関するキャッシュステータスは“M”から“I”に変更される一方、CPU2−1−2に関するキャッシュステータスは“I”から“E”に変更される。この場合、セルC1におけるキャッシュステータスに“E”が含まれているため、CPU2−1−1が発行するリクエストライトバックのディレクトリ更新情報は「NC更新」に設定されるとよい。

【0089】

キャッシュコヒーレンシ回路3−1のCPUリクエスト制御部10は、CPU2−1−1からリクエストライトバック(U更新)を受け取ると、ライトバック対象アドレスA0に基づいて、アクセス先となるホームセルC2を判別する。そして、CPUリクエスト制御部10は、そのリクエストライトバックをクロスバースイッチ9を介してホームセルC2に送信する。

【0090】

ステップS19:ホームセルC2:リクエストライトバックの検出

ホームセルC2のキャッシュコヒーレンシ回路3−2のクロスバーリクエスト制御部20は、リクエストセルC1からリクエストライトバックを受け取る。そして、クロスバーリクエスト制御部20は、受け取ったリクエストライトバックをメインパイプ部30に転送する。メインパイプ部30の調停制御回路35は、そのリクエストライトバックとCPUリクエスト制御部10からのリクエストとの調停を行う。

【0091】

クロスバーリクエスト制御部20からのリクエストライトバックが調停を獲得すると、そのリクエストライトバックは、ライトバック検出回路32及びディスカード判定回路34に転送される。ライトバック検出回路32において、アドレス情報比較器321は、図11に示されたスヌープ管理テーブル31のアドレス情報312(“A0”)と、リクエストライトバックが示すライトバック対象アドレスA0とが一致していることを検出する。また、セル情報比較器322は、図11に示されたスヌープ管理テーブル31のセル情報313(“C1”)と、リクエストライトバックが示す発行元情報(“C1”)とが一致していることを検出する。そして、AND323の演算により、一致エントリが検出される。この場合、ライトバック検出回路32は、スヌープ管理テーブル31中の当該一致エントリのライトバック検出情報314を更新する。具体的には、当該一致エントリの検出フラグが“1”にセットされる。また、リクエストライトバックに含まれるディレクトリ更新情報(U更新)に応じて、当該一致エントリのディレクトリ更新情報は「U」にセットされる。

【0092】

以上に説明されたように、ホームセルC2において、アドレスA0に対するリクエストライトバックが検出されたことが記憶される。また、スヌープ管理テーブル31の更新が行われる。続いて、メインパイプ部30(ディスカード判定回路34)は、ディレクトリアクセス制御部40及びメインメモリアクセス制御部50にリクエストライトバックを送信する。

【0093】

ステップS20:ホームセルC2:ディレクトリアクセス、メモリアクセス

ホームセルC2のメインメモリアクセス制御部50は、受け取ったリクエストライトバックに応答して、メインメモリ5−2中のライトバック対象アドレスA0に、ライトバックデータを書き戻す。

【0094】

また、ディレクトリアクセス制御部40は、受け取ったリクエストライトバックに応答して、ディレクトリ4−2の索引・更新を行う。図11に示されるように、ディレクトリ4−2において、オーナーセル情報は“セルC3”である。つまり、ディレクトリ4−2の索引の結果、リクエストライトバックが示す発行元情報(リクエストセルC1)はディレクトリ4−2中のオーナーセル情報(オーナーセルC3)と異なっていることが分かる。この場合、図9を参照して、ディレクトリアクセス制御部40は、ディレクトリ4−2のステータス及びオーナーセル情報を更新しない(NC:No Change)。

【0095】

ステップS21:ホームセルC2:リプライライトバックの破棄

ホームセルC2は、ステップS19による「リクエストライトバック」よりも後に、上記ステップS16−1による「リプライライトバック」を受け取るとする。ホームセルC2のキャッシュコヒーレンシ回路3−2のクロスバーリクエスト制御部20は、オーナーセルC3からリプライライトバックを受け取る。そして、クロスバーリクエスト制御部20は、受け取ったリプライライトバックをメインパイプ部30に転送する。メインパイプ部30の調停制御回路35は、そのリプライライトバックとCPUリクエスト制御部10からのリクエストとの調停を行う。

【0096】

クロスバーリクエスト制御部20からのリプライライトバックが調停を獲得すると、そのリプライライトバックは、ライトバック検出回路32及びディスカード判定回路34に転送される。ライトバック検出回路32において、アドレス情報比較器321は、リプライライトバックが示すライトバック対象アドレスA0とスヌープ管理テーブル31のアドレス情報312との比較を行う。そして、ライトバック検出回路32は、ライトバック対象アドレスA0と一致するアドレス一致エントリを、ディスカード判定回路34に通知する。

【0097】

ディスカード判定回路34は、リプライライトバックを受け取った場合、スヌープ管理テーブル31中の当該アドレス一致エントリのライトバック検出情報314を読み出す。図11に示されるように、当該アドレス一致エントリの検出フラグは“1”にセットされている。これは、リクエストライトバックが既に行われていることを意味する。これにより、ディスカード判定回路34は、リプライライトバックよりも前にリクエストライトバックが行われたことを認識する。この場合、ディスカード判定回路34は、リプライライトバックを破棄(ディスカード)し、メインメモリアクセス制御部50に対してリプライライトバックを出力しない。その結果、リクエストセルCRからのリクエストライトバックによって更新されたデータが、オーナーセルCOからのリプライライトバックによる古いデータで上書きされることが防止される。

【0098】

ステップS22:ホームセルC2:ディレクトリの更新

また、ディスカード判定回路34は、ライトバック検出情報314を参照した際、当該アドレス一致エントリのディレクトリ更新情報が「U」にセットされていることを検知する(図11参照)。この場合、ディスカード判定回路34は、ディレクトリアクセス制御部40に「更新リクエスト(U更新)」を発行する。ディレクトリアクセス制御部40は、受け取った更新リクエストに応答して、ディレクトリ4−2の更新を行う。図9に示された規定によるとリプライライトバックの場合は「NC」であるが、今回の場合、「更新リクエスト(U更新)」が優先される。よって、ディレクトリアクセス制御部40は、更新リクエストに応じて、ディレクトリ4−2のステータスを“P”から“U”に変更し、オーナーセル情報を消去する。図11に示されるように、セルC1のキャッシュステータス(“I”)、セルC2のディレクトリ4−2のステータス(“U”)、及びセルC3のキャッシュステータス(“I”)の間に不整合が無いことが分かる。すなわち、セル間のコヒーレンシが保たれている。

【0099】

尚、リプライライトバックを受け取った場合、ライトバック検出回路32は、アドレス情報比較器321からの出力に基づいて、スヌープ管理テーブル31中のアドレス一致エントリを初期化する。具体的には、ライトバック検出回路32は、そのアドレス一致エントリに関するVビット311を“0”に戻す。これにより、一連の処理が終わる。

【0100】

また、ホームセルC2がリプライライトバックをリクエストライトバックよりも前に受け取った場合の処理は、次の通りである。ライトバック検出情報314の検出フラグは“0”のままなので、ディスカード判定回路34は、リプライライトバックをディレクトリアクセス制御部40及びメインメモリアクセス制御部50に出力する。これにより、通常通りライトバックが行われ、ライトバックデータがアドレスA0に書き戻される。また、図9に示されたルールに従い、ディレクトリ4−2のステータスは“P”のまま維持され、オーナーセル情報は「セルC3」から「セルC1(リクエストセル)」に変更される。セルC1は、リプライライトバックに含まれる「リクエストセルの発行元情報」により指定される。また、リプライライトバックによって、当該エントリは初期化される。従って、その後にリクエストライトバックが受信されても、ライトバック検出情報314の検出フラグは有効化されない。リクエストライトバックがそのまま実行されるのみである。

【0101】

4.まとめ

以上に説明されたように、本発明によれば、リクエストセルCRとホームセルCHとオーナーセルCOがそれぞれ異なる状態においても、コヒーレンシの保障とレイテンシの短縮が実現される。

【0102】

リクエストセルCRからオーナーセルCOのキャッシュ7に対するアクセスが発生した場合、オーナーセルCOは、メインメモリ5へのライトバックと同時に、リクエストセルCRに最新データを返却する。これにより、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。

【0103】

また、セルCjに搭載されるキャッシュコヒーレンシ回路3−jにスヌープ管理テーブル31、ライトバック検出回路32、及びディスカード判定回路34を設けることにより、各セルCjには次の機能が提供される:(1)リクエストセルCRからのリードリクエストを登録する機能、(2)登録されたリードリクエストの対象と同じアドレスに対するリクエストライトバックを検出したときに、検出フラグを有効にする機能、(3)そのリクエストライトバックよりも後にリプライライトバックを受け取った場合、上記検出フラグを参照することによって、受け取ったリプライライトバックを破棄する機能、及び(4)リプライライトバックの破棄と共に、ディレクトリを更新する機能。これらの機能により、リクエストセルCRからのリクエストライトバックによって更新されたデータが、オーナーセルCOからのリプライライトバックによる古いデータで上書きされることが防止される。従って、リクエストライトバックとリプライライトバックの経路が異なっていても、コヒーレンシを保障することが可能となる。言い換えれば、オーナーセルCOがリプライデータDR’を直接リクエストセルCRに送信しても、セル間のコヒーレンシが保たれる。

【0104】

以上に説明されたように、本発明によれば、コヒーレンシを保障しつつ、リードリクエストの発行からリプライデータの受け取りまでのレイテンシを3HOPで実現することが可能となる。すなわち、コヒーレンシの保障とレイテンシの短縮(処理速度の向上)との両立が実現される。本発明は、リクエストセルCRとホームセルCH間の距離(HOP数)と、ホームセルCHとオーナーセルCO間の距離が遠くなるような、大規模なマルチプロセッサシステムにおいては、さらに効果が大きくなる。

【図面の簡単な説明】

【0105】

【図1】図1は、分散共有メモリ型マルチプロセッサシステムの構成を示すブロック図である。

【図2】図2は、従来のマルチプロセッサシステムの動作を示す概念図である。

【図3】図3は、従来のマルチプロセッサシステムの動作を示す概念図である。

【図4】図4は、本発明に係るマルチプロセッサシステムの動作を示す概念図である。

【図5】図5は、本発明の実施の形態に係るディレクトリに格納される情報の一例を示すテーブルである。

【図6】図6は、本実施の形態に係るキャッシュコヒーレンシ回路の構成を示すブロック図である。

【図7】図7は、本実施の形態に係るメインパイプ部の構成を示すブロック図である。

【図8】図8は、本実施の形態に係るスヌープ管理テーブルの一例を示すテーブルである。

【図9】図9は、本実施の形態に係るディレクトリの更新方法を要約的に示すテーブルである。

【図10】図10は、本実施の形態に係るマルチプロセッサシステムの動作フローの一例を示す図である。

【図11】図11は、キャッシュステータス、スヌープ管理テーブル、及びディレクトリに格納される情報の遷移を示すテーブルである。

【符号の説明】

【0106】

1 分散共有メモリ型マルチプロセッサシステム

2 CPU

3 キャッシュコヒーレンシ回路

4 ディレクトリ

5 メインメモリ

7 キャッシュ

9 クロスバースイッチ

C セル

CR リクエストセル

CH ホームセル

CO オーナーセル

10 CPUリクエスト制御部

20 クロスバーリクエスト制御部

30 メインパイプ部

31 スヌープ管理テーブル

311 Vビット

312 アドレス情報

313 セル情報

314 ライトバック検出情報

32 ライトバック検出回路

321 アドレス情報比較器

322 セル情報比較器

323 AND

33 キャンセル判定回路

34 ディスカード判定回路

35 調停制御回路

40 ディレクトリアクセス制御部

50 メインメモリアクセス制御部

60 リプライデータ制御部

【特許請求の範囲】

【請求項1】

同一の機能を有する複数のセルと、

前記複数のセル間を接続するネットワークと

を具備し、

前記複数のセルの各々は、プロセッサ、キャッシュメモリ、及びメインメモリを備え、

前記複数のセルは、

リクエストセルとしての第1セルと、

ホームセルとしての第2セルと、

オーナーセルとしての第3セルと

を含み、

前記第2セルの前記メインメモリに記憶された対象データの最新版は、前記第3セルの前記キャッシュメモリに格納され、

前記第1セルは、前記対象データに対するリードリクエストを前記第2セルに発行し、

前記第2セルは、前記リードリクエストに応答して、スヌープリクエストを前記第3セルに発行し、

前記第3セルは、前記スヌープリクエストに応答して、前記対象データを前記第1セルに直接送信し、リプライライトバックを前記第2セルに送信し、

前記第1セルは、前記第2セル中の前記対象データと同じアドレスに対してリクエストライトバックを発行し、

前記第2セルは、前記第3セルからの前記リプライライトバックを前記第1セルからの前記リクエストライトバックよりも後に受信した場合、前記リプライライトバックを破棄する

マルチプロセッサシステム。

【請求項2】

請求項1に記載のマルチプロセッサシステムであって、

前記各々のセルは、更にディレクトリを備え、

前記第1セルが発行する前記リクエストライトバックは、前記第1セルに含まれる前記キャッシュのステータスと前記第2セルの前記ディレクトリのステータスとを整合させるためのディレクトリ更新情報を含み、

前記第2セルは、前記リプライライトバックを前記リクエストライトバックよりも後に受信した場合、前記リプライライトバックを破棄すると共に、前記ディレクトリ更新情報に基づいて前記ディレクトリのステータスを更新する

マルチプロセッサシステム。

【請求項3】

請求項2に記載のマルチプロセッサシステムであって

前記各々のセルは、更にスヌープ管理テーブルを備え、

前記リードリクエストは、当該リクエストの発行元を示すリクエストセル情報と、リード対象アドレスを示すアドレス情報とを含み、

前記第2セルは、前記リードリクエストに応答して、前記リクエストセル情報と前記アドレス情報を前記スヌープ管理テーブルに登録する

マルチプロセッサシステム。

【請求項4】

請求項3に記載のマルチプロセッサシステムであって、

前記各々のセルは、更にライトバック検出回路を備え、

前記スヌープ管理テーブルは、前記登録されたリクエストセル情報及びアドレス情報に対応付けられた検出フラグを有し、

前記第2セルの前記ライトバック検出回路は、前記登録されたアドレス情報が示す前記リード対象アドレスと同じアドレスに対する前記リクエストライトバックを検出し、前記リクエストライトバックが検出された場合、前記検出フラグを有効にする

マルチプロセッサシステム。

【請求項5】

請求項4に記載のマルチプロセッサシステムであって、

前記リクエストライトバックは、当該リクエストの発行元を示すリクエストライトバックセル情報と、ライトバック対象アドレスを示すライトバックアドレス情報とを含み、

前記第2セルの前記ライトバック検出回路は、前記リクエストライトバックセル情報及び前記ライトバックアドレス情報のそれぞれを、前記スヌープ管理テーブルに登録されたリクエストセル情報及びアドレス情報と比較することによって、前記リード対象アドレスと同じアドレスに対する前記リクエストライトバックを検出する

マルチプロセッサシステム。

【請求項6】

請求項4又は5に記載のマルチプロセッサシステムであって、

前記各々のセルは、更にディスカード判定回路を有し、

前記第2セルの前記ディスカード判定回路は、前記第3セルからの前記リプライライトバックに応答して前記検出フラグを参照し、前記検出フラグが有効化されている場合、前記リプライライトバックを破棄する

マルチプロセッサシステム。

【請求項7】

請求項6に記載のマルチプロセッサシステムであって、

前記第2セルの前記ライトバック検出回路は、前記検出フラグを有効にすると共に、前記リクエストライトバックが示す前記ディレクトリ更新情報を、前記有効化された検出フラグと対応づけて前記スヌープ管理テーブルに格納し、

前記第2セルの前記ディスカード判定回路は、前記第3セルからの前記リプライライトバックに応答して前記検出フラグと前記ディレクトリ更新情報を参照し、前記リプライライトバックを破棄すると共に、前記ディレクトリ更新情報に基づいて前記ディレクトリのステータスを更新させる

マルチプロセッサシステム。

【請求項8】

請求項3乃至7のいずれかに記載のマルチプロセッサシステムであって、

前記第2セルは、前記リプライライトバックに応答して、前記スヌープ管理テーブル中の前記登録されたリクエストセル情報とアドレス情報に対応するエントリを初期化する

マルチプロセッサシステム。

【請求項9】

請求項2乃至8のいずれかに記載のマルチプロセッサシステムであって、

前記ディレクトリには、自セルの前記メインメモリの全アドレスのデータに関して、最新のデータを有するセルを示す情報が含まれ、

前記リードリクエストは、当該リクエストの発行元を示すリクエストセル情報と、リード対象アドレスを示すアドレス情報とを含み、

前記第2セルは、前記リードリクエストに応答して前記ディレクトリを参照し、前記リード対象アドレスのデータの最新版が前記第3セルに格納されていることを認識し、前記スヌープリクエストを前記第3セルに発行する

マルチプロセッサシステム。

【請求項10】

請求項9に記載のマルチプロセッサシステムであって、

前記発行されたスヌープリクエストは、前記リードリクエストに含まれる情報を含み、

前記第3セルは、前記スヌープリクエストに含まれる前記リクエストセル情報に基づいて、前記対象データの送信先が前記第1セルであることを認識し、前記キャッシュから読みだされた前記対象データを前記第1セルに直接送信する

マルチプロセッサシステム。

【請求項11】

マルチプロセッサシステムの動作方法であって、

前記マルチプロセッサシステムは、同一の機能を有する複数のセルを具備し、

前記複数のセルの各々は、プロセッサ、キャッシュメモリ、及びメインメモリを備え、

前記複数のセルは、

リクエストセルとしての第1セルと、

ホームセルとしての第2セルと、

オーナーセルとしての第3セルと

を含み、

前記第2セルの前記メインメモリに記憶された対象データの最新版は、前記第3セルの前記キャッシュメモリに格納され、

前記動作方法は、

(A)前記第1セルが、前記対象データに対するリードリクエストを前記第2セルに発行するステップと、

(B)前記第2セルが、前記リードリクエストに応答して、スヌープリクエストを前記第3セルに発行するステップと、

(C)前記第3セルが、前記スヌープリクエストに応答して、前記対象データを前記第1セルに直接送信するステップと、

(D)前記第3セルが、前記スヌープリクエストに応答して、リプライライトバックを前記第2セルに発行するステップと、

(E)前記第1セルが、前記第2セル中の前記対象データと同じアドレスに対してリクエストライトバックを発行するステップと、

(F)前記第2セルが、前記第3セルからの前記リプライライトバックを前記第1セルからの前記リクエストライトバックよりも後に受信した場合、前記リプライライトバックを破棄するステップと

を有する

マルチプロセッサシステムの動作方法。

【請求項12】

請求項11に記載のマルチプロセッサシステムの動作方法であって、

前記各々のセルは、更にディレクトリを備え、

前記(E)ステップにおいて、前記リクエストライトバックは、前記第1セルに含まれる前記キャッシュのステータスと前記第2セルの前記ディレクトリのステータスとを整合させるためのディレクトリ更新情報を含み、

前記(F)ステップにおいて、前記第2セルは、前記リプライライトバックを破棄すると共に、前記ディレクトリ更新情報に基づいて前記ディレクトリのステータスを更新する

マルチプロセッサシステムの動作方法。

【請求項1】

同一の機能を有する複数のセルと、

前記複数のセル間を接続するネットワークと

を具備し、

前記複数のセルの各々は、プロセッサ、キャッシュメモリ、及びメインメモリを備え、

前記複数のセルは、

リクエストセルとしての第1セルと、

ホームセルとしての第2セルと、

オーナーセルとしての第3セルと

を含み、

前記第2セルの前記メインメモリに記憶された対象データの最新版は、前記第3セルの前記キャッシュメモリに格納され、

前記第1セルは、前記対象データに対するリードリクエストを前記第2セルに発行し、

前記第2セルは、前記リードリクエストに応答して、スヌープリクエストを前記第3セルに発行し、

前記第3セルは、前記スヌープリクエストに応答して、前記対象データを前記第1セルに直接送信し、リプライライトバックを前記第2セルに送信し、

前記第1セルは、前記第2セル中の前記対象データと同じアドレスに対してリクエストライトバックを発行し、

前記第2セルは、前記第3セルからの前記リプライライトバックを前記第1セルからの前記リクエストライトバックよりも後に受信した場合、前記リプライライトバックを破棄する

マルチプロセッサシステム。

【請求項2】

請求項1に記載のマルチプロセッサシステムであって、

前記各々のセルは、更にディレクトリを備え、

前記第1セルが発行する前記リクエストライトバックは、前記第1セルに含まれる前記キャッシュのステータスと前記第2セルの前記ディレクトリのステータスとを整合させるためのディレクトリ更新情報を含み、

前記第2セルは、前記リプライライトバックを前記リクエストライトバックよりも後に受信した場合、前記リプライライトバックを破棄すると共に、前記ディレクトリ更新情報に基づいて前記ディレクトリのステータスを更新する

マルチプロセッサシステム。

【請求項3】

請求項2に記載のマルチプロセッサシステムであって

前記各々のセルは、更にスヌープ管理テーブルを備え、

前記リードリクエストは、当該リクエストの発行元を示すリクエストセル情報と、リード対象アドレスを示すアドレス情報とを含み、

前記第2セルは、前記リードリクエストに応答して、前記リクエストセル情報と前記アドレス情報を前記スヌープ管理テーブルに登録する

マルチプロセッサシステム。

【請求項4】

請求項3に記載のマルチプロセッサシステムであって、

前記各々のセルは、更にライトバック検出回路を備え、

前記スヌープ管理テーブルは、前記登録されたリクエストセル情報及びアドレス情報に対応付けられた検出フラグを有し、

前記第2セルの前記ライトバック検出回路は、前記登録されたアドレス情報が示す前記リード対象アドレスと同じアドレスに対する前記リクエストライトバックを検出し、前記リクエストライトバックが検出された場合、前記検出フラグを有効にする

マルチプロセッサシステム。

【請求項5】

請求項4に記載のマルチプロセッサシステムであって、

前記リクエストライトバックは、当該リクエストの発行元を示すリクエストライトバックセル情報と、ライトバック対象アドレスを示すライトバックアドレス情報とを含み、

前記第2セルの前記ライトバック検出回路は、前記リクエストライトバックセル情報及び前記ライトバックアドレス情報のそれぞれを、前記スヌープ管理テーブルに登録されたリクエストセル情報及びアドレス情報と比較することによって、前記リード対象アドレスと同じアドレスに対する前記リクエストライトバックを検出する

マルチプロセッサシステム。

【請求項6】

請求項4又は5に記載のマルチプロセッサシステムであって、

前記各々のセルは、更にディスカード判定回路を有し、

前記第2セルの前記ディスカード判定回路は、前記第3セルからの前記リプライライトバックに応答して前記検出フラグを参照し、前記検出フラグが有効化されている場合、前記リプライライトバックを破棄する

マルチプロセッサシステム。

【請求項7】

請求項6に記載のマルチプロセッサシステムであって、

前記第2セルの前記ライトバック検出回路は、前記検出フラグを有効にすると共に、前記リクエストライトバックが示す前記ディレクトリ更新情報を、前記有効化された検出フラグと対応づけて前記スヌープ管理テーブルに格納し、

前記第2セルの前記ディスカード判定回路は、前記第3セルからの前記リプライライトバックに応答して前記検出フラグと前記ディレクトリ更新情報を参照し、前記リプライライトバックを破棄すると共に、前記ディレクトリ更新情報に基づいて前記ディレクトリのステータスを更新させる

マルチプロセッサシステム。

【請求項8】

請求項3乃至7のいずれかに記載のマルチプロセッサシステムであって、

前記第2セルは、前記リプライライトバックに応答して、前記スヌープ管理テーブル中の前記登録されたリクエストセル情報とアドレス情報に対応するエントリを初期化する

マルチプロセッサシステム。

【請求項9】

請求項2乃至8のいずれかに記載のマルチプロセッサシステムであって、

前記ディレクトリには、自セルの前記メインメモリの全アドレスのデータに関して、最新のデータを有するセルを示す情報が含まれ、

前記リードリクエストは、当該リクエストの発行元を示すリクエストセル情報と、リード対象アドレスを示すアドレス情報とを含み、

前記第2セルは、前記リードリクエストに応答して前記ディレクトリを参照し、前記リード対象アドレスのデータの最新版が前記第3セルに格納されていることを認識し、前記スヌープリクエストを前記第3セルに発行する

マルチプロセッサシステム。

【請求項10】

請求項9に記載のマルチプロセッサシステムであって、

前記発行されたスヌープリクエストは、前記リードリクエストに含まれる情報を含み、

前記第3セルは、前記スヌープリクエストに含まれる前記リクエストセル情報に基づいて、前記対象データの送信先が前記第1セルであることを認識し、前記キャッシュから読みだされた前記対象データを前記第1セルに直接送信する

マルチプロセッサシステム。

【請求項11】

マルチプロセッサシステムの動作方法であって、

前記マルチプロセッサシステムは、同一の機能を有する複数のセルを具備し、

前記複数のセルの各々は、プロセッサ、キャッシュメモリ、及びメインメモリを備え、

前記複数のセルは、

リクエストセルとしての第1セルと、

ホームセルとしての第2セルと、

オーナーセルとしての第3セルと

を含み、

前記第2セルの前記メインメモリに記憶された対象データの最新版は、前記第3セルの前記キャッシュメモリに格納され、

前記動作方法は、

(A)前記第1セルが、前記対象データに対するリードリクエストを前記第2セルに発行するステップと、

(B)前記第2セルが、前記リードリクエストに応答して、スヌープリクエストを前記第3セルに発行するステップと、

(C)前記第3セルが、前記スヌープリクエストに応答して、前記対象データを前記第1セルに直接送信するステップと、

(D)前記第3セルが、前記スヌープリクエストに応答して、リプライライトバックを前記第2セルに発行するステップと、

(E)前記第1セルが、前記第2セル中の前記対象データと同じアドレスに対してリクエストライトバックを発行するステップと、

(F)前記第2セルが、前記第3セルからの前記リプライライトバックを前記第1セルからの前記リクエストライトバックよりも後に受信した場合、前記リプライライトバックを破棄するステップと

を有する

マルチプロセッサシステムの動作方法。

【請求項12】

請求項11に記載のマルチプロセッサシステムの動作方法であって、

前記各々のセルは、更にディレクトリを備え、

前記(E)ステップにおいて、前記リクエストライトバックは、前記第1セルに含まれる前記キャッシュのステータスと前記第2セルの前記ディレクトリのステータスとを整合させるためのディレクトリ更新情報を含み、

前記(F)ステップにおいて、前記第2セルは、前記リプライライトバックを破棄すると共に、前記ディレクトリ更新情報に基づいて前記ディレクトリのステータスを更新する

マルチプロセッサシステムの動作方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2007−199999(P2007−199999A)

【公開日】平成19年8月9日(2007.8.9)

【国際特許分類】

【出願番号】特願2006−17533(P2006−17533)

【出願日】平成18年1月26日(2006.1.26)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成19年8月9日(2007.8.9)

【国際特許分類】

【出願日】平成18年1月26日(2006.1.26)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]