マルチプロセッサシステム及びそれに用いるコピーキャッシュ情報掃き出しレベル選択方法

【課題】 プロセッサに対して発行されるデータ掃き出し命令数を削減することが可能なマルチプロセッサシステムを提供する。

【解決手段】 コヒーレンシ制御回路11,21はあるレベルが管理しているアドレスの数を調べ、その数が規定数に満たない場合にスワップ優先レベルとして識別し、さらにスワップ優先レベル数の数をカウントしてその数が規定数以上であった場合にスワップ優先レベルの中から既存のLRU法またはランダム法にてスワップ対象レベルを決定する。これによって、プロセッサキャッシュ無効化命令の発行数が削減され、スワップ動作に伴うI/O帯域の使用頻度を抑えるとともに、プロセッサ12,13,22,23のキャッシュ使用率を高めることができる。

【解決手段】 コヒーレンシ制御回路11,21はあるレベルが管理しているアドレスの数を調べ、その数が規定数に満たない場合にスワップ優先レベルとして識別し、さらにスワップ優先レベル数の数をカウントしてその数が規定数以上であった場合にスワップ優先レベルの中から既存のLRU法またはランダム法にてスワップ対象レベルを決定する。これによって、プロセッサキャッシュ無効化命令の発行数が削減され、スワップ動作に伴うI/O帯域の使用頻度を抑えるとともに、プロセッサ12,13,22,23のキャッシュ使用率を高めることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はマルチプロセッサシステム及びそれに用いるコピーキャッシュ情報掃き出しレベル選択方法並びにそのプログラムに関し、特にマルチプロセッサシステムにおけるコピーキャッシュのスワップ処理を規定するコピーキャッシュ情報掃き出しレベル選択方法に関する。

【背景技術】

【0002】

一般に、分散共有メモリ方式を採用したマルチプロセッサシステムでは、複数個のセルがバス型、スター型、リング型等の信号線によって相互に接続されている。これら複数個のセル各々はキャッシュメモリを有する複数個のプロセッサと、これらのプロセッサキャッシュのコピーを保持するコピーキャッシュを有するコヒーレンシ制御回路とを備え、これらの間も上記とは別の信号線によって相互に接続されている。さらに、各セルの主メモリは上記のコヒーレンシ制御回路に専用線で接続されており、システム全体で共有されている。

【0003】

上記のようなマルチプロセッサシステムのセルにおいて、プロセッサが発行したリードリクエストを取込んだコヒーレンシ制御回路は、満杯のコピーキャッシュを索引してヒットミスとなった場合、コピーキャッシュの一部をスワップしなければならない。

【0004】

従来、コピーキャッシュの中のスワップ対象を決定する方法としては、LRU(Least Recently Used)法やランダム法等が採用されている。しかしながら、これらの方法はスワップ対象の決定時にその主メモリが搭載されているセルを考慮していないので、スワップ対象となったアドレスデータを保持していたプロセッサから再びそのアドレスに対するリクエストが発生した場合には、他のセルの主メモリにデータを取りに行く必要が発生することがあり、その時にはメモリアクセスレイテンシが増大する。

【0005】

このようなスワップ対象アドレスに対するアクセスがスワップ対象データを保持していたプロセッサから再び発生した場合に、メモリアクセスレイテンシが増大するという問題を解決するために、リクエスト発行元のプロセッサと同じセルに搭載された主メモリに対応するアドレスデータを優先的にスワップ対象とすることで、メモリアクセスレイテンシを小さくする方法が提案されている(例えば、特許文献1参照)。

【0006】

上記と同様な技術としては、TAGメモリと、TAGメモリからの掃き出し情報を保持するTAGスワップバッファとによって、TAGスワップバッファに有効な情報があり、TAGメモリのエリアが空いた際にTAGスワップバッファからの再登録を行う技術がある(例えば、特許文献2参照)。

【0007】

TAGスワップバッファはフル状態となるまで、バスへのコヒーレントリクエストを発行しない。また、TAGスワップバッファ内にTAGメモリへの再登録対象が複数ある場合、TAGステータスが“S”よりも“P”であるものを優先する。TAGスワップバッファからバスへのコヒーレントリクエストを発行する場合も、ステータスが“S”よりも“P”を優先させる機構を具備することによって、各ノード内のバスへの負荷を低減し、TAGメモリを有効に活用することから、CPUに搭載されるキャッシュからの掃き出しが低減されので、システム全体の性能が向上する。

【0008】

【特許文献1】特開2000−66955号公報

【特許文献2】特開2003−316756号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

従来の技術としては、コピーキャッシュ1レベルで管理することができるアドレスを複数倍にする技術が存在するが、従来のスワップ対象決定処理によってn個(2≦n)のアドレスを管理しているレベルがスワップ対象に決定された場合、プロセッサに対してn個のアドレス分のプロセッサキャッシュ無効化命令を発行する必要が生じ、命令の数だけプロセッサからリプライが発行されるため、1アドレス分のプロセッサキャッシュ無効化命令を発行する場合に比べてn倍のI/O(Input/Output)帯域を消費することとなり、同時にプロセッサのキャッシュ利用効率も低下するため、情報処理性能の向上を図る際のマイナス要因になるという問題がある。

【0010】

そこで、本発明の目的は上記の問題点を解消し、プロセッサに対して発行されるデータ掃き出し命令数を削減することができるマルチプロセッサシステム及びそれに用いるコピーキャッシュ情報掃き出しレベル選択方法並びにそのプログラムを提供することにある。

【課題を解決するための手段】

【0011】

本発明によるマルチプロセッサシステムは、各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを複数接続した分散共有メモリ方式のマルチプロセッサシステムであって、

前記コヒーレンシ制御回路は、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュと、前記コピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する手段とを備えている。

【0012】

本発明によるコピーキャッシュ情報掃き出しレベル選択方法は、各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを複数接続した分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法であって、

前記コヒーレンシ制御回路が、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行している。

【0013】

本発明によるコピーキャッシュ情報掃き出しレベル選択方法のプログラムは、各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを複数接続した分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法のプログラムであって、前記コヒーレンシ制御回路のコンピュータに、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行させている。

【0014】

すなわち、本発明のマルチプロセッサシステムは、各々キャッシュメモリを備える複数個のプロセッサと、キャッシュメモリのコピーを保持するコピーキャッシュを備えるコヒーレンシ制御回路と、コヒーレンシ制御回路に接続された主メモリとを含むセルを複数個接続した分散共有メモリ方式のマルチプロセッサシステムであり、コピーキャッシュが複数個のアドレスを1レベルで管理可能な機能を備え、コピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すように構成している。

【0015】

また、本発明のマルチプロセッサシステムでは、コピーキャッシュがプロセッサが発行するリクエストアドレスに含まれるキーアドレスと、アドレスの一部に対応して割当てたアドレス管理情報と、管理する複数アドレス各々に対応したステータス情報とを格納し、リクエストアドレスに含まれるセットアドレスによってアクセスされるように構成している。

【0016】

さらに、本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットした場合にコピーキャッシュを更新せずに該当するアドレスデータをプロセッサに受け渡すことを該当するプロセッサに指示し、ヒットミスした場合にコピーキャッシュに空きレベルがある時にリードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納している。

【0017】

さらにまた、本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がヒットミスした場合、コピーキャッシュに空きレベルがない時に管理しているアドレスの数が規定数以下のレベルを優先的に掃き出して空きレベルを生成した後、リードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納している。

【0018】

本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットミスした場合、コピーキャッシュに空きレベルがない時にアドレスの数が規定数以下のレベルをスワップ優先レベルとして識別し、さらにそのスワップ優先レベルの数を認識するとともに、優先レベルの数が規定数以上であることを識別した時に優先レベルの中からLRU方式またはランダム方式によってスワップ対象レベルを決定している。

【0019】

また、本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットミスした場合、コピーキャッシュに空きレベルがない時、優先レベルと識別しかつ管理しているアドレスの数が規定数以下のレベルの数が規定数に満たなければ、全レベルの中からLRU法またはランダム法等の既知の手順によってスワップ対象レベルを決定している。

【0020】

さらに、本発明のマルチプロセッサシステムでは、各々がキャッシュメモリを備える複数個のプロセッサと、キャッシュメモリのコピーを保持するコピーキャッシュを備えるコヒーレンシ制御回路と、コヒーレンシ制御回路に接続された主メモリとを含むセルを複数個接続した分散共有メモリ方式のシステムにおいて、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットした場合にコピーキャッシュを更新せず、該当するアドレスデータをプロセッサに受け渡すことを該当するプロセッサに指示している。

【0021】

さらにまた、本発明のマルチプロセッサシステムでは、ヒットミスした場合、コピーキャッシュに空きレベルがある時にリードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納している。

【0022】

本発明のマルチプロセッサシステムでは、ヒットミスした場合、コピーキャッシュに空きレベルがない時にアドレスの数が規定数のレベルを優先的に掃き出して空きレベルを生成した後、リードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納するとともに、掃き出されたアドレスについてキャッシュ掃き出し命令を作成し、プロセッサに対して発行している。

【0023】

一方、本発明のマルチプロセッサシステムでは、コピーキャッシュ情報をセットアドレスによって読出した後にECC(Error Correction Coding)論理にて1ビットエラー訂正を行う構成を採る場合、アドレスの数が規定数以下のレベルをスワップ優先レベルとして識別する回路と、さらにそのスワップ優先レベルの数を認識する回路と、優先レベルの数が規定数以上であることを認識する回路について1ビットエラー訂正を行う前のコピーキャッシュ情報読出し情報を入力信号としてECC論理と平行して論理回路の結果を出力するように構成している。

【0024】

また、本発明のマルチプロセッサシステムでは、優先レベル認識回路において規定数以下のアドレスのみを管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路との3つを組込んでおき、3つの回路の中からプログラムアクセス可能なレジスタの設定値によって選択可能とする手段を持っている。

【0025】

上記のように、本発明のマルチプロセッサシステムでは、メモリアクセスTAT(Turn Around Time)を増加することなく、スワップ対象レベル選択時に管理アドレス数の少ないレベルを優先的にスワップし、プロセッサに対して発行されるデータ掃き出し命令数を削減することによって、通常命令が使用するI/O(Input/Output)帯域を増加してデータ処理能力を向上させることが可能となる。

【0026】

また、本発明のマルチプロセッサシステムでは、優先対象レベル数をカウントして、その数が一定数以上である場合にのみ優先対象の中からスワップ対象レベルを決定する構成をとり、優先度の高いレベル数が少なくなった時にスワップ対象レベルが極端に集中してしまうことを防ぐことによって、性能低下を抑えることが可能となる。

【0027】

さらに、本発明のマルチプロセッサシステムでは、管理アドレス数の少ないレベルが優先してスワップされるため、管理アドレス数の大きいレベルの存在確率が上がり、これはコピーキャッシュを利用効率が向上を意味するが、結果的にプロセッサが持っているコピーキャッシュの利用効率を向上させることも可能となる。

【発明の効果】

【0028】

本発明は、以下に述べるような構成及び動作とすることで、プロセッサに対して発行されるデータ掃き出し命令数を削減することができるという効果が得られる。

【発明を実施するための最良の形態】

【0029】

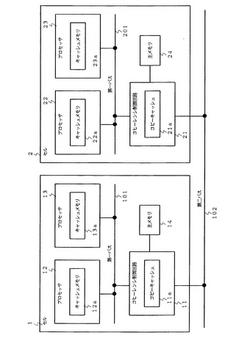

次に、本発明の実施例について図面を参照して説明する。図1は本発明の一実施例によるマルチプロセッサシステムの構成を示すブロック図である。図1において、本発明の一実施例によるマルチプロセッサシステムはセル1,2を第二バス102で接続した分散共有メモリ方式のシステムである。

【0030】

セル1,2は各々キャッシュメモリ12a,13a,22a,23aを備える複数のプロセッサ12,13,22,23と、キャッシュメモリ12a,13a,22a,23aのコピーを保持するコピーキャッシュ11a,21aを備えるコヒーレンシ制御回路11,21と、コヒーレンシ制御回路11,21に接続された主メモリ14,24とを含んで構成されており、複数のプロセッサ12,13,22,23とコヒーレンシ制御回路11,21とは第一バス101,201で相互に接続されている。また、コヒーレンシ制御回路11,21は第二バス102で相互に接続されている。

【0031】

このシステムにおいて、コピーキャッシュ11a,21aの情報を掃き出す時には、そのコピーキャッシュ11a,21aを備えるコヒーレンシ制御回路11,21に接続された主メモリ14,24に対応するアドレスデータの情報を優先的に掃き出すようにしている。

【0032】

プロセッサ12,13,22,23はそれぞれストアイン方式を採用するキャッシュメモリ12a,13a,22a,23aを有している。キャッシュメモリ12a,13a,22a,23aは、データを記憶する領域であるデータアレイキャッシュ(DA:Data Array cache)と、データアレイキャッシュに格納されたデータのアドレスに対応するキーアドレス及びデータアレイキャッシュに格納されたデータのステータスを保持するアドレスアレイキャッシュ(AA:Address Array cache)とによって構成されている。アドレスアレイキャッシュはセットアソシアティブ方式によって、上記のキーアドレス及びデータステータスを格納している。

【0033】

コヒーレンシ制御回路11,21はプロセッサ12,13,22,23と主メモリ14,24との間のキャッシュコヒーレンシを保証するための回路であり、プロセッサ12,13,22,23が有するアドレスアレイキャッシュのデータがコピーされるコピーキャッシュ11a,21aを有している。尚、コピーキャッシュ11a,21aはプロセッサ12,13,22,23のそれぞれに固有ではなく、両プロセッサ12,13,22,23にて共有するものである。

【0034】

セル1,2は上記のプロセッサ12,13,22,23とコヒーレンシ制御回路11,21とを相互に第一バス101,201によって接続して構成されている。尚、主メモリ14,24はコヒーレンシ制御回路11,21に専用線で接続されている。

【0035】

本発明の一実施例によるマルチプロセッサシステムは、上記のようなセルを複数個備え、各セルのコヒーレンシ制御回路を相互に第二バス102によって接続して構成される。各セル1,2の主メモリ14,24はセル1,2内のプロセッサで共有されるだけでなく、全セル1,2のプロセッサ12,13,22,23で共有されている。尚、最小構成時のマルチプロセッサシステムとしてはセルの数は1個でよい。

【0036】

図2は図1のコピーキャッシュ11aの構成を示すブロック図である。図2において、コピーキャッシュ11aはセットアソシアティブ方式を採用し、リクエストアドレス112の一部をセットアドレス1101としてコピーキャッシュ111にアクセスし、アドレスの一部に対応して割当てたアドレス管理情報114と、残りのリクエストアドレスであるキーアドレス1102とアドレスのステータスを示すステータス情報113とを格納する。

【0037】

ステータス情報113は2つのアドレスを管理する場合に2つ分のステータス情報を、4つのアドレスを管理する場合に4つ分のステータス情報をそれぞれ保持する。

【0038】

また、物理的要因によってコピーキャッシュ111のレベル数(L)は、第一バス101で接続された複数のプロセッサ12,13のアドレスアレイキャッシュのレベル数の合計と同等、もしくは少ないものとする。これはあるリクエストをプロセッサ12,13が実行しようとした場合に、プロセッサ12,13のアドレスアレイキャッシュには情報を格納することができるが、コピーキャッシュ11aの対応するレベルが全て使用されており、新たなリクエストによる情報を格納できないことがあるということである。

【0039】

アドレス管理情報114はリクエストアドレス112の一部をデコーダ115でデコードしたもので、1つのセットアドレスで2つのアドレスを管理する場合に2ビットとなり、1つのセットアドレスで4つのアドレスを管理する場合に4ビットとなり、各々のビットが管理対象のアドレスに対応しているため、複数のアドレスを管理している場合にこのアドレス管理情報には複数のビットが“1”となる。

【0040】

ステータス情報113に対応するアドレスが有効または無効であることを識別できるコードを使うことによってアドレス管理情報114を不要とする構成をとることも可能である。

【0041】

図3は図1のコヒーレンシ制御回路11,21の動作を示すフローチャートである。これら図1〜図3を参照してコヒーレンシ制御回路11,21の動作について説明する。

【0042】

プロセッサ12が発行したリードリクエストは第一バス101を介してコヒーレンシ制御回路11に取込まれる。コヒーレンシ制御回路11はそのリードリクエストを基にコピーキャッシュ11aを索引する(図3ステップS1)。

【0043】

コヒーレンシ制御回路11はこのコピーキャッシュ11aの索引の結果、コピーキャッシュ11aに既に該リクエストアドレス及びデータステータス情報が格納されているヒット状態か、コピーキャッシュ11aに該リクエストアドレス及びデータステータス情報が格納されていないミス状態かを判別する(図3ステップS2)。

【0044】

ヒット状態と判別された場合には、コピーキャッシュ11aの更新の必要はない。コピーキャッシュ11aにヒットするということは、この例ではプロセッサ13が該アドレスデータを保持していることを意味するので、コヒーレンシ制御回路11はプロセッサ13に対して第一バス101を介してプロセッサ12に該アドレスデータを受け渡すことを指示する(図3ステップS3)。

【0045】

ミス状態と判別された場合には、コピーキャッシュ11aに該リクエストアドレスやステータス情報、及びセル情報を格納する必要がある。そこで、コヒーレンシ制御回路11は上記のステップS1においてコピーキャッシュ11aを索引した時のデータからコピーキャッシュ11aに新たな情報を格納することができる空きレベルが存在するか否かを確認する(図3ステップS4)。

【0046】

コピーキャッシュ11aに空きレベルが存在する場合には、コピーキャッシュミス時の動作、すなわち第二バス102に該リードリクエストを発行し、第二バス102に接続される全てのセルのコヒーレンシ制御回路がそのリクエストを取込み、コピーキャッシュを索引し、配下のプロセッサがダーティで該アドレスデータを保持していたならばそのデータを、いずれのプロセッサもダーティデータを保持していないのならば該リクエストアドレスのデータを保持する主メモリからの読出しデータを、リクエスト元のプロセッサ12に返却する処理を行う(図3ステップS7)。

【0047】

続いて、コヒーレンシ制御回路11はコピーキャッシュ11aに該リクエストアドレスやステータス情報、及びセル情報(該リクエストアドレスのデータを保持する主メモリを搭載したセルを示す情報)を格納する(図3ステップS8)。

【0048】

コピーキャッシュ11aに空きレベルが存在しない場合、コヒーレンシ制御回路11は使用されているレベルのいずれかの情報を選択し、その情報に対応するアドレスのデータを保持しているプロセッサに対して問い合わせ、そのデータがダーティならば主メモリへの書き戻しを、そうでなければ廃棄を指示し、空きレベルを生成する必要がある。この処理をスワップ処理と称する。

【0049】

従来、スワップ処理レベルの決定法としてはLRU(Least Recently Used)法やランダム法が利用されているが、本実施例ではプロセッサへのデータ無効化命令発効数の削減を目的として1つのアドレスのみを管理しているレベルを優先してスワップ対象レベルに選択する(図3ステップS5)。

【0050】

図4は図3のスワップ対象レベル決定(図3ステップS5)の処理を示すフローチャートである。この図4を参照してスワップ対象レベル決定の処理について説明する。

【0051】

まず、コヒーレンシ制御回路11は上記のステップS1でコピーキャッシュ11aを索引した時の情報を用いて、1つのみアドレスを管理しているレベルを優先対象レベルと認識するとともに、その数を認識して、その数がn個以上(2≦n≦最大レベル数)であることを確認する(図4ステップS11)。

【0052】

この条件を満たしていない場合、コヒーレンシ制御回路11は全レベルの中からLRU法やランダム法等でスワップ対象レベルを選択する(図4ステップS12)。また、この条件を満たしている場合、コヒーレンシ制御回路11は優先対象レベルの中からLRU法やランダム法等でスワップ対象レベルを選択する(図4ステップS13)。

【0053】

コヒーレンシ制御回路11は、上記のようにして選択されたスワップ対象レベルに格納されていたアドレスのデータを保持するプロセッサに対してデータ掃き出し命令を出力するが(図3ステップS6)、その際、2つのアドレスを管理しているレベルがスワップ対象レベルとして選択された場合には2つのデータ掃き出し命令がプロセッサに対して出力され、1つのアドレスを管理しているレベルがスワップ対象レベルとして選択された場合には1つのデータ掃き出し命令がプロセッサに対して出力される。プロセッサはデータ掃き出し命令を受取ると、そのデータがダーティならば主メモリへの書き戻しを、そうでないならば破棄する処理を行う。

【0054】

この後、コヒーレンシ制御回路11はコピーキャッシュミス時の動作、すなわち第二バス102に該リードリクエストを発行し、第二バス102に接続される全てのセルのコヒーレンシ制御回路がそのリクエストを取込み、コピーキャッシュを索引し、配下のプロセッサがダーティで該アドレスデータを保持していたならばそのデータを、いずれのプロセッサもダーティデータを保持していないのならば該リクエストアドレスのデータを保持する主メモリからの読出しデータを、リクエスト元のプロセッサ12に返却する処理を行う(図3ステップS7)。

【0055】

コヒーレンシ制御回路11は上記のステップS6の処理で空いたレベルに該リクエストアドレスやステータス情報、及びセル情報を格納し(図3ステップS8)、リードリクエストの処理を終了する。尚、上記のコピーキャッシュ情報掃き出しレベル選択の処理は主メモリに保持されたプログラムを実行することによって動作する。このプログラムはマルチプロセッサシステムを構成するオペレーティングシステム(OS)の一機能であり、通常、ハードディスク等に格納されており、システム運用時に主メモリにロードされて実行される。

【0056】

図5〜図7は図1のコピーキャッシュ11aから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路(図示せず)に送るまでの構成を示すブロック図である。これら図5〜図7を参照してメモリアクセスTAT(Turn Around Time)を増加させることなく、上述した機能を実現する例について説明する。以下の説明では、本実施例ではコピーキャッシュレベル数を12とし、1つのセットアドレスで管理できるアドレス数を2とする。

【0057】

図5は従来技術における構成例で、最初のクロックサイクルでセットアドレス1101によってコピーキャッシュ111から格納データを読出してレジスタ116で受ける。次のクロックサイクルでは、ECC(Error Correction Coding)回路117によって1ビットエラーを訂正し、レジスタ118で受ける。

【0058】

次のクロックサイクルでは、ヒット/ミスチェック(Hit/Miss Check)回路119にてコピーキャッシュ111に該リクエストアドレス及びデータステータス情報が格納されていないことと、レベルに空きがないこととを識別し、スワップ決定回路121にその識別情報を送る。このヒット/ミスチェック回路119の動作と平行して、スワップレベル決定回路120にてLRU法またはランダム法等の既存の方法を用いて複数レベルの中からスワップ対象レベルを決定する。

【0059】

スワップ決定回路121はヒット/ミスチェック回路119及びスワップレベル決定回路120からの信号を受けて対象レベルをスワップする決定を行い、レジスタ122を介して図示せぬデータ掃き出し命令生成回路にスワップ対象レベル情報を送出する。

【0060】

図6を参照して、従来の回路構成をベースにして本発明の機能を実装した時の例について説明する。図6は図5に対して優先レベル認識回路123と優先レベル数カウント回路124とレジスタ125,126とが追加されており、スワップ決定までのクロックサイクルが1サイクル増加してしまっている。

【0061】

図6の図5との差分について説明すると、優先レベル認識回路123は1ビットエラー修正後の情報から優先レベルとなる1つの(X個以下の)アドレスのみを管理しているレベルを識別する。Xは固定値“1”またはプログラムにて設定できるものである。

【0062】

優先レベル数カウント回路124は優先レベルと認識された数をカウントし、そのカウント数をスワップレベル決定回路120に送るが、回路遅延の関係上、一旦レジスタ125に格納する必要が生じてしまう。

【0063】

スワップレベル決定回路120は優先レベル数が4以上(m個以上)であった場合に優先レベルの中からLRU法またはランダム法等にてスワップレベルを決定し、優先レベル数が4(m個)に満たない場合に全12レベルの中からLRU法またはランダム法等にてスワップレベルを決定する。

【0064】

図7を参照して本発明における回路構成例について説明する。本発明における回路構成の特徴として、優先レベル認識回路123と優先レベル数カウント回路124とをECC回路117と平行して設けることによって、図6に示す構成に比べて1クロック早く優先レベル数をカウントすることができる。

【0065】

このため、スワップレベル決定回路120も1クロック早くスワップレベルを決定することが可能となるため、データ掃き出し命令生成回路にスワップ対象レベル情報を従来例の図5と同じタイミングで送出することが可能となる。つまり、メモリアクセスTATに影響を与えることなく、本発明の機能を実装可能としている。

【0066】

ここで問題になるのは、優先レベル認識回路123に入力する信号としてECC回路117による1ビットエラー訂正を行う前の読出しデータを入力しているため、確率的には低いが優先レベル認識を誤ってしまう可能性があるということである。

【0067】

この場合、優先レベル数カウント回路124の結果が±1の誤差を含むこととなり、厳密には優先レベルの中からスワップレベルを決定するところを全12レベルの中からスワップレベルを決定してしまうケースやそれとは逆に、全12レベルの中からスワップレベルを決定するところを優先レベル3個(m−1個)の中からスワップレベルを決定してしまうこともあり得る。

【0068】

しかしながら、上記のケースでスワップレベルの決定に厳密さが欠けたとしても、もともとランダムな要素が大きいことから問題となることはなく、目的の機能を達成することができる。

【0069】

近年のプロセッサでは、プログラムコードを主メモリからリードする場合に、プロセッサで読込んだデータを更新しないことを示すフラグ(以下、コマンドフラグとする)を付与してリード命令を発行する場合がある。並列処理等で複数のプロセッサで同じプログラムコードを使用するケースを想定すると、コピーキャッシュからスワップレベルを決定する際に、プログラムコード以外の一過性のデータ等をスワップレベルとして優先的に選択することによって、プロセッサで使用中のプログラムコードがスワップアウトされる可能性が減少して高速化につながることが考えられる。

【0070】

このケースに対応するにはコピーキャッシュに格納する情報にコマンドフラグを加え、さらに優先レベル認識回路において規定数以下のアドレスのみ管理しているレベルを認識する部分をコマンドフラグ認識回路に置き換えて、コマンドフラグが有効でないレベルを優先レベルとして認識することによって実現可能である。

【0071】

この他にも、特開2003−316756号公報に記載のように複数のプロセッサが共有していることを示すステータス情報を持つレベルを優先的にコピーキャッシュからスワップアウトする方式もあり、この場合、プロセッサのキャッシュからダーティデータが出力されないため、I/O帯域有効利用に効果がある反面、管理下にある複数のプロセッサで共有していた命令コードがスワップアウトされると、共有していた全プロセッサでキャッシングされていた命令コードが無効になってしまい、この場合、キャッシュ利用効率が低下してしまうことが予想される。

【0072】

このように、プログラムの特性によって理想的なスワップアウト処理は変わるため、優先レベル認識回路において規定数以下のアドレスのみ管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路の3つを組み込んでおき、3つの回路の中からプログラムアクセス可能なレジスタの設定値によって選択可能とする手段を持つことも可能である。

【0073】

図8は図1のコピーキャッシュ11aから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路(図示せず)に送るまでの他の構成を示すブロック図である。図8に示す構成は上述した3つの回路の中からプログラムアクセス可能なレジスタの設定値によって選択可能とする時の構成例を示している。

【0074】

図8において、最初のクロックサイクルでセットアドレス1101によってコピーキャッシュ111から格納データを読出してレジスタ132で受ける。次のクロックサイクルでは、規定数以下のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路133と、プログラムコード以外のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路134と、複数プロセッサで共有していることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路135と、自セル搭載のメモリアドレス帯に格納されているレベルをスワップ優先レベルとして認識する回路136とでそれぞれ処理が行われる。

【0075】

131は優先モード切替レジスタで、プログラムがアクセス可能なレジスタである。優先モード切替レジスタ131の値によって4つの優先レベル認識回路133〜136の中の1つを選択器137で選択し、優先レベル数カウント回路138に送出する。優先レベル数カウント回路138以降の動作は上述した通りである。

【0076】

このように、本実施例では、メモリアクセスTATを増加することなく、スワップ対象レベル選択時に管理アドレス数の少ないレベルを優先的にスワップし、プロセッサに対して発行されるデータ掃き出し命令数を削減することによって、通常命令が使用するI/O(Input/Output)帯域を増加してデータ処理能力を向上させることができる。

【0077】

また、本実施例では、優先対象レベル数をカウントして、その数が一定数以上である場合にのみ優先対象の中からスワップ対象レベルを決定する構成をとり、優先度の高いレベル数が少なくなった時にスワップ対象レベルが極端に集中してしまうことを防ぐことによって、性能低下を抑えることができる。

【0078】

さらに、本実施例では、管理アドレス数の少ないレベルが優先してスワップされるため、管理アドレス数の大きいレベルの存在確率が上がり、これはコピーキャッシュの利用効率向上を意味するが、結果的にプロセッサが持っているコピーキャッシュの利用効率を向上させることになる。

【図面の簡単な説明】

【0079】

【図1】本発明の一実施例によるマルチプロセッサシステムの構成を示すブロック図である。

【図2】図1のコピーキャッシュの構成を示すブロック図である。

【図3】図1のコヒーレンシ制御回路の動作を示すフローチャートである。

【図4】図3のスワップ対象レベル決定の処理を示すフローチャートである。

【図5】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの構成を示すブロック図である。

【図6】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの構成を示すブロック図である。

【図7】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの構成を示すブロック図である。

【図8】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの他の構成を示すブロック図である。

【符号の説明】

【0080】

1,2 セル

11,21 コヒーレンシ制御回路

11a,21a コピーキャッシュ

12,13,

22,23 プロセッサ

12a,13a,

22a,23a キャッシュメモリ

14,24 主メモリ

101 第一バス

102 第二バス

111 コピーキャッシュ

112 リクエストアドレス

113 ステータス情報

114 複数アドレス管理情報

115 デコーダ

116,118,

122,125,

126,132,

139 レジスタ

123 優先レベル認識回路

124,138 優先レベル数カウント回路

131 優先モード切替レジスタ

133 規定数以下のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路

134 プログラムコード以外のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路

135 複数プロセッサで共有していることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路

136 自セル搭載のメモリアドレス帯に格納されているレベルをスワップ優先レベルとして認識する回路

137 選択器

1101 セットアドレス

1102 キーアドレス

【技術分野】

【0001】

本発明はマルチプロセッサシステム及びそれに用いるコピーキャッシュ情報掃き出しレベル選択方法並びにそのプログラムに関し、特にマルチプロセッサシステムにおけるコピーキャッシュのスワップ処理を規定するコピーキャッシュ情報掃き出しレベル選択方法に関する。

【背景技術】

【0002】

一般に、分散共有メモリ方式を採用したマルチプロセッサシステムでは、複数個のセルがバス型、スター型、リング型等の信号線によって相互に接続されている。これら複数個のセル各々はキャッシュメモリを有する複数個のプロセッサと、これらのプロセッサキャッシュのコピーを保持するコピーキャッシュを有するコヒーレンシ制御回路とを備え、これらの間も上記とは別の信号線によって相互に接続されている。さらに、各セルの主メモリは上記のコヒーレンシ制御回路に専用線で接続されており、システム全体で共有されている。

【0003】

上記のようなマルチプロセッサシステムのセルにおいて、プロセッサが発行したリードリクエストを取込んだコヒーレンシ制御回路は、満杯のコピーキャッシュを索引してヒットミスとなった場合、コピーキャッシュの一部をスワップしなければならない。

【0004】

従来、コピーキャッシュの中のスワップ対象を決定する方法としては、LRU(Least Recently Used)法やランダム法等が採用されている。しかしながら、これらの方法はスワップ対象の決定時にその主メモリが搭載されているセルを考慮していないので、スワップ対象となったアドレスデータを保持していたプロセッサから再びそのアドレスに対するリクエストが発生した場合には、他のセルの主メモリにデータを取りに行く必要が発生することがあり、その時にはメモリアクセスレイテンシが増大する。

【0005】

このようなスワップ対象アドレスに対するアクセスがスワップ対象データを保持していたプロセッサから再び発生した場合に、メモリアクセスレイテンシが増大するという問題を解決するために、リクエスト発行元のプロセッサと同じセルに搭載された主メモリに対応するアドレスデータを優先的にスワップ対象とすることで、メモリアクセスレイテンシを小さくする方法が提案されている(例えば、特許文献1参照)。

【0006】

上記と同様な技術としては、TAGメモリと、TAGメモリからの掃き出し情報を保持するTAGスワップバッファとによって、TAGスワップバッファに有効な情報があり、TAGメモリのエリアが空いた際にTAGスワップバッファからの再登録を行う技術がある(例えば、特許文献2参照)。

【0007】

TAGスワップバッファはフル状態となるまで、バスへのコヒーレントリクエストを発行しない。また、TAGスワップバッファ内にTAGメモリへの再登録対象が複数ある場合、TAGステータスが“S”よりも“P”であるものを優先する。TAGスワップバッファからバスへのコヒーレントリクエストを発行する場合も、ステータスが“S”よりも“P”を優先させる機構を具備することによって、各ノード内のバスへの負荷を低減し、TAGメモリを有効に活用することから、CPUに搭載されるキャッシュからの掃き出しが低減されので、システム全体の性能が向上する。

【0008】

【特許文献1】特開2000−66955号公報

【特許文献2】特開2003−316756号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

従来の技術としては、コピーキャッシュ1レベルで管理することができるアドレスを複数倍にする技術が存在するが、従来のスワップ対象決定処理によってn個(2≦n)のアドレスを管理しているレベルがスワップ対象に決定された場合、プロセッサに対してn個のアドレス分のプロセッサキャッシュ無効化命令を発行する必要が生じ、命令の数だけプロセッサからリプライが発行されるため、1アドレス分のプロセッサキャッシュ無効化命令を発行する場合に比べてn倍のI/O(Input/Output)帯域を消費することとなり、同時にプロセッサのキャッシュ利用効率も低下するため、情報処理性能の向上を図る際のマイナス要因になるという問題がある。

【0010】

そこで、本発明の目的は上記の問題点を解消し、プロセッサに対して発行されるデータ掃き出し命令数を削減することができるマルチプロセッサシステム及びそれに用いるコピーキャッシュ情報掃き出しレベル選択方法並びにそのプログラムを提供することにある。

【課題を解決するための手段】

【0011】

本発明によるマルチプロセッサシステムは、各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを複数接続した分散共有メモリ方式のマルチプロセッサシステムであって、

前記コヒーレンシ制御回路は、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュと、前記コピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する手段とを備えている。

【0012】

本発明によるコピーキャッシュ情報掃き出しレベル選択方法は、各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを複数接続した分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法であって、

前記コヒーレンシ制御回路が、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行している。

【0013】

本発明によるコピーキャッシュ情報掃き出しレベル選択方法のプログラムは、各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを複数接続した分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法のプログラムであって、前記コヒーレンシ制御回路のコンピュータに、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行させている。

【0014】

すなわち、本発明のマルチプロセッサシステムは、各々キャッシュメモリを備える複数個のプロセッサと、キャッシュメモリのコピーを保持するコピーキャッシュを備えるコヒーレンシ制御回路と、コヒーレンシ制御回路に接続された主メモリとを含むセルを複数個接続した分散共有メモリ方式のマルチプロセッサシステムであり、コピーキャッシュが複数個のアドレスを1レベルで管理可能な機能を備え、コピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すように構成している。

【0015】

また、本発明のマルチプロセッサシステムでは、コピーキャッシュがプロセッサが発行するリクエストアドレスに含まれるキーアドレスと、アドレスの一部に対応して割当てたアドレス管理情報と、管理する複数アドレス各々に対応したステータス情報とを格納し、リクエストアドレスに含まれるセットアドレスによってアクセスされるように構成している。

【0016】

さらに、本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットした場合にコピーキャッシュを更新せずに該当するアドレスデータをプロセッサに受け渡すことを該当するプロセッサに指示し、ヒットミスした場合にコピーキャッシュに空きレベルがある時にリードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納している。

【0017】

さらにまた、本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がヒットミスした場合、コピーキャッシュに空きレベルがない時に管理しているアドレスの数が規定数以下のレベルを優先的に掃き出して空きレベルを生成した後、リードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納している。

【0018】

本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットミスした場合、コピーキャッシュに空きレベルがない時にアドレスの数が規定数以下のレベルをスワップ優先レベルとして識別し、さらにそのスワップ優先レベルの数を認識するとともに、優先レベルの数が規定数以上であることを識別した時に優先レベルの中からLRU方式またはランダム方式によってスワップ対象レベルを決定している。

【0019】

また、本発明のマルチプロセッサシステムでは、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットミスした場合、コピーキャッシュに空きレベルがない時、優先レベルと識別しかつ管理しているアドレスの数が規定数以下のレベルの数が規定数に満たなければ、全レベルの中からLRU法またはランダム法等の既知の手順によってスワップ対象レベルを決定している。

【0020】

さらに、本発明のマルチプロセッサシステムでは、各々がキャッシュメモリを備える複数個のプロセッサと、キャッシュメモリのコピーを保持するコピーキャッシュを備えるコヒーレンシ制御回路と、コヒーレンシ制御回路に接続された主メモリとを含むセルを複数個接続した分散共有メモリ方式のシステムにおいて、コヒーレンシ制御回路がプロセッサの発行したリードリクエストによってコピーキャッシュを索引し、ヒットした場合にコピーキャッシュを更新せず、該当するアドレスデータをプロセッサに受け渡すことを該当するプロセッサに指示している。

【0021】

さらにまた、本発明のマルチプロセッサシステムでは、ヒットミスした場合、コピーキャッシュに空きレベルがある時にリードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納している。

【0022】

本発明のマルチプロセッサシステムでは、ヒットミスした場合、コピーキャッシュに空きレベルがない時にアドレスの数が規定数のレベルを優先的に掃き出して空きレベルを生成した後、リードリクエストを他のすべてのセルに発行して検索させ、その検索で得られたアドレスデータをプロセッサに受け渡し、さらにコピーキャッシュの空きレベルにアドレスデータを格納するとともに、掃き出されたアドレスについてキャッシュ掃き出し命令を作成し、プロセッサに対して発行している。

【0023】

一方、本発明のマルチプロセッサシステムでは、コピーキャッシュ情報をセットアドレスによって読出した後にECC(Error Correction Coding)論理にて1ビットエラー訂正を行う構成を採る場合、アドレスの数が規定数以下のレベルをスワップ優先レベルとして識別する回路と、さらにそのスワップ優先レベルの数を認識する回路と、優先レベルの数が規定数以上であることを認識する回路について1ビットエラー訂正を行う前のコピーキャッシュ情報読出し情報を入力信号としてECC論理と平行して論理回路の結果を出力するように構成している。

【0024】

また、本発明のマルチプロセッサシステムでは、優先レベル認識回路において規定数以下のアドレスのみを管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路との3つを組込んでおき、3つの回路の中からプログラムアクセス可能なレジスタの設定値によって選択可能とする手段を持っている。

【0025】

上記のように、本発明のマルチプロセッサシステムでは、メモリアクセスTAT(Turn Around Time)を増加することなく、スワップ対象レベル選択時に管理アドレス数の少ないレベルを優先的にスワップし、プロセッサに対して発行されるデータ掃き出し命令数を削減することによって、通常命令が使用するI/O(Input/Output)帯域を増加してデータ処理能力を向上させることが可能となる。

【0026】

また、本発明のマルチプロセッサシステムでは、優先対象レベル数をカウントして、その数が一定数以上である場合にのみ優先対象の中からスワップ対象レベルを決定する構成をとり、優先度の高いレベル数が少なくなった時にスワップ対象レベルが極端に集中してしまうことを防ぐことによって、性能低下を抑えることが可能となる。

【0027】

さらに、本発明のマルチプロセッサシステムでは、管理アドレス数の少ないレベルが優先してスワップされるため、管理アドレス数の大きいレベルの存在確率が上がり、これはコピーキャッシュを利用効率が向上を意味するが、結果的にプロセッサが持っているコピーキャッシュの利用効率を向上させることも可能となる。

【発明の効果】

【0028】

本発明は、以下に述べるような構成及び動作とすることで、プロセッサに対して発行されるデータ掃き出し命令数を削減することができるという効果が得られる。

【発明を実施するための最良の形態】

【0029】

次に、本発明の実施例について図面を参照して説明する。図1は本発明の一実施例によるマルチプロセッサシステムの構成を示すブロック図である。図1において、本発明の一実施例によるマルチプロセッサシステムはセル1,2を第二バス102で接続した分散共有メモリ方式のシステムである。

【0030】

セル1,2は各々キャッシュメモリ12a,13a,22a,23aを備える複数のプロセッサ12,13,22,23と、キャッシュメモリ12a,13a,22a,23aのコピーを保持するコピーキャッシュ11a,21aを備えるコヒーレンシ制御回路11,21と、コヒーレンシ制御回路11,21に接続された主メモリ14,24とを含んで構成されており、複数のプロセッサ12,13,22,23とコヒーレンシ制御回路11,21とは第一バス101,201で相互に接続されている。また、コヒーレンシ制御回路11,21は第二バス102で相互に接続されている。

【0031】

このシステムにおいて、コピーキャッシュ11a,21aの情報を掃き出す時には、そのコピーキャッシュ11a,21aを備えるコヒーレンシ制御回路11,21に接続された主メモリ14,24に対応するアドレスデータの情報を優先的に掃き出すようにしている。

【0032】

プロセッサ12,13,22,23はそれぞれストアイン方式を採用するキャッシュメモリ12a,13a,22a,23aを有している。キャッシュメモリ12a,13a,22a,23aは、データを記憶する領域であるデータアレイキャッシュ(DA:Data Array cache)と、データアレイキャッシュに格納されたデータのアドレスに対応するキーアドレス及びデータアレイキャッシュに格納されたデータのステータスを保持するアドレスアレイキャッシュ(AA:Address Array cache)とによって構成されている。アドレスアレイキャッシュはセットアソシアティブ方式によって、上記のキーアドレス及びデータステータスを格納している。

【0033】

コヒーレンシ制御回路11,21はプロセッサ12,13,22,23と主メモリ14,24との間のキャッシュコヒーレンシを保証するための回路であり、プロセッサ12,13,22,23が有するアドレスアレイキャッシュのデータがコピーされるコピーキャッシュ11a,21aを有している。尚、コピーキャッシュ11a,21aはプロセッサ12,13,22,23のそれぞれに固有ではなく、両プロセッサ12,13,22,23にて共有するものである。

【0034】

セル1,2は上記のプロセッサ12,13,22,23とコヒーレンシ制御回路11,21とを相互に第一バス101,201によって接続して構成されている。尚、主メモリ14,24はコヒーレンシ制御回路11,21に専用線で接続されている。

【0035】

本発明の一実施例によるマルチプロセッサシステムは、上記のようなセルを複数個備え、各セルのコヒーレンシ制御回路を相互に第二バス102によって接続して構成される。各セル1,2の主メモリ14,24はセル1,2内のプロセッサで共有されるだけでなく、全セル1,2のプロセッサ12,13,22,23で共有されている。尚、最小構成時のマルチプロセッサシステムとしてはセルの数は1個でよい。

【0036】

図2は図1のコピーキャッシュ11aの構成を示すブロック図である。図2において、コピーキャッシュ11aはセットアソシアティブ方式を採用し、リクエストアドレス112の一部をセットアドレス1101としてコピーキャッシュ111にアクセスし、アドレスの一部に対応して割当てたアドレス管理情報114と、残りのリクエストアドレスであるキーアドレス1102とアドレスのステータスを示すステータス情報113とを格納する。

【0037】

ステータス情報113は2つのアドレスを管理する場合に2つ分のステータス情報を、4つのアドレスを管理する場合に4つ分のステータス情報をそれぞれ保持する。

【0038】

また、物理的要因によってコピーキャッシュ111のレベル数(L)は、第一バス101で接続された複数のプロセッサ12,13のアドレスアレイキャッシュのレベル数の合計と同等、もしくは少ないものとする。これはあるリクエストをプロセッサ12,13が実行しようとした場合に、プロセッサ12,13のアドレスアレイキャッシュには情報を格納することができるが、コピーキャッシュ11aの対応するレベルが全て使用されており、新たなリクエストによる情報を格納できないことがあるということである。

【0039】

アドレス管理情報114はリクエストアドレス112の一部をデコーダ115でデコードしたもので、1つのセットアドレスで2つのアドレスを管理する場合に2ビットとなり、1つのセットアドレスで4つのアドレスを管理する場合に4ビットとなり、各々のビットが管理対象のアドレスに対応しているため、複数のアドレスを管理している場合にこのアドレス管理情報には複数のビットが“1”となる。

【0040】

ステータス情報113に対応するアドレスが有効または無効であることを識別できるコードを使うことによってアドレス管理情報114を不要とする構成をとることも可能である。

【0041】

図3は図1のコヒーレンシ制御回路11,21の動作を示すフローチャートである。これら図1〜図3を参照してコヒーレンシ制御回路11,21の動作について説明する。

【0042】

プロセッサ12が発行したリードリクエストは第一バス101を介してコヒーレンシ制御回路11に取込まれる。コヒーレンシ制御回路11はそのリードリクエストを基にコピーキャッシュ11aを索引する(図3ステップS1)。

【0043】

コヒーレンシ制御回路11はこのコピーキャッシュ11aの索引の結果、コピーキャッシュ11aに既に該リクエストアドレス及びデータステータス情報が格納されているヒット状態か、コピーキャッシュ11aに該リクエストアドレス及びデータステータス情報が格納されていないミス状態かを判別する(図3ステップS2)。

【0044】

ヒット状態と判別された場合には、コピーキャッシュ11aの更新の必要はない。コピーキャッシュ11aにヒットするということは、この例ではプロセッサ13が該アドレスデータを保持していることを意味するので、コヒーレンシ制御回路11はプロセッサ13に対して第一バス101を介してプロセッサ12に該アドレスデータを受け渡すことを指示する(図3ステップS3)。

【0045】

ミス状態と判別された場合には、コピーキャッシュ11aに該リクエストアドレスやステータス情報、及びセル情報を格納する必要がある。そこで、コヒーレンシ制御回路11は上記のステップS1においてコピーキャッシュ11aを索引した時のデータからコピーキャッシュ11aに新たな情報を格納することができる空きレベルが存在するか否かを確認する(図3ステップS4)。

【0046】

コピーキャッシュ11aに空きレベルが存在する場合には、コピーキャッシュミス時の動作、すなわち第二バス102に該リードリクエストを発行し、第二バス102に接続される全てのセルのコヒーレンシ制御回路がそのリクエストを取込み、コピーキャッシュを索引し、配下のプロセッサがダーティで該アドレスデータを保持していたならばそのデータを、いずれのプロセッサもダーティデータを保持していないのならば該リクエストアドレスのデータを保持する主メモリからの読出しデータを、リクエスト元のプロセッサ12に返却する処理を行う(図3ステップS7)。

【0047】

続いて、コヒーレンシ制御回路11はコピーキャッシュ11aに該リクエストアドレスやステータス情報、及びセル情報(該リクエストアドレスのデータを保持する主メモリを搭載したセルを示す情報)を格納する(図3ステップS8)。

【0048】

コピーキャッシュ11aに空きレベルが存在しない場合、コヒーレンシ制御回路11は使用されているレベルのいずれかの情報を選択し、その情報に対応するアドレスのデータを保持しているプロセッサに対して問い合わせ、そのデータがダーティならば主メモリへの書き戻しを、そうでなければ廃棄を指示し、空きレベルを生成する必要がある。この処理をスワップ処理と称する。

【0049】

従来、スワップ処理レベルの決定法としてはLRU(Least Recently Used)法やランダム法が利用されているが、本実施例ではプロセッサへのデータ無効化命令発効数の削減を目的として1つのアドレスのみを管理しているレベルを優先してスワップ対象レベルに選択する(図3ステップS5)。

【0050】

図4は図3のスワップ対象レベル決定(図3ステップS5)の処理を示すフローチャートである。この図4を参照してスワップ対象レベル決定の処理について説明する。

【0051】

まず、コヒーレンシ制御回路11は上記のステップS1でコピーキャッシュ11aを索引した時の情報を用いて、1つのみアドレスを管理しているレベルを優先対象レベルと認識するとともに、その数を認識して、その数がn個以上(2≦n≦最大レベル数)であることを確認する(図4ステップS11)。

【0052】

この条件を満たしていない場合、コヒーレンシ制御回路11は全レベルの中からLRU法やランダム法等でスワップ対象レベルを選択する(図4ステップS12)。また、この条件を満たしている場合、コヒーレンシ制御回路11は優先対象レベルの中からLRU法やランダム法等でスワップ対象レベルを選択する(図4ステップS13)。

【0053】

コヒーレンシ制御回路11は、上記のようにして選択されたスワップ対象レベルに格納されていたアドレスのデータを保持するプロセッサに対してデータ掃き出し命令を出力するが(図3ステップS6)、その際、2つのアドレスを管理しているレベルがスワップ対象レベルとして選択された場合には2つのデータ掃き出し命令がプロセッサに対して出力され、1つのアドレスを管理しているレベルがスワップ対象レベルとして選択された場合には1つのデータ掃き出し命令がプロセッサに対して出力される。プロセッサはデータ掃き出し命令を受取ると、そのデータがダーティならば主メモリへの書き戻しを、そうでないならば破棄する処理を行う。

【0054】

この後、コヒーレンシ制御回路11はコピーキャッシュミス時の動作、すなわち第二バス102に該リードリクエストを発行し、第二バス102に接続される全てのセルのコヒーレンシ制御回路がそのリクエストを取込み、コピーキャッシュを索引し、配下のプロセッサがダーティで該アドレスデータを保持していたならばそのデータを、いずれのプロセッサもダーティデータを保持していないのならば該リクエストアドレスのデータを保持する主メモリからの読出しデータを、リクエスト元のプロセッサ12に返却する処理を行う(図3ステップS7)。

【0055】

コヒーレンシ制御回路11は上記のステップS6の処理で空いたレベルに該リクエストアドレスやステータス情報、及びセル情報を格納し(図3ステップS8)、リードリクエストの処理を終了する。尚、上記のコピーキャッシュ情報掃き出しレベル選択の処理は主メモリに保持されたプログラムを実行することによって動作する。このプログラムはマルチプロセッサシステムを構成するオペレーティングシステム(OS)の一機能であり、通常、ハードディスク等に格納されており、システム運用時に主メモリにロードされて実行される。

【0056】

図5〜図7は図1のコピーキャッシュ11aから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路(図示せず)に送るまでの構成を示すブロック図である。これら図5〜図7を参照してメモリアクセスTAT(Turn Around Time)を増加させることなく、上述した機能を実現する例について説明する。以下の説明では、本実施例ではコピーキャッシュレベル数を12とし、1つのセットアドレスで管理できるアドレス数を2とする。

【0057】

図5は従来技術における構成例で、最初のクロックサイクルでセットアドレス1101によってコピーキャッシュ111から格納データを読出してレジスタ116で受ける。次のクロックサイクルでは、ECC(Error Correction Coding)回路117によって1ビットエラーを訂正し、レジスタ118で受ける。

【0058】

次のクロックサイクルでは、ヒット/ミスチェック(Hit/Miss Check)回路119にてコピーキャッシュ111に該リクエストアドレス及びデータステータス情報が格納されていないことと、レベルに空きがないこととを識別し、スワップ決定回路121にその識別情報を送る。このヒット/ミスチェック回路119の動作と平行して、スワップレベル決定回路120にてLRU法またはランダム法等の既存の方法を用いて複数レベルの中からスワップ対象レベルを決定する。

【0059】

スワップ決定回路121はヒット/ミスチェック回路119及びスワップレベル決定回路120からの信号を受けて対象レベルをスワップする決定を行い、レジスタ122を介して図示せぬデータ掃き出し命令生成回路にスワップ対象レベル情報を送出する。

【0060】

図6を参照して、従来の回路構成をベースにして本発明の機能を実装した時の例について説明する。図6は図5に対して優先レベル認識回路123と優先レベル数カウント回路124とレジスタ125,126とが追加されており、スワップ決定までのクロックサイクルが1サイクル増加してしまっている。

【0061】

図6の図5との差分について説明すると、優先レベル認識回路123は1ビットエラー修正後の情報から優先レベルとなる1つの(X個以下の)アドレスのみを管理しているレベルを識別する。Xは固定値“1”またはプログラムにて設定できるものである。

【0062】

優先レベル数カウント回路124は優先レベルと認識された数をカウントし、そのカウント数をスワップレベル決定回路120に送るが、回路遅延の関係上、一旦レジスタ125に格納する必要が生じてしまう。

【0063】

スワップレベル決定回路120は優先レベル数が4以上(m個以上)であった場合に優先レベルの中からLRU法またはランダム法等にてスワップレベルを決定し、優先レベル数が4(m個)に満たない場合に全12レベルの中からLRU法またはランダム法等にてスワップレベルを決定する。

【0064】

図7を参照して本発明における回路構成例について説明する。本発明における回路構成の特徴として、優先レベル認識回路123と優先レベル数カウント回路124とをECC回路117と平行して設けることによって、図6に示す構成に比べて1クロック早く優先レベル数をカウントすることができる。

【0065】

このため、スワップレベル決定回路120も1クロック早くスワップレベルを決定することが可能となるため、データ掃き出し命令生成回路にスワップ対象レベル情報を従来例の図5と同じタイミングで送出することが可能となる。つまり、メモリアクセスTATに影響を与えることなく、本発明の機能を実装可能としている。

【0066】

ここで問題になるのは、優先レベル認識回路123に入力する信号としてECC回路117による1ビットエラー訂正を行う前の読出しデータを入力しているため、確率的には低いが優先レベル認識を誤ってしまう可能性があるということである。

【0067】

この場合、優先レベル数カウント回路124の結果が±1の誤差を含むこととなり、厳密には優先レベルの中からスワップレベルを決定するところを全12レベルの中からスワップレベルを決定してしまうケースやそれとは逆に、全12レベルの中からスワップレベルを決定するところを優先レベル3個(m−1個)の中からスワップレベルを決定してしまうこともあり得る。

【0068】

しかしながら、上記のケースでスワップレベルの決定に厳密さが欠けたとしても、もともとランダムな要素が大きいことから問題となることはなく、目的の機能を達成することができる。

【0069】

近年のプロセッサでは、プログラムコードを主メモリからリードする場合に、プロセッサで読込んだデータを更新しないことを示すフラグ(以下、コマンドフラグとする)を付与してリード命令を発行する場合がある。並列処理等で複数のプロセッサで同じプログラムコードを使用するケースを想定すると、コピーキャッシュからスワップレベルを決定する際に、プログラムコード以外の一過性のデータ等をスワップレベルとして優先的に選択することによって、プロセッサで使用中のプログラムコードがスワップアウトされる可能性が減少して高速化につながることが考えられる。

【0070】

このケースに対応するにはコピーキャッシュに格納する情報にコマンドフラグを加え、さらに優先レベル認識回路において規定数以下のアドレスのみ管理しているレベルを認識する部分をコマンドフラグ認識回路に置き換えて、コマンドフラグが有効でないレベルを優先レベルとして認識することによって実現可能である。

【0071】

この他にも、特開2003−316756号公報に記載のように複数のプロセッサが共有していることを示すステータス情報を持つレベルを優先的にコピーキャッシュからスワップアウトする方式もあり、この場合、プロセッサのキャッシュからダーティデータが出力されないため、I/O帯域有効利用に効果がある反面、管理下にある複数のプロセッサで共有していた命令コードがスワップアウトされると、共有していた全プロセッサでキャッシングされていた命令コードが無効になってしまい、この場合、キャッシュ利用効率が低下してしまうことが予想される。

【0072】

このように、プログラムの特性によって理想的なスワップアウト処理は変わるため、優先レベル認識回路において規定数以下のアドレスのみ管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路の3つを組み込んでおき、3つの回路の中からプログラムアクセス可能なレジスタの設定値によって選択可能とする手段を持つことも可能である。

【0073】

図8は図1のコピーキャッシュ11aから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路(図示せず)に送るまでの他の構成を示すブロック図である。図8に示す構成は上述した3つの回路の中からプログラムアクセス可能なレジスタの設定値によって選択可能とする時の構成例を示している。

【0074】

図8において、最初のクロックサイクルでセットアドレス1101によってコピーキャッシュ111から格納データを読出してレジスタ132で受ける。次のクロックサイクルでは、規定数以下のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路133と、プログラムコード以外のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路134と、複数プロセッサで共有していることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路135と、自セル搭載のメモリアドレス帯に格納されているレベルをスワップ優先レベルとして認識する回路136とでそれぞれ処理が行われる。

【0075】

131は優先モード切替レジスタで、プログラムがアクセス可能なレジスタである。優先モード切替レジスタ131の値によって4つの優先レベル認識回路133〜136の中の1つを選択器137で選択し、優先レベル数カウント回路138に送出する。優先レベル数カウント回路138以降の動作は上述した通りである。

【0076】

このように、本実施例では、メモリアクセスTATを増加することなく、スワップ対象レベル選択時に管理アドレス数の少ないレベルを優先的にスワップし、プロセッサに対して発行されるデータ掃き出し命令数を削減することによって、通常命令が使用するI/O(Input/Output)帯域を増加してデータ処理能力を向上させることができる。

【0077】

また、本実施例では、優先対象レベル数をカウントして、その数が一定数以上である場合にのみ優先対象の中からスワップ対象レベルを決定する構成をとり、優先度の高いレベル数が少なくなった時にスワップ対象レベルが極端に集中してしまうことを防ぐことによって、性能低下を抑えることができる。

【0078】

さらに、本実施例では、管理アドレス数の少ないレベルが優先してスワップされるため、管理アドレス数の大きいレベルの存在確率が上がり、これはコピーキャッシュの利用効率向上を意味するが、結果的にプロセッサが持っているコピーキャッシュの利用効率を向上させることになる。

【図面の簡単な説明】

【0079】

【図1】本発明の一実施例によるマルチプロセッサシステムの構成を示すブロック図である。

【図2】図1のコピーキャッシュの構成を示すブロック図である。

【図3】図1のコヒーレンシ制御回路の動作を示すフローチャートである。

【図4】図3のスワップ対象レベル決定の処理を示すフローチャートである。

【図5】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの構成を示すブロック図である。

【図6】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの構成を示すブロック図である。

【図7】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの構成を示すブロック図である。

【図8】図1のコピーキャッシュから読出したキーアドレス、アドレス管理情報、ステータス情報を読出してからスワップ対象レベルを決定してデータ掃き出し命令生成回路に送るまでの他の構成を示すブロック図である。

【符号の説明】

【0080】

1,2 セル

11,21 コヒーレンシ制御回路

11a,21a コピーキャッシュ

12,13,

22,23 プロセッサ

12a,13a,

22a,23a キャッシュメモリ

14,24 主メモリ

101 第一バス

102 第二バス

111 コピーキャッシュ

112 リクエストアドレス

113 ステータス情報

114 複数アドレス管理情報

115 デコーダ

116,118,

122,125,

126,132,

139 レジスタ

123 優先レベル認識回路

124,138 優先レベル数カウント回路

131 優先モード切替レジスタ

133 規定数以下のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路

134 プログラムコード以外のアドレスを管理しているレベルをスワップ優先レベルとして認識する回路

135 複数プロセッサで共有していることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路

136 自セル搭載のメモリアドレス帯に格納されているレベルをスワップ優先レベルとして認識する回路

137 選択器

1101 セットアドレス

1102 キーアドレス

【特許請求の範囲】

【請求項1】

各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを1以上備える分散共有メモリ方式のマルチプロセッサシステムであって、

前記コヒーレンシ制御回路は、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュと、前記コピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する手段とを有することを特徴とするマルチプロセッサシステム。

【請求項2】

前記コピーキャッシュは、前記プロセッサが発行するリクエストアドレスに含まれるキーアドレスと、前記リクエストアドレスの一部に対応して割り当てたアドレス管理情報と、管理する複数アドレス各々に対応したステータス情報とを格納し、前記リクエストアドレスに含まれるセットアドレスによってアクセスされることを特徴とする請求項1記載のマルチプロセッサシステム。

【請求項3】

前記コヒーレンシ制御回路は、前記プロセッサが発行したリードリクエストによって前記コピーキャッシュを索引する索引手段と、

前記索引手段でヒットした時に前記コピーキャッシュを更新せずに該当するアドレスデータを前記プロセッサに受け渡すことを該当するプロセッサに指示する第1の手段と、

前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがあれば前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第2の手段と、

前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがなければ管理しているアドレスの数が規定数以下のレベルを優先的に掃き出して空きレベルを生成した後に前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第3の手段とを含むことを特徴とする請求項1または請求項2記載のマルチプロセッサシステム。

【請求項4】

前記コヒーレンシ制御回路は、前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがなければアドレスの数が規定数以下のレベルをスワップ優先レベルとして識別する手段と、

そのスワップ優先レベルの数を認識するとともに優先レベルの数が規定数以上であることを識別した時に前記優先レベルの中から少なくともLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する手段とを含むことを特徴とする請求項3記載のマルチプロセッサシステム。

【請求項5】

前記コヒーレンシ制御回路は、前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがなければ優先レベルと識別しかつ管理しているアドレスの数が規定数以下のレベルの数が規定数に満たない場合に全レベルの中からLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する手段を含むことを特徴とする請求項3記載のマルチプロセッサシステム。

【請求項6】

前記コヒーレンシ制御回路は、前記第3の手段で前記コピーキャッシュの空きレベルに前記アドレスデータを格納する時に前記掃き出されたアドレスについてキャッシュ掃き出し命令を作成して前記プロセッサに発行する手段を含むことを特徴とする請求項3から請求項5のいずれか記載のマルチプロセッサシステム。

【請求項7】

コピーキャッシュ情報を前記セットアドレスにて読出した後にECC(Error Correction Coding)論理にて1ビットエラー訂正を行う構成を採る場合に、前記アドレスの数が1つだけのレベルを前記スワップ優先レベルとして識別する回路と、そのスワップ優先レベルの数を認識する回路と、前記優先レベルの数が規定数以上であることを認識する回路とが、前記1ビットエラー訂正を行う前のコピーキャッシュ情報読出し情報を入力信号として前記ECC論理と平行してその認識結果を出力することを特徴とする請求項4または請求項5記載のマルチプロセッサシステム。

【請求項8】

前記優先レベルを認識する回路において、規定数以下のアドレスのみ管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路との3つの回路を組み込んでおき、前記3つの回路の中からプログラムアクセス可能なレジスタの設定値に応じて選択可能とすることを特徴とする請求項7記載のマルチプロセッサシステム。

【請求項9】

各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを1以上備える分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法であって、

前記コヒーレンシ制御回路が、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行することを特徴とするコピーキャッシュ情報掃き出しレベル選択方法。

【請求項10】

前記コピーキャッシュが、前記プロセッサが発行するリクエストアドレスに含まれるキーアドレスと、前記リクエストアドレスの一部に対応して割り当てたアドレス管理情報と、管理する複数アドレス各々に対応したステータス情報とを格納し、前記リクエストアドレスに含まれるセットアドレスによってアクセスされることを特徴とする請求項9記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項11】

前記コヒーレンシ制御回路が、前記プロセッサが発行したリードリクエストによって前記コピーキャッシュを索引する第1の処理と、前記第1の処理でヒットした時に前記コピーキャッシュを更新せずに該当するアドレスデータを前記プロセッサに受け渡すことを該当するプロセッサに指示する第2の処理と、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがあれば前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第3の処理と、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがなければ管理しているアドレスの数が規定数以下のレベルを優先的に掃き出して空きレベルを生成した後に前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第4の処理とを実行することを特徴とする請求項9または請求項10記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項12】

前記コヒーレンシ制御回路が、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがなければアドレスの数が規定数以下のレベルをスワップ優先レベルとして識別する処理と、そのスワップ優先レベルの数を認識するとともに優先レベルの数が規定数以上であることを識別した時に前記優先レベルの中から少なくともLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する処理とを実行することを特徴とする請求項11記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項13】

前記コヒーレンシ制御回路が、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがなければ優先レベルと識別しかつ管理しているアドレスの数が規定数以下のレベルの数が規定数に満たない場合に全レベルの中からLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する処理を実行することを特徴とする請求項11記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項14】

前記コヒーレンシ制御回路が、前記第4の処理で前記コピーキャッシュの空きレベルに前記アドレスデータを格納する時に前記掃き出されたアドレスについてキャッシュ掃き出し命令を作成して前記プロセッサに発行する処理を実行することを特徴とする請求項11から請求項13のいずれか記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項15】

コピーキャッシュ情報を前記セットアドレスにて読出した後にECC(Error Correction Coding)論理にて1ビットエラー訂正を行う構成を採る場合に、前記アドレスの数が1つだけのレベルを前記スワップ優先レベルとして識別する回路と、そのスワップ優先レベルの数を認識する回路と、前記優先レベルの数が規定数以上であることを認識する回路とが、前記1ビットエラー訂正を行う前のコピーキャッシュ情報読出し情報を入力信号として前記ECC論理と平行してその認識結果を出力することを特徴とする請求項12または請求項13記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項16】

前記優先レベルを認識する回路において、規定数以下のアドレスのみ管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路との3つの回路を組み込んでおき、前記3つの回路の中からプログラムアクセス可能なレジスタの設定値に応じて選択可能とすることを特徴とする請求項15記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項17】

各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを1以上備える分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法のプログラムであって、前記コヒーレンシ制御回路のコンピュータに、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行させるためのプログラム。

【請求項1】

各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを1以上備える分散共有メモリ方式のマルチプロセッサシステムであって、

前記コヒーレンシ制御回路は、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュと、前記コピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する手段とを有することを特徴とするマルチプロセッサシステム。

【請求項2】

前記コピーキャッシュは、前記プロセッサが発行するリクエストアドレスに含まれるキーアドレスと、前記リクエストアドレスの一部に対応して割り当てたアドレス管理情報と、管理する複数アドレス各々に対応したステータス情報とを格納し、前記リクエストアドレスに含まれるセットアドレスによってアクセスされることを特徴とする請求項1記載のマルチプロセッサシステム。

【請求項3】

前記コヒーレンシ制御回路は、前記プロセッサが発行したリードリクエストによって前記コピーキャッシュを索引する索引手段と、

前記索引手段でヒットした時に前記コピーキャッシュを更新せずに該当するアドレスデータを前記プロセッサに受け渡すことを該当するプロセッサに指示する第1の手段と、

前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがあれば前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第2の手段と、

前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがなければ管理しているアドレスの数が規定数以下のレベルを優先的に掃き出して空きレベルを生成した後に前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第3の手段とを含むことを特徴とする請求項1または請求項2記載のマルチプロセッサシステム。

【請求項4】

前記コヒーレンシ制御回路は、前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがなければアドレスの数が規定数以下のレベルをスワップ優先レベルとして識別する手段と、

そのスワップ優先レベルの数を認識するとともに優先レベルの数が規定数以上であることを識別した時に前記優先レベルの中から少なくともLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する手段とを含むことを特徴とする請求項3記載のマルチプロセッサシステム。

【請求項5】

前記コヒーレンシ制御回路は、前記索引手段でヒットミスした時に前記コピーキャッシュに空きレベルがなければ優先レベルと識別しかつ管理しているアドレスの数が規定数以下のレベルの数が規定数に満たない場合に全レベルの中からLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する手段を含むことを特徴とする請求項3記載のマルチプロセッサシステム。

【請求項6】

前記コヒーレンシ制御回路は、前記第3の手段で前記コピーキャッシュの空きレベルに前記アドレスデータを格納する時に前記掃き出されたアドレスについてキャッシュ掃き出し命令を作成して前記プロセッサに発行する手段を含むことを特徴とする請求項3から請求項5のいずれか記載のマルチプロセッサシステム。

【請求項7】

コピーキャッシュ情報を前記セットアドレスにて読出した後にECC(Error Correction Coding)論理にて1ビットエラー訂正を行う構成を採る場合に、前記アドレスの数が1つだけのレベルを前記スワップ優先レベルとして識別する回路と、そのスワップ優先レベルの数を認識する回路と、前記優先レベルの数が規定数以上であることを認識する回路とが、前記1ビットエラー訂正を行う前のコピーキャッシュ情報読出し情報を入力信号として前記ECC論理と平行してその認識結果を出力することを特徴とする請求項4または請求項5記載のマルチプロセッサシステム。

【請求項8】

前記優先レベルを認識する回路において、規定数以下のアドレスのみ管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路との3つの回路を組み込んでおき、前記3つの回路の中からプログラムアクセス可能なレジスタの設定値に応じて選択可能とすることを特徴とする請求項7記載のマルチプロセッサシステム。

【請求項9】

各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを1以上備える分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法であって、

前記コヒーレンシ制御回路が、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行することを特徴とするコピーキャッシュ情報掃き出しレベル選択方法。

【請求項10】

前記コピーキャッシュが、前記プロセッサが発行するリクエストアドレスに含まれるキーアドレスと、前記リクエストアドレスの一部に対応して割り当てたアドレス管理情報と、管理する複数アドレス各々に対応したステータス情報とを格納し、前記リクエストアドレスに含まれるセットアドレスによってアクセスされることを特徴とする請求項9記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項11】

前記コヒーレンシ制御回路が、前記プロセッサが発行したリードリクエストによって前記コピーキャッシュを索引する第1の処理と、前記第1の処理でヒットした時に前記コピーキャッシュを更新せずに該当するアドレスデータを前記プロセッサに受け渡すことを該当するプロセッサに指示する第2の処理と、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがあれば前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第3の処理と、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがなければ管理しているアドレスの数が規定数以下のレベルを優先的に掃き出して空きレベルを生成した後に前記リードリクエストを他のすべてのセルに発行して検索させて得られたアドレスデータを前記プロセッサに受け渡しかつ前記コピーキャッシュの空きレベルに前記アドレスデータを格納する第4の処理とを実行することを特徴とする請求項9または請求項10記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項12】

前記コヒーレンシ制御回路が、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがなければアドレスの数が規定数以下のレベルをスワップ優先レベルとして識別する処理と、そのスワップ優先レベルの数を認識するとともに優先レベルの数が規定数以上であることを識別した時に前記優先レベルの中から少なくともLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する処理とを実行することを特徴とする請求項11記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項13】

前記コヒーレンシ制御回路が、前記第1の処理でヒットミスした時に前記コピーキャッシュに空きレベルがなければ優先レベルと識別しかつ管理しているアドレスの数が規定数以下のレベルの数が規定数に満たない場合に全レベルの中からLRU(Least Recently Used)法及びランダム法のいずれかにてスワップ対象レベルを決定する処理を実行することを特徴とする請求項11記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項14】

前記コヒーレンシ制御回路が、前記第4の処理で前記コピーキャッシュの空きレベルに前記アドレスデータを格納する時に前記掃き出されたアドレスについてキャッシュ掃き出し命令を作成して前記プロセッサに発行する処理を実行することを特徴とする請求項11から請求項13のいずれか記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項15】

コピーキャッシュ情報を前記セットアドレスにて読出した後にECC(Error Correction Coding)論理にて1ビットエラー訂正を行う構成を採る場合に、前記アドレスの数が1つだけのレベルを前記スワップ優先レベルとして識別する回路と、そのスワップ優先レベルの数を認識する回路と、前記優先レベルの数が規定数以上であることを認識する回路とが、前記1ビットエラー訂正を行う前のコピーキャッシュ情報読出し情報を入力信号として前記ECC論理と平行してその認識結果を出力することを特徴とする請求項12または請求項13記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項16】

前記優先レベルを認識する回路において、規定数以下のアドレスのみ管理しているレベルをスワップ優先レベルとして認識する回路と、コマンドフラグが点灯していないレベルをスワップ優先レベルとして認識する回路と、共有されていることを示すステータスを持つレベルをスワップ優先レベルとして認識する回路との3つの回路を組み込んでおき、前記3つの回路の中からプログラムアクセス可能なレジスタの設定値に応じて選択可能とすることを特徴とする請求項15記載のコピーキャッシュ情報掃き出しレベル選択方法。

【請求項17】

各々キャッシュメモリを備える複数のプロセッサと、主メモリと、前記プロセッサと前記主メモリとの間のキャッシュコヒーレンシを保証するコヒーレンシ制御回路とを含むセルを1以上備える分散共有メモリ方式のマルチプロセッサシステムに用いるコピーキャッシュ情報掃き出しレベル選択方法のプログラムであって、前記コヒーレンシ制御回路のコンピュータに、前記キャッシュメモリのコピーを保持しかつ複数のアドレスを1レベルで管理可能なコピーキャッシュのスワップが発生した際に管理しているアドレス数の少ないレベルを優先的に掃き出すよう制御する処理を実行させるためのプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−330948(P2006−330948A)

【公開日】平成18年12月7日(2006.12.7)

【国際特許分類】

【出願番号】特願2005−151728(P2005−151728)

【出願日】平成17年5月25日(2005.5.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成18年12月7日(2006.12.7)

【国際特許分類】

【出願日】平成17年5月25日(2005.5.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]