マルチプロセッサシステム及び入出力制御装置並びにリクエスト発行方法

【課題】マルチプロセッサシステムにおいて、アドレス一致先行ライトリクエストが存在するか否かを判定するための判定処理によって、後続のリクエストの処理が待たされないようにする。

【解決手段】アドレス一致先行ライトリクエスト検出処理部23は、入力バッファ21の入力側において、外部から入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファ21に登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報22を登録する。登録処理部27は、アドレス一致情報が登録されるまで、入力バッファ21に登録されているリクエストの出力(順序保証バッファ28への登録)を待ち合わせる。

【解決手段】アドレス一致先行ライトリクエスト検出処理部23は、入力バッファ21の入力側において、外部から入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファ21に登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報22を登録する。登録処理部27は、アドレス一致情報が登録されるまで、入力バッファ21に登録されているリクエストの出力(順序保証バッファ28への登録)を待ち合わせる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードと、クロスバーネットワークを介して各ノードと接続される入出力制御装置とを備えたマルチプロセッサシステムに関し、特に、共有メモリの一貫性が保たれるように、入出力制御装置からノードに対して発行するライトリクエスト及びリードリクエストの発行順を制御するリクエスト発行技術に関する。

【背景技術】

【0002】

従来から、メモリの一貫性を保証するため、入力されたリードリクエストとアクセス先のアドレスを同一にする未完了のライトリクエスト(アドレス一致先行ライトリクエスト)が存在するか否かを判定するということが行われている。その際、従来は、一般に、入力されたリードリクエストを入力バッファに一旦登録し、その後、アドレス一致先行ライトリクエストが存在するか否かを判定するようにしている(例えば、特許文献1参照)。

【0003】

このような処理は、図15に示すようなマルチプロセッサシステムにおいても行われている。同図に示すマルチプロセッサシステムは、複数の入出力デバイス1−1〜1−nと、各入出力デバイス毎の入出力制御装置2−1〜2−nと、クロスバーネットワーク3と、複数のノード4−1〜4−mとから構成されている。

【0004】

各入出力デバイス1−1〜1−nは、それぞれ入出力制御装置2−1〜2−nを介してクロスバーネットワーク3に接続され、更に、クロスバーネットワーク3を介して各ノード4−1〜4−mに接続されている。

【0005】

ノード4−1〜4−mは、それぞれクロスバーネットワーク3に接続されるメモリ制御部41を備え、メモリ制御部41は、その配下にプロセッサ44、45と、ディレクトリ42と、各プロセッサ44、45によって共有される共有メモリ43とを備えている。

【0006】

各入出力デバイス1−1〜1−nからのメモリリクエスト(ライトリクエスト及びリードリクエストを含む。単にリクエストという場合もある)は、それぞれ入出力制御装置2−1〜2−n及びクロスバーネットワーク3を介して該当するノードに送られる。入出力制御装置2−1〜2−nは、入出力デバイス1−1〜1−nからのメモリリクエストをノードに対して発行する際、共有メモリ43の一貫性が保たれるように、その発行順を制御する機能を有する。即ち、PCIバス仕様リビジョン2.1等に規定されているように、ライトリクエストに関しては、先行するライトリクエストが完了してから後続のライトリクエストを発行し、リードリクエストに関しては、アクセス先を同じにする未完了のライトリクエスト(アドレス一致先行ライトリクエスト)が存在するか否かを調べ、存在する場合は、アドレス一致先行ライトリクエストが完了してから後続のリードリクエストを発行するようにしている。

【0007】

図16は、入出力制御装置2−1の構成例を示すブロック図であり、入出力デバイス1−1から入力されたリードリクエストに対するアドレス一致先行ライトリクエストが存在するか否かの判定処理を、従来一般的に行われているように、リードリクエストを一旦入力バッファに登録してから行うようにした場合の構成を示している。即ち、図16は、従来の入出力制御装置2−1の構成例を示すブロック図である。

【0008】

図16に示した入出力制御装置2−1は、入力バッファ101と、アドレス一致先行ライトリクエスト検出処理部102と、アドレス一致管理バッファ103と、一致判定回路105と、順序保証バッファ106と、引き抜きポインタ108と、FIFOポインタ109と、ポインタセレクタ110と、発行処理部111と、リクエストセレクタ112と、制御部113とを備えている。なお、他の入出力制御装置も入出力制御装置2−1と同様の構成を有している。

【0009】

〔動作の説明〕

次に、入出力制御装置として図16に示した構成を有する入出力制御装置を用いた場合の、マルチプロセッサシステムの動作について説明する。

【0010】

入出力デバイス1−1が発行したメモリリクエストは、一旦、入出力制御装置2−1内の入力バッファに登録される。

【0011】

入出力制御装置2−1内のアドレス一致先行ライトリクエスト検出処理部102は、図17のフローチャートに示すように、入力バッファ101の先頭に登録されているリクエストを入力し、そのリクエストがライトリクエストなのかリードリクエストなのかを判定する(ステップA1、A2)。

【0012】

今、入力バッファ101から入力したリクエストがライトリクエストであったとすると(ステップA2がYES)、アドレス一致先行ライトリクエスト検出処理部102は、上記ライトリクエストに含まれているライトアドレスをアドレス一致管理バッファ103に登録すると共に、そのライトアドレスに対する有効フラグを「有効」とする(ステップA3、A4)。

【0013】

その後、アドレス一致先行ライトリクエスト検出処理部102は、上記ライトリクエストを順序保証バッファ106に登録すると共に、そのライトリクエストに対する待ち合わせフラグを「有効」にする(ステップA5、A6)。待ち合わせフラグが「有効」になっている間、上記ライトリクエストは、発行を待ち合わされる。

【0014】

更に、アドレス一致先行ライトリクエスト検出処理部102は、上記ライトリクエストの発行許可を受けるために、リクエストセレクタ112及びクロスバーネットワーク3を介して該当するノード(例えば、ノード4−1)に対して、ライトアドレスを含むディレクトリ検索要求を発行する(ステップA7)。その際、アドレス一致先行ライトリクエスト検出処理部102は、制御部113に対してセレクタ切り替え要求を送り、制御部113から切り替え完了通知が送られてきてからディレクトリ検索要求を発行する。また、制御部113は、アドレス一致先行ライトリクエスト検出処理部102からセレクタ切り替え要求が送られてくると、リクエストセレクタ112を発行処理部111を選択する状態からアドレス一致先行ライトリクエスト検出処理部102を選択する状態に変更し、その後、切り替え完了通知を返却する。また、制御部113は、切り替え完了通知を返却してから所定時間(アドレス一致先行ライトリクエスト検索処理部102がディレクトリ検索要求を発行するのに十分な時間)が経過すると、リクエストセレクタ112を、発行処理部111を選択する状態に戻す。

【0015】

入出力制御装置2−1からディレクトリ検索要求が送られてきたノード4−1内のメモリ制御部41は、ディレクトリ42を参照し、上記ディレクトリ検索要求に含まれているライトアドレスをアクセスすることが可能か否かを判定する。ディレクトリ42には、例えば、共有メモリ43の各アドレスがロック状態にあるのか、フリー状態にあるのかを示すロック情報が登録されていおり、上記ライトアドレスに対するロック情報がフリー状態の場合は、アクセス可能であると判定し、ロック状態の場合は、アクセス不能と判定する。

【0016】

そして、メモリ制御部41は、アクセス可能と判定した場合は、上記ライトアドレスに対応するロック情報をロック状態にした後、要求元の入出力制御装置2−1に対して発行許可を返却し、アクセス不能と判定した場合は、差戻指示を返却する。

【0017】

ノード4−1から返却された発行許可、差戻指示は、入出力制御装置2−1内の制御部113で受信される。

【0018】

制御部113は、ノード4−1から発行許可が返却された場合は、図18のフローチャートに示すように、発行許可されたライトリクエストの待ち合わせフラグ107を解除し、その値を「有効」から「無効」に変更する(ステップB1)。これにより、上記ライトリクエストは、順序保証バッファ106から発行可能な状態になる。なお、順序保証バッファ106に登録されたリクエストの発行動作は、後で、図20を用いて説明する。

【0019】

これに対して、ノード4−1から差戻指示が返却された場合は、図19のフローチャートに示すように、先ず、引き抜きポインタ108が指し示す順序保証バッファ106のエントリを、差戻が指示されたライトリクエストが格納されているエントリを指し示すものに変更し(ステップC1)、次いで、ポインタセレクタ110をFIFOポインタ109を選択する状態から引き抜きポインタ108を選択する状態に切り替え(ステップC2)、更に、発行処理部111に対してディレクトリ検索要求の発行を指示する(ステップC3)。その後、制御部113は、ポインタセレクタ110の状態を、FIFOポインタ109を選択する状態に戻す(ステップC4)。

【0020】

上記したステップC2において、ポインタセレクタ110の状態が切り替えられることにより、順序保証バッファ106からは、差戻が指示されたライトリクエストが発行処理部111に対して出力される。

【0021】

発行処理部111は、順序保証バッファ106からリクエストが入力された後、制御部113からディレクトリ検索要求の発行が指示された場合は、上記リクエストの代わりに、上記リクエスト中のライトアドレスを含んだディレクトリ検索要求を該当するノードに対して発行する。これに対して、順序保証バッファ106からリクエストが入力された後、制御部113からディレクトリ検索要求の発行が指示されなかった場合は、上記リクエストをそのまま該当するノード4−1に発行する。この例では、制御部113がステップC3において、ディレクトリ検索要求の発行を指示しているので、発行処理部111は、リクエスト中のライトアドレスを含んだディレクトリ検索要求を該当するノード4−1に対して発行することになる。

【0022】

アドレス一致先行ライトリクエスト検出処理部102が入力バッファ101から入力したリクエストがライトリクエストの場合は、上記した処理が行われる。次に、アドレス一致先行ライトリクエスト検出処理部102が入力バッファ101からリードリクエストを入力した場合の動作について説明する。

【0023】

図17のフローチャートに示すように、アドレス一致先行ライトリクエスト検出処理部102は、入力バッファ101から入力したリクエストがリードリクエストの場合(ステップA1、A2がNO)は、先ず、上記リードリクエストに含まれているリードアドレスを一致判定回路105に渡す(ステップA8)。

【0024】

一致判定回路105は、リードアドレスが渡されると、アドレス一致管理バッファ103を検索し、有効フラグ104が「有効」となっているライトアドレスの中に、上記リードアドレスと同一のアドレスが存在するか否かを調べる。そして、そのようなアドレスが存在する場合には、アドレス一致先行ライトリクエスト検出処理部102に対してアドレス一致先行ライトリクエストが有ることを通知し、そのようなアドレスが存在しない場合は、アドレス一致先行ライトリクエストが無いことを通知する。

【0025】

アドレス一致先行ライトリクエスト検出処理部102は、アドレス一致先行ライトリクエスト無しが通知された場合(ステップA9がNO)は、ステップA1で入力したリードリクエストを該当するノードに発行する(ステップA12)。その際、ステップA7でディレクトリ検索要求を発行した場合と同様に、制御部113に対してセレクタ切り替え要求を出力し、制御部113から切り替え完了が通知された後、リードリクエストを発行する。

【0026】

これに対して、アドレス一致先行ライトリクエスト有りが通知された場合(ステップA9がYES)は、ステップA1で入力したリードリクエストを順序保証バッファ106に登録すると共に、上記リードリクエストの待ち合わせフラグ107を無効にする(ステップA10、A11)。

【0027】

次に、順序保証バッファ106に登録されているリクエストを発行する場合の動作を、図20のフローチャートを参照して説明する。

【0028】

制御部113は、順序保証バッファ106に登録されているリクエストを、登録順に発行するため、FIFOポインタ109が指し示している順序保証バッファ106のエントリに登録されているリクエストの待ち合わせフラグ107が有効になっている場合(ステップD1、D2がYES)は、無効に変更されるのを待ち合わせ(ステップD2がNOとなるのを待ち合わせ)、無効になっている場合(ステップD2がNO)は、FIFOポインタ109によって指し示されているリクエストを順序保証バッファ106から読み出す(ステップD3)。このリクエストは、発行処理部111に入力され、該当するノードに発行される。

【0029】

その後、制御部113は、ステップD3で読み出したリクエストがライトリクエストであったか否かを判断し(ステップD4)、ライトリクエストであった場合(ステップD4がYES)は、アドレス一致管理バッファ104に登録されている有効フラグ104の内の、今回読み出したライトリクエストに対応する有効フラグを「無効」に変更し(ステップD5)、その後、FIFOポインタ109を更新し、次のエントリを指し示すようにする(ステップD6)。これに対して、ステップD3で読み出したリクエストがリードリクエストであった場合(ステップD4がNO)は、ステップD5を飛ばしてステップD6の処理を行う。ステップD6が終了すると、制御手段113は、ステップD1の処理に戻る。

【0030】

【特許文献1】特開2001−331363号公報

【発明の開示】

【発明が解決しようとする課題】

【0031】

従来は、上述したように、図16に示すような入出力制御装置2−1〜2−nを用いてメモリの一貫性が保証されるように、リクエストの発行順を制御しているが、次のような問題があった。

【0032】

第1に、リードリクエストを入力バッファ101に一旦登録し、その後、上記リードリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを判定するアドレス一致判定処理を行っているため、このアドレス一致判定処理に要する時間だけ、後続のリクエストの処理が遅れてしまうという問題がある。

【0033】

第2に、入力バッファ101で受け付けたリクエストがライトリクエストである場合、アドレス一致先行ライトリクエスト検出処理部102が無条件でディレクトリ検索要求を発行しているため、同一のライトアドレスを含むライトリクエストが連続した場合、差戻指示が多発してトラフィックが増加してしまうという問題がある。

【0034】

第3に、アドレス一致先行ライトリクエストが存在するリードリクエストは一旦順序保証バッファ106に登録され、その後、FIFOポインタ109によってその登録エントリが指し示されるまで、発行が待ち合わされるため、上記アドレス一致先行ライトリクエストと上記リードリクエストとの間に存在する無関係なライトリクエストの発行許可待ちの影響を受けてしまい性能が低下するという問題がある。

【0035】

第4に、アドレス一致先行ライトリクエストが存在しないリードリクエストは、順序保証バッファ106をバイパスさせるが、このときリクエストセレクタ112が順序保証バッファ106を選択する状態になっていると、上記リードリクエストの発行が待たされるため、後続のリクエストに対する処理が止まってしまうという問題がある。

【0036】

〔発明の目的〕

そこで、本発明の目的は、マルチプロセッサシステムの処理速度を向上させると共に、トラフィックを低減させることにある。

【課題を解決するための手段】

【0037】

本発明にかかる第1のマルチプロセッサシステムは、

複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードと、該各ノードとクロスバーネットワークを介して接続された入出力制御装置とを備え、前記入出力制御装置が、リクエストが登録されると共に該登録されたリクエストの発行を待ち合わせることが必要か否かを示す待ち合わせフラグが登録される順序保証バッファと、該順序保証バッファに登録されている待ち合わせフラグの内の、ノードから発行許可されたリクエストに対応する待ち合わせフラグを待ち合わせ不要を示すものに変更し、前記順序保証バッファに登録されている最古のリクエストに対応する待ち合わせフラグが待ち合わせ不要を示している場合、前記最古のリクエストを該当するノードに発行する制御部とを有するマルチプロセッサシステムであって、

外部から入力されたリクエストが登録されると共に、該リクエストに対するアドレス一致情報が登録される入力バッファと、

該入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、前記入力バッファに登録された前記リクエストに対応付けてアドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録するアドレス一致先行ライトリクエスト検出処理部と、

前記入力バッファに登録されている最古のリクエストに対応付けてアドレス一致情報が登録されていることを条件にして、前記最古のリクエストと待ち合わせ必要を示す待ち合わせフラグとを前記順序保証バッファに登録する登録処理部とを備えたことを特徴とする。

【0038】

本発明にかかる第2のマルチプロセッサシステムは、第1のマルチプロセッサシステムにおいて、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがライトリクエストで、且つ該ライトリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記最古のリクエストの発行許可要求を該当するノードに対して発行する構成を有し、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続ライトリクエストが登録されている場合は、該アドレス一致後続ライトリクエストの発行許可要求を該当するノードに対して発行し、該発行許可要求に応答してノードから発行許可が返却された場合は、前記アドレス一致後続ライトリクエストの待ち合わせフラグを待ち合わせ不要を示すものに変更する構成を有することを特徴とする。

【0039】

本発明にかかる第3のマルチプロセッサシステムは、第2のマルチプロセッサシステムにおいて、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、該アドレス一致後続リードリクエストを該当するノードに発行する構成を有することを特徴とする。

【0040】

本発明にかかる第4のマルチプロセッサシステムは、第3のマルチプロセッサシステムにおいて、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがリードリクエストで、且つ該リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを前記順序保証バッファに登録する構成を有し、

前記制御部が、

前記登録処理部によって前記順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、該リードリクエストを該当するノードへ発行する構成を有することを特徴とする。

【0041】

本発明にかかる第5のマルチプロセッサシステムは、第1〜第4のマルチプロセッサシステムにおいて、

前記順序保証バッファのエントリ数と同数のエントリを有するアドレス一致管理バッファと、

前記入力バッファのエントリ数と前記順序保証バッファのエントリ数とを加算した数の有効フラグを保持する有効フラグ保持部とを備え、且つ、

前記アドレス一致先行ライトリクエスト検出処理部が、

前記入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを、前記アドレス一致管理バッファに登録されているアドレスの中に、前記リクエスト中のアドレスと一致し、且つ対応する有効フラグが有効になっているアドレスが存在するか否かに基づいて判定する構成と、

前記入力バッファに入力されるリクエストがライトリクエストの場合、該ライトリクエストに含まれているアドレスを前記アドレス一致管理バッファに登録すると共に、前記有効フラグ保持部に保持されている有効フラグの内の、前回有効にした有効フラグの次の有効フラグを有効にする構成とを有し、

前記制御部が、

前記順序保証バッファからライトリクエストが発行されたとき、前記有効フラグ保持部に保持されている有効フラグの内の、有効にされた時期が最も古い有効フラグを無効に変更する構成を有することを特徴とする。

【0042】

本発明にかかる第1の入出力制御装置は、

複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードとクロスバーネットワークを介して接続され、且つ、リクエストが登録されると共に該登録されたリクエストの発行を待ち合わせることが必要か否かを示す待ち合わせフラグが登録される順序保証バッファと、該順序保証バッファに登録されている待ち合わせフラグの内の、ノードから発行許可されたリクエストに対応する待ち合わせフラグを待ち合わせ不要を示すものに変更し、前記順序保証バッファに登録されている最古のリクエストに対応する待ち合わせフラグが待ち合わせ不要を示している場合、前記最古のリクエストを該当するノードに発行する制御部とを備えた入出力制御装置であって、

外部から入力されたリクエストが登録されると共に、該リクエストに対するアドレス一致情報が登録される入力バッファと、

該入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、前記入力バッファに登録された前記リクエストに対応付けてアドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録するアドレス一致先行ライトリクエスト検出処理部と、

前記入力バッファに登録されている最古のリクエストに対応付けてアドレス一致情報が登録されていることを条件にして、前記最古のリクエストと待ち合わせ必要を示す待ち合わせフラグとを前記順序保証バッファに登録する登録処理部とを備えたことを特徴とする。

【0043】

本発明にかかる第2の入出力制御装置は、第1の入出力制御装置において、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがライトリクエストで、且つ該ライトリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記最古のリクエストの発行許可要求を該当するノードに対して発行する構成を有し、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続ライトリクエストが登録されている場合は、該アドレス一致後続ライトリクエストの発行許可要求を該当するノードに対して発行し、該発行許可要求に応答してノードから発行許可が返却された場合は、前記アドレス一致後続ライトリクエストの待ち合わせフラグを待ち合わせ不要を示すものに変更する構成を有することを特徴とする。

【0044】

本発明にかかる第3の入出力制御装置は、第2の入出力制御装置において、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、該アドレス一致後続リードリクエストを該当するノードに発行する構成を有することを特徴とする。

【0045】

本発明にかかる第4の入出力制御装置は、第3の入出力制御装置において、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがリードリクエストで、且つ該リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを前記順序保証バッファに登録する構成を有し、

前記制御部が、

前記登録処理部によって前記順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、該リードリクエストを該当するノードへ発行する構成を有することを特徴とする。

【0046】

本発明にかかる第5の入出力制御装置は、第1〜第4の入出力制御装置において、

前記順序保証バッファのエントリ数と同数のエントリを有するアドレス一致管理バッファと、

前記入力バッファのエントリ数と前記順序保証バッファのエントリ数とを加算した数の有効フラグを保持する有効フラグ保持部とを備え、且つ、

前記アドレス一致先行ライトリクエスト検出処理部が、

前記入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを、前記アドレス一致管理バッファに登録されているアドレスの中に、前記リクエスト中のアドレスと一致し、且つ対応する有効フラグが有効になっているアドレスが存在するか否かに基づいて判定する構成と、

前記入力バッファに入力されるリクエストがライトリクエストの場合、該ライトリクエストに含まれているアドレスを前記アドレス一致管理バッファに登録すると共に、前記有効フラグ保持部に保持されている有効フラグの内の、前回有効にした有効フラグの次の有効フラグを有効にする構成とを有し、

前記制御部が、

前記順序保証バッファからライトリクエストが発行されたとき、前記有効フラグ保持部に保持されている有効フラグの内の、有効にされた時期が最も古い有効フラグを無効に変更する構成を有することを特徴とする。

【0047】

本発明にかかる第1のリクエスト発行方法は、

複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードと、該各ノードとクロスバーネットワークを介して接続された入出力制御装置とを備え、前記入出力制御装置が、リクエストが登録されると共に該登録されたリクエストの発行を待ち合わせることが必要か否かを示す待ち合わせフラグが登録される順序保証バッファと、該順序保証バッファに登録されている待ち合わせフラグの内の、ノードから発行許可されたリクエストに対応する待ち合わせフラグを待ち合わせ不要を示すものに変更し、前記順序保証バッファに登録されている最古のリクエストに対応する待ち合わせフラグが待ち合わせ不要を示している場合、前記最古のリクエストを該当するノードに発行する制御部とを有するマルチプロセッサシステムにおけるリクエスト発行方法であって、

外部から入力されたリクエストが登録されると共に、該リクエストに対するアドレス一致情報が登録される入力バッファに対して外部からリクエストが入力されたとき、アドレス一致先行ライトリクエスト検出処理部が、前記リクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、前記入力バッファに登録された前記リクエストに対応付けてアドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録し、

登録処理部が、前記入力バッファに登録されている最古のリクエストに対応付けてアドレス一致情報が登録されていることを条件にして、前記最古のリクエストと待ち合わせ必要を示す待ち合わせフラグとを前記順序保証バッファに登録することを特徴とする。

【0048】

本発明にかかる第2のリクエスト発行方法は、第1のリクエスト発行方法において、

前記登録処理部が、前記入力バッファに登録されている最古のリクエストがライトリクエストで、且つ該ライトリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記最古のリクエストの発行許可要求を該当するノードに対して発行し、

前記制御部が、前記順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続ライトリクエストが登録されている場合は、該アドレス一致後続ライトリクエストの発行許可要求を該当するノードに対して発行し、該発行許可要求に応答してノードから発行許可が返却された場合は、前記アドレス一致後続ライトリクエストの待ち合わせフラグを待ち合わせ不要を示すものに変更することを特徴とする。

【0049】

本発明にかかる第3のリクエスト発行方法は、第2のリクエスト発行方法において、

前記制御部が、前記順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、該アドレス一致後続リードリクエストを該当するノードに発行することを特徴とする。

【0050】

本発明にかかる第4のリクエスト発行方法は、第3のリクエスト発行方法において、

前記登録処理部が、前記入力バッファに登録されている最古のリクエストがリードリクエストで、且つ該リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを前記順序保証バッファに登録し、

前記制御部が、前記登録処理部によって前記順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、該リードリクエストを該当するノードへ発行することを特徴とする。

【0051】

〔作用〕

アドレス一致先行ライトリクエスト検出処理部は、入力バッファの入力側において、入力バッファに外部から入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファに登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録する。登録処理部では、アドレス一致情報が登録されるまで、入力バッファからのリクエストの出力(順序保証バッファへの登録)を待ち合わせる。即ち、アドレス一致先行ライトリクエストが存在するか否かの判定処理がパイプライン化されるため、後続のリクエストの処理が待たされることがなくなる。

【0052】

また、登録処理部は、入力バッファに登録されている最古のリクエストがライトリクエストであっても、上記ライトリクエストに対するアドレス一致先行ライトリクエストが存在する場合には、上記リクエストの発行許可要求は発行せず、アドレス一致先行ライトリクエストが存在しない場合のみ、発行許可要求を発行する。また、制御部は、順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、上記最古のリクエストをアドレス一致先行ライトリクエストとしているライトリクエスト(アドレス一致後続ライトリクエスト)が存在する場合は、このアドレス一致後続ライトリクエストの発行許可要求を該当するノードに発行する。これにより、トラフィックの増加を防止することができる。

【0053】

また、制御部は、順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、順序保証バッファに上記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、そのアドレス一致後続リードリクエストを該当するノードに発行する。これにより、アドレス一致先行ライトリクエストとアドレス一致後続リードリクエストとの間に、他のライトリクエストが存在する場合であっても、アドレス一致後続リードリクエストの発行が待たされることがなくなる。

【0054】

また、登録処理部は、入力バッファに登録されている最古のリクエストがリードリクエストで、且つ上記リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、上記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを順序保証バッファに登録する。また、制御部は、登録処理部によって順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、そのリードリクエストを該当するノードへ発行する。これにより、入力バッファにおいて、アドレス一致先行ライトリクエストが存在しないリードリクエストによって、後続のリクエストが待たされることがなくなる。

【発明の効果】

【0055】

本発明によれば、アドレス一致先行ライトリクエストが存在するか否かを判定するための判定処理によって、後続のリクエストの処理が待たされることがないという効果を得ることができる。その理由は、入力バッファの入力側において、外部から入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファに登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録するアドレス一致先行ライトリクエスト検出処理部と、アドレス一致情報が登録されるまで、入力バッファに登録されているリクエストの出力(順序保証バッファへの登録)を待ち合わせる登録処理部とを備えているからである。即ち、アドレス一致先行ライトリクエストが存在するか否かの判定処理がパイプライン化されるため、後続のリクエストの処理が待たされることがなくなる。

【発明を実施するための最良の形態】

【0056】

次に本発明の実施の形態について図面を参照して詳細に説明する。

【0057】

〔実施の形態の構成の説明〕

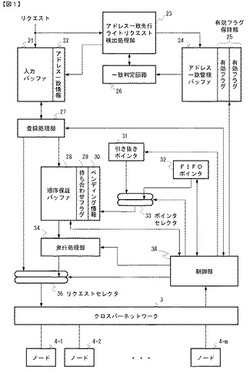

本発明にかかるマルチプロセッサシステムの実施の形態は、図15に示したマルチプロセッサシステムにおいて、入出力制御装置2−1〜2−nとして図1に示す構成を有する入出力制御装置を使用することにより実現される。

【0058】

図1を参照すると、本実施の形態で使用する入出力制御装置2−1〜2−nは、入力バッファ21と、アドレス一致先行ライトリクエスト検出処理部23と、アドレス一致管理バッファ24と、有効フラグ保持部25と、一致判定回路26と、登録処理部27と、順序保証バッファ28と、引き抜きポインタ31と、FIFOポインタ32と、ポインタセレクタ33と、発行処理部34と、リクエストセレクタ35と、制御部36とから構成されている。なお、入出力制御装置2−1〜2−nは、同一の構成を有しているため、以下では入出力制御装置2−1を例に挙げて構成を説明する。

【0059】

入力バッファ21は、複数のエントリ(例えば、128エントリ)を有し、各エントリには、入出力デバイス1−1から発行されたリクエスト(リードリクエスト及びライトリクエストを含む)が登録されると共に、そのリクエストに対するアドレス一致情報22が登録される。アドレス一致情報22は、図2に示すように、アドレス一致先行ライトリクエストが存在するか否かを示す有無情報と、アドレス一致先行ライトリクエストを特定する先行リクエスト特定情報とを含んでいる。なお、リクエストの登録時、入力バッファ21の各エントリは循環的に使用される。即ち、最初のリクエストが入力された場合は、入力バッファ21の第0番目のエントリにリクエストを登録し、次のリクエストが入力された場合は、第1番目のエントリにリクエストを登録するというように、登録対象エントリを順次変更していき、最後のエントリ(第127番目のエントリ)にリクエストを登録した場合は、再び、第0番目のエントリを登録対象エントリとする。

【0060】

アドレス一致管理バッファ24は、順序保証バッファ28と同数のエントリ(例えば、64エントリ)を有し、最新の64個分のライトリクエスト中のライトアドレスが登録される。アドレス一致管理バッファ24のエントリ数が順序保証バッファ28のエントリ数と同数で良い理由は、入力バッファ21から或るリクエストが出力されたとき、そのリクエストに対するアドレス一致先行ライトリクエストとなる可能性のあるリクエストは、順序保証バッファ28にその時点で登録されている64個のリクエストだけであるからである。

【0061】

有効フラグ保持部25は、入力バッファ21のエントリ数(この例では128エントリ)と順序保証バッファ28のエントリ数(この例では64エントリ)とを加算した数のエントリ(この例では192エントリ)を有しており、各エントリには、アドレス一致管理バッファ24の対応するエントリに格納されているライトアドレスが有効であるか否かを示す有効フラグが登録されている。有効フラグ保持部25の第j番目、第(j+64)番目、第(j+128)番目のエントリが、アドレス一致管理バッファ24の第j番目のエントリと対応している。

【0062】

順序保証バッファ28は、複数のエントリ(例えば64エントリ)を有し、各エントリには、登録処理部27によってリクエストが登録されると共に、そのリクエストに対する待ち合わせフラグ29およびペンディング情報30が登録される。なお、待ち合わせフラグ29は、対応するリクエストの発行を待ち合わせることが必要か否かを示すものであり、ペンディング情報は、それと対応付けて登録されているリクエストにアドレス一致先行ライトリクエストが存在するか否かを示す有無情報と、アドレス一致先行ライトリクエストを特定するための先行リクエスト特定情報とを含んでいる。また、順序保証バッファ28は、引き抜きポインタ31、FIFOポインタ32の内の、ポインタセレクタ33によって選択されているポインタが指し示しているエントリに登録されているリクエスト、待ち合わせフラグ29及びペンディング情報30を発行処理部34に対して出力している。

【0063】

引き抜きポインタ31及びFIFOポインタ32は、順序保証バッファ28の読み出し対象エントリを指し示すポインタである。ポインタセレクタ33は、制御部36の指示に従って引き抜きポインタ31、FIFOポインタ32の内の一方を選択するセレクタである。リクエストセレクタ35は、制御部36の指示に従って登録処理部27、発行処理部34の内の一方を選択するセレクタである。

【0064】

アドレス一致先行ライトリクエスト検出処理部23は、入力バッファ21の入力側に接続されている点、およびリードリクエストだけでなく、ライトリクエストについてもアドレス一致先行ライトリクエストが存在するか否かを調べる点が、図16に示した従来のアドレス一致先行ライトリクエスト検出処理部102との大きな相違点である。このアドレス一致先行ライトリクエスト検出処理部23が備えている主な機能は次の通りである。

【0065】

・入力バッファ21に入力されるリクエストがライトリクエストの場合は、一致判定回路26を利用して上記ライトリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べると共に、どのライトリクエストがアドレス一致先行ライトリクエストとなるのかを調べる。その後、調べた結果に基づいてアドレス一致情報22を作成し、上記ライトリクエストが登録された入力バッファ21のエントリにアドレス一致情報22を登録する。更に、上記ライトリクエスト中のライトアドレスを最新のライトアドレスとしてアドレス一致管理バッファ24に登録すると共に、有効フラグ保持部25の該当するエントリに有効を示す有効フラグを登録する。

【0066】

なお、アドレス一致管理バッファ24にライトアドレスを登録する際、アドレス一致先行ライトリクエスト検出処理部23は、アドレス一致管理バッファ24の各エントリを循環的に使用する。即ち、最初のライトアドレスはアドレス一致管理バッファ24の第0番目のエントリに登録し、次のライトアドレスは、第1番目のエントリに登録するというように順次登録対象エントリを更新していき、最後のエントリ(第63番目のエントリ)にライトアドレスを登録した場合は、再び、第0番目のエントリを登録対象エントリとする。また、有効フラグ保持部25に有効フラグを登録する場合、アドレス一致先行ライトアドレス検出処理部24は、有効フラグ保持部25の各エントリを循環的に使用する。即ち、アドレス一致管理バッファ24の第0番目のエントリに最初のライトアドレスを登録した場合は、有効フラグ保持部25の第0番目のエントリに有効を示す有効フラグを登録し、アドレス一致管理バッファ24に次のライトアドレスを登録した場合は、有効フラグ保持部25の第1番目のエントリに有効を示す有効フラグを登録するというように、順次登録対象エントリを更新していき、最後のエントリ(第191番目のエントリ)に有効を示す有効フラグを登録した場合は、再び、第0番目のエントリを登録対象エントリとする。

【0067】

・入力バッファ21に入力されるリクエストが、リードリクエストの場合、一致判定回路26を利用して上記リードリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べると共に、どのライトリクエストがアドレス一致先行ライトリクエストとなるかを調べる。その後、調べた結果に基づいてアドレス一致情報22を生成し、上記リードリクエストが登録された入力バッファ21のエントリにアドレス一致情報22を登録する。

【0068】

登録処理部27は、次のような機能を有する。

【0069】

・入力バッファ21の第0番目〜第127番目のエントリを順次読み出し対象エントリにし、最後のエントリ(第127番目のエントリ)を読み出し対象エントリにしたら、再び第0番目のエントリを読み出し対象エントリにする。読み出し対象エントリに、有効なアドレス一致情報22が登録されている場合は、読み出し対象エントリからリクエスト及びアドレス一致情報22を読み出し、アドレス一致情報22が無効になっている場合は、有効なアドレス一致情報22が登録されるのを待ってからリクエスト及びアドレス一致情報22を読み出す。読み出し対象エントリからリクエスト及びアドレス一致情報22を読み出すと、読み出し対象エントリ中のアドレス一致情報22を無効にすると共に、入力バッファ21から読み出したリクエストを順序保証バッファ28に登録する。リクエストの登録時、登録処理部27は、順序保証バッファ28の各エントリを循環的に使用する。

【0070】

・順序保証バッファ28に登録したリクエストが、ライトリクエストで、且つそのライトリクエストに対応するアドレス一致情報22が、アドレス一致先行ライトリクエストが無いことを示している場合は、上記ライトリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが必要なことを示す有効フラグ29(値が「有効」)を登録すると共に、ペンディング情報30として「無効」を登録する。更に、上記ライトリクエストに対するディレクトリ検索要求を該当するノードに発行し、その後、入力バッファ21の読み出し対象エントリを次のエントリに更新する。このディレクトリ検索要求には、上記ライトリクエスト中のライトアドレスが含まれると共に、上記ライトリクエストを格納した順序保証バッファ28のエントリを示す情報(エントリ番号)が含まれる。

【0071】

・順序保証バッファ28に登録したリクエストが、ライトリクエストで、且つそのライトリクエストに対応するアドレス一致情報22が、アドレス一致先行ライトリクエストが存在することを示している場合は、上記ライトリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが必要なことを示す有効フラグを登録すると共に、上記アドレス一致情報22をペンディング情報30として登録する。その後、入力バッファ21の読み出し対象エントリを次のエントリに更新する。

【0072】

・順序保証バッファ28に登録したリクエストが、リードリクエストで、且つそのリードリクエストに対応するアドレス一致情報22が、アドレス一致先行ライトリクエストが無いことを示している場合は、上記リードリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが不要なことを示す待ち合わせフラグ29(値が「無効」)を登録すると共に、ペンディング情報30として「無効」を登録する。更に、制御部36に対して、リードリクエスト発行要求を出力し、その後、読み出し対象エントリを次のエントリに更新する。なお、上記リードリクエスト発行要求には、上記リードリクエストを登録したエントリのエントリ番号が含まれている。

【0073】

・順序保証バッファ28に登録したリクエストが、リードリクエストで、且つそのリードリクエストに対するアドレス一致情報22が、アドレス一致先行ライトリクエストが存在することを示している場合は、上記リードリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが必要なことを示す有効フラグ29を登録すると共に、上記アドレス一致情報22をペンディング情報30として登録する。その後、入力バッファ21の読み出し対象エントリを次のエントリに更新する。

【0074】

制御部36は、次のような機能を有する。

【0075】

・ノード4−k(1≦k≦m)からリクエストの発行許可が返却された場合は、順序保証バッファ28に登録されているリクエストの内の、発行許可されたリクエストに対応する待ち合わせフラグ29の値を「無効」に変更し、そのリクエストの発行待ち合わせを解除する。なお、ノード4−kからの発行許可には、発行を許可するリクエストが格納されているエントリを示す情報が含まれている。即ち、ノード4−kは、入出力制御装置2−1から、ライトアドレス及びエントリ番号を含むディレクトリ検索要求が送られてきたとき、ディレクトリ42を検索してリクエストの発行を許可するか否かを決定し、リクエストの発行を許可するのであれば、上記エントリ番号を含む発行許可を返却し、許可しないのであれば、上記エントリ番号を含む差戻指示を返却する。

【0076】

・ノード4−kから差戻指示が返却された場合は、引き抜きポインタ31に上記差戻指示に含まれているエントリ番号を設定すると共に、ポインタセレクタ33の状態を引き抜きポインタ31を選択する状態に切り替え、更に、発行処理部34に対してディレクトリ検索要求の発行指示を出力する。その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。なお、上記ディレクトリ検索要求の発行指示には、上記エントリ番号が含まれている。

【0077】

・登録処理部27からリードリクエスト発行要求が入力された場合は、引き抜きポインタ31に上記リードリクエスト発行要求に含まれているエントリ番号を設定すると共に、ポインタセレクタ33の状態を引き抜きポインタ31を選択する状態に切り替え、更に、発行処理部34に対してリクエストの発行指示を出力する。その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。

【0078】

・FIFOポインタ32が指し示す順序保証バッファ28のエントリ(登録時期が最も古い、未発行のリクエストが登録されているエントリ)に登録されている待ち合わせフラグ29の値が「無効」で、且つ登録されているリクエストがライトリクエストの場合、発行処理部34に対してリクエストの発行指示を出力し、更に、有効フラグ保持部25の各エントリに保持されている有効フラグの内の、該当する有効フラグの値を「無効」に変更する。即ち、発行したライトリクエストに対応する有効フラグの値を「無効」にする。

【0079】

・発行処理部34に対して発行を指示したライトリクエストをアドレス一致先行ライトリクエストとしているライトリクエスト(アドレス一致後続ライトリクエスト)が順序保証バッファ28に登録されている場合は、引き抜きポインタ31に上記アドレス一致後続ライトリクエストが登録されているエントリのエントリ番号を設定すると共にポインタセレクタ33を引き抜きポインタ31を選択する状態にし、更に、発行処理部34に対してディレクトリ検索要求の発行指示を出力し、その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。なお、このディレクトリ検索要求の発行指示には、上記アドレス一致後続ライトリクエストが格納されているエントリのエントリ番号が含まれている。

【0080】

・発行処理部34に対して発行を指示したライトリクエストをアドレス一致先行ライトリクエストとしているリードリクエスト(アドレス一致後続リードリクエスト)が順序保証バッファ28に登録されている場合は、引き抜きポインタ31に上記アドレス一致後続リードリクエストが登録されているエントリのエントリ番号を登録すると共にポインタセレクタ33を引き抜きポインタ31を選択する状態にし、更に、発行処理部34に対してリクエストの発行指示を出力し、その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。

【0081】

発行処理部34は、次のような機能を有する。

【0082】

・制御部36からディレクトリ検索要求の発行指示が入力された場合は、順序保証バッファ28から出力されているライトリクエスト中のライトアドレスと上記発行指示中のエントリ番号とを含んだディレクトリ検索要求をリクエストセレクタ35を介して該当するノードに発行する。

【0083】

・制御部36からリクエストの発行指示が入力されている場合は、順序保証バッファ28から読み出されているリクエスト(リードリクエストの場合もあれば、ライトリクエストの場合もある)をリクエストセレクタ35を介して該当するノードに発行する。

【0084】

〔実施の形態の動作の説明〕

次に本実施の形態の動作について詳細に説明する。なお、以下の説明では、入出力デバイス1−1が入出力制御装置2−1に対してリクエストを発行した場合について説明するが、他の入出力デバイス1−2〜1−nが入出力制御装置2−2〜2−nに対してリクエストを発行した場合も同様の動作が行われる。

【0085】

入出力デバイス1−1が入出力制御装置2−1に発行したリクエストは、入出力制御装置2−1内の入力バッファ21及びアドレス一致先行ライトリクエスト検出処理部23に入力される。

【0086】

入力バッファ21は、リクエストが入力されると、自バッファ21が有している128個のエントリの内の、現在登録対象エントリとしているエントリに上記リクエストを登録し、その後、登録対象エントリを次のエントリに変更する。なお、初期状態においては、登録対象エントリは、第0番目のエントリになっている。

【0087】

一方、アドレス一致先行ライトリクエスト検出処理部23は、リクエストが入力される毎に、図3のフローチャートに示す処理を行う。

【0088】

アドレス一致先行ライトリクエスト検出処理部23は、リクエストが入力されると、先ず、入力されたリクエストがライトリクエストなのか、リードリクエストかを判定する(ステップS31)。

【0089】

そして、ライトリクエストである場合(ステップS31がYES)は、ライトリクエストに含まれているライトアドレスを一致判定回路26に渡し(ステップS32)、その後、一致判定回路26からの応答を待つ(ステップS33)。

【0090】

一致判定回路26は、ライトアドレスが渡されると、アドレス一致管理バッファ24に登録されているアドレスの中に、上記ライトアドレスと一致し、且つ有効フラグ保持部25に保持されている対応する有効フラグが「有効」になっているアドレスが存在するか否かに基づいて、アドレス一致先行ライトリクエストが存在するか否かを判定し、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。なお、アドレス一致先行ライトリクエストが存在すると判定した場合には、判定結果として、どのライトリクエスト(例えば、何個前のライトリクエスト)が、アドレス一致先行ライトリクエストとなるのかもアドレス一致先行ライトリクエスト検出処理部23に通知する。

【0091】

アドレス一致先行ライトリクエスト検出処理部23は、一致判定回路26からの通知に従ってアドレス一致情報22を生成し、入力バッファ21中の該当するエントリ(今回処理対象にしているライトリクエストが登録されたエントリ)に登録する(ステップS34)。即ち、一致判定回路26からアドレス一致先行ライトリクエストが存在しないことが通知された場合は、アドレス一致先行ライトリクエストが存在しないことを示す有無情報を含んだアドレス一致情報22を生成して該当するエントリに登録し、存在することが通知された場合は、アドレス一致先行ライトリクエストが存在することを示す有無情報およびどのライトリクエストがアドレス一致先行ライトリクエストとなるのかを示す先行リクエスト特定情報を含んだアドレス一致情報22を該当するエントリに登録する(ステップS34)。

【0092】

その後、アドレス一致先行ライトリクエスト検出処理部23は、今回処理対象にしているライトリクエスト中のライトアドレスを、アドレス一致管理バッファ24のエントリの内の、現在登録対象エントリにしているエントリに登録すると共に、有効フラグ保持部25の該当するエントリに登録されている有効フラグを「有効」にする(ステップS35、S36)。なお、アドレス一致先行ライトリクエスト検出処理部23は、初期状態においては、アドレス一致管理バッファ24の第0番目のエントリを登録対象エントリにしており、アドレスを格納する毎に、登録対象エントリを更新する。

【0093】

これに対して、入力されたリクエストがリードリクエストであると判定した場合(ステップS31がNO)は、上記リードリクエストに含まれているリードアドレスを一致判定回路26に渡し(ステップS37)、その後、一致判定回路26からの応答を待つ(ステップS38)。一致判定回路26は、リードアドレスが渡されると、前述した処理と同様の処理を行い、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。これにより、アドレス一致先行ライトリクエスト検出処理部23は、入力バッファ21のエントリの内の、今回処理対象にしているリードリクエストが登録されているエントリにアドレス一致情報22を登録する(ステップS39)。

【0094】

次に、アドレス一致先行ライトリクエスト検出処理部23およびアドレス一致判定回路26の動作を、具体例を挙げて説明する。

【0095】

今、有効フラグ保持部25の第0番目〜第191番目のエントリに登録されている有効フラグの値が図4(A)に示すものであるとする。なお、図4では、有効フラグの値「有効」を「1」で表し、「無効」を「0」で表している。

【0096】

図4(A)に示すように、有効フラグ保持部25の第0番目〜第7番目のエントリに登録されている有効フラグの値が「有効」になっているときに、ライトリクエスト(初期状態から数えて第8番目のリクエストであるとする。但し、最初のリクエストを第0番目のリクエストとする)が入力されると、アドレス一致先行ライトリクエスト検出処理部23は、上記ライトリクエスト中のライトアドレスを一致判定回路26に渡し、待ち状態となる(図3のステップS31がYES、S32、S33)。

【0097】

一致判定回路26は、ライトアドレスが渡されると、有効フラグ保持部25の第0番目〜第7番目のエントリに登録されている有効フラグの値が「有効」となっているので、上記エントリと対応するアドレス一致管理バッファ24の第0番目〜第7番目のエントリを比較対象エントリにして、上記ライトアドレスと一致するアドレスが登録されているか否かを調べることにより、アドレス一致先行ライトリクエストが存在するか否かを判定する。

【0098】

なお、前述したように、アドレス一致管理バッファ24の第j番目のエントリに対応する有効フラグ保持部25上のエントリは、第j番目、第(j+64)番目、第(j+128)番目の計3個のエントリであり、一致判定回路26は、アドレス一致管理バッファ24の第j番目のエントリに対応する有効フラグ保持部25上の3個のエントリの何れかに「有効」を示す有効フラグが登録されていれば、上記第j番目のエントリを比較対象エントリとする。また、一致判定回路26は、ライトアドレスと一致するアドレスが比較対象エントリ(第0番目〜第7番目のエントリ)に登録されているか否かを調べる際、アドレスの登録時期が最も新しいエントリ(第7番目のエントリ)から最も古いエントリ(第0番目のエントリ)に向かって比較処理を行う。そして、アドレスの登録時期が最も古いエントリまで調べてもライトアドレスと一致するアドレスが格納されているエントリが存在しなかった場合は、アドレス一致先行ライトリクエスト無しと判定し、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。これに対して、ライトアドレスと一致するアドレスが登録されているエントリを見つけた場合は、アドレス一致先行ライトリクエスト有りと判定し、アドレス一致先行ライトリクエスト検出処理部23に判定結果を通知する。このときの判定結果には、何個前のライトリクエストがアドレス一致先行ライトリクエストとなるのかを示す情報も含まれる。なお、アドレス一致先行ライトリクエストとなるライトリクエストが何個前のライトリクエストであるかは、例えば、ライトアドレスと一致するアドレスが登録されているエントリが、比較対象エントリの内の、アドレスの登録時期が新しい方から何番目のエントリであるかを調べることにより求めることができる。

【0099】

アドレス一致先行ライトリクエスト検出処理部23は、一致判定回路26から判定結果が通知されると、それに基づいてアドレス一致情報22を生成し、入力バッファ21の各エントリの内の、現在処理対象としているライトリクエストが登録されているエントリにアドレス一致情報22を登録する(ステップS34)。この例の場合、現在処理対象にしているライトリクエストは、初期状態から数えて第8番目のリクエストであり、上記ライトリクエストは、入力バッファ21の第8番目のエントリに格納されているので、第8番目のエントリにアドレス一致情報22を登録することになる。

【0100】

その後、アドレス一致先行ライトリクエスト検出処理部23は、現在処理対象にしているライトリクエスト中のライトアドレスを、アドレス一致管理バッファ24の第8番目のエントリに登録し(ステップS35)、更に、値「有効」が設定されている有効バッファ保持部25上のエントリの内の、エントリ番号が最も大きいエントリ(第7番目のエントリ)の次のエントリ(第8番目のエントリ)に、値「有効」を登録する(ステップS36)。

【0101】

また、図4(B)に示すように、有効フラグ保持部25の第3番目〜第135番目のエントリに登録されている有効フラグが値が「有効」になっているときにライトリクエスト(初期状態から数えて第136番目のリクエストとする)が入力された場合は、アドレス一致先行ライトリクエスト検出処理部23は、上記ライトリクエスト中のライトアドレスを一致判定回路26に渡し、待ち状態となる(ステップS31がYES、S32、S33)。

【0102】

一致判定回路26は、ライトアドレスが渡されると、有効フラグ保持部25の第3番目〜第135番目のエントリに登録されている有効フラグの値が「有効」となっているので、上記エントリと対応するアドレス一致管理バッファ24の第0番目〜第63番目のエントリを比較対象エントリにして、上記ライトアドレスと一致するアドレスが登録されているか否かを調べることにより、アドレス一致先行ライトリクエストが存在するか否かを判定する。その際、アドレスの登録時期が最も新しいエントリ(第7番目のエントリ)から順番に、比較処理を行うエントリのエントリ番号を順次減少させて比較処理を行う(但し、比較処理を行うエントリのエントリ番号が「0」となった場合は、次に比較処理を行うエントリのエントリ番号を「63」とする)。そして、アドレスの登録時期が最も古いエントリ(第8番目のエントリ)まで調べてもライトアドレスと一致するアドレスが格納されているエントリが存在しなかった場合は、アドレス一致先行ライトリクエスト無しと判定し、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。これに対して、ライトアドレスと一致するアドレスが登録されているエントリを見つけた場合は、アドレス一致先行ライトリクエスト有りと判定し、アドレス一致先行ライトリクエスト検出処理部23に判定結果を通知する。

【0103】

アドレス一致先行ライトリクエスト検出処理部23は、一致判定回路26から判定結果が通知されると、それに基づいてアドレス一致情報22を生成し、入力バッファ21の各エントリの内の、現在処理対象としているライトリクエストが登録されているエントリにアドレス一致情報22を登録する(ステップS34)。この例の場合、現在処理対象にしているライトリクエストは、初期状態から数えて第136番目のリクエストであり、上記ライトリクエストは、入力バッファ21の第8番目(136÷64=2余り8)のエントリに格納されているので、第8番目のエントリにアドレス一致情報22を登録することになる。

【0104】

その後、アドレス一致先行ライトリクエスト検出処理部23は、現在処理対象にしているライトリクエスト中のライトアドレスを、アドレス一致管理バッファ24の第8番目のエントリに登録し(ステップS35)、更に、値「有効」が設定されている有効バッファ保持部25上のエントリの内の、エントリ番号が最も大きいエントリ(第135番目のエントリ)の次のエントリ(第136番目のエントリ)に、値「有効」を登録する(ステップS36)。

【0105】

次に、登録処理部27の動作について説明する。

【0106】

登録処理部27は、図5のフローチャートに示すように、入力バッファ21の第0番目〜第127番目のエントリの内の、読み出し対象エントリに注目し、そのエントリに有効なアドレス一致情報22が登録されるのを待つ(ステップS501、S502)。なお、初期状態においては、第0番目のエントリを読み出し対象エントリにしている。

【0107】

そして、読み出し対象エントリに有効なアドレス一致情報が登録されると(ステップS502がYES)、読み出し対象エントリに登録されているリクエスト及びアドレス一致情報22を入力し、入力したリクエストを順序保証バッファ28の登録対象エントリに登録し、更に、登録対象エントリを次のエントリに更新する(ステップS503)。なお、初期状態においては、登録対象エントリは、第0番目のエントリになっている。

【0108】

その後、登録処理部27は、入力バッファ21から入力したリクエストがライトリクエストなのか、リードリクエストなのかを調べる(ステップS504)。

【0109】

ライトリクエストであった場合(ステップS504がYES)は、ステップS503で入力したアドレス一致情報22中の有無情報に基づいて、アドレス一致先行ライトリクエストが存在するか否かを判断する(ステップS505)。

【0110】

そして、アドレス一致先行ライトリクエストが存在しない場合(ステップS505がNO)は、ステップS503においてこのライトリクエストを登録した、順序保証バッファ28のエントリ中の待ち合わせフラグ29を「有効」にして上記リクエストが発行待ち合わせ状態となるようにすると共に、ペンディング情報30を「無効」にして上記ライトリクエストに関するディレクトリ検索要求の発行を許可する(ステップS506)。その後、発行処理部27は、制御部36に対してディレクトリ検索要求の発行許可要求を送り、制御部36から発行許可を受けたら、上記ライトリクエストに関するディレクトリ検索要求を発行する(ステップS507)。ディレクトリ検索要求には、上記ライトリクエスト中のライトアドレス及び上記ライトリクエストを登録した順序保証バッファ28のエントリ番号が含まれており、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードへ送られる。また、登録処理部27からのディレクトリ検索要求の発行許可要求を受け付けた制御部36は、リクエストセレクタ35を登録処理部27を選択する状態に切り替えた後、登録処理部27に対して発行許可を与え、更に所定時間後、リクエストセレクタ35を発行処理部34を選択する状態に戻す。その後、登録処理部27は、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再び、ステップS501の処理を行う。

【0111】

これに対して、アドレス一致先行ライトリクエストが存在する場合(ステップS505がYES)は、ステップS503においてこのライトリクエストを登録した、順序保証バッファ28のエントリ中の待ち合わせフラグ29を「有効」にして上記ライトリクエストが発行待ち合わせ状態になるようにすると共に、ペンディング情報30としてステップS503で入力したアドレス一致情報22を登録し、上記ライトリクエストに関するディレクトリ検索要求が発行待ち合わせ状態になるようにする(ステップS509)。その後、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再びステップS501の処理を行う。

【0112】

一方、ステップS503で入力したリクエストがリードリクエストであると判断した場合(ステップS504がNO)は、ステップS503で入力したアドレス一致情報22中の有無情報に基づいて、アドレス一致先行ライトリクエストが存在するか否かを判断する(ステップS510)。

【0113】

そして、アドレス一致先行ライトリクエストが存在しない場合(ステップS510がNO)は、ステップS503においてこのリードリクエストを格納した、順序保証バッファ28のエントリ中の待ち合わせフラグを「無効」にして上記リードリクエストを発行可能状態にすると共に、ペンディング情報30を「無効」にする(ステップS511)。次いで、登録処理部27は、制御部36に対して上記リードリクエストの発行を要求するリードリクエスト発行要求を出力し(ステップS512)、その後、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再び、ステップS501の処理を行う。なお、リードリクエスト発行要求には、リードリクエストを登録した順序保証バッファ28のエントリ番号が含まれている。また、制御部36がリードリクエスト発行要求を受け付けたときの動作は、図6のフローチャートを用いて後で詳しく説明する。

【0114】

これに対してアドレス一致先行ライトリクエストが存在する場合(ステップS510がYES)は、ステップS503においてこのリードリクエストを登録した、順序保証バッファ28のエントリ中の待ち合わせフラグ29を「有効」にして上記リードリクエストを発行待ち合わせ状態にすると共に、ステップS503で入力したアドレス一致情報22をペンディング情報30として登録する(ステップS513)。その後、登録処理部27は、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再びステップS501の処理を行う。

【0115】

次に、制御部36の動作について説明する。

【0116】

先ず、登録処理部27からのリードリクエスト発行要求を受け付けたときの動作を、図6のフローチャートを参照して説明する。

【0117】

制御部36は、登録処理部27からのリードリクエスト発行要求を受け付けると、先ず、上記要求に含まれているエントリ番号を引き抜きポインタに設定する(ステップS61)。上記エントリ番号は、発行対象にしているリードリクエストが格納されている、順序保証バッファ28上のエントリを示している。次いで、制御部36は、ポインタセレクタ33の状態を、引き抜きポインタ31を選択する状態に変更する(ステップS62)。これにより、順序保証バッファ28は、引き抜きポインタ31が指し示すエントリに登録されているリクエスト(発行対象にしているリードリクエスト)を、発行処理部34に対して出力する。その後、制御部36は、発行処理部34に対してリクエストの発行を指示する(ステップS63)。これにより、発行処理部34は、順序保証バッファ28から出力されているリードリクエストを、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。その後、制御部36は、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す(ステップS64)。

【0118】

次に、ノード(例えば、ノード4−1)からライトリクエストの発行許可が返却された場合の動作を、図7のフローチャートを参照して説明する。

【0119】

制御部36は、ノード4−1からライトリクエストの発行許可(発行を許可するライトリクエストが登録されているエントリのエントリ番号が含まれている)が送られてくると、順序保証バッファ28上のエントリの内の、上記発行許可に含まれているエントリ番号のエントリに登録されている待ち合わせフラグ29の値を「有効」から「無効」に変更し、上記ライトリクエストを発行可能状態にする(ステップS71)。

【0120】

次に、ノード(例えば、ノード4−1)から差戻指示が返却された場合の動作を、図8のフローチャートを参照して説明する。

【0121】

制御部36は、ノード4−1から差戻指示(差し戻すライトリクエストが登録されているエントリのエントリ番号を含む)が送られてくると、先ず、引き抜きポインタ31に、上記差戻指示に含まれているエントリ番号を設定し、その後、ポインタセレクタ33の状態を引き抜きポインタ31を選択する状態にする(ステップS81、S82)。これにより、順序保証バッファ28は、引き抜きポインタ31が指し示すエントリの登録されているライトリクエストを発行処理部34に対して出力する。その後、制御部36は、発行処理部34に対してディレクトリ検索要求の発行指示を出力する(ステップS83)。この発行指示には、差し戻すライトリクエストが登録されているエントリのエントリ番号が含まれている。発行処理部34は、ディレクトリ検索要求の発行指示が入力されると、順序保証バッファ28から出力されているライトリクエスト中のライトアドレス及び上記発行指示中のエントリ番号を含んだディレクトリ検索要求を生成し、生成したディレクトリ検索要求を、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノード4−1に発行する。その後、制御部36は、ポインタセレクタ33の状態を、FIFOポインタ32を選択する状態に戻す(ステップS84)。

【0122】

次に制御部36が順序保証バッファ28に登録されているライトリクエストを登録順に発行するために行っている動作を図9のフローチャートを参照して説明する。

【0123】

制御部36は、FIFOポインタ32が指し示している順序保証バッファ28のエントリに登録されている待ち合わせフラグ29が「無効」になるのを待ち合わせており(ステップS901、S902)、該当する待ち合わせフラグ29が「無効」となると(ステップS902がNO)、上記エントリに登録されているリクエストの種別を調べる(ステップS903)。

【0124】

そして、リードリクエストであった場合(ステップS903がYES)は、FIFOポインタ32を更新し、次のエントリを指し示すようにした後(ステップS918)、再び、ステップS901の処理を行う。

【0125】

これに対して、ライトリクエストであった場合(ステップS903がNO)は、発行処理部34に対してリクエストの発行を指示する(ステップS904)。これにより、発行処理部34は、順序保証バッファ28から出力されているライトリクエスト(FIFOポインタ32が指し示すエントリに登録されているリクエスト)を、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。

【0126】

その後、制御部36は、有効フラグ保持部25の各エントリに保持されている有効フラグの内の、今回発行したライトリクエストに対応する有効フラグを「無効」とする(ステップS905)。

【0127】

次に、制御部36は、今回発行したライトリクエストをアドレス一致先行ライトリクエストとしているライトリクエスト(アドレス一致後続ライトリクエスト)が、順序保証バッファ28に登録されているか否かを調べる(ステップS906)。この処理は、ペンディング情報30中の先行リクエスト特定情報を利用して行う。

【0128】

そして、アドレス一致後続ライトリクエストが登録されている場合(ステップS906がYES)は、先ず、上記アドレス一致後続ライトリクエストに対応するペンディング情報30を「無効」にする(ステップS907)。次いで、引き抜きポインタ31に、上記アドレス一致後続ライトリクエストが登録されているエントリのエントリ番号を設定し(ステップS908)、更に、ポインタセレクタ33を引き抜きポインタ31を選択する状態にする(ステップS909)。これにより、順序保証バッファ28からは、上記アドレス一致後続ライトリクエストが出力される。

【0129】

その後、制御部36は、発行処理部34に対してディレクトリ検索要求の発行指示を出力する(ステップS910)。この発行指示には、アドレス一致後続ライトリクエストが登録されているエントリのエントリ番号が含まれている。発行処理部34は、上記指示を受け付けると、順序保証バッファ28から出力されているアドレス一致後続ライトリクエスト中のライトアドレスと、上記発行指示中のエントリ番号とを含んだディレクトリ検索要求を、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。その後、制御部36は、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す(ステップS911)。

【0130】

これに対して、アドレス一致後続ライトリクエストが登録されていなかった場合(ステップS906がNO)及びステップS911の処理が終了した場合、制御部36は、今回発行したライトリクエストをアドレス一致先行ライトリクエストとしているリードリクエスト(アドレス一致後続リードリクエスト)が、順序保証バッファ28に登録されているか否かを調べる(ステップS912)。

【0131】

そして、登録されていない場合(ステップS912がNO)は、FIFOポインタ32が指し示すエントリを次のエントリに更新した後(ステップS918)、再び、ステップS901の処理を行う。

【0132】

これに対して、アドレス一致後続リードリクエストが登録されている場合(ステップS912がYES)は、先ず、上記アドレス一致後続リードリクエストに対応する待ち合わせフラグ29、ペンディング情報30を「無効」にする(ステップS913)。次いで、引き抜きポインタ31に上記アドレス一致後続リードリクエストが登録されているエントリのエントリ番号を設定し(ステップS914)、更に、ポインタセレクタ33を引き抜きポインタ31を選択する状態に切り替える(ステップS915)。これにより、順序保証バッファ28からは、上記アドレス一致後続リードリクエストが出力される。

【0133】

その後、制御部36は、発行処理部34に対してリクエストの発行を指示する(ステップS916)。これにより、発行処理部34は、順序保証バッファ28から出力されているアドレス一致後続リードリクエストを、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。

【0134】

次いで、制御部36は、ポインタセレクタ33を、FIFOポインタ32を選択する状態に戻し(ステップS917)、その後、ステップS912の処理を行う。ステップS912がNOとなると、FIFOポインタ32が保持しているエントリ番号をインクリメントし、次のエントリを指し示すようにする(ステップS918)。その後、制御部36は、再び、ステップS901の処理を行う。

【0135】

次に、タイミングチャートを用いて本実施の形態および従来技術の動作を説明する。

【0136】

図10は、本実施の形態の動作を示すタイミングチャートであり、本実施の形態の入出力制御装置2−1(図1参照)が、ライトアドレスの異なる3個のライトリクエストA、B、Cを受け付けたときの動作を示している。

【0137】

各ライトリクエストA、B、Cは、それぞれサイクル1、2、3において入力バッファ21のエントリa、b、cに登録される。また、各ライトリクエストA、B、Cのライトアドレスは、アドレス一致先行ライトリクエスト検出処理部23においてアドレス一致先行ライトリクエストの有無が調べられた後、それぞれサイクル2、3、4においてアドレス一致管理バッファ24のエントリα、β、γに登録される。

【0138】

その後、サイクル3、4、5において、入力バッファ21からライトリクエストA、B、Cが順次読み出され、順序保証バッファ28のエントリ0、1、2に登録される。ライトリクエストA、B、Cは、ライトアドレスが異なるため、アドレス一致先行ライトリクエストは存在しない。従って、各ライトリクエストA、B、Cが順序保証バッファ28に登録されると同時に、サイクル3、4、5において、ライトリクエストA、B、Cについてのディレクトリ検索要求A、B、Cがクロスバーネットワーク3を介して該当するノードに発行される。

【0139】

ノードにおいて、ディレクトリの検索が行われ、サイクル7においてライトリクエストAに対する発行許可Aが送られてくると、FIFOポインタ32が指し示しているエントリ0に登録されているライトリクエストがサイクル8においてリクエストセレクタ35、クロスバーネットワーク3を介して該当するネットワークに発行される。この後、FIFOポインタ32は、エントリ1を指し示す。

【0140】

サイクル9において、ライトリクエストCに対する発行許可Cが送られてくると、ライトリクエストCは、発行可能な状態になるが、このとき、FIFOポインタ32は、エントリ1を指し示しているので、エントリ2に登録されているライトリクエストCは、発行されない。

【0141】

その後、サイクル11において、ライトリクエストBに対する発行許可Bが送られてくると、ライトリクエストBが発行可能な状態となり、サイクル12において、該当するノードに発行され、その後、FIFOポインタ32が、エントリ2を指し示す。これにより、サイクル13において、ライトリクエストCが該当するノードに発行される。

【0142】

図11及び図12は、それぞれ従来技術及び本実施の形態の動作を示すタイミングチャートであり、ライトアドレスが同一のライトリクエストA、A'、A"を、従来技術及び本実施の形態の入出力制御装置2−1(図16及び図1参照)が受け付けた場合の動作を示している。

【0143】

従来技術の動作を示す図11を参照すると、各ライトリクエストA、A'、A"は、それぞれサイクル1、2、3において、入力バッファ101のエントリa、b、cに登録される。また、各ライトリクエストA、A'、A"のライトアドレスは、それぞれサイクル2、3、4において、アドレス一致管理バッファ23のエントリα、β、γに登録される。また、従来技術では、ライトリクエストアドレスの一致判定処理を行わないので、サイクル3、4、5において、ライトリクエストA、A'、A"が順序保証バッファ106のエントリ0、1、2に登録されると同時に、ライトリクエストA、A'、A"についてのディレクトリ検索要求A、A'、A"が該当するノードに発行される。

【0144】

ノードは、ディレクトリ検索要求A、A'、A"が競合するので、サイクル7、8、9において、ライトリクエストAの発行許可A、ライトリクエストA'、A"の差戻指示A'、A"を返却する。これにより、サイクル8においてライトリクエストAが該当するノードに発行され、サイクル9、10において、ライトリクエストA'、A"についてのディレクトリ検索要求A'、A"が該当するノードへ発行される。

【0145】

ノードは、ディレクトリ検索要求A'、A"が競合するので、サイクル11、12において、ライトリクエストA'の発行許可A'、ライトリクエストA"の差戻指示を返却する。これにより、サイクル12においてライトリクエストA'が該当するノードに発行され、サイクル13においてライトリクエストA"に関するディレクトリ検索要求A"が該当するノードに発行される。

【0146】

ノードは、ディレクトリ検索要求A"はアドレス競合しないので、ライトリクエストA"に対する発行許可A"を返却する。サイクル15において、発行許可A"を受信すると、サイクル16において、ライトリクエストA"を該当するノードに対して発行する。

【0147】

上記した動作が行われている間にクロスバーネットワーク3上を通過したリクエスト数は15個となり、要したサイクル数は16サイクルとなる。

【0148】

一方、本実施の形態の動作を示す図12を参照すると、各ライトリクエストA、A'、A"は、それぞれサイクル1、2、3において、入力バッファ21のエントリa、b、cに登録され、サイクル2、3、4において、アドレス一致管理バッファ24のエントリα、β、γに登録され、サイクル3、4、5において、順序保証バッファ28のエントリ0、1、2に登録される。本実施の形態では、ライトアドレスについてもアドレス一致先行ライトリクエストが存在するか否かを判定し、存在しない場合のみ、ディレクトリ検索要求を発行するようにしているので、ライトリクエストAに関するディレクトリ検索要求Aは、サイクル3において発行されるが、ライトリクエストA'、A"に関するディレクトリ検索要求A'、A"は、アドレス一致先行ライトリクエストAが存在するため、発行待ち状態となる。

【0149】

ノードでは、ディレクトリ検索要求Aは、アドレス競合がないので、サイクル7において、ライトリクエストAに対する発行許可Aを返却する。これより、サイクル8において、ライトリクエストAが該当するノードに発行される。

【0150】

ライトリクエストAが発行されると、ライトリクエストA'に対するアドレス一致先行ライトリクエストが存在しなくなるので、サイクル9において、ライトリクエストA'に対するディレクトリ検索要求A'が発行される。ライトリクエストA"には、アドレス一致先行ライトリクエストA'が存在するので、ディレクトリ検索要求A"の発行は待ち合わされる。

【0151】

ノードでは、ディレクトリ検索要求A'には、アドレス競合がないので、サイクル11において、ライトリクエストA'に対する発行許可A'を返却する。これにより、サイクル12において、ライトリクエストA'が該当するノードに発行される。

【0152】

ライトリクエストA'が発行されると、ライトリクエストA"に対するアドレス一致先行ライトリクエストが存在しなくなるので、サイクル13において、ライトリクエストA"に対するディレクトリ検索要求A"が該当するノードに発行される。

【0153】

ノードでは、ディレクトリ検索要求A"には、アドレス競合がないので、サイクル15において、ライトリクエストA"に対する発行許可A"を返却する。これにより、サイクル16において、ライトリクエストA"が発行される。

【0154】

上記した動作が行われている間にクロスバーネットワーク3上を通過したリクエスト数は9個となり、要したサイクル数は16サイクルとなる。本実施の形態では、リクエスト数が9個で済むため、リクエスト数が15個であった従来技術に比較してトラフィックを低減させることができる。

【0155】

図13及び図14は、それぞれ従来技術及び本実施の形態の動作を示すタイミングチャートであり、ライトリクエストA、B及びリードリクエストA、Cを、従来技術及び本実施の形態の入出力制御装置2−1(図16及び図1参照)が受け付けた場合の動作を示している。なお、ライトリクエストAのライトアドレスと、リードリクエストAのリードアドレスは同一であるとする。

【0156】

従来技術の動作を示す図13を参照すると、従来技術では、リードリクエストを入力バッファ101から読み出した後、アドレス一致判定を行うため、リードリクエストAのアドレス一致判定の影響でリードリクエストCのクロスバーネットワーク3への発行が遅れている。また、順序保証バッファ106に登録されたリードリクエストAは、アドレス一致先行ライトリクエストAが存在するので、ライトリクエストAの発行を待ち合わせるが、ライトリクエストAとリードリクエストAとの間に異なるアドレスのライトリクエストBがあるため、ライトリクエストAの発行だけでなく、ライトリクエストBの発行も待ち合わせなければならない。

【0157】

ライトリクエストA、Bが、サイクル3、4において順序保証バッファ106に登録されると同時に、ディレクトリ検索要求A、Bがクロスバーネットワーク3を介して該当するノードへ発行される。

【0158】

ノードは、ディレクトリ検索要求Aにはアドレス競合がないので、サイクル7において、ライトリクエストAの発行許可を返却する。これにより、サイクル8において、順序保証バッファ106からライトリクエストAが発行される。その後、サイクル11においてノードからライトリクエストBに対する発行許可が返却されると、サイクル12において、順序保証バッファ106からライトリクエストBが発行される。その後、サイクル13において、漸くリードリクエストAが発行されることになる。この動作の要するサイクル数は13サイクルである。

【0159】

一方、本実施の形態の動作を示す図14を参照すると、リードリクエストを入力バッファ21へ登録する時に、アドレス一致判定を行うためアドレス一致判定をパイプライン化でき、リードリクエストCはリードリクエストAのアドレス一致判定の影響を受けない。順序保証バッファ28に登録されたリードリクエストAは、アドレス一致先行リードリクエストが存在するので、ライトリクエストAの発行を待ち合わせるが、ライトリクエストAとリードリクエストAとの間に異なるアドレスのライトリクエストBがあっても、引き抜きポインタ31を利用した引き抜き制御の対象となるので、ライトリクエストBの発行まで待ち合わせる必要はない。

【0160】

ライトリクエストA、Bが、サイクル3、4において順序保証バッファに登録されると同時に、ディレクトリ検索要求A、Bがクロスバーネットワーク3を介して該当するノードへ発行される。

【0161】

ノードは、ディレクトリ検索要求Aには、アドレス競合がないので、サイクル7において、ライトリクエストAの発行許可を返却する。これにより、サイクル8において順序保証バッファ28からライトリクエストAが該当するノードへ発行される。

【0162】

リードリクエストAは、アドレス一致先行ライトリクエストであるライトリクエストAが、サイクル8において、順序保証バッファ28から発行されると、ペンディングが解除され、引き抜きポインタ31を利用した引き抜き制御により、サイクル9において、クロスバーネットワーク3を介して該当するノードに発行される。その後、サイクル11において、ノードからライトリクエストBに対する発行許可が返却されると、サイクル12において、順序保証バッファ28からライトリクエストBが発行される。この動作に要するサイクル数は12サイクルであり、13サイクル必要であった従来の技術に比較して性能が向上している。

【0163】

〔実施の形態の効果〕

本実施の形態によれば、アドレス一致先行ライトリクエストが存在するか否かを判定するための判定処理によって、後続のリクエストの処理が待たされることがないという効果を得ることができる。その理由は、入力バッファ21の入力側において、入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファ21に登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報22を登録するアドレス一致先行ライトリクエスト検出処理部23と、アドレス一致情報が登録されるまで、入力バッファ21に登録されているリクエストの出力(順序保証バッファ28への登録)を待ち合わせる登録処理部27とを備えているからである。即ち、アドレス一致先行ライトリクエストが存在するか否かの判定処理がパイプライン化されるため、後続のリクエストの処理が待たされることがなくなる。

【0164】

また、本実施の形態によれば、トラフィックの増加を防止することができるという効果を得ることができる。その理由は、入力バッファ21に登録されている最古のライトリクエストがライトリクエストであっても、上記ライトリクエストに対するアドレス一致先行ライトリクエストが存在する場合には、上記リクエストの発行許可要求(ディレクトリ検索要求)は発行せず、アドレス一致先行ライトリクエストが存在しない場合のみ、発行許可要求を発行する登録処理部27と、順序保証バッファ28に登録されている最古のリクエストを該当するノードに対して発行した際、上記最古のリクエストをアドレス一致先行ライトリクエストとしているライトリクエスト(アドレス一致後続ライトリクエスト)が存在する場合は、このアドレス一致後続ライトリクエストの発行許可要求(ディレクトリ検索要求)を該当するノードに発行する制御部36とを備えているからである。

【0165】

更に、本実施の形態によれば、アドレス一致先行ライトリクエストとアドレス一致後続リードリクエストとの間に、他のライトリクエストが存在する場合であっても、上記アドレス一致後続リードリクエストの発行が待たされることがなくなるという効果を得ることができる。その理由は、順序保証バッファ28に登録されている最古のリクエストを該当するノードに発行した際、順序保証バッファ28に上記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、そのアドレス一致後続リードリクエストを該当するノードに発行する制御部36を備えているからである。

【0166】

更に、本実施の形態によれば、入力バッファ21において、アドレス一致先行ライトリクエストが存在しないリードリクエストによって、後続のリクエストが待たされることがなくなるという効果を得ることができる。その理由は、入力バッファ21に登録されている最古のリクエストがリードリクエストで、且つ上記リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、上記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを順序保証バッファ28に登録する登録処理部27と、登録処理部27によって順序保証バッファ28に、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、そのリードリクエストを該当するノードへ発行する制御部36とを備えているからである。

【産業上の利用可能性】

【0167】

本発明は、複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードと、各ノードとクロスバーネットワークを介して接続された入出力制御装置とを備えたマルチプロセッサシステム等に利用することができる。

【図面の簡単な説明】

【0168】

【図1】本発明にかかる入出力制御装置2−1の実施の形態の構成例を示すブロック図である。

【図2】アドレス一致情報の一例を示す図である。

【図3】アドレス一致先行ライトリクエスト検出処理部23の処理例を示すフローチャートである。

【図4】アドレス一致先行ライトリクエスト検出処理部23及び一致判定回路26の動作を説明するための図である。

【図5】登録処理部27の処理例を示すフローチャートである。

【図6】リードリクエスト発行要求を受け付けたときの制御部36の処理例を示すフローチャートである。

【図7】ライトリクエストの発行許可を受け付けたときの制御部36の処理例を示すフローチャートである。

【図8】差戻指示を受け付けたときの制御部36の処理例を示すフローチャートである。

【図9】リクエストを登録順に発行するときの制御部36の処理例を示すフローチャートである。

【図10】実施の形態の動作を示すためのタイミングチャートである。

【図11】従来技術の動作を説明するためのタイミングチャートである。

【図12】実施の形態の動作を示すためのタイミングチャートである。

【図13】従来技術の動作を説明するためのタイミングチャートである。

【図14】実施の形態の動作を示すためのタイミングチャートである。

【図15】本発明を適用するマルチプロセッサシステムの構成例を示すブロック図である。

【図16】従来の入出力制御装置2−1の構成例を示すブロック図である。

【図17】アドレス一致先行ライトリクエスト検出処理部102の処理例を示すフローチャートである。

【図18】ライトリクエストの発行許可を受け付けたときの制御部113の処理例を示すフローチャートである。

【図19】差戻指示を受け付けたときの制御部113の処理例を示すフローチャートである。

【図20】リクエストを登録順に発行するときの制御部113の処理例を示すフローチャートである。

【符号の説明】

【0169】

1−1〜1−n…入出力デバイス

2−1〜2−n…入出力制御装置

21、101…入力バッファ

22…アドレス一致情報

23、102…アドレス一致先行ライトリクエスト検出処理部

24、103…アドレス一致管理バッファ

104…有効フラグ

25…有効フラグ保持部

26、105…一致判定回路

27…登録処理部

28、106…順序保証バッファ

29、107…待ち合わせフラグ

30…ペンディング情報

31、108…引き抜きポインタ

32、109…FIFOポインタ

33、110…ポインタセレクタ

34、111…発行処理部

35、112…リクエストセレクタ

36、113…制御部

3…クロスバーネットワーク

4−1〜4−m…ノード

41…メモリ制御部

42…ディレクトリ

43…共有メモリ

44、45…プロセッサ

【技術分野】

【0001】

本発明は、複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードと、クロスバーネットワークを介して各ノードと接続される入出力制御装置とを備えたマルチプロセッサシステムに関し、特に、共有メモリの一貫性が保たれるように、入出力制御装置からノードに対して発行するライトリクエスト及びリードリクエストの発行順を制御するリクエスト発行技術に関する。

【背景技術】

【0002】

従来から、メモリの一貫性を保証するため、入力されたリードリクエストとアクセス先のアドレスを同一にする未完了のライトリクエスト(アドレス一致先行ライトリクエスト)が存在するか否かを判定するということが行われている。その際、従来は、一般に、入力されたリードリクエストを入力バッファに一旦登録し、その後、アドレス一致先行ライトリクエストが存在するか否かを判定するようにしている(例えば、特許文献1参照)。

【0003】

このような処理は、図15に示すようなマルチプロセッサシステムにおいても行われている。同図に示すマルチプロセッサシステムは、複数の入出力デバイス1−1〜1−nと、各入出力デバイス毎の入出力制御装置2−1〜2−nと、クロスバーネットワーク3と、複数のノード4−1〜4−mとから構成されている。

【0004】

各入出力デバイス1−1〜1−nは、それぞれ入出力制御装置2−1〜2−nを介してクロスバーネットワーク3に接続され、更に、クロスバーネットワーク3を介して各ノード4−1〜4−mに接続されている。

【0005】

ノード4−1〜4−mは、それぞれクロスバーネットワーク3に接続されるメモリ制御部41を備え、メモリ制御部41は、その配下にプロセッサ44、45と、ディレクトリ42と、各プロセッサ44、45によって共有される共有メモリ43とを備えている。

【0006】

各入出力デバイス1−1〜1−nからのメモリリクエスト(ライトリクエスト及びリードリクエストを含む。単にリクエストという場合もある)は、それぞれ入出力制御装置2−1〜2−n及びクロスバーネットワーク3を介して該当するノードに送られる。入出力制御装置2−1〜2−nは、入出力デバイス1−1〜1−nからのメモリリクエストをノードに対して発行する際、共有メモリ43の一貫性が保たれるように、その発行順を制御する機能を有する。即ち、PCIバス仕様リビジョン2.1等に規定されているように、ライトリクエストに関しては、先行するライトリクエストが完了してから後続のライトリクエストを発行し、リードリクエストに関しては、アクセス先を同じにする未完了のライトリクエスト(アドレス一致先行ライトリクエスト)が存在するか否かを調べ、存在する場合は、アドレス一致先行ライトリクエストが完了してから後続のリードリクエストを発行するようにしている。

【0007】

図16は、入出力制御装置2−1の構成例を示すブロック図であり、入出力デバイス1−1から入力されたリードリクエストに対するアドレス一致先行ライトリクエストが存在するか否かの判定処理を、従来一般的に行われているように、リードリクエストを一旦入力バッファに登録してから行うようにした場合の構成を示している。即ち、図16は、従来の入出力制御装置2−1の構成例を示すブロック図である。

【0008】

図16に示した入出力制御装置2−1は、入力バッファ101と、アドレス一致先行ライトリクエスト検出処理部102と、アドレス一致管理バッファ103と、一致判定回路105と、順序保証バッファ106と、引き抜きポインタ108と、FIFOポインタ109と、ポインタセレクタ110と、発行処理部111と、リクエストセレクタ112と、制御部113とを備えている。なお、他の入出力制御装置も入出力制御装置2−1と同様の構成を有している。

【0009】

〔動作の説明〕

次に、入出力制御装置として図16に示した構成を有する入出力制御装置を用いた場合の、マルチプロセッサシステムの動作について説明する。

【0010】

入出力デバイス1−1が発行したメモリリクエストは、一旦、入出力制御装置2−1内の入力バッファに登録される。

【0011】

入出力制御装置2−1内のアドレス一致先行ライトリクエスト検出処理部102は、図17のフローチャートに示すように、入力バッファ101の先頭に登録されているリクエストを入力し、そのリクエストがライトリクエストなのかリードリクエストなのかを判定する(ステップA1、A2)。

【0012】

今、入力バッファ101から入力したリクエストがライトリクエストであったとすると(ステップA2がYES)、アドレス一致先行ライトリクエスト検出処理部102は、上記ライトリクエストに含まれているライトアドレスをアドレス一致管理バッファ103に登録すると共に、そのライトアドレスに対する有効フラグを「有効」とする(ステップA3、A4)。

【0013】

その後、アドレス一致先行ライトリクエスト検出処理部102は、上記ライトリクエストを順序保証バッファ106に登録すると共に、そのライトリクエストに対する待ち合わせフラグを「有効」にする(ステップA5、A6)。待ち合わせフラグが「有効」になっている間、上記ライトリクエストは、発行を待ち合わされる。

【0014】

更に、アドレス一致先行ライトリクエスト検出処理部102は、上記ライトリクエストの発行許可を受けるために、リクエストセレクタ112及びクロスバーネットワーク3を介して該当するノード(例えば、ノード4−1)に対して、ライトアドレスを含むディレクトリ検索要求を発行する(ステップA7)。その際、アドレス一致先行ライトリクエスト検出処理部102は、制御部113に対してセレクタ切り替え要求を送り、制御部113から切り替え完了通知が送られてきてからディレクトリ検索要求を発行する。また、制御部113は、アドレス一致先行ライトリクエスト検出処理部102からセレクタ切り替え要求が送られてくると、リクエストセレクタ112を発行処理部111を選択する状態からアドレス一致先行ライトリクエスト検出処理部102を選択する状態に変更し、その後、切り替え完了通知を返却する。また、制御部113は、切り替え完了通知を返却してから所定時間(アドレス一致先行ライトリクエスト検索処理部102がディレクトリ検索要求を発行するのに十分な時間)が経過すると、リクエストセレクタ112を、発行処理部111を選択する状態に戻す。

【0015】

入出力制御装置2−1からディレクトリ検索要求が送られてきたノード4−1内のメモリ制御部41は、ディレクトリ42を参照し、上記ディレクトリ検索要求に含まれているライトアドレスをアクセスすることが可能か否かを判定する。ディレクトリ42には、例えば、共有メモリ43の各アドレスがロック状態にあるのか、フリー状態にあるのかを示すロック情報が登録されていおり、上記ライトアドレスに対するロック情報がフリー状態の場合は、アクセス可能であると判定し、ロック状態の場合は、アクセス不能と判定する。

【0016】

そして、メモリ制御部41は、アクセス可能と判定した場合は、上記ライトアドレスに対応するロック情報をロック状態にした後、要求元の入出力制御装置2−1に対して発行許可を返却し、アクセス不能と判定した場合は、差戻指示を返却する。

【0017】

ノード4−1から返却された発行許可、差戻指示は、入出力制御装置2−1内の制御部113で受信される。

【0018】

制御部113は、ノード4−1から発行許可が返却された場合は、図18のフローチャートに示すように、発行許可されたライトリクエストの待ち合わせフラグ107を解除し、その値を「有効」から「無効」に変更する(ステップB1)。これにより、上記ライトリクエストは、順序保証バッファ106から発行可能な状態になる。なお、順序保証バッファ106に登録されたリクエストの発行動作は、後で、図20を用いて説明する。

【0019】

これに対して、ノード4−1から差戻指示が返却された場合は、図19のフローチャートに示すように、先ず、引き抜きポインタ108が指し示す順序保証バッファ106のエントリを、差戻が指示されたライトリクエストが格納されているエントリを指し示すものに変更し(ステップC1)、次いで、ポインタセレクタ110をFIFOポインタ109を選択する状態から引き抜きポインタ108を選択する状態に切り替え(ステップC2)、更に、発行処理部111に対してディレクトリ検索要求の発行を指示する(ステップC3)。その後、制御部113は、ポインタセレクタ110の状態を、FIFOポインタ109を選択する状態に戻す(ステップC4)。

【0020】

上記したステップC2において、ポインタセレクタ110の状態が切り替えられることにより、順序保証バッファ106からは、差戻が指示されたライトリクエストが発行処理部111に対して出力される。

【0021】

発行処理部111は、順序保証バッファ106からリクエストが入力された後、制御部113からディレクトリ検索要求の発行が指示された場合は、上記リクエストの代わりに、上記リクエスト中のライトアドレスを含んだディレクトリ検索要求を該当するノードに対して発行する。これに対して、順序保証バッファ106からリクエストが入力された後、制御部113からディレクトリ検索要求の発行が指示されなかった場合は、上記リクエストをそのまま該当するノード4−1に発行する。この例では、制御部113がステップC3において、ディレクトリ検索要求の発行を指示しているので、発行処理部111は、リクエスト中のライトアドレスを含んだディレクトリ検索要求を該当するノード4−1に対して発行することになる。

【0022】

アドレス一致先行ライトリクエスト検出処理部102が入力バッファ101から入力したリクエストがライトリクエストの場合は、上記した処理が行われる。次に、アドレス一致先行ライトリクエスト検出処理部102が入力バッファ101からリードリクエストを入力した場合の動作について説明する。

【0023】

図17のフローチャートに示すように、アドレス一致先行ライトリクエスト検出処理部102は、入力バッファ101から入力したリクエストがリードリクエストの場合(ステップA1、A2がNO)は、先ず、上記リードリクエストに含まれているリードアドレスを一致判定回路105に渡す(ステップA8)。

【0024】

一致判定回路105は、リードアドレスが渡されると、アドレス一致管理バッファ103を検索し、有効フラグ104が「有効」となっているライトアドレスの中に、上記リードアドレスと同一のアドレスが存在するか否かを調べる。そして、そのようなアドレスが存在する場合には、アドレス一致先行ライトリクエスト検出処理部102に対してアドレス一致先行ライトリクエストが有ることを通知し、そのようなアドレスが存在しない場合は、アドレス一致先行ライトリクエストが無いことを通知する。

【0025】

アドレス一致先行ライトリクエスト検出処理部102は、アドレス一致先行ライトリクエスト無しが通知された場合(ステップA9がNO)は、ステップA1で入力したリードリクエストを該当するノードに発行する(ステップA12)。その際、ステップA7でディレクトリ検索要求を発行した場合と同様に、制御部113に対してセレクタ切り替え要求を出力し、制御部113から切り替え完了が通知された後、リードリクエストを発行する。

【0026】

これに対して、アドレス一致先行ライトリクエスト有りが通知された場合(ステップA9がYES)は、ステップA1で入力したリードリクエストを順序保証バッファ106に登録すると共に、上記リードリクエストの待ち合わせフラグ107を無効にする(ステップA10、A11)。

【0027】

次に、順序保証バッファ106に登録されているリクエストを発行する場合の動作を、図20のフローチャートを参照して説明する。

【0028】

制御部113は、順序保証バッファ106に登録されているリクエストを、登録順に発行するため、FIFOポインタ109が指し示している順序保証バッファ106のエントリに登録されているリクエストの待ち合わせフラグ107が有効になっている場合(ステップD1、D2がYES)は、無効に変更されるのを待ち合わせ(ステップD2がNOとなるのを待ち合わせ)、無効になっている場合(ステップD2がNO)は、FIFOポインタ109によって指し示されているリクエストを順序保証バッファ106から読み出す(ステップD3)。このリクエストは、発行処理部111に入力され、該当するノードに発行される。

【0029】

その後、制御部113は、ステップD3で読み出したリクエストがライトリクエストであったか否かを判断し(ステップD4)、ライトリクエストであった場合(ステップD4がYES)は、アドレス一致管理バッファ104に登録されている有効フラグ104の内の、今回読み出したライトリクエストに対応する有効フラグを「無効」に変更し(ステップD5)、その後、FIFOポインタ109を更新し、次のエントリを指し示すようにする(ステップD6)。これに対して、ステップD3で読み出したリクエストがリードリクエストであった場合(ステップD4がNO)は、ステップD5を飛ばしてステップD6の処理を行う。ステップD6が終了すると、制御手段113は、ステップD1の処理に戻る。

【0030】

【特許文献1】特開2001−331363号公報

【発明の開示】

【発明が解決しようとする課題】

【0031】

従来は、上述したように、図16に示すような入出力制御装置2−1〜2−nを用いてメモリの一貫性が保証されるように、リクエストの発行順を制御しているが、次のような問題があった。

【0032】

第1に、リードリクエストを入力バッファ101に一旦登録し、その後、上記リードリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを判定するアドレス一致判定処理を行っているため、このアドレス一致判定処理に要する時間だけ、後続のリクエストの処理が遅れてしまうという問題がある。

【0033】

第2に、入力バッファ101で受け付けたリクエストがライトリクエストである場合、アドレス一致先行ライトリクエスト検出処理部102が無条件でディレクトリ検索要求を発行しているため、同一のライトアドレスを含むライトリクエストが連続した場合、差戻指示が多発してトラフィックが増加してしまうという問題がある。

【0034】

第3に、アドレス一致先行ライトリクエストが存在するリードリクエストは一旦順序保証バッファ106に登録され、その後、FIFOポインタ109によってその登録エントリが指し示されるまで、発行が待ち合わされるため、上記アドレス一致先行ライトリクエストと上記リードリクエストとの間に存在する無関係なライトリクエストの発行許可待ちの影響を受けてしまい性能が低下するという問題がある。

【0035】

第4に、アドレス一致先行ライトリクエストが存在しないリードリクエストは、順序保証バッファ106をバイパスさせるが、このときリクエストセレクタ112が順序保証バッファ106を選択する状態になっていると、上記リードリクエストの発行が待たされるため、後続のリクエストに対する処理が止まってしまうという問題がある。

【0036】

〔発明の目的〕

そこで、本発明の目的は、マルチプロセッサシステムの処理速度を向上させると共に、トラフィックを低減させることにある。

【課題を解決するための手段】

【0037】

本発明にかかる第1のマルチプロセッサシステムは、

複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードと、該各ノードとクロスバーネットワークを介して接続された入出力制御装置とを備え、前記入出力制御装置が、リクエストが登録されると共に該登録されたリクエストの発行を待ち合わせることが必要か否かを示す待ち合わせフラグが登録される順序保証バッファと、該順序保証バッファに登録されている待ち合わせフラグの内の、ノードから発行許可されたリクエストに対応する待ち合わせフラグを待ち合わせ不要を示すものに変更し、前記順序保証バッファに登録されている最古のリクエストに対応する待ち合わせフラグが待ち合わせ不要を示している場合、前記最古のリクエストを該当するノードに発行する制御部とを有するマルチプロセッサシステムであって、

外部から入力されたリクエストが登録されると共に、該リクエストに対するアドレス一致情報が登録される入力バッファと、

該入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、前記入力バッファに登録された前記リクエストに対応付けてアドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録するアドレス一致先行ライトリクエスト検出処理部と、

前記入力バッファに登録されている最古のリクエストに対応付けてアドレス一致情報が登録されていることを条件にして、前記最古のリクエストと待ち合わせ必要を示す待ち合わせフラグとを前記順序保証バッファに登録する登録処理部とを備えたことを特徴とする。

【0038】

本発明にかかる第2のマルチプロセッサシステムは、第1のマルチプロセッサシステムにおいて、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがライトリクエストで、且つ該ライトリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記最古のリクエストの発行許可要求を該当するノードに対して発行する構成を有し、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続ライトリクエストが登録されている場合は、該アドレス一致後続ライトリクエストの発行許可要求を該当するノードに対して発行し、該発行許可要求に応答してノードから発行許可が返却された場合は、前記アドレス一致後続ライトリクエストの待ち合わせフラグを待ち合わせ不要を示すものに変更する構成を有することを特徴とする。

【0039】

本発明にかかる第3のマルチプロセッサシステムは、第2のマルチプロセッサシステムにおいて、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、該アドレス一致後続リードリクエストを該当するノードに発行する構成を有することを特徴とする。

【0040】

本発明にかかる第4のマルチプロセッサシステムは、第3のマルチプロセッサシステムにおいて、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがリードリクエストで、且つ該リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを前記順序保証バッファに登録する構成を有し、

前記制御部が、

前記登録処理部によって前記順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、該リードリクエストを該当するノードへ発行する構成を有することを特徴とする。

【0041】

本発明にかかる第5のマルチプロセッサシステムは、第1〜第4のマルチプロセッサシステムにおいて、

前記順序保証バッファのエントリ数と同数のエントリを有するアドレス一致管理バッファと、

前記入力バッファのエントリ数と前記順序保証バッファのエントリ数とを加算した数の有効フラグを保持する有効フラグ保持部とを備え、且つ、

前記アドレス一致先行ライトリクエスト検出処理部が、

前記入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを、前記アドレス一致管理バッファに登録されているアドレスの中に、前記リクエスト中のアドレスと一致し、且つ対応する有効フラグが有効になっているアドレスが存在するか否かに基づいて判定する構成と、

前記入力バッファに入力されるリクエストがライトリクエストの場合、該ライトリクエストに含まれているアドレスを前記アドレス一致管理バッファに登録すると共に、前記有効フラグ保持部に保持されている有効フラグの内の、前回有効にした有効フラグの次の有効フラグを有効にする構成とを有し、

前記制御部が、

前記順序保証バッファからライトリクエストが発行されたとき、前記有効フラグ保持部に保持されている有効フラグの内の、有効にされた時期が最も古い有効フラグを無効に変更する構成を有することを特徴とする。

【0042】

本発明にかかる第1の入出力制御装置は、

複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードとクロスバーネットワークを介して接続され、且つ、リクエストが登録されると共に該登録されたリクエストの発行を待ち合わせることが必要か否かを示す待ち合わせフラグが登録される順序保証バッファと、該順序保証バッファに登録されている待ち合わせフラグの内の、ノードから発行許可されたリクエストに対応する待ち合わせフラグを待ち合わせ不要を示すものに変更し、前記順序保証バッファに登録されている最古のリクエストに対応する待ち合わせフラグが待ち合わせ不要を示している場合、前記最古のリクエストを該当するノードに発行する制御部とを備えた入出力制御装置であって、

外部から入力されたリクエストが登録されると共に、該リクエストに対するアドレス一致情報が登録される入力バッファと、

該入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、前記入力バッファに登録された前記リクエストに対応付けてアドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録するアドレス一致先行ライトリクエスト検出処理部と、

前記入力バッファに登録されている最古のリクエストに対応付けてアドレス一致情報が登録されていることを条件にして、前記最古のリクエストと待ち合わせ必要を示す待ち合わせフラグとを前記順序保証バッファに登録する登録処理部とを備えたことを特徴とする。

【0043】

本発明にかかる第2の入出力制御装置は、第1の入出力制御装置において、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがライトリクエストで、且つ該ライトリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記最古のリクエストの発行許可要求を該当するノードに対して発行する構成を有し、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続ライトリクエストが登録されている場合は、該アドレス一致後続ライトリクエストの発行許可要求を該当するノードに対して発行し、該発行許可要求に応答してノードから発行許可が返却された場合は、前記アドレス一致後続ライトリクエストの待ち合わせフラグを待ち合わせ不要を示すものに変更する構成を有することを特徴とする。

【0044】

本発明にかかる第3の入出力制御装置は、第2の入出力制御装置において、

前記制御部が、

前記順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、該アドレス一致後続リードリクエストを該当するノードに発行する構成を有することを特徴とする。

【0045】

本発明にかかる第4の入出力制御装置は、第3の入出力制御装置において、

前記登録処理部が、

前記入力バッファに登録されている最古のリクエストがリードリクエストで、且つ該リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを前記順序保証バッファに登録する構成を有し、

前記制御部が、

前記登録処理部によって前記順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、該リードリクエストを該当するノードへ発行する構成を有することを特徴とする。

【0046】

本発明にかかる第5の入出力制御装置は、第1〜第4の入出力制御装置において、

前記順序保証バッファのエントリ数と同数のエントリを有するアドレス一致管理バッファと、

前記入力バッファのエントリ数と前記順序保証バッファのエントリ数とを加算した数の有効フラグを保持する有効フラグ保持部とを備え、且つ、

前記アドレス一致先行ライトリクエスト検出処理部が、

前記入力バッファに入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを、前記アドレス一致管理バッファに登録されているアドレスの中に、前記リクエスト中のアドレスと一致し、且つ対応する有効フラグが有効になっているアドレスが存在するか否かに基づいて判定する構成と、

前記入力バッファに入力されるリクエストがライトリクエストの場合、該ライトリクエストに含まれているアドレスを前記アドレス一致管理バッファに登録すると共に、前記有効フラグ保持部に保持されている有効フラグの内の、前回有効にした有効フラグの次の有効フラグを有効にする構成とを有し、

前記制御部が、

前記順序保証バッファからライトリクエストが発行されたとき、前記有効フラグ保持部に保持されている有効フラグの内の、有効にされた時期が最も古い有効フラグを無効に変更する構成を有することを特徴とする。

【0047】

本発明にかかる第1のリクエスト発行方法は、

複数のプロセッサ及びそれらによって共有される共有メモリを有する複数のノードと、該各ノードとクロスバーネットワークを介して接続された入出力制御装置とを備え、前記入出力制御装置が、リクエストが登録されると共に該登録されたリクエストの発行を待ち合わせることが必要か否かを示す待ち合わせフラグが登録される順序保証バッファと、該順序保証バッファに登録されている待ち合わせフラグの内の、ノードから発行許可されたリクエストに対応する待ち合わせフラグを待ち合わせ不要を示すものに変更し、前記順序保証バッファに登録されている最古のリクエストに対応する待ち合わせフラグが待ち合わせ不要を示している場合、前記最古のリクエストを該当するノードに発行する制御部とを有するマルチプロセッサシステムにおけるリクエスト発行方法であって、

外部から入力されたリクエストが登録されると共に、該リクエストに対するアドレス一致情報が登録される入力バッファに対して外部からリクエストが入力されたとき、アドレス一致先行ライトリクエスト検出処理部が、前記リクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、前記入力バッファに登録された前記リクエストに対応付けてアドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録し、

登録処理部が、前記入力バッファに登録されている最古のリクエストに対応付けてアドレス一致情報が登録されていることを条件にして、前記最古のリクエストと待ち合わせ必要を示す待ち合わせフラグとを前記順序保証バッファに登録することを特徴とする。

【0048】

本発明にかかる第2のリクエスト発行方法は、第1のリクエスト発行方法において、

前記登録処理部が、前記入力バッファに登録されている最古のリクエストがライトリクエストで、且つ該ライトリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記最古のリクエストの発行許可要求を該当するノードに対して発行し、

前記制御部が、前記順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続ライトリクエストが登録されている場合は、該アドレス一致後続ライトリクエストの発行許可要求を該当するノードに対して発行し、該発行許可要求に応答してノードから発行許可が返却された場合は、前記アドレス一致後続ライトリクエストの待ち合わせフラグを待ち合わせ不要を示すものに変更することを特徴とする。

【0049】

本発明にかかる第3のリクエスト発行方法は、第2のリクエスト発行方法において、

前記制御部が、前記順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、前記順序保証バッファに、前記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、該アドレス一致後続リードリクエストを該当するノードに発行することを特徴とする。

【0050】

本発明にかかる第4のリクエスト発行方法は、第3のリクエスト発行方法において、

前記登録処理部が、前記入力バッファに登録されている最古のリクエストがリードリクエストで、且つ該リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、前記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを前記順序保証バッファに登録し、

前記制御部が、前記登録処理部によって前記順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、該リードリクエストを該当するノードへ発行することを特徴とする。

【0051】

〔作用〕

アドレス一致先行ライトリクエスト検出処理部は、入力バッファの入力側において、入力バッファに外部から入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファに登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録する。登録処理部では、アドレス一致情報が登録されるまで、入力バッファからのリクエストの出力(順序保証バッファへの登録)を待ち合わせる。即ち、アドレス一致先行ライトリクエストが存在するか否かの判定処理がパイプライン化されるため、後続のリクエストの処理が待たされることがなくなる。

【0052】

また、登録処理部は、入力バッファに登録されている最古のリクエストがライトリクエストであっても、上記ライトリクエストに対するアドレス一致先行ライトリクエストが存在する場合には、上記リクエストの発行許可要求は発行せず、アドレス一致先行ライトリクエストが存在しない場合のみ、発行許可要求を発行する。また、制御部は、順序保証バッファに登録されている最古のリクエストを該当するノードに対して発行した際、上記最古のリクエストをアドレス一致先行ライトリクエストとしているライトリクエスト(アドレス一致後続ライトリクエスト)が存在する場合は、このアドレス一致後続ライトリクエストの発行許可要求を該当するノードに発行する。これにより、トラフィックの増加を防止することができる。

【0053】

また、制御部は、順序保証バッファに登録されている最古のリクエストを該当するノードに発行した際、順序保証バッファに上記最古のリクエストに対するアドレス一致後続リードリクエストが登録されている場合は、そのアドレス一致後続リードリクエストを該当するノードに発行する。これにより、アドレス一致先行ライトリクエストとアドレス一致後続リードリクエストとの間に、他のライトリクエストが存在する場合であっても、アドレス一致後続リードリクエストの発行が待たされることがなくなる。

【0054】

また、登録処理部は、入力バッファに登録されている最古のリクエストがリードリクエストで、且つ上記リードリクエストに対応するアドレス一致情報がアドレス一致先行ライトアドレスが存在しないことを示している場合、上記リードリクエストと待ち合わせ不要を示す待ち合わせフラグとを順序保証バッファに登録する。また、制御部は、登録処理部によって順序保証バッファに、待ち合わせフラグが待ち合わせ不要となっているリードリクエストが登録されたとき、そのリードリクエストを該当するノードへ発行する。これにより、入力バッファにおいて、アドレス一致先行ライトリクエストが存在しないリードリクエストによって、後続のリクエストが待たされることがなくなる。

【発明の効果】

【0055】

本発明によれば、アドレス一致先行ライトリクエストが存在するか否かを判定するための判定処理によって、後続のリクエストの処理が待たされることがないという効果を得ることができる。その理由は、入力バッファの入力側において、外部から入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファに登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報を登録するアドレス一致先行ライトリクエスト検出処理部と、アドレス一致情報が登録されるまで、入力バッファに登録されているリクエストの出力(順序保証バッファへの登録)を待ち合わせる登録処理部とを備えているからである。即ち、アドレス一致先行ライトリクエストが存在するか否かの判定処理がパイプライン化されるため、後続のリクエストの処理が待たされることがなくなる。

【発明を実施するための最良の形態】

【0056】

次に本発明の実施の形態について図面を参照して詳細に説明する。

【0057】

〔実施の形態の構成の説明〕

本発明にかかるマルチプロセッサシステムの実施の形態は、図15に示したマルチプロセッサシステムにおいて、入出力制御装置2−1〜2−nとして図1に示す構成を有する入出力制御装置を使用することにより実現される。

【0058】

図1を参照すると、本実施の形態で使用する入出力制御装置2−1〜2−nは、入力バッファ21と、アドレス一致先行ライトリクエスト検出処理部23と、アドレス一致管理バッファ24と、有効フラグ保持部25と、一致判定回路26と、登録処理部27と、順序保証バッファ28と、引き抜きポインタ31と、FIFOポインタ32と、ポインタセレクタ33と、発行処理部34と、リクエストセレクタ35と、制御部36とから構成されている。なお、入出力制御装置2−1〜2−nは、同一の構成を有しているため、以下では入出力制御装置2−1を例に挙げて構成を説明する。

【0059】

入力バッファ21は、複数のエントリ(例えば、128エントリ)を有し、各エントリには、入出力デバイス1−1から発行されたリクエスト(リードリクエスト及びライトリクエストを含む)が登録されると共に、そのリクエストに対するアドレス一致情報22が登録される。アドレス一致情報22は、図2に示すように、アドレス一致先行ライトリクエストが存在するか否かを示す有無情報と、アドレス一致先行ライトリクエストを特定する先行リクエスト特定情報とを含んでいる。なお、リクエストの登録時、入力バッファ21の各エントリは循環的に使用される。即ち、最初のリクエストが入力された場合は、入力バッファ21の第0番目のエントリにリクエストを登録し、次のリクエストが入力された場合は、第1番目のエントリにリクエストを登録するというように、登録対象エントリを順次変更していき、最後のエントリ(第127番目のエントリ)にリクエストを登録した場合は、再び、第0番目のエントリを登録対象エントリとする。

【0060】

アドレス一致管理バッファ24は、順序保証バッファ28と同数のエントリ(例えば、64エントリ)を有し、最新の64個分のライトリクエスト中のライトアドレスが登録される。アドレス一致管理バッファ24のエントリ数が順序保証バッファ28のエントリ数と同数で良い理由は、入力バッファ21から或るリクエストが出力されたとき、そのリクエストに対するアドレス一致先行ライトリクエストとなる可能性のあるリクエストは、順序保証バッファ28にその時点で登録されている64個のリクエストだけであるからである。

【0061】

有効フラグ保持部25は、入力バッファ21のエントリ数(この例では128エントリ)と順序保証バッファ28のエントリ数(この例では64エントリ)とを加算した数のエントリ(この例では192エントリ)を有しており、各エントリには、アドレス一致管理バッファ24の対応するエントリに格納されているライトアドレスが有効であるか否かを示す有効フラグが登録されている。有効フラグ保持部25の第j番目、第(j+64)番目、第(j+128)番目のエントリが、アドレス一致管理バッファ24の第j番目のエントリと対応している。

【0062】

順序保証バッファ28は、複数のエントリ(例えば64エントリ)を有し、各エントリには、登録処理部27によってリクエストが登録されると共に、そのリクエストに対する待ち合わせフラグ29およびペンディング情報30が登録される。なお、待ち合わせフラグ29は、対応するリクエストの発行を待ち合わせることが必要か否かを示すものであり、ペンディング情報は、それと対応付けて登録されているリクエストにアドレス一致先行ライトリクエストが存在するか否かを示す有無情報と、アドレス一致先行ライトリクエストを特定するための先行リクエスト特定情報とを含んでいる。また、順序保証バッファ28は、引き抜きポインタ31、FIFOポインタ32の内の、ポインタセレクタ33によって選択されているポインタが指し示しているエントリに登録されているリクエスト、待ち合わせフラグ29及びペンディング情報30を発行処理部34に対して出力している。

【0063】

引き抜きポインタ31及びFIFOポインタ32は、順序保証バッファ28の読み出し対象エントリを指し示すポインタである。ポインタセレクタ33は、制御部36の指示に従って引き抜きポインタ31、FIFOポインタ32の内の一方を選択するセレクタである。リクエストセレクタ35は、制御部36の指示に従って登録処理部27、発行処理部34の内の一方を選択するセレクタである。

【0064】

アドレス一致先行ライトリクエスト検出処理部23は、入力バッファ21の入力側に接続されている点、およびリードリクエストだけでなく、ライトリクエストについてもアドレス一致先行ライトリクエストが存在するか否かを調べる点が、図16に示した従来のアドレス一致先行ライトリクエスト検出処理部102との大きな相違点である。このアドレス一致先行ライトリクエスト検出処理部23が備えている主な機能は次の通りである。

【0065】

・入力バッファ21に入力されるリクエストがライトリクエストの場合は、一致判定回路26を利用して上記ライトリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べると共に、どのライトリクエストがアドレス一致先行ライトリクエストとなるのかを調べる。その後、調べた結果に基づいてアドレス一致情報22を作成し、上記ライトリクエストが登録された入力バッファ21のエントリにアドレス一致情報22を登録する。更に、上記ライトリクエスト中のライトアドレスを最新のライトアドレスとしてアドレス一致管理バッファ24に登録すると共に、有効フラグ保持部25の該当するエントリに有効を示す有効フラグを登録する。

【0066】

なお、アドレス一致管理バッファ24にライトアドレスを登録する際、アドレス一致先行ライトリクエスト検出処理部23は、アドレス一致管理バッファ24の各エントリを循環的に使用する。即ち、最初のライトアドレスはアドレス一致管理バッファ24の第0番目のエントリに登録し、次のライトアドレスは、第1番目のエントリに登録するというように順次登録対象エントリを更新していき、最後のエントリ(第63番目のエントリ)にライトアドレスを登録した場合は、再び、第0番目のエントリを登録対象エントリとする。また、有効フラグ保持部25に有効フラグを登録する場合、アドレス一致先行ライトアドレス検出処理部24は、有効フラグ保持部25の各エントリを循環的に使用する。即ち、アドレス一致管理バッファ24の第0番目のエントリに最初のライトアドレスを登録した場合は、有効フラグ保持部25の第0番目のエントリに有効を示す有効フラグを登録し、アドレス一致管理バッファ24に次のライトアドレスを登録した場合は、有効フラグ保持部25の第1番目のエントリに有効を示す有効フラグを登録するというように、順次登録対象エントリを更新していき、最後のエントリ(第191番目のエントリ)に有効を示す有効フラグを登録した場合は、再び、第0番目のエントリを登録対象エントリとする。

【0067】

・入力バッファ21に入力されるリクエストが、リードリクエストの場合、一致判定回路26を利用して上記リードリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べると共に、どのライトリクエストがアドレス一致先行ライトリクエストとなるかを調べる。その後、調べた結果に基づいてアドレス一致情報22を生成し、上記リードリクエストが登録された入力バッファ21のエントリにアドレス一致情報22を登録する。

【0068】

登録処理部27は、次のような機能を有する。

【0069】

・入力バッファ21の第0番目〜第127番目のエントリを順次読み出し対象エントリにし、最後のエントリ(第127番目のエントリ)を読み出し対象エントリにしたら、再び第0番目のエントリを読み出し対象エントリにする。読み出し対象エントリに、有効なアドレス一致情報22が登録されている場合は、読み出し対象エントリからリクエスト及びアドレス一致情報22を読み出し、アドレス一致情報22が無効になっている場合は、有効なアドレス一致情報22が登録されるのを待ってからリクエスト及びアドレス一致情報22を読み出す。読み出し対象エントリからリクエスト及びアドレス一致情報22を読み出すと、読み出し対象エントリ中のアドレス一致情報22を無効にすると共に、入力バッファ21から読み出したリクエストを順序保証バッファ28に登録する。リクエストの登録時、登録処理部27は、順序保証バッファ28の各エントリを循環的に使用する。

【0070】

・順序保証バッファ28に登録したリクエストが、ライトリクエストで、且つそのライトリクエストに対応するアドレス一致情報22が、アドレス一致先行ライトリクエストが無いことを示している場合は、上記ライトリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが必要なことを示す有効フラグ29(値が「有効」)を登録すると共に、ペンディング情報30として「無効」を登録する。更に、上記ライトリクエストに対するディレクトリ検索要求を該当するノードに発行し、その後、入力バッファ21の読み出し対象エントリを次のエントリに更新する。このディレクトリ検索要求には、上記ライトリクエスト中のライトアドレスが含まれると共に、上記ライトリクエストを格納した順序保証バッファ28のエントリを示す情報(エントリ番号)が含まれる。

【0071】

・順序保証バッファ28に登録したリクエストが、ライトリクエストで、且つそのライトリクエストに対応するアドレス一致情報22が、アドレス一致先行ライトリクエストが存在することを示している場合は、上記ライトリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが必要なことを示す有効フラグを登録すると共に、上記アドレス一致情報22をペンディング情報30として登録する。その後、入力バッファ21の読み出し対象エントリを次のエントリに更新する。

【0072】

・順序保証バッファ28に登録したリクエストが、リードリクエストで、且つそのリードリクエストに対応するアドレス一致情報22が、アドレス一致先行ライトリクエストが無いことを示している場合は、上記リードリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが不要なことを示す待ち合わせフラグ29(値が「無効」)を登録すると共に、ペンディング情報30として「無効」を登録する。更に、制御部36に対して、リードリクエスト発行要求を出力し、その後、読み出し対象エントリを次のエントリに更新する。なお、上記リードリクエスト発行要求には、上記リードリクエストを登録したエントリのエントリ番号が含まれている。

【0073】

・順序保証バッファ28に登録したリクエストが、リードリクエストで、且つそのリードリクエストに対するアドレス一致情報22が、アドレス一致先行ライトリクエストが存在することを示している場合は、上記リードリクエストを登録した順序保証バッファ28のエントリに、待ち合わせが必要なことを示す有効フラグ29を登録すると共に、上記アドレス一致情報22をペンディング情報30として登録する。その後、入力バッファ21の読み出し対象エントリを次のエントリに更新する。

【0074】

制御部36は、次のような機能を有する。

【0075】

・ノード4−k(1≦k≦m)からリクエストの発行許可が返却された場合は、順序保証バッファ28に登録されているリクエストの内の、発行許可されたリクエストに対応する待ち合わせフラグ29の値を「無効」に変更し、そのリクエストの発行待ち合わせを解除する。なお、ノード4−kからの発行許可には、発行を許可するリクエストが格納されているエントリを示す情報が含まれている。即ち、ノード4−kは、入出力制御装置2−1から、ライトアドレス及びエントリ番号を含むディレクトリ検索要求が送られてきたとき、ディレクトリ42を検索してリクエストの発行を許可するか否かを決定し、リクエストの発行を許可するのであれば、上記エントリ番号を含む発行許可を返却し、許可しないのであれば、上記エントリ番号を含む差戻指示を返却する。

【0076】

・ノード4−kから差戻指示が返却された場合は、引き抜きポインタ31に上記差戻指示に含まれているエントリ番号を設定すると共に、ポインタセレクタ33の状態を引き抜きポインタ31を選択する状態に切り替え、更に、発行処理部34に対してディレクトリ検索要求の発行指示を出力する。その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。なお、上記ディレクトリ検索要求の発行指示には、上記エントリ番号が含まれている。

【0077】

・登録処理部27からリードリクエスト発行要求が入力された場合は、引き抜きポインタ31に上記リードリクエスト発行要求に含まれているエントリ番号を設定すると共に、ポインタセレクタ33の状態を引き抜きポインタ31を選択する状態に切り替え、更に、発行処理部34に対してリクエストの発行指示を出力する。その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。

【0078】

・FIFOポインタ32が指し示す順序保証バッファ28のエントリ(登録時期が最も古い、未発行のリクエストが登録されているエントリ)に登録されている待ち合わせフラグ29の値が「無効」で、且つ登録されているリクエストがライトリクエストの場合、発行処理部34に対してリクエストの発行指示を出力し、更に、有効フラグ保持部25の各エントリに保持されている有効フラグの内の、該当する有効フラグの値を「無効」に変更する。即ち、発行したライトリクエストに対応する有効フラグの値を「無効」にする。

【0079】

・発行処理部34に対して発行を指示したライトリクエストをアドレス一致先行ライトリクエストとしているライトリクエスト(アドレス一致後続ライトリクエスト)が順序保証バッファ28に登録されている場合は、引き抜きポインタ31に上記アドレス一致後続ライトリクエストが登録されているエントリのエントリ番号を設定すると共にポインタセレクタ33を引き抜きポインタ31を選択する状態にし、更に、発行処理部34に対してディレクトリ検索要求の発行指示を出力し、その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。なお、このディレクトリ検索要求の発行指示には、上記アドレス一致後続ライトリクエストが格納されているエントリのエントリ番号が含まれている。

【0080】

・発行処理部34に対して発行を指示したライトリクエストをアドレス一致先行ライトリクエストとしているリードリクエスト(アドレス一致後続リードリクエスト)が順序保証バッファ28に登録されている場合は、引き抜きポインタ31に上記アドレス一致後続リードリクエストが登録されているエントリのエントリ番号を登録すると共にポインタセレクタ33を引き抜きポインタ31を選択する状態にし、更に、発行処理部34に対してリクエストの発行指示を出力し、その後、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す。

【0081】

発行処理部34は、次のような機能を有する。

【0082】

・制御部36からディレクトリ検索要求の発行指示が入力された場合は、順序保証バッファ28から出力されているライトリクエスト中のライトアドレスと上記発行指示中のエントリ番号とを含んだディレクトリ検索要求をリクエストセレクタ35を介して該当するノードに発行する。

【0083】

・制御部36からリクエストの発行指示が入力されている場合は、順序保証バッファ28から読み出されているリクエスト(リードリクエストの場合もあれば、ライトリクエストの場合もある)をリクエストセレクタ35を介して該当するノードに発行する。

【0084】

〔実施の形態の動作の説明〕

次に本実施の形態の動作について詳細に説明する。なお、以下の説明では、入出力デバイス1−1が入出力制御装置2−1に対してリクエストを発行した場合について説明するが、他の入出力デバイス1−2〜1−nが入出力制御装置2−2〜2−nに対してリクエストを発行した場合も同様の動作が行われる。

【0085】

入出力デバイス1−1が入出力制御装置2−1に発行したリクエストは、入出力制御装置2−1内の入力バッファ21及びアドレス一致先行ライトリクエスト検出処理部23に入力される。

【0086】

入力バッファ21は、リクエストが入力されると、自バッファ21が有している128個のエントリの内の、現在登録対象エントリとしているエントリに上記リクエストを登録し、その後、登録対象エントリを次のエントリに変更する。なお、初期状態においては、登録対象エントリは、第0番目のエントリになっている。

【0087】

一方、アドレス一致先行ライトリクエスト検出処理部23は、リクエストが入力される毎に、図3のフローチャートに示す処理を行う。

【0088】

アドレス一致先行ライトリクエスト検出処理部23は、リクエストが入力されると、先ず、入力されたリクエストがライトリクエストなのか、リードリクエストかを判定する(ステップS31)。

【0089】

そして、ライトリクエストである場合(ステップS31がYES)は、ライトリクエストに含まれているライトアドレスを一致判定回路26に渡し(ステップS32)、その後、一致判定回路26からの応答を待つ(ステップS33)。

【0090】

一致判定回路26は、ライトアドレスが渡されると、アドレス一致管理バッファ24に登録されているアドレスの中に、上記ライトアドレスと一致し、且つ有効フラグ保持部25に保持されている対応する有効フラグが「有効」になっているアドレスが存在するか否かに基づいて、アドレス一致先行ライトリクエストが存在するか否かを判定し、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。なお、アドレス一致先行ライトリクエストが存在すると判定した場合には、判定結果として、どのライトリクエスト(例えば、何個前のライトリクエスト)が、アドレス一致先行ライトリクエストとなるのかもアドレス一致先行ライトリクエスト検出処理部23に通知する。

【0091】

アドレス一致先行ライトリクエスト検出処理部23は、一致判定回路26からの通知に従ってアドレス一致情報22を生成し、入力バッファ21中の該当するエントリ(今回処理対象にしているライトリクエストが登録されたエントリ)に登録する(ステップS34)。即ち、一致判定回路26からアドレス一致先行ライトリクエストが存在しないことが通知された場合は、アドレス一致先行ライトリクエストが存在しないことを示す有無情報を含んだアドレス一致情報22を生成して該当するエントリに登録し、存在することが通知された場合は、アドレス一致先行ライトリクエストが存在することを示す有無情報およびどのライトリクエストがアドレス一致先行ライトリクエストとなるのかを示す先行リクエスト特定情報を含んだアドレス一致情報22を該当するエントリに登録する(ステップS34)。

【0092】

その後、アドレス一致先行ライトリクエスト検出処理部23は、今回処理対象にしているライトリクエスト中のライトアドレスを、アドレス一致管理バッファ24のエントリの内の、現在登録対象エントリにしているエントリに登録すると共に、有効フラグ保持部25の該当するエントリに登録されている有効フラグを「有効」にする(ステップS35、S36)。なお、アドレス一致先行ライトリクエスト検出処理部23は、初期状態においては、アドレス一致管理バッファ24の第0番目のエントリを登録対象エントリにしており、アドレスを格納する毎に、登録対象エントリを更新する。

【0093】

これに対して、入力されたリクエストがリードリクエストであると判定した場合(ステップS31がNO)は、上記リードリクエストに含まれているリードアドレスを一致判定回路26に渡し(ステップS37)、その後、一致判定回路26からの応答を待つ(ステップS38)。一致判定回路26は、リードアドレスが渡されると、前述した処理と同様の処理を行い、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。これにより、アドレス一致先行ライトリクエスト検出処理部23は、入力バッファ21のエントリの内の、今回処理対象にしているリードリクエストが登録されているエントリにアドレス一致情報22を登録する(ステップS39)。

【0094】

次に、アドレス一致先行ライトリクエスト検出処理部23およびアドレス一致判定回路26の動作を、具体例を挙げて説明する。

【0095】

今、有効フラグ保持部25の第0番目〜第191番目のエントリに登録されている有効フラグの値が図4(A)に示すものであるとする。なお、図4では、有効フラグの値「有効」を「1」で表し、「無効」を「0」で表している。

【0096】

図4(A)に示すように、有効フラグ保持部25の第0番目〜第7番目のエントリに登録されている有効フラグの値が「有効」になっているときに、ライトリクエスト(初期状態から数えて第8番目のリクエストであるとする。但し、最初のリクエストを第0番目のリクエストとする)が入力されると、アドレス一致先行ライトリクエスト検出処理部23は、上記ライトリクエスト中のライトアドレスを一致判定回路26に渡し、待ち状態となる(図3のステップS31がYES、S32、S33)。

【0097】

一致判定回路26は、ライトアドレスが渡されると、有効フラグ保持部25の第0番目〜第7番目のエントリに登録されている有効フラグの値が「有効」となっているので、上記エントリと対応するアドレス一致管理バッファ24の第0番目〜第7番目のエントリを比較対象エントリにして、上記ライトアドレスと一致するアドレスが登録されているか否かを調べることにより、アドレス一致先行ライトリクエストが存在するか否かを判定する。

【0098】

なお、前述したように、アドレス一致管理バッファ24の第j番目のエントリに対応する有効フラグ保持部25上のエントリは、第j番目、第(j+64)番目、第(j+128)番目の計3個のエントリであり、一致判定回路26は、アドレス一致管理バッファ24の第j番目のエントリに対応する有効フラグ保持部25上の3個のエントリの何れかに「有効」を示す有効フラグが登録されていれば、上記第j番目のエントリを比較対象エントリとする。また、一致判定回路26は、ライトアドレスと一致するアドレスが比較対象エントリ(第0番目〜第7番目のエントリ)に登録されているか否かを調べる際、アドレスの登録時期が最も新しいエントリ(第7番目のエントリ)から最も古いエントリ(第0番目のエントリ)に向かって比較処理を行う。そして、アドレスの登録時期が最も古いエントリまで調べてもライトアドレスと一致するアドレスが格納されているエントリが存在しなかった場合は、アドレス一致先行ライトリクエスト無しと判定し、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。これに対して、ライトアドレスと一致するアドレスが登録されているエントリを見つけた場合は、アドレス一致先行ライトリクエスト有りと判定し、アドレス一致先行ライトリクエスト検出処理部23に判定結果を通知する。このときの判定結果には、何個前のライトリクエストがアドレス一致先行ライトリクエストとなるのかを示す情報も含まれる。なお、アドレス一致先行ライトリクエストとなるライトリクエストが何個前のライトリクエストであるかは、例えば、ライトアドレスと一致するアドレスが登録されているエントリが、比較対象エントリの内の、アドレスの登録時期が新しい方から何番目のエントリであるかを調べることにより求めることができる。

【0099】

アドレス一致先行ライトリクエスト検出処理部23は、一致判定回路26から判定結果が通知されると、それに基づいてアドレス一致情報22を生成し、入力バッファ21の各エントリの内の、現在処理対象としているライトリクエストが登録されているエントリにアドレス一致情報22を登録する(ステップS34)。この例の場合、現在処理対象にしているライトリクエストは、初期状態から数えて第8番目のリクエストであり、上記ライトリクエストは、入力バッファ21の第8番目のエントリに格納されているので、第8番目のエントリにアドレス一致情報22を登録することになる。

【0100】

その後、アドレス一致先行ライトリクエスト検出処理部23は、現在処理対象にしているライトリクエスト中のライトアドレスを、アドレス一致管理バッファ24の第8番目のエントリに登録し(ステップS35)、更に、値「有効」が設定されている有効バッファ保持部25上のエントリの内の、エントリ番号が最も大きいエントリ(第7番目のエントリ)の次のエントリ(第8番目のエントリ)に、値「有効」を登録する(ステップS36)。

【0101】

また、図4(B)に示すように、有効フラグ保持部25の第3番目〜第135番目のエントリに登録されている有効フラグが値が「有効」になっているときにライトリクエスト(初期状態から数えて第136番目のリクエストとする)が入力された場合は、アドレス一致先行ライトリクエスト検出処理部23は、上記ライトリクエスト中のライトアドレスを一致判定回路26に渡し、待ち状態となる(ステップS31がYES、S32、S33)。

【0102】

一致判定回路26は、ライトアドレスが渡されると、有効フラグ保持部25の第3番目〜第135番目のエントリに登録されている有効フラグの値が「有効」となっているので、上記エントリと対応するアドレス一致管理バッファ24の第0番目〜第63番目のエントリを比較対象エントリにして、上記ライトアドレスと一致するアドレスが登録されているか否かを調べることにより、アドレス一致先行ライトリクエストが存在するか否かを判定する。その際、アドレスの登録時期が最も新しいエントリ(第7番目のエントリ)から順番に、比較処理を行うエントリのエントリ番号を順次減少させて比較処理を行う(但し、比較処理を行うエントリのエントリ番号が「0」となった場合は、次に比較処理を行うエントリのエントリ番号を「63」とする)。そして、アドレスの登録時期が最も古いエントリ(第8番目のエントリ)まで調べてもライトアドレスと一致するアドレスが格納されているエントリが存在しなかった場合は、アドレス一致先行ライトリクエスト無しと判定し、判定結果をアドレス一致先行ライトリクエスト検出処理部23に通知する。これに対して、ライトアドレスと一致するアドレスが登録されているエントリを見つけた場合は、アドレス一致先行ライトリクエスト有りと判定し、アドレス一致先行ライトリクエスト検出処理部23に判定結果を通知する。

【0103】

アドレス一致先行ライトリクエスト検出処理部23は、一致判定回路26から判定結果が通知されると、それに基づいてアドレス一致情報22を生成し、入力バッファ21の各エントリの内の、現在処理対象としているライトリクエストが登録されているエントリにアドレス一致情報22を登録する(ステップS34)。この例の場合、現在処理対象にしているライトリクエストは、初期状態から数えて第136番目のリクエストであり、上記ライトリクエストは、入力バッファ21の第8番目(136÷64=2余り8)のエントリに格納されているので、第8番目のエントリにアドレス一致情報22を登録することになる。

【0104】

その後、アドレス一致先行ライトリクエスト検出処理部23は、現在処理対象にしているライトリクエスト中のライトアドレスを、アドレス一致管理バッファ24の第8番目のエントリに登録し(ステップS35)、更に、値「有効」が設定されている有効バッファ保持部25上のエントリの内の、エントリ番号が最も大きいエントリ(第135番目のエントリ)の次のエントリ(第136番目のエントリ)に、値「有効」を登録する(ステップS36)。

【0105】

次に、登録処理部27の動作について説明する。

【0106】

登録処理部27は、図5のフローチャートに示すように、入力バッファ21の第0番目〜第127番目のエントリの内の、読み出し対象エントリに注目し、そのエントリに有効なアドレス一致情報22が登録されるのを待つ(ステップS501、S502)。なお、初期状態においては、第0番目のエントリを読み出し対象エントリにしている。

【0107】

そして、読み出し対象エントリに有効なアドレス一致情報が登録されると(ステップS502がYES)、読み出し対象エントリに登録されているリクエスト及びアドレス一致情報22を入力し、入力したリクエストを順序保証バッファ28の登録対象エントリに登録し、更に、登録対象エントリを次のエントリに更新する(ステップS503)。なお、初期状態においては、登録対象エントリは、第0番目のエントリになっている。

【0108】

その後、登録処理部27は、入力バッファ21から入力したリクエストがライトリクエストなのか、リードリクエストなのかを調べる(ステップS504)。

【0109】

ライトリクエストであった場合(ステップS504がYES)は、ステップS503で入力したアドレス一致情報22中の有無情報に基づいて、アドレス一致先行ライトリクエストが存在するか否かを判断する(ステップS505)。

【0110】

そして、アドレス一致先行ライトリクエストが存在しない場合(ステップS505がNO)は、ステップS503においてこのライトリクエストを登録した、順序保証バッファ28のエントリ中の待ち合わせフラグ29を「有効」にして上記リクエストが発行待ち合わせ状態となるようにすると共に、ペンディング情報30を「無効」にして上記ライトリクエストに関するディレクトリ検索要求の発行を許可する(ステップS506)。その後、発行処理部27は、制御部36に対してディレクトリ検索要求の発行許可要求を送り、制御部36から発行許可を受けたら、上記ライトリクエストに関するディレクトリ検索要求を発行する(ステップS507)。ディレクトリ検索要求には、上記ライトリクエスト中のライトアドレス及び上記ライトリクエストを登録した順序保証バッファ28のエントリ番号が含まれており、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードへ送られる。また、登録処理部27からのディレクトリ検索要求の発行許可要求を受け付けた制御部36は、リクエストセレクタ35を登録処理部27を選択する状態に切り替えた後、登録処理部27に対して発行許可を与え、更に所定時間後、リクエストセレクタ35を発行処理部34を選択する状態に戻す。その後、登録処理部27は、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再び、ステップS501の処理を行う。

【0111】

これに対して、アドレス一致先行ライトリクエストが存在する場合(ステップS505がYES)は、ステップS503においてこのライトリクエストを登録した、順序保証バッファ28のエントリ中の待ち合わせフラグ29を「有効」にして上記ライトリクエストが発行待ち合わせ状態になるようにすると共に、ペンディング情報30としてステップS503で入力したアドレス一致情報22を登録し、上記ライトリクエストに関するディレクトリ検索要求が発行待ち合わせ状態になるようにする(ステップS509)。その後、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再びステップS501の処理を行う。

【0112】

一方、ステップS503で入力したリクエストがリードリクエストであると判断した場合(ステップS504がNO)は、ステップS503で入力したアドレス一致情報22中の有無情報に基づいて、アドレス一致先行ライトリクエストが存在するか否かを判断する(ステップS510)。

【0113】

そして、アドレス一致先行ライトリクエストが存在しない場合(ステップS510がNO)は、ステップS503においてこのリードリクエストを格納した、順序保証バッファ28のエントリ中の待ち合わせフラグを「無効」にして上記リードリクエストを発行可能状態にすると共に、ペンディング情報30を「無効」にする(ステップS511)。次いで、登録処理部27は、制御部36に対して上記リードリクエストの発行を要求するリードリクエスト発行要求を出力し(ステップS512)、その後、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再び、ステップS501の処理を行う。なお、リードリクエスト発行要求には、リードリクエストを登録した順序保証バッファ28のエントリ番号が含まれている。また、制御部36がリードリクエスト発行要求を受け付けたときの動作は、図6のフローチャートを用いて後で詳しく説明する。

【0114】

これに対してアドレス一致先行ライトリクエストが存在する場合(ステップS510がYES)は、ステップS503においてこのリードリクエストを登録した、順序保証バッファ28のエントリ中の待ち合わせフラグ29を「有効」にして上記リードリクエストを発行待ち合わせ状態にすると共に、ステップS503で入力したアドレス一致情報22をペンディング情報30として登録する(ステップS513)。その後、登録処理部27は、入力バッファ21の読み出し対象エントリを次のエントリに更新し(ステップS508)、再びステップS501の処理を行う。

【0115】

次に、制御部36の動作について説明する。

【0116】

先ず、登録処理部27からのリードリクエスト発行要求を受け付けたときの動作を、図6のフローチャートを参照して説明する。

【0117】

制御部36は、登録処理部27からのリードリクエスト発行要求を受け付けると、先ず、上記要求に含まれているエントリ番号を引き抜きポインタに設定する(ステップS61)。上記エントリ番号は、発行対象にしているリードリクエストが格納されている、順序保証バッファ28上のエントリを示している。次いで、制御部36は、ポインタセレクタ33の状態を、引き抜きポインタ31を選択する状態に変更する(ステップS62)。これにより、順序保証バッファ28は、引き抜きポインタ31が指し示すエントリに登録されているリクエスト(発行対象にしているリードリクエスト)を、発行処理部34に対して出力する。その後、制御部36は、発行処理部34に対してリクエストの発行を指示する(ステップS63)。これにより、発行処理部34は、順序保証バッファ28から出力されているリードリクエストを、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。その後、制御部36は、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す(ステップS64)。

【0118】

次に、ノード(例えば、ノード4−1)からライトリクエストの発行許可が返却された場合の動作を、図7のフローチャートを参照して説明する。

【0119】

制御部36は、ノード4−1からライトリクエストの発行許可(発行を許可するライトリクエストが登録されているエントリのエントリ番号が含まれている)が送られてくると、順序保証バッファ28上のエントリの内の、上記発行許可に含まれているエントリ番号のエントリに登録されている待ち合わせフラグ29の値を「有効」から「無効」に変更し、上記ライトリクエストを発行可能状態にする(ステップS71)。

【0120】

次に、ノード(例えば、ノード4−1)から差戻指示が返却された場合の動作を、図8のフローチャートを参照して説明する。

【0121】

制御部36は、ノード4−1から差戻指示(差し戻すライトリクエストが登録されているエントリのエントリ番号を含む)が送られてくると、先ず、引き抜きポインタ31に、上記差戻指示に含まれているエントリ番号を設定し、その後、ポインタセレクタ33の状態を引き抜きポインタ31を選択する状態にする(ステップS81、S82)。これにより、順序保証バッファ28は、引き抜きポインタ31が指し示すエントリの登録されているライトリクエストを発行処理部34に対して出力する。その後、制御部36は、発行処理部34に対してディレクトリ検索要求の発行指示を出力する(ステップS83)。この発行指示には、差し戻すライトリクエストが登録されているエントリのエントリ番号が含まれている。発行処理部34は、ディレクトリ検索要求の発行指示が入力されると、順序保証バッファ28から出力されているライトリクエスト中のライトアドレス及び上記発行指示中のエントリ番号を含んだディレクトリ検索要求を生成し、生成したディレクトリ検索要求を、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノード4−1に発行する。その後、制御部36は、ポインタセレクタ33の状態を、FIFOポインタ32を選択する状態に戻す(ステップS84)。

【0122】

次に制御部36が順序保証バッファ28に登録されているライトリクエストを登録順に発行するために行っている動作を図9のフローチャートを参照して説明する。

【0123】

制御部36は、FIFOポインタ32が指し示している順序保証バッファ28のエントリに登録されている待ち合わせフラグ29が「無効」になるのを待ち合わせており(ステップS901、S902)、該当する待ち合わせフラグ29が「無効」となると(ステップS902がNO)、上記エントリに登録されているリクエストの種別を調べる(ステップS903)。

【0124】

そして、リードリクエストであった場合(ステップS903がYES)は、FIFOポインタ32を更新し、次のエントリを指し示すようにした後(ステップS918)、再び、ステップS901の処理を行う。

【0125】

これに対して、ライトリクエストであった場合(ステップS903がNO)は、発行処理部34に対してリクエストの発行を指示する(ステップS904)。これにより、発行処理部34は、順序保証バッファ28から出力されているライトリクエスト(FIFOポインタ32が指し示すエントリに登録されているリクエスト)を、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。

【0126】

その後、制御部36は、有効フラグ保持部25の各エントリに保持されている有効フラグの内の、今回発行したライトリクエストに対応する有効フラグを「無効」とする(ステップS905)。

【0127】

次に、制御部36は、今回発行したライトリクエストをアドレス一致先行ライトリクエストとしているライトリクエスト(アドレス一致後続ライトリクエスト)が、順序保証バッファ28に登録されているか否かを調べる(ステップS906)。この処理は、ペンディング情報30中の先行リクエスト特定情報を利用して行う。

【0128】

そして、アドレス一致後続ライトリクエストが登録されている場合(ステップS906がYES)は、先ず、上記アドレス一致後続ライトリクエストに対応するペンディング情報30を「無効」にする(ステップS907)。次いで、引き抜きポインタ31に、上記アドレス一致後続ライトリクエストが登録されているエントリのエントリ番号を設定し(ステップS908)、更に、ポインタセレクタ33を引き抜きポインタ31を選択する状態にする(ステップS909)。これにより、順序保証バッファ28からは、上記アドレス一致後続ライトリクエストが出力される。

【0129】

その後、制御部36は、発行処理部34に対してディレクトリ検索要求の発行指示を出力する(ステップS910)。この発行指示には、アドレス一致後続ライトリクエストが登録されているエントリのエントリ番号が含まれている。発行処理部34は、上記指示を受け付けると、順序保証バッファ28から出力されているアドレス一致後続ライトリクエスト中のライトアドレスと、上記発行指示中のエントリ番号とを含んだディレクトリ検索要求を、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。その後、制御部36は、ポインタセレクタ33をFIFOポインタ32を選択する状態に戻す(ステップS911)。

【0130】

これに対して、アドレス一致後続ライトリクエストが登録されていなかった場合(ステップS906がNO)及びステップS911の処理が終了した場合、制御部36は、今回発行したライトリクエストをアドレス一致先行ライトリクエストとしているリードリクエスト(アドレス一致後続リードリクエスト)が、順序保証バッファ28に登録されているか否かを調べる(ステップS912)。

【0131】

そして、登録されていない場合(ステップS912がNO)は、FIFOポインタ32が指し示すエントリを次のエントリに更新した後(ステップS918)、再び、ステップS901の処理を行う。

【0132】

これに対して、アドレス一致後続リードリクエストが登録されている場合(ステップS912がYES)は、先ず、上記アドレス一致後続リードリクエストに対応する待ち合わせフラグ29、ペンディング情報30を「無効」にする(ステップS913)。次いで、引き抜きポインタ31に上記アドレス一致後続リードリクエストが登録されているエントリのエントリ番号を設定し(ステップS914)、更に、ポインタセレクタ33を引き抜きポインタ31を選択する状態に切り替える(ステップS915)。これにより、順序保証バッファ28からは、上記アドレス一致後続リードリクエストが出力される。

【0133】

その後、制御部36は、発行処理部34に対してリクエストの発行を指示する(ステップS916)。これにより、発行処理部34は、順序保証バッファ28から出力されているアドレス一致後続リードリクエストを、リクエストセレクタ35及びクロスバーネットワーク3を介して該当するノードに発行する。

【0134】

次いで、制御部36は、ポインタセレクタ33を、FIFOポインタ32を選択する状態に戻し(ステップS917)、その後、ステップS912の処理を行う。ステップS912がNOとなると、FIFOポインタ32が保持しているエントリ番号をインクリメントし、次のエントリを指し示すようにする(ステップS918)。その後、制御部36は、再び、ステップS901の処理を行う。

【0135】

次に、タイミングチャートを用いて本実施の形態および従来技術の動作を説明する。

【0136】

図10は、本実施の形態の動作を示すタイミングチャートであり、本実施の形態の入出力制御装置2−1(図1参照)が、ライトアドレスの異なる3個のライトリクエストA、B、Cを受け付けたときの動作を示している。

【0137】

各ライトリクエストA、B、Cは、それぞれサイクル1、2、3において入力バッファ21のエントリa、b、cに登録される。また、各ライトリクエストA、B、Cのライトアドレスは、アドレス一致先行ライトリクエスト検出処理部23においてアドレス一致先行ライトリクエストの有無が調べられた後、それぞれサイクル2、3、4においてアドレス一致管理バッファ24のエントリα、β、γに登録される。

【0138】

その後、サイクル3、4、5において、入力バッファ21からライトリクエストA、B、Cが順次読み出され、順序保証バッファ28のエントリ0、1、2に登録される。ライトリクエストA、B、Cは、ライトアドレスが異なるため、アドレス一致先行ライトリクエストは存在しない。従って、各ライトリクエストA、B、Cが順序保証バッファ28に登録されると同時に、サイクル3、4、5において、ライトリクエストA、B、Cについてのディレクトリ検索要求A、B、Cがクロスバーネットワーク3を介して該当するノードに発行される。

【0139】

ノードにおいて、ディレクトリの検索が行われ、サイクル7においてライトリクエストAに対する発行許可Aが送られてくると、FIFOポインタ32が指し示しているエントリ0に登録されているライトリクエストがサイクル8においてリクエストセレクタ35、クロスバーネットワーク3を介して該当するネットワークに発行される。この後、FIFOポインタ32は、エントリ1を指し示す。

【0140】

サイクル9において、ライトリクエストCに対する発行許可Cが送られてくると、ライトリクエストCは、発行可能な状態になるが、このとき、FIFOポインタ32は、エントリ1を指し示しているので、エントリ2に登録されているライトリクエストCは、発行されない。

【0141】

その後、サイクル11において、ライトリクエストBに対する発行許可Bが送られてくると、ライトリクエストBが発行可能な状態となり、サイクル12において、該当するノードに発行され、その後、FIFOポインタ32が、エントリ2を指し示す。これにより、サイクル13において、ライトリクエストCが該当するノードに発行される。

【0142】

図11及び図12は、それぞれ従来技術及び本実施の形態の動作を示すタイミングチャートであり、ライトアドレスが同一のライトリクエストA、A'、A"を、従来技術及び本実施の形態の入出力制御装置2−1(図16及び図1参照)が受け付けた場合の動作を示している。

【0143】

従来技術の動作を示す図11を参照すると、各ライトリクエストA、A'、A"は、それぞれサイクル1、2、3において、入力バッファ101のエントリa、b、cに登録される。また、各ライトリクエストA、A'、A"のライトアドレスは、それぞれサイクル2、3、4において、アドレス一致管理バッファ23のエントリα、β、γに登録される。また、従来技術では、ライトリクエストアドレスの一致判定処理を行わないので、サイクル3、4、5において、ライトリクエストA、A'、A"が順序保証バッファ106のエントリ0、1、2に登録されると同時に、ライトリクエストA、A'、A"についてのディレクトリ検索要求A、A'、A"が該当するノードに発行される。

【0144】

ノードは、ディレクトリ検索要求A、A'、A"が競合するので、サイクル7、8、9において、ライトリクエストAの発行許可A、ライトリクエストA'、A"の差戻指示A'、A"を返却する。これにより、サイクル8においてライトリクエストAが該当するノードに発行され、サイクル9、10において、ライトリクエストA'、A"についてのディレクトリ検索要求A'、A"が該当するノードへ発行される。

【0145】

ノードは、ディレクトリ検索要求A'、A"が競合するので、サイクル11、12において、ライトリクエストA'の発行許可A'、ライトリクエストA"の差戻指示を返却する。これにより、サイクル12においてライトリクエストA'が該当するノードに発行され、サイクル13においてライトリクエストA"に関するディレクトリ検索要求A"が該当するノードに発行される。

【0146】

ノードは、ディレクトリ検索要求A"はアドレス競合しないので、ライトリクエストA"に対する発行許可A"を返却する。サイクル15において、発行許可A"を受信すると、サイクル16において、ライトリクエストA"を該当するノードに対して発行する。

【0147】

上記した動作が行われている間にクロスバーネットワーク3上を通過したリクエスト数は15個となり、要したサイクル数は16サイクルとなる。

【0148】

一方、本実施の形態の動作を示す図12を参照すると、各ライトリクエストA、A'、A"は、それぞれサイクル1、2、3において、入力バッファ21のエントリa、b、cに登録され、サイクル2、3、4において、アドレス一致管理バッファ24のエントリα、β、γに登録され、サイクル3、4、5において、順序保証バッファ28のエントリ0、1、2に登録される。本実施の形態では、ライトアドレスについてもアドレス一致先行ライトリクエストが存在するか否かを判定し、存在しない場合のみ、ディレクトリ検索要求を発行するようにしているので、ライトリクエストAに関するディレクトリ検索要求Aは、サイクル3において発行されるが、ライトリクエストA'、A"に関するディレクトリ検索要求A'、A"は、アドレス一致先行ライトリクエストAが存在するため、発行待ち状態となる。

【0149】

ノードでは、ディレクトリ検索要求Aは、アドレス競合がないので、サイクル7において、ライトリクエストAに対する発行許可Aを返却する。これより、サイクル8において、ライトリクエストAが該当するノードに発行される。

【0150】