マルチレベルインバータ回路

【課題】4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供する。

【解決手段】本発明に係るマルチレベルインバータ回路は、共振形スイッチトキャパシターコンバータを用い手いることを特徴のひとつとする。また、マルチレベルインバータ回路は、マルチレベルインバータ部と、マルチレベルインバータ部とDCリンクコンデンサ部を介して接続されるRSCC部と、を有することを特徴とする。

【解決手段】本発明に係るマルチレベルインバータ回路は、共振形スイッチトキャパシターコンバータを用い手いることを特徴のひとつとする。また、マルチレベルインバータ回路は、マルチレベルインバータ部と、マルチレベルインバータ部とDCリンクコンデンサ部を介して接続されるRSCC部と、を有することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マルチレベルインバータ回路に関する。

【背景技術】

【0002】

マルチレベルインバータは、フィルタの小型化・除去、冷却装置の小型化、電磁ノイズの低減等が期待できるため、今後の適用範囲拡大が期待される。その中でも3レベルダイオードクランプ形インバータの回路方式及び制御法が、例えば下記非特許文献1に開示されているように、実用技術として確立されている。

【先行技術文献】

【非特許文献】

【0003】

【特許文献1】Akira Nabae,etc.IEEE Trans.onIA,1981,Vol.IA−17,No.5,pp.518−523

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、マルチレベルインバータにおいて、4レベル以上のダイオードクランプ形マルチレベルインバータでは、DCリンクコンデンサの電圧不均一が生じてしまうといった課題がある。

【0005】

そこで、本発明は、上記課題を鑑み、4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一観点に係るマルチレベルインバータ回路は、共振形スイッチトキャパシターコンバータを用いていることを特徴の一つとする。

【発明の効果】

【0007】

以上、本発明により、4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供することができる。

【図面の簡単な説明】

【0008】

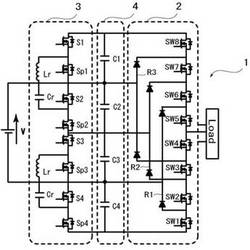

【図1】実施形態に係るマルチレベルインバータ回路を示す図である。

【図2】RSCC電圧均一化回路の例を示す図である。

【図3】図2におけるRSCC電圧均一化回路のスイッチングパターンを示す図である。

【図4】実施形態に係るマルチレベルインバータ回路の(a)出力電圧及び出力電流、(b)RSCCの電圧及び電流、を示す図である。

【図5】実施形態に係るマルチレベルインバータ回路の出力電流とDCリンクコンデンサの電圧偏差

【図6】実施形態に係るマルチレベルインバータ回路の出力電流と共振電流の関係を示す図である。

【図7】実施形態に係るマルチレベルインバータ回路の出力電圧とDCリンクコンデンサの電圧脈動の関係を示す図である。

【図8】実施形態に係るマルチレベルインバータ回路のDCリンクコンデンサの容量と電圧脈動の関係について示す図である。

【発明を実施するための最良の形態】

【0009】

以下、本発明を実施するための形態について、図面を用いて詳細に説明する。ただし、本発明は多くの異なる形態による実施が可能であり、以下に示す実施形態の例示にのみ狭く限定されるものではない。

【0010】

図1は、本実施形態に係るマルチレベルインバータ回路(以下「本回路」という。)1の概略を示す図である。本実施形態に係るマルチレベルインバータ回路1は、共振形スイッチトキャパシターコンバータを用いていることを特徴の一つとする。図1は、三相の5レベルインバータ回路を示している。

【0011】

より具体的に説明すると、本回路1は、マルチレベルインバータ部2と、このマルチレベルインバータ部2にDCリンクコンデンサ部4を介して接続されるRSCC部3と、を有する。

【0012】

本実施形態において、マルチレベルインバータ部2は、複数のスイッチング素子を直列に接続して構成されており、負荷(Load)に接続されている。また、この直列に接続されたスイッチング素子は、一定の数毎に、直列に接続されたダイオードと並列に接続されており、これが一つのスイッチング素子おきに同様な構成で連続的に接続されている。図1の例では、8個のスイッチング素子SW1〜SW8が直列に接続されており、4つのスイッチング素子毎が直列に接続された二つのダイオードに並列に接続されており、3つの回路R1〜R3が形成されている。なお、一段目の回路R1と三段目の回路R3は、入力電圧Vに並列に接続されている。

【0013】

また本実施形態において、DCリンクコンデンサ部4は、複数のDCリンクコンデンサを直列に接続して構成されている。図1の例では、4つのDCリンクコンデンサC1〜C4を有して構成されている。

【0014】

また本実施形態においてRSCC部は、複数のスイッチング素子が直列に接続されており、かつ、そのうちの一部の隣接するスイッチング素子は、直列に接続された共振リアクトルLrと共振コンデンサCrと並列に接続されている。本図の例では、スイッチング素子Sp1とS2が直列に接続された共振リアクトルLrと共振コンデンサCrと並列に接続されており、スイッチング素子Sp3とS4も上記と同様に、直列に接続された共振リアクトルLrと共振コンデンサCrと並列に接続されている。

【0015】

ここで、図2に、RCC電圧均一化回路の例を示しておく。本実施形態においてRSCCとは、共振形スイッチとキャパシタコンバータをいう。本回路は、RSCCが出力電圧の昇圧機能を実現できることに着目し、このRSCCを昇圧形直流電圧均一化回路として適用しているところが特徴の一つである。

【0016】

図2で示すように、RSCCは、スイッチング素子S、Spと共振リアクトルLr、共振コンデンサCrを有して構成されている。より具体的に説明すると、複数のスイッチング素子を直列に接続し、このうち隣り合う二つのスイッチング素子と、直列に接続された共振リアクトルLr及び共振コンデンサCrと、を並列に接続した回路を有している。

【0017】

ここで図3に、図2で示すRSCCのスイッチングパターンを示す。このRSCCは、、スイッチング素子S、Spを、共振リアクトルLr、共振コンデンサCrの共振周波数で交互にスイッチングすることでDCリンクコンデンサC1、C2の直流電圧を均一化することができ、入力電圧の2倍の出力電圧Voutを得ることができる。

【0018】

ここで、上記図1で用いた本回路1について、実験を行い、その結果を検討した。以下具体的に説明する。

【0019】

まず、DCリンクコンデンサの容量を220μF、560μF、1mFとし、付加電流を変化させるために負荷抵抗を15Ω、20Ω、30Ω、50Ωとした。図4(a)に、出力電圧及び出力電流を示し、図4(b)にRSCCの電圧及び電流を示す。

【0020】

図4(a)で示すように、入力電圧50Vに対して、振幅100Vの5レベルの出力電圧波形と正弦波状の出力電流波形が得られていることが確認でき、また、図4(b)で示すように、RSCCに出力電流の2倍以上の電流が流れていることが確認できた。

【0021】

なお、ここで本回路1における出力電流とDCリンクコンデンサの電圧偏差について確認を行なった。この結果を図5に示しておく。なお本図では電流値はピーク値で考えている。

【0022】

図5によると、出力電流が増加するに従いDCリンクコンデンサの電圧偏差も増加するという傾向が見られた。これは、RSCCは隣り合う2つのDCリンクコンデンサ間の電位差により共振電流を流し電流を補償するため、出力電流が大きくなると補償電流も大きくなる。そのため、RSCCの素子による等価直列抵抗やスイッチング素子の抵抗による損失が増加し、隣り合う2つのDCリンクコンデンサ間の電圧偏差が大きくなると考えられる。

【0023】

またここで、本回路1における出力電流と共振電流の関係について検討した。この結果を図6に示しておく。

【0024】

本図で示すように、本回路1では、出力電流と共振電流は比例しており、DCリンクコンデンサの容量を変化させても出力電流と共振電流の値はあまり変わっていないことが確認できた。これは、RSCCがDCリンクコンデンサの容量にかかわらず、出力電流により決定される電荷を送る必要があるためであると考えられる。

【0025】

またここで、出力電圧とDCリンクコンデンサの電圧脈動の関係、DCリンクコンデンサの容量と電圧脈動の関係について検討した。出力電圧とDCリンクコンデンサの電圧脈動の関係については図7に、DCリンクコンデンサの容量と電圧脈動の関係については図8にそれぞれ示しておく。

【0026】

これらの図で示すように、電圧脈動は出力電流に比例し、DCリンクコンデンサの容量に反比例することが分かった。これは、電荷が一定のとき、DCリンクコンデンサの電圧脈動はDCリンクコンデンサの容量に反比例するということから説明できる。これらの関係により、設計を行なう上で、DCリンクコンデンサ容量について設計の指針を得ることができる。具体的には、限定されるわけではないが、電圧脈動を10%以下に抑えたい場合、電圧脈動が2.5V以下の点において負荷電流を行使した上で、DCリンクコンデンサの容量を決定する必要がある。

【0027】

以上、本実施形態により、4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供することができる。

【産業上の利用可能性】

【0028】

本発明は、マルチレベルインバータ回路として産業上の利用可能性がある。

【技術分野】

【0001】

本発明は、マルチレベルインバータ回路に関する。

【背景技術】

【0002】

マルチレベルインバータは、フィルタの小型化・除去、冷却装置の小型化、電磁ノイズの低減等が期待できるため、今後の適用範囲拡大が期待される。その中でも3レベルダイオードクランプ形インバータの回路方式及び制御法が、例えば下記非特許文献1に開示されているように、実用技術として確立されている。

【先行技術文献】

【非特許文献】

【0003】

【特許文献1】Akira Nabae,etc.IEEE Trans.onIA,1981,Vol.IA−17,No.5,pp.518−523

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、マルチレベルインバータにおいて、4レベル以上のダイオードクランプ形マルチレベルインバータでは、DCリンクコンデンサの電圧不均一が生じてしまうといった課題がある。

【0005】

そこで、本発明は、上記課題を鑑み、4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一観点に係るマルチレベルインバータ回路は、共振形スイッチトキャパシターコンバータを用いていることを特徴の一つとする。

【発明の効果】

【0007】

以上、本発明により、4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供することができる。

【図面の簡単な説明】

【0008】

【図1】実施形態に係るマルチレベルインバータ回路を示す図である。

【図2】RSCC電圧均一化回路の例を示す図である。

【図3】図2におけるRSCC電圧均一化回路のスイッチングパターンを示す図である。

【図4】実施形態に係るマルチレベルインバータ回路の(a)出力電圧及び出力電流、(b)RSCCの電圧及び電流、を示す図である。

【図5】実施形態に係るマルチレベルインバータ回路の出力電流とDCリンクコンデンサの電圧偏差

【図6】実施形態に係るマルチレベルインバータ回路の出力電流と共振電流の関係を示す図である。

【図7】実施形態に係るマルチレベルインバータ回路の出力電圧とDCリンクコンデンサの電圧脈動の関係を示す図である。

【図8】実施形態に係るマルチレベルインバータ回路のDCリンクコンデンサの容量と電圧脈動の関係について示す図である。

【発明を実施するための最良の形態】

【0009】

以下、本発明を実施するための形態について、図面を用いて詳細に説明する。ただし、本発明は多くの異なる形態による実施が可能であり、以下に示す実施形態の例示にのみ狭く限定されるものではない。

【0010】

図1は、本実施形態に係るマルチレベルインバータ回路(以下「本回路」という。)1の概略を示す図である。本実施形態に係るマルチレベルインバータ回路1は、共振形スイッチトキャパシターコンバータを用いていることを特徴の一つとする。図1は、三相の5レベルインバータ回路を示している。

【0011】

より具体的に説明すると、本回路1は、マルチレベルインバータ部2と、このマルチレベルインバータ部2にDCリンクコンデンサ部4を介して接続されるRSCC部3と、を有する。

【0012】

本実施形態において、マルチレベルインバータ部2は、複数のスイッチング素子を直列に接続して構成されており、負荷(Load)に接続されている。また、この直列に接続されたスイッチング素子は、一定の数毎に、直列に接続されたダイオードと並列に接続されており、これが一つのスイッチング素子おきに同様な構成で連続的に接続されている。図1の例では、8個のスイッチング素子SW1〜SW8が直列に接続されており、4つのスイッチング素子毎が直列に接続された二つのダイオードに並列に接続されており、3つの回路R1〜R3が形成されている。なお、一段目の回路R1と三段目の回路R3は、入力電圧Vに並列に接続されている。

【0013】

また本実施形態において、DCリンクコンデンサ部4は、複数のDCリンクコンデンサを直列に接続して構成されている。図1の例では、4つのDCリンクコンデンサC1〜C4を有して構成されている。

【0014】

また本実施形態においてRSCC部は、複数のスイッチング素子が直列に接続されており、かつ、そのうちの一部の隣接するスイッチング素子は、直列に接続された共振リアクトルLrと共振コンデンサCrと並列に接続されている。本図の例では、スイッチング素子Sp1とS2が直列に接続された共振リアクトルLrと共振コンデンサCrと並列に接続されており、スイッチング素子Sp3とS4も上記と同様に、直列に接続された共振リアクトルLrと共振コンデンサCrと並列に接続されている。

【0015】

ここで、図2に、RCC電圧均一化回路の例を示しておく。本実施形態においてRSCCとは、共振形スイッチとキャパシタコンバータをいう。本回路は、RSCCが出力電圧の昇圧機能を実現できることに着目し、このRSCCを昇圧形直流電圧均一化回路として適用しているところが特徴の一つである。

【0016】

図2で示すように、RSCCは、スイッチング素子S、Spと共振リアクトルLr、共振コンデンサCrを有して構成されている。より具体的に説明すると、複数のスイッチング素子を直列に接続し、このうち隣り合う二つのスイッチング素子と、直列に接続された共振リアクトルLr及び共振コンデンサCrと、を並列に接続した回路を有している。

【0017】

ここで図3に、図2で示すRSCCのスイッチングパターンを示す。このRSCCは、、スイッチング素子S、Spを、共振リアクトルLr、共振コンデンサCrの共振周波数で交互にスイッチングすることでDCリンクコンデンサC1、C2の直流電圧を均一化することができ、入力電圧の2倍の出力電圧Voutを得ることができる。

【0018】

ここで、上記図1で用いた本回路1について、実験を行い、その結果を検討した。以下具体的に説明する。

【0019】

まず、DCリンクコンデンサの容量を220μF、560μF、1mFとし、付加電流を変化させるために負荷抵抗を15Ω、20Ω、30Ω、50Ωとした。図4(a)に、出力電圧及び出力電流を示し、図4(b)にRSCCの電圧及び電流を示す。

【0020】

図4(a)で示すように、入力電圧50Vに対して、振幅100Vの5レベルの出力電圧波形と正弦波状の出力電流波形が得られていることが確認でき、また、図4(b)で示すように、RSCCに出力電流の2倍以上の電流が流れていることが確認できた。

【0021】

なお、ここで本回路1における出力電流とDCリンクコンデンサの電圧偏差について確認を行なった。この結果を図5に示しておく。なお本図では電流値はピーク値で考えている。

【0022】

図5によると、出力電流が増加するに従いDCリンクコンデンサの電圧偏差も増加するという傾向が見られた。これは、RSCCは隣り合う2つのDCリンクコンデンサ間の電位差により共振電流を流し電流を補償するため、出力電流が大きくなると補償電流も大きくなる。そのため、RSCCの素子による等価直列抵抗やスイッチング素子の抵抗による損失が増加し、隣り合う2つのDCリンクコンデンサ間の電圧偏差が大きくなると考えられる。

【0023】

またここで、本回路1における出力電流と共振電流の関係について検討した。この結果を図6に示しておく。

【0024】

本図で示すように、本回路1では、出力電流と共振電流は比例しており、DCリンクコンデンサの容量を変化させても出力電流と共振電流の値はあまり変わっていないことが確認できた。これは、RSCCがDCリンクコンデンサの容量にかかわらず、出力電流により決定される電荷を送る必要があるためであると考えられる。

【0025】

またここで、出力電圧とDCリンクコンデンサの電圧脈動の関係、DCリンクコンデンサの容量と電圧脈動の関係について検討した。出力電圧とDCリンクコンデンサの電圧脈動の関係については図7に、DCリンクコンデンサの容量と電圧脈動の関係については図8にそれぞれ示しておく。

【0026】

これらの図で示すように、電圧脈動は出力電流に比例し、DCリンクコンデンサの容量に反比例することが分かった。これは、電荷が一定のとき、DCリンクコンデンサの電圧脈動はDCリンクコンデンサの容量に反比例するということから説明できる。これらの関係により、設計を行なう上で、DCリンクコンデンサ容量について設計の指針を得ることができる。具体的には、限定されるわけではないが、電圧脈動を10%以下に抑えたい場合、電圧脈動が2.5V以下の点において負荷電流を行使した上で、DCリンクコンデンサの容量を決定する必要がある。

【0027】

以上、本実施形態により、4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供することができる。

【産業上の利用可能性】

【0028】

本発明は、マルチレベルインバータ回路として産業上の利用可能性がある。

【特許請求の範囲】

【請求項1】

共振形スイッチトキャパシターコンバータを用いたマルチレベルインバータ回路。

【請求項2】

マルチレベルインバータ部と、前記マルチレベルインバータ部とDCリンクコンデンサ部を介して接続されるRSCC部と、を有するマルチレベルインバータ回路。

【請求項1】

共振形スイッチトキャパシターコンバータを用いたマルチレベルインバータ回路。

【請求項2】

マルチレベルインバータ部と、前記マルチレベルインバータ部とDCリンクコンデンサ部を介して接続されるRSCC部と、を有するマルチレベルインバータ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−55830(P2013−55830A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−193412(P2011−193412)

【出願日】平成23年9月5日(2011.9.5)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 社団法人電気学会主催、第23回電気学会全国大会、平成23年3月5日発行

【出願人】(304021831)国立大学法人 千葉大学 (601)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月5日(2011.9.5)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 社団法人電気学会主催、第23回電気学会全国大会、平成23年3月5日発行

【出願人】(304021831)国立大学法人 千葉大学 (601)

【Fターム(参考)】

[ Back to top ]