マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、集積回路のためのテスト方法および装置に関する。

【背景技術】

【0002】

デバッグ作業を促進するために、多くの現行の集積回路(IC)は、ジョイント・テスト・アクション・グループ(JTAG)準拠回路(IEEE 1149.1標準テスト・アクセス・ポートおよびバウンダリスキャン・アーキテクチャとして標準化されている)を含む。特許文献1には、集積回路内に搭載されるマルチコアデバイスをテストする方法及びシステムが開示されている。JTAG準拠回路およびICのテストにおいて当該回路を使用する方法(まとめて単純に「JTAG」と称される)はICの内部ブロックに対するアクセスを提供し、これによって、JTAGは組込みシステムのデバッグによく適するようになる。より具体的には、JTAG準拠バウンダリスキャン技術をサポートするデバイスにおいて、デバイスのコアロジックとデバイスのピンとの間の信号がバウンダリ・スキャン・セルによってインターセプトされ、当該セルは、共に結合されてバウンダリ・スキャン・レジスタ(BSR)として既知のシリアルスキャンパスを形成する。通常、バウンダリ・スキャン・セルはIC動作に影響を与えない。しかしながら、テストモードにおいて、バウンダリ・スキャン・セルは値をセットしかつ/または読み出すために使用されることができる。例えば、JTAGは、特定の種類の障害(例えば、短絡、開放、および論理的な障害)に関してテストするために、ICのBSRに対する外部インタフェースを操作するのに使用されることができる。

【0003】

IC上で実装される場合、JTAG準拠回路は少なくとも、命令レジスタおよび複数のデータレジスタに対するアクセスを有するJTAGインタフェースおよびコントローラを含む。JTAGインタフェース(まとめてテスト・アクセス・ポート、すなわちTAPとして既知である)は、4相互接続インタフェースまたは5相互接続インタフェースのいずれかである。4つの主要な相互接続は、TMS(テストモード状態)、TCK(クロック)、TDI(テスト・データ・イン)、およびTDO(テスト・データ・アウト)を含む。JTAGインタフェースは、TRST(テスト・リセット)相互接続が実装される場合、追加の相互接続を含むことができる。一実施形態において、TRST相互接続を介して提供されるテスト・リセット信号は、対応するテスト・リセット回路に、システム・レベル・リセットを生成させることができる。

【0004】

JTAGインタフェースと通信するために、ホストコンピュータは、目標ICのJTAGインタフェースに(例えば、JTAGアダプタを通じて)接続されることができ、ホストコンピュータは、信号がJTAGインタフェースに提供されるか、または信号がJTAGインタフェースから読み出されるようにすることができる。より具体的には、ホストコンピュータは、TCK上のクロッキング信号とともにTMSおよびTDI上の信号を操作することによって、ならびに、TDO上でICによって提示される信号を読み出すことによって、ICのTAPコントローラと通信する。TAPコントローラの状態は、TCK遷移において変化する場合がある。

【0005】

システム・イン・パッケージ(SiP)のようないくつかのマルチICシステムにおいては、システムの各ICに対して専用の外部JTAGインタフェースピンをサポートするのに利用可能なパッケージピンの数が十分でない場合がある。これらのシステムのいくつかは、直接的にまたは間接的にさまざまなICのJTAGインタフェースに接続する、1セットの外部JTAGインタフェースピンを含む場合がある。ICのうちの1つをテストするために、被試験ICを除くすべてのICが「TDI−TDOバイパス」モード(すなわち、ICのTDIおよびTDO相互接続がICのTDI−TDOバイパスレジスタを通じて事実上直接接続されるモード)にセットされる。このような構成においては、外部TDIピンにおいて提示されるTDI信号は被試験ICに渡され、被試験ICによって生成されるTDO信号は外部TDOピンにある。

【0006】

例えば、図1は、従来技術による、それらのJTAG TDOおよびTDI相互接続が共にデイジーチェーン接続されている複数のIC102、103、104の簡略化された回路図100を示す。図示されている構成において、IC102〜104のすべてに対するアクセスは、単一の外部JTAGインタフェース110を通じて提供されることができる。TMSピン112およびTCKピン114は各IC102〜104のTMSおよびTCK相互接続に直接接続され、TDIおよびTDO相互接続は共にデイジーチェーン接続される。換言すれば、第1のIC102のTDI相互接続は外部TDIピン116に直接接続され、第1のIC102のTDO相互接続は第2のIC103のTDI相互接続に接続され、第2のIC103のTDO相互接続は第3のIC104のTDI相互接続に接続され、第3のIC104のTDO相互接続は外部TDOピン118に直接接続される。

【0007】

ICのいずれか1つ(例えば、IC104)をテストするために、他のIC(例えば、IC102、103)は(例えば、BYPASS命令においてクロッキングすることによって)TDI−TDOバイパスモードにセットされる。クロック入力はTCKピン114において提供され、クロッキングは、ICのTAPコントローラ(図示せず)の各々において実装される標準化JTAGステートマシンによってTMSピン112の段階で変化する。Shift_IRおよびShift_DR状態において、1ビットのデータが各TCKクロックパルスとともに、それぞれ、TDIピン116から各タップコントローラ命令またはデータレジスタ(これも図示せず)を出入りして転送されることができる。例えば、一般的な命令は、データレジスタ(例えば、BSR、TDI−TDOバイパスレジスタ、またはIDCODEレジスタ)に対するデータの読み出しまたは書き込み、入力ピンのサンプリング、出力ピンの駆動(または浮動)などを含み得る。IC102〜104のすべてはロックステップにおいて動作するが、被試験IC(すなわち、TDI−TDOバイパスモードにないIC)のみは、そのTDOポートにおいて有効なテストデータを生成するために外部TDIピン116上の入力信号によって影響される。次いで、その有効なテストデータは外部TDOピン118において生成される。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】米国特許第7,590,910号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

JTAG準拠である従来のマルチIC SiP(例えば、図1の回路100)が提供する、SiP内の複数のICの各々をテストする能力はいくらか限られているが、パッケージピンの必要な数およびパッケージ内のIC間ルーティングを低減することができるテスト構成が望ましい。

【課題を解決するための手段】

【0010】

上記問題点を解決するために、請求項1に記載の発明は、集積回路であって、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備えることを要旨とする。

【0011】

請求項2に記載の発明は、請求項1に記載の集積回路において、前記コントローラはジョイント・テスト・アクション・グループ準拠コントローラであり、前記入力ポートは集積回路間ポートおよびシリアル周辺機器インタフェースポートから成る群から選択される、ことを要旨とする。

【0012】

請求項3に記載の発明は、請求項1に記載の集積回路において、出力信号を生成するように構成される第1の出力相互接続と、前記第1の出力相互接続および前記第1の入力相互接続に結合され、前記テスト・イネーブル信号がアサートされることに応答して、前記出力信号として生成されるために前記入力信号を前記第1の出力相互接続に渡すように制御可能である第2のマルチプレクサとをさらに備える、ことを要旨とする。

【0013】

請求項4に記載の発明は、請求項3に記載の集積回路において、前記第2のマルチプレクサに結合され、出力ポート信号を生成するように構成される出力ポートをさらに備え、前記第2のマルチプレクサは、前記テスト・イネーブル信号がアサートされていないことに応答して、前記出力信号として生成されるために前記出力ポート信号を前記第1の出力相互接続に渡すように制御可能である、ことを要旨とする。

【0014】

請求項5に記載の発明は、請求項4に記載の集積回路において、前記出力ポートは集積回路間ポート、シリアル周辺機器インタフェースポート、および二重モードI2C/SPIポートから成る群から選択される、ことを要旨とする。

【0015】

請求項6に記載の発明は、請求項1に記載の集積回路において、前記集積回路がJTAG通過モードにあるか否かの第2の指示を記憶するように構成される制御ビットと、テスト出力データを生成するように構成される第1のテスト・データ・アウト相互接続と、下流の集積回路から遠隔生成されるテスト出力データを受け取るように構成される第2のテスト・データ・アウト相互接続と、前記第1のテスト・データ・アウト相互接続に結合され、第1の指示が前記集積回路が前記JTAG通過モードにないことである場合に前記テスト出力データとして生成されるために、前記集積回路によって生成される第1のテスト出力データを前記第1のテスト・データ・アウト相互接続に渡すように制御可能である、第2のマルチプレクサと、前記第2のテスト・データ・アウト相互接続および前記第2のマルチプレクサに結合され、前記第2の指示が前記集積回路が前記JTAG通過モードにあることである場合に前記第1のテスト・データ・アウト相互接続上の前記テスト出力データとして生成されるために、前記遠隔生成されるテスト出力データを前記第2のマルチプレクサに渡すように制御可能である、第3のマルチプレクサとをさらに備える、ことを要旨とする。

【0016】

請求項7に記載の発明は、請求項1に記載の集積回路において、出力信号として前記テスト・イネーブル信号を生成するように構成される第2のテスト・イネーブル相互接続をさらに備える、ことを要旨とする。

【0017】

請求項8に記載の発明は、請求項1に記載の集積回路において、外部リセット信号を受け取るように構成されるリセット相互接続と、前記リセット相互接続に結合され、前記テスト・イネーブル信号がアサートされることに応答して、前記外部リセット信号に対応する出力リセット信号を生成するように構成される、リセット回路とをさらに備える、ことを要旨とする。

【0018】

請求項9に記載の発明は、請求項1に記載の集積回路において、外部クロック信号を受け取るように構成される外部クロック相互接続と、前記外部クロック相互接続に結合され、前記テスト・イネーブル信号がアサートされることに応答して、前記外部クロック信号に対応する出力クロック信号を生成するように構成される、クロック回路とをさらに備える、ことを要旨とする。

【0019】

請求項10に記載の発明は、マルチ集積回路システムであって、複数の外部ピンと、第1のテスト・アクセス・ポートコントローラ、第1の命令レジスタ、少なくとも1つの第1のテスト・データ・レジスタ、前記複数の外部ピンに結合される複数の第1の相互接続、および、複数の第2の相互接続を有する、第1の集積回路と、第2のTAPコントローラ、第2の命令レジスタ、少なくとも1つの第2のTDR、および、前記複数の第2の相互接続に結合される複数の第3の相互接続を有する第2の集積回路とを備え、前記第1のTAPコントローラは、前記第1の命令レジスタにクロッキングされるとオペコードを、前記第1のTAPコントローラに第1の動作を実行させる第1の命令にマッピングするように構成され、前記第2のTAPコントローラは、前記第2の命令レジスタにクロッキングされると前記オペコードを、前記第1の命令と異なる第2の命令にマッピングするように構成され、前記第2の命令は前記第2のTAPコントローラに、前記第1の動作と異なる第2の動作を実行させることを要旨とする。

【0020】

請求項11に記載の発明は、請求項10に記載のマルチ集積回路システムにおいて、前記複数の外部ピンはTE信号を受け取るように構成されるテスト・イネーブルピンを含み、前記複数の第1の相互接続は前記TEピンに結合されるTE相互接続を含み、前記第1の集積回路はスレーブポートをさらに含み、前記TE信号がディアサートされると前記第1の相互接続のセットが前記スレーブポートに結合され、前記TE信号がアサートされると前記第1の相互接続の前記セットが前記第1のTAPコントローラに結合される、ことを要旨とする。

【0021】

請求項12に記載の発明は、請求項11に記載のマルチ集積回路システムにおいて、前記第1の集積回路は、前記第1の相互接続の前記セットに、前記スレーブポートに、および前記第1のTAPコントローラに結合される第1のマルチプレクサをさらに備え、前記第1のマルチプレクサは前記TE信号に基づいて、前記TE信号がディアサートされると前記第1の相互接続の前記セットを前記スレーブポートに結合するように、および、前記TE信号がアサートされると前記第1の相互接続の前記セットを前記TAPコントローラに結合するように制御可能である、ことを要旨とする。

【0022】

請求項13に記載の発明は、請求項12に記載のマルチ集積回路システムにおいて、前記第1の集積回路は、マスタポートと、前記第1の相互接続の前記セットに、前記マスタポートに、および、前記第2の相互接続のセットに結合される第2のマルチプレクサとをさらに備え、前記第2のマルチプレクサは前記TE信号に基づいて、該TE信号がディアサートされると前記マスタポートを前記第2の相互接続の前記セットに結合するように、および、該TE信号がアサートされると前記第1の相互接続の前記セットを前記第2の相互接続の前記セットに結合するように制御可能である、ことを要旨とする。

【0023】

請求項14に記載の発明は、請求項10に記載のマルチ集積回路システムにおいて、前記複数の外部ピンはTE信号を受け取るように構成されるテスト・イネーブルピンを含み、前記複数の第1の相互接続は前記TEピンに結合される第1のTE相互接続を含み、前記複数の第2の相互接続はTE転送相互接続を含み、前記複数の第3の相互接続は前記TE転送相互接続に結合される第2のTE相互接続を含み、前記第1の集積回路は、前記TE信号を該第1の集積回路から前記TE転送相互接続と、前記第3の相互接続のうちの1つと、前記第2のTE相互接続とを通じて前記第2の集積回路に伝達するために、前記TE相互接続と前記TE転送相互接続との間に結合される回路をさらに含む、ことを要旨とする。

【0024】

請求項15に記載の発明は、請求項10に記載のマルチ集積回路システムにおいて、前記第2の集積回路は複数の第4の相互接続も含み、前記システムは、第3のTAPコントローラと、第3の命令レジスタと、少なくとも1つの第3のTDRと、前記複数の第4の相互接続に結合される複数の第5の相互接続とを有する少なくとも第3の集積回路をさらに備え、前記第3のTAPコントローラは前記第3の命令レジスタにクロッキングされると前記オペコードを、前記第1の命令または前記第2の命令のいずれかにマッピングするように構成される、ことを要旨とする。

【0025】

請求項16に記載の発明は、少なくとも、第1のテストコントローラを有する第1の集積回路と、第2のテストコントローラを有する第2の集積回路とを含むマルチ集積回路システムをテストするための方法であって、該方法は、前記第1のテストコントローラおよび前記第2のテストコントローラをテストモードにおいて構成するステップと、第1のオペコードを、前記第1のテストコントローラに関連付けられる第1の命令レジスタに、および、前記第2のテストコントローラに関連付けられる第2の命令レジスタにクロッキングするステップと、前記第1のテストコントローラが前記第1のオペコードに基づいて第1の命令を実行するステップであって、前記第1の命令は前記第1のテストコントローラに第1の動作を実行させる、実行するステップと、前記第2のテストコントローラが前記第1のオペコードに基づいて第2の命令を実行するステップであって、該第2の命令は前記第1の命令と異なり、該第2の命令は前記第2のテストコントローラに、前記第1の動作と異なる第2の動作を実行させる、実行するステップとを含むことを要旨とする。

【0026】

請求項17に記載の発明は、請求項16に記載の方法において、前記構成するステップは、前記第1の集積回路を前記テストモードにするために該第1の集積回路に提供されるテスト・イネーブル信号をアサートすることと、前記第2の集積回路を前記テストモードにするために、前記第1の集積回路を、前記テスト・イネーブル信号を前記第2の集積回路に伝達するように構成することとを含む、ことを要旨とする。

【0027】

請求項18に記載の発明は、請求項16に記載の方法において、前記構成するステップは、前記第1の集積回路の二重目的相互接続の第1のセットを前記第1の集積回路の第1のスレーブポートから結合解除するとともに、該第1の集積回路の二重目的相互接続の該第1のセットを前記第1のテストコントローラに結合するために、前記第1の集積回路に提供されるテスト・イネーブル信号をアサートすることを含む、ことを要旨とする。

【0028】

請求項19に記載の発明は、請求項18に記載の方法において、二重目的相互接続の前記第1のセットを前記第1のテストコントローラから結合解除するとともに、二重目的相互接続の該第1のセットを前記第1のスレーブポートに結合するために、前記第1の集積回路に提供される前記テスト・イネーブル信号をディアサートすることをさらに含む、ことを要旨とする。

【0029】

請求項20に記載の発明は、請求項16に記載の方法において、前記第1の命令または前記第2の命令のうちの一方はBYPASS命令であり、該第1の命令および該第2の命令のうちの他方は非BYPASS命令である、ことを要旨とする。

【0030】

請求項21に記載の発明は、請求項16に記載の方法において、第2のオペコードを、前記第2のテストコントローラに関連付けられる前記第2の命令レジスタにクロッキングするステップであって、前記第2のオペコードは前記第1のオペコードと異なる、クロッキングするステップと、前記第2のテストコントローラが前記第2のオペコードに基づいて前記第1の命令を実行するステップとをさらに含む、ことを要旨とする。

【図面の簡単な説明】

【0031】

【図1】従来技術による、JTAGテスト能力を有する複数の相互接続されたICの簡略化された回路図。

【図2】本発明の主題の一実施形態が実装されることができる例示のシステムの簡略化されたブロック図。

【図3】例示の実施形態による、統合テスト回路を有するICの簡略化されたブロック図。

【図4】例示の実施形態による、統合テスト回路を有するマルチICシステムの簡略化されたブロック図。

【図5】例示の実施形態による、マルチICシステムをテストするための方法のフローチャート。

【発明を実施するための形態】

【0032】

実施形態は、複数のIC(例えば、複数のコントローラ)上の補助的テスト回路が、外部回路への直接JTAG接続を有しない(例えば、外部JTAGピンがない)内部ICを完全にテスト可能にすることができるシステム(例えば、SiP)を含む。加えて、実施形態は、外部パッケージピンおよびIC間ルーティングを低減するために、JTAG相互接続が、入力スレーブポートおよび出力マスタポートによって多重化される構成を含む。本発明の主題の実施形態は、SiP、システム・オン・チップ(SoC)、および、回路基板を通じて相互接続される別個にパッケージされるICを含むシステムのような、さまざまなマルチICシステムのいずれかとともに使用されることができる。本明細書においてSiPの特定の例が説明されるが、当該例は限定であるようには意図されていないこと、および、当該例はさまざまな実施形態の理解を高めるために提供されることを理解されたい。

【0033】

本明細書において使用される場合、「ピン」という用語は、パッケージの外部の回路とパッケージの内部の回路との間の導電性接続を意味する。「ピン」は、ピン、パッド、バンプ、ボール、および任意の他の導電性接続を含むように解釈されるべきである。「相互接続」という用語は、特定のICに対する入力(I)導体、特定のICに対する出力(O)導体、または特定のICに対して二重I/O目的を果たす導体を意味する。本明細書においてより詳細に説明されるように、いくつかの事例において、相互接続はパッケージピンと直接結合されてもよく、他の事例においては、相互接続は別のICの相互接続と結合されてもよい。

【0034】

図2は、本発明の主題の一実施形態が実装されることができる例示のシステム200の簡略化されたブロック図を示す。より詳細には、システム200は、(6自由度の測定値を提供する)三次元空間内にあるデバイスの動き(例えば、変位および回転)を検知するための、およびさらにデバイスの地球上のロケーションを追跡するためのデバイス内に組み込まれることができるSiPである。

【0035】

システム200は、複数のコントローラIC210,212(本明細書においては「コントローラ」と称される)と、複数のトランスデューサ220,221,222とを含む。より具体的には、マスタコントローラ210は、磁気トランスデューサ220および加速度計トランスデューサ221とインタフェースするために使用され、スレーブコントローラ212はレート・ジャイロ・トランスデューサ222とインタフェースするために使用される。磁気トランスデューサ220は、地球の磁場の強度を示す信号を生成するように構成され、その情報はナビゲーション関連およびロケーション関連の用途に使用されることができる。加速度計トランスデューサ221およびレート・ジャイロ・トランスデューサ222は、信号(例えば、加速度および角度変化率を示す)を生成し、これは、デバイスの直線運動および向きが求められることを可能にする。この情報は、とりわけ、表示デバイス上で情報を表示するのに使用する向き(例えば、縦方向または横方向)の決定を含む、さまざまな目的に対して有用であり得る。

【0036】

マスタコントローラ210およびスレーブコントローラ212の両方は、機能モード、JTAGテストモード、または別の種類のテストモードにおいて構成されることができる。上記で示されているように、機能モードにおいて構成される場合、マスタコントローラ210は、磁気トランスデューサ220および加速度計トランスデューサ221とインタフェースするために使用され、スレーブコントローラ212はレート・ジャイロ・トランスデューサ222とインタフェースするために使用される。JTAGテストモードにおいて構成される場合、マスタコントローラ210およびスレーブコントローラ212は、JTAG準拠テストをサポートするように設計される。

【0037】

図示されるように、スレーブコントローラ212の上流にあるマスタコントローラ210は、システムのI/Oピンのさまざまなものに直接接続され、一方でスレーブコントローラ212はシステムI/Oピンには直接接続されない。図示されている実施形態において、マスタコントローラ210はピン230,232,234,および236に接続されているものとして示されている。ピン230は、マスタコントローラ210に対する1つまたは複数のアナログ入力を表し、これは、例えば、1つまたは複数の遠隔アナログセンサから発する場合がある。ピン232はシリアルポートを表し、これは、1つまたは複数の他の外部デバイス(例えば、図示されていない他のセンサ)に接続されることができる。このシリアルポートは、例えば、他の外部デバイスをマスタリングするマスタコントローラ210をサポートするマスタ/スレーブ・シリアル・ポートに対応することができる。シリアルポートがI2C(集積回路間)ポートである一実施形態において、例えば、ピン232は実際には2つ以上のピンを含むことができる。代替的には、シリアルポートがSPI(シリアル周辺機器インタフェース)である一実施形態において、ピン232は実際には4つ以上のピンを含むことができる。いくつかのデバイスは、SPIまたはI2Cポートを実装するためのオプションを有してもよい(例えば、ポートは二重モードI2C/SPIポートであってもよい)。他の実施形態においては、他のシリアルまたはパラレル・ポート・プロトコルも実装されてもよい。

【0038】

一実施形態において、マスタコントローラ210は、機能モードおよびJTAGテストモードの両方において使用されることができる複数の「二重目的」ピン234にも接続される。より詳細には、マスタコントローラ210が機能モードにおいて構成される場合、ピン234は外部スレーブポート(例えば、SPI、I2C、または他のインタフェース)に対応し、これは外部プロセッサ(例えば、外部アプリケーションプロセッサ)との相互接続性を提供することができる。マスタコントローラ210がJTAGテストモードにおいて構成される場合、ピン234は外部JTAGポートに対応する。後により詳細に説明されるように、マスタコントローラのスレーブポートおよびタップコントローラ(いずれも図示されていない)は、ピン234の二重目的機能をイネーブルするために多重化される。同様に、マスタコントローラ210およびスレーブコントローラ212の両方が「二重目的」相互接続を含む。後により詳細に説明されるように、マスタコントローラ210の二重目的相互接続は二重目的ピン234に結合され、スレーブコントローラ210の二重目的接続はマスタコントローラ210の対応するバイパス相互接続に結合される。基本的に、マスタコントローラ210およびスレーブコントローラ212の二重目的接続は、コントローラが機能モードにあるかまたはJTAGテストモードにあるかに応じて、スレーブポートまたはJTAGポートに対応する。

【0039】

一実施形態によれば、マスタコントローラ210は外部テスト・イネーブル(TE)ピン236にも結合され、これは、マスタコントローラ210およびスレーブコントローラ212を機能モードまたはJTAGテストモードのいずれかにおいて構成するために使用される。一実施形態において、TEピン236上で信号がアサートされない場合、マスタコントローラ210およびスレーブコントローラ212は機能モードにあり、二重目的ピン234は外部スレーブポート(例えば、SPIまたはI2Cインタフェース)に対応する。逆に、TEピン236上で信号がアサートされ、その信号がマスタコントローラ210からスレーブコントローラ212へ伝達される場合、マスタコントローラ210およびスレーブコントローラ212の両方はJTAGテストモードにあり、二重目的ピン234は外部JTAGポートに対応する。より具体的には、JTAGテストモードにおいて、ピン234はTDI(テスト・データ・イン)、TMS(テストモード状態)、TCK(クロック)、およびTDO(テスト・データ・アウト)ピンに対応する。JTAGピンはTRST(テスト・リセット)ピン(図示せず)も含むことができる。

【0040】

一度JTAGテストモードになると、マスタコントローラ210またはスレーブコントローラ212のいずれかは、BYPASS命令をマスタコントローラ210またはスレーブコントローラ212のいずれかのTAPコントローラ命令レジスタ(図示せず)にクロッキングすることによって、「TDI−TDOバイパスモード」において構成されることができる。TDI−TDOバイパスモードにおいて、TDI相互接続上でクロッキングされるデータは、TDI−TDOバイパスレジスタを通じてTDO相互接続へ通過する。マスタコントローラ210上でJTAGテストを実行するために、スレーブコントローラ212はさまざまな時点においてTDI−TDOバイパスモードにおいて構成されることができ、ただし、TDI−TDOバイパスモードにおける構成はすべてのJTAGテストに対して必要とされるものではない。同様に、スレーブコントローラ212上でJTAGテストを実行するために、マスタコントローラ210はさまざまな時点においてTDI−TDOバイパスモードにおいて構成されることができる。マスタコントローラ210がTDI−TDOバイパスモードにある場合、マスタコントローラ210は外部TDI、TMS、TCK、およびTEピン234,236上に存在する信号を、スレーブコントローラ212の対応するJTAG相互接続まで通過させ、スレーブコントローラのTDO相互接続上に存在する信号を外部TDOピン234まで通過させる。

【0041】

図示されていないが、システム200は、追加の周辺機器、メモリなども含むことができる。加えて、システム200は、本発明の主題の実施形態が組み込まれることができるシステムの単なる一例を表すことは理解されたい。他の実施形態においては、システムは3つ以上のコントローラ、コントローラ以外のICを含んでもよく、かつ/またはコントローラもしくはICの各々は異なる種類のトランスデューサ、ポートもしくは他の回路とインタフェースしてもよい。一実施形態による、JTAGテスト能力を有するICのより一般的な説明がここで与えられる。

【0042】

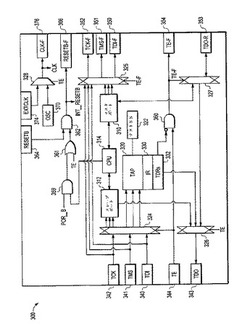

より具体的には、図3は、例示の実施形態による、統合テスト回路300を含むIC(例えば、コントローラまたは他のIC)の簡略化されたブロック図を示す。テスト回路300に加えて、ICは、マスタポート310(例えば、SPIまたはI2Cポート)、スレーブポート312(例えば、SPIまたはI2Cポート)、および中央処理装置(CPU)314も含む。他の実施形態においては、本明細書に記載されるもののようなテスト回路は、FPGA(フィールド・プログラマブル・ゲート・アレイ)、ASIC(特定用途向け集積回路)、および他の種類のICをテストするのに使用されてもよい。図示されていないが、ICは、CPU314とインタフェースする複数の信号(I/O)相互接続、1つまたは複数の電源相互接続、および1つまたは複数の接地相互接続も含む。加えて、ICは、テスト回路300を使用して実行される動作によって影響を受け得る状態を有する他のハードウェア、および、テストパターンをCPU314または他のハードウェアに供給するのに使用されることができる1つまたは複数のスキャンチェーン(図示せず)を含んでもよい。

【0043】

テスト回路300はJTAGポートを通じてアクセスされ、これは、複数のJTAG相互接続を含む。JTAG相互接続は、TDI相互接続340と、TMS相互接続341と、TCK相互接続342と、TDO相互接続343とを含む。JTAG相互接続はTRST(テスト・リセット)相互接続(図示せず)も含むことができる。下記により詳細に説明されるように、JTAG相互接続340〜343は二重目的であり、すなわち、それらはICが機能モードにおいて構成される場合スレーブポート312に対する相互接続としても機能することができる。しかしながら、簡便にするために、図3は相互接続340〜343(および対応する相互接続350〜353、後述)を、それらのJTAG指定によって指定する。

【0044】

ICのテスト回路300は、複数のシフトレジスタ、TAPコントローラ320、テストサブシステム(SS)322、マルチプレクサ324,325,326,327,328、およびさまざまな他のロジックを含み、それらの機能は下記により詳細に説明される。シフトレジスタは例えば、命令レジスタ(IR)330および複数のテスト・データ・レジスタ(TDR)332を含むことができる。

【0045】

IR330は、TDI相互接続340からマルチプレクサ324およびTAPコントローラ320を介して信号を受け取る。IR330はシフトレジスタであり、これは、TAPコントローラ320による実行のために現在の命令を保持することができる。基本的に、IR330の内容は、TAPコントローラ320が、TDI相互接続340を介して受け取る信号をどのように処理するかを決定するために使用される。多くの事例において、IR330は、TDI相互接続340からの入力信号をいずれのTDR332に渡すべきかを定義する命令を含む。IR330は例えば、4〜7ビット幅の間であることができる。ただし、IR330はさまざまな実施形態においてより狭いかまたはより広くてもよい。

【0046】

TDR332は、(介在するマルチプレクサ324およびTAPコントローラ320によって)TDI相互接続340と、(介在するマルチプレクサ326を用いて)TDO相互接続343との間に並列接続され、それによって、TAPコントローラ320が適切な状態にある(例えば、Shift_DR状態にある)ときに、TCK相互接続342上のクロック信号の各立ち上がりエッジの後に選択されたTDR332がデータをTDO相互接続343に向かって1段階シフトさせることになる。TDR332のサイズは固定であってもよいし、可変であってもよい。例えば、TDR332のサイズは、とりわけ、現在IR330内にある命令(または値)の関数であってもよい。

【0047】

TDR332は、後述されるような、バウンダリ・スキャン・シフト・レジスタ(BSR)(バウンダリ・スキャン・チェーンまたはEXTESTレジスタとも称される)、TDI−TDOバイパスレジスタ、オプションの識別レジスタ、および、ICの機能に影響を与えるさまざまな他のレジスタを含むことができる。さまざまな実施形態において、実装される場合もあり、されない場合もあるBSRは、ICの周辺を取り巻く専用パス内に接続される複数のバウンダリ・スキャン・セルから成り、BSRは、データをICのI/Oピンに、またI/Oピンから移動させるのに使用される。より詳細には、バウンダリ・スキャン・セルは、各信号相互接続(またはピン)と内部ロジックとの間に接続されることができる。BSRの内容は、BSDL(バウンダリスキャン記述言語)ファイルを使用して記述されることができる。ICがTDI−TDOバイパスモードにある場合、TDI−TDOバイパスレジスタ(例えば、シングル・ビット・レジスタ)は、データをTDI相互接続340からTDO相互接続343へ渡すのに使用される。識別レジスタ(例えば、32ビットのIDCODEレジスタ)は、ICのための識別コードを記憶するのに使用されることができる。識別コードは例えば、製造者コード、製造者によって割り当てられる部品番号、および部品バージョンコード(または改訂番号)を含むフォーマットを有することができる。IDCODEレジスタ内の情報は、ICが対応するBSDLファイルにリンクされることを可能にすることができる。同様に、JTAGテストに関連付けられるさまざまな制御ビットがTDR332内で指定されることができる。例えば、一実施形態において実装される或るTDR制御ビットが、本明細書において「JTAG通過」制御ビットと称され、これは、ICがJTAG通過モードにあるか否かを制御する。ICがJTAG通過モードにない(例えば、JTAG通過制御ビットがセットされている)場合、ICは、ICのTDO相互接続において提供されるべきTDO信号を生成する。逆に、ICがJTAG通過モードにある(例えば、JTAG通過制御ビットがクリアされている)場合、ICは下流のICからTDO信号を受け取り、当該TDO信号を下流のICからICのTDO相互接続に渡す。換言すれば、JTAG通過ビットの状態が、最上流のICが外部TDO相互接続343を駆動するか、または下流のICが駆動するかを決定することができる。

【0048】

タップコントローラ320はIR330およびTDR332にアクセスすることができ、(例えば、IEEE標準1149.1において定義されるような)JTAGステートマシーンを実装し、ここで、TMS相互接続341上のクロッキング変更に基づいて状態遷移が起こる。例えば、JTAGステートマシンは、(例えば、Shift_IR状態における)IR330への命令のシフトに関連付けられる1つの状態、および、(例えば、Shift_DR状態における)TDR332を通じてのデータのシフトに関連付けられる別の状態を有することになる。命令がIR330にシフトされると、TAPコントローラ320は、その命令を実行することができる。より詳細に後述されるように、さまざまな命令オペコードがTAPコントローラ320のために定義され、オペコードの命令への事前定義のマッピングに従って、IR330にシフトされるオペコードを復合する命令復号ロジック(図示せず)を含む。より詳細に後述されるように、TAPコントローラ320の復号ロジックは、システムの他のTAPコントローラの復号ロジックとは異なる様式で、オペコードを命令にマッピングする。TAPコントローラ320は、テストサブシステム322ともインタフェースすることができ、当該サブシステムは、さまざまなテストモード(例えば、RAM BIST(ビルトイン・セルフテスト)、スキャン(例えば、バッテリスキャン、内部スキャン)、専門アナログ・テスト・モードなど)に対する追加の制御を提供する。

【0049】

すでに述べたように、ICは機能モードまたはJTAGテストモードにおかれることができる。一実施形態によれば、テスト・イネーブル(TE)相互接続344上で提供される信号は、ICが機能モードにあるかまたはJTAGテストモードにあるかを制御し、マルチプレクサ324〜326の動作にも影響を与える。より詳細には、信号がTE相互接続344上でアサートされる場合、ICはJTAGテストモードにあり、より詳細に後述されるように、マルチプレクサ324〜326の各々はJTAGテストに関連する信号を渡す。逆に、信号がTE相互接続344上でアサートされない場合、ICは機能モードにあり、マルチプレクサ324〜326の各々は機能モードに関連する信号を渡す。当業者であれば、代替の実施形態において、TE相互接続344上で信号がアサートされた場合にICが機能モードにあってもよく、TE相互接続344上で信号がアサートされなかった場合にJTAGテストモードにあってもよいことを理解しよう。しかしながら、簡便にするために、下記説明は、信号がTE相互接続344上でアサートされる場合にICがJTAGテストモードにある実施形態に対応する。下記により詳細に説明されるように、マルチプレクサ326,327は、さまざまな時点においてICをJTAG通過モードにおくように制御可能である。JTAG通過モードにおいて、マルチプレクサ326,327は、下流のICから(TDO−R(TDO逆)相互接続353を介して)受け取るTDO信号をICのTDO相互接続343に向けて通過させるように構成される。従って、マルチプレクサ326,327は本明細書において「TDOマルチプレクサ」と称される場合がある。TDOマルチプレクサ326の動作は、上記のように主にTE相互接続344上で提供される信号によって制御され、TDOマルチプレクサ327の動作は、TE−F相互接続354上で提供されるテスト・イネーブル転送(TE−F)信号の状態によって制御される。すでに述べたように、かつより詳細に後述されるように、一実施形態において、TE−F信号の状態は、TDR332内のJTAG通過制御ビットによって影響を受ける。

【0050】

基本的に、マルチプレクサ324〜327は、相互接続340〜343,350〜353の二重目的機能を提供し、ICを通じてのJTAGおよび他の信号の転送を促進する回路を備える。上記で述べたように、マルチプレクサ324〜327の動作は、TE相互接続344上に存在する信号、およびTDR332内のJTAG通過制御ビットの状態によって影響を受ける。より具体的には、TE相互接続344上の信号が機能動作モードに対応し(例えば、信号がアサートされない)、JTAG通過制御ビットがセットまたはクリアされる場合、マルチプレクサ324〜326は、二重目的相互接続340〜343,350〜353を、CPU314と接続されるシリアルポート(例えば、I2CまたはSPIポート)に対する相互接続に対応させる。より具体的には、機能モードにおいて、マルチプレクサ324は、TDI、TMS、およびTCK相互接続340〜342からの信号をスレーブポート312に渡し、マルチプレクサ325は、マスタポート310からの信号をTDI−F(TDI転送)、TMS−F(TMS転送)、およびTCK−F(TCK転送)相互接続350,351,352に渡す。すでに述べたように、マスタポート310はSPIポートであり得る。このような実施形態では、機能モードにおいて、マルチプレクサ327はマスタポート310からの(例えば、SPI MISO(マスタ入力/スレーブ出力)信号に対応する)信号をTDO−R相互接続353に渡すことができる。同様に、スレーブポート312がSPIポートである場合、マルチプレクサ326はスレーブポート312からの(例えば、SPI MISO信号に対応する)信号をTDO相互接続343に渡すことができる。

【0051】

逆に、JTAGテストモードにおいて(例えば、TE相互接続344上で信号がアサートされる場合)、マルチプレクサ324〜326は、二重目的相互接続340〜343,350〜352を、JTAG相互接続と対応させる。より具体的には、マルチプレクサ324はTDI相互接続340からの信号を、TAPコントローラ320に渡し、当該TAPコントローラは、信号を(TAPコントローラ320の状態に応じて)IR330またはTDR332のいずれかにシフトさせ、マルチプレクサ324はさらにTMSおよびTCK相互接続341,342からの信号を、タップコントローラ320に渡す。加えて、マルチプレクサ325は、TDI、TMS、およびTCK相互接続340〜342からの信号を、TDI−F、TMS−F、およびTCK−F相互接続350〜352に渡す。JTAG通過制御ビットがリセット/クリアされ、TE−F信号がアサートされる(すなわち、ICがJTAG通過モードにある)場合、TDO−R相互接続353上に存在する信号は、マルチプレクサ327を介してマルチプレクサ326まで通過させられ、マルチプレクサ326は、マルチプレクサ327からの信号をTDO相互接続343まで通過させる。そうではない場合、ICはJTAG通過モードになく(例えば、JTAG通過制御ビットがセットされる)、マルチプレクサ326は、TDR332のうちの1つからのデータをTDO相互接続343に渡す。JTAG通過モードにおいて、TDI/TMS/TCKインタフェース340〜342とTDI−F/TMS−F/TCK−Fインタフェース350〜352との間で転送されている信号はクロッキングされていない。同様に、TDO−Rインタフェース353とTDOインタフェース343との間で転送されている信号もクロッキングされていない。

【0052】

一実施形態において、TE信号は、ANDロジック360およびTE−F(テスト・イネーブル転送)相互接続354を介して下流のデバイス(例えば、下流のIC)に渡されることができる。より詳細には、ANDロジック360はTE相互接続344上に存在する信号およびTE通過イネーブル信号の両方を受け取る。TE信号およびTDR332内のJTAG通過制御ビットの状態に基づいて生成されることができるTE通過イネーブル信号は、ICが、TE信号が下流のデバイスまで通過することを許可またはブロックしているか否かを示す。TE相互接続344上で信号がアサートされ、かつTE通過イネーブル信号がアサートされる(例えば、TDR332内の指定されるビットがリセット/クリアされ、ICがJTAG通過モードにある)場合、ANDロジック360はTE−F相互接続354上でTE−F信号をアサートする。TE−F相互接続354は、次いで、下流のIC(図示せず)のTE相互接続と結合されることができる。

【0053】

TE−F相互接続354と同様に、かつ図4とともにより詳細に説明されるように、TDI−F、TMS−F、およびTCK−F相互接続350〜352は、下流のICの対応するTDI、TMS、およびTCK相互接続に結合されることができる。加えて、TDO−R相互接続353は、下流のICの対応するTDO相互接続に結合されることができる。上記で述べたように、TDOマルチプレクサ327の動作はTE−F信号の状態によって制御される。従って、一実施形態において、TDOマルチプレクサ327の動作は、JTAG通過制御ビットの状態および対応するTE通過イネーブル信号によって影響を受ける。TE−F信号がアサートされる場合、TDOマルチプレクサ327は、TDO−R相互接続353上に存在する信号を、TDOマルチプレクサ326まで通過させる(当該TDOマルチプレクサは、次いで、信号をTDO相互接続343まで通過させることができる)。

【0054】

一実施形態によれば、テスト回路300は、ICおよび任意の下流のICの協調リセットをサポートする回路も含む。下記の記載は、システムがアクティブ・ロー・リセットをサポートしていることを想定しており、ただし、システムは代替的にアクティブ・ハイ・リセットをサポートしてもよいことを当業者であれば理解しよう。一実施形態によれば、リセット回路は、TE相互接続344上で信号がアサートされる場合、リセットは外部リセット信号(例えば、外部テスト機器または上流のICからの、RESETB相互接続364上に存在するリセット信号)によって制御され、他のシステムリセット(例えば、パワー・オン・リセットまたはCPU314からのリセット)は無関係であるように構成される。

【0055】

一実施形態において、リセット回路はANDロジック359、ORロジック361、およびANDロジック362を含む。ANDロジック359、ORロジック361、およびANDロジック362は、リセット条件に関連するさまざまな信号を受け取る。ANDロジック359に入力される信号は例えば、POR_B(ローでアサートされるパワー・オン・リセット)信号、CPU314からの(ローでアサートされる)リセット信号を含むことができる。ANDロジック359に入力される両方の信号がハイである場合、ANDロジック359の出力はハイであり、信号のいずれかがローである場合、ANDロジック359の出力はローである。POR_B信号はデバイスが電源投入されている間はローであり、それ以外ではハイであり得、CPUリセット信号はCPU314が下流のICをリセットしようとしている場合はローであり得る。ORロジック361に入力される信号は、ANDロジック359からの出力信号および(例えば、TE相互接続344からの)TE信号を含む。ORロジック361に入力されるいずれかの信号がハイである場合、ORロジック361の出力はハイであり、すべての信号がローである場合、ORロジック361の出力はローである。TE信号は機能モードにおいてはローであり、それゆえ、機能モードにおけるリセットは、RESETB相互接続364上に存在する外部リセット信号に加えてPOR_BおよびCPUリセット信号によって左右される。逆に、JTAGテストモードにおいてはTE信号はハイであり、それゆえ、ICがJTAGテストモードにあるときはORロジック361の出力は常にハイである。換言すれば、TE信号がハイである場合、外部リセット364のみがINT_RESETBおよびRESETB_Fをアサートすることができる。

【0056】

ORロジック361からの出力はANDロジック362に提供され、当該ANDロジックは外部リセット相互接続364からの信号も受け取る。ORロジック361からの信号がローであるか、または外部リセット相互接続364からの信号がローである場合、ANDロジック362は内部リセット(INT_RESETB)およびRESETB−F(リセット転送)相互接続366上の信号をアサートする。代替的に、ORロジック361からの信号および外部リセット相互接続364からの信号の両方がハイである場合、ANDロジック362はRESETB−F相互接続366上の信号をアサートしない。上記の記載が示すように、JTAGテストモードにおいて(すなわち、ORロジック361からの出力がハイである場合)、RESETB−F相互接続366上の信号状態は、外部リセット相互接続364上の信号によって左右される。RESETB−F相互接続366は、下流のICの対応するリセット相互接続に結合されることができる。このようにして、リセット信号はICによって下流のICに提供されることができる。

【0057】

さまざまな実施形態において、ICが機能モードにある場合、システムクロック(CLK)は、オンチップ発振器(OSC)370、オンチップ位相ロックループ、オンチップデジタル位相ロックループ、他のオンチップクロック源、または外部(オフチップ)クロック源によって提供されることができる。逆に、ICがJTAGテストモードにある場合、システムクロックはEXTCLK(外部クロック)相互接続374を介して外部クロック源(例えば、外部テスト機器によって生成されるクロック)によって提供される。一実施形態によれば、ICはマルチプレクサ328も含み、当該マルチプレクサはTE相互接続344上でアサートされる信号に基づいてシステムクロックを選択的に供給し、クロック信号をCLK−F(クロック転送)相互接続376に渡す。TE相互接続344上で信号がアサートされない(例えば、ICが機能モードにある)場合、マルチプレクサ328はシステムクロックとしてOSC370(または別のクロック源)からのクロック信号を使用し、そのクロック信号をCLK−F相互接続376に渡す。逆に、TE相互接続344上で信号がアサートされる(例えば、ICがJTAGテストモードにある)場合、マルチプレクサ328はシステムクロックとしてEXTCLK相互接続374上で提供されるクロック信号を使用し、そのクロック信号をCLK−F相互接続376に渡す。CLK−F相互接続376は、下流のICの対応するEXTCLK相互接続に結合されることができる。このようにして、クロック信号はICによって下流のICに提供されることができる。

【0058】

上記で述べたように、機能モードおよびJTAGテストモードに関連付けられるさまざまな信号が複数のIC間で渡されることを可能にするように、複数のICがともに結合されることができる。図4は、例示の実施形態による、統合テスト回路を有するマルチICシステム400(例えば、システム・イン・パッケージ(SiP))の簡略化されたブロック図を示す。より詳細には、マルチICシステム400は3つのIC402,403,404を含むように示されている。システム400は3つのIC402〜404および関連テスト回路412〜414を含むように示されているが、実施形態は、2つのみのICおよびテスト回路を含むシステム、または4つ以上のICおよびテスト回路を含むシステムにおいて実装されてもよい。加えて、IC402〜404の各々は図3のICとともに示されたもののような構成を有することができるが、IC402〜404は簡略化された形式で示されている(例えば、簡潔かつ明瞭にするために、図3のCPU、リセット回路、クロック回路、およびさまざまな他の回路は図4においては図示されていない)。

【0059】

システム400は二重目的ピン440,441,442,443を通じて外部回路(例えば、他のシステム回路または外部テスト機器)と通信することができ、IC402〜404の各々は、対応する相互接続を介して二重目的ピン440〜443と、または互いにインタフェースすることができる。ピン440〜443および相互接続はすでに記載されたように、それらが、IC402〜404がJTAGテストモードにある場合はJTAGピン/相互接続として、および、代替的にIC402〜404が機能モードにおいて構成される場合はIC402〜404のスレーブポート412〜414との接続を提供するピン/相互接続としての両方で機能することができるという点で、二重目的である。加えて、システム400はTEピン444を含み、これは、IC402上のTE相互接続(図示せず)と接続する。図3とともにすでに説明されたように、TEピン444上でアサートされるTE信号は、IC402によって、ANDロジック460を使用して下流のIC403のTE相互接続(図示せず)に渡されることができ、TE信号は、IC403によって、ANDロジック461を使用して下流のIC404のTE相互接続445にも渡されることができる。

【0060】

IC402〜404は直列に接続され(例えば、ともにデイジーチェーン接続され)、それによって、各ICは他のICから下流または上流となる。本明細書において使用される場合、直列構成にある2つのIC間の関係に関連する「上流のIC」という用語は、それが接続されている他のICよりも外部ピン(例えば、ピン440〜443)により近く結合されている直列対のICを意味する。同様に、「下流のIC」という用語は、それが接続されている他のICよりも外部JTAGピンにより近くに結合されていない直列対のICを意味する。従って、図4において、IC402はIC403および404の上流にあり、IC403はIC402の下流にあるとともにIC404の上流にあり、IC404はIC402および403の下流にある。

【0061】

IC402〜404の各々はテスト回路405,406,407およびスレーブポート412,413,414(例えば、SPIまたはI2Cポート)を含む。IC402および403の各々は、マスタポート415、416(例えば、SPIまたはI2Cポート)も含む。IC404は最下流のICであるため、IC404は任意選択的にマスタポート417(およびマルチプレクサ429,432)を含んでもよいが、これは必須ではない。簡潔にするために図示されていないが、IC402〜404の各々は、マスタおよびスレーブポート412〜417間に結合されるCPU(または他の回路)、CPU(または他の回路)とインタフェースする信号(I/O)相互接続、1つまたは複数のスキャンチェーン、1つまたは複数の電力相互接続、1つまたは複数の接地相互接続なども含んでもよい。

【0062】

IC402が機能モードにある(例えば、TE信号がアサートされない)場合、二重目的ピン440〜442上に存在する信号はIC402の二重目的相互接続(図示せず)およびマルチプレクサ424を介してスレーブポート412に提供され、これらの信号はIC402のCPU(または他の回路)によって作用されることができる。加えて、IC402のCPU(または他の回路)は、マスタポート415、マルチプレクサ427、およびIC402,403間のさまざまな相互接続を介して下流のIC403のマルチプレクサ425およびスレーブポート413に信号を提供することができる。同様に、IC403のCPU(または他の回路)は、マスタポート416、マルチプレクサ428、およびIC403,404間のさまざまな相互接続を介してさらに下流のIC404のマルチプレクサ426およびスレーブポート414に信号を提供することができる。従って、システム400のさまざまなIC402〜404はマスタ−スレーブ構成において動作することができ、ここで、IC402はICF403のマスタであることができ、IC403はIC404のマスタであることができる。

【0063】

図3のICと同様に、テスト回路405〜407はJTAGポートを通じてアクセスされ、その各々がすでに説明されたような、複数のJTAG相互接続(例えば、TDI、TMS、TCK、およびTDO相互接続)を含む。最上流のIC(例えば、IC402)のJTAG相互接続は二重目的ピン440〜443に結合される。より詳細には、二重目的ピン440〜443は、TDIピン440、TMSピン441、TCKピン442、およびTDOピン443を含み、これらは上述のように、IC402〜404が機能モードにある場合はシリアル・ポート・ピンの役割も担う。二重目的ピン440〜443および対応する相互接続は、TRSTピンおよび相互接続(図示せず)も含む。

【0064】

各テスト回路405〜407は、図3とともにすでに説明されたように、複数のシフトレジスタ、TAPコントローラ420,421,422、テストサブシステム(図示せず)、マルチプレクサ424,425,426,427,428,429(任意選択)、430,431,432(任意選択)、433,434,435、およびさまざまな他のロジックを含む。加えて、システム400は、IC402のTE相互接続(図示せず)と接続されるTEピン444も含むことができ、各テスト回路405〜407は、TEピン上に存在する信号が、下流のICに渡されてマルチプレクサ424〜435の機能を制御することを可能にする回路を含むことができる。すでに説明されたように、TE信号がTEピン上でアサートされ、かつTAPコントローラ420、421が他の様態でTE信号の下流のICへの伝搬を妨げていない場合、IC402〜404の各々はTE信号を受け取る。

【0065】

TE信号がアサートされる(例えば、IC402〜404がJTAGテストモードにある)場合、マルチプレクサ424〜426は、それらのJTAGインタフェースに存在する入力JTAG信号(すなわち、TDI、TMS、TCK)を、TAPコントローラ420〜422およびそれらの関連データおよび命令レジスタに渡し、マルチプレクサ427,428は入力JTAG信号を対応する下流のICに渡す。例えば、IC402のマルチプレクサ427は、入力JTAG信号(すなわち、二重目的ピン440〜442およびIC402の二重目的相互接続を介して受け取られる信号)をIC403に渡し、IC403のマルチプレクサ428は、入力JTAG信号(すなわち、IC402,403の二重目的相互接続を介して受け取られる信号)をIC404に渡す。従って、JTAGテストモードにおいて、各IC402〜404は同じJTAG信号を受け取る。

【0066】

一度にただ1つのIC402〜404のTAPコントローラ420〜422が、TDOピン443上で出力されるべき信号を生成し、テスト回路405〜407は、TDOピン443上に存在する信号が、単一のTAPコントローラ420〜422によって生成される信号に対応するように構成される。特定のTAPコントローラ420〜422から出力信号(すなわち、TDO信号)を受け取るために、すべての上流のICがリセット/クリアされてJTAG通過モードになる。すでに述べたように、ICをリセット/クリアしてJTAG通過モードにするために、ICのTE相互接続上で信号がアサートされ、上流のICのTDR内のJTAG通過制御ビットがリセット/クリアされる。この構成において、すでに説明されたように、ICは、そのTDO−R相互接続(例えば、図3のTDO−R相互接続353)上で受け取られる信号をそのTDO相互接続(例えば、図3のTDO相互接続343)に渡すことになる。例えば、IC404のTAPコントローラ422から出力信号を受け取るために、IC402,403はJTAG通過モードにおいて構成される。従って、マルチプレクサ435は、TAPコントローラ422から受け取られるテスト出力信号をIC404のTDO相互接続(図示せず)に渡し、当該信号は、IC403のTDO−R相互接続(図示せず)およびマルチプレクサ431において受け取られる。そして、IC403のマルチプレクサ431および434は、(TAPコントローラ422からの)テスト出力信号をIC403のTDO相互接続(図示せず)に渡し、当該信号は、IC402のTDO−R相互接続(図示せず)およびマルチプレクサ430において受け取られる。そして、IC402のマルチプレクサ430および433は、(TAPコントローラ422からの)テスト出力信号をIC402のTDO相互接続(図示せず)に渡し、当該相互接続は、TDOピン443に接続されている。このようにして、IC402、403がJTAG通過モードにある場合、IC404のTAPコントローラ422からのテスト出力信号は、IC402,403を通じてシステム400のTDOピン443に渡されることができる。

【0067】

同様に、IC403のTAPコントローラ421から出力信号を受け取るために、IC402はJTAG通過モードにおいて構成される。従って、マルチプレクサ434は、TAPコントローラ421から受け取られるテスト出力信号をIC403のTDO相互接続(図示せず)に渡し、当該信号は、IC402のTDO−R相互接続(図示せず)およびマルチプレクサ430において受け取られる。次いで、IC402のマルチプレクサ430および433は、(TAPコントローラ421からの)テスト出力信号をIC402のTDO相互接続(図示せず)に渡し、当該相互接続は、TDOピン443に接続されている。このようにして、IC402が適切に構成される場合、IC403のTAPコントローラ421からのテスト出力信号は、IC402を通じてシステム400のTDOピン443に渡されることができる。

【0068】

すでに述べたように、TAPコントローラに関連付けられる命令レジスタ(例えば、図3のIR330)は現在の命令を保持する。IRの内容およびテスト・データ・レジスタ(例えば、図3のTDR332)内のさまざまなビットの状態が、TAPコントローラが受信信号をどのように処理または転送するかに影響を与える。より具体的には、各TAPコントローラ420〜422は、オペコードの命令への事前定義のマッピングに従って、TAPコントローラのIRにシフトされるオペコードを復号する命令復号ロジック(図示せず)を含む。上記の記載が示すように、JTAG通過モードにおいて、各IC402〜404は同じJTAG入力信号(すなわち、TDI、TMS、TCK)を受け取る。従って、各IC402〜404は同一のオペコードにおいてその対応するIRにクロッキングする。複数のICがTDOピン443上で出力テストデータを生成しようとするシナリオを回避するために、一実施形態において、複数のICおよびTAPコントローラを含むシステム(例えば、システム400)内の各TAPコントローラは、他のTAPコントローラとは異なる事前定義のオペコード−命令マッピング(例えば、各TAP内にハードコード化されるマッピング)に基づいて操作される。より具体的には、各TAPコントローラの復号ロジックは、オペコードのセットを、他のTAPコントローラが同じオペコードのセットを復合するのとは異なる様式で復号する。換言すれば、第1のTAPコントローラがオペコードを、第1のTAPコントローラに第1の動作を実行させる第1の命令にマッピングするのに対して、第2のTAPコントローラは同じオペコードを、第2のTAPコントローラに第1の動作と異なる第2の動作を実行させる、第2の異なる命令にマッピングする。

【0069】

マルチICシステムの各ICのための異なるオペコード−命令マッピングの実施態様をさらに説明するために図4のシステム400を使用することになる。説明を容易にするために、図4のシステム400はIC402,403のみを含むものと想定し、ここでIC402がマスタコントローラであり、IC403がスレーブコントローラである。一実施形態によれば、IC402のTAPコントローラ復号ロジックは、第1の事前定義のオペコード−命令マッピングに基づいて動作することになり、IC403のTAPコントローラ復号ロジックが第1のものと異なる第2の事前定義のオペコード−命令マッピングに基づいて動作することになる。一実施形態において、オペコード−命令マッピングは、TAPコントローラが異なる命令を同時に実行することができるように定義される。しかしながら、一度にただ1つのICのTAPコントローラが信号をTDO相互接続443上に駆動する命令を実行することができるという点で、オペコード−命令マッピングは両立できる。一実施形態において、オペコード−命令マッピングは、他の各TAPコントローラがBYPASS命令または何らかの他の命令(すなわち、BYPASS命令以外の命令を含む「非BYPASS」命令)のいずれかを実行するようなものである。

【0070】

例えば、一実施形態において、オペコード−命令マッピングは、任意の所与のオペコードがシステムのただ1つのICに対する非BYPASS命令のみにマッピングし、同じオペコードがシステムのすべての他のICに対するBYPASS命令にマッピングするように、事前定義されることができる。従って、マスタコントローラIC402は事前定義のマッピングに基づいて動作し、当該マッピングにおいて第1のグループのオペコードは非BYPASS命令に対応し、第2の相互排他的なグループのオペコードはBYPASS命令に対応する。加えて、スレーブコントローラIC403は異なる事前定義のマッピングに基づいて動作し、当該マッピングにおいて、同じ第1のグループのオペコードがBYPASS命令に対応し、同じ第2のグループのオペコードのうちの少なくともいくらかは非BYPASS命令に対応し得る(ただし、それらは非BYPASS命令に対応する必要はなく、同様にBYPASS命令に対応し得る)。

【0071】

下記の表1は、3つのICおよび対応するTAPコントローラ(例えば、図4のTAP420〜422)を含むシステムに対するJTAG命令セットの一例である。オペコードから命令への具体的なマッピングが表1に列挙されているが、表1の命令セットとは異なる命令セットが定義されてもよく、かつ/またはさまざまな命令が異なるオペコードにマッピングされてもよいことは理解されたい。

【0072】

【表1】

表1が示すように、一実施形態において、1つのコントローラに対して非BYPASS命令にマッピングするオペコードは、他のコントローラに対してはBYPASS命令にマッピングする。例えば、オペコード1,4,7,10,13,16、および19がコントローラ1に対して非BYPASS命令にマッピングしている場合、これらのオペコードはコントローラ2および3に対してはBYPASS命令にマッピングする。同様に、オペコード2,5,8,11,14,17、および20がコントローラ2に対して非BYPASS命令にマッピングしている場合、これらのオペコードはコントローラ1および3に対してはBYPASS命令にマッピングする、などである。従って、同じオペコードが各コントローラ(例えば、すべてのIC402〜404)に同時にクロッキングされる場合があるけれども、ただ1つのIC(例えば、そのテストデータ出力がTDOピン443上で望まれるIC)がオペコードを非BYPASS命令にマッピングすることができる。例えば、表1を参照すると、オペコード13がコントローラ1〜3にクロッキングされた後、オペコード13がマッピングする命令(すなわち、IDCODE命令)のコントローラ1による実行は、コントローラ1に、TDO相互接続443上でIDCODEレジスタからTAP識別子を送出させることになる。しかしながら、オペコード13がマッピングする命令(すなわち、BYPASS命令)のコントローラ2および3による実行は、コントローラ2および3にBYPASSに入らせるかまたは留まらせ、コントローラ2および3はTDO相互接続443上でデータを送出しない。表1および上記の説明も示すように、異なる複数のオペコードが異なる複数のコントローラに同じ命令を実行させる。例えば、オペコード1,2、および3(すなわち、「異なる複数のオペコード」)が、コントローラ1,2、および3(すなわち、「異なる複数のコントローラ」)に、SAMPLE/PRELOAD命令(すなわち、「同じ命令」)を実行させる。TDR制御ビットが(TE信号とともに)最上流のICが外部TDOピン(例えば、図4のTDOピン443)を駆動するか、または下流のICが外部TDOピンを駆動するかを決定することを想起されたい。換言すれば、IC(例えば、図4のIC402,403,404)内に存在するTAPコントローラオペコード(例えば、上記表1のオペコード)はどのICが外部TDOピンを駆動するかを決定しない。

【0073】

一実施形態によれば、BYPASS命令は実行されると、TDI−TDOバイパスレジスタ(例えば、図3のTDR332のうちの1つ)を選択し、当該レジスタは、ICをTDI−TDOバイパスモードにおくか、または当該モードに留める。SAMPLE命令は、実行されると、バウンダリ・スキャン・レジスタ(例えば、図3のTDR332のうちの1つ)を選択し、それによって、相互接続値がバウンダリ・スキャン・レジスタ内に読み出されることができ、PRELOAD命令は、実行されると、EXTESTの前に相互接続出力値を読み出す。表1とともに表されている実施形態において、SAMPLEおよびPRELOAD命令は組み合わされている(すなわち、SAMPLE/PRELOAD命令として)。EXTEST命令は、実行されると、基板レベルの挙動を精査するための相互接続の使用のように、外部テストのために使用されることができる。EXTEST命令は代替的に、コア上で動作してもよい(例えば、コアへのデータの書き込み)。INTEST命令は、実行されると、オンチップ挙動を精査するための相互接続の使用のように、内部テストのために使用されることができる。INTEST命令は代替的に、コア上で動作してもよい(例えば、コアからのデータの読み出し)。CLAMP命令は、実行されると、事前ロードされている値を使用して出力相互接続を駆動する。IDCODE命令は、実行されると、IDCODEレジスタ(例えば、図3のTDR332のうちの1つ)を選択し、それによって、TAP識別子がIDCODEレジスタから読み出されることができる。SELECT TDR(テスト・データ・レジスタ)命令は、実行されると、結果として、値が実質的にクロックインまたはクロックアウトされ得る、設計特有のテスト・データ・レジスタ(例えば、図3のTDR332のうちの1つ)が選択されることになる。TDRは、設計特有のテストサポート機構(例えば、セルフテスト、スキャンパスなど)に対するアクセスの提供のような、さまざまな目的に使用されることができる。

【0074】

表1に列挙されている命令の他に、例えば、HIGHZ(すべての相互接続の出力を無効にする)、RUNBIST(ICをセルフテストモードにおく)、SCAN_N(他のバウンダリスキャン動作を適用する信号に影響を与えるスキャンパス選択レジスタを構成する)、USERCODE(ユーザ定義のコードを返す)、他のSELECT_TDR命令(例えば、追加のTDRを選択する)、および他の製造者またはユーザ定義の命令を含む、他の命令も同じく、または代替的に定義されることができる。

【0075】

図5は、例示の実施形態による、マルチICシステム(例えば、図4のシステム400)をテストするための方法のフローチャートを示す。本方法は、上記のように直列に相互接続される任意の数のICを有するマルチICシステムをテストするのに使用されることができる。本方法の説明を容易にするために、図4のさまざまな要素が参照される場合がある。しかしながら、本方法は、3つよりも少ないかまたは多いICを含むシステムにおいて使用されてもよいことは理解されたい。任意の数のICを有するシステムに適用するために図5のフローチャートを一般化する利益のために、列内のICの数を示すためにフローチャートにおいて固定数Nが使用され、さまざまなステップを適用する列内の特定のICを示すためにパラメータnが使用される。ICの数が分かっているシステムにおいては、パラメータnのセッティングおよび更新に関連付けられるステップは本方法から除外されてもよく、代わりにフローチャートはより直線的に流れるように改変されることができることは理解されたい。図5に示される一連のステップに対するこれらのおよび他の改変は、本発明の主題の範囲内に含まれることが意図されている。

【0076】

本方法は、列内のすべてのICのTAPコントローラ(例えば、図4のTAPコントローラ420〜422)をリセットすることによって開始することができる。TAPがTRSTピンおよび対応する相互接続を含む場合、TAPコントローラは、ロジック0がTRSTピンに印加されると、リセット状態(例えば、IEEE標準1149.1において定義されているテスト−ロジック−リセット(Test−Logic−Reset)コントローラ状態)に非同期的にリセットされることができる。そうではなく、TRSTピン上の信号を使用してリセットが実行されない場合、リセットプロセスは基本的に、この時点において任意の状態にあり得る各TAPコントローラがリセット状態に遷移されることが確実になる回数だけ各TAPコントローラをクロッキングすることを含む。このような実施形態において、リセットは下記に記載されるブロック502〜508を含むことができる。より詳細には、リセットプロセスは例えば、ブロック502において、少なくとも列内の最上流のIC(例えば、図4のIC402)に提供される外部ICリセット信号をアサートすることによって開始することができる。例えば、これは、外部テスト機器が、列内の最上流のICのリセット相互接続(例えば、図3のRESETB相互接続364)に信号を提供することを含むことができる。

【0077】

TRSTピンが利用可能でありリセットの実行に使用されるか否かにかかわらず実行されるブロック504において、テスト・イネーブル(TE)信号がアサートされる。一実施形態によれば、これは、外部テスト機器が列内の最上流のIC(例えば、図4のIC402)のTE相互接続と結合される外部TEピン(例えば、図4のTEピン444)に提供される信号(すなわち、TE信号)をアサートすることを含むことができる。すでに説明されたように、ICのリセット回路は、TE相互接続(例えば、図3のTE相互接続344)上で信号がアサートされる場合、リセットが外部リセット信号(例えば、図3のRESETB相互接続364上のリセット信号)によって制御されるように構成される。従って、TE信号および外部リセット信号が正しい状態にある場合、ICのリセット回路(例えば、図3のORロジック361およびANDロジック362)は内部リセット(INT_RESETB)信号を生成し、さらに、リセット信号を(例えば、RESETB−F相互接続366、およびRESETB−F相互接続366と次の下流のICのRESETB相互接続364との間のIC間導体を介して)次の下流のICのRESETB相互接続に伝達する。加えて、すでに説明されたように、TE信号のアサートは、(例えば、図3のマルチプレクサ324〜326を介して)TE信号を受け取る任意のICの二重目的相互接続を、JTAG相互接続として構成する。従って、TE信号がICのためにアサートされると、JTAG相互接続を介してICのTAPコントローラ(例えば、図3のTAPコントローラ320)およびレジスタ(例えば、図3のIR330およびTDR332)との通信が可能となる。TE信号のアサートおよびIC内のJTAG通過制御ビット(例えば、図3のTDR332内のビット)の状態は、さまざまな入力JTAG相互接続(例えば、図3のTDI相互接続340、TMS相互接続341、TCK相互接続342、およびTDO−R353)上に存在する信号の、対応する出力JTAG相互接続(例えば、図3のTDI−F相互接続350、TMS−F相互接続351、TCK−F相互接続352、およびTDO343)への転送も提供する。

【0078】

最初、最上流のIC(例えば、図4のIC402)は、TE信号を次の下流のIC(例えば、図4のIC403)に伝達するように構成されなくてもよい。すでに述べたように、各上流のIC(例えば、図4のIC402、403)は、TE信号が下流のICに対してブロックまたは伝達されることを可能にする回路(例えば、図3、4のANDロジック360、460、461)を含むことができる。すでに述べたように、TE信号を下流のICに伝達するために、上流のICはTE通過イネーブル信号をアサートすることができる。TE通過イネーブル信号は、TDR(例えば、図3のTDR332のうちの1つ)内の指定されるビットの状態に基づいて生成されることができ、それゆえ、TE通過信号をアサートするために、およびTE信号を下流のICに伝達するために、適切な値が上流のICの指定されるビット(例えば、図3のTDR332のうちの1つの指定されるビット)にクロッキングされるべきである。

【0079】

各ICのTAPコントローラをリセットするために、およびTE信号を各下流のICに伝達するために、ブロック506において、適切な信号が(例えば、外部テスト機器によって)外部TAPインタフェースに提供される。換言すれば、TAPインタフェースは、列内のすべてのICのTAPコントローラをリセットするために使用される。一実施形態によれば、これは、すべてのICのTAPコントローラにリセット状態(例えば、IEEE標準1149.1において定義されているテスト−ロジック−リセットコントローラ状態)に入らせるための、および、値を上流のICの適切なTDRビットにリセットしてICにアサートされたTE信号を下流のICに伝達させるための回数だけTMSピン(例えば、図4のピン441)をクロッキングすることを含むことができる。このプロセスは連続して、最上流のIC(例えば、図4のIC402)における開始に進む。換言すれば、最上流のICのTAPコントローラ(例えば、図4のTAPコントローラ420)は、TAPコントローラをリセット状態においてセットするように、および、TDRビットを、TE通過イネーブル信号がアサートされる状態にリセットするようにクロッキングされる。この時点において、TE信号が次の下流のIC(例えば、図4のIC403)に提供され、そのICのTAPコントローラ(例えば、図4のTAPコントローラ421)がリセットされることができ、そのIC内のTE通過イネーブル信号がリセットされてTE信号が次の下流のIC(例えば、図4のIC404)に伝達されることができる。このプロセスは、列内のすべてのICのTAPコントローラがリセットされるまで繰り返される。

【0080】

ブロック506においてTAPコントローラリセットが完了すると、ブロック508において外部ICリセットがディアサートされる。この時点において、すべての上流のIC(例えば、図4のIC402,403)は、テスト・イネーブル信号を次の下流のデバイスに(例えば、次の下流のデバイスのTE相互接続344に接続される、図3のTE−F相互接続354を介して)提供する構成にある。列内のすべてのICはリセットされてアサートされたTE信号を受け取っており、従って列内のすべてのICはテスト動作モードにあり、それらの二重目的相互接続はそれらのそれぞれのTAPコントローラとの通信を提供する。次に説明されることになるブロック510〜526は、(例えば、図4のTDOピン443上の)出力テストデータを提供する特定のICを選択するための、および、システム上でJTAGテストを実行するための方法の実施形態を示す。

【0081】

ブロック510において、パラメータnはNの値に初期化され、これは列内のICの数に等しい。上記で述べたように、値Nおよびnは図5のフローチャートを、任意の数のICを有するシステムに適用可能であるように一般化するために使用され、実際には値Nおよびnは、実際のシステムにおいて方法を実施する際には使用されない場合がある。それにも関わらず、値Nおよびnは本方法の実施形態の一般性および説明を促進するために使用される。下記で明確にされるように、パラメータnの現在の値は、未だにテストモードにある(すなわち、そのTE相互接続上でアサートされたテスト・イネーブル信号を受け取っている)最下流のデバイスに対応する。

【0082】

リセット後、ブロック512によって示されるように、TAPインタフェースは列内のn個のICにとって利用可能である。ブロック512を含むループの1回目の反復の間、nの値はNに等しいため、TAPインタフェースは列内のすべてのICにとって(例えば、図4のIC401〜403にとって)利用可能である。

【0083】

ブロック514において、列内のn個のIC上で所望のTAPトランザクションが実行される。ブロック514を含むループの最初の反復の間、列内のすべてのIC上で所望のTAPトランザクションが実行される。基本的に、各タップトランザクションは、命令オペコード(例えば、上記表1に列挙されているオペコード)の、各TAPコントローラに関連付けられる命令レジスタ(例えば、図3のIR330)へのクロッキング、および、場合によっては(例えば、オペコードがSELECT_TDR命令に対応する場合)、データのTDR(例えば、図3のTDR332のうちの1つ)へのクロッキングを含む。すでに詳細に述べたように、各TAPコントローラは、特定のオペコードがただ1つのICに対する非BYPASS命令にマッピングし、同じオペコードがすべての他のICに対するBYPASS命令にマッピングする、異なるオペコード−命令マッピングによって左右され得る。従って、任意の所与の時点において、ただ1つのICが外部TDO相互接続を駆動しており、他のICはブロックされて外部TDO相互接続を駆動することができない。

【0084】

本方法の前または後に実行されてもよいブロック516において、(例えば、図4のTEピン444において提供される)TE信号がディアサートされているか否かの判定を行うことができる。そうである場合、JTAGテストは完了しており(または終了しており)、ブロック528において、所望の場合にはシリアルポート(例えば、I2CポートもしくはSPIポート)または任意の他のインタフェースとともに使用されるために二重目的相互接続が再び利用可能となる。

【0085】

一実施形態によれば、JTAGテストが継続している(例えば、すべてのICに対してTE信号がアサートされたままである)間、所望の場合、列のICは、最下流のIC(例えば、図4のIC404)から開始して上流へと動作して、順次JTAGテストモードを中止されることができる。基本的に、下流のICのJTAGテストモードを中止することは、そのICに対するTE信号の提供を中断することによって達成されることができる。ブロック518〜526は、ICがこのようにしてJTAGテストモードを中止されることができる実施形態に対応し、またはブロック518および520の場合は、1つまたは複数の下流のICがJTAGテストモードを中止された場合にはTAPコントローラは、JTAGインタフェースをすべてのTAPコントローラに対して再び利用可能とするためにリセットされることができる。

【0086】

再びブロック516を参照して、TE信号がディアサートされていない場合、ブロック518においてTAPリセットが起こったか否かがさらに判定されることができ、これは他の実施形態においては本方法の前または後に実行されてもよい。TAPリセットは、例えば、各TAPコントローラがリセット状態(例えば、IEEE標準1149.1において定義されているテスト−ロジック−リセットコントローラ状態)に遷移し戻るだけの回数分(例えば、最大5×N回)TMSピン(例えば、図4のTMSピン441)上の信号をローでクロッキングすることによって、外部テスト機器によって実施されることができる。TAPリセットが起こると、パラメータnは列内のICの数Nにリセットされ、図示されるように方法は反復する。TRSTピンが提供される代替の実施形態において、ロジック0がTRSTピンに印加されると、TAPコントローラはリセット状態に非同期的にリセットされることができる。いずれにせよ、TAPリセットが起こると、ブロック512においてすべてのICに対してTAPインタフェースが利用可能となり、図示されるように方法は反復する。

【0087】

TAPリセットが起こらなかった場合、ブロック522において、列内の最上流のIC(例えば、図4のIC402)が、未だにJTAGテストモード(すなわち、n = 1である場合)にある唯一のICであるか否かが判定されることができる。そうである場合、本方法は図示されるように反復する。そうでない場合、上流のICがTE信号の列内の次の下流のICへの伝達を中断する可能性が存在し、従って下流のICをJTAGテストモードから実効的に遷移させる(すなわち、JTAGインタフェースを下流のICにとって利用不可能にする)。一実施形態において、かつすでに述べたように、上流のICは内部において、TE通過イネーブル信号を生成することができ、これは、TDR(例えば、図3のTDR332のうちの1つ)内の指定されるビットの状態に基づいて生成されることができる。TE通過イネーブル信号がアサートされると、アサートされたTE信号は、(例えば、図3のTE−F相互接続354を介して)次の下流のICのTE相互接続に提供される。逆に、TE通過イネーブル信号がディアサートされると、TE信号は次の下流のICのTE相互接続に提供されず、この次の下流のICはもはやJTAGテストモードにはない。

【0088】

ブロック524において、ICn−1(すなわち、依然としてJTAGテストモードにある最下流から2番目のIC)内のTE通過イネーブル信号がディアサートされているか否かが判定されることができる。例えば、n = Nのときのブロック524の1回目の反復の間、ICn−1(例えば、図4のIC403)内のTE通過イネーブル信号がディアサートされているか否かが判定されることができる。特定の実施形態において、この判定は、ICn−1(例えば、図4のIC403)内のTE通過イネーブル信号に関連付けられるTDRビットがICn(例えば、依然としてJTAGテストモードにある最下流のICであろう、IC404)へのTE入力を選択解除するように設定されているか否かを判定することを含む。そうである場合、最下流のIC(例えば、図4のIC404)はもはやJTAGモードになく、ブロック526においてパラメータnが1デクリメントされ、これはTAPインタフェースがそのICにとってはもはや利用可能でないことを示す。本方法は、その後図示されるように反復することができ、ここで、TAPインタフェースは列内の1つ少ないICにとって(例えば、IC402および403のみにとって)利用可能である。本方法は、(例えば、上記ブロック516において判定されるように)TE信号がディアサートされるか、またはJTAGテストを終了させる他の何らかの事象が発生するまで反復し続ける。

【0089】

このように、集積回路テスト方法および装置のさまざまな実施形態が上記で説明されてきた。一実施形態は、入力信号を受け取るように構成される入力相互接続と、テスト・イネーブル信号を受け取るように構成されるテスト・イネーブル相互接続と、入力信号に対応する値に基づいてICのテストを実行するためのコントローラとを有するICを含む。ICはさらに、入力ポートと、入力相互接続、コントローラ、および入力ポートに結合されるマルチプレクサとを含む。マルチプレクサは、テスト・イネーブル信号がアサートされていないことに応答して入力信号を入力ポートに渡し、テスト・イネーブル信号がアサートされていることに応答して入力信号をコントローラに渡すように制御可能である。

【0090】

別の実施形態は、複数の外部ピンと、第1のICと、第2のICとを含むマルチICシステムを含む。第1のICは、第1のTAPコントローラと、第1の命令レジスタと、少なくとも1つの第1のTDRと、複数の外部ピンに結合される複数の第1の相互接続と、複数の第2の相互接続とを有する。第2のICは、第2のTAPコントローラと、第2の命令レジスタと、少なくとも1つの第2のTDRと、複数の第2の相互接続に結合される複数の第3の相互接続とを有する。第1のTAPコントローラは、第1の命令レジスタにクロッキングされるとオペコードを第1の命令にマッピングするように構成され、第2のTAPコントローラは、第2の命令レジスタにクロッキングされるとオペコードを、第1の命令と異なる第2の命令にマッピングするように構成される。

【0091】

別の実施形態は、第1のテストコントローラを有する第1のICと、第2のテストコントローラを有する第2のICとを少なくとも含むマルチICシステムをテストするための方法を含む。本方法は、第1のテストコントローラおよび第2のテストコントローラをテストモードにおいて構成すること、オペコードを、第1のテストコントローラに関連付けられる第1の命令レジスタに、および、第2のテストコントローラに関連付けられる第2の命令レジスタにクロッキングすることを含む。本方法は、第1のテストコントローラがオペコードに基づいて第1の命令を実行することと、第2のテストコントローラがオペコードに基づいて第2の命令を実行することとをさらに含み、第2の命令は第1の命令とは異なる。

【0092】

本記載および特許請求の範囲における「第1」、「第2」、「第3」、「第4」などの用語がある場合、これらは、同様の要素またはステップ間で区別するために使用されることができ、必ずしも特定の連続する、または経時的な順序を説明するためのものではない。このように使用される用語は、本明細書に記載されている実施形態が例えば、本明細書において例示または他の様態で記載されている以外の順序または構成で動作または製造することが可能であるように、適切な状況下で置き換え可能であることが理解されるべきである。加えて、任意のフローチャートとともに図示および記載されているプロセス、ブロックもしくはステップの順序は例示のみを目的としており、他の実施形態においてさまざまなプロセス、ブロックもしくはステップが他の順序で、かつ/もしくは並行して実行されてもよいこと、および/または、それらのプロセス、ブロック、ステップのうちの特定のものは組み合わされるか、削除されるか、もしくは複数のプロセス、ブロックもしくはステップに分解されてもよいこと、および/または、本実施形態とともに追加のもしくは異なるプロセス、ブロックもしくはステップが実行されてもよいことは理解されたい。さらに、「備える(comprise)」、「含む(include)」、「有する(have)」といった用語およびそれらの任意の変化形は非排他的な包含をカバーするように意図され、それによって、要素またはステップのリストを含むプロセス、方法、製品、または装置が必ずしもそれらの要素またはステップに限定されず、このようなプロセス、方法、製品、または装置に明示的に列挙されまたは内在していない他の要素またはステップを含むことができる。

【0093】

本発明の主題の範囲から逸脱することなく、上記の実施形態にさまざまな改変を行うことができることは理解されたい。本発明の主題の原理が特定のシステム、装置、および方法に関連して上記で説明されてきたが、この説明は例示のみを目的としており、本発明の主題に対する限定としてではないことは明瞭に理解されたい。本明細書において述べられ図面内に示されたさまざまな機能または処理ブロックは、ハードウェア、ファームウェア、ソフトウェアまたはそれらの任意の組み合わせにおいて実装されることができる。さらに、本明細書において採用されている表現または専門用語は説明を目的としており、限定ではない。

【0094】

特定の実施形態の上記の記載は、他者が、現在の知識を適用することによって、一般的な概念から逸脱することなくさまざまな用途のためにそれを容易に改変および/または適合することができるだけ十分に本発明の主題の一般的な性質を公開している。従って、このような適合および改変は開示されている実施形態の均等物の意図および範囲内にある。本発明の主題は、すべてのこのような代替形態、改変形態、均等物、および変形形態を、添付の特許請求の範囲の精神および広い範囲内に入るものとして包含する。

【技術分野】

【0001】

本開示は、集積回路のためのテスト方法および装置に関する。

【背景技術】

【0002】

デバッグ作業を促進するために、多くの現行の集積回路(IC)は、ジョイント・テスト・アクション・グループ(JTAG)準拠回路(IEEE 1149.1標準テスト・アクセス・ポートおよびバウンダリスキャン・アーキテクチャとして標準化されている)を含む。特許文献1には、集積回路内に搭載されるマルチコアデバイスをテストする方法及びシステムが開示されている。JTAG準拠回路およびICのテストにおいて当該回路を使用する方法(まとめて単純に「JTAG」と称される)はICの内部ブロックに対するアクセスを提供し、これによって、JTAGは組込みシステムのデバッグによく適するようになる。より具体的には、JTAG準拠バウンダリスキャン技術をサポートするデバイスにおいて、デバイスのコアロジックとデバイスのピンとの間の信号がバウンダリ・スキャン・セルによってインターセプトされ、当該セルは、共に結合されてバウンダリ・スキャン・レジスタ(BSR)として既知のシリアルスキャンパスを形成する。通常、バウンダリ・スキャン・セルはIC動作に影響を与えない。しかしながら、テストモードにおいて、バウンダリ・スキャン・セルは値をセットしかつ/または読み出すために使用されることができる。例えば、JTAGは、特定の種類の障害(例えば、短絡、開放、および論理的な障害)に関してテストするために、ICのBSRに対する外部インタフェースを操作するのに使用されることができる。

【0003】

IC上で実装される場合、JTAG準拠回路は少なくとも、命令レジスタおよび複数のデータレジスタに対するアクセスを有するJTAGインタフェースおよびコントローラを含む。JTAGインタフェース(まとめてテスト・アクセス・ポート、すなわちTAPとして既知である)は、4相互接続インタフェースまたは5相互接続インタフェースのいずれかである。4つの主要な相互接続は、TMS(テストモード状態)、TCK(クロック)、TDI(テスト・データ・イン)、およびTDO(テスト・データ・アウト)を含む。JTAGインタフェースは、TRST(テスト・リセット)相互接続が実装される場合、追加の相互接続を含むことができる。一実施形態において、TRST相互接続を介して提供されるテスト・リセット信号は、対応するテスト・リセット回路に、システム・レベル・リセットを生成させることができる。

【0004】

JTAGインタフェースと通信するために、ホストコンピュータは、目標ICのJTAGインタフェースに(例えば、JTAGアダプタを通じて)接続されることができ、ホストコンピュータは、信号がJTAGインタフェースに提供されるか、または信号がJTAGインタフェースから読み出されるようにすることができる。より具体的には、ホストコンピュータは、TCK上のクロッキング信号とともにTMSおよびTDI上の信号を操作することによって、ならびに、TDO上でICによって提示される信号を読み出すことによって、ICのTAPコントローラと通信する。TAPコントローラの状態は、TCK遷移において変化する場合がある。

【0005】

システム・イン・パッケージ(SiP)のようないくつかのマルチICシステムにおいては、システムの各ICに対して専用の外部JTAGインタフェースピンをサポートするのに利用可能なパッケージピンの数が十分でない場合がある。これらのシステムのいくつかは、直接的にまたは間接的にさまざまなICのJTAGインタフェースに接続する、1セットの外部JTAGインタフェースピンを含む場合がある。ICのうちの1つをテストするために、被試験ICを除くすべてのICが「TDI−TDOバイパス」モード(すなわち、ICのTDIおよびTDO相互接続がICのTDI−TDOバイパスレジスタを通じて事実上直接接続されるモード)にセットされる。このような構成においては、外部TDIピンにおいて提示されるTDI信号は被試験ICに渡され、被試験ICによって生成されるTDO信号は外部TDOピンにある。

【0006】

例えば、図1は、従来技術による、それらのJTAG TDOおよびTDI相互接続が共にデイジーチェーン接続されている複数のIC102、103、104の簡略化された回路図100を示す。図示されている構成において、IC102〜104のすべてに対するアクセスは、単一の外部JTAGインタフェース110を通じて提供されることができる。TMSピン112およびTCKピン114は各IC102〜104のTMSおよびTCK相互接続に直接接続され、TDIおよびTDO相互接続は共にデイジーチェーン接続される。換言すれば、第1のIC102のTDI相互接続は外部TDIピン116に直接接続され、第1のIC102のTDO相互接続は第2のIC103のTDI相互接続に接続され、第2のIC103のTDO相互接続は第3のIC104のTDI相互接続に接続され、第3のIC104のTDO相互接続は外部TDOピン118に直接接続される。

【0007】

ICのいずれか1つ(例えば、IC104)をテストするために、他のIC(例えば、IC102、103)は(例えば、BYPASS命令においてクロッキングすることによって)TDI−TDOバイパスモードにセットされる。クロック入力はTCKピン114において提供され、クロッキングは、ICのTAPコントローラ(図示せず)の各々において実装される標準化JTAGステートマシンによってTMSピン112の段階で変化する。Shift_IRおよびShift_DR状態において、1ビットのデータが各TCKクロックパルスとともに、それぞれ、TDIピン116から各タップコントローラ命令またはデータレジスタ(これも図示せず)を出入りして転送されることができる。例えば、一般的な命令は、データレジスタ(例えば、BSR、TDI−TDOバイパスレジスタ、またはIDCODEレジスタ)に対するデータの読み出しまたは書き込み、入力ピンのサンプリング、出力ピンの駆動(または浮動)などを含み得る。IC102〜104のすべてはロックステップにおいて動作するが、被試験IC(すなわち、TDI−TDOバイパスモードにないIC)のみは、そのTDOポートにおいて有効なテストデータを生成するために外部TDIピン116上の入力信号によって影響される。次いで、その有効なテストデータは外部TDOピン118において生成される。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】米国特許第7,590,910号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

JTAG準拠である従来のマルチIC SiP(例えば、図1の回路100)が提供する、SiP内の複数のICの各々をテストする能力はいくらか限られているが、パッケージピンの必要な数およびパッケージ内のIC間ルーティングを低減することができるテスト構成が望ましい。

【課題を解決するための手段】

【0010】

上記問題点を解決するために、請求項1に記載の発明は、集積回路であって、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備えることを要旨とする。

【0011】

請求項2に記載の発明は、請求項1に記載の集積回路において、前記コントローラはジョイント・テスト・アクション・グループ準拠コントローラであり、前記入力ポートは集積回路間ポートおよびシリアル周辺機器インタフェースポートから成る群から選択される、ことを要旨とする。

【0012】

請求項3に記載の発明は、請求項1に記載の集積回路において、出力信号を生成するように構成される第1の出力相互接続と、前記第1の出力相互接続および前記第1の入力相互接続に結合され、前記テスト・イネーブル信号がアサートされることに応答して、前記出力信号として生成されるために前記入力信号を前記第1の出力相互接続に渡すように制御可能である第2のマルチプレクサとをさらに備える、ことを要旨とする。

【0013】

請求項4に記載の発明は、請求項3に記載の集積回路において、前記第2のマルチプレクサに結合され、出力ポート信号を生成するように構成される出力ポートをさらに備え、前記第2のマルチプレクサは、前記テスト・イネーブル信号がアサートされていないことに応答して、前記出力信号として生成されるために前記出力ポート信号を前記第1の出力相互接続に渡すように制御可能である、ことを要旨とする。

【0014】

請求項5に記載の発明は、請求項4に記載の集積回路において、前記出力ポートは集積回路間ポート、シリアル周辺機器インタフェースポート、および二重モードI2C/SPIポートから成る群から選択される、ことを要旨とする。

【0015】

請求項6に記載の発明は、請求項1に記載の集積回路において、前記集積回路がJTAG通過モードにあるか否かの第2の指示を記憶するように構成される制御ビットと、テスト出力データを生成するように構成される第1のテスト・データ・アウト相互接続と、下流の集積回路から遠隔生成されるテスト出力データを受け取るように構成される第2のテスト・データ・アウト相互接続と、前記第1のテスト・データ・アウト相互接続に結合され、第1の指示が前記集積回路が前記JTAG通過モードにないことである場合に前記テスト出力データとして生成されるために、前記集積回路によって生成される第1のテスト出力データを前記第1のテスト・データ・アウト相互接続に渡すように制御可能である、第2のマルチプレクサと、前記第2のテスト・データ・アウト相互接続および前記第2のマルチプレクサに結合され、前記第2の指示が前記集積回路が前記JTAG通過モードにあることである場合に前記第1のテスト・データ・アウト相互接続上の前記テスト出力データとして生成されるために、前記遠隔生成されるテスト出力データを前記第2のマルチプレクサに渡すように制御可能である、第3のマルチプレクサとをさらに備える、ことを要旨とする。

【0016】

請求項7に記載の発明は、請求項1に記載の集積回路において、出力信号として前記テスト・イネーブル信号を生成するように構成される第2のテスト・イネーブル相互接続をさらに備える、ことを要旨とする。

【0017】

請求項8に記載の発明は、請求項1に記載の集積回路において、外部リセット信号を受け取るように構成されるリセット相互接続と、前記リセット相互接続に結合され、前記テスト・イネーブル信号がアサートされることに応答して、前記外部リセット信号に対応する出力リセット信号を生成するように構成される、リセット回路とをさらに備える、ことを要旨とする。

【0018】

請求項9に記載の発明は、請求項1に記載の集積回路において、外部クロック信号を受け取るように構成される外部クロック相互接続と、前記外部クロック相互接続に結合され、前記テスト・イネーブル信号がアサートされることに応答して、前記外部クロック信号に対応する出力クロック信号を生成するように構成される、クロック回路とをさらに備える、ことを要旨とする。

【0019】

請求項10に記載の発明は、マルチ集積回路システムであって、複数の外部ピンと、第1のテスト・アクセス・ポートコントローラ、第1の命令レジスタ、少なくとも1つの第1のテスト・データ・レジスタ、前記複数の外部ピンに結合される複数の第1の相互接続、および、複数の第2の相互接続を有する、第1の集積回路と、第2のTAPコントローラ、第2の命令レジスタ、少なくとも1つの第2のTDR、および、前記複数の第2の相互接続に結合される複数の第3の相互接続を有する第2の集積回路とを備え、前記第1のTAPコントローラは、前記第1の命令レジスタにクロッキングされるとオペコードを、前記第1のTAPコントローラに第1の動作を実行させる第1の命令にマッピングするように構成され、前記第2のTAPコントローラは、前記第2の命令レジスタにクロッキングされると前記オペコードを、前記第1の命令と異なる第2の命令にマッピングするように構成され、前記第2の命令は前記第2のTAPコントローラに、前記第1の動作と異なる第2の動作を実行させることを要旨とする。

【0020】

請求項11に記載の発明は、請求項10に記載のマルチ集積回路システムにおいて、前記複数の外部ピンはTE信号を受け取るように構成されるテスト・イネーブルピンを含み、前記複数の第1の相互接続は前記TEピンに結合されるTE相互接続を含み、前記第1の集積回路はスレーブポートをさらに含み、前記TE信号がディアサートされると前記第1の相互接続のセットが前記スレーブポートに結合され、前記TE信号がアサートされると前記第1の相互接続の前記セットが前記第1のTAPコントローラに結合される、ことを要旨とする。

【0021】

請求項12に記載の発明は、請求項11に記載のマルチ集積回路システムにおいて、前記第1の集積回路は、前記第1の相互接続の前記セットに、前記スレーブポートに、および前記第1のTAPコントローラに結合される第1のマルチプレクサをさらに備え、前記第1のマルチプレクサは前記TE信号に基づいて、前記TE信号がディアサートされると前記第1の相互接続の前記セットを前記スレーブポートに結合するように、および、前記TE信号がアサートされると前記第1の相互接続の前記セットを前記TAPコントローラに結合するように制御可能である、ことを要旨とする。

【0022】

請求項13に記載の発明は、請求項12に記載のマルチ集積回路システムにおいて、前記第1の集積回路は、マスタポートと、前記第1の相互接続の前記セットに、前記マスタポートに、および、前記第2の相互接続のセットに結合される第2のマルチプレクサとをさらに備え、前記第2のマルチプレクサは前記TE信号に基づいて、該TE信号がディアサートされると前記マスタポートを前記第2の相互接続の前記セットに結合するように、および、該TE信号がアサートされると前記第1の相互接続の前記セットを前記第2の相互接続の前記セットに結合するように制御可能である、ことを要旨とする。

【0023】

請求項14に記載の発明は、請求項10に記載のマルチ集積回路システムにおいて、前記複数の外部ピンはTE信号を受け取るように構成されるテスト・イネーブルピンを含み、前記複数の第1の相互接続は前記TEピンに結合される第1のTE相互接続を含み、前記複数の第2の相互接続はTE転送相互接続を含み、前記複数の第3の相互接続は前記TE転送相互接続に結合される第2のTE相互接続を含み、前記第1の集積回路は、前記TE信号を該第1の集積回路から前記TE転送相互接続と、前記第3の相互接続のうちの1つと、前記第2のTE相互接続とを通じて前記第2の集積回路に伝達するために、前記TE相互接続と前記TE転送相互接続との間に結合される回路をさらに含む、ことを要旨とする。

【0024】

請求項15に記載の発明は、請求項10に記載のマルチ集積回路システムにおいて、前記第2の集積回路は複数の第4の相互接続も含み、前記システムは、第3のTAPコントローラと、第3の命令レジスタと、少なくとも1つの第3のTDRと、前記複数の第4の相互接続に結合される複数の第5の相互接続とを有する少なくとも第3の集積回路をさらに備え、前記第3のTAPコントローラは前記第3の命令レジスタにクロッキングされると前記オペコードを、前記第1の命令または前記第2の命令のいずれかにマッピングするように構成される、ことを要旨とする。

【0025】

請求項16に記載の発明は、少なくとも、第1のテストコントローラを有する第1の集積回路と、第2のテストコントローラを有する第2の集積回路とを含むマルチ集積回路システムをテストするための方法であって、該方法は、前記第1のテストコントローラおよび前記第2のテストコントローラをテストモードにおいて構成するステップと、第1のオペコードを、前記第1のテストコントローラに関連付けられる第1の命令レジスタに、および、前記第2のテストコントローラに関連付けられる第2の命令レジスタにクロッキングするステップと、前記第1のテストコントローラが前記第1のオペコードに基づいて第1の命令を実行するステップであって、前記第1の命令は前記第1のテストコントローラに第1の動作を実行させる、実行するステップと、前記第2のテストコントローラが前記第1のオペコードに基づいて第2の命令を実行するステップであって、該第2の命令は前記第1の命令と異なり、該第2の命令は前記第2のテストコントローラに、前記第1の動作と異なる第2の動作を実行させる、実行するステップとを含むことを要旨とする。

【0026】

請求項17に記載の発明は、請求項16に記載の方法において、前記構成するステップは、前記第1の集積回路を前記テストモードにするために該第1の集積回路に提供されるテスト・イネーブル信号をアサートすることと、前記第2の集積回路を前記テストモードにするために、前記第1の集積回路を、前記テスト・イネーブル信号を前記第2の集積回路に伝達するように構成することとを含む、ことを要旨とする。

【0027】

請求項18に記載の発明は、請求項16に記載の方法において、前記構成するステップは、前記第1の集積回路の二重目的相互接続の第1のセットを前記第1の集積回路の第1のスレーブポートから結合解除するとともに、該第1の集積回路の二重目的相互接続の該第1のセットを前記第1のテストコントローラに結合するために、前記第1の集積回路に提供されるテスト・イネーブル信号をアサートすることを含む、ことを要旨とする。

【0028】

請求項19に記載の発明は、請求項18に記載の方法において、二重目的相互接続の前記第1のセットを前記第1のテストコントローラから結合解除するとともに、二重目的相互接続の該第1のセットを前記第1のスレーブポートに結合するために、前記第1の集積回路に提供される前記テスト・イネーブル信号をディアサートすることをさらに含む、ことを要旨とする。

【0029】

請求項20に記載の発明は、請求項16に記載の方法において、前記第1の命令または前記第2の命令のうちの一方はBYPASS命令であり、該第1の命令および該第2の命令のうちの他方は非BYPASS命令である、ことを要旨とする。

【0030】

請求項21に記載の発明は、請求項16に記載の方法において、第2のオペコードを、前記第2のテストコントローラに関連付けられる前記第2の命令レジスタにクロッキングするステップであって、前記第2のオペコードは前記第1のオペコードと異なる、クロッキングするステップと、前記第2のテストコントローラが前記第2のオペコードに基づいて前記第1の命令を実行するステップとをさらに含む、ことを要旨とする。

【図面の簡単な説明】

【0031】

【図1】従来技術による、JTAGテスト能力を有する複数の相互接続されたICの簡略化された回路図。

【図2】本発明の主題の一実施形態が実装されることができる例示のシステムの簡略化されたブロック図。

【図3】例示の実施形態による、統合テスト回路を有するICの簡略化されたブロック図。

【図4】例示の実施形態による、統合テスト回路を有するマルチICシステムの簡略化されたブロック図。

【図5】例示の実施形態による、マルチICシステムをテストするための方法のフローチャート。

【発明を実施するための形態】

【0032】

実施形態は、複数のIC(例えば、複数のコントローラ)上の補助的テスト回路が、外部回路への直接JTAG接続を有しない(例えば、外部JTAGピンがない)内部ICを完全にテスト可能にすることができるシステム(例えば、SiP)を含む。加えて、実施形態は、外部パッケージピンおよびIC間ルーティングを低減するために、JTAG相互接続が、入力スレーブポートおよび出力マスタポートによって多重化される構成を含む。本発明の主題の実施形態は、SiP、システム・オン・チップ(SoC)、および、回路基板を通じて相互接続される別個にパッケージされるICを含むシステムのような、さまざまなマルチICシステムのいずれかとともに使用されることができる。本明細書においてSiPの特定の例が説明されるが、当該例は限定であるようには意図されていないこと、および、当該例はさまざまな実施形態の理解を高めるために提供されることを理解されたい。

【0033】

本明細書において使用される場合、「ピン」という用語は、パッケージの外部の回路とパッケージの内部の回路との間の導電性接続を意味する。「ピン」は、ピン、パッド、バンプ、ボール、および任意の他の導電性接続を含むように解釈されるべきである。「相互接続」という用語は、特定のICに対する入力(I)導体、特定のICに対する出力(O)導体、または特定のICに対して二重I/O目的を果たす導体を意味する。本明細書においてより詳細に説明されるように、いくつかの事例において、相互接続はパッケージピンと直接結合されてもよく、他の事例においては、相互接続は別のICの相互接続と結合されてもよい。

【0034】

図2は、本発明の主題の一実施形態が実装されることができる例示のシステム200の簡略化されたブロック図を示す。より詳細には、システム200は、(6自由度の測定値を提供する)三次元空間内にあるデバイスの動き(例えば、変位および回転)を検知するための、およびさらにデバイスの地球上のロケーションを追跡するためのデバイス内に組み込まれることができるSiPである。

【0035】

システム200は、複数のコントローラIC210,212(本明細書においては「コントローラ」と称される)と、複数のトランスデューサ220,221,222とを含む。より具体的には、マスタコントローラ210は、磁気トランスデューサ220および加速度計トランスデューサ221とインタフェースするために使用され、スレーブコントローラ212はレート・ジャイロ・トランスデューサ222とインタフェースするために使用される。磁気トランスデューサ220は、地球の磁場の強度を示す信号を生成するように構成され、その情報はナビゲーション関連およびロケーション関連の用途に使用されることができる。加速度計トランスデューサ221およびレート・ジャイロ・トランスデューサ222は、信号(例えば、加速度および角度変化率を示す)を生成し、これは、デバイスの直線運動および向きが求められることを可能にする。この情報は、とりわけ、表示デバイス上で情報を表示するのに使用する向き(例えば、縦方向または横方向)の決定を含む、さまざまな目的に対して有用であり得る。

【0036】

マスタコントローラ210およびスレーブコントローラ212の両方は、機能モード、JTAGテストモード、または別の種類のテストモードにおいて構成されることができる。上記で示されているように、機能モードにおいて構成される場合、マスタコントローラ210は、磁気トランスデューサ220および加速度計トランスデューサ221とインタフェースするために使用され、スレーブコントローラ212はレート・ジャイロ・トランスデューサ222とインタフェースするために使用される。JTAGテストモードにおいて構成される場合、マスタコントローラ210およびスレーブコントローラ212は、JTAG準拠テストをサポートするように設計される。

【0037】

図示されるように、スレーブコントローラ212の上流にあるマスタコントローラ210は、システムのI/Oピンのさまざまなものに直接接続され、一方でスレーブコントローラ212はシステムI/Oピンには直接接続されない。図示されている実施形態において、マスタコントローラ210はピン230,232,234,および236に接続されているものとして示されている。ピン230は、マスタコントローラ210に対する1つまたは複数のアナログ入力を表し、これは、例えば、1つまたは複数の遠隔アナログセンサから発する場合がある。ピン232はシリアルポートを表し、これは、1つまたは複数の他の外部デバイス(例えば、図示されていない他のセンサ)に接続されることができる。このシリアルポートは、例えば、他の外部デバイスをマスタリングするマスタコントローラ210をサポートするマスタ/スレーブ・シリアル・ポートに対応することができる。シリアルポートがI2C(集積回路間)ポートである一実施形態において、例えば、ピン232は実際には2つ以上のピンを含むことができる。代替的には、シリアルポートがSPI(シリアル周辺機器インタフェース)である一実施形態において、ピン232は実際には4つ以上のピンを含むことができる。いくつかのデバイスは、SPIまたはI2Cポートを実装するためのオプションを有してもよい(例えば、ポートは二重モードI2C/SPIポートであってもよい)。他の実施形態においては、他のシリアルまたはパラレル・ポート・プロトコルも実装されてもよい。

【0038】

一実施形態において、マスタコントローラ210は、機能モードおよびJTAGテストモードの両方において使用されることができる複数の「二重目的」ピン234にも接続される。より詳細には、マスタコントローラ210が機能モードにおいて構成される場合、ピン234は外部スレーブポート(例えば、SPI、I2C、または他のインタフェース)に対応し、これは外部プロセッサ(例えば、外部アプリケーションプロセッサ)との相互接続性を提供することができる。マスタコントローラ210がJTAGテストモードにおいて構成される場合、ピン234は外部JTAGポートに対応する。後により詳細に説明されるように、マスタコントローラのスレーブポートおよびタップコントローラ(いずれも図示されていない)は、ピン234の二重目的機能をイネーブルするために多重化される。同様に、マスタコントローラ210およびスレーブコントローラ212の両方が「二重目的」相互接続を含む。後により詳細に説明されるように、マスタコントローラ210の二重目的相互接続は二重目的ピン234に結合され、スレーブコントローラ210の二重目的接続はマスタコントローラ210の対応するバイパス相互接続に結合される。基本的に、マスタコントローラ210およびスレーブコントローラ212の二重目的接続は、コントローラが機能モードにあるかまたはJTAGテストモードにあるかに応じて、スレーブポートまたはJTAGポートに対応する。

【0039】

一実施形態によれば、マスタコントローラ210は外部テスト・イネーブル(TE)ピン236にも結合され、これは、マスタコントローラ210およびスレーブコントローラ212を機能モードまたはJTAGテストモードのいずれかにおいて構成するために使用される。一実施形態において、TEピン236上で信号がアサートされない場合、マスタコントローラ210およびスレーブコントローラ212は機能モードにあり、二重目的ピン234は外部スレーブポート(例えば、SPIまたはI2Cインタフェース)に対応する。逆に、TEピン236上で信号がアサートされ、その信号がマスタコントローラ210からスレーブコントローラ212へ伝達される場合、マスタコントローラ210およびスレーブコントローラ212の両方はJTAGテストモードにあり、二重目的ピン234は外部JTAGポートに対応する。より具体的には、JTAGテストモードにおいて、ピン234はTDI(テスト・データ・イン)、TMS(テストモード状態)、TCK(クロック)、およびTDO(テスト・データ・アウト)ピンに対応する。JTAGピンはTRST(テスト・リセット)ピン(図示せず)も含むことができる。

【0040】

一度JTAGテストモードになると、マスタコントローラ210またはスレーブコントローラ212のいずれかは、BYPASS命令をマスタコントローラ210またはスレーブコントローラ212のいずれかのTAPコントローラ命令レジスタ(図示せず)にクロッキングすることによって、「TDI−TDOバイパスモード」において構成されることができる。TDI−TDOバイパスモードにおいて、TDI相互接続上でクロッキングされるデータは、TDI−TDOバイパスレジスタを通じてTDO相互接続へ通過する。マスタコントローラ210上でJTAGテストを実行するために、スレーブコントローラ212はさまざまな時点においてTDI−TDOバイパスモードにおいて構成されることができ、ただし、TDI−TDOバイパスモードにおける構成はすべてのJTAGテストに対して必要とされるものではない。同様に、スレーブコントローラ212上でJTAGテストを実行するために、マスタコントローラ210はさまざまな時点においてTDI−TDOバイパスモードにおいて構成されることができる。マスタコントローラ210がTDI−TDOバイパスモードにある場合、マスタコントローラ210は外部TDI、TMS、TCK、およびTEピン234,236上に存在する信号を、スレーブコントローラ212の対応するJTAG相互接続まで通過させ、スレーブコントローラのTDO相互接続上に存在する信号を外部TDOピン234まで通過させる。

【0041】

図示されていないが、システム200は、追加の周辺機器、メモリなども含むことができる。加えて、システム200は、本発明の主題の実施形態が組み込まれることができるシステムの単なる一例を表すことは理解されたい。他の実施形態においては、システムは3つ以上のコントローラ、コントローラ以外のICを含んでもよく、かつ/またはコントローラもしくはICの各々は異なる種類のトランスデューサ、ポートもしくは他の回路とインタフェースしてもよい。一実施形態による、JTAGテスト能力を有するICのより一般的な説明がここで与えられる。

【0042】

より具体的には、図3は、例示の実施形態による、統合テスト回路300を含むIC(例えば、コントローラまたは他のIC)の簡略化されたブロック図を示す。テスト回路300に加えて、ICは、マスタポート310(例えば、SPIまたはI2Cポート)、スレーブポート312(例えば、SPIまたはI2Cポート)、および中央処理装置(CPU)314も含む。他の実施形態においては、本明細書に記載されるもののようなテスト回路は、FPGA(フィールド・プログラマブル・ゲート・アレイ)、ASIC(特定用途向け集積回路)、および他の種類のICをテストするのに使用されてもよい。図示されていないが、ICは、CPU314とインタフェースする複数の信号(I/O)相互接続、1つまたは複数の電源相互接続、および1つまたは複数の接地相互接続も含む。加えて、ICは、テスト回路300を使用して実行される動作によって影響を受け得る状態を有する他のハードウェア、および、テストパターンをCPU314または他のハードウェアに供給するのに使用されることができる1つまたは複数のスキャンチェーン(図示せず)を含んでもよい。

【0043】

テスト回路300はJTAGポートを通じてアクセスされ、これは、複数のJTAG相互接続を含む。JTAG相互接続は、TDI相互接続340と、TMS相互接続341と、TCK相互接続342と、TDO相互接続343とを含む。JTAG相互接続はTRST(テスト・リセット)相互接続(図示せず)も含むことができる。下記により詳細に説明されるように、JTAG相互接続340〜343は二重目的であり、すなわち、それらはICが機能モードにおいて構成される場合スレーブポート312に対する相互接続としても機能することができる。しかしながら、簡便にするために、図3は相互接続340〜343(および対応する相互接続350〜353、後述)を、それらのJTAG指定によって指定する。

【0044】

ICのテスト回路300は、複数のシフトレジスタ、TAPコントローラ320、テストサブシステム(SS)322、マルチプレクサ324,325,326,327,328、およびさまざまな他のロジックを含み、それらの機能は下記により詳細に説明される。シフトレジスタは例えば、命令レジスタ(IR)330および複数のテスト・データ・レジスタ(TDR)332を含むことができる。

【0045】

IR330は、TDI相互接続340からマルチプレクサ324およびTAPコントローラ320を介して信号を受け取る。IR330はシフトレジスタであり、これは、TAPコントローラ320による実行のために現在の命令を保持することができる。基本的に、IR330の内容は、TAPコントローラ320が、TDI相互接続340を介して受け取る信号をどのように処理するかを決定するために使用される。多くの事例において、IR330は、TDI相互接続340からの入力信号をいずれのTDR332に渡すべきかを定義する命令を含む。IR330は例えば、4〜7ビット幅の間であることができる。ただし、IR330はさまざまな実施形態においてより狭いかまたはより広くてもよい。

【0046】

TDR332は、(介在するマルチプレクサ324およびTAPコントローラ320によって)TDI相互接続340と、(介在するマルチプレクサ326を用いて)TDO相互接続343との間に並列接続され、それによって、TAPコントローラ320が適切な状態にある(例えば、Shift_DR状態にある)ときに、TCK相互接続342上のクロック信号の各立ち上がりエッジの後に選択されたTDR332がデータをTDO相互接続343に向かって1段階シフトさせることになる。TDR332のサイズは固定であってもよいし、可変であってもよい。例えば、TDR332のサイズは、とりわけ、現在IR330内にある命令(または値)の関数であってもよい。

【0047】

TDR332は、後述されるような、バウンダリ・スキャン・シフト・レジスタ(BSR)(バウンダリ・スキャン・チェーンまたはEXTESTレジスタとも称される)、TDI−TDOバイパスレジスタ、オプションの識別レジスタ、および、ICの機能に影響を与えるさまざまな他のレジスタを含むことができる。さまざまな実施形態において、実装される場合もあり、されない場合もあるBSRは、ICの周辺を取り巻く専用パス内に接続される複数のバウンダリ・スキャン・セルから成り、BSRは、データをICのI/Oピンに、またI/Oピンから移動させるのに使用される。より詳細には、バウンダリ・スキャン・セルは、各信号相互接続(またはピン)と内部ロジックとの間に接続されることができる。BSRの内容は、BSDL(バウンダリスキャン記述言語)ファイルを使用して記述されることができる。ICがTDI−TDOバイパスモードにある場合、TDI−TDOバイパスレジスタ(例えば、シングル・ビット・レジスタ)は、データをTDI相互接続340からTDO相互接続343へ渡すのに使用される。識別レジスタ(例えば、32ビットのIDCODEレジスタ)は、ICのための識別コードを記憶するのに使用されることができる。識別コードは例えば、製造者コード、製造者によって割り当てられる部品番号、および部品バージョンコード(または改訂番号)を含むフォーマットを有することができる。IDCODEレジスタ内の情報は、ICが対応するBSDLファイルにリンクされることを可能にすることができる。同様に、JTAGテストに関連付けられるさまざまな制御ビットがTDR332内で指定されることができる。例えば、一実施形態において実装される或るTDR制御ビットが、本明細書において「JTAG通過」制御ビットと称され、これは、ICがJTAG通過モードにあるか否かを制御する。ICがJTAG通過モードにない(例えば、JTAG通過制御ビットがセットされている)場合、ICは、ICのTDO相互接続において提供されるべきTDO信号を生成する。逆に、ICがJTAG通過モードにある(例えば、JTAG通過制御ビットがクリアされている)場合、ICは下流のICからTDO信号を受け取り、当該TDO信号を下流のICからICのTDO相互接続に渡す。換言すれば、JTAG通過ビットの状態が、最上流のICが外部TDO相互接続343を駆動するか、または下流のICが駆動するかを決定することができる。

【0048】

タップコントローラ320はIR330およびTDR332にアクセスすることができ、(例えば、IEEE標準1149.1において定義されるような)JTAGステートマシーンを実装し、ここで、TMS相互接続341上のクロッキング変更に基づいて状態遷移が起こる。例えば、JTAGステートマシンは、(例えば、Shift_IR状態における)IR330への命令のシフトに関連付けられる1つの状態、および、(例えば、Shift_DR状態における)TDR332を通じてのデータのシフトに関連付けられる別の状態を有することになる。命令がIR330にシフトされると、TAPコントローラ320は、その命令を実行することができる。より詳細に後述されるように、さまざまな命令オペコードがTAPコントローラ320のために定義され、オペコードの命令への事前定義のマッピングに従って、IR330にシフトされるオペコードを復合する命令復号ロジック(図示せず)を含む。より詳細に後述されるように、TAPコントローラ320の復号ロジックは、システムの他のTAPコントローラの復号ロジックとは異なる様式で、オペコードを命令にマッピングする。TAPコントローラ320は、テストサブシステム322ともインタフェースすることができ、当該サブシステムは、さまざまなテストモード(例えば、RAM BIST(ビルトイン・セルフテスト)、スキャン(例えば、バッテリスキャン、内部スキャン)、専門アナログ・テスト・モードなど)に対する追加の制御を提供する。

【0049】

すでに述べたように、ICは機能モードまたはJTAGテストモードにおかれることができる。一実施形態によれば、テスト・イネーブル(TE)相互接続344上で提供される信号は、ICが機能モードにあるかまたはJTAGテストモードにあるかを制御し、マルチプレクサ324〜326の動作にも影響を与える。より詳細には、信号がTE相互接続344上でアサートされる場合、ICはJTAGテストモードにあり、より詳細に後述されるように、マルチプレクサ324〜326の各々はJTAGテストに関連する信号を渡す。逆に、信号がTE相互接続344上でアサートされない場合、ICは機能モードにあり、マルチプレクサ324〜326の各々は機能モードに関連する信号を渡す。当業者であれば、代替の実施形態において、TE相互接続344上で信号がアサートされた場合にICが機能モードにあってもよく、TE相互接続344上で信号がアサートされなかった場合にJTAGテストモードにあってもよいことを理解しよう。しかしながら、簡便にするために、下記説明は、信号がTE相互接続344上でアサートされる場合にICがJTAGテストモードにある実施形態に対応する。下記により詳細に説明されるように、マルチプレクサ326,327は、さまざまな時点においてICをJTAG通過モードにおくように制御可能である。JTAG通過モードにおいて、マルチプレクサ326,327は、下流のICから(TDO−R(TDO逆)相互接続353を介して)受け取るTDO信号をICのTDO相互接続343に向けて通過させるように構成される。従って、マルチプレクサ326,327は本明細書において「TDOマルチプレクサ」と称される場合がある。TDOマルチプレクサ326の動作は、上記のように主にTE相互接続344上で提供される信号によって制御され、TDOマルチプレクサ327の動作は、TE−F相互接続354上で提供されるテスト・イネーブル転送(TE−F)信号の状態によって制御される。すでに述べたように、かつより詳細に後述されるように、一実施形態において、TE−F信号の状態は、TDR332内のJTAG通過制御ビットによって影響を受ける。

【0050】

基本的に、マルチプレクサ324〜327は、相互接続340〜343,350〜353の二重目的機能を提供し、ICを通じてのJTAGおよび他の信号の転送を促進する回路を備える。上記で述べたように、マルチプレクサ324〜327の動作は、TE相互接続344上に存在する信号、およびTDR332内のJTAG通過制御ビットの状態によって影響を受ける。より具体的には、TE相互接続344上の信号が機能動作モードに対応し(例えば、信号がアサートされない)、JTAG通過制御ビットがセットまたはクリアされる場合、マルチプレクサ324〜326は、二重目的相互接続340〜343,350〜353を、CPU314と接続されるシリアルポート(例えば、I2CまたはSPIポート)に対する相互接続に対応させる。より具体的には、機能モードにおいて、マルチプレクサ324は、TDI、TMS、およびTCK相互接続340〜342からの信号をスレーブポート312に渡し、マルチプレクサ325は、マスタポート310からの信号をTDI−F(TDI転送)、TMS−F(TMS転送)、およびTCK−F(TCK転送)相互接続350,351,352に渡す。すでに述べたように、マスタポート310はSPIポートであり得る。このような実施形態では、機能モードにおいて、マルチプレクサ327はマスタポート310からの(例えば、SPI MISO(マスタ入力/スレーブ出力)信号に対応する)信号をTDO−R相互接続353に渡すことができる。同様に、スレーブポート312がSPIポートである場合、マルチプレクサ326はスレーブポート312からの(例えば、SPI MISO信号に対応する)信号をTDO相互接続343に渡すことができる。

【0051】

逆に、JTAGテストモードにおいて(例えば、TE相互接続344上で信号がアサートされる場合)、マルチプレクサ324〜326は、二重目的相互接続340〜343,350〜352を、JTAG相互接続と対応させる。より具体的には、マルチプレクサ324はTDI相互接続340からの信号を、TAPコントローラ320に渡し、当該TAPコントローラは、信号を(TAPコントローラ320の状態に応じて)IR330またはTDR332のいずれかにシフトさせ、マルチプレクサ324はさらにTMSおよびTCK相互接続341,342からの信号を、タップコントローラ320に渡す。加えて、マルチプレクサ325は、TDI、TMS、およびTCK相互接続340〜342からの信号を、TDI−F、TMS−F、およびTCK−F相互接続350〜352に渡す。JTAG通過制御ビットがリセット/クリアされ、TE−F信号がアサートされる(すなわち、ICがJTAG通過モードにある)場合、TDO−R相互接続353上に存在する信号は、マルチプレクサ327を介してマルチプレクサ326まで通過させられ、マルチプレクサ326は、マルチプレクサ327からの信号をTDO相互接続343まで通過させる。そうではない場合、ICはJTAG通過モードになく(例えば、JTAG通過制御ビットがセットされる)、マルチプレクサ326は、TDR332のうちの1つからのデータをTDO相互接続343に渡す。JTAG通過モードにおいて、TDI/TMS/TCKインタフェース340〜342とTDI−F/TMS−F/TCK−Fインタフェース350〜352との間で転送されている信号はクロッキングされていない。同様に、TDO−Rインタフェース353とTDOインタフェース343との間で転送されている信号もクロッキングされていない。

【0052】

一実施形態において、TE信号は、ANDロジック360およびTE−F(テスト・イネーブル転送)相互接続354を介して下流のデバイス(例えば、下流のIC)に渡されることができる。より詳細には、ANDロジック360はTE相互接続344上に存在する信号およびTE通過イネーブル信号の両方を受け取る。TE信号およびTDR332内のJTAG通過制御ビットの状態に基づいて生成されることができるTE通過イネーブル信号は、ICが、TE信号が下流のデバイスまで通過することを許可またはブロックしているか否かを示す。TE相互接続344上で信号がアサートされ、かつTE通過イネーブル信号がアサートされる(例えば、TDR332内の指定されるビットがリセット/クリアされ、ICがJTAG通過モードにある)場合、ANDロジック360はTE−F相互接続354上でTE−F信号をアサートする。TE−F相互接続354は、次いで、下流のIC(図示せず)のTE相互接続と結合されることができる。

【0053】

TE−F相互接続354と同様に、かつ図4とともにより詳細に説明されるように、TDI−F、TMS−F、およびTCK−F相互接続350〜352は、下流のICの対応するTDI、TMS、およびTCK相互接続に結合されることができる。加えて、TDO−R相互接続353は、下流のICの対応するTDO相互接続に結合されることができる。上記で述べたように、TDOマルチプレクサ327の動作はTE−F信号の状態によって制御される。従って、一実施形態において、TDOマルチプレクサ327の動作は、JTAG通過制御ビットの状態および対応するTE通過イネーブル信号によって影響を受ける。TE−F信号がアサートされる場合、TDOマルチプレクサ327は、TDO−R相互接続353上に存在する信号を、TDOマルチプレクサ326まで通過させる(当該TDOマルチプレクサは、次いで、信号をTDO相互接続343まで通過させることができる)。

【0054】

一実施形態によれば、テスト回路300は、ICおよび任意の下流のICの協調リセットをサポートする回路も含む。下記の記載は、システムがアクティブ・ロー・リセットをサポートしていることを想定しており、ただし、システムは代替的にアクティブ・ハイ・リセットをサポートしてもよいことを当業者であれば理解しよう。一実施形態によれば、リセット回路は、TE相互接続344上で信号がアサートされる場合、リセットは外部リセット信号(例えば、外部テスト機器または上流のICからの、RESETB相互接続364上に存在するリセット信号)によって制御され、他のシステムリセット(例えば、パワー・オン・リセットまたはCPU314からのリセット)は無関係であるように構成される。

【0055】

一実施形態において、リセット回路はANDロジック359、ORロジック361、およびANDロジック362を含む。ANDロジック359、ORロジック361、およびANDロジック362は、リセット条件に関連するさまざまな信号を受け取る。ANDロジック359に入力される信号は例えば、POR_B(ローでアサートされるパワー・オン・リセット)信号、CPU314からの(ローでアサートされる)リセット信号を含むことができる。ANDロジック359に入力される両方の信号がハイである場合、ANDロジック359の出力はハイであり、信号のいずれかがローである場合、ANDロジック359の出力はローである。POR_B信号はデバイスが電源投入されている間はローであり、それ以外ではハイであり得、CPUリセット信号はCPU314が下流のICをリセットしようとしている場合はローであり得る。ORロジック361に入力される信号は、ANDロジック359からの出力信号および(例えば、TE相互接続344からの)TE信号を含む。ORロジック361に入力されるいずれかの信号がハイである場合、ORロジック361の出力はハイであり、すべての信号がローである場合、ORロジック361の出力はローである。TE信号は機能モードにおいてはローであり、それゆえ、機能モードにおけるリセットは、RESETB相互接続364上に存在する外部リセット信号に加えてPOR_BおよびCPUリセット信号によって左右される。逆に、JTAGテストモードにおいてはTE信号はハイであり、それゆえ、ICがJTAGテストモードにあるときはORロジック361の出力は常にハイである。換言すれば、TE信号がハイである場合、外部リセット364のみがINT_RESETBおよびRESETB_Fをアサートすることができる。

【0056】

ORロジック361からの出力はANDロジック362に提供され、当該ANDロジックは外部リセット相互接続364からの信号も受け取る。ORロジック361からの信号がローであるか、または外部リセット相互接続364からの信号がローである場合、ANDロジック362は内部リセット(INT_RESETB)およびRESETB−F(リセット転送)相互接続366上の信号をアサートする。代替的に、ORロジック361からの信号および外部リセット相互接続364からの信号の両方がハイである場合、ANDロジック362はRESETB−F相互接続366上の信号をアサートしない。上記の記載が示すように、JTAGテストモードにおいて(すなわち、ORロジック361からの出力がハイである場合)、RESETB−F相互接続366上の信号状態は、外部リセット相互接続364上の信号によって左右される。RESETB−F相互接続366は、下流のICの対応するリセット相互接続に結合されることができる。このようにして、リセット信号はICによって下流のICに提供されることができる。

【0057】

さまざまな実施形態において、ICが機能モードにある場合、システムクロック(CLK)は、オンチップ発振器(OSC)370、オンチップ位相ロックループ、オンチップデジタル位相ロックループ、他のオンチップクロック源、または外部(オフチップ)クロック源によって提供されることができる。逆に、ICがJTAGテストモードにある場合、システムクロックはEXTCLK(外部クロック)相互接続374を介して外部クロック源(例えば、外部テスト機器によって生成されるクロック)によって提供される。一実施形態によれば、ICはマルチプレクサ328も含み、当該マルチプレクサはTE相互接続344上でアサートされる信号に基づいてシステムクロックを選択的に供給し、クロック信号をCLK−F(クロック転送)相互接続376に渡す。TE相互接続344上で信号がアサートされない(例えば、ICが機能モードにある)場合、マルチプレクサ328はシステムクロックとしてOSC370(または別のクロック源)からのクロック信号を使用し、そのクロック信号をCLK−F相互接続376に渡す。逆に、TE相互接続344上で信号がアサートされる(例えば、ICがJTAGテストモードにある)場合、マルチプレクサ328はシステムクロックとしてEXTCLK相互接続374上で提供されるクロック信号を使用し、そのクロック信号をCLK−F相互接続376に渡す。CLK−F相互接続376は、下流のICの対応するEXTCLK相互接続に結合されることができる。このようにして、クロック信号はICによって下流のICに提供されることができる。

【0058】

上記で述べたように、機能モードおよびJTAGテストモードに関連付けられるさまざまな信号が複数のIC間で渡されることを可能にするように、複数のICがともに結合されることができる。図4は、例示の実施形態による、統合テスト回路を有するマルチICシステム400(例えば、システム・イン・パッケージ(SiP))の簡略化されたブロック図を示す。より詳細には、マルチICシステム400は3つのIC402,403,404を含むように示されている。システム400は3つのIC402〜404および関連テスト回路412〜414を含むように示されているが、実施形態は、2つのみのICおよびテスト回路を含むシステム、または4つ以上のICおよびテスト回路を含むシステムにおいて実装されてもよい。加えて、IC402〜404の各々は図3のICとともに示されたもののような構成を有することができるが、IC402〜404は簡略化された形式で示されている(例えば、簡潔かつ明瞭にするために、図3のCPU、リセット回路、クロック回路、およびさまざまな他の回路は図4においては図示されていない)。

【0059】

システム400は二重目的ピン440,441,442,443を通じて外部回路(例えば、他のシステム回路または外部テスト機器)と通信することができ、IC402〜404の各々は、対応する相互接続を介して二重目的ピン440〜443と、または互いにインタフェースすることができる。ピン440〜443および相互接続はすでに記載されたように、それらが、IC402〜404がJTAGテストモードにある場合はJTAGピン/相互接続として、および、代替的にIC402〜404が機能モードにおいて構成される場合はIC402〜404のスレーブポート412〜414との接続を提供するピン/相互接続としての両方で機能することができるという点で、二重目的である。加えて、システム400はTEピン444を含み、これは、IC402上のTE相互接続(図示せず)と接続する。図3とともにすでに説明されたように、TEピン444上でアサートされるTE信号は、IC402によって、ANDロジック460を使用して下流のIC403のTE相互接続(図示せず)に渡されることができ、TE信号は、IC403によって、ANDロジック461を使用して下流のIC404のTE相互接続445にも渡されることができる。

【0060】

IC402〜404は直列に接続され(例えば、ともにデイジーチェーン接続され)、それによって、各ICは他のICから下流または上流となる。本明細書において使用される場合、直列構成にある2つのIC間の関係に関連する「上流のIC」という用語は、それが接続されている他のICよりも外部ピン(例えば、ピン440〜443)により近く結合されている直列対のICを意味する。同様に、「下流のIC」という用語は、それが接続されている他のICよりも外部JTAGピンにより近くに結合されていない直列対のICを意味する。従って、図4において、IC402はIC403および404の上流にあり、IC403はIC402の下流にあるとともにIC404の上流にあり、IC404はIC402および403の下流にある。

【0061】

IC402〜404の各々はテスト回路405,406,407およびスレーブポート412,413,414(例えば、SPIまたはI2Cポート)を含む。IC402および403の各々は、マスタポート415、416(例えば、SPIまたはI2Cポート)も含む。IC404は最下流のICであるため、IC404は任意選択的にマスタポート417(およびマルチプレクサ429,432)を含んでもよいが、これは必須ではない。簡潔にするために図示されていないが、IC402〜404の各々は、マスタおよびスレーブポート412〜417間に結合されるCPU(または他の回路)、CPU(または他の回路)とインタフェースする信号(I/O)相互接続、1つまたは複数のスキャンチェーン、1つまたは複数の電力相互接続、1つまたは複数の接地相互接続なども含んでもよい。

【0062】

IC402が機能モードにある(例えば、TE信号がアサートされない)場合、二重目的ピン440〜442上に存在する信号はIC402の二重目的相互接続(図示せず)およびマルチプレクサ424を介してスレーブポート412に提供され、これらの信号はIC402のCPU(または他の回路)によって作用されることができる。加えて、IC402のCPU(または他の回路)は、マスタポート415、マルチプレクサ427、およびIC402,403間のさまざまな相互接続を介して下流のIC403のマルチプレクサ425およびスレーブポート413に信号を提供することができる。同様に、IC403のCPU(または他の回路)は、マスタポート416、マルチプレクサ428、およびIC403,404間のさまざまな相互接続を介してさらに下流のIC404のマルチプレクサ426およびスレーブポート414に信号を提供することができる。従って、システム400のさまざまなIC402〜404はマスタ−スレーブ構成において動作することができ、ここで、IC402はICF403のマスタであることができ、IC403はIC404のマスタであることができる。

【0063】

図3のICと同様に、テスト回路405〜407はJTAGポートを通じてアクセスされ、その各々がすでに説明されたような、複数のJTAG相互接続(例えば、TDI、TMS、TCK、およびTDO相互接続)を含む。最上流のIC(例えば、IC402)のJTAG相互接続は二重目的ピン440〜443に結合される。より詳細には、二重目的ピン440〜443は、TDIピン440、TMSピン441、TCKピン442、およびTDOピン443を含み、これらは上述のように、IC402〜404が機能モードにある場合はシリアル・ポート・ピンの役割も担う。二重目的ピン440〜443および対応する相互接続は、TRSTピンおよび相互接続(図示せず)も含む。

【0064】

各テスト回路405〜407は、図3とともにすでに説明されたように、複数のシフトレジスタ、TAPコントローラ420,421,422、テストサブシステム(図示せず)、マルチプレクサ424,425,426,427,428,429(任意選択)、430,431,432(任意選択)、433,434,435、およびさまざまな他のロジックを含む。加えて、システム400は、IC402のTE相互接続(図示せず)と接続されるTEピン444も含むことができ、各テスト回路405〜407は、TEピン上に存在する信号が、下流のICに渡されてマルチプレクサ424〜435の機能を制御することを可能にする回路を含むことができる。すでに説明されたように、TE信号がTEピン上でアサートされ、かつTAPコントローラ420、421が他の様態でTE信号の下流のICへの伝搬を妨げていない場合、IC402〜404の各々はTE信号を受け取る。

【0065】

TE信号がアサートされる(例えば、IC402〜404がJTAGテストモードにある)場合、マルチプレクサ424〜426は、それらのJTAGインタフェースに存在する入力JTAG信号(すなわち、TDI、TMS、TCK)を、TAPコントローラ420〜422およびそれらの関連データおよび命令レジスタに渡し、マルチプレクサ427,428は入力JTAG信号を対応する下流のICに渡す。例えば、IC402のマルチプレクサ427は、入力JTAG信号(すなわち、二重目的ピン440〜442およびIC402の二重目的相互接続を介して受け取られる信号)をIC403に渡し、IC403のマルチプレクサ428は、入力JTAG信号(すなわち、IC402,403の二重目的相互接続を介して受け取られる信号)をIC404に渡す。従って、JTAGテストモードにおいて、各IC402〜404は同じJTAG信号を受け取る。

【0066】

一度にただ1つのIC402〜404のTAPコントローラ420〜422が、TDOピン443上で出力されるべき信号を生成し、テスト回路405〜407は、TDOピン443上に存在する信号が、単一のTAPコントローラ420〜422によって生成される信号に対応するように構成される。特定のTAPコントローラ420〜422から出力信号(すなわち、TDO信号)を受け取るために、すべての上流のICがリセット/クリアされてJTAG通過モードになる。すでに述べたように、ICをリセット/クリアしてJTAG通過モードにするために、ICのTE相互接続上で信号がアサートされ、上流のICのTDR内のJTAG通過制御ビットがリセット/クリアされる。この構成において、すでに説明されたように、ICは、そのTDO−R相互接続(例えば、図3のTDO−R相互接続353)上で受け取られる信号をそのTDO相互接続(例えば、図3のTDO相互接続343)に渡すことになる。例えば、IC404のTAPコントローラ422から出力信号を受け取るために、IC402,403はJTAG通過モードにおいて構成される。従って、マルチプレクサ435は、TAPコントローラ422から受け取られるテスト出力信号をIC404のTDO相互接続(図示せず)に渡し、当該信号は、IC403のTDO−R相互接続(図示せず)およびマルチプレクサ431において受け取られる。そして、IC403のマルチプレクサ431および434は、(TAPコントローラ422からの)テスト出力信号をIC403のTDO相互接続(図示せず)に渡し、当該信号は、IC402のTDO−R相互接続(図示せず)およびマルチプレクサ430において受け取られる。そして、IC402のマルチプレクサ430および433は、(TAPコントローラ422からの)テスト出力信号をIC402のTDO相互接続(図示せず)に渡し、当該相互接続は、TDOピン443に接続されている。このようにして、IC402、403がJTAG通過モードにある場合、IC404のTAPコントローラ422からのテスト出力信号は、IC402,403を通じてシステム400のTDOピン443に渡されることができる。

【0067】

同様に、IC403のTAPコントローラ421から出力信号を受け取るために、IC402はJTAG通過モードにおいて構成される。従って、マルチプレクサ434は、TAPコントローラ421から受け取られるテスト出力信号をIC403のTDO相互接続(図示せず)に渡し、当該信号は、IC402のTDO−R相互接続(図示せず)およびマルチプレクサ430において受け取られる。次いで、IC402のマルチプレクサ430および433は、(TAPコントローラ421からの)テスト出力信号をIC402のTDO相互接続(図示せず)に渡し、当該相互接続は、TDOピン443に接続されている。このようにして、IC402が適切に構成される場合、IC403のTAPコントローラ421からのテスト出力信号は、IC402を通じてシステム400のTDOピン443に渡されることができる。

【0068】

すでに述べたように、TAPコントローラに関連付けられる命令レジスタ(例えば、図3のIR330)は現在の命令を保持する。IRの内容およびテスト・データ・レジスタ(例えば、図3のTDR332)内のさまざまなビットの状態が、TAPコントローラが受信信号をどのように処理または転送するかに影響を与える。より具体的には、各TAPコントローラ420〜422は、オペコードの命令への事前定義のマッピングに従って、TAPコントローラのIRにシフトされるオペコードを復号する命令復号ロジック(図示せず)を含む。上記の記載が示すように、JTAG通過モードにおいて、各IC402〜404は同じJTAG入力信号(すなわち、TDI、TMS、TCK)を受け取る。従って、各IC402〜404は同一のオペコードにおいてその対応するIRにクロッキングする。複数のICがTDOピン443上で出力テストデータを生成しようとするシナリオを回避するために、一実施形態において、複数のICおよびTAPコントローラを含むシステム(例えば、システム400)内の各TAPコントローラは、他のTAPコントローラとは異なる事前定義のオペコード−命令マッピング(例えば、各TAP内にハードコード化されるマッピング)に基づいて操作される。より具体的には、各TAPコントローラの復号ロジックは、オペコードのセットを、他のTAPコントローラが同じオペコードのセットを復合するのとは異なる様式で復号する。換言すれば、第1のTAPコントローラがオペコードを、第1のTAPコントローラに第1の動作を実行させる第1の命令にマッピングするのに対して、第2のTAPコントローラは同じオペコードを、第2のTAPコントローラに第1の動作と異なる第2の動作を実行させる、第2の異なる命令にマッピングする。

【0069】

マルチICシステムの各ICのための異なるオペコード−命令マッピングの実施態様をさらに説明するために図4のシステム400を使用することになる。説明を容易にするために、図4のシステム400はIC402,403のみを含むものと想定し、ここでIC402がマスタコントローラであり、IC403がスレーブコントローラである。一実施形態によれば、IC402のTAPコントローラ復号ロジックは、第1の事前定義のオペコード−命令マッピングに基づいて動作することになり、IC403のTAPコントローラ復号ロジックが第1のものと異なる第2の事前定義のオペコード−命令マッピングに基づいて動作することになる。一実施形態において、オペコード−命令マッピングは、TAPコントローラが異なる命令を同時に実行することができるように定義される。しかしながら、一度にただ1つのICのTAPコントローラが信号をTDO相互接続443上に駆動する命令を実行することができるという点で、オペコード−命令マッピングは両立できる。一実施形態において、オペコード−命令マッピングは、他の各TAPコントローラがBYPASS命令または何らかの他の命令(すなわち、BYPASS命令以外の命令を含む「非BYPASS」命令)のいずれかを実行するようなものである。

【0070】

例えば、一実施形態において、オペコード−命令マッピングは、任意の所与のオペコードがシステムのただ1つのICに対する非BYPASS命令のみにマッピングし、同じオペコードがシステムのすべての他のICに対するBYPASS命令にマッピングするように、事前定義されることができる。従って、マスタコントローラIC402は事前定義のマッピングに基づいて動作し、当該マッピングにおいて第1のグループのオペコードは非BYPASS命令に対応し、第2の相互排他的なグループのオペコードはBYPASS命令に対応する。加えて、スレーブコントローラIC403は異なる事前定義のマッピングに基づいて動作し、当該マッピングにおいて、同じ第1のグループのオペコードがBYPASS命令に対応し、同じ第2のグループのオペコードのうちの少なくともいくらかは非BYPASS命令に対応し得る(ただし、それらは非BYPASS命令に対応する必要はなく、同様にBYPASS命令に対応し得る)。

【0071】

下記の表1は、3つのICおよび対応するTAPコントローラ(例えば、図4のTAP420〜422)を含むシステムに対するJTAG命令セットの一例である。オペコードから命令への具体的なマッピングが表1に列挙されているが、表1の命令セットとは異なる命令セットが定義されてもよく、かつ/またはさまざまな命令が異なるオペコードにマッピングされてもよいことは理解されたい。

【0072】

【表1】

表1が示すように、一実施形態において、1つのコントローラに対して非BYPASS命令にマッピングするオペコードは、他のコントローラに対してはBYPASS命令にマッピングする。例えば、オペコード1,4,7,10,13,16、および19がコントローラ1に対して非BYPASS命令にマッピングしている場合、これらのオペコードはコントローラ2および3に対してはBYPASS命令にマッピングする。同様に、オペコード2,5,8,11,14,17、および20がコントローラ2に対して非BYPASS命令にマッピングしている場合、これらのオペコードはコントローラ1および3に対してはBYPASS命令にマッピングする、などである。従って、同じオペコードが各コントローラ(例えば、すべてのIC402〜404)に同時にクロッキングされる場合があるけれども、ただ1つのIC(例えば、そのテストデータ出力がTDOピン443上で望まれるIC)がオペコードを非BYPASS命令にマッピングすることができる。例えば、表1を参照すると、オペコード13がコントローラ1〜3にクロッキングされた後、オペコード13がマッピングする命令(すなわち、IDCODE命令)のコントローラ1による実行は、コントローラ1に、TDO相互接続443上でIDCODEレジスタからTAP識別子を送出させることになる。しかしながら、オペコード13がマッピングする命令(すなわち、BYPASS命令)のコントローラ2および3による実行は、コントローラ2および3にBYPASSに入らせるかまたは留まらせ、コントローラ2および3はTDO相互接続443上でデータを送出しない。表1および上記の説明も示すように、異なる複数のオペコードが異なる複数のコントローラに同じ命令を実行させる。例えば、オペコード1,2、および3(すなわち、「異なる複数のオペコード」)が、コントローラ1,2、および3(すなわち、「異なる複数のコントローラ」)に、SAMPLE/PRELOAD命令(すなわち、「同じ命令」)を実行させる。TDR制御ビットが(TE信号とともに)最上流のICが外部TDOピン(例えば、図4のTDOピン443)を駆動するか、または下流のICが外部TDOピンを駆動するかを決定することを想起されたい。換言すれば、IC(例えば、図4のIC402,403,404)内に存在するTAPコントローラオペコード(例えば、上記表1のオペコード)はどのICが外部TDOピンを駆動するかを決定しない。

【0073】

一実施形態によれば、BYPASS命令は実行されると、TDI−TDOバイパスレジスタ(例えば、図3のTDR332のうちの1つ)を選択し、当該レジスタは、ICをTDI−TDOバイパスモードにおくか、または当該モードに留める。SAMPLE命令は、実行されると、バウンダリ・スキャン・レジスタ(例えば、図3のTDR332のうちの1つ)を選択し、それによって、相互接続値がバウンダリ・スキャン・レジスタ内に読み出されることができ、PRELOAD命令は、実行されると、EXTESTの前に相互接続出力値を読み出す。表1とともに表されている実施形態において、SAMPLEおよびPRELOAD命令は組み合わされている(すなわち、SAMPLE/PRELOAD命令として)。EXTEST命令は、実行されると、基板レベルの挙動を精査するための相互接続の使用のように、外部テストのために使用されることができる。EXTEST命令は代替的に、コア上で動作してもよい(例えば、コアへのデータの書き込み)。INTEST命令は、実行されると、オンチップ挙動を精査するための相互接続の使用のように、内部テストのために使用されることができる。INTEST命令は代替的に、コア上で動作してもよい(例えば、コアからのデータの読み出し)。CLAMP命令は、実行されると、事前ロードされている値を使用して出力相互接続を駆動する。IDCODE命令は、実行されると、IDCODEレジスタ(例えば、図3のTDR332のうちの1つ)を選択し、それによって、TAP識別子がIDCODEレジスタから読み出されることができる。SELECT TDR(テスト・データ・レジスタ)命令は、実行されると、結果として、値が実質的にクロックインまたはクロックアウトされ得る、設計特有のテスト・データ・レジスタ(例えば、図3のTDR332のうちの1つ)が選択されることになる。TDRは、設計特有のテストサポート機構(例えば、セルフテスト、スキャンパスなど)に対するアクセスの提供のような、さまざまな目的に使用されることができる。

【0074】

表1に列挙されている命令の他に、例えば、HIGHZ(すべての相互接続の出力を無効にする)、RUNBIST(ICをセルフテストモードにおく)、SCAN_N(他のバウンダリスキャン動作を適用する信号に影響を与えるスキャンパス選択レジスタを構成する)、USERCODE(ユーザ定義のコードを返す)、他のSELECT_TDR命令(例えば、追加のTDRを選択する)、および他の製造者またはユーザ定義の命令を含む、他の命令も同じく、または代替的に定義されることができる。

【0075】

図5は、例示の実施形態による、マルチICシステム(例えば、図4のシステム400)をテストするための方法のフローチャートを示す。本方法は、上記のように直列に相互接続される任意の数のICを有するマルチICシステムをテストするのに使用されることができる。本方法の説明を容易にするために、図4のさまざまな要素が参照される場合がある。しかしながら、本方法は、3つよりも少ないかまたは多いICを含むシステムにおいて使用されてもよいことは理解されたい。任意の数のICを有するシステムに適用するために図5のフローチャートを一般化する利益のために、列内のICの数を示すためにフローチャートにおいて固定数Nが使用され、さまざまなステップを適用する列内の特定のICを示すためにパラメータnが使用される。ICの数が分かっているシステムにおいては、パラメータnのセッティングおよび更新に関連付けられるステップは本方法から除外されてもよく、代わりにフローチャートはより直線的に流れるように改変されることができることは理解されたい。図5に示される一連のステップに対するこれらのおよび他の改変は、本発明の主題の範囲内に含まれることが意図されている。

【0076】

本方法は、列内のすべてのICのTAPコントローラ(例えば、図4のTAPコントローラ420〜422)をリセットすることによって開始することができる。TAPがTRSTピンおよび対応する相互接続を含む場合、TAPコントローラは、ロジック0がTRSTピンに印加されると、リセット状態(例えば、IEEE標準1149.1において定義されているテスト−ロジック−リセット(Test−Logic−Reset)コントローラ状態)に非同期的にリセットされることができる。そうではなく、TRSTピン上の信号を使用してリセットが実行されない場合、リセットプロセスは基本的に、この時点において任意の状態にあり得る各TAPコントローラがリセット状態に遷移されることが確実になる回数だけ各TAPコントローラをクロッキングすることを含む。このような実施形態において、リセットは下記に記載されるブロック502〜508を含むことができる。より詳細には、リセットプロセスは例えば、ブロック502において、少なくとも列内の最上流のIC(例えば、図4のIC402)に提供される外部ICリセット信号をアサートすることによって開始することができる。例えば、これは、外部テスト機器が、列内の最上流のICのリセット相互接続(例えば、図3のRESETB相互接続364)に信号を提供することを含むことができる。

【0077】

TRSTピンが利用可能でありリセットの実行に使用されるか否かにかかわらず実行されるブロック504において、テスト・イネーブル(TE)信号がアサートされる。一実施形態によれば、これは、外部テスト機器が列内の最上流のIC(例えば、図4のIC402)のTE相互接続と結合される外部TEピン(例えば、図4のTEピン444)に提供される信号(すなわち、TE信号)をアサートすることを含むことができる。すでに説明されたように、ICのリセット回路は、TE相互接続(例えば、図3のTE相互接続344)上で信号がアサートされる場合、リセットが外部リセット信号(例えば、図3のRESETB相互接続364上のリセット信号)によって制御されるように構成される。従って、TE信号および外部リセット信号が正しい状態にある場合、ICのリセット回路(例えば、図3のORロジック361およびANDロジック362)は内部リセット(INT_RESETB)信号を生成し、さらに、リセット信号を(例えば、RESETB−F相互接続366、およびRESETB−F相互接続366と次の下流のICのRESETB相互接続364との間のIC間導体を介して)次の下流のICのRESETB相互接続に伝達する。加えて、すでに説明されたように、TE信号のアサートは、(例えば、図3のマルチプレクサ324〜326を介して)TE信号を受け取る任意のICの二重目的相互接続を、JTAG相互接続として構成する。従って、TE信号がICのためにアサートされると、JTAG相互接続を介してICのTAPコントローラ(例えば、図3のTAPコントローラ320)およびレジスタ(例えば、図3のIR330およびTDR332)との通信が可能となる。TE信号のアサートおよびIC内のJTAG通過制御ビット(例えば、図3のTDR332内のビット)の状態は、さまざまな入力JTAG相互接続(例えば、図3のTDI相互接続340、TMS相互接続341、TCK相互接続342、およびTDO−R353)上に存在する信号の、対応する出力JTAG相互接続(例えば、図3のTDI−F相互接続350、TMS−F相互接続351、TCK−F相互接続352、およびTDO343)への転送も提供する。

【0078】

最初、最上流のIC(例えば、図4のIC402)は、TE信号を次の下流のIC(例えば、図4のIC403)に伝達するように構成されなくてもよい。すでに述べたように、各上流のIC(例えば、図4のIC402、403)は、TE信号が下流のICに対してブロックまたは伝達されることを可能にする回路(例えば、図3、4のANDロジック360、460、461)を含むことができる。すでに述べたように、TE信号を下流のICに伝達するために、上流のICはTE通過イネーブル信号をアサートすることができる。TE通過イネーブル信号は、TDR(例えば、図3のTDR332のうちの1つ)内の指定されるビットの状態に基づいて生成されることができ、それゆえ、TE通過信号をアサートするために、およびTE信号を下流のICに伝達するために、適切な値が上流のICの指定されるビット(例えば、図3のTDR332のうちの1つの指定されるビット)にクロッキングされるべきである。

【0079】

各ICのTAPコントローラをリセットするために、およびTE信号を各下流のICに伝達するために、ブロック506において、適切な信号が(例えば、外部テスト機器によって)外部TAPインタフェースに提供される。換言すれば、TAPインタフェースは、列内のすべてのICのTAPコントローラをリセットするために使用される。一実施形態によれば、これは、すべてのICのTAPコントローラにリセット状態(例えば、IEEE標準1149.1において定義されているテスト−ロジック−リセットコントローラ状態)に入らせるための、および、値を上流のICの適切なTDRビットにリセットしてICにアサートされたTE信号を下流のICに伝達させるための回数だけTMSピン(例えば、図4のピン441)をクロッキングすることを含むことができる。このプロセスは連続して、最上流のIC(例えば、図4のIC402)における開始に進む。換言すれば、最上流のICのTAPコントローラ(例えば、図4のTAPコントローラ420)は、TAPコントローラをリセット状態においてセットするように、および、TDRビットを、TE通過イネーブル信号がアサートされる状態にリセットするようにクロッキングされる。この時点において、TE信号が次の下流のIC(例えば、図4のIC403)に提供され、そのICのTAPコントローラ(例えば、図4のTAPコントローラ421)がリセットされることができ、そのIC内のTE通過イネーブル信号がリセットされてTE信号が次の下流のIC(例えば、図4のIC404)に伝達されることができる。このプロセスは、列内のすべてのICのTAPコントローラがリセットされるまで繰り返される。

【0080】

ブロック506においてTAPコントローラリセットが完了すると、ブロック508において外部ICリセットがディアサートされる。この時点において、すべての上流のIC(例えば、図4のIC402,403)は、テスト・イネーブル信号を次の下流のデバイスに(例えば、次の下流のデバイスのTE相互接続344に接続される、図3のTE−F相互接続354を介して)提供する構成にある。列内のすべてのICはリセットされてアサートされたTE信号を受け取っており、従って列内のすべてのICはテスト動作モードにあり、それらの二重目的相互接続はそれらのそれぞれのTAPコントローラとの通信を提供する。次に説明されることになるブロック510〜526は、(例えば、図4のTDOピン443上の)出力テストデータを提供する特定のICを選択するための、および、システム上でJTAGテストを実行するための方法の実施形態を示す。

【0081】

ブロック510において、パラメータnはNの値に初期化され、これは列内のICの数に等しい。上記で述べたように、値Nおよびnは図5のフローチャートを、任意の数のICを有するシステムに適用可能であるように一般化するために使用され、実際には値Nおよびnは、実際のシステムにおいて方法を実施する際には使用されない場合がある。それにも関わらず、値Nおよびnは本方法の実施形態の一般性および説明を促進するために使用される。下記で明確にされるように、パラメータnの現在の値は、未だにテストモードにある(すなわち、そのTE相互接続上でアサートされたテスト・イネーブル信号を受け取っている)最下流のデバイスに対応する。

【0082】

リセット後、ブロック512によって示されるように、TAPインタフェースは列内のn個のICにとって利用可能である。ブロック512を含むループの1回目の反復の間、nの値はNに等しいため、TAPインタフェースは列内のすべてのICにとって(例えば、図4のIC401〜403にとって)利用可能である。

【0083】

ブロック514において、列内のn個のIC上で所望のTAPトランザクションが実行される。ブロック514を含むループの最初の反復の間、列内のすべてのIC上で所望のTAPトランザクションが実行される。基本的に、各タップトランザクションは、命令オペコード(例えば、上記表1に列挙されているオペコード)の、各TAPコントローラに関連付けられる命令レジスタ(例えば、図3のIR330)へのクロッキング、および、場合によっては(例えば、オペコードがSELECT_TDR命令に対応する場合)、データのTDR(例えば、図3のTDR332のうちの1つ)へのクロッキングを含む。すでに詳細に述べたように、各TAPコントローラは、特定のオペコードがただ1つのICに対する非BYPASS命令にマッピングし、同じオペコードがすべての他のICに対するBYPASS命令にマッピングする、異なるオペコード−命令マッピングによって左右され得る。従って、任意の所与の時点において、ただ1つのICが外部TDO相互接続を駆動しており、他のICはブロックされて外部TDO相互接続を駆動することができない。

【0084】

本方法の前または後に実行されてもよいブロック516において、(例えば、図4のTEピン444において提供される)TE信号がディアサートされているか否かの判定を行うことができる。そうである場合、JTAGテストは完了しており(または終了しており)、ブロック528において、所望の場合にはシリアルポート(例えば、I2CポートもしくはSPIポート)または任意の他のインタフェースとともに使用されるために二重目的相互接続が再び利用可能となる。

【0085】

一実施形態によれば、JTAGテストが継続している(例えば、すべてのICに対してTE信号がアサートされたままである)間、所望の場合、列のICは、最下流のIC(例えば、図4のIC404)から開始して上流へと動作して、順次JTAGテストモードを中止されることができる。基本的に、下流のICのJTAGテストモードを中止することは、そのICに対するTE信号の提供を中断することによって達成されることができる。ブロック518〜526は、ICがこのようにしてJTAGテストモードを中止されることができる実施形態に対応し、またはブロック518および520の場合は、1つまたは複数の下流のICがJTAGテストモードを中止された場合にはTAPコントローラは、JTAGインタフェースをすべてのTAPコントローラに対して再び利用可能とするためにリセットされることができる。

【0086】

再びブロック516を参照して、TE信号がディアサートされていない場合、ブロック518においてTAPリセットが起こったか否かがさらに判定されることができ、これは他の実施形態においては本方法の前または後に実行されてもよい。TAPリセットは、例えば、各TAPコントローラがリセット状態(例えば、IEEE標準1149.1において定義されているテスト−ロジック−リセットコントローラ状態)に遷移し戻るだけの回数分(例えば、最大5×N回)TMSピン(例えば、図4のTMSピン441)上の信号をローでクロッキングすることによって、外部テスト機器によって実施されることができる。TAPリセットが起こると、パラメータnは列内のICの数Nにリセットされ、図示されるように方法は反復する。TRSTピンが提供される代替の実施形態において、ロジック0がTRSTピンに印加されると、TAPコントローラはリセット状態に非同期的にリセットされることができる。いずれにせよ、TAPリセットが起こると、ブロック512においてすべてのICに対してTAPインタフェースが利用可能となり、図示されるように方法は反復する。

【0087】

TAPリセットが起こらなかった場合、ブロック522において、列内の最上流のIC(例えば、図4のIC402)が、未だにJTAGテストモード(すなわち、n = 1である場合)にある唯一のICであるか否かが判定されることができる。そうである場合、本方法は図示されるように反復する。そうでない場合、上流のICがTE信号の列内の次の下流のICへの伝達を中断する可能性が存在し、従って下流のICをJTAGテストモードから実効的に遷移させる(すなわち、JTAGインタフェースを下流のICにとって利用不可能にする)。一実施形態において、かつすでに述べたように、上流のICは内部において、TE通過イネーブル信号を生成することができ、これは、TDR(例えば、図3のTDR332のうちの1つ)内の指定されるビットの状態に基づいて生成されることができる。TE通過イネーブル信号がアサートされると、アサートされたTE信号は、(例えば、図3のTE−F相互接続354を介して)次の下流のICのTE相互接続に提供される。逆に、TE通過イネーブル信号がディアサートされると、TE信号は次の下流のICのTE相互接続に提供されず、この次の下流のICはもはやJTAGテストモードにはない。

【0088】

ブロック524において、ICn−1(すなわち、依然としてJTAGテストモードにある最下流から2番目のIC)内のTE通過イネーブル信号がディアサートされているか否かが判定されることができる。例えば、n = Nのときのブロック524の1回目の反復の間、ICn−1(例えば、図4のIC403)内のTE通過イネーブル信号がディアサートされているか否かが判定されることができる。特定の実施形態において、この判定は、ICn−1(例えば、図4のIC403)内のTE通過イネーブル信号に関連付けられるTDRビットがICn(例えば、依然としてJTAGテストモードにある最下流のICであろう、IC404)へのTE入力を選択解除するように設定されているか否かを判定することを含む。そうである場合、最下流のIC(例えば、図4のIC404)はもはやJTAGモードになく、ブロック526においてパラメータnが1デクリメントされ、これはTAPインタフェースがそのICにとってはもはや利用可能でないことを示す。本方法は、その後図示されるように反復することができ、ここで、TAPインタフェースは列内の1つ少ないICにとって(例えば、IC402および403のみにとって)利用可能である。本方法は、(例えば、上記ブロック516において判定されるように)TE信号がディアサートされるか、またはJTAGテストを終了させる他の何らかの事象が発生するまで反復し続ける。