メモリの管理方法及びフラッシュメモリデバイス

【課題】予備ブロックの急激な減少を防止して、フラッシュメモリデバイスの安全な運用を図るためのメモリの管理方法及び該方法を使用するフラッシュメモリデバイスの提供。

【解決手段】

フラッシュメモリデバイスにエラー訂正回路とブロック管理手段とを設け、予備ブロックの残数が前記ブロック管理手段に設定された閾値に至った後は、bitエラーがbadブロック閾値未満であったデータをエラー訂正してホストに送出するとともに、該エラーを生起したブロックをリフレッシュする。リフレッシュは当該ブロックのエラー訂正されたデータを含む全データを空きブロック若しくは予備ブロックに書き写し、元のブロックのデータを消去することにより実行する。又は、空きブロック若しくは予備ブロックに書き写してから元のブロックに書き戻すことにより実行する。

【解決手段】

フラッシュメモリデバイスにエラー訂正回路とブロック管理手段とを設け、予備ブロックの残数が前記ブロック管理手段に設定された閾値に至った後は、bitエラーがbadブロック閾値未満であったデータをエラー訂正してホストに送出するとともに、該エラーを生起したブロックをリフレッシュする。リフレッシュは当該ブロックのエラー訂正されたデータを含む全データを空きブロック若しくは予備ブロックに書き写し、元のブロックのデータを消去することにより実行する。又は、空きブロック若しくは予備ブロックに書き写してから元のブロックに書き戻すことにより実行する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリ、取り分けフラッシュメモリの管理方法及び該方法を使用するフラッシュメモリデバイスに関する。

【背景技術】

【0002】

EEPROM(電気的にデータの消去及び書き換えが可能な不揮発性メモリ)の一種としてフラッシュメモリが知られている。取り分けNAND型フラッシュメモリは、安価で且つデータの書き込み時間が短いため、ハードディスクの置き換えや、各種コンテンツを格納する用途で使用されている。NAND型フラッシュメモリは、その構造上、製造段階で不良ブロックが存在する。また、書き込み回数や読み出し回数の増大によってもデータ化けが生じ、不良ブロックとなる。このため、不良ブロックが生じる度に、予め設けられた代替ブロック(予備ブロック)に置き換えられる。予備ブロックがゼロになると、もはやメモリは使用不可能となる。そのため、本出願人は、斯かる事態が発生する前にメモリを新品と交換させるべく、管理者に通知する記憶装置について提案している。

【0003】

しかしながら、メモリが専らコンテンツを読み出す用途に使用されているような場合、リードディスターブエラーによりユーザデータ領域の多数のブロックが一度に不良ブロックになり、予備ブロックが急激に減少する可能性がある。斯かる場合には、管理者に通知しても、新品との交換に間に合わない事態も想定される。

【特許文献1】特開2000−181805号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ここにおいて、本発明が解決すべき課題は、予備ブロックの急激な減少を防止して、フラッシュメモリデバイスの安全な運用を図るためのメモリの管理方法及び該方法を使用するフラッシュメモリデバイスの提供にある。その他の課題は、明細書、図面、特に特許請求の範囲から自ずと明らかとなろう。

【課題を解決するための手段】

【0005】

上記課題解決のため、本発明が特許請求範囲において、上位概念から下位概念に亙り列挙する新規な特徴的構成を採用することにより、上記課題を解決する。即ち、本発明方法の第1の特徴は、ユーザデータ領域の他に予備ブロックと少なくとも一つ空きブロックを有するメモリと、エラー訂正回路とブロック管理手段とブロック管理テーブルとを有するコントローラと、前記ユーザデータ領域から読み出されたデータをホストに送出する前に一旦保存するRAMとを備えたフラッシュメモリデバイスのメモリ管理方法であって、エラー訂正回路によって検出されたbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)未満であったとき、前記予備ブロックの残数がブロック管理手段に設定された閾値に至った後は、当該エラーを起こしたデータを含むブロックのデータをリフレッシュすることを特徴とするメモリの管理方法の構成採用にある。

【0006】

(作用)

通常、メモリから読み出したデータにbitエラー(ECCエラー)があった場合は、エラー訂正回路でエラー訂正したデータをホストに送出する。またbitエラー数が当該ブロックをbadブロックと看做す閾値(「badブロック閾値」という)以上であった場合は、そのブロックを予備ブロックに置き換えている(「badブロック処理」という)。しかし、頻繁にデータの読み出しが行われるようなシステムでは、ブロックに対する読み出し回数が増えるに従い、リードディスターブエラーが発生する。このため、本発明では、予備ブロック残数が閾値に至った後は、badブロック閾値未満のbitエラーを生起したブロックにリフレッシュを実行する。リフレッシュを実行することにより、事後発生するbitエラー数を軽減することが期待でき、予備ブロック残数が閾値に至った後は予備ブロックの減少速度を遅くすることができるため、メモリの寿命延命を図ることができる。

【0007】

この場合、リフレッシュを、エラーを生起したブロックの全データをエラー訂正してから空きブロック若しくは予備ブロックに書き写すことにより実行すれば、潜在的なエラーを含めてそのブロックの全てのエラーが訂正されるので、データの信頼性を高めることができる。

【0008】

また、本発明方法の第2の特徴は、フラッシュメモリデバイスに表示手段を設け、予備ブロックの残数が所定数に至った段階で該表示手段を駆動するメモリの管理方法の構成採用にある。

【0009】

(作用)

頻繁にデータの読み出しが行われるようなシステムにおいて、従来方法によれば、予備ブロックが急激に減少し、たとえ管理者に予備ブロックが残り少なくなったことを知らせても、新品との交換まで間に合わない事態も想定されるが、この構成によれば、管理者に通知した後、予備ブロックの減少速度を遅らせることができるので、斯かる事態を回避することができ、システムのより安全な運用を図ることができる。ここで“所定数”とは、予備ブロック残数閾値を複数設定した場合のいずれかである。

【発明を実施するための最良の形態】

【0010】

以下、本発明を実施するための最良の形態について図面を用いて説明するが、本発明は特許請求の範囲内において種々の形態を採ることができ、下記実施形態に限定されないことはいうまでもない。

【0011】

(システム基本構成)

図1は、本発明におけるフラッシュメモリデバイスのシステム基本構成図である。本発明は、NAND型フラッシュメモリ12(本明細書において、特に必要のない限り、単に“フラッシュメモリ”という)とフラッシュメモリ12にデータの書き込みや読み出しを実行するコントローラ11からなるフラッシュメモリデバイス2と、フラッシュメモリデバイス2にデータの書き込みや読み出しのコマンドを発行するホスト1を基本構成として有するシステムにおいて実行され得る。コントローラ11には、フラッシュメモリ12から読み出されたデータをホスト1に送出する前に一旦保存するためのRAM13と、フラッシュメモリ12の状態を表示する表示手段としてのLED(Light Emitting Diode)17が接続されている。RAM13はコントローラ11の内部に設けてもよい。フラッシュメモリデバイス2とホスト1は、例えばMPEG音楽プレーヤのように、所定の機器として一体に構成されていてもよいし、ホスト1がPCで構成され、フラッシュメモリデバイス2がPCとUSB接続される機器のように、別体で構成してもよい。近年では、ハードディスクの置き換えとして、SSD(Solid

State Drive)のように、複数のフラッシュメモリ12とコントローラ11とRAM13とが一体に構成され、PCとIDE接続される機器でもよい。

【0012】

図2は、フラッシュメモリ12のブロック構成図である。フラッシュメモリ12は、ユーザデータ領域、予備領域、管理領域を有する。ユーザデータ領域は、主記憶領域とも呼ばれる。ユーザデータ領域を構成する物理ブロックは、論理ブロックと一対一に対応する関係を有し、その関係は論理/物理ブロック管理テーブルで管理され、その対応関係が変わると、随時該テーブルで更新される。予備ブロック(予備領域を構成するブロック)は、ユーザデータ領域を構成する物理ブロックが不良ブロックとなったときに使用される代替ブロックである。また、フラッシュメモリ22には空きブロックが少なくとも一つ確保される。この空きブロックは、通常、ユーザデータ領域の物理ブロックにデータを上書きするときに使用されるブロックである。この場合空きブロックは、予備ブロック同様、論理ブロックと関連付けされない。

【0013】

本構成例では、物理ブロックは、Block0乃至Block8291の8292ブロックで構成され、その内Block0乃至Block8190がユーザデータ領域であり、Block8191が空きブロックであり、Block8192乃至Block8291が予備領域である。同図において、(valid)と記されたブロックがユーザデータ領域中の有効ブロックを表し、(empty)と記されたブロックが空きブロックを表し、(reserve)と記されたブロックが予備ブロックを表す。その他、不図示の管理領域を有する。

【0014】

コントローラ11は、ブロック管理手段16とブロック管理テーブル14を含む。ブロック管理手段16は、ユーザデータ領域の物理ブロック番号と論理ブロック番号との関係を論理/物理ブロック管理テーブルで随時管理する。また空きブロックの物理ブロック番号及び予備ブロックの物理ブロック番号を把握するため、それぞれ不図示の空きブロックテーブル、予備ブロックテーブルで管理する。本願では論理/物理ブロック管理テーブル、空きブロックテーブル、予備ブロックテーブルを総称して、ブロック管理テーブル14というものとする。ブロック管理テーブル14はフラッシュメモリ12内に設けてもよい。なお、詳細は後述するが、本願のリフレッシュは、この空きブロック若しくは予備ブロックのいずれかを使用して実行する。

【0015】

ブロック管理手段16は、さらにカウンター回路と、予備ブロックの残数の閾値を設定するための回路を有し、予備ブロックの残数と当該閾値とを比較判定する機能を有する。カウンター回路は予備ブロックの残数を計数するとともに、予備ブロックの残数を記憶する。ブロック管理手段16が、予備ブロック残数が予め設定されている所定の値以下であると判定すると、コントローラ11は表示手段を点灯させる。

【0016】

更に、コントローラ11はエラー訂正回路(ECC)15を含む。エラー訂正回路15は、コントローラ11がホスト1から書き込み命令を受けると、エラーデータを復元するためのエラーチェックコードを生成する。そして、ユーザデータにエラーチェックコードを付加して、フラッシュメモリ12の書き込み及び読み出しの単位であるセクター内の冗長領域に記憶する。ホストから読み出し命令を受けたときは、エラー訂正回路15はフラッシュメモリ12から読み出したユーザデータをエラーチェックコードによりチェックし、bitエラーが検出されると、該bitエラーを訂正してホスト1に送出する。エラー訂正回路15は、エラー訂正可能なbit数(能力値という)が設定されており、この能力値を超えるともはやエラー訂正が不可能となる。そこで本発明では、安全を図るため、この能力値よりも小さい値を閾値(「badブロック閾値」という)として設定し、該閾値以上のbitエラーのあったブロックを不良ブロックと看做して、以下に説明するbadブロック処理を実行する。

【0017】

まず、ホスト1からのデータ読み出しコマンドに対応して、bitエラーのあったデータはエラー訂正回路15により訂正してからRAM13を経由してホスト1に送出する。そしてbitエラーのあったブロックの全データをエラー訂正しながらRAM13に一時格納する。そして格納されたエラー訂正済のデータを予備ブロックにコピーし、ブロック管理テーブル14の一つである論理/物理ブロック管理テーブルを更新する。RAM13への格納及び予備ブロックへのコピーは、1ブロック分を一度に実行してもよいし、ページ単位で実行してもよい。これにより、予備ブロックであるコピー先のブロックをユーザデータ領域のブロックとし、不良ブロックをアドレスの対応付けのエントリーから外してホスト1からアクセス不可能にする。コントローラ11には、不図示のCPU並びに該CPUに実行させるためのプログラム(ファームウエア)が具備されており、エラー訂正回路15その他の処理を統括的に制御する。

【0018】

(メモリの管理方法)

以下、本発明のメモリの管理方法例を説明する。以下の例では、予備ブロック数を100ブロック、予備ブロック残数の閾値を50ブロックとし、エラー訂正回路15の能力値を6bit、不良ブロックと看做すbitエラー数の最小値(badブロック閾値)を4ビットとする。予備ブロック残数が前記閾値50以下となったとき、LEDが点灯する。以下、図7及び図8を用いて、ブロックの管理方法について説明する。尚、以下の説明は、ホスト1がデバイスから専らデータの読み出しを行う場合の例である。

【0019】

電源がONされシステムが駆動すると(ST1)、ブロック管理手段16は、該手段に設けられたカウンター回路に記憶された予備ブロックの残数と閾値とを比較判定する(ST2)。その結果、予備ブロックの残数が閾値(50ブロック)以下である場合、コントローラ11は表示手段であるLED17を点灯する(ST3)。

【0020】

次にホスト1からデータ読み出しコマンドがないか判断し(ST4)、YESであれば、フラッシュメモリ12の指定されたアドレスからデータを読み出してエラー訂正回路15によってエラーチェックを行い(ST5)、エラーがあるか判断する(ST6)。エラーがない場合は、フラッシュメモリ12に記憶されているユーザデータをそのままホスト1へ送出し(ST18)、読み出しを完了する。

【0021】

ST6において、エラーがあると判断されると、次にbitエラー数が6以下であるかの判断が行われる(ST7)。6を超える場合はエラー訂正回路15の能力値を超え、もはや訂正不可能であるため、ホスト1へエラーを返す(ST8)。6以下の場合は、更にbitエラー数が4未満であるかの判断が行われる(ST9)。4未満でない場合(4,5又は6)は、まずエラー訂正回路15によりエラーを訂正し(ST10)、訂正済みのデータをホスト1へ送出し(ST18)、読み出しを完了する。そしてエラーを生起したブロックの全データをエラー訂正して一旦RAM13に格納して予備ブロックに書き込み、badブロック処理を行なう(ST11)。なお、ST11において、ブロック管理手段16のカウンター回路は、badブロック処理が1回行われるごとに、予備ブロック残数を一つデクリメントする。

【0022】

デバイス使用開始直後は、不良ブロックが発生する確率が低く、予備ブロックを殆ど使用しないため、予備ブロック残数は100に近い値を示し、その後デバイスの使用回数が増加してくると、不良ブロックの代替が行われて予備ブロックが少なくなり、予備ブロック残数は50に近づく。

【0023】

ST9において、bitエラー数が4未満の場合は、ブロック管理手段16により予備ブロック残数が閾値50ブロックに至る前かどうか判断し(ST12)、YESであればエラー訂正回路15によりエラーを訂正して(ST15)、訂正済のデータをホスト1へ送出し(ST18)、読み出しを完了する(リフレッシュは行わない)。

【0024】

デバイス使用開始から時間が経過してくると、不良ブロックが発生する確率が高くなり、予備ブロック残数は50以下となり、更にデバイスを使用し続けると0となる。

【0025】

ST12において、予備ブロック残数が閾値50ブロックに至った後であると判断されると、まずLED点灯済みか判断し(ST13)、NOであれば、LEDを点灯し(ST14)フラッシュメモリデバイス2の交換時期が近いことを管理者に知らせる。そしてエラー訂正回路15によりエラーを訂正して(ST16)、訂正済のデータをホスト1へ送出し(ST18)、読み出しを完了する。そしてエラーのあったブロックのリフレッシュを行う(ST17)。以上の処理をマップ状に表したものが図6である。

【0026】

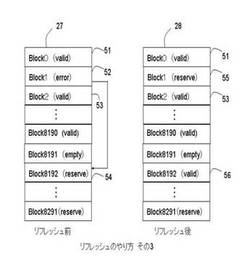

以下、リフレッシュの具体的やり方について説明するが、その前に図3乃至図5について説明する。図3、図4及び図5は、リフレッシュ前後のメモリの状態を表したものである。図3、図4及び図5は、それぞれリフレッシュの第1、第2 及び第3の例である。図3に示すメモリセルアレイ23、図4に示すメモリセルアレイ25、図5に示すメモリアレイセル27はリフレッシュ前の物理ブロックの状態を表す。図3に示すメモリセルアレイ24、図4に示すメモリセルアレイ26、図5におけるメモリアレイセル28はリフレッシュ後の物理ブロックの状態を表す。尚、いうまでもないが、メモリセルアレイ23乃至28は便宜上区別して表しているが、実質同一のものである。

【0027】

(リフレッシュの方法例1)

図8のST17におけるリフレッシュのやり方の第1の例について、図3を用いて説明する。今、メモリセルアレイ23に示すBlock1(error)32でbitエラーが発生したとする。ホスト1へデータ転送後、Block1(error)32の全データをエラー訂正回路15によりbitエラーを訂正してから、一旦、RAM13に格納し、その後、メモリセルアレイ23に示す空きブロックであるBlock8191(empty)33にコピーする。その後、Block1(error)32はその全データを消去し、空きブロック(empty)として空きブロック管理テーブル14を更新する。これと同時に、Block8191をメモリセルアレイ24に示すBlock8191(valid)36の状態にして、ユーザデータ領域中の有効ブロックとし、論理/物理ブロック管理テーブルを更新する。尚、ホスト1に対しては、前記RAM23に一旦保存しておいたエラー訂正済みのデータを送出すればよい。ホスト1へのデータの送出は、リフレッシュの前でも後でもよい。同時に行なってもよい。以下の方法例においても同様であることは言うまでもない。

【0028】

(リフレッシュの方法例2)

次に、リフレッシュのやり方の第2例について、図4を用いて説明する。今、メモリセルアレイ25に示すBlock1(error)42でbitエラーが発生したとする。ホスト1へデータ転送後、Block1(error)42の全データをエラー訂正回路15によりbitエラーを訂正してから、一旦、RAM13に格納し、Block1(error)42の全データを消去する。そして、元のBlock1(error)42に書き戻す。この例では、データを元のブロックに書き戻しているにすぎないため、ブロック管理テーブル14の更新を行う必要はない。

【0029】

(リフレッシュの方法例3)

リフレッシュのやり方の第3の例について、図5を用いて説明する。今、メモリセルアレイ27に示すBlock1(error)52でbitエラーが発生したとする。ホスト1へデータ転送後、Block1(error)52の全データをエラー訂正回路15によりbitエラーを訂正してから、一旦、RAM13に格納し、その後、メモリセルアレイ27に示す予備ブロックであるBlock8192(reserve)54にコピーする。これによりBlock8192はメモリセルアレイ28に示すように、有効ブロック56となり、論理/物理管理テーブルが更新される。また、Block1(error)52の全データは消去する。これによりBlock1はメモリセルアレイ28に示すように、予備ブロック(reserve)55となる。変更後の状態は予備ブロック管理テーブルに記録される。

【0030】

上記LED表示において、予備ブロック残数閾値を複数設け、各段階で異なる態様で表示するようにしてもよい(例えば、注意、警告、緊急の3段階を定義する)。また、フラッシュメモリ12の交換時期が近いことをLED表示によって管理者に通知する他、フラッシュメモリデバイス2のコントローラ11がその旨をホスト1に通知するのでもよい。このようにすれば、所謂S・M・A・R・T方式により、種々の態様でシステム管理をより容易に行うことができる。また上記実施例の他、予備ブロック残数が閾値に至った後に、bitエラー数が4、5のブロックをbadブロック処理せずに、リフレッシュして使いまわしてもよい。このようにすれば、さらにフラッシュメモリ12の延命を図ることができる。

【0031】

(発明の効果)

以上述べたように、本発明によれば、例えば専ら若しくは頻繁にデータの読み出しが実行されるようなシステムにおいて、予備ブロックの残数が閾値に至った後に、badブロック閾値未満のbitエラーが検出された場合に、該エラーの生起されたブロックをリフレッシュすることにより、リードディスターブエラーによるbitエラーの増加を防止し、予備ブロックの減少速度を低下させることができる。即ち、フラッシュメモリデバイスの寿命延命を図ることができる。特にリフレッシュ(他のブロックへのデータの書き写し)を、エラー訂正を伴って実行すると、システムの信頼性を一層高めることができる。また、本発明によれば、予備ブロックの残数状態を管理者が知った後の、新品との交換時間を延ばすことができ、システムのより安全な運用を図ることができる。

【図面の簡単な説明】

【0032】

【図1】本発明を実行するシステムの基本構成例である。

【図2】フラッシュメモリアレイの構成例である。

【図3】リフレッシュにおけるブロック管理テーブルの第1の例である。

【図4】リフレッシュにおけるブロック管理テーブルの第2の例である。

【図5】リフレッシュにおけるブロック管理テーブルの第3の例である。

【図6】本発明のメモリ管理方法例をマップ状に表したものである。

【図7】本発明のメモリ管理方法のフローチャート例である。

【図8】本発明のメモリ管理方法のフローチャート例(続き)である。

【符号の説明】

【0033】

1 ホスト

2 フラッシュメモリデバイス

11 コントローラ

12 フラッシュメモリ

13 RAM

14 ブロック管理テーブル

15 エラー訂正回路

16 ブロック管理手段

17 LED

【技術分野】

【0001】

本発明は、メモリ、取り分けフラッシュメモリの管理方法及び該方法を使用するフラッシュメモリデバイスに関する。

【背景技術】

【0002】

EEPROM(電気的にデータの消去及び書き換えが可能な不揮発性メモリ)の一種としてフラッシュメモリが知られている。取り分けNAND型フラッシュメモリは、安価で且つデータの書き込み時間が短いため、ハードディスクの置き換えや、各種コンテンツを格納する用途で使用されている。NAND型フラッシュメモリは、その構造上、製造段階で不良ブロックが存在する。また、書き込み回数や読み出し回数の増大によってもデータ化けが生じ、不良ブロックとなる。このため、不良ブロックが生じる度に、予め設けられた代替ブロック(予備ブロック)に置き換えられる。予備ブロックがゼロになると、もはやメモリは使用不可能となる。そのため、本出願人は、斯かる事態が発生する前にメモリを新品と交換させるべく、管理者に通知する記憶装置について提案している。

【0003】

しかしながら、メモリが専らコンテンツを読み出す用途に使用されているような場合、リードディスターブエラーによりユーザデータ領域の多数のブロックが一度に不良ブロックになり、予備ブロックが急激に減少する可能性がある。斯かる場合には、管理者に通知しても、新品との交換に間に合わない事態も想定される。

【特許文献1】特開2000−181805号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ここにおいて、本発明が解決すべき課題は、予備ブロックの急激な減少を防止して、フラッシュメモリデバイスの安全な運用を図るためのメモリの管理方法及び該方法を使用するフラッシュメモリデバイスの提供にある。その他の課題は、明細書、図面、特に特許請求の範囲から自ずと明らかとなろう。

【課題を解決するための手段】

【0005】

上記課題解決のため、本発明が特許請求範囲において、上位概念から下位概念に亙り列挙する新規な特徴的構成を採用することにより、上記課題を解決する。即ち、本発明方法の第1の特徴は、ユーザデータ領域の他に予備ブロックと少なくとも一つ空きブロックを有するメモリと、エラー訂正回路とブロック管理手段とブロック管理テーブルとを有するコントローラと、前記ユーザデータ領域から読み出されたデータをホストに送出する前に一旦保存するRAMとを備えたフラッシュメモリデバイスのメモリ管理方法であって、エラー訂正回路によって検出されたbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)未満であったとき、前記予備ブロックの残数がブロック管理手段に設定された閾値に至った後は、当該エラーを起こしたデータを含むブロックのデータをリフレッシュすることを特徴とするメモリの管理方法の構成採用にある。

【0006】

(作用)

通常、メモリから読み出したデータにbitエラー(ECCエラー)があった場合は、エラー訂正回路でエラー訂正したデータをホストに送出する。またbitエラー数が当該ブロックをbadブロックと看做す閾値(「badブロック閾値」という)以上であった場合は、そのブロックを予備ブロックに置き換えている(「badブロック処理」という)。しかし、頻繁にデータの読み出しが行われるようなシステムでは、ブロックに対する読み出し回数が増えるに従い、リードディスターブエラーが発生する。このため、本発明では、予備ブロック残数が閾値に至った後は、badブロック閾値未満のbitエラーを生起したブロックにリフレッシュを実行する。リフレッシュを実行することにより、事後発生するbitエラー数を軽減することが期待でき、予備ブロック残数が閾値に至った後は予備ブロックの減少速度を遅くすることができるため、メモリの寿命延命を図ることができる。

【0007】

この場合、リフレッシュを、エラーを生起したブロックの全データをエラー訂正してから空きブロック若しくは予備ブロックに書き写すことにより実行すれば、潜在的なエラーを含めてそのブロックの全てのエラーが訂正されるので、データの信頼性を高めることができる。

【0008】

また、本発明方法の第2の特徴は、フラッシュメモリデバイスに表示手段を設け、予備ブロックの残数が所定数に至った段階で該表示手段を駆動するメモリの管理方法の構成採用にある。

【0009】

(作用)

頻繁にデータの読み出しが行われるようなシステムにおいて、従来方法によれば、予備ブロックが急激に減少し、たとえ管理者に予備ブロックが残り少なくなったことを知らせても、新品との交換まで間に合わない事態も想定されるが、この構成によれば、管理者に通知した後、予備ブロックの減少速度を遅らせることができるので、斯かる事態を回避することができ、システムのより安全な運用を図ることができる。ここで“所定数”とは、予備ブロック残数閾値を複数設定した場合のいずれかである。

【発明を実施するための最良の形態】

【0010】

以下、本発明を実施するための最良の形態について図面を用いて説明するが、本発明は特許請求の範囲内において種々の形態を採ることができ、下記実施形態に限定されないことはいうまでもない。

【0011】

(システム基本構成)

図1は、本発明におけるフラッシュメモリデバイスのシステム基本構成図である。本発明は、NAND型フラッシュメモリ12(本明細書において、特に必要のない限り、単に“フラッシュメモリ”という)とフラッシュメモリ12にデータの書き込みや読み出しを実行するコントローラ11からなるフラッシュメモリデバイス2と、フラッシュメモリデバイス2にデータの書き込みや読み出しのコマンドを発行するホスト1を基本構成として有するシステムにおいて実行され得る。コントローラ11には、フラッシュメモリ12から読み出されたデータをホスト1に送出する前に一旦保存するためのRAM13と、フラッシュメモリ12の状態を表示する表示手段としてのLED(Light Emitting Diode)17が接続されている。RAM13はコントローラ11の内部に設けてもよい。フラッシュメモリデバイス2とホスト1は、例えばMPEG音楽プレーヤのように、所定の機器として一体に構成されていてもよいし、ホスト1がPCで構成され、フラッシュメモリデバイス2がPCとUSB接続される機器のように、別体で構成してもよい。近年では、ハードディスクの置き換えとして、SSD(Solid

State Drive)のように、複数のフラッシュメモリ12とコントローラ11とRAM13とが一体に構成され、PCとIDE接続される機器でもよい。

【0012】

図2は、フラッシュメモリ12のブロック構成図である。フラッシュメモリ12は、ユーザデータ領域、予備領域、管理領域を有する。ユーザデータ領域は、主記憶領域とも呼ばれる。ユーザデータ領域を構成する物理ブロックは、論理ブロックと一対一に対応する関係を有し、その関係は論理/物理ブロック管理テーブルで管理され、その対応関係が変わると、随時該テーブルで更新される。予備ブロック(予備領域を構成するブロック)は、ユーザデータ領域を構成する物理ブロックが不良ブロックとなったときに使用される代替ブロックである。また、フラッシュメモリ22には空きブロックが少なくとも一つ確保される。この空きブロックは、通常、ユーザデータ領域の物理ブロックにデータを上書きするときに使用されるブロックである。この場合空きブロックは、予備ブロック同様、論理ブロックと関連付けされない。

【0013】

本構成例では、物理ブロックは、Block0乃至Block8291の8292ブロックで構成され、その内Block0乃至Block8190がユーザデータ領域であり、Block8191が空きブロックであり、Block8192乃至Block8291が予備領域である。同図において、(valid)と記されたブロックがユーザデータ領域中の有効ブロックを表し、(empty)と記されたブロックが空きブロックを表し、(reserve)と記されたブロックが予備ブロックを表す。その他、不図示の管理領域を有する。

【0014】

コントローラ11は、ブロック管理手段16とブロック管理テーブル14を含む。ブロック管理手段16は、ユーザデータ領域の物理ブロック番号と論理ブロック番号との関係を論理/物理ブロック管理テーブルで随時管理する。また空きブロックの物理ブロック番号及び予備ブロックの物理ブロック番号を把握するため、それぞれ不図示の空きブロックテーブル、予備ブロックテーブルで管理する。本願では論理/物理ブロック管理テーブル、空きブロックテーブル、予備ブロックテーブルを総称して、ブロック管理テーブル14というものとする。ブロック管理テーブル14はフラッシュメモリ12内に設けてもよい。なお、詳細は後述するが、本願のリフレッシュは、この空きブロック若しくは予備ブロックのいずれかを使用して実行する。

【0015】

ブロック管理手段16は、さらにカウンター回路と、予備ブロックの残数の閾値を設定するための回路を有し、予備ブロックの残数と当該閾値とを比較判定する機能を有する。カウンター回路は予備ブロックの残数を計数するとともに、予備ブロックの残数を記憶する。ブロック管理手段16が、予備ブロック残数が予め設定されている所定の値以下であると判定すると、コントローラ11は表示手段を点灯させる。

【0016】

更に、コントローラ11はエラー訂正回路(ECC)15を含む。エラー訂正回路15は、コントローラ11がホスト1から書き込み命令を受けると、エラーデータを復元するためのエラーチェックコードを生成する。そして、ユーザデータにエラーチェックコードを付加して、フラッシュメモリ12の書き込み及び読み出しの単位であるセクター内の冗長領域に記憶する。ホストから読み出し命令を受けたときは、エラー訂正回路15はフラッシュメモリ12から読み出したユーザデータをエラーチェックコードによりチェックし、bitエラーが検出されると、該bitエラーを訂正してホスト1に送出する。エラー訂正回路15は、エラー訂正可能なbit数(能力値という)が設定されており、この能力値を超えるともはやエラー訂正が不可能となる。そこで本発明では、安全を図るため、この能力値よりも小さい値を閾値(「badブロック閾値」という)として設定し、該閾値以上のbitエラーのあったブロックを不良ブロックと看做して、以下に説明するbadブロック処理を実行する。

【0017】

まず、ホスト1からのデータ読み出しコマンドに対応して、bitエラーのあったデータはエラー訂正回路15により訂正してからRAM13を経由してホスト1に送出する。そしてbitエラーのあったブロックの全データをエラー訂正しながらRAM13に一時格納する。そして格納されたエラー訂正済のデータを予備ブロックにコピーし、ブロック管理テーブル14の一つである論理/物理ブロック管理テーブルを更新する。RAM13への格納及び予備ブロックへのコピーは、1ブロック分を一度に実行してもよいし、ページ単位で実行してもよい。これにより、予備ブロックであるコピー先のブロックをユーザデータ領域のブロックとし、不良ブロックをアドレスの対応付けのエントリーから外してホスト1からアクセス不可能にする。コントローラ11には、不図示のCPU並びに該CPUに実行させるためのプログラム(ファームウエア)が具備されており、エラー訂正回路15その他の処理を統括的に制御する。

【0018】

(メモリの管理方法)

以下、本発明のメモリの管理方法例を説明する。以下の例では、予備ブロック数を100ブロック、予備ブロック残数の閾値を50ブロックとし、エラー訂正回路15の能力値を6bit、不良ブロックと看做すbitエラー数の最小値(badブロック閾値)を4ビットとする。予備ブロック残数が前記閾値50以下となったとき、LEDが点灯する。以下、図7及び図8を用いて、ブロックの管理方法について説明する。尚、以下の説明は、ホスト1がデバイスから専らデータの読み出しを行う場合の例である。

【0019】

電源がONされシステムが駆動すると(ST1)、ブロック管理手段16は、該手段に設けられたカウンター回路に記憶された予備ブロックの残数と閾値とを比較判定する(ST2)。その結果、予備ブロックの残数が閾値(50ブロック)以下である場合、コントローラ11は表示手段であるLED17を点灯する(ST3)。

【0020】

次にホスト1からデータ読み出しコマンドがないか判断し(ST4)、YESであれば、フラッシュメモリ12の指定されたアドレスからデータを読み出してエラー訂正回路15によってエラーチェックを行い(ST5)、エラーがあるか判断する(ST6)。エラーがない場合は、フラッシュメモリ12に記憶されているユーザデータをそのままホスト1へ送出し(ST18)、読み出しを完了する。

【0021】

ST6において、エラーがあると判断されると、次にbitエラー数が6以下であるかの判断が行われる(ST7)。6を超える場合はエラー訂正回路15の能力値を超え、もはや訂正不可能であるため、ホスト1へエラーを返す(ST8)。6以下の場合は、更にbitエラー数が4未満であるかの判断が行われる(ST9)。4未満でない場合(4,5又は6)は、まずエラー訂正回路15によりエラーを訂正し(ST10)、訂正済みのデータをホスト1へ送出し(ST18)、読み出しを完了する。そしてエラーを生起したブロックの全データをエラー訂正して一旦RAM13に格納して予備ブロックに書き込み、badブロック処理を行なう(ST11)。なお、ST11において、ブロック管理手段16のカウンター回路は、badブロック処理が1回行われるごとに、予備ブロック残数を一つデクリメントする。

【0022】

デバイス使用開始直後は、不良ブロックが発生する確率が低く、予備ブロックを殆ど使用しないため、予備ブロック残数は100に近い値を示し、その後デバイスの使用回数が増加してくると、不良ブロックの代替が行われて予備ブロックが少なくなり、予備ブロック残数は50に近づく。

【0023】

ST9において、bitエラー数が4未満の場合は、ブロック管理手段16により予備ブロック残数が閾値50ブロックに至る前かどうか判断し(ST12)、YESであればエラー訂正回路15によりエラーを訂正して(ST15)、訂正済のデータをホスト1へ送出し(ST18)、読み出しを完了する(リフレッシュは行わない)。

【0024】

デバイス使用開始から時間が経過してくると、不良ブロックが発生する確率が高くなり、予備ブロック残数は50以下となり、更にデバイスを使用し続けると0となる。

【0025】

ST12において、予備ブロック残数が閾値50ブロックに至った後であると判断されると、まずLED点灯済みか判断し(ST13)、NOであれば、LEDを点灯し(ST14)フラッシュメモリデバイス2の交換時期が近いことを管理者に知らせる。そしてエラー訂正回路15によりエラーを訂正して(ST16)、訂正済のデータをホスト1へ送出し(ST18)、読み出しを完了する。そしてエラーのあったブロックのリフレッシュを行う(ST17)。以上の処理をマップ状に表したものが図6である。

【0026】

以下、リフレッシュの具体的やり方について説明するが、その前に図3乃至図5について説明する。図3、図4及び図5は、リフレッシュ前後のメモリの状態を表したものである。図3、図4及び図5は、それぞれリフレッシュの第1、第2 及び第3の例である。図3に示すメモリセルアレイ23、図4に示すメモリセルアレイ25、図5に示すメモリアレイセル27はリフレッシュ前の物理ブロックの状態を表す。図3に示すメモリセルアレイ24、図4に示すメモリセルアレイ26、図5におけるメモリアレイセル28はリフレッシュ後の物理ブロックの状態を表す。尚、いうまでもないが、メモリセルアレイ23乃至28は便宜上区別して表しているが、実質同一のものである。

【0027】

(リフレッシュの方法例1)

図8のST17におけるリフレッシュのやり方の第1の例について、図3を用いて説明する。今、メモリセルアレイ23に示すBlock1(error)32でbitエラーが発生したとする。ホスト1へデータ転送後、Block1(error)32の全データをエラー訂正回路15によりbitエラーを訂正してから、一旦、RAM13に格納し、その後、メモリセルアレイ23に示す空きブロックであるBlock8191(empty)33にコピーする。その後、Block1(error)32はその全データを消去し、空きブロック(empty)として空きブロック管理テーブル14を更新する。これと同時に、Block8191をメモリセルアレイ24に示すBlock8191(valid)36の状態にして、ユーザデータ領域中の有効ブロックとし、論理/物理ブロック管理テーブルを更新する。尚、ホスト1に対しては、前記RAM23に一旦保存しておいたエラー訂正済みのデータを送出すればよい。ホスト1へのデータの送出は、リフレッシュの前でも後でもよい。同時に行なってもよい。以下の方法例においても同様であることは言うまでもない。

【0028】

(リフレッシュの方法例2)

次に、リフレッシュのやり方の第2例について、図4を用いて説明する。今、メモリセルアレイ25に示すBlock1(error)42でbitエラーが発生したとする。ホスト1へデータ転送後、Block1(error)42の全データをエラー訂正回路15によりbitエラーを訂正してから、一旦、RAM13に格納し、Block1(error)42の全データを消去する。そして、元のBlock1(error)42に書き戻す。この例では、データを元のブロックに書き戻しているにすぎないため、ブロック管理テーブル14の更新を行う必要はない。

【0029】

(リフレッシュの方法例3)

リフレッシュのやり方の第3の例について、図5を用いて説明する。今、メモリセルアレイ27に示すBlock1(error)52でbitエラーが発生したとする。ホスト1へデータ転送後、Block1(error)52の全データをエラー訂正回路15によりbitエラーを訂正してから、一旦、RAM13に格納し、その後、メモリセルアレイ27に示す予備ブロックであるBlock8192(reserve)54にコピーする。これによりBlock8192はメモリセルアレイ28に示すように、有効ブロック56となり、論理/物理管理テーブルが更新される。また、Block1(error)52の全データは消去する。これによりBlock1はメモリセルアレイ28に示すように、予備ブロック(reserve)55となる。変更後の状態は予備ブロック管理テーブルに記録される。

【0030】

上記LED表示において、予備ブロック残数閾値を複数設け、各段階で異なる態様で表示するようにしてもよい(例えば、注意、警告、緊急の3段階を定義する)。また、フラッシュメモリ12の交換時期が近いことをLED表示によって管理者に通知する他、フラッシュメモリデバイス2のコントローラ11がその旨をホスト1に通知するのでもよい。このようにすれば、所謂S・M・A・R・T方式により、種々の態様でシステム管理をより容易に行うことができる。また上記実施例の他、予備ブロック残数が閾値に至った後に、bitエラー数が4、5のブロックをbadブロック処理せずに、リフレッシュして使いまわしてもよい。このようにすれば、さらにフラッシュメモリ12の延命を図ることができる。

【0031】

(発明の効果)

以上述べたように、本発明によれば、例えば専ら若しくは頻繁にデータの読み出しが実行されるようなシステムにおいて、予備ブロックの残数が閾値に至った後に、badブロック閾値未満のbitエラーが検出された場合に、該エラーの生起されたブロックをリフレッシュすることにより、リードディスターブエラーによるbitエラーの増加を防止し、予備ブロックの減少速度を低下させることができる。即ち、フラッシュメモリデバイスの寿命延命を図ることができる。特にリフレッシュ(他のブロックへのデータの書き写し)を、エラー訂正を伴って実行すると、システムの信頼性を一層高めることができる。また、本発明によれば、予備ブロックの残数状態を管理者が知った後の、新品との交換時間を延ばすことができ、システムのより安全な運用を図ることができる。

【図面の簡単な説明】

【0032】

【図1】本発明を実行するシステムの基本構成例である。

【図2】フラッシュメモリアレイの構成例である。

【図3】リフレッシュにおけるブロック管理テーブルの第1の例である。

【図4】リフレッシュにおけるブロック管理テーブルの第2の例である。

【図5】リフレッシュにおけるブロック管理テーブルの第3の例である。

【図6】本発明のメモリ管理方法例をマップ状に表したものである。

【図7】本発明のメモリ管理方法のフローチャート例である。

【図8】本発明のメモリ管理方法のフローチャート例(続き)である。

【符号の説明】

【0033】

1 ホスト

2 フラッシュメモリデバイス

11 コントローラ

12 フラッシュメモリ

13 RAM

14 ブロック管理テーブル

15 エラー訂正回路

16 ブロック管理手段

17 LED

【特許請求の範囲】

【請求項1】

ユーザデータ領域の他に予備ブロックと少なくとも一つ空きブロックを有するメモリと、エラー訂正回路とブロック管理手段とブロック管理テーブルとを有するコントローラと、前記ユーザデータ領域から読み出されたデータをホストに送出する前に一旦保存するRAMとを備えたフラッシュメモリデバイスのメモリ管理方法であって、

エラー訂正回路によって検出されたbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)未満であったとき、前記予備ブロックの残数がブロック管理手段に設定された閾値に至った後は、当該エラーを起こしたデータを含むブロックのデータをリフレッシュすることを特徴とするメモリの管理方法。

【請求項2】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦RAMに格納してから空きブロック若しくは予備ブロックにコピーし、当該エラーを生起したブロックはその全データを消去してから前記空きブロック若しくは前記予備ブロックとして、ブロック管理テーブルを更新することにより実行することを特徴とする請求項1記載のメモリの管理方法。

【請求項3】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦前記RAMに格納し、該ブロックを消去後、前記RAMから該ブロックに書き戻すことにより実行することを特徴とする請求項1記載のフラッシュメモリの管理方法。

【請求項4】

フラッシュメモリデバイスは表示手段をさらに有し、予備ブロックの残数が所定数に至った段階で、該表示手段を駆動することを特徴とする請求項1乃至請求項3いずれか1項記載のメモリの管理方法。

【請求項5】

予備ブロックの残数が所定数に至った段階で、該状態をホストに通知することを特徴とする請求項1乃至請求項3いずれか1項記載のメモリの管理方法。

【請求項6】

ユーザデータ領域の他に予備ブロックと少なくとも一つ空きブロックを有するメモリと、エラー訂正回路とブロック管理手段とブロック管理テーブルとを有するコントローラと、前記ユーザデータ領域から読み出されたデータをホストに送出する前に一旦保存するRAMとを備えたフラッシュメモリデバイスであって、

エラー訂正回路によって検出されたbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)未満であったとき、前記予備ブロックの残数がブロック管理手段に設定された閾値に至った後は、当該エラーを起こしたデータを含むブロックのデータをリフレッシュすることを特徴とするフラッシュメモリデバイス。

【請求項7】

ブロック管理テーブルは、論理/物理ブロック管理テーブル、空きブロック管理テーブル、及び予備ブロック管理テーブルの3種で構成されることを特徴とする請求項6記載のフラッシュメモリデバイス。

【請求項8】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦RAMに格納してから空きブロック若しくは予備ブロックにコピーし、当該エラーを生起したブロックはその全データを消去してから前記空きブロック若しくは前記予備ブロックとして、ブロック管理テーブルを更新することにより実行することを特徴とする請求項7記載のフラッシュメモリデバイス。

【請求項9】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦前記RAMに格納し、該ブロックを消去後、前記RAMから該ブロックに書き戻すことにより実行することを特徴とする請求項7記載のフラッシュメモリデバイス。

【請求項10】

表示手段を更に有し、コントローラは、予備ブロックの残数が所定数に至った段階で、該表示手段を駆動することを特徴とする請求項6記載のフラッシュメモリデバイス。

【請求項11】

コントローラは、予備ブロックの残数が所定数に至った段階で、該状態をホストに通知することを特徴とする請求項6記載のフラッシュメモリデバイス。

【請求項1】

ユーザデータ領域の他に予備ブロックと少なくとも一つ空きブロックを有するメモリと、エラー訂正回路とブロック管理手段とブロック管理テーブルとを有するコントローラと、前記ユーザデータ領域から読み出されたデータをホストに送出する前に一旦保存するRAMとを備えたフラッシュメモリデバイスのメモリ管理方法であって、

エラー訂正回路によって検出されたbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)未満であったとき、前記予備ブロックの残数がブロック管理手段に設定された閾値に至った後は、当該エラーを起こしたデータを含むブロックのデータをリフレッシュすることを特徴とするメモリの管理方法。

【請求項2】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦RAMに格納してから空きブロック若しくは予備ブロックにコピーし、当該エラーを生起したブロックはその全データを消去してから前記空きブロック若しくは前記予備ブロックとして、ブロック管理テーブルを更新することにより実行することを特徴とする請求項1記載のメモリの管理方法。

【請求項3】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦前記RAMに格納し、該ブロックを消去後、前記RAMから該ブロックに書き戻すことにより実行することを特徴とする請求項1記載のフラッシュメモリの管理方法。

【請求項4】

フラッシュメモリデバイスは表示手段をさらに有し、予備ブロックの残数が所定数に至った段階で、該表示手段を駆動することを特徴とする請求項1乃至請求項3いずれか1項記載のメモリの管理方法。

【請求項5】

予備ブロックの残数が所定数に至った段階で、該状態をホストに通知することを特徴とする請求項1乃至請求項3いずれか1項記載のメモリの管理方法。

【請求項6】

ユーザデータ領域の他に予備ブロックと少なくとも一つ空きブロックを有するメモリと、エラー訂正回路とブロック管理手段とブロック管理テーブルとを有するコントローラと、前記ユーザデータ領域から読み出されたデータをホストに送出する前に一旦保存するRAMとを備えたフラッシュメモリデバイスであって、

エラー訂正回路によって検出されたbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)未満であったとき、前記予備ブロックの残数がブロック管理手段に設定された閾値に至った後は、当該エラーを起こしたデータを含むブロックのデータをリフレッシュすることを特徴とするフラッシュメモリデバイス。

【請求項7】

ブロック管理テーブルは、論理/物理ブロック管理テーブル、空きブロック管理テーブル、及び予備ブロック管理テーブルの3種で構成されることを特徴とする請求項6記載のフラッシュメモリデバイス。

【請求項8】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦RAMに格納してから空きブロック若しくは予備ブロックにコピーし、当該エラーを生起したブロックはその全データを消去してから前記空きブロック若しくは前記予備ブロックとして、ブロック管理テーブルを更新することにより実行することを特徴とする請求項7記載のフラッシュメモリデバイス。

【請求項9】

リフレッシュは、エラーを生起したブロックの全データをエラー訂正して一旦前記RAMに格納し、該ブロックを消去後、前記RAMから該ブロックに書き戻すことにより実行することを特徴とする請求項7記載のフラッシュメモリデバイス。

【請求項10】

表示手段を更に有し、コントローラは、予備ブロックの残数が所定数に至った段階で、該表示手段を駆動することを特徴とする請求項6記載のフラッシュメモリデバイス。

【請求項11】

コントローラは、予備ブロックの残数が所定数に至った段階で、該状態をホストに通知することを特徴とする請求項6記載のフラッシュメモリデバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2010−86402(P2010−86402A)

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願番号】特願2008−256483(P2008−256483)

【出願日】平成20年10月1日(2008.10.1)

【出願人】(594096966)株式会社ハギワラシスコム (32)

【Fターム(参考)】

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願日】平成20年10月1日(2008.10.1)

【出願人】(594096966)株式会社ハギワラシスコム (32)

【Fターム(参考)】

[ Back to top ]