メモリカードとホストデバイスとの間で通信を実現するための回路および方法

【課題】UHS-IIモードと従来のモードのいずれかで信号を伝送するための、簡素かつ効率的な回路および方法。

【解決手段】インターフェース回路は、メモリカードとホストデバイスとの間の通信を実現する。インターフェース回路は、ピンの第1のセットと、ピンの第2のセットと、制御ユニットとを含む。制御ユニットは、ピンの第1のセットを介して第1のモードで信号の第1のセットを伝送する場合、ピンの第1のセットを有効にしてピンの第2のセットを無効にし、ピンの第2のセットを介して第2のモードで信号の第2のセットを伝送する場合、ピンの第1のセットを無効にしてピンの第2のセットを有効にする。制御ユニットは、ピンの第2のセットのクロックピンを介して、第2のモードで、差動シグナリングによって、信号の第2のセットのクロック信号を伝送する。第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。

【解決手段】インターフェース回路は、メモリカードとホストデバイスとの間の通信を実現する。インターフェース回路は、ピンの第1のセットと、ピンの第2のセットと、制御ユニットとを含む。制御ユニットは、ピンの第1のセットを介して第1のモードで信号の第1のセットを伝送する場合、ピンの第1のセットを有効にしてピンの第2のセットを無効にし、ピンの第2のセットを介して第2のモードで信号の第2のセットを伝送する場合、ピンの第1のセットを無効にしてピンの第2のセットを有効にする。制御ユニットは、ピンの第2のセットのクロックピンを介して、第2のモードで、差動シグナリングによって、信号の第2のセットのクロック信号を伝送する。第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、2011年7月18日に出願された、係属中の米国特許仮出願第61/508954号の本出願であり、上記の仮出願の内容は全体が参照により組み込まれる。

【背景技術】

【0002】

図1は、従来のモードあるいはultra high speed-II (UHS-II)モードで、secure digital (SD)カードにより通信するための、ホストデバイス向けの従来のインターフェース回路100を示す。インターフェース回路100は、制御ユニット110および入力/出力(I/O)ユニット120を含む。I/Oユニット120はUHS-II I/Oユニット122、従来のI/Oユニット126、および共通のI/Oユニット124を含む。UHS-II I/Oユニット122は共通のI/Oユニット124とともに、UHS-IIモードで信号を伝送し、従来のI/Oユニット126は共通のI/Oユニット124とともに、従来のモードで信号を伝送する。

【0003】

UHS-II I/Oユニット122は、伝送回路Aに接続されたピンP1〜P4を含み、従来のI/Oユニット126は、伝送回路Cに接続されたピンP7〜P10を含み、共通のI/Oユニット124は、伝送回路Bに接続されたピンP5およびP6を含む。伝送回路Bは、従来のモードおよびUHS-IIモードに対応する。UHS-IIモードでは、伝送回路Aおよび伝送回路Bは、ピンP1〜P6を介して信号を伝送する。従来のモードでは、伝送回路Bおよび伝送回路Cは、ピンP5〜P10を介して信号を伝送する。制御ユニット110は、I/Oユニット120の中の対応するI/Oユニットを制御して、従来のモードまたはUHS-IIモードで信号を伝送する。

【0004】

より具体的には、伝送回路Bは、UHS-IIモードで動作する回路B1、従来のモードとUHS-IIモードの両方で動作する回路B2、および従来のモードで動作する回路B3を含む。制御ユニット110は、信号A'、B1'〜B3'、およびC'を生成する。UHS-IIモードでは、伝送回路Aと回路B1とB2とが、それぞれ信号A'とB1'〜B2'とを介して有効にされ、回路B3と伝送回路Cとが、それぞれ信号B3'とC'とを介して無効にされる。従来のモードでは、伝送回路Aと回路B1とが、それぞれ信号A'とB1'とを介して無効にされ、回路B2とB3と伝送回路Cとが、それぞれ信号B2'〜B3'とC'とを介して有効にされる。

【発明の概要】

【発明が解決しようとする課題】

【0005】

不利なことに、共通のI/Oユニット124は従来のモードとUHS-IIモードの両方に対応するので、複雑な制御が要求され得る。言い換えると、伝送モードに従ってI/Oユニット120の中の対応する伝送回路および回路を、有効および無効にするために、信号A'、B1'〜B3'、およびC'のような複数の信号が用いられる。したがって、本発明が主に対象とするのは、UHS-IIモードと従来のモードのいずれかで信号を伝送するための、簡素かつ効率的な回路および方法である。

【課題を解決するための手段】

【0006】

ある実施形態では、本発明は、メモリカードとホストデバイスとの間で通信を実現する、インターフェース回路を提供する。インターフェース回路は、ピンの第1のセット、ピンの第2のセット、および制御ユニットを含む。ピンの第1のセットおよび第2のセットは、インターフェース回路に接続される。ピンの第1のセットおよび第2のセットに接続される制御ユニットは、ピンの第1のセットを介して、ホストデバイスとメモリカードとの間で、第1のモードで信号の第1のセットを伝送する場合は、ピンの第1のセットを有効にしてピンの第2のセットを無効にし、ピンの第2のセットを介して、ホストデバイスとメモリカードとの間で、第2のモードで信号の第2のセットを伝送する場合は、ピンの第1のセットを無効にしてピンの第2のセットを有効にする。制御ユニットは、ピンの第2のセットのクロックピンを介して、差動シグナリングによって、第2のモードで信号の第2のセットのクロック信号を伝送する。第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。

【0007】

別の実施形態では、本発明は、ホストデバイスと、メモリカードと、ホストデバイスとメモリカードとの間で通信を実現するためのインターフェース回路とを含む、システムを提供する。インターフェース回路は、第1のユニット、第2のユニット、および制御ユニットを含む。制御ユニットは、選択信号を受信し、その選択信号に従って、第1のユニットを有効にして第2のユニットを無効にして、ホストデバイスとメモリカードとの間で、第1のユニットを介して第1の信号伝送速度で第1の信号を伝送することによって、および第1のユニットを無効にして第2のユニットを有効にして、ホストデバイスとメモリカードとの間で、第2のユニットを介してクロック信号を伝送し、ホストデバイスとメモリカードとの間で、第2のユニットを介して第2の信号伝送速度で第2の信号を伝送することによって、信号伝送速度を調整する。制御ユニットは、第2のユニットを介した差動シグナリングによって、クロック信号を伝送する。

【0008】

さらに別の実施形態では、本発明は、ホストデバイスとメモリカードとの間で通信を実現するための方法を提供する。この方法は、ピンの第1のセットを有効にするステップと、ピンの第2のセットを無効にするステップと、第1のモードが選択された場合に、ホストデバイスとメモリカードとの間でピンの第1のセットを介して信号の第1のセットを伝送するステップと、ピンの第1のセットを無効にするステップと、ピンの第2のセットを有効にするステップと、第2のモードが選択された場合に、ホストデバイスとメモリカードとの間でピンの第2のセットを介して信号の第2のセットを伝送するステップを含む。信号の第2のセットを伝送するステップは、第2のモードでの差動シグナリングによって、ピンの第2のセットのクロックピンを介して、信号の第2のセットのクロック信号を伝送するステップを含む。第2のモードでの信号伝送速度は、第1のモードでの信号伝送速度よりも速い。

【0009】

本明細書に組み込まれ、本明細書の一部を形成する添付の図面は、本発明の実施形態を例示し、説明とともに、本発明の原理を説明する役割を果たす。

【図面の簡単な説明】

【0010】

【図1】ホストデバイスとSDカードとの間で通信を実現するための、従来のインターフェース回路を示す図である。

【図2】本発明の一実施形態による、メモリカードとホストデバイスとの間で通信を実現するための、インターフェース回路の例を示す図である。

【図3】本発明の一実施形態による、メモリカードとホストデバイスとの間で通信を実現するための方法の、ある例の流れ図である。

【発明を実施するための形態】

【0011】

ここで、本発明の実施形態に対して詳細な言及がなされ、実施形態の例が添付の図面に示される。本発明はそうした実施形態とともに説明されるが、本発明をそうした実施形態に限定することは意図されないことが理解されよう。逆に、本発明は、添付の特許請求の範囲により定義される本発明の趣旨および範囲に含まれ得る、代替の形態、修正された形態、および等価の形態を包含することが意図される。

【0012】

さらに、本発明の実施形態の以下の詳細な説明では、本発明の完全な理解をもたらすために、多くの具体的な詳細事項が説明される。しかし、本発明はこれらの詳細事項なしで実行され得ることが、当業者には認識されよう。他の例では、よく知られた方法、手順、コンポーネント、および回路は、本発明の実施形態の態様を不必要に曖昧にしないように、詳細には説明されていない。

【0013】

本発明は、ホストデバイスが、異なる伝送規格を用いて異なる信号伝送速度で、メモリカードから/メモリカードへ信号を適応可能に伝送できるようにする。本発明はまた、メモリカードが、異なる伝送規格を用いて異なる信号伝送速度で、異なるホストデバイスから/異なるホストデバイスへ信号を適応可能に伝送できるようにもする。

【0014】

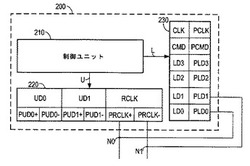

図2は、本発明の一実施形態による、ホストデバイスとメモリカードとの間で通信を実現するための、インターフェース回路200の例を示す。ホストデバイスは、限定はされないが、メモリカードからデータを読み取ることができ、またはメモリカードにデータを書き込むことができる、電子デバイスであってよい。例として、電子デバイスは、メモリカードコントローラチップ、メモリカードリーダ、またはデジタルカムコーダであってよい。メモリカードは、限定はされないが、secure digital (SD)カードであってよい。インターフェース回路200は、メモリカードとホストデバイスとの間で信号を伝送する。一実施形態では、インターフェース回路200は、ホストデバイスに含まれる。あるいは、別の実施形態では、インターフェース回路200は、SDカードに含まれる。

【0015】

インターフェース回路200は、複数の伝送モードに対応する。複数の伝送モードは、限定はされないが、従来のモード、たとえば、high speed (HS)モードまたはultra high speed-I (UHS-I)モード、および改良型モード、たとえば、ultra high speed-II (UHS-II)モードを含む。改良型モードでの信号伝送は、従来のモードでの信号伝送よりも高速である。複数の伝送モードで伝送される信号は、限定はされないが、データ信号、命令信号、またはクロック信号を含む。一実施形態では、改良型モードでのデータ伝送は、従来のモードでのデータ伝送よりも高速である。

【0016】

一実施形態では、ホストデバイスはメモリカードの種類を検出し、検出結果に従って、複数の伝送モードの中から伝送モードを選択する。検出結果が、メモリカードが1つのモードのみに対応することを示し、ホストデバイスが同じモードに対応する場合、ホストデバイスは、メモリカードが対応するモードを選択する。検出結果が、メモリカードが複数のモードに対応することを示し、ホストデバイスが、メモリカードが対応する複数のモードのうち1つのモードのみに対応する場合、ホストデバイスは、ホストデバイスが対応するモードを選択する。メモリカードとホストデバイスの両方が複数のモードに対応する場合、ホストデバイスは、メモリカードとホストデバイスの両方が対応し、信号伝送の速度がより高速なモードを、選択する。

【0017】

図2の例では、インターフェース回路200は、第1のモードで信号を伝送するための第1の入力/出力(I/O)ユニット230と、第2のモードで信号を伝送するための第2のI/Oユニット220、たとえば、従来のモードで信号を伝送するための従来のI/Oユニット230と、UHS-IIモードで信号を伝送するためのUHS-II I/Oユニット220を含む。インターフェース回路200はさらに、ホストデバイスから選択信号を受信するための、制御ユニット210を含む。選択信号は、ホストデバイスとメモリカードの両方が対応する伝送モードに従って決定され、複数の伝送モードの中から選択されたモードを示す。制御ユニット210は、信号を伝送する目的で、従来のI/Oユニット230およびUHS-II I/Oユニット220を制御する。たとえば、従来のモードが選択されると、制御ユニット210は、従来のI/Oユニット230を信号Lを介して有効にし、UHS-II I/Oユニット220を信号Uを介して無効にし、UHS-IIモードが選択されると、制御ユニット210は従来のI/Oユニット230を信号Lを介して無効にし、UHS-II I/Oユニット220を信号Uを介して有効にする。言い換えると、制御ユニット210は、選択信号に従って、従来のI/Oユニット230とUHS-II I/Oユニット220のいずれかを有効にする。

【0018】

図2の例では、UHS-II I/Oユニット220のためのI/Oピンのセットは、インターフェース回路200の中の伝送回路のセットに接続する。たとえば、それぞれ、I/OピンPUD0+およびPUD0-は伝送回路UD0に接続し、I/OピンPUD1+およびPUD1-は伝送回路UD1に接続し、I/OピンPRCLK+およびPRCLK-は伝送回路RCLKに接続する。一実施形態では、I/OピンPUD0+、PUD0-、PUD1+、およびPUD1-、ならびにPRCLK+およびPRCLK-、ならびに伝送回路UD0、UD1、およびRCLKは、インターフェース回路200に組み込まれる。ここで、本開示における用語「I/Oピン」は、入力機能を果たすピン、または出力機能を果たすピン、または入力機能と出力機能を果たすピンを意味する。

【0019】

UHS-IIモードでは、インターフェース回路200は、I/OピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を介して、信号のセットを伝送する。より具体的には、UHS-IIモードでは、制御ユニット210は、伝送回路UD0およびUD1を制御して、I/OピンPUD0+およびPUD0-、ならびにI/OピンPUD1+およびPUD1-をそれぞれ介して、信号を伝送する。一実施形態では、伝送回路UD0は、I/OピンPUD0+およびPUD0-を介して、ホストデバイスからSDカードに信号を伝送し、伝送回路UD1は、I/OピンPUD1+およびPUD1-を介して、SDカードからホストデバイスに信号を伝送する。ある代替的な実施形態では、伝送回路UD1が、I/OピンPUD1+およびPUD1-を介して、ホストデバイスからSDカードに信号を伝送し、伝送回路UD0が、I/OピンPUD0+およびPUD0-を介して、SDカードからホストデバイスに信号を伝送する。

【0020】

UHS-IIモードでは、制御ユニット210は、伝送回路RCLKを制御して、ホストデバイスとSDカードとの間で、たとえば、ホストデバイスからSDカードへ、I/OピンPRCLK+およびPRCLK-を介してクロック信号を伝送する。一実施形態では、伝送回路RCLKにより伝送されるクロック信号の周波数は、伝送回路UD0およびUD1により伝送される信号の周波数よりも低い。一実施形態では、伝送回路UD0、UD1およびRCLKは、差動シグナリングにより信号を伝送する。たとえば、伝送回路RCLKは、ピンPRCLK+およびPRCLK-を介して、相補信号を伝送する。

【0021】

図2の例では、従来のI/Oユニット230のためのI/Oピンのセットは、インターフェース回路200の中の伝送回路のセットに接続する。たとえば、I/OピンPLD0〜PLD3は、それぞれ伝送回路LD0〜LD3に接続し、I/OピンPCMDは伝送回路CMDに接続し、I/OピンPCLKは伝送回路CLKに接続する。一実施形態では、I/OピンPLD0〜PLD3、PCMDおよびPCLK、ならびに伝送回路LD0〜LD3、CMDおよびCLKは、インターフェース回路200に組み込まれる。

【0022】

従来のモードでは、インターフェース回路200は、I/OピンPLD0〜PLD3、PCMD、およびPCLKを介して、信号のセットを伝送する。より具体的には、従来のモードでは、制御ユニット210は、SDカードとホストデバイスとの間で、伝送回路LD0〜LD3を制御してI/OピンPLD0〜PLD3を介して信号を伝送し、伝送回路CMDを制御してI/OピンPCMDを介して命令信号を伝送し、伝送回路CLKを制御してI/OピンPCLKを介してクロック信号を伝送する。一実施形態では、命令信号は、伝送回路LD0〜LD3によりなされる信号伝送の方向、たとえば、SDカードからホストデバイス、またはホストデバイスからSDカードのような方向を示す。一実施形態では、I/OピンPCLKを介して伝送されるクロック信号の周波数は、I/OピンPLD0〜PLD3を介して伝送される信号の周波数と等しい。

【0023】

言い換えると、制御ユニット210は選択信号を受信し、選択信号に従って、信号伝送速度を調整する。より具体的には、制御ユニット210は、ピンPLD0〜PLD3、PCMDおよびPCLKを有効にし、ピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を無効にして、ホストデバイスとSDカードとの間を、ピンPLD0〜PLD3、PCMDおよびPCLKを介して、従来のモードで信号を伝送する。ピンPLD0〜PLD3は、従来のモードの第1の信号伝送速度で、データを伝送する。インターフェース回路200は、ピンPLD0〜PLD3、PCMDおよびPCLKを無効にし、ピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を有効にして、ホストデバイスとSDカードとの間を、ピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を介して、UHS-IIモードで信号を伝送する。ピンPUD0+/-およびPUD1+/-は、UHS-IIモードの第2の信号伝送速度で、データを伝送する。UHS-IIモードの第2の信号伝送速度は、従来のモードの第1の信号伝送速度よりも速い。

【0024】

図2の例では、UHS-II I/Oユニット220のピンPRCLK+および従来のI/Oユニット230のピンPLD0は、共通のノードN0に接続され、UHS-II I/Oユニット220のピンPRCLK-および従来のI/Oユニット230のピンPLD1は、共通のノードN1に接続される。ノードに接続されるI/Oピンから伝送される/I/Oピンへ伝送される信号は、それらのノードを介して伝送される。たとえば、I/OピンPRCLK+およびPLD0から/I/OピンPRCLK+およびPLD0へ伝送される信号は、ノードN0を介して伝送される。言い換えると、一実施形態では、UHS-IIモードでは、インターフェース回路200は、ノードN0を介して、第1の通信回路とピンPRCLK+との間で第1のクロック信号を伝送し、ノードN1を介して、第1の通信回路とピンPRCLK-との間で第2のクロック信号を伝送する。従来のモードでは、インターフェース回路200は、ノードN0を介して、第2の通信回路とピンPLD0との間で第1のデータ信号を伝送し、ノードN1を介して、第2の通信回路とピンPLD1との間で第2のデータ信号を伝送する。第1の通信回路および第2の通信回路は、ホストデバイスとSDカードのいずれかであってよい。たとえば、インターフェース回路がホストデバイスに含まれる場合、第1の通信回路および第2の通信回路はSDカードである。インターフェース回路がSDカードに含まれる場合、第1の通信回路および第2の通信回路はホストデバイスである。一実施形態では、制御ユニット210、UHS-II I/Oユニット220、および従来のI/Oユニット230は、チップに組み込まれる。

【0025】

有利なことに、従来のモードで信号を伝送するための従来のI/Oユニット230と、UHS-IIモードで信号を伝送するためのUHS-II I/Oユニット220とは独立であってよいので、より複雑ではない制御を採用することができる。より具体的には、信号LおよびUのような、より少数の信号を与えることで、対応するユニットを、選択された伝送モードに従って有効または無効にすることができ、インターフェース回路200は、選択された伝送モードで信号を伝送することができる。

【0026】

インターフェース回路200は、デジタルカムコーダ、デジタルカメラ、テレビ、セットトップボックス、パーソナルコンピュータ、携帯電話、SDカード、およびSDカードリーダのような、様々な用途で用いられ得る。

【0027】

図3は、メモリカード(たとえばSDカード)とホストデバイスとの間で通信を実現するための、方法300の流れ図を示す。図3は、図2と組み合わせて説明される。具体的なステップが図3に開示されるが、そのようなステップは例である。つまり、本発明は、図3に記載されたステップとは別の様々なステップまたは変形形態のステップを実行するのに、よく適している。

【0028】

ステップ302において、ホストデバイス、たとえばデジタルカムコーダは、メモリカードの種類を検出し、検出結果に従って、第1のモードおよび第2のモードのような複数の伝送モードから、メモリカードとホストデバイスとの間の通信のための伝送モードを選択する。たとえば、検出結果が、メモリカードが1つのみのモードに対応することを示し、ホストデバイスが同じモードに対応する場合、ホストデバイスは、メモリカードが対応するモードを選択する。検出結果が、メモリカードが複数のモードに対応し、ホストデバイスがその複数のモードのうちの1つのモードのみに対応する場合、ホストデバイスは、ホストデバイスが対応するモードを選択する。メモリカードとホストデバイスの両方が複数のモードに対応する場合、ホストデバイスは、メモリカードとホストデバイスの両方が対応し、信号伝送速度がより高速なモードを、選択する。一実施形態では、第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。複数の伝送モードで伝送される信号は、限定はされないが、データ信号、命令信号、またはクロック信号を含む。一実施形態では、第2のモードでのデータ伝送は、第1のモードでのデータ伝送よりも高速である。

【0029】

ステップ304において、制御ユニットは、ホストデバイスからの選択信号を受信し、選択信号に従って、第1のユニットまたは第2のユニットを制御して信号を伝送する。選択信号は、第1のモードおよび第2のモードから選択されたモードを示す。たとえば、従来のモードが選択されると、制御ユニット210は、従来のI/Oユニット230を信号Lを介して有効にし、UHS-II I/Oユニット220を信号Uを介して無効にし、UHS-IIモードが選択されると、制御ユニット210は従来のI/Oユニット230を信号Lを介して無効にし、UHS-II I/Oユニット220を信号Uを介して有効にする。

【0030】

より具体的には、制御ユニット210は、選択信号に従って、ピンの第1のセットまたはピンの第2のセットを制御して、信号を伝送する。従来のI/Oユニット230は、ピンの第1のセットPLD0〜PLD3、PCMDおよびPCLKを含み、UHS-II I/Oユニット220は、ピンの第2のセットPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を含む。

【0031】

ステップ306において、従来のモードが選択されると、制御ユニット210はピンの第1のセットを有効にし、ピンの第2のセットを無効にする。従来のI/Oユニット230は、ピンの第1のセットを介して信号の第1のセットを伝送する。UHS-IIモードが選択されると、制御ユニット210はピンの第1のセットを無効にし、ピンの第2のセットを有効にする。UHS-II I/Oユニット220は、ピンの第2のセットを介して信号の第2のセットを伝送する。ステップ308において、UHS-IIモードが選択されると、UHS-II I/Oユニット220は、差動シグナリングによって、ピンの第2のセットのクロックピンを介して、信号の第2のセットのクロック信号を伝送する。たとえば、UHS-II I/Oユニット220は、差動シグナリングによって、ピンPRCLK+およびPRCLK-を介して、クロック信号を伝送する。

【0032】

一実施形態では、ピンの第1のセットの第1のピンは、あるノードを介してクロックピンに接続される。たとえば、ピンPLD0およびPLD1は、それぞれ、ノードN0およびN1を介して、ピンPRCLK+およびPRCLK-に接続される。

【0033】

第1のモードでは、第1のユニットが、ノードを介して、第1のピンと第1の通信回路との間で、信号の第1のセットの第1の信号を伝送し、第2のモードでは、第2のユニットが、ノードを介して、クロックピンと第2の通信回路との間で、クロック信号を伝送する。例として、従来のモードでは、従来のI/Oユニット230が、ノードN0を介して、ピンPLD0と第1の通信回路との間でデータ信号を伝送し、ノードN1を介して、ピンPLD1と第1の通信回路との間でデータ信号を伝送する。UHS-IIモードでは、UHS-II I/Oユニット220が、ノードN0を介して、ピンPRCLK+と第2の通信回路との間で第1のクロック信号を伝送し、ノードN1を介して、ピンPRCLK-と第2の通信回路との間で第2のクロック信号を伝送する。

【0034】

一実施形態では、信号の第1のセットは命令信号を含む。命令信号は、信号の第1のセットのデータ信号の伝送の方向、たとえば、SDカードからホストデバイス、またはホストデバイスからSDカードのような方向を示す。一実施形態では、信号の第1のセットのクロック信号の周波数は、信号の第1のセットのデータ信号の周波数に等しい。

【0035】

一実施形態では、UHS-II I/Oユニット220は、ピンPUD1+/-を介して、SDカードからホストデバイスに、信号の第2のセットのデータ信号を伝送し、ピンPUD0+/-を介して、ホストデバイスからSDカードに、信号の第2のセットのデータ信号を伝送する。ある代替的な実施形態では、UHS-II I/Oユニット220は、ピンPUD1+/-を介して、ホストデバイスからSDカードにデータ信号を伝送し、ピンPUD0+/-を介して、SDカードからホストデバイスにデータ信号を伝送する。一実施形態では、ピンPRCLK+/-を介して伝送されるクロック信号の周波数は、ピンPUD0+/-およびPUD1+/-を介して伝送されるデータ信号の周波数よりも低い。

【0036】

前述の説明および図面は本発明の実施形態を代表するものであるが、添付の特許請求の範囲で定義されるような本発明の原理の趣旨および範囲から逸脱することなく、様々な追加、修正、および置換がなされ得ることが、理解されよう。本発明は、形状、構造、構成、比率、材料、要素、および部品の多くの修正形態とともに用いられてもよく、場合によっては、本発明を実行する際に用いられてもよく、上記の修正形態は、本発明の原理から逸脱することなく、具体的な環境および動作要件に対して具体的に適合されていることを、当業者は理解するだろう。したがって、ここで開示された実施形態は、あらゆる面で、限定的ではなく例示的であるものとして考えられるべきであり、本発明の範囲は、添付の特許請求の範囲とその法律上の等価物により示され、前述の説明により限定はされない。

【符号の説明】

【0037】

100 従来のインターフェース回路

110 制御ユニット

120 I/Oユニット

122 UHS-II I/Oユニット

124 共通のI/Oユニット

126 従来のI/Oユニット

200 インターフェース回路

210 制御ユニット

220 第2のI/Oユニット

230 従来のI/Oユニット

【技術分野】

【0001】

本出願は、2011年7月18日に出願された、係属中の米国特許仮出願第61/508954号の本出願であり、上記の仮出願の内容は全体が参照により組み込まれる。

【背景技術】

【0002】

図1は、従来のモードあるいはultra high speed-II (UHS-II)モードで、secure digital (SD)カードにより通信するための、ホストデバイス向けの従来のインターフェース回路100を示す。インターフェース回路100は、制御ユニット110および入力/出力(I/O)ユニット120を含む。I/Oユニット120はUHS-II I/Oユニット122、従来のI/Oユニット126、および共通のI/Oユニット124を含む。UHS-II I/Oユニット122は共通のI/Oユニット124とともに、UHS-IIモードで信号を伝送し、従来のI/Oユニット126は共通のI/Oユニット124とともに、従来のモードで信号を伝送する。

【0003】

UHS-II I/Oユニット122は、伝送回路Aに接続されたピンP1〜P4を含み、従来のI/Oユニット126は、伝送回路Cに接続されたピンP7〜P10を含み、共通のI/Oユニット124は、伝送回路Bに接続されたピンP5およびP6を含む。伝送回路Bは、従来のモードおよびUHS-IIモードに対応する。UHS-IIモードでは、伝送回路Aおよび伝送回路Bは、ピンP1〜P6を介して信号を伝送する。従来のモードでは、伝送回路Bおよび伝送回路Cは、ピンP5〜P10を介して信号を伝送する。制御ユニット110は、I/Oユニット120の中の対応するI/Oユニットを制御して、従来のモードまたはUHS-IIモードで信号を伝送する。

【0004】

より具体的には、伝送回路Bは、UHS-IIモードで動作する回路B1、従来のモードとUHS-IIモードの両方で動作する回路B2、および従来のモードで動作する回路B3を含む。制御ユニット110は、信号A'、B1'〜B3'、およびC'を生成する。UHS-IIモードでは、伝送回路Aと回路B1とB2とが、それぞれ信号A'とB1'〜B2'とを介して有効にされ、回路B3と伝送回路Cとが、それぞれ信号B3'とC'とを介して無効にされる。従来のモードでは、伝送回路Aと回路B1とが、それぞれ信号A'とB1'とを介して無効にされ、回路B2とB3と伝送回路Cとが、それぞれ信号B2'〜B3'とC'とを介して有効にされる。

【発明の概要】

【発明が解決しようとする課題】

【0005】

不利なことに、共通のI/Oユニット124は従来のモードとUHS-IIモードの両方に対応するので、複雑な制御が要求され得る。言い換えると、伝送モードに従ってI/Oユニット120の中の対応する伝送回路および回路を、有効および無効にするために、信号A'、B1'〜B3'、およびC'のような複数の信号が用いられる。したがって、本発明が主に対象とするのは、UHS-IIモードと従来のモードのいずれかで信号を伝送するための、簡素かつ効率的な回路および方法である。

【課題を解決するための手段】

【0006】

ある実施形態では、本発明は、メモリカードとホストデバイスとの間で通信を実現する、インターフェース回路を提供する。インターフェース回路は、ピンの第1のセット、ピンの第2のセット、および制御ユニットを含む。ピンの第1のセットおよび第2のセットは、インターフェース回路に接続される。ピンの第1のセットおよび第2のセットに接続される制御ユニットは、ピンの第1のセットを介して、ホストデバイスとメモリカードとの間で、第1のモードで信号の第1のセットを伝送する場合は、ピンの第1のセットを有効にしてピンの第2のセットを無効にし、ピンの第2のセットを介して、ホストデバイスとメモリカードとの間で、第2のモードで信号の第2のセットを伝送する場合は、ピンの第1のセットを無効にしてピンの第2のセットを有効にする。制御ユニットは、ピンの第2のセットのクロックピンを介して、差動シグナリングによって、第2のモードで信号の第2のセットのクロック信号を伝送する。第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。

【0007】

別の実施形態では、本発明は、ホストデバイスと、メモリカードと、ホストデバイスとメモリカードとの間で通信を実現するためのインターフェース回路とを含む、システムを提供する。インターフェース回路は、第1のユニット、第2のユニット、および制御ユニットを含む。制御ユニットは、選択信号を受信し、その選択信号に従って、第1のユニットを有効にして第2のユニットを無効にして、ホストデバイスとメモリカードとの間で、第1のユニットを介して第1の信号伝送速度で第1の信号を伝送することによって、および第1のユニットを無効にして第2のユニットを有効にして、ホストデバイスとメモリカードとの間で、第2のユニットを介してクロック信号を伝送し、ホストデバイスとメモリカードとの間で、第2のユニットを介して第2の信号伝送速度で第2の信号を伝送することによって、信号伝送速度を調整する。制御ユニットは、第2のユニットを介した差動シグナリングによって、クロック信号を伝送する。

【0008】

さらに別の実施形態では、本発明は、ホストデバイスとメモリカードとの間で通信を実現するための方法を提供する。この方法は、ピンの第1のセットを有効にするステップと、ピンの第2のセットを無効にするステップと、第1のモードが選択された場合に、ホストデバイスとメモリカードとの間でピンの第1のセットを介して信号の第1のセットを伝送するステップと、ピンの第1のセットを無効にするステップと、ピンの第2のセットを有効にするステップと、第2のモードが選択された場合に、ホストデバイスとメモリカードとの間でピンの第2のセットを介して信号の第2のセットを伝送するステップを含む。信号の第2のセットを伝送するステップは、第2のモードでの差動シグナリングによって、ピンの第2のセットのクロックピンを介して、信号の第2のセットのクロック信号を伝送するステップを含む。第2のモードでの信号伝送速度は、第1のモードでの信号伝送速度よりも速い。

【0009】

本明細書に組み込まれ、本明細書の一部を形成する添付の図面は、本発明の実施形態を例示し、説明とともに、本発明の原理を説明する役割を果たす。

【図面の簡単な説明】

【0010】

【図1】ホストデバイスとSDカードとの間で通信を実現するための、従来のインターフェース回路を示す図である。

【図2】本発明の一実施形態による、メモリカードとホストデバイスとの間で通信を実現するための、インターフェース回路の例を示す図である。

【図3】本発明の一実施形態による、メモリカードとホストデバイスとの間で通信を実現するための方法の、ある例の流れ図である。

【発明を実施するための形態】

【0011】

ここで、本発明の実施形態に対して詳細な言及がなされ、実施形態の例が添付の図面に示される。本発明はそうした実施形態とともに説明されるが、本発明をそうした実施形態に限定することは意図されないことが理解されよう。逆に、本発明は、添付の特許請求の範囲により定義される本発明の趣旨および範囲に含まれ得る、代替の形態、修正された形態、および等価の形態を包含することが意図される。

【0012】

さらに、本発明の実施形態の以下の詳細な説明では、本発明の完全な理解をもたらすために、多くの具体的な詳細事項が説明される。しかし、本発明はこれらの詳細事項なしで実行され得ることが、当業者には認識されよう。他の例では、よく知られた方法、手順、コンポーネント、および回路は、本発明の実施形態の態様を不必要に曖昧にしないように、詳細には説明されていない。

【0013】

本発明は、ホストデバイスが、異なる伝送規格を用いて異なる信号伝送速度で、メモリカードから/メモリカードへ信号を適応可能に伝送できるようにする。本発明はまた、メモリカードが、異なる伝送規格を用いて異なる信号伝送速度で、異なるホストデバイスから/異なるホストデバイスへ信号を適応可能に伝送できるようにもする。

【0014】

図2は、本発明の一実施形態による、ホストデバイスとメモリカードとの間で通信を実現するための、インターフェース回路200の例を示す。ホストデバイスは、限定はされないが、メモリカードからデータを読み取ることができ、またはメモリカードにデータを書き込むことができる、電子デバイスであってよい。例として、電子デバイスは、メモリカードコントローラチップ、メモリカードリーダ、またはデジタルカムコーダであってよい。メモリカードは、限定はされないが、secure digital (SD)カードであってよい。インターフェース回路200は、メモリカードとホストデバイスとの間で信号を伝送する。一実施形態では、インターフェース回路200は、ホストデバイスに含まれる。あるいは、別の実施形態では、インターフェース回路200は、SDカードに含まれる。

【0015】

インターフェース回路200は、複数の伝送モードに対応する。複数の伝送モードは、限定はされないが、従来のモード、たとえば、high speed (HS)モードまたはultra high speed-I (UHS-I)モード、および改良型モード、たとえば、ultra high speed-II (UHS-II)モードを含む。改良型モードでの信号伝送は、従来のモードでの信号伝送よりも高速である。複数の伝送モードで伝送される信号は、限定はされないが、データ信号、命令信号、またはクロック信号を含む。一実施形態では、改良型モードでのデータ伝送は、従来のモードでのデータ伝送よりも高速である。

【0016】

一実施形態では、ホストデバイスはメモリカードの種類を検出し、検出結果に従って、複数の伝送モードの中から伝送モードを選択する。検出結果が、メモリカードが1つのモードのみに対応することを示し、ホストデバイスが同じモードに対応する場合、ホストデバイスは、メモリカードが対応するモードを選択する。検出結果が、メモリカードが複数のモードに対応することを示し、ホストデバイスが、メモリカードが対応する複数のモードのうち1つのモードのみに対応する場合、ホストデバイスは、ホストデバイスが対応するモードを選択する。メモリカードとホストデバイスの両方が複数のモードに対応する場合、ホストデバイスは、メモリカードとホストデバイスの両方が対応し、信号伝送の速度がより高速なモードを、選択する。

【0017】

図2の例では、インターフェース回路200は、第1のモードで信号を伝送するための第1の入力/出力(I/O)ユニット230と、第2のモードで信号を伝送するための第2のI/Oユニット220、たとえば、従来のモードで信号を伝送するための従来のI/Oユニット230と、UHS-IIモードで信号を伝送するためのUHS-II I/Oユニット220を含む。インターフェース回路200はさらに、ホストデバイスから選択信号を受信するための、制御ユニット210を含む。選択信号は、ホストデバイスとメモリカードの両方が対応する伝送モードに従って決定され、複数の伝送モードの中から選択されたモードを示す。制御ユニット210は、信号を伝送する目的で、従来のI/Oユニット230およびUHS-II I/Oユニット220を制御する。たとえば、従来のモードが選択されると、制御ユニット210は、従来のI/Oユニット230を信号Lを介して有効にし、UHS-II I/Oユニット220を信号Uを介して無効にし、UHS-IIモードが選択されると、制御ユニット210は従来のI/Oユニット230を信号Lを介して無効にし、UHS-II I/Oユニット220を信号Uを介して有効にする。言い換えると、制御ユニット210は、選択信号に従って、従来のI/Oユニット230とUHS-II I/Oユニット220のいずれかを有効にする。

【0018】

図2の例では、UHS-II I/Oユニット220のためのI/Oピンのセットは、インターフェース回路200の中の伝送回路のセットに接続する。たとえば、それぞれ、I/OピンPUD0+およびPUD0-は伝送回路UD0に接続し、I/OピンPUD1+およびPUD1-は伝送回路UD1に接続し、I/OピンPRCLK+およびPRCLK-は伝送回路RCLKに接続する。一実施形態では、I/OピンPUD0+、PUD0-、PUD1+、およびPUD1-、ならびにPRCLK+およびPRCLK-、ならびに伝送回路UD0、UD1、およびRCLKは、インターフェース回路200に組み込まれる。ここで、本開示における用語「I/Oピン」は、入力機能を果たすピン、または出力機能を果たすピン、または入力機能と出力機能を果たすピンを意味する。

【0019】

UHS-IIモードでは、インターフェース回路200は、I/OピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を介して、信号のセットを伝送する。より具体的には、UHS-IIモードでは、制御ユニット210は、伝送回路UD0およびUD1を制御して、I/OピンPUD0+およびPUD0-、ならびにI/OピンPUD1+およびPUD1-をそれぞれ介して、信号を伝送する。一実施形態では、伝送回路UD0は、I/OピンPUD0+およびPUD0-を介して、ホストデバイスからSDカードに信号を伝送し、伝送回路UD1は、I/OピンPUD1+およびPUD1-を介して、SDカードからホストデバイスに信号を伝送する。ある代替的な実施形態では、伝送回路UD1が、I/OピンPUD1+およびPUD1-を介して、ホストデバイスからSDカードに信号を伝送し、伝送回路UD0が、I/OピンPUD0+およびPUD0-を介して、SDカードからホストデバイスに信号を伝送する。

【0020】

UHS-IIモードでは、制御ユニット210は、伝送回路RCLKを制御して、ホストデバイスとSDカードとの間で、たとえば、ホストデバイスからSDカードへ、I/OピンPRCLK+およびPRCLK-を介してクロック信号を伝送する。一実施形態では、伝送回路RCLKにより伝送されるクロック信号の周波数は、伝送回路UD0およびUD1により伝送される信号の周波数よりも低い。一実施形態では、伝送回路UD0、UD1およびRCLKは、差動シグナリングにより信号を伝送する。たとえば、伝送回路RCLKは、ピンPRCLK+およびPRCLK-を介して、相補信号を伝送する。

【0021】

図2の例では、従来のI/Oユニット230のためのI/Oピンのセットは、インターフェース回路200の中の伝送回路のセットに接続する。たとえば、I/OピンPLD0〜PLD3は、それぞれ伝送回路LD0〜LD3に接続し、I/OピンPCMDは伝送回路CMDに接続し、I/OピンPCLKは伝送回路CLKに接続する。一実施形態では、I/OピンPLD0〜PLD3、PCMDおよびPCLK、ならびに伝送回路LD0〜LD3、CMDおよびCLKは、インターフェース回路200に組み込まれる。

【0022】

従来のモードでは、インターフェース回路200は、I/OピンPLD0〜PLD3、PCMD、およびPCLKを介して、信号のセットを伝送する。より具体的には、従来のモードでは、制御ユニット210は、SDカードとホストデバイスとの間で、伝送回路LD0〜LD3を制御してI/OピンPLD0〜PLD3を介して信号を伝送し、伝送回路CMDを制御してI/OピンPCMDを介して命令信号を伝送し、伝送回路CLKを制御してI/OピンPCLKを介してクロック信号を伝送する。一実施形態では、命令信号は、伝送回路LD0〜LD3によりなされる信号伝送の方向、たとえば、SDカードからホストデバイス、またはホストデバイスからSDカードのような方向を示す。一実施形態では、I/OピンPCLKを介して伝送されるクロック信号の周波数は、I/OピンPLD0〜PLD3を介して伝送される信号の周波数と等しい。

【0023】

言い換えると、制御ユニット210は選択信号を受信し、選択信号に従って、信号伝送速度を調整する。より具体的には、制御ユニット210は、ピンPLD0〜PLD3、PCMDおよびPCLKを有効にし、ピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を無効にして、ホストデバイスとSDカードとの間を、ピンPLD0〜PLD3、PCMDおよびPCLKを介して、従来のモードで信号を伝送する。ピンPLD0〜PLD3は、従来のモードの第1の信号伝送速度で、データを伝送する。インターフェース回路200は、ピンPLD0〜PLD3、PCMDおよびPCLKを無効にし、ピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を有効にして、ホストデバイスとSDカードとの間を、ピンPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を介して、UHS-IIモードで信号を伝送する。ピンPUD0+/-およびPUD1+/-は、UHS-IIモードの第2の信号伝送速度で、データを伝送する。UHS-IIモードの第2の信号伝送速度は、従来のモードの第1の信号伝送速度よりも速い。

【0024】

図2の例では、UHS-II I/Oユニット220のピンPRCLK+および従来のI/Oユニット230のピンPLD0は、共通のノードN0に接続され、UHS-II I/Oユニット220のピンPRCLK-および従来のI/Oユニット230のピンPLD1は、共通のノードN1に接続される。ノードに接続されるI/Oピンから伝送される/I/Oピンへ伝送される信号は、それらのノードを介して伝送される。たとえば、I/OピンPRCLK+およびPLD0から/I/OピンPRCLK+およびPLD0へ伝送される信号は、ノードN0を介して伝送される。言い換えると、一実施形態では、UHS-IIモードでは、インターフェース回路200は、ノードN0を介して、第1の通信回路とピンPRCLK+との間で第1のクロック信号を伝送し、ノードN1を介して、第1の通信回路とピンPRCLK-との間で第2のクロック信号を伝送する。従来のモードでは、インターフェース回路200は、ノードN0を介して、第2の通信回路とピンPLD0との間で第1のデータ信号を伝送し、ノードN1を介して、第2の通信回路とピンPLD1との間で第2のデータ信号を伝送する。第1の通信回路および第2の通信回路は、ホストデバイスとSDカードのいずれかであってよい。たとえば、インターフェース回路がホストデバイスに含まれる場合、第1の通信回路および第2の通信回路はSDカードである。インターフェース回路がSDカードに含まれる場合、第1の通信回路および第2の通信回路はホストデバイスである。一実施形態では、制御ユニット210、UHS-II I/Oユニット220、および従来のI/Oユニット230は、チップに組み込まれる。

【0025】

有利なことに、従来のモードで信号を伝送するための従来のI/Oユニット230と、UHS-IIモードで信号を伝送するためのUHS-II I/Oユニット220とは独立であってよいので、より複雑ではない制御を採用することができる。より具体的には、信号LおよびUのような、より少数の信号を与えることで、対応するユニットを、選択された伝送モードに従って有効または無効にすることができ、インターフェース回路200は、選択された伝送モードで信号を伝送することができる。

【0026】

インターフェース回路200は、デジタルカムコーダ、デジタルカメラ、テレビ、セットトップボックス、パーソナルコンピュータ、携帯電話、SDカード、およびSDカードリーダのような、様々な用途で用いられ得る。

【0027】

図3は、メモリカード(たとえばSDカード)とホストデバイスとの間で通信を実現するための、方法300の流れ図を示す。図3は、図2と組み合わせて説明される。具体的なステップが図3に開示されるが、そのようなステップは例である。つまり、本発明は、図3に記載されたステップとは別の様々なステップまたは変形形態のステップを実行するのに、よく適している。

【0028】

ステップ302において、ホストデバイス、たとえばデジタルカムコーダは、メモリカードの種類を検出し、検出結果に従って、第1のモードおよび第2のモードのような複数の伝送モードから、メモリカードとホストデバイスとの間の通信のための伝送モードを選択する。たとえば、検出結果が、メモリカードが1つのみのモードに対応することを示し、ホストデバイスが同じモードに対応する場合、ホストデバイスは、メモリカードが対応するモードを選択する。検出結果が、メモリカードが複数のモードに対応し、ホストデバイスがその複数のモードのうちの1つのモードのみに対応する場合、ホストデバイスは、ホストデバイスが対応するモードを選択する。メモリカードとホストデバイスの両方が複数のモードに対応する場合、ホストデバイスは、メモリカードとホストデバイスの両方が対応し、信号伝送速度がより高速なモードを、選択する。一実施形態では、第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。複数の伝送モードで伝送される信号は、限定はされないが、データ信号、命令信号、またはクロック信号を含む。一実施形態では、第2のモードでのデータ伝送は、第1のモードでのデータ伝送よりも高速である。

【0029】

ステップ304において、制御ユニットは、ホストデバイスからの選択信号を受信し、選択信号に従って、第1のユニットまたは第2のユニットを制御して信号を伝送する。選択信号は、第1のモードおよび第2のモードから選択されたモードを示す。たとえば、従来のモードが選択されると、制御ユニット210は、従来のI/Oユニット230を信号Lを介して有効にし、UHS-II I/Oユニット220を信号Uを介して無効にし、UHS-IIモードが選択されると、制御ユニット210は従来のI/Oユニット230を信号Lを介して無効にし、UHS-II I/Oユニット220を信号Uを介して有効にする。

【0030】

より具体的には、制御ユニット210は、選択信号に従って、ピンの第1のセットまたはピンの第2のセットを制御して、信号を伝送する。従来のI/Oユニット230は、ピンの第1のセットPLD0〜PLD3、PCMDおよびPCLKを含み、UHS-II I/Oユニット220は、ピンの第2のセットPUD0+およびPUD0-、PUD1+およびPUD1-、ならびにPRCLK+およびPRCLK-を含む。

【0031】

ステップ306において、従来のモードが選択されると、制御ユニット210はピンの第1のセットを有効にし、ピンの第2のセットを無効にする。従来のI/Oユニット230は、ピンの第1のセットを介して信号の第1のセットを伝送する。UHS-IIモードが選択されると、制御ユニット210はピンの第1のセットを無効にし、ピンの第2のセットを有効にする。UHS-II I/Oユニット220は、ピンの第2のセットを介して信号の第2のセットを伝送する。ステップ308において、UHS-IIモードが選択されると、UHS-II I/Oユニット220は、差動シグナリングによって、ピンの第2のセットのクロックピンを介して、信号の第2のセットのクロック信号を伝送する。たとえば、UHS-II I/Oユニット220は、差動シグナリングによって、ピンPRCLK+およびPRCLK-を介して、クロック信号を伝送する。

【0032】

一実施形態では、ピンの第1のセットの第1のピンは、あるノードを介してクロックピンに接続される。たとえば、ピンPLD0およびPLD1は、それぞれ、ノードN0およびN1を介して、ピンPRCLK+およびPRCLK-に接続される。

【0033】

第1のモードでは、第1のユニットが、ノードを介して、第1のピンと第1の通信回路との間で、信号の第1のセットの第1の信号を伝送し、第2のモードでは、第2のユニットが、ノードを介して、クロックピンと第2の通信回路との間で、クロック信号を伝送する。例として、従来のモードでは、従来のI/Oユニット230が、ノードN0を介して、ピンPLD0と第1の通信回路との間でデータ信号を伝送し、ノードN1を介して、ピンPLD1と第1の通信回路との間でデータ信号を伝送する。UHS-IIモードでは、UHS-II I/Oユニット220が、ノードN0を介して、ピンPRCLK+と第2の通信回路との間で第1のクロック信号を伝送し、ノードN1を介して、ピンPRCLK-と第2の通信回路との間で第2のクロック信号を伝送する。

【0034】

一実施形態では、信号の第1のセットは命令信号を含む。命令信号は、信号の第1のセットのデータ信号の伝送の方向、たとえば、SDカードからホストデバイス、またはホストデバイスからSDカードのような方向を示す。一実施形態では、信号の第1のセットのクロック信号の周波数は、信号の第1のセットのデータ信号の周波数に等しい。

【0035】

一実施形態では、UHS-II I/Oユニット220は、ピンPUD1+/-を介して、SDカードからホストデバイスに、信号の第2のセットのデータ信号を伝送し、ピンPUD0+/-を介して、ホストデバイスからSDカードに、信号の第2のセットのデータ信号を伝送する。ある代替的な実施形態では、UHS-II I/Oユニット220は、ピンPUD1+/-を介して、ホストデバイスからSDカードにデータ信号を伝送し、ピンPUD0+/-を介して、SDカードからホストデバイスにデータ信号を伝送する。一実施形態では、ピンPRCLK+/-を介して伝送されるクロック信号の周波数は、ピンPUD0+/-およびPUD1+/-を介して伝送されるデータ信号の周波数よりも低い。

【0036】

前述の説明および図面は本発明の実施形態を代表するものであるが、添付の特許請求の範囲で定義されるような本発明の原理の趣旨および範囲から逸脱することなく、様々な追加、修正、および置換がなされ得ることが、理解されよう。本発明は、形状、構造、構成、比率、材料、要素、および部品の多くの修正形態とともに用いられてもよく、場合によっては、本発明を実行する際に用いられてもよく、上記の修正形態は、本発明の原理から逸脱することなく、具体的な環境および動作要件に対して具体的に適合されていることを、当業者は理解するだろう。したがって、ここで開示された実施形態は、あらゆる面で、限定的ではなく例示的であるものとして考えられるべきであり、本発明の範囲は、添付の特許請求の範囲とその法律上の等価物により示され、前述の説明により限定はされない。

【符号の説明】

【0037】

100 従来のインターフェース回路

110 制御ユニット

120 I/Oユニット

122 UHS-II I/Oユニット

124 共通のI/Oユニット

126 従来のI/Oユニット

200 インターフェース回路

210 制御ユニット

220 第2のI/Oユニット

230 従来のI/Oユニット

【特許請求の範囲】

【請求項1】

メモリカードとホストデバイスとの間で通信を実現するためのインターフェース回路であって、

前記インターフェース回路に接続される第1の複数のピンと、

前記インターフェース回路に接続される第2の複数のピンと、

前記第1の複数のピンおよび前記第2の複数のピンに接続される制御ユニットであって、前記第1の複数のピンを介して、第1のモードで前記ホストデバイスと前記メモリカードとの間で第1の複数の信号を伝送する場合に、前記第1の複数のピンを有効にして前記第2の複数のピンを無効にし、前記第2の複数のピンを介して、第2のモードで前記ホストデバイスと前記メモリカードとの間で第2の複数の信号を伝送する場合に、前記第1の複数のピンを無効にして前記第2の複数のピンを有効にする、制御ユニットと

を含み、

前記制御ユニットが、前記第2の複数のピンのクロックピンを介して、差動シグナリングによって、前記第2のモードで前記第2の複数の信号のクロック信号を伝送し、前記第2のモードでの信号伝送が、前記第1のモードでの信号伝送よりも高速である、インターフェース回路。

【請求項2】

前記第1の複数のピンの第1のピンが、ノードを介して前記クロックピンに接続され、前記インターフェース回路が、前記第1のモードで、前記ノードを介して、前記第1のピンと第1の通信回路との間で、前記第1の複数の信号の第1の信号を伝送し、前記第2のモードで、前記ノードを介して、前記クロックピンと第2の通信回路との間で、前記クロック信号を伝送する、請求項1に記載のインターフェース回路。

【請求項3】

前記第1の信号がデータ信号を含み、前記第1の複数の信号が、前記第1の信号の伝送の方向を示す命令信号を含む、請求項2に記載のインターフェース回路。

【請求項4】

前記第2のモードが、ultra high speed-IIモードを含む、請求項1に記載のインターフェース回路。

【請求項5】

前記ホストデバイスがデジタルカムコーダを含む、請求項1に記載のインターフェース回路。

【請求項6】

前記メモリカードがSDカードを含む、請求項1に記載のインターフェース回路。

【請求項7】

前記インターフェース回路が前記ホストデバイスに含まれる、請求項1に記載のインターフェース回路。

【請求項8】

前記制御ユニットが、前記第1のモードおよび前記第2のモードから選択されたモードを示す選択信号をさらに受信し、前記選択信号に従って、前記第1の複数のピンおよび前記第2の複数のピンを選択的に有効にする、請求項1に記載のインターフェース回路。

【請求項9】

前記選択信号が、前記ホストデバイスと前記メモリカードの両方が対応する伝送モードに従って決定される、請求項8に記載のインターフェース回路。

【請求項10】

ホストデバイスと、

メモリカードと、

前記ホストデバイスと前記メモリカードとの間で通信を実現するためのインターフェース回路と

を含むシステムであって、前記インターフェース回路が、

第1のユニットと、

第2のユニットと、

選択信号を受信し、前記選択信号に従って、前記第1のユニットを有効にして前記第2のユニットを無効にして、前記第1のユニットを介して、第1の信号伝送速度で、前記ホストデバイスと前記メモリカードとの間で第1の信号を伝送することによって、および前記第1のユニットを無効にして前記第2のユニットを有効にして、前記第2のユニットを介して、前記ホストデバイスと前記メモリカードとの間でクロック信号を伝送し、前記第2のユニットを介して、第2の信号伝送速度で、前記ホストデバイスと前記メモリカードとの間で第2の信号を伝送することによって、信号伝送速度を調整する制御ユニットと

を含み、

前記制御ユニットが、前記第2のユニットを介して、差動シグナリングによって前記クロック信号を伝送する、システム。

【請求項11】

前記第1のユニットが第1のピンを含み、前記第2のユニットがクロックピンを含み、前記第1のピンが、ノードを介して前記クロックピンに接続され、前記インターフェース回路が、前記ノードを介して、前記第1のピンと第1の通信回路との間で前記第1の信号を伝送し、前記ノードを介して、前記クロックピンと第2の通信回路との間で前記クロック信号を伝送する、請求項10に記載のシステム。

【請求項12】

前記第1の信号および前記第2の信号がデータ信号を含む、請求項10に記載のシステム。

【請求項13】

前記第2のモードがultra high speed-IIモードを含む、請求項10に記載のシステム。

【請求項14】

前記ホストデバイスがデジタルカムコーダを含む、請求項10に記載のシステム。

【請求項15】

前記インターフェース回路が前記ホストデバイスに含まれる、請求項10に記載のシステム。

【請求項16】

ホストデバイスとメモリカードとの間で通信を実現するための方法であって、

第1の複数のピンを有効にして、第2の複数のピンを無効にするステップと、

第1のモードが選択された場合に、前記ホストデバイスと前記メモリカードとの間で、前記第1の複数のピンを介して、第1の複数の信号を伝送するステップと、

前記第1の複数のピンを無効にするステップと、

前記第2の複数のピンを有効にするステップと、

第2のモードが選択された場合に、前記ホストデバイスと前記メモリカードとの間で、前記第2の複数のピンを介して、第2の複数の信号を伝送するステップと

を含み、

前記第2の複数の信号を伝送する前記ステップが、前記第2のモードで、差動シグナリングによって、前記第2の複数のピンのクロックピンを介して、前記第2の複数の信号のクロック信号を伝送するステップを含み、前記第2のモードでの信号伝送は、前記第1のモードでの信号伝送よりも高速である、方法。

【請求項17】

前記第1のモードおよび前記第2のモードから選択されたモードを示す、選択信号を受信するステップ

をさらに含む、請求項16に記載の方法。

【請求項18】

前記第1の複数のピンの第1のピンが、ノードを介して前記クロックピンに接続され、前記第1の複数の信号を伝送する前記ステップが、前記第1のモードで、前記ノードを介して、前記第1のピンと第1の通信回路との間で、前記第1の複数の信号の第1の信号を伝送するステップを含み、前記第2の複数の信号を伝送する前記ステップが、前記第2のモードで、前記ノードを介して、前記クロックピンと第2の通信回路との間で、前記クロック信号を伝送するステップを含む、請求項16に記載の方法。

【請求項19】

前記ホストデバイスがデジタルカムコーダを含む、請求項16に記載の方法。

【請求項20】

前記第2のモードがultra high speed-IIモードを含む、請求項16に記載の方法。

【請求項1】

メモリカードとホストデバイスとの間で通信を実現するためのインターフェース回路であって、

前記インターフェース回路に接続される第1の複数のピンと、

前記インターフェース回路に接続される第2の複数のピンと、

前記第1の複数のピンおよび前記第2の複数のピンに接続される制御ユニットであって、前記第1の複数のピンを介して、第1のモードで前記ホストデバイスと前記メモリカードとの間で第1の複数の信号を伝送する場合に、前記第1の複数のピンを有効にして前記第2の複数のピンを無効にし、前記第2の複数のピンを介して、第2のモードで前記ホストデバイスと前記メモリカードとの間で第2の複数の信号を伝送する場合に、前記第1の複数のピンを無効にして前記第2の複数のピンを有効にする、制御ユニットと

を含み、

前記制御ユニットが、前記第2の複数のピンのクロックピンを介して、差動シグナリングによって、前記第2のモードで前記第2の複数の信号のクロック信号を伝送し、前記第2のモードでの信号伝送が、前記第1のモードでの信号伝送よりも高速である、インターフェース回路。

【請求項2】

前記第1の複数のピンの第1のピンが、ノードを介して前記クロックピンに接続され、前記インターフェース回路が、前記第1のモードで、前記ノードを介して、前記第1のピンと第1の通信回路との間で、前記第1の複数の信号の第1の信号を伝送し、前記第2のモードで、前記ノードを介して、前記クロックピンと第2の通信回路との間で、前記クロック信号を伝送する、請求項1に記載のインターフェース回路。

【請求項3】

前記第1の信号がデータ信号を含み、前記第1の複数の信号が、前記第1の信号の伝送の方向を示す命令信号を含む、請求項2に記載のインターフェース回路。

【請求項4】

前記第2のモードが、ultra high speed-IIモードを含む、請求項1に記載のインターフェース回路。

【請求項5】

前記ホストデバイスがデジタルカムコーダを含む、請求項1に記載のインターフェース回路。

【請求項6】

前記メモリカードがSDカードを含む、請求項1に記載のインターフェース回路。

【請求項7】

前記インターフェース回路が前記ホストデバイスに含まれる、請求項1に記載のインターフェース回路。

【請求項8】

前記制御ユニットが、前記第1のモードおよび前記第2のモードから選択されたモードを示す選択信号をさらに受信し、前記選択信号に従って、前記第1の複数のピンおよび前記第2の複数のピンを選択的に有効にする、請求項1に記載のインターフェース回路。

【請求項9】

前記選択信号が、前記ホストデバイスと前記メモリカードの両方が対応する伝送モードに従って決定される、請求項8に記載のインターフェース回路。

【請求項10】

ホストデバイスと、

メモリカードと、

前記ホストデバイスと前記メモリカードとの間で通信を実現するためのインターフェース回路と

を含むシステムであって、前記インターフェース回路が、

第1のユニットと、

第2のユニットと、

選択信号を受信し、前記選択信号に従って、前記第1のユニットを有効にして前記第2のユニットを無効にして、前記第1のユニットを介して、第1の信号伝送速度で、前記ホストデバイスと前記メモリカードとの間で第1の信号を伝送することによって、および前記第1のユニットを無効にして前記第2のユニットを有効にして、前記第2のユニットを介して、前記ホストデバイスと前記メモリカードとの間でクロック信号を伝送し、前記第2のユニットを介して、第2の信号伝送速度で、前記ホストデバイスと前記メモリカードとの間で第2の信号を伝送することによって、信号伝送速度を調整する制御ユニットと

を含み、

前記制御ユニットが、前記第2のユニットを介して、差動シグナリングによって前記クロック信号を伝送する、システム。

【請求項11】

前記第1のユニットが第1のピンを含み、前記第2のユニットがクロックピンを含み、前記第1のピンが、ノードを介して前記クロックピンに接続され、前記インターフェース回路が、前記ノードを介して、前記第1のピンと第1の通信回路との間で前記第1の信号を伝送し、前記ノードを介して、前記クロックピンと第2の通信回路との間で前記クロック信号を伝送する、請求項10に記載のシステム。

【請求項12】

前記第1の信号および前記第2の信号がデータ信号を含む、請求項10に記載のシステム。

【請求項13】

前記第2のモードがultra high speed-IIモードを含む、請求項10に記載のシステム。

【請求項14】

前記ホストデバイスがデジタルカムコーダを含む、請求項10に記載のシステム。

【請求項15】

前記インターフェース回路が前記ホストデバイスに含まれる、請求項10に記載のシステム。

【請求項16】

ホストデバイスとメモリカードとの間で通信を実現するための方法であって、

第1の複数のピンを有効にして、第2の複数のピンを無効にするステップと、

第1のモードが選択された場合に、前記ホストデバイスと前記メモリカードとの間で、前記第1の複数のピンを介して、第1の複数の信号を伝送するステップと、

前記第1の複数のピンを無効にするステップと、

前記第2の複数のピンを有効にするステップと、

第2のモードが選択された場合に、前記ホストデバイスと前記メモリカードとの間で、前記第2の複数のピンを介して、第2の複数の信号を伝送するステップと

を含み、

前記第2の複数の信号を伝送する前記ステップが、前記第2のモードで、差動シグナリングによって、前記第2の複数のピンのクロックピンを介して、前記第2の複数の信号のクロック信号を伝送するステップを含み、前記第2のモードでの信号伝送は、前記第1のモードでの信号伝送よりも高速である、方法。

【請求項17】

前記第1のモードおよび前記第2のモードから選択されたモードを示す、選択信号を受信するステップ

をさらに含む、請求項16に記載の方法。

【請求項18】

前記第1の複数のピンの第1のピンが、ノードを介して前記クロックピンに接続され、前記第1の複数の信号を伝送する前記ステップが、前記第1のモードで、前記ノードを介して、前記第1のピンと第1の通信回路との間で、前記第1の複数の信号の第1の信号を伝送するステップを含み、前記第2の複数の信号を伝送する前記ステップが、前記第2のモードで、前記ノードを介して、前記クロックピンと第2の通信回路との間で、前記クロック信号を伝送するステップを含む、請求項16に記載の方法。

【請求項19】

前記ホストデバイスがデジタルカムコーダを含む、請求項16に記載の方法。

【請求項20】

前記第2のモードがultra high speed-IIモードを含む、請求項16に記載の方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−25811(P2013−25811A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−158424(P2012−158424)

【出願日】平成24年7月17日(2012.7.17)

【出願人】(500521843)オーツー マイクロ, インコーポレーテッド (138)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2012−158424(P2012−158424)

【出願日】平成24年7月17日(2012.7.17)

【出願人】(500521843)オーツー マイクロ, インコーポレーテッド (138)

【Fターム(参考)】

[ Back to top ]