メモリカードコントローラファームウェアのハードウェアドライバ完全性チェック

【課題】カード上で常時実行するファームウェアの完全性および信頼性の両方を確実にする。

【解決手段】メモリシステム10のフラッシュメモリ20内に前記メモリシステム10のファームウェアを設け、前記ファームウェアを前記メモリシステム10のハードウェアで実施される暗号化エンジン40に通し、前記ファームウェアについてのハッシュ値を前記ハードウェアで実施される暗号化エンジン40で計算し、計算されたハッシュ値を記憶されたハッシュ値と比較し、前記計算されたハッシュ値が前記記憶されたハッシュ値と一致する場合に、前記ファームウェアを実行する。

【解決手段】メモリシステム10のフラッシュメモリ20内に前記メモリシステム10のファームウェアを設け、前記ファームウェアを前記メモリシステム10のハードウェアで実施される暗号化エンジン40に通し、前記ファームウェアについてのハッシュ値を前記ハードウェアで実施される暗号化エンジン40で計算し、計算されたハッシュ値を記憶されたハッシュ値と比較し、前記計算されたハッシュ値が前記記憶されたハッシュ値と一致する場合に、前記ファームウェアを実行する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的には、安全なコンテンツを有するメモリカードおよび当該コンテンツの暗号化に関し、特に、安全なメモリカードを実行するファームウェアの完全性(integrity) をベリファイすることに関する。

【背景技術】

【0002】

商用のメモリカードの機能を工場から出荷する前にベリファイし、工場から出荷されてもハッカーから保護されていることを確実にすることは、極めて重要である。デジタル権利管理の出現と、音楽および映画などの保護されたコンテンツの普及とに伴い、カードのコンテンツが自由にコピーできないことを確実にする必要がある。ハッカーがこれを行おうと試みるやり方の1つとして、カード内のコンテンツを無断使用することができるようにするために、メモリカードを実行するファームウェアを変更または取り替えさえするということがある。よって、カード上で常時実行するファームウェアの完全性および信頼性の両方を確実にするシステムを提供することが不可欠である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許出願第11/053,273号

【非特許文献】

【0004】

【非特許文献1】シーラ・フランケルによる「RFC3566−AES−XCBC−MAC−96アルゴリズムおよびIPsecを伴うその使用」

【非特許文献2】ジャナカ・ディーパクマラ、ハワード・M・ヘイズおよびR・ベンカテザンによる「インターネットプロトコルセキュリティ(IPSEC)のためのメッセージ認証コード(MAC)アルゴリズムの性能比較」

【非特許文献3】ネバダ大学のジョン・ブラック、カリフォルニア大学デービス校のフィリップ・ロガウェイによる「AES動作モードに関するNISTに対するコメント:CBC MACを使用する任意長メッセージのハンドリングについての提言」

【発明の概要】

【0005】

ファームウェアの完全性をベリファイすることは、安全かつ信頼性のあるメモリカードを実行するのに重要な態様の1つである。本発明は、メモリカード、ユニバーサル・シリアル・バス(USB)フラッシュドライブ、または他のメモリシステムを実行するファームウェアの完全性をベリファイする。ファームウェアの完全性は、実行される前にベリファイされる。これにより、工場のファームウェアではないファームウェアの実行が防止される。このことが特に重要なのは、コンテンツが自由にコピーされないように保護することを意図した暗号化アルゴリズムを含むセキュリティ機構を、工場のファームウェアが備えているからである。本発明は、メモリカードにおいて実施される場合に、工場以外のファームウェア、または安全なコンテンツのコピーを許可するような変更された工場のファームウェアをカードが実行することを防止する。よって、ハッカーは、カードを「騙して(trick) 」間違ったファームウェアを実行させるようにすることができなくなる。ベリファイ処理は、任意の記憶データの完全性をベリファイするためにも使用することができる。

【0006】

本発明の一態様は、メモリ記憶装置の動作を開始するための方法に関し、装置の大容量記憶ユニット内にファームウェアを提供するステップと、ファームウェアを暗号化エンジンに通すステップと、ファームウェアについてのハッシュ値を前記暗号化エンジンで計算するステップと、計算されたハッシュ値を記憶されたハッシュ値と比較するステップと、計算されたハッシュ値が記憶されたハッシュ値と一致する場合に、ファームウェアを実行するステップと、を含む。

【0007】

本発明の他の態様は、大容量記憶装置に関し、フラッシュメモリと、読み出し専用メモリと、フラッシュメモリに記憶された、大容量記憶装置のデータ記憶動作を制御する第1の命令セットと、第1の命令セットをフラッシュから実行可能なランダムアクセスメモリへのシャドウイングする、読み出し専用メモリ内に常駐する第2の命令セットと、を備える。暗号化エンジンが、大容量記憶装置のハードウェア回路において実施され、フラッシュメモリに記憶されるおよびそこから読み出されるデータを暗号化および復号化することができる。暗号化エンジンは、第1の命令セットの完全性をベリファイするように動作可能である。

【0008】

本発明のさらに他の態様は、メモリ記憶装置の動作を開始するための他の方法に関する。この方法は、装置の大容量記憶ユニット内にファームウェアを提供するステップと、ファームウェアを大容量記憶ユニットからランダムアクセスメモリへコピーする、読み出し専用メモリ内の第1の命令セットを実行するステップと、を含む。また、この方法は、暗号化エンジンを使用してブートファームウェアの完全性をベリファイするステップと、完全性がベリファイされた後に、ランダムアクセスメモリからファームウェアをマイクロプロセッサで実行するステップと、を含む。

【0009】

本発明のさらなる態様、利点、および特徴は、以下の例示の例の説明に含まれ、その説明は、添付の図面と共に解釈されるべきであり、同様の参照番号は、特に指示のない限り、全ての図を通じて同一の特徴を説明するために使用される。本願明細書において援用されているすべての特許、特許出願、記事、および他の出版物は、あらゆる目的のためにその全体が本願明細書において参照により援用されている。

【図面の簡単な説明】

【0010】

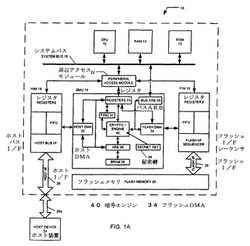

【図1A】本発明の一実施形態によるシステム10の概略図である。

【図1B】本発明の他の実施形態によるシステム10の概略図である。

【図2】図1に示すフラッシュメモリのメモリ図である。

【図3】ブートローダ200aの概略図である。

【図4】ファームウェアのハードウェアベースの完全性チェックを含むブート処理の部分のフローチャートである。

【図5】図4の完全性ベリファイ処理410のフローチャートである。

【図6】ブート中のハードウェアループのフローチャートである。

【図7】ブート中のファームウェアループのフローチャートである。

【発明を実施するための形態】

【0011】

メッセージ認証コード(MAC)は、何らかのコンテンツ(または、メッセージ)から計算されるコンテンツの完全性を証明するために使用される数である。その目的は、コンテンツが変更されたかどうかを検出することである。メッセージ認証コードは、メッセージおよび何らかの秘密データから計算されるハッシュである。秘密データを知らなければ、偽造することは困難である。MACは、秘密鍵を使用するDESまたはAES暗号に基づくアルゴリズムを使用して計算される。その後、MACは、メッセージと共に記憶または送られる。受信者は、同一のアルゴリズムおよび秘密鍵を使用してMACを再計算し、それを記憶または送られたものと比較する。それらが同一であれば、コンテンツまたはメッセージは改変されていないものとされる。

【0012】

DES(データ暗号化標準)は、56ビットキーを使用するNIST標準の暗号化暗号である。NISTによって1977年に採用されたが、2001年にはAESが公式標準として取って代わった。DESは、4つの異なる動作モードにおける64ビットのブロックを処理する対称ブロック暗号であって、電子コードブック(ECB)が最も一般的である。

【0013】

トリプルDESは、いくつかの複数パス方法を追加することによって安全性を増強した。例えば、1つの鍵で暗号化し、その結果を第2の鍵で復号化し、それを再び第3の鍵で暗号化する。しかし、追加のパスは、多大な計算時間を処理に追加する。DESは、最強のセキュリティを必要としないアプリケーションにおいて今でも使用されている。

【0014】

改良形暗号化標準(Advanced Encryption Standard(「AES」))は、NIST標準の暗号化暗号であって、128ビットのブロック長と、128,192,または256ビットのキー長とを使用する。2001年にトリプルDES方法に公式に取って代わったAESは、ベルギーのヨアン・ダーメン (Joan Daemen)およびビンセント・ライメン (Vincent Rijmen) によって開発されたラインダールアルゴリズムを使用する。AESは、3つに変わって1つのパスで暗号化でき、そのキーサイズは、トリプルDESの168ビットより大きい。

【0015】

セキュアハッシュアルゴリズム(SHA−1)は、20バイトの出力を生じさせる。NISTおよびNSAは、これをデジタル署名標準と共に使用するように設計し、現在幅広く使用されている。MD5は、本発明と共に使用されるような他のハッシュ関数である。前述した標準および様々な他のアルゴリズムは、本発明と共に使用されるようなハッシュ関数および値の例示的な例である。今日利用可能かつ将来開発される他の形のハッシュ関数および値も、本発明と共に使用できる。

【0016】

前述した規格および様々な他のアルゴリズムおよび/または標準は、暗号化技術における当業者に周知であるが、以下の出版物は有益であり、その全体が本願明細書において参照により援用されている。これら出版物とは、シーラ・フランケル (Sheila Frankel) による「RFC3566−AES−XCBC−MAC−96アルゴリズムおよびIPsecを伴うその使用 (RFC3566-The AES-XCBC-MAC-96 Algorithm and Its Use With IPsec) 」,アメリカ合衆国、メリーランド、20899、ゲイザースブルグ、820 ウエスト・ダイアモンド・アベニュー、ルーム 677にあるNIST−国立標準技術研究所 (National Institute of Standards and Technology), (http://www.faqs.org/rfcs/rfc3566.html において利用可能)(非特許文献1)、ジャナカ・ディーパクマラ (Janaka Deepakumara) 、ハワード・M・ヘイズ (Howard M. Heys) およびR・ベンカテザン (R. Venkatesan)による「インターネットプロトコルセキュリティ(IPSEC)のためのメッセージ認証コード(MAC)アルゴリズムの性能比較 (Performance Comparison of Message Authentication Code (MAC) Algorithms for the Internet Protocol Security (IPSEC))」,電気およびコンピュータエンジニアリング(Electrical and Computer Engineering) ,ニューファンドランドのメモリアル大学(カナダ、A1B3S7、ニューファンドランド、セント・ジョンズ), http://www.engr.mun.ca/~howard/PAPERS/necec_2003b.pdf (非特許文献2)、およびリノにあるネバダ大学のジョン・ブラック (John Black) 、カリフォルニア大学デービス校のフィリップ・ロガウェイ (Philip Rogaway) による「AES動作モードに関するNISTに対するコメント:CBC MACを使用する任意長メッセージのハンドリングについての提言 (Comments to NIST concerning AES Modes of Operations: A Suggestion for Handling Arbitrary-Length Messages with the CBC Mac)」,(http://csrc.nist.gov/CryptoToolkit/modes/proposedmodes/xcbc-mac/xcbc-mac-spec.pdfにおいて利用可能)(非特許文献3)である。

【0017】

メモリシステムアーキテクチャ

本発明の様々な態様が実施されるようなメモリシステム例を、図1Aのブロック図に示す。図1Aに示すように、メモリシステム10は、中央処理装置(CPU)または「コントローラ」12と、バッファ管理ユニット(BMU)14と、ホストインターフェイスモジュール(HIM)16と、フラッシュインターフェイスモジュール(FIM)18と、フラッシュメモリ20と、周辺アクセスモジュール22とを含む。メモリシステム10は、ホストインターフェイスバス26およびポート26aとを通じてホスト装置24と通信する。フラッシュメモリ20は、NAND形であってもよく、ホスト装置24に対してデータ記憶を提供する。CPU12のためのソフトウェアコードも、フラッシュメモリ20に記憶されてもよい。FIM18は、フラッシュインターフェイスバス28を通じて、および、場合によってはフラッシュメモリ20が着脱可能な要素であるときには図に示さないポートとを通じて、フラッシュメモリ20に接続する。HIM16は、デジタルカメラ、パーソナルコンピュータ、個人用携帯情報端末(PDA)、MP−3プレーヤ、携帯電話、または他のデジタル装置のようなホストシステムに対する接続に適している。周辺アクセスモジュール22は、CPU12と通信するために、FIM、HIM、およびBMUなどの適切なコンローラモジュールを選択する。一実施形態において、点線のボックス内のシステム10のすべての要素が、メモリカードなどの単一のユニット、好ましくはカード内に密封されていてもよい。

【0018】

バッファ管理ユニット14は、ホスト直接メモリアクセスユニット(HDMA)32と、フラッシュ直接メモリアクセスユニット(FDMA)34と、アービタ36と、CPUバスアービタ35と、レジスタ33と、ファームウェア完全性回路(FWIC)31と、バッファランダムアクセスメモリ(BRAM)38と、暗号化エンジン(encryption engine) とも称される暗号エンジン(crypto engine) 40とを備える。アービタ36は、1つのマスタまたはイニシエータ(HDMA32、FDMA34、またはCPU12であってもよい)だけが任意のときにアクティブであることができ、かつ、スレーブまたはターゲットはBRAM38であるような共有バスアービタである。アービタは、適切なイニシエータの要求をBRAM38へ振り向ける役割を担う。HDMA32およびFDMA34は、HIM16、FIM18、およびBRAM38またはRAM11間で搬送されるデータを担当する。CPUバスアービタ35は、例えば暗号エンジンを迂回したい場合のような所定の状況において使用されるシステムバス15を通じた暗号エンジン40およびフラッシュDMA34からRAM11への直接データ搬送を可能にする。HDMA32の動作およびFDMA34の動作は従来どおりであり、本願明細書において詳述する必要はない。BRAM38は、ホスト装置24およびフラッシュメモリ20間を通るデータを記憶するために使用される。HDMA32およびFDMA34は、HIM16/FIM18およびBRAM38またはCPU RAM12a間のデータの転送と、セクタ完了の指摘という役割を担う。

【0019】

フラッシュメモリ20からのデータがホスト装置24によって読み出されると、メモリ20内の暗号化されたデータは、バス28、FIM18、FDMA34、および暗号エンジン40を通じてフェッチされ、暗号化されたデータは、BRAM38において復号化および記憶される。その後、復号化されたデータは、BRAM38からHDMA32、HIM16、およびバス26を通じてホスト装置24へ送られる。BRAM38からフェッチされたデータは、HDMA32へ渡される前に、暗号エンジン40によって暗号化されてもよく、ホスト装置24へ送られるデータは、メモリ20に記憶されたデータを暗号化したものと比べて異なるキーおよび/またはアルゴリズムによって再び暗号化される。前述した処理において復号化されたデータをBRAM38に記憶すると、権限のないアクセスに対してデータが脆弱となりうるが、その代わりに、BRAM38へ送る前に、メモリ20からのデータを復号化して、暗号エンジン40によって再び暗号化してもよい。その後、BRAM38内の暗号化されたデータは、以前のようにホスト装置24へ送られる。これは、読み出し処理中のデータストリームを示すものである。

【0020】

データがホスト装置24によってメモリ20に書き込まれると、データストリームの方向が逆となる。例えば、暗号化されていないデータがホスト装置によってバス26、HIM16、HDMA32を介して暗号エンジン40へ送られると、そのようなデータは、BRAM38に記憶される前に、エンジン40によって暗号化されてもよい。代わりに、暗号化されていないデータは、BRAM38に記憶されてもよい。その後、データは、メモリ20へ向かう途中でFDMA34へ送られる前に暗号化される。

【0021】

図1Bは、システム10の他の実施形態を示す。この好ましい実施形態において、暗号化エンジン40およびファームウェア完全性回路31は、コントローラ12の一部として示されている。これらの要素は、コントローラの一部であるのが好ましいが、ある実施形態において、コントローラのパッケージ内に統合されていなくてもよい。前述したように、RAM11、フラッシュメモリ20、およびコントローラ12は、すべてシステムバス15に接続されている。ホストインターフェイスバス26は、ホスト装置24(図示せず)と通信する。

【0022】

ファームウェアの完全性ベリファイ

図2は、システム10を実行するファームウェア200を含むフラッシュメモリのメモリ空間の図である。システムファームウェア200は、フラッシュメモリ20内に常駐して変更不可能なのが好ましいブートローダ(BLR)部200aと、フラッシュメモリ20内に常駐して必要に応じて変更可能なシステムファームウェア200bとを備える。ある実施形態において、直接またはシャドウイングされたコピーから実行される場合にBLR部200aをポイントする追加のファームウェアがROM13内にあってもよい。システムファームウェア200のサイズは、実行元であるRAMモジュールよりも大きいので、システムファームウェアは、オーバーレイと称されるより小さい部分に分割される。好ましい実施形態におけるBLRの完全性ベリファイは、固有のその場の(on the fly)計算を使用し、当該計算において、期待値がデータ自身に記憶され、コピーがフラッシュメモリ20以外のメモリ内のレジスタに一時的に記憶される。しかし、ある実施形態において、BLRの完全性をベリファイするために使用される手法は、システムファームウェア200bの完全性をベリファイするためにも使用可能である。前述したように、任意のハッシュ値およびハッシュ手法を使用可能であるが、MACまたはSHA−1の値が現時点においては好ましく、簡素化のために、好ましい一実施形態において、一方または他方の使用について説明する。通常、SHA−1のダイジェストをMAC値の代わりに使用してもよく、その逆であってもよい。MAC値を使用する利点として、MAC値が、ハードウェアと、MACを作成したハードウェアのキーとに関連していることが挙げられる。SHA−1値は、単にデータ自体に基づいて所定のデータセットのために作成可能だが、MAC値は、キーなしでは再作成することは不可能であり、したがって、より強固なセキュリティを提供する。特定的には、MAC値を作成するには、暗号化エンジン40の不揮発性メモリに記憶されたキー99を使用しなければならないが、MAC値を再作成するには、他のプロセッサを使用することができない。例えば、ハッカーは、ファームウェアおよび関連するMAC値を複製するために、システム外部から他のプロセッサを使用することはできない。

【0023】

同じくフラッシュメモリに記憶されるのは、様々なユーザデータファイル204である。図に示していない様々な他のプログラムおよびデータがフラッシュメモリ(図示せず)内に記憶されてもよい。これらのファイルは、暗号化されてもよく、その完全性は、同様または他のやり方でベリファイされてもよい。

【0024】

図3は、完全性チェックモードの場合のシステム10によって使用されるいつかのデータセクタの構造を示す。特に、BLRは、この構造を使用するのが好ましい。BLRコード307自体は、他のデータ間に挟まれるようにしてBLR201aを構成している。BLRコード307がロードされる前に、いくつかの構成情報がロードされる。構成情報は、ファイル識別(FID)セクタ1および7に含まれている。BLRコード307に続いて、メッセージ認証コードセクタ309がある。MACセクタ309内には、BLRコード307の対応する部分についてのMAC値がある。これが、より詳細に以下に説明する、図5において計算された値と比較されるMAC値である。MACセクタは、様々な長さのデータを収容するためにゼロで埋められて、セクタの最終128ビットをMACが常に占めるようにする。BLRコード307は、BLR部分200a内のフラッシュメモリ20に記憶され、構成情報もフラッシュメモリ20に記憶されてもよい。

【0025】

図4は、BLRコードおよびファームウェアの完全性をベリファイすることを含む、システム10をブートおよび実行する処理を示す。特に、図4は、ファームウェア200のBLR部分200aに関するような完全性ベリファイ処理の概観を含む。好ましい一実施形態において、システムファームウェア200bおよびアプリケーションファームウェアのベリファイは、BLRのベリファイとは別個のものであり、かつ、当該ベリファイの後に生じる。注目すべきなのは、ファームウェアは、BLRによって一度に全てロードされるわけではないということである。BLRは、いつかのモジュールのみ(RAM常駐ファームウェア)をロードし、他のモジュール(オーバーレイ)は、必要に応じてロードされ、RAM内の(複数の)同じ位置へスワップされる。

【0026】

システム10が起動すると、ステップ404に示すように、完全性チェックモードで起動することになる。一般的に、このモードにおいて、暗号エンジン40は、前述した説明および図5に詳細に示すように、すべての入力データのMAC値を計算している。この処理は、入力データが可変長であり得、かつ、NANDフラッシュメモリ20内の任意の位置に記憶されうることを保証するものである。好ましい実施形態において、データは、書き込まれたのと同一の順序で読み出され、最終のブロックの読み出しにはMACが含まれることになる。MAC比較の結果は、ファームウェアがいつでもチェックするのに利用可能である。ここで、図4に示す個々のステップを説明する。

【0027】

ステップ410において、システムは、同じく図5のフローチャートに詳しく見受けられる処理に従って、BLRの完全性をチェックする。これは、(システムが完全性チェックモードにある際に)フラッシュメモリ20からの他のデータがベリファイされたのと同じやり方でBLRが暗号エンジン40を通ることで行われる。ステップ420において、システムは、ステップ410において行われた完全性チェックの結果をチェックする。これは、図5に見受けられる処理200の完全性チェックのステップ270で記憶された、問題があるかないかを示す結果(フラグまたは他の指標)をチェックすることによって行われる。BLRがOKでない場合、システムは、ステップ430に見受けられるようなホストコマンドを待って、返品許可(RMA)状態として知られる障害分析状態へシステムを送ることになる。この動作状態および他の動作状態またはモードについてのさらなる詳細については、ホルツマンら(Holtzman et al.) の同時継続中の米国特許出願第11/053,273号「ライフサイクルフェーズを有するセキュアメモリカード (SECURE MEMORY CARD WITH LIFE CYCLE PHASES)」(特許文献1)を参照されたい。この特許出願は、その全体が本願明細書において参照により援用されている。しかし、BLRがOKの場合、システムは、ステップ440において、BLRを実行することになる。ブートが完了すると、システムは、図4のステップ440に見受けられるように、BLR自身に含まれる命令に基づいて、完全性チェックモードを去ることになる。BLRは、数多くの命令または「ステップ」を含む。そのうちの1つは、ステップ440aであって、BLRは、暗号エンジン40を通常モードに再構築し、言い換えれば、完全性チェックモードから暗号エンジン40を抜け出させる。BLRは、ステップ440bに示すように、システムにシステムファームウェア200bの完全性をチェックさせる命令も含む。

【0028】

図5は、図4に関して説明したような完全性ベリファイ処理410のフローチャートである。これは、システムが完全性チェックモードにある場合に、フラッシュメモリ20に記憶されたデータを読み出しおよびハッシュする一般的な処理を示す。NAND形フラッシュメモリの読み出しを例示の目的のために説明するものであるが、本発明は、大容量記憶の目的のために使用される任意の種類のメモリまたは媒体と共に使用することができる。繰り返すが、MAC値の使用を例示し、かつ説明するが、他のハッシュ値を使用してもよい。図2Bの表は、一般的に、対応する開始バイトと、バイト数とをエントリ毎に含むことになる(図示せず)。一般的に、好ましい実施形態において、処理全体は、NANDの完全性をページ毎ベースでベリファイするために使用される。この処理は、NANDに記憶された任意のデータの完全性をベリファイすることになる。データがたまたまファームウェアの場合には、ファームウェアの完全性をベリファイする。このようなページ毎の比較が好ましいが、より小さな単位またはより大きな単位での比較を行ってもよい。

【0029】

好ましい一実施形態における完全性ベリファイ処理は、図5に示すような固有の計算と制御ループとを使用する。ループは、連続する計算および比較動作を伴う。典型的には、ベリファイ手法において、何らかの種類の「正しい(correct) 」値または期待値が予め記憶され、計算された値と比較される。図5に示す処理を有する好ましい一実施形態において、「正しい」値または期待値が、「被テストデータ(data under test) 」内に記憶される。それは、特定的には、前述した好ましい実施形態において、データブロックの最終128ビット内にある。読み出し中のセクタの最終128ビットは、実際上の目的のためには、正しいセクタが読み出された際に、記憶されたMAC(または他のハッシュ値)といったん対応するだけとなる。(誤った肯定(false positive))一致が最終以外のページで生じるであろう確率は非常に小さいので、これは実際上の目的では無視できる。

【0030】

ステップ210において、NANDブロック(i)が読み出される。次に、ステップ215において、ブロックがチェックされて、必要があれば、ECC回路でオプションで訂正される。ECCは周知であり、データ内の物理的な誤りを訂正するために使用できる。完全性ベリファイ処理と共にECCを使用することが好ましいが、これは必須ではなく、完全性は、ステップ215を含んでも含まなくてもベリファイされる。ステップ220において、ハッシュ値が計算され、好ましい一実施形態において、MAC値が好ましい。ブロック(i)についてのMACが計算されるが、完全性ベリファイ処理410において、結果生じたMACは、ブロック0から(i)までを対象として含み、数学的には以下のように表現できる。

MAC[0...(i)]=MAC[MAC[0...(i−1)],

block(i)]

【0031】

ステップ220での計算後、ステップ260において比較が行われる。ステップ260において、コントローラのハードウェア、特にFWIC31が、ブロック(i)の最終128ビットを以前記憶されたMAC、すなわちMAC[0...(i−1)]と比較する。ステップ270において、比較結果がシステムのメモリに記憶される。ステップ260の比較が最初に行われる際には、MACレジスタに「記憶された」値は、実際には、適切な記憶済みMAC値ではないことになるが、どんな値であれたまたまレジスタ内にあることになり、よって、ランダムであると考えられる。その後、ステップ270において、比較結果は記憶されることになる。第1のブロックについて、比較はチェックされないことになる。ステップ230において、ステップ220において計算されたMAC値は、コントローラのレジスタ内、好ましくはFWIC31のレジスタ内に記憶されることになる。次に、ステップ235において、(i)の値が1増分されるようにカウンタが増分され、次のブロックがまたステップ210で読み出されることになる。ループは、ブロック(i)が読み出されるまで継続することになる。最終ブロックが読み出されて暗号化エンジンによって処理されると、ステップ230で記憶されたMACと最終128ビットが一致すれば、比較は一致を生じさせて、ステップ270において記憶された結果は、完全性がハードウェアによってベリファイされたことを反映することになる。BLRの最終ページが読み出された場合にのみ、完全性がベリファイされたことを示すために一致が使用されることになる。これまでのすべての一致(誤った真の値(false true value))は、無視されることになる。値が異なる場合には、データの完全性に問題があることを示すこととなる。逆に、値が同一の場合には、データの完全性が確実となる。

【0032】

一致が生じた後に、ステップ230において、MAC値は再び更新されることになるが、これは影響を及ぼさない、ループの冗長動作である。この連続計算処理によって、ハードウェアは、不確定なコンテンツのサイズをベリファイすることができる。言い換えれば、MAC値を適切に計算することができ、ブロックからなるファイルのブロック数またはサイズをまず確認する必要なく、完全性をハードウェアによってベリファイすることができる。

【0033】

前述した処理は、メモリカードのフラッシュメモリ20内に常駐する任意のデータについて、ある動作状態またはモード、特に完全性チェックモードにおいて使用される。本発明によるメモリカードの好ましい一実施形態において、当該データのいくらかは、実行されるとメモリカードを実行するファームウェアである。特に、システム10の電源投入の際に、システムがその通常の動作状態またはテスト状態である場合に、暗号エンジン40は、任意の入力データの完全性をベリファイするために、(完全性チェックモードにおいて開始することによって)暗号エンジン40自体を初期化する。データがたまたまファームウェアである場合には、BMU14および特に暗号エンジン40を通る際にファームウェアの完全性がベリファイされる。記憶された結果(完全性自体ではない)は、一実施形態において、ROM13に記憶されたコード内の命令を伴うソフトウェアによってチェックできる。注意すべきなのは、ROM13に記憶されたコードは結果をチェックするものの、データのフローを開始してもよく、これはフラッシュメモリ内のファームウェアの完全性をベリファイする際には含まれないということである。言い換えれば、コードは、ベリファイするためにファームウェアの数値計算もデータ操作も行う役割はない。ファームウェアの完全性をベリファイするのは、コントローラ12またはBMU14、FWIC31、および暗号エンジン40のハードウェアであり、これには、ブートローダ(BLR)部分と、ある実施形態において、ファームウェアの他の部分も含まれる。

【0034】

図5で説明した処理は、ハードウェア(HW)とファームウェア(FW)との両方が関与する。前述したように、ハードウェアが完全性チェックを行うのに対して、ファームウェアは、HW完全性チェックの末尾のフラグセットを単にチェックするだけである。HWおよびSWの機能または「ループ」を、それぞれ図6および図7にさらに詳細に示す。

【0035】

図6を参照すると、ステップ320において、システムに電源が投入される。ステップ322において、コントローラのハードウェアが、FW完全性モードを開始する。これは、2つの中心的な行為を備える。第1は、図1のFWIC31を作動させることである。いったん作動されたFWIC31は、図6の残りのステップをうまくまとめあげ、これによって、暗号エンジン40と共に、ファームウェアのBLR部分の完全性をチェックする。第2の行為には、暗号エンジン40によって使用される暗号アルゴリズムを選択することが含まれる。前述したように、暗号エンジン40のハードウェアは、様々な互いに異なるアルゴリズムでデータを暗号化および復号化するように構成されている。

【0036】

ステップ328において、コントローラのハードウェアは、入力ブロックのダイジェストを計算する。この計算は、暗号エンジン40によって行われる。次に、ステップ330において、ステップ328において計算されたダイジェストを、以前のダイジェストの値と比較する。前述したように、値を保持するレジスタがチェックされて、ループの反復毎に比較されるが、最初の反復の際には、レジスタ内の値はランダムである。その後、完全性を示すフラグが、ステップ332において設定される。HWがファームウェアのBLR部分の完全性をベリファイしたかを確認するために、このフラグがシステムのファームウェアによってチェックされることになる。

【0037】

図7は、図6においてHWが完全性をチェックする一方で生じるファームウェアのループを示す。ステップ320においてシステムに電源が投入された後に、ステップ340においてCPUが初期化される。その後、ステップ342において、構成データ(好ましい一実施形態において、図3のFID1)が最初の有効ページに読み出される。次に、ステップ344において、システムは、BLR 201Aの開始および終了ページを抽出する。これがいったんわかると、BLRページのすべてが読み出される。各ページが読み出されるにつれて、誤り訂正符号(ECC)が生成される。前述したように、ECC回路動作は周知であり、データ内の物理的な誤りをある一定の限界まで訂正するために使用することができる。完全性ベリファイ処理と共にECCを使用することが好ましいが、これは必須ではなく、完全性は、ECCを使用してもしなくてもベリファイされる。ページが読み出された後に、ステップ348においてECC回路でチェックされ、OKでない場合には、ページはECC訂正機構で訂正されるか、またはステップ352において代替のページが取り出されることになる。訂正または新規のページがOKであるとステップ354において判断されると、システムは、ステップ350において、読み出されるべきページがさらにあるかどうかをチェックする。そうである場合には、システムはステップ346へ戻り、他のページを読み出す。ステップ354において訂正されたまたは代替コピーがOKではないとステップ354が示す場合には、失敗状態がステップ356において示されることになる。ステップ350においてこれ以上ページがないと判断されると、失敗は示されず、システムは、完全性フラグ(図6に示すようにハードウェアによって設定されている)をステップ360においてチェックすることになる。ステップ360において、BLRがOKであるとフラグが示す場合には、HWによってベリファイされたので、ステップ362においてBLRが実行されることになる。この実行は、図4のステップ440において示したのと同じである。

【0038】

この完全性チェックは、ファームウェアの一部分、すなわちBLRについてのみ行われるが、ファームウェアのすべてもこのようにチェックすることができ、また、この説明はファームウェアのブートスラップを使用する好ましい実施形態に関することが理解されるべきである。加えて、本願において使用されるようなメモリカードという用語は、USBフラッシュドライブの形式要因をも含んでいるつもりである。

【0039】

本発明の様々な態様についてそれらの例示の実施形態に関して説明してきたが、本発明が、添付の特許請求の範囲の全範囲内においてその権利が保護されるべきであることが理解できよう。

【技術分野】

【0001】

本発明は、一般的には、安全なコンテンツを有するメモリカードおよび当該コンテンツの暗号化に関し、特に、安全なメモリカードを実行するファームウェアの完全性(integrity) をベリファイすることに関する。

【背景技術】

【0002】

商用のメモリカードの機能を工場から出荷する前にベリファイし、工場から出荷されてもハッカーから保護されていることを確実にすることは、極めて重要である。デジタル権利管理の出現と、音楽および映画などの保護されたコンテンツの普及とに伴い、カードのコンテンツが自由にコピーできないことを確実にする必要がある。ハッカーがこれを行おうと試みるやり方の1つとして、カード内のコンテンツを無断使用することができるようにするために、メモリカードを実行するファームウェアを変更または取り替えさえするということがある。よって、カード上で常時実行するファームウェアの完全性および信頼性の両方を確実にするシステムを提供することが不可欠である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許出願第11/053,273号

【非特許文献】

【0004】

【非特許文献1】シーラ・フランケルによる「RFC3566−AES−XCBC−MAC−96アルゴリズムおよびIPsecを伴うその使用」

【非特許文献2】ジャナカ・ディーパクマラ、ハワード・M・ヘイズおよびR・ベンカテザンによる「インターネットプロトコルセキュリティ(IPSEC)のためのメッセージ認証コード(MAC)アルゴリズムの性能比較」

【非特許文献3】ネバダ大学のジョン・ブラック、カリフォルニア大学デービス校のフィリップ・ロガウェイによる「AES動作モードに関するNISTに対するコメント:CBC MACを使用する任意長メッセージのハンドリングについての提言」

【発明の概要】

【0005】

ファームウェアの完全性をベリファイすることは、安全かつ信頼性のあるメモリカードを実行するのに重要な態様の1つである。本発明は、メモリカード、ユニバーサル・シリアル・バス(USB)フラッシュドライブ、または他のメモリシステムを実行するファームウェアの完全性をベリファイする。ファームウェアの完全性は、実行される前にベリファイされる。これにより、工場のファームウェアではないファームウェアの実行が防止される。このことが特に重要なのは、コンテンツが自由にコピーされないように保護することを意図した暗号化アルゴリズムを含むセキュリティ機構を、工場のファームウェアが備えているからである。本発明は、メモリカードにおいて実施される場合に、工場以外のファームウェア、または安全なコンテンツのコピーを許可するような変更された工場のファームウェアをカードが実行することを防止する。よって、ハッカーは、カードを「騙して(trick) 」間違ったファームウェアを実行させるようにすることができなくなる。ベリファイ処理は、任意の記憶データの完全性をベリファイするためにも使用することができる。

【0006】

本発明の一態様は、メモリ記憶装置の動作を開始するための方法に関し、装置の大容量記憶ユニット内にファームウェアを提供するステップと、ファームウェアを暗号化エンジンに通すステップと、ファームウェアについてのハッシュ値を前記暗号化エンジンで計算するステップと、計算されたハッシュ値を記憶されたハッシュ値と比較するステップと、計算されたハッシュ値が記憶されたハッシュ値と一致する場合に、ファームウェアを実行するステップと、を含む。

【0007】

本発明の他の態様は、大容量記憶装置に関し、フラッシュメモリと、読み出し専用メモリと、フラッシュメモリに記憶された、大容量記憶装置のデータ記憶動作を制御する第1の命令セットと、第1の命令セットをフラッシュから実行可能なランダムアクセスメモリへのシャドウイングする、読み出し専用メモリ内に常駐する第2の命令セットと、を備える。暗号化エンジンが、大容量記憶装置のハードウェア回路において実施され、フラッシュメモリに記憶されるおよびそこから読み出されるデータを暗号化および復号化することができる。暗号化エンジンは、第1の命令セットの完全性をベリファイするように動作可能である。

【0008】

本発明のさらに他の態様は、メモリ記憶装置の動作を開始するための他の方法に関する。この方法は、装置の大容量記憶ユニット内にファームウェアを提供するステップと、ファームウェアを大容量記憶ユニットからランダムアクセスメモリへコピーする、読み出し専用メモリ内の第1の命令セットを実行するステップと、を含む。また、この方法は、暗号化エンジンを使用してブートファームウェアの完全性をベリファイするステップと、完全性がベリファイされた後に、ランダムアクセスメモリからファームウェアをマイクロプロセッサで実行するステップと、を含む。

【0009】

本発明のさらなる態様、利点、および特徴は、以下の例示の例の説明に含まれ、その説明は、添付の図面と共に解釈されるべきであり、同様の参照番号は、特に指示のない限り、全ての図を通じて同一の特徴を説明するために使用される。本願明細書において援用されているすべての特許、特許出願、記事、および他の出版物は、あらゆる目的のためにその全体が本願明細書において参照により援用されている。

【図面の簡単な説明】

【0010】

【図1A】本発明の一実施形態によるシステム10の概略図である。

【図1B】本発明の他の実施形態によるシステム10の概略図である。

【図2】図1に示すフラッシュメモリのメモリ図である。

【図3】ブートローダ200aの概略図である。

【図4】ファームウェアのハードウェアベースの完全性チェックを含むブート処理の部分のフローチャートである。

【図5】図4の完全性ベリファイ処理410のフローチャートである。

【図6】ブート中のハードウェアループのフローチャートである。

【図7】ブート中のファームウェアループのフローチャートである。

【発明を実施するための形態】

【0011】

メッセージ認証コード(MAC)は、何らかのコンテンツ(または、メッセージ)から計算されるコンテンツの完全性を証明するために使用される数である。その目的は、コンテンツが変更されたかどうかを検出することである。メッセージ認証コードは、メッセージおよび何らかの秘密データから計算されるハッシュである。秘密データを知らなければ、偽造することは困難である。MACは、秘密鍵を使用するDESまたはAES暗号に基づくアルゴリズムを使用して計算される。その後、MACは、メッセージと共に記憶または送られる。受信者は、同一のアルゴリズムおよび秘密鍵を使用してMACを再計算し、それを記憶または送られたものと比較する。それらが同一であれば、コンテンツまたはメッセージは改変されていないものとされる。

【0012】

DES(データ暗号化標準)は、56ビットキーを使用するNIST標準の暗号化暗号である。NISTによって1977年に採用されたが、2001年にはAESが公式標準として取って代わった。DESは、4つの異なる動作モードにおける64ビットのブロックを処理する対称ブロック暗号であって、電子コードブック(ECB)が最も一般的である。

【0013】

トリプルDESは、いくつかの複数パス方法を追加することによって安全性を増強した。例えば、1つの鍵で暗号化し、その結果を第2の鍵で復号化し、それを再び第3の鍵で暗号化する。しかし、追加のパスは、多大な計算時間を処理に追加する。DESは、最強のセキュリティを必要としないアプリケーションにおいて今でも使用されている。

【0014】

改良形暗号化標準(Advanced Encryption Standard(「AES」))は、NIST標準の暗号化暗号であって、128ビットのブロック長と、128,192,または256ビットのキー長とを使用する。2001年にトリプルDES方法に公式に取って代わったAESは、ベルギーのヨアン・ダーメン (Joan Daemen)およびビンセント・ライメン (Vincent Rijmen) によって開発されたラインダールアルゴリズムを使用する。AESは、3つに変わって1つのパスで暗号化でき、そのキーサイズは、トリプルDESの168ビットより大きい。

【0015】

セキュアハッシュアルゴリズム(SHA−1)は、20バイトの出力を生じさせる。NISTおよびNSAは、これをデジタル署名標準と共に使用するように設計し、現在幅広く使用されている。MD5は、本発明と共に使用されるような他のハッシュ関数である。前述した標準および様々な他のアルゴリズムは、本発明と共に使用されるようなハッシュ関数および値の例示的な例である。今日利用可能かつ将来開発される他の形のハッシュ関数および値も、本発明と共に使用できる。

【0016】

前述した規格および様々な他のアルゴリズムおよび/または標準は、暗号化技術における当業者に周知であるが、以下の出版物は有益であり、その全体が本願明細書において参照により援用されている。これら出版物とは、シーラ・フランケル (Sheila Frankel) による「RFC3566−AES−XCBC−MAC−96アルゴリズムおよびIPsecを伴うその使用 (RFC3566-The AES-XCBC-MAC-96 Algorithm and Its Use With IPsec) 」,アメリカ合衆国、メリーランド、20899、ゲイザースブルグ、820 ウエスト・ダイアモンド・アベニュー、ルーム 677にあるNIST−国立標準技術研究所 (National Institute of Standards and Technology), (http://www.faqs.org/rfcs/rfc3566.html において利用可能)(非特許文献1)、ジャナカ・ディーパクマラ (Janaka Deepakumara) 、ハワード・M・ヘイズ (Howard M. Heys) およびR・ベンカテザン (R. Venkatesan)による「インターネットプロトコルセキュリティ(IPSEC)のためのメッセージ認証コード(MAC)アルゴリズムの性能比較 (Performance Comparison of Message Authentication Code (MAC) Algorithms for the Internet Protocol Security (IPSEC))」,電気およびコンピュータエンジニアリング(Electrical and Computer Engineering) ,ニューファンドランドのメモリアル大学(カナダ、A1B3S7、ニューファンドランド、セント・ジョンズ), http://www.engr.mun.ca/~howard/PAPERS/necec_2003b.pdf (非特許文献2)、およびリノにあるネバダ大学のジョン・ブラック (John Black) 、カリフォルニア大学デービス校のフィリップ・ロガウェイ (Philip Rogaway) による「AES動作モードに関するNISTに対するコメント:CBC MACを使用する任意長メッセージのハンドリングについての提言 (Comments to NIST concerning AES Modes of Operations: A Suggestion for Handling Arbitrary-Length Messages with the CBC Mac)」,(http://csrc.nist.gov/CryptoToolkit/modes/proposedmodes/xcbc-mac/xcbc-mac-spec.pdfにおいて利用可能)(非特許文献3)である。

【0017】

メモリシステムアーキテクチャ

本発明の様々な態様が実施されるようなメモリシステム例を、図1Aのブロック図に示す。図1Aに示すように、メモリシステム10は、中央処理装置(CPU)または「コントローラ」12と、バッファ管理ユニット(BMU)14と、ホストインターフェイスモジュール(HIM)16と、フラッシュインターフェイスモジュール(FIM)18と、フラッシュメモリ20と、周辺アクセスモジュール22とを含む。メモリシステム10は、ホストインターフェイスバス26およびポート26aとを通じてホスト装置24と通信する。フラッシュメモリ20は、NAND形であってもよく、ホスト装置24に対してデータ記憶を提供する。CPU12のためのソフトウェアコードも、フラッシュメモリ20に記憶されてもよい。FIM18は、フラッシュインターフェイスバス28を通じて、および、場合によってはフラッシュメモリ20が着脱可能な要素であるときには図に示さないポートとを通じて、フラッシュメモリ20に接続する。HIM16は、デジタルカメラ、パーソナルコンピュータ、個人用携帯情報端末(PDA)、MP−3プレーヤ、携帯電話、または他のデジタル装置のようなホストシステムに対する接続に適している。周辺アクセスモジュール22は、CPU12と通信するために、FIM、HIM、およびBMUなどの適切なコンローラモジュールを選択する。一実施形態において、点線のボックス内のシステム10のすべての要素が、メモリカードなどの単一のユニット、好ましくはカード内に密封されていてもよい。

【0018】

バッファ管理ユニット14は、ホスト直接メモリアクセスユニット(HDMA)32と、フラッシュ直接メモリアクセスユニット(FDMA)34と、アービタ36と、CPUバスアービタ35と、レジスタ33と、ファームウェア完全性回路(FWIC)31と、バッファランダムアクセスメモリ(BRAM)38と、暗号化エンジン(encryption engine) とも称される暗号エンジン(crypto engine) 40とを備える。アービタ36は、1つのマスタまたはイニシエータ(HDMA32、FDMA34、またはCPU12であってもよい)だけが任意のときにアクティブであることができ、かつ、スレーブまたはターゲットはBRAM38であるような共有バスアービタである。アービタは、適切なイニシエータの要求をBRAM38へ振り向ける役割を担う。HDMA32およびFDMA34は、HIM16、FIM18、およびBRAM38またはRAM11間で搬送されるデータを担当する。CPUバスアービタ35は、例えば暗号エンジンを迂回したい場合のような所定の状況において使用されるシステムバス15を通じた暗号エンジン40およびフラッシュDMA34からRAM11への直接データ搬送を可能にする。HDMA32の動作およびFDMA34の動作は従来どおりであり、本願明細書において詳述する必要はない。BRAM38は、ホスト装置24およびフラッシュメモリ20間を通るデータを記憶するために使用される。HDMA32およびFDMA34は、HIM16/FIM18およびBRAM38またはCPU RAM12a間のデータの転送と、セクタ完了の指摘という役割を担う。

【0019】

フラッシュメモリ20からのデータがホスト装置24によって読み出されると、メモリ20内の暗号化されたデータは、バス28、FIM18、FDMA34、および暗号エンジン40を通じてフェッチされ、暗号化されたデータは、BRAM38において復号化および記憶される。その後、復号化されたデータは、BRAM38からHDMA32、HIM16、およびバス26を通じてホスト装置24へ送られる。BRAM38からフェッチされたデータは、HDMA32へ渡される前に、暗号エンジン40によって暗号化されてもよく、ホスト装置24へ送られるデータは、メモリ20に記憶されたデータを暗号化したものと比べて異なるキーおよび/またはアルゴリズムによって再び暗号化される。前述した処理において復号化されたデータをBRAM38に記憶すると、権限のないアクセスに対してデータが脆弱となりうるが、その代わりに、BRAM38へ送る前に、メモリ20からのデータを復号化して、暗号エンジン40によって再び暗号化してもよい。その後、BRAM38内の暗号化されたデータは、以前のようにホスト装置24へ送られる。これは、読み出し処理中のデータストリームを示すものである。

【0020】

データがホスト装置24によってメモリ20に書き込まれると、データストリームの方向が逆となる。例えば、暗号化されていないデータがホスト装置によってバス26、HIM16、HDMA32を介して暗号エンジン40へ送られると、そのようなデータは、BRAM38に記憶される前に、エンジン40によって暗号化されてもよい。代わりに、暗号化されていないデータは、BRAM38に記憶されてもよい。その後、データは、メモリ20へ向かう途中でFDMA34へ送られる前に暗号化される。

【0021】

図1Bは、システム10の他の実施形態を示す。この好ましい実施形態において、暗号化エンジン40およびファームウェア完全性回路31は、コントローラ12の一部として示されている。これらの要素は、コントローラの一部であるのが好ましいが、ある実施形態において、コントローラのパッケージ内に統合されていなくてもよい。前述したように、RAM11、フラッシュメモリ20、およびコントローラ12は、すべてシステムバス15に接続されている。ホストインターフェイスバス26は、ホスト装置24(図示せず)と通信する。

【0022】

ファームウェアの完全性ベリファイ

図2は、システム10を実行するファームウェア200を含むフラッシュメモリのメモリ空間の図である。システムファームウェア200は、フラッシュメモリ20内に常駐して変更不可能なのが好ましいブートローダ(BLR)部200aと、フラッシュメモリ20内に常駐して必要に応じて変更可能なシステムファームウェア200bとを備える。ある実施形態において、直接またはシャドウイングされたコピーから実行される場合にBLR部200aをポイントする追加のファームウェアがROM13内にあってもよい。システムファームウェア200のサイズは、実行元であるRAMモジュールよりも大きいので、システムファームウェアは、オーバーレイと称されるより小さい部分に分割される。好ましい実施形態におけるBLRの完全性ベリファイは、固有のその場の(on the fly)計算を使用し、当該計算において、期待値がデータ自身に記憶され、コピーがフラッシュメモリ20以外のメモリ内のレジスタに一時的に記憶される。しかし、ある実施形態において、BLRの完全性をベリファイするために使用される手法は、システムファームウェア200bの完全性をベリファイするためにも使用可能である。前述したように、任意のハッシュ値およびハッシュ手法を使用可能であるが、MACまたはSHA−1の値が現時点においては好ましく、簡素化のために、好ましい一実施形態において、一方または他方の使用について説明する。通常、SHA−1のダイジェストをMAC値の代わりに使用してもよく、その逆であってもよい。MAC値を使用する利点として、MAC値が、ハードウェアと、MACを作成したハードウェアのキーとに関連していることが挙げられる。SHA−1値は、単にデータ自体に基づいて所定のデータセットのために作成可能だが、MAC値は、キーなしでは再作成することは不可能であり、したがって、より強固なセキュリティを提供する。特定的には、MAC値を作成するには、暗号化エンジン40の不揮発性メモリに記憶されたキー99を使用しなければならないが、MAC値を再作成するには、他のプロセッサを使用することができない。例えば、ハッカーは、ファームウェアおよび関連するMAC値を複製するために、システム外部から他のプロセッサを使用することはできない。

【0023】

同じくフラッシュメモリに記憶されるのは、様々なユーザデータファイル204である。図に示していない様々な他のプログラムおよびデータがフラッシュメモリ(図示せず)内に記憶されてもよい。これらのファイルは、暗号化されてもよく、その完全性は、同様または他のやり方でベリファイされてもよい。

【0024】

図3は、完全性チェックモードの場合のシステム10によって使用されるいつかのデータセクタの構造を示す。特に、BLRは、この構造を使用するのが好ましい。BLRコード307自体は、他のデータ間に挟まれるようにしてBLR201aを構成している。BLRコード307がロードされる前に、いくつかの構成情報がロードされる。構成情報は、ファイル識別(FID)セクタ1および7に含まれている。BLRコード307に続いて、メッセージ認証コードセクタ309がある。MACセクタ309内には、BLRコード307の対応する部分についてのMAC値がある。これが、より詳細に以下に説明する、図5において計算された値と比較されるMAC値である。MACセクタは、様々な長さのデータを収容するためにゼロで埋められて、セクタの最終128ビットをMACが常に占めるようにする。BLRコード307は、BLR部分200a内のフラッシュメモリ20に記憶され、構成情報もフラッシュメモリ20に記憶されてもよい。

【0025】

図4は、BLRコードおよびファームウェアの完全性をベリファイすることを含む、システム10をブートおよび実行する処理を示す。特に、図4は、ファームウェア200のBLR部分200aに関するような完全性ベリファイ処理の概観を含む。好ましい一実施形態において、システムファームウェア200bおよびアプリケーションファームウェアのベリファイは、BLRのベリファイとは別個のものであり、かつ、当該ベリファイの後に生じる。注目すべきなのは、ファームウェアは、BLRによって一度に全てロードされるわけではないということである。BLRは、いつかのモジュールのみ(RAM常駐ファームウェア)をロードし、他のモジュール(オーバーレイ)は、必要に応じてロードされ、RAM内の(複数の)同じ位置へスワップされる。

【0026】

システム10が起動すると、ステップ404に示すように、完全性チェックモードで起動することになる。一般的に、このモードにおいて、暗号エンジン40は、前述した説明および図5に詳細に示すように、すべての入力データのMAC値を計算している。この処理は、入力データが可変長であり得、かつ、NANDフラッシュメモリ20内の任意の位置に記憶されうることを保証するものである。好ましい実施形態において、データは、書き込まれたのと同一の順序で読み出され、最終のブロックの読み出しにはMACが含まれることになる。MAC比較の結果は、ファームウェアがいつでもチェックするのに利用可能である。ここで、図4に示す個々のステップを説明する。

【0027】

ステップ410において、システムは、同じく図5のフローチャートに詳しく見受けられる処理に従って、BLRの完全性をチェックする。これは、(システムが完全性チェックモードにある際に)フラッシュメモリ20からの他のデータがベリファイされたのと同じやり方でBLRが暗号エンジン40を通ることで行われる。ステップ420において、システムは、ステップ410において行われた完全性チェックの結果をチェックする。これは、図5に見受けられる処理200の完全性チェックのステップ270で記憶された、問題があるかないかを示す結果(フラグまたは他の指標)をチェックすることによって行われる。BLRがOKでない場合、システムは、ステップ430に見受けられるようなホストコマンドを待って、返品許可(RMA)状態として知られる障害分析状態へシステムを送ることになる。この動作状態および他の動作状態またはモードについてのさらなる詳細については、ホルツマンら(Holtzman et al.) の同時継続中の米国特許出願第11/053,273号「ライフサイクルフェーズを有するセキュアメモリカード (SECURE MEMORY CARD WITH LIFE CYCLE PHASES)」(特許文献1)を参照されたい。この特許出願は、その全体が本願明細書において参照により援用されている。しかし、BLRがOKの場合、システムは、ステップ440において、BLRを実行することになる。ブートが完了すると、システムは、図4のステップ440に見受けられるように、BLR自身に含まれる命令に基づいて、完全性チェックモードを去ることになる。BLRは、数多くの命令または「ステップ」を含む。そのうちの1つは、ステップ440aであって、BLRは、暗号エンジン40を通常モードに再構築し、言い換えれば、完全性チェックモードから暗号エンジン40を抜け出させる。BLRは、ステップ440bに示すように、システムにシステムファームウェア200bの完全性をチェックさせる命令も含む。

【0028】

図5は、図4に関して説明したような完全性ベリファイ処理410のフローチャートである。これは、システムが完全性チェックモードにある場合に、フラッシュメモリ20に記憶されたデータを読み出しおよびハッシュする一般的な処理を示す。NAND形フラッシュメモリの読み出しを例示の目的のために説明するものであるが、本発明は、大容量記憶の目的のために使用される任意の種類のメモリまたは媒体と共に使用することができる。繰り返すが、MAC値の使用を例示し、かつ説明するが、他のハッシュ値を使用してもよい。図2Bの表は、一般的に、対応する開始バイトと、バイト数とをエントリ毎に含むことになる(図示せず)。一般的に、好ましい実施形態において、処理全体は、NANDの完全性をページ毎ベースでベリファイするために使用される。この処理は、NANDに記憶された任意のデータの完全性をベリファイすることになる。データがたまたまファームウェアの場合には、ファームウェアの完全性をベリファイする。このようなページ毎の比較が好ましいが、より小さな単位またはより大きな単位での比較を行ってもよい。

【0029】

好ましい一実施形態における完全性ベリファイ処理は、図5に示すような固有の計算と制御ループとを使用する。ループは、連続する計算および比較動作を伴う。典型的には、ベリファイ手法において、何らかの種類の「正しい(correct) 」値または期待値が予め記憶され、計算された値と比較される。図5に示す処理を有する好ましい一実施形態において、「正しい」値または期待値が、「被テストデータ(data under test) 」内に記憶される。それは、特定的には、前述した好ましい実施形態において、データブロックの最終128ビット内にある。読み出し中のセクタの最終128ビットは、実際上の目的のためには、正しいセクタが読み出された際に、記憶されたMAC(または他のハッシュ値)といったん対応するだけとなる。(誤った肯定(false positive))一致が最終以外のページで生じるであろう確率は非常に小さいので、これは実際上の目的では無視できる。

【0030】

ステップ210において、NANDブロック(i)が読み出される。次に、ステップ215において、ブロックがチェックされて、必要があれば、ECC回路でオプションで訂正される。ECCは周知であり、データ内の物理的な誤りを訂正するために使用できる。完全性ベリファイ処理と共にECCを使用することが好ましいが、これは必須ではなく、完全性は、ステップ215を含んでも含まなくてもベリファイされる。ステップ220において、ハッシュ値が計算され、好ましい一実施形態において、MAC値が好ましい。ブロック(i)についてのMACが計算されるが、完全性ベリファイ処理410において、結果生じたMACは、ブロック0から(i)までを対象として含み、数学的には以下のように表現できる。

MAC[0...(i)]=MAC[MAC[0...(i−1)],

block(i)]

【0031】

ステップ220での計算後、ステップ260において比較が行われる。ステップ260において、コントローラのハードウェア、特にFWIC31が、ブロック(i)の最終128ビットを以前記憶されたMAC、すなわちMAC[0...(i−1)]と比較する。ステップ270において、比較結果がシステムのメモリに記憶される。ステップ260の比較が最初に行われる際には、MACレジスタに「記憶された」値は、実際には、適切な記憶済みMAC値ではないことになるが、どんな値であれたまたまレジスタ内にあることになり、よって、ランダムであると考えられる。その後、ステップ270において、比較結果は記憶されることになる。第1のブロックについて、比較はチェックされないことになる。ステップ230において、ステップ220において計算されたMAC値は、コントローラのレジスタ内、好ましくはFWIC31のレジスタ内に記憶されることになる。次に、ステップ235において、(i)の値が1増分されるようにカウンタが増分され、次のブロックがまたステップ210で読み出されることになる。ループは、ブロック(i)が読み出されるまで継続することになる。最終ブロックが読み出されて暗号化エンジンによって処理されると、ステップ230で記憶されたMACと最終128ビットが一致すれば、比較は一致を生じさせて、ステップ270において記憶された結果は、完全性がハードウェアによってベリファイされたことを反映することになる。BLRの最終ページが読み出された場合にのみ、完全性がベリファイされたことを示すために一致が使用されることになる。これまでのすべての一致(誤った真の値(false true value))は、無視されることになる。値が異なる場合には、データの完全性に問題があることを示すこととなる。逆に、値が同一の場合には、データの完全性が確実となる。

【0032】

一致が生じた後に、ステップ230において、MAC値は再び更新されることになるが、これは影響を及ぼさない、ループの冗長動作である。この連続計算処理によって、ハードウェアは、不確定なコンテンツのサイズをベリファイすることができる。言い換えれば、MAC値を適切に計算することができ、ブロックからなるファイルのブロック数またはサイズをまず確認する必要なく、完全性をハードウェアによってベリファイすることができる。

【0033】

前述した処理は、メモリカードのフラッシュメモリ20内に常駐する任意のデータについて、ある動作状態またはモード、特に完全性チェックモードにおいて使用される。本発明によるメモリカードの好ましい一実施形態において、当該データのいくらかは、実行されるとメモリカードを実行するファームウェアである。特に、システム10の電源投入の際に、システムがその通常の動作状態またはテスト状態である場合に、暗号エンジン40は、任意の入力データの完全性をベリファイするために、(完全性チェックモードにおいて開始することによって)暗号エンジン40自体を初期化する。データがたまたまファームウェアである場合には、BMU14および特に暗号エンジン40を通る際にファームウェアの完全性がベリファイされる。記憶された結果(完全性自体ではない)は、一実施形態において、ROM13に記憶されたコード内の命令を伴うソフトウェアによってチェックできる。注意すべきなのは、ROM13に記憶されたコードは結果をチェックするものの、データのフローを開始してもよく、これはフラッシュメモリ内のファームウェアの完全性をベリファイする際には含まれないということである。言い換えれば、コードは、ベリファイするためにファームウェアの数値計算もデータ操作も行う役割はない。ファームウェアの完全性をベリファイするのは、コントローラ12またはBMU14、FWIC31、および暗号エンジン40のハードウェアであり、これには、ブートローダ(BLR)部分と、ある実施形態において、ファームウェアの他の部分も含まれる。

【0034】

図5で説明した処理は、ハードウェア(HW)とファームウェア(FW)との両方が関与する。前述したように、ハードウェアが完全性チェックを行うのに対して、ファームウェアは、HW完全性チェックの末尾のフラグセットを単にチェックするだけである。HWおよびSWの機能または「ループ」を、それぞれ図6および図7にさらに詳細に示す。

【0035】

図6を参照すると、ステップ320において、システムに電源が投入される。ステップ322において、コントローラのハードウェアが、FW完全性モードを開始する。これは、2つの中心的な行為を備える。第1は、図1のFWIC31を作動させることである。いったん作動されたFWIC31は、図6の残りのステップをうまくまとめあげ、これによって、暗号エンジン40と共に、ファームウェアのBLR部分の完全性をチェックする。第2の行為には、暗号エンジン40によって使用される暗号アルゴリズムを選択することが含まれる。前述したように、暗号エンジン40のハードウェアは、様々な互いに異なるアルゴリズムでデータを暗号化および復号化するように構成されている。

【0036】

ステップ328において、コントローラのハードウェアは、入力ブロックのダイジェストを計算する。この計算は、暗号エンジン40によって行われる。次に、ステップ330において、ステップ328において計算されたダイジェストを、以前のダイジェストの値と比較する。前述したように、値を保持するレジスタがチェックされて、ループの反復毎に比較されるが、最初の反復の際には、レジスタ内の値はランダムである。その後、完全性を示すフラグが、ステップ332において設定される。HWがファームウェアのBLR部分の完全性をベリファイしたかを確認するために、このフラグがシステムのファームウェアによってチェックされることになる。

【0037】

図7は、図6においてHWが完全性をチェックする一方で生じるファームウェアのループを示す。ステップ320においてシステムに電源が投入された後に、ステップ340においてCPUが初期化される。その後、ステップ342において、構成データ(好ましい一実施形態において、図3のFID1)が最初の有効ページに読み出される。次に、ステップ344において、システムは、BLR 201Aの開始および終了ページを抽出する。これがいったんわかると、BLRページのすべてが読み出される。各ページが読み出されるにつれて、誤り訂正符号(ECC)が生成される。前述したように、ECC回路動作は周知であり、データ内の物理的な誤りをある一定の限界まで訂正するために使用することができる。完全性ベリファイ処理と共にECCを使用することが好ましいが、これは必須ではなく、完全性は、ECCを使用してもしなくてもベリファイされる。ページが読み出された後に、ステップ348においてECC回路でチェックされ、OKでない場合には、ページはECC訂正機構で訂正されるか、またはステップ352において代替のページが取り出されることになる。訂正または新規のページがOKであるとステップ354において判断されると、システムは、ステップ350において、読み出されるべきページがさらにあるかどうかをチェックする。そうである場合には、システムはステップ346へ戻り、他のページを読み出す。ステップ354において訂正されたまたは代替コピーがOKではないとステップ354が示す場合には、失敗状態がステップ356において示されることになる。ステップ350においてこれ以上ページがないと判断されると、失敗は示されず、システムは、完全性フラグ(図6に示すようにハードウェアによって設定されている)をステップ360においてチェックすることになる。ステップ360において、BLRがOKであるとフラグが示す場合には、HWによってベリファイされたので、ステップ362においてBLRが実行されることになる。この実行は、図4のステップ440において示したのと同じである。

【0038】

この完全性チェックは、ファームウェアの一部分、すなわちBLRについてのみ行われるが、ファームウェアのすべてもこのようにチェックすることができ、また、この説明はファームウェアのブートスラップを使用する好ましい実施形態に関することが理解されるべきである。加えて、本願において使用されるようなメモリカードという用語は、USBフラッシュドライブの形式要因をも含んでいるつもりである。

【0039】

本発明の様々な態様についてそれらの例示の実施形態に関して説明してきたが、本発明が、添付の特許請求の範囲の全範囲内においてその権利が保護されるべきであることが理解できよう。

【特許請求の範囲】

【請求項1】

動作を開始するとともにメモリ記憶装置を動作するための方法であって、

前記メモリ記憶装置の大容量記憶ユニット内に前記メモリ記憶装置のファームウェアを設けるステップと、

前記ファームウェアを前記メモリ記憶装置のハードウェアで実施される暗号化エンジンに通すステップと、

前記ファームウェアについてのハッシュ値を前記ハードウェアで実施される暗号化エンジンで計算するステップと、

計算されたハッシュ値を記憶されたハッシュ値と比較するステップと、

前記計算されたハッシュ値が前記記憶されたハッシュ値と一致する場合に、前記ファームウェアを実行するステップと、

を含む方法。

【請求項2】

メモリ記憶装置の動作を開始するための方法であって、

前記メモリ記憶装置の大容量記憶ユニット内に、前記メモリ記憶装置の動作を制御するファームウェアを設けるステップと、

前記ファームウェアを前記メモリ記憶装置の大容量記憶ユニットから前記メモリ記憶装置のランダムアクセスメモリへコピーする、読み出し専用メモリ内の第1の命令セットを実行するステップと、

前記ファームウェアを前記大容量記憶ユニットから前記メモリ記憶装置のメモリコントローラ内のハードウェアで実施される暗号化エンジンに通すときに、ファームウェアの完全性をベリファイするステップと、

完全性がベリファイされた後に、ランダムアクセスメモリからファームウェアをマイクロプロセッサで実行するステップと、

を含む方法。

【請求項3】

請求項2記載の方法において、

前記ファームウェアは、前記大容量記憶ユニットからさらなるファームウェアをフェッチするための命令を含む方法。

【請求項4】

請求項3記載の方法において、

さらなるファームウェアを実行するステップをさらに含む方法。

【請求項5】

請求項1記載の方法において、

前記ファームウェアを設けるステップは、複数のファームウェアオーバーレイを設けることを含む方法。

【請求項6】

請求項5記載の方法において、

複数のファームウェアオーバーレイのそれぞれのオーバーレイ内に、ハッシュを備えるオーバーレイを含む多数のファームウェアの計算されたハッシュ値に等しいことを期待されたハッシュ値を記憶するステップをさらに含む方法。

【請求項7】

請求項6記載の方法において、

読み出される多数のファームウェアの計算されたハッシュ値は、期待されたハッシュ値を含むセクタが読み出されたときに、期待されたハッシュ値だけに対応し得る方法。

【請求項8】

請求項6記載の方法において、

前記期待されたハッシュ値を含むセクタブロックまたはページ以外のセクタブロックまたはページ上の誤った肯定一致を無視するステップをさらに含む方法。

【請求項9】

請求項1記載の方法において、

前記ハッシュ値を計算するステップは、MAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]でブロック(i)についてのMAC値が計算されることを含むが、結果生じたMAC値はブロック0から(i)までを対象として含む方法。

【請求項10】

請求項9記載の方法において、

前記メモリ記憶装置のメモリコントローラの、前記大容量記憶ユニット内にはないレジスタ内にブロック(i)についての計算されたMAC値を記憶するステップをさらに含む方法。

【請求項11】

請求項9記載の方法において、

結果生じたMAC値がブロック0から(i)までを対象として含むMAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]で前記ブロック(i)についてのハッシュ値を計算するステップは、前記ファームウェアのブートローダに対して行われる方法。

【請求項12】

請求項9記載の方法において、

結果生じたMAC値がブロック0から(i)までを対象として含むMAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]で前記ブロック(i)についてのハッシュ値を計算するステップは、前記ファームウェアのブートローダに対して行われるが、前記ファームウェア全体に対しては行われない方法。

【請求項13】

請求項9記載の方法において、

結果生じたMAC値がブロック0から(i)までを対象として含むMAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]で前記ブロック(i)についてのハッシュ値を計算するステップは、前記ファームウェア全体に対して行われる方法。

【請求項1】

動作を開始するとともにメモリ記憶装置を動作するための方法であって、

前記メモリ記憶装置の大容量記憶ユニット内に前記メモリ記憶装置のファームウェアを設けるステップと、

前記ファームウェアを前記メモリ記憶装置のハードウェアで実施される暗号化エンジンに通すステップと、

前記ファームウェアについてのハッシュ値を前記ハードウェアで実施される暗号化エンジンで計算するステップと、

計算されたハッシュ値を記憶されたハッシュ値と比較するステップと、

前記計算されたハッシュ値が前記記憶されたハッシュ値と一致する場合に、前記ファームウェアを実行するステップと、

を含む方法。

【請求項2】

メモリ記憶装置の動作を開始するための方法であって、

前記メモリ記憶装置の大容量記憶ユニット内に、前記メモリ記憶装置の動作を制御するファームウェアを設けるステップと、

前記ファームウェアを前記メモリ記憶装置の大容量記憶ユニットから前記メモリ記憶装置のランダムアクセスメモリへコピーする、読み出し専用メモリ内の第1の命令セットを実行するステップと、

前記ファームウェアを前記大容量記憶ユニットから前記メモリ記憶装置のメモリコントローラ内のハードウェアで実施される暗号化エンジンに通すときに、ファームウェアの完全性をベリファイするステップと、

完全性がベリファイされた後に、ランダムアクセスメモリからファームウェアをマイクロプロセッサで実行するステップと、

を含む方法。

【請求項3】

請求項2記載の方法において、

前記ファームウェアは、前記大容量記憶ユニットからさらなるファームウェアをフェッチするための命令を含む方法。

【請求項4】

請求項3記載の方法において、

さらなるファームウェアを実行するステップをさらに含む方法。

【請求項5】

請求項1記載の方法において、

前記ファームウェアを設けるステップは、複数のファームウェアオーバーレイを設けることを含む方法。

【請求項6】

請求項5記載の方法において、

複数のファームウェアオーバーレイのそれぞれのオーバーレイ内に、ハッシュを備えるオーバーレイを含む多数のファームウェアの計算されたハッシュ値に等しいことを期待されたハッシュ値を記憶するステップをさらに含む方法。

【請求項7】

請求項6記載の方法において、

読み出される多数のファームウェアの計算されたハッシュ値は、期待されたハッシュ値を含むセクタが読み出されたときに、期待されたハッシュ値だけに対応し得る方法。

【請求項8】

請求項6記載の方法において、

前記期待されたハッシュ値を含むセクタブロックまたはページ以外のセクタブロックまたはページ上の誤った肯定一致を無視するステップをさらに含む方法。

【請求項9】

請求項1記載の方法において、

前記ハッシュ値を計算するステップは、MAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]でブロック(i)についてのMAC値が計算されることを含むが、結果生じたMAC値はブロック0から(i)までを対象として含む方法。

【請求項10】

請求項9記載の方法において、

前記メモリ記憶装置のメモリコントローラの、前記大容量記憶ユニット内にはないレジスタ内にブロック(i)についての計算されたMAC値を記憶するステップをさらに含む方法。

【請求項11】

請求項9記載の方法において、

結果生じたMAC値がブロック0から(i)までを対象として含むMAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]で前記ブロック(i)についてのハッシュ値を計算するステップは、前記ファームウェアのブートローダに対して行われる方法。

【請求項12】

請求項9記載の方法において、

結果生じたMAC値がブロック0から(i)までを対象として含むMAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]で前記ブロック(i)についてのハッシュ値を計算するステップは、前記ファームウェアのブートローダに対して行われるが、前記ファームウェア全体に対しては行われない方法。

【請求項13】

請求項9記載の方法において、

結果生じたMAC値がブロック0から(i)までを対象として含むMAC[0...(i)]=MAC[MAC[0...(i−1)],block(i)]で前記ブロック(i)についてのハッシュ値を計算するステップは、前記ファームウェア全体に対して行われる方法。

【図1A】

【図1B】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図1B】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−210278(P2011−210278A)

【公開日】平成23年10月20日(2011.10.20)

【国際特許分類】

【出願番号】特願2011−137416(P2011−137416)

【出願日】平成23年6月21日(2011.6.21)

【分割の表示】特願2008−531324(P2008−531324)の分割

【原出願日】平成18年9月13日(2006.9.13)

【出願人】(506197901)サンディスク コーポレイション (175)

【Fターム(参考)】

【公開日】平成23年10月20日(2011.10.20)

【国際特許分類】

【出願日】平成23年6月21日(2011.6.21)

【分割の表示】特願2008−531324(P2008−531324)の分割

【原出願日】平成18年9月13日(2006.9.13)

【出願人】(506197901)サンディスク コーポレイション (175)

【Fターム(参考)】

[ Back to top ]