メモリコントローラ、これを備えたメモリシステム及びメモリデバイスの制御方法

【課題】データの信頼性を確保したままライト/リード動作の高速化を実現する。

【解決手段】本発明に係るメモリコントローラは、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成するデータ制御回路と、ライト動作においてデータ制御回路により生成される、ライトストローブ信号のタイミングをメモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作においてメモリデバイスにより生成される、リードストローブ信号のタイミングをメモリアクセス単位毎に調整し、データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行する調整回路と、を有する。

【解決手段】本発明に係るメモリコントローラは、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成するデータ制御回路と、ライト動作においてデータ制御回路により生成される、ライトストローブ信号のタイミングをメモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作においてメモリデバイスにより生成される、リードストローブ信号のタイミングをメモリアクセス単位毎に調整し、データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行する調整回路と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリコントローラ、これを備えたメモリシステム及びメモリデバイスの制御方法に関する。

【背景技術】

【0002】

従来より、メモリデバイスへライト/リードするアクセス単位が、複数のメモリ素子を含むランクにより構成されるメモリシステムが知られている。このようなメモリシステムにおいては、メモリコントローラと複数のランクのメモリ素子同士がワイアード接続される。

【0003】

本願発明に関連する技術として、特許文献1乃至3がある。特許文献1(特開2003−60488号公報)には、信号を伝播させる複数の伝送路毎に、調整した複数の遅延回路を設け、伝送路選択信号によって複数の遅延回路を切り替えることで、データ信号の遅延調整を行なう回路が開示されている。

【0004】

特許文献2(特開2007−12245号公報)には、メモリ装置が第1ランクに配置されるのか、第2ランクに配置されるかによって、ODT動作されるタイミングを異なるように調整する装置が開示されている。

【0005】

また、特許文献3(特開2009−217344号公報)には、データ及びストローブ信号のタイミング調整に用いるタイミング調整用データを、遅延調整用記憶部に記憶させ、タイミング調整用データを読み出すタイミングを変えながら、データの読み出しが可能な読み出しタイミングを選択設定するシステムが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−60488号公報

【特許文献2】特開2007−12245号公報

【特許文献3】特開2009−217344号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

従来のメモリコントローラを含むメモリシステムでは、ライト/リードのタイミングを指定するストローブ信号が複数のランクに対して共通であった。しかしながら、近年では、ランク単位で制御を行うメモリコントローラにおいては、データ転送速度は年々向上しており、従来では考慮されていなかったランク間の遅延バラつきが、今後の高速データ転送の阻害要因になってくる。この問題点について、図1及び図2を用いて説明する。図1及び図2は、メモリ素子の入力ポイントで見たタイミングチャートである。

【0008】

まず、図1で示すように、データ転送速度が遅い場合では、各ランク共通のストローブ信号のタイミング調整を行うだけで、各ランクのSETUP/HOLDを満足させることが可能であった。つまり、従来では、データ確定時間が、ランク間の遅延バラつきより十分大きかったため、ランク間の遅延バラつきは、問題にならなかった。

【0009】

しかしながら、図2で示すように、データ転送速度が速い場合は、各ランク共通のストローブ信号のタイミング調整を行うだけでは、各ランクのSETUP/HOLDを満足することができない。つまり、各ランクにおけるデータ確定時間が小さくなると、ランク間の遅延バラつきが、データ転送の阻害要因となる。

【0010】

特許文献1では、上述のように、メモリコントローラとメモリ素子間のデータ転送のタイミングを調整することができる回路が開示されている。しかしながら、特許文献1では、ランク間のデータ信号の遅延バラつきについては何ら考慮されていないため、上述したように、高速データ転送を行なう場合に各ランクのSETUP/HOLDを満足させることができない。そのため、特許文献1の回路では、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができない。

【0011】

また、特許文献1では、あくまでもメモリコントローラ側からメモリ素子への転送、つまりライト動作のみデータ転送のタイミングが調整されており、リード動作において、データ信号を調整する機能を有していない。そのため特許文献1では、リード動作におけるデータ転送の高速化を図ることができない。

【0012】

また、特許文献2及び3についても同様に、ランク間のデータ信号の遅延バラつきについては、何ら考慮されていない。

【0013】

本発明は、上記のような問題点に対してなされたものであり、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができるメモリコントローラ及びこれを含むメモリシステム及びメモリデバイスの制御方法を提供することを目的とする。

【課題を解決するための手段】

【0014】

本発明に係るメモリコントローラの一態様は、複数のメモリ素子から構成されるライト/リードアクセス単位である、二以上のメモリアクセス単位を有するメモリデバイスを制御するメモリコントローラである。この装置は、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成するデータ制御回路と、ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行する調整回路と、を有することを特徴とする。

【0015】

また、本発明に係るメモリデバイスの制御方法は、複数のメモリ素子から構成されるアクセス単位によってリード/ライト動作を行うメモリデバイスの制御方法であって、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成し、ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行することを特徴とする。

【発明の効果】

【0016】

本発明によれば、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができる。

【図面の簡単な説明】

【0017】

【図1】従来のメモリシステムにおいて、データ転送速度が遅い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。

【図2】従来のメモリシステムにおいて、データ転送速度が速い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。

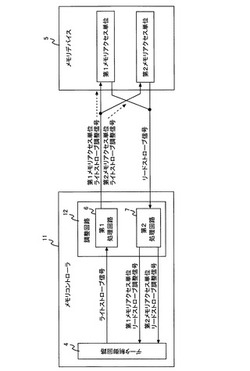

【図3】本発明に係るメモリコントローラの概要を示すブロック図である。

【図4】本発明の実施の形態1に係るメモリコントローラを含むメモリシステムにおける、データ転送速度が速い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。

【図5】本発明の実施の形態1に係るメモリコントローラを含むメモリシステムの構成を示すブロック図である。

【図6】本発明の実施の形態1に係るメモリコントローラの遅延回路の構成を示す図である。

【図7】本発明の実施の形態2に係るメモリコントローラを含むメモリシステムを示すブロック図である。

【発明を実施するための形態】

【0018】

以下、添付した図面を参照し、本発明の最良な実施の形態について説明する。はじめに、各実施の形態に係るメモリコントローラについて説明する前に、本発明に係るメモリコントローラの概要について説明する。図3は、本発明に係るメモリコントローラの概要を示すブロック図である。メモリコントローラ11は、図示しない上位装置とメモリデバイス5との間を中継する装置である。メモリコントローラ11は、CPU等の上位装置側に設けられていてもよく、また、メモリデバイス5側に設けられていてもよい。

【0019】

本願発明の1つの特徴は、ライト/リード動作のタイミングを指定するライト/リードストローブ信号を、メモリアクセス単位毎にタイミング調整した点にある。なお、メモリコントローラ11とメモリデバイス5間では、ストローブ信号の他にもライト/リードデータも入出力されているが、図3では、説明のため、ライト/リードデータの入出力については省略している。

【0020】

メモリコントローラ11の制御対象であるメモリデバイス5は、二以上のメモリアクセス単位により構成されている。1つのメモリアクセス単位は、複数のメモリ素子によって構成されている。メモリコントローラ11は、上位装置のライト/リード要求に応じ、メモリデバイス5に対して実行されるライト/リード処理を、ライト/リードアクセス単位毎に制御する。ライト/リードアクセス単位は、メモリデバイス5のランクとして構成することができる。

【0021】

メモリコントローラ11は、データ制御回路4と、調整回路12を備えている。データ制御回路4は、上位装置との間でライト/リードデータの入出力を行なう。また、データ制御回路4は、上位装置から入力されたライトデータを、メモリデバイス5が取り込むタイミングを指定するための、ライトストローブ信号を生成する。データ制御装置4によって生成されたライトストローブ信号は、調整回路12に出力される。また、データ制御回路4は、メモリデバイス5によって生成されたリードストローブ信号により指定されるタイミングで、メモリデバイス5から読み出されたリードデータを取り込む。

【0022】

調整回路12は、ライト動作において使用される第1処理回路6と、リード動作において使用される第2処理回路7のうち、少なくとも一方を備えている。なお、図3では、説明のため、第1処理回路6及び第2処理回路7の両方を図示しているが、本発明はこれに限られず、いずれか一方のみを備えていればよい。

【0023】

第1処理回路6は、ライト動作においてデータ制御回路4により生成される、ライトストローブ信号のタイミングをメモリアクセス単位毎に調整する。第1処理回路6は、入力されたライトストローブ信号を遅延調整することで、第1メモリアクセス単位がライトデータを取り込むタイミングを指定する第1メモリアクセス単位ライトストローブ信号を生成する。また、第1処理回路6は、入力されたライトストローブ信号を遅延調整することで、第2メモリアクセス単位がライトデータを取り込むタイミングを指定する第2メモリアクセス単位ライトストローブ信号を生成する。ここで、第1処理回路6によってタイミング調整される前のライトストローブ信号を、単にライトストローブ信号とし、調整された後の信号を、ライトストローブ調整信号と呼ぶこととする。

【0024】

第1処理回路6によって生成された第1ライトストローブ調整信号は、図示しない制御信号(チップセレクト)によって有効となった第1メモリアクセス単位に供給される。同様に、第1処理回路6によって生成された第2ライトストローブ調整信号は、制御信号(チップセレクト)によって有効となった第2メモリアクセス単位に供給される。

【0025】

第1メモリアクセス単位においては、入力された第1ライトストローブ調整信号のエッジタイミングで、上位装置から入力されたライトデータが取り込まれる。同様に、第2メモリアクセス単位においては、入力された第2ライトストローブ調整信号のエッジタイミングで、上位装置から入力されたライトデータが取り込まれる。

【0026】

第2処理回路7は、リード動作においてメモリデバイス5により生成される、リードストローブ信号をメモリデバイス5より入力し、メモリアクセス単位毎にタイミング調整して、データ制御回路4に出力する。具体的には、第2処理回路7は、データ制御回路4が第1メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定する第1メモリアクセス単位リードストローブ信号を生成する。また、第2処理回路7は、データ制御回路4が第2メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定する第2メモリアクセス単位リードストローブ信号を生成する。ここで、第2処理回路7によってタイミング調整される前のリードストローブ信号を、単にリードストローブ信号とし、調整された後の信号を、リードストローブ調整信号と呼ぶこととする。

【0027】

なお、第1処理回路6及び第2処理回路7におけるライト/ストローブ信号のタイミング調整は、各メモリアクセス単位に入力されるクロックに同期させるように調整すればよい。

【0028】

データ制御回路4においては、調整回路2から入力された第1リードストローブ調整信号のエッジタイミングで、第1メモリアクセス単位から読み出されたリードデータを取り込む。また、データ制御回路4は、調整回路2から入力された第2リードストローブ調整信号のエッジタイミングで、第2メモリアクセス単位から読み出されたリードデータを取り込む。

【0029】

このように、本発明に係るメモリコントローラでは、ライト/リードアクセス単位毎にライト/リードストローブ信号のタイミングを調整し、ライト/リードアクセス単位毎にライト/リードストローブ調整信号を生成する。これにより、ランク間に生じるデータ信号の遅延バラつきによって、ライト/リード処理の高速化が妨げられるのを防止することができる。

【0030】

これを図2及び4を用いて、より具体的に説明する。図4は、本発明の実施の形態1に係るメモリコントローラを含むメモリシステムにおける、データ転送速度が速い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。従来では、図2に示すように、第1ランク及び第2ランクに対し、共通の(ライト/リード)ストローブ信号が用いられていた。そのため、図2に示すように、データの取り込みタイミングを規定するストローブ信号は、立ち上がりエッジが第1ランクデータ及び第2ランクデータのいずれもが確定している間、すなわち、第1、2共通ウィンドウ内に存在する必要があった。しかしながら、図2に示すようにデータ転送速度が高速である場合には、各ランクのデータ確定時間は、十分なSETUP/HOLD時間を確保できず、ライト/リードされたデータの信頼性が低くなるという問題があった。

【0031】

これに対し、本発明に係るメモリコントローラ11では、図4に示すように、第1ランク及び第2ランクのそれぞれに対し、自己のランクデータが確定している間のみを考慮して(ライト/リード)ストローブ調整信号のエッジのタイミングを調整すればよい。そのため、各ランクにおいて十分なSETUP/HOLD時間を確保できる最適なタイミングにストローブ調整信号のタイミングを調整することができる。これにより、図4に示すような、データの転送レートが高い場合であっても、メモリデバイス5に記憶されたデータ及びリードデータの信頼性を維持することが可能となる。

【0032】

また、メモリコントローラ11では、ライト動作においてライトストローブ信号の遅延調整を行う第1処理回路6と、リード動作においてリードストローブ信号の遅延調整を行う第2処理回路7が設けられているため、ライト動作及びリード動作のいずれについても、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができる。

【0033】

実施の形態1.

次に、本発明の実施の形態1に係るメモリコントローラについて説明する。図5は、本発明の実施の形態1に係るメモリコントローラを含むメモリシステムの構成を示す図である。実施の形態1において、図3のデータ制御回路4、第1処理回路6、第2処理回路7、第1メモリアクセス単位、及び第2メモリアクセス単位は、図5のデータ制御回路4、ライトデータ調整回路21、リードデータ調整回路22、第1ランク及び第2にランクに相当する。実施の形態1において、調整回路2は、各ランクのメモリ素子a〜zによって共有される複数の調整回路2a〜2zにより構成されている。各調整回路2a〜2zでは、ライト/リードストローブ信号のタイミング調整が行われると共に、メモリ素子a〜z毎にライト/リードデータのタイミング調整が行われている。

【0034】

メモリコントローラ1の制御対象であるメモリデバイス5は、2つランク、すなわち、第1ランク及び第2ランクに接続されている。第1ランク及び第2ランクのそれぞれは、複数のメモリ素子a〜zにより構成されている。

【0035】

メモリコントローラ1は、データ制御回路4、調整回路2及びアドレス/コマンド制御回路3を備えている。データ制御回路4は、前述のように、上位装置からライトデータを入力すると共に、メモリデバイス5から読み出されたライトデータを、上位装置に出力する。上位装置からのライト/リード要求に従って生成されたコマンド(CMD)/アドレス(AD)信号を伝送する伝送路は、第1ランク及び第2ランクの全てのメモリ素子a〜zに接続されている。コマンド(CMD)/アドレス(AD)信号は、アドレス/コマンド制御回路3により、全てのメモリ素子a〜zに分配されている。

【0036】

クロック(CLK)/チップセレクト(CS)信号を伝送する伝送路は、各ランク内のメモリ素子a〜zに接続されている。クロック(CLK)/チップセレクト(CS)信号は、ランク単位にアドレス/コマンド制御回路3から出力されている。ストローブ信号(DQS)及びデータ信号(DQ)は、双方向信号である。ストローブ信号(DQS)及びデータ信号(DQ)を伝送する伝送路は、各ランクのメモリ素子a〜z同士でワイアード接続され、メモリコントローラ1と接続されている。なお、前述では、調整回路2によって調整されたストローブ信号を、ストローブ調整信号とすると説明したが、図5において図示されるストローブ信号(DQS)及びデータ信号(DQ)は、調整回路2によって調整される前後のストローブ信号及びデータ信号を含むものとする。

【0037】

アドレス/コマンド制御回路3は、上位装置から発行されるライト要求又はリード要求を受信すると、メモリ素子a〜zに対し、ライトコマンド又はリードコマンド、及びアドレスを発行すると共に、メモリアクセスするランクに対して、チップセレクト(CS)を発行する。

【0038】

データ制御回路4は、ライト動作時には、ライトデータを上位装置より受付け、調整回路2へライトデータを発行する。データ制御回路4は、リード動作時には、調整回路2より発行されるランク単位のリードデータを、同じく調整回路2より発行されるランク単位に調整された、第1リードストローブ調整信号又は第2リードストローブ調整信号のエッジタイミングで取り込み、取り込んだリードデータを上位装置へ送信する。

【0039】

調整回路2は、メモリ素子a〜z毎に設けられた調整回路2a〜2zを有している。調整回路2a〜2zは、第1ランクと第2ランクとで共有される。例えば、調整回路2aは、第1ランクのメモリ素子aと第2ランクのメモリ素子aとで共有され、調整回路2zは、第1ランクのメモリ素子zと第2ランクのメモリ素子zとで共有されている。各調整回路2a〜2zは、ライトデータ調整回路21と、リードデータ調整回路22から構成される。

【0040】

ライトデータ調整回路21は、ライト処理時に、データ制御回路4からメモリデバイス5へ伝送される、ライトデータ(DQ)とライトストローブ信号(DQS)のタイミングを調整し、メモリデバイス5の各メモリ素子a〜zに出力する。ライトデータ調整回路21は、第1ランクライトストローブ調整回路211、第2ランクライトストローブ調整回路212、第1ランクライトデータ調整回路213、第2ランクライトデータ調整回路214及びセレクタ215、216を備えている。

【0041】

第1ランクライトストローブ調整回路211は、データ制御回路4によって生成されるライトストローブ信号を、第1ランクのメモリ素子a〜zがライトデータを取り込むための最適なタイミングに遅延調整する。第1ランクライトストローブ調整回路211には、第1ランクのメモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD1が入力されている。第1ランクライトストローブ調整回路211は、ライト遅延調整信号WD1に基づいて調整された信号を、第1ライトストローブ調整信号としてセレクタ215に出力する。なお、各調整回路2a〜2zの第1ランクライトストローブ調整回路211によって生成される第1ライトストローブ調整信号は、共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第1ランクライトストローブ調整回路211に入力されるライト遅延調整信号WD1は共通である。

【0042】

第2ランクライトストローブ調整回路212は、データ制御回路4によって生成されるライトストローブ信号を、第2ランクのメモリ素子a〜zが、ライトデータを取り込むための最適なタイミングに調整する。第2ランクライトストローブ調整回路212には、第2ランクのメモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD2が入力されている。第1ランクライトストローブ調整回路212は、ライト遅延調整信号WD2に基づいて調整された信号を、第2ランクライトストローブ調整信号としてセレクタ215に出力する。なお、各調整回路2a〜2zの第2ランクライトストローブ調整回路212によって生成される第2ランクライトストローブ調整信号は、共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第2ランクライトストローブ調整回路212に入力されるライト遅延調整信号WD2は共通である。

【0043】

セレクタ215は、第1ランクライトストローブ調整回路211によって生成された第1ランクライトストローブ調整信号と、第2ランクライトストローブ調整回路212によって生成された第2ランクライトストローブ調整信号を入力し、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ライトストローブ調整信号又は第2ライトストローブ調整信号を選択し、ストローブ信号(DQS)としてメモリデバイス5に出力する。ここで、ライトランク有効信号WRとは、ライト動作において、チップセレクト(CS)により有効となる第1ランク又は第2ランクのいずれかを指定する信号である。

【0044】

第1ランクライトデータ調整回路213は、データ制御回路4から入力されたライトデータ信号を、第1ランクのメモリ素子a〜zに、ライトデータを書き込むための最適なタイミングに遅延調整する。第1ランクライトデータ調整回路213には、第1ランクの各メモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD3が入力されている。第1ランクライトデータ調整回路213は、ライト遅延調整信号WD3により調整された信号を、第1ランクライトデータ調整信号a〜zとして各メモリ素子a〜zに出力する。

【0045】

ライト遅延調整信号WD3は、ライトデータ信号の遅延時間を、ライト可能な時間に設定する信号である。ライト遅延調整信号WD3は、所定のデータをメモリ素子に書き込み、メモリ素子から返されたデータが、書き込みデータと一致するか否かを判定することにより、ライトデータ信号を適切な遅延時間に設定できるように、設定される。第1ランクライトデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、メモリ素子a〜z毎にライト可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第1ランクライトデータ調整回路213に入力されるライト遅延調整信号WD3は、各メモリ素子a〜zに応じて異なる値に設定される。

【0046】

第2ランクライトデータ調整回路214は、データ制御回路4から入力されたライトデータ信号を、第2ランクのメモリ素子a〜zに、ライトデータを書き込むための最適なタイミングに遅延調整する。第2ランクライトデータ調整回路214には、第2ランクのメモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD4が入力されている。なお、ライト遅延調整信号WD4は、ライト遅延調整信号WD3と同様の方法で設定される。第2ランクライトデータ調整回路214は、遅延調整信号により調整された第2ランクライトデータ調整信号a〜zを各メモリ素子a〜zに出力する。各調整回路2a〜2zの第2ランクライトデータ調整回路214によって生成される第2ランクライトデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、メモリ素子a〜z毎にライト可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第2ランクライトデータ調整回路214に入力されるライト遅延調整信号WD4は、各メモリ素子a〜zに応じて異なる値に設定される。

【0047】

セレクタ216は、第1ランクライトデータ調整回路213によって生成された第1ランクライトデータ調整信号と、第2ランクライトデータ調整回路214によって生成された第2ランクライトデータ調整信号を入力し、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ランクライトデータ調整信号又は第2ランクライトデータ調整信号を選択し、メモリデバイス5に出力する。

【0048】

リードデータ調整回路22は、第1ランクリードストローブ調整回路221、第2ランクリードストローブ調整回路222、第1ランクリードデータ調整回路223、第2ランクリードデータ調整回路224及びセレクタ225、226を備えている。

【0049】

第1ランクリードストローブ調整回路221は、メモリデバイス5によって生成されるリードストローブ信号を、データ制御回路4が第1ランクからのリードデータを読み出すのに最適なタイミングに遅延調整する。第1ランクリードストローブ調整回路221には、データ制御装置4が第1ランクから読み出されたリードデータを取り込める遅延値に設定されたリード遅延調整信号RD1が入力されている。第1ランクリードストローブ調整回路221は、リード遅延調整信号RD1により調整された信号を、第1ランクリードストローブ調整信号としてセレクタ225に出力する。なお、第1ランクリードストローブ調整回路221によって生成される、第1ランクリードストローブ調整信号は、第1ランクの各メモリ素子a〜zにおいて共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第1ランクリードストローブ調整回路221に入力されるリード遅延調整信号RD1は共通である。

【0050】

第2ランクリードストローブ調整回路222は、メモリデバイス5によって生成されるリードストローブ信号を、第2ランクから出力されたリードデータを、データ制御回路4が読み出すのに最適なタイミングに遅延調整する。第2ランクリードストローブ調整回路222には、データ制御装置4が第2ランクから読み出されたリードデータを取り込める遅延値に設定されたリード遅延調整信号RD2が入力されている。第2ランクリードストローブ調整回路222は、ライト遅延調整信号RD2により調整された信号を、第2リードストローブ調整信号としてセレクタ225に出力する。なお、第2ランクリードストローブ調整回路222によって生成される、第2ランクリードストローブ調整信号は、第2ランクの各メモリ素子a〜zにおいて共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第2ランクリードストローブ調整回路222に入力されるリード遅延調整信号RD2は共通である。

【0051】

セレクタ225は、第1ランクリードストローブ調整回路221によって生成された第1ランクリードストローブ調整信号と、第2ランクリードストローブ調整回路222によって生成された第2ランクリードストローブ調整信号を入力し、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1ランクリードストローブ調整信号又は第2ランクリードストローブ調整信号を、データ制御装置4に出力する。ここで、リードランク有効信号RRとは、リード動作において、チップセレクト(CS)により有効となる第1ランク又は第2ランクのいずれかを指定する信号である。

【0052】

メモリ素子a〜zから発行されたリードデータ信号(DQ)は、ランク単位に用意された調整回路(第1ランクリードデータ調整回路223、第2ランクリードデータ調整回路224)に分配される。第1ランクリードデータ調整回路223及び第2ランクリードデータ調整回路224は、リード遅延調整信号RD3、4に基づいて、リードデータ信号(DQ)を遅延調整する。なお、リード遅延調整信号RD3、4は、ライト遅延調整信号WD3、4と同様に、入力値と期待値を比較することにより、予め最適なタイミングに遅延調整することができる信号に設定されている。

【0053】

第1ランクリードデータ調整回路223は、メモリデバイス5から入力されたリードデータ信号を、データ制御回路4がリードデータを読み出すための最適なタイミングに遅延調整する。第1ランクリードデータ調整回路223は、調整された信号を、第2リードデータ調整信号a〜zとしてデータ制御回路4に出力する。第1リードデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、各メモリ素子a〜z毎にリード可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第1ランクリードデータ調整回路223に入力されるリード遅延調整信号RD3は、各メモリ素子a〜zに応じて異なる値に設定される。

【0054】

第2ランクリード調整回路224は、メモリデバイス5から入力されたリードデータ信号を、データ制御回路4がリードデータを読み出すための最適なタイミングに遅延調整する。第2ランクリードデータ調整回路224は、調整された信号を第2リードデータ調整信号a〜zとしてデータ制御回路4に出力する。第2リードデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、各メモリ素子a〜z毎にリード可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第2ランクリードデータ調整回路224に入力されるリード遅延調整信号RD4は、各メモリ素子a〜zに応じて異なる値に設定される。

【0055】

セレクタ226は、第1ランクリードデータ調整回路223によって生成された第1リードデータ調整信号と、第2ランクリードデータ調整回路224によって生成された第2リードデータ調整信号を入力し、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1リードデータ調整信号又は第2リードデータ調整信号を、データ制御回路4に出力する。

【0056】

次に、調整回路2の構成について説明する。図6は、本発明の実施の形態1に係るメモリコントローラ1の調整回路2の構成例を示す図である。図6に示すように、調整回路2は、複数の遅延ゲートが直列に接続されている。また、各遅延ゲート間からは、分岐した複数の信号線がセレクタに入力されている。各調整回路の出力、つまり遅延量は、セレクト信号により選択された遅延ゲート段数により決定される。このセレクト信号が、ライト遅延調整信号WD1〜4、及びリード遅延調整信号RD1〜4である。なお、調整回路2の構成は、これに限られるものではなく、任意の回路構成を用いることができる。

【0057】

次に、このように構成されたメモリコントローラ1及びこれを含むメモリシステムの動作について説明する。

【0058】

[ライト動作]

本発明の実施の形態1に係るメモリコントローラ1及びこれを含むメモリシステムのライト動作について、図5を用いて説明する。上位装置からランク1へのライト要求及びライトデータがメモリコントローラ1に発行されると、アドレス/コマンド制御回路3は、第1ランクのメモリ素子a〜zに対し、チップセレクト信号(CS)、ライトコマンド、及びアドレスを発行する。一般的なメモリ素子(例えば、DDR−SDRAM:Double-Data-Rate Synchronous Dynamic Random Access Memory)においては、ライトデータについては、ライトコマンドに対し十分な時間経過した後に発行すればよい。すわなち、データ制御回路4は、メモリ素子の仕様を満足するだけの時間経過した後に、遅延調整回路2a〜2zに対しストローブ信号およびライトデータを送出すればよい。

【0059】

アドレス/コマンド制御回路3は、このタイミングで、ライトランク有効信号WRを調整回路2a〜2zに発行する。ここで、第1ランクへライト動作を行う場合には、アドレス/コマンド制御回路3は、ライトデータ調整回路21内のセレクタ215および216に対し、第1ランク側の調整回路(第1ランクライトストローブ調整回路211、第1ランクライトデータ調整回路213)を選択するよう、ライトランク有効信号WRを発行する。

【0060】

これにより、セレクタ215からは、第1ランクのメモリ素子a〜zに対し、第1ランクライトストローブ調整信号が送出される。一方、セレクタ216からは、第1ランクのメモリ素子a〜zに対し、第2ランクライトデータ調整信号が送出される。この時、第1ランクライトストローブ調整回路211及び第1ランクライトデータ調整回路213に入力されるライト遅延調整信号WR1、WR3は、予め第1ランクのメモリ素子a〜zに対しライトできる様に設定しておく。

【0061】

第1ランクのメモリ素子a〜zでは、調整回路2から入力された第1ランクライトストローブ調整信号(DQS)のエッジのタイミングで、遅延調整がされた各メモリ素子に入力される第1ランクライトデータ調整信号が取り込まれる。

【0062】

一方、第2ランクへライト動作を行う場合には、アドレス/コマンド制御回路3は、ライトデータ調整回路21内のセレクタ215および216に対し、第2ランク側の調整回路(第2ランクライトストローブ調整回路212、第2ランクライトデータ調整回路214)を選択するよう、ライトランク有効信号WRを発行する。

【0063】

これにより、セレクタ215からは、第2ランクのメモリ素子a〜zに対し、第2ランクライトストローブ調整信号(DQS)が送出される。一方、セレクタ216からは、第2ランクのメモリ素子a〜zに対し、第2ランクライトデータ調整信号(DQ)が送出される。この時、第2ランクライトストローブ調整回路212及び第2ランクライトデータ調整回路214に入力されるライト遅延調整信号WR2、4は、予め第2ランクのメモリ素子a〜zに対しライトできる様に設定しておく。

【0064】

第2ランクのメモリ素子a〜zでは、調整回路2から入力された第2ランクライトストローブ調整信号(DQS)のエッジのタイミングで、遅延調整がされた各メモリ素子に入力される、第2ランクライトデータ調整信号が取り込まれる。

【0065】

これにより、メモリデバイス5では、第1ランクの最適タイミングで、ライトデータを取り込むことができると共に、第2ランクの最適タイミングで、ライトデータを取り込むことができる。

【0066】

[リード動作]

次に、本発明の実施の形態1に係るメモリコントローラ1及びこれを含むメモリシステムのリード動作について説明する。上位装置からリード要求がメモリコントローラ1に発行されると、アドレス/コマンド制御回路3は、第1ランクのメモリ素子a〜zに対し、チップセレクト信号(CS)、リードコマンド及びアドレスを発行する。一般的なメモリ素子(例えば、DDR−SDRAM)において、リードデータは、リードコマンドに対し十分な時間経過した後に発行される。そのため、アドレス/コマンド制御回路3は、このタイミングで、リードランク有効信号を調整回路2a〜2zに対して発行すればよい。

【0067】

ここで、第1ランクへリード動作を行う場合には、アドレス/コマンド制御回路3は、ライトデータ調整回路22内のセレクタ225および226に対し、第1ランク側の調整回路(第1ランクリードストローブ調整回路221、第1ランクリードデータ調整回路223)を選択するよう、リードランク有効信号RRを発行する。これにより、セレクタ225からは、データ制御回路4に対し、第1ランクリードストローブ調整信号(DQS)が送出される。一方、セレクタ226からは、データ制御回路4に対し、第1ランクライトデータ調整信号(DQ)が送出される。この時、第1ランクリードストローブ調整回路221、第1ランクリードデータ調整回路223に入力されるリード遅延調整信号RD1、3は、予め第1ランクのメモリ素子a〜zからのリードデータをデータ制御装置4がリードできる様に設定しておく。

【0068】

第2ランクへリード動作を行う場合には、アドレス/コマンド制御回路3は、リードデータ調整回路22内のセレクタ225および226に対し、第2ランク側の調整回路(第2ランクリードストローブ調整回路222、第2ランクリードデータ調整回路224)を選択するよう、リードランク有効信号RRを発行する。これにより、セレクタ225からは、データ制御回路4に対し、第2ランクリードストローブ調整信号(DQS)が送出される。一方、セレクタ226からは、データ制御回路4に対し、第2ランクリードデータ調整信号(DQ)が送出される。この時、第2ランクリードストローブ調整回路222、第2ランクリードデータ調整回路224に入力されるリード遅延調整信号RD2、4は、予め第2ランクのメモリ素子a〜zからのリードデータを、データ制御装置4がリードできる様に設定しておく。

【0069】

第1ランクへの読み出し動作において、データ制御回路4は、調整回路2より入力された第1リードデータ調整信号を、同じく調整回路2より入力された第1ランクリードストローブ調整信号によって指定されたタイミングで取り込む。一方、第2ランクへの読み出し動作においては、データ制御回路4は、調整回路2により入力された第2リードデータ調整信号を、同じく調整回路2より入力された第2リードストローブ調整信号によって指定されたタイミングで取り込む。

【0070】

これにより、データ制御回路4では、第1ランクの最適タイミングで、第1ランクから読み出されたリードデータを取り込むことができると共に、第2ランクの最適タイミングで、第2ランクから読み出されたリードデータを取り込むことができる。データ制御回路4は、このように第1ランク及び第2ランクから読み出したデータを、上位装置に出力する。

【0071】

このように、本実施の形態1に係るメモリコントローラ1は、年々高速化するメモリインタフェースのデータ転送において、ランク毎に調整回路(211〜214、221〜224)を具備することにより、ランク間の遅延バラつきを抑えることができ、高速データ転送を実現することができる。具体的には、図4に示すように、第1ランク及び第2ランクのそれぞれに対し、自己のランクデータが確定している間のみを考慮してランク毎にストローブ調整信号のエッジのタイミングを調整することができる。これにより、各ランクにおいて十分なSETUP/HOLDを確保できる最適なタイミングに、ストローブ調整信号のタイミングを調整することができる。これにより、図4に示すような、データの転送レートが高い場合であっても、メモリデバイス5に記憶されたデータ及びリードデータの信頼性を維持することができる。

【0072】

実施の形態2.

次に、本発明の実施の形態2に係るメモリコンロトーラ及びこれを含むメモリシステムについて説明する。図7は、本発明の実施の形態2にかかるメモリコントローラ8及びこれを含むメモリシステムの構成を示すブロック図である。なお、実施の形態2の基本的な構成については、実施の形態1と同様である。ここで、実施の形態1に係るメモリコントローラ1は、ストローブ信号及びデータ信号を調整するライト/リードストローブ信号調整回路及びライト/リードデータ信号調整回路がランク毎に、それぞれ設けられていた。

【0073】

これに対し、実施の形態2に係るメモリコントローラ8は、ライト/リードストローブ信号調整回路及びライト/リードデータ信号調整回路が、複数のランクにおいて共通に設けられている。なお、アドレス/コマンド制御回路3、データ制御回路4及びメモリデバイス5については、実施の形態1と略同一であるため、同一符号を付すことによりその説明を省略する。また、図7においても、図示されるストローブ信号(DQS)及びデータ信号(DQ)は、調整回路9によって調整される前後のストローブ信号及びデータ信号を含むものとする。

【0074】

図7に示すように、本発明に係るメモリコントローラ8は、調整回路9を備えている。調整回路9は、メモリ素子a〜zに対応する調整回路9a〜9zを備えている。調整回路9は、ライトデータ調整回路91及びリードデータ調整回路92を備えている。ライトデータ調整回路91は、図3の第1処理回路6に相当し、リードデータ調整回路92は、図3の第2処理回路7に相当する。ライトデータ調整回路91は、ライトストローブ調整回路911、ライトデータ調整回路912、及びセレクタ913、914を備えている。

【0075】

ライトストローブ調整回路911には、第1ランクに対して生成されたライト遅延調整信号WD1と、第2ランクに対して生成されたライト遅延調整信号WD2が、セレクタ913を介して入力されている。セレクタ913は、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ランクに対して生成されたライト遅延調整信号WD1又は第2ランクに対して生成されたライト遅延調整信号WD2を選択して、ライトストローブ調整回路911に出力する。

【0076】

ライトストローブ調整回路911は、セレクタ913から第1ランクに対して生成されたライト遅延調整信号WD1を入力すると、このライト遅延調整信号WD1に基づいてストローブ信号(DQS)を遅延調整し、第1ランクのメモリ素子a〜zに対して、第1ライトストローブ調整信号を出力する。同様に、ライトストローブ調整回路911は、セレクタ913から第2ランクに対して生成されたライト遅延調整信号WD2を入力すると、このライト遅延調整信号WD2に基づいてストローブ信号(DQS)を遅延調整し、第2ランクのメモリ素子a〜zに対して、第2ライトストローブ調整信号を出力する。なお、ライト遅延調整信号WD1は、第1ランクのメモリ素子a〜zで共通な値に設定され、ライト遅延調整信号WD2は、第2ランクのメモリ素子a〜zで共通な値に設定されている。

【0077】

ライトデータ調整回路912には、データ制御回路4から、第1ランク又は第2ランクに書き込まれるライトデータ信号が入力される。ライトデータ調整回路912には、第1ランクに対して生成されたライト遅延調整信号WD3と、第2ランクに対して生成されたライト遅延調整信号WD4がセレクタ914を介して入力されている。セレクタ914は、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ランクに対して生成されたライト遅延調整信号WD3又は第2ランクに対して生成されたライト遅延調整信号WD4を選択し、ライトデータ調整回路912に出力する。なお、ライト遅延調整信号WD3、4は、各ランクのメモリ素子a〜z毎に、異なる最適な遅延時間に調整されている。

【0078】

リードデータ調整回路92は、リードストローブ調整回路921、リードデータ調整回路922、セレクタ923、924を備えている。リードストローブ調整回路921は、第1ランク又は第2ランクのメモリ素子a〜zからリードストローブ信号が入力される。リードストローブ調整回路921には、セレクタ923を介して、第1ランクに対して生成されたリード遅延調整信号RD1又は第2ランクに対して生成されたリード遅延調整信号RD2が入力されている。セレクタ923は、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1ランクに対して生成されたリード遅延調整信号RD1又は第2ランクに対して生成されたリード遅延調整信号RD2を選択して、リードストローブ調整回路921に出力する。

【0079】

同様に、リードデータ調整回路922は、第1ランク又は第2ランクのメモリ素子a〜zから出力されたリードデータ信号が入力される。リードデータ調整回路922には、セレクタ924を介して、第1ランクに対して生成されたリード遅延調整信号RD3又は第2ランクに対して生成されたリード遅延調整信号RD4が入力されている。セレクタ924は、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1ランクに対して生成されたライト遅延調整信号RD3又は第2ランクに対して生成されたライト遅延調整信号RD4を選択して、リードデータ調整回路922に出力する。

【0080】

このように、本発明の実施の形態2に係るメモリコントローラ8では、調整回路を各ランク間で共有することで、回路が小さく済むという利点がある。なお、データの信頼性を確保したままライト/リード動作の高速化を実現するという本願の効果については、実施の形態1と同様である。

【0081】

なお、本発明は上記実施の形態1、2に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。また、各実施の形態の全体又は一部の構成は、任意に組合せて実施することができる。

【0082】

また、上記の説明では、本願発明を装置の発明として説明したが、本発明は、メモリデバイスの制御方法としても実施することができる。具体的には、本発明は、複数のメモリ素子から構成されるアクセス単位によってリード/ライト動作を行うメモリデバイスの制御方法であって、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成し、ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行するメモリデバイスの制御方法として実施することができる。また、このメモリデバイスの制御方法は、コンピュータプログラムに格納することで実施することもできる。

【0083】

なお、上記の実施の形態1、2においては、メモリデバイスが、第1ランク及び第2ランクにより構成されているが、本発明は限られるものでなく、3以上のランクを備えるように構成してもよい。

【0084】

また、上記の説明では、ライト/リードストローブ調整信号は、ランク単位で異なる値に設定されるが、ストローブ調整信号は、メモリ素子毎に各メモリ素子の動作に対して最適化した値に設定するように構成することもできる。

【符号の説明】

【0085】

2、2a〜2z、9、9a〜9z 調整回路

3 アドレス/コマンド制御回路

4 データ制御回路

5 メモリデバイス

6 第1処理回路

7 第2処理回路

1、8、11 メモリコントローラ

21、91 ライトデータ調整回路

22、92 リードデータ調整回路

211 第1ランクライトストローブ調整回路

212 第2ランクライトストローブ調整回路

213 第1ランクライトデータ調整回路

214 第2ランクライトデータ調整回路

215、216、225、226、913、914、923、924 セレクタ

221 第1ランクリードストローブ調整回路

222 第2ランクリードストローブ調整回路

223 第1ランクリードデータ調整回路

224 第2ランクリードデータ調整回路

911 ライトストローブ調整回路

912 ライトデータ調整回路

921 リードストローブ調整回路

922 リードデータ調整回路

【技術分野】

【0001】

本発明は、メモリコントローラ、これを備えたメモリシステム及びメモリデバイスの制御方法に関する。

【背景技術】

【0002】

従来より、メモリデバイスへライト/リードするアクセス単位が、複数のメモリ素子を含むランクにより構成されるメモリシステムが知られている。このようなメモリシステムにおいては、メモリコントローラと複数のランクのメモリ素子同士がワイアード接続される。

【0003】

本願発明に関連する技術として、特許文献1乃至3がある。特許文献1(特開2003−60488号公報)には、信号を伝播させる複数の伝送路毎に、調整した複数の遅延回路を設け、伝送路選択信号によって複数の遅延回路を切り替えることで、データ信号の遅延調整を行なう回路が開示されている。

【0004】

特許文献2(特開2007−12245号公報)には、メモリ装置が第1ランクに配置されるのか、第2ランクに配置されるかによって、ODT動作されるタイミングを異なるように調整する装置が開示されている。

【0005】

また、特許文献3(特開2009−217344号公報)には、データ及びストローブ信号のタイミング調整に用いるタイミング調整用データを、遅延調整用記憶部に記憶させ、タイミング調整用データを読み出すタイミングを変えながら、データの読み出しが可能な読み出しタイミングを選択設定するシステムが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−60488号公報

【特許文献2】特開2007−12245号公報

【特許文献3】特開2009−217344号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

従来のメモリコントローラを含むメモリシステムでは、ライト/リードのタイミングを指定するストローブ信号が複数のランクに対して共通であった。しかしながら、近年では、ランク単位で制御を行うメモリコントローラにおいては、データ転送速度は年々向上しており、従来では考慮されていなかったランク間の遅延バラつきが、今後の高速データ転送の阻害要因になってくる。この問題点について、図1及び図2を用いて説明する。図1及び図2は、メモリ素子の入力ポイントで見たタイミングチャートである。

【0008】

まず、図1で示すように、データ転送速度が遅い場合では、各ランク共通のストローブ信号のタイミング調整を行うだけで、各ランクのSETUP/HOLDを満足させることが可能であった。つまり、従来では、データ確定時間が、ランク間の遅延バラつきより十分大きかったため、ランク間の遅延バラつきは、問題にならなかった。

【0009】

しかしながら、図2で示すように、データ転送速度が速い場合は、各ランク共通のストローブ信号のタイミング調整を行うだけでは、各ランクのSETUP/HOLDを満足することができない。つまり、各ランクにおけるデータ確定時間が小さくなると、ランク間の遅延バラつきが、データ転送の阻害要因となる。

【0010】

特許文献1では、上述のように、メモリコントローラとメモリ素子間のデータ転送のタイミングを調整することができる回路が開示されている。しかしながら、特許文献1では、ランク間のデータ信号の遅延バラつきについては何ら考慮されていないため、上述したように、高速データ転送を行なう場合に各ランクのSETUP/HOLDを満足させることができない。そのため、特許文献1の回路では、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができない。

【0011】

また、特許文献1では、あくまでもメモリコントローラ側からメモリ素子への転送、つまりライト動作のみデータ転送のタイミングが調整されており、リード動作において、データ信号を調整する機能を有していない。そのため特許文献1では、リード動作におけるデータ転送の高速化を図ることができない。

【0012】

また、特許文献2及び3についても同様に、ランク間のデータ信号の遅延バラつきについては、何ら考慮されていない。

【0013】

本発明は、上記のような問題点に対してなされたものであり、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができるメモリコントローラ及びこれを含むメモリシステム及びメモリデバイスの制御方法を提供することを目的とする。

【課題を解決するための手段】

【0014】

本発明に係るメモリコントローラの一態様は、複数のメモリ素子から構成されるライト/リードアクセス単位である、二以上のメモリアクセス単位を有するメモリデバイスを制御するメモリコントローラである。この装置は、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成するデータ制御回路と、ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行する調整回路と、を有することを特徴とする。

【0015】

また、本発明に係るメモリデバイスの制御方法は、複数のメモリ素子から構成されるアクセス単位によってリード/ライト動作を行うメモリデバイスの制御方法であって、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成し、ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行することを特徴とする。

【発明の効果】

【0016】

本発明によれば、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができる。

【図面の簡単な説明】

【0017】

【図1】従来のメモリシステムにおいて、データ転送速度が遅い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。

【図2】従来のメモリシステムにおいて、データ転送速度が速い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。

【図3】本発明に係るメモリコントローラの概要を示すブロック図である。

【図4】本発明の実施の形態1に係るメモリコントローラを含むメモリシステムにおける、データ転送速度が速い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。

【図5】本発明の実施の形態1に係るメモリコントローラを含むメモリシステムの構成を示すブロック図である。

【図6】本発明の実施の形態1に係るメモリコントローラの遅延回路の構成を示す図である。

【図7】本発明の実施の形態2に係るメモリコントローラを含むメモリシステムを示すブロック図である。

【発明を実施するための形態】

【0018】

以下、添付した図面を参照し、本発明の最良な実施の形態について説明する。はじめに、各実施の形態に係るメモリコントローラについて説明する前に、本発明に係るメモリコントローラの概要について説明する。図3は、本発明に係るメモリコントローラの概要を示すブロック図である。メモリコントローラ11は、図示しない上位装置とメモリデバイス5との間を中継する装置である。メモリコントローラ11は、CPU等の上位装置側に設けられていてもよく、また、メモリデバイス5側に設けられていてもよい。

【0019】

本願発明の1つの特徴は、ライト/リード動作のタイミングを指定するライト/リードストローブ信号を、メモリアクセス単位毎にタイミング調整した点にある。なお、メモリコントローラ11とメモリデバイス5間では、ストローブ信号の他にもライト/リードデータも入出力されているが、図3では、説明のため、ライト/リードデータの入出力については省略している。

【0020】

メモリコントローラ11の制御対象であるメモリデバイス5は、二以上のメモリアクセス単位により構成されている。1つのメモリアクセス単位は、複数のメモリ素子によって構成されている。メモリコントローラ11は、上位装置のライト/リード要求に応じ、メモリデバイス5に対して実行されるライト/リード処理を、ライト/リードアクセス単位毎に制御する。ライト/リードアクセス単位は、メモリデバイス5のランクとして構成することができる。

【0021】

メモリコントローラ11は、データ制御回路4と、調整回路12を備えている。データ制御回路4は、上位装置との間でライト/リードデータの入出力を行なう。また、データ制御回路4は、上位装置から入力されたライトデータを、メモリデバイス5が取り込むタイミングを指定するための、ライトストローブ信号を生成する。データ制御装置4によって生成されたライトストローブ信号は、調整回路12に出力される。また、データ制御回路4は、メモリデバイス5によって生成されたリードストローブ信号により指定されるタイミングで、メモリデバイス5から読み出されたリードデータを取り込む。

【0022】

調整回路12は、ライト動作において使用される第1処理回路6と、リード動作において使用される第2処理回路7のうち、少なくとも一方を備えている。なお、図3では、説明のため、第1処理回路6及び第2処理回路7の両方を図示しているが、本発明はこれに限られず、いずれか一方のみを備えていればよい。

【0023】

第1処理回路6は、ライト動作においてデータ制御回路4により生成される、ライトストローブ信号のタイミングをメモリアクセス単位毎に調整する。第1処理回路6は、入力されたライトストローブ信号を遅延調整することで、第1メモリアクセス単位がライトデータを取り込むタイミングを指定する第1メモリアクセス単位ライトストローブ信号を生成する。また、第1処理回路6は、入力されたライトストローブ信号を遅延調整することで、第2メモリアクセス単位がライトデータを取り込むタイミングを指定する第2メモリアクセス単位ライトストローブ信号を生成する。ここで、第1処理回路6によってタイミング調整される前のライトストローブ信号を、単にライトストローブ信号とし、調整された後の信号を、ライトストローブ調整信号と呼ぶこととする。

【0024】

第1処理回路6によって生成された第1ライトストローブ調整信号は、図示しない制御信号(チップセレクト)によって有効となった第1メモリアクセス単位に供給される。同様に、第1処理回路6によって生成された第2ライトストローブ調整信号は、制御信号(チップセレクト)によって有効となった第2メモリアクセス単位に供給される。

【0025】

第1メモリアクセス単位においては、入力された第1ライトストローブ調整信号のエッジタイミングで、上位装置から入力されたライトデータが取り込まれる。同様に、第2メモリアクセス単位においては、入力された第2ライトストローブ調整信号のエッジタイミングで、上位装置から入力されたライトデータが取り込まれる。

【0026】

第2処理回路7は、リード動作においてメモリデバイス5により生成される、リードストローブ信号をメモリデバイス5より入力し、メモリアクセス単位毎にタイミング調整して、データ制御回路4に出力する。具体的には、第2処理回路7は、データ制御回路4が第1メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定する第1メモリアクセス単位リードストローブ信号を生成する。また、第2処理回路7は、データ制御回路4が第2メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定する第2メモリアクセス単位リードストローブ信号を生成する。ここで、第2処理回路7によってタイミング調整される前のリードストローブ信号を、単にリードストローブ信号とし、調整された後の信号を、リードストローブ調整信号と呼ぶこととする。

【0027】

なお、第1処理回路6及び第2処理回路7におけるライト/ストローブ信号のタイミング調整は、各メモリアクセス単位に入力されるクロックに同期させるように調整すればよい。

【0028】

データ制御回路4においては、調整回路2から入力された第1リードストローブ調整信号のエッジタイミングで、第1メモリアクセス単位から読み出されたリードデータを取り込む。また、データ制御回路4は、調整回路2から入力された第2リードストローブ調整信号のエッジタイミングで、第2メモリアクセス単位から読み出されたリードデータを取り込む。

【0029】

このように、本発明に係るメモリコントローラでは、ライト/リードアクセス単位毎にライト/リードストローブ信号のタイミングを調整し、ライト/リードアクセス単位毎にライト/リードストローブ調整信号を生成する。これにより、ランク間に生じるデータ信号の遅延バラつきによって、ライト/リード処理の高速化が妨げられるのを防止することができる。

【0030】

これを図2及び4を用いて、より具体的に説明する。図4は、本発明の実施の形態1に係るメモリコントローラを含むメモリシステムにおける、データ転送速度が速い場合のメモリ素子の入力ポイントでみた入力信号のタイミングチャートである。従来では、図2に示すように、第1ランク及び第2ランクに対し、共通の(ライト/リード)ストローブ信号が用いられていた。そのため、図2に示すように、データの取り込みタイミングを規定するストローブ信号は、立ち上がりエッジが第1ランクデータ及び第2ランクデータのいずれもが確定している間、すなわち、第1、2共通ウィンドウ内に存在する必要があった。しかしながら、図2に示すようにデータ転送速度が高速である場合には、各ランクのデータ確定時間は、十分なSETUP/HOLD時間を確保できず、ライト/リードされたデータの信頼性が低くなるという問題があった。

【0031】

これに対し、本発明に係るメモリコントローラ11では、図4に示すように、第1ランク及び第2ランクのそれぞれに対し、自己のランクデータが確定している間のみを考慮して(ライト/リード)ストローブ調整信号のエッジのタイミングを調整すればよい。そのため、各ランクにおいて十分なSETUP/HOLD時間を確保できる最適なタイミングにストローブ調整信号のタイミングを調整することができる。これにより、図4に示すような、データの転送レートが高い場合であっても、メモリデバイス5に記憶されたデータ及びリードデータの信頼性を維持することが可能となる。

【0032】

また、メモリコントローラ11では、ライト動作においてライトストローブ信号の遅延調整を行う第1処理回路6と、リード動作においてリードストローブ信号の遅延調整を行う第2処理回路7が設けられているため、ライト動作及びリード動作のいずれについても、データの信頼性を確保したまま、メモリアクセスの高速化を実現することができる。

【0033】

実施の形態1.

次に、本発明の実施の形態1に係るメモリコントローラについて説明する。図5は、本発明の実施の形態1に係るメモリコントローラを含むメモリシステムの構成を示す図である。実施の形態1において、図3のデータ制御回路4、第1処理回路6、第2処理回路7、第1メモリアクセス単位、及び第2メモリアクセス単位は、図5のデータ制御回路4、ライトデータ調整回路21、リードデータ調整回路22、第1ランク及び第2にランクに相当する。実施の形態1において、調整回路2は、各ランクのメモリ素子a〜zによって共有される複数の調整回路2a〜2zにより構成されている。各調整回路2a〜2zでは、ライト/リードストローブ信号のタイミング調整が行われると共に、メモリ素子a〜z毎にライト/リードデータのタイミング調整が行われている。

【0034】

メモリコントローラ1の制御対象であるメモリデバイス5は、2つランク、すなわち、第1ランク及び第2ランクに接続されている。第1ランク及び第2ランクのそれぞれは、複数のメモリ素子a〜zにより構成されている。

【0035】

メモリコントローラ1は、データ制御回路4、調整回路2及びアドレス/コマンド制御回路3を備えている。データ制御回路4は、前述のように、上位装置からライトデータを入力すると共に、メモリデバイス5から読み出されたライトデータを、上位装置に出力する。上位装置からのライト/リード要求に従って生成されたコマンド(CMD)/アドレス(AD)信号を伝送する伝送路は、第1ランク及び第2ランクの全てのメモリ素子a〜zに接続されている。コマンド(CMD)/アドレス(AD)信号は、アドレス/コマンド制御回路3により、全てのメモリ素子a〜zに分配されている。

【0036】

クロック(CLK)/チップセレクト(CS)信号を伝送する伝送路は、各ランク内のメモリ素子a〜zに接続されている。クロック(CLK)/チップセレクト(CS)信号は、ランク単位にアドレス/コマンド制御回路3から出力されている。ストローブ信号(DQS)及びデータ信号(DQ)は、双方向信号である。ストローブ信号(DQS)及びデータ信号(DQ)を伝送する伝送路は、各ランクのメモリ素子a〜z同士でワイアード接続され、メモリコントローラ1と接続されている。なお、前述では、調整回路2によって調整されたストローブ信号を、ストローブ調整信号とすると説明したが、図5において図示されるストローブ信号(DQS)及びデータ信号(DQ)は、調整回路2によって調整される前後のストローブ信号及びデータ信号を含むものとする。

【0037】

アドレス/コマンド制御回路3は、上位装置から発行されるライト要求又はリード要求を受信すると、メモリ素子a〜zに対し、ライトコマンド又はリードコマンド、及びアドレスを発行すると共に、メモリアクセスするランクに対して、チップセレクト(CS)を発行する。

【0038】

データ制御回路4は、ライト動作時には、ライトデータを上位装置より受付け、調整回路2へライトデータを発行する。データ制御回路4は、リード動作時には、調整回路2より発行されるランク単位のリードデータを、同じく調整回路2より発行されるランク単位に調整された、第1リードストローブ調整信号又は第2リードストローブ調整信号のエッジタイミングで取り込み、取り込んだリードデータを上位装置へ送信する。

【0039】

調整回路2は、メモリ素子a〜z毎に設けられた調整回路2a〜2zを有している。調整回路2a〜2zは、第1ランクと第2ランクとで共有される。例えば、調整回路2aは、第1ランクのメモリ素子aと第2ランクのメモリ素子aとで共有され、調整回路2zは、第1ランクのメモリ素子zと第2ランクのメモリ素子zとで共有されている。各調整回路2a〜2zは、ライトデータ調整回路21と、リードデータ調整回路22から構成される。

【0040】

ライトデータ調整回路21は、ライト処理時に、データ制御回路4からメモリデバイス5へ伝送される、ライトデータ(DQ)とライトストローブ信号(DQS)のタイミングを調整し、メモリデバイス5の各メモリ素子a〜zに出力する。ライトデータ調整回路21は、第1ランクライトストローブ調整回路211、第2ランクライトストローブ調整回路212、第1ランクライトデータ調整回路213、第2ランクライトデータ調整回路214及びセレクタ215、216を備えている。

【0041】

第1ランクライトストローブ調整回路211は、データ制御回路4によって生成されるライトストローブ信号を、第1ランクのメモリ素子a〜zがライトデータを取り込むための最適なタイミングに遅延調整する。第1ランクライトストローブ調整回路211には、第1ランクのメモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD1が入力されている。第1ランクライトストローブ調整回路211は、ライト遅延調整信号WD1に基づいて調整された信号を、第1ライトストローブ調整信号としてセレクタ215に出力する。なお、各調整回路2a〜2zの第1ランクライトストローブ調整回路211によって生成される第1ライトストローブ調整信号は、共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第1ランクライトストローブ調整回路211に入力されるライト遅延調整信号WD1は共通である。

【0042】

第2ランクライトストローブ調整回路212は、データ制御回路4によって生成されるライトストローブ信号を、第2ランクのメモリ素子a〜zが、ライトデータを取り込むための最適なタイミングに調整する。第2ランクライトストローブ調整回路212には、第2ランクのメモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD2が入力されている。第1ランクライトストローブ調整回路212は、ライト遅延調整信号WD2に基づいて調整された信号を、第2ランクライトストローブ調整信号としてセレクタ215に出力する。なお、各調整回路2a〜2zの第2ランクライトストローブ調整回路212によって生成される第2ランクライトストローブ調整信号は、共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第2ランクライトストローブ調整回路212に入力されるライト遅延調整信号WD2は共通である。

【0043】

セレクタ215は、第1ランクライトストローブ調整回路211によって生成された第1ランクライトストローブ調整信号と、第2ランクライトストローブ調整回路212によって生成された第2ランクライトストローブ調整信号を入力し、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ライトストローブ調整信号又は第2ライトストローブ調整信号を選択し、ストローブ信号(DQS)としてメモリデバイス5に出力する。ここで、ライトランク有効信号WRとは、ライト動作において、チップセレクト(CS)により有効となる第1ランク又は第2ランクのいずれかを指定する信号である。

【0044】

第1ランクライトデータ調整回路213は、データ制御回路4から入力されたライトデータ信号を、第1ランクのメモリ素子a〜zに、ライトデータを書き込むための最適なタイミングに遅延調整する。第1ランクライトデータ調整回路213には、第1ランクの各メモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD3が入力されている。第1ランクライトデータ調整回路213は、ライト遅延調整信号WD3により調整された信号を、第1ランクライトデータ調整信号a〜zとして各メモリ素子a〜zに出力する。

【0045】

ライト遅延調整信号WD3は、ライトデータ信号の遅延時間を、ライト可能な時間に設定する信号である。ライト遅延調整信号WD3は、所定のデータをメモリ素子に書き込み、メモリ素子から返されたデータが、書き込みデータと一致するか否かを判定することにより、ライトデータ信号を適切な遅延時間に設定できるように、設定される。第1ランクライトデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、メモリ素子a〜z毎にライト可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第1ランクライトデータ調整回路213に入力されるライト遅延調整信号WD3は、各メモリ素子a〜zに応じて異なる値に設定される。

【0046】

第2ランクライトデータ調整回路214は、データ制御回路4から入力されたライトデータ信号を、第2ランクのメモリ素子a〜zに、ライトデータを書き込むための最適なタイミングに遅延調整する。第2ランクライトデータ調整回路214には、第2ランクのメモリ素子a〜zが、ライトデータを取り込める遅延値に設定されたライト遅延調整信号WD4が入力されている。なお、ライト遅延調整信号WD4は、ライト遅延調整信号WD3と同様の方法で設定される。第2ランクライトデータ調整回路214は、遅延調整信号により調整された第2ランクライトデータ調整信号a〜zを各メモリ素子a〜zに出力する。各調整回路2a〜2zの第2ランクライトデータ調整回路214によって生成される第2ランクライトデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、メモリ素子a〜z毎にライト可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第2ランクライトデータ調整回路214に入力されるライト遅延調整信号WD4は、各メモリ素子a〜zに応じて異なる値に設定される。

【0047】

セレクタ216は、第1ランクライトデータ調整回路213によって生成された第1ランクライトデータ調整信号と、第2ランクライトデータ調整回路214によって生成された第2ランクライトデータ調整信号を入力し、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ランクライトデータ調整信号又は第2ランクライトデータ調整信号を選択し、メモリデバイス5に出力する。

【0048】

リードデータ調整回路22は、第1ランクリードストローブ調整回路221、第2ランクリードストローブ調整回路222、第1ランクリードデータ調整回路223、第2ランクリードデータ調整回路224及びセレクタ225、226を備えている。

【0049】

第1ランクリードストローブ調整回路221は、メモリデバイス5によって生成されるリードストローブ信号を、データ制御回路4が第1ランクからのリードデータを読み出すのに最適なタイミングに遅延調整する。第1ランクリードストローブ調整回路221には、データ制御装置4が第1ランクから読み出されたリードデータを取り込める遅延値に設定されたリード遅延調整信号RD1が入力されている。第1ランクリードストローブ調整回路221は、リード遅延調整信号RD1により調整された信号を、第1ランクリードストローブ調整信号としてセレクタ225に出力する。なお、第1ランクリードストローブ調整回路221によって生成される、第1ランクリードストローブ調整信号は、第1ランクの各メモリ素子a〜zにおいて共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第1ランクリードストローブ調整回路221に入力されるリード遅延調整信号RD1は共通である。

【0050】

第2ランクリードストローブ調整回路222は、メモリデバイス5によって生成されるリードストローブ信号を、第2ランクから出力されたリードデータを、データ制御回路4が読み出すのに最適なタイミングに遅延調整する。第2ランクリードストローブ調整回路222には、データ制御装置4が第2ランクから読み出されたリードデータを取り込める遅延値に設定されたリード遅延調整信号RD2が入力されている。第2ランクリードストローブ調整回路222は、ライト遅延調整信号RD2により調整された信号を、第2リードストローブ調整信号としてセレクタ225に出力する。なお、第2ランクリードストローブ調整回路222によって生成される、第2ランクリードストローブ調整信号は、第2ランクの各メモリ素子a〜zにおいて共通のタイミングに調整されている。換言すれば、各調整回路2a〜2zの第2ランクリードストローブ調整回路222に入力されるリード遅延調整信号RD2は共通である。

【0051】

セレクタ225は、第1ランクリードストローブ調整回路221によって生成された第1ランクリードストローブ調整信号と、第2ランクリードストローブ調整回路222によって生成された第2ランクリードストローブ調整信号を入力し、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1ランクリードストローブ調整信号又は第2ランクリードストローブ調整信号を、データ制御装置4に出力する。ここで、リードランク有効信号RRとは、リード動作において、チップセレクト(CS)により有効となる第1ランク又は第2ランクのいずれかを指定する信号である。

【0052】

メモリ素子a〜zから発行されたリードデータ信号(DQ)は、ランク単位に用意された調整回路(第1ランクリードデータ調整回路223、第2ランクリードデータ調整回路224)に分配される。第1ランクリードデータ調整回路223及び第2ランクリードデータ調整回路224は、リード遅延調整信号RD3、4に基づいて、リードデータ信号(DQ)を遅延調整する。なお、リード遅延調整信号RD3、4は、ライト遅延調整信号WD3、4と同様に、入力値と期待値を比較することにより、予め最適なタイミングに遅延調整することができる信号に設定されている。

【0053】

第1ランクリードデータ調整回路223は、メモリデバイス5から入力されたリードデータ信号を、データ制御回路4がリードデータを読み出すための最適なタイミングに遅延調整する。第1ランクリードデータ調整回路223は、調整された信号を、第2リードデータ調整信号a〜zとしてデータ制御回路4に出力する。第1リードデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、各メモリ素子a〜z毎にリード可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第1ランクリードデータ調整回路223に入力されるリード遅延調整信号RD3は、各メモリ素子a〜zに応じて異なる値に設定される。

【0054】

第2ランクリード調整回路224は、メモリデバイス5から入力されたリードデータ信号を、データ制御回路4がリードデータを読み出すための最適なタイミングに遅延調整する。第2ランクリードデータ調整回路224は、調整された信号を第2リードデータ調整信号a〜zとしてデータ制御回路4に出力する。第2リードデータ調整信号a〜zは、メモリ素子a〜z毎に設定され、各メモリ素子a〜z毎にリード可能な最適なタイミングに調整される。換言すれば、各調整回路2a〜2zの第2ランクリードデータ調整回路224に入力されるリード遅延調整信号RD4は、各メモリ素子a〜zに応じて異なる値に設定される。

【0055】

セレクタ226は、第1ランクリードデータ調整回路223によって生成された第1リードデータ調整信号と、第2ランクリードデータ調整回路224によって生成された第2リードデータ調整信号を入力し、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1リードデータ調整信号又は第2リードデータ調整信号を、データ制御回路4に出力する。

【0056】

次に、調整回路2の構成について説明する。図6は、本発明の実施の形態1に係るメモリコントローラ1の調整回路2の構成例を示す図である。図6に示すように、調整回路2は、複数の遅延ゲートが直列に接続されている。また、各遅延ゲート間からは、分岐した複数の信号線がセレクタに入力されている。各調整回路の出力、つまり遅延量は、セレクト信号により選択された遅延ゲート段数により決定される。このセレクト信号が、ライト遅延調整信号WD1〜4、及びリード遅延調整信号RD1〜4である。なお、調整回路2の構成は、これに限られるものではなく、任意の回路構成を用いることができる。

【0057】

次に、このように構成されたメモリコントローラ1及びこれを含むメモリシステムの動作について説明する。

【0058】

[ライト動作]

本発明の実施の形態1に係るメモリコントローラ1及びこれを含むメモリシステムのライト動作について、図5を用いて説明する。上位装置からランク1へのライト要求及びライトデータがメモリコントローラ1に発行されると、アドレス/コマンド制御回路3は、第1ランクのメモリ素子a〜zに対し、チップセレクト信号(CS)、ライトコマンド、及びアドレスを発行する。一般的なメモリ素子(例えば、DDR−SDRAM:Double-Data-Rate Synchronous Dynamic Random Access Memory)においては、ライトデータについては、ライトコマンドに対し十分な時間経過した後に発行すればよい。すわなち、データ制御回路4は、メモリ素子の仕様を満足するだけの時間経過した後に、遅延調整回路2a〜2zに対しストローブ信号およびライトデータを送出すればよい。

【0059】

アドレス/コマンド制御回路3は、このタイミングで、ライトランク有効信号WRを調整回路2a〜2zに発行する。ここで、第1ランクへライト動作を行う場合には、アドレス/コマンド制御回路3は、ライトデータ調整回路21内のセレクタ215および216に対し、第1ランク側の調整回路(第1ランクライトストローブ調整回路211、第1ランクライトデータ調整回路213)を選択するよう、ライトランク有効信号WRを発行する。

【0060】

これにより、セレクタ215からは、第1ランクのメモリ素子a〜zに対し、第1ランクライトストローブ調整信号が送出される。一方、セレクタ216からは、第1ランクのメモリ素子a〜zに対し、第2ランクライトデータ調整信号が送出される。この時、第1ランクライトストローブ調整回路211及び第1ランクライトデータ調整回路213に入力されるライト遅延調整信号WR1、WR3は、予め第1ランクのメモリ素子a〜zに対しライトできる様に設定しておく。

【0061】

第1ランクのメモリ素子a〜zでは、調整回路2から入力された第1ランクライトストローブ調整信号(DQS)のエッジのタイミングで、遅延調整がされた各メモリ素子に入力される第1ランクライトデータ調整信号が取り込まれる。

【0062】

一方、第2ランクへライト動作を行う場合には、アドレス/コマンド制御回路3は、ライトデータ調整回路21内のセレクタ215および216に対し、第2ランク側の調整回路(第2ランクライトストローブ調整回路212、第2ランクライトデータ調整回路214)を選択するよう、ライトランク有効信号WRを発行する。

【0063】

これにより、セレクタ215からは、第2ランクのメモリ素子a〜zに対し、第2ランクライトストローブ調整信号(DQS)が送出される。一方、セレクタ216からは、第2ランクのメモリ素子a〜zに対し、第2ランクライトデータ調整信号(DQ)が送出される。この時、第2ランクライトストローブ調整回路212及び第2ランクライトデータ調整回路214に入力されるライト遅延調整信号WR2、4は、予め第2ランクのメモリ素子a〜zに対しライトできる様に設定しておく。

【0064】

第2ランクのメモリ素子a〜zでは、調整回路2から入力された第2ランクライトストローブ調整信号(DQS)のエッジのタイミングで、遅延調整がされた各メモリ素子に入力される、第2ランクライトデータ調整信号が取り込まれる。

【0065】

これにより、メモリデバイス5では、第1ランクの最適タイミングで、ライトデータを取り込むことができると共に、第2ランクの最適タイミングで、ライトデータを取り込むことができる。

【0066】

[リード動作]

次に、本発明の実施の形態1に係るメモリコントローラ1及びこれを含むメモリシステムのリード動作について説明する。上位装置からリード要求がメモリコントローラ1に発行されると、アドレス/コマンド制御回路3は、第1ランクのメモリ素子a〜zに対し、チップセレクト信号(CS)、リードコマンド及びアドレスを発行する。一般的なメモリ素子(例えば、DDR−SDRAM)において、リードデータは、リードコマンドに対し十分な時間経過した後に発行される。そのため、アドレス/コマンド制御回路3は、このタイミングで、リードランク有効信号を調整回路2a〜2zに対して発行すればよい。

【0067】

ここで、第1ランクへリード動作を行う場合には、アドレス/コマンド制御回路3は、ライトデータ調整回路22内のセレクタ225および226に対し、第1ランク側の調整回路(第1ランクリードストローブ調整回路221、第1ランクリードデータ調整回路223)を選択するよう、リードランク有効信号RRを発行する。これにより、セレクタ225からは、データ制御回路4に対し、第1ランクリードストローブ調整信号(DQS)が送出される。一方、セレクタ226からは、データ制御回路4に対し、第1ランクライトデータ調整信号(DQ)が送出される。この時、第1ランクリードストローブ調整回路221、第1ランクリードデータ調整回路223に入力されるリード遅延調整信号RD1、3は、予め第1ランクのメモリ素子a〜zからのリードデータをデータ制御装置4がリードできる様に設定しておく。

【0068】

第2ランクへリード動作を行う場合には、アドレス/コマンド制御回路3は、リードデータ調整回路22内のセレクタ225および226に対し、第2ランク側の調整回路(第2ランクリードストローブ調整回路222、第2ランクリードデータ調整回路224)を選択するよう、リードランク有効信号RRを発行する。これにより、セレクタ225からは、データ制御回路4に対し、第2ランクリードストローブ調整信号(DQS)が送出される。一方、セレクタ226からは、データ制御回路4に対し、第2ランクリードデータ調整信号(DQ)が送出される。この時、第2ランクリードストローブ調整回路222、第2ランクリードデータ調整回路224に入力されるリード遅延調整信号RD2、4は、予め第2ランクのメモリ素子a〜zからのリードデータを、データ制御装置4がリードできる様に設定しておく。

【0069】

第1ランクへの読み出し動作において、データ制御回路4は、調整回路2より入力された第1リードデータ調整信号を、同じく調整回路2より入力された第1ランクリードストローブ調整信号によって指定されたタイミングで取り込む。一方、第2ランクへの読み出し動作においては、データ制御回路4は、調整回路2により入力された第2リードデータ調整信号を、同じく調整回路2より入力された第2リードストローブ調整信号によって指定されたタイミングで取り込む。

【0070】

これにより、データ制御回路4では、第1ランクの最適タイミングで、第1ランクから読み出されたリードデータを取り込むことができると共に、第2ランクの最適タイミングで、第2ランクから読み出されたリードデータを取り込むことができる。データ制御回路4は、このように第1ランク及び第2ランクから読み出したデータを、上位装置に出力する。

【0071】

このように、本実施の形態1に係るメモリコントローラ1は、年々高速化するメモリインタフェースのデータ転送において、ランク毎に調整回路(211〜214、221〜224)を具備することにより、ランク間の遅延バラつきを抑えることができ、高速データ転送を実現することができる。具体的には、図4に示すように、第1ランク及び第2ランクのそれぞれに対し、自己のランクデータが確定している間のみを考慮してランク毎にストローブ調整信号のエッジのタイミングを調整することができる。これにより、各ランクにおいて十分なSETUP/HOLDを確保できる最適なタイミングに、ストローブ調整信号のタイミングを調整することができる。これにより、図4に示すような、データの転送レートが高い場合であっても、メモリデバイス5に記憶されたデータ及びリードデータの信頼性を維持することができる。

【0072】

実施の形態2.

次に、本発明の実施の形態2に係るメモリコンロトーラ及びこれを含むメモリシステムについて説明する。図7は、本発明の実施の形態2にかかるメモリコントローラ8及びこれを含むメモリシステムの構成を示すブロック図である。なお、実施の形態2の基本的な構成については、実施の形態1と同様である。ここで、実施の形態1に係るメモリコントローラ1は、ストローブ信号及びデータ信号を調整するライト/リードストローブ信号調整回路及びライト/リードデータ信号調整回路がランク毎に、それぞれ設けられていた。

【0073】

これに対し、実施の形態2に係るメモリコントローラ8は、ライト/リードストローブ信号調整回路及びライト/リードデータ信号調整回路が、複数のランクにおいて共通に設けられている。なお、アドレス/コマンド制御回路3、データ制御回路4及びメモリデバイス5については、実施の形態1と略同一であるため、同一符号を付すことによりその説明を省略する。また、図7においても、図示されるストローブ信号(DQS)及びデータ信号(DQ)は、調整回路9によって調整される前後のストローブ信号及びデータ信号を含むものとする。

【0074】

図7に示すように、本発明に係るメモリコントローラ8は、調整回路9を備えている。調整回路9は、メモリ素子a〜zに対応する調整回路9a〜9zを備えている。調整回路9は、ライトデータ調整回路91及びリードデータ調整回路92を備えている。ライトデータ調整回路91は、図3の第1処理回路6に相当し、リードデータ調整回路92は、図3の第2処理回路7に相当する。ライトデータ調整回路91は、ライトストローブ調整回路911、ライトデータ調整回路912、及びセレクタ913、914を備えている。

【0075】

ライトストローブ調整回路911には、第1ランクに対して生成されたライト遅延調整信号WD1と、第2ランクに対して生成されたライト遅延調整信号WD2が、セレクタ913を介して入力されている。セレクタ913は、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ランクに対して生成されたライト遅延調整信号WD1又は第2ランクに対して生成されたライト遅延調整信号WD2を選択して、ライトストローブ調整回路911に出力する。

【0076】

ライトストローブ調整回路911は、セレクタ913から第1ランクに対して生成されたライト遅延調整信号WD1を入力すると、このライト遅延調整信号WD1に基づいてストローブ信号(DQS)を遅延調整し、第1ランクのメモリ素子a〜zに対して、第1ライトストローブ調整信号を出力する。同様に、ライトストローブ調整回路911は、セレクタ913から第2ランクに対して生成されたライト遅延調整信号WD2を入力すると、このライト遅延調整信号WD2に基づいてストローブ信号(DQS)を遅延調整し、第2ランクのメモリ素子a〜zに対して、第2ライトストローブ調整信号を出力する。なお、ライト遅延調整信号WD1は、第1ランクのメモリ素子a〜zで共通な値に設定され、ライト遅延調整信号WD2は、第2ランクのメモリ素子a〜zで共通な値に設定されている。

【0077】

ライトデータ調整回路912には、データ制御回路4から、第1ランク又は第2ランクに書き込まれるライトデータ信号が入力される。ライトデータ調整回路912には、第1ランクに対して生成されたライト遅延調整信号WD3と、第2ランクに対して生成されたライト遅延調整信号WD4がセレクタ914を介して入力されている。セレクタ914は、アドレス/コマンド制御回路3から入力されるライトランク有効信号WRに応じて、第1ランクに対して生成されたライト遅延調整信号WD3又は第2ランクに対して生成されたライト遅延調整信号WD4を選択し、ライトデータ調整回路912に出力する。なお、ライト遅延調整信号WD3、4は、各ランクのメモリ素子a〜z毎に、異なる最適な遅延時間に調整されている。

【0078】

リードデータ調整回路92は、リードストローブ調整回路921、リードデータ調整回路922、セレクタ923、924を備えている。リードストローブ調整回路921は、第1ランク又は第2ランクのメモリ素子a〜zからリードストローブ信号が入力される。リードストローブ調整回路921には、セレクタ923を介して、第1ランクに対して生成されたリード遅延調整信号RD1又は第2ランクに対して生成されたリード遅延調整信号RD2が入力されている。セレクタ923は、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1ランクに対して生成されたリード遅延調整信号RD1又は第2ランクに対して生成されたリード遅延調整信号RD2を選択して、リードストローブ調整回路921に出力する。

【0079】

同様に、リードデータ調整回路922は、第1ランク又は第2ランクのメモリ素子a〜zから出力されたリードデータ信号が入力される。リードデータ調整回路922には、セレクタ924を介して、第1ランクに対して生成されたリード遅延調整信号RD3又は第2ランクに対して生成されたリード遅延調整信号RD4が入力されている。セレクタ924は、アドレス/コマンド制御回路3から入力されるリードランク有効信号RRに応じて、第1ランクに対して生成されたライト遅延調整信号RD3又は第2ランクに対して生成されたライト遅延調整信号RD4を選択して、リードデータ調整回路922に出力する。

【0080】

このように、本発明の実施の形態2に係るメモリコントローラ8では、調整回路を各ランク間で共有することで、回路が小さく済むという利点がある。なお、データの信頼性を確保したままライト/リード動作の高速化を実現するという本願の効果については、実施の形態1と同様である。

【0081】

なお、本発明は上記実施の形態1、2に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。また、各実施の形態の全体又は一部の構成は、任意に組合せて実施することができる。

【0082】

また、上記の説明では、本願発明を装置の発明として説明したが、本発明は、メモリデバイスの制御方法としても実施することができる。具体的には、本発明は、複数のメモリ素子から構成されるアクセス単位によってリード/ライト動作を行うメモリデバイスの制御方法であって、上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成し、ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行するメモリデバイスの制御方法として実施することができる。また、このメモリデバイスの制御方法は、コンピュータプログラムに格納することで実施することもできる。

【0083】

なお、上記の実施の形態1、2においては、メモリデバイスが、第1ランク及び第2ランクにより構成されているが、本発明は限られるものでなく、3以上のランクを備えるように構成してもよい。

【0084】

また、上記の説明では、ライト/リードストローブ調整信号は、ランク単位で異なる値に設定されるが、ストローブ調整信号は、メモリ素子毎に各メモリ素子の動作に対して最適化した値に設定するように構成することもできる。

【符号の説明】

【0085】

2、2a〜2z、9、9a〜9z 調整回路

3 アドレス/コマンド制御回路

4 データ制御回路

5 メモリデバイス

6 第1処理回路

7 第2処理回路

1、8、11 メモリコントローラ

21、91 ライトデータ調整回路

22、92 リードデータ調整回路

211 第1ランクライトストローブ調整回路

212 第2ランクライトストローブ調整回路

213 第1ランクライトデータ調整回路

214 第2ランクライトデータ調整回路

215、216、225、226、913、914、923、924 セレクタ

221 第1ランクリードストローブ調整回路

222 第2ランクリードストローブ調整回路

223 第1ランクリードデータ調整回路

224 第2ランクリードデータ調整回路

911 ライトストローブ調整回路

912 ライトデータ調整回路

921 リードストローブ調整回路

922 リードデータ調整回路

【特許請求の範囲】

【請求項1】

複数のメモリ素子から構成されるライト/リードアクセス単位である、二以上のメモリアクセス単位を有するメモリデバイスを制御するメモリコントローラであって、

上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成するデータ制御回路と、

ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、

リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行する調整回路と、を有する、メモリコントローラ。

【請求項2】

前記調整回路は、

前記ライトストローブ信号のタイミングを調整し、前記第1メモリアクセス単位におけるライトデータを取り込むタイミングを指定する第1メモリアクセス単位ストローブ調整信号を生成する第1メモリアクセス単位ライトストロ−ブ調整信号生成回路と、

前記ライトストローブ信号のタイミングを調整し、前記第2メモリアクセス単位におけるライトデータを取り込むタイミングを指定する第2メモリアクセス単位ライトストローブ調整信号を生成する第2メモリアクセス単位ライトストロ−ブ調整信号生成回路と、を有する

請求項1に記載のメモリコントローラ。

【請求項3】

前記調整回路は、

前記リードストローブ信号のタイミングを調整し、前記データ制御回路が前記第1メモリアクセス単位からのリードデータを読み出すタイミングを指定する第1メモリアクセス単位リードストローブ調整信号を生成する第1メモリアクセス単位リードストローブ調整信号生成回路と、

前記リードストローブ信号のタイミングを調整し、前記データ制御回路が前記第2メモリアクセス単位からのリードデータを読み出すタイミングを指定する第2メモリアクセス単位リードストローブ調整信号を生成する第2メモリアクセス単位リードストローブ調整信号生成回路と、を有する

請求項1又は2に記載のメモリコントローラ。

【請求項4】

前記調整回路は、前記ライトストローブ信号のタイミングを選択的に調整可能に構成され、

第1タイミングに調整された前記第1メモリアクセス単位ライトストローブ調整信号を生成して前記第1メモリアクセス単位に供給し、

第2タイミングに調整された前記第2メモリアクセス単位ライトストローブ調整信号を生成して前記第2メモリアクセス単位に供給する

請求項1に記載のメモリコントローラ。

【請求項5】

前記調整回路は、前記リードストローブ信号のタイミングを選択的に調整可能に構成され、

第1タイミングに調整された前記第1メモリアクセス単位リードストローブ調整信号を生成して前記第1メモリアクセス単位に供給し、

第2タイミングに調整された前記第2メモリアクセス単位リードストローブ調整信号を生成して前記第2メモリアクセス単位に供給する

請求項1又は4に記載のメモリコントローラ。

【請求項6】

前記調整回路は、前記メモリ素子毎に、ライト/リードデータ信号のタイミングを調整するデータ調整信号を生成するデータ調整信号生成回路を有する

請求項1乃至5のうちいずれか1項に記載のメモリコントローラ。

【請求項7】

前記第1メモリアクセス単位ライトストローブ信号は、前記第1メモリアクセス単位に入力されるクロックのタイミングに基づいて生成され、

前記第2メモリアクセス単位ライトストローブ信号は、前記第2メモリアクセス単位に入力されるクロックのタイミングに基づいて生成される

請求項2又は4に記載のメモリコントローラ。

【請求項8】

前記第1及び第2メモリアクセス単位は、メモリのランクである、請求項1乃至7のうちいずれか1項に記載のメモリコントローラ。

【請求項9】

メモリデバイスと、請求項1乃至8のうちいずれか1項に記載のメモリコントローラを備えたメモリシステム。

【請求項10】

複数のメモリ素子から構成されるアクセス単位によってリード/ライト動作を行うメモリデバイスの制御方法であって、

上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成し、

ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、

リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行するメモリデバイスの制御方法。

【請求項1】

複数のメモリ素子から構成されるライト/リードアクセス単位である、二以上のメモリアクセス単位を有するメモリデバイスを制御するメモリコントローラであって、

上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成するデータ制御回路と、

ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、

リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行する調整回路と、を有する、メモリコントローラ。

【請求項2】

前記調整回路は、

前記ライトストローブ信号のタイミングを調整し、前記第1メモリアクセス単位におけるライトデータを取り込むタイミングを指定する第1メモリアクセス単位ストローブ調整信号を生成する第1メモリアクセス単位ライトストロ−ブ調整信号生成回路と、

前記ライトストローブ信号のタイミングを調整し、前記第2メモリアクセス単位におけるライトデータを取り込むタイミングを指定する第2メモリアクセス単位ライトストローブ調整信号を生成する第2メモリアクセス単位ライトストロ−ブ調整信号生成回路と、を有する

請求項1に記載のメモリコントローラ。

【請求項3】

前記調整回路は、

前記リードストローブ信号のタイミングを調整し、前記データ制御回路が前記第1メモリアクセス単位からのリードデータを読み出すタイミングを指定する第1メモリアクセス単位リードストローブ調整信号を生成する第1メモリアクセス単位リードストローブ調整信号生成回路と、

前記リードストローブ信号のタイミングを調整し、前記データ制御回路が前記第2メモリアクセス単位からのリードデータを読み出すタイミングを指定する第2メモリアクセス単位リードストローブ調整信号を生成する第2メモリアクセス単位リードストローブ調整信号生成回路と、を有する

請求項1又は2に記載のメモリコントローラ。

【請求項4】

前記調整回路は、前記ライトストローブ信号のタイミングを選択的に調整可能に構成され、

第1タイミングに調整された前記第1メモリアクセス単位ライトストローブ調整信号を生成して前記第1メモリアクセス単位に供給し、

第2タイミングに調整された前記第2メモリアクセス単位ライトストローブ調整信号を生成して前記第2メモリアクセス単位に供給する

請求項1に記載のメモリコントローラ。

【請求項5】

前記調整回路は、前記リードストローブ信号のタイミングを選択的に調整可能に構成され、

第1タイミングに調整された前記第1メモリアクセス単位リードストローブ調整信号を生成して前記第1メモリアクセス単位に供給し、

第2タイミングに調整された前記第2メモリアクセス単位リードストローブ調整信号を生成して前記第2メモリアクセス単位に供給する

請求項1又は4に記載のメモリコントローラ。

【請求項6】

前記調整回路は、前記メモリ素子毎に、ライト/リードデータ信号のタイミングを調整するデータ調整信号を生成するデータ調整信号生成回路を有する

請求項1乃至5のうちいずれか1項に記載のメモリコントローラ。

【請求項7】

前記第1メモリアクセス単位ライトストローブ信号は、前記第1メモリアクセス単位に入力されるクロックのタイミングに基づいて生成され、

前記第2メモリアクセス単位ライトストローブ信号は、前記第2メモリアクセス単位に入力されるクロックのタイミングに基づいて生成される

請求項2又は4に記載のメモリコントローラ。

【請求項8】

前記第1及び第2メモリアクセス単位は、メモリのランクである、請求項1乃至7のうちいずれか1項に記載のメモリコントローラ。

【請求項9】

メモリデバイスと、請求項1乃至8のうちいずれか1項に記載のメモリコントローラを備えたメモリシステム。

【請求項10】

複数のメモリ素子から構成されるアクセス単位によってリード/ライト動作を行うメモリデバイスの制御方法であって、

上位装置との間でライト/リードデータの入出力を行なうと共に、ライトストローブ信号を生成し、

ライト動作において前記データ制御回路により生成される、前記ライトストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、各メモリアクセス単位がライトデータを取り込むタイミングを指定するライトストローブ調整信号を生成する第1処理と、

リード動作において前記メモリデバイスにより生成される、リードストローブ信号のタイミングを前記メモリアクセス単位毎に調整し、前記データ制御部が各メモリアクセス単位から読み出されたリードデータを読み出すタイミングを指定するリードストローブ調整信号を生成する第2処理のうち、少なくとも一方の処理を実行するメモリデバイスの制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−59184(P2012−59184A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−204114(P2010−204114)

【出願日】平成22年9月13日(2010.9.13)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月13日(2010.9.13)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]