メモリコントローラ及びその動作方法、並びにメモリコントローラを含むメモリシステム、3次元メモリシステム、メモリカード、ソリッドステートドライブ、及び携帯用通信装置

【課題】プログラムされるデータのランダム性を増加させるメモリコントローラ及びその動作方法、並びにメモリコントローラを含むメモリシステム、3次元メモリシステム、メモリカード、ソリッドステートドライブ、及び携帯用通信装置を提供する。

【解決手段】本発明のメモリコントローラの動作方法は、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、擬似乱数を用いてページにプログラムされるデータをランダマイズし、ランダマイズされたデータを出力する段階と、を有する。

【解決手段】本発明のメモリコントローラの動作方法は、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、擬似乱数を用いてページにプログラムされるデータをランダマイズし、ランダマイズされたデータを出力する段階と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリコントローラに係り、より詳しくは、隣接する複数のページ(pages)間のシード関連性(seed correlation)を減少させるメモリコントローラ及びその動作方法、並びにメモリコントローラを含むメモリシステム、3次元メモリシステム、メモリカード、ソリッドステートドライブ、及び携帯用通信装置に関する。

【背景技術】

【0002】

擬似乱数(Pseudo−Random Numbers)は、通信システム又はデータ保存システムで広く使われる。擬似乱数は、擬似乱数シーケンス(PseudoRandom Sequence)を発生するために使われる。即ち、擬似乱数は、最初に与えられる初期値を用いて、既に決定されているメカニズム、例えば擬似乱数生成器によって生成される数を意味する。

【0003】

乱数は、その生成方法が決定されていないので、次に生成される値、即ち数(number)を全く予測することができない。しかし、擬似乱数生成器によって生成される数は、擬似乱数生成器の初期値が分かると計算され得るので、本当の乱数と区別するために、擬似乱数と言う。

【0004】

線形フィードバックシフトレジスタ(Linear Feedback Shift Register:LFSR)は、擬似乱数シーケンスを発生するために使われる。LFSRは、シード(seed)と呼ばれる初期値を変更するか、又はフィードバックタップ(feedback taps)を変更することによって、擬似乱数シーケンスを変更することができる。上述したように、擬似乱数は初期値を用いて計算され得るので、擬似乱数は計算され得る。従って、擬似乱数を容易に計算することができない方法が要求される。

【0005】

ランダマイザー(randomizer)は、LFSRによって生成された擬似乱数シーケンスを用いて、データをランダマイズされたデータに変換する。デランダマイザー(derandomizer)は、LFSRによって生成された擬似乱数シーケンスを用いて、ランダマイズされたデータをデランダマイズされたデータに変換する。従って、擬似乱数シーケンスを容易に計算することができないランダマイザー又はデランダマイザーが要求される。

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は上記従来技術に鑑みてなされたものであって、本発明の目的は、プログラムされるデータのランダム性(randomness)を増加させるために、隣接する複数のページ間のシード関連性を減少又は除去するメモリコントローラ及びその動作方法、並びにメモリコントローラを含むメモリシステム、3次元メモリシステム、メモリカード、ソリッドステートドライブ、及び携帯用通信装置を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するためになされた本発明の一特徴によるメモリコントローラの動作方法は、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有する。

【0008】

一態様において、前記擬似乱数を生成する段階は、前記ページのページアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリー(entry)を前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含む。

前記メモリコントローラの動作方法は、前記エントリーポインターによって指定されたエントリーが選択された後、前記エントリーポインターを変更する段階を更に有し、前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト(default)値にリセットされる。

他の態様において、前記擬似乱数を生成する段階は、前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含む。

前記複数のシードグループのそれぞれが複数のページのそれぞれに対応する場合、前記複数のページの数は、1本のワードラインに接続された複数のマルチレベルセルのそれぞれに保存されるビットの数と同一である。

【0009】

上記目的を達成するためになされた本発明の他の特徴によるメモリコントローラの動作方法は、それぞれが異なるシードテーブル(seed table)に保存された複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、前記擬似乱数を用いて、前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有する。

【0010】

上記目的を達成するためになされた本発明の更に他の特徴によるメモリコントローラの動作方法は、複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを用いて擬似乱数を生成する段階と、前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有し、前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、前記複数のゾーンのうちから前記シードグループに相応するゾーンは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択され、前記シードは、前記選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーである。

【0011】

上記目的を達成するためになされた本発明の一特徴によるメモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を備え、前記マイクロプロセッサは、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択した後、前記エントリーポインターを変更し、前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト値にリセットされる。

【0012】

前記メモリコントローラは、前記複数のシードグループを保存するROM(Read Only Memory)を更に備える。

一態様において、前記マイクロプロセッサは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する。

前記複数のシードグループのそれぞれは、異なるシードテーブルに保存される。

他の態様において、前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、前記マイクロプロセッサは、前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択する。

【0013】

上記目的を達成するためになされた本発明の一特徴によるメモリシステムは、複数のページを有するメモリセルアレイを含む不揮発性メモリ装置と、前記不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記不揮発性メモリ装置に出力するランダマイザーと、を含む。

【0014】

一態様において、前記複数のシードグループのそれぞれが互いに異なるシードテーブルに保存される場合、前記マイクロプロセッサは、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択する。

前記マイクロプロセッサは、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択する。

他の態様において、前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、前記マイクロプロセッサは、前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択する。

前記メモリシステムは、前記不揮発性メモリ装置と前記メモリコントローラとを含むマルチチップパッケージ(Multi−Chip Package)である。

【0015】

上記目的を達成するためになされた本発明の一特徴によるメモリカードは、複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、ホストと通信するためのカードインターフェースと、前記フラッシュメモリ装置と前記カードインターフェースとの間の通信を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含む。

【0016】

前記メモリカードは、MMC(MultimMedia Card)、SD(Secure Digital)カード、又はUSBフラッシュドライブである。

【0017】

上記目的を達成するためになされた本発明の一特徴による携帯用通信装置は、複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、前記フラッシュメモリ装置の動作を制御するメモリコントローラと、前記メモリコントローラの制御によって前記フラッシュメモリ装置から出力されたデータをディスプレイするディスプレイと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含む。

【0018】

上記目的を達成するためになされた本発明の一特徴による3次元メモリシステムは、それぞれが複数のページを有する複数のレイヤを含む3次元不揮発性メモリ装置と、前記3次元不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を含む。

【0019】

上記目的を達成するためになされた本発明の一特徴によるソリッドステイブドライブは、それぞれが複数のページを含む複数のソリッドステートメモリ装置と、前記複数のソリッドステートメモリ装置のそれぞれの動作を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを現在プログラムされる前記ページに出力するランダマイザーと、を含む。

【発明の効果】

【0020】

本発明によるメモリコントローラ及びその動作方法によれば、ページ毎に異なるシードテーブルに含まれるシード又はページ毎に異なるゾーンに含まれるシードを用いて生成された擬似乱数によってデータをランダマイズすることによって、複数のページ間のシード関連性を防止することができる。

【図面の簡単な説明】

【0021】

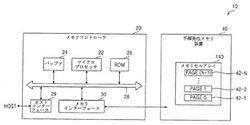

【図1】本発明の一実施形態によるメモリコントローラを含むメモリシステムのブロック図を示す。

【図2】図1に示したメモリシステムを含むマルチチップパッケージの一例を示す。

【図3】図1に示したメモリシステムを含むマルチチップパッケージの他の例を示す。

【図4】図1に示したメモリインターフェースのブロック図の一例を示す。

【図5】図1に示したメモリインターフェースのブロック図の他の例を示す。

【図6】ページ別に割り当てられたシードテーブルの一例を示す。

【図7】ページ別に割り当てられたシードテーブルの他の例を示す。

【図8】ページ別に割り当てられたゾーン(zones)を含む1つのシードテーブルを示す。

【図9】図8に示した1つのゾーン(zone)に含まれるエントリーを示す。

【図10】図1に示した不揮発性メモリ装置の2次元的な構造のメモリセルアレイを含むブロック図の一例を示す。

【図11】図1に示した不揮発性メモリ装置の3次元的な構造のメモリセルアレイの一例を示す。

【図12】ページ別に割り当てられたシードテーブルを用いる図1に示したメモリシステムの動作を説明するフローチャートである。

【図13】1つのシードテーブルに含まれる複数のゾーンを用いる図1に示したメモリシステムの動作を説明するフローチャートである。

【図14】図1に示したメモリシステムを含む電子装置の一実施例を示す。

【図15】図1に示したメモリシステムを含む電子装置の他の実施例を示す。

【図16】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図17】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図18】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図19】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図20】図19に示した電子装置を含むデータ処理システムのブロック図を示す。

【発明を実施するための形態】

【0022】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳しく説明する。

【0023】

図1は、本発明の一実施形態によるメモリコントローラ20を含むメモリシステム10のブロック図を示す。図1を参照すると、メモリシステム10は、メモリコントローラ20及び不揮発性メモリ装置40を含む。メモリコントローラ20は、ホストHOSTの制御によって、不揮発性メモリ装置40のデータ処理動作、例えば、プログラム(program)動作、リード(read)動作、及びイレーズ(erase)動作を制御する。

【0024】

後述する図6及び図7に示す実施例において、メモリコントローラ20は、複数のシードテーブルST1〜ST4及びST11〜ST13のうちから現在プログラムされるページに対する(又は、割り当てられた)シードテーブルを選択し、選択されたシードテーブルに含まれる1つ又はそれ以上のエントリー(entries)のうちからエントリーポインター(entry pointer)によって指定されたエントリーをページのシードとして選択し、選択されたシードを用いて擬似乱数を生成し、生成された擬似乱数によって、ページにプログラムされるデータをランダマイズ(randomize)し、ランダマイズされたデータを不揮発性メモリ装置40に出力する。

【0025】

ここで、複数のページのそれぞれは、プログラム動作によるワードライン(word line)方向のフローティングゲートカップリング(floating gate coupling)、リードディスターバンス(read disturbance)、又はバックパターンディペンデンシー(back−pattern dependancy)などによって、互いに影響を受けるものと仮定する。ここで、リードディスターバンスは、リード動作の間に選択されていない複数のワードラインのそれぞれに接続された複数のメモリセルがプログラムされる現象を意味する。

【0026】

後述する図8及び図9に示す他の実施例において、メモリコントローラ20は、1つのシードテーブルST21に含まれ、それぞれが複数のエントリーを含み、それぞれが複数のページのそれぞれに割り当てられた複数のゾーンZONE0〜ZONE15のうちの何れか1つのゾーンを選択し、選択されたゾーンに含まれる1つ又はそれ以上のエントリーのうちからエントリーポインターENTRY_PNTZ0によって指定されたエントリーENTRY_Z11を現在プログラムされるページのシードとして選択し、選択されたシードを用いて擬似乱数を生成し、擬似乱数を用いて、ページにプログラムされるデータをランダマイズし、ランダマイズされたデータを不揮発性メモリ装置40に出力する。

【0027】

メモリコントローラ20は、マイクロプロセッサ22、バッファ24、ROM26、ホストインターフェース29、及びメモリインターフェース30を含む。これらの各構成要素(22、24、26、29、及び30)は、バス28を通じて互いに通信することができる。

【0028】

回路(circuit)、ロジック(logic)、コード(code)、又はこれらの組合せで具現可能なマイクロプロセッサ22は、各構成要素(24、26、29、及び30)の動作を制御する。

【0029】

図6及び図7に示す実施例において、マイクロプロセッサ22は、複数のシードテーブルST1〜ST4又はST11〜ST13、例えばページ別に割り当てられた複数のシードテーブルST1〜ST4又はST11〜ST13のうちから現在プログラムされるページに割り当てられたシードテーブルを選択する動作、及び/又は選択されたシードテーブルに含まれる1つ又はそれ以上のエントリーのうちの何れか1つのエントリーを選択するエントリーポインターを変更する動作を行う。

【0030】

この際、マイクロプロセッサ22は、現在プログラムされるページのページアドレスの少なくとも一部のビット、又はページに相応するワードラインアドレスの少なくとも一部のビットを用いて、複数のシードテーブルのうちの何れか1つを選択する。ここで、一部のビットは、1ビット又はそれ以上のビットを意味する。

【0031】

図8及び図9に示す他の実施例において、マイクロプロセッサ22は、1つのシードテーブルST21に含まれる複数のゾーンZONE0〜ZONE15のうちの何れか1つのゾーンを選択する動作、及び/又は選択されたゾーンに含まれる1つ又はそれ以上のエントリーのうちの何れか1つのエントリーを選択するエントリーポインターを変更する動作を行う。一実施例において、1つのシードテーブルST21は、独立した複数のゾーンにパーティション(partition)される。この際、マイクロプロセッサ22は、現在プログラムされるページのページアドレスの少なくとも一部のビット、又はページに相応するワードラインアドレスの少なくとも一部のビットを用いて、複数のゾーンのうちの何れか1つを選択する。

【0032】

バッファ24は、DRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)、又はデュアルポート(Dual−Port)SRAMのような揮発性(volatile)メモリとして具現可能である。一実施例において、複数のシードテーブルは、不揮発性メモリ装置40のメモリセルアレイ140に保存されるか、又はROM26に保存される。この場合、メモリセルアレイ140又はROM26に保存された複数のシードテーブルのそれぞれは、マイクロプロセッサ22の制御によってバッファ24にローディングされる。ここで、複数のページ42−1〜42−Nが複数のグループにグルーピングされる場合、複数のシードテーブルのそれぞれは、複数のグループのそれぞれに対応する。

【0033】

他の実施例において、複数のゾーンZONE0〜ZONE15を含む1つのシードテーブルST21は、メモリセルアレイ140又はROM26に保存される。この場合、メモリセルアレイ140又はROM26に保存された1つのシードテーブルST21は、マイクロプロセッサ22の制御によってバッファ24にローディングされる。例えば、ページ別のシードテーブル又は1つのシードテーブルは、メモリコントローラ20のパワーアップ(power−up)動作の間にバッファ24にローディングされるか、又はメモリコントローラ20の動作の間にリアルタイムでバッファ24にローディングされる。

【0034】

ROM26は、メモリコントローラ20の動作に必要なプログラムコードを保存する。上述したように、ROM26には、ページ別に割り当てられたシードテーブル又は1つのシードテーブルを保存することができる。

【0035】

ホストHOSTとメモリコントローラ20は、ホストインターフェース29を通じて通信する。ホストHOSTは、プログラム要求(program request)と不揮発性メモリ装置40にプログラムされるデータを、ホストインターフェース29を通じてメモリコントローラ20に伝送する。この際、メモリコントローラ20は、プログラム要求によって、データが保存される不揮発性メモリ装置40のページのページアドレス及び/又はページに相応するワードラインアドレスを生成する。

【0036】

メモリコントローラ20と不揮発性メモリ装置40は、メモリインターフェース30を通じて互いに通信する。

【0037】

不揮発性メモリ装置40のメモリセルアレイ140は、複数のメモリブロック(memory block)を含み、複数のメモリブロックのそれぞれは、複数のページ42−1〜42−Nを含み、複数のページ42−1〜42−Nのそれぞれは、複数の不揮発性メモリセル、例えばNANDフラッシュメモリセルを含む。NANDフラッシュメモリセルのそれぞれは、1ビット又はそれ以上のビットを保存する。

【0038】

不揮発性メモリ装置40、例えばNANDフラッシュメモリ装置で、プログラム動作又はリード動作はページ(page)単位で行われ、イレーズ動作はメモリブロック単位で行われる。ここで、ページは、1本のワードラインに接続された複数の不揮発性メモリセル、例えばNANDフラッシュメモリセルに定義されるメモリ領域を意味する。例えば、NANDフラッシュメモリセルのそれぞれが、1ビットを保存するSLC(Single Level Cell)である場合、1本のワードラインは、1枚のページと定義される。

【0039】

NANDフラッシュメモリセルのそれぞれが、2ビット以上を保存するMLC(Multi Level Cell)である場合、1本のワードラインは、1本のワードラインに接続された複数のMLCのそれぞれにプログラムされるビット数と同じページ数を有すると定義される。

【0040】

例えば、複数のMLCのそれぞれが2ビットMLCである場合、1本のワードラインは、2枚のページ、例えば第1ページと第2ページとを含み、複数のMLCのそれぞれが3ビットMLCである場合、1本のワードラインは、3枚のページ、例えば第1ページ、第2ページ、及び第3ページを含む。

【0041】

第1ページは、LSB(Least Significant Bit)ページを意味し、第2ページは、MSB(Most Significant Bit)ページを意味し、第3ページは、CSB(Center Significant Bit)ページを意味する。

【0042】

図2は、図1に示したメモリシステムを含むマルチチップパッケージの一例を示す。図2を参照すると、マルチチップパッケージ11は、回路基板11−1、例えばPCB(Printed Circuit Board)上にマウント(mounted)又は積層された(stacked)メモリコントローラ20と、メモリコントローラ20上にマウント又は積層された不揮発性メモリ装置40とを含む。メモリコントローラ20は、ボンディングワイヤ(bonding wires)11−2とソルダボール(solder balls)11−3とを通じて外部装置と通信する。また、メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ11−4を通じて通信する。

【0043】

図2では、説明の便宜上、不揮発性メモリ装置40がメモリコントローラ20上に形成された例を示したが、一実施例として、これらの2つの装置(20、40)の具現位置が互いに変わり得る。また、メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ11−4以外の接続手段を通じて互いに通信し、メモリコントローラ20とソルダボール11−3は、ボンディングワイヤ11−2以外の接続手段を通じて互いに接続され得る。接続手段は、垂直電気素子(vertical electrical element)、例えば、TSV(Through Silicon Via)として具現されることもある

【0044】

図3は、図1に示したメモリシステムを含むマルチチップパッケージの他の例を示す。図3を参照すると、マルチチップパッケージ13は、回路基板13−1、例えば、PCB上に接続されたメモリコントローラ20と不揮発性メモリ装置40とを含む。メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ13−2を通じて互いに通信し、メモリコントローラ20と不揮発性メモリ装置40のそれぞれは、ボンディングワイヤ13−3とソルダボール13−4とを通じて外部装置と通信する。

【0045】

一実施例として、メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ13−2以外の接続手段を通じて互いに通信することができる。接続手段は、垂直電気素子、例えばTSVとして具現されることもある。例えば、メモリコントローラ20と不揮発性メモリ装置40のそれぞれが垂直電気素子を通じて回路基板13−1に接続される場合、メモリコントローラ20と不揮発性メモリ装置40は、垂直電気素子と回路基板13−1とを通じて互いに通信することができる。

【0046】

それぞれのチップ(chip)として具現されたメモリコントローラ20と不揮発性メモリ装置40は、PoP(Package on Package)、BGAs(BallGrid Arrays)、CSPs(Chip Scale Packages)、PLCC(Plastic Leaded Chip Carrier)、PDIP(Plastic Dual In−Line Package)、Die in Waffle Pack、Din in Wafer Form、COB(Chip On Board)、CERDIP(CERamic Dual In−Line Package)、MQFP(Plastic Metric Quad Flat Pack)、TQFP(ThinQuad FlatPack)、SOIC(Small−Outline Integrated Circuit)、SSOP(Shrink Small Outline Package)、TSOP(Thin Small Outline Package)、SiP(System in Package)、MCP(Multi Chip Package)、WFP(Wafer−level Fabricated Package)、又はWSP(Wafer−level processed Stack Package)のようなパッケージとして具現可能である。

【0047】

図4は、図1に示したメモリインターフェースのブロック図の一例を示す。図4を参照すると、図1に示したメモリインターフェース30の一例として具現されたメモリインターフェース30は、データ変換装置30Aとして使用される。

【0048】

データ変換装置30Aは、データ経路(data path)によってランダマイザー又はデランダマイザーとして使用される。データ変換装置30Aは、擬似乱数生成器(pseudo random number generator)32とモジュロ演算器(modulo operator)34とを含む。

【0049】

擬似乱数生成器32は、ページ別に割り当てられた(assigned)シードテーブルに含まれるシードSEED、又はページ別に割り当てられたゾーンに含まれるシードSEEDを用いて、擬似乱数(又は、擬似乱数シーケンス)RSを生成する。一実施例として、擬似乱数生成器32は、LFSR(Linear Feedback Shift Register)として具現され、LFSRは、シードSEEDを用いてフィードバック多項式(feedback polynomial)を決定する。従って、擬似乱数RSは、フィードバック多項式によって決定される。LFSRは、フィボナッチ(Fibonacci)LFSR又はガロア(Galois)LFSRとして具現可能である。擬似乱数生成器32に含まれる構成要素によって、擬似乱数生成器32は、線形擬似乱数RS又は非線形擬似乱数RSを発生する。

【0050】

モジュロ演算器34は、擬似乱数RSと現在プログラムされるページにプログラムされるデータDATA1とをモジュロ演算(modulo operation)して、ランダマイズされたデータRDATAを発生する。擬似乱数RSを用いてデータDATA1をランダマイズする場合、モジュロ演算器34は、擬似乱数RSとデータDATA1とをモジュロ加算(modulo addition)して、ランダマイズされたデータRDATAを生成する。

【0051】

擬似乱数RSを用いてランダマイズされたデータRRDATA2をデランダマイズする場合、モジュロ演算器34は、ランダマイズされたデータRRDATA2から擬似乱数RSをモジュロ減算(modulo subtraction)して、データDATA2を生成する。

【0052】

モジュロ2加算の結果とモジュロ2減算の結果は、互いに同一なので、擬似乱数RSが2進シーケンス(binary sequence)である場合、モジュロ演算器34は、排他論理和ゲート(exclusive OR gate)として具現可能である。

【0053】

データ変換装置30Aは、エラー訂正コード(Error Correction Code、ECC)ブロック36を更に含む。

【0054】

プログラム動作の間に、ECCブロック36は、ランダマイズされたデータRDATAにECCパリティビットを付け加え、ECCパリティビットを含むランダマイズされたデータERDATAを生成する。また、リード動作の間に、ECCブロック36は、ランダマイズされたデータRRDATA1とECCパリティビットとを受信し、ECCパリティビットを用いてランダマイズされたデータRRDATA1に含まれる少なくとも1つのエラーを訂正し、エラー訂正されたランダマイズされたデータRRDATA2をモジュロ演算器34に出力する。

【0055】

モジュロ演算器34は、エラー訂正されたランダマイズされたデータRRDATA2から擬似乱数RSをモジュロ減算して、データDATA2を生成する。

【0056】

図5は、図1に示したメモリインターフェースのブロック図の他の例を示す。図5を参照すると、図1に示したメモリインターフェース30の他の例として具現されたメモリインターフェース30は、データ変換装置30Bとして使用される。

【0057】

第1モジュロ演算器34−1と第2モジュロ演算器34−2は、1つの擬似乱数生成器32を共有する。

【0058】

プログラム動作の間に、第1レベル、例えばハイレベルを有するプログラムイネーブル信号WEによってイネーブルされた第1モジュロ演算器34−1は、擬似乱数RSを用いてデータDATA1をランダマイズされたデータRDATAにランダマイズする。リード動作の間に、第1レベルを有するリードイネーブル信号REによってイネーブルされた第2モジュロ演算器34−2は、ランダマイズされたデータRRDATA2を、擬似乱数RSを用いてデータDATA2にデランダマイズする。

【0059】

プログラムイネーブル信号WEが、第2レベル、例えばローレベルから第1レベルに変更される時点と、リードイネーブル信号REが、第2レベルから第1レベルに変更される時点とを適切に調節することにより、プログラム動作とリード動作は、互いに異なる時点又は同時に行われる。

【0060】

第1モジュロ演算器34−1はモジュロ加算を行い、第2モジュロ演算器34−2はモジュロ減算を行う。一実施例として、擬似乱数RSが2進シーケンスである場合、これらの各モジュロ演算器(34−1、34−2)は、排他論理和ゲートとして具現可能である。データ変換装置30Bは、ECCブロック36を更に含む。

【0061】

図6は、ページ別に割り当てられたシードテーブルの一例を示す。図6は、説明の便宜上、それぞれが4枚のページのそれぞれに割り当てられた4つのシードテーブルST1〜ST4を示しており、4つのシードテーブルST1〜ST4のそれぞれは、複数のエントリーENTRY11〜ENTRY1m、ENTRY21〜ENTRY2l、ENTRY31〜ENTRY3k、及びENTRY41〜ENTRY4pを含む。ここで、m、l、k、及びpは、自然数である。

【0062】

複数のエントリーENTRY11〜ENTRY1m、ENTRY21〜ENTRY2l、ENTRY31〜ENTRY3k、及びENTRY41〜ENTRY4pのそれぞれは、図4又は図5に示した擬似乱数生成器32で使われるシード値(これを、‘シード’と称する)を含む。

【0063】

図6では、説明の便宜上、各エントリーポインターENTRY_PNT1〜ENTRY_PNT4が、各シードテーブルST1〜ST4の最初のエントリーENTRY11、ENTRY21、ENTRY31、及びENTRY41をデフォルトに指定することを示す。しかし、各エントリーポインターENTRY_PNT1〜ENTRY_PNT4は、図1のマイクロプロセッサ22の制御によって、複数のエントリーのうちの何れか1つのエントリーを指定できるように設定し得る。

【0064】

例えば、ホストHOSTから第1データをプログラムせよとの要請が入力されると、マイクロプロセッサ22は、この要請に応答して、第1データを第1ページ42−1にプログラムするために、第1アドレス、例えば、第1ページアドレス又は第1ページ42−1に相応する第1ワードラインアドレスを生成し、生成された第1アドレスの少なくとも一部のビットを用いて、複数のシードテーブルST1〜ST4のうちから第1シードテーブルST1を選択する。

【0065】

そして、マイクロプロセッサ22は、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちから現在エントリーポインターENTRY_PNT1が指定するエントリーENTRY11を、第1データをプログラムするためのシードとして選択し、エントリーポインターENTRY_PNT1を次のエントリーENTRY12を指定するためにインクリメントする。

【0066】

ホストHOSTから第2データ、第3データ、又は第4データをプログラムせよとの要請が入力されると、マイクロプロセッサ22は、上述したような方法でそれぞれのシードテーブルST2、ST3、又はST4でそれぞれの現在エントリーポインターENTRY_PNT2、ENTRY_PNT3、又はENTRY_PNT4が指定するそれぞれのエントリーENTRY21、ENTRY31、又はENTRY41を第1データ、第2データ、又は第3データをプログラムするためのそれぞれのシードとして選択し、それぞれの現在エントリーポインターENTRY_PNT2、ENTRY_PNT3、又はENTRY_PNT4をインクリメントする。

【0067】

メモリコントローラ20がリセットされると、プログラム動作によってインクリメントされたそれぞれのエントリーポインターは、それぞれのデフォルト値ENTRY11、ENTRY21、ENTRY31、及びENTRY41にリセットされる。

【0068】

例えば、シードテーブルST1〜ST4が4つである場合、T(Tは、自然数)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちの何れか1つが選択され、(T+1)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第2シードテーブルST2に含まれる複数のエントリーENTRY21〜ENTRY2lのうちの何れか1つが選択され、(T+2)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第3シードテーブルST3に含まれる複数のエントリーENTRY31〜ENTRY3kのうちの何れか1つが選択され、(T+3)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第4シードテーブルST4に含まれる複数のエントリーENTRY41〜ENTRY4pのうちの何れか1つが選択される。

【0069】

例えば、最初のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちから第1エントリーENTRY11が選択され、5番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちから第2エントリーENTRY12が選択され得る。

【0070】

図7は、ページ別に割り当てられたシードテーブルの他の例を示す。図7に示したように、1本のワードラインに接続された複数の3ビットMLCのそれぞれが互いに影響を与える場合、ページ別にそれぞれ異なるシードテーブルST11、ST12、又はST13が使われる。複数のシードテーブルST11〜ST13のそれぞれは、ページアドレスの少なくとも一部のビットを用いて選択される。

【0071】

例えば、LSBページに、LSBデータをプログラムする際、マイクロプロセッサ22は、LSBシードテーブルST11に含まれる複数のエントリーENTRYL01、ENTRYL02、ENTRYL03,…のうちから現在エントリーポインターENTRY_PNTLが指定するエントリーENTRYL01を選択した後、現在エントリーポインターENTRY_PNTLをインクリメントする。

【0072】

CSBページに、CSBデータをプログラムする際、マイクロプロセッサ22は、CSBシードテーブルST12に含まれる複数のエントリーENTRYC01、ENTRYC02、ENTRYC03、…のうちから現在エントリーポインターENTRY_PNTCが指定するエントリーENTRYC01を選択した後、現在エントリーポインターENTRY_PNTCをインクリメントする。

【0073】

MSBページに、MSBデータをプログラムする際、マイクロプロセッサ22は、MSBシードテーブルST13に含まれる複数のエントリーENTRYM01、ENTRYM02、ENTRYM03、…のうちから現在エントリーポインターENTRY_PNTMが指定するエントリーENTRYM01を選択した後、現在エントリーポインターENTRY_PNTMをインクリメントする。

【0074】

各エントリーポインターENTRY_PNTL、ENTRY_PNTC、及びENTRY_PNTMを如何に、及び/又はどれほどインクリメントするかは、マイクロプロセッサ22によって決定される。

【0075】

メモリコントローラ20がリセットされると、プログラム動作によってインクリメントされたそれぞれのエントリーポインターENTRY_PNTL、ENTRY_PNTC、及びENTRY_PNTMは、それぞれのデフォルト値ENTRYL01、ENTRYC01、及びENTRYC01にリセットされる。

【0076】

図8は、ページ別に割り当てられたゾーンを含む1つのシードテーブルを示し、図9は、図8に示した1つのゾーンに含まれるエントリーを示す。

【0077】

図8及び図9を参照すると、1つのシードテーブルST21は、複数のゾーンZONE0〜ZONE15を含み、複数のゾーンZONE0〜ZONE15のそれぞれは、複数のエントリーを含む。図8及び図9は、説明の便宜上、16個のゾーンZONE0〜ZONE15を含む1つのシードテーブルST21を示しているが、これは例示的なものに過ぎない。16個のゾーンZONE0〜ZONE15のそれぞれは、ページアドレスPADDの下位ビットPADD[3:0]によって選択され、16個のゾーンZONE0〜ZONE15のそれぞれに含まれる複数のエントリーのうちの何れか1つのエントリーは、現在エントリーポインターによって指定される。

【0078】

例えば、5つのエントリーENTRY_Z11〜ENTRY_Z15を含む第1ゾーンZONE0は、ページアドレスの下位ビットPADD[3:0]=0000によって選択され、エントリーENTRY_Z11は、エントリーポインターENTRY_PNTZ0によって選択される。エントリーENTRY_Z11が選択された後、エントリーポインターENTRY_PNTZ0は、次のエントリーENTRY_Z12を指定するためにインクリメントされる。即ち、プログラム動作によってエントリーが選択された後、エントリーポインターENTRY_PNTZ0は、次のエントリーを指定するためにインクリメントされる。メモリコントローラ20がリセットされる度に、エントリーポインターENTRY_PNTZ0は、デフォルト値、例えば、ENTRY_Z11に初期化される。

【0079】

上述したように、1つのシードテーブルST21は、不揮発性メモリ装置40のメモリセルアレイ140に保存されるか、又はメモリコントローラ20のROM26に保存されて、マイクロプロセッサ22の制御によってバッファ24にローディングされるか、又はマイクロプロセッサ22によって参照(reference)される。

【0080】

図10は、図1に示した不揮発性メモリ装置の2次元的な構造のメモリセルアレイを含むブロック図の一例を示す。図1及び図10を参照すると、不揮発性メモリ装置40、例えば、NANDフラッシュメモリ装置は、データを保存するためのメモリセルアレイ140、コントロールロジック43、電圧発生器44、ローデコーダ45、ページバッファブロック46、カラムデコーダ47、Y−ゲーティング回路48、及び入出力ブロック49を含む。

【0081】

メモリセルアレイ140は、複数のNANDメモリセルストリング(strings)を含む。複数のNANDメモリセルストリングのそれぞれは、直列に接続された複数のNANDメモリセル41を含む。例えば、第1NANDメモリセルストリングは、ビットラインBL1に接続された第1選択トランジスタ(又は、ストリング選択トランジスタ(string selection transistor))と共通ソースライン(Common Source Line、CSL)に接続された第2選択トランジスタ(又は、接地選択トランジスタ(ground selection transistor))との間に直列に接続された複数のNANDメモリセル41を含む。

【0082】

第1選択トランジスタのゲートは、ストリング選択ライン(String Selection Line、SSL)に接続され、複数のNANDメモリセル41のそれぞれのゲートは、複数のワードラインWL0〜WL63のそれぞれに接続され、第2選択トランジスタのゲートは、接地選択ライン(Ground Selection Line、GSL)に接続される。上述したように、メモリセルのそれぞれがSLCである場合、各ワードライン(例えば、WL0〜WL3)は、各ページPAGE0〜PAGE3を定義する。

【0083】

図10は、64本のワードラインWL0〜WL63を含むメモリセルアレイ140を示しているが、ワードラインの個数に限定されるものではない。

【0084】

図11は、図1に示した不揮発性メモリ装置の3次元的な構造のメモリセルアレイの一例を示す。図1及び図11に示したように、各NANDメモリセルストリング40′−1、40′−2、…、40′−t(tは、自然数)は、3次元的にそれぞれ異なる平面に配置される。図11に示したように、第1NANDメモリセルストリング40′−1は、第1レイヤ41−1に配され、第2NANDメモリセルストリング40′−2は、第1レイヤ41−1と互いに異なる第2レイヤ41−2に配され、第t NANDメモリセルストリング40′−tは、第2レイヤ41−2とそれぞれ異なるレイヤ41−kに3次元的に配置される。

【0085】

複数のレイヤ41−1〜41−tは、ウェーハ積層(wafer stack)、チップ積層、又はセル(cell)積層を通じて形成される。複数のレイヤ41−1〜41−tは、TSVを含む電気垂直素子(electrical vertical element)、ポンプ(bump)、又はワイヤボンディング(wire bonding)を通じて接続される。複数のレイヤ41−1〜41−tのそれぞれは、複数のセルストリングを含む。

【0086】

図11に示したように、各NANDメモリセルストリング40′−1、40′−2、…、40′−tは、複数のワードラインWL0〜WL63、CSL、及びビットラインBL1を共有する。

【0087】

本明細書で使用するメモリセルアレイ140、140′は、図10に示した2次元メモリセルアレイ140と図11に示した3次元メモリセルアレイ140′とを総括的に意味する。

【0088】

図10を再び参照すると、回路、ロジック、コード、又はこれらの組合せで具現可能なコントロールロジック43は、NANDフラッシュメモリ装置140のデータ処理動作、例えば、プログラム動作、リード動作、及びイレーズ動作を制御する。例えば、コントロールロジック43は、メモリコントローラ20から出力された複数の制御信号によって、データ処理動作を行うために、各構成要素44〜49の動作を制御する。

【0089】

電圧発生器44は、プログラム動作を行うために必要なプログラム電圧を含む複数の電圧、リード動作を行うために必要なリード電圧を含む複数の電圧、又はイレーズ動作を行うために必要なイレーズ電圧を含む複数の電圧を発生する。電圧発生器44は、それぞれの動作に必要な複数の電圧をローデコーダに出力する。

【0090】

ローデコーダ45は、コントロールロジック43から出力されたローアドレスによって、電圧発生器44から出力された複数の電圧を複数のワードラインWL0〜WL63に供給する。カラムデコーダ47は、コントロールロジック43の制御下でカラムアドレスをデコーディングして、複数の選択信号をY−ゲーティング回路48に出力する。

【0091】

ページバッファブロック46は、複数のページバッファを含む。複数のページバッファのそれぞれは、複数のビットラインBL1〜BLx(xは、自然数)のそれぞれに接続される。複数のページバッファのそれぞれは、コントロールロジック43の制御によるプログラム動作の間、メモリセルアレイ140にデータをプログラムするためのドライバーとして作動する。また、複数のページバッファのそれぞれは、コントロールロジック43の制御によるリード動作の間、又は検証(verify)動作の間、複数のビットラインBL1〜BLxのそれぞれの電圧レベルを感知増幅する感知増幅器として作動する。

【0092】

Y−ゲーティング回路48は、カラムデコーダ47から出力された複数の選択信号に応答して、ページバッファブロック46と入出力ブロック49との間でデータDATAの伝送を制御する。入出力ブロック49は、メモリコントローラ20から入力されたデータDATAをY−ゲーティング回路48に伝送するか、又はY−ゲーティング回路48から出力されたデータDATAを複数の入出力ピン又はデータバスを通じてメモリコントローラ20に伝送する。

【0093】

図12は、ページ別に割り当てられたシードテーブルを用いる図1に示したメモリシステムの動作を説明するフローチャートであり、図13は、1つのシードテーブルに含まれる複数のゾーンを用いる図1に示したメモリシステムの動作を説明するフローチャートである。

【0094】

図1〜図13を参照して、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するメモリコントローラ20の動作を説明すると、次の通りである。

【0095】

図6及び図7に示したように、複数のシードグループのそれぞれは、それぞれ異なるシードテーブルST1〜ST4又はST11〜ST13に保存されるか、或いは図8に示したように、1つのシードテーブルST21に保存される。

【0096】

メモリコントローラ20は、パワーアップされる(ステップS110)。この際、以前プログラム動作によってインクリメントされたエントリーポインターENTRY_PNT1、ENTRY_PNT2、ENTRY_PNT3、ENTRY_PNT4、ENTRY_PNTL、ENTRY_PNTC、ENTRY_PNTM、又はENTRY_PNTZ0は、デフォルト値ENTRY11、ENTRY21、ENTRY31、ENTRY41、ENTRYL01、ENTRYC01、ENTRYM01、又はENTRY_Z11に初期化される。

【0097】

メモリコントローラ20は、ホストHOSTから出力されたデータとプログラム要求とを受信する。一実施例において、複数のシードテーブルST1〜ST4、ST11〜ST13は、パワーアップ動作の間にバッファ24にローディングされるか、又はプログラム動作の間にリアルタイムでバッファ24にローディングされる(ステップS120)。他の実施例において、1つのシードテーブルST21は、パワーアップ動作の間にバッファ24にローディングされるか、又はプログラム動作の間にリアルタイムでバッファ24にローディングされる(ステップS220)。

【0098】

プログラム要求によって、データを不揮発性メモリ装置40にプログラムするために、マイクロプロセッサ22は、データが保存されるページに対するページアドレス又はワードラインアドレスを生成する。

【0099】

一実施例において、マイクロプロセッサ22は、ページアドレスの少なくとも一部のビット又はワードラインアドレスの少なくとも一部のビットを用いて、複数のシードテーブルST1〜ST4のうちの何れか1つを選択し、選択されたシードテーブルに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーをシードSEEDとして選択し、エントリーポインターをインクリメントする(ステップS130)。

【0100】

他の実施例において、マイクロプロセッサ22は、ページアドレスの少なくとも一部のビット又はワードラインアドレスの少なくとも一部のビットを用いて、1つのシードテーブルST21に含まれる複数のゾーンZONE0〜ZONE15のうちの何れか1つのゾーンを選択し、選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーをシードSEEDとして選択し、エントリーポインターをインクリメントする(ステップS230)。

【0101】

擬似乱数生成器32は、マイクロプロセッサ22によって選択されたシードSEEDを用いて擬似乱数RSを生成する(ステップS140)。モジュロ演算器34は、擬似乱数RSと入力データDATA1とをモジュロ加算し、その結果として、ランダマイズされたデータRDATAを生成する。即ち、モジュロ演算器34は、擬似乱数RSを用いて入力データDATA1をランダマイズする(ステップS150)。

【0102】

ECCブロック36は、ランダマイズされたデータRDATAを用いてパリティビットを生成し(ステップS160)、パリティビットを含むランダマイズされたデータERDATAを不揮発性メモリ装置40に出力する(ステップS170)。例えば、マイクロプロセッサ22は、ホストHOSTから出力されたデータ又は自ら生成したメタデータ(metadata)を不揮発性メモリ装置40にプログラムするために必要なアドレスを生成する。

【0103】

図14は、図1に示したメモリシステムを含む電子装置の一実施例を示す。図1、図2、図7、及び図14を参照すると、電子装置(electronic device)100は、携帯電話(cellular/mobile phone)、スマートフォン(smart phone)、タブレットPC(tablet Personal Computer)、PDA(Personal Digital Assistant)、ビデオゲームコンソール(video game console)、又は携帯用(handheld)通信装置として具現可能である。

【0104】

電子装置100は、メモリコントローラ20と不揮発性メモリ装置40とを含む。メモリコントローラ20は、プロセッサ110の制御によって不揮発性メモリ装置40のデータ処理動作、例えばプログラム動作、イレーズ動作、又はリード動作を制御する。

【0105】

プログラム要求によって、メモリコントローラ20は、ページ別に割り当てられたシードテーブルに含まれるシード、又はページ別に割り当てられたゾーンに含まれるシードを用いて擬似乱数RSを生成し、擬似乱数RSを用いてデータDATA1をランダマイズし、ランダマイズされたデータRDATAを出力する。従って、不揮発性メモリ装置40は、ランダマイズされたデータを現在プログラムされるページにプログラムすることができる。

【0106】

不揮発性メモリ装置40にプログラムされたデータは、プロセッサ110及び/又はメモリコントローラ20の制御によってディスプレイ120を通じてディスプレイされる。ディスプレイ120は、TFT−LCD(Thin Film Transistor−Liquid Crystal Display)、LED(Light−Emitting Diode)ディスプレイ、OLED(Organic LED)ディスプレイ、又はAMOLED(Active Matrix OLED)ディスプレイのような平板ディスプレイ(Flat Panel Display)として具現可能である。

【0107】

無線送受信器130は、アンテナANTを通じて無線信号を送受信する。例えば、無線送受信器130は、アンテナANTを通じて受信した無線信号をプロセッサ110で処理される信号に変更する。従って、プロセッサ110は、無線送受信器130から出力された信号を処理し、処理された信号をメモリコントローラ20又はディスプレイ120に伝送する。本実施例によるメモリコントローラ20は、プロセッサ110によって処理された信号を不揮発性メモリ装置40にプログラムする。また、無線送受信器130は、プロセッサ110から出力された信号を無線信号に変更し、変更された無線信号を、アンテナANTを通じて外部装置に出力する。

【0108】

入力装置134は、プロセッサ110の動作を制御するための制御信号又はプロセッサ110によって処理されるデータを入力する装置であり、タッチパッド(touch pad)とコンピュータマウス(computer mouse)のようなポインティング装置(pointing device)、キーパッド(keypad)、又はキーボードとして具現可能である。

【0109】

プロセッサ110は、メモリコントローラ20から出力されたデータ、無線送受信器130から出力されたデータ、又は入力装置140から出力されたデータが、ディスプレイ120を通じてディスプレイされるように、ディスプレイ120の動作を制御する。一実施例として、不揮発性メモリ装置40の動作を制御するメモリコントローラ20は、プロセッサ110の一部として具現され、またプロセッサ110と別途のチップとして具現可能である。

【0110】

図15は、図1に示したメモリシステムを含む電子装置の他の実施例を示す。図15に示した電子装置200は、PC(Personal Computer)、ラップトップ(laptop)コンピュータ、ネットブック(net−book)、イーリーダー(e−reader)、PMP(Portable Multimedia Player)、MP3プレーヤー、又はMP4プレーヤーとして具現可能である。

【0111】

電子装置200は、不揮発性メモリ装置40と、不揮発性メモリ装置40のデータ処理動作を制御するメモリコントローラ20と、を含む。

【0112】

プロセッサ210は、入力装置220を通じて入力されたデータによって不揮発性メモリ装置40に保存されたデータを、ディスプレイ230を通じてディスプレイする。例えば、入力装置220は、タッチパッド又はコンピュータマウスのようなポインティング装置、キーパッド、又はキーボードとして具現可能である。また、入力装置220は、他の装置とデータをインターフェーシングするインターフェースであり得る。プロセッサ210は、電子装置200の全般的な動作を制御し、メモリコントローラ20の動作を制御する。

【0113】

一実施例として、不揮発性メモリ装置40の動作を制御することができるメモリコントローラ20は、プロセッサ210の一部として具現され、またプロセッサ210と別途のチップとして具現可能である。

【0114】

図16は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図16では、説明の便宜上、電子装置300とホスト330とを共に示す。図16に示した電子装置300は、メモリカード(memory card)又はスマートカード(smart card)として具現可能である。デジタル情報を保存するために使われる電子フラッシュメモリデータ保存装置であるメモリカードは、PCカード、MMC、e−MMC(embedded MMC)、SDカード、又はUSB(Universal Serial Bus)フラッシュドライブ(flash drive)を含む。

【0115】

メモリカードのような電子装置300は、メモリコントローラ20、不揮発性メモリ装置40、カードインターフェース320を含む。メモリコントローラ20は、不揮発性メモリ装置40とカードインターフェース320との間でデータの交換を制御する。

【0116】

一実施例として、カードインターフェース320は、SDカードインターフェース又はMMCインターフェースであり得るが、これに限定されるものではない。

【0117】

カードインターフェース320は、ホスト330のプロトコルによってホスト330とメモリコントローラ20との間でデータ交換をインターフェーシングする。一実施例として、カードインターフェース320は、USBプロトコル、IC(InterChip)−USBプロトコルを支援することができる。ここで、カードインターフェースとは、ホスト330が使うプロトコルを支援するハードウェア、ハードウェアに搭載されたソフトウェア、又は信号伝送方式を意味する。

【0118】

電子装置300が、PC、ラップトップコンピュータ、タブレット(tablet)PC、デジタルカメラ(digital camera)、デジタルオーディオプレーヤー(digital audio player)、携帯電話、ビデオゲームコンソール、MP3プレーヤー、PMP、イーブック、又はデジタルセットトップボックス(digitalset−topn box)のようなホスト330のホストインターフェース350に接続されると、ホストインターフェース350は、マイクロプロセッサ340の制御によってカードインターフェース320とメモリコントローラ20とを通じて不揮発性メモリ装置40とデータ通信を行う。

【0119】

図17は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図17に示した電子装置400は、イメージ処理装置、例えば、デジタルカメラ、デジタルカメラ付き携帯電話、デジタルカメラ付きスマートフォン、又はデジタルカメラ付きタブレットPCとして具現可能である。

【0120】

電子装置400は、不揮発性メモリ装置40と、不揮発性メモリ装置40のデータ処理動作、例えばプログラム動作、イレーズ動作、又はリード動作を制御するメモリコントローラ20とを含む。電子装置400のイメージセンサー420は、光学イメージをデジタルイメージ信号に変換し、変換されたデジタルイメージ信号は、プロセッサ410及び/又はメモリコントローラ20に伝送される。プロセッサ410の制御によって、変換されたデジタルイメージ信号は、ディスプレイ430を通じてディスプレイされるか、又はメモリコントローラ20を通じて不揮発性メモリ装置40に保存される。

【0121】

また、不揮発性メモリ装置40に保存されたデータは、プロセッサ410及び/又はメモリコントローラ20の制御によってディスプレイ430を通じてディスプレイされる。

【0122】

一実施例として、不揮発性メモリ装置40の動作を制御するメモリコントローラ20は、プロセッサ410の一部として具現され、またプロセッサ410と別個のチップとして具現可能である。

【0123】

図18は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図18を参照すると、電子装置500は、不揮発性メモリ装置40と、不揮発性メモリ装置40の動作を制御するメモリコントローラ20とを含む。

【0124】

電子装置500は、CPU(Central Processing Unit)510の動作メモリ(operation memory)として使われるメモリ装置550を含む。メモリ装置550は、ROMのような不揮発性メモリとして具現され、SRAMのような不揮発性メモリとして具現可能である。

【0125】

電子装置500に接続されたホストHOSTは、メモリコントローラ20とホストインターフェース540とを通じて不揮発性メモリ装置40とデータ通信を行う。

【0126】

CPU510の制御によって、ECCブロック530は、メモリコントローラ20を通じて不揮発性メモリ装置40から出力されたデータに含まれるエラービットを検出し、エラービットを訂正し、エラー訂正されたデータを、ホストインターフェース540を通じてホストHOSTに伝送する。一実施例として、ECCブロック530は、電子装置500に含まれないこともある。

【0127】

CPU510は、バス501を通じて、メモリコントローラ20、ECCブロック530、ホストインターフェース540、及びメモリ装置550の間でデータ通信を制御する。

【0128】

電子装置500は、フラッシュメモリドライブ、USBメモリドライブ、IC−USBメモリドライブ、又はメモリスティック(memory stick)として具現可能である。

【0129】

図19は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図19を参照すると、電子装置600は、SSD(Solid State Drive)のようなデータ処理装置として具現可能である。

【0130】

電子装置600は、複数のソリッドステートメモリ装置40、メモリコントローラ20、揮発性メモリ装置630、及びバッファマネージャー620を含む。メモリコントローラ20は、複数のソリッドステートメモリ装置40のそれぞれのデータ処理動作を制御する。複数のソリッドステートメモリ装置40のそれぞれは、図1及び図10に示した不揮発性メモリ装置、例えば、NANDフラッシュメモリ装置であり、複数のページを含む。メモリコントローラ20は、ランダマイズされたデータを複数のソリッドステートメモリ装置40のうちの1つに含まれるページにプログラムする。

【0131】

揮発性メモリ装置630は、DRAMとして具現され、メモリコントローラ20とホスト640との間で送受信するデータを一時的に保存する。バッファマネージャー620は、揮発性メモリ装置630及び/又はメモリコントローラ20のデータバッファリング動作を制御する。

【0132】

図20は、図19に示した電子装置を含むデータ処理システムのブロック図を示す。図19及び図20を参照すると、RAID(Redundant Array of Independent Disks)システムとして具現可能なデータ処理装置700は、RAIDコントローラ710と複数の電子装置600−1〜600−n(nは、自然数)とを含む。

【0133】

電子装置600−1〜600−nのそれぞれは、図19に示した電子装置600である。複数の電子装置600−1〜600−nは、RAIDアレイを構成する。データ処理装置700は、PC(Personal Computer)、NAS(Network−Attached Storage)、又はSSDとして具現可能である。電子装置600−1〜600−nのそれぞれは、メモリモジュール(memory module)形態で具現されたメモリシステムであり得る。

【0134】

プログラム動作の間、ホストHOSTから出力されたプログラム要求によって、RAIDコントローラ710は、ホストHOSTから出力されたデータをRAIDレベルに基づいて、複数の電子装置600−1〜600−nのうちの少なくとも何れか1つの電子装置に出力する。リード動作の間、RAIDコントローラ710は、ホストHOSTから出力されたリード命令によって複数の電子装置600−1〜600−nのうちの少なくとも何れか1つの電子装置から読み取られたデータをホストHOSTに伝送する。

【0135】

以上、本発明の実施形態について図面を参照しながら詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

【符号の説明】

【0136】

10 メモリシステム

11、13 マルチチップパッケージ

11−1、13−1 回路基板

11−2、11−4、13−2、13−3 ボンディングワイヤ

11−3、13−4 ソルダボール

20 メモリコントローラ

22、340 マイクロプロセッサ

24 バッファ

26 ROM

28、501 バス

29、350、540 ホストインターフェース

30 メモリインターフェース

30A、30B データ変換装置

32 擬似乱数生成器

34 モジュロ演算器

34−1 第1モジュロ演算器

34−2 第2モジュロ演算器

36、530 ECC(エラー訂正コード)ブロック

40 不揮発性メモリ装置

42−1〜N 第1〜第Nページ

43 コントロールロジック

44 電圧発生器

45 ローデコーダ

46 ページバッファブロック

47 カラムデコーダ

48 Y−ゲーティング回路

49 入出力ブロック

100、200、400、500、600、600−1〜n 電子装置

110、210、410 プロセッサ

120、230、430 ディスプレイ

130 無線送受信器

134、220 入出力装置

140 メモリセルアレイ

300 メモリカード

320 カードインターフェース

330、640 ホスト

420 イメージセンサー

510 CPU

550 メモリ装置

620 バッファマネージャー

630 揮発性メモリ装置(DRAM)

700 データ処理装置

710 RAIDコントローラ

【技術分野】

【0001】

本発明は、メモリコントローラに係り、より詳しくは、隣接する複数のページ(pages)間のシード関連性(seed correlation)を減少させるメモリコントローラ及びその動作方法、並びにメモリコントローラを含むメモリシステム、3次元メモリシステム、メモリカード、ソリッドステートドライブ、及び携帯用通信装置に関する。

【背景技術】

【0002】

擬似乱数(Pseudo−Random Numbers)は、通信システム又はデータ保存システムで広く使われる。擬似乱数は、擬似乱数シーケンス(PseudoRandom Sequence)を発生するために使われる。即ち、擬似乱数は、最初に与えられる初期値を用いて、既に決定されているメカニズム、例えば擬似乱数生成器によって生成される数を意味する。

【0003】

乱数は、その生成方法が決定されていないので、次に生成される値、即ち数(number)を全く予測することができない。しかし、擬似乱数生成器によって生成される数は、擬似乱数生成器の初期値が分かると計算され得るので、本当の乱数と区別するために、擬似乱数と言う。

【0004】

線形フィードバックシフトレジスタ(Linear Feedback Shift Register:LFSR)は、擬似乱数シーケンスを発生するために使われる。LFSRは、シード(seed)と呼ばれる初期値を変更するか、又はフィードバックタップ(feedback taps)を変更することによって、擬似乱数シーケンスを変更することができる。上述したように、擬似乱数は初期値を用いて計算され得るので、擬似乱数は計算され得る。従って、擬似乱数を容易に計算することができない方法が要求される。

【0005】

ランダマイザー(randomizer)は、LFSRによって生成された擬似乱数シーケンスを用いて、データをランダマイズされたデータに変換する。デランダマイザー(derandomizer)は、LFSRによって生成された擬似乱数シーケンスを用いて、ランダマイズされたデータをデランダマイズされたデータに変換する。従って、擬似乱数シーケンスを容易に計算することができないランダマイザー又はデランダマイザーが要求される。

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は上記従来技術に鑑みてなされたものであって、本発明の目的は、プログラムされるデータのランダム性(randomness)を増加させるために、隣接する複数のページ間のシード関連性を減少又は除去するメモリコントローラ及びその動作方法、並びにメモリコントローラを含むメモリシステム、3次元メモリシステム、メモリカード、ソリッドステートドライブ、及び携帯用通信装置を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するためになされた本発明の一特徴によるメモリコントローラの動作方法は、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有する。

【0008】

一態様において、前記擬似乱数を生成する段階は、前記ページのページアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリー(entry)を前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含む。

前記メモリコントローラの動作方法は、前記エントリーポインターによって指定されたエントリーが選択された後、前記エントリーポインターを変更する段階を更に有し、前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト(default)値にリセットされる。

他の態様において、前記擬似乱数を生成する段階は、前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含む。

前記複数のシードグループのそれぞれが複数のページのそれぞれに対応する場合、前記複数のページの数は、1本のワードラインに接続された複数のマルチレベルセルのそれぞれに保存されるビットの数と同一である。

【0009】

上記目的を達成するためになされた本発明の他の特徴によるメモリコントローラの動作方法は、それぞれが異なるシードテーブル(seed table)に保存された複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、前記擬似乱数を用いて、前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有する。

【0010】

上記目的を達成するためになされた本発明の更に他の特徴によるメモリコントローラの動作方法は、複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを用いて擬似乱数を生成する段階と、前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有し、前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、前記複数のゾーンのうちから前記シードグループに相応するゾーンは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択され、前記シードは、前記選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーである。

【0011】

上記目的を達成するためになされた本発明の一特徴によるメモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を備え、前記マイクロプロセッサは、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択した後、前記エントリーポインターを変更し、前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト値にリセットされる。

【0012】

前記メモリコントローラは、前記複数のシードグループを保存するROM(Read Only Memory)を更に備える。

一態様において、前記マイクロプロセッサは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する。

前記複数のシードグループのそれぞれは、異なるシードテーブルに保存される。

他の態様において、前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、前記マイクロプロセッサは、前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択する。

【0013】

上記目的を達成するためになされた本発明の一特徴によるメモリシステムは、複数のページを有するメモリセルアレイを含む不揮発性メモリ装置と、前記不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記不揮発性メモリ装置に出力するランダマイザーと、を含む。

【0014】

一態様において、前記複数のシードグループのそれぞれが互いに異なるシードテーブルに保存される場合、前記マイクロプロセッサは、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択する。

前記マイクロプロセッサは、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択する。

他の態様において、前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、前記マイクロプロセッサは、前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択する。

前記メモリシステムは、前記不揮発性メモリ装置と前記メモリコントローラとを含むマルチチップパッケージ(Multi−Chip Package)である。

【0015】

上記目的を達成するためになされた本発明の一特徴によるメモリカードは、複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、ホストと通信するためのカードインターフェースと、前記フラッシュメモリ装置と前記カードインターフェースとの間の通信を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含む。

【0016】

前記メモリカードは、MMC(MultimMedia Card)、SD(Secure Digital)カード、又はUSBフラッシュドライブである。

【0017】

上記目的を達成するためになされた本発明の一特徴による携帯用通信装置は、複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、前記フラッシュメモリ装置の動作を制御するメモリコントローラと、前記メモリコントローラの制御によって前記フラッシュメモリ装置から出力されたデータをディスプレイするディスプレイと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含む。

【0018】

上記目的を達成するためになされた本発明の一特徴による3次元メモリシステムは、それぞれが複数のページを有する複数のレイヤを含む3次元不揮発性メモリ装置と、前記3次元不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を含む。

【0019】

上記目的を達成するためになされた本発明の一特徴によるソリッドステイブドライブは、それぞれが複数のページを含む複数のソリッドステートメモリ装置と、前記複数のソリッドステートメモリ装置のそれぞれの動作を制御するメモリコントローラと、を備え、前記メモリコントローラは、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを現在プログラムされる前記ページに出力するランダマイザーと、を含む。

【発明の効果】

【0020】

本発明によるメモリコントローラ及びその動作方法によれば、ページ毎に異なるシードテーブルに含まれるシード又はページ毎に異なるゾーンに含まれるシードを用いて生成された擬似乱数によってデータをランダマイズすることによって、複数のページ間のシード関連性を防止することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の一実施形態によるメモリコントローラを含むメモリシステムのブロック図を示す。

【図2】図1に示したメモリシステムを含むマルチチップパッケージの一例を示す。

【図3】図1に示したメモリシステムを含むマルチチップパッケージの他の例を示す。

【図4】図1に示したメモリインターフェースのブロック図の一例を示す。

【図5】図1に示したメモリインターフェースのブロック図の他の例を示す。

【図6】ページ別に割り当てられたシードテーブルの一例を示す。

【図7】ページ別に割り当てられたシードテーブルの他の例を示す。

【図8】ページ別に割り当てられたゾーン(zones)を含む1つのシードテーブルを示す。

【図9】図8に示した1つのゾーン(zone)に含まれるエントリーを示す。

【図10】図1に示した不揮発性メモリ装置の2次元的な構造のメモリセルアレイを含むブロック図の一例を示す。

【図11】図1に示した不揮発性メモリ装置の3次元的な構造のメモリセルアレイの一例を示す。

【図12】ページ別に割り当てられたシードテーブルを用いる図1に示したメモリシステムの動作を説明するフローチャートである。

【図13】1つのシードテーブルに含まれる複数のゾーンを用いる図1に示したメモリシステムの動作を説明するフローチャートである。

【図14】図1に示したメモリシステムを含む電子装置の一実施例を示す。

【図15】図1に示したメモリシステムを含む電子装置の他の実施例を示す。

【図16】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図17】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図18】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図19】図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。

【図20】図19に示した電子装置を含むデータ処理システムのブロック図を示す。

【発明を実施するための形態】

【0022】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳しく説明する。

【0023】

図1は、本発明の一実施形態によるメモリコントローラ20を含むメモリシステム10のブロック図を示す。図1を参照すると、メモリシステム10は、メモリコントローラ20及び不揮発性メモリ装置40を含む。メモリコントローラ20は、ホストHOSTの制御によって、不揮発性メモリ装置40のデータ処理動作、例えば、プログラム(program)動作、リード(read)動作、及びイレーズ(erase)動作を制御する。

【0024】

後述する図6及び図7に示す実施例において、メモリコントローラ20は、複数のシードテーブルST1〜ST4及びST11〜ST13のうちから現在プログラムされるページに対する(又は、割り当てられた)シードテーブルを選択し、選択されたシードテーブルに含まれる1つ又はそれ以上のエントリー(entries)のうちからエントリーポインター(entry pointer)によって指定されたエントリーをページのシードとして選択し、選択されたシードを用いて擬似乱数を生成し、生成された擬似乱数によって、ページにプログラムされるデータをランダマイズ(randomize)し、ランダマイズされたデータを不揮発性メモリ装置40に出力する。

【0025】

ここで、複数のページのそれぞれは、プログラム動作によるワードライン(word line)方向のフローティングゲートカップリング(floating gate coupling)、リードディスターバンス(read disturbance)、又はバックパターンディペンデンシー(back−pattern dependancy)などによって、互いに影響を受けるものと仮定する。ここで、リードディスターバンスは、リード動作の間に選択されていない複数のワードラインのそれぞれに接続された複数のメモリセルがプログラムされる現象を意味する。

【0026】

後述する図8及び図9に示す他の実施例において、メモリコントローラ20は、1つのシードテーブルST21に含まれ、それぞれが複数のエントリーを含み、それぞれが複数のページのそれぞれに割り当てられた複数のゾーンZONE0〜ZONE15のうちの何れか1つのゾーンを選択し、選択されたゾーンに含まれる1つ又はそれ以上のエントリーのうちからエントリーポインターENTRY_PNTZ0によって指定されたエントリーENTRY_Z11を現在プログラムされるページのシードとして選択し、選択されたシードを用いて擬似乱数を生成し、擬似乱数を用いて、ページにプログラムされるデータをランダマイズし、ランダマイズされたデータを不揮発性メモリ装置40に出力する。

【0027】

メモリコントローラ20は、マイクロプロセッサ22、バッファ24、ROM26、ホストインターフェース29、及びメモリインターフェース30を含む。これらの各構成要素(22、24、26、29、及び30)は、バス28を通じて互いに通信することができる。

【0028】

回路(circuit)、ロジック(logic)、コード(code)、又はこれらの組合せで具現可能なマイクロプロセッサ22は、各構成要素(24、26、29、及び30)の動作を制御する。

【0029】

図6及び図7に示す実施例において、マイクロプロセッサ22は、複数のシードテーブルST1〜ST4又はST11〜ST13、例えばページ別に割り当てられた複数のシードテーブルST1〜ST4又はST11〜ST13のうちから現在プログラムされるページに割り当てられたシードテーブルを選択する動作、及び/又は選択されたシードテーブルに含まれる1つ又はそれ以上のエントリーのうちの何れか1つのエントリーを選択するエントリーポインターを変更する動作を行う。

【0030】

この際、マイクロプロセッサ22は、現在プログラムされるページのページアドレスの少なくとも一部のビット、又はページに相応するワードラインアドレスの少なくとも一部のビットを用いて、複数のシードテーブルのうちの何れか1つを選択する。ここで、一部のビットは、1ビット又はそれ以上のビットを意味する。

【0031】

図8及び図9に示す他の実施例において、マイクロプロセッサ22は、1つのシードテーブルST21に含まれる複数のゾーンZONE0〜ZONE15のうちの何れか1つのゾーンを選択する動作、及び/又は選択されたゾーンに含まれる1つ又はそれ以上のエントリーのうちの何れか1つのエントリーを選択するエントリーポインターを変更する動作を行う。一実施例において、1つのシードテーブルST21は、独立した複数のゾーンにパーティション(partition)される。この際、マイクロプロセッサ22は、現在プログラムされるページのページアドレスの少なくとも一部のビット、又はページに相応するワードラインアドレスの少なくとも一部のビットを用いて、複数のゾーンのうちの何れか1つを選択する。

【0032】

バッファ24は、DRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)、又はデュアルポート(Dual−Port)SRAMのような揮発性(volatile)メモリとして具現可能である。一実施例において、複数のシードテーブルは、不揮発性メモリ装置40のメモリセルアレイ140に保存されるか、又はROM26に保存される。この場合、メモリセルアレイ140又はROM26に保存された複数のシードテーブルのそれぞれは、マイクロプロセッサ22の制御によってバッファ24にローディングされる。ここで、複数のページ42−1〜42−Nが複数のグループにグルーピングされる場合、複数のシードテーブルのそれぞれは、複数のグループのそれぞれに対応する。

【0033】

他の実施例において、複数のゾーンZONE0〜ZONE15を含む1つのシードテーブルST21は、メモリセルアレイ140又はROM26に保存される。この場合、メモリセルアレイ140又はROM26に保存された1つのシードテーブルST21は、マイクロプロセッサ22の制御によってバッファ24にローディングされる。例えば、ページ別のシードテーブル又は1つのシードテーブルは、メモリコントローラ20のパワーアップ(power−up)動作の間にバッファ24にローディングされるか、又はメモリコントローラ20の動作の間にリアルタイムでバッファ24にローディングされる。

【0034】

ROM26は、メモリコントローラ20の動作に必要なプログラムコードを保存する。上述したように、ROM26には、ページ別に割り当てられたシードテーブル又は1つのシードテーブルを保存することができる。

【0035】

ホストHOSTとメモリコントローラ20は、ホストインターフェース29を通じて通信する。ホストHOSTは、プログラム要求(program request)と不揮発性メモリ装置40にプログラムされるデータを、ホストインターフェース29を通じてメモリコントローラ20に伝送する。この際、メモリコントローラ20は、プログラム要求によって、データが保存される不揮発性メモリ装置40のページのページアドレス及び/又はページに相応するワードラインアドレスを生成する。

【0036】

メモリコントローラ20と不揮発性メモリ装置40は、メモリインターフェース30を通じて互いに通信する。

【0037】

不揮発性メモリ装置40のメモリセルアレイ140は、複数のメモリブロック(memory block)を含み、複数のメモリブロックのそれぞれは、複数のページ42−1〜42−Nを含み、複数のページ42−1〜42−Nのそれぞれは、複数の不揮発性メモリセル、例えばNANDフラッシュメモリセルを含む。NANDフラッシュメモリセルのそれぞれは、1ビット又はそれ以上のビットを保存する。

【0038】

不揮発性メモリ装置40、例えばNANDフラッシュメモリ装置で、プログラム動作又はリード動作はページ(page)単位で行われ、イレーズ動作はメモリブロック単位で行われる。ここで、ページは、1本のワードラインに接続された複数の不揮発性メモリセル、例えばNANDフラッシュメモリセルに定義されるメモリ領域を意味する。例えば、NANDフラッシュメモリセルのそれぞれが、1ビットを保存するSLC(Single Level Cell)である場合、1本のワードラインは、1枚のページと定義される。

【0039】

NANDフラッシュメモリセルのそれぞれが、2ビット以上を保存するMLC(Multi Level Cell)である場合、1本のワードラインは、1本のワードラインに接続された複数のMLCのそれぞれにプログラムされるビット数と同じページ数を有すると定義される。

【0040】

例えば、複数のMLCのそれぞれが2ビットMLCである場合、1本のワードラインは、2枚のページ、例えば第1ページと第2ページとを含み、複数のMLCのそれぞれが3ビットMLCである場合、1本のワードラインは、3枚のページ、例えば第1ページ、第2ページ、及び第3ページを含む。

【0041】

第1ページは、LSB(Least Significant Bit)ページを意味し、第2ページは、MSB(Most Significant Bit)ページを意味し、第3ページは、CSB(Center Significant Bit)ページを意味する。

【0042】

図2は、図1に示したメモリシステムを含むマルチチップパッケージの一例を示す。図2を参照すると、マルチチップパッケージ11は、回路基板11−1、例えばPCB(Printed Circuit Board)上にマウント(mounted)又は積層された(stacked)メモリコントローラ20と、メモリコントローラ20上にマウント又は積層された不揮発性メモリ装置40とを含む。メモリコントローラ20は、ボンディングワイヤ(bonding wires)11−2とソルダボール(solder balls)11−3とを通じて外部装置と通信する。また、メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ11−4を通じて通信する。

【0043】

図2では、説明の便宜上、不揮発性メモリ装置40がメモリコントローラ20上に形成された例を示したが、一実施例として、これらの2つの装置(20、40)の具現位置が互いに変わり得る。また、メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ11−4以外の接続手段を通じて互いに通信し、メモリコントローラ20とソルダボール11−3は、ボンディングワイヤ11−2以外の接続手段を通じて互いに接続され得る。接続手段は、垂直電気素子(vertical electrical element)、例えば、TSV(Through Silicon Via)として具現されることもある

【0044】

図3は、図1に示したメモリシステムを含むマルチチップパッケージの他の例を示す。図3を参照すると、マルチチップパッケージ13は、回路基板13−1、例えば、PCB上に接続されたメモリコントローラ20と不揮発性メモリ装置40とを含む。メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ13−2を通じて互いに通信し、メモリコントローラ20と不揮発性メモリ装置40のそれぞれは、ボンディングワイヤ13−3とソルダボール13−4とを通じて外部装置と通信する。

【0045】

一実施例として、メモリコントローラ20と不揮発性メモリ装置40は、ボンディングワイヤ13−2以外の接続手段を通じて互いに通信することができる。接続手段は、垂直電気素子、例えばTSVとして具現されることもある。例えば、メモリコントローラ20と不揮発性メモリ装置40のそれぞれが垂直電気素子を通じて回路基板13−1に接続される場合、メモリコントローラ20と不揮発性メモリ装置40は、垂直電気素子と回路基板13−1とを通じて互いに通信することができる。

【0046】

それぞれのチップ(chip)として具現されたメモリコントローラ20と不揮発性メモリ装置40は、PoP(Package on Package)、BGAs(BallGrid Arrays)、CSPs(Chip Scale Packages)、PLCC(Plastic Leaded Chip Carrier)、PDIP(Plastic Dual In−Line Package)、Die in Waffle Pack、Din in Wafer Form、COB(Chip On Board)、CERDIP(CERamic Dual In−Line Package)、MQFP(Plastic Metric Quad Flat Pack)、TQFP(ThinQuad FlatPack)、SOIC(Small−Outline Integrated Circuit)、SSOP(Shrink Small Outline Package)、TSOP(Thin Small Outline Package)、SiP(System in Package)、MCP(Multi Chip Package)、WFP(Wafer−level Fabricated Package)、又はWSP(Wafer−level processed Stack Package)のようなパッケージとして具現可能である。

【0047】

図4は、図1に示したメモリインターフェースのブロック図の一例を示す。図4を参照すると、図1に示したメモリインターフェース30の一例として具現されたメモリインターフェース30は、データ変換装置30Aとして使用される。

【0048】

データ変換装置30Aは、データ経路(data path)によってランダマイザー又はデランダマイザーとして使用される。データ変換装置30Aは、擬似乱数生成器(pseudo random number generator)32とモジュロ演算器(modulo operator)34とを含む。

【0049】

擬似乱数生成器32は、ページ別に割り当てられた(assigned)シードテーブルに含まれるシードSEED、又はページ別に割り当てられたゾーンに含まれるシードSEEDを用いて、擬似乱数(又は、擬似乱数シーケンス)RSを生成する。一実施例として、擬似乱数生成器32は、LFSR(Linear Feedback Shift Register)として具現され、LFSRは、シードSEEDを用いてフィードバック多項式(feedback polynomial)を決定する。従って、擬似乱数RSは、フィードバック多項式によって決定される。LFSRは、フィボナッチ(Fibonacci)LFSR又はガロア(Galois)LFSRとして具現可能である。擬似乱数生成器32に含まれる構成要素によって、擬似乱数生成器32は、線形擬似乱数RS又は非線形擬似乱数RSを発生する。

【0050】

モジュロ演算器34は、擬似乱数RSと現在プログラムされるページにプログラムされるデータDATA1とをモジュロ演算(modulo operation)して、ランダマイズされたデータRDATAを発生する。擬似乱数RSを用いてデータDATA1をランダマイズする場合、モジュロ演算器34は、擬似乱数RSとデータDATA1とをモジュロ加算(modulo addition)して、ランダマイズされたデータRDATAを生成する。

【0051】

擬似乱数RSを用いてランダマイズされたデータRRDATA2をデランダマイズする場合、モジュロ演算器34は、ランダマイズされたデータRRDATA2から擬似乱数RSをモジュロ減算(modulo subtraction)して、データDATA2を生成する。

【0052】

モジュロ2加算の結果とモジュロ2減算の結果は、互いに同一なので、擬似乱数RSが2進シーケンス(binary sequence)である場合、モジュロ演算器34は、排他論理和ゲート(exclusive OR gate)として具現可能である。

【0053】

データ変換装置30Aは、エラー訂正コード(Error Correction Code、ECC)ブロック36を更に含む。

【0054】

プログラム動作の間に、ECCブロック36は、ランダマイズされたデータRDATAにECCパリティビットを付け加え、ECCパリティビットを含むランダマイズされたデータERDATAを生成する。また、リード動作の間に、ECCブロック36は、ランダマイズされたデータRRDATA1とECCパリティビットとを受信し、ECCパリティビットを用いてランダマイズされたデータRRDATA1に含まれる少なくとも1つのエラーを訂正し、エラー訂正されたランダマイズされたデータRRDATA2をモジュロ演算器34に出力する。

【0055】

モジュロ演算器34は、エラー訂正されたランダマイズされたデータRRDATA2から擬似乱数RSをモジュロ減算して、データDATA2を生成する。

【0056】

図5は、図1に示したメモリインターフェースのブロック図の他の例を示す。図5を参照すると、図1に示したメモリインターフェース30の他の例として具現されたメモリインターフェース30は、データ変換装置30Bとして使用される。

【0057】

第1モジュロ演算器34−1と第2モジュロ演算器34−2は、1つの擬似乱数生成器32を共有する。

【0058】

プログラム動作の間に、第1レベル、例えばハイレベルを有するプログラムイネーブル信号WEによってイネーブルされた第1モジュロ演算器34−1は、擬似乱数RSを用いてデータDATA1をランダマイズされたデータRDATAにランダマイズする。リード動作の間に、第1レベルを有するリードイネーブル信号REによってイネーブルされた第2モジュロ演算器34−2は、ランダマイズされたデータRRDATA2を、擬似乱数RSを用いてデータDATA2にデランダマイズする。

【0059】

プログラムイネーブル信号WEが、第2レベル、例えばローレベルから第1レベルに変更される時点と、リードイネーブル信号REが、第2レベルから第1レベルに変更される時点とを適切に調節することにより、プログラム動作とリード動作は、互いに異なる時点又は同時に行われる。

【0060】

第1モジュロ演算器34−1はモジュロ加算を行い、第2モジュロ演算器34−2はモジュロ減算を行う。一実施例として、擬似乱数RSが2進シーケンスである場合、これらの各モジュロ演算器(34−1、34−2)は、排他論理和ゲートとして具現可能である。データ変換装置30Bは、ECCブロック36を更に含む。

【0061】

図6は、ページ別に割り当てられたシードテーブルの一例を示す。図6は、説明の便宜上、それぞれが4枚のページのそれぞれに割り当てられた4つのシードテーブルST1〜ST4を示しており、4つのシードテーブルST1〜ST4のそれぞれは、複数のエントリーENTRY11〜ENTRY1m、ENTRY21〜ENTRY2l、ENTRY31〜ENTRY3k、及びENTRY41〜ENTRY4pを含む。ここで、m、l、k、及びpは、自然数である。

【0062】

複数のエントリーENTRY11〜ENTRY1m、ENTRY21〜ENTRY2l、ENTRY31〜ENTRY3k、及びENTRY41〜ENTRY4pのそれぞれは、図4又は図5に示した擬似乱数生成器32で使われるシード値(これを、‘シード’と称する)を含む。

【0063】

図6では、説明の便宜上、各エントリーポインターENTRY_PNT1〜ENTRY_PNT4が、各シードテーブルST1〜ST4の最初のエントリーENTRY11、ENTRY21、ENTRY31、及びENTRY41をデフォルトに指定することを示す。しかし、各エントリーポインターENTRY_PNT1〜ENTRY_PNT4は、図1のマイクロプロセッサ22の制御によって、複数のエントリーのうちの何れか1つのエントリーを指定できるように設定し得る。

【0064】

例えば、ホストHOSTから第1データをプログラムせよとの要請が入力されると、マイクロプロセッサ22は、この要請に応答して、第1データを第1ページ42−1にプログラムするために、第1アドレス、例えば、第1ページアドレス又は第1ページ42−1に相応する第1ワードラインアドレスを生成し、生成された第1アドレスの少なくとも一部のビットを用いて、複数のシードテーブルST1〜ST4のうちから第1シードテーブルST1を選択する。

【0065】

そして、マイクロプロセッサ22は、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちから現在エントリーポインターENTRY_PNT1が指定するエントリーENTRY11を、第1データをプログラムするためのシードとして選択し、エントリーポインターENTRY_PNT1を次のエントリーENTRY12を指定するためにインクリメントする。

【0066】

ホストHOSTから第2データ、第3データ、又は第4データをプログラムせよとの要請が入力されると、マイクロプロセッサ22は、上述したような方法でそれぞれのシードテーブルST2、ST3、又はST4でそれぞれの現在エントリーポインターENTRY_PNT2、ENTRY_PNT3、又はENTRY_PNT4が指定するそれぞれのエントリーENTRY21、ENTRY31、又はENTRY41を第1データ、第2データ、又は第3データをプログラムするためのそれぞれのシードとして選択し、それぞれの現在エントリーポインターENTRY_PNT2、ENTRY_PNT3、又はENTRY_PNT4をインクリメントする。

【0067】

メモリコントローラ20がリセットされると、プログラム動作によってインクリメントされたそれぞれのエントリーポインターは、それぞれのデフォルト値ENTRY11、ENTRY21、ENTRY31、及びENTRY41にリセットされる。

【0068】

例えば、シードテーブルST1〜ST4が4つである場合、T(Tは、自然数)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちの何れか1つが選択され、(T+1)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第2シードテーブルST2に含まれる複数のエントリーENTRY21〜ENTRY2lのうちの何れか1つが選択され、(T+2)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第3シードテーブルST3に含まれる複数のエントリーENTRY31〜ENTRY3kのうちの何れか1つが選択され、(T+3)番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第4シードテーブルST4に含まれる複数のエントリーENTRY41〜ENTRY4pのうちの何れか1つが選択される。

【0069】

例えば、最初のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちから第1エントリーENTRY11が選択され、5番目のワードラインに接続された複数のメモリセルにページデータをプログラムするためのシードとして、第1シードテーブルST1に含まれる複数のエントリーENTRY11〜ENTRY1mのうちから第2エントリーENTRY12が選択され得る。

【0070】

図7は、ページ別に割り当てられたシードテーブルの他の例を示す。図7に示したように、1本のワードラインに接続された複数の3ビットMLCのそれぞれが互いに影響を与える場合、ページ別にそれぞれ異なるシードテーブルST11、ST12、又はST13が使われる。複数のシードテーブルST11〜ST13のそれぞれは、ページアドレスの少なくとも一部のビットを用いて選択される。

【0071】

例えば、LSBページに、LSBデータをプログラムする際、マイクロプロセッサ22は、LSBシードテーブルST11に含まれる複数のエントリーENTRYL01、ENTRYL02、ENTRYL03,…のうちから現在エントリーポインターENTRY_PNTLが指定するエントリーENTRYL01を選択した後、現在エントリーポインターENTRY_PNTLをインクリメントする。

【0072】

CSBページに、CSBデータをプログラムする際、マイクロプロセッサ22は、CSBシードテーブルST12に含まれる複数のエントリーENTRYC01、ENTRYC02、ENTRYC03、…のうちから現在エントリーポインターENTRY_PNTCが指定するエントリーENTRYC01を選択した後、現在エントリーポインターENTRY_PNTCをインクリメントする。

【0073】

MSBページに、MSBデータをプログラムする際、マイクロプロセッサ22は、MSBシードテーブルST13に含まれる複数のエントリーENTRYM01、ENTRYM02、ENTRYM03、…のうちから現在エントリーポインターENTRY_PNTMが指定するエントリーENTRYM01を選択した後、現在エントリーポインターENTRY_PNTMをインクリメントする。

【0074】

各エントリーポインターENTRY_PNTL、ENTRY_PNTC、及びENTRY_PNTMを如何に、及び/又はどれほどインクリメントするかは、マイクロプロセッサ22によって決定される。

【0075】

メモリコントローラ20がリセットされると、プログラム動作によってインクリメントされたそれぞれのエントリーポインターENTRY_PNTL、ENTRY_PNTC、及びENTRY_PNTMは、それぞれのデフォルト値ENTRYL01、ENTRYC01、及びENTRYC01にリセットされる。

【0076】

図8は、ページ別に割り当てられたゾーンを含む1つのシードテーブルを示し、図9は、図8に示した1つのゾーンに含まれるエントリーを示す。

【0077】

図8及び図9を参照すると、1つのシードテーブルST21は、複数のゾーンZONE0〜ZONE15を含み、複数のゾーンZONE0〜ZONE15のそれぞれは、複数のエントリーを含む。図8及び図9は、説明の便宜上、16個のゾーンZONE0〜ZONE15を含む1つのシードテーブルST21を示しているが、これは例示的なものに過ぎない。16個のゾーンZONE0〜ZONE15のそれぞれは、ページアドレスPADDの下位ビットPADD[3:0]によって選択され、16個のゾーンZONE0〜ZONE15のそれぞれに含まれる複数のエントリーのうちの何れか1つのエントリーは、現在エントリーポインターによって指定される。

【0078】

例えば、5つのエントリーENTRY_Z11〜ENTRY_Z15を含む第1ゾーンZONE0は、ページアドレスの下位ビットPADD[3:0]=0000によって選択され、エントリーENTRY_Z11は、エントリーポインターENTRY_PNTZ0によって選択される。エントリーENTRY_Z11が選択された後、エントリーポインターENTRY_PNTZ0は、次のエントリーENTRY_Z12を指定するためにインクリメントされる。即ち、プログラム動作によってエントリーが選択された後、エントリーポインターENTRY_PNTZ0は、次のエントリーを指定するためにインクリメントされる。メモリコントローラ20がリセットされる度に、エントリーポインターENTRY_PNTZ0は、デフォルト値、例えば、ENTRY_Z11に初期化される。

【0079】

上述したように、1つのシードテーブルST21は、不揮発性メモリ装置40のメモリセルアレイ140に保存されるか、又はメモリコントローラ20のROM26に保存されて、マイクロプロセッサ22の制御によってバッファ24にローディングされるか、又はマイクロプロセッサ22によって参照(reference)される。

【0080】

図10は、図1に示した不揮発性メモリ装置の2次元的な構造のメモリセルアレイを含むブロック図の一例を示す。図1及び図10を参照すると、不揮発性メモリ装置40、例えば、NANDフラッシュメモリ装置は、データを保存するためのメモリセルアレイ140、コントロールロジック43、電圧発生器44、ローデコーダ45、ページバッファブロック46、カラムデコーダ47、Y−ゲーティング回路48、及び入出力ブロック49を含む。

【0081】

メモリセルアレイ140は、複数のNANDメモリセルストリング(strings)を含む。複数のNANDメモリセルストリングのそれぞれは、直列に接続された複数のNANDメモリセル41を含む。例えば、第1NANDメモリセルストリングは、ビットラインBL1に接続された第1選択トランジスタ(又は、ストリング選択トランジスタ(string selection transistor))と共通ソースライン(Common Source Line、CSL)に接続された第2選択トランジスタ(又は、接地選択トランジスタ(ground selection transistor))との間に直列に接続された複数のNANDメモリセル41を含む。

【0082】

第1選択トランジスタのゲートは、ストリング選択ライン(String Selection Line、SSL)に接続され、複数のNANDメモリセル41のそれぞれのゲートは、複数のワードラインWL0〜WL63のそれぞれに接続され、第2選択トランジスタのゲートは、接地選択ライン(Ground Selection Line、GSL)に接続される。上述したように、メモリセルのそれぞれがSLCである場合、各ワードライン(例えば、WL0〜WL3)は、各ページPAGE0〜PAGE3を定義する。

【0083】

図10は、64本のワードラインWL0〜WL63を含むメモリセルアレイ140を示しているが、ワードラインの個数に限定されるものではない。

【0084】

図11は、図1に示した不揮発性メモリ装置の3次元的な構造のメモリセルアレイの一例を示す。図1及び図11に示したように、各NANDメモリセルストリング40′−1、40′−2、…、40′−t(tは、自然数)は、3次元的にそれぞれ異なる平面に配置される。図11に示したように、第1NANDメモリセルストリング40′−1は、第1レイヤ41−1に配され、第2NANDメモリセルストリング40′−2は、第1レイヤ41−1と互いに異なる第2レイヤ41−2に配され、第t NANDメモリセルストリング40′−tは、第2レイヤ41−2とそれぞれ異なるレイヤ41−kに3次元的に配置される。

【0085】

複数のレイヤ41−1〜41−tは、ウェーハ積層(wafer stack)、チップ積層、又はセル(cell)積層を通じて形成される。複数のレイヤ41−1〜41−tは、TSVを含む電気垂直素子(electrical vertical element)、ポンプ(bump)、又はワイヤボンディング(wire bonding)を通じて接続される。複数のレイヤ41−1〜41−tのそれぞれは、複数のセルストリングを含む。

【0086】

図11に示したように、各NANDメモリセルストリング40′−1、40′−2、…、40′−tは、複数のワードラインWL0〜WL63、CSL、及びビットラインBL1を共有する。

【0087】

本明細書で使用するメモリセルアレイ140、140′は、図10に示した2次元メモリセルアレイ140と図11に示した3次元メモリセルアレイ140′とを総括的に意味する。

【0088】

図10を再び参照すると、回路、ロジック、コード、又はこれらの組合せで具現可能なコントロールロジック43は、NANDフラッシュメモリ装置140のデータ処理動作、例えば、プログラム動作、リード動作、及びイレーズ動作を制御する。例えば、コントロールロジック43は、メモリコントローラ20から出力された複数の制御信号によって、データ処理動作を行うために、各構成要素44〜49の動作を制御する。

【0089】

電圧発生器44は、プログラム動作を行うために必要なプログラム電圧を含む複数の電圧、リード動作を行うために必要なリード電圧を含む複数の電圧、又はイレーズ動作を行うために必要なイレーズ電圧を含む複数の電圧を発生する。電圧発生器44は、それぞれの動作に必要な複数の電圧をローデコーダに出力する。

【0090】

ローデコーダ45は、コントロールロジック43から出力されたローアドレスによって、電圧発生器44から出力された複数の電圧を複数のワードラインWL0〜WL63に供給する。カラムデコーダ47は、コントロールロジック43の制御下でカラムアドレスをデコーディングして、複数の選択信号をY−ゲーティング回路48に出力する。

【0091】

ページバッファブロック46は、複数のページバッファを含む。複数のページバッファのそれぞれは、複数のビットラインBL1〜BLx(xは、自然数)のそれぞれに接続される。複数のページバッファのそれぞれは、コントロールロジック43の制御によるプログラム動作の間、メモリセルアレイ140にデータをプログラムするためのドライバーとして作動する。また、複数のページバッファのそれぞれは、コントロールロジック43の制御によるリード動作の間、又は検証(verify)動作の間、複数のビットラインBL1〜BLxのそれぞれの電圧レベルを感知増幅する感知増幅器として作動する。

【0092】

Y−ゲーティング回路48は、カラムデコーダ47から出力された複数の選択信号に応答して、ページバッファブロック46と入出力ブロック49との間でデータDATAの伝送を制御する。入出力ブロック49は、メモリコントローラ20から入力されたデータDATAをY−ゲーティング回路48に伝送するか、又はY−ゲーティング回路48から出力されたデータDATAを複数の入出力ピン又はデータバスを通じてメモリコントローラ20に伝送する。

【0093】

図12は、ページ別に割り当てられたシードテーブルを用いる図1に示したメモリシステムの動作を説明するフローチャートであり、図13は、1つのシードテーブルに含まれる複数のゾーンを用いる図1に示したメモリシステムの動作を説明するフローチャートである。

【0094】

図1〜図13を参照して、複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するメモリコントローラ20の動作を説明すると、次の通りである。

【0095】

図6及び図7に示したように、複数のシードグループのそれぞれは、それぞれ異なるシードテーブルST1〜ST4又はST11〜ST13に保存されるか、或いは図8に示したように、1つのシードテーブルST21に保存される。

【0096】

メモリコントローラ20は、パワーアップされる(ステップS110)。この際、以前プログラム動作によってインクリメントされたエントリーポインターENTRY_PNT1、ENTRY_PNT2、ENTRY_PNT3、ENTRY_PNT4、ENTRY_PNTL、ENTRY_PNTC、ENTRY_PNTM、又はENTRY_PNTZ0は、デフォルト値ENTRY11、ENTRY21、ENTRY31、ENTRY41、ENTRYL01、ENTRYC01、ENTRYM01、又はENTRY_Z11に初期化される。

【0097】

メモリコントローラ20は、ホストHOSTから出力されたデータとプログラム要求とを受信する。一実施例において、複数のシードテーブルST1〜ST4、ST11〜ST13は、パワーアップ動作の間にバッファ24にローディングされるか、又はプログラム動作の間にリアルタイムでバッファ24にローディングされる(ステップS120)。他の実施例において、1つのシードテーブルST21は、パワーアップ動作の間にバッファ24にローディングされるか、又はプログラム動作の間にリアルタイムでバッファ24にローディングされる(ステップS220)。

【0098】

プログラム要求によって、データを不揮発性メモリ装置40にプログラムするために、マイクロプロセッサ22は、データが保存されるページに対するページアドレス又はワードラインアドレスを生成する。

【0099】

一実施例において、マイクロプロセッサ22は、ページアドレスの少なくとも一部のビット又はワードラインアドレスの少なくとも一部のビットを用いて、複数のシードテーブルST1〜ST4のうちの何れか1つを選択し、選択されたシードテーブルに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーをシードSEEDとして選択し、エントリーポインターをインクリメントする(ステップS130)。

【0100】

他の実施例において、マイクロプロセッサ22は、ページアドレスの少なくとも一部のビット又はワードラインアドレスの少なくとも一部のビットを用いて、1つのシードテーブルST21に含まれる複数のゾーンZONE0〜ZONE15のうちの何れか1つのゾーンを選択し、選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーをシードSEEDとして選択し、エントリーポインターをインクリメントする(ステップS230)。

【0101】

擬似乱数生成器32は、マイクロプロセッサ22によって選択されたシードSEEDを用いて擬似乱数RSを生成する(ステップS140)。モジュロ演算器34は、擬似乱数RSと入力データDATA1とをモジュロ加算し、その結果として、ランダマイズされたデータRDATAを生成する。即ち、モジュロ演算器34は、擬似乱数RSを用いて入力データDATA1をランダマイズする(ステップS150)。

【0102】

ECCブロック36は、ランダマイズされたデータRDATAを用いてパリティビットを生成し(ステップS160)、パリティビットを含むランダマイズされたデータERDATAを不揮発性メモリ装置40に出力する(ステップS170)。例えば、マイクロプロセッサ22は、ホストHOSTから出力されたデータ又は自ら生成したメタデータ(metadata)を不揮発性メモリ装置40にプログラムするために必要なアドレスを生成する。

【0103】

図14は、図1に示したメモリシステムを含む電子装置の一実施例を示す。図1、図2、図7、及び図14を参照すると、電子装置(electronic device)100は、携帯電話(cellular/mobile phone)、スマートフォン(smart phone)、タブレットPC(tablet Personal Computer)、PDA(Personal Digital Assistant)、ビデオゲームコンソール(video game console)、又は携帯用(handheld)通信装置として具現可能である。

【0104】

電子装置100は、メモリコントローラ20と不揮発性メモリ装置40とを含む。メモリコントローラ20は、プロセッサ110の制御によって不揮発性メモリ装置40のデータ処理動作、例えばプログラム動作、イレーズ動作、又はリード動作を制御する。

【0105】

プログラム要求によって、メモリコントローラ20は、ページ別に割り当てられたシードテーブルに含まれるシード、又はページ別に割り当てられたゾーンに含まれるシードを用いて擬似乱数RSを生成し、擬似乱数RSを用いてデータDATA1をランダマイズし、ランダマイズされたデータRDATAを出力する。従って、不揮発性メモリ装置40は、ランダマイズされたデータを現在プログラムされるページにプログラムすることができる。

【0106】

不揮発性メモリ装置40にプログラムされたデータは、プロセッサ110及び/又はメモリコントローラ20の制御によってディスプレイ120を通じてディスプレイされる。ディスプレイ120は、TFT−LCD(Thin Film Transistor−Liquid Crystal Display)、LED(Light−Emitting Diode)ディスプレイ、OLED(Organic LED)ディスプレイ、又はAMOLED(Active Matrix OLED)ディスプレイのような平板ディスプレイ(Flat Panel Display)として具現可能である。

【0107】

無線送受信器130は、アンテナANTを通じて無線信号を送受信する。例えば、無線送受信器130は、アンテナANTを通じて受信した無線信号をプロセッサ110で処理される信号に変更する。従って、プロセッサ110は、無線送受信器130から出力された信号を処理し、処理された信号をメモリコントローラ20又はディスプレイ120に伝送する。本実施例によるメモリコントローラ20は、プロセッサ110によって処理された信号を不揮発性メモリ装置40にプログラムする。また、無線送受信器130は、プロセッサ110から出力された信号を無線信号に変更し、変更された無線信号を、アンテナANTを通じて外部装置に出力する。

【0108】

入力装置134は、プロセッサ110の動作を制御するための制御信号又はプロセッサ110によって処理されるデータを入力する装置であり、タッチパッド(touch pad)とコンピュータマウス(computer mouse)のようなポインティング装置(pointing device)、キーパッド(keypad)、又はキーボードとして具現可能である。

【0109】

プロセッサ110は、メモリコントローラ20から出力されたデータ、無線送受信器130から出力されたデータ、又は入力装置140から出力されたデータが、ディスプレイ120を通じてディスプレイされるように、ディスプレイ120の動作を制御する。一実施例として、不揮発性メモリ装置40の動作を制御するメモリコントローラ20は、プロセッサ110の一部として具現され、またプロセッサ110と別途のチップとして具現可能である。

【0110】

図15は、図1に示したメモリシステムを含む電子装置の他の実施例を示す。図15に示した電子装置200は、PC(Personal Computer)、ラップトップ(laptop)コンピュータ、ネットブック(net−book)、イーリーダー(e−reader)、PMP(Portable Multimedia Player)、MP3プレーヤー、又はMP4プレーヤーとして具現可能である。

【0111】

電子装置200は、不揮発性メモリ装置40と、不揮発性メモリ装置40のデータ処理動作を制御するメモリコントローラ20と、を含む。

【0112】

プロセッサ210は、入力装置220を通じて入力されたデータによって不揮発性メモリ装置40に保存されたデータを、ディスプレイ230を通じてディスプレイする。例えば、入力装置220は、タッチパッド又はコンピュータマウスのようなポインティング装置、キーパッド、又はキーボードとして具現可能である。また、入力装置220は、他の装置とデータをインターフェーシングするインターフェースであり得る。プロセッサ210は、電子装置200の全般的な動作を制御し、メモリコントローラ20の動作を制御する。

【0113】

一実施例として、不揮発性メモリ装置40の動作を制御することができるメモリコントローラ20は、プロセッサ210の一部として具現され、またプロセッサ210と別途のチップとして具現可能である。

【0114】

図16は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図16では、説明の便宜上、電子装置300とホスト330とを共に示す。図16に示した電子装置300は、メモリカード(memory card)又はスマートカード(smart card)として具現可能である。デジタル情報を保存するために使われる電子フラッシュメモリデータ保存装置であるメモリカードは、PCカード、MMC、e−MMC(embedded MMC)、SDカード、又はUSB(Universal Serial Bus)フラッシュドライブ(flash drive)を含む。

【0115】

メモリカードのような電子装置300は、メモリコントローラ20、不揮発性メモリ装置40、カードインターフェース320を含む。メモリコントローラ20は、不揮発性メモリ装置40とカードインターフェース320との間でデータの交換を制御する。

【0116】

一実施例として、カードインターフェース320は、SDカードインターフェース又はMMCインターフェースであり得るが、これに限定されるものではない。

【0117】

カードインターフェース320は、ホスト330のプロトコルによってホスト330とメモリコントローラ20との間でデータ交換をインターフェーシングする。一実施例として、カードインターフェース320は、USBプロトコル、IC(InterChip)−USBプロトコルを支援することができる。ここで、カードインターフェースとは、ホスト330が使うプロトコルを支援するハードウェア、ハードウェアに搭載されたソフトウェア、又は信号伝送方式を意味する。

【0118】

電子装置300が、PC、ラップトップコンピュータ、タブレット(tablet)PC、デジタルカメラ(digital camera)、デジタルオーディオプレーヤー(digital audio player)、携帯電話、ビデオゲームコンソール、MP3プレーヤー、PMP、イーブック、又はデジタルセットトップボックス(digitalset−topn box)のようなホスト330のホストインターフェース350に接続されると、ホストインターフェース350は、マイクロプロセッサ340の制御によってカードインターフェース320とメモリコントローラ20とを通じて不揮発性メモリ装置40とデータ通信を行う。

【0119】

図17は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図17に示した電子装置400は、イメージ処理装置、例えば、デジタルカメラ、デジタルカメラ付き携帯電話、デジタルカメラ付きスマートフォン、又はデジタルカメラ付きタブレットPCとして具現可能である。

【0120】

電子装置400は、不揮発性メモリ装置40と、不揮発性メモリ装置40のデータ処理動作、例えばプログラム動作、イレーズ動作、又はリード動作を制御するメモリコントローラ20とを含む。電子装置400のイメージセンサー420は、光学イメージをデジタルイメージ信号に変換し、変換されたデジタルイメージ信号は、プロセッサ410及び/又はメモリコントローラ20に伝送される。プロセッサ410の制御によって、変換されたデジタルイメージ信号は、ディスプレイ430を通じてディスプレイされるか、又はメモリコントローラ20を通じて不揮発性メモリ装置40に保存される。

【0121】

また、不揮発性メモリ装置40に保存されたデータは、プロセッサ410及び/又はメモリコントローラ20の制御によってディスプレイ430を通じてディスプレイされる。

【0122】

一実施例として、不揮発性メモリ装置40の動作を制御するメモリコントローラ20は、プロセッサ410の一部として具現され、またプロセッサ410と別個のチップとして具現可能である。

【0123】

図18は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図18を参照すると、電子装置500は、不揮発性メモリ装置40と、不揮発性メモリ装置40の動作を制御するメモリコントローラ20とを含む。

【0124】

電子装置500は、CPU(Central Processing Unit)510の動作メモリ(operation memory)として使われるメモリ装置550を含む。メモリ装置550は、ROMのような不揮発性メモリとして具現され、SRAMのような不揮発性メモリとして具現可能である。

【0125】

電子装置500に接続されたホストHOSTは、メモリコントローラ20とホストインターフェース540とを通じて不揮発性メモリ装置40とデータ通信を行う。

【0126】

CPU510の制御によって、ECCブロック530は、メモリコントローラ20を通じて不揮発性メモリ装置40から出力されたデータに含まれるエラービットを検出し、エラービットを訂正し、エラー訂正されたデータを、ホストインターフェース540を通じてホストHOSTに伝送する。一実施例として、ECCブロック530は、電子装置500に含まれないこともある。

【0127】

CPU510は、バス501を通じて、メモリコントローラ20、ECCブロック530、ホストインターフェース540、及びメモリ装置550の間でデータ通信を制御する。

【0128】

電子装置500は、フラッシュメモリドライブ、USBメモリドライブ、IC−USBメモリドライブ、又はメモリスティック(memory stick)として具現可能である。

【0129】

図19は、図1に示したメモリシステムを含む電子装置の更に他の実施例を示す。図19を参照すると、電子装置600は、SSD(Solid State Drive)のようなデータ処理装置として具現可能である。

【0130】

電子装置600は、複数のソリッドステートメモリ装置40、メモリコントローラ20、揮発性メモリ装置630、及びバッファマネージャー620を含む。メモリコントローラ20は、複数のソリッドステートメモリ装置40のそれぞれのデータ処理動作を制御する。複数のソリッドステートメモリ装置40のそれぞれは、図1及び図10に示した不揮発性メモリ装置、例えば、NANDフラッシュメモリ装置であり、複数のページを含む。メモリコントローラ20は、ランダマイズされたデータを複数のソリッドステートメモリ装置40のうちの1つに含まれるページにプログラムする。

【0131】

揮発性メモリ装置630は、DRAMとして具現され、メモリコントローラ20とホスト640との間で送受信するデータを一時的に保存する。バッファマネージャー620は、揮発性メモリ装置630及び/又はメモリコントローラ20のデータバッファリング動作を制御する。

【0132】

図20は、図19に示した電子装置を含むデータ処理システムのブロック図を示す。図19及び図20を参照すると、RAID(Redundant Array of Independent Disks)システムとして具現可能なデータ処理装置700は、RAIDコントローラ710と複数の電子装置600−1〜600−n(nは、自然数)とを含む。

【0133】

電子装置600−1〜600−nのそれぞれは、図19に示した電子装置600である。複数の電子装置600−1〜600−nは、RAIDアレイを構成する。データ処理装置700は、PC(Personal Computer)、NAS(Network−Attached Storage)、又はSSDとして具現可能である。電子装置600−1〜600−nのそれぞれは、メモリモジュール(memory module)形態で具現されたメモリシステムであり得る。

【0134】

プログラム動作の間、ホストHOSTから出力されたプログラム要求によって、RAIDコントローラ710は、ホストHOSTから出力されたデータをRAIDレベルに基づいて、複数の電子装置600−1〜600−nのうちの少なくとも何れか1つの電子装置に出力する。リード動作の間、RAIDコントローラ710は、ホストHOSTから出力されたリード命令によって複数の電子装置600−1〜600−nのうちの少なくとも何れか1つの電子装置から読み取られたデータをホストHOSTに伝送する。

【0135】

以上、本発明の実施形態について図面を参照しながら詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

【符号の説明】

【0136】

10 メモリシステム

11、13 マルチチップパッケージ

11−1、13−1 回路基板

11−2、11−4、13−2、13−3 ボンディングワイヤ

11−3、13−4 ソルダボール

20 メモリコントローラ

22、340 マイクロプロセッサ

24 バッファ

26 ROM

28、501 バス

29、350、540 ホストインターフェース

30 メモリインターフェース

30A、30B データ変換装置

32 擬似乱数生成器

34 モジュロ演算器

34−1 第1モジュロ演算器

34−2 第2モジュロ演算器

36、530 ECC(エラー訂正コード)ブロック

40 不揮発性メモリ装置

42−1〜N 第1〜第Nページ

43 コントロールロジック

44 電圧発生器

45 ローデコーダ

46 ページバッファブロック

47 カラムデコーダ

48 Y−ゲーティング回路

49 入出力ブロック

100、200、400、500、600、600−1〜n 電子装置

110、210、410 プロセッサ

120、230、430 ディスプレイ

130 無線送受信器

134、220 入出力装置

140 メモリセルアレイ

300 メモリカード

320 カードインターフェース

330、640 ホスト

420 イメージセンサー

510 CPU

550 メモリ装置

620 バッファマネージャー

630 揮発性メモリ装置(DRAM)

700 データ処理装置

710 RAIDコントローラ

【特許請求の範囲】

【請求項1】

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシード(seed)を用いて擬似乱数を生成する段階と、

前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有することを特徴とするメモリコントローラの動作方法。

【請求項2】

前記擬似乱数を生成する段階は、

前記ページのページアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、

前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含むことを特徴とする請求項1に記載のメモリコントローラの動作方法。

【請求項3】

前記エントリーポインターによって指定されたエントリーが選択された後、前記エントリーポインターを変更する段階を更に有し、

前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト値にリセットされることを特徴とする請求項2に記載のメモリコントローラの動作方法。

【請求項4】

前記擬似乱数を生成する段階は、

前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、

前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含むことを特徴とする請求項1に記載のメモリコントローラの動作方法。

【請求項5】

前記複数のシードグループのそれぞれが複数のページのそれぞれに対応する場合、

前記複数のページの数は、1本のワードラインに接続された複数のマルチレベルセルのそれぞれに保存されるビットの数と同一であることを特徴とする請求項1に記載のメモリコントローラの動作方法。

【請求項6】

それぞれが異なるシードテーブルに保存された複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、

前記擬似乱数を用いて、前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有することを特徴とするメモリコントローラの動作方法。

【請求項7】

複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを用いて擬似乱数を生成する段階と、

前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有し、

前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、

前記複数のゾーンのうちから前記シードグループに相応するゾーンは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択され、

前記シードは、前記選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーであることを特徴とするメモリコントローラの動作方法。

【請求項8】

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を備え、

前記マイクロプロセッサは、

前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択した後、前記エントリーポインターを変更し、

前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト値にリセットされることを特徴とするメモリコントローラ。

【請求項9】

前記複数のシードグループを保存するROMを更に備えることを特徴とする請求項8に記載のメモリコントローラ。

【請求項10】

前記マイクロプロセッサは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択することを特徴とする請求項8に記載のメモリコントローラ。

【請求項11】

前記複数のシードグループのそれぞれは、異なるシードテーブルに保存されることを特徴とする請求項8に記載のメモリコントローラ。

【請求項12】

前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、

前記マイクロプロセッサは、

前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択することを特徴とする請求項8に記載のメモリコントローラ。

【請求項13】

複数のページを有するメモリセルアレイを含む不揮発性メモリ装置と、

前記不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記不揮発性メモリ装置に出力するランダマイザーと、を含むことを特徴とするメモリシステム。

【請求項14】

前記複数のシードグループのそれぞれが互いに異なるシードテーブルに保存される場合、

前記マイクロプロセッサは、

前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択することを特徴とする請求項13に記載のメモリシステム。

【請求項15】

前記マイクロプロセッサは、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択することを特徴とする請求項14に記載のメモリシステム。

【請求項16】

前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、

前記マイクロプロセッサは、

前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択することを特徴とする請求項13に記載のメモリシステム。

【請求項17】

前記メモリシステムは、前記不揮発性メモリ装置と前記メモリコントローラとを含むマルチチップパッケージであることを特徴とする請求項13に記載のメモリシステム。

【請求項18】

複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、

ホストと通信するためのカードインターフェースと、

前記フラッシュメモリ装置と前記カードインターフェースとの間の通信を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含むことを特徴とするメモリカード。

【請求項19】

前記メモリカードは、MMC、SDカード、又はUSBフラッシュドライブであることを特徴とする請求項18に記載のメモリカード。

【請求項20】

複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、

前記フラッシュメモリ装置の動作を制御するメモリコントローラと、

前記メモリコントローラの制御によって前記フラッシュメモリ装置から出力されたデータをディスプレイするディスプレイと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含むことを特徴とする携帯用通信装置。

【請求項21】

それぞれが複数のページを有する複数のレイヤを含む3次元不揮発性メモリ装置と、

前記3次元不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を含むことを特徴とする3次元メモリシステム。

【請求項22】

それぞれが複数のページを含む複数のソリッドステートメモリ装置と、

前記複数のソリッドステートメモリ装置のそれぞれの動作を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを現在プログラムされる前記ページに出力するランダマイザーと、を含むことを特徴とするソリッドステートドライブ。

【請求項1】

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシード(seed)を用いて擬似乱数を生成する段階と、

前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有することを特徴とするメモリコントローラの動作方法。

【請求項2】

前記擬似乱数を生成する段階は、

前記ページのページアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、

前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含むことを特徴とする請求項1に記載のメモリコントローラの動作方法。

【請求項3】

前記エントリーポインターによって指定されたエントリーが選択された後、前記エントリーポインターを変更する段階を更に有し、

前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト値にリセットされることを特徴とする請求項2に記載のメモリコントローラの動作方法。

【請求項4】

前記擬似乱数を生成する段階は、

前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択する段階と、

前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択し、該選択されたシードを用いて前記擬似乱数を生成する段階と、を含むことを特徴とする請求項1に記載のメモリコントローラの動作方法。

【請求項5】

前記複数のシードグループのそれぞれが複数のページのそれぞれに対応する場合、

前記複数のページの数は、1本のワードラインに接続された複数のマルチレベルセルのそれぞれに保存されるビットの数と同一であることを特徴とする請求項1に記載のメモリコントローラの動作方法。

【請求項6】

それぞれが異なるシードテーブルに保存された複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを用いて擬似乱数を生成する段階と、

前記擬似乱数を用いて、前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有することを特徴とするメモリコントローラの動作方法。

【請求項7】

複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを用いて擬似乱数を生成する段階と、

前記擬似乱数を用いて前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力する段階と、を有し、

前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、

前記複数のゾーンのうちから前記シードグループに相応するゾーンは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択され、

前記シードは、前記選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーであることを特徴とするメモリコントローラの動作方法。

【請求項8】

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を備え、

前記マイクロプロセッサは、

前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択した後、前記エントリーポインターを変更し、

前記メモリコントローラがリセットされると、変更されたエントリーポインターは、デフォルト値にリセットされることを特徴とするメモリコントローラ。

【請求項9】

前記複数のシードグループを保存するROMを更に備えることを特徴とする請求項8に記載のメモリコントローラ。

【請求項10】

前記マイクロプロセッサは、前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットを用いて、前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを選択することを特徴とする請求項8に記載のメモリコントローラ。

【請求項11】

前記複数のシードグループのそれぞれは、異なるシードテーブルに保存されることを特徴とする請求項8に記載のメモリコントローラ。

【請求項12】

前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、

前記マイクロプロセッサは、

前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択することを特徴とする請求項8に記載のメモリコントローラ。

【請求項13】

複数のページを有するメモリセルアレイを含む不揮発性メモリ装置と、

前記不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記不揮発性メモリ装置に出力するランダマイザーと、を含むことを特徴とするメモリシステム。

【請求項14】

前記複数のシードグループのそれぞれが互いに異なるシードテーブルに保存される場合、

前記マイクロプロセッサは、

前記複数のシードグループのうちから現在プログラムされるページに対する前記シードグループを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択することを特徴とする請求項13に記載のメモリシステム。

【請求項15】

前記マイクロプロセッサは、前記選択されたシードグループに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択することを特徴とする請求項14に記載のメモリシステム。

【請求項16】

前記複数のシードグループが同じシードテーブルに保存され、前記複数のシードグループのそれぞれが複数のエントリーを含む複数のゾーンのそれぞれに対応する場合、

前記マイクロプロセッサは、

前記複数のゾーンのうちから前記シードグループに相応するゾーンを前記ページのページアドレスの少なくとも一部のビット又は前記ページに相応するワードラインアドレスの少なくとも一部のビットによって選択し、該選択されたゾーンに含まれる複数のエントリーのうちからエントリーポインターによって指定されたエントリーを前記シードとして選択することを特徴とする請求項13に記載のメモリシステム。

【請求項17】

前記メモリシステムは、前記不揮発性メモリ装置と前記メモリコントローラとを含むマルチチップパッケージであることを特徴とする請求項13に記載のメモリシステム。

【請求項18】

複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、

ホストと通信するためのカードインターフェースと、

前記フラッシュメモリ装置と前記カードインターフェースとの間の通信を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含むことを特徴とするメモリカード。

【請求項19】

前記メモリカードは、MMC、SDカード、又はUSBフラッシュドライブであることを特徴とする請求項18に記載のメモリカード。

【請求項20】

複数のページを有するメモリセルアレイを含むフラッシュメモリ装置と、

前記フラッシュメモリ装置の動作を制御するメモリコントローラと、

前記メモリコントローラの制御によって前記フラッシュメモリ装置から出力されたデータをディスプレイするディスプレイと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを前記フラッシュメモリ装置に出力するランダマイザーと、を含むことを特徴とする携帯用通信装置。

【請求項21】

それぞれが複数のページを有する複数のレイヤを含む3次元不揮発性メモリ装置と、

前記3次元不揮発性メモリ装置の動作を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに割り当てられたシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを出力するランダマイザーと、を含むことを特徴とする3次元メモリシステム。

【請求項22】

それぞれが複数のページを含む複数のソリッドステートメモリ装置と、

前記複数のソリッドステートメモリ装置のそれぞれの動作を制御するメモリコントローラと、を備え、

前記メモリコントローラは、

複数のシードグループのうちから現在プログラムされるページに対するシードグループに含まれるシードを選択するマイクロプロセッサと、

前記選択されたシードを用いて擬似乱数を生成し、該生成された擬似乱数によって前記ページにプログラムされるデータをランダマイズし、該ランダマイズされたデータを現在プログラムされる前記ページに出力するランダマイザーと、を含むことを特徴とするソリッドステートドライブ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2013−20620(P2013−20620A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2012−153392(P2012−153392)

【出願日】平成24年7月9日(2012.7.9)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.MEMORY STICK

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成24年7月9日(2012.7.9)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.MEMORY STICK

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]