メモリコントローラ及びSIMD型プロセッサ

【課題】画像処理などの所定の処理に用いられるSIMD型プロセッサ全体の処理時間を従来技術に比較して削減できるメモリコントローラと、当該メモリコントローラを備えたSIMD型プロセッサとを提供する。

【解決手段】リードバッファカウンタ回路51は、リードバッファRB0がプロセッサエレメントPE0〜PENのレジスタRjにデータを転送する毎にアドレス値C51をインクリメントして出力する。ループレジスタ52は、所定の最大アドレス値を格納する。比較器53は、リードバッファカウンタ回路51から出力されるアドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したとき、リードバッファカウンタ回路51をリセットするためのカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。

【解決手段】リードバッファカウンタ回路51は、リードバッファRB0がプロセッサエレメントPE0〜PENのレジスタRjにデータを転送する毎にアドレス値C51をインクリメントして出力する。ループレジスタ52は、所定の最大アドレス値を格納する。比較器53は、リードバッファカウンタ回路51から出力されるアドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したとき、リードバッファカウンタ回路51をリセットするためのカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、SIMD(Single Instruction-stream Multiple Data-stream)プロセッサのためのメモリコントローラ及び当該メモリコントローラを備えたSIMD型プロセッサに関する。

【背景技術】

【0002】

近年、ディジタル複写機、プリンタ及びカメラなどの画像処理装置では、画素数の増加及び画像処理の多様化などにより画質の向上が図られている。このような画像処理装置では、複数の画素データに対して同一の処理を行うことが多いため、1つの演算命令により1つのデータを処理するSISD(Single Instruction-stream Single Data-stream)型のマイクロプロセッサより、1つの演算命令により複数のデータを並列処理するSIMD型のマイクロプロセッサ(以下、SIMD型プロセッサという。)が用いられることが多い。

【0003】

SIMD型プロセッサは、算術論理演算器(ALU(Arithmetic Logic Unit))と複数の汎用レジスタとをそれぞれ備えた複数のプロセッサエレメントと、そのプロセッサエレメントを制御するグローバルプロセッサとを備えて構成されている。プロセッサエレメントの個数は画像データの大きさに応じて決定され、これらの複数のプロセッサエレメントを、単一のグローバルプロセッサが、同時に演算処理を行うように制御している。具体的には、SIMD型プロセッサにおいて、各プロセッサエレメントは、画像データのうちの1画素の画素データの画像処理を行う。1画素に対応するプロセッサエレメントが複数あるため、複数の画素に対応する画素データが並列に演算処理される。このように、複数の画素データを同時に処理することで、画像処理の効率を高めている。

【0004】

SIMD型プロセッサによって実行される画像処理の中には、ディザ処理のようなテーブルデータを扱う処理がある。通常、ディザ処理のためのディザテーブルデータなどのテーブルデータは、SIMD型プロセッサの外部メモリにあらかじめ格納されている。SIMD型プロセッサの外部に設けられた従来技術に係るメモリコントローラは、外部メモリからテーブルデータをリードし、各プロセッサエレメントの汎用レジスタに転送する。一方、グローバルプロセッサは各プロセッサエレメントの演算用のレジスタに画素データを格納し、汎用レジスタに転送されたテーブルデータから演算用レジスタに格納された画素データを減算するように各プロセッサエレメントを制御し、これによりディザ処理を実行できる。

【0005】

特許文献1及び2は、従来技術に係るメモリコントローラを開示している。また、特許文献3は、ディザマトリクスを格納する領域を削減できる従来技術に係る画像生成方法を開示している。

【発明の概要】

【発明が解決しようとする課題】

【0006】

一般に、従来技術に係るSIMD型プロセッサは、メモリコントローラが外部メモリから読み出したテーブルデータを、1つの処理単位として処理される所定数(以下、SIMD数という。SIMD数はプロセッサエレメントの個数と等しい。)の画素データ単位又は1ライン分の画素データ単位に展開するように各プロセッサエレメントの汎用レジスタに格納するとき、プロセッサエレメントのシフト動作を利用したり、グローバルプロセッサから各汎用レジスタに同じデータを繰り返して転送したりしていた。この場合、各プロセッサエレメントへのテーブルデータの転送時間はSIMD数に比例して増加し、転送中にはSIMD型プロセッサでの演算が行えないという弊害が生じた。このため、SIMD型プロセッサの全体の処理時間を削減できなかった。

【0007】

本発明の目的は以上の問題点を解決し、画像処理などの所定の処理に用いられるSIMD型プロセッサ全体の処理時間を従来技術に比較して削減できるメモリコントローラと、当該メモリコントローラを備えたSIMD型プロセッサとを提供することにある。

【課題を解決するための手段】

【0008】

本発明に係るメモリコントローラは、

記憶装置からのデータを順次それぞれ所定のアドレスに一時的に格納し、入力されるアドレス値のアドレスに格納されたデータを、SIMD型プロセッサの複数のプロセッサエレメントに転送するリードバッファと、

上記アドレス値を発生して上記リードバッファに出力するリードバッファコントローラとを備えたメモリコントローラにおいて、

上記リードバッファコントローラは、

上記リードバッファが上記各プロセッサエレメントに上記データを転送する毎に上記アドレス値をインクリメントして出力するリードバッファカウンタ回路と、

所定の最大アドレス値を格納するループレジスタと、

上記リードバッファカウンタ回路から出力されるアドレス値を上記最大アドレス値と比較し、上記アドレス値が上記最大アドレス値と一致したとき、上記リードバッファカウンタ回路をリセットするためのカウンタリセット信号を発生して上記リードバッファカウンタ回路に出力する比較器とを備えたことを特徴とする。

【発明の効果】

【0009】

本発明に係るメモリコントローラによれば、リードバッファコントローラは、リードバッファが各プロセッサエレメントにデータを転送する毎にアドレス値をインクリメントして出力するリードバッファカウンタ回路と、所定の最大アドレス値を格納するループレジスタと、リードバッファカウンタ回路から出力されるアドレス値を最大アドレス値と比較し、アドレス値が最大アドレス値と一致したとき、リードバッファカウンタ回路をリセットするためのカウンタリセット信号を発生してリードバッファカウンタ回路に出力する比較器とを備える。従って、リードバッファに格納されたデータをプロセッサエレメントに繰り返して転送でき、当該転送中にプロセッサエレメントで他の演算処理を実行できるので、画像処理などの所定の処理に用いられるSIMD型プロセッサ全体の処理時間を従来技術に比較して削減できる。

【図面の簡単な説明】

【0010】

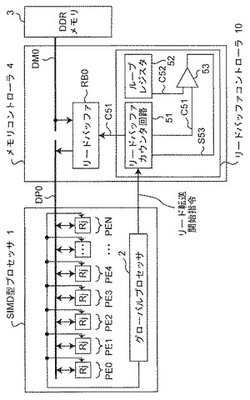

【図1】本発明の第1の実施形態に係るメモリコントローラ4と、SIMD型プロセッサ1と、DDRメモリ3とを示すブロック図である。

【図2】図1の各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3をより詳細に示すブロック図である。

【図3】図1のメモリコントローラ4のリードバッファコントローラ10をより詳細に示すブロック図である。

【図4】図1のDDRメモリ3に格納される4×4のマトリクスサイズを有するディザテーブルデータの構成を示すブロック図である。

【図5】(a)は、図1のDDRメモリ3に格納されるディザテーブルデータの一例を示すブロック図であり、(b)は、図1のSIMD型プロセッサ1により処理される画像データの一例を示すブロック図であり、(c)は、図5(b)の画像データに対して図5(a)のディザテーブルデータを用いてディザ処理を行ったときの処理結果の2値化データを示すブロック図であり、(d)は、図5(c)の2値化データに対応する印刷イメージを示すブロック図である。

【図6】図1のSIMD型プロセッサ1により図4のディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データを示すブロック図である。

【図7】本発明の第2の実施形態に係るメモリコントローラ4Aの構成を示すブロック図である。

【図8】本発明の第3の実施形態に係るメモリコントローラ4Bの構成を示すブロック図である。

【図9】本発明の第4の実施形態に係るメモリコントローラ4Cの構成を示すブロック図である。

【図10】図9のDDRメモリ3に格納される8×8のマトリクスサイズを有するディザテーブルデータと、当該ディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。

【図11】図10のDDRメモリ3に格納されているディザテーブルデータと、図9のリードバッファRB0〜RB3へのしきい値データの格納状態と、オフセット値C58が0でありかつ最大アドレス値C52Aが8であるとき(1回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データと、オフセット値C58が8でありかつ最大アドレス値C52Aが16であるとき(2回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。

【発明を実施するための形態】

【0011】

以下、本発明に係る実施形態について図面を参照して説明する。なお、以下の各実施形態において、同様の構成要素については同一の符号を付している。

【0012】

第1の実施形態.

図1は、本発明の第1の実施形態に係るメモリコントローラ4と、SIMD型プロセッサ1と、DDR(Double-Data-Rate)メモリ3とを示すブロック図である。また、図2は、図1の各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3をより詳細に示すブロック図であり、図3は、図1のメモリコントローラ4のリードバッファコントローラ10をより詳細に示すブロック図である。図1のSIMD型プロセッサ1は、ディジタル複写機、高性能プリンタ又はカメラなどの画像処理装置において、ディザ処理などの画像処理を行うためのマイクロプロセッサである。

【0013】

図1において、SIMD型プロセッサ1は、複数(N+1)個のプロセッサエレメントPE0,PE1,…,PEN(Nは正の整数である。)と、グローバルプロセッサ2とを備えて構成される。また、各プロセッサエレメントPEn(n=0,1,…,N)は、複数(J+1)個の汎用レジスタ(以下、レジスタという。)R0,R1,…,RJ(Jは3以上の整数である。)と、算術論理演算器91と、算術論理演算器91による演算結果を示すデータを格納するアキュムレータ92とを備えて構成される。なお、各プロセッサエレメントPEn(n=0,1,…,N)には、固有のアドレスが割り当てられている。また、本実施形態において、各レジスタR0〜RJのサイズは8ビットである。

【0014】

図3を参照して詳細後述するように、本実施形態に係るメモリコントローラ4は、DDRメモリ3からのデータを順次それぞれ所定のアドレスに一時的に格納し、入力されるアドレス値のアドレスに格納されたデータを、SIMD型プロセッサ1の複数のプロセッサエレメントPE0〜PENに転送するリードバッファRB0と、アドレス値C51を発生してリードバッファRB0に出力するリードバッファコントローラ10とを備えて構成される。

【0015】

ここで、リードバッファコントローラ10は、図3を参照して詳細後述するように、

(a)リードバッファRB0が各プロセッサエレメントPE0〜PENにデータを転送する毎にアドレス値C51をインクリメントして出力するリードバッファカウンタ回路51と、

(b)所定の最大アドレス値C52を格納するループレジスタと、

(c)リードバッファカウンタ回路51から出力されるアドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したとき、リードバッファカウンタ回路51をリセットするためのカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する比較器53とを備えたことを特徴としている。

【0016】

さらに、リードバッファRB0は、DDRメモリ3からのディザテーブルデータの第1行の各列のしきい値データを順次それぞれ所定のアドレスに格納し、最大アドレス値C52は、リードバッファRB0に最後に格納されたしきい値データの格納アドレスの次のリードバッファRB0のアドレスに設定されたことを特徴としている。

【0017】

図1において、グローバルプロセッサ2は、当該グローバルプロセッサ2内のプログラムメモリに格納されたプログラムを実行することにより、各プロセッサエレメントPE0〜PEN及びSIMD型プロセッサ1の外部に設けられたメモリコントローラ4を制御する。ここで、グローバルプロセッサ2は、制御対象のプロセッサエレメントPEn(n=0,1,…,N)のアドレスを指定して、各プロセッサエレメントPEnを制御する。また、グローバルプロセッサ2は、各プロセッサエレメントPEn(n=0,1,…,N)を、レジスタR0〜RJのうちの所定の1つのレジスタからデータをリードして算術論理演算器91に出力し、算術論理演算器91による演算結果をアキュムレータ92及びレジスタR0〜RJのうちの所定の1つのレジスタに出力するように制御する。グローバルプロセッサ2は、プロセッサエレメントPE0〜PENを同時に同一の処理を並列に行うように制御し、これにより、複数のデータを並列処理する。

【0018】

図2に示すように、各プロセッサエレメントPE0〜PENの4個のレジスタRj,Rj+1,Rj+2,Rj+3(jは、0以上J−3以下の所定の整数である。)は、メモリコントローラ4を介して、DDR、DDR2又はDDR3などの大容量メモリであるDDRメモリ3に接続されている。DDRメモリ3は、電源のオン時などの所定のタイミングにおいて、処理対象の画像データの種類(文字、写真、又は文字及び写真)及び画像処理の内容(ディザ処理、ぼかし処理、又はシャープネス処理など)毎に、画像処理のためのテーブルデータを格納する。

【0019】

ここで、ディザ処理及びディザ処理のためのディザテーブルデータを説明する。ディザ処理は、P階調の画像データをQ階調(Q<P)の画像データに変換する階調処理である。例えば、シアン、マゼンタ、イエロー及びブラックの各8ビットの画素データを含む多値の画像データ(1画素当たりのデータサイズは32ビットである。)を、シアン、マゼンタ、イエロー及びブラックの各2ビット、4ビット又は16ビットの画素データを含む2値、4値又は16値の印刷用の画像データ(1画素当たりのデータサイズは4ビット、8ビット又は16ビットである。)に変換するとき、ディザ処理が行われる。図4は、図1のDDRメモリ3に格納される4×4のマトリクスサイズを有するディザテーブルデータの構成を示すブロック図である。図4の横方向は画像データの主走査方向に対応しており、縦方向は画像データの副走査方向に対応している。図4のディザテーブルデータの各セルA〜Pには各画素位置で用いられるしきい値データが格納される。

【0020】

図5(a)は、図1のDDRメモリ3に格納されるディザテーブルデータの一例を示すブロック図である。図5(a)において、ディザテーブルデータの各セルには、256階調の(すなわち、8ビットの)画素データを2値化するためのしきい値データが格納されている。また、図5(b)は、図1のSIMD型プロセッサ1により処理される画像データの一例を示すブロック図であり、処理対象の画像データは、所定のカラーの8ビットの画素データを含む。図5(b)の画像データを図5(a)のディザテーブルデータを用いて2値化する場合、各画素位置において、画素データ値はしきい値データ値と比較される。そして、画素データ値がしきい値データ以上であるときは、当該画素位置における2値化結果は「1」となり、画素データ値がしきい値データ未満であるときは、当該画素位置における2値化結果は「0」となる。このため、図5(b)の画像データを図5(a)のディザテーブルデータを用いて2値化すると、図5(c)の2値化結果データが得られる。そして、2値化結果が「1」の画素位置にインクを置かず白色に設定し、2値化結果が「0」の画素位置にインクをおいて黒色に設定することにより、例えば図5(d)のような、白黒の印刷イメージを得ることができる。

【0021】

図6は、図1のSIMD型プロセッサ1により図4のディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データを示すブロック図である。グローバルプロセッサ2は、画像データに対して図4のディザテーブルデータを用いてディザ処理を行うとき、始めに、プロセッサエレメントPE0〜PENのレジスタRjにディザテーブルデータ第1行の各列のセルA,B,C,Dの各しきい値データを繰り返して格納し、プロセッサエレメントPE0〜PENのレジスタRj+1にディザテーブルデータの第2行の各列のセルE,F,G,Hの各しきい値データを繰り返して格納し、プロセッサエレメントPE0〜PENのレジスタRj+2にディザテーブルデータの第3行の各列のセルI,J,K,Lの各しきい値データを繰り返して格納し、プロセッサエレメントPE0〜PENのレジスタRj+3にディザテーブルデータの第4行の各列のセルM,N,O,Pの各しきい値データを繰り返して格納するように、メモリコントローラ4を制御する。なお、グローバルプロセッサ2によるメモリコントローラ4の制御方法は後述する。

【0022】

さらに、グローバルプロセッサ2は、ディザ処理において、処理対象の1ライン目の画像データを各プロセッサエレメントPE0〜PENのアキュムレータ92に格納する。そして、グローバルプロセッサ2は、アキュムレータ92に格納された画素データ値から、レジスタRjに格納されたしきい値データ値を減算し、減算結果が正であれば1を出力し、減算結果が負であれば0を出力するように各算術論理演算器91を制御する。これにより、最大でプロセッサエレメントPE0〜PENの個数(N+1)と同一の数の画素データに対してディザ処理を行う。以下同様に、レジスタRj+1,Rj+2,Rj+3に格納されたしきい値データを用いて2ライン目、3ライン目及び4ライン目の画像データに対してディザ処理を行う。また、5ライン目以降の画像データを処理するときは、Rj,Rj+1,Rj+2,Rj+3に格納されたしきい値データを繰り返して使用する。

【0023】

図2に戻り参照すると、メモリコントローラ4は、SIMD型プロセッサ1とDDRメモリ3との間のインターフェース処理を行うための回路であって、DDRアドレスコントローラ41と、リードバッファRB0,RB1,RB2,RB3と、ライトバッファWB0,WB1,WB2,WB3と、リードバッファRB0,RB1,RB2,RB3をそれぞれ制御するリードバッファコントローラ10,11,12,13と、ライトバッファWB0,WB1,WB2,WB3を制御するライトバッファコントローラ42とを備えて構成される。

【0024】

図2において、リードバッファRB0及びライトバッファWB0は、8ビットのデータバスDP0を介してプロセッサエレメントPE0〜PENのレジスタRjに接続され、8ビットのデータバスDM0を介してDDRメモリ3に接続されている。また、リードバッファRB1及びライトバッファWB1は、8ビットのデータバスDP1を介してプロセッサエレメントPE0〜PENのレジスタRj+1に接続され、8ビットのデータバスDM1を介してDDRメモリ3に接続されている。さらに、リードバッファRB2及びライトバッファWB2は、8ビットのデータバスDP2を介してプロセッサエレメントPE0〜PENのレジスタRj+2に接続され、8ビットのデータバスDM2を介してDDRメモリ3に接続されている。またさらに、リードバッファRB3及びライトバッファWB3は、8ビットのデータバスDP3を介してプロセッサエレメントPE0〜PENのレジスタRj+3に接続され、8ビットのデータバスDM3を介してDDRメモリ3に接続されている。

【0025】

図2において、グローバルプロセッサ2は、SIMD型プロセッサ1からDDRメモリ3へのデータ転送(以下、ライト転送という。)時に、DDRメモリ3へのライト時のライト開始のアドレスとデータ転送数(バースト数)とを含むライト転送開始指令を、DDRアドレスコントローラ41及びライトバッファコントローラ42に出力する。これに応答して、DDRアドレスコントローラ41は、DDRメモリ3のライト対象のアドレスを、ライト開始のアドレスから、当該アドレスにデータ転送数を加算したアドレスまで、1ずつインクリメントする。また、ライトバッファコントローラ42は、ライト転送開始指令に応答して、プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3からデータをリードしてライトバッファWB0〜WB3に転送し、転送されたデータをバッファリング(一時的に格納)した後に、DDRメモリ3のDDRアドレスコントローラ41により指定されたアドレスに転送してライトするように、ライトバッファWB0〜WB3を制御する。従って、1回のライト転送により、SIMD型プロセッサ1からDDRメモリ3に4×(N+1)個のデータが転送される。本実施形態では、レジスタRj〜Rj+3のサイズはそれぞれ8ビットであるので、SIMD型プロセッサ1とDDRメモリ3との間のデータ転送幅は32ビットである。なお、グローバルプロセッサ2は、プロセッサエレメントPE0〜PENのうちのライト転送の対象となるプロセッサエレメントを示す制御信号をプロセッサエレメントPE0〜PENに出力することにより、ライト転送の対象となるプロセッサエレメントを順次指定する。

【0026】

次に、図3を参照してリードバッファコントローラ10の構成及び動作を説明する。なお、リードバッファコントローラ11〜13はリードバッファコントローラ10と同様に構成される。図3において、リードバッファコントローラ10は、リードバッファカウンタ回路51と、ループレジスタ52と、比較器53とを備えて構成される。ここで、ループレジスタ52は、所定の最大アドレス値C52をあらかじめ格納し、当該最大アドレス値C52を比較器53に出力する。また、リードバッファカウンタ回路51は、グローバルプロセッサ2から、SIMD型プロセッサ1へのデータ転送を指示するリード転送開始指令を受信すると、アドレス値C51を0にリセットし、リードバッファRB0がSIMD型プロセッサ1に1つのデータを転送する毎に、アドレス値C51を1だけインクリメントしてリードバッファRB0と比較器53とに出力する。

【0027】

さらに、図3において、比較器53は、アドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したときにカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。リードバッファカウンタ回路51は、カウンタリセット信号S53に応答してアドレス値C51を0にリセットする。また、リードバッファRB0は、アドレス値C51のアドレスに格納されたしきい値データを、所定の転送タイミングにおいてデータバスDP0に出力する。

【0028】

次に、SIMD型プロセッサ1によるディザ処理時の、DDRメモリ3からSIMD型プロセッサ1への図6のディザテーブルデータの転送(以下、リード転送という。)方法を説明する。図2において、グローバルプロセッサ2は、ディザ処理の開始時に、DDRメモリ3に格納されたディザテーブルデータの第1行の各列のセルA,B,C,Dの各しきい値データをリードバッファRB0のアドレス0,1,2,3に順次それぞれ格納し、ディザテーブルデータの第2行の各列のセルE,F,G,Hの各しきい値データをリードバッファRB1のアドレス0,1,2,3に順次それぞれ格納し、ディザテーブルデータの第3行の各列のセルI,J,K,Lの各しきい値データをリードバッファRB2アドレス0,1,2,3に順次それぞれ格納し、ディザテーブルデータの第3行の各列のセルM,N,O,Pの各しきい値データを順次それぞれリードバッファRB3のアドレス0,1,2,3に格納するように、メモリコントローラ4を制御する。また、図3において、最大アドレス値C52は、各リードバッファRB0〜RB3に最後に格納されたしきい値データの格納アドレス(3である。)の次のアドレスである4に設定される。

【0029】

次に、グローバルプロセッサ2は、リードバッファコントローラ10〜13の各リードバッファカウンタ回路51にリード転送開始指令を出力する。図3において、リードバッファコントローラ10のリードバッファカウンタ回路51は、グローバルプロセッサ2からのリード転送開始指令に応答して、アドレス値C51を0にリセットしてリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第1の転送タイミングにおいて、アドレス0に格納されたセルAのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルAのしきい値データを、プロセッサエレメントPE0のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。

【0030】

次に、リードバッファカウンタ回路51はアドレス値C51(1である。)をリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第2の転送タイミングにおいて、アドレス1に格納されたセルBのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルBのしきい値データを、プロセッサエレメントPE1のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。

【0031】

次に、リードバッファカウンタ回路51はアドレス値C51(2である。)をリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第3の転送タイミングにおいて、アドレス2に格納されたセルCのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルCのしきい値データを、プロセッサエレメントPE2のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。

【0032】

次に、リードバッファカウンタ回路51はアドレス値C51(3である。)をリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第4の転送タイミングにおいて、アドレス3に格納されたセルDのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルDのしきい値データを、プロセッサエレメントPE3のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。この結果、アドレス値C51は4になり最大アドレス値C52と一致するので、比較器53はカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。これに応答して、リードバッファカウンタ回路51はアドレス値C51をゼロにリセットする。

【0033】

次に、リードバッファカウンタ回路51はアドレス値C51(0である。)をリードバッファRB0及び比較器53に出力する。従って、リードバッファRB0は、第5の転送タイミングにおいて、アドレス0に格納されたセルAのしきい値データをデータバスDP0に出力する。以下同様に、リードバッファRB0のアドレス0,1,2,3にそれぞれ格納されたセルA,B,C,Dのしきい値データは、セルA,B,C,D,A,B,C,…のように、繰り返してデータバスDP0に出力され、SIMD型プロセッサ1のプロセッサエレメントPE0〜PENのレジスタRjに格納される(図6参照。)。

【0034】

図2において、リードバッファコントローラ11は、リードバッファコントローラ10と同様に、ディザテーブルデータのセルE,F,G,Hのしきい値データをプロセッサエレメントPE0〜PENの各レジスタRj+1に繰り返して転送する。また、リードバッファコントローラ12は、リードバッファコントローラ10と同様に、ディザテーブルデータのセルI,J,K,Lのしきい値データをプロセッサエレメントPE0〜PENの各レジスタRj+2に繰り返して転送する。さらに、リードバッファコントローラ13は、リードバッファコントローラ10と同様に、ディザテーブルデータのセルM,N,O,Pのしきい値データをプロセッサエレメントPE0〜PENの各レジスタRj+3に繰り返して転送する。最後に、グローバルプロセッサ2は、プロセッサエレメントPENのレジスタRj〜Rj+3にしきい値データを格納すると、SIMD型プロセッサ1へのリード転送を終了するようにメモリコントローラ4を制御する。

【0035】

以上説明したように、本実施形態によれば、DDRメモリ3に格納されたディザテーブルデータの1行目のセルA〜Dの4個しきい値データをリードバッファRB0に転送する。そして、リードバッファRB0に格納された4個のしきい値データを繰り返してデータバスDP0を介してプロセッサエレメントPE0〜PENのレジスタRjに出力する。このとき、プロセッサエレメントPE0〜PENの個数(N+1)が352である場合、352をディザマトリクスの列数4で割った剰余はゼロであるので、セルDのしきい値データが、リードバッファRB0からSIMD型プロセッサ1に最後に転送される。また、リードバッファRB0からSIMD型プロセッサ1に転送されたしきい値データのセット数は88である。このため、ディザテーブルデータの各セルA〜Pのしきい値データは、図6に示すように、各プロセッサエレメントPE0〜PENのレジスタRj,Rj+1,Rj+2,Rj+3に繰り返して格納される。

【0036】

以上説明したように、本実施形態によれば、メモリコントローラ4からSIMD型プロセッサ1への1回のリード転送により、4×4のマトリクスサイズを有するディザテーブルデータを、メモリコントローラ4からSIMD型プロセッサ1に転送できる。

【0037】

なお、リードバッファRB0,RB1,RB2,RB3のサイズは、DDRメモリ3に格納されたディザテーブルデータの列数と同一の個数のしきい値データを格納できるサイズ(本実施形態の場合、8ビット×4である。)以上であればよい。また、アドレス値C51のビット数はリードバッファRB0,RB1,RB2,RB3のサイズに依存する。例えば、リードバッファRB0,RB1,RB2,RB3のサイズが8ビット×352の場合、アドレス値C51のビット数は9ビット(29=512>352)以上であればよい。さらに、ループレジスタ52のビット数はリードバッファカウンタ回路51のビット数と同一、又は最大アドレス値C52を格納できるビット数であればよい。

【0038】

なお、リードバッファRB0〜RB3からSIMD型プロセッサ1にしきい値データが繰り返して転送されている間は、DDRメモリ3から各リードバッファRB0〜RB3のアドレス4以降に、ディザテーブルデータ以外のデータが転送される。しかしながら、各リードバッファRB0〜RB3のアドレス0〜3のみからSIMD型プロセッサ1へのデータ転送が行われるので、問題は生じない。

【0039】

以上説明したように、本実施形態によれば、プロセッサエレメントPE0〜PENの各算術論理演算器91がレジスタR0〜RJのうちレジスタRj〜Rj+3以外のレジスタに格納されたデータを用いて演算を行っているときに、リードバッファRB0〜RB3から各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3にしきい値データを並行して転送できる。従って、従来技術に比較してSIMD型プロセッサ1全体の処理時間を削減できる。

【0040】

また、一般に、従来技術に係るメモリコントローラはリードバッファカウンタ回路51を備えているので、従来技術に係るメモリコントローラにループレジスタ52及び比較器53を設けるだけで、本実施形態に係るメモリコントローラ4を実現できる。

【0041】

第2の実施形態.

図7は、本発明の第2の実施形態に係るメモリコントローラ4Aの構成を示すブロック図である。図7において、メモリコントローラ4Aは、図3のメモリコントローラ4に比較して、DDRコントローラ45をさらに備え、リードバッファコントローラ10,11,12,13に代えてリードバッファコントローラ10A,11A,12A,13Aを備えた点が異なる。なお、リードバッファコントローラ11A,12A,13Aはリードバッファコントローラ10Aと同様に構成されるので、図示及び説明を省略する。

【0042】

図7において、リードバッファコントローラ10Aは、リードバッファカウンタ回路51と、ループレジスタ52と、比較器53とを備えて構成される。ここで、リードバッファカウンタ回路51は、図3のメモリコントローラ4のリードバッファカウンタ回路51と同様に、グローバルプロセッサ2からリード転送開始指令を受信すると、アドレス値C51を0にリセットし、リードバッファRB0からSIMD型プロセッサ1に1つのデータが転送される毎に、アドレス値C51を1だけインクリメントしてリードバッファRB0と比較器53とに出力する。また、ループレジスタ52は、図3のメモリコントローラ4のループレジスタ52と同様に、所定の最大アドレス値C52をあらかじめ格納し、比較器53に出力する。さらに、比較器53は、アドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したときにカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力すると、DDRコントローラ45とに出力する。

【0043】

図7において、DDRコントローラ45は、カウンタリセット信号S53に応答して、DDRメモリ3からリードバッファRB0へのデータ転送を停止させるためのストップ信号S45を発生し、DDRメモリ3に出力する。これに応答して、DDRメモリ3はリードバッファRB0へのデータ転送を停止する。

【0044】

一般に、DDRメモリ3は所定のデータ群を連続して転送するバースト転送を行うので、ストップ信号S45に応答してリアルタイムでは転送を停止できない(オーバーランする)。しかしながら、本実施形態によれば、DDRメモリ3がプロセッサエレメントPE0〜PENの個数(N+1)分の最大のデータ数のデータ転送を行っている場合であっても、リードバッファRB0へのデータ転送を停止できるので、第1の実施形態に比較して、DDRメモリ3からメモリコントローラ4へのディザテーブルデータ以外のデータの余分な転送を大幅に削減できる。このため、メモリコントローラ4AからDDRメモリ3へのアクセス回数が削減され、SIMD型プロセッサ1を搭載した装置の消費電流を削減できる。また、メモリコントローラ4AからSIMD型プロセッサ1へのリード転送を行っているときに、SIMD型プロセッサ1以外の回路からDDRメモリ3にアクセスできるので、第1の実施形態に比較して、SIMD型プロセッサ1を搭載した装置の処理速度を向上できる。

【0045】

第3の実施形態.

上述した各実施形態では、プロセッサエレメントPE0〜PENの個数(N+1)がDDRメモリ3に格納されたディザテーブルデータの列数で割り切れる場合のリード転送を説明した。しかしながら、1ライン分の画像データに含まれる画素データの数がプロセッサエレメントPE0〜PENの個数(N+1)よりも多く、かつ個数(N+1)がディザテーブルデータの列数で割り切れないときは、以下の問題が生じる。

【0046】

例えば、1ライン分の画像データに含まれる画素データの数が700個であり、プロセッサエレメントPE0〜PENの個数が350個であり、ディザテーブルデータの列数が4であるとき、1ライン分の画像データの前半の350個の画素データに対してディザ処理を行うときは、プロセッサエレメントPE0〜PE349の各レジスタRjに、ディザテーブルデータのセルA,B,C,D,A,B…,A,Bのようにしきい値データが格納される。次に、1ライン分の画像データの後半の350個の画素データに対してディザ処理を行うときは、プロセッサエレメントPE0〜PE351の各レジスタRjに、ディザテーブルデータのセルC,D,A,B,C,D,…のしきい値データを格納する必要がある。しかしながら、上述した実施形態の場合、メモリコントローラ4及び4AからSIMD型プロセッサ1へのリード転送開始時のリードバッファRB0〜RB3のアドレスは0であるので、プロセッサエレメントPE0のレジスタRjには、ディザテーブルデータのセルAのデータし格納できない。このため、1ライン分の画像データの後半の350個の画素データに対してディザ処理を行えないという問題がある。本実施形態はこの問題を解決することを目的とする。

【0047】

図8は、本発明の第3の実施形態に係るメモリコントローラ4Bの構成を示すブロック図である。本実施形態に係るメモリコントローラ4Bは、図3のメモリコントローラ4に比較して、リードバッファコントローラ10,11,12,13に代えてリードバッファコントローラ10B,11B,12B,13Bを備えた点が異なる。なお、リードバッファコントローラ11B,12B,13Bはリードバッファコントローラ10Bと同様に構成されるので、図示及び説明を省略する。

【0048】

図8において、リードバッファコントローラ10Bは、リードバッファコントローラ10に比較して、リセット値レジスタ54及びマルチプレクサ55を備えたリセット値設定回路56をさらに備えたことを特徴とする。図8において、リセット値レジスタ54は、リセット値0,1,2,3をあらかじめ格納し、マルチプレクサ55に出力する。また、グローバルプロセッサ2は、メモリコントローラ4BからSIMD型プロセッサ1へのリード転送の開始時に、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつリセット値を指定するリード転送開始指令をマルチプレクサ55に出力する。これに応答して、マルチプレクサ55は、リセット値レジスタ54からのリセット値0〜3のうち、リード転送開始指令に含まれるリセット値をリセット値C55としてリードバッファカウンタ回路51に出力する。

【0049】

また、図8において、リードバッファカウンタ回路51は、メモリコントローラ4BからSIMD型プロセッサ1へのリード転送の開始時に、アドレス値C51をマルチプレクサ55からのリセット値C55にリセットする。従って、本実施形態によれば、グローバルプロセッサ2は、メモリコントローラ4BからSIMD型プロセッサ1へのリード転送開始時に、リードバッファカウンタ回路51のアドレス値C51を所望の値にリセットできる。このため、リード転送開始時に、リードバッファカウンタ回路51のアドレス値C51が例えば2にリセットされると、リードバッファRB0のアドレス2に格納されたディザテーブルデータのセルCのしきい値データから、セルD,A,B,C,D,A…のしきい値データが順次繰り返して転送される。このため、上述した問題を解決できる。

【0050】

一般に、SIMD型プロセッサ1のプロセッサエレメントPE0〜PENの個数(N+1)は、ディザテーブルデータの列数で割り切れることが多い。しかしながら、ディザテーブルデータのマトリクスサイズが大きくなるほど(例えば、64×64など。)、SIMD型プロセッサ1のプロセッサエレメントPE0〜PENの個数(N+1)がディザテーブルデータの列数で割り切れない可能性が高くなり、このような場合、本実施形態に係るメモリコントローラ4Bは有効である。

【0051】

なお、本実施形態においてリセット値設定回路56は図8に示した構成を有したが、本発明はこれに限られず、リードバッファコントローラ51に対して任意のリセット値C55を出力する構成を有していればよい。例えば、グローバルプロセッサ2を、リード転送終了時のリードバッファカウンタ回路51のアドレス値C51をリセット値トレジスタに転送するようにリードバッファコントローラ51を制御するように構成し、リセット値設定回路を、リード転送開始時に、リセット値トレジスタに格納されたリセット値をリセット値C55としてリードバッファカウンタ回路51に出力するように構成してもよい。また、ユーザがプログラムでリセット値レジスタに所望のリセット値を設定し、リセット値設定回路を、ユーザがプログラムで設定可能なリセット値を格納するオフセットレジスタを備えるように構成してもよい。

【0052】

また、第2の実施形態に係るメモリコントローラ4Aと同様に、カウンタリセット信号S53に基づいてストップ信号を発生してDDRメモリ3に出力してもよい。

【0053】

第4の実施形態.

上述した各実施形態において、SIMD型プロセッサ1とメモリコントローラ4,4A,4Bとは、4本のデータバスDP0〜DP3を介して接続された。このため、ディザテーブルデータの行数が4であるときは、メモリコントローラ4,4A,4BからSIMD型プロセッサ1への1回のリード転送で、ディザテーブルデータの全てのセルA〜Pのしきい値データを、図6に示すようにプロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納できた。

【0054】

上述した各実施形態において、例えば8×8のマトリクスサイズを有するディザテーブルデータを用いる場合、メモリコントローラ4,4A又は4Bと、SIMD型プロセッサ1はとの間で以下のようなリード転送が行われる。図10は、図9のDDRメモリ3に格納される8×8のマトリクスサイズを有するディザテーブルデータと、当該ディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。なお、図10のディザテーブルにおいて、各セル内の数字はセル番号を示す。

【0055】

例えば、第1の実施形態の場合、図10において、始めに、DDRメモリ3からメモリコントローラ4(図2参照。)のリードバッファRB0にディザテーブルデータのセル1〜8のしきい値データを転送し、リードバッファRB1にディザテーブルデータのセル9〜16のしきい値データを転送し、リードバッファRB2にディザテーブルデータのセル17〜24のしきい値データを転送し、リードバッファRB3にディザテーブルデータのセル25〜32のしきい値データを転送する。そして、リードバッファRB0〜RB3に格納された各しきい値データをプロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に繰り返して転送する。そして、グローバルプロセッサ2は、1ライン目〜4ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。

【0056】

次に、図10において、DDRメモリ3からメモリコントローラ4のリードバッファRB0にディザテーブルデータのセル33〜40のしきい値データを転送し、リードバッファRB1にディザテーブルデータのセル41〜48のしきい値データを転送し、リードバッファRB2にディザテーブルデータのセル49〜56のしきい値データを転送し、リードバッファRB3にディザテーブルデータのセル57〜64のしきい値データを転送する。そして、リードバッファRB0〜RB3に格納された各しきい値データをプロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に繰り返して転送する。そして、グローバルプロセッサ2は、5ライン目〜8ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。従って、DDRメモリ3からメモリコントローラ4へのリード転送を2回行う必要があった。本実施形態は、上記各実施形態に比較して、DDRメモリ3からメモリコントローラ4への転送回数を削減することを目的とする。

【0057】

図9は、本発明の第4の実施形態に係るメモリコントローラ4Cの構成を示すブロック図である。図9において、メモリコントローラ4Cは、図3のメモリコントローラ4に比較して、リードバッファコントローラ10,11,12,13に代えてリードバッファコントローラ10C,11C,12C,13Cを備えて構成される。ここで、リードバッファコントローラ10Cは、リードバッファカウンタ回路51と、ループレジスタ52Aと、比較器53と、オフセット値レジスタ57及びマルチプレクサ58を備えたオフセット値設定回路60と、加算器C59とを備えて構成される。また、リードバッファコントローラ11C,12C,13Cはリードバッファコントローラ10Cと同様に構成されるので、図示及び説明を省略する。

【0058】

また、図9において、グローバルプロセッサ2は、メモリコントローラ4CからSIMD型プロセッサ1へのリード転送の開始時に、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつオフセット値及び最大アドレス値を指定するリード転送開始指令をマルチプレクサ58と、リードバッファカウンタ回路51と、ループレジスタ52Aとに出力する。オフセット値レジスタ57は、オフセット値0及び8をあらかじめ格納し、マルチプレクサ58に出力する。また、マルチプレクサ58は、オフセット値レジスタ57からのオフセット値のうち、グローバルプロセッサ2からのリード転送開始指令に含まれるオフセット値を、オフセット値C58として加算器59に出力する。

【0059】

図9において、ループレジスタ52Aは、グローバルプロセッサ2からのリード転送開始指令に含まれる最大アドレス値を格納し、最大アドレス値C52Aとして比較器53に出力する。リードバッファカウンタ回路51は、グローバルプロセッサ2からのリード転送開始指令に応答してアドレス値C51を0にリセットし、リードバッファRB0がSIMD型プロセッサ1に1つのデータを転送する毎に、アドレス値C51を1だけインクリメントして加算器59に出力する。さらに、加算器59は、リードバッファカウンタ回路51からのアドレス値C51にオフセット値レジスタ57からのオフセット値C58を加算し、加算結果の加算値をアドレス値C59としてリードバッファRB0と比較器53とに出力する。これに応答して、リードバッファRB0は、アドレス値C59を有するアドレスに格納されたしきい値データをデータバスDP0に出力する。また、比較器53は、アドレス値C59を最大アドレス値C52Aと比較し、アドレス値C59が最大アドレス値C52Aと一致したとき、カウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。これに応答して、リードバッファカウンタ回路51はアドレス値C51を0にリセットする。

【0060】

次に、図11を参照して、図10の8×8のマトリクスサイズを有するディザテーブルテータを用いてディザ処理を行うときのグローバルプロセッサ2及びメモリコントローラ4Cの動作を説明する。図11は、図10のDDRメモリ3に格納されているディザテーブルデータと、図9のリードバッファRB0〜RB3へのしきい値データの格納状態と、オフセット値C58が0でありかつ最大アドレス値C52Aが8であるとき(1回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データと、オフセット値C58が8でありかつ最大アドレス値C52Aが16であるとき(2回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。

【0061】

まず始めに、図11において、グローバルプロセッサ2は、ディザ処理の開始時に、DDRメモリ3に格納された8×8のディザテーブルデータの第1行の各列のセル1〜8及び第5行の各列のセル33〜40の各しきい値データをリードバッファRB0のアドレス1〜16に順次それぞれ格納し、ディザテーブルデータの第2行の各列のセル9〜16及び第2行の各列のセル41〜48の各しきい値データをリードバッファRB1のアドレス1〜16に順次それぞれ格納し、ディザテーブルデータの第3行の各列のセル17〜24及び第7行の各列のセル49〜56の各しきい値データをリードバッファRB2のアドレス1〜16に順次それぞれ格納し、ディザテーブルデータの第4行の各列のセル25〜32及び第8行の各列のセル57〜64の各しきい値データをリードバッファRB3のアドレス1〜16に順次それぞれ格納するように、メモリコントローラ4Cを制御する。これにより、DDRメモリ3からメモリコントローラ4Cへの1回のデータ転送により、図11に示すように、リードバッファRB0〜RB3に全てのしきい値データが格納される。

【0062】

次に、グローバルプロセッサ2は、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつオフセット値0及び最大アドレス値8を指定するリード転送開始指令をマルチプレクサ58と、リードバッファカウンタ回路51と、ループレジスタ52Aとに出力する。これに応答して、マルチプレクサ58はオフセット値C58(0である。)を加算器59に出力し、リードバッファカウンタ回路51はアドレス値C51を0にリセットし、ループレジスタ52Aは最大アドレス値C52A(8である。)を比較器53に出力する。

【0063】

従って、リードバッファカウンタ回路51からのアドレス値C51は0,1,2,…,7,8,0,1,…のように変化する。また、アドレス値C51が8になるとアドレス値C51は0にリセットされるので、メモリコントローラ4CからSIMD型プロセッサ1へのデータ転送タイミングにおける加算器59からのアドレス値C59は、0,1,2,…,7,0,1,2,…のように変化する。これにより、リードバッファRB0のアドレス0,1,2,…,7に格納されたセル0〜7の各しきい値データがデータバスDP0に順次繰り返して出力される。グローバルプロセッサ2は、データバスDP0に出力されたしきい値データを、プロセッサエレメントPE0〜PENのレジスタRjに順次それぞれ格納するように制御する。

【0064】

また、グローバルプロセッサ2は、リードバッファコントローラ10Cと同様に構成されたリードバッファコントローラ11C,12C,13Cを、リードバッファコントローラ10Cと同様に制御する。これにより、図11に示すように、プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に、ディザテーブルデータのセル1〜32のしきい値データが格納される。そして、グローバルプロセッサ2は、1ライン目〜4ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。

【0065】

次に、グローバルプロセッサ2は、グローバルプロセッサ2は、DDRメモリ3からメモリコントローラ4Cへのデータ転送を行うことなく、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつオフセット値8及び最大アドレス値16を指定するリード転送開始指令をマルチプレクサ58と、リードバッファカウンタ回路51と、ループレジスタ52Aとに出力する。これに応答して、マルチプレクサ58はオフセット値C58(8である。)を加算器59に出力し、リードバッファカウンタ回路51はアドレス値C51を0にリセットし、ループレジスタ52Aは最大アドレス値C52A(16である。)を比較器53に出力する。

【0066】

従って、リードバッファカウンタ回路51からのアドレス値C51は0,1,2,…,7,8,0,1,…のように変化する。また、アドレス値C51が16になるとアドレス値C51は0にリセットされるので、メモリコントローラ4CからSIMD型プロセッサ1へのデータ転送タイミングにおける加算器59からのアドレス値C59は、8,9,10…,15,8,9,10,…のように変化する。これにより、リードバッファRB0のアドレス8,9,10…,15に格納されたセル33〜40の各しきい値データがデータバスDP0に順次繰り返して出力される。グローバルプロセッサ2は、データバスDP0に出力されたしきい値データを、プロセッサエレメントPE0〜PENのレジスタRjに順次それぞれ格納するように制御する。

【0067】

また、グローバルプロセッサ2は、リードバッファコントローラ10Cと同様に構成されたリードバッファコントローラ11C,12C,13Cを、リードバッファコントローラ10Cと同様に制御する。これにより、図11に示すように、プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に、ディザテーブルデータのセル33〜64のしきい値データが格納される。そして、グローバルプロセッサ2は、5ライン目〜8ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。

【0068】

以上説明したように、本実施形態によれば、SIMD型プロセッサ1とDDRメモリ3との間のデータ転送幅が32ビットであるとき、DDRメモリ3からメモリコントローラ4Cへのデータ転送を1回だけ行い、メモリコントローラ4CからSIMD型プロセッサ1へのデータ転送を2回行うことにより、8×8のディザテーブルデータをSIMD型プロセッサ1に転送できる。

【0069】

なお、本実施形態において、8×8のマトリクスサイズを有するディザテーブルデータをSIMD型プロセッサ1に転送したが、本発明はこれに限られない。K×Lのマトリクスサイズ(K及びLは正の整数。)を有するディザテーブルデータをSIMD型プロセッサ1に転送する場合、例えば、リードバッファRB0はディザテーブルデータの所定の第1の行の各列のデータと、ディザテーブルデータの所定の第2の行の各列のデータとを順次それぞれ所定のアドレスに格納する。さらに、上述した第1の行の各列のデータの各プロセッサエレメントPE0〜PENへの転送時は、オフセット値C58は第1の行の第1の列のデータの格納アドレスに設定され、かつ最大アドレス値C52Aは第1の行の各列のデータのうちリードバッファRB0に最後に格納されたデータの格納アドレスの次のリードバッファRB0のアドレスに設定される。また、上述した第2の行の各列のデータの各プロセッサエレメントPE0〜PENへの転送時は、オフセット値C58は第2の行の第1の列のデータの格納アドレスに設定され、かつ最大アドレス値C52Aは第2の行の各列のデータのうちリードバッファRB0に最後に格納されたデータの格納アドレスの次のリードバッファRB0のアドレスに設定される。

【0070】

また、本実施形態において、各リードバッファRB0〜RB3にディザテーブルデータの2行分のしきい値データを転送したが、本発明はこれに限られず、3行以上の複数の行のしきい値データを転送してもよい。例えば、リードバッファRB0にディザテーブルデータの複数の行のしきい値データを順次転送した場合、オフセット値C58を、SIMD型プロセッサ1に繰り返して転送する行の第1の列のしきい値データの格納アドレスに設定し、最大アドレス値C52Aを、SIMD型プロセッサ1に繰り返して転送する行の各列のしきい値データのうちリードバッファRB0に最後に格納されたデータの格納アドレスの次のリードバッファRB0のアドレスに設定すればよい。

【0071】

また、本実施形態において、リードバッファコントローラ10Cは、第3の実施形態のリセット値設定回路56をさらに備えてもよい。

【0072】

さらに、上記各実施形態において、ディザテーブルデータのマトリクスサイズは4×4又は8×8であったが、本発明はこれに限られず、16×16又は32×32等の他のマトリクスサイズであってもよい。

【0073】

またさらに、上記各実施形態において、メモリコントローラ4,4A,4B,4Cは、ディザ処理に用いるディザテーブルデータをSIMD型プロセッサ1に転送したが、本発明はこれに限られず、画像処理などの所定の処理に用いる所定のデータをDDRメモリ3からSIMD型プロセッサ1に転送してもよい。

【0074】

また、上述した各実施形態において、各プロセッサエレメントPE0〜PENの各4個レジスタRj〜Rj+3をメモリコントローラ4,4A,4B,4Cを介してDDRメモリ3に接続したが、本発明はこれに限られず、各プロセッサエレメントPE0〜PENの少なくとも1個のレジスタをメモリコントローラ4,4A,4B,4Cを介してDDRメモリ3に接続すればよい。この場合、各プロセッサエレメントPE0〜PENにおいてDDRメモリ3に接続されたレジスタの個数と同数のリードバッファコントローラ10,10A,10B又は10Cを設ければよい。

【0075】

さらに、上述した各実施形態において、メモリコントローラ4,4A,4B,4CはSIMD型プロセッサ1の外部に設けられたが、本発明はこれに限られず、メモリコントローラ4,4A,4B,4CはSIMD型プロセッサ1の内部に設けられてもよい。これにより、プロセッサエレメントPE0〜PENと、メモリコントローラ4,4A,4B又は4Cとを備えたSIMD型プロセッサを提供できる。

【符号の説明】

【0076】

1…SIMD型プロセッサ、

2…グローバルプロセッサ、

3…DDRメモリ、

4,4A,4B,4C…メモリコントローラ、

10,10A,10B,10C,11,12,13…リードバッファコントローラ、

51…リードバッファカウンタ回路、

52,52A…ループレジスタ、

53…比較器、

54…リセット値レジスタ、

55…マルチプレクサ、

56…リセット値設定回路、

57…オフセット値レジスタ、

58…マルチプレクサ、

59…加算器、

60…オフセット値レジスタ、

PE0〜PEN…プロセッサエレメント、

RB0,RB1,RB2,RB3…リードバッファ。

【先行技術文献】

【特許文献】

【0077】

【特許文献1】特開2010−15438号公報。

【特許文献2】特表2006−509284号公報。

【特許文献3】特開2002−127503号公報。

【技術分野】

【0001】

本発明は、SIMD(Single Instruction-stream Multiple Data-stream)プロセッサのためのメモリコントローラ及び当該メモリコントローラを備えたSIMD型プロセッサに関する。

【背景技術】

【0002】

近年、ディジタル複写機、プリンタ及びカメラなどの画像処理装置では、画素数の増加及び画像処理の多様化などにより画質の向上が図られている。このような画像処理装置では、複数の画素データに対して同一の処理を行うことが多いため、1つの演算命令により1つのデータを処理するSISD(Single Instruction-stream Single Data-stream)型のマイクロプロセッサより、1つの演算命令により複数のデータを並列処理するSIMD型のマイクロプロセッサ(以下、SIMD型プロセッサという。)が用いられることが多い。

【0003】

SIMD型プロセッサは、算術論理演算器(ALU(Arithmetic Logic Unit))と複数の汎用レジスタとをそれぞれ備えた複数のプロセッサエレメントと、そのプロセッサエレメントを制御するグローバルプロセッサとを備えて構成されている。プロセッサエレメントの個数は画像データの大きさに応じて決定され、これらの複数のプロセッサエレメントを、単一のグローバルプロセッサが、同時に演算処理を行うように制御している。具体的には、SIMD型プロセッサにおいて、各プロセッサエレメントは、画像データのうちの1画素の画素データの画像処理を行う。1画素に対応するプロセッサエレメントが複数あるため、複数の画素に対応する画素データが並列に演算処理される。このように、複数の画素データを同時に処理することで、画像処理の効率を高めている。

【0004】

SIMD型プロセッサによって実行される画像処理の中には、ディザ処理のようなテーブルデータを扱う処理がある。通常、ディザ処理のためのディザテーブルデータなどのテーブルデータは、SIMD型プロセッサの外部メモリにあらかじめ格納されている。SIMD型プロセッサの外部に設けられた従来技術に係るメモリコントローラは、外部メモリからテーブルデータをリードし、各プロセッサエレメントの汎用レジスタに転送する。一方、グローバルプロセッサは各プロセッサエレメントの演算用のレジスタに画素データを格納し、汎用レジスタに転送されたテーブルデータから演算用レジスタに格納された画素データを減算するように各プロセッサエレメントを制御し、これによりディザ処理を実行できる。

【0005】

特許文献1及び2は、従来技術に係るメモリコントローラを開示している。また、特許文献3は、ディザマトリクスを格納する領域を削減できる従来技術に係る画像生成方法を開示している。

【発明の概要】

【発明が解決しようとする課題】

【0006】

一般に、従来技術に係るSIMD型プロセッサは、メモリコントローラが外部メモリから読み出したテーブルデータを、1つの処理単位として処理される所定数(以下、SIMD数という。SIMD数はプロセッサエレメントの個数と等しい。)の画素データ単位又は1ライン分の画素データ単位に展開するように各プロセッサエレメントの汎用レジスタに格納するとき、プロセッサエレメントのシフト動作を利用したり、グローバルプロセッサから各汎用レジスタに同じデータを繰り返して転送したりしていた。この場合、各プロセッサエレメントへのテーブルデータの転送時間はSIMD数に比例して増加し、転送中にはSIMD型プロセッサでの演算が行えないという弊害が生じた。このため、SIMD型プロセッサの全体の処理時間を削減できなかった。

【0007】

本発明の目的は以上の問題点を解決し、画像処理などの所定の処理に用いられるSIMD型プロセッサ全体の処理時間を従来技術に比較して削減できるメモリコントローラと、当該メモリコントローラを備えたSIMD型プロセッサとを提供することにある。

【課題を解決するための手段】

【0008】

本発明に係るメモリコントローラは、

記憶装置からのデータを順次それぞれ所定のアドレスに一時的に格納し、入力されるアドレス値のアドレスに格納されたデータを、SIMD型プロセッサの複数のプロセッサエレメントに転送するリードバッファと、

上記アドレス値を発生して上記リードバッファに出力するリードバッファコントローラとを備えたメモリコントローラにおいて、

上記リードバッファコントローラは、

上記リードバッファが上記各プロセッサエレメントに上記データを転送する毎に上記アドレス値をインクリメントして出力するリードバッファカウンタ回路と、

所定の最大アドレス値を格納するループレジスタと、

上記リードバッファカウンタ回路から出力されるアドレス値を上記最大アドレス値と比較し、上記アドレス値が上記最大アドレス値と一致したとき、上記リードバッファカウンタ回路をリセットするためのカウンタリセット信号を発生して上記リードバッファカウンタ回路に出力する比較器とを備えたことを特徴とする。

【発明の効果】

【0009】

本発明に係るメモリコントローラによれば、リードバッファコントローラは、リードバッファが各プロセッサエレメントにデータを転送する毎にアドレス値をインクリメントして出力するリードバッファカウンタ回路と、所定の最大アドレス値を格納するループレジスタと、リードバッファカウンタ回路から出力されるアドレス値を最大アドレス値と比較し、アドレス値が最大アドレス値と一致したとき、リードバッファカウンタ回路をリセットするためのカウンタリセット信号を発生してリードバッファカウンタ回路に出力する比較器とを備える。従って、リードバッファに格納されたデータをプロセッサエレメントに繰り返して転送でき、当該転送中にプロセッサエレメントで他の演算処理を実行できるので、画像処理などの所定の処理に用いられるSIMD型プロセッサ全体の処理時間を従来技術に比較して削減できる。

【図面の簡単な説明】

【0010】

【図1】本発明の第1の実施形態に係るメモリコントローラ4と、SIMD型プロセッサ1と、DDRメモリ3とを示すブロック図である。

【図2】図1の各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3をより詳細に示すブロック図である。

【図3】図1のメモリコントローラ4のリードバッファコントローラ10をより詳細に示すブロック図である。

【図4】図1のDDRメモリ3に格納される4×4のマトリクスサイズを有するディザテーブルデータの構成を示すブロック図である。

【図5】(a)は、図1のDDRメモリ3に格納されるディザテーブルデータの一例を示すブロック図であり、(b)は、図1のSIMD型プロセッサ1により処理される画像データの一例を示すブロック図であり、(c)は、図5(b)の画像データに対して図5(a)のディザテーブルデータを用いてディザ処理を行ったときの処理結果の2値化データを示すブロック図であり、(d)は、図5(c)の2値化データに対応する印刷イメージを示すブロック図である。

【図6】図1のSIMD型プロセッサ1により図4のディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データを示すブロック図である。

【図7】本発明の第2の実施形態に係るメモリコントローラ4Aの構成を示すブロック図である。

【図8】本発明の第3の実施形態に係るメモリコントローラ4Bの構成を示すブロック図である。

【図9】本発明の第4の実施形態に係るメモリコントローラ4Cの構成を示すブロック図である。

【図10】図9のDDRメモリ3に格納される8×8のマトリクスサイズを有するディザテーブルデータと、当該ディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。

【図11】図10のDDRメモリ3に格納されているディザテーブルデータと、図9のリードバッファRB0〜RB3へのしきい値データの格納状態と、オフセット値C58が0でありかつ最大アドレス値C52Aが8であるとき(1回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データと、オフセット値C58が8でありかつ最大アドレス値C52Aが16であるとき(2回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。

【発明を実施するための形態】

【0011】

以下、本発明に係る実施形態について図面を参照して説明する。なお、以下の各実施形態において、同様の構成要素については同一の符号を付している。

【0012】

第1の実施形態.

図1は、本発明の第1の実施形態に係るメモリコントローラ4と、SIMD型プロセッサ1と、DDR(Double-Data-Rate)メモリ3とを示すブロック図である。また、図2は、図1の各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3をより詳細に示すブロック図であり、図3は、図1のメモリコントローラ4のリードバッファコントローラ10をより詳細に示すブロック図である。図1のSIMD型プロセッサ1は、ディジタル複写機、高性能プリンタ又はカメラなどの画像処理装置において、ディザ処理などの画像処理を行うためのマイクロプロセッサである。

【0013】

図1において、SIMD型プロセッサ1は、複数(N+1)個のプロセッサエレメントPE0,PE1,…,PEN(Nは正の整数である。)と、グローバルプロセッサ2とを備えて構成される。また、各プロセッサエレメントPEn(n=0,1,…,N)は、複数(J+1)個の汎用レジスタ(以下、レジスタという。)R0,R1,…,RJ(Jは3以上の整数である。)と、算術論理演算器91と、算術論理演算器91による演算結果を示すデータを格納するアキュムレータ92とを備えて構成される。なお、各プロセッサエレメントPEn(n=0,1,…,N)には、固有のアドレスが割り当てられている。また、本実施形態において、各レジスタR0〜RJのサイズは8ビットである。

【0014】

図3を参照して詳細後述するように、本実施形態に係るメモリコントローラ4は、DDRメモリ3からのデータを順次それぞれ所定のアドレスに一時的に格納し、入力されるアドレス値のアドレスに格納されたデータを、SIMD型プロセッサ1の複数のプロセッサエレメントPE0〜PENに転送するリードバッファRB0と、アドレス値C51を発生してリードバッファRB0に出力するリードバッファコントローラ10とを備えて構成される。

【0015】

ここで、リードバッファコントローラ10は、図3を参照して詳細後述するように、

(a)リードバッファRB0が各プロセッサエレメントPE0〜PENにデータを転送する毎にアドレス値C51をインクリメントして出力するリードバッファカウンタ回路51と、

(b)所定の最大アドレス値C52を格納するループレジスタと、

(c)リードバッファカウンタ回路51から出力されるアドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したとき、リードバッファカウンタ回路51をリセットするためのカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する比較器53とを備えたことを特徴としている。

【0016】

さらに、リードバッファRB0は、DDRメモリ3からのディザテーブルデータの第1行の各列のしきい値データを順次それぞれ所定のアドレスに格納し、最大アドレス値C52は、リードバッファRB0に最後に格納されたしきい値データの格納アドレスの次のリードバッファRB0のアドレスに設定されたことを特徴としている。

【0017】

図1において、グローバルプロセッサ2は、当該グローバルプロセッサ2内のプログラムメモリに格納されたプログラムを実行することにより、各プロセッサエレメントPE0〜PEN及びSIMD型プロセッサ1の外部に設けられたメモリコントローラ4を制御する。ここで、グローバルプロセッサ2は、制御対象のプロセッサエレメントPEn(n=0,1,…,N)のアドレスを指定して、各プロセッサエレメントPEnを制御する。また、グローバルプロセッサ2は、各プロセッサエレメントPEn(n=0,1,…,N)を、レジスタR0〜RJのうちの所定の1つのレジスタからデータをリードして算術論理演算器91に出力し、算術論理演算器91による演算結果をアキュムレータ92及びレジスタR0〜RJのうちの所定の1つのレジスタに出力するように制御する。グローバルプロセッサ2は、プロセッサエレメントPE0〜PENを同時に同一の処理を並列に行うように制御し、これにより、複数のデータを並列処理する。

【0018】

図2に示すように、各プロセッサエレメントPE0〜PENの4個のレジスタRj,Rj+1,Rj+2,Rj+3(jは、0以上J−3以下の所定の整数である。)は、メモリコントローラ4を介して、DDR、DDR2又はDDR3などの大容量メモリであるDDRメモリ3に接続されている。DDRメモリ3は、電源のオン時などの所定のタイミングにおいて、処理対象の画像データの種類(文字、写真、又は文字及び写真)及び画像処理の内容(ディザ処理、ぼかし処理、又はシャープネス処理など)毎に、画像処理のためのテーブルデータを格納する。

【0019】

ここで、ディザ処理及びディザ処理のためのディザテーブルデータを説明する。ディザ処理は、P階調の画像データをQ階調(Q<P)の画像データに変換する階調処理である。例えば、シアン、マゼンタ、イエロー及びブラックの各8ビットの画素データを含む多値の画像データ(1画素当たりのデータサイズは32ビットである。)を、シアン、マゼンタ、イエロー及びブラックの各2ビット、4ビット又は16ビットの画素データを含む2値、4値又は16値の印刷用の画像データ(1画素当たりのデータサイズは4ビット、8ビット又は16ビットである。)に変換するとき、ディザ処理が行われる。図4は、図1のDDRメモリ3に格納される4×4のマトリクスサイズを有するディザテーブルデータの構成を示すブロック図である。図4の横方向は画像データの主走査方向に対応しており、縦方向は画像データの副走査方向に対応している。図4のディザテーブルデータの各セルA〜Pには各画素位置で用いられるしきい値データが格納される。

【0020】

図5(a)は、図1のDDRメモリ3に格納されるディザテーブルデータの一例を示すブロック図である。図5(a)において、ディザテーブルデータの各セルには、256階調の(すなわち、8ビットの)画素データを2値化するためのしきい値データが格納されている。また、図5(b)は、図1のSIMD型プロセッサ1により処理される画像データの一例を示すブロック図であり、処理対象の画像データは、所定のカラーの8ビットの画素データを含む。図5(b)の画像データを図5(a)のディザテーブルデータを用いて2値化する場合、各画素位置において、画素データ値はしきい値データ値と比較される。そして、画素データ値がしきい値データ以上であるときは、当該画素位置における2値化結果は「1」となり、画素データ値がしきい値データ未満であるときは、当該画素位置における2値化結果は「0」となる。このため、図5(b)の画像データを図5(a)のディザテーブルデータを用いて2値化すると、図5(c)の2値化結果データが得られる。そして、2値化結果が「1」の画素位置にインクを置かず白色に設定し、2値化結果が「0」の画素位置にインクをおいて黒色に設定することにより、例えば図5(d)のような、白黒の印刷イメージを得ることができる。

【0021】

図6は、図1のSIMD型プロセッサ1により図4のディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データを示すブロック図である。グローバルプロセッサ2は、画像データに対して図4のディザテーブルデータを用いてディザ処理を行うとき、始めに、プロセッサエレメントPE0〜PENのレジスタRjにディザテーブルデータ第1行の各列のセルA,B,C,Dの各しきい値データを繰り返して格納し、プロセッサエレメントPE0〜PENのレジスタRj+1にディザテーブルデータの第2行の各列のセルE,F,G,Hの各しきい値データを繰り返して格納し、プロセッサエレメントPE0〜PENのレジスタRj+2にディザテーブルデータの第3行の各列のセルI,J,K,Lの各しきい値データを繰り返して格納し、プロセッサエレメントPE0〜PENのレジスタRj+3にディザテーブルデータの第4行の各列のセルM,N,O,Pの各しきい値データを繰り返して格納するように、メモリコントローラ4を制御する。なお、グローバルプロセッサ2によるメモリコントローラ4の制御方法は後述する。

【0022】

さらに、グローバルプロセッサ2は、ディザ処理において、処理対象の1ライン目の画像データを各プロセッサエレメントPE0〜PENのアキュムレータ92に格納する。そして、グローバルプロセッサ2は、アキュムレータ92に格納された画素データ値から、レジスタRjに格納されたしきい値データ値を減算し、減算結果が正であれば1を出力し、減算結果が負であれば0を出力するように各算術論理演算器91を制御する。これにより、最大でプロセッサエレメントPE0〜PENの個数(N+1)と同一の数の画素データに対してディザ処理を行う。以下同様に、レジスタRj+1,Rj+2,Rj+3に格納されたしきい値データを用いて2ライン目、3ライン目及び4ライン目の画像データに対してディザ処理を行う。また、5ライン目以降の画像データを処理するときは、Rj,Rj+1,Rj+2,Rj+3に格納されたしきい値データを繰り返して使用する。

【0023】

図2に戻り参照すると、メモリコントローラ4は、SIMD型プロセッサ1とDDRメモリ3との間のインターフェース処理を行うための回路であって、DDRアドレスコントローラ41と、リードバッファRB0,RB1,RB2,RB3と、ライトバッファWB0,WB1,WB2,WB3と、リードバッファRB0,RB1,RB2,RB3をそれぞれ制御するリードバッファコントローラ10,11,12,13と、ライトバッファWB0,WB1,WB2,WB3を制御するライトバッファコントローラ42とを備えて構成される。

【0024】

図2において、リードバッファRB0及びライトバッファWB0は、8ビットのデータバスDP0を介してプロセッサエレメントPE0〜PENのレジスタRjに接続され、8ビットのデータバスDM0を介してDDRメモリ3に接続されている。また、リードバッファRB1及びライトバッファWB1は、8ビットのデータバスDP1を介してプロセッサエレメントPE0〜PENのレジスタRj+1に接続され、8ビットのデータバスDM1を介してDDRメモリ3に接続されている。さらに、リードバッファRB2及びライトバッファWB2は、8ビットのデータバスDP2を介してプロセッサエレメントPE0〜PENのレジスタRj+2に接続され、8ビットのデータバスDM2を介してDDRメモリ3に接続されている。またさらに、リードバッファRB3及びライトバッファWB3は、8ビットのデータバスDP3を介してプロセッサエレメントPE0〜PENのレジスタRj+3に接続され、8ビットのデータバスDM3を介してDDRメモリ3に接続されている。

【0025】

図2において、グローバルプロセッサ2は、SIMD型プロセッサ1からDDRメモリ3へのデータ転送(以下、ライト転送という。)時に、DDRメモリ3へのライト時のライト開始のアドレスとデータ転送数(バースト数)とを含むライト転送開始指令を、DDRアドレスコントローラ41及びライトバッファコントローラ42に出力する。これに応答して、DDRアドレスコントローラ41は、DDRメモリ3のライト対象のアドレスを、ライト開始のアドレスから、当該アドレスにデータ転送数を加算したアドレスまで、1ずつインクリメントする。また、ライトバッファコントローラ42は、ライト転送開始指令に応答して、プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3からデータをリードしてライトバッファWB0〜WB3に転送し、転送されたデータをバッファリング(一時的に格納)した後に、DDRメモリ3のDDRアドレスコントローラ41により指定されたアドレスに転送してライトするように、ライトバッファWB0〜WB3を制御する。従って、1回のライト転送により、SIMD型プロセッサ1からDDRメモリ3に4×(N+1)個のデータが転送される。本実施形態では、レジスタRj〜Rj+3のサイズはそれぞれ8ビットであるので、SIMD型プロセッサ1とDDRメモリ3との間のデータ転送幅は32ビットである。なお、グローバルプロセッサ2は、プロセッサエレメントPE0〜PENのうちのライト転送の対象となるプロセッサエレメントを示す制御信号をプロセッサエレメントPE0〜PENに出力することにより、ライト転送の対象となるプロセッサエレメントを順次指定する。

【0026】

次に、図3を参照してリードバッファコントローラ10の構成及び動作を説明する。なお、リードバッファコントローラ11〜13はリードバッファコントローラ10と同様に構成される。図3において、リードバッファコントローラ10は、リードバッファカウンタ回路51と、ループレジスタ52と、比較器53とを備えて構成される。ここで、ループレジスタ52は、所定の最大アドレス値C52をあらかじめ格納し、当該最大アドレス値C52を比較器53に出力する。また、リードバッファカウンタ回路51は、グローバルプロセッサ2から、SIMD型プロセッサ1へのデータ転送を指示するリード転送開始指令を受信すると、アドレス値C51を0にリセットし、リードバッファRB0がSIMD型プロセッサ1に1つのデータを転送する毎に、アドレス値C51を1だけインクリメントしてリードバッファRB0と比較器53とに出力する。

【0027】

さらに、図3において、比較器53は、アドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したときにカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。リードバッファカウンタ回路51は、カウンタリセット信号S53に応答してアドレス値C51を0にリセットする。また、リードバッファRB0は、アドレス値C51のアドレスに格納されたしきい値データを、所定の転送タイミングにおいてデータバスDP0に出力する。

【0028】

次に、SIMD型プロセッサ1によるディザ処理時の、DDRメモリ3からSIMD型プロセッサ1への図6のディザテーブルデータの転送(以下、リード転送という。)方法を説明する。図2において、グローバルプロセッサ2は、ディザ処理の開始時に、DDRメモリ3に格納されたディザテーブルデータの第1行の各列のセルA,B,C,Dの各しきい値データをリードバッファRB0のアドレス0,1,2,3に順次それぞれ格納し、ディザテーブルデータの第2行の各列のセルE,F,G,Hの各しきい値データをリードバッファRB1のアドレス0,1,2,3に順次それぞれ格納し、ディザテーブルデータの第3行の各列のセルI,J,K,Lの各しきい値データをリードバッファRB2アドレス0,1,2,3に順次それぞれ格納し、ディザテーブルデータの第3行の各列のセルM,N,O,Pの各しきい値データを順次それぞれリードバッファRB3のアドレス0,1,2,3に格納するように、メモリコントローラ4を制御する。また、図3において、最大アドレス値C52は、各リードバッファRB0〜RB3に最後に格納されたしきい値データの格納アドレス(3である。)の次のアドレスである4に設定される。

【0029】

次に、グローバルプロセッサ2は、リードバッファコントローラ10〜13の各リードバッファカウンタ回路51にリード転送開始指令を出力する。図3において、リードバッファコントローラ10のリードバッファカウンタ回路51は、グローバルプロセッサ2からのリード転送開始指令に応答して、アドレス値C51を0にリセットしてリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第1の転送タイミングにおいて、アドレス0に格納されたセルAのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルAのしきい値データを、プロセッサエレメントPE0のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。

【0030】

次に、リードバッファカウンタ回路51はアドレス値C51(1である。)をリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第2の転送タイミングにおいて、アドレス1に格納されたセルBのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルBのしきい値データを、プロセッサエレメントPE1のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。

【0031】

次に、リードバッファカウンタ回路51はアドレス値C51(2である。)をリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第3の転送タイミングにおいて、アドレス2に格納されたセルCのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルCのしきい値データを、プロセッサエレメントPE2のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。

【0032】

次に、リードバッファカウンタ回路51はアドレス値C51(3である。)をリードバッファRB0及び比較器53に出力する。そして、リードバッファRB0は、第4の転送タイミングにおいて、アドレス3に格納されたセルDのしきい値データをデータバスDP0に出力する。グローバルプロセッサ2は、データバスDP0に出力されたセルDのしきい値データを、プロセッサエレメントPE3のレジスタRjに格納するように制御する。さらに、リードバッファカウンタ回路51はアドレス値C51を1だけインクリメントする。この結果、アドレス値C51は4になり最大アドレス値C52と一致するので、比較器53はカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。これに応答して、リードバッファカウンタ回路51はアドレス値C51をゼロにリセットする。

【0033】

次に、リードバッファカウンタ回路51はアドレス値C51(0である。)をリードバッファRB0及び比較器53に出力する。従って、リードバッファRB0は、第5の転送タイミングにおいて、アドレス0に格納されたセルAのしきい値データをデータバスDP0に出力する。以下同様に、リードバッファRB0のアドレス0,1,2,3にそれぞれ格納されたセルA,B,C,Dのしきい値データは、セルA,B,C,D,A,B,C,…のように、繰り返してデータバスDP0に出力され、SIMD型プロセッサ1のプロセッサエレメントPE0〜PENのレジスタRjに格納される(図6参照。)。

【0034】

図2において、リードバッファコントローラ11は、リードバッファコントローラ10と同様に、ディザテーブルデータのセルE,F,G,Hのしきい値データをプロセッサエレメントPE0〜PENの各レジスタRj+1に繰り返して転送する。また、リードバッファコントローラ12は、リードバッファコントローラ10と同様に、ディザテーブルデータのセルI,J,K,Lのしきい値データをプロセッサエレメントPE0〜PENの各レジスタRj+2に繰り返して転送する。さらに、リードバッファコントローラ13は、リードバッファコントローラ10と同様に、ディザテーブルデータのセルM,N,O,Pのしきい値データをプロセッサエレメントPE0〜PENの各レジスタRj+3に繰り返して転送する。最後に、グローバルプロセッサ2は、プロセッサエレメントPENのレジスタRj〜Rj+3にしきい値データを格納すると、SIMD型プロセッサ1へのリード転送を終了するようにメモリコントローラ4を制御する。

【0035】

以上説明したように、本実施形態によれば、DDRメモリ3に格納されたディザテーブルデータの1行目のセルA〜Dの4個しきい値データをリードバッファRB0に転送する。そして、リードバッファRB0に格納された4個のしきい値データを繰り返してデータバスDP0を介してプロセッサエレメントPE0〜PENのレジスタRjに出力する。このとき、プロセッサエレメントPE0〜PENの個数(N+1)が352である場合、352をディザマトリクスの列数4で割った剰余はゼロであるので、セルDのしきい値データが、リードバッファRB0からSIMD型プロセッサ1に最後に転送される。また、リードバッファRB0からSIMD型プロセッサ1に転送されたしきい値データのセット数は88である。このため、ディザテーブルデータの各セルA〜Pのしきい値データは、図6に示すように、各プロセッサエレメントPE0〜PENのレジスタRj,Rj+1,Rj+2,Rj+3に繰り返して格納される。

【0036】

以上説明したように、本実施形態によれば、メモリコントローラ4からSIMD型プロセッサ1への1回のリード転送により、4×4のマトリクスサイズを有するディザテーブルデータを、メモリコントローラ4からSIMD型プロセッサ1に転送できる。

【0037】

なお、リードバッファRB0,RB1,RB2,RB3のサイズは、DDRメモリ3に格納されたディザテーブルデータの列数と同一の個数のしきい値データを格納できるサイズ(本実施形態の場合、8ビット×4である。)以上であればよい。また、アドレス値C51のビット数はリードバッファRB0,RB1,RB2,RB3のサイズに依存する。例えば、リードバッファRB0,RB1,RB2,RB3のサイズが8ビット×352の場合、アドレス値C51のビット数は9ビット(29=512>352)以上であればよい。さらに、ループレジスタ52のビット数はリードバッファカウンタ回路51のビット数と同一、又は最大アドレス値C52を格納できるビット数であればよい。

【0038】

なお、リードバッファRB0〜RB3からSIMD型プロセッサ1にしきい値データが繰り返して転送されている間は、DDRメモリ3から各リードバッファRB0〜RB3のアドレス4以降に、ディザテーブルデータ以外のデータが転送される。しかしながら、各リードバッファRB0〜RB3のアドレス0〜3のみからSIMD型プロセッサ1へのデータ転送が行われるので、問題は生じない。

【0039】

以上説明したように、本実施形態によれば、プロセッサエレメントPE0〜PENの各算術論理演算器91がレジスタR0〜RJのうちレジスタRj〜Rj+3以外のレジスタに格納されたデータを用いて演算を行っているときに、リードバッファRB0〜RB3から各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3にしきい値データを並行して転送できる。従って、従来技術に比較してSIMD型プロセッサ1全体の処理時間を削減できる。

【0040】

また、一般に、従来技術に係るメモリコントローラはリードバッファカウンタ回路51を備えているので、従来技術に係るメモリコントローラにループレジスタ52及び比較器53を設けるだけで、本実施形態に係るメモリコントローラ4を実現できる。

【0041】

第2の実施形態.

図7は、本発明の第2の実施形態に係るメモリコントローラ4Aの構成を示すブロック図である。図7において、メモリコントローラ4Aは、図3のメモリコントローラ4に比較して、DDRコントローラ45をさらに備え、リードバッファコントローラ10,11,12,13に代えてリードバッファコントローラ10A,11A,12A,13Aを備えた点が異なる。なお、リードバッファコントローラ11A,12A,13Aはリードバッファコントローラ10Aと同様に構成されるので、図示及び説明を省略する。

【0042】

図7において、リードバッファコントローラ10Aは、リードバッファカウンタ回路51と、ループレジスタ52と、比較器53とを備えて構成される。ここで、リードバッファカウンタ回路51は、図3のメモリコントローラ4のリードバッファカウンタ回路51と同様に、グローバルプロセッサ2からリード転送開始指令を受信すると、アドレス値C51を0にリセットし、リードバッファRB0からSIMD型プロセッサ1に1つのデータが転送される毎に、アドレス値C51を1だけインクリメントしてリードバッファRB0と比較器53とに出力する。また、ループレジスタ52は、図3のメモリコントローラ4のループレジスタ52と同様に、所定の最大アドレス値C52をあらかじめ格納し、比較器53に出力する。さらに、比較器53は、アドレス値C51を最大アドレス値C52と比較し、アドレス値C51が最大アドレス値C52と一致したときにカウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力すると、DDRコントローラ45とに出力する。

【0043】

図7において、DDRコントローラ45は、カウンタリセット信号S53に応答して、DDRメモリ3からリードバッファRB0へのデータ転送を停止させるためのストップ信号S45を発生し、DDRメモリ3に出力する。これに応答して、DDRメモリ3はリードバッファRB0へのデータ転送を停止する。

【0044】

一般に、DDRメモリ3は所定のデータ群を連続して転送するバースト転送を行うので、ストップ信号S45に応答してリアルタイムでは転送を停止できない(オーバーランする)。しかしながら、本実施形態によれば、DDRメモリ3がプロセッサエレメントPE0〜PENの個数(N+1)分の最大のデータ数のデータ転送を行っている場合であっても、リードバッファRB0へのデータ転送を停止できるので、第1の実施形態に比較して、DDRメモリ3からメモリコントローラ4へのディザテーブルデータ以外のデータの余分な転送を大幅に削減できる。このため、メモリコントローラ4AからDDRメモリ3へのアクセス回数が削減され、SIMD型プロセッサ1を搭載した装置の消費電流を削減できる。また、メモリコントローラ4AからSIMD型プロセッサ1へのリード転送を行っているときに、SIMD型プロセッサ1以外の回路からDDRメモリ3にアクセスできるので、第1の実施形態に比較して、SIMD型プロセッサ1を搭載した装置の処理速度を向上できる。

【0045】

第3の実施形態.

上述した各実施形態では、プロセッサエレメントPE0〜PENの個数(N+1)がDDRメモリ3に格納されたディザテーブルデータの列数で割り切れる場合のリード転送を説明した。しかしながら、1ライン分の画像データに含まれる画素データの数がプロセッサエレメントPE0〜PENの個数(N+1)よりも多く、かつ個数(N+1)がディザテーブルデータの列数で割り切れないときは、以下の問題が生じる。

【0046】

例えば、1ライン分の画像データに含まれる画素データの数が700個であり、プロセッサエレメントPE0〜PENの個数が350個であり、ディザテーブルデータの列数が4であるとき、1ライン分の画像データの前半の350個の画素データに対してディザ処理を行うときは、プロセッサエレメントPE0〜PE349の各レジスタRjに、ディザテーブルデータのセルA,B,C,D,A,B…,A,Bのようにしきい値データが格納される。次に、1ライン分の画像データの後半の350個の画素データに対してディザ処理を行うときは、プロセッサエレメントPE0〜PE351の各レジスタRjに、ディザテーブルデータのセルC,D,A,B,C,D,…のしきい値データを格納する必要がある。しかしながら、上述した実施形態の場合、メモリコントローラ4及び4AからSIMD型プロセッサ1へのリード転送開始時のリードバッファRB0〜RB3のアドレスは0であるので、プロセッサエレメントPE0のレジスタRjには、ディザテーブルデータのセルAのデータし格納できない。このため、1ライン分の画像データの後半の350個の画素データに対してディザ処理を行えないという問題がある。本実施形態はこの問題を解決することを目的とする。

【0047】

図8は、本発明の第3の実施形態に係るメモリコントローラ4Bの構成を示すブロック図である。本実施形態に係るメモリコントローラ4Bは、図3のメモリコントローラ4に比較して、リードバッファコントローラ10,11,12,13に代えてリードバッファコントローラ10B,11B,12B,13Bを備えた点が異なる。なお、リードバッファコントローラ11B,12B,13Bはリードバッファコントローラ10Bと同様に構成されるので、図示及び説明を省略する。

【0048】

図8において、リードバッファコントローラ10Bは、リードバッファコントローラ10に比較して、リセット値レジスタ54及びマルチプレクサ55を備えたリセット値設定回路56をさらに備えたことを特徴とする。図8において、リセット値レジスタ54は、リセット値0,1,2,3をあらかじめ格納し、マルチプレクサ55に出力する。また、グローバルプロセッサ2は、メモリコントローラ4BからSIMD型プロセッサ1へのリード転送の開始時に、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつリセット値を指定するリード転送開始指令をマルチプレクサ55に出力する。これに応答して、マルチプレクサ55は、リセット値レジスタ54からのリセット値0〜3のうち、リード転送開始指令に含まれるリセット値をリセット値C55としてリードバッファカウンタ回路51に出力する。

【0049】

また、図8において、リードバッファカウンタ回路51は、メモリコントローラ4BからSIMD型プロセッサ1へのリード転送の開始時に、アドレス値C51をマルチプレクサ55からのリセット値C55にリセットする。従って、本実施形態によれば、グローバルプロセッサ2は、メモリコントローラ4BからSIMD型プロセッサ1へのリード転送開始時に、リードバッファカウンタ回路51のアドレス値C51を所望の値にリセットできる。このため、リード転送開始時に、リードバッファカウンタ回路51のアドレス値C51が例えば2にリセットされると、リードバッファRB0のアドレス2に格納されたディザテーブルデータのセルCのしきい値データから、セルD,A,B,C,D,A…のしきい値データが順次繰り返して転送される。このため、上述した問題を解決できる。

【0050】

一般に、SIMD型プロセッサ1のプロセッサエレメントPE0〜PENの個数(N+1)は、ディザテーブルデータの列数で割り切れることが多い。しかしながら、ディザテーブルデータのマトリクスサイズが大きくなるほど(例えば、64×64など。)、SIMD型プロセッサ1のプロセッサエレメントPE0〜PENの個数(N+1)がディザテーブルデータの列数で割り切れない可能性が高くなり、このような場合、本実施形態に係るメモリコントローラ4Bは有効である。

【0051】

なお、本実施形態においてリセット値設定回路56は図8に示した構成を有したが、本発明はこれに限られず、リードバッファコントローラ51に対して任意のリセット値C55を出力する構成を有していればよい。例えば、グローバルプロセッサ2を、リード転送終了時のリードバッファカウンタ回路51のアドレス値C51をリセット値トレジスタに転送するようにリードバッファコントローラ51を制御するように構成し、リセット値設定回路を、リード転送開始時に、リセット値トレジスタに格納されたリセット値をリセット値C55としてリードバッファカウンタ回路51に出力するように構成してもよい。また、ユーザがプログラムでリセット値レジスタに所望のリセット値を設定し、リセット値設定回路を、ユーザがプログラムで設定可能なリセット値を格納するオフセットレジスタを備えるように構成してもよい。

【0052】

また、第2の実施形態に係るメモリコントローラ4Aと同様に、カウンタリセット信号S53に基づいてストップ信号を発生してDDRメモリ3に出力してもよい。

【0053】

第4の実施形態.

上述した各実施形態において、SIMD型プロセッサ1とメモリコントローラ4,4A,4Bとは、4本のデータバスDP0〜DP3を介して接続された。このため、ディザテーブルデータの行数が4であるときは、メモリコントローラ4,4A,4BからSIMD型プロセッサ1への1回のリード転送で、ディザテーブルデータの全てのセルA〜Pのしきい値データを、図6に示すようにプロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納できた。

【0054】

上述した各実施形態において、例えば8×8のマトリクスサイズを有するディザテーブルデータを用いる場合、メモリコントローラ4,4A又は4Bと、SIMD型プロセッサ1はとの間で以下のようなリード転送が行われる。図10は、図9のDDRメモリ3に格納される8×8のマトリクスサイズを有するディザテーブルデータと、当該ディザテーブルデータを用いてディザ処理を行うとき、各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。なお、図10のディザテーブルにおいて、各セル内の数字はセル番号を示す。

【0055】

例えば、第1の実施形態の場合、図10において、始めに、DDRメモリ3からメモリコントローラ4(図2参照。)のリードバッファRB0にディザテーブルデータのセル1〜8のしきい値データを転送し、リードバッファRB1にディザテーブルデータのセル9〜16のしきい値データを転送し、リードバッファRB2にディザテーブルデータのセル17〜24のしきい値データを転送し、リードバッファRB3にディザテーブルデータのセル25〜32のしきい値データを転送する。そして、リードバッファRB0〜RB3に格納された各しきい値データをプロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に繰り返して転送する。そして、グローバルプロセッサ2は、1ライン目〜4ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。

【0056】

次に、図10において、DDRメモリ3からメモリコントローラ4のリードバッファRB0にディザテーブルデータのセル33〜40のしきい値データを転送し、リードバッファRB1にディザテーブルデータのセル41〜48のしきい値データを転送し、リードバッファRB2にディザテーブルデータのセル49〜56のしきい値データを転送し、リードバッファRB3にディザテーブルデータのセル57〜64のしきい値データを転送する。そして、リードバッファRB0〜RB3に格納された各しきい値データをプロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に繰り返して転送する。そして、グローバルプロセッサ2は、5ライン目〜8ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。従って、DDRメモリ3からメモリコントローラ4へのリード転送を2回行う必要があった。本実施形態は、上記各実施形態に比較して、DDRメモリ3からメモリコントローラ4への転送回数を削減することを目的とする。

【0057】

図9は、本発明の第4の実施形態に係るメモリコントローラ4Cの構成を示すブロック図である。図9において、メモリコントローラ4Cは、図3のメモリコントローラ4に比較して、リードバッファコントローラ10,11,12,13に代えてリードバッファコントローラ10C,11C,12C,13Cを備えて構成される。ここで、リードバッファコントローラ10Cは、リードバッファカウンタ回路51と、ループレジスタ52Aと、比較器53と、オフセット値レジスタ57及びマルチプレクサ58を備えたオフセット値設定回路60と、加算器C59とを備えて構成される。また、リードバッファコントローラ11C,12C,13Cはリードバッファコントローラ10Cと同様に構成されるので、図示及び説明を省略する。

【0058】

また、図9において、グローバルプロセッサ2は、メモリコントローラ4CからSIMD型プロセッサ1へのリード転送の開始時に、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつオフセット値及び最大アドレス値を指定するリード転送開始指令をマルチプレクサ58と、リードバッファカウンタ回路51と、ループレジスタ52Aとに出力する。オフセット値レジスタ57は、オフセット値0及び8をあらかじめ格納し、マルチプレクサ58に出力する。また、マルチプレクサ58は、オフセット値レジスタ57からのオフセット値のうち、グローバルプロセッサ2からのリード転送開始指令に含まれるオフセット値を、オフセット値C58として加算器59に出力する。

【0059】

図9において、ループレジスタ52Aは、グローバルプロセッサ2からのリード転送開始指令に含まれる最大アドレス値を格納し、最大アドレス値C52Aとして比較器53に出力する。リードバッファカウンタ回路51は、グローバルプロセッサ2からのリード転送開始指令に応答してアドレス値C51を0にリセットし、リードバッファRB0がSIMD型プロセッサ1に1つのデータを転送する毎に、アドレス値C51を1だけインクリメントして加算器59に出力する。さらに、加算器59は、リードバッファカウンタ回路51からのアドレス値C51にオフセット値レジスタ57からのオフセット値C58を加算し、加算結果の加算値をアドレス値C59としてリードバッファRB0と比較器53とに出力する。これに応答して、リードバッファRB0は、アドレス値C59を有するアドレスに格納されたしきい値データをデータバスDP0に出力する。また、比較器53は、アドレス値C59を最大アドレス値C52Aと比較し、アドレス値C59が最大アドレス値C52Aと一致したとき、カウンタリセット信号S53を発生してリードバッファカウンタ回路51に出力する。これに応答して、リードバッファカウンタ回路51はアドレス値C51を0にリセットする。

【0060】

次に、図11を参照して、図10の8×8のマトリクスサイズを有するディザテーブルテータを用いてディザ処理を行うときのグローバルプロセッサ2及びメモリコントローラ4Cの動作を説明する。図11は、図10のDDRメモリ3に格納されているディザテーブルデータと、図9のリードバッファRB0〜RB3へのしきい値データの格納状態と、オフセット値C58が0でありかつ最大アドレス値C52Aが8であるとき(1回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データと、オフセット値C58が8でありかつ最大アドレス値C52Aが16であるとき(2回目のリード転送時)に各プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に格納されるしきい値データとを示すブロック図である。

【0061】

まず始めに、図11において、グローバルプロセッサ2は、ディザ処理の開始時に、DDRメモリ3に格納された8×8のディザテーブルデータの第1行の各列のセル1〜8及び第5行の各列のセル33〜40の各しきい値データをリードバッファRB0のアドレス1〜16に順次それぞれ格納し、ディザテーブルデータの第2行の各列のセル9〜16及び第2行の各列のセル41〜48の各しきい値データをリードバッファRB1のアドレス1〜16に順次それぞれ格納し、ディザテーブルデータの第3行の各列のセル17〜24及び第7行の各列のセル49〜56の各しきい値データをリードバッファRB2のアドレス1〜16に順次それぞれ格納し、ディザテーブルデータの第4行の各列のセル25〜32及び第8行の各列のセル57〜64の各しきい値データをリードバッファRB3のアドレス1〜16に順次それぞれ格納するように、メモリコントローラ4Cを制御する。これにより、DDRメモリ3からメモリコントローラ4Cへの1回のデータ転送により、図11に示すように、リードバッファRB0〜RB3に全てのしきい値データが格納される。

【0062】

次に、グローバルプロセッサ2は、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつオフセット値0及び最大アドレス値8を指定するリード転送開始指令をマルチプレクサ58と、リードバッファカウンタ回路51と、ループレジスタ52Aとに出力する。これに応答して、マルチプレクサ58はオフセット値C58(0である。)を加算器59に出力し、リードバッファカウンタ回路51はアドレス値C51を0にリセットし、ループレジスタ52Aは最大アドレス値C52A(8である。)を比較器53に出力する。

【0063】

従って、リードバッファカウンタ回路51からのアドレス値C51は0,1,2,…,7,8,0,1,…のように変化する。また、アドレス値C51が8になるとアドレス値C51は0にリセットされるので、メモリコントローラ4CからSIMD型プロセッサ1へのデータ転送タイミングにおける加算器59からのアドレス値C59は、0,1,2,…,7,0,1,2,…のように変化する。これにより、リードバッファRB0のアドレス0,1,2,…,7に格納されたセル0〜7の各しきい値データがデータバスDP0に順次繰り返して出力される。グローバルプロセッサ2は、データバスDP0に出力されたしきい値データを、プロセッサエレメントPE0〜PENのレジスタRjに順次それぞれ格納するように制御する。

【0064】

また、グローバルプロセッサ2は、リードバッファコントローラ10Cと同様に構成されたリードバッファコントローラ11C,12C,13Cを、リードバッファコントローラ10Cと同様に制御する。これにより、図11に示すように、プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に、ディザテーブルデータのセル1〜32のしきい値データが格納される。そして、グローバルプロセッサ2は、1ライン目〜4ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。

【0065】

次に、グローバルプロセッサ2は、グローバルプロセッサ2は、DDRメモリ3からメモリコントローラ4Cへのデータ転送を行うことなく、リードバッファRB0からSIMD型プロセッサ1へのデータ転送を指示しかつオフセット値8及び最大アドレス値16を指定するリード転送開始指令をマルチプレクサ58と、リードバッファカウンタ回路51と、ループレジスタ52Aとに出力する。これに応答して、マルチプレクサ58はオフセット値C58(8である。)を加算器59に出力し、リードバッファカウンタ回路51はアドレス値C51を0にリセットし、ループレジスタ52Aは最大アドレス値C52A(16である。)を比較器53に出力する。

【0066】

従って、リードバッファカウンタ回路51からのアドレス値C51は0,1,2,…,7,8,0,1,…のように変化する。また、アドレス値C51が16になるとアドレス値C51は0にリセットされるので、メモリコントローラ4CからSIMD型プロセッサ1へのデータ転送タイミングにおける加算器59からのアドレス値C59は、8,9,10…,15,8,9,10,…のように変化する。これにより、リードバッファRB0のアドレス8,9,10…,15に格納されたセル33〜40の各しきい値データがデータバスDP0に順次繰り返して出力される。グローバルプロセッサ2は、データバスDP0に出力されたしきい値データを、プロセッサエレメントPE0〜PENのレジスタRjに順次それぞれ格納するように制御する。

【0067】

また、グローバルプロセッサ2は、リードバッファコントローラ10Cと同様に構成されたリードバッファコントローラ11C,12C,13Cを、リードバッファコントローラ10Cと同様に制御する。これにより、図11に示すように、プロセッサエレメントPE0〜PENのレジスタRj〜Rj+3に、ディザテーブルデータのセル33〜64のしきい値データが格納される。そして、グローバルプロセッサ2は、5ライン目〜8ライン目の画像データに対して、プロセッサエレメントPE0〜PENの各レジスタRj〜Rj+3に格納されたしきい値データを用いてディザ処理を行う。

【0068】

以上説明したように、本実施形態によれば、SIMD型プロセッサ1とDDRメモリ3との間のデータ転送幅が32ビットであるとき、DDRメモリ3からメモリコントローラ4Cへのデータ転送を1回だけ行い、メモリコントローラ4CからSIMD型プロセッサ1へのデータ転送を2回行うことにより、8×8のディザテーブルデータをSIMD型プロセッサ1に転送できる。

【0069】

なお、本実施形態において、8×8のマトリクスサイズを有するディザテーブルデータをSIMD型プロセッサ1に転送したが、本発明はこれに限られない。K×Lのマトリクスサイズ(K及びLは正の整数。)を有するディザテーブルデータをSIMD型プロセッサ1に転送する場合、例えば、リードバッファRB0はディザテーブルデータの所定の第1の行の各列のデータと、ディザテーブルデータの所定の第2の行の各列のデータとを順次それぞれ所定のアドレスに格納する。さらに、上述した第1の行の各列のデータの各プロセッサエレメントPE0〜PENへの転送時は、オフセット値C58は第1の行の第1の列のデータの格納アドレスに設定され、かつ最大アドレス値C52Aは第1の行の各列のデータのうちリードバッファRB0に最後に格納されたデータの格納アドレスの次のリードバッファRB0のアドレスに設定される。また、上述した第2の行の各列のデータの各プロセッサエレメントPE0〜PENへの転送時は、オフセット値C58は第2の行の第1の列のデータの格納アドレスに設定され、かつ最大アドレス値C52Aは第2の行の各列のデータのうちリードバッファRB0に最後に格納されたデータの格納アドレスの次のリードバッファRB0のアドレスに設定される。

【0070】

また、本実施形態において、各リードバッファRB0〜RB3にディザテーブルデータの2行分のしきい値データを転送したが、本発明はこれに限られず、3行以上の複数の行のしきい値データを転送してもよい。例えば、リードバッファRB0にディザテーブルデータの複数の行のしきい値データを順次転送した場合、オフセット値C58を、SIMD型プロセッサ1に繰り返して転送する行の第1の列のしきい値データの格納アドレスに設定し、最大アドレス値C52Aを、SIMD型プロセッサ1に繰り返して転送する行の各列のしきい値データのうちリードバッファRB0に最後に格納されたデータの格納アドレスの次のリードバッファRB0のアドレスに設定すればよい。

【0071】

また、本実施形態において、リードバッファコントローラ10Cは、第3の実施形態のリセット値設定回路56をさらに備えてもよい。

【0072】

さらに、上記各実施形態において、ディザテーブルデータのマトリクスサイズは4×4又は8×8であったが、本発明はこれに限られず、16×16又は32×32等の他のマトリクスサイズであってもよい。

【0073】

またさらに、上記各実施形態において、メモリコントローラ4,4A,4B,4Cは、ディザ処理に用いるディザテーブルデータをSIMD型プロセッサ1に転送したが、本発明はこれに限られず、画像処理などの所定の処理に用いる所定のデータをDDRメモリ3からSIMD型プロセッサ1に転送してもよい。

【0074】

また、上述した各実施形態において、各プロセッサエレメントPE0〜PENの各4個レジスタRj〜Rj+3をメモリコントローラ4,4A,4B,4Cを介してDDRメモリ3に接続したが、本発明はこれに限られず、各プロセッサエレメントPE0〜PENの少なくとも1個のレジスタをメモリコントローラ4,4A,4B,4Cを介してDDRメモリ3に接続すればよい。この場合、各プロセッサエレメントPE0〜PENにおいてDDRメモリ3に接続されたレジスタの個数と同数のリードバッファコントローラ10,10A,10B又は10Cを設ければよい。

【0075】

さらに、上述した各実施形態において、メモリコントローラ4,4A,4B,4CはSIMD型プロセッサ1の外部に設けられたが、本発明はこれに限られず、メモリコントローラ4,4A,4B,4CはSIMD型プロセッサ1の内部に設けられてもよい。これにより、プロセッサエレメントPE0〜PENと、メモリコントローラ4,4A,4B又は4Cとを備えたSIMD型プロセッサを提供できる。

【符号の説明】

【0076】

1…SIMD型プロセッサ、

2…グローバルプロセッサ、

3…DDRメモリ、

4,4A,4B,4C…メモリコントローラ、

10,10A,10B,10C,11,12,13…リードバッファコントローラ、

51…リードバッファカウンタ回路、

52,52A…ループレジスタ、

53…比較器、

54…リセット値レジスタ、

55…マルチプレクサ、

56…リセット値設定回路、

57…オフセット値レジスタ、

58…マルチプレクサ、

59…加算器、

60…オフセット値レジスタ、

PE0〜PEN…プロセッサエレメント、

RB0,RB1,RB2,RB3…リードバッファ。

【先行技術文献】

【特許文献】

【0077】

【特許文献1】特開2010−15438号公報。

【特許文献2】特表2006−509284号公報。

【特許文献3】特開2002−127503号公報。

【特許請求の範囲】

【請求項1】

記憶装置からのデータを順次それぞれ所定のアドレスに一時的に格納し、入力されるアドレス値のアドレスに格納されたデータを、SIMD(Single Instruction-stream Multiple Data-stream)型プロセッサの複数のプロセッサエレメントに転送するリードバッファと、

上記アドレス値を発生して上記リードバッファに出力するリードバッファコントローラとを備えたメモリコントローラにおいて、

上記リードバッファコントローラは、

上記リードバッファが上記各プロセッサエレメントに上記データを転送する毎に上記アドレス値をインクリメントして出力するリードバッファカウンタ回路と、

所定の最大アドレス値を格納するループレジスタと、

上記リードバッファカウンタ回路から出力されるアドレス値を上記最大アドレス値と比較し、上記アドレス値が上記最大アドレス値と一致したとき、上記リードバッファカウンタ回路をリセットするためのカウンタリセット信号を発生して上記リードバッファカウンタ回路に出力する比較器とを備えたことを特徴とするメモリコントローラ。

【請求項2】

上記メモリコントローラは、上記カウンタリセット信号に基づいて、上記記憶装置から上記メモリコントローラへのデータ転送を停止させるためのストップ信号を発生して上記記憶装置に出力することを特徴とする請求項1記載のメモリコントローラ。

【請求項3】

上記リードバッファコントローラは、上記リードバッファから上記各プロセッサエレメントへのデータ転送の開始時に、所定のリセット値を上記リードバッファカウンタ回路に出力するリセット値設定回路をさらに備え、

上記リードバッファカウンタ回路は、上記リードバッファから上記各プロセッサエレメントへのデータ転送の開始時に、上記アドレス値を上記リセット値にリセットすることを特徴とする請求項1又は2記載のメモリコントローラ。

【請求項4】

上記リードバッファは、上記記憶装置からの所定のテーブルデータの所定の行の各列のデータを順次それぞれ所定のアドレスに格納し、

上記最大アドレス値は、上記リードバッファに最後に格納されたデータの格納アドレスの次の上記リードバッファのアドレスに設定されたことを特徴とする請求項1乃至3のうちのいずれか1つに記載のメモリコントローラ。

【請求項5】

上記リードバッファコントローラは、

所定のオフセット値を出力するオフセット値設定回路と、

上記リードバッファカウンタ回路から出力されるアドレス値に上記オフセット値を加算し、当該加算結果のアドレス値を上記リードバッファと上記比較器とに出力する加算器とをさらに備え、

上記比較器は、上記リードバッファカウンタ回路から出力されるアドレス値に代えて、上記加算器からのアドレス値を上記最大アドレス値と比較することを特徴とする請求項1乃至3のうちのいずれか1つに記載のメモリコントローラ。

【請求項6】

上記リードバッファは、上記記憶装置からの所定のテーブルデータの所定の第1の行の各列のデータと、上記テーブルデータの所定の第2の行の各列のデータとを順次それぞれ所定のアドレスに格納し、

上記第1の行の各列のデータの上記各プロセッサエレメントへの転送時は、上記オフセット値は上記第1の行の第1の列のデータの格納アドレスに設定され、かつ上記最大アドレス値は上記第1の行の各列のデータのうち上記リードバッファに最後に格納されたデータの格納アドレスの次の上記リードバッファのアドレスに設定され、

上記第2の行の各列のデータの上記各プロセッサエレメントへの転送時は、上記オフセット値は上記第2の行の第1の列のデータの格納アドレスに設定され、かつ上記最大アドレス値は上記第2の行の各列のデータのうち上記リードバッファに最後に格納されたデータの格納アドレスの次の上記リードバッファのアドレスに設定されたことを特徴とする請求項5記載のメモリコントローラ。

【請求項7】

上記テーブルデータは、ディザ処理のためのディザテーブルデータであることを特徴とする請求項4又は6記載のメモリコントローラ。

【請求項8】

上記複数のプロセッサエレメントと、

請求項1乃至7のうちのいずれか1つに記載のメモリコントローラとを備えたことを特徴とするSIMD型プロセッサ。

【請求項1】

記憶装置からのデータを順次それぞれ所定のアドレスに一時的に格納し、入力されるアドレス値のアドレスに格納されたデータを、SIMD(Single Instruction-stream Multiple Data-stream)型プロセッサの複数のプロセッサエレメントに転送するリードバッファと、

上記アドレス値を発生して上記リードバッファに出力するリードバッファコントローラとを備えたメモリコントローラにおいて、

上記リードバッファコントローラは、

上記リードバッファが上記各プロセッサエレメントに上記データを転送する毎に上記アドレス値をインクリメントして出力するリードバッファカウンタ回路と、

所定の最大アドレス値を格納するループレジスタと、

上記リードバッファカウンタ回路から出力されるアドレス値を上記最大アドレス値と比較し、上記アドレス値が上記最大アドレス値と一致したとき、上記リードバッファカウンタ回路をリセットするためのカウンタリセット信号を発生して上記リードバッファカウンタ回路に出力する比較器とを備えたことを特徴とするメモリコントローラ。

【請求項2】

上記メモリコントローラは、上記カウンタリセット信号に基づいて、上記記憶装置から上記メモリコントローラへのデータ転送を停止させるためのストップ信号を発生して上記記憶装置に出力することを特徴とする請求項1記載のメモリコントローラ。

【請求項3】

上記リードバッファコントローラは、上記リードバッファから上記各プロセッサエレメントへのデータ転送の開始時に、所定のリセット値を上記リードバッファカウンタ回路に出力するリセット値設定回路をさらに備え、

上記リードバッファカウンタ回路は、上記リードバッファから上記各プロセッサエレメントへのデータ転送の開始時に、上記アドレス値を上記リセット値にリセットすることを特徴とする請求項1又は2記載のメモリコントローラ。

【請求項4】

上記リードバッファは、上記記憶装置からの所定のテーブルデータの所定の行の各列のデータを順次それぞれ所定のアドレスに格納し、

上記最大アドレス値は、上記リードバッファに最後に格納されたデータの格納アドレスの次の上記リードバッファのアドレスに設定されたことを特徴とする請求項1乃至3のうちのいずれか1つに記載のメモリコントローラ。

【請求項5】

上記リードバッファコントローラは、

所定のオフセット値を出力するオフセット値設定回路と、

上記リードバッファカウンタ回路から出力されるアドレス値に上記オフセット値を加算し、当該加算結果のアドレス値を上記リードバッファと上記比較器とに出力する加算器とをさらに備え、

上記比較器は、上記リードバッファカウンタ回路から出力されるアドレス値に代えて、上記加算器からのアドレス値を上記最大アドレス値と比較することを特徴とする請求項1乃至3のうちのいずれか1つに記載のメモリコントローラ。

【請求項6】

上記リードバッファは、上記記憶装置からの所定のテーブルデータの所定の第1の行の各列のデータと、上記テーブルデータの所定の第2の行の各列のデータとを順次それぞれ所定のアドレスに格納し、

上記第1の行の各列のデータの上記各プロセッサエレメントへの転送時は、上記オフセット値は上記第1の行の第1の列のデータの格納アドレスに設定され、かつ上記最大アドレス値は上記第1の行の各列のデータのうち上記リードバッファに最後に格納されたデータの格納アドレスの次の上記リードバッファのアドレスに設定され、

上記第2の行の各列のデータの上記各プロセッサエレメントへの転送時は、上記オフセット値は上記第2の行の第1の列のデータの格納アドレスに設定され、かつ上記最大アドレス値は上記第2の行の各列のデータのうち上記リードバッファに最後に格納されたデータの格納アドレスの次の上記リードバッファのアドレスに設定されたことを特徴とする請求項5記載のメモリコントローラ。

【請求項7】

上記テーブルデータは、ディザ処理のためのディザテーブルデータであることを特徴とする請求項4又は6記載のメモリコントローラ。

【請求項8】

上記複数のプロセッサエレメントと、

請求項1乃至7のうちのいずれか1つに記載のメモリコントローラとを備えたことを特徴とするSIMD型プロセッサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−61851(P2013−61851A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−200529(P2011−200529)

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]