メモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラム

【課題】ストアイン方式のメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステムを提供すること

【解決手段】本発明のメモリシステムは、1stキャッシュメモリ10と1stキャッシュメモリ10に優先してプロセッサからアクセスされる1stキャッシュメモリ20と、1stキャッシュメモリ10においてキャッシュデータのリプレースを行う場合に、1stキャッシュメモリ10に格納されているキャッシュデータのうち、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、1stキャッシュメモリ20に格納されているキャッシュデータのうちリプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部4と、を備える。

【解決手段】本発明のメモリシステムは、1stキャッシュメモリ10と1stキャッシュメモリ10に優先してプロセッサからアクセスされる1stキャッシュメモリ20と、1stキャッシュメモリ10においてキャッシュデータのリプレースを行う場合に、1stキャッシュメモリ10に格納されているキャッシュデータのうち、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、1stキャッシュメモリ20に格納されているキャッシュデータのうちリプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部4と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はメモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラムに関し、特に階層化されたキャッシュメモリにより構成されるメモリシステム、そのメモリシステムにおけるキャッシュメモリ制御方法及びそのメモリシステムに用いられるメモリ制御方法に関する。

【背景技術】

【0002】

一般的に、CPU(Central Processing Unit)等のプロセッサの性能と比較して、記憶装置に用いられるメモリの性能が劣ることが知られている。このように、メモリの性能が劣っていることにより、プロセッサの性能を十分に発揮することができないことが問題となっていた。そこで、プロセッサとメモリとの性能差を補うために、キャッシュメモリを用いる構成が用いられている。キャッシュメモリは、メモリ(メインメモリ)よりも記憶容量は小さいが、処理能力が高い。そのため、プロセッサは、キャッシュメモリにアクセスすることにより、処理能力の向上を実現している。

【0003】

ここで、キャッシュメモリを用いるメモリシステムとして、ストアイン方式の階層キャッシュメモリを持つメモリシステムについて説明する。

【0004】

CPUがメインメモリのあるアドレスをリードするとメインメモリからデータが読み出される。さらに、上位キャッシュメモリおよび下位キャッシュメモリへデータが登録される。キャッシュメモリが無効化されるまではCPUが同一アドレスをリードすると上位キャッシュメモリまたは下位キャッシュメモリからキャッシュデータが読み出される。

【0005】

CPUがメインメモリのあるアドレスに対してリードを発行し、上位キャッシュメモリにキャッシュデータが登録されていれば、CPUは、上位キャッシュメモリからキャッシュデータを読み出す。そのため、同一アドレスのキャッシュデータが格納された下位キャッシュメモリのアクセス頻度が下がる。これにより、下位キャッシュメモリにおいて、上位キャッシュメモリに登録されているデータと同一のアドレスのキャッシュデータは、LRU(Least Recently Used)方式に従いリプレース対象になりやすい。

【0006】

ストアイン方式の階層キャッシュメモリをもつメモリシステムでは、キャッシュメモリが無効化されるまでは上位キャッシュメモリと下位キャッシュメモリとメインメモリとでデータが異なる事がある。そのため、キャッシュメモリのリプレースの際にはキャッシュコヒーレンシの保障のため、全キャッシュにおいて、対象となるアドレスのデータを無効化する必要がある。

【0007】

続いて、図7を用いて一般的に用いられるメモリシステムの構成について説明する。図7は、2ndキャッシュメモリ装置300の構成とCPU100及びCPU200と、メインメモリ400との関係を示している。本図に示したCPU100とCPU200とは、コア110又はコア210からメインメモリ400へのアクセス時間を短縮するために、上位キャッシュ又は下位キャッシュにアクセスを行う。上位キャッシュは、1stキャッシュメモリ装置100と1stキャッシュメモリ装置200とに相当する。下位キャッシュは、キャッシュタグ部310と、キャッシュデータ部320とを備えた2ndキャッシュメモリ装置300に相当する。

【0008】

CPU100内のコア110およびCPU200内のコア210は、1stキャッシュメモリ装置120および1stキャッシュメモリ装置220に対して、データのリードまたはライトに関するリクエストを発行する。CPU100内のコア110およびCPU200内のコア210は、1stキャッシュメモリ装置、1stキャッシュメモリ装置220、2ndキャッシュメモリ装置300またはメインメモリ400からデータのリード/ライトを行う。

【0009】

メインメモリ400は、大容量であってかつアクセス時間が2ndキャッシュタグメモリ311および2ndキャッシュデータメモリ321より遅いという特性を備えている。また2ndキャッシュメモリ装置300内の2ndキャッシュタグメモリ311および2ndキャッシュデータメモリ321は、CPU100内の1stキャッシュメモリ装置120およびCPU200内の1stキャッシュメモリ装置220より大容量であってかつアクセス時間が遅いという特性を備えている。

【0010】

ここで2ndキャッシュメモリ装置300は、データ格納方式としてセットアソシアティブ方式を採用している。このセットアソシアティブ方式は、図8に示すように2ndキャッシュメモリ(2ndキャッシュタグメモリ311および2ndキャッシュデータメモリ321を含む、以下にも同様に記載する。)を複数のウェイ(ウェイ0およびウェイ1)に分割し、各ウェイにおける決められたラインにデータを格納する方式である。同図に示した2ndキャッシュタグメモリ311においては、例えば、ウェイ0のラインNにアドレスAが格納されており、ウェイ1のラインNにアドレスBが格納されている。また、2ndキャッシュデータメモリ321には、例えばウェイ0のラインにデータAが格納されており、ウェイ1のラインNにデータBが格納されている。2ndキャッシュタグメモリ311と2ndキャッシュデータメモリ321とは、アドレスAとデータAとが、アドレスBとデータBとがそれぞれ一対一で対応している。

【0011】

図7に戻り、2ndキャッシュタグ部310は、CPU100およびCPU200からのリクエストを受け付ける。また、2ndキャッシュタグ部310は、2ndキャッシュタグメモリ311とキャッシュヒット判定回路312と選択回路313とから構成されている。

【0012】

2ndキャッシュタグメモリ311は、2ndキャッシュデータメモリ320に格納されているデータに対応するアドレス(タグ)を格納している。キャッシュヒット判定回路312は、CPU100およびCPU200から出力されるアドレスと2ndキャッシュタグメモリ311に格納されているアドレスとを比較し、両者が一致した場合、ヒット判定結果を「キャッシュヒット」とする。「キャッシュヒット」の場合には、当該アドレスに対応するデータが2ndキャッシュデータメモリ321に存在する事を意味する。一方、CPU100およびCPU200から出力されるアドレスと2ndキャッシュタグメモリ311に格納されているアドレスとが不一致である場合、キャッシュヒット判定回路312はヒット判定結果を「キャッシュミス」とする。

【0013】

「キャッシュミス」の場合には、当該アドレスに対応するデータが2ndキャッシュデータメモリ321に存在しない事を意味する。「キャッシュミス」の場合には、メインメモリ400から当該アドレスに対応するデータが読み出され、2ndキャッシュデータメモリ321において当該データがリプレースされた後、CPU100およびCPU200へ当該アドレスに対応するデータが出力される。

【0014】

ここで、リプレースする場合には、2ndキャッシュデータメモリ321のウェイに格納されているデータを追い出す必要がある。そして、上記ウェイにメインメモリ400から出力されたデータが格納される。ここで、一般的な2ndキャッシュメモリ装置300において、複数のウェイの中からリプレース対象のウェイ(以下、リプレースウェイとする)を選択するアルゴリズムとしては、最も使用されていなかったデータが格納されたウェイを選択するというLRU方式が採用されている。

【0015】

図7に戻り、キャッシュヒット判定回路312は、ヒット判定結果を2ndキャッシュデータメモリ321及びリプレース部330の2ndLRUメモリ331へ通知する。

【0016】

リプレース部330は、ヒット判定結果が「キャッシュミス」である場合に2ndキャッシュデータメモリ321においてリプレースすべきウェイを選択する機能を備えている。リプレース部330は、2ndLRUメモリ331およびリプレースウェイ判定回路332から構成されている。2ndLRUメモリ331は、一つの入力ポートを備えており、2ndキャッシュデータメモリ321においてデータをリプレースする場合に、前述したLRU方式により選択されたリプレースウェイを表すリプレースウェイ情報を格納している。具体的には、図8に示すように、2ndLRUメモリ331にはラインごとにリプレースウェイの番号に対応するリプレースウェイ情報が格納されている。同図ではラインNに、リプレースウェイがウェイ0であることを示すリプレースウェイ情報が格納されている。つまり、2ndキャッシュデータメモリ321のラインNにおいてはウェイ0に格納されているデータAが最も使用もしくはアクセスされていないデータである。

【0017】

図7に戻り、リプレースウェイ判定回路332は、2ndキャッシュメモリにおける複数のウェイの中から、リプレースウェイを選択する。リプレースウェイ判定回路332は、2ndLRUメモリ320を参照してLRU方式によりリプレースウェイを選択する。リプレースウェイ判定回路332は、リプレースウェイを選択した後、リプレース要求を選択回路313及び322へ発行する。

【0018】

メインメモリ400は、CPU100又は200からリクエストされたアドレスに対応するデータを読み出し、これを2ndキャッシュデータメモリ321のリプレースウェイに格納する。このようにして、メモリシステムは、リプレース処理を実行する。

【0019】

1stキャッシュメモリ装置120および1stキャッシュメモリ装置220についても2ndキャッシュメモリ装置3と同様にキャッシュヒット判定を行い、「キャッシュヒット」したときは1stキャッシュメモリよりデータが読み出され、「キャッシュミス」したときは2ndキャッシュメモリにリクエストを発行する。

【0020】

ストアイン方式の階層キャッシュメモリをもつメモリシステムにおいては、コア110およびコア210からのリード/ライトにより1stキャッシュまたは2ndキャッシュの内容が変更されても無効化(インバリデート)されるまではメインメモリ400と1stキャッシュメモリ装置120内のキャッシュメモリおよび1stキャッシュメモリ装置220内のキャッシュメモリおよび2ndキャッシュメモリの内容が異なる場合がある。そしてキャッシュコヒーレンシを保障するためには、1stキャッシュまたは2ndキャッシュのリプレースの際には、当該アドレスに対応する両キャッシュのキャッシュデータを無効化する必要がある。

【0021】

リプレース部330は、1stキャッシュメモリ装置120および1stキャッシュメモリ装置220に対して当該アドレスに対する無効化要求を発行する。要求を受けたCPU100の1stキャッシュメモリ装置120およびCPU200の1stキャッシュメモリ装置220は、該当するアドレスのデータを無効化し、リプレース部330へ報告する。

【0022】

次に、コア110およびコア210から出力されるリクエストに対し、1stキャッシュメモリ装置120、1stキャッシュメモリ装置220及び2ndキャッシュメモリ装置300の動作について、図9及び図10を用いて説明する。

【0023】

ステップ1において、コア110がメインメモリ400のアドレスA0に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、1stキャッシュメモリ装置120内のキャッシュデータメモリのウェイ0および2ndキャッシュデータメモリ321のウェイ0にデータA0が格納される。さらに、1stキャッシュメモリ装置120内の1stLRUメモリおよび2ndLRUメモリ331にウェイ1を示す1が格納される。

【0024】

ステップ2において、コア110がメインメモリ400のアドレスA1に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、1stキャッシュメモリ装置120内のキャッシュデータメモリのウェイ1および2ndキャッシュデータメモリ321のウェイ1にデータA1が格納される。さらに、1stキャッシュメモリ装置120内の1stLRUメモリおよび2ndLRUメモリ331にウェイ0を示す0が格納される。

【0025】

ステップ3、ステップ4及びステップ5において、コア110がメインメモリ400のアドレスA0に対してリクエストを発行すると1stキャッシュメモリ装置120において「キャッシュヒット」と判定され、データA0を読み出す。さらに、LRU方式により1stキャッシュメモリ装置120内の1stLRUメモリに1が格納される。

【0026】

ステップ6において、コア210がメインメモリ400のアドレスA2に対してリクエストを発行すると1stキャッシュメモリ装置220および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ310のウェイ0よりデータA0がリプレースされる。さらに、1stキャッシュメモリ装置120のウェイ0にデータA0が格納されているため、キャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置220のキャッシュデータメモリのウェイ0および2ndキャッシュデータメモリ321のウェイ0にデータA2が格納される。また、1stキャッシュメモリ装置220内の1stLRUメモリおよび2ndLRUメモリ331に1が格納される。1stキャッシュメモリ装置120内の1stLRUメモリには、0が格納される。

【0027】

ステップ7において、コア110がメインメモリ400のアドレスA0に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ310のウェイ1よりデータA1がリプレースされる。さらに、1stキャッシュメモリ装置120のウェイ1にデータA1が格納されているためキャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置120のキャッシュデータメモリのウェイ0および2ndキャッシュデータメモリ321のウェイ0にデータA0が格納される。また、1stキャッシュメモリ装置120内の1stLRUメモリに1が格納され、2ndLRUメモリ331に0が格納される。

【0028】

ステップ8において、コア210がメインメモリ400のアドレスA3に対してリクエストを発行すると1stキャッシュメモリ装置220および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ321のウェイ0よりデータA2がリプレースされる。さらに、1stキャッシュメモリ装置220のウェイ0にデータA2が格納されているためキャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置220のキャッシュデータメモリのウェイ1および2ndキャッシュデータメモリ321のウェイ0にデータA3が格納される。また、1stキャッシュメモリ装置220内の1stLRUメモリに0が格納され、2ndLRUメモリ331に1が格納される。

【0029】

ステップ9において、コア110がメインメモリ400のアドレスA4に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ321のウェイ1よりデータA0がリプレースされる。さらに、1stキャッシュメモリ装置120のウェイ0にデータA0が格納されているためキャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置120のキャッシュデータメモリのウェイ1および2ndキャッシュデータメモリ321のウェイ1にデータA4が格納される。また、1stキャッシュメモリ装置120内の1stLRUメモリに0が格納され、2ndLRUメモリ331に0が格納される。

【先行技術文献】

【特許文献】

【0030】

【特許文献1】特開2000−200221号公報

【特許文献2】特開平06−266623号公報

【発明の概要】

【発明が解決しようとする課題】

【0031】

しかし、上述したストアイン方式の階層キャッシュを持つメモリシステムにおいて、アクセス頻度の高いアドレスは常に上位キャッシュメモリにヒットし、下位キャッシュメモリではアクセス頻度が低くなる。そのため、上位キャッシュメモリにおいてアクセス頻度の高いアドレスは、下位キャッシュメモリにおいてLRU方式によりリプレース対象になりやすい。その結果、リプレース時にコヒーレンシ保障のため上位キャッシュメモリにおけるアドレスも無効化対象となるため、アクセス頻度の高いアドレスにアクセスするために、メインメモリに再度アクセスする必要があり、性能が悪化するという問題がある。

【0032】

アクセス頻度の高いアドレスに対しリプレースを行わないようにする方法として、特許文献1に記載されているように、キャッシュメモリの中に書き換え不可のエリアを設ける、という方法がある。また、特許文献2にも、追い出し禁止フラグを設けて、追い出し禁止フラグがセットされたブロックは、リプレース対象となっても、リプレースされないように制御される、という内容が開示されている。しかし、常にアクセス頻度の高いアドレスに対しては、上述した方法は有効であるが、処理に応じてアクセス頻度が変わるアドレスに対しては有効ではない。

【0033】

本発明は、このような課題を解決するためになされたものであり、ストアイン方式の階層キャッシュメモリを持つメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラムを提供することを目的とする。

【課題を解決するための手段】

【0034】

本発明の第1の態様にかかるメモリシステムは、第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、前記第2のキャッシュメモリに格納されているキャッシュデータのうち前記リプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部と、を備えるものである。

【0035】

本発明の第2の態様にかかるキャッシュメモリ制御方法は、第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるキャッシュメモリ制御方法であって、前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象キャッシュデータと同一のキャッシュデータを無効化するものである。

【0036】

本発明の第3の態様にかかるメモリ制御プログラムは、第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるメモリ制御プログラムであって、前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定するステップと、前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象データと同一のデータを無効化するステップと、をコンピュータに実行させるものである。

【発明の効果】

【0037】

本発明を用いることにより、ストアイン方式の階層キャッシュメモリを持つメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラムを提供することができる。

【図面の簡単な説明】

【0038】

【図1】実施の形態1にかかるメモリシステムの構成図である。

【図2】実施の形態1にかかるメモリシステムの構成図である。

【図3】実施の形態1にかかる2ndキャッシュメモリのデータ格納方式を説明する図である。

【図4】実施の形態1にかかるフラグの値と、選択されるリプレースウェイの関係を示す図である。

【図5】実施の形態1にかかるキャッシュメモリへデータが格納される状態を示す図である。

【図6】実施の形態1にかかるキャッシュメモリへデータが格納される状態を示す図である。

【図7】一般的なメモリシステムの構成図である。

【図8】一般的なメモリシステムにおけるデータ格納方式を説明する図である。

【図9】一般的なキャッシュメモリへデータが格納される状態を示す図である。

【図10】一般的なキャッシュメモリへデータが格納される状態を示す図である。

【発明を実施するための形態】

【0039】

(実施の形態1)

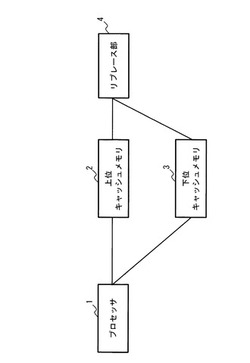

以下、図面を参照して本発明の実施の形態について説明する。図1を用いて本発明の実施の形態1にかかるメモリシステムの構成例について説明する。図1におけるメモリシステムは、プロセッサ1と、上位キャッシュメモリ2と、下位キャッシュメモリ3と、リプレース部4と、を備えている。

【0040】

プロセッサ1は、コンピュータもしくは回路等を制御するために用いられ、例えば、CPU(Central Processing Unit)、MPU(Micro Processing Unit)等により構成される。プロセッサ1は、メインメモリ(図示せず)に格納されているデータにアクセスする際に、高速処理を実現するために、処理速度がメインメモリよりも高いキャッシュメモリへアクセスする。

【0041】

キャッシュメモリは、上位キャッシュメモリ2と下位キャッシュメモリ3とを有しており、階層的に構成されている。プロセッサ1は、優先的に上位キャッシュメモリ2へアクセスし、上位キャッシュメモリ2に必要とするデータが存在しない場合、下位キャッシュメモリ3へアクセスする。上位キャッシュメモリ2及び下位キャッシュメモリ3に、プロセッサ1からのアクセス対象となるデータが存在しない場合、プロセッサ1は、メインメモリからデータを取得する。また、上位キャッシュメモリ2及び下位キャッシュメモリ3は、プロセッサ1がメインメモリから取得したデータを格納(キャッシュ)する。上位キャッシュメモリ2又は下位キャッシュメモリ3は、メインメモリよりも記憶容量が小さい。そのため、メインメモリから新たにデータを取得して格納する場合、上位キャッシュメモリ2又は下位キャッシュメモリ3は、すでに格納しているデータ(キャッシュデータ)を削除して、メインメモリから新たなデータを取得する。キャッシュメモリにおけるこのような動作を、キャッシュデータのリプレースと称する。

【0042】

下位キャッシュメモリ3においてキャッシュデータのリプレースを行う場合に、リプレース部4は、下位キャッシュメモリ3に格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いてリプレース対象キャッシュデータを決定し、上位キャッシュメモリ2に格納されており、下位キャッシュメモリ3におけるリプレース対象のキャッシュデータと同一のキャッシュデータを無効化する。

【0043】

リプレース部4は、上位キャッシュメモリ2と下位キャッシュメモリ3とのキャッシュコヒーレンシの保障のため、下位キャッシュメモリ3においてリプレースされたデータと同一のデータを、上位キャッシュメモリ2において無効化する。

【0044】

以上説明したように、図1におけるメモリシステムを用いることにより、リプレース部4は、下位キャッシュメモリ3に格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定することができる。つまり、過去にリプレース対象となり、再度下位キャッシュメモリ3に格納されているデータは、プロセッサ1からのアクセス頻度が高いため、このようなデータをリプレース対象外、もしくはリプレースする優先順位を下げることにより、上位キャッシュメモリ2においてもキャッシュデータは有効に存在することになる。その結果、アクセス頻度が高いキャッシュデータを、上位キャッシュメモリ2に格納しておくことができるため、プロセッサ1が、メインメモリへアクセスすることによるアクセス性能の低下を防止することができる。

【0045】

続いて、図2を用いて本発明の実施の形態1にかかるメモリシステムの詳細な構成例について説明する。図2におけるメモリシステムは、CPU10及び20と、2ndキャッシュメモリ30と、メインメモリ80と、を備えている。

【0046】

CPU10は、コア11と、1stキャッシュメモリ12とを有している。コア11は、メモリアクセスを発行し、1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、コア11から受けたメモリアクセスに対応するキャッシュデータが1stキャッシュメモリ12に格納されているか判定する。1stキャッシュメモリ12は、キャッシュヒットと判定したらキャッシュデータをコア11に返却する。1stキャッシュメモリ12は、キャッシュミスと判定したらメモリアクセスを発行し、2ndキャッシュメモリ30へ出力する。また、1stキャッシュメモリ12は、2ndキャッシュメモリ30より無効化要求を受け取ったら、対象となるキャッシュデータを無効化する。さらに、1stキャッシュメモリ12は、コア11がアクセスを希望するデータであって、2ndキャッシュメモリ30から出力されたデータを格納する。

【0047】

CPU20は、コア21と、1stキャッシュメモリ22とを有している。CPU20における構成は、CPU10と同様であるため、詳細な説明を省略する。

【0048】

2ndキャッシュメモリ30は、キャッシュタグ部40と、キャッシュデータ部50と、リプレース部60と、バッファ部70と、を有している。以下に、それぞれの構成について説明する。

【0049】

キャッシュタグ部40は、2ndキャッシュタグメモリ41と、キャッシュヒット判定回路42と、選択回路43とを有している。2ndキャッシュタグメモリ41は、キャッシュデータ部50に格納されているデータに対応付けられているタグを格納している。2ndキャッシュタグメモリ41に格納されているタグは、アドレスと称してもよい。

【0050】

ここで、2ndキャッシュタグメモリ41のデータ格納方式について、図3を用いて説明する。2ndキャッシュタグメモリ41のデータ格納方式には、セットアソシアティブ方式が採用されている。2ndキャッシュタグメモリ41においては、メモリが複数のウェイに分割される。さらに、それぞれのウェイは、複数のラインに分割される。タグは、それぞれのラインに格納される。図3においては、2ndキャッシュタグメモリ41は、ウェイ0及びウェイ1に分割されている例を示している。また、ウェイ0のラインNにアドレスAが格納されており、ウェイ1のラインNにアドレスBが格納されている例を示している。また、それぞれのアドレスには、フラグ(F)が関連付けられている。フラグは、関連付けられているアドレスが、過去にリプレース対象のアドレスとなっていたかを示している。フラグについては、後に詳述する。

【0051】

図2に戻り、キャッシュヒット判定回路42は、CPU10もしくはCPU20からメモリアクセスを受け取ると、メモリアクセスに含まれるタグと、2ndキャッシュタグメモリ41に格納されているタグとを比較する。キャッシュヒット判定回路42は、メモリアクセスに含まれるタグと、2ndキャッシュタグメモリ41に格納されているタグとが一致した場合、キャッシュヒットと判定し、メモリアクセスに含まれるタグと、2ndキャッシュタグメモリ41に格納されているタグとが一致しない場合、キャッシュミスと判定する。

【0052】

選択回路43は、リプレース部60から、リプレースされたキャッシュデータに関する情報を受け取ると、リプレースされたキャッシュデータに対応するタグをバッファ部70へ出力する。

【0053】

続いて、キャッシュデータ部50は、2ndキャッシュデータメモリ51と、選択回路52とを有している。2ndキャッシュデータメモリ51は、2ndキャッシュタグメモリ41に格納されているタグと対応付けられているキャッシュデータを格納している。2ndキャッシュデータメモリ51は、キャッシュヒット判定回路42からキャッシュヒットとの通知を受け取った場合、選択回路52を介して、該当するキャッシュデータをCPU10又は20へ出力する。

【0054】

2ndキャッシュデータメモリ51は、2ndキャッシュタグメモリ41と同様に、セットアソシアティブ方式が採用されている。図3に示されるように、2ndキャッシュデータメモリ51は、例えば、ウェイ0のラインNにデータAを格納し、ウェイ1のラインNにデータBを格納している。データAは、2ndキャッシュタグメモリ41のアドレスAと対応付けられている。データBは、2ndキャッシュタグメモリ41のアドレスBと対応付けられている。

【0055】

続いて、リプレース部60は、2ndLRUメモリ61と、リプレースウェイ判定回路62とを有している。2ndLRUメモリ61は、2ndキャッシュデータメモリ51の各ラインに格納されているウェイ0及びウェイ1のデータのうち、どちらが古いデータかを示している。つまり、2ndLRUメモリ61は、ウェイ0及びウェイ1のデータのうち、アクセスされたタイミングが古い方を示している。たとえば、2ndLRUメモリ61のラインNに、「0」が設定されている場合、データAは、データBがアクセスされたタイミングよりも後に、アクセスされていないことを示している。

【0056】

リプレースウェイ判定回路62は、2ndキャッシュタグメモリ41におけるフラグの情報と、2ndLRUメモリ61が保持する情報とを用いて、リプレース対象となるウェイを判定する。たとえば、2ndキャッシュタグメモリ41におけるウェイ0及び1のフラグが設定されていない場合、つまり、フラグに「0」が設定されている場合であって、2ndLRUメモリ61にウェイ0を示す「0」が設定されている場合、リプレース対象となるウェイは、ウェイ0と判定される。また、2ndキャッシュタグメモリ41において、ウェイ0のフラグに「1」が設定されており、2ndLRUメモリ61にウェイ0を示す「0」が設定されている場合、アドレスAにおけるデータのアクセス頻度が高いと考えられるため、2ndLRUメモリ61の設定にかかわらず、リプレース対象となるウェイは1と判定される。フラグの設定と、2ndLRUメモリ61の設定とから決定されるリプレース対象ウェイは、図4に示すとおりに決定される。

【0057】

図4の項番1及び2は、フラグ0及び1に0が設定されているため、リプレース対象となるウェイは、2ndLRUメモリの値に従って決定される。リプレース後は、リプレースされたウェイとは異なるウェイが2ndLRUメモリに設定される。項番3及び4は、ウェイ1のフラグに1が設定されているため、2ndLRUメモリの設定によらず、リプレース対象となるウェイは、ウェイ0となる。項番3において、リプレース後は、ウェイ1のフラグは1に設定されたまま、2ndLRUメモリの値が1に設定される。項番4において、リプレース後は、2ndLRUメモリの値によらずリプレース対象となるウェイが決定されたため、ウェイ1のフラグは0に設定され、さらに2ndLRUメモリは0に設定される。

【0058】

図4の項番5及び6は、ウェイ0のフラグが1に設定されているため、リプレース対象となるウェイは、2ndLRUメモリの値によらず、ウェイ1となる。項番5において、リプレース後は、2ndLRUメモリの値によらずリプレース対象となるウェイが決定されたため、ウェイ0のフラグは0に設定され、さらに2ndLRUメモリは1に設定される。項番6において、リプレース後は、ウェイ0のフラグは1に設定されたまま、2ndLRUメモリの値が0に設定される。

【0059】

図4の項番7及び8は、ウェイ0及び1のフラグに1が設定されているため、リプレース対象となるウェイは、2ndLRUメモリに従って決定される。リプレース後は、リプレース対象となったウェイのフラグが0に設定され、2ndLRUメモリは、リプレース対象となったウェイとは異なるウェイが設定される。

【0060】

図2に戻り、リプレースウェイ判定回路62は、リプレース対象となったウェイに関する情報を、選択回路43及び選択回路52へ出力する。選択回路52は、リプレース対象となったデータを、2ndキャッシュデータメモリ51から削除する。

【0061】

続いて、バッファ部70は、バッファ71と、ヒット判定回路72とを有している。バッファ71は、選択回路43から出力されるリプレース対象となったデータのタグ(アドレス)を格納する。

【0062】

ヒット判定回路72は、コア11もしくはコア21から発行されるメモリアクセスにより、メインメモリ80から新たに2ndキャッシュメモリ30に格納されるデータのタグと、バッファ71に格納されているタグとを比較する。ヒット判定回路72は、比較した結果を、2ndキャッシュタグメモリ41へ出力する。新たに2ndキャッシュメモリ30に格納されるデータのタグと、バッファ71に格納されているタグとが一致した場合、2ndキャッシュタグメモリ41は、該当するデータのフラグを「1」にセットする。新たに2ndキャッシュメモリ30に格納されるデータのタグと、バッファ71に格納されているタグとが一致しない場合、2ndキャッシュタグメモリ41は、該当するデータのフラグを「0」にセットする。

【0063】

続いて、図5及び図6を用いて本発明の実施の形態1にかかる1stキャッシュメモリ12及び22と、2ndキャッシュタグメモリ41とにデータを格納する動作について説明する。

【0064】

はじめに、ステップ1の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA0に対するリードリクエストを発行する。アドレスA0へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA0へのリードリクエストを発行する。アドレスA0へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80に対して、アドレスA0へのリードリクエストを発行する。

【0065】

メインメモリ80は、アドレスA0に格納されたデータA0を2ndキャッシュメモリ30に返却する。つまり、メインメモリ80は、アドレスA0に格納されたデータA0を2ndキャッシュメモリ30へ出力する。2ndキャッシュメモリ30に返却されたアドレスA0とデータA0とは、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。さらに、2ndLRUメモリ61のラインNには1が格納される。また、2ndキャッシュメモリ30は、返却されたアドレスA0とデータA0をCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、2ndキャッシュメモリ30と同様に、1stキャッシュタグメモリ(図示せず)と1stキャッシュデータメモリ(図示せず)のラインNのウェイ0にそれぞれアドレスA0とデータA0を格納する。さらに、1stキャッシュメモリ12は、コア11へデータA0を出力し、1stLRUメモリ(図示せず)のラインNに1が格納される。

【0066】

次に、ステップ2の動作を説明する。コア11は1stキャッシュメモリ12へアドレスA1に対するリードリクエストを発行する。アドレスA1へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA1へのリードリクエストを発行する。アドレスA1へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA1へのリードリクエストを発行する。

【0067】

メインメモリ80は、アドレスA1に格納されたデータA1を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30に返却されたアドレスA1とデータA1とは、それぞれラインNのウェイ1の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。さらに、2ndLRUメモリ61のラインNに、0が格納される。また、2ndキャッシュメモリ30は、返却されたアドレスA1とデータA1をCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、1stキャッシュタグメモリと1stキャッシュデータメモリのラインNのウェイ1にそれぞれアドレスA1とデータA1を格納する。さらに、1stキャッシュメモリ12は、コア11にデータA1を送出し1stLRUメモリのラインNに0が格納される。

【0068】

次に、ステップ3、ステップ4及びステップ5の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA0に対するリードリクエストを発行する。アドレスA0へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュヒットと判定すると、1stキャッシュデータメモリのラインNのウェイ0からデータA0を読み出しコア11へ出力する。また、1stLRUメモリのラインNに1が格納される。2ndキャッシュメモリ30には、リードリクエストは、発行されない。

【0069】

次に、ステップ6の動作を説明する。コア21は、1stキャッシュメモリ22へアドレスA2に対するリードリクエストを発行する。アドレスA2へのリードリクエストを受けた1stキャッシュメモリ22は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA2へのリードリクエストを発行する。アドレスA2へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA2へのリードリクエストを発行する。

【0070】

メインメモリ80は、アドレスA2に格納されたデータA2を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30がアドレスA2とデータA2を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出し、リプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、リプレースするウェイを0と決定する。リプレースウェイ判定回路62は、決定した情報を、選択回路43および選択回路52へ出力する。

【0071】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ0からアドレスA0のリプレースを実行する。リプレースされたアドレスA0は、バッファ71のエントリ0に格納される。選択回路52は、2ndキャッシュデータメモリ51のラインNのウェイ0からのデータA0のリプレースを実行する。リプレースが発生したため、リプレース部60は、CPU10およびCPU20に対してリプレースされたデータA0の無効化リクエストを発行する。1stキャッシュメモリ12は、1stキャッシュメモリに格納されているデータA0の無効化を行いリプレース部60へ報告する。1stキャッシュメモリ22は、対象となるデータがないので完了報告のみをリプレース部60に通知する。

【0072】

リプレース及び無効化が完了した後、メインメモリ80から返却されたアドレスA2とデータA2は、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。さらに、2ndLRUメモリ61のラインNに1が、格納される。また2ndキャッシュメモリ30は、返却されたアドレスA2とデータA2とをCPU20の1stキャッシュメモリ22へ出力する。1stキャッシュメモリ22は、1stキャッシュタグメモリと1stキャッシュデータメモリのラインNのウェイ0とにそれぞれアドレスA2とデータA2を格納する。さらに1stキャッシュメモリ22は、コア21にデータA2を出力する。1stLRUメモリのラインNには、1が格納される。

【0073】

次に、ステップ7の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA0に対するリードリクエストを発行する。アドレスA0へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA0へのリードリクエストを発行する。アドレスA0へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA0へのリードリクエストを発行する。

【0074】

メインメモリ80は、アドレスA0に格納されたデータA0を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30がアドレスA0とデータA0を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出しリプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、リプレースするウェイを1と決定する。リプレースウェイ判定回路62は、決定した情報を選択回路43および選択回路52へ出力する。

【0075】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ1からアドレスA1のリプレースを実行する。リプレースされたアドレスA1は、バッファ71のエントリ1に格納される。選択回路52は、2ndキャッシュデータメモリ51のラインNのウェイ1からデータA1のリプレースを実行する。リプレースが発生したのでリプレース部60は、CPU10およびCPU20にリプレースされたデータA1の無効化リクエストを発行する。1stキャッシュメモリ12は、格納しているデータA1の無効化を行いリプレース部321に報告する。1stキャッシュメモリ22は、対象となるデータがないので完了報告のみリプレース部60へ通知する。

【0076】

リプレース及び無効化が完了したら、メインメモリ80から返却されたアドレスA0とデータA0は、それぞれラインNのウェイ1の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。また、2ndLRUメモリ61のラインNに0が格納される。さらに、ヒット判定回路72は、2ndキャッシュタグメモリ41に新たに格納したアドレスA0とバッファ71に格納されているアドレスとを比較する。ヒット判定回路72は、新たに格納したアドレスA0と、バッファ71のエントリ0のアドレスとが一致するため、2ndキャッシュタグメモリ41のラインNのウェイ1に対応するフラグに1を格納する。また2ndキャッシュメモリ30は、返却されたアドレスA0とデータA0とをCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、1stキャッシュタグメモリと1stキャッシュデータメモリとのラインNのウェイ0にそれぞれアドレスA0とデータA0を格納する。さらに、1stキャッシュメモリ12は、コア11にデータA0を送出する。1stLRUメモリのラインNには、1が格納される。

【0077】

次に、ステップ8の動作を説明する。コア21は、1stキャッシュメモリ12へアドレスA3に対するリードリクエストを発行する。アドレスA3へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA3へのリードリクエストを発行する。アドレスA3へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA3へのリードリクエストを発行する。

【0078】

メインメモリ80は、アドレスA3に格納されたデータA3を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30がアドレスA3とデータA3を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出しリプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、リプレースするウェイを0と決定し選択回路43および選択回路52へ出力する。

【0079】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ0からアドレスA2のリプレースを実行する。リプレースされたアドレスA2は、バッファ71のエントリ2に格納される。選択回路52は、2ndキャッシュデータメモリ51のラインNのウェイ0からデータA2のリプレースを実行する。リプレースが発生したため、リプレース部60は、CPU10およびCPU20に対して、リプレースされたデータA2の無効化リクエストを発行する。1stキャッシュメモリ12は、対象となるデータがないので完了報告のみリプレース部60へ通知する。1stキャッシュメモリ22は、格納しているデータA2の無効化を行いリプレース部60に報告する。

【0080】

リプレース及び無効化が完了した後、メインメモリ80から出力されたアドレスA3とデータA3は、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。2ndLRUメモリ320のラインNには、1が格納される。また2ndキャッシュメモリ30は、返却されたアドレスA3とデータA3をCPU20の1stキャッシュメモリ22へ出力する。1stキャッシュメモリ22は、1stキャッシュタグメモリと1stキャッシュデータメモリとのラインNのウェイ1にそれぞれアドレスA3とデータA3とを格納する。さらに、1stキャッシュメモリ22は、コア21にデータA3を出力し1stLRUメモリのラインNに0を格納する。

【0081】

次に、ステップ9の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA4に対するリードリクエストを発行する。アドレスA4へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA4へのリードリクエストを発行する。アドレスA4へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA4へのリードリクエストを発行する。

【0082】

メインメモリ80は、アドレスA4に格納されたデータA4を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ装置30がアドレスA3とデータA3を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出しリプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、2ndキャッシュタグメモリ41のラインNのウェイ1のフラグが1になっていて、2ndLRUメモリ61のラインNのウェイ1が1になっているため図4の項番4に従い、リプレースするウェイを0と決定する。リプレースウェイ判定回路62は、決定した情報を選択回路43および選択回路52へ出力する。

【0083】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ0からアドレスA3のリプレースを実行する。リプレースされたアドレスA3は、バッファ71のエントリ3に格納される。選択回路311は、2ndキャッシュデータメモリ52のラインNのウェイ0からデータA3のリプレースを実行する。リプレースが発生したため、リプレース部60は、CPU10およびCPU20にリプレースされたデータA3の無効化リクエストを発行する。1stキャッシュメモリ12は、対象となるデータがないため完了報告のみリプレース部60へ通知する。1stキャッシュメモリ12は、1stキャッシュメモリの無効化を行いリプレース部60に報告する。

【0084】

リプレース及び無効化が完了したら、メインメモリ80から出力されたアドレスA4とデータA4とは、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。2ndLRUメモリ320のラインNには0が格納される。さらに、図4の項番4に従い、2ndキャッシュタグメモリ300のラインNのウェイ1に対応するフラグに0を格納する。また2ndキャッシュメモリ30は、返却されたアドレスA4とデータA4とをCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、1stキャッシュタグメモリと1stキャッシュデータメモリのラインNのウェイ1にそれぞれアドレスA4とデータA4を格納する。さらに、1stキャッシュメモリ12は、コア11にデータA4を送出し1stLRUメモリのラインNに0を格納する。

【0085】

以上説明したように、本発明の実施の形態1にかかるメモリシステムを用いることにより、2ndキャッシュメモリにおいてリプレース対象となるウェイを決定する際に、ウェイに格納されているデータが、過去にリプレース対象となったデータであるか否かを考慮して、リプレース対象となるウェイを決定することができる。過去にリプレースされて、再度2ndキャッシュメモリに登録されているデータのアクセス頻度は高いと考えられるため、このようなデータが再度リプレース対象となることを防止することができる。これより、アクセス頻度の高いデータがリプレース対象となる頻度を低下させることができる。

【0086】

上述の実施の形態では、本発明をハードウェアの構成として説明したが、本発明は、これに限定されるものではない。本発明は、図5及び図6において説明した1stキャッシュメモリ12及び22と、2ndキャッシュタグメモリ41とにデータを格納する処理及び1stキャッシュメモリ12及び22のデータを無効化する処理を、CPU(Central Processing Unit)にコンピュータプログラムを実行させることにより実現することも可能である。

【0087】

上述の例において、プログラムは、様々なタイプの非一時的なコンピュータ可読媒体(non-transitory computer readable medium)を用いて格納され、コンピュータに供給することができる。非一時的なコンピュータ可読媒体は、様々なタイプの実体のある記録媒体(tangible storage medium)を含む。非一時的なコンピュータ可読媒体の例は、磁気記録媒体(例えばフレキシブルディスク、磁気テープ、ハードディスクドライブ)、光磁気記録媒体(例えば光磁気ディスク)、CD−ROM(Read Only Memory)、CD−R、CD−R/W、半導体メモリ(例えば、マスクROM、PROM(Programmable ROM)、EPROM(Erasable PROM)、フラッシュROM、RAM(Random Access Memory))を含む。また、プログラムは、様々なタイプの一時的なコンピュータ可読媒体(transitory computer readable medium)によってコンピュータに供給されてもよい。一時的なコンピュータ可読媒体の例は、電気信号、光信号、及び電磁波を含む。一時的なコンピュータ可読媒体は、電線及び光ファイバ等の有線通信路、又は無線通信路を介して、プログラムをコンピュータに供給できる。

【0088】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、上述した例においては、1stキャッシュメモリがCPUに備えられている構成例について説明したが、1stキャッシュメモリは、CPUの外部に備えられてもよい。また、図4において、フラグとの関係においてリプレース対象となるウェイを決定するパターンについて説明したが、異なるパターンを設定してもよい。

【符号の説明】

【0089】

1 プロセッサ

2 上位キャッシュメモリ

3 下位キャッシュメモリ

4 リプレース部

10 CPU

11 コア

12 1stキャッシュメモリ

20 CPU

21 コア

22 1stキャッシュメモリ

30 2ndキャッシュメモリ

40 キャッシュタグ部

41 2ndキャッシュタグメモリ

42 キャッシュヒット判定回路

43 選択回路

50 キャッシュデータ部

51 2ndキャッシュデータメモリ

52 選択回路

60 リプレース部

61 2ndLRUメモリ

62 リプレースウェイ判定回路

70 バッファ部

71 バッファ

72 ヒット判定回路

80 メインメモリ

【技術分野】

【0001】

本発明はメモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラムに関し、特に階層化されたキャッシュメモリにより構成されるメモリシステム、そのメモリシステムにおけるキャッシュメモリ制御方法及びそのメモリシステムに用いられるメモリ制御方法に関する。

【背景技術】

【0002】

一般的に、CPU(Central Processing Unit)等のプロセッサの性能と比較して、記憶装置に用いられるメモリの性能が劣ることが知られている。このように、メモリの性能が劣っていることにより、プロセッサの性能を十分に発揮することができないことが問題となっていた。そこで、プロセッサとメモリとの性能差を補うために、キャッシュメモリを用いる構成が用いられている。キャッシュメモリは、メモリ(メインメモリ)よりも記憶容量は小さいが、処理能力が高い。そのため、プロセッサは、キャッシュメモリにアクセスすることにより、処理能力の向上を実現している。

【0003】

ここで、キャッシュメモリを用いるメモリシステムとして、ストアイン方式の階層キャッシュメモリを持つメモリシステムについて説明する。

【0004】

CPUがメインメモリのあるアドレスをリードするとメインメモリからデータが読み出される。さらに、上位キャッシュメモリおよび下位キャッシュメモリへデータが登録される。キャッシュメモリが無効化されるまではCPUが同一アドレスをリードすると上位キャッシュメモリまたは下位キャッシュメモリからキャッシュデータが読み出される。

【0005】

CPUがメインメモリのあるアドレスに対してリードを発行し、上位キャッシュメモリにキャッシュデータが登録されていれば、CPUは、上位キャッシュメモリからキャッシュデータを読み出す。そのため、同一アドレスのキャッシュデータが格納された下位キャッシュメモリのアクセス頻度が下がる。これにより、下位キャッシュメモリにおいて、上位キャッシュメモリに登録されているデータと同一のアドレスのキャッシュデータは、LRU(Least Recently Used)方式に従いリプレース対象になりやすい。

【0006】

ストアイン方式の階層キャッシュメモリをもつメモリシステムでは、キャッシュメモリが無効化されるまでは上位キャッシュメモリと下位キャッシュメモリとメインメモリとでデータが異なる事がある。そのため、キャッシュメモリのリプレースの際にはキャッシュコヒーレンシの保障のため、全キャッシュにおいて、対象となるアドレスのデータを無効化する必要がある。

【0007】

続いて、図7を用いて一般的に用いられるメモリシステムの構成について説明する。図7は、2ndキャッシュメモリ装置300の構成とCPU100及びCPU200と、メインメモリ400との関係を示している。本図に示したCPU100とCPU200とは、コア110又はコア210からメインメモリ400へのアクセス時間を短縮するために、上位キャッシュ又は下位キャッシュにアクセスを行う。上位キャッシュは、1stキャッシュメモリ装置100と1stキャッシュメモリ装置200とに相当する。下位キャッシュは、キャッシュタグ部310と、キャッシュデータ部320とを備えた2ndキャッシュメモリ装置300に相当する。

【0008】

CPU100内のコア110およびCPU200内のコア210は、1stキャッシュメモリ装置120および1stキャッシュメモリ装置220に対して、データのリードまたはライトに関するリクエストを発行する。CPU100内のコア110およびCPU200内のコア210は、1stキャッシュメモリ装置、1stキャッシュメモリ装置220、2ndキャッシュメモリ装置300またはメインメモリ400からデータのリード/ライトを行う。

【0009】

メインメモリ400は、大容量であってかつアクセス時間が2ndキャッシュタグメモリ311および2ndキャッシュデータメモリ321より遅いという特性を備えている。また2ndキャッシュメモリ装置300内の2ndキャッシュタグメモリ311および2ndキャッシュデータメモリ321は、CPU100内の1stキャッシュメモリ装置120およびCPU200内の1stキャッシュメモリ装置220より大容量であってかつアクセス時間が遅いという特性を備えている。

【0010】

ここで2ndキャッシュメモリ装置300は、データ格納方式としてセットアソシアティブ方式を採用している。このセットアソシアティブ方式は、図8に示すように2ndキャッシュメモリ(2ndキャッシュタグメモリ311および2ndキャッシュデータメモリ321を含む、以下にも同様に記載する。)を複数のウェイ(ウェイ0およびウェイ1)に分割し、各ウェイにおける決められたラインにデータを格納する方式である。同図に示した2ndキャッシュタグメモリ311においては、例えば、ウェイ0のラインNにアドレスAが格納されており、ウェイ1のラインNにアドレスBが格納されている。また、2ndキャッシュデータメモリ321には、例えばウェイ0のラインにデータAが格納されており、ウェイ1のラインNにデータBが格納されている。2ndキャッシュタグメモリ311と2ndキャッシュデータメモリ321とは、アドレスAとデータAとが、アドレスBとデータBとがそれぞれ一対一で対応している。

【0011】

図7に戻り、2ndキャッシュタグ部310は、CPU100およびCPU200からのリクエストを受け付ける。また、2ndキャッシュタグ部310は、2ndキャッシュタグメモリ311とキャッシュヒット判定回路312と選択回路313とから構成されている。

【0012】

2ndキャッシュタグメモリ311は、2ndキャッシュデータメモリ320に格納されているデータに対応するアドレス(タグ)を格納している。キャッシュヒット判定回路312は、CPU100およびCPU200から出力されるアドレスと2ndキャッシュタグメモリ311に格納されているアドレスとを比較し、両者が一致した場合、ヒット判定結果を「キャッシュヒット」とする。「キャッシュヒット」の場合には、当該アドレスに対応するデータが2ndキャッシュデータメモリ321に存在する事を意味する。一方、CPU100およびCPU200から出力されるアドレスと2ndキャッシュタグメモリ311に格納されているアドレスとが不一致である場合、キャッシュヒット判定回路312はヒット判定結果を「キャッシュミス」とする。

【0013】

「キャッシュミス」の場合には、当該アドレスに対応するデータが2ndキャッシュデータメモリ321に存在しない事を意味する。「キャッシュミス」の場合には、メインメモリ400から当該アドレスに対応するデータが読み出され、2ndキャッシュデータメモリ321において当該データがリプレースされた後、CPU100およびCPU200へ当該アドレスに対応するデータが出力される。

【0014】

ここで、リプレースする場合には、2ndキャッシュデータメモリ321のウェイに格納されているデータを追い出す必要がある。そして、上記ウェイにメインメモリ400から出力されたデータが格納される。ここで、一般的な2ndキャッシュメモリ装置300において、複数のウェイの中からリプレース対象のウェイ(以下、リプレースウェイとする)を選択するアルゴリズムとしては、最も使用されていなかったデータが格納されたウェイを選択するというLRU方式が採用されている。

【0015】

図7に戻り、キャッシュヒット判定回路312は、ヒット判定結果を2ndキャッシュデータメモリ321及びリプレース部330の2ndLRUメモリ331へ通知する。

【0016】

リプレース部330は、ヒット判定結果が「キャッシュミス」である場合に2ndキャッシュデータメモリ321においてリプレースすべきウェイを選択する機能を備えている。リプレース部330は、2ndLRUメモリ331およびリプレースウェイ判定回路332から構成されている。2ndLRUメモリ331は、一つの入力ポートを備えており、2ndキャッシュデータメモリ321においてデータをリプレースする場合に、前述したLRU方式により選択されたリプレースウェイを表すリプレースウェイ情報を格納している。具体的には、図8に示すように、2ndLRUメモリ331にはラインごとにリプレースウェイの番号に対応するリプレースウェイ情報が格納されている。同図ではラインNに、リプレースウェイがウェイ0であることを示すリプレースウェイ情報が格納されている。つまり、2ndキャッシュデータメモリ321のラインNにおいてはウェイ0に格納されているデータAが最も使用もしくはアクセスされていないデータである。

【0017】

図7に戻り、リプレースウェイ判定回路332は、2ndキャッシュメモリにおける複数のウェイの中から、リプレースウェイを選択する。リプレースウェイ判定回路332は、2ndLRUメモリ320を参照してLRU方式によりリプレースウェイを選択する。リプレースウェイ判定回路332は、リプレースウェイを選択した後、リプレース要求を選択回路313及び322へ発行する。

【0018】

メインメモリ400は、CPU100又は200からリクエストされたアドレスに対応するデータを読み出し、これを2ndキャッシュデータメモリ321のリプレースウェイに格納する。このようにして、メモリシステムは、リプレース処理を実行する。

【0019】

1stキャッシュメモリ装置120および1stキャッシュメモリ装置220についても2ndキャッシュメモリ装置3と同様にキャッシュヒット判定を行い、「キャッシュヒット」したときは1stキャッシュメモリよりデータが読み出され、「キャッシュミス」したときは2ndキャッシュメモリにリクエストを発行する。

【0020】

ストアイン方式の階層キャッシュメモリをもつメモリシステムにおいては、コア110およびコア210からのリード/ライトにより1stキャッシュまたは2ndキャッシュの内容が変更されても無効化(インバリデート)されるまではメインメモリ400と1stキャッシュメモリ装置120内のキャッシュメモリおよび1stキャッシュメモリ装置220内のキャッシュメモリおよび2ndキャッシュメモリの内容が異なる場合がある。そしてキャッシュコヒーレンシを保障するためには、1stキャッシュまたは2ndキャッシュのリプレースの際には、当該アドレスに対応する両キャッシュのキャッシュデータを無効化する必要がある。

【0021】

リプレース部330は、1stキャッシュメモリ装置120および1stキャッシュメモリ装置220に対して当該アドレスに対する無効化要求を発行する。要求を受けたCPU100の1stキャッシュメモリ装置120およびCPU200の1stキャッシュメモリ装置220は、該当するアドレスのデータを無効化し、リプレース部330へ報告する。

【0022】

次に、コア110およびコア210から出力されるリクエストに対し、1stキャッシュメモリ装置120、1stキャッシュメモリ装置220及び2ndキャッシュメモリ装置300の動作について、図9及び図10を用いて説明する。

【0023】

ステップ1において、コア110がメインメモリ400のアドレスA0に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、1stキャッシュメモリ装置120内のキャッシュデータメモリのウェイ0および2ndキャッシュデータメモリ321のウェイ0にデータA0が格納される。さらに、1stキャッシュメモリ装置120内の1stLRUメモリおよび2ndLRUメモリ331にウェイ1を示す1が格納される。

【0024】

ステップ2において、コア110がメインメモリ400のアドレスA1に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、1stキャッシュメモリ装置120内のキャッシュデータメモリのウェイ1および2ndキャッシュデータメモリ321のウェイ1にデータA1が格納される。さらに、1stキャッシュメモリ装置120内の1stLRUメモリおよび2ndLRUメモリ331にウェイ0を示す0が格納される。

【0025】

ステップ3、ステップ4及びステップ5において、コア110がメインメモリ400のアドレスA0に対してリクエストを発行すると1stキャッシュメモリ装置120において「キャッシュヒット」と判定され、データA0を読み出す。さらに、LRU方式により1stキャッシュメモリ装置120内の1stLRUメモリに1が格納される。

【0026】

ステップ6において、コア210がメインメモリ400のアドレスA2に対してリクエストを発行すると1stキャッシュメモリ装置220および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ310のウェイ0よりデータA0がリプレースされる。さらに、1stキャッシュメモリ装置120のウェイ0にデータA0が格納されているため、キャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置220のキャッシュデータメモリのウェイ0および2ndキャッシュデータメモリ321のウェイ0にデータA2が格納される。また、1stキャッシュメモリ装置220内の1stLRUメモリおよび2ndLRUメモリ331に1が格納される。1stキャッシュメモリ装置120内の1stLRUメモリには、0が格納される。

【0027】

ステップ7において、コア110がメインメモリ400のアドレスA0に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ310のウェイ1よりデータA1がリプレースされる。さらに、1stキャッシュメモリ装置120のウェイ1にデータA1が格納されているためキャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置120のキャッシュデータメモリのウェイ0および2ndキャッシュデータメモリ321のウェイ0にデータA0が格納される。また、1stキャッシュメモリ装置120内の1stLRUメモリに1が格納され、2ndLRUメモリ331に0が格納される。

【0028】

ステップ8において、コア210がメインメモリ400のアドレスA3に対してリクエストを発行すると1stキャッシュメモリ装置220および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ321のウェイ0よりデータA2がリプレースされる。さらに、1stキャッシュメモリ装置220のウェイ0にデータA2が格納されているためキャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置220のキャッシュデータメモリのウェイ1および2ndキャッシュデータメモリ321のウェイ0にデータA3が格納される。また、1stキャッシュメモリ装置220内の1stLRUメモリに0が格納され、2ndLRUメモリ331に1が格納される。

【0029】

ステップ9において、コア110がメインメモリ400のアドレスA4に対してリクエストを発行すると1stキャッシュメモリ装置120および2ndキャッシュメモリ装置300において「キャッシュミス」と判定される。そのため、LRU方式により2ndキャッシュデータメモリ321のウェイ1よりデータA0がリプレースされる。さらに、1stキャッシュメモリ装置120のウェイ0にデータA0が格納されているためキャッシュコヒーレンシ保障のためこのデータを無効化する。さらに、メインメモリ400より1stキャッシュメモリ装置120のキャッシュデータメモリのウェイ1および2ndキャッシュデータメモリ321のウェイ1にデータA4が格納される。また、1stキャッシュメモリ装置120内の1stLRUメモリに0が格納され、2ndLRUメモリ331に0が格納される。

【先行技術文献】

【特許文献】

【0030】

【特許文献1】特開2000−200221号公報

【特許文献2】特開平06−266623号公報

【発明の概要】

【発明が解決しようとする課題】

【0031】

しかし、上述したストアイン方式の階層キャッシュを持つメモリシステムにおいて、アクセス頻度の高いアドレスは常に上位キャッシュメモリにヒットし、下位キャッシュメモリではアクセス頻度が低くなる。そのため、上位キャッシュメモリにおいてアクセス頻度の高いアドレスは、下位キャッシュメモリにおいてLRU方式によりリプレース対象になりやすい。その結果、リプレース時にコヒーレンシ保障のため上位キャッシュメモリにおけるアドレスも無効化対象となるため、アクセス頻度の高いアドレスにアクセスするために、メインメモリに再度アクセスする必要があり、性能が悪化するという問題がある。

【0032】

アクセス頻度の高いアドレスに対しリプレースを行わないようにする方法として、特許文献1に記載されているように、キャッシュメモリの中に書き換え不可のエリアを設ける、という方法がある。また、特許文献2にも、追い出し禁止フラグを設けて、追い出し禁止フラグがセットされたブロックは、リプレース対象となっても、リプレースされないように制御される、という内容が開示されている。しかし、常にアクセス頻度の高いアドレスに対しては、上述した方法は有効であるが、処理に応じてアクセス頻度が変わるアドレスに対しては有効ではない。

【0033】

本発明は、このような課題を解決するためになされたものであり、ストアイン方式の階層キャッシュメモリを持つメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラムを提供することを目的とする。

【課題を解決するための手段】

【0034】

本発明の第1の態様にかかるメモリシステムは、第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、前記第2のキャッシュメモリに格納されているキャッシュデータのうち前記リプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部と、を備えるものである。

【0035】

本発明の第2の態様にかかるキャッシュメモリ制御方法は、第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるキャッシュメモリ制御方法であって、前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象キャッシュデータと同一のキャッシュデータを無効化するものである。

【0036】

本発明の第3の態様にかかるメモリ制御プログラムは、第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるメモリ制御プログラムであって、前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定するステップと、前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象データと同一のデータを無効化するステップと、をコンピュータに実行させるものである。

【発明の効果】

【0037】

本発明を用いることにより、ストアイン方式の階層キャッシュメモリを持つメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラムを提供することができる。

【図面の簡単な説明】

【0038】

【図1】実施の形態1にかかるメモリシステムの構成図である。

【図2】実施の形態1にかかるメモリシステムの構成図である。

【図3】実施の形態1にかかる2ndキャッシュメモリのデータ格納方式を説明する図である。

【図4】実施の形態1にかかるフラグの値と、選択されるリプレースウェイの関係を示す図である。

【図5】実施の形態1にかかるキャッシュメモリへデータが格納される状態を示す図である。

【図6】実施の形態1にかかるキャッシュメモリへデータが格納される状態を示す図である。

【図7】一般的なメモリシステムの構成図である。

【図8】一般的なメモリシステムにおけるデータ格納方式を説明する図である。

【図9】一般的なキャッシュメモリへデータが格納される状態を示す図である。

【図10】一般的なキャッシュメモリへデータが格納される状態を示す図である。

【発明を実施するための形態】

【0039】

(実施の形態1)

以下、図面を参照して本発明の実施の形態について説明する。図1を用いて本発明の実施の形態1にかかるメモリシステムの構成例について説明する。図1におけるメモリシステムは、プロセッサ1と、上位キャッシュメモリ2と、下位キャッシュメモリ3と、リプレース部4と、を備えている。

【0040】

プロセッサ1は、コンピュータもしくは回路等を制御するために用いられ、例えば、CPU(Central Processing Unit)、MPU(Micro Processing Unit)等により構成される。プロセッサ1は、メインメモリ(図示せず)に格納されているデータにアクセスする際に、高速処理を実現するために、処理速度がメインメモリよりも高いキャッシュメモリへアクセスする。

【0041】

キャッシュメモリは、上位キャッシュメモリ2と下位キャッシュメモリ3とを有しており、階層的に構成されている。プロセッサ1は、優先的に上位キャッシュメモリ2へアクセスし、上位キャッシュメモリ2に必要とするデータが存在しない場合、下位キャッシュメモリ3へアクセスする。上位キャッシュメモリ2及び下位キャッシュメモリ3に、プロセッサ1からのアクセス対象となるデータが存在しない場合、プロセッサ1は、メインメモリからデータを取得する。また、上位キャッシュメモリ2及び下位キャッシュメモリ3は、プロセッサ1がメインメモリから取得したデータを格納(キャッシュ)する。上位キャッシュメモリ2又は下位キャッシュメモリ3は、メインメモリよりも記憶容量が小さい。そのため、メインメモリから新たにデータを取得して格納する場合、上位キャッシュメモリ2又は下位キャッシュメモリ3は、すでに格納しているデータ(キャッシュデータ)を削除して、メインメモリから新たなデータを取得する。キャッシュメモリにおけるこのような動作を、キャッシュデータのリプレースと称する。

【0042】

下位キャッシュメモリ3においてキャッシュデータのリプレースを行う場合に、リプレース部4は、下位キャッシュメモリ3に格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いてリプレース対象キャッシュデータを決定し、上位キャッシュメモリ2に格納されており、下位キャッシュメモリ3におけるリプレース対象のキャッシュデータと同一のキャッシュデータを無効化する。

【0043】

リプレース部4は、上位キャッシュメモリ2と下位キャッシュメモリ3とのキャッシュコヒーレンシの保障のため、下位キャッシュメモリ3においてリプレースされたデータと同一のデータを、上位キャッシュメモリ2において無効化する。

【0044】

以上説明したように、図1におけるメモリシステムを用いることにより、リプレース部4は、下位キャッシュメモリ3に格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定することができる。つまり、過去にリプレース対象となり、再度下位キャッシュメモリ3に格納されているデータは、プロセッサ1からのアクセス頻度が高いため、このようなデータをリプレース対象外、もしくはリプレースする優先順位を下げることにより、上位キャッシュメモリ2においてもキャッシュデータは有効に存在することになる。その結果、アクセス頻度が高いキャッシュデータを、上位キャッシュメモリ2に格納しておくことができるため、プロセッサ1が、メインメモリへアクセスすることによるアクセス性能の低下を防止することができる。

【0045】

続いて、図2を用いて本発明の実施の形態1にかかるメモリシステムの詳細な構成例について説明する。図2におけるメモリシステムは、CPU10及び20と、2ndキャッシュメモリ30と、メインメモリ80と、を備えている。

【0046】

CPU10は、コア11と、1stキャッシュメモリ12とを有している。コア11は、メモリアクセスを発行し、1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、コア11から受けたメモリアクセスに対応するキャッシュデータが1stキャッシュメモリ12に格納されているか判定する。1stキャッシュメモリ12は、キャッシュヒットと判定したらキャッシュデータをコア11に返却する。1stキャッシュメモリ12は、キャッシュミスと判定したらメモリアクセスを発行し、2ndキャッシュメモリ30へ出力する。また、1stキャッシュメモリ12は、2ndキャッシュメモリ30より無効化要求を受け取ったら、対象となるキャッシュデータを無効化する。さらに、1stキャッシュメモリ12は、コア11がアクセスを希望するデータであって、2ndキャッシュメモリ30から出力されたデータを格納する。

【0047】

CPU20は、コア21と、1stキャッシュメモリ22とを有している。CPU20における構成は、CPU10と同様であるため、詳細な説明を省略する。

【0048】

2ndキャッシュメモリ30は、キャッシュタグ部40と、キャッシュデータ部50と、リプレース部60と、バッファ部70と、を有している。以下に、それぞれの構成について説明する。

【0049】

キャッシュタグ部40は、2ndキャッシュタグメモリ41と、キャッシュヒット判定回路42と、選択回路43とを有している。2ndキャッシュタグメモリ41は、キャッシュデータ部50に格納されているデータに対応付けられているタグを格納している。2ndキャッシュタグメモリ41に格納されているタグは、アドレスと称してもよい。

【0050】

ここで、2ndキャッシュタグメモリ41のデータ格納方式について、図3を用いて説明する。2ndキャッシュタグメモリ41のデータ格納方式には、セットアソシアティブ方式が採用されている。2ndキャッシュタグメモリ41においては、メモリが複数のウェイに分割される。さらに、それぞれのウェイは、複数のラインに分割される。タグは、それぞれのラインに格納される。図3においては、2ndキャッシュタグメモリ41は、ウェイ0及びウェイ1に分割されている例を示している。また、ウェイ0のラインNにアドレスAが格納されており、ウェイ1のラインNにアドレスBが格納されている例を示している。また、それぞれのアドレスには、フラグ(F)が関連付けられている。フラグは、関連付けられているアドレスが、過去にリプレース対象のアドレスとなっていたかを示している。フラグについては、後に詳述する。

【0051】

図2に戻り、キャッシュヒット判定回路42は、CPU10もしくはCPU20からメモリアクセスを受け取ると、メモリアクセスに含まれるタグと、2ndキャッシュタグメモリ41に格納されているタグとを比較する。キャッシュヒット判定回路42は、メモリアクセスに含まれるタグと、2ndキャッシュタグメモリ41に格納されているタグとが一致した場合、キャッシュヒットと判定し、メモリアクセスに含まれるタグと、2ndキャッシュタグメモリ41に格納されているタグとが一致しない場合、キャッシュミスと判定する。

【0052】

選択回路43は、リプレース部60から、リプレースされたキャッシュデータに関する情報を受け取ると、リプレースされたキャッシュデータに対応するタグをバッファ部70へ出力する。

【0053】

続いて、キャッシュデータ部50は、2ndキャッシュデータメモリ51と、選択回路52とを有している。2ndキャッシュデータメモリ51は、2ndキャッシュタグメモリ41に格納されているタグと対応付けられているキャッシュデータを格納している。2ndキャッシュデータメモリ51は、キャッシュヒット判定回路42からキャッシュヒットとの通知を受け取った場合、選択回路52を介して、該当するキャッシュデータをCPU10又は20へ出力する。

【0054】

2ndキャッシュデータメモリ51は、2ndキャッシュタグメモリ41と同様に、セットアソシアティブ方式が採用されている。図3に示されるように、2ndキャッシュデータメモリ51は、例えば、ウェイ0のラインNにデータAを格納し、ウェイ1のラインNにデータBを格納している。データAは、2ndキャッシュタグメモリ41のアドレスAと対応付けられている。データBは、2ndキャッシュタグメモリ41のアドレスBと対応付けられている。

【0055】

続いて、リプレース部60は、2ndLRUメモリ61と、リプレースウェイ判定回路62とを有している。2ndLRUメモリ61は、2ndキャッシュデータメモリ51の各ラインに格納されているウェイ0及びウェイ1のデータのうち、どちらが古いデータかを示している。つまり、2ndLRUメモリ61は、ウェイ0及びウェイ1のデータのうち、アクセスされたタイミングが古い方を示している。たとえば、2ndLRUメモリ61のラインNに、「0」が設定されている場合、データAは、データBがアクセスされたタイミングよりも後に、アクセスされていないことを示している。

【0056】

リプレースウェイ判定回路62は、2ndキャッシュタグメモリ41におけるフラグの情報と、2ndLRUメモリ61が保持する情報とを用いて、リプレース対象となるウェイを判定する。たとえば、2ndキャッシュタグメモリ41におけるウェイ0及び1のフラグが設定されていない場合、つまり、フラグに「0」が設定されている場合であって、2ndLRUメモリ61にウェイ0を示す「0」が設定されている場合、リプレース対象となるウェイは、ウェイ0と判定される。また、2ndキャッシュタグメモリ41において、ウェイ0のフラグに「1」が設定されており、2ndLRUメモリ61にウェイ0を示す「0」が設定されている場合、アドレスAにおけるデータのアクセス頻度が高いと考えられるため、2ndLRUメモリ61の設定にかかわらず、リプレース対象となるウェイは1と判定される。フラグの設定と、2ndLRUメモリ61の設定とから決定されるリプレース対象ウェイは、図4に示すとおりに決定される。

【0057】

図4の項番1及び2は、フラグ0及び1に0が設定されているため、リプレース対象となるウェイは、2ndLRUメモリの値に従って決定される。リプレース後は、リプレースされたウェイとは異なるウェイが2ndLRUメモリに設定される。項番3及び4は、ウェイ1のフラグに1が設定されているため、2ndLRUメモリの設定によらず、リプレース対象となるウェイは、ウェイ0となる。項番3において、リプレース後は、ウェイ1のフラグは1に設定されたまま、2ndLRUメモリの値が1に設定される。項番4において、リプレース後は、2ndLRUメモリの値によらずリプレース対象となるウェイが決定されたため、ウェイ1のフラグは0に設定され、さらに2ndLRUメモリは0に設定される。

【0058】

図4の項番5及び6は、ウェイ0のフラグが1に設定されているため、リプレース対象となるウェイは、2ndLRUメモリの値によらず、ウェイ1となる。項番5において、リプレース後は、2ndLRUメモリの値によらずリプレース対象となるウェイが決定されたため、ウェイ0のフラグは0に設定され、さらに2ndLRUメモリは1に設定される。項番6において、リプレース後は、ウェイ0のフラグは1に設定されたまま、2ndLRUメモリの値が0に設定される。

【0059】

図4の項番7及び8は、ウェイ0及び1のフラグに1が設定されているため、リプレース対象となるウェイは、2ndLRUメモリに従って決定される。リプレース後は、リプレース対象となったウェイのフラグが0に設定され、2ndLRUメモリは、リプレース対象となったウェイとは異なるウェイが設定される。

【0060】

図2に戻り、リプレースウェイ判定回路62は、リプレース対象となったウェイに関する情報を、選択回路43及び選択回路52へ出力する。選択回路52は、リプレース対象となったデータを、2ndキャッシュデータメモリ51から削除する。

【0061】

続いて、バッファ部70は、バッファ71と、ヒット判定回路72とを有している。バッファ71は、選択回路43から出力されるリプレース対象となったデータのタグ(アドレス)を格納する。

【0062】

ヒット判定回路72は、コア11もしくはコア21から発行されるメモリアクセスにより、メインメモリ80から新たに2ndキャッシュメモリ30に格納されるデータのタグと、バッファ71に格納されているタグとを比較する。ヒット判定回路72は、比較した結果を、2ndキャッシュタグメモリ41へ出力する。新たに2ndキャッシュメモリ30に格納されるデータのタグと、バッファ71に格納されているタグとが一致した場合、2ndキャッシュタグメモリ41は、該当するデータのフラグを「1」にセットする。新たに2ndキャッシュメモリ30に格納されるデータのタグと、バッファ71に格納されているタグとが一致しない場合、2ndキャッシュタグメモリ41は、該当するデータのフラグを「0」にセットする。

【0063】

続いて、図5及び図6を用いて本発明の実施の形態1にかかる1stキャッシュメモリ12及び22と、2ndキャッシュタグメモリ41とにデータを格納する動作について説明する。

【0064】

はじめに、ステップ1の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA0に対するリードリクエストを発行する。アドレスA0へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA0へのリードリクエストを発行する。アドレスA0へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80に対して、アドレスA0へのリードリクエストを発行する。

【0065】

メインメモリ80は、アドレスA0に格納されたデータA0を2ndキャッシュメモリ30に返却する。つまり、メインメモリ80は、アドレスA0に格納されたデータA0を2ndキャッシュメモリ30へ出力する。2ndキャッシュメモリ30に返却されたアドレスA0とデータA0とは、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。さらに、2ndLRUメモリ61のラインNには1が格納される。また、2ndキャッシュメモリ30は、返却されたアドレスA0とデータA0をCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、2ndキャッシュメモリ30と同様に、1stキャッシュタグメモリ(図示せず)と1stキャッシュデータメモリ(図示せず)のラインNのウェイ0にそれぞれアドレスA0とデータA0を格納する。さらに、1stキャッシュメモリ12は、コア11へデータA0を出力し、1stLRUメモリ(図示せず)のラインNに1が格納される。

【0066】

次に、ステップ2の動作を説明する。コア11は1stキャッシュメモリ12へアドレスA1に対するリードリクエストを発行する。アドレスA1へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA1へのリードリクエストを発行する。アドレスA1へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA1へのリードリクエストを発行する。

【0067】

メインメモリ80は、アドレスA1に格納されたデータA1を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30に返却されたアドレスA1とデータA1とは、それぞれラインNのウェイ1の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。さらに、2ndLRUメモリ61のラインNに、0が格納される。また、2ndキャッシュメモリ30は、返却されたアドレスA1とデータA1をCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、1stキャッシュタグメモリと1stキャッシュデータメモリのラインNのウェイ1にそれぞれアドレスA1とデータA1を格納する。さらに、1stキャッシュメモリ12は、コア11にデータA1を送出し1stLRUメモリのラインNに0が格納される。

【0068】

次に、ステップ3、ステップ4及びステップ5の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA0に対するリードリクエストを発行する。アドレスA0へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュヒットと判定すると、1stキャッシュデータメモリのラインNのウェイ0からデータA0を読み出しコア11へ出力する。また、1stLRUメモリのラインNに1が格納される。2ndキャッシュメモリ30には、リードリクエストは、発行されない。

【0069】

次に、ステップ6の動作を説明する。コア21は、1stキャッシュメモリ22へアドレスA2に対するリードリクエストを発行する。アドレスA2へのリードリクエストを受けた1stキャッシュメモリ22は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA2へのリードリクエストを発行する。アドレスA2へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA2へのリードリクエストを発行する。

【0070】

メインメモリ80は、アドレスA2に格納されたデータA2を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30がアドレスA2とデータA2を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出し、リプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、リプレースするウェイを0と決定する。リプレースウェイ判定回路62は、決定した情報を、選択回路43および選択回路52へ出力する。

【0071】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ0からアドレスA0のリプレースを実行する。リプレースされたアドレスA0は、バッファ71のエントリ0に格納される。選択回路52は、2ndキャッシュデータメモリ51のラインNのウェイ0からのデータA0のリプレースを実行する。リプレースが発生したため、リプレース部60は、CPU10およびCPU20に対してリプレースされたデータA0の無効化リクエストを発行する。1stキャッシュメモリ12は、1stキャッシュメモリに格納されているデータA0の無効化を行いリプレース部60へ報告する。1stキャッシュメモリ22は、対象となるデータがないので完了報告のみをリプレース部60に通知する。

【0072】

リプレース及び無効化が完了した後、メインメモリ80から返却されたアドレスA2とデータA2は、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。さらに、2ndLRUメモリ61のラインNに1が、格納される。また2ndキャッシュメモリ30は、返却されたアドレスA2とデータA2とをCPU20の1stキャッシュメモリ22へ出力する。1stキャッシュメモリ22は、1stキャッシュタグメモリと1stキャッシュデータメモリのラインNのウェイ0とにそれぞれアドレスA2とデータA2を格納する。さらに1stキャッシュメモリ22は、コア21にデータA2を出力する。1stLRUメモリのラインNには、1が格納される。

【0073】

次に、ステップ7の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA0に対するリードリクエストを発行する。アドレスA0へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA0へのリードリクエストを発行する。アドレスA0へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA0へのリードリクエストを発行する。

【0074】

メインメモリ80は、アドレスA0に格納されたデータA0を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30がアドレスA0とデータA0を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出しリプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、リプレースするウェイを1と決定する。リプレースウェイ判定回路62は、決定した情報を選択回路43および選択回路52へ出力する。

【0075】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ1からアドレスA1のリプレースを実行する。リプレースされたアドレスA1は、バッファ71のエントリ1に格納される。選択回路52は、2ndキャッシュデータメモリ51のラインNのウェイ1からデータA1のリプレースを実行する。リプレースが発生したのでリプレース部60は、CPU10およびCPU20にリプレースされたデータA1の無効化リクエストを発行する。1stキャッシュメモリ12は、格納しているデータA1の無効化を行いリプレース部321に報告する。1stキャッシュメモリ22は、対象となるデータがないので完了報告のみリプレース部60へ通知する。

【0076】

リプレース及び無効化が完了したら、メインメモリ80から返却されたアドレスA0とデータA0は、それぞれラインNのウェイ1の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。また、2ndLRUメモリ61のラインNに0が格納される。さらに、ヒット判定回路72は、2ndキャッシュタグメモリ41に新たに格納したアドレスA0とバッファ71に格納されているアドレスとを比較する。ヒット判定回路72は、新たに格納したアドレスA0と、バッファ71のエントリ0のアドレスとが一致するため、2ndキャッシュタグメモリ41のラインNのウェイ1に対応するフラグに1を格納する。また2ndキャッシュメモリ30は、返却されたアドレスA0とデータA0とをCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、1stキャッシュタグメモリと1stキャッシュデータメモリとのラインNのウェイ0にそれぞれアドレスA0とデータA0を格納する。さらに、1stキャッシュメモリ12は、コア11にデータA0を送出する。1stLRUメモリのラインNには、1が格納される。

【0077】

次に、ステップ8の動作を説明する。コア21は、1stキャッシュメモリ12へアドレスA3に対するリードリクエストを発行する。アドレスA3へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA3へのリードリクエストを発行する。アドレスA3へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA3へのリードリクエストを発行する。

【0078】

メインメモリ80は、アドレスA3に格納されたデータA3を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ30がアドレスA3とデータA3を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出しリプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、リプレースするウェイを0と決定し選択回路43および選択回路52へ出力する。

【0079】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ0からアドレスA2のリプレースを実行する。リプレースされたアドレスA2は、バッファ71のエントリ2に格納される。選択回路52は、2ndキャッシュデータメモリ51のラインNのウェイ0からデータA2のリプレースを実行する。リプレースが発生したため、リプレース部60は、CPU10およびCPU20に対して、リプレースされたデータA2の無効化リクエストを発行する。1stキャッシュメモリ12は、対象となるデータがないので完了報告のみリプレース部60へ通知する。1stキャッシュメモリ22は、格納しているデータA2の無効化を行いリプレース部60に報告する。

【0080】

リプレース及び無効化が完了した後、メインメモリ80から出力されたアドレスA3とデータA3は、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。2ndLRUメモリ320のラインNには、1が格納される。また2ndキャッシュメモリ30は、返却されたアドレスA3とデータA3をCPU20の1stキャッシュメモリ22へ出力する。1stキャッシュメモリ22は、1stキャッシュタグメモリと1stキャッシュデータメモリとのラインNのウェイ1にそれぞれアドレスA3とデータA3とを格納する。さらに、1stキャッシュメモリ22は、コア21にデータA3を出力し1stLRUメモリのラインNに0を格納する。

【0081】

次に、ステップ9の動作を説明する。コア11は、1stキャッシュメモリ12へアドレスA4に対するリードリクエストを発行する。アドレスA4へのリードリクエストを受けた1stキャッシュメモリ12は、キャッシュミスと判定すると2ndキャッシュメモリ30にアドレスA4へのリードリクエストを発行する。アドレスA4へのリードリクエストを受けた2ndキャッシュメモリ30は、キャッシュミスと判定するとメインメモリ80にアドレスA4へのリードリクエストを発行する。

【0082】

メインメモリ80は、アドレスA4に格納されたデータA4を2ndキャッシュメモリ30に返却する。2ndキャッシュメモリ装置30がアドレスA3とデータA3を受け付けると、リプレース部60は、2ndLRUメモリ61のラインNに格納された値を読み出しリプレースウェイ判定回路62へ出力する。リプレースウェイ判定回路62は、2ndキャッシュタグメモリ41のラインNのウェイ1のフラグが1になっていて、2ndLRUメモリ61のラインNのウェイ1が1になっているため図4の項番4に従い、リプレースするウェイを0と決定する。リプレースウェイ判定回路62は、決定した情報を選択回路43および選択回路52へ出力する。

【0083】

選択回路43は、2ndキャッシュタグメモリ41のラインNのウェイ0からアドレスA3のリプレースを実行する。リプレースされたアドレスA3は、バッファ71のエントリ3に格納される。選択回路311は、2ndキャッシュデータメモリ52のラインNのウェイ0からデータA3のリプレースを実行する。リプレースが発生したため、リプレース部60は、CPU10およびCPU20にリプレースされたデータA3の無効化リクエストを発行する。1stキャッシュメモリ12は、対象となるデータがないため完了報告のみリプレース部60へ通知する。1stキャッシュメモリ12は、1stキャッシュメモリの無効化を行いリプレース部60に報告する。

【0084】

リプレース及び無効化が完了したら、メインメモリ80から出力されたアドレスA4とデータA4とは、それぞれラインNのウェイ0の2ndキャッシュタグメモリ41および2ndキャッシュデータメモリ51に格納される。2ndLRUメモリ320のラインNには0が格納される。さらに、図4の項番4に従い、2ndキャッシュタグメモリ300のラインNのウェイ1に対応するフラグに0を格納する。また2ndキャッシュメモリ30は、返却されたアドレスA4とデータA4とをCPU10の1stキャッシュメモリ12へ出力する。1stキャッシュメモリ12は、1stキャッシュタグメモリと1stキャッシュデータメモリのラインNのウェイ1にそれぞれアドレスA4とデータA4を格納する。さらに、1stキャッシュメモリ12は、コア11にデータA4を送出し1stLRUメモリのラインNに0を格納する。

【0085】

以上説明したように、本発明の実施の形態1にかかるメモリシステムを用いることにより、2ndキャッシュメモリにおいてリプレース対象となるウェイを決定する際に、ウェイに格納されているデータが、過去にリプレース対象となったデータであるか否かを考慮して、リプレース対象となるウェイを決定することができる。過去にリプレースされて、再度2ndキャッシュメモリに登録されているデータのアクセス頻度は高いと考えられるため、このようなデータが再度リプレース対象となることを防止することができる。これより、アクセス頻度の高いデータがリプレース対象となる頻度を低下させることができる。

【0086】

上述の実施の形態では、本発明をハードウェアの構成として説明したが、本発明は、これに限定されるものではない。本発明は、図5及び図6において説明した1stキャッシュメモリ12及び22と、2ndキャッシュタグメモリ41とにデータを格納する処理及び1stキャッシュメモリ12及び22のデータを無効化する処理を、CPU(Central Processing Unit)にコンピュータプログラムを実行させることにより実現することも可能である。

【0087】

上述の例において、プログラムは、様々なタイプの非一時的なコンピュータ可読媒体(non-transitory computer readable medium)を用いて格納され、コンピュータに供給することができる。非一時的なコンピュータ可読媒体は、様々なタイプの実体のある記録媒体(tangible storage medium)を含む。非一時的なコンピュータ可読媒体の例は、磁気記録媒体(例えばフレキシブルディスク、磁気テープ、ハードディスクドライブ)、光磁気記録媒体(例えば光磁気ディスク)、CD−ROM(Read Only Memory)、CD−R、CD−R/W、半導体メモリ(例えば、マスクROM、PROM(Programmable ROM)、EPROM(Erasable PROM)、フラッシュROM、RAM(Random Access Memory))を含む。また、プログラムは、様々なタイプの一時的なコンピュータ可読媒体(transitory computer readable medium)によってコンピュータに供給されてもよい。一時的なコンピュータ可読媒体の例は、電気信号、光信号、及び電磁波を含む。一時的なコンピュータ可読媒体は、電線及び光ファイバ等の有線通信路、又は無線通信路を介して、プログラムをコンピュータに供給できる。

【0088】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、上述した例においては、1stキャッシュメモリがCPUに備えられている構成例について説明したが、1stキャッシュメモリは、CPUの外部に備えられてもよい。また、図4において、フラグとの関係においてリプレース対象となるウェイを決定するパターンについて説明したが、異なるパターンを設定してもよい。

【符号の説明】

【0089】

1 プロセッサ

2 上位キャッシュメモリ

3 下位キャッシュメモリ

4 リプレース部

10 CPU

11 コア

12 1stキャッシュメモリ

20 CPU

21 コア

22 1stキャッシュメモリ

30 2ndキャッシュメモリ

40 キャッシュタグ部

41 2ndキャッシュタグメモリ

42 キャッシュヒット判定回路

43 選択回路

50 キャッシュデータ部

51 2ndキャッシュデータメモリ

52 選択回路

60 リプレース部

61 2ndLRUメモリ

62 リプレースウェイ判定回路

70 バッファ部

71 バッファ

72 ヒット判定回路

80 メインメモリ

【特許請求の範囲】

【請求項1】

第1のキャッシュメモリと、

前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、前記第2のキャッシュメモリに格納されているキャッシュデータのうち前記リプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部と、を備えるメモリシステム。

【請求項2】

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースが行われた場合に、前記リプレースされたキャッシュデータに関連付けられているアドレスを格納するバッファをさらに備え、

前記リプレース部は、

前記第1のキャッシュメモリに新たにキャッシュデータが格納される際に、前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとを比較して、前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとが一致した場合、前記新たなキャッシュデータに過去にリプレースされたデータである旨の情報を付加する、請求項1記載のメモリシステム。

【請求項3】

前記リプレース部は、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータのリプレース優先順位を下げて前記リプレース対象キャッシュデータを決定する、請求項2記載のメモリシステム。

【請求項4】

前記リプレース部は、

前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータが複数あり、前記過去にリプレースされたデータである旨の情報が付加された複数のキャッシュデータのいずれかを選択してリプレースする場合、アクセスされたタイミングが古いキャッシュデータを選択してリプレースする、請求項2又は3記載のメモリシステム。

【請求項5】

第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるキャッシュメモリ制御方法であって、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、

前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象キャッシュデータと同一のキャッシュデータを無効化する、キャッシュメモリ制御方法。

【請求項6】

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースが行われた場合に、前記キャッシュデータに関連付けられているアドレスをバッファに格納し、

前記第1のキャッシュメモリに新たにキャッシュデータが格納される際に、前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとを比較し、

前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとが一致した場合、前記新たなキャッシュデータに過去にリプレースされたデータである旨の情報を付加する、請求項5記載のキャッシュメモリ制御方法。

【請求項7】

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータのリプレース優先順位を下げて前記リプレース対象キャッシュデータを決定する、請求項6記載のキャッシュメモリ制御方法。

【請求項8】

前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータが複数あり、前記過去にリプレースされたデータである旨の情報が付加された複数のキャッシュデータのいずれかを選択してリプレースする場合、アクセスされたタイミングが古いキャッシュデータを選択してリプレースする、請求項6又は7記載のキャッシュメモリ制御方法。

【請求項9】

第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるメモリ制御プログラムであって、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定するステップと、

前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象データと同一のデータを無効化するステップと、をコンピュータに実行させるメモリ制御プログラム。

【請求項1】

第1のキャッシュメモリと、

前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、前記第2のキャッシュメモリに格納されているキャッシュデータのうち前記リプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部と、を備えるメモリシステム。

【請求項2】

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースが行われた場合に、前記リプレースされたキャッシュデータに関連付けられているアドレスを格納するバッファをさらに備え、

前記リプレース部は、

前記第1のキャッシュメモリに新たにキャッシュデータが格納される際に、前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとを比較して、前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとが一致した場合、前記新たなキャッシュデータに過去にリプレースされたデータである旨の情報を付加する、請求項1記載のメモリシステム。

【請求項3】

前記リプレース部は、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータのリプレース優先順位を下げて前記リプレース対象キャッシュデータを決定する、請求項2記載のメモリシステム。

【請求項4】

前記リプレース部は、

前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータが複数あり、前記過去にリプレースされたデータである旨の情報が付加された複数のキャッシュデータのいずれかを選択してリプレースする場合、アクセスされたタイミングが古いキャッシュデータを選択してリプレースする、請求項2又は3記載のメモリシステム。

【請求項5】

第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるキャッシュメモリ制御方法であって、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、

前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象キャッシュデータと同一のキャッシュデータを無効化する、キャッシュメモリ制御方法。

【請求項6】

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースが行われた場合に、前記キャッシュデータに関連付けられているアドレスをバッファに格納し、

前記第1のキャッシュメモリに新たにキャッシュデータが格納される際に、前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとを比較し、

前記新たなキャッシュデータに関連付けられているアドレスと、前記バッファに格納されているアドレスとが一致した場合、前記新たなキャッシュデータに過去にリプレースされたデータである旨の情報を付加する、請求項5記載のキャッシュメモリ制御方法。

【請求項7】

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータのリプレース優先順位を下げて前記リプレース対象キャッシュデータを決定する、請求項6記載のキャッシュメモリ制御方法。

【請求項8】

前記過去にリプレースされたデータである旨の情報が付加されたキャッシュデータが複数あり、前記過去にリプレースされたデータである旨の情報が付加された複数のキャッシュデータのいずれかを選択してリプレースする場合、アクセスされたタイミングが古いキャッシュデータを選択してリプレースする、請求項6又は7記載のキャッシュメモリ制御方法。

【請求項9】

第1のキャッシュメモリと、前記第1のキャッシュメモリに優先してプロセッサからアクセスされる第2のキャッシュメモリと、を備えるメモリシステムにおけるメモリ制御プログラムであって、

前記第1のキャッシュメモリにおいてキャッシュデータのリプレースを行う場合に、前記第1のキャッシュメモリに格納されているキャッシュデータの中から、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定するステップと、

前記第2のキャッシュメモリに格納されているキャッシュデータのうち、前記第1のキャッシュメモリにおいて決定されたリプレース対象データと同一のデータを無効化するステップと、をコンピュータに実行させるメモリ制御プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−185649(P2012−185649A)

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【出願番号】特願2011−47906(P2011−47906)

【出願日】平成23年3月4日(2011.3.4)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【出願日】平成23年3月4日(2011.3.4)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]