メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は不揮発性メモリ装置及び制御器を含むメモリシステムに関する。

【背景技術】

【0002】

半導体メモリは、一般的に、衛星から消費者電子技術までの範囲に属するマイクロプロセッサーを基づいた応用及びコンピューターのようなデジタルロジック設計の最も必須的なマイクロ電子素子である。したがって、高い集積度及び速い速度のための縮小(Scaling)を通じて得られるプロセスの向上及び技術開発を含む半導体メモリの製造技術の進歩は他のデジタルロジック系列の性能基準を確立するのに役に立つ。

【0003】

半導体メモリ装置は大きく揮発性半導体メモリ装置と不揮発性半導体メモリ装置とに分けられる。揮発性半導体メモリ装置において、ロジック情報はスタティックランダムアクセスメモリの場合、双安定フリップフロップのロジック状態を設定することによって又はダイナミックランダムアクセスメモリの場合、キャパシターの充電を通じて格納される。揮発性半導体メモリ装置の場合、電源が印加される間にデータが格納され、読み出され、電源が遮断される時データは消失される。

【0004】

MROM、PROM、EPROM、EEPROM、PRAM、等のような不揮発性半導体メモリ装置は電源が遮断されてもデータを格納できる。不揮発性メモリデータ格納状態は使用される製造技術によって永久的であるか、或いは再プログラムできる。不揮発性半導体メモリ装置はコンピューター、航行電子工学、通信、及び消費者電子技術産業のような広い範囲の応用でプログラム及びマイクロコードを格納するために使用される。単一チップで揮発性及び不揮発性メモリ格納モードの組合が速くて再プログラムできる不揮発性メモリを要求するシステムで不揮発性RAM(nvRAM)のような装置でまた使用できる。その上に、応用指向業務のための性能を最適化させるために幾つかの追加的なロジック回路を含む特定メモリ構造が開発されてくる。

【0005】

不揮発性半導体メモリ装置において、MROM、PROM、及びEPROMはシステム自体的に消去及び書込みが容易でないので、一般の使用者が記憶内容を新しくするのが容易でない。これに反して、EEPROM、PRAM、等のような不揮発性半導体メモリ装置は電気的に消去及び書込みができるので、継続的な更新が必要であるシステムプログラミング(system programming)や補助記憶装置としての応用が拡大されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許公報第7,941,586号公報

【特許文献2】米国特許公開第20080/0023747号公報

【特許文献3】米国特許公開第2008/0084729号公報

【特許文献4】米国特許第7,697,359号公報

【特許文献5】米国特許第7,529,124号公報

【特許文献6】米国特許第6,858,906号公報

【特許文献7】米国公開特許第2004−0169238号公報

【特許文献8】米国公開特許第2006−0180851号公報

【特許文献9】韓国特許第10−673020号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は動作速度を向上させることができるメモリシステム及びそれの動作方法を提供することにある。

【0008】

本発明の他の目的は電力消耗を減らすことができるメモリシステム及びそれの動作方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明の例示的な実施形態はデータを読出し、エラー情報を受信し、前記受信したエラー情報にしたがって前記読出しデータを訂正するように構成された不揮発性メモリ装置と、前記読出しデータを受信するように構成され、インターフェイスが前記受信したデータのエラービット位置に前記エラー情報を出力するように前記受信したデータのエラービットの位置を決定するユニットを有する制御器と、を含み、前記エラー情報は前記読み出されたデータのビットに対応したビットを含み、前記エラー情報のビットは前記読み出されたデータのビットのエラーを示すビットを含み、前記読み出されたデータのビットの値は前記エラー情報のビットの値にしたがって変更されるメモリシステムを提供する。

【0010】

前記不揮発性メモリ装置は前記読み出されたデータを前記制御器へ出力し、前記エラー情報を前記制御器から受信する。

【0011】

前記制御器は前記エラー情報を前記不揮発性メモリ装置へ出力し、前記エラー情報は前記読み出されたデータと前記読み出されたデータの訂正データとを包含しない。

【0012】

前記不揮発性メモリ装置はランダム化されたデータとして前記読み出されたデータを前記制御器へ出力し、デランダム化されたデータとして前記エラー情報を前記制御器から受信する。

【0013】

前記不揮発性メモリ装置は前記読み出されたデータが前記エラー情報にしたがって訂正されるように前記読み出されたデータを前記制御器へ出力した後、そして前記エラー情報が前記制御器から入力される時に前記前記読み出されたデータを格納するページバッファを含む。

【0014】

前記エラー情報は前記読み出されたデータの全てのビットと対応しているわけではない。

【0015】

前記不揮発性メモリ装置は変更されたビットとして前記受信したエラー情報のビットの値に対応する前記ビットの値を変更し、前記変更されたビットと維持されたビットとを前記訂正されたデータとして格納する。

【0016】

前記不揮発性メモリ装置は前記エラー情報に対応しないビットの値を維持し、前記変更された値を有する前記ビットと前記維持された値を有するビットとを含む前記訂正されたデータを格納する。

【0017】

前記不揮発性メモリ装置は単一ビットメモリアレイとマルチビットメモリアレイとを含み、前記データを前記単一ビットメモリアレイから読出し、前記訂正されたデータを前記マルチビットメモリアレイに格納する。

【0018】

前記不揮発性メモリ装置はSLCプログラム方法を利用してプログラムされた前記データを読出し、MLCプログラム方法によって前記訂正されたデータを格納する。

【0019】

前記不揮発性メモリ装置は前記制御器から前記エラー情報をページ単位で受信する。

【0020】

前記読み出されたデータと前記エラー情報とは同一なデータ大きさを有する。

【0021】

前記不揮発性メモリ装置は前記データを第1領域から第2領域に複写する複写動作の時、前記読み出されたデータに対応する前記エラー情報を受信する。

【0022】

前記不揮発性メモリ装置は複写動作を示す命令に応答して前記データを読み出すことと前記受信したエラー情報にしたがって前記訂正されたデータを格納することとを活性化させる。

【0023】

前記不揮発性メモリ装置は前記読み出されたデータのページ単位で前記エラー情報にしたがって前記エラーを有するビットを訂正するように構成されたページバッファラッチを含み、前記ページバッファラッチは前記読み出されたデータ、前記エラー情報、及び前記訂正されたデータを格納するように構成される。

【0024】

前記不揮発性メモリ装置は前記読み出されたデータのビットと前記エラー情報とをビット単位で比較して排他的OR方式又は排他的NOR方式にしたがって前記読み出されたデータのエラービットを訂正する。

【0025】

前記エラー情報のビットは前記読み出されたデータの他の1つのビットのエラー無しを示す第2ビットを含み、前記読み出されたデータの他の1つのビットの値は前記エラー情報の第2ビットの値にしたがって変更されない。

【0026】

本発明の例示的な実施形態は、また、データを出力する不揮発性メモリ装置と、前記不揮発性メモリ装置から前記データを受信するように構成され、インターフェイスが前記受信したデータのエラービット位置に情報を前記不揮発性メモリ装置へ出力するように前記受信したデータのエラービットの位置を決定するユニットを有する制御器と、を含むメモリシステムを提供する。

【0027】

前記制御器は前記受信したデータをデランダム化させて前記受信したデータから前記エラービットの位置を決定し、ランダム化無しで前記情報を出力する。

【0028】

前記制御器は前記受信したデータをデランダム化させるランダム化器/デランダム化器を含み、前記制御器は前記ランダム化器/デランダム化器が前記情報をランダム化することを防止する。

【0029】

前記不揮発性メモリ装置は前記受信したエラー位置情報にしたがって前記データを訂正する。

【0030】

前記不揮発性メモリ装置はデータが読み出された領域を含み、前記不揮発性メモリ装置は前記訂正されたデータにしたがって前記領域に対するリフレッシュ動作を遂行する。

【0031】

前記不揮発性メモリ装置は前記訂正されたデータを格納する第2領域を含み、前記第2領域はマルチビットメモリアレイである。

【0032】

前記受信したデータの決定されたエラービット位置に対する情報は前記不揮発性メモリ装置がアドレスにしたがって前記データを訂正するように前記読み出されたデータの決定されたエラービット位置のアドレスを含む。

【0033】

本発明の例示的な実施形態は、また、制御器と、第1プログラム方法によってデータを格納する単一ビットメモリアレイを含む第1領域とマルチビットメモリアレイを含む第2領域とを含み、複数のページ各々のデータを前記第1領域から読出し、そして前記複数のページ各々のデータを前記制御器へ出力するように構成された不揮発性メモリ装置と、を含み、前記制御器は前記複数のページ各々のデータのエラー位置情報を発生し、前記複数のページ各々のデータのエラー位置情報を前記不揮発性メモリ装置に出力し、前記不揮発性メモリ装置は前記複数のページ各々のデータに対応する前記エラー位置情報にしたがって前記複数のページ各々のデータを訂正し、前記複数のページの訂正されたデータを第2プログラム方法によって前記第2領域に1回に格納するメモリシステムを提供する。

【0034】

前記データは少なくとも第1ページ及び第2ページを有する複数のページを含み、前記制御器は第1エラー情報が前記第1ページに応答して決定されて出力されるように、そして第2エラー情報が前記第2ページに応答して決定されて出力されるように前記データを反復的に受信する。

【0035】

前記不揮発性メモリ装置は前記データを同時に読出し、前記エラー位置情報を受信する。

【0036】

前記不揮発性メモリ装置は前記読み出されたデータと前記受信したエラー位置情報とを同時に格納するバッファ回路を含む。

【0037】

前記不揮発性メモリ装置は前記読み出されたデータを読み出すメインバッファと前記エラー位置情報を受信するキャッシュバッファとを含み、前記エラー位置情報にしたがって前記メインバッファに格納されたデータを訂正する。

【0038】

前記不揮発性メモリ装置は前記読み出されたデータと前記訂正されたデータとを格納するように前記第1領域と前記第2領域と通信するメインバッファと、前記エラー位置情報を受信するように前記制御器と通信するキャッシュバッファと、を含む。

【0039】

前記不揮発性メモリ装置は前記エラー位置情報にしたがって前記読み出されたデータのビットを覆すフリップ動作を遂行して前記訂正されたデータを発生する。

【0040】

前記第2領域のマルチビットメモリアレイは3ビットメモリアレイを含む。

【0041】

前記第2プログラム方法は各々が前記第2領域のマルチビットメモリアレイに格納される前記訂正されたデータにしたがって異なる電圧を発生する複数の動作を含む。

【0042】

前記第2プログラム方法は前記第2領域のマルチビットメモリアレイに格納される前記訂正されたデータにしたがって異なる電圧を発生する再プログラム方法を含む。

【0043】

前記情報は前記読み出されたデータの部分の中の1つに対応し、前記読み出されたデータは前記制御器から前記不揮発性メモリ装置へ反復的に伝達され、一部の情報が前記読み出されたデータの全ての部分に対応する時まで前記制御器から前記不揮発性メモリ装置へ伝達され、前記不揮発性メモリ装置は前記対応する情報を受信する時、前記対応する情報にしたがって前記データの各部分を訂正する。

【0044】

前記メモリシステムは機能ユニットと前記不揮発性メモリ装置にデータを格納する前記制御器に連結できる端子を有するホスト装置とをさらに含む。

【0045】

前記ホスト装置は前記制御器を通じて前記不揮発性メモリ装置に格納される前記機能ユニットから生成されたデータを出力するか、或いは前記機能ユニットで使用されるデータを前記不揮発性メモリ装置から受信する。

【0046】

前記ホスト装置はビデオカメラ、テレビジョン装置、オーディオ装置、ゲーム機、電子音楽装置、携帯電話、コンピューター、PDA、ボイスレコーダー、移動装置、及び非接触式スマトカードの中で少なくとも1つを含む。

【発明の効果】

【0047】

本発明の実施形態によれば、動作速度を向上させることが可能である。また、電力消耗を減らすことが可能である。

【図面の簡単な説明】

【0048】

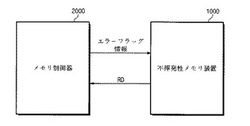

【図1】本発明の実施形態によるメモリシステムを概略的に示すブロック図である。

【図2】図1に図示されたメモリ制御器を概略的に示すブロック図である。

【図3】本発明の他の実施形態による図1に図示されたメモリ制御器を概略的に示すブロック図である。

【図4】本発明の一実施形態による図1に図示された不揮発性メモリ装置を概略的に示すブロック図である。

【図5】全てのビットラインメモリ構造又はオッドイ−ブンメモリ構造のためにメモリセルアレイをメモリブロックで構成する例を示す図面である。

【図6】本発明の例示的な実施形態による図5に図示されたページバッファ回路の一部を示すブロック図である。

【図7】本発明の実施形態による不揮発性メモリ装置のエラー訂正動作を概略的に説明するための図面である。

【図8】本発明の実施形態によるメモリシステムの複写動作を説明するためのフローチャートである。

【図9】図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。

【図10】本発明の他の実施形態による図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。

【図11】本発明の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【図12】本発明の他の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【図13A】マルチレベルメモリ装置に適用されるアドレススクランブル方式の一例を説明するための図面である。

【図13B】各メモリセル当たり3ビットデータを格納し、3ステッププログラム方式にしたがってプログラム動作が遂行される時に変化される閾値電圧分布を示す図面である。

【図14】本発明の例示的な実施形態によるデータ格納システムを概略的に示すブロック図である。

【図15A】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図15B】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図15C】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図15D】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図16】本発明の例示的な実施形態による1ステッププログラム動作のための命令シーケンスを示す図面である。

【図17】図16に図示された1ステッププログラム命令シーケンスにしたがうデータの流れを示す図面である。

【図18】エラー訂正動作(又は、ビットフリップ動作)にしたがうデータの流れを示す図面である。

【図19】粗いプログラム動作のための命令シーケンスを示す図面である。

【図20】図19に図示された粗いプログラム命令シーケンスにしたがうデータの流れを示す図面である。

【図21】本発明の他の実施形態による粗い/精巧なプログラム動作の時のデータの流れを説明するための図面である。

【図22】本発明の例示的な実施形態によるメモリシステムのリフレッシュプログラム動作を概略的に説明するための図面である。

【図23】本発明のその他の例示的な実施形態によるメモリシステムを概略的に示すブロック図である。

【図24】本発明の例示的な実施形態によるコンピューティングシステムを概略的に示すブロック図である。

【図25】本発明の例示的な実施形態による半導体ドライブを概略的に示すブロック図である。

【図26】図25に図示された半導体ドライブを利用するストレージを概略的に示すブロック図である。

【図27】図25に図示された半導体ドライブを利用する格納サーバーを概略的に示すブロック図である。

【図28】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図29】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図30】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図31】本発明の実施形態によるメモリカード(memory card)を概略的に示すブロック図である。

【図32】本発明の実施形態によるデジタルスチールカメラ(digital still camera)を概略的に示すブロック図である。

【図33】図32のメモリカードが使用される多様なシステムを説明する例示的な図面である。

【発明を実施するための形態】

【0049】

本発明の長所及び特徴、及びそれを達成する方法は添付される図面と共に詳細に後述する実施形態を通じて説明される。しかし、本発明はここで説明される実施形態に限定されなく他の形態に具体化されることもあり得る。単なる、本実施形態は本発明が属する技術分野で通常の知識を有する者に本発明の技術的思想を容易に実施できる程度に詳細に説明するために提供されることである。

【0050】

図面において、本発明の実施形態は図示された特定形態に制限されることではなく、明確性を期するために誇張されたことである。また、明細書全体に掛けて同一な参照番号に表示された部分は同一な構成要素を示す。

【0051】

本明細書で‘及び/又は’という表現は前後に羅列された構成要素の中で少なくとも1つを含む意味に使用される。また、‘連結される/結合される’という表現は他の構成要素と直接的に連結されたり、他の構成要素を通じて間接的に連結されたりすることを含む意味で使われる。本明細書で、単数型は文句で特別に言及しない限り複数型も含む。また、明細書で使用される‘含む’又は‘包含する’と言及された構成要素、段階、動作及び素子は1つ以上の他の構成要素、段階、動作、素子及び装置の存在又は追加を意味する。

【0052】

図1は本発明の実施形態によるメモリシステムを概略的に示すブロック図である。

【0053】

図1を参照すれば、本発明の実施形態によるメモリシステムは不揮発性メモリ装置1000とメモリ制御器2000とを含む。不揮発性メモリ装置1000はデータ情報を格納する一種の格納媒体として使用される。格納媒体は1つ又はそれより多いメモリチップで構成され得る。不揮発性メモリ装置1000とメモリ制御器2000とは1つ又はそれより多いチャンネルを通じて通信する。不揮発性メモリ装置1000は、例えば、NANDフラッシュメモリ装置を含む。メモリ制御器2000は外部装置(例えば、ホスト)の要請又は内部的な要請(例えば、マージ、ガーベッジコレクション、等のような背景動作に関連された要請)にしたがって不揮発性メモリ装置1000を制御するように構成される。

【0054】

例示的な実施形態において、不揮発性メモリ装置1000がNANDフラッシュメモリ装置に制限されない。例えば、不揮発性メモリ装置1000はNORフラッシュメモリ装置、抵抗性RAM(Resistive Random Access Memory:RRAM(登録商標))装置、相変化メモリ(Phase−Change Memory:PRAM)装置、磁気抵抗メモリ(Magnetoresistive Random Access Memory:MRAM)装置、強誘電体メモリ(Ferroelectric Random Access Memory:FRAM(登録商標))装置、スピン注入磁化反転メモリ(Spin Transfer Torque Random Access Memory:STT−RAM)、又はそのようなことで構成され得る。また、本発明の不揮発性メモリ装置1000は3次元アレイ構造を有するように具現され得る。3次元アレイ構造を有する不揮発性メモリ装置は垂直NANDフラッシュメモリ装置と称される。本発明は電荷格納層が伝導性浮遊ゲートで構成されたフラッシュメモリ装置のみで無く、電荷格納層が絶縁膜で構成されたチャージトラップ形フラッシュ(Charge Trap Flash、“CTF”と称される)メモリ装置にも全て適用できる。

【0055】

本発明の実施形態によるメモリシステムは不揮発性メモリ装置1000の第1格納領域から第2格納領域にデータを複写する動作(例えば、コピーバック動作:copyback operation)を支援する。第1格納領域から第2格納領域にデータを複写する動作は第1格納領域で読み出されたデータに対するエラー検出及び訂正動作を必然的に随伴する。これはデータ信頼性を高くするためである。ここで、第1格納領域は第2格納領域と異なるか、或いは同一であり得る。本発明のメモリシステムによれば、不揮発性メモリ装置1000から読み出されたデータRDのエラー検出(error detection)はメモリ制御器2000によって行われ、エラー訂正(error correction)は不揮発性メモリ装置1000内で行われる。特に、メモリ制御器2000は検出されたエラーの位置情報(以下、エラー位置情報と称される)及びパターン情報(以下、エラーフラッグ情報(error flag information)と称される)を不揮発性メモリ装置1000へ提供し、不揮発性メモリ装置1000はメモリ制御器2000から提供されるエラー位置情報及びエラーフラッグ情報に基づいてデータのエラーを訂正する。即ち、エラー検出の以後、メモリ制御器2000によってエラー訂正が行われないので(又は、エラー検出の以後、不揮発性メモリ装置1000によってエラー訂正が行われるので)、不揮発性メモリ装置1000から出力されたデータ(又は、訂正されたデータ)を全て不揮発性メモリ装置1000へ伝送する必要がない。これはメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに掛かる時間及び/又はメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに消耗される電力が減少されることを意味する。

【0056】

図2は図1に図示されたメモリ制御器を概略的に示すブロック図である。図2を参照すれば、メモリ制御器2000は第1インターフェイスとしてホストインターフェイス2100、第2インターフェイスとしてメモリインターフェイス2200、CPUのような処理ユニット2300、バッファメモリ2400、及びエラー検出及び訂正回路2500を含む。

【0057】

ホストインターフェイス2100は外部(又は、ホスト)とインターフェイスするように構成される。メモリインターフェイス2200は図1に図示された不揮発性メモリ装置1000とインターフェイスするように構成される。処理ユニット2300、例えばCPUはメモリ制御器2000の全般的な動作を制御するように構成される。例えば、処理ユニット2300はフラッシュ変換階層(Flash Translation Layer:FTL)のようなファームウェアを運用するように構成される。バッファメモリ2400はホストインターフェイス2100を通じて外部へ伝達されるデータを臨時格納するのに使用される。バッファメモリ2400はメモリインターフェイス2200を通じて不揮発性メモリ装置1000から伝達されるデータを臨時格納するのに使用される。

【0058】

エラー検出及び訂正回路2500は不揮発性メモリ装置1000に格納されるデータを符号化するように、そして不揮発性メモリ装置4100から読み出されたデータを復号化するように構成される。符号化はパリティー情報を生成する動作を含み、パリティー情報はフィールド単位で生成され得る。1ページのデータは1つ又はそれより多いフィールドで構成され得る。復号化はエラー検出動作とエラー訂正動作を含む。不揮発性メモリ装置1000で出力されたデータが外部へ伝送される時、エラー検出動作とエラー訂正動作とを含む復号化がエラー検出及び訂正回路2500によって行われる。先に説明された複写動作の時、エラー検出及び訂正回路2500はエラー訂正動作無しで不揮発性メモリ装置1000から読み出されたデータに対するエラー検出動作のみを遂行する。エラー検出及び訂正回路2500はエラー検出動作の結果としてエラー位置情報及びエラーフラッグ情報を発生し、エラー位置情報及びエラーフラッグ情報は処理ユニット2300の制御の下にメモリインターフェイス2200を通じて不揮発性メモリ装置1000へ伝送される。例えば、エラー位置情報はエラーが発生したデータビットを指定するための列アドレスを含み、エラーフラッグ情報はエラー位置情報によって指定される位置のデータビットがエラーであることを示すビット情報である。他の例として、エラー検出及び訂正回路2500はエラー検出動作の結果としてエラー位置情報によって指定される位置のデータビットがエラーであることを示すビット情報(即ち、エラーフラッグ情報)を包含するフィールドデータ(エラー訂正されたデータでないことに注意する)を不揮発性メモリ装置1000へ伝送する。これは以後詳細に説明される。

【0059】

たとえ図面には図示せずが、メモリ制御器2000はROMをさらに包含できる。ROMはフラッシュ変換階層(Flash Translation Layer:FTL)のようなファームウェアを格納するのに使用され得る。他の例として、ROMを包含しないようにメモリ制御器2000を構成することが可能である。このような場合、ROMに格納されるファームウェアはメモリ制御器2000によって制御される不揮発性メモリ装置1000に格納され、パワーアップの時に不揮発性メモリ装置1000からメモリ制御器2000へロードされる。

【0060】

例示的な実施形態において、ホストインターフェイス2100はコンピューターバス標準、ストレージバス標準、iFCP Peripheralバス標準等の中で1つ又はそれより多いことの組合で構成され得る。コンピューターバス標準(computer bus standards)はS−100 bus、Mbus、Smbus、Q−Bus、ISA、Zorro II、Zorro III、CAMAC、FASTBUS、LPC、EISA、VME、VXI、NuBus、TURBOchannel、MCA、Sbus、VLB、PCI、PXI、HP GSC bus、CoreConnect、InfiniBand、UPA、PCI−X、AGP、PCIe、Intel QuickPath Interconnect、Hyper Transport、等を含む。ストレージバス標準(Storage bus standards)は ST−506、ESDI、SMD、Parallel ATA、DMA、SSA、HIPPI、USB MSC、FireWire(1394)、Serial ATA、eSATA、SCSI、Parallel SCSI、Serial Attached SCSI、Fibre Channel、iSCSI、SAS、RapidIO、FCIP、等を含む。iFCP Peripheralバス標準(iFCP Peripheral bus standards)は Apple Desktop Bus、HIL、MIDI、Multibus、RS−232、DMX512−A、EIA/RS−422、IEEE−1284、UNI/O、1−Wire、I2C、SPI、EIA/RS−485、USB、Camera Link、External PCIe、Light Peak、Multidrop Bus、等を含む。

【0061】

図3は本発明の他の実施形態による図1に図示されたメモリ制御器を概略的に示すブロック図である。図3において、図2に図示されたことと実質的に同一な構成要素は同一な参照番号に付し、それに対する説明はしたがって省略される。図3に図示されたメモリ制御器2000aはランダム化器/デランダム化器2600をさらに含む。

【0062】

ランダム化器/デランダム化器2600は不揮発性メモリ装置1000へ伝送されるデータをランダム化するように、そして不揮発性メモリ装置1000から出力されるデータ(例えば、ランダム化されたデータ)をデランダム化するように構成される。先に説明された複写動作の時、ランダム化器/デランダム化器2600は不揮発性メモリ装置1000から出力されるデータ(例えば、ランダム化されたデータ)をデランダム化し、エラー検出及び訂正回路2500はデランダム化されたデータのエラーを検出する。先に説明されたように、メモリ制御器2000aから不揮発性メモリ装置1000へ伝送されるエラーフラッグ情報はランダム化器/デランダム化器2600によってランダム化されない。同様に、エラーフラッグ情報を含むフィールドデータが伝送される場合にも、ランダム化器/デランダム化器2600は動作しない。エラー訂正されたデータが不揮発性メモリ装置1000へ伝送される場合、エラー訂正されたデータはランダム化器/デランダム化器2600によってランダム化される。本発明の場合、エラー訂正がメモリ制御器2000aによって提供されるエラーフラッグ情報にしたがって不揮発性メモリ装置1000によって行われるので、ランダム化器/デランダム化器2600のランダム化はエラーフラッグ情報/フィールドデータ(エラーフラッグ情報を含む)の伝送の時に行われない。

【0063】

図4は本発明の一実施形態による図1に図示された不揮発性メモリ装置を概略的に示すブロック図である。図4を参照すれば、不揮発性メモリ装置1000はメモリセルアレイ1100、アドレスデコーダー1200、電圧発生器1300、制御ロジック1400、ページバッファ回路1500、及び入出力インターフェイス1600を含む。

【0064】

メモリセルアレイ1100は行(例えば、ワードライン)と列(例えば、ビットライン)との交差領域に配列されたメモリセルを含む。メモリセルの各々は1ビットデータ又はマルチビットデータを格納する。アドレスデコーダー1200は制御ロジック1400によって制御され、メモリセルアレイ1100の行(例えば、ワードライン、ストリング選択ライン、接地選択ライン、共通ソースライン、等)の選択及び駆動を行う。電圧発生器1300は制御ロジック1400によって制御され、各動作に必要である電圧(例えば、高電圧、プログラム電圧、読出し電圧、検証電圧、消去電圧、パス電圧、バルク電圧、等)を発生する。電圧発生器1300によって電圧はアドレスデコーダー1200を通じてメモリセルアレイ1100へ提供される。制御ロジック1400は不揮発性メモリ装置1000の全般的な動作を制御するように構成される。ページバッファ回路1500は制御ロジック1400によって制御され、メモリセルアレイ1100からデータを読み出すように、又はプログラムデータにしたがってメモリセルアレイ1100の列(例えば、ビットライン)を駆動するように構成される。入出力インターフェイス1600は制御ロジック1400によって制御され、外部(例えば、図1のメモリ制御器)とインターフェイスするように構成される。

【0065】

ページバッファ回路1500はビットライン又はビットライン対に各々対応する複数のページバッファで構成される。ページバッファの各々は複数のラッチを含む。ページバッファ回路1500は制御ロジック1400の制御の下に各ページバッファのラッチを利用してエラー訂正動作を遂行する。即ち、ページバッファ回路1500は制御ロジック1400の制御の下にメモリ制御器2000から提供されたエラーフラッグ情報にしたがってエラー訂正動作を遂行する。本発明の例示的な実施形態において、エラー訂正動作はエラー位置情報に対応するデータビットの値を反転させることによって、達成される。即ち、エラー位置情報に対応するデータビットの値はエラーフラッグ情報にしたがって反転される。このようなエラー訂正動作をビットフリップ動作と称する。これは以後詳細に説明する。

【0066】

図5は全てのビットラインメモリ構造又はオッドイ−ブンメモリ構造のためにメモリセルアレイをメモリブロックで構成する例を示す図面である。メモリセルアレイ1100の例示的な構造が説明される。一例として、メモリセルアレイ1100が1024個のメモリブロックに分けられたNANDフラッシュメモリ装置が説明される。各メモリブロックに格納されたデータは同時に消去され得る。一実施形態において、メモリブロックは同時に消去される格納素子の最小単位である。各メモリブロックには、例えば、ビットラインに各々対応する複数の列がある。全てのビットライン(all bit line:ABL)構造と称される一実施形態において、メモリブロックの全てのビットラインは読出し及びプログラム動作の間に同時に選択され得る。選択されたワードラインに属し、全てのビットラインと連結された格納素子は同時にプログラムされ得る。

【0067】

例示的な実施形態において、同一な列に属する複数の格納素子はNANDストリング111を構成するように直列に連結される。NANDストリングの一端子はストリング選択ラインSSLによって制御される選択トランジスターを通じて対応するビットラインに連結され、他の端子は接地選択ラインGSLによって制御される選択トランジスターを通じて共通ソースラインCSLに連結される。

【0068】

オッドイ−ブン構造(odd−even architecture)と称される他の例示的な実施形態において、ビットラインはイ−ブンビットラインBLeとオッドビットラインBLoとに区分される。オッド/イ−ブンビットライン構造において、選択されたワードラインに属し、オッドビットラインと連結された格納素子が第1時間にプログラムされる反面に、選択されたワードラインに属し、イ−ブンビットラインと連結された格納素子は第2時間にプログラムされる。データは他のブロックにプログラムされ得り、他のメモリブロックから読み出され得る。このような動作は同時に遂行できる。

【0069】

図6は本発明の例示的な実施形態による図5に図示されたページバッファ回路の一部を示すブロック図である。本発明の実施形態によるページバッファ回路1500はビットラインに各々連結された複数のページバッファPBを含む。図6には単なる1つのページバッファPBが図示されている。残りページバッファの各々は図6に図示されたことと実質的に同様に構成される。

【0070】

図6を参照すれば、ページバッファPBは図4の制御ロジック1400によって制御され、プリチャージ回路1510、ラッチブロック1520、及びデータ入出力回路1530を含む。プリチャージ回路1510はビットラインBLに連結され、ビットラインBLをプリチャージするように構成される。一対のビットラインにページバッファPBが連結される場合、プリチャージ回路1510は一対のビットラインの中から1つを選択する機能を含む。ラッチブロック1520は感知ノードSOに連結される。ラッチブロック1520は複数の、例えば5つのラッチユニット1521〜1525(図面にはS、L、M、F、及びCに各々示す)を含む。ページバッファPBに含まれたラッチユニットの数がここに開示されたことに制限されない。ラッチブロック1520は感知動作(プログラム検証動作、読出し動作、消去検証動作等に関連される)の時、制御ロジック1400の制御の下に感知ノードSOの値をラッチするように構成される。制御ロジック1400はラッチの間からデータが伝達されるダンプ動作を実行するようにラッチブロック1520を制御する。ダンプ動作の時、ラッチの間から伝達されるデータの位相は制御ロジック1400の制御にしたがって反転されるか、或いはそのまま維持される。ラッチブロック1520はプログラム動作の時、プログラムデータにしたがってビットラインBLをビットラインプログラム電圧(例えば、0V又は0Vより高くて電源電圧より低い電圧)又はビットラインプログラム禁止電圧(例えば、電源電圧)で駆動する。

【0071】

以後説明されるように、ラッチブロック1520は制御ロジック1400の制御にしたがってエラーフラッグ情報を利用して先に説明されたビットフリップ動作(又は、エラー訂正動作)を遂行する。これは制御ロジック1400の制御にしたがってラッチユニット1521〜1525の間で行われるデータ伝送動作を通じて達成される。データ入出力回路1530はラッチブロック1520のデータをデータラインDLへ伝送するか、或いはデータラインDLのデータをラッチブロック1520へ伝送するように構成される。

【0072】

図6に図示されたページバッファPBの構成がここに開示されたことに制限されない。

【0073】

図7は本発明の実施形態による不揮発性メモリ装置のエラー訂正動作を概略的に説明するための図面である。以下、本発明の実施形態による不揮発性メモリ装置1000のエラー訂正動作が参照図面に基づいて詳細に説明される。

【0074】

メモリセルアレイ1100の第1格納領域から読み出されたデータを第2格納領域に複写する場合、第1格納領域から読み出されたデータに対するエラー訂正が行われる。第1格納領域から読み出されたデータに対するエラー訂正は、先に説明されたように、メモリ制御器2000によって行われることではなく、不揮発性メモリ装置1000によって行われる。エラー訂正はメモリ制御器2000から提供されるエラーフラッグ情報にしたがって行われる。例えば、エラー訂正はビットフリップ動作を通じて行われる。

【0075】

図7に図示されたように、説明の便宜上、メモリセルアレイ1100の第1格納領域から読み出されたデータが“01010011”の8ビットデータであると仮定する。第1格納領域から読み出されたデータは、先ず、メモリ制御器2000へ提供される。メモリ制御器2000のエラー検出及び訂正回路2500は不揮発性メモリ装置1000から提供されるデータがエラーがあるか否かを判別する。仮に不揮発性メモリ装置1000から提供されるデータがエラーがあると判別されれば、エラー検出及び訂正回路2500はエラー位置情報及びエラーフラッグ情報を発生する。エラー位置情報及びエラーフラッグ情報は処理ユニット2300の制御の下に不揮発性メモリ装置1000へ提供される。ここで、エラーフラッグ情報はエラー位置情報に対応するデータビットがエラーがあることを示す。例えば、図7に図示されたように、エラーフラッグ情報はエラー位置情報に対応するデータビットが誤ったことと判別される時、メモリの値を有する。しかし、エラーフラッグ情報がエラー位置情報に対応するデータビットが誤ったことと判別される時、‘0’の値を有するように設定され得ることは理解できる。

【0076】

エラーフラッグ情報は第1格納領域から読み出されたデータと独立的に不揮発性メモリ装置1000のページバッファ回路1500に格納される。エラーフラッグ情報に基づいてページバッファ回路1500を通じてエラー訂正動作又はビットフリップ動作が行われる。図7に図示されたように、エラー位置情報に対応するデータビットはエラーフラッグ情報に基づいて‘1’から‘0’に変更される。変更されたデータビットを含むデータはエラー訂正されたデータである。以後、エラー訂正されたデータはメモリセルアレイ1100の第2格納領域に格納される。

【0077】

エラーフラッグ情報に基づいて行われるページバッファのエラー訂正動作又はビットフリップ動作が以下詳細に説明される。

【0078】

エラー訂正動作(又は、ビットフリップ動作)はページバッファPBのラッチユニットを利用して行われる。例えば、エラー訂正動作は3つのラッチユニット1521、1522、1525を利用して排他的OR動作を通じて行われる。エラー訂正動作が排他的OR(XOR)動作に制限されない。例えば、エラー訂正動作はエラーフラッグ情報の値にしたがって排他的NOR(XNOR)動作を通じて行われ得る。エラー訂正動作は制御ロジック1400の制御の下に行われる。

【0079】

先ず、第1格納領域から読み出されたデータはラッチユニット1521(以下、Sラッチユニットと称する)に格納される。Sラッチユニット1521に格納されたデータはラッチユニット1522、1525(以下、Lラッチユニット及びCラッチユニットと称する)へ各々ダンプされる。Cラッチユニット1525に格納されたデータはエラーを検出するためにメモリ制御器2000へ出力される。説明の便宜上、1つのデータビットを基準としてエラー訂正動作が説明される。このような場合、1つの読み出されたデータビット及び1つのエラーフラッグビットの組合は4つの種類である場合(例えば、‘00’、‘01’、‘10’、及び‘11’)の中の1つである。下の表1はエラーを検出するためにメモリ制御器2000にデータが出力される時、各ラッチユニットの状態を示す。下の表で‘X’はdon’t careを意味する。先に説明によれば、下の表1で分かるように、Sラッチユニット1521、Lラッチユニット1522、及びCラッチユニット1525は同一な状態を有する。

【0080】

【表1】

【0081】

Cラッチユニット1525からメモリ制御器2000へデータが出力された後、Cラッチユニット1525は‘0’の値を有するように初期化される。メモリ制御器2000は不揮発性メモリ装置1000から出力されたデータに対するエラー検出動作を遂行し、エラー検出動作の結果としてエラー位置情報及びエラーフラッグ情報(又は、エラーフラッグビット)を不揮発性メモリ装置1000へ提供する。エラーフラッグ情報(又は、エラーフラッグビット)はメモリの値を有する。エラーフラッグ情報を入力する前にSラッチユニット1521は‘0’に初期化される。下の表2はLラッチユニット1522の値(読み出されたデータビットの値)とCラッチユニット1525の値(エラーフラッグ情報/ビット)との組合にしたがう場合を示す。

【0082】

【表2】

【0083】

Cラッチユニット1525へロードされた‘1’に対応するLラッチユニット1522の値を反転させることによって、エラー訂正動作が達成され、これは以下詳細に説明される。

【0084】

先ず、制御ロジック1400はCラッチユニット1525へロードされたエラーフラッグビットを反転させ、反転されたビットをSラッチユニット1521に格納するようにページバッファPBを制御する。エラーフラッグビットの反転はCラッチユニット1525からSラッチユニット1521にデータがダンプされる過程で行われる。このような動作の結果は下の表3の通りである。

【0085】

【表3】

【0086】

制御ロジック1400はSラッチユニット1521の値が‘0’であり、Lラッチユニット1522の値が‘0’である時、Sラッチユニット1521の値及びLラッチユニット1522の値が‘1’に変更されるようにページバッファPBを制御する。このような動作の結果は下の表4の通りである。

【0087】

【表4】

【0088】

制御ロジック1400はSラッチユニット1521の値が‘0’である時、Lラッチユニット1522の値が‘0’に変更されるようにページバッファPBを制御する。このような動作の結果は下の表5の通りである。

【0089】

【表5】

【0090】

Lラッチユニット1522に格納されたデータがエラー訂正されたデータになる。即ち、読み出されたデータビットがメモリの値を有し、対応するエラーフラッグビットがメモリの値を有する時、表2及び表5で分かるように、Lラッチユニット1522の値は‘1’から‘0’に変更される。読み出されたデータビットが‘0’の値を有し、対応するエラーフラッグビットがメモリの値を有する時、表2及び表5で分かるように、Lラッチユニット1522の値は‘0’から‘1’に変更される。

【0091】

先に説明されたエラー訂正動作又はビットフリップ動作は例示的なことであり、本発明はここに開示されたことに制限されない。エラー訂正動作又はビットフリップ動作はページバッファの構造、エラーフラッグ情報の値、等にしたがって多様に変更される。

【0092】

図8は本発明の実施形態によるメモリシステムの複写動作を説明するためのフローチャートであり、図9は図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。以下、本発明の実施形態によるメモリシステムの複写動作が参照図面に基づいて詳細に説明される。

【0093】

以後説明される複写動作は、先に説明されたように、メモリセルアレイ1100の第1格納領域(例えば、第1メモリブロックに属する1つのページに対応する)から第2格納領域(例えば、第2メモリブロックに属する1つのページに対応する)へデータを複写する動作を意味する。複写動作という用語が特定動作に制限されない。例えば、複写動作は1つの格納領域から他の格納領域へデータを移る全て動作を包含するように解釈される。

【0094】

先ず、S100段階で、ページバッファ回路1500はメモリセルアレイ1100の第1メモリブロックの第1格納領域(又は、選択されたページ)からデータを読み出す。読み出されたデータはページバッファ回路1500のSラッチユニット1521に格納される。読み出されたデータは読出し動作の間に発生され得るエラービットを包含できる。エラー訂正無しで第2メモリブロックの第2格納領域にエラービットを含む読み出されたデータがそのまま格納される場合、第2格納領域に格納されたデータのエラービットの数はメモリ制御器2000のエラー訂正範囲を超過され得る。即ち、データ信頼性が低下され得る。その故に、読み出されたデータに対するエラー検出及び訂正動作が行われる。このために、S110段階で、読み出されたデータはメモリ制御器2000へ出力される。先に説明されたように、読み出されたデータは外部へ出力される以前にLラッチユニット1522及びCラッチユニット1525へダンプされる。Cラッチユニット1525に格納された読み出されたデータがメモリ制御器2000へ出力される。

【0095】

S120段階で、メモリ制御器2000は読み出されたデータがエラービットを含むか否かを判別する。これはメモリ制御器2000のエラー検出及び訂正回路2500を通じて行われる。読み出されたデータがエラービットを包含しないことと判別されれば、手続はS160段階に進行する。読み出されたデータがエラービットを含むことと判別されれば、エラー検出及び訂正回路2500はエラー位置情報及びエラーフラッグ情報を発生させる。エラー検出及び訂正回路2500はエラー位置情報及びエラーフラッグ情報を発生するためのエラー検出動作を遂行する。即ち、複写動作の時、エラー検出及び訂正回路2500はエラー訂正動作を遂行する必要性がない。S140段階で、メモリ制御器2000から不揮発性メモリ装置1000へエラー位置情報及びエラーフラッグ情報が伝送される。これは図9を参照して以下詳細に説明される。

【0096】

不揮発性メモリ装置1000から出力された読み出されたデータは1つ又はそれより多いエラービットを包含できる。エラー位置情報及びエラーフラッグ情報はエラービット単位で反復的に不揮発性メモリ装置1000へ伝送される。図9に図示されたように、エラービットの中の第1番目のエラービットに対応したエラー位置情報は第1命令86hに続いて伝送されるアドレスC1C2R1R2R3に包含され、エラーフラッグ情報EFIはアドレスC1C2R1R2R3に続いて伝送される。ここで、アドレスC1C2R1R2R3の中の列アドレスC1C2はエラー位置情報を含む。アドレスC1C2R1R2R3は第1格納領域を含むメモリブロック(又はプラン/マット)を指定するための行アドレスR1R2R3を含む。このようなシーケンスは1つのエラービットに関連されて行われる。残りのエラービット各々に対応するエラー位置情報は、図9に図示されたように、第1命令86hに続いて伝送されるアドレスC1C2に包含され、エラーフラッグ情報EFIはアドレスC1C2に続いて伝送される。ここで、アドレスC1C2、即ち列アドレスC1C2はエラー位置情報を含む。全てのエラービットによって対するエラーフラッグ情報が図9に図示されたタイミングにしたがって不揮発性メモリ装置1000へ伝送された後、第2命令12hがメモリ制御器2000から不揮発性メモリ装置1000へ伝送される。以後、以下で説明されるように、エラー訂正動作(又は、ビットフリップ動作)及びプログラム動作が行われる。

【0097】

再び図8を参照すれば、S140段階で続いてS150段階で、不揮発性メモリ装置1000はメモリ制御器2000から提供されたエラーフラッグ情報に基づいてエラー訂正動作(又は、ビットフリップ動作)を遂行する。エラー訂正動作(又は、ビットフリップ動作)は表2乃至表5を参照して説明されたことと実質的に同様に行われるので、それに対する説明は省略される。S160段階で、エラー訂正されたデータはメモリセルアレイ1100の第2格納領域にプログラム/格納される。以後、手続は終了される。

【0098】

先の説明のよれば、エラー検出はメモリ制御器2000によって行われ、エラー訂正は不揮発性メモリ装置1000内で行われる。即ち、エラー検出の以後、メモリ制御器2000によってエラー訂正が行われないので(又は、エラー検出の以後、不揮発性メモリ装置1000によってエラー訂正が行われるので)、不揮発性メモリ装置1000から出力されたデータ(又は、訂正されたデータ)を全ての不揮発性メモリ装置1000へ伝送する必要がない。これはメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに掛かる時間及び/又はメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに消耗される電力が減少されることを意味する。

【0099】

図10は本発明の他の実施形態による図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。

【0100】

エラービット単位でエラーフラッグ情報が伝送される図9の伝送方式と異なりに、エラーフラッグ情報(エラービットによって各々対応するエラーフラッグビットを包含する)を含むデータ(以下、フィールドデータと称する)が命令86h及びアドレスC1C2R1R2R3に続いて不揮発性メモリ装置1000へ伝送される。そのようなフィールドデータの大きさは読み出されたデータの大きさと同一である。フィールドデータにおいて、エラー位置情報に対応する位置の値(即ち、エラーフラッグビットの値)はロジック値‘1’(ロジック値がエラービットであることを示す)であり、残りの位置の値は反転されたロジック値‘0’(ロジック値がノンエラービット(non−error bit)であることを示す)である。例えば、データがメモリ制御器2000から不揮発性メモリ装置1000へバイト単位で伝送される場合、エラー位置情報に対応する位置は8つのデータビット(例えば、D0〜D7)の中の1つ(例えば、D1)に対応する。エラーフラッグ情報を含むフィールドデータが伝送される方式の場合、バス遷移回数が非常に少ない。これはデータ伝送の時、消耗される電力が減少することを意味する。また、エラー検出がメモリ制御器によって行われ、エラー訂正が不揮発性メモリ装置内で行われるので、メモリ制御器から不揮発性メモリ装置へデータを伝送するのに掛かる時間及び/又はメモリ制御器から不揮発性メモリ装置へデータを伝送するのに消耗される電力が減少される。

【0101】

図11は本発明の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【0102】

メモリセルアレイMCAの第1格納領域(例えば、第1メモリブロックの1ページに対応する)のデータはメインバッファMBを通じて読出し、メインバッファMBに格納された読み出されたデータはキャッシュバッファCBを通じてメモリ制御器2000へ伝送される。ここで、メインバッファMBはSラッチユニット1521で構成され得り、キャッシュバッファCBはCラッチユニット1525で構成され得る。しかし、本発明はそれに制限されない。メインバッファMBとキャッシュバッファCBとはページバッファ回路1500を構成する。メモリ制御器2000へ伝送されたデータはランダム化器/デランダム化器2600を通じてデランダム化され、エラー検出及び訂正回路2500はランダム化器/デランダム化器2600によってデランダム化されたデータに対するエラー検出動作を遂行する。ここで、不揮発性メモリ装置1000から出力される読み出されたデータRDのデランダム化されたデータはバッファメモリ2400に格納される。エラー検出動作の結果として、エラーフラッグ情報が不揮発性メモリ装置1000のキャッシュバッファCBへ伝送される。ここで、エラーフラッグ情報は図9で説明された方式又は図10で説明された方式にしたがってメモリ制御器2000から不揮発性メモリ装置1000へ伝送される。エラーフラッグ情報又はエラーフラッグ情報を含むフィールドデータはランダム化器/デランダム化器2600を経由しなくて直接不揮発性メモリ装置1000へ伝送される。キャッシュバッファCBに格納されたエラーフラッグ情報に基づいてビットフリップ動作(又は、エラー訂正動作)が行われ、ビットフリップ動作(又は、エラー訂正動作)を通じて訂正されたデータはメインバッファMBを通じてメモリセルアレイMCAの第2格納領域(例えば、第2メモリブロックの1ページに対応する)に格納される。ビットフリップ動作(又は、エラー訂正動作)は表3乃至図5で説明されたことと実質的に同一であるので、それに対する説明は省略される。

【0103】

例示的な実施形態において、メモリ制御器2000から提供されるエラーフラッグ情報はページバッファ回路1500のキャッシュバッファCBへロードされる。この時、メインバッファMBには読み出されたデータが格納されている。即ち、キャッシュバッファCBへロードされる情報はメインバッファMBにされたデータビットが誤ったか否かを示す値である。

【0104】

例示的な実施形態において、図11で説明された複写動作は点線で示されたランダム化器/デランダム化器2600を含むメモリ制御器(例えば、図3に図示されたことに対応する)のみでなく、点線で示されたランダム化器/デランダム化器2600を包含しないメモリ制御器(例えば、図2に図示されたことに対応する)に適用できる。ランダム化器/デランダム化器2600を含むメモリ制御器2000において、仮に第1格納領域を含む第1メモリブロック及び第2格納領域を含む第2メモリブロックに対するランダム化のためのシードが互に同一な場合、エラーフラッグ情報に対するランダム化は行われない。

【0105】

例示的な実施形態において、シード値はランダム化されたデータが格納される領域のメモリセルに格納される。

【0106】

複写動作であるコピーバック動作(又はコピーバックプログラム動作)が特許文献1に開示され、この出願のレファレンスとして包含される。

【0107】

図12は本発明の他の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【0108】

メモリセルアレイMCAの第1格納領域のデータはメインバッファMBを通じて読出し、メインバッファMBに格納された読み出されたデータはキャッシュバッファCBを通じてメモリ制御器2000へ伝送される。ここで、メインバッファMBはSラッチユニット1521で構成され得り、キャッシュバッファCBはCラッチユニット1525で構成され得る。しかし、本発明はそれに制限されない。ここで、不揮発性メモリ装置1000から出力される読み出されたデータRDのデランダム化されたデータはバッファメモリ2400に格納される。メモリ制御器2000へ伝送されたデータはランダム化器/デランダム化器2600を通じてデランダム化され、エラー検出及び訂正回路2500はランダム化器/デランダム化器2600によってデランダム化されたデータに対するエラー検出動作を遂行する。仮にメモリセルアレイMCAの第1格納領域に関連されたランダム化動作のためのシード値が第2格納領域に関連されたランダム化動作のためのシード値と一致しなければ、メモリ制御器2000は読み出されたデータに対するエラー検出動作のみで無く、エラー訂正動作を遂行する。ここで、不揮発性メモリ装置1000から出力される読み出されたデータRDのデランダム化されたデータはバッファメモリ2400に格納される。読み出されたデータのエラーはエラー検出及び訂正回路2500によって訂正される。訂正されたデータはランダム化器/デランダム化器2600を通じて不揮発性メモリ装置1000のキャッシュバッファCBへ伝送される。キャッシュバッファCBに格納されたエラー訂正されたデータはメインバッファMBへ伝送され、メインバッファMBへ伝送されたデータ(即ち、エラー訂正されたデータ)はメモリセルアレイMCAの第2格納領域に格納される。

【0109】

先に説明されたエラー検出動作及びエラー訂正動作を含む複写動作は多様なメモリシステムに適用できる。以下、先に説明されたエラー検出動作及びエラー訂正動作を含む複写動作が適用されるメモリシステムの一例が説明される。

【0110】

図13Aはマルチレベルメモリ装置に適用されるアドレススクランブル方式の一例を説明するための図面である。

【0111】

各メモリセルに格納されるデータビットの数が増加されることによって、マルチビット(又は、マルチレベル)データを格納するメモリ装置(以下、マルチレベルメモリ装置と称する)の信頼性を確保することが漸次的に難しくなり得る。信頼性を低下させる要因の中で代表的な1つは隣接メモリセルの間のカップリングによる閾値電圧の変化である。例えば、以前にプログラムされたメモリセルの閾値電圧はプログラムされたメモリセルに隣接するメモリセルがプログラムされる時、生じるカップリングによって変化され得る。

【0112】

1つのメモリセルに3ビットデータが格納されると仮定の下でアドレススクランブル方式が説明される。図示の便宜上、図13Aには単なる4つのワードラインWL0−WL3が図示されている。ワードラインWL0−WL3各々には複数のメモリセルMCが連結される。先ず、下位2ビットデータが第1番目のワードラインWL0に連結されたメモリセル各々に格納される1ステッププログラム動作が遂行される。即ち、1ステッププログラム動作の間に、第1番目のワードラインWL0に連結されたメモリセルには2ページデータが格納される。これは図13Aで(1)に表記されている。その次に、第2番目のワードラインWL1に連結されたメモリセルに対して1ステッププログラム動作が遂行される。これは図13Aで(2)に表記されている。第2番目のワードラインWL1に対する1ステッププログラム動作が遂行された後、第2番目のワードラインWL1の下に位置し、下位2ビットデータがプログラムされた第1番目のワードラインWL0に連結されたメモリセルに上位1ビットデータが格納される粗いプログラム動作(coarse program operation)(又は、第2番目のステッププログラム(2−step programming)と称される)が遂行される。これは図13Aで(3)に表記されている。第1番目のワードラインWL0に連結されたメモリセルに対して粗いプログラム動作が遂行された後、第3番目のワードラインWL2に対する1ステッププログラム動作が遂行される、これは図13Aで(4)に表記されている。第3番目のワードラインWL2に対する1ステッププログラム動作の以後、下位2ビットデータがプログラムされた第2番目のワードラインWL1に連結されたメモリセルに上位1ビットデータが格納される粗いプログラム動作が遂行される。これは図13Aで(5)に表記されている。その後、第1番目のワードラインWL0に対する精巧なプログラム動作(fine program operation)が遂行される。これは図13Aで(6)に表記されている。以後、1ステップ、粗い、そして精巧なプログラム動作が先に説明されたプログラム順序(図13A参照)にしたがって順次的に遂行される。図13で説明されたプログラム順序にしたがってワードラインが選択される方式をアドレススクランブル方式と称する。アドレススクランブル方式がここに開示されたことに制限されない。

【0113】

1ステッププログラム動作と粗いプログラム動作とが完了されれば、Mビットデータ(Mは2又はそれより大きい整数)に対応する閾値電圧分布(例えば、2Mつの閾値電圧分布)が全て形成される。たとえ粗いプログラム動作が完了されることにしたがって全て閾値電圧分布が形成されても、閾値電圧分布間のマージンは閾値電圧分布を明確に区分するのに充分でない。閾値電圧分布を明確に区分するのに充分なマージンを確保するために精巧なプログラム動作が遂行される。精巧なプログラム動作は各閾値電圧分布の幅を狭くするために行われ、粗いプログラム動作で使用される閾値電圧分布の検証電圧より所定電圧程度各々高い検証電圧を使用して行われる。このようなプログラム方式を通じて隣接するメモリセルの間のカップリングを減らすことが可能である。このようなプログラム方法/アルゴリズムは再プログラム方法/アルゴリズム(reprogram method/algorithm)と称する。

【0114】

例示的な実施形態において、3ビットデータのための再プログラム方法、即ち、1ステッププログラミング、粗いプログラミング、及び精巧なプログラミングが2ビットデータ及び4ビットデータの再プログラム方法にも全て適用され得ることはよく理解できる。

【0115】

このような再プログラム方法によると、任意のワードラインに対する精巧なプログラム動作が終了される時まで任意のワードラインのメモリセルに格納されたデータを維持する必要がある。例えば、1ステッププログラム動作はメモリ制御器からマルチビットメモリ装置へ提供されるデータに基づいて行われ、粗いプログラム動作は1ステッププログラム動作を通じて格納されたデータとメモリ制御器から提供されるデータとに基づいて行われる。精巧なプログラム動作は1ステッププログラム動作と粗いプログラム動作とを通じて格納されたデータに基づいて行われる。しかし、先に説明されたように、1ステッププログラム動作と粗いプログラム動作とを通じて格納されたデータを正確に読み出すことは難しい。これは精巧なプログラム動作に必要であるデータはメモリ制御器からマルチビットメモリ装置へ提供されなければならないことを意味する。そのような理由で、任意のワードラインに対する精巧なプログラム動作が終了される時まで任意のワードラインのメモリセルに格納されたデータがメモリ制御器によって維持される。これは精巧なプログラム動作に必要であるデータを維持するための大きい容量のバッファメモリがメモリ制御器へ提供されることを意味する。バッファメモリの容量を減らすために以後説明されるオンチップバッファプログラミング(On−chip Buffered Programming:OBP)技術がメモリシステムに適用され得る。

【0116】

図13Bは各メモリセル当たり3ビットデータを格納し、3ステッププログラム方式にしたがってプログラム動作が遂行される時、変化される閾値電圧分布を示す図面である。以下、3ステッププログラム方式によるプログラム方法が参照図面に基づいて説明される。

【0117】

先ず、選択されたワードライン(例えば、WL0、図13A参照)のメモリセルには2ページデータ(即ち、第1及び第2ページデータ)が同時に格納される。この時、図13Bのボックス31に図示されたように、消去状態Eに対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態Q1、Q2、Q3に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。

【0118】

先に説明されたように、ワードライン(例えば、WL0)に属する1ステッププログラムされたメモリセルの粗いプログラム動作は隣接するワードライン(例えば、WL1)に属するメモリセルの1ステッププログラム動作の以後に行われる。この時、図13Bのボックス31の実線で表示されたように、ワードライン(例えば、WL0)に属する1ステッププログラムされたメモリセルの散布が隣接するワードライン(例えば、WL1)に属するメモリセルがプログラムされる時に生じるカップリングによって広くなる。

【0119】

その次に、選択されたワードラインWL0のメモリセルには1ページデータが格納される。この時、図13Bのボックス32に図示されたように、各状態に対応する閾値電圧分布に属するメモリセルは対応する閾値電圧散布に属する閾値電圧を有するようにプログラムされる。例えば、消去状態Eに対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P1に対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。プログラム状態Q1に対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P2、P3に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。プログラム状態Q2に対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P4、P5に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。プログラム状態Q3に対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P6、P7に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。

【0120】

先に説明されたように、ワードライン(例えば、WL0)に属する粗いプログラムされたメモリセルの精巧なプログラム動作は隣接するワードライン(例えば、WL2、WL1)に対する1ステッププログラム動作及び粗いプログラム動作の以後に行われる。この時、図13Bのボックス32の実線で図示されたように、ワードライン(例えば、WL0)に属する粗いプログラムされたメモリセルの散布が隣接するワードライン(例えば、WL2、WL1)に属するメモリセルがプログラムされる時に生じるカップリングによって広くなる。このような理由で、粗いプログラムされたメモリセルからデータを正確に読み出すことが難しい。

【0121】

ワードラインWL0に属するメモリセルが図13Bのボックス33に図示されたような最終閾値電圧分布P1を有するようにプログラムされる。このような動作は精巧なプログラム動作と称される。先に説明されたように、精巧なプログラム動作は以前にプログラムされたデータ(例えば、第1乃至第3ページデータ)を必要とし、これはワードラインWL0に属するメモリセルから以前にプログラムされたデータを正確に読み出すことが難しいので、メモリ制御器から提供されるデータ(又は、メモリ装置によって維持されるデータ)に基づいて行われる。図13Bのボックス33の実線で図示されたように、精巧なプログラムされたメモリセルやはり隣接するワードラインに属するメモリセルの散布はプログラムされる時に生じるカップリングによって広くなり得る。

【0122】

以後、各ワードラインに対する1ステッププログラム動作、粗いプログラム動作、及び精巧なプログラム動作が図13Aで説明されたプログラム順序にしたがって行われ、これは図13Bで説明されたことと同一な方式に行われる。

【0123】

図14は本発明の例示的な実施形態によるデータ格納システムを概略的に示すブロック図である。

【0124】

図14を参照すれば、データ格納システム3000は不揮発性メモリ装置としてマルチビットメモリ装置3100、メモリ制御器3200、及びホスト3300を含む。マルチビットメモリ装置3100は1つ又はそれより多いメモリチップで構成され得る。マルチビットメモリ装置3100とメモリ制御器3200とは、データ格納装置として、メモリカード、半導体ディスク(Solid State Drive:SSD)、メモリスティック、又はそのようなことを構成する。マルチビットメモリ装置3100は複数のメモリブロック(セクター/バンク)を含み、各メモリブロックは行と列とに配列されたメモリセルを含む。メモリセルの各々はマルチビット(又は、マルチレベル)データを格納する。メモリセルは2次元アレイ構造を有するように又は3次元/垂直アレイ構造を有するように配列される。例示的な3次元アレイ構造が特許文献2に“SEMICONDUCTOR MEMORY DEVICE WITH MEMORY CELLS ON MULTIPLE LAYERS”という名称にて、及び特許文献3に“EMICONDUCTOR DEVICE WITH THREE−DIMENSIONAL ARRAY STRUCTURE”という名称にて各々開示されているし、この出願のレファレンスとして包含される。

【0125】

本発明の例示的な実施形態によるマルチビットメモリ装置3100のメモリブロックは第1メモリ領域3101と第2メモリ領域3102とに区分される。ここで、第1及び第2メモリ領域3101、3102の区分が物理的なことでは無くて論理的に行われることが理解できる。第1及び第2メモリ領域3101、3102の区分は論理的に可変できる。第1メモリ領域3101に属するメモリブロックは第2メモリ領域3102に属するメモリブロックと異なる方式にプログラムされる。例えば、第1メモリ領域3101に属するメモリブロックは単一ビットプログラム方式(以下、SLCプログラム方式と称する)にしたがってプログラムされ、第2メモリ領域3102に属するメモリブロックはマルチビットプログラム方式(以下、MLCプログラム方式と称する)にしたがってプログラムされる。言い換えれば、第1メモリ領域3101に属するメモリセルの各々は1ビットデータを格納し、第2メモリ領域3102に属するメモリセルの各々はMビットデータ(Mは2又はそれより大きい整数)を格納する。結果的に、第1メモリ領域3101に属するメモリセルの各々は第2メモリ領域3102に属するメモリセルの各々に格納されるMビットデータより小さい数のデータビットを格納する。

【0126】

続いて図14を参照すれば、メモリ制御器3200はホスト3300の要請に応答してマルチビットメモリ装置3100を制御するように構成される。メモリ制御器3200はバッファメモリ3201とエラー検出及び訂正回路3202とを含む。バッファメモリ3201はホスト3300から伝送されたデータを臨時に格納するのに、そしてマルチビットメモリ装置3100から読み出されたデータを臨時に格納するのに使用される。エラー検出及び訂正回路3202はマルチビットメモリ装置3100に格納されるデータを符号化するように、そしてマルチビットメモリ装置3100から読み出されたデータを復号化するように構成される。符号化はパリティー情報を生成する動作を含み、パリティー情報はフィールド単位で生成され得る。1ページのデータは1つ又はそれより多いフィールドで構成され得る。復号化はエラー検出動作とエラー訂正動作とを含む。先に説明された複写動作の時、エラー検出動作はメモリ制御器3200によって行われ、エラー訂正動作はマルチビットメモリ装置3100によって行われる。

【0127】

メモリ制御器3200は静的なスケジューリング方式(static scheduling manner)にメモリ装置3100のプログラム動作を制御する。例えば、第1メモリ領域3101に対する最小プログラム単位のデータがバッファメモリ3201に格納されれば、メモリ制御器3200は最小プログラム単位のデータが第1メモリ領域3101に格納されるようにマルチビットメモリ装置3100を制御する。これはバッファプログラム動作と称する。第2メモリ領域3102に対する最小プログラム単位のデータが第1メモリ領域3101に集まれれば、メモリ制御器3200は第2メモリ領域3102に対する最小プログラム単位のデータが第2メモリ領域3102に格納されるようにマルチビットメモリ装置3100を制御する。これはメインプログラム動作と称する。バッファプログラム動作とメインプログラム動作とはオンチップバッファプログラミング動作を構成する。

【0128】

本発明の例示的な実施形態によれば、メインプログラム動作は第1メモリ領域3101でからみ出されたデータが第2メモリ領域3102に複写される以前に行われるエラー検出動作とエラー訂正動作とを含む。エラー検出動作はメモリ制御器3200によって行われ、エラー訂正動作はマルチビットメモリ装置3100によって行われる。これは以後詳細に説明される。

【0129】

例示的な実施形態において、第1メモリ領域3101に対する最小プログラム単位と第2メモリ領域3102に対する最小プログラム単位とはプログラム方式、セル当りビット数、等にしたがって多様に決定される。第1メモリ領域3101に対する最小プログラム単位は第2メモリ領域3102に対する最小プログラム単位と異なる。

【0130】

例示的な実施形態において、バッファプログラム動作を通じて第1メモリ領域3101にデータを格納し、メインプログラム動作を通じて第2メモリ領域3102にデータを格納することによってメモリ制御器3200のバッファメモリ3201の大きさを最小化させ得る。言い換えれば、バッファメモリ3201に精巧なプログラム動作のためのデータを維持する必要が無い。そのような理由で、メモリ制御器3200のバッファメモリ3201の大きさを最小化させ得る。

【0131】

図15A乃至図15Dは本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。図面で、“BP”は第1メモリ領域3101に対するバッファプログラミングを示し、“MP”は第2メモリ領域3102に対するメインプログラミングを示す。

【0132】

先に説明されたように、マルチビットメモリ装置3100は第1メモリ領域3101と第2メモリ領域3102とを含む。ここで、第1メモリ領域3101と第2メモリ領域3102とはマルチビットメモリ装置3100のメモリセルアレイを構成する。たとえ図面には図示せずが、メモリセルアレイはさらに多い領域(例えば、メタ領域、予備領域、等)を含む。メモリセルアレイのメモリ領域が物理的に区分されることでは無く、論理的に区分されることはよく理解できる。これはメモリ制御器3200のアドレスマッピングにしたがって領域が定義されることを意味する。

【0133】

図15Aを参照すれば、セル当り3ビットデータを格納するマルチビットメモリ装置の場合、第1メモリ領域3101は1ビットデータを各々格納するメモリセルで構成され、第2メモリ領域3102は3ビットデータを各々格納するメモリセルで構成され得る。この場合、バッファプログラミングはSLCプログラム方式にしたがって行われる。メインプログラミングは先に説明されたMLCプログラム方式にしたがって行われる。

【0134】

図15Bを参照すれば、セル当り4ビットデータを格納するマルチビットメモリ装置の場合、第1メモリ領域3101は1ビットデータを各々格納するメモリセルで構成され、第2メモリ領域3102は4ビットデータを各々格納するメモリセルで構成され得る。この場合、バッファプログラミングはSLCプログラム方式にしたがって行われる。メインプログラミングは先に説明されたMLCプログラム方式にしたがって行われる。

【0135】

図15Cを参照すれば、セル当り3ビットデータを格納するマルチビットメモリ装置の場合、第1メモリ領域3101は2ビットデータを各々格納するメモリセルで構成され、第2メモリ領域3102は3ビットデータを各々格納するメモリセルで構成され得る。この場合、バッファプログラミングは一般的な又は先に説明されたMLCプログラム方式にしたがって行われる。メインプログラミングは先に説明されたMLCプログラム方式(例えば、再プログラム方式)にしたがって行われる。

【0136】

図15Dを参照すれば、セル当り4ビットデータを格納するマルチビットメモリ装置の場合、第1メモリ領域3101は2ビットデータを各々格納するメモリセルで構成され、第2メモリ領域3102は4ビットデータを各々格納するメモリセルで構成され得る。この場合、バッファプログラミングは一般的な又は先に説明されたMLCプログラム方式にしたがって行われる。メインプログラミングは先に説明されたMLCプログラム方式(例えば、再プログラム方式)にしたがって行われる。

【0137】

例示的な実施形態において、図15A乃至図15Dに図示された第1及び第2メモリ領域3101、3102の定義がここに開示されたことに制限されない。例えば、データ格納システムに含まれる格納媒体が複数のマルチビットメモリ装置で構成される場合、各マルチビットメモリ装置に第1及び第2メモリ領域3101、3102が定義され得る。他の例として、任意のマルチビットメモリ装置のみに第1メモリ領域101が定義され得る。又は、任意のマルチビットメモリ装置が第1メモリ領域3101として定義され得る。

【0138】

図16は本発明の例示的な実施形態による1ステッププログラム動作のための命令シーケンスを示す図面であり、図17は図16に図示された1ステッププログラム命令シーケンスにしたがうデータの流れを示す図面である。図18はエラー訂正動作(又は、ビットフリップ動作)にしたがうデータの流れを示す図面である。以下、本発明の例示的な実施形態によるデータ格納システムの動作が参照図面に基づいて詳細に説明される。

【0139】

1ステッププログラム動作は第2メモリ領域3102に対する最小プログラム単位(例えば、2ページ)が第1メモリ領域3101に格納された場合に行われる。メインプログラム動作として、第2メモリ領域3102に対する1ステッププログラム動作は第1メモリ領域3101に対する2回のSLC読出し動作と第2メモリ領域3102に対する1回のMLCプログラム動作とを随伴する。各SLC読出し動作は先に説明されたエラー検出動作とエラー訂正動作とを含む。

【0140】

本発明の例示的な実施形態によるデータ格納システム3000の場合、1ステッププログラム動作を遂行される先に、SLC動作モードの転換のための命令DAhがメモリ制御器3200からマルチビットメモリ装置3100へ伝送される。モード転換のための命令DAhが入力される時、マルチビットメモリ装置3100はメモリ制御器3200から提供される命令をSLC動作に関連された命令として認識する。

【0141】

モード転換のための命令DAhに続いて、図16に図示されたように、メモリ制御器3200は一連の命令00h、アドレスADDR、及び命令39hをマルチビットメモリ装置3100へ伝送する。この時、アドレスADDRは1ステッププログラム動作に必要である2ページデータの中の1つのページを指定するためのアドレスである。命令39hが入力された後、マルチビットメモリ装置3100のページバッファ3103は、図17に図示されたように、第1メモリ領域3101から第1番目のデータを読み出す。読み出されたデータはSラッチユニットに格納される。読出し動作の間に、図16に図示されたように、マルチビットメモリ装置3100はビジー状態を示すようにレディ/ビジー信号RnBを設定する。読出し動作が完了された後、マルチビットメモリ装置3100はレディ状態を示すようにレディ/ビジー信号RnBを設定する。

【0142】

その次に、図16に図示されたように、マルチビットメモリ装置3100からメモリ制御器3200へ読み出されたデータが出力される。データ出力に先に、SラッチユニットのデータはCラッチユニットへダンプされる。Cラッチユニットへダンプされたデータはメモリ制御器3200へ出力される。メモリ制御器3200は先に説明されたことと実質的に同一な方式にエラー検出動作を遂行し、エラー検出動作の結果としてエラー位置情報及びエラーフラッグ情報を生成する。エラー検出動作が遂行された後、メモリ制御器3200は一連の命令86h、アドレスADDR、及びデータEFIをマルチビットメモリ装置3100へ伝送する。ここで、データEFIはエラーフラッグ情報を含み、図17に図示されたように、Cラッチユニットへロードされる。エラーフラッグ情報は図9で説明された方式又は図10で説明された方式にしたがって伝送される。図9で説明された方式の場合、たとえ図面には図示せずが、図16に図示されたエラーフラッグ入力手続86h、ADDR、EFIがエラービットの数程度に反複される。

【0143】

エラーフラッグ情報の伝送に続いて、メモリ制御器3200は一連の命令C0h及びアドレスADDRをマルチビットメモリ装置3100へ伝送する。ここで、命令C0hは先に説明されたビットフリップ動作(又は、エラー訂正動作)の実行を通知する命令であり、アドレスADDRはエラー訂正されたデータが格納されたラッチユニットを指定するためのアドレスである。一連の命令C0h及びアドレスADDRの入力に続いて、レディ/ビジー信号RnBはビジー状態に設定される。レディ/ビジー信号RnBのビジー状態の間に、先に説明されたエラー訂正動作(又は、ビットフリップ動作)が行われる。

【0144】

エラー訂正動作(又は、ビットフリップ動作)にしたがうデータの流れを示す図18を参照すれば、ST1段階で、メモリ制御器3200から提供されたエラーフラッグ情報はCラッチユニットへロードされる。ST2段階で、Cラッチユニットへロードされたエラーフラッグ情報はSラッチユニットへダンプされる。この時、CラッチユニットからSラッチユニットへダンプされるデータは反転される。ST3段階で、XNOR演算を通じてSラッチユニットのデータがLラッチユニットへダンプされる。この時、LラッチユニットへダンプされたデータはXNOR演算を通じてエラー訂正されたデータである。エラー訂正されたデータが格納される位置、即ちLラッチユニットは命令C0hと共に入力されたアドレスADDRによって指定される。反転演算及びXNOR演算はビットフリップ動作に対応するXOR演算を構成する。先に説明された動作(即ち、エラーフラッグローディング、エラーフラッグ反転、及びXNOR演算を包含する)は表2乃至表5で説明されたことと実質的に同様に遂行され、それに対する説明はしたがって省略される。

【0145】

再び図16を参照すれば、エラー訂正動作(又は、ビットフリップ動作)が完了された後、マルチビットメモリ装置3100はレディ状態を示すようにレディ/ビジー信号RnBを設定する。メモリ制御器3200はレディ/ビジー信号RnBの状態に応答してマルチビットメモリ装置3100に一連の命令00h、アドレスADDR、及び命令39h)をマルチビットメモリ装置3100へ伝送する。この時、アドレスADDRは1ステッププログラム動作に必要である2ページデータの中の残りページを指定するためのアドレスである。命令39hが入力された後、マルチビットメモリ装置3100のページバッファ3103は、図17に図示されたように、第1メモリ領域3101からデータを読み出す。読み出されたデータはSラッチユニットに格納される。読出し動作の間に、図16に図示されたように、マルチビットメモリ装置3100はビジー状態を示すようにレディ/ビジー信号RnBを設定する。読出し動作が完了された後、マルチビットメモリ装置3100はレディ状態を示すようにレディ/ビジー信号RnBを設定する。

【0146】

その次に、図16に図示されたように、マルチビットメモリ装置3100からメモリ制御器3200へ読み出されたデータが出力される。データ出力の前に、図17に図示されたように、SラッチユニットのデータはCラッチユニットへダンプされる。Cラッチユニットへダンプされたデータはメモリ制御器3200へ出力される。メモリ制御器3200は先に説明されたことと実質的に同一な方式にエラー検出動作を遂行し、エラー検出動作の結果としてエラー位置情報及びエラーフラッグ情報を生成する。エラー検出動作が遂行された後、メモリ制御器3200は一連の命令86h、アドレスADDR、及びデータEFIをマルチビットメモリ装置3100へ伝送する。ここで、データEFIはエラーフラッグ情報を含み、図17に図示されたように、Cラッチユニットへロードされる。エラーフラッグ情報は図9で説明された方式又は図10で説明された方式にしたがって伝送される。図9で説明された方式の場合、たとえ図面には図示せずが、図16に図示されたエラーフラッグ入力手続86h、ADDR、EFIがエラービットの数程度反複される。

【0147】

エラーフラッグ情報の伝送に続いて、メモリ制御器3200は一連の命令C0h及びアドレスADDRをマルチビットメモリ装置3100へ伝送する。一連の命令C0h及びアドレスADDRの入力に続いて、レディ/ビジー信号RnBはビジー状態に設定される。レディ/ビジー信号RnBのビジー状態の間に、図18を参照して説明されたエラー訂正動作(又は、ビットフリップ動作)が行われる。但し、図17に図示されたように、エラー訂正されたデータは命令C0hと共に入力されたアドレスADDRによって指定されるFラッチユニットに格納される。

【0148】

先ず、1ステッププログラム動作に必要であるデータが準備されれば、第2メモリ領域3102に対する1ステッププログラム動作が行われる。1ステッププログラム動作を遂行される以前に、メモリ制御器3200はモード転換のための命令DFhをマルチビットメモリ装置3100へ伝送する。そのような命令DFhはSLC動作のためのモードから抜け出されるためのことである。命令DFhが入力されることにしたがって、マルチビットメモリ装置3100はメモリ制御器3200から提供される命令をメインプログラム動作、例えば、MLC動作に関連された命令として認識する。

【0149】

以後、メモリ制御器3200は、図16に図示されたように、一連の命令8Bh、アドレスADDR、及び命令10hをマルチビットメモリ装置3100へ伝送する。この時、アドレスADDRは1ステッププログラムされるページの中の1つを指定するためのアドレスである。1ステッププログラム動作に必要であるデータがページバッファ3103に準備されているので、メモリ制御器3200からマルチビットメモリ装置3100へデータが伝送されない。命令10hが入力された後、図17に図示されたように、ページバッファ3103に格納されたデータは第2メモリ領域3102にプログラムされる。プログラム動作の間に、図16に図示されたように、マルチビットメモリ装置3100はビジー状態を示すようにレディ/ビジー信号RnBを設定する。プログラム動作が完了された後、マルチビットメモリ装置3100はレディ状態を示すようにレディ/ビジー信号RnBを設定する。

【0150】

図19は粗いプログラム動作のための命令シーケンスを示す図面であり、図20は図19に図示された粗いプログラム命令シーケンスにしたがうデータの流れを示す図面である。以下、本発明の例示的な実施形態によるデータ格納システムの動作が参照図面に基づいて詳細に説明される。

【0151】

詳細は後ほど説明するとして、粗いプログラム動作は第2メモリ領域3102に対する最小プログラム単位(例えば、3ページ)が第1メモリ領域3101に格納された場合に行われる。第2メモリ領域3102に対する粗いプログラム動作は第1メモリ領域3101に対する3回のSLC読出し動作と第2メモリ領域3102に対する1回のMLCプログラム動作とを随伴する。

【0152】

SLC読出し動作の各々は、図20に図示されたように、図16乃至図18で説明されたことと実質的に同一であるので、それに対する説明は省略される。第1番目のSLC読出し動作を遂行される以前に、図19に図示されたように、モード転換のための命令DAhがメモリ制御器3200からマルチビットメモリ装置3100へ伝送される。第2メモリ領域3102に対するMLCプログラム動作は3ビットデータが第2メモリ領域3102に格納されるは点を除外すれば、図16乃至図18で説明されたことと実質的に同一であるので、それに対する説明は省略される。粗いプログラム動作を遂行される以前に、図19に図示されたように、モード転換のための命令DFhがメモリ制御器3200からマルチビットメモリ装置3100へ伝送される。たとえ図面には図示せずが、メインプログラム動作として精巧なプログラム動作は図19に図示された命令シーケンスにしたがって同様に行われる。

【0153】

図16乃至図20を参照して説明された1ステッププログラム動作及び粗いプログラム動作がここに開示されたことに制限されない。また、オンチップバッファプログラム方式もやはりここに開示されたことに制限されない。

【0154】

粗い/精巧なプログラム動作及び精巧なプログラム動作の時、SLC読出し動作が連続的に3回行われる。このような場合、図20に図示されたことと異なりに、第1番目のSLC読出し動作を通じて読み出されたデータは第2番目のSLC読出し動作が行われる間にメモリ制御器2000へ出力され、メモリ制御器2000は第2番目のSLC読出し動作が行われる間にエラーフラッグ情報を生成する。言い換えれば、本発明の他の実施形態による粗い/精巧なプログラム動作の時のデータの流れを説明するための図21を参照すれば、SLC読出し動作が連続的に実行される場合、以前のSLC読出し動作に関連されたデータ出力動作及びエラーフラッグ生成動作は次のSLC読出し動作が実行される間に行われる。

【0155】

図22は本発明の例示的な実施形態によるメモリシステムのリフレッシュプログラム動作を概略的に説明するための図面である。

【0156】

反複的なプログラム/消去サイクルはメモリトランジスター酸化膜にストレスを加え、そのようなストレスはメモリトランジスターのトンネル酸化膜がブレークダウンに成るようにする。メモリセルの閾値電圧はそのようなストレスによって漸次的に低くなる。即ち、プログラムされたメモリセルの電荷格納層から電子が漏洩される。これはプログラムされたメモリセルの閾値電圧散布が低い電圧の方に移動されるようにし、その結果プログラム検証電圧より低い閾値電圧を有するメモリセルが発生されるようになる。これは読出しマージンの減少によって読出しフェイルが発生され得ることを意味する。読出しフェイルが発生される以前にプログラム検証電圧より低い閾値電圧を有するメモリセルを再プログラムすることが可能である。このような動作をリフレッシュプログラム動作が称する。

【0157】

図22を参照すれば、再プログラム/リフレッシュプログラム動作の時、先ず、ページバッファ回路1500のメインバッファMBを通じてメモリセルアレイMCAの特定ページからデータを読み出す。メインバッファMBに格納された読み出されたデータはキャッシュバッファCBを通じてメモリ制御器2000へ伝送される。ここで、メインバッファMBはSラッチユニット1521で構成され得、キャッシュバッファCBはCラッチユニット1525で構成され得る。しかし、本発明はそれに制限されない。メインバッファMBとキャッシュバッファCBとはページバッファ回路1500を構成する。メモリ制御器2000へ伝送されたデータはランダム化器/デランダム化器2600を通じてデランダム化され、エラー検出及び訂正回路2500はランダム化器/デランダム化器2600によってデランダム化されたデータに対するエラー検出動作を遂行する。ここで、不揮発性メモリ装置1000から出力される読み出されたデータRDのデランダム化されたデータはバッファメモリ2400に格納される。エラー検出動作の結果として、エラーフラッグ情報が不揮発性メモリ装置1000のキャッシュバッファCBへ伝送される。ここで、エラーフラッグ情報は図9で説明された方式又は図10で説明された方式にしたがってメモリ制御器2000から不揮発性メモリ装置1000へ伝送される。エラーフラッグ情報又はエラーフラッグ情報を含むフィールドデータはランダム化器/デランダム化器2600を経由しなくて直接不揮発性メモリ装置1000へ伝送される。キャッシュバッファCBに格納されたエラーフラッグ情報に基づいてビットフリップ動作(又は、エラー訂正動作)が行われ、ビットフリップ動作(又は、エラー訂正動作)を通じて訂正されたデータはメインバッファMBを通じてメモリセルアレイMCAの特定ページ(即ち、データが読み出された位置はエラー訂正されたデータが格納される位置と同一である)に格納される。即ち、特定ページから読み出されたデータに対する再プログラム動作が行われる。言い換えれば、特定ページのメモリセルがリフレッシュされる。ビットフリップ動作(又は、エラー訂正動作)は表3乃至図5で説明されたことと実質的に同一であるので、それに対する説明は省略される。

【0158】

リフレッシュプログラム動作に対する追加的なそしてより詳細な説明は特許文献4に開示され、この出願のレファレンスとして包含される。

【0159】

図23は本発明のその他の例示的な実施形態によるメモリシステムを概略的に示すブロック図である。図23を参照すれば、メモリシステム3000は不揮発性メモリ装置3100aとメモリ制御器3200bとを含む。

【0160】

不揮発性メモリ装置3100aはメモリセルアレイ3110、行デコーダー回路3120、電圧発生回路3130、制御ロジック3140、ページバッファ回路3150、及び入出力インターフェイス3160を含む。図23において、メモリセルアレイ3110、行デコーダー回路3120、及び電圧発生回路3130は図4に図示されたことと実質的に同一であるので、それに対する説明は省略される。制御ロジック3140は不揮発性メモリ装置3100aの全般的な動作を制御するように構成される。制御ロジック3140はランダムシーケンスデータ発生器3141(図面には、RDGで示した)を含む。ランダムシーケンスデータ発生器3140はシード値を利用してランダムシーケンスデータを発生する。ランダムシーケンスデータは入出力インターフェイス3160を通じてページバッファ回路3150へ伝達される。

【0161】

ページバッファ回路3150は制御ロジック3140の制御にしたがってプログラムデータ及びランダムシーケンスデータに対するXOR演算を遂行し、その結果、プログラムデータがランダム化される。また、ページバッファ回路3150はメモリセルアレイ3110から読み出されたデータとランダムシーケンスデータとに対するXOR演算を遂行し、その結果読み出されたデータ(又は、ランダム化された読み出されたデータ)がデランダム化される。ページバッファ回路3150は制御ロジック3140の制御の下に先に説明されたエラー訂正動作(又は、ビットフリップ動作)を遂行する。ここで、データランダム化がエラー訂正の先に行われるか、或いはデータランダム化がエラー訂正に続いて行われ得る。

【0162】

メモリ制御器3200aはバッファメモリ3210とエラー検出及び訂正回路3220とを含む。バッファメモリ3210は不揮発性メモリ装置3100aから読み出されたデータを臨時格納するように構成される。エラー検出及び訂正回路3220は不揮発性メモリ装置3100aから読み出されたデータのエラーを検出し、エラー検出結果としてエラー位置情報及びエラーフラッグ情報を発生する。これは先に説明されたことと実質的に同様に行われ、それに対する説明はしたがって省略される。エラー位置情報及びエラーフラッグ情報は図9で説明された方式に又は図10で説明された方式に不揮発性メモリ装置3100aへ伝送される。

【0163】

結論的に、エラー検出はメモリ制御器3200aによって行われ、エラー訂正及びデータランダム化/デランダム化(又は、オンチップランダム化/デランダム化)は不揮発性メモリ装置3100aによって行われる。

【0164】

図24は本発明の例示的な実施形態によるコンピューティングシステムを概略的に示すブロック図である。

【0165】

コンピューティングシステムはマイクロプロセッサー2101、使用者インターフェイス2202、ベースバンドチップセット(baseband chipset)のようなモデム2303、メモリ制御器2404、及び格納媒体として不揮発性メモリ装置2505を含む。メモリ制御器2404と不揮発性メモリ装置2505とは図1に図示されたこと又は図14に図示されたことと実質的に同様に構成される。即ち、エラー検出がメモリ制御器2404によって行われ、エラー訂正が不揮発性メモリ装置2505内で行われるので、メモリ制御器から不揮発性メモリ装置へデータを伝送するのに掛かる時間及び/又はメモリ制御器から不揮発性メモリ装置へデータを伝送するのに消耗される電力が減少される。不揮発性メモリ装置2505にはマイクロプロセッサー2101によって処理された/処理されるNビットデータ(Nは1又はそれより大きい整数)がメモリ制御器2404を通じて格納される。コンピューティングシステムがモバイル装置である場合、コンピューティングシステムの動作電圧を供給するためのバッテリー2606が追加的に提供される。たとえ図面には図示せずが、本発明によるコンピューティングシステムには応用チップセット(application chipset)、カメライメージプロセッサー(Camera Image Processor:CIS)、モバイルDRAM、等がさらに提供され得ることは理解できる。

【0166】

図25は本発明の例示的な実施形態による半導体ドライブを概略的に示すブロック図である。

【0167】

図25を参照すれば、半導体ドライブ4000(SSD)は格納媒体4100と制御器4200とを含む。格納媒体4100は複数のチャンネルを通じて制御器4200に連結される。各チャンネルには複数の不揮発性メモリが共通に連結される。各不揮発性メモリは図1で説明されたメモリに構成され、制御器4200は図1乃至図19を参照して説明された方式にしたがって格納媒体4100を制御するように構成される。即ち、エラー検出がメモリ制御器2404によって行われ、エラー訂正が不揮発性メモリ装置2505内で行われるので、メモリ制御器から不揮発性メモリ装置へデータを伝送するのに掛かる時間及び/又はメモリ制御器から不揮発性メモリ装置へデータを伝送するのに消耗される電力が減少される。

【0168】

図26は図25に図示された半導体ドライブを利用するストレージを概略的に示すブロック図であり、図27は図25に図示された半導体ドライブを利用するストレージサーバーを概略的に示すブロック図である。

【0169】

本発明の例示的な実施形態による半導体ドライブ4000はストレージを構成するのに使用され得る。図26に図示されたように、ストレージは図25で説明されたことと実質的に同様に構成される複数の半導体ドライブを含む。本発明の例示的な実施形態による半導体ドライブ4000はストレージサーバーを構成するのに使用され得る。図27に図示されたように、ストレージサーバーは図25で説明されたことと実質的に同様に構成される複数の半導体ドライブ4000、及びサーバー4000Aを含む。また、この分野に広く公知されたRAID制御器4000Bがストレージサーバーとして提供され得ることは理解できる。

【0170】

図28乃至図30は本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【0171】

本発明の例示的な実施形態によるメモリ制御器及びマルチビットメモリ装置に構成されるデータ格納装置を含む半導体ドライブがストレージに適用される場合、図28に図示されたように、システム6000は有線及び/又は無線でホストと通信するストレージ6100を含む。本発明の例示的な実施形態によるデータ格納装置を含む半導体ドライブがストレージサーバーに適用される場合、図29に図示されたように、システム7000は有線及び/又は無線でホストと通信するストレージサーバー7100、7200を含む。また、図30に図示されたように、本発明の例示的な実施形態によるデータ格納装置を含む半導体ドライブはメールサーバー8100にも適用され得る。

【0172】

図31は本発明の実施形態によるメモリカード(memory card)を概略的に示すブロック図である。

【0173】

メモリカードは、例えばMMCカード、SDカード、マルチユーズ(multiuse)カード、マイクロSDカード、メモリスティック、コンパクトSDカード、IDカード、PCMCIAカード、SSDカード、チップカード(chipcard)、スマトカード(smartcard)、USBカード等であり得る。

【0174】

図31を参照すれば、メモリカードは外部とのインターフェイスを遂行するインターフェイス部9221、バッファメモリを有し、メモリカードの動作を制御する制御器9222、1つ又はそれより多い不揮発性メモリ装置9207を含む。制御器9222はプロセッサーとして、不揮発性メモリ装置9207の書込み動作及びリード動作を制御することができる。具体的に、コントローラ9222はデータバス(DATA)とアドレスバス(ADDRESS)とを通じて不揮発性メモリ装置9207及びインターフェイス部9221とカップリングされている。制御器9222と不揮発性メモリ9207とは図1で説明された又は図14で説明されたメモリ制御器と不揮発性メモリ装置とに対応する。制御器9222は図1乃至図19を参照して説明された方式にしたがって不揮発性メモリ9207を制御するように構成される。即ち、エラー検出がメモリ制御器によって行われ、エラー訂正が不揮発性メモリ装置内で行われるので、メモリ制御器から不揮発性メモリ装置へデータを伝送するのに掛かる時間及び/又はメモリ制御器から不揮発性メモリ装置へデータを伝送するのに消耗される電力が減少される。

【0175】

図32は本発明の実施形態によるデジタルスチールカメラ(digital still camera)を概略的に示すブロック図である。

【0176】

図32を参照すれば、デジタルスチールカメラはボディー9301、スロット9302、レンズ9303、ディスプレイ部9308、シャッターボタン9312、ストロボ(strobe)9318等を含む。特に、スロット9308にはメモリカード9331が挿入され得り、メモリカード9331は図1で説明された又は図14で説明されたメモリ制御器及び不揮発性メモリ装置を含む。メモリカード9331内に含まれたメモリ制御器は図1乃至図19を参照して説明された方式にしたがってメモリ装置を制御するように構成される。即ち、エラー検出がメモリ制御器によって行われ、エラー訂正が不揮発性メモリ装置内で行われるので、メモリ制御器から不揮発性メモリ装置へデータを伝送するのに掛かる時間及び/又はメモリ制御器から不揮発性メモリ装置へデータを伝送するのに消耗される電力が減少される。

【0177】

メモリカード9331が接触形(contact type)である場合、メモリカード9331がスロット9308に挿入される時、メモリカード9331と回路基板の上の特定電気回路とが電気的に接触される。メモリカード9331が非接触形(non−contact type)である場合、無線信号を通じてメモリカード9331がアクセスされる。

【0178】

図33は図32のメモリカードが使用される多様なシステムを説明する例示的な図面である。

【0179】

図32を参照すれば、メモリカード9331はビデオカメラ(VC)、テレビジョン(TV)、オーディオ装置(AD)、ゲーム装置(GM)、電子音楽装置(EMD)、携帯電話(HP)、コンピューター(CP)、PDA(Personal Digital Assistant)、ボイスレコーダー(voice recorder)(VR)、PCカード(PCC)、等に使用され得る。

【0180】

本発明の例示的な実施形態において、メモリセルは可変抵抗メモリセルから構成され得り、例示的な可変抵抗メモリセル及びそれを含むメモリ装置が特許文献5に開示され、この出願のレファレンスとして包含される。

【0181】

本発明の他の例示的な実施形態において、メモリセルは電荷格納層を有する多様なセル構造の中から1つを利用して具現され得る。電荷格納層を有するセル構造は電荷トラップ層を利用する電荷トラップフラッシュ構造、アレイが多層に積層されるスタックフラッシュ構造、ソースドレーンが無いフラッシュ構造、ピンタイプフラッシュ構造、等を含む。

【0182】

電荷格納層として電荷トラップフラッシュ構造を有するメモリ装置が特許文献6、特許文献7、及び特許文献8に各々開示され、この出願のレファレンスとして包含される。ソース/ドレーンが無いフラッシュ構造は特許文献9に開示され、この出願のレファレンスとして包含される。

【0183】

本発明によるフラッシュメモリ装置及び/又はメモリ制御器は多様な形態のパッケージを利用して実装され得る。例えば、本発明によるフラッシュメモリ装置及び/又はメモリコントローラはPoP(Package on Package)、Ball grid arrays(BGAs)、Chip scale packages(CSPs)、Plastic Leaded Chip Carrier(PLCC)、Plastic Dual In−Line Package(PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board(COB)、Ceramic Dual In−Line Package(CERDIP)、Plastic Metric Quad Flat Pack(MQFP)、Thin Quad Flatpack(TQFP)、Small Outline(SOIC)、Shrink Small Outline Package(SSOP)、Thin Small Outline(TSOP)、In Package(SIP)、Multi Chip Package(MCP)、Wafer−level Fabricated Package(WFP)、Wafer−Level Processed Stack Package(WSP)等のようなパッケージを利用して実装され得る。

【0184】

本発明の範囲又は技術的思想を逸脱しなく本発明の構造が多様に修正されるか、或いは変更され得ることはこの分野に熟練された者に明確である。上述した内容を鑑みて見る時、仮に本発明の修正及び変更が下の請求項及び同等物の範疇内に属すれば、本発明がこの発明の変更及び修正を含むことと看做す。

【符号の説明】

【0185】

1000・・・不揮発性メモリ装置

1100・・・メモリセルアレイ

1200・・・アドレスデコーダー

1300・・・電圧発生器

1400・・・制御ロジック

1500・・・ペ−ジバッファ回路

1600・・・入出力インタ−フェイス

2000・・・メモリ制御器

2100・・・ホストインターフェイス

2200・・・メモリインターフェイス

2300・・・処理ユニット

2400・・・バッファメモリ

2600・・・ランダム化器/デランダム化器

【技術分野】

【0001】

本発明は不揮発性メモリ装置及び制御器を含むメモリシステムに関する。

【背景技術】

【0002】

半導体メモリは、一般的に、衛星から消費者電子技術までの範囲に属するマイクロプロセッサーを基づいた応用及びコンピューターのようなデジタルロジック設計の最も必須的なマイクロ電子素子である。したがって、高い集積度及び速い速度のための縮小(Scaling)を通じて得られるプロセスの向上及び技術開発を含む半導体メモリの製造技術の進歩は他のデジタルロジック系列の性能基準を確立するのに役に立つ。

【0003】

半導体メモリ装置は大きく揮発性半導体メモリ装置と不揮発性半導体メモリ装置とに分けられる。揮発性半導体メモリ装置において、ロジック情報はスタティックランダムアクセスメモリの場合、双安定フリップフロップのロジック状態を設定することによって又はダイナミックランダムアクセスメモリの場合、キャパシターの充電を通じて格納される。揮発性半導体メモリ装置の場合、電源が印加される間にデータが格納され、読み出され、電源が遮断される時データは消失される。

【0004】

MROM、PROM、EPROM、EEPROM、PRAM、等のような不揮発性半導体メモリ装置は電源が遮断されてもデータを格納できる。不揮発性メモリデータ格納状態は使用される製造技術によって永久的であるか、或いは再プログラムできる。不揮発性半導体メモリ装置はコンピューター、航行電子工学、通信、及び消費者電子技術産業のような広い範囲の応用でプログラム及びマイクロコードを格納するために使用される。単一チップで揮発性及び不揮発性メモリ格納モードの組合が速くて再プログラムできる不揮発性メモリを要求するシステムで不揮発性RAM(nvRAM)のような装置でまた使用できる。その上に、応用指向業務のための性能を最適化させるために幾つかの追加的なロジック回路を含む特定メモリ構造が開発されてくる。

【0005】

不揮発性半導体メモリ装置において、MROM、PROM、及びEPROMはシステム自体的に消去及び書込みが容易でないので、一般の使用者が記憶内容を新しくするのが容易でない。これに反して、EEPROM、PRAM、等のような不揮発性半導体メモリ装置は電気的に消去及び書込みができるので、継続的な更新が必要であるシステムプログラミング(system programming)や補助記憶装置としての応用が拡大されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許公報第7,941,586号公報

【特許文献2】米国特許公開第20080/0023747号公報

【特許文献3】米国特許公開第2008/0084729号公報

【特許文献4】米国特許第7,697,359号公報

【特許文献5】米国特許第7,529,124号公報

【特許文献6】米国特許第6,858,906号公報

【特許文献7】米国公開特許第2004−0169238号公報

【特許文献8】米国公開特許第2006−0180851号公報

【特許文献9】韓国特許第10−673020号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は動作速度を向上させることができるメモリシステム及びそれの動作方法を提供することにある。

【0008】

本発明の他の目的は電力消耗を減らすことができるメモリシステム及びそれの動作方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明の例示的な実施形態はデータを読出し、エラー情報を受信し、前記受信したエラー情報にしたがって前記読出しデータを訂正するように構成された不揮発性メモリ装置と、前記読出しデータを受信するように構成され、インターフェイスが前記受信したデータのエラービット位置に前記エラー情報を出力するように前記受信したデータのエラービットの位置を決定するユニットを有する制御器と、を含み、前記エラー情報は前記読み出されたデータのビットに対応したビットを含み、前記エラー情報のビットは前記読み出されたデータのビットのエラーを示すビットを含み、前記読み出されたデータのビットの値は前記エラー情報のビットの値にしたがって変更されるメモリシステムを提供する。

【0010】

前記不揮発性メモリ装置は前記読み出されたデータを前記制御器へ出力し、前記エラー情報を前記制御器から受信する。

【0011】

前記制御器は前記エラー情報を前記不揮発性メモリ装置へ出力し、前記エラー情報は前記読み出されたデータと前記読み出されたデータの訂正データとを包含しない。

【0012】

前記不揮発性メモリ装置はランダム化されたデータとして前記読み出されたデータを前記制御器へ出力し、デランダム化されたデータとして前記エラー情報を前記制御器から受信する。

【0013】

前記不揮発性メモリ装置は前記読み出されたデータが前記エラー情報にしたがって訂正されるように前記読み出されたデータを前記制御器へ出力した後、そして前記エラー情報が前記制御器から入力される時に前記前記読み出されたデータを格納するページバッファを含む。

【0014】

前記エラー情報は前記読み出されたデータの全てのビットと対応しているわけではない。

【0015】

前記不揮発性メモリ装置は変更されたビットとして前記受信したエラー情報のビットの値に対応する前記ビットの値を変更し、前記変更されたビットと維持されたビットとを前記訂正されたデータとして格納する。

【0016】

前記不揮発性メモリ装置は前記エラー情報に対応しないビットの値を維持し、前記変更された値を有する前記ビットと前記維持された値を有するビットとを含む前記訂正されたデータを格納する。

【0017】

前記不揮発性メモリ装置は単一ビットメモリアレイとマルチビットメモリアレイとを含み、前記データを前記単一ビットメモリアレイから読出し、前記訂正されたデータを前記マルチビットメモリアレイに格納する。

【0018】

前記不揮発性メモリ装置はSLCプログラム方法を利用してプログラムされた前記データを読出し、MLCプログラム方法によって前記訂正されたデータを格納する。

【0019】

前記不揮発性メモリ装置は前記制御器から前記エラー情報をページ単位で受信する。

【0020】

前記読み出されたデータと前記エラー情報とは同一なデータ大きさを有する。

【0021】

前記不揮発性メモリ装置は前記データを第1領域から第2領域に複写する複写動作の時、前記読み出されたデータに対応する前記エラー情報を受信する。

【0022】

前記不揮発性メモリ装置は複写動作を示す命令に応答して前記データを読み出すことと前記受信したエラー情報にしたがって前記訂正されたデータを格納することとを活性化させる。

【0023】

前記不揮発性メモリ装置は前記読み出されたデータのページ単位で前記エラー情報にしたがって前記エラーを有するビットを訂正するように構成されたページバッファラッチを含み、前記ページバッファラッチは前記読み出されたデータ、前記エラー情報、及び前記訂正されたデータを格納するように構成される。

【0024】

前記不揮発性メモリ装置は前記読み出されたデータのビットと前記エラー情報とをビット単位で比較して排他的OR方式又は排他的NOR方式にしたがって前記読み出されたデータのエラービットを訂正する。

【0025】

前記エラー情報のビットは前記読み出されたデータの他の1つのビットのエラー無しを示す第2ビットを含み、前記読み出されたデータの他の1つのビットの値は前記エラー情報の第2ビットの値にしたがって変更されない。

【0026】

本発明の例示的な実施形態は、また、データを出力する不揮発性メモリ装置と、前記不揮発性メモリ装置から前記データを受信するように構成され、インターフェイスが前記受信したデータのエラービット位置に情報を前記不揮発性メモリ装置へ出力するように前記受信したデータのエラービットの位置を決定するユニットを有する制御器と、を含むメモリシステムを提供する。

【0027】

前記制御器は前記受信したデータをデランダム化させて前記受信したデータから前記エラービットの位置を決定し、ランダム化無しで前記情報を出力する。

【0028】

前記制御器は前記受信したデータをデランダム化させるランダム化器/デランダム化器を含み、前記制御器は前記ランダム化器/デランダム化器が前記情報をランダム化することを防止する。

【0029】

前記不揮発性メモリ装置は前記受信したエラー位置情報にしたがって前記データを訂正する。

【0030】

前記不揮発性メモリ装置はデータが読み出された領域を含み、前記不揮発性メモリ装置は前記訂正されたデータにしたがって前記領域に対するリフレッシュ動作を遂行する。

【0031】

前記不揮発性メモリ装置は前記訂正されたデータを格納する第2領域を含み、前記第2領域はマルチビットメモリアレイである。

【0032】

前記受信したデータの決定されたエラービット位置に対する情報は前記不揮発性メモリ装置がアドレスにしたがって前記データを訂正するように前記読み出されたデータの決定されたエラービット位置のアドレスを含む。

【0033】

本発明の例示的な実施形態は、また、制御器と、第1プログラム方法によってデータを格納する単一ビットメモリアレイを含む第1領域とマルチビットメモリアレイを含む第2領域とを含み、複数のページ各々のデータを前記第1領域から読出し、そして前記複数のページ各々のデータを前記制御器へ出力するように構成された不揮発性メモリ装置と、を含み、前記制御器は前記複数のページ各々のデータのエラー位置情報を発生し、前記複数のページ各々のデータのエラー位置情報を前記不揮発性メモリ装置に出力し、前記不揮発性メモリ装置は前記複数のページ各々のデータに対応する前記エラー位置情報にしたがって前記複数のページ各々のデータを訂正し、前記複数のページの訂正されたデータを第2プログラム方法によって前記第2領域に1回に格納するメモリシステムを提供する。

【0034】

前記データは少なくとも第1ページ及び第2ページを有する複数のページを含み、前記制御器は第1エラー情報が前記第1ページに応答して決定されて出力されるように、そして第2エラー情報が前記第2ページに応答して決定されて出力されるように前記データを反復的に受信する。

【0035】

前記不揮発性メモリ装置は前記データを同時に読出し、前記エラー位置情報を受信する。

【0036】

前記不揮発性メモリ装置は前記読み出されたデータと前記受信したエラー位置情報とを同時に格納するバッファ回路を含む。

【0037】

前記不揮発性メモリ装置は前記読み出されたデータを読み出すメインバッファと前記エラー位置情報を受信するキャッシュバッファとを含み、前記エラー位置情報にしたがって前記メインバッファに格納されたデータを訂正する。

【0038】

前記不揮発性メモリ装置は前記読み出されたデータと前記訂正されたデータとを格納するように前記第1領域と前記第2領域と通信するメインバッファと、前記エラー位置情報を受信するように前記制御器と通信するキャッシュバッファと、を含む。

【0039】

前記不揮発性メモリ装置は前記エラー位置情報にしたがって前記読み出されたデータのビットを覆すフリップ動作を遂行して前記訂正されたデータを発生する。

【0040】

前記第2領域のマルチビットメモリアレイは3ビットメモリアレイを含む。

【0041】

前記第2プログラム方法は各々が前記第2領域のマルチビットメモリアレイに格納される前記訂正されたデータにしたがって異なる電圧を発生する複数の動作を含む。

【0042】

前記第2プログラム方法は前記第2領域のマルチビットメモリアレイに格納される前記訂正されたデータにしたがって異なる電圧を発生する再プログラム方法を含む。

【0043】

前記情報は前記読み出されたデータの部分の中の1つに対応し、前記読み出されたデータは前記制御器から前記不揮発性メモリ装置へ反復的に伝達され、一部の情報が前記読み出されたデータの全ての部分に対応する時まで前記制御器から前記不揮発性メモリ装置へ伝達され、前記不揮発性メモリ装置は前記対応する情報を受信する時、前記対応する情報にしたがって前記データの各部分を訂正する。

【0044】

前記メモリシステムは機能ユニットと前記不揮発性メモリ装置にデータを格納する前記制御器に連結できる端子を有するホスト装置とをさらに含む。

【0045】

前記ホスト装置は前記制御器を通じて前記不揮発性メモリ装置に格納される前記機能ユニットから生成されたデータを出力するか、或いは前記機能ユニットで使用されるデータを前記不揮発性メモリ装置から受信する。

【0046】

前記ホスト装置はビデオカメラ、テレビジョン装置、オーディオ装置、ゲーム機、電子音楽装置、携帯電話、コンピューター、PDA、ボイスレコーダー、移動装置、及び非接触式スマトカードの中で少なくとも1つを含む。

【発明の効果】

【0047】

本発明の実施形態によれば、動作速度を向上させることが可能である。また、電力消耗を減らすことが可能である。

【図面の簡単な説明】

【0048】

【図1】本発明の実施形態によるメモリシステムを概略的に示すブロック図である。

【図2】図1に図示されたメモリ制御器を概略的に示すブロック図である。

【図3】本発明の他の実施形態による図1に図示されたメモリ制御器を概略的に示すブロック図である。

【図4】本発明の一実施形態による図1に図示された不揮発性メモリ装置を概略的に示すブロック図である。

【図5】全てのビットラインメモリ構造又はオッドイ−ブンメモリ構造のためにメモリセルアレイをメモリブロックで構成する例を示す図面である。

【図6】本発明の例示的な実施形態による図5に図示されたページバッファ回路の一部を示すブロック図である。

【図7】本発明の実施形態による不揮発性メモリ装置のエラー訂正動作を概略的に説明するための図面である。

【図8】本発明の実施形態によるメモリシステムの複写動作を説明するためのフローチャートである。

【図9】図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。

【図10】本発明の他の実施形態による図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。

【図11】本発明の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【図12】本発明の他の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【図13A】マルチレベルメモリ装置に適用されるアドレススクランブル方式の一例を説明するための図面である。

【図13B】各メモリセル当たり3ビットデータを格納し、3ステッププログラム方式にしたがってプログラム動作が遂行される時に変化される閾値電圧分布を示す図面である。

【図14】本発明の例示的な実施形態によるデータ格納システムを概略的に示すブロック図である。

【図15A】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図15B】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図15C】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図15D】本発明の例示的な実施形態によるマルチビットメモリ装置の第1及び第2メモリ領域に対する多様な組合を説明するための図面である。

【図16】本発明の例示的な実施形態による1ステッププログラム動作のための命令シーケンスを示す図面である。

【図17】図16に図示された1ステッププログラム命令シーケンスにしたがうデータの流れを示す図面である。

【図18】エラー訂正動作(又は、ビットフリップ動作)にしたがうデータの流れを示す図面である。

【図19】粗いプログラム動作のための命令シーケンスを示す図面である。

【図20】図19に図示された粗いプログラム命令シーケンスにしたがうデータの流れを示す図面である。

【図21】本発明の他の実施形態による粗い/精巧なプログラム動作の時のデータの流れを説明するための図面である。

【図22】本発明の例示的な実施形態によるメモリシステムのリフレッシュプログラム動作を概略的に説明するための図面である。

【図23】本発明のその他の例示的な実施形態によるメモリシステムを概略的に示すブロック図である。

【図24】本発明の例示的な実施形態によるコンピューティングシステムを概略的に示すブロック図である。

【図25】本発明の例示的な実施形態による半導体ドライブを概略的に示すブロック図である。

【図26】図25に図示された半導体ドライブを利用するストレージを概略的に示すブロック図である。

【図27】図25に図示された半導体ドライブを利用する格納サーバーを概略的に示すブロック図である。

【図28】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図29】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図30】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図31】本発明の実施形態によるメモリカード(memory card)を概略的に示すブロック図である。

【図32】本発明の実施形態によるデジタルスチールカメラ(digital still camera)を概略的に示すブロック図である。

【図33】図32のメモリカードが使用される多様なシステムを説明する例示的な図面である。

【発明を実施するための形態】

【0049】

本発明の長所及び特徴、及びそれを達成する方法は添付される図面と共に詳細に後述する実施形態を通じて説明される。しかし、本発明はここで説明される実施形態に限定されなく他の形態に具体化されることもあり得る。単なる、本実施形態は本発明が属する技術分野で通常の知識を有する者に本発明の技術的思想を容易に実施できる程度に詳細に説明するために提供されることである。

【0050】

図面において、本発明の実施形態は図示された特定形態に制限されることではなく、明確性を期するために誇張されたことである。また、明細書全体に掛けて同一な参照番号に表示された部分は同一な構成要素を示す。

【0051】

本明細書で‘及び/又は’という表現は前後に羅列された構成要素の中で少なくとも1つを含む意味に使用される。また、‘連結される/結合される’という表現は他の構成要素と直接的に連結されたり、他の構成要素を通じて間接的に連結されたりすることを含む意味で使われる。本明細書で、単数型は文句で特別に言及しない限り複数型も含む。また、明細書で使用される‘含む’又は‘包含する’と言及された構成要素、段階、動作及び素子は1つ以上の他の構成要素、段階、動作、素子及び装置の存在又は追加を意味する。

【0052】

図1は本発明の実施形態によるメモリシステムを概略的に示すブロック図である。

【0053】

図1を参照すれば、本発明の実施形態によるメモリシステムは不揮発性メモリ装置1000とメモリ制御器2000とを含む。不揮発性メモリ装置1000はデータ情報を格納する一種の格納媒体として使用される。格納媒体は1つ又はそれより多いメモリチップで構成され得る。不揮発性メモリ装置1000とメモリ制御器2000とは1つ又はそれより多いチャンネルを通じて通信する。不揮発性メモリ装置1000は、例えば、NANDフラッシュメモリ装置を含む。メモリ制御器2000は外部装置(例えば、ホスト)の要請又は内部的な要請(例えば、マージ、ガーベッジコレクション、等のような背景動作に関連された要請)にしたがって不揮発性メモリ装置1000を制御するように構成される。

【0054】

例示的な実施形態において、不揮発性メモリ装置1000がNANDフラッシュメモリ装置に制限されない。例えば、不揮発性メモリ装置1000はNORフラッシュメモリ装置、抵抗性RAM(Resistive Random Access Memory:RRAM(登録商標))装置、相変化メモリ(Phase−Change Memory:PRAM)装置、磁気抵抗メモリ(Magnetoresistive Random Access Memory:MRAM)装置、強誘電体メモリ(Ferroelectric Random Access Memory:FRAM(登録商標))装置、スピン注入磁化反転メモリ(Spin Transfer Torque Random Access Memory:STT−RAM)、又はそのようなことで構成され得る。また、本発明の不揮発性メモリ装置1000は3次元アレイ構造を有するように具現され得る。3次元アレイ構造を有する不揮発性メモリ装置は垂直NANDフラッシュメモリ装置と称される。本発明は電荷格納層が伝導性浮遊ゲートで構成されたフラッシュメモリ装置のみで無く、電荷格納層が絶縁膜で構成されたチャージトラップ形フラッシュ(Charge Trap Flash、“CTF”と称される)メモリ装置にも全て適用できる。

【0055】

本発明の実施形態によるメモリシステムは不揮発性メモリ装置1000の第1格納領域から第2格納領域にデータを複写する動作(例えば、コピーバック動作:copyback operation)を支援する。第1格納領域から第2格納領域にデータを複写する動作は第1格納領域で読み出されたデータに対するエラー検出及び訂正動作を必然的に随伴する。これはデータ信頼性を高くするためである。ここで、第1格納領域は第2格納領域と異なるか、或いは同一であり得る。本発明のメモリシステムによれば、不揮発性メモリ装置1000から読み出されたデータRDのエラー検出(error detection)はメモリ制御器2000によって行われ、エラー訂正(error correction)は不揮発性メモリ装置1000内で行われる。特に、メモリ制御器2000は検出されたエラーの位置情報(以下、エラー位置情報と称される)及びパターン情報(以下、エラーフラッグ情報(error flag information)と称される)を不揮発性メモリ装置1000へ提供し、不揮発性メモリ装置1000はメモリ制御器2000から提供されるエラー位置情報及びエラーフラッグ情報に基づいてデータのエラーを訂正する。即ち、エラー検出の以後、メモリ制御器2000によってエラー訂正が行われないので(又は、エラー検出の以後、不揮発性メモリ装置1000によってエラー訂正が行われるので)、不揮発性メモリ装置1000から出力されたデータ(又は、訂正されたデータ)を全て不揮発性メモリ装置1000へ伝送する必要がない。これはメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに掛かる時間及び/又はメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに消耗される電力が減少されることを意味する。

【0056】

図2は図1に図示されたメモリ制御器を概略的に示すブロック図である。図2を参照すれば、メモリ制御器2000は第1インターフェイスとしてホストインターフェイス2100、第2インターフェイスとしてメモリインターフェイス2200、CPUのような処理ユニット2300、バッファメモリ2400、及びエラー検出及び訂正回路2500を含む。

【0057】

ホストインターフェイス2100は外部(又は、ホスト)とインターフェイスするように構成される。メモリインターフェイス2200は図1に図示された不揮発性メモリ装置1000とインターフェイスするように構成される。処理ユニット2300、例えばCPUはメモリ制御器2000の全般的な動作を制御するように構成される。例えば、処理ユニット2300はフラッシュ変換階層(Flash Translation Layer:FTL)のようなファームウェアを運用するように構成される。バッファメモリ2400はホストインターフェイス2100を通じて外部へ伝達されるデータを臨時格納するのに使用される。バッファメモリ2400はメモリインターフェイス2200を通じて不揮発性メモリ装置1000から伝達されるデータを臨時格納するのに使用される。

【0058】

エラー検出及び訂正回路2500は不揮発性メモリ装置1000に格納されるデータを符号化するように、そして不揮発性メモリ装置4100から読み出されたデータを復号化するように構成される。符号化はパリティー情報を生成する動作を含み、パリティー情報はフィールド単位で生成され得る。1ページのデータは1つ又はそれより多いフィールドで構成され得る。復号化はエラー検出動作とエラー訂正動作を含む。不揮発性メモリ装置1000で出力されたデータが外部へ伝送される時、エラー検出動作とエラー訂正動作とを含む復号化がエラー検出及び訂正回路2500によって行われる。先に説明された複写動作の時、エラー検出及び訂正回路2500はエラー訂正動作無しで不揮発性メモリ装置1000から読み出されたデータに対するエラー検出動作のみを遂行する。エラー検出及び訂正回路2500はエラー検出動作の結果としてエラー位置情報及びエラーフラッグ情報を発生し、エラー位置情報及びエラーフラッグ情報は処理ユニット2300の制御の下にメモリインターフェイス2200を通じて不揮発性メモリ装置1000へ伝送される。例えば、エラー位置情報はエラーが発生したデータビットを指定するための列アドレスを含み、エラーフラッグ情報はエラー位置情報によって指定される位置のデータビットがエラーであることを示すビット情報である。他の例として、エラー検出及び訂正回路2500はエラー検出動作の結果としてエラー位置情報によって指定される位置のデータビットがエラーであることを示すビット情報(即ち、エラーフラッグ情報)を包含するフィールドデータ(エラー訂正されたデータでないことに注意する)を不揮発性メモリ装置1000へ伝送する。これは以後詳細に説明される。

【0059】

たとえ図面には図示せずが、メモリ制御器2000はROMをさらに包含できる。ROMはフラッシュ変換階層(Flash Translation Layer:FTL)のようなファームウェアを格納するのに使用され得る。他の例として、ROMを包含しないようにメモリ制御器2000を構成することが可能である。このような場合、ROMに格納されるファームウェアはメモリ制御器2000によって制御される不揮発性メモリ装置1000に格納され、パワーアップの時に不揮発性メモリ装置1000からメモリ制御器2000へロードされる。

【0060】

例示的な実施形態において、ホストインターフェイス2100はコンピューターバス標準、ストレージバス標準、iFCP Peripheralバス標準等の中で1つ又はそれより多いことの組合で構成され得る。コンピューターバス標準(computer bus standards)はS−100 bus、Mbus、Smbus、Q−Bus、ISA、Zorro II、Zorro III、CAMAC、FASTBUS、LPC、EISA、VME、VXI、NuBus、TURBOchannel、MCA、Sbus、VLB、PCI、PXI、HP GSC bus、CoreConnect、InfiniBand、UPA、PCI−X、AGP、PCIe、Intel QuickPath Interconnect、Hyper Transport、等を含む。ストレージバス標準(Storage bus standards)は ST−506、ESDI、SMD、Parallel ATA、DMA、SSA、HIPPI、USB MSC、FireWire(1394)、Serial ATA、eSATA、SCSI、Parallel SCSI、Serial Attached SCSI、Fibre Channel、iSCSI、SAS、RapidIO、FCIP、等を含む。iFCP Peripheralバス標準(iFCP Peripheral bus standards)は Apple Desktop Bus、HIL、MIDI、Multibus、RS−232、DMX512−A、EIA/RS−422、IEEE−1284、UNI/O、1−Wire、I2C、SPI、EIA/RS−485、USB、Camera Link、External PCIe、Light Peak、Multidrop Bus、等を含む。

【0061】

図3は本発明の他の実施形態による図1に図示されたメモリ制御器を概略的に示すブロック図である。図3において、図2に図示されたことと実質的に同一な構成要素は同一な参照番号に付し、それに対する説明はしたがって省略される。図3に図示されたメモリ制御器2000aはランダム化器/デランダム化器2600をさらに含む。

【0062】

ランダム化器/デランダム化器2600は不揮発性メモリ装置1000へ伝送されるデータをランダム化するように、そして不揮発性メモリ装置1000から出力されるデータ(例えば、ランダム化されたデータ)をデランダム化するように構成される。先に説明された複写動作の時、ランダム化器/デランダム化器2600は不揮発性メモリ装置1000から出力されるデータ(例えば、ランダム化されたデータ)をデランダム化し、エラー検出及び訂正回路2500はデランダム化されたデータのエラーを検出する。先に説明されたように、メモリ制御器2000aから不揮発性メモリ装置1000へ伝送されるエラーフラッグ情報はランダム化器/デランダム化器2600によってランダム化されない。同様に、エラーフラッグ情報を含むフィールドデータが伝送される場合にも、ランダム化器/デランダム化器2600は動作しない。エラー訂正されたデータが不揮発性メモリ装置1000へ伝送される場合、エラー訂正されたデータはランダム化器/デランダム化器2600によってランダム化される。本発明の場合、エラー訂正がメモリ制御器2000aによって提供されるエラーフラッグ情報にしたがって不揮発性メモリ装置1000によって行われるので、ランダム化器/デランダム化器2600のランダム化はエラーフラッグ情報/フィールドデータ(エラーフラッグ情報を含む)の伝送の時に行われない。

【0063】

図4は本発明の一実施形態による図1に図示された不揮発性メモリ装置を概略的に示すブロック図である。図4を参照すれば、不揮発性メモリ装置1000はメモリセルアレイ1100、アドレスデコーダー1200、電圧発生器1300、制御ロジック1400、ページバッファ回路1500、及び入出力インターフェイス1600を含む。

【0064】

メモリセルアレイ1100は行(例えば、ワードライン)と列(例えば、ビットライン)との交差領域に配列されたメモリセルを含む。メモリセルの各々は1ビットデータ又はマルチビットデータを格納する。アドレスデコーダー1200は制御ロジック1400によって制御され、メモリセルアレイ1100の行(例えば、ワードライン、ストリング選択ライン、接地選択ライン、共通ソースライン、等)の選択及び駆動を行う。電圧発生器1300は制御ロジック1400によって制御され、各動作に必要である電圧(例えば、高電圧、プログラム電圧、読出し電圧、検証電圧、消去電圧、パス電圧、バルク電圧、等)を発生する。電圧発生器1300によって電圧はアドレスデコーダー1200を通じてメモリセルアレイ1100へ提供される。制御ロジック1400は不揮発性メモリ装置1000の全般的な動作を制御するように構成される。ページバッファ回路1500は制御ロジック1400によって制御され、メモリセルアレイ1100からデータを読み出すように、又はプログラムデータにしたがってメモリセルアレイ1100の列(例えば、ビットライン)を駆動するように構成される。入出力インターフェイス1600は制御ロジック1400によって制御され、外部(例えば、図1のメモリ制御器)とインターフェイスするように構成される。

【0065】

ページバッファ回路1500はビットライン又はビットライン対に各々対応する複数のページバッファで構成される。ページバッファの各々は複数のラッチを含む。ページバッファ回路1500は制御ロジック1400の制御の下に各ページバッファのラッチを利用してエラー訂正動作を遂行する。即ち、ページバッファ回路1500は制御ロジック1400の制御の下にメモリ制御器2000から提供されたエラーフラッグ情報にしたがってエラー訂正動作を遂行する。本発明の例示的な実施形態において、エラー訂正動作はエラー位置情報に対応するデータビットの値を反転させることによって、達成される。即ち、エラー位置情報に対応するデータビットの値はエラーフラッグ情報にしたがって反転される。このようなエラー訂正動作をビットフリップ動作と称する。これは以後詳細に説明する。

【0066】

図5は全てのビットラインメモリ構造又はオッドイ−ブンメモリ構造のためにメモリセルアレイをメモリブロックで構成する例を示す図面である。メモリセルアレイ1100の例示的な構造が説明される。一例として、メモリセルアレイ1100が1024個のメモリブロックに分けられたNANDフラッシュメモリ装置が説明される。各メモリブロックに格納されたデータは同時に消去され得る。一実施形態において、メモリブロックは同時に消去される格納素子の最小単位である。各メモリブロックには、例えば、ビットラインに各々対応する複数の列がある。全てのビットライン(all bit line:ABL)構造と称される一実施形態において、メモリブロックの全てのビットラインは読出し及びプログラム動作の間に同時に選択され得る。選択されたワードラインに属し、全てのビットラインと連結された格納素子は同時にプログラムされ得る。

【0067】

例示的な実施形態において、同一な列に属する複数の格納素子はNANDストリング111を構成するように直列に連結される。NANDストリングの一端子はストリング選択ラインSSLによって制御される選択トランジスターを通じて対応するビットラインに連結され、他の端子は接地選択ラインGSLによって制御される選択トランジスターを通じて共通ソースラインCSLに連結される。

【0068】

オッドイ−ブン構造(odd−even architecture)と称される他の例示的な実施形態において、ビットラインはイ−ブンビットラインBLeとオッドビットラインBLoとに区分される。オッド/イ−ブンビットライン構造において、選択されたワードラインに属し、オッドビットラインと連結された格納素子が第1時間にプログラムされる反面に、選択されたワードラインに属し、イ−ブンビットラインと連結された格納素子は第2時間にプログラムされる。データは他のブロックにプログラムされ得り、他のメモリブロックから読み出され得る。このような動作は同時に遂行できる。

【0069】

図6は本発明の例示的な実施形態による図5に図示されたページバッファ回路の一部を示すブロック図である。本発明の実施形態によるページバッファ回路1500はビットラインに各々連結された複数のページバッファPBを含む。図6には単なる1つのページバッファPBが図示されている。残りページバッファの各々は図6に図示されたことと実質的に同様に構成される。

【0070】

図6を参照すれば、ページバッファPBは図4の制御ロジック1400によって制御され、プリチャージ回路1510、ラッチブロック1520、及びデータ入出力回路1530を含む。プリチャージ回路1510はビットラインBLに連結され、ビットラインBLをプリチャージするように構成される。一対のビットラインにページバッファPBが連結される場合、プリチャージ回路1510は一対のビットラインの中から1つを選択する機能を含む。ラッチブロック1520は感知ノードSOに連結される。ラッチブロック1520は複数の、例えば5つのラッチユニット1521〜1525(図面にはS、L、M、F、及びCに各々示す)を含む。ページバッファPBに含まれたラッチユニットの数がここに開示されたことに制限されない。ラッチブロック1520は感知動作(プログラム検証動作、読出し動作、消去検証動作等に関連される)の時、制御ロジック1400の制御の下に感知ノードSOの値をラッチするように構成される。制御ロジック1400はラッチの間からデータが伝達されるダンプ動作を実行するようにラッチブロック1520を制御する。ダンプ動作の時、ラッチの間から伝達されるデータの位相は制御ロジック1400の制御にしたがって反転されるか、或いはそのまま維持される。ラッチブロック1520はプログラム動作の時、プログラムデータにしたがってビットラインBLをビットラインプログラム電圧(例えば、0V又は0Vより高くて電源電圧より低い電圧)又はビットラインプログラム禁止電圧(例えば、電源電圧)で駆動する。

【0071】

以後説明されるように、ラッチブロック1520は制御ロジック1400の制御にしたがってエラーフラッグ情報を利用して先に説明されたビットフリップ動作(又は、エラー訂正動作)を遂行する。これは制御ロジック1400の制御にしたがってラッチユニット1521〜1525の間で行われるデータ伝送動作を通じて達成される。データ入出力回路1530はラッチブロック1520のデータをデータラインDLへ伝送するか、或いはデータラインDLのデータをラッチブロック1520へ伝送するように構成される。

【0072】

図6に図示されたページバッファPBの構成がここに開示されたことに制限されない。

【0073】

図7は本発明の実施形態による不揮発性メモリ装置のエラー訂正動作を概略的に説明するための図面である。以下、本発明の実施形態による不揮発性メモリ装置1000のエラー訂正動作が参照図面に基づいて詳細に説明される。

【0074】

メモリセルアレイ1100の第1格納領域から読み出されたデータを第2格納領域に複写する場合、第1格納領域から読み出されたデータに対するエラー訂正が行われる。第1格納領域から読み出されたデータに対するエラー訂正は、先に説明されたように、メモリ制御器2000によって行われることではなく、不揮発性メモリ装置1000によって行われる。エラー訂正はメモリ制御器2000から提供されるエラーフラッグ情報にしたがって行われる。例えば、エラー訂正はビットフリップ動作を通じて行われる。

【0075】

図7に図示されたように、説明の便宜上、メモリセルアレイ1100の第1格納領域から読み出されたデータが“01010011”の8ビットデータであると仮定する。第1格納領域から読み出されたデータは、先ず、メモリ制御器2000へ提供される。メモリ制御器2000のエラー検出及び訂正回路2500は不揮発性メモリ装置1000から提供されるデータがエラーがあるか否かを判別する。仮に不揮発性メモリ装置1000から提供されるデータがエラーがあると判別されれば、エラー検出及び訂正回路2500はエラー位置情報及びエラーフラッグ情報を発生する。エラー位置情報及びエラーフラッグ情報は処理ユニット2300の制御の下に不揮発性メモリ装置1000へ提供される。ここで、エラーフラッグ情報はエラー位置情報に対応するデータビットがエラーがあることを示す。例えば、図7に図示されたように、エラーフラッグ情報はエラー位置情報に対応するデータビットが誤ったことと判別される時、メモリの値を有する。しかし、エラーフラッグ情報がエラー位置情報に対応するデータビットが誤ったことと判別される時、‘0’の値を有するように設定され得ることは理解できる。

【0076】

エラーフラッグ情報は第1格納領域から読み出されたデータと独立的に不揮発性メモリ装置1000のページバッファ回路1500に格納される。エラーフラッグ情報に基づいてページバッファ回路1500を通じてエラー訂正動作又はビットフリップ動作が行われる。図7に図示されたように、エラー位置情報に対応するデータビットはエラーフラッグ情報に基づいて‘1’から‘0’に変更される。変更されたデータビットを含むデータはエラー訂正されたデータである。以後、エラー訂正されたデータはメモリセルアレイ1100の第2格納領域に格納される。

【0077】

エラーフラッグ情報に基づいて行われるページバッファのエラー訂正動作又はビットフリップ動作が以下詳細に説明される。

【0078】

エラー訂正動作(又は、ビットフリップ動作)はページバッファPBのラッチユニットを利用して行われる。例えば、エラー訂正動作は3つのラッチユニット1521、1522、1525を利用して排他的OR動作を通じて行われる。エラー訂正動作が排他的OR(XOR)動作に制限されない。例えば、エラー訂正動作はエラーフラッグ情報の値にしたがって排他的NOR(XNOR)動作を通じて行われ得る。エラー訂正動作は制御ロジック1400の制御の下に行われる。

【0079】

先ず、第1格納領域から読み出されたデータはラッチユニット1521(以下、Sラッチユニットと称する)に格納される。Sラッチユニット1521に格納されたデータはラッチユニット1522、1525(以下、Lラッチユニット及びCラッチユニットと称する)へ各々ダンプされる。Cラッチユニット1525に格納されたデータはエラーを検出するためにメモリ制御器2000へ出力される。説明の便宜上、1つのデータビットを基準としてエラー訂正動作が説明される。このような場合、1つの読み出されたデータビット及び1つのエラーフラッグビットの組合は4つの種類である場合(例えば、‘00’、‘01’、‘10’、及び‘11’)の中の1つである。下の表1はエラーを検出するためにメモリ制御器2000にデータが出力される時、各ラッチユニットの状態を示す。下の表で‘X’はdon’t careを意味する。先に説明によれば、下の表1で分かるように、Sラッチユニット1521、Lラッチユニット1522、及びCラッチユニット1525は同一な状態を有する。

【0080】

【表1】

【0081】

Cラッチユニット1525からメモリ制御器2000へデータが出力された後、Cラッチユニット1525は‘0’の値を有するように初期化される。メモリ制御器2000は不揮発性メモリ装置1000から出力されたデータに対するエラー検出動作を遂行し、エラー検出動作の結果としてエラー位置情報及びエラーフラッグ情報(又は、エラーフラッグビット)を不揮発性メモリ装置1000へ提供する。エラーフラッグ情報(又は、エラーフラッグビット)はメモリの値を有する。エラーフラッグ情報を入力する前にSラッチユニット1521は‘0’に初期化される。下の表2はLラッチユニット1522の値(読み出されたデータビットの値)とCラッチユニット1525の値(エラーフラッグ情報/ビット)との組合にしたがう場合を示す。

【0082】

【表2】

【0083】

Cラッチユニット1525へロードされた‘1’に対応するLラッチユニット1522の値を反転させることによって、エラー訂正動作が達成され、これは以下詳細に説明される。

【0084】

先ず、制御ロジック1400はCラッチユニット1525へロードされたエラーフラッグビットを反転させ、反転されたビットをSラッチユニット1521に格納するようにページバッファPBを制御する。エラーフラッグビットの反転はCラッチユニット1525からSラッチユニット1521にデータがダンプされる過程で行われる。このような動作の結果は下の表3の通りである。

【0085】

【表3】

【0086】

制御ロジック1400はSラッチユニット1521の値が‘0’であり、Lラッチユニット1522の値が‘0’である時、Sラッチユニット1521の値及びLラッチユニット1522の値が‘1’に変更されるようにページバッファPBを制御する。このような動作の結果は下の表4の通りである。

【0087】

【表4】

【0088】

制御ロジック1400はSラッチユニット1521の値が‘0’である時、Lラッチユニット1522の値が‘0’に変更されるようにページバッファPBを制御する。このような動作の結果は下の表5の通りである。

【0089】

【表5】

【0090】

Lラッチユニット1522に格納されたデータがエラー訂正されたデータになる。即ち、読み出されたデータビットがメモリの値を有し、対応するエラーフラッグビットがメモリの値を有する時、表2及び表5で分かるように、Lラッチユニット1522の値は‘1’から‘0’に変更される。読み出されたデータビットが‘0’の値を有し、対応するエラーフラッグビットがメモリの値を有する時、表2及び表5で分かるように、Lラッチユニット1522の値は‘0’から‘1’に変更される。

【0091】

先に説明されたエラー訂正動作又はビットフリップ動作は例示的なことであり、本発明はここに開示されたことに制限されない。エラー訂正動作又はビットフリップ動作はページバッファの構造、エラーフラッグ情報の値、等にしたがって多様に変更される。

【0092】

図8は本発明の実施形態によるメモリシステムの複写動作を説明するためのフローチャートであり、図9は図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。以下、本発明の実施形態によるメモリシステムの複写動作が参照図面に基づいて詳細に説明される。

【0093】

以後説明される複写動作は、先に説明されたように、メモリセルアレイ1100の第1格納領域(例えば、第1メモリブロックに属する1つのページに対応する)から第2格納領域(例えば、第2メモリブロックに属する1つのページに対応する)へデータを複写する動作を意味する。複写動作という用語が特定動作に制限されない。例えば、複写動作は1つの格納領域から他の格納領域へデータを移る全て動作を包含するように解釈される。

【0094】

先ず、S100段階で、ページバッファ回路1500はメモリセルアレイ1100の第1メモリブロックの第1格納領域(又は、選択されたページ)からデータを読み出す。読み出されたデータはページバッファ回路1500のSラッチユニット1521に格納される。読み出されたデータは読出し動作の間に発生され得るエラービットを包含できる。エラー訂正無しで第2メモリブロックの第2格納領域にエラービットを含む読み出されたデータがそのまま格納される場合、第2格納領域に格納されたデータのエラービットの数はメモリ制御器2000のエラー訂正範囲を超過され得る。即ち、データ信頼性が低下され得る。その故に、読み出されたデータに対するエラー検出及び訂正動作が行われる。このために、S110段階で、読み出されたデータはメモリ制御器2000へ出力される。先に説明されたように、読み出されたデータは外部へ出力される以前にLラッチユニット1522及びCラッチユニット1525へダンプされる。Cラッチユニット1525に格納された読み出されたデータがメモリ制御器2000へ出力される。

【0095】

S120段階で、メモリ制御器2000は読み出されたデータがエラービットを含むか否かを判別する。これはメモリ制御器2000のエラー検出及び訂正回路2500を通じて行われる。読み出されたデータがエラービットを包含しないことと判別されれば、手続はS160段階に進行する。読み出されたデータがエラービットを含むことと判別されれば、エラー検出及び訂正回路2500はエラー位置情報及びエラーフラッグ情報を発生させる。エラー検出及び訂正回路2500はエラー位置情報及びエラーフラッグ情報を発生するためのエラー検出動作を遂行する。即ち、複写動作の時、エラー検出及び訂正回路2500はエラー訂正動作を遂行する必要性がない。S140段階で、メモリ制御器2000から不揮発性メモリ装置1000へエラー位置情報及びエラーフラッグ情報が伝送される。これは図9を参照して以下詳細に説明される。

【0096】

不揮発性メモリ装置1000から出力された読み出されたデータは1つ又はそれより多いエラービットを包含できる。エラー位置情報及びエラーフラッグ情報はエラービット単位で反復的に不揮発性メモリ装置1000へ伝送される。図9に図示されたように、エラービットの中の第1番目のエラービットに対応したエラー位置情報は第1命令86hに続いて伝送されるアドレスC1C2R1R2R3に包含され、エラーフラッグ情報EFIはアドレスC1C2R1R2R3に続いて伝送される。ここで、アドレスC1C2R1R2R3の中の列アドレスC1C2はエラー位置情報を含む。アドレスC1C2R1R2R3は第1格納領域を含むメモリブロック(又はプラン/マット)を指定するための行アドレスR1R2R3を含む。このようなシーケンスは1つのエラービットに関連されて行われる。残りのエラービット各々に対応するエラー位置情報は、図9に図示されたように、第1命令86hに続いて伝送されるアドレスC1C2に包含され、エラーフラッグ情報EFIはアドレスC1C2に続いて伝送される。ここで、アドレスC1C2、即ち列アドレスC1C2はエラー位置情報を含む。全てのエラービットによって対するエラーフラッグ情報が図9に図示されたタイミングにしたがって不揮発性メモリ装置1000へ伝送された後、第2命令12hがメモリ制御器2000から不揮発性メモリ装置1000へ伝送される。以後、以下で説明されるように、エラー訂正動作(又は、ビットフリップ動作)及びプログラム動作が行われる。

【0097】

再び図8を参照すれば、S140段階で続いてS150段階で、不揮発性メモリ装置1000はメモリ制御器2000から提供されたエラーフラッグ情報に基づいてエラー訂正動作(又は、ビットフリップ動作)を遂行する。エラー訂正動作(又は、ビットフリップ動作)は表2乃至表5を参照して説明されたことと実質的に同様に行われるので、それに対する説明は省略される。S160段階で、エラー訂正されたデータはメモリセルアレイ1100の第2格納領域にプログラム/格納される。以後、手続は終了される。

【0098】

先の説明のよれば、エラー検出はメモリ制御器2000によって行われ、エラー訂正は不揮発性メモリ装置1000内で行われる。即ち、エラー検出の以後、メモリ制御器2000によってエラー訂正が行われないので(又は、エラー検出の以後、不揮発性メモリ装置1000によってエラー訂正が行われるので)、不揮発性メモリ装置1000から出力されたデータ(又は、訂正されたデータ)を全ての不揮発性メモリ装置1000へ伝送する必要がない。これはメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに掛かる時間及び/又はメモリ制御器2000から不揮発性メモリ装置1000へデータを伝送するのに消耗される電力が減少されることを意味する。

【0099】

図10は本発明の他の実施形態による図8で説明される複写動作の時、エラーフラッグ情報を不揮発性メモリ装置へ伝送するためのタイミング図である。

【0100】

エラービット単位でエラーフラッグ情報が伝送される図9の伝送方式と異なりに、エラーフラッグ情報(エラービットによって各々対応するエラーフラッグビットを包含する)を含むデータ(以下、フィールドデータと称する)が命令86h及びアドレスC1C2R1R2R3に続いて不揮発性メモリ装置1000へ伝送される。そのようなフィールドデータの大きさは読み出されたデータの大きさと同一である。フィールドデータにおいて、エラー位置情報に対応する位置の値(即ち、エラーフラッグビットの値)はロジック値‘1’(ロジック値がエラービットであることを示す)であり、残りの位置の値は反転されたロジック値‘0’(ロジック値がノンエラービット(non−error bit)であることを示す)である。例えば、データがメモリ制御器2000から不揮発性メモリ装置1000へバイト単位で伝送される場合、エラー位置情報に対応する位置は8つのデータビット(例えば、D0〜D7)の中の1つ(例えば、D1)に対応する。エラーフラッグ情報を含むフィールドデータが伝送される方式の場合、バス遷移回数が非常に少ない。これはデータ伝送の時、消耗される電力が減少することを意味する。また、エラー検出がメモリ制御器によって行われ、エラー訂正が不揮発性メモリ装置内で行われるので、メモリ制御器から不揮発性メモリ装置へデータを伝送するのに掛かる時間及び/又はメモリ制御器から不揮発性メモリ装置へデータを伝送するのに消耗される電力が減少される。

【0101】

図11は本発明の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【0102】

メモリセルアレイMCAの第1格納領域(例えば、第1メモリブロックの1ページに対応する)のデータはメインバッファMBを通じて読出し、メインバッファMBに格納された読み出されたデータはキャッシュバッファCBを通じてメモリ制御器2000へ伝送される。ここで、メインバッファMBはSラッチユニット1521で構成され得り、キャッシュバッファCBはCラッチユニット1525で構成され得る。しかし、本発明はそれに制限されない。メインバッファMBとキャッシュバッファCBとはページバッファ回路1500を構成する。メモリ制御器2000へ伝送されたデータはランダム化器/デランダム化器2600を通じてデランダム化され、エラー検出及び訂正回路2500はランダム化器/デランダム化器2600によってデランダム化されたデータに対するエラー検出動作を遂行する。ここで、不揮発性メモリ装置1000から出力される読み出されたデータRDのデランダム化されたデータはバッファメモリ2400に格納される。エラー検出動作の結果として、エラーフラッグ情報が不揮発性メモリ装置1000のキャッシュバッファCBへ伝送される。ここで、エラーフラッグ情報は図9で説明された方式又は図10で説明された方式にしたがってメモリ制御器2000から不揮発性メモリ装置1000へ伝送される。エラーフラッグ情報又はエラーフラッグ情報を含むフィールドデータはランダム化器/デランダム化器2600を経由しなくて直接不揮発性メモリ装置1000へ伝送される。キャッシュバッファCBに格納されたエラーフラッグ情報に基づいてビットフリップ動作(又は、エラー訂正動作)が行われ、ビットフリップ動作(又は、エラー訂正動作)を通じて訂正されたデータはメインバッファMBを通じてメモリセルアレイMCAの第2格納領域(例えば、第2メモリブロックの1ページに対応する)に格納される。ビットフリップ動作(又は、エラー訂正動作)は表3乃至図5で説明されたことと実質的に同一であるので、それに対する説明は省略される。

【0103】

例示的な実施形態において、メモリ制御器2000から提供されるエラーフラッグ情報はページバッファ回路1500のキャッシュバッファCBへロードされる。この時、メインバッファMBには読み出されたデータが格納されている。即ち、キャッシュバッファCBへロードされる情報はメインバッファMBにされたデータビットが誤ったか否かを示す値である。

【0104】

例示的な実施形態において、図11で説明された複写動作は点線で示されたランダム化器/デランダム化器2600を含むメモリ制御器(例えば、図3に図示されたことに対応する)のみでなく、点線で示されたランダム化器/デランダム化器2600を包含しないメモリ制御器(例えば、図2に図示されたことに対応する)に適用できる。ランダム化器/デランダム化器2600を含むメモリ制御器2000において、仮に第1格納領域を含む第1メモリブロック及び第2格納領域を含む第2メモリブロックに対するランダム化のためのシードが互に同一な場合、エラーフラッグ情報に対するランダム化は行われない。

【0105】

例示的な実施形態において、シード値はランダム化されたデータが格納される領域のメモリセルに格納される。

【0106】

複写動作であるコピーバック動作(又はコピーバックプログラム動作)が特許文献1に開示され、この出願のレファレンスとして包含される。

【0107】

図12は本発明の他の実施形態によるメモリシステムのエラー検出動作及びエラー訂正動作を概略的に説明するための図面である。

【0108】

メモリセルアレイMCAの第1格納領域のデータはメインバッファMBを通じて読出し、メインバッファMBに格納された読み出されたデータはキャッシュバッファCBを通じてメモリ制御器2000へ伝送される。ここで、メインバッファMBはSラッチユニット1521で構成され得り、キャッシュバッファCBはCラッチユニット1525で構成され得る。しかし、本発明はそれに制限されない。ここで、不揮発性メモリ装置1000から出力される読み出されたデータRDのデランダム化されたデータはバッファメモリ2400に格納される。メモリ制御器2000へ伝送されたデータはランダム化器/デランダム化器2600を通じてデランダム化され、エラー検出及び訂正回路2500はランダム化器/デランダム化器2600によってデランダム化されたデータに対するエラー検出動作を遂行する。仮にメモリセルアレイMCAの第1格納領域に関連されたランダム化動作のためのシード値が第2格納領域に関連されたランダム化動作のためのシード値と一致しなければ、メモリ制御器2000は読み出されたデータに対するエラー検出動作のみで無く、エラー訂正動作を遂行する。ここで、不揮発性メモリ装置1000から出力される読み出されたデータRDのデランダム化されたデータはバッファメモリ2400に格納される。読み出されたデータのエラーはエラー検出及び訂正回路2500によって訂正される。訂正されたデータはランダム化器/デランダム化器2600を通じて不揮発性メモリ装置1000のキャッシュバッファCBへ伝送される。キャッシュバッファCBに格納されたエラー訂正されたデータはメインバッファMBへ伝送され、メインバッファMBへ伝送されたデータ(即ち、エラー訂正されたデータ)はメモリセルアレイMCAの第2格納領域に格納される。

【0109】

先に説明されたエラー検出動作及びエラー訂正動作を含む複写動作は多様なメモリシステムに適用できる。以下、先に説明されたエラー検出動作及びエラー訂正動作を含む複写動作が適用されるメモリシステムの一例が説明される。

【0110】

図13Aはマルチレベルメモリ装置に適用されるアドレススクランブル方式の一例を説明するための図面である。

【0111】

各メモリセルに格納されるデータビットの数が増加されることによって、マルチビット(又は、マルチレベル)データを格納するメモリ装置(以下、マルチレベルメモリ装置と称する)の信頼性を確保することが漸次的に難しくなり得る。信頼性を低下させる要因の中で代表的な1つは隣接メモリセルの間のカップリングによる閾値電圧の変化である。例えば、以前にプログラムされたメモリセルの閾値電圧はプログラムされたメモリセルに隣接するメモリセルがプログラムされる時、生じるカップリングによって変化され得る。

【0112】

1つのメモリセルに3ビットデータが格納されると仮定の下でアドレススクランブル方式が説明される。図示の便宜上、図13Aには単なる4つのワードラインWL0−WL3が図示されている。ワードラインWL0−WL3各々には複数のメモリセルMCが連結される。先ず、下位2ビットデータが第1番目のワードラインWL0に連結されたメモリセル各々に格納される1ステッププログラム動作が遂行される。即ち、1ステッププログラム動作の間に、第1番目のワードラインWL0に連結されたメモリセルには2ページデータが格納される。これは図13Aで(1)に表記されている。その次に、第2番目のワードラインWL1に連結されたメモリセルに対して1ステッププログラム動作が遂行される。これは図13Aで(2)に表記されている。第2番目のワードラインWL1に対する1ステッププログラム動作が遂行された後、第2番目のワードラインWL1の下に位置し、下位2ビットデータがプログラムされた第1番目のワードラインWL0に連結されたメモリセルに上位1ビットデータが格納される粗いプログラム動作(coarse program operation)(又は、第2番目のステッププログラム(2−step programming)と称される)が遂行される。これは図13Aで(3)に表記されている。第1番目のワードラインWL0に連結されたメモリセルに対して粗いプログラム動作が遂行された後、第3番目のワードラインWL2に対する1ステッププログラム動作が遂行される、これは図13Aで(4)に表記されている。第3番目のワードラインWL2に対する1ステッププログラム動作の以後、下位2ビットデータがプログラムされた第2番目のワードラインWL1に連結されたメモリセルに上位1ビットデータが格納される粗いプログラム動作が遂行される。これは図13Aで(5)に表記されている。その後、第1番目のワードラインWL0に対する精巧なプログラム動作(fine program operation)が遂行される。これは図13Aで(6)に表記されている。以後、1ステップ、粗い、そして精巧なプログラム動作が先に説明されたプログラム順序(図13A参照)にしたがって順次的に遂行される。図13で説明されたプログラム順序にしたがってワードラインが選択される方式をアドレススクランブル方式と称する。アドレススクランブル方式がここに開示されたことに制限されない。

【0113】

1ステッププログラム動作と粗いプログラム動作とが完了されれば、Mビットデータ(Mは2又はそれより大きい整数)に対応する閾値電圧分布(例えば、2Mつの閾値電圧分布)が全て形成される。たとえ粗いプログラム動作が完了されることにしたがって全て閾値電圧分布が形成されても、閾値電圧分布間のマージンは閾値電圧分布を明確に区分するのに充分でない。閾値電圧分布を明確に区分するのに充分なマージンを確保するために精巧なプログラム動作が遂行される。精巧なプログラム動作は各閾値電圧分布の幅を狭くするために行われ、粗いプログラム動作で使用される閾値電圧分布の検証電圧より所定電圧程度各々高い検証電圧を使用して行われる。このようなプログラム方式を通じて隣接するメモリセルの間のカップリングを減らすことが可能である。このようなプログラム方法/アルゴリズムは再プログラム方法/アルゴリズム(reprogram method/algorithm)と称する。

【0114】

例示的な実施形態において、3ビットデータのための再プログラム方法、即ち、1ステッププログラミング、粗いプログラミング、及び精巧なプログラミングが2ビットデータ及び4ビットデータの再プログラム方法にも全て適用され得ることはよく理解できる。

【0115】

このような再プログラム方法によると、任意のワードラインに対する精巧なプログラム動作が終了される時まで任意のワードラインのメモリセルに格納されたデータを維持する必要がある。例えば、1ステッププログラム動作はメモリ制御器からマルチビットメモリ装置へ提供されるデータに基づいて行われ、粗いプログラム動作は1ステッププログラム動作を通じて格納されたデータとメモリ制御器から提供されるデータとに基づいて行われる。精巧なプログラム動作は1ステッププログラム動作と粗いプログラム動作とを通じて格納されたデータに基づいて行われる。しかし、先に説明されたように、1ステッププログラム動作と粗いプログラム動作とを通じて格納されたデータを正確に読み出すことは難しい。これは精巧なプログラム動作に必要であるデータはメモリ制御器からマルチビットメモリ装置へ提供されなければならないことを意味する。そのような理由で、任意のワードラインに対する精巧なプログラム動作が終了される時まで任意のワードラインのメモリセルに格納されたデータがメモリ制御器によって維持される。これは精巧なプログラム動作に必要であるデータを維持するための大きい容量のバッファメモリがメモリ制御器へ提供されることを意味する。バッファメモリの容量を減らすために以後説明されるオンチップバッファプログラミング(On−chip Buffered Programming:OBP)技術がメモリシステムに適用され得る。

【0116】

図13Bは各メモリセル当たり3ビットデータを格納し、3ステッププログラム方式にしたがってプログラム動作が遂行される時、変化される閾値電圧分布を示す図面である。以下、3ステッププログラム方式によるプログラム方法が参照図面に基づいて説明される。

【0117】

先ず、選択されたワードライン(例えば、WL0、図13A参照)のメモリセルには2ページデータ(即ち、第1及び第2ページデータ)が同時に格納される。この時、図13Bのボックス31に図示されたように、消去状態Eに対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態Q1、Q2、Q3に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。

【0118】

先に説明されたように、ワードライン(例えば、WL0)に属する1ステッププログラムされたメモリセルの粗いプログラム動作は隣接するワードライン(例えば、WL1)に属するメモリセルの1ステッププログラム動作の以後に行われる。この時、図13Bのボックス31の実線で表示されたように、ワードライン(例えば、WL0)に属する1ステッププログラムされたメモリセルの散布が隣接するワードライン(例えば、WL1)に属するメモリセルがプログラムされる時に生じるカップリングによって広くなる。

【0119】

その次に、選択されたワードラインWL0のメモリセルには1ページデータが格納される。この時、図13Bのボックス32に図示されたように、各状態に対応する閾値電圧分布に属するメモリセルは対応する閾値電圧散布に属する閾値電圧を有するようにプログラムされる。例えば、消去状態Eに対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P1に対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。プログラム状態Q1に対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P2、P3に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。プログラム状態Q2に対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P4、P5に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。プログラム状態Q3に対応する閾値電圧分布に属するメモリセルはプログラムされるデータにしたがってプログラム状態P6、P7に各々対応する閾値電圧分布に属する閾値電圧を有するようにプログラムされる。

【0120】

先に説明されたように、ワードライン(例えば、WL0)に属する粗いプログラムされたメモリセルの精巧なプログラム動作は隣接するワードライン(例えば、WL2、WL1)に対する1ステッププログラム動作及び粗いプログラム動作の以後に行われる。この時、図13Bのボックス32の実線で図示されたように、ワードライン(例えば、WL0)に属する粗いプログラムされたメモリセルの散布が隣接するワードライン(例えば、WL2、WL1)に属するメモリセルがプログラムされる時に生じるカップリングによって広くなる。このような理由で、粗いプログラムされたメモリセルからデータを正確に読み出すことが難しい。

【0121】