メモリシステム及びメモリモジュール制御方法

【課題】1枚の汎用のメモリモジュールのみで高度なエラー訂正を実現し、信頼性の高いメモリシステムを提供すること。

【解決手段】nビット入出力の第1〜第8半導体メモリを有するメモリモジュールと、外部装置から受け取る4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成し、4×nビットのデータをnビットずつ第1〜第4半導体メモリのそれぞれに格納し、3×nビットの誤り検出訂正符号をnビットずつ第5〜第7半導体メモリのそれぞれに格納するメモリ制御部とを具備する。メモリ制御部は、第1〜第4半導体メモリに格納された4×nビットのデータを読み出すとき、第5〜第7半導体メモリに格納された3×nビットの誤り検出訂正符号に基づいて、第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行する。改行しないで書き始める。スペース入れない。クレーム1を書き下す。

【解決手段】nビット入出力の第1〜第8半導体メモリを有するメモリモジュールと、外部装置から受け取る4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成し、4×nビットのデータをnビットずつ第1〜第4半導体メモリのそれぞれに格納し、3×nビットの誤り検出訂正符号をnビットずつ第5〜第7半導体メモリのそれぞれに格納するメモリ制御部とを具備する。メモリ制御部は、第1〜第4半導体メモリに格納された4×nビットのデータを読み出すとき、第5〜第7半導体メモリに格納された3×nビットの誤り検出訂正符号に基づいて、第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行する。改行しないで書き始める。スペース入れない。クレーム1を書き下す。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はメモリシステム及びメモリモジュール制御方法に関する。

【背景技術】

【0002】

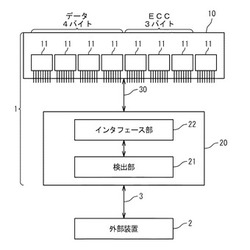

サーバ等のミッションクリティカルシステムにおいては、DIMM(Dual Inline Memory Module)のデータエラー対策の為に、ECC(Error Check and Correction:誤り検出及び訂正)による保護を実施している。図1は、ECC付の汎用のDIMM110を具備するメモリシステム100を示した図である。図1を参照すると、メモリシステム100は、DIMM110と、メモリ制御部120と、汎用DIMMインタフェース部130とを具備する。メモリシステム100は、システムインタフェース部300を介して外部装置200と接続され、データの受け渡しを行う。

【0003】

DIMM110は9つのDRAM(Dynamic Random Access Memory)111を有し、各DRAM111は8ビット入出力である。このDIMM110は、8つのDRAM111から構成されるデータ8バイトの汎用DIMMに対して、1つのDRAM111をECC1バイト用に追加したものであり、データ8バイトとECC1バイトとから構成されている。メモリ制御部120は、検出部121と、DIMMインタフェース部122とを備える。

【0004】

メモリシステム100の動作方法を説明する。まず、DIMM110へのデータ書き込み動作を説明する。外部装置200は、8バイトのデータ及び書き込み要求を、システムインタフェース部300を介してメモリシステム100に提供する。検出部121は、8バイトのデータ及び書き込み要求を受け取ると、8バイトのデータに基づいて1バイトの誤り検出訂正符号を生成する。検出部121は、8バイトのデータと1バイトの誤り検出訂正符号とをDIMMインタフェース部122に提供する。DIMMインタフェース部122は、検出部121から8バイトのデータ、1バイトの誤り検出訂正符号、及び書き込み要求を受け取ると、汎用DIMMインタフェース部130を介して、8バイトのデータ及び1バイトの誤り検出訂正符号をメモリモジュール110に格納する。詳細には、DIMMインタフェース部122は、8バイトのデータを1バイトずつ8つのDRAM111に格納し、1バイトの誤り検出訂正符号を残り1つのDRAM111に格納する。

【0005】

次に、DIMM110からのデータ読み出し動作を説明する。外部装置200はデータの読み出し要求を、システムインタフェース部300を介してメモリシステム100に提供する。検出部121は、データの読み出し要求をDIMMインタフェース部122に提供する。DIMMインタフェース部122は、検出部121から読み出し要求を受け取ると、8つのDRAM111から8バイトのデータを読み出し、1つのDRAM111から1バイトの誤り検出訂正符号を読み出す。DIMMインタフェース部122は、8バイトのデータと1バイトの誤り検出訂正符号とを検出部121に提供する。検出部121は、1バイトの誤り検出訂正符号に基づいて、1ビット訂正又は2ビットエラー検出を実行する。

【0006】

エラー訂正及び検出に関連する技術が、特許文献1〜4に開示されている。特許文献1には、汎用のDIMM製品を利用でき、チップ故障を含めてデータを訂正するメモリ装置が開示されている。このメモリ装置は、ECCとして任意のバイト数を指定する手段を有し、データと誤り訂正符号とがメモリ上で同一ワード上に存在することを特徴としている。

【0007】

特許文献2には、EEPROM(Electrically Erasable Programmable Read−Only Memory)のメモリデータ入出力制御方式が開示されている。このメモリデータ入出力制御方式は、書き込むデータをメモリ番地単位で半分のビットを真のデータとし、残り半分のビットは真のデータの論理値を反転させたパリティ情報とすることを特徴としている。

【0008】

特許文献3には、ローエンドサーバシステムにおいて、コストのかかるカスタムASICチップや追加のメモリモジュール等を必要とせずに、チップキルによるエラー検出を実行可能なメモリシステムが開示されている。

【0009】

特許文献4には、既存のSIMM(Single In−line Memory Module)等のメモリを用いて、ECC誤り訂正検出の可能な記憶回路モジュールが開示されている。この記憶回路モジュールは、データ記憶部と、ECC記憶部と、誤り訂正符号を生成する訂正符号生成部と、ECC記憶部の誤り訂正符号を利用して誤り訂正・検出を行う訂正・検出部とを備える。そして、ECC記憶部が誤り訂正機能を有していない記憶素子から構成されることを特徴としている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2009−245218号公報

【特許文献2】特開平02−122349号公報

【特許文献3】特開2001−142789号公報

【特許文献4】特開平10−111839号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

ECCコード(誤り検出訂正符号)の1バイトによって実現可能であるのはSECDED(1ビット訂正2ビット検出)までであるため、前述したメモリシステム100はS8ECD8ED(1バイト訂正2バイト検出)を実行することはできない。つまり、メモリシステム100では、1つのDRAM111の故障を訂正することができないことを意味している。S8ECD8EDに必要な誤り検出訂正符号は3バイトである。従って、メモリシステム100がこれを実現しようとすると、3枚のECC付の汎用のDIMM110を同時に用いる必要がある。図2は、3枚のECC付の汎用のDIMM110を具備するメモリシステム101を示した図である。尚、図2のメモリシステム101の各部は図1のメモリシステム100と同様であるため詳細な説明は省略する。図2のメモリシステム101は、ECC無しの汎用DIMMに比べて高価なECC付の汎用のDIMM110を3枚必要とすることや、汎用DIMMインタフェース130が3倍必要となることによって高価となり、しかも設計も困難になるという問題がある。

【0012】

本発明の目的は、1枚の汎用のメモリモジュールのみで高度なエラー訂正を実現し、信頼性の高いメモリシステムを提供することにある。

【課題を解決するための手段】

【0013】

本発明のメモリシステムは、nビット入出力の第1〜第8半導体メモリを有するメモリモジュールと、外部装置から受け取る4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成し、4×nビットのデータをnビットずつ第1〜第4半導体メモリのそれぞれに格納し、3×nビットの誤り検出訂正符号をnビットずつ第5〜第7半導体メモリのそれぞれに格納するメモリ制御部とを具備する。メモリ制御部は、第1〜第4半導体メモリに格納された4×nビットのデータを読み出すとき、第5〜第7半導体メモリに格納された3×nビットの誤り検出訂正符号に基づいて、第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行する。

【0014】

本発明のメモリモジュール制御方法は、外部装置から受け取る4×nビットのデータを、nビット入出力の第1〜第8半導体メモリを有するメモリモジュールに書き込むステップと、外部装置の要求に基づいて、メモリモジュールから4×nビットのデータを読み出すステップとを具備する。書き込むステップは、外部装置から4×nビットのデータを受け取るステップと、4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成するステップと、4×nビットのデータをnビットずつ、第1〜第4半導体メモリのそれぞれに格納するステップと、3×nビットの誤り検出訂正符号をnビットずつ、第5〜第7半導体メモリのそれぞれに格納するステップとを備える。読み出すステップは、外部装置の要求に基づいて、第1〜第4半導体メモリに格納された4×nビットのデータを読み出すステップと、第5〜第7半導体メモリに格納された3×nビットの誤り検出訂正符号を読み出すステップと、読み出された4×nビットのデータ及び3×nビットの誤り検出訂正符号に基づいて、第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行するステップとを備える。

【発明の効果】

【0015】

本発明のメモリシステムは、1枚の汎用のメモリモジュールのみで高度なエラー訂正を実現し、高い信頼性を得ることができる。

【図面の簡単な説明】

【0016】

【図1】図1は、ECC付の汎用のDIMM110を具備するメモリシステム100を示した図である。

【図2】図2は、3枚のECC付の汎用のDIMM110を具備するメモリシステム101を示した図である。

【図3】図3は、本発明の第1の実施の形態によるメモリシステム1を表す図である。

【図4】図4は、本発明の第1の実施の形態によるメモリシステム1のデータ書き込み動作を示したフローチャートである。

【図5】図5は、本発明の第1の実施の形態によるメモリシステム1のデータ読み出し動作を示したフローチャートである。

【図6】図6は、本発明の第2の実施の形態によるメモリシステム1aを表す図である。

【図7】図7は、本発明の第3の実施の形態によるメモリシステム1bを表す図である。

【発明を実施するための形態】

【0017】

以下、添付図面を参照して本発明の実施の形態によるメモリシステムを説明する。

【0018】

(第1の実施の形態)

本発明の第1の実施の形態を説明する。図3は、本発明の第1の実施の形態によるメモリシステム1を表す図である。図3を参照すると、メモリシステム1は、メモリモジュール10と、メモリ制御部20と、インタフェース部30とを具備する。メモリシステム1は、外部装置2とシステムインタフェース3を介して接続される。

【0019】

メモリモジュール10は、汎用のメモリモジュールであり、プリント基板上に搭載された、少なくとも8つの半導体メモリ11を有する。メモリモジュール10は、DIMM(Dual Inline Memory Module)やSIMM(Single In−line Memory Module)が例示される。本発明のメモリモジュール10は汎用タイプであることが好ましいため、メモリモジュール10は8つの半導体メモリ11を有することが好適である。しかし、図1に示したDIMM110を用いることも可能であり、メモリモジュール10は9つの半導体メモリ11を有するものであってもよい。

【0020】

半導体メモリ11は、データを記憶可能な半導体素子のチップであり、DRAM(Dynamic Random Access Memory)やSRAM(Static Random Access Memory)が例示される。図3を参照すると、半導体メモリ11は8ビット入出力であるが、4ビット入出力であってもよい。本実施の形態では、半導体メモリ11が8ビット入出力である場合を例に説明する。

【0021】

メモリ制御部20は、外部装置2から受け取る4×8ビット(4バイト)のデータをメモリモジュール10に書き込むとき、4×8ビット(4バイト)のデータに基づいて3×8ビット(3バイト)の誤り検出訂正符号を生成する。尚、3バイトの誤り検出訂正符号は、S8ECD8ED(1バイト訂正2バイト検出)を実現する符号である。メモリ制御部20は、4バイトのデータを1バイトずつ、4つの半導体メモリ11のそれぞれに格納し、3バイトの誤り検出訂正符号を1バイトずつ、他の3つの半導体メモリ11のそれぞれに格納する。

また、メモリ制御部20は、メモリモジュール10の4つの半導体メモリ11に格納された4バイトのデータを読み出すとき、3つの半導体メモリ11に格納された3バイトの誤り検出訂正符号に基づいて、1バイトの誤り訂正、又は2バイトの誤り検出を実行する。言い換えると、メモリ制御部20は、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。

【0022】

メモリ制御部20の詳細を説明する。メモリ制御部20は、検出部21と、インタフェース部22とを備える。検出部21は、データの書き込み時、即ち、システムインタフェース部3を介して外部装置2から提供される4バイトのデータ及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21は、4バイトのデータ、3バイトの誤り検出訂正符号、及び書き込み要求をインタフェース部22に提供する。

【0023】

また、検出部21はデータの読み出し時、即ち、インタフェース部22から4バイトのデータと3バイトの誤り検出訂正符号とを受け取ると、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。詳細には、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11に誤りがあるか否かを判定する。誤りがないと判定した場合、検出部21は読み出した4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。一方、誤りがあると判定した場合、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。ここで、1つの半導体メモリ11の誤り訂正を実行した場合、検出部21は訂正した1バイトのデータを、誤りのデータを格納している半導体メモリ11に提供するために、インタフェース部22へ提供する。そして、検出部21は訂正したデータとして、訂正した1バイトのデータを含む4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。一方、2つの半導体メモリ11の誤り検出を実行した場合、検出部21は異常を外部装置2に知らせる。

【0024】

インタフェース部22は、データの書き込み時、即ち、検出部21から4バイトのデータ、3バイトの誤り検出訂正符号、及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22は、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納する。

【0025】

また、インタフェース部22はデータの読み出し時、即ち、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22は、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。

【0026】

第1の実施の形態によるメモリシステム1の動作を説明する。図4は、本発明の第1の実施の形態によるメモリシステム1のデータ書き込み動作を示したフローチャートである。図4を参照して、本発明の第1の実施の形態によるデータ書き込み動作を説明する。

【0027】

[データ書き込み動作]

ステップS01:

外部装置2は、4バイトのデータ及び書き込み要求を、システムインタフェース部3を介してメモリシステム1に提供する。

【0028】

ステップS02:

検出部21は、4バイトのデータ及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21は、4バイトのデータと、3バイトの誤り検出訂正符号と、書き込み要求とをインタフェース部22に提供する。

【0029】

ステップS03:

インタフェース部22は、検出部21から4バイトのデータ、3バイトの誤り検出訂正符号、及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22は、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納する。

【0030】

図5は、本発明の第1の実施の形態によるメモリシステム1のデータ読み出し動作を示したフローチャートである。図5を参照して、本発明の第1の実施の形態によるデータ読み出し動作を説明する。

【0031】

[データ読み出し動作]

ステップS10:

外部装置2はデータの読み出し要求を、システムインタフェース部3を介してメモリシステム1に提供する。

【0032】

ステップS11:

検出部21は、データの読み出し要求をインタフェース部22に提供する。インタフェース部22は、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22は、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。

【0033】

ステップS12:

検出部21は、インタフェース部22から4バイトのデータと3バイトの誤り検出訂正符号とを受け取る。検出部21は、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11に誤りがあるか否かを判定する。

【0034】

ステップS13:

ステップS12において誤りがないと判定した場合、検出部21は読み出した4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。

【0035】

ステップS14:

ステップS12において誤りがあると判定した場合、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。

【0036】

ステップS15:

ステップS14において、1つの半導体メモリ11の誤り訂正を実行した場合、検出部21は訂正した1バイトのデータを、誤りのデータを格納している半導体メモリ11に提供するために、インタフェース部22へ提供する。そして、検出部21は、訂正したデータとして、訂正した1バイトのデータを含む4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。

【0037】

ステップS16:

ステップS14において、2つの半導体メモリ11の誤り検出を実行した場合、検出部21は異常を外部装置2に知らせる。

【0038】

尚、検出部21は、メモリモジュール10の半導体メモリ11が8ビット入出力の半導体メモリでなく4ビット入出力の半導体メモリである場合、誤り検出訂正符号をS8ECD8EDではなくS4ECD4ED(4ビット訂正8ビット検出)を実現する符号とする。この場合、メモリ制御部20は、12ビットの誤り検出訂正符号に基づいて、4ビットの誤り訂正、又は8ビットの誤り検出を実行する。即ち、この場合でも、メモリシステム1は1枚のメモリモジュール10が有する半導体メモリ11のうちから、1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行することができる。

【0039】

以上のように、本発明のメモリシステム1は、1枚のメモリモジュールのみで1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出という高度なエラー訂正を実現し、高い信頼性を有することができる。その結果、本発明のメモリシステム1は、インタフェース部30を増加することなく、単純で安価なシステムを実現できる効果を奏している。特に、メモリモジュール10としてECC無しの汎用のメモリモジュールを使用すると、より安価にメモリシステム1を実現することができる。

【0040】

(第2の実施の形態)

本発明の第2の実施の形態を説明する。本発明の第2の実施の形態によるメモリシステムは、その基本的構成は第1の実施の形態と同様であり、残った1つの半導体メモリ11に着目したものである。詳細には、第2の実施の形態のメモリシステムは、残った1つの半導体メモリ11を他の半導体メモリ11が故障した場合のスペアとして使用する。

【0041】

図6は、本発明の第2の実施の形態によるメモリシステム1aを表す図である。図6を参照すると、メモリシステム1aは、メモリモジュール10と、メモリ制御部20aと、インタフェース部30とを具備する。メモリモジュール10及びインタフェース部30は、第1の実施の形態のメモリシステム1と同様であるため説明を省略する。

【0042】

メモリ制御部20aは、1つの半導体メモリの誤り訂正を実行した場合、訂正したデータをメモリモジュール10で使用されていない残りの半導体メモリ11に格納する。メモリ制御部20aは、検出部21と、インタフェース部22aとを備える。検出部21は、第1の実施の形態と同様である。

【0043】

インタフェース部22aのデータの書き込み動作は、第1の実施の形態のインタフェース部22と同様であるため、データの読み出し動作について説明する。インタフェース部22aは、データの読み出し時、即ち、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22は、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。その後、検出部21が1つの半導体メモリ11の誤り訂正を実行した場合、インタフェース部22aは検出部21から訂正した1バイトのデータを受け取り、故障した半導体メモリ11の情報を保持する。そして、インタフェース部22aは、訂正された1バイトのデータをデータ及び誤り検出訂正符号が格納されていない残りの半導体メモリ11に格納する。

【0044】

本発明の第2の実施の形態によるメモリシステム1aのデータ読み出し動作を説明する。ここでは、前述した図5を参照して、本発明の第2の実施の形態によるデータ読み出し動作を説明する。

【0045】

[データ読み出し動作]

ステップS10:

外部装置2はデータの読み出し要求を、システムインタフェース部3を介してメモリシステム1に提供する。

【0046】

ステップS11:

検出部21は、データの読み出し要求をインタフェース部22aに提供する。インタフェース部22aは、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22aは、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。

【0047】

ステップS12:

検出部21は、インタフェース部22aから4バイトのデータと3バイトの誤り検出訂正符号とを受け取る。検出部21は、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11に誤りがあるか否かを判定する。

【0048】

ステップS13:

ステップS12において誤りがないと判定した場合、検出部21は読み出した4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。

【0049】

ステップS14:

ステップS12において誤りがあると判定した場合、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。

【0050】

ステップS15:

ステップS14において、1つの半導体メモリ11の誤り訂正を実行した場合、検出部21は訂正した1バイトのデータを、誤りのデータを格納している半導体メモリ11に提供するために、インタフェース部22aへ提供する。そして、検出部21は、訂正した1バイトのデータを含む4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。ここで、インタフェース部22aは検出部21から訂正した1バイトのデータを受け取り、故障した半導体メモリ11の情報を保持する。そして、インタフェース部22aは、訂正された1バイトのデータをデータ及び誤り検出訂正符号が格納されていない残りの半導体メモリ11に格納する。

【0051】

ステップS16:

ステップS14において、2つの半導体メモリ11の誤り検出を実行した場合、検出部21は異常を外部装置2に知らせる。

【0052】

以上のように、本発明の第2の実施の形態のメモリシステム1aは、第1の実施の形態と同様の効果奏すると共に、残った半導体メモリ11をスペアとして使用することによって、更に信頼性に優れたメモリシステムを実現することができる。尚、第2の実施の形態におけるメモリモジュール10は、図1のDIMM110と同様に、9つの半導体メモリ11を有するものであってもよい。この場合、スペア用に用いる半導体メモリ11を2つ(2バイト)とすることができるため、信頼性をより高めることができる。

【0053】

(第3の実施の形態)

本発明の第3の実施の形態を説明する。本発明の第3の実施の形態によるメモリシステムは、その基本的構成は第1の実施の形態と同様であり、残った1つの半導体メモリ11に着目したものである。第3の実施の形態のメモリシステムは、残った1つの半導体メモリ11に外部装置2から受け取ったディレクトリ等の補助情報を格納する。

【0054】

図7は、本発明の第3の実施の形態によるメモリシステム1bを表す図である。図7を参照すると、メモリシステム1bは、メモリモジュール10と、メモリ制御部20bと、インタフェース部30とを具備する。メモリモジュール10及びインタフェース部30は、第1の実施の形態のメモリシステム1と同様であるため説明を省略する。

【0055】

メモリ制御部20bは、外部装置2から4×nビットのデータと共に1×nビットの補助情報を受け取る場合、1×nビットの補助情報をメモリモジュール10で使用されていない残りの半導体メモリ11に格納する。メモリ制御部20bは、検出部21bと、インタフェース部22bとを備える。検出部21bは、データの書き込み時、即ち、システムインタフェース部3を介して外部装置2から提供される4バイトのデータと、書き込み要求と、更に1バイトの補助情報とを受け取る。補助情報はディレクトリ等であり、例えば、外部装置2が複数のCPU(Central Processing Unit)を持つシステムであって、メモリモジュール10を共有する場合に、どのCPUがデータを持っているかを表す情報である。検出部21bは、第1の実施の形態と同様に、4バイトのデータ及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21bは、4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報、及び書き込み要求をインタフェース部22bに提供する。

【0056】

また、検出部21bはデータの読み出し時、即ち、インタフェース部22bから4バイトのデータと、3バイトの誤り検出訂正符号と、1バイトの補助情報とを受け取ると、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。尚、誤りの訂正、又は誤りの検出については、第1の実施の形態の検出部21と同様である。

【0057】

インタフェース部22bは、データの書き込み時、即ち、検出部21bから4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22は、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納し、1バイトの補助情報を残りの半導体メモリ11に格納する。

【0058】

また、インタフェース部22bはデータの読み出し時、即ち、検出部21bから読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出し、残りの半導体メモリ11から補助情報を読み出す。インタフェース部22bは、4バイトのデータ、3バイトの誤り検出訂正符号及び1バイトの補助情報を検出部21bに提供する。

【0059】

本発明の第3の実施の形態によるメモリシステム1bのデータ書き込み動作を説明する。ここでは、前述した図4を参照して、本発明の第3の実施の形態によるデータ書き込み動作を説明する。

【0060】

[データ書き込み動作]

ステップS01:

外部装置2は、4バイトのデータと、書き込み要求と、1バイトの補助情報とを、システムインタフェース部3を介してメモリシステム1に提供する。

【0061】

ステップS02:

検出部21bは、4バイトのデータ、1バイトの補助情報、及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21bは、4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報、及び書き込み要求をインタフェース部22bに提供する。

【0062】

ステップS03:

インタフェース部22bは、検出部21bから4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報、及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22bは、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納し、更に、1バイトの補助情報を残りの半導体メモリ11に格納する。

【0063】

以上のように、本発明の第3の実施の形態のメモリシステム1bは、第1の実施の形態と同様の効果奏すると共に、残った半導体メモリ11に外部装置2から提供される補助情報を格納することができる。つまり、メモリシステム1bは、外部装置2が複数のCPUを持つシステムであって、メモリモジュール10を共有する場合に、どのCPUがデータを持っているかをメモリモジュール10に格納することができる。その結果、メモリシステム1bは、複数のメモリモジュール10を使用しなくても、1枚のメモリモジュール10だけで複数のCPUを持つシステムに対応できる効果を奏する。尚、第3の実施の形態におけるメモリモジュール10は、図1のDIMM110と同様に、9つの半導体メモリ11を有するものであってもよい。この場合、補助情報を2バイトとする構成にしても良いし、補助情報を1バイト、スペア用に1バイトとしてもよい。

【0064】

以上説明した本発明の実施の形態は、矛盾無い範囲で組み合わせることができる。

【符号の説明】

【0065】

1、1a、1b メモリシステム

2 外部装置

3 システムインタフェース部

10 メモリモジュール

11 半導体メモリ

20 メモリ制御部

21、21b 検出部

22、22a、22b インタフェース部

30 インタフェース部

100、101 メモリシステム

110 DIMM

111 DRAM

120 メモリ制御部

121 検出部

122 DIMMインタフェース部

130 汎用DIMMインタフェース部

200 外部装置

300 システムインタフェース部

【技術分野】

【0001】

本発明はメモリシステム及びメモリモジュール制御方法に関する。

【背景技術】

【0002】

サーバ等のミッションクリティカルシステムにおいては、DIMM(Dual Inline Memory Module)のデータエラー対策の為に、ECC(Error Check and Correction:誤り検出及び訂正)による保護を実施している。図1は、ECC付の汎用のDIMM110を具備するメモリシステム100を示した図である。図1を参照すると、メモリシステム100は、DIMM110と、メモリ制御部120と、汎用DIMMインタフェース部130とを具備する。メモリシステム100は、システムインタフェース部300を介して外部装置200と接続され、データの受け渡しを行う。

【0003】

DIMM110は9つのDRAM(Dynamic Random Access Memory)111を有し、各DRAM111は8ビット入出力である。このDIMM110は、8つのDRAM111から構成されるデータ8バイトの汎用DIMMに対して、1つのDRAM111をECC1バイト用に追加したものであり、データ8バイトとECC1バイトとから構成されている。メモリ制御部120は、検出部121と、DIMMインタフェース部122とを備える。

【0004】

メモリシステム100の動作方法を説明する。まず、DIMM110へのデータ書き込み動作を説明する。外部装置200は、8バイトのデータ及び書き込み要求を、システムインタフェース部300を介してメモリシステム100に提供する。検出部121は、8バイトのデータ及び書き込み要求を受け取ると、8バイトのデータに基づいて1バイトの誤り検出訂正符号を生成する。検出部121は、8バイトのデータと1バイトの誤り検出訂正符号とをDIMMインタフェース部122に提供する。DIMMインタフェース部122は、検出部121から8バイトのデータ、1バイトの誤り検出訂正符号、及び書き込み要求を受け取ると、汎用DIMMインタフェース部130を介して、8バイトのデータ及び1バイトの誤り検出訂正符号をメモリモジュール110に格納する。詳細には、DIMMインタフェース部122は、8バイトのデータを1バイトずつ8つのDRAM111に格納し、1バイトの誤り検出訂正符号を残り1つのDRAM111に格納する。

【0005】

次に、DIMM110からのデータ読み出し動作を説明する。外部装置200はデータの読み出し要求を、システムインタフェース部300を介してメモリシステム100に提供する。検出部121は、データの読み出し要求をDIMMインタフェース部122に提供する。DIMMインタフェース部122は、検出部121から読み出し要求を受け取ると、8つのDRAM111から8バイトのデータを読み出し、1つのDRAM111から1バイトの誤り検出訂正符号を読み出す。DIMMインタフェース部122は、8バイトのデータと1バイトの誤り検出訂正符号とを検出部121に提供する。検出部121は、1バイトの誤り検出訂正符号に基づいて、1ビット訂正又は2ビットエラー検出を実行する。

【0006】

エラー訂正及び検出に関連する技術が、特許文献1〜4に開示されている。特許文献1には、汎用のDIMM製品を利用でき、チップ故障を含めてデータを訂正するメモリ装置が開示されている。このメモリ装置は、ECCとして任意のバイト数を指定する手段を有し、データと誤り訂正符号とがメモリ上で同一ワード上に存在することを特徴としている。

【0007】

特許文献2には、EEPROM(Electrically Erasable Programmable Read−Only Memory)のメモリデータ入出力制御方式が開示されている。このメモリデータ入出力制御方式は、書き込むデータをメモリ番地単位で半分のビットを真のデータとし、残り半分のビットは真のデータの論理値を反転させたパリティ情報とすることを特徴としている。

【0008】

特許文献3には、ローエンドサーバシステムにおいて、コストのかかるカスタムASICチップや追加のメモリモジュール等を必要とせずに、チップキルによるエラー検出を実行可能なメモリシステムが開示されている。

【0009】

特許文献4には、既存のSIMM(Single In−line Memory Module)等のメモリを用いて、ECC誤り訂正検出の可能な記憶回路モジュールが開示されている。この記憶回路モジュールは、データ記憶部と、ECC記憶部と、誤り訂正符号を生成する訂正符号生成部と、ECC記憶部の誤り訂正符号を利用して誤り訂正・検出を行う訂正・検出部とを備える。そして、ECC記憶部が誤り訂正機能を有していない記憶素子から構成されることを特徴としている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2009−245218号公報

【特許文献2】特開平02−122349号公報

【特許文献3】特開2001−142789号公報

【特許文献4】特開平10−111839号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

ECCコード(誤り検出訂正符号)の1バイトによって実現可能であるのはSECDED(1ビット訂正2ビット検出)までであるため、前述したメモリシステム100はS8ECD8ED(1バイト訂正2バイト検出)を実行することはできない。つまり、メモリシステム100では、1つのDRAM111の故障を訂正することができないことを意味している。S8ECD8EDに必要な誤り検出訂正符号は3バイトである。従って、メモリシステム100がこれを実現しようとすると、3枚のECC付の汎用のDIMM110を同時に用いる必要がある。図2は、3枚のECC付の汎用のDIMM110を具備するメモリシステム101を示した図である。尚、図2のメモリシステム101の各部は図1のメモリシステム100と同様であるため詳細な説明は省略する。図2のメモリシステム101は、ECC無しの汎用DIMMに比べて高価なECC付の汎用のDIMM110を3枚必要とすることや、汎用DIMMインタフェース130が3倍必要となることによって高価となり、しかも設計も困難になるという問題がある。

【0012】

本発明の目的は、1枚の汎用のメモリモジュールのみで高度なエラー訂正を実現し、信頼性の高いメモリシステムを提供することにある。

【課題を解決するための手段】

【0013】

本発明のメモリシステムは、nビット入出力の第1〜第8半導体メモリを有するメモリモジュールと、外部装置から受け取る4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成し、4×nビットのデータをnビットずつ第1〜第4半導体メモリのそれぞれに格納し、3×nビットの誤り検出訂正符号をnビットずつ第5〜第7半導体メモリのそれぞれに格納するメモリ制御部とを具備する。メモリ制御部は、第1〜第4半導体メモリに格納された4×nビットのデータを読み出すとき、第5〜第7半導体メモリに格納された3×nビットの誤り検出訂正符号に基づいて、第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行する。

【0014】

本発明のメモリモジュール制御方法は、外部装置から受け取る4×nビットのデータを、nビット入出力の第1〜第8半導体メモリを有するメモリモジュールに書き込むステップと、外部装置の要求に基づいて、メモリモジュールから4×nビットのデータを読み出すステップとを具備する。書き込むステップは、外部装置から4×nビットのデータを受け取るステップと、4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成するステップと、4×nビットのデータをnビットずつ、第1〜第4半導体メモリのそれぞれに格納するステップと、3×nビットの誤り検出訂正符号をnビットずつ、第5〜第7半導体メモリのそれぞれに格納するステップとを備える。読み出すステップは、外部装置の要求に基づいて、第1〜第4半導体メモリに格納された4×nビットのデータを読み出すステップと、第5〜第7半導体メモリに格納された3×nビットの誤り検出訂正符号を読み出すステップと、読み出された4×nビットのデータ及び3×nビットの誤り検出訂正符号に基づいて、第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行するステップとを備える。

【発明の効果】

【0015】

本発明のメモリシステムは、1枚の汎用のメモリモジュールのみで高度なエラー訂正を実現し、高い信頼性を得ることができる。

【図面の簡単な説明】

【0016】

【図1】図1は、ECC付の汎用のDIMM110を具備するメモリシステム100を示した図である。

【図2】図2は、3枚のECC付の汎用のDIMM110を具備するメモリシステム101を示した図である。

【図3】図3は、本発明の第1の実施の形態によるメモリシステム1を表す図である。

【図4】図4は、本発明の第1の実施の形態によるメモリシステム1のデータ書き込み動作を示したフローチャートである。

【図5】図5は、本発明の第1の実施の形態によるメモリシステム1のデータ読み出し動作を示したフローチャートである。

【図6】図6は、本発明の第2の実施の形態によるメモリシステム1aを表す図である。

【図7】図7は、本発明の第3の実施の形態によるメモリシステム1bを表す図である。

【発明を実施するための形態】

【0017】

以下、添付図面を参照して本発明の実施の形態によるメモリシステムを説明する。

【0018】

(第1の実施の形態)

本発明の第1の実施の形態を説明する。図3は、本発明の第1の実施の形態によるメモリシステム1を表す図である。図3を参照すると、メモリシステム1は、メモリモジュール10と、メモリ制御部20と、インタフェース部30とを具備する。メモリシステム1は、外部装置2とシステムインタフェース3を介して接続される。

【0019】

メモリモジュール10は、汎用のメモリモジュールであり、プリント基板上に搭載された、少なくとも8つの半導体メモリ11を有する。メモリモジュール10は、DIMM(Dual Inline Memory Module)やSIMM(Single In−line Memory Module)が例示される。本発明のメモリモジュール10は汎用タイプであることが好ましいため、メモリモジュール10は8つの半導体メモリ11を有することが好適である。しかし、図1に示したDIMM110を用いることも可能であり、メモリモジュール10は9つの半導体メモリ11を有するものであってもよい。

【0020】

半導体メモリ11は、データを記憶可能な半導体素子のチップであり、DRAM(Dynamic Random Access Memory)やSRAM(Static Random Access Memory)が例示される。図3を参照すると、半導体メモリ11は8ビット入出力であるが、4ビット入出力であってもよい。本実施の形態では、半導体メモリ11が8ビット入出力である場合を例に説明する。

【0021】

メモリ制御部20は、外部装置2から受け取る4×8ビット(4バイト)のデータをメモリモジュール10に書き込むとき、4×8ビット(4バイト)のデータに基づいて3×8ビット(3バイト)の誤り検出訂正符号を生成する。尚、3バイトの誤り検出訂正符号は、S8ECD8ED(1バイト訂正2バイト検出)を実現する符号である。メモリ制御部20は、4バイトのデータを1バイトずつ、4つの半導体メモリ11のそれぞれに格納し、3バイトの誤り検出訂正符号を1バイトずつ、他の3つの半導体メモリ11のそれぞれに格納する。

また、メモリ制御部20は、メモリモジュール10の4つの半導体メモリ11に格納された4バイトのデータを読み出すとき、3つの半導体メモリ11に格納された3バイトの誤り検出訂正符号に基づいて、1バイトの誤り訂正、又は2バイトの誤り検出を実行する。言い換えると、メモリ制御部20は、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。

【0022】

メモリ制御部20の詳細を説明する。メモリ制御部20は、検出部21と、インタフェース部22とを備える。検出部21は、データの書き込み時、即ち、システムインタフェース部3を介して外部装置2から提供される4バイトのデータ及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21は、4バイトのデータ、3バイトの誤り検出訂正符号、及び書き込み要求をインタフェース部22に提供する。

【0023】

また、検出部21はデータの読み出し時、即ち、インタフェース部22から4バイトのデータと3バイトの誤り検出訂正符号とを受け取ると、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。詳細には、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11に誤りがあるか否かを判定する。誤りがないと判定した場合、検出部21は読み出した4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。一方、誤りがあると判定した場合、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。ここで、1つの半導体メモリ11の誤り訂正を実行した場合、検出部21は訂正した1バイトのデータを、誤りのデータを格納している半導体メモリ11に提供するために、インタフェース部22へ提供する。そして、検出部21は訂正したデータとして、訂正した1バイトのデータを含む4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。一方、2つの半導体メモリ11の誤り検出を実行した場合、検出部21は異常を外部装置2に知らせる。

【0024】

インタフェース部22は、データの書き込み時、即ち、検出部21から4バイトのデータ、3バイトの誤り検出訂正符号、及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22は、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納する。

【0025】

また、インタフェース部22はデータの読み出し時、即ち、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22は、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。

【0026】

第1の実施の形態によるメモリシステム1の動作を説明する。図4は、本発明の第1の実施の形態によるメモリシステム1のデータ書き込み動作を示したフローチャートである。図4を参照して、本発明の第1の実施の形態によるデータ書き込み動作を説明する。

【0027】

[データ書き込み動作]

ステップS01:

外部装置2は、4バイトのデータ及び書き込み要求を、システムインタフェース部3を介してメモリシステム1に提供する。

【0028】

ステップS02:

検出部21は、4バイトのデータ及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21は、4バイトのデータと、3バイトの誤り検出訂正符号と、書き込み要求とをインタフェース部22に提供する。

【0029】

ステップS03:

インタフェース部22は、検出部21から4バイトのデータ、3バイトの誤り検出訂正符号、及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22は、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納する。

【0030】

図5は、本発明の第1の実施の形態によるメモリシステム1のデータ読み出し動作を示したフローチャートである。図5を参照して、本発明の第1の実施の形態によるデータ読み出し動作を説明する。

【0031】

[データ読み出し動作]

ステップS10:

外部装置2はデータの読み出し要求を、システムインタフェース部3を介してメモリシステム1に提供する。

【0032】

ステップS11:

検出部21は、データの読み出し要求をインタフェース部22に提供する。インタフェース部22は、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22は、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。

【0033】

ステップS12:

検出部21は、インタフェース部22から4バイトのデータと3バイトの誤り検出訂正符号とを受け取る。検出部21は、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11に誤りがあるか否かを判定する。

【0034】

ステップS13:

ステップS12において誤りがないと判定した場合、検出部21は読み出した4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。

【0035】

ステップS14:

ステップS12において誤りがあると判定した場合、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。

【0036】

ステップS15:

ステップS14において、1つの半導体メモリ11の誤り訂正を実行した場合、検出部21は訂正した1バイトのデータを、誤りのデータを格納している半導体メモリ11に提供するために、インタフェース部22へ提供する。そして、検出部21は、訂正したデータとして、訂正した1バイトのデータを含む4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。

【0037】

ステップS16:

ステップS14において、2つの半導体メモリ11の誤り検出を実行した場合、検出部21は異常を外部装置2に知らせる。

【0038】

尚、検出部21は、メモリモジュール10の半導体メモリ11が8ビット入出力の半導体メモリでなく4ビット入出力の半導体メモリである場合、誤り検出訂正符号をS8ECD8EDではなくS4ECD4ED(4ビット訂正8ビット検出)を実現する符号とする。この場合、メモリ制御部20は、12ビットの誤り検出訂正符号に基づいて、4ビットの誤り訂正、又は8ビットの誤り検出を実行する。即ち、この場合でも、メモリシステム1は1枚のメモリモジュール10が有する半導体メモリ11のうちから、1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行することができる。

【0039】

以上のように、本発明のメモリシステム1は、1枚のメモリモジュールのみで1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出という高度なエラー訂正を実現し、高い信頼性を有することができる。その結果、本発明のメモリシステム1は、インタフェース部30を増加することなく、単純で安価なシステムを実現できる効果を奏している。特に、メモリモジュール10としてECC無しの汎用のメモリモジュールを使用すると、より安価にメモリシステム1を実現することができる。

【0040】

(第2の実施の形態)

本発明の第2の実施の形態を説明する。本発明の第2の実施の形態によるメモリシステムは、その基本的構成は第1の実施の形態と同様であり、残った1つの半導体メモリ11に着目したものである。詳細には、第2の実施の形態のメモリシステムは、残った1つの半導体メモリ11を他の半導体メモリ11が故障した場合のスペアとして使用する。

【0041】

図6は、本発明の第2の実施の形態によるメモリシステム1aを表す図である。図6を参照すると、メモリシステム1aは、メモリモジュール10と、メモリ制御部20aと、インタフェース部30とを具備する。メモリモジュール10及びインタフェース部30は、第1の実施の形態のメモリシステム1と同様であるため説明を省略する。

【0042】

メモリ制御部20aは、1つの半導体メモリの誤り訂正を実行した場合、訂正したデータをメモリモジュール10で使用されていない残りの半導体メモリ11に格納する。メモリ制御部20aは、検出部21と、インタフェース部22aとを備える。検出部21は、第1の実施の形態と同様である。

【0043】

インタフェース部22aのデータの書き込み動作は、第1の実施の形態のインタフェース部22と同様であるため、データの読み出し動作について説明する。インタフェース部22aは、データの読み出し時、即ち、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22は、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。その後、検出部21が1つの半導体メモリ11の誤り訂正を実行した場合、インタフェース部22aは検出部21から訂正した1バイトのデータを受け取り、故障した半導体メモリ11の情報を保持する。そして、インタフェース部22aは、訂正された1バイトのデータをデータ及び誤り検出訂正符号が格納されていない残りの半導体メモリ11に格納する。

【0044】

本発明の第2の実施の形態によるメモリシステム1aのデータ読み出し動作を説明する。ここでは、前述した図5を参照して、本発明の第2の実施の形態によるデータ読み出し動作を説明する。

【0045】

[データ読み出し動作]

ステップS10:

外部装置2はデータの読み出し要求を、システムインタフェース部3を介してメモリシステム1に提供する。

【0046】

ステップS11:

検出部21は、データの読み出し要求をインタフェース部22aに提供する。インタフェース部22aは、検出部21から読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出す。インタフェース部22aは、4バイトのデータと3バイトの誤り検出訂正符号とを検出部21に提供する。

【0047】

ステップS12:

検出部21は、インタフェース部22aから4バイトのデータと3バイトの誤り検出訂正符号とを受け取る。検出部21は、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11に誤りがあるか否かを判定する。

【0048】

ステップS13:

ステップS12において誤りがないと判定した場合、検出部21は読み出した4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。

【0049】

ステップS14:

ステップS12において誤りがあると判定した場合、検出部21は3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。

【0050】

ステップS15:

ステップS14において、1つの半導体メモリ11の誤り訂正を実行した場合、検出部21は訂正した1バイトのデータを、誤りのデータを格納している半導体メモリ11に提供するために、インタフェース部22aへ提供する。そして、検出部21は、訂正した1バイトのデータを含む4バイトのデータを、システムインタフェース3を介して外部装置2に提供する。ここで、インタフェース部22aは検出部21から訂正した1バイトのデータを受け取り、故障した半導体メモリ11の情報を保持する。そして、インタフェース部22aは、訂正された1バイトのデータをデータ及び誤り検出訂正符号が格納されていない残りの半導体メモリ11に格納する。

【0051】

ステップS16:

ステップS14において、2つの半導体メモリ11の誤り検出を実行した場合、検出部21は異常を外部装置2に知らせる。

【0052】

以上のように、本発明の第2の実施の形態のメモリシステム1aは、第1の実施の形態と同様の効果奏すると共に、残った半導体メモリ11をスペアとして使用することによって、更に信頼性に優れたメモリシステムを実現することができる。尚、第2の実施の形態におけるメモリモジュール10は、図1のDIMM110と同様に、9つの半導体メモリ11を有するものであってもよい。この場合、スペア用に用いる半導体メモリ11を2つ(2バイト)とすることができるため、信頼性をより高めることができる。

【0053】

(第3の実施の形態)

本発明の第3の実施の形態を説明する。本発明の第3の実施の形態によるメモリシステムは、その基本的構成は第1の実施の形態と同様であり、残った1つの半導体メモリ11に着目したものである。第3の実施の形態のメモリシステムは、残った1つの半導体メモリ11に外部装置2から受け取ったディレクトリ等の補助情報を格納する。

【0054】

図7は、本発明の第3の実施の形態によるメモリシステム1bを表す図である。図7を参照すると、メモリシステム1bは、メモリモジュール10と、メモリ制御部20bと、インタフェース部30とを具備する。メモリモジュール10及びインタフェース部30は、第1の実施の形態のメモリシステム1と同様であるため説明を省略する。

【0055】

メモリ制御部20bは、外部装置2から4×nビットのデータと共に1×nビットの補助情報を受け取る場合、1×nビットの補助情報をメモリモジュール10で使用されていない残りの半導体メモリ11に格納する。メモリ制御部20bは、検出部21bと、インタフェース部22bとを備える。検出部21bは、データの書き込み時、即ち、システムインタフェース部3を介して外部装置2から提供される4バイトのデータと、書き込み要求と、更に1バイトの補助情報とを受け取る。補助情報はディレクトリ等であり、例えば、外部装置2が複数のCPU(Central Processing Unit)を持つシステムであって、メモリモジュール10を共有する場合に、どのCPUがデータを持っているかを表す情報である。検出部21bは、第1の実施の形態と同様に、4バイトのデータ及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21bは、4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報、及び書き込み要求をインタフェース部22bに提供する。

【0056】

また、検出部21bはデータの読み出し時、即ち、インタフェース部22bから4バイトのデータと、3バイトの誤り検出訂正符号と、1バイトの補助情報とを受け取ると、3バイトの誤り検出訂正符号に基づいて、4つの半導体メモリ11のうちの1つの半導体メモリ11の誤り訂正、又は2つの半導体メモリ11の誤り検出を実行する。尚、誤りの訂正、又は誤りの検出については、第1の実施の形態の検出部21と同様である。

【0057】

インタフェース部22bは、データの書き込み時、即ち、検出部21bから4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22は、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納し、1バイトの補助情報を残りの半導体メモリ11に格納する。

【0058】

また、インタフェース部22bはデータの読み出し時、即ち、検出部21bから読み出し要求を受け取ると、4つの半導体メモリ11から4バイトのデータを読み出し、3つの半導体メモリ11から3バイトの誤り検出訂正符号を読み出し、残りの半導体メモリ11から補助情報を読み出す。インタフェース部22bは、4バイトのデータ、3バイトの誤り検出訂正符号及び1バイトの補助情報を検出部21bに提供する。

【0059】

本発明の第3の実施の形態によるメモリシステム1bのデータ書き込み動作を説明する。ここでは、前述した図4を参照して、本発明の第3の実施の形態によるデータ書き込み動作を説明する。

【0060】

[データ書き込み動作]

ステップS01:

外部装置2は、4バイトのデータと、書き込み要求と、1バイトの補助情報とを、システムインタフェース部3を介してメモリシステム1に提供する。

【0061】

ステップS02:

検出部21bは、4バイトのデータ、1バイトの補助情報、及び書き込み要求を受け取ると、4バイトのデータに基づいて3バイトの誤り検出訂正符号を生成する。検出部21bは、4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報、及び書き込み要求をインタフェース部22bに提供する。

【0062】

ステップS03:

インタフェース部22bは、検出部21bから4バイトのデータ、3バイトの誤り検出訂正符号、1バイトの補助情報、及び書き込み要求を受け取ると、インタフェース部30を介して、それらをメモリモジュール10に格納する。詳細には、インタフェース部22bは、4バイトのデータを1バイトずつ4つの半導体メモリ11に格納し、3バイトの誤り検出訂正符号を1バイトずつ他の3つの半導体メモリ11に格納し、更に、1バイトの補助情報を残りの半導体メモリ11に格納する。

【0063】

以上のように、本発明の第3の実施の形態のメモリシステム1bは、第1の実施の形態と同様の効果奏すると共に、残った半導体メモリ11に外部装置2から提供される補助情報を格納することができる。つまり、メモリシステム1bは、外部装置2が複数のCPUを持つシステムであって、メモリモジュール10を共有する場合に、どのCPUがデータを持っているかをメモリモジュール10に格納することができる。その結果、メモリシステム1bは、複数のメモリモジュール10を使用しなくても、1枚のメモリモジュール10だけで複数のCPUを持つシステムに対応できる効果を奏する。尚、第3の実施の形態におけるメモリモジュール10は、図1のDIMM110と同様に、9つの半導体メモリ11を有するものであってもよい。この場合、補助情報を2バイトとする構成にしても良いし、補助情報を1バイト、スペア用に1バイトとしてもよい。

【0064】

以上説明した本発明の実施の形態は、矛盾無い範囲で組み合わせることができる。

【符号の説明】

【0065】

1、1a、1b メモリシステム

2 外部装置

3 システムインタフェース部

10 メモリモジュール

11 半導体メモリ

20 メモリ制御部

21、21b 検出部

22、22a、22b インタフェース部

30 インタフェース部

100、101 メモリシステム

110 DIMM

111 DRAM

120 メモリ制御部

121 検出部

122 DIMMインタフェース部

130 汎用DIMMインタフェース部

200 外部装置

300 システムインタフェース部

【特許請求の範囲】

【請求項1】

nビット入出力の第1〜第8半導体メモリを有するメモリモジュールと、

外部装置から受け取る4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成し、前記4×nビットのデータをnビットずつ前記第1〜第4半導体メモリのそれぞれに格納し、前記3×nビットの誤り検出訂正符号をnビットずつ前記第5〜第7半導体メモリのそれぞれに格納するメモリ制御部と

を具備し、

前記メモリ制御部は、前記第1〜第4半導体メモリに格納された前記4×nビットのデータを読み出すとき、前記第5〜第7半導体メモリに格納された前記3×nビットの誤り検出訂正符号に基づいて、前記第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行する

メモリシステム。

【請求項2】

請求項1に記載のメモリシステムであって、

前記メモリ制御部は、1つの半導体メモリの誤り訂正を実行した場合、訂正したデータを前記第8半導体メモリに格納する

メモリシステム。

【請求項3】

請求項2に記載のメモリシステムであって、

前記メモリモジュールは、

nビット入出力の第9半導体メモリ

を更に有し、

前記メモリ制御部は、

前記外部装置から前記4×nビットのデータと共に1×nビットのディレクトリデータを受け取る場合、前記1×nビットのディレクトリデータを前記第9半導体メモリに格納する

メモリシステム。

【請求項4】

請求項1乃至3の何れか一項に記載のメモリシステムであって、

nは4又は8である

メモリシステム。

【請求項5】

外部装置から受け取る4×nビットのデータを、nビット入出力の第1〜第8半導体メモリを有するメモリモジュールに書き込むステップと、

前記外部装置の要求に基づいて、前記メモリモジュールから前記4×nビットのデータを読み出すステップと

を具備し、

前記書き込むステップは、

前記外部装置から前記4×nビットのデータを受け取るステップと、

前記4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成するステップと、

前記4×nビットのデータをnビットずつ、前記第1〜第4半導体メモリのそれぞれに格納するステップと、

前記3×nビットの誤り検出訂正符号をnビットずつ、前記第5〜第7半導体メモリのそれぞれに格納するステップと

を備え、

前記読み出すステップは、

前記外部装置の要求に基づいて、前記第1〜第4半導体メモリに格納された前記4×nビットのデータを読み出すステップと、

前記第5〜第7半導体メモリに格納された前記3×nビットの誤り検出訂正符号を読み出すステップと、

読み出された前記4×nビットのデータ及び前記3×nビットの誤り検出訂正符号に基づいて、前記第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行するステップと

を備える

メモリモジュール制御方法。

【請求項6】

請求項5に記載のメモリモジュール制御方法であって、

前記実行するステップは、

1つの半導体メモリの誤り訂正を実行した場合、訂正したデータを前記第8半導体メモリに格納するステップ

を備える

メモリモジュール制御方法。

【請求項7】

請求項6に記載のメモリモジュール制御方法であって、

前記書き込むステップは、

前記外部装置から前記4×nビットのデータと、1×nビットのディレクトリデータとを受け取るステップと、

前記1×nビットのディレクトリデータを、前記メモリモジュールが有するnビット入出力の第9半導体メモリに格納するステップと

を更に備える

メモリモジュール制御方法。

【請求項8】

請求項5乃至7の何れか一項に記載のメモリモジュール制御方法であって、

nは4又は8である

メモリモジュール制御方法。

【請求項1】

nビット入出力の第1〜第8半導体メモリを有するメモリモジュールと、

外部装置から受け取る4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成し、前記4×nビットのデータをnビットずつ前記第1〜第4半導体メモリのそれぞれに格納し、前記3×nビットの誤り検出訂正符号をnビットずつ前記第5〜第7半導体メモリのそれぞれに格納するメモリ制御部と

を具備し、

前記メモリ制御部は、前記第1〜第4半導体メモリに格納された前記4×nビットのデータを読み出すとき、前記第5〜第7半導体メモリに格納された前記3×nビットの誤り検出訂正符号に基づいて、前記第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行する

メモリシステム。

【請求項2】

請求項1に記載のメモリシステムであって、

前記メモリ制御部は、1つの半導体メモリの誤り訂正を実行した場合、訂正したデータを前記第8半導体メモリに格納する

メモリシステム。

【請求項3】

請求項2に記載のメモリシステムであって、

前記メモリモジュールは、

nビット入出力の第9半導体メモリ

を更に有し、

前記メモリ制御部は、

前記外部装置から前記4×nビットのデータと共に1×nビットのディレクトリデータを受け取る場合、前記1×nビットのディレクトリデータを前記第9半導体メモリに格納する

メモリシステム。

【請求項4】

請求項1乃至3の何れか一項に記載のメモリシステムであって、

nは4又は8である

メモリシステム。

【請求項5】

外部装置から受け取る4×nビットのデータを、nビット入出力の第1〜第8半導体メモリを有するメモリモジュールに書き込むステップと、

前記外部装置の要求に基づいて、前記メモリモジュールから前記4×nビットのデータを読み出すステップと

を具備し、

前記書き込むステップは、

前記外部装置から前記4×nビットのデータを受け取るステップと、

前記4×nビットのデータに基づいて、3×nビットの誤り検出訂正符号を生成するステップと、

前記4×nビットのデータをnビットずつ、前記第1〜第4半導体メモリのそれぞれに格納するステップと、

前記3×nビットの誤り検出訂正符号をnビットずつ、前記第5〜第7半導体メモリのそれぞれに格納するステップと

を備え、

前記読み出すステップは、

前記外部装置の要求に基づいて、前記第1〜第4半導体メモリに格納された前記4×nビットのデータを読み出すステップと、

前記第5〜第7半導体メモリに格納された前記3×nビットの誤り検出訂正符号を読み出すステップと、

読み出された前記4×nビットのデータ及び前記3×nビットの誤り検出訂正符号に基づいて、前記第1〜第4半導体メモリのうちの1つの半導体メモリの誤り訂正、又は2つの半導体メモリの誤り検出を実行するステップと

を備える

メモリモジュール制御方法。

【請求項6】

請求項5に記載のメモリモジュール制御方法であって、

前記実行するステップは、

1つの半導体メモリの誤り訂正を実行した場合、訂正したデータを前記第8半導体メモリに格納するステップ

を備える

メモリモジュール制御方法。

【請求項7】

請求項6に記載のメモリモジュール制御方法であって、

前記書き込むステップは、

前記外部装置から前記4×nビットのデータと、1×nビットのディレクトリデータとを受け取るステップと、

前記1×nビットのディレクトリデータを、前記メモリモジュールが有するnビット入出力の第9半導体メモリに格納するステップと

を更に備える

メモリモジュール制御方法。

【請求項8】

請求項5乃至7の何れか一項に記載のメモリモジュール制御方法であって、

nは4又は8である

メモリモジュール制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−177964(P2012−177964A)

【公開日】平成24年9月13日(2012.9.13)

【国際特許分類】

【出願番号】特願2011−39210(P2011−39210)

【出願日】平成23年2月25日(2011.2.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年9月13日(2012.9.13)

【国際特許分類】

【出願日】平成23年2月25日(2011.2.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]