メモリシステム

【課題】フラッシュメモリに記録されたデータの信頼性を向上させることができる技術を提供することを課題とする。

【解決手段】メモリ4,6は、NANDフラッシュメモリである。メモリコントローラ3は、ホストシステム1の要求に応じてメモリ4からデータ45Mを読み出し、データ45Mをホストシステム1へ出力する。メモリコントローラ5は、バックアップ用のメモリ6の各ブロックに格納されたデータを検査する。メモリコントローラ5は、メモリ6のページの中から検査対象のブロックを決定し、検査対象のブロックからデータ45Cを読み出す。ECC回路51は、データ45Cのエラーを検出する。データ45Cからエラーが検出された場合、エラー訂正されたデータ45Cが、検査対象のブロックに書き戻される。メモリコントローラ3は、所定の切り替え条件が満たされた場合、アクセス対象をメモリ4からメモリ6へ切り替える。

【解決手段】メモリ4,6は、NANDフラッシュメモリである。メモリコントローラ3は、ホストシステム1の要求に応じてメモリ4からデータ45Mを読み出し、データ45Mをホストシステム1へ出力する。メモリコントローラ5は、バックアップ用のメモリ6の各ブロックに格納されたデータを検査する。メモリコントローラ5は、メモリ6のページの中から検査対象のブロックを決定し、検査対象のブロックからデータ45Cを読み出す。ECC回路51は、データ45Cのエラーを検出する。データ45Cからエラーが検出された場合、エラー訂正されたデータ45Cが、検査対象のブロックに書き戻される。メモリコントローラ3は、所定の切り替え条件が満たされた場合、アクセス対象をメモリ4からメモリ6へ切り替える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フラッシュメモリからデータが繰り返し読み出されることにより、データが意図せず書き換えられるリードディスターブ現象に対処する技術に関する。

【背景技術】

【0002】

NANDフラッシュメモリは、再書き込み可能な不揮発性半導体メモリである。NANDフラッシュメモリは、高集積化を実現しながら、低コスト化が図られているため、SDメモリカードなどの形態で広く普及している。

【0003】

NANDフラッシュメモリにおいては、特定のセルが繰り返し読み出されることにより、記憶データが意図せず書き換えられる現象が生じることが分かっている。この現象は、リードディスターブ(Read Disturb)現象と呼ばれている現象であり、NANDフラッシュメモリを利用する上での課題となっている。

【0004】

特定のセルに対する読み出し処理が繰り返し行われた場合であっても、一旦、そのセルを含む領域に対してデータの更新が行われれば、セルの状態が修復されるため、リードディスターブの発生が情報処理に影響を与えることを回避できる。しかし、特定のセルに対して書き込み処理が行われず、読み出し処理だけが繰り返し行われる場合、リードディスターブの発生する可能性が高くなり、情報処理に影響を与える可能性もある。

【0005】

最近では、NANDフラッシュメモリは、情報処理装置のプログラムメモリとしてROMのような役割で利用されるケースが多くなっている。NANDフラッシュメモリがそのように利用された場合、連続的な読み出し処理のみが行われるため、リードディスターブの発生可能性が高くなる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−139503号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記特許文献1には、第1の記録媒体及び第2の記録媒体に同一のデータを書き込む記憶装置が記載されている。第1の記録媒体及び第2の記録媒体は、不揮発性メモリである。第2の記録媒体は、ミラー書き込み用として用いられる。上記特許文献1の記憶装置は、データ読み出し指令が記憶装置に入力された場合、第1の記録媒体及び第2の記録媒体の両者からデータを読み出す。第1の記録媒体から読み出されたデータからエラーを検出した場合、記憶装置は、第2の記録媒体から読み出したデータを出力する。

【0008】

上記特許文献1では、第2の記録媒体からの読み出しが第1の記録媒体からの読み出しと同じ頻度で行われる。このため、リードディスターブが、第1記録媒体だけでなく、第2記録媒体で発生する可能性が高い。第2の記録媒体がミラー書き込み用として用いられるにも関わらず、第2の記録媒体に書き込まれたデータの信頼性を確保することができない。

【0009】

そこで、本発明は前記問題点に鑑み、フラッシュメモリに記録されたデータの信頼性を向上させることができる技術を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記課題を解決するため、請求項1記載の発明は、メモリシステムであって、再書き込み可能な不揮発性メモリである第1メモリと、再書き込み可能な不揮発性メモリであり、前記第1メモリのバックアップ用のメモリとして設定された第2メモリと、前記第1メモリと前記第2メモリとにアクセスするメモリコントローラと、を備え、前記メモリコントローラは、ホストから書き込み要求を受け付けた場合、前記第1メモリ及び前記第2メモリに対して同一のデータを書き込み、前記ホストから読み出し要求を受け付けた場合、前記第1メモリからデータを読み出すアクセス制御部と、前記第2メモリが有するデータ領域のうちいずれかの領域を検査領域として決定する検査領域決定部と、前記検査領域から読み出された検査対象データに対してエラー検出を行い、前記検査対象データからエラーが検出された場合、前記検査対象データのエラーを訂正するエラー訂正部と、を備え、前記アクセス制御部は、訂正された検査対象データを前記検査領域に再書き込みする。

【0011】

請求項2記載の発明は、請求項1に記載のメモリシステムであって、前記検査領域決定部は、前記第1メモリに含まれる第1領域が優先検査条件を満たした場合、前記第2メモリに含まれ、かつ、前記第1領域に格納されたデータと同一のデータを格納する第2領域を、優先的に前記検査領域として決定する。

【0012】

請求項3記載の発明は、請求項1に記載のメモリシステムであって、前記エラー訂正部は、前記検査対象データからエラーを検出した場合、前記検査対象データのエラーを訂正するか否かを判定し、前記アクセス制御部は、エラーを訂正すると判定された場合、前記訂正された検査対象データを前記検査領域に再書き込みする。

【0013】

請求項4記載の発明は、請求項2または請求項3に記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、を備え、前記優先検査条件は、前記第1メモリから読み出されたデータのエラービット数が予め設定された第1優先検査基準値を超えることである。

【0014】

請求項5記載の発明は、請求項2または請求項3に記載のメモリシステムであって、前記メモリコントローラは、前記第1メモリが有するデータ領域ごとに、データが読み出される回数をカウントするカウンタ、を備え、前記優先検査条件は、前記読み出し回数が予め設定された第2優先検査基準値を超えることである。

【0015】

請求項6記載の発明は、請求項2ないし請求項5のいずれかに記載のメモリシステムであって、前記検査領域決定部は、前記第1領域が前記優先検査条件を満たし、かつ、前記第2領域が検査されていない場合、前記第2領域を優先的に前記検査領域として決定する。

【0016】

請求項7記載の発明は、請求項1ないし請求項6のいずれかに記載のメモリシステムであって、前記アクセス制御部は、前記エラー訂正部が前記検査対象データのエラーを訂正できない場合、前記第1メモリに含まれ、かつ、前記検査領域に格納されたデータと同一のデータを格納するデータ領域から復旧データを読み出し、前記復旧データを前記検査領域に再書き込みする。

【0017】

請求項8記載の発明は、請求項1または請求項2に記載のメモリシステムであって、前記アクセス制御部は、所定の切り替え条件が満たされた場合、前記読み出し要求を受け付けたときにデータを読み出すメモリを、前記第1メモリから前記第2メモリに切り替えるとともに、前記第2メモリのバックアップ用のメモリとして前記第1メモリを設定する。

【0018】

請求項9記載の発明は、請求項8に記載のメモリシステムであって、前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記読み出し要求に応じて前記第1メモリから読み出されたデータのエラービット数が予め設定された第1切替基準値を超えることである。

【0019】

請求項10記載の発明は、請求項8に記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリからのデータの読み出し回数をカウントするカウンタ、を備え、前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記第1メモリからのデータの読み出し回数が予め設定された第2切替基準値を超えることである。

【0020】

請求項11記載の発明は、請求項8ないし請求項10のいずれかに記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、を備え、前記切り替え条件は、前記第1メモリから読み出されたデータのエラーを訂正できないことである。

【0021】

請求項12記載の発明は、請求項1ないし請求項11のいずれかに記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリ及び前記第2メモリのうち、前記読み出し要求に基づいてデータが読み出されるメモリに対するアクセスを制御する第1メモリコントローラと、前記第1メモリ及び前記第2メモリのうち、バックアップ用のメモリに対するアクセスを制御する第2メモリコントローラと、を備える。

【発明の効果】

【0022】

本発明のメモリシステムは、バックアップ用の第2メモリのデータ領域のいずれかを検査領域として決定し、検査領域からデータを読み出す。読み出したデータにエラーがある場合、エラー訂正されたデータが、検査領域に書き戻される。検査領域に格納されたデータと同一のデータを格納する第1メモリのデータ領域でリードディスターブが発生した場合であっても、検査領域に格納されたデータのエラーが訂正されているため、フラッシュメモリに格納されるデータの信頼性を向上させることができる。

【0023】

また、本発明のメモリシステムは、切り替え条件が満たされた場合、第1メモリを読み出し用のメモリからバックアップ用のメモリに変更し、第2メモリをバックアップ用のメモリから読み出し用のメモリに変更する。第1メモリ及び第2メモリが交互に読み出し用のメモリとして使用されるため、第1メモリ及び第2メモリの読み出し負荷を軽減でき、リードディスターブの発生を抑制することができる。

【図面の簡単な説明】

【0024】

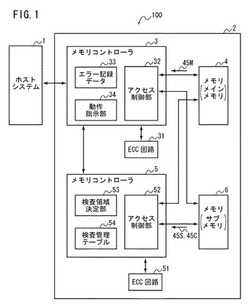

【図1】本発明の実施の形態による情報処理システムの構成を示す機能ブロック図である。

【図2】図1に示すメモリの構成を示す図である。

【図3】図1に示すメモリシステムの動作の概略を示す図である。

【図4】図1に示すメインメモリにアクセスするメモリコントローラの動作を示すフローチャートである。

【図5】図1に示すエラー記録データの一例を示す図である。

【図6】図4に示す代替データ取得処理のフローチャートである。

【図7】図1に示すサブメモリにアクセスするメモリコントローラの動作を示すフローチャートである。

【図8】図1に示す検査管理テーブルを示す図である。

【図9】図1に示すサブメモリにアクセスするメモリコントローラの動作を示すフローチャートである。

【図10】図9に示すデータ復旧処理のフローチャートである。

【図11】図4に示すアクセス対象のメモリを切り替える処理のフローチャートである。

【図12】図1に示すメモリコントローラの変形例を示す図である。

【発明を実施するための形態】

【0025】

以下、図面を参照しつつ本発明の実施の形態について説明する。

【0026】

{1.全体構成}

図1は、本実施の形態に係る情報処理システム100の機能ブロック図である。情報処理システム100は、ホストシステム1と、メモリシステム2とを備える。メモリシステム2は、メモリコントローラ3,5と、メモリ4,6と、ECC(Error Checking and Correction)回路31,51とを備える。

【0027】

情報処理システム100は、たとえば、ゲームシステムを構成する。この場合、ホストシステム1は、ゲーム装置本体を構成し、メモリシステム2は、ゲーム装置本体に対して着脱可能なゲームカートリッジを構成する。なお、メモリシステム2は、ゲーム装置本体に内蔵されてもよい。

【0028】

メモリ4,6は、再書き込み可能な不揮発性半導体メモリである。本実施の形態において、メモリ4,6は、NANDフラッシュメモリである。ここで、メモリ4は、読み出し用のメモリ(メインメモリ)である。メインメモリは、読み出し要求がホストシステム1から入力された際に、データの読み出し対象となるメモリである。メモリ6は、バックアップ用のメモリ(サブメモリ)である。メモリ4,6は、後述する切り替え条件が満たされた場合、機能が切り替わる。すなわち、メモリ4は、メインメモリからサブメモリへ切り替わり、メモリ6は、サブメモリからメインメモリへ切り替わる。

【0029】

メモリコントローラ3は、メモリ4,6のうち、メインメモリに設定されたメモリに対するデータの読み出し及び書き込みを制御する。メモリコントローラ5は、メモリ4,6のうち、サブメモリに設定されたメモリに対するデータの読み出し及び書き込みを制御する。すなわち、メモリコントローラ3、5は、切り替え条件に基づいて、アクセス対象のメモリを切り替える。

【0030】

ECC回路31は、メモリコントローラ3がメインメモリから読み出したデータに対するエラー検出処理と、エラー訂正処理とを実行する。ECC回路51は、メモリコントローラ5がサブメモリから読み出したデータに対するエラー検出処理と、エラー訂正処理とを実行する。

【0031】

以下、メモリ4がメインメモリに設定され、メモリ6がサブメモリに設定されていると仮定して、本実施の形態を説明する。メモリ4を、「メインメモリ4」と呼び、メモリ6を、「サブメモリ6」と呼ぶ。

【0032】

メモリコントローラ3は、ホストシステム1からの各種要求を受け付けるとともに、メインメモリ4に対するアクセスを制御する。メモリコントローラ3は、ホストシステム1からデータの書き込み要求を受け付けた場合、メモリコントローラ5に対して、データの書き込みを指示する。メモリコントローラ3は、アクセス制御部32と、動作指示部34とを備える。

【0033】

アクセス制御部32は、ホストシステム1の要求に応じて、メインメモリ4からデータを読み出し、メインメモリ4にデータを書き込む。メインメモリ4から読み出されたデータを、データ45Mと呼ぶ。データ45Mは、1ページ分のデータである。

【0034】

動作指示部34は、メモリコントローラ5に対して各種動作の実行を指示する。たとえば、動作指示部34は、ホストシステム1からデータの書き込み要求を受け付けた場合、データの書き込みをメモリコントローラ5に指示する。動作指示部34は、切り替え条件が満たされた場合、アクセス対象の変更をメモリコントローラ5に指示する。

【0035】

メモリコントローラ3は、エラー記録データ33を保持する。エラー記録データ33は、読み出し対象のページを有するブロックの論理アドレスと、読み出されたデータ45Mのエラービット数とが記録されたデータである。具体的には、ECC回路31が、メインメモリ4から読み出されたデータ45Mに対してエラー検出処理を行う。メモリコントローラ3は、エラー記録データ33として、データ45Mが格納されたページを含むブロックの論理アドレスと、検出されたエラービット数とを対応付けて記録する。エラー記録データ33の詳細は、後述する。

【0036】

メモリコントローラ5は、サブメモリ6に格納されたデータにエラーが発生しているか否かを、ブロックごとに検査する。メモリコントローラ5は、動作指示部34から指示を受け付けた場合を除き、メモリコントローラ3とは独立に動作する。メモリコントローラ5は、アクセス制御部52と、検査領域決定部53とを備える。

【0037】

アクセス制御部52は、サブメモリ6からデータを読み出し、サブメモリ6にデータを書き込む。検査領域決定部53は、サブメモリ6が有するブロックの中から検査対象のブロックを決定する。通常であれば、検査領域決定部53は、予め設定された順序に基づいて、サブメモリ6の各ブロックを検査対象として決定する。しかし、サブメモリ6の中で優先検査ブロックに設定されたブロックが存在する場合、検査領域決定部53は、設定された順序に関係なく、検査対象として優先検査ブロックを決定する。

【0038】

メモリコントローラ5は、検査管理テーブル54を保持する。検査管理テーブル54は、サブメモリ6の各ブロックの検査状況を記録したテーブルである。サブメモリ6の各ブロックの検査の詳細については、後述する。

【0039】

{2.メインメモリ4及びサブメモリ6の構成}

図2は、メインメモリ4及びサブメモリ6の構成を示す図である。具体的には、メインメモリ4及びサブメモリ6は、同一の構成を有し、それぞれ1枚のダイで構成される。ダイは、複数のバンクを含む。図2に示す例では、ダイは、J個のバンクを含む。バンクは、複数のブロックを含む。図2に示す例では、バンクは、M個のブロックを含む。ブロックは、複数のページを含む。図2に示す例では、ブロックは、Z個のページを含む。

【0040】

ページは、メインメモリ4及びサブメモリ6におけるデータの読み出し単位及び書き込み単位である。メモリコントローラ3は、メインメモリ4に記録されているデータをページ単位で読み出し、書き込みが指示されたデータをページ単位でメインメモリ4に書き込むことができる。同様に、メモリコントローラ5は、サブメモリ6に記録されているデータをページ単位で読み出し、書き込みが指示されたデータをページ単位でサブメモリ6に書き込むことができる。

【0041】

メインメモリ4及びサブメモリ6は、同一の論理アドレス空間を有する。メモリコントローラ3,5は、メインメモリ4及びサブメモリ6にそれぞれデータを書き込む場合、同一の論理アドレスを有するページにデータを書き込む。たとえば、メモリコントローラ3がメインメモリ4のページ7Pにデータを書き込む場合、メモリコントローラ5は、同様に、サブメモリ6のページ7Pに同一のデータを書き込む。図2に示すように、メインメモリ4のページ7Pと、サブメモリ6のページ7Pとは、両者ともに、ブロック7B(BANK#0)に含まれる先頭ページ(Page#0)であることがわかる。

【0042】

ブロックは、メインメモリ4及びサブメモリ6におけるデータの消去単位である。メモリコントローラ3,5は、メインメモリ4及びサブメモリ6に格納されたデータをブロック単位で消去することができる。

【0043】

{3.動作概略}

以下、図3を用いて、メモリシステム2の動作の概略を説明する。図3は、メモリシステム2の動作の概略を示す図である。図3において、ホストシステム1、メモリコントローラ3,5、メインメモリ4及びサブメモリ6以外の構成の表示を省略している。

【0044】

{3.1.データ書き込み}

ホストシステム1が、データの書き込み要求をメモリシステム2へ出力する(ステップS1)。メモリコントローラ3が、書き込み要求に基づいて、データを書き込む対象となるページ(書き込みページ)を決定する。メモリコントローラ3は、メインメモリ4の書き込みページにデータを書き込む(ステップS2)。また、メモリコントローラ3は、書き込み指示として、データと、書き込みページの論理アドレスとをメモリコントローラ5に通知する(ステップS3)。メモリコントローラ5は、書き込み指示に基づいて、サブメモリ6の書き込みページにデータを書き込む(ステップS4)。これにより、メインメモリ4及びサブメモリ6の同一アドレスには、同一のデータが書き込まれる。

【0045】

{3.2.データ読み出し}

ホストシステム1が、データの読み出し要求をメモリシステム2へ出力する(ステップS5)。メモリコントローラ3は、読み出し要求に基づいて、メインメモリ4からデータ45Mを読み出し、データ45Mをホストシステム1へ出力する(ステップS6)。ECC回路31は、メインメモリ4から読み出されたデータ45Mに対してエラー検出処理を行う。エラーが検出された場合、エラー訂正されたデータ45Mが、ホストシステム1に出力される。

【0046】

メモリコントローラ5は、原則として、ホストシステム1の読み出し要求に応じて、サブメモリ6からデータを読み出さない。しかし、ECC回路31がデータ45Mのエラーを訂正できない場合、メモリコントローラ5は、メモリコントローラ3の指示に応じて、サブメモリ6からデータ45Sを読み出す。メモリコントローラ3は、データ45Mに代えて、データ45Sをホストシステム1へ出力する。この結果、サブメモリ6に対するデータの読み出し回数が減少するため、サブメモリ6におけるリードディスターブの発生が抑制される。

【0047】

{3.3.サブメモリ6の検査}

メモリコントローラ5は、サブメモリ6に格納されたデータの信頼性を向上させるために、サブメモリ6に格納されたデータを検査する。サブメモリ6の検査は、メインメモリ4が読み出し用のメモリとして用いられている間に実行される。

【0048】

具体的には、メモリコントローラ5は、サブメモリ6の検査対象のブロックからデータ45Cを読み出す(ステップS7)。データ45Cは、検査用に読み出されたデータであり、1ブロック分のデータである。データ45Cからエラーが検出された場合、メモリコントローラ5は、エラー訂正されたデータ45Cを、検査対象のブロックに書き戻す。

【0049】

メモリコントローラ5は、通常であれば、予め設定された順序で、サブメモリ6の各ブロックを検査する。しかし、リードディスターブなどにより、メインメモリ4においてビットエラーを有するページ(エラーページ)が発生することがある。この場合、メモリコントローラ3は、エラーページを有するブロック(エラーブロック)を特定する。メモリコントローラ5は、エラーブロックに格納されたデータと同一のデータを格納するサブメモリ6のブロックを優先的に検査する。たとえば、メインメモリ4のブロック7Bと、サブメモリ6のブロック7Bとには、同一のデータが書き込まれている。メインメモリ4のページ7Pから読み出されたデータにエラーが検出された場合、メモリコントローラ5は、サブメモリ6のブロックのうち、ページ7Pを有するブロック7Bを優先的に検査する。これにより、サブメモリ6に格納されるデータのうち、エラーブロックに書き込まれたデータと同一のデータの信頼性を向上させることができる。

【0050】

{3.4.メモリの切り替え}

メモリコントローラ3は、切り替え条件が満たされた場合、アクセス対象のメモリを切り替える(ステップS8)。切り替え条件は、サブメモリ6の全てのブロックの検査が終了し、かつ、ホストシステム1の読み出し要求に基づいて、メインメモリ4から読み出されたデータ45Mのエラービット数が所定のしきい値を超えた場合である。以後、メモリコントローラ3は、ホストシステム1から読み出し要求を受け付けた場合、メモリ6からデータを読み出す。メモリコントローラ5は、メモリ4の各ページの検査を開始する。

【0051】

このように、メモリ4,6が、交互にメインメモリとして使用されるため、メモリ4,6の読み出し負荷を分散させることができる。したがって、メモリ4,6におけるリードディスターブの発生を抑制することができる。また、メモリ4,6の各ページは、メモリ4,6がサブメモリとして用いられる間に、メモリコントローラ5により検査される。このため、メモリ4,6に格納されるデータの信頼性を維持することができる。

【0052】

{4.メモリコントローラ3の動作}

以下、メモリコントローラ3の動作について、図1及び図4を参照しながら説明する。

【0053】

{4.1.読み出し処理}

図4は、読み出し要求(ステップS5、図3参照)を受け付けたときのメモリコントローラ3の動作を示すフローチャートである。メモリコントローラ3は、ホストシステム1の読み出し要求に応じてメインメモリ4からデータ45Mを読み出す。データ45Mのエラーを訂正できない場合、メモリコントローラ3は、データ45Mに代えて、サブメモリ6から読み出されたデータ45Sをホストシステム1へ出力する。

【0054】

メモリコントローラ3は、ホストシステム1から読み出し要求(ステップS5)を受け付けた場合、図4の処理を開始する。アクセス制御部32が、読み出し要求に基づいて読み出し対象ページを決定し、メインメモリ4の読み出し対象ページからデータ45Mを読み出す(ステップS401)。ECC回路31は、読み出したデータ45Mに対してエラー検出処理を行う(ステップS402)。データ45Mからエラーが検出されなかった場合(ステップS402においてNo)、メモリコントローラ3は、データ45Mをホストシステム1へ出力する(ステップS407)。読み出し対象ページが複数である場合、ECC回路31は、各ページから読み出されたデータ45Mに対してエラー検出処理を行う。

【0055】

データ45Mからエラーが検出された場合(ステップS402においてYes)、ECC回路31は、検出されたエラーの訂正が可能であるか否かを確認する(ステップS403)。具体的には、ECC回路31のエラー訂正能力に基づいて、データ45Mのエラーの訂正が可能であるか否かが判断される。

【0056】

データ45Mのエラーを訂正できない場合(ステップS403においてNo)、メモリコントローラ3は、データ45Mをホストシステム1に出力することができない。このため、メモリコントローラ3は、メモリコントローラ5を介して、サブメモリからデータ45Sを取得する代替データ取得処理を実行する(ステップS411)。データ45M、45Sは、メインメモリ4及びサブメモリ6にそれぞれ書き込まれるときには、同一のデータである。すなわち、代替データ取得処理は、メモリ45Mに代わるデータとして、データ45Mと同一のデータを格納するページからデータ45Sを取得する処理である。代替データ取得処理の後に、メモリコントローラ3は、アクセス対象のメモリを切り替える(ステップS410)。ステップS410,S411の詳細は後述する。

【0057】

データ45Mのエラーの訂正が可能な場合(ステップS403においてYes)、ECC回路31は、データ45Mのエラーを訂正する(ステップS404)。訂正されたデータ45Mは、後述するように、ホストシステム1へ出力されるが(ステップS407)、メインメモリ4へ書き戻されることはない。これは、訂正されたデータ45Mをメインメモリ4に書き戻すことにより、メモリコントローラ3の負荷が大きくなることを防止するためである。データ45Mのエラーは、メインメモリ4がサブメモリに切り替えられた後に、メモリコントローラ5により訂正される。

【0058】

メモリコントローラ3は、エラーページを有するエラーブロックに関する情報を、エラー記録データ33として作成する(ステップS405)。エラーページは、データ45Mからエラーが検出されたページである。エラー記録データ33は、たとえば、メモリコントローラ3が備えるレジスタまたはメインメモリ4に格納される。

【0059】

図5は、エラー記録データ33の一例を示す図である。図5に示すように、エラー記録データ33は、データ45Mを格納するエラーブロックの論理アドレスと、データ45Mのエラービット数とを有する。メモリコントローラ3は、ホストシステム1からの読み出し要求に応じて、複数のページからデータ45Mを読み出すことがある。この場合、メモリコントローラ3は、複数のページの中から、エラービット数が最大のエラーページを特定する。メモリコントローラ3は、特定されたエラーページを有するブロックの論理アドレスと、特定されたエラーページのエラービット数とを対応付けて、エラー記録データ33に記録する。メモリコントローラ3は、エラー記録データ33をメモリコントローラ5へ出力することにより、エラーブロックの発生を通知する(ステップS406)。詳細は後述するが、メモリコントローラ5は、サブメモリ6のブロックのうち、エラーブロックに格納されたデータと同一のデータを格納するブロックを優先的に検査する。

【0060】

エラー記録データ33は、複数のエラーブロックを記録したデータであってもよい。たとえば、メモリコントローラ3は、10ブロック分のエラーブロックに関する情報を、エラー記録データ33として保持してもよい。この場合、メモリコントローラ3は、10ブロック分のエラーブロックがエラー記録データ33に記録された場合、エラー記録データ33をメモリコントローラ5に出力すればよい。また、エラー記録データ33は、エラーページの論理アドレスと、エラービット数とを対応付けたデータであってもよい。この場合、メモリコントローラ5が、エラーページの論理アドレスに基づいて、エラーブロックのアドレスを特定すればよい。

【0061】

再び、図1及び図4を参照する。ステップS406の後、または、データ45Mからエラーが検出されなかった場合(ステップS402においてNo)、メモリコントローラ3は、データ45Mをホストシステム1に出力する(ステップS407)。

【0062】

次に、メモリコントローラ3は、アクセス対象のメモリの切り替え条件が満たされているか否かを確認する。これは、メインメモリ4に格納されているデータのエラー訂正が不可能となる前にアクセス対象のメモリを切り替えることにより、データの信頼性を確保するためである。

【0063】

具体的には、メモリコントローラ3は、読み出し要求に基づいて読み出されたデータ45Mのエラービット数が切替基準値を超えているか否かを確認する(ステップS408)。複数のページからデータ45Mがそれぞれ読み出された場合、メモリコントローラ3は、エラービットが最も多いデータ45Mのエラービット数が、切替基準値を超えているか否かを確認する。切替基準値は、1ページあたりのビット数として設定される。データ45Mのエラービット数が切替基準値以上である場合(ステップS408においてYes)、メモリコントローラ3は、サブメモリ6の全ブロックの検査が終了したか否かを確認する(ステップS409)。動作指示部34は、メモリコントローラ5に対して、サブメモリ6の検査状況を問い合わせる。メモリコントローラ3は、サブメモリ6の全ブロックの検査終了を示す応答が入力された場合、サブメモリ6の検査が終了したと判定する。なお、メモリコントローラ5が、サブメモリ6の全ブロックの検査を終了していた場合、検査終了を通知するようにしてもよい。

【0064】

サブメモリ6の検査が終了していた場合(ステップS409においてYes)、メモリコントローラ3は、切り替え条件が満たされたと判断し、アクセス対象のメモリを切り替える(ステップS410)。具体的には、メモリコントローラ3は、アクセス対象のメモリを、メモリ6に変更する。ステップS410は、図3に示すステップS8に対応する。ステップS410の詳細は、後述する。

【0065】

ステップS408の説明に戻る。データ45Mのエラービット数が切替基準値よりも小さい場合(ステップS408においてNo)、メモリコントローラ3は、読み出し対象のメモリを切り替えることなく、図4に示す処理を終了する。同様に、サブメモリ6の検査が終了していない場合(ステップS409においてNo)、メモリコントローラ3は、読み出し対象のメモリを切り替えることなく、図4に示す処理を終了する。

【0066】

{4.2.代替データ取得処理(ステップS411)}

図6は、代替データ取得処理(ステップS411、図4参照)の流れを示すフローチャートである。上述したように、メモリコントローラ3は、メインメモリ4から読み出したデータ45Mのエラーを訂正できない場合(ステップS403においてNo)、サブメモリ6からデータ45Sを取得する。データ45M,45Sは、メインメモリ4、サブメモリ6において、同一の論理アドレスを有するページに格納されたデータである。

【0067】

メモリコントローラ3は、メモリコントローラ5に対して、サブメモリ6からのデータの読み出しを要求する(ステップS451)。具体的には、メモリコントローラ3は、エラー訂正できないデータ45Mが格納されたエラーページの論理アドレスを出力する。

【0068】

メモリコントローラ5は、メモリコントローラ3から入力した論理アドレスに基づいて、サブメモリ6からデータ45Sを読み出し、読み出したデータ45Sを出力する。データの読み出し要求を受け付けたときのメモリコントローラ5の動作の詳細は、後述する。メモリコントローラ3は、データ45Sがメモリコントローラ5から入力された場合(ステップS452においてYes)、データ45Mに代わる代替データとして、データ45Sをホストシステム1へ出力する(ステップS453)。このとき、アクセス制御部32は、データ45Sをメインメモリ4に書き戻さない。メインメモリ4のエラーは、メインメモリ4がサブメモリに切り替わった後に訂正される。

【0069】

図7は、ステップS451(図6参照)の読み出し要求を受け付けたときのメモリコントローラ5の動作を示すフローチャートである。

【0070】

メモリコントローラ5は、サブメモリ6から、データの読み出し要求をメモリコントローラ3から受け付けた場合(ステップS551においてYes)、エラーページの論理アドレスに基づいて、サブメモリ6からデータ45Sを読み出す(ステップS552)。すなわち、メモリコントローラ5は、メモリコントローラ3の要求に応じて、書き込み時にエラーページに格納されたデータと同一のデータを、サブメモリ6から読み出す。

【0071】

ECC回路51が、読み出したデータ45Sに対してエラー検出処理を行う(ステップS553)。データ45Sからエラーが検出されなかった場合(ステップS553においてNo)、メモリコントローラ5は、データ45Sをメモリコントローラ3へ出力する(ステップS556)。

【0072】

データ45Sからエラーが検出された場合(ステップS553においてYes)、ECC回路51は、検出されたエラーの訂正が可能であるか否かを確認する(ステップS554)。具体的には、ECC回路51のエラー訂正能力に基づいて、データ45Sのエラーの訂正が可能であるか否かが判断される。

【0073】

エラーの訂正が可能である場合(ステップS554においてYes)、ECC回路51は、読み出したデータ45Sのエラーを訂正する(ステップS555)。メモリコントローラ5は、訂正されたデータ45をメモリコントローラ3へ出力する(ステップS556。)

【0074】

データ45Sのエラーを訂正できない場合(ステップS554においてNo)、メモリコントローラ5は、メモリシステム2が故障したと判定する(ステップS557)。メインメモリ4から読み出されたデータ45M、及びサブメモリ6から読み出されたデータ45Sのエラーを訂正できないため、メモリシステム2は、ホストシステム1のデータ読み出し要求に応答することができない。メモリコントローラ5は、データ45Sのエラーを訂正できない旨をメモリコントローラ3に通知する。メモリコントローラ3は、データを出力することができないエラーメッセージをホストシステム1へ出力する。

【0075】

このように、サブメモリ6からのデータの読み出しは、ホストシステム1が読み出し要求を入力するたびに実行されない。サブメモリ6の読み出し負荷を軽減することができるため、サブメモリ6におけるリードディスターブの発生を抑制し、サブメモリ6に格納されたデータの信頼性を確保することができる。

【0076】

{5.サブメモリ6の検査}

以下、サブメモリ6を検査するときのメモリコントローラ5の動作について説明する。メモリコントローラ5は、メモリコントローラ3がホストシステム1からの読み出し要求に応答するのと並行して、サブメモリ6の各ブロックを検査する。これにより、バックアップ用のサブメモリ6に格納されたデータの信頼性を向上させる。

【0077】

図8は、検査管理テーブル54を示す図である。メモリコントローラ5は、検査管理テーブル54を参照しながら、サブメモリ6の各ページを検査する。

【0078】

図8に示すように、検査管理テーブル54は、サブメモリ6の各ブロックの論理アドレスと、検査状況と、エラービット数とを対応付けて記録する。検査状況には、「0」、「1」、「2」のいずれかの数値が設定される。「0」は、未検査のブロックであることを示す。「1」は、未検査のブロックであり、かつ、優先的に検査する必要がある優先検査ブロックであることを示す。「2」は、検査が既に終了したブロックであることを示す。

【0079】

エラービット数は、サブメモリ6の各ブロックで検出されたエラービット数ではない。検査管理テーブル54のエラービット数は、メインメモリ4の各ブロックにおいて、最も多くのエラービットを有するエラーページのエラービット数である。たとえば、メインメモリ4のブロック7Bに含まれるページのうち、ページ7Pのエラービット数「6」が最大である場合を考える。この場合、検査管理テーブル54において、ブロック7Bに対応するエラービット数として、「6」が記録される。

【0080】

図9は、サブメモリ6を検査するメモリコントローラ5の動作を示すフローチャートである。以下、図8及び図9を参照しながら、サブメモリ6の各ブロックの検査について詳しく説明する。

【0081】

メモリコントローラ5は、エラー記録データ33がメモリコントローラ3から入力された場合(ステップS501においてYes)、検査管理テーブル54を更新し、優先検査ブロックを設定する(ステップS502)。たとえば、メモリコントローラ3が、ブロック8B(図2参照)の論理アドレス「0x0514」と、エラービット数「9」とが記録されたエラー記録データ33をメモリコントローラ5へ出力した場合を考える。この場合、図8に示すように、検査管理テーブル54において、ブロック8Bのエラービット数が、「9」に更新される。ブロック8Bのエラービット数が既に記録されている場合、ブロック8Bのエラービット数は、エラー記録データ33に基づいて上書きされる。

【0082】

メモリコントローラ5は、検査管理テーブル54に記録されたブロック8Bのエラービット数と、優先検査基準値とに基づいて、ブロック8Bを優先検査ブロックに設定するか否かを判定する。優先検査基準値は、サブメモリ6の未検査のブロックの中で、優先検査ブロックとして設定するか否かを判定するためのしきい値であり、1ページあたりのエラービット数として設定される。これは、検査管理テーブル54のエラービット数が、ブロックの中でエラービットが最も多く発生しているページのエラービット数を示しているためである。

【0083】

検査管理テーブル54のブロック8Bにおいて、検査状況が「0」(未検査)に設定され、かつ、エラービット数が優先検査基準値を超えている場合、メモリコントローラ5は、ブロック8Bの検査状況を「1」に変更する。つまり、サブメモリ6のブロック8Bが、優先検査ブロックページに設定される。

【0084】

検査管理テーブル54のブロック8Bにおいて、検査状況が「0」(未検査)に設定され、かつ、エラービット数が優先検査基準値を超えていない場合、メモリコントローラ5は、ブロック8Bの検査状況を「0」のまま変更しない。これは、メインメモリ4のブロック8Bにおいて、リードディスターブが発生していないため、サブメモリ6のブロック8Bを優先的に検査する必要性が低いと考えられるためである。

【0085】

検査管理テーブル54のブロック8Bの検査状況が「2」(検査済み)に設定されている場合、メモリコントローラ5は、検査状況を「2」のまま変更しない。各ブロックの検査状況が「2」に設定された場合、検査状況が「0」または「1」に変更されることはない。これは、サブメモリ6のブロック8Bが既に検査されているため、サブメモリ6のブロック8Bに格納されたデータの信頼性が確保されているためである。この結果、検査済みのブロックのデータが繰り返し読み出されることを防止できる。

【0086】

再び、図9を参照する。検査領域決定部53は、検査管理テーブル54を参照して、検査対象のブロックを決定する(ステップS503〜S505)。優先検査ブロックが検査管理テーブル54に設定されている場合(ステップS503においてYes)、検査領域決定部53は、優先検査ブロックを検査対象として決定する(ステップS504)。複数の優先検査ブロックが検査管理テーブル54に設定されている場合、検査対象は、エラービット数の大きい順に決定されればよい。

【0087】

優先検査ブロックが検査管理テーブル54に設定されていない場合(ステップS503においてNo)、検査領域決定部53は、未検査のブロックの中から検査対象を決定する(ステップS505)。検査対象は、たとえば、論理アドレスの順に設定される。

【0088】

アクセス制御部52は、サブメモリ6の検査対象のブロックから、データ45Cを読み出す(ステップS506)。データ45Cは、検査用に読み出された、1ブロック分のデータである。データ45Cが検査対象のブロックにエラーなく記録されているか否かを確認するために、ECC回路51は、データ45Cに対するエラー検出処理を行う(ステップS507)。

【0089】

データ45Cからエラーが検出されなかった場合(ステップS507においてNo)、メモリコントローラ5は、検査対象のブロックの検査状況を、検査済みを示す「2」に変更する(ステップS511)。

【0090】

一方、データ45Cからエラーが検出された場合(ステップS507においてYes)、ECC回路51は、ステップS403(図4参照)と同様に、検出されたエラーの訂正が可能であるか否かを確認する(ステップS508)。

【0091】

検出されたエラーの訂正が不可能な場合(ステップS508においてNo)、メモリコントローラ3は、データ復旧処理を実行する(ステップS513)。データ復旧処理は、メインメモリ4に格納されたデータを、検査対象のブロックに書き戻す処理である。データ復旧処理の詳細は後述する。

【0092】

検出されたエラーの訂正が可能な場合(ステップS508においてYes)、ECC回路51は、データ45Cのエラーを訂正する(ステップS509)。アクセス制御部52は、訂正されたデータ45Cを検査対象のブロックに書き戻す(ステップS510)。

【0093】

なお、検査領域決定部53は、ページ単位でサブメモリ6を検査してもよい。この場合、検査対象のデータ45Cは、1ページ分のデータとなる。サブメモリ6がページ単位で検査される場合、訂正されたデータ45Cが書き戻されるタイミングは、エラー訂正直後でなくてもよい。これは、サブメモリ6に対するデータの書き戻しが、ブロック単位で行われるためである。たとえば、検査対象がページ8Pであり、かつ、ページ8Pのデータ45Cにエラーが検出された場合、アクセス制御部52は、ブロック7B(図2参照)に属する全てのページの検査が終了した後に、訂正されたデータ45Cをページ8Pに書き戻せばよい。この場合、訂正されたデータ45Cは、メモリコントローラ3により保持される。これにより、ページ8Pだけでなく、ブロック7Bに属する他のページで発生したエラーもリフレッシュすることができる。

【0094】

また、NANDフラッシュメモリの場合、データの書き込み時にエラービットが発生する可能性がある。このため、データ45Cのエラービット数が所定のしきい値よりも小さい場合、メモリコントローラ5は、サブメモリ6に対する負荷を軽減するために、データ45Cのエラー訂正及び再書き込みを実行しなくてもよい。

【0095】

訂正されたデータ45Cがサブメモリ6に書き戻された後に(ステップS510)、検査管理テーブル54が更新される(ステップS511)。具体的には、検査管理テーブル54において、検査対象のブロックの検査状況が、「2」に変更される。

【0096】

メモリコントローラ5は、サブメモリ6の全ブロックの検査が終了したか否かを確認する(ステップS512)。サブメモリ6の全ブロックの検査が終了した場合(ステップS512においてYes)、メモリコントローラ5は、図9の処理を終了する。サブメモリ6の全ブロックの検査が終了していない場合(ステップS512においてNo)、メモリコントローラ5は、未検査のブロックを検査するために、ステップS501に戻る。

【0097】

{6.データ復旧処理(ステップS513)}

図10は、データ復旧処理(ステップS513、図9参照)の流れを示すフローチャートである。上述したように、メモリコントローラ5は、検査対象のブロックから読み出したデータ45Cのエラーを訂正できない場合、メインメモリ4から書き戻し用のデータを取得する。

【0098】

メモリコントローラ5は、メモリコントローラ3に対して、データの読み出しを要求する(ステップS561)。具体的には、メモリコントローラ5は、検査対象のブロックの論理アドレスを出力する。メモリコントローラ3は、入力された論理アドレスに基づいて、検査対象のブロックに書き込まれたデータと同一のデータを、メインメモリ4から読み出し、読み出したデータをメモリコントローラ5へ出力する。このとき、メモリコントローラ3は、1ブロック分のデータを読み出す点を除き、図7に示す処理と同様の処理を実行する。

【0099】

メモリコントローラ3は、図7に示す処理を実行する際に、読み出したデータのエラー検出を行い(ステップS553)、エラー訂正が可能であるか否かを判定する(ステップS554)。読み出したデータから検出されたエラーの訂正ができない場合(ステップS554においてNo)、メモリコントローラ3は、メモリシステム2が故障したと判定する(ステップS557)。この場合、メモリコントローラ3は、検査対象のブロックに含まれるページの読み出し要求をホストシステム1から受け付けた際に、エラーメッセージをホストシステム1へ出力する。

【0100】

再び、図10を参照する。メモリコントローラ5は、読み出しデータがメモリコントローラ3から入力された場合(ステップS562においてYes)、入力されたデータを検査対象のブロックに書き戻す(ステップS563)。これにより、サブメモリ6においてエラー訂正できないデータ45Cが存在しても、サブメモリ6に記録されたデータ45Cを復旧することができる。

【0101】

{7.メモリ切替処理(ステップS410)}

以下、メモリコントローラ3が、アクセス対象をメモリ4からメモリ6へ切り替える処理(ステップS410、図4参照)について説明する。メモリコントローラ3は、読み出したデータ45Mのエラービット数が切替基準値よりも大きく(ステップS408においてYes)、かつ、サブメモリ6の検査が終了した場合(ステップS409においてYes)、アクセス対象のメモリを切り替える(ステップS410)。

【0102】

図11は、読み出し対象のメモリを切り替えるときのメモリコントローラ3の動作を示すフローチャートである。動作指示部34が、メモリコントローラ5に対して、アクセス対象のメモリをメモリ4からメモリ6へ切り替えることを指示する(ステップS461)。

【0103】

メモリコントローラ5は、アクセス対象の切り替え指示が入力された場合、検査管理テーブル54を初期化する。すなわち、検査管理テーブル54において、全ブロックの検査状況が「0」に設定され、エラービット数が消去される。メモリコントローラ5は、アクセス対象のメモリを、メモリ6からメモリ4へ切り替える。その後、メモリコントローラ5は、アクセス対象の切り替えが完了したことをメモリコントローラ3へ通知する。

【0104】

メモリコントローラ3は、切替完了の通知を受け付けた場合(ステップS462においてYes)、エラー記録データ33を消去する(ステップS463)。エラー記録データ33には、メインメモリ4におけるエラーページの情報が記録されているためである。メモリコントローラ3は、アクセス対象をメモリ4からメモリ6に切り替える(ステップS464)。これにより、アクセス対象の切り替え処理(ステップS410)が完了する。

【0105】

以後、メモリ6がメインメモリとして使用され、メモリ4がサブメモリとして使用される。そして、メモリの切り替え条件が満たされた場合、メモリコントローラ3は、再び、アクセス対象のメモリを切り替える。本実施の形態において、読み出し用のメインメモリと、バックアップ用のサブメモリとが切り替わることによって、メインメモリとして使用されるメモリの読み出し負荷が軽減される。また、メモリ4でリードディスターブが発生した場合であっても、メモリ4がサブメモリに切り替えられた後に、メモリ4のエラーを復旧することができる。したがって、メモリ4,6に格納されるデータの信頼性を確保することができる。

【0106】

{8.変形例}

上記実施の形態において、メモリコントローラ3は、アクセス対象のメモリの切り替え条件の一つとして、読み出したデータ45Mのエラービット数が切替基準値よりも大きいか否かを判定した(ステップS408)。しかし、メモリの切り替え条件は、これに限られない。

【0107】

図12は、メモリコントローラ3の変形例に係る機能ブロック図である。図12において、メモリコントローラ3は、リードカウンタ35を備える。リードカウンタ35は、メインメモリ4からのデータの読み出し回数をカウントする。読み出し回数は、メモリコントローラ3が各ページからデータを読み出すたびにカウントされる。メモリコントローラ3は、ステップS408の処理に代えて、リードカウンタ35のカウント数が読み出し上限値を超えているか否かを判定する。この場合、読み出し上限値は、リードディスターブが発生すると想定される読み出し回数よりも小さく設定されることが望ましい。これにより、メモリコントローラ3は、リードディスターブが実際に発生する前に、アクセス対象のメモリを切り替えることができるため、データの信頼性を確保することができる。

【0108】

また、リードカウンタ35は、メインメモリ4のページごとの読み出し回数をカウントしてもよい。この場合、メモリコントローラ3は、エラー記録データ33をメモリコントローラ5に出力しなくてもよい(ステップS406、図4参照)。メモリコントローラ3は、ステップS406に代えて、読み出し回数が所定の読み出し基準値を超えたページが発生した場合、そのページを有するブロックの論理アドレスをメモリコントローラ5へ通知する。たとえば、ページ7P(図2参照)の読み出し回数が所定の読み出し基準値を超えた場合、動作指示部34は、ブロック7Bの論理アドレスをメモリコントローラ5に出力する。メモリコントローラ5は、検査管理テーブル54において、ブロック7Bの検査状況を、優先検査を示す「1」に設定すればよい。

【0109】

上記実施の形態において、メモリコントローラ3,5が、メモリシステム2に搭載される構成を説明した。しかし、ホストシステム1が、メモリコントローラ3,5を備える構成であってもよい。また、ECC回路31,51は、メモリ4,6の内部にそれぞれ設けられてもよい。あるいは、ECC回路31,51は、メモリコントローラ3及びメモリコントローラ5の内部に設けられてもよい。

【0110】

上記実施の形態において、メモリシステム2が、メモリコントローラ3,5を備える構成を説明した。しかし、メモリシステム2において、メモリコントローラ3が、メモリ4,6の両者に対するアクセスを制御してもよい。この場合、メモリコントローラ3は、ホストシステム1の読み出し要求及び書き込み要求を優先的に処理する。メモリコントローラ3は、ホストシステム1からの要求がないときに、サブメモリ6の検査を行えばよい。

【0111】

本実施の形態において、メモリ4,6が同一の論理アドレス空間を有する例について説明した。しかし、メモリ4,6は、互いに異なる論理アドレス空間を有していてもよい。この場合、メモリコントローラ3,5のいずれかが、メモリ4の論理アドレスと、メモリ6の論理アドレスとの対応関係を示すアドレステーブルを保持すればよい。

【符号の説明】

【0112】

1 ホストシステム

2 メモリシステム

3,5 メモリコントローラ

4 メモリ(メインメモリ)

6 メモリ(サブメモリ)

31,51 ECC回路

32,52 アクセス制御部

33 エラー記録データ

34 動作指示部

35 リードカウンタ

53 検査領域決定部

54 検査管理テーブル

【技術分野】

【0001】

本発明は、フラッシュメモリからデータが繰り返し読み出されることにより、データが意図せず書き換えられるリードディスターブ現象に対処する技術に関する。

【背景技術】

【0002】

NANDフラッシュメモリは、再書き込み可能な不揮発性半導体メモリである。NANDフラッシュメモリは、高集積化を実現しながら、低コスト化が図られているため、SDメモリカードなどの形態で広く普及している。

【0003】

NANDフラッシュメモリにおいては、特定のセルが繰り返し読み出されることにより、記憶データが意図せず書き換えられる現象が生じることが分かっている。この現象は、リードディスターブ(Read Disturb)現象と呼ばれている現象であり、NANDフラッシュメモリを利用する上での課題となっている。

【0004】

特定のセルに対する読み出し処理が繰り返し行われた場合であっても、一旦、そのセルを含む領域に対してデータの更新が行われれば、セルの状態が修復されるため、リードディスターブの発生が情報処理に影響を与えることを回避できる。しかし、特定のセルに対して書き込み処理が行われず、読み出し処理だけが繰り返し行われる場合、リードディスターブの発生する可能性が高くなり、情報処理に影響を与える可能性もある。

【0005】

最近では、NANDフラッシュメモリは、情報処理装置のプログラムメモリとしてROMのような役割で利用されるケースが多くなっている。NANDフラッシュメモリがそのように利用された場合、連続的な読み出し処理のみが行われるため、リードディスターブの発生可能性が高くなる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−139503号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記特許文献1には、第1の記録媒体及び第2の記録媒体に同一のデータを書き込む記憶装置が記載されている。第1の記録媒体及び第2の記録媒体は、不揮発性メモリである。第2の記録媒体は、ミラー書き込み用として用いられる。上記特許文献1の記憶装置は、データ読み出し指令が記憶装置に入力された場合、第1の記録媒体及び第2の記録媒体の両者からデータを読み出す。第1の記録媒体から読み出されたデータからエラーを検出した場合、記憶装置は、第2の記録媒体から読み出したデータを出力する。

【0008】

上記特許文献1では、第2の記録媒体からの読み出しが第1の記録媒体からの読み出しと同じ頻度で行われる。このため、リードディスターブが、第1記録媒体だけでなく、第2記録媒体で発生する可能性が高い。第2の記録媒体がミラー書き込み用として用いられるにも関わらず、第2の記録媒体に書き込まれたデータの信頼性を確保することができない。

【0009】

そこで、本発明は前記問題点に鑑み、フラッシュメモリに記録されたデータの信頼性を向上させることができる技術を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記課題を解決するため、請求項1記載の発明は、メモリシステムであって、再書き込み可能な不揮発性メモリである第1メモリと、再書き込み可能な不揮発性メモリであり、前記第1メモリのバックアップ用のメモリとして設定された第2メモリと、前記第1メモリと前記第2メモリとにアクセスするメモリコントローラと、を備え、前記メモリコントローラは、ホストから書き込み要求を受け付けた場合、前記第1メモリ及び前記第2メモリに対して同一のデータを書き込み、前記ホストから読み出し要求を受け付けた場合、前記第1メモリからデータを読み出すアクセス制御部と、前記第2メモリが有するデータ領域のうちいずれかの領域を検査領域として決定する検査領域決定部と、前記検査領域から読み出された検査対象データに対してエラー検出を行い、前記検査対象データからエラーが検出された場合、前記検査対象データのエラーを訂正するエラー訂正部と、を備え、前記アクセス制御部は、訂正された検査対象データを前記検査領域に再書き込みする。

【0011】

請求項2記載の発明は、請求項1に記載のメモリシステムであって、前記検査領域決定部は、前記第1メモリに含まれる第1領域が優先検査条件を満たした場合、前記第2メモリに含まれ、かつ、前記第1領域に格納されたデータと同一のデータを格納する第2領域を、優先的に前記検査領域として決定する。

【0012】

請求項3記載の発明は、請求項1に記載のメモリシステムであって、前記エラー訂正部は、前記検査対象データからエラーを検出した場合、前記検査対象データのエラーを訂正するか否かを判定し、前記アクセス制御部は、エラーを訂正すると判定された場合、前記訂正された検査対象データを前記検査領域に再書き込みする。

【0013】

請求項4記載の発明は、請求項2または請求項3に記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、を備え、前記優先検査条件は、前記第1メモリから読み出されたデータのエラービット数が予め設定された第1優先検査基準値を超えることである。

【0014】

請求項5記載の発明は、請求項2または請求項3に記載のメモリシステムであって、前記メモリコントローラは、前記第1メモリが有するデータ領域ごとに、データが読み出される回数をカウントするカウンタ、を備え、前記優先検査条件は、前記読み出し回数が予め設定された第2優先検査基準値を超えることである。

【0015】

請求項6記載の発明は、請求項2ないし請求項5のいずれかに記載のメモリシステムであって、前記検査領域決定部は、前記第1領域が前記優先検査条件を満たし、かつ、前記第2領域が検査されていない場合、前記第2領域を優先的に前記検査領域として決定する。

【0016】

請求項7記載の発明は、請求項1ないし請求項6のいずれかに記載のメモリシステムであって、前記アクセス制御部は、前記エラー訂正部が前記検査対象データのエラーを訂正できない場合、前記第1メモリに含まれ、かつ、前記検査領域に格納されたデータと同一のデータを格納するデータ領域から復旧データを読み出し、前記復旧データを前記検査領域に再書き込みする。

【0017】

請求項8記載の発明は、請求項1または請求項2に記載のメモリシステムであって、前記アクセス制御部は、所定の切り替え条件が満たされた場合、前記読み出し要求を受け付けたときにデータを読み出すメモリを、前記第1メモリから前記第2メモリに切り替えるとともに、前記第2メモリのバックアップ用のメモリとして前記第1メモリを設定する。

【0018】

請求項9記載の発明は、請求項8に記載のメモリシステムであって、前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記読み出し要求に応じて前記第1メモリから読み出されたデータのエラービット数が予め設定された第1切替基準値を超えることである。

【0019】

請求項10記載の発明は、請求項8に記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリからのデータの読み出し回数をカウントするカウンタ、を備え、前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記第1メモリからのデータの読み出し回数が予め設定された第2切替基準値を超えることである。

【0020】

請求項11記載の発明は、請求項8ないし請求項10のいずれかに記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、を備え、前記切り替え条件は、前記第1メモリから読み出されたデータのエラーを訂正できないことである。

【0021】

請求項12記載の発明は、請求項1ないし請求項11のいずれかに記載のメモリシステムであって、前記メモリコントローラは、さらに、前記第1メモリ及び前記第2メモリのうち、前記読み出し要求に基づいてデータが読み出されるメモリに対するアクセスを制御する第1メモリコントローラと、前記第1メモリ及び前記第2メモリのうち、バックアップ用のメモリに対するアクセスを制御する第2メモリコントローラと、を備える。

【発明の効果】

【0022】

本発明のメモリシステムは、バックアップ用の第2メモリのデータ領域のいずれかを検査領域として決定し、検査領域からデータを読み出す。読み出したデータにエラーがある場合、エラー訂正されたデータが、検査領域に書き戻される。検査領域に格納されたデータと同一のデータを格納する第1メモリのデータ領域でリードディスターブが発生した場合であっても、検査領域に格納されたデータのエラーが訂正されているため、フラッシュメモリに格納されるデータの信頼性を向上させることができる。

【0023】

また、本発明のメモリシステムは、切り替え条件が満たされた場合、第1メモリを読み出し用のメモリからバックアップ用のメモリに変更し、第2メモリをバックアップ用のメモリから読み出し用のメモリに変更する。第1メモリ及び第2メモリが交互に読み出し用のメモリとして使用されるため、第1メモリ及び第2メモリの読み出し負荷を軽減でき、リードディスターブの発生を抑制することができる。

【図面の簡単な説明】

【0024】

【図1】本発明の実施の形態による情報処理システムの構成を示す機能ブロック図である。

【図2】図1に示すメモリの構成を示す図である。

【図3】図1に示すメモリシステムの動作の概略を示す図である。

【図4】図1に示すメインメモリにアクセスするメモリコントローラの動作を示すフローチャートである。

【図5】図1に示すエラー記録データの一例を示す図である。

【図6】図4に示す代替データ取得処理のフローチャートである。

【図7】図1に示すサブメモリにアクセスするメモリコントローラの動作を示すフローチャートである。

【図8】図1に示す検査管理テーブルを示す図である。

【図9】図1に示すサブメモリにアクセスするメモリコントローラの動作を示すフローチャートである。

【図10】図9に示すデータ復旧処理のフローチャートである。

【図11】図4に示すアクセス対象のメモリを切り替える処理のフローチャートである。

【図12】図1に示すメモリコントローラの変形例を示す図である。

【発明を実施するための形態】

【0025】

以下、図面を参照しつつ本発明の実施の形態について説明する。

【0026】

{1.全体構成}

図1は、本実施の形態に係る情報処理システム100の機能ブロック図である。情報処理システム100は、ホストシステム1と、メモリシステム2とを備える。メモリシステム2は、メモリコントローラ3,5と、メモリ4,6と、ECC(Error Checking and Correction)回路31,51とを備える。

【0027】

情報処理システム100は、たとえば、ゲームシステムを構成する。この場合、ホストシステム1は、ゲーム装置本体を構成し、メモリシステム2は、ゲーム装置本体に対して着脱可能なゲームカートリッジを構成する。なお、メモリシステム2は、ゲーム装置本体に内蔵されてもよい。

【0028】

メモリ4,6は、再書き込み可能な不揮発性半導体メモリである。本実施の形態において、メモリ4,6は、NANDフラッシュメモリである。ここで、メモリ4は、読み出し用のメモリ(メインメモリ)である。メインメモリは、読み出し要求がホストシステム1から入力された際に、データの読み出し対象となるメモリである。メモリ6は、バックアップ用のメモリ(サブメモリ)である。メモリ4,6は、後述する切り替え条件が満たされた場合、機能が切り替わる。すなわち、メモリ4は、メインメモリからサブメモリへ切り替わり、メモリ6は、サブメモリからメインメモリへ切り替わる。

【0029】

メモリコントローラ3は、メモリ4,6のうち、メインメモリに設定されたメモリに対するデータの読み出し及び書き込みを制御する。メモリコントローラ5は、メモリ4,6のうち、サブメモリに設定されたメモリに対するデータの読み出し及び書き込みを制御する。すなわち、メモリコントローラ3、5は、切り替え条件に基づいて、アクセス対象のメモリを切り替える。

【0030】

ECC回路31は、メモリコントローラ3がメインメモリから読み出したデータに対するエラー検出処理と、エラー訂正処理とを実行する。ECC回路51は、メモリコントローラ5がサブメモリから読み出したデータに対するエラー検出処理と、エラー訂正処理とを実行する。

【0031】

以下、メモリ4がメインメモリに設定され、メモリ6がサブメモリに設定されていると仮定して、本実施の形態を説明する。メモリ4を、「メインメモリ4」と呼び、メモリ6を、「サブメモリ6」と呼ぶ。

【0032】

メモリコントローラ3は、ホストシステム1からの各種要求を受け付けるとともに、メインメモリ4に対するアクセスを制御する。メモリコントローラ3は、ホストシステム1からデータの書き込み要求を受け付けた場合、メモリコントローラ5に対して、データの書き込みを指示する。メモリコントローラ3は、アクセス制御部32と、動作指示部34とを備える。

【0033】

アクセス制御部32は、ホストシステム1の要求に応じて、メインメモリ4からデータを読み出し、メインメモリ4にデータを書き込む。メインメモリ4から読み出されたデータを、データ45Mと呼ぶ。データ45Mは、1ページ分のデータである。

【0034】

動作指示部34は、メモリコントローラ5に対して各種動作の実行を指示する。たとえば、動作指示部34は、ホストシステム1からデータの書き込み要求を受け付けた場合、データの書き込みをメモリコントローラ5に指示する。動作指示部34は、切り替え条件が満たされた場合、アクセス対象の変更をメモリコントローラ5に指示する。

【0035】

メモリコントローラ3は、エラー記録データ33を保持する。エラー記録データ33は、読み出し対象のページを有するブロックの論理アドレスと、読み出されたデータ45Mのエラービット数とが記録されたデータである。具体的には、ECC回路31が、メインメモリ4から読み出されたデータ45Mに対してエラー検出処理を行う。メモリコントローラ3は、エラー記録データ33として、データ45Mが格納されたページを含むブロックの論理アドレスと、検出されたエラービット数とを対応付けて記録する。エラー記録データ33の詳細は、後述する。

【0036】

メモリコントローラ5は、サブメモリ6に格納されたデータにエラーが発生しているか否かを、ブロックごとに検査する。メモリコントローラ5は、動作指示部34から指示を受け付けた場合を除き、メモリコントローラ3とは独立に動作する。メモリコントローラ5は、アクセス制御部52と、検査領域決定部53とを備える。

【0037】

アクセス制御部52は、サブメモリ6からデータを読み出し、サブメモリ6にデータを書き込む。検査領域決定部53は、サブメモリ6が有するブロックの中から検査対象のブロックを決定する。通常であれば、検査領域決定部53は、予め設定された順序に基づいて、サブメモリ6の各ブロックを検査対象として決定する。しかし、サブメモリ6の中で優先検査ブロックに設定されたブロックが存在する場合、検査領域決定部53は、設定された順序に関係なく、検査対象として優先検査ブロックを決定する。

【0038】

メモリコントローラ5は、検査管理テーブル54を保持する。検査管理テーブル54は、サブメモリ6の各ブロックの検査状況を記録したテーブルである。サブメモリ6の各ブロックの検査の詳細については、後述する。

【0039】

{2.メインメモリ4及びサブメモリ6の構成}

図2は、メインメモリ4及びサブメモリ6の構成を示す図である。具体的には、メインメモリ4及びサブメモリ6は、同一の構成を有し、それぞれ1枚のダイで構成される。ダイは、複数のバンクを含む。図2に示す例では、ダイは、J個のバンクを含む。バンクは、複数のブロックを含む。図2に示す例では、バンクは、M個のブロックを含む。ブロックは、複数のページを含む。図2に示す例では、ブロックは、Z個のページを含む。

【0040】

ページは、メインメモリ4及びサブメモリ6におけるデータの読み出し単位及び書き込み単位である。メモリコントローラ3は、メインメモリ4に記録されているデータをページ単位で読み出し、書き込みが指示されたデータをページ単位でメインメモリ4に書き込むことができる。同様に、メモリコントローラ5は、サブメモリ6に記録されているデータをページ単位で読み出し、書き込みが指示されたデータをページ単位でサブメモリ6に書き込むことができる。

【0041】

メインメモリ4及びサブメモリ6は、同一の論理アドレス空間を有する。メモリコントローラ3,5は、メインメモリ4及びサブメモリ6にそれぞれデータを書き込む場合、同一の論理アドレスを有するページにデータを書き込む。たとえば、メモリコントローラ3がメインメモリ4のページ7Pにデータを書き込む場合、メモリコントローラ5は、同様に、サブメモリ6のページ7Pに同一のデータを書き込む。図2に示すように、メインメモリ4のページ7Pと、サブメモリ6のページ7Pとは、両者ともに、ブロック7B(BANK#0)に含まれる先頭ページ(Page#0)であることがわかる。

【0042】

ブロックは、メインメモリ4及びサブメモリ6におけるデータの消去単位である。メモリコントローラ3,5は、メインメモリ4及びサブメモリ6に格納されたデータをブロック単位で消去することができる。

【0043】

{3.動作概略}

以下、図3を用いて、メモリシステム2の動作の概略を説明する。図3は、メモリシステム2の動作の概略を示す図である。図3において、ホストシステム1、メモリコントローラ3,5、メインメモリ4及びサブメモリ6以外の構成の表示を省略している。

【0044】

{3.1.データ書き込み}

ホストシステム1が、データの書き込み要求をメモリシステム2へ出力する(ステップS1)。メモリコントローラ3が、書き込み要求に基づいて、データを書き込む対象となるページ(書き込みページ)を決定する。メモリコントローラ3は、メインメモリ4の書き込みページにデータを書き込む(ステップS2)。また、メモリコントローラ3は、書き込み指示として、データと、書き込みページの論理アドレスとをメモリコントローラ5に通知する(ステップS3)。メモリコントローラ5は、書き込み指示に基づいて、サブメモリ6の書き込みページにデータを書き込む(ステップS4)。これにより、メインメモリ4及びサブメモリ6の同一アドレスには、同一のデータが書き込まれる。

【0045】

{3.2.データ読み出し}

ホストシステム1が、データの読み出し要求をメモリシステム2へ出力する(ステップS5)。メモリコントローラ3は、読み出し要求に基づいて、メインメモリ4からデータ45Mを読み出し、データ45Mをホストシステム1へ出力する(ステップS6)。ECC回路31は、メインメモリ4から読み出されたデータ45Mに対してエラー検出処理を行う。エラーが検出された場合、エラー訂正されたデータ45Mが、ホストシステム1に出力される。

【0046】

メモリコントローラ5は、原則として、ホストシステム1の読み出し要求に応じて、サブメモリ6からデータを読み出さない。しかし、ECC回路31がデータ45Mのエラーを訂正できない場合、メモリコントローラ5は、メモリコントローラ3の指示に応じて、サブメモリ6からデータ45Sを読み出す。メモリコントローラ3は、データ45Mに代えて、データ45Sをホストシステム1へ出力する。この結果、サブメモリ6に対するデータの読み出し回数が減少するため、サブメモリ6におけるリードディスターブの発生が抑制される。

【0047】

{3.3.サブメモリ6の検査}

メモリコントローラ5は、サブメモリ6に格納されたデータの信頼性を向上させるために、サブメモリ6に格納されたデータを検査する。サブメモリ6の検査は、メインメモリ4が読み出し用のメモリとして用いられている間に実行される。

【0048】

具体的には、メモリコントローラ5は、サブメモリ6の検査対象のブロックからデータ45Cを読み出す(ステップS7)。データ45Cは、検査用に読み出されたデータであり、1ブロック分のデータである。データ45Cからエラーが検出された場合、メモリコントローラ5は、エラー訂正されたデータ45Cを、検査対象のブロックに書き戻す。

【0049】

メモリコントローラ5は、通常であれば、予め設定された順序で、サブメモリ6の各ブロックを検査する。しかし、リードディスターブなどにより、メインメモリ4においてビットエラーを有するページ(エラーページ)が発生することがある。この場合、メモリコントローラ3は、エラーページを有するブロック(エラーブロック)を特定する。メモリコントローラ5は、エラーブロックに格納されたデータと同一のデータを格納するサブメモリ6のブロックを優先的に検査する。たとえば、メインメモリ4のブロック7Bと、サブメモリ6のブロック7Bとには、同一のデータが書き込まれている。メインメモリ4のページ7Pから読み出されたデータにエラーが検出された場合、メモリコントローラ5は、サブメモリ6のブロックのうち、ページ7Pを有するブロック7Bを優先的に検査する。これにより、サブメモリ6に格納されるデータのうち、エラーブロックに書き込まれたデータと同一のデータの信頼性を向上させることができる。

【0050】

{3.4.メモリの切り替え}

メモリコントローラ3は、切り替え条件が満たされた場合、アクセス対象のメモリを切り替える(ステップS8)。切り替え条件は、サブメモリ6の全てのブロックの検査が終了し、かつ、ホストシステム1の読み出し要求に基づいて、メインメモリ4から読み出されたデータ45Mのエラービット数が所定のしきい値を超えた場合である。以後、メモリコントローラ3は、ホストシステム1から読み出し要求を受け付けた場合、メモリ6からデータを読み出す。メモリコントローラ5は、メモリ4の各ページの検査を開始する。

【0051】

このように、メモリ4,6が、交互にメインメモリとして使用されるため、メモリ4,6の読み出し負荷を分散させることができる。したがって、メモリ4,6におけるリードディスターブの発生を抑制することができる。また、メモリ4,6の各ページは、メモリ4,6がサブメモリとして用いられる間に、メモリコントローラ5により検査される。このため、メモリ4,6に格納されるデータの信頼性を維持することができる。

【0052】

{4.メモリコントローラ3の動作}

以下、メモリコントローラ3の動作について、図1及び図4を参照しながら説明する。

【0053】

{4.1.読み出し処理}

図4は、読み出し要求(ステップS5、図3参照)を受け付けたときのメモリコントローラ3の動作を示すフローチャートである。メモリコントローラ3は、ホストシステム1の読み出し要求に応じてメインメモリ4からデータ45Mを読み出す。データ45Mのエラーを訂正できない場合、メモリコントローラ3は、データ45Mに代えて、サブメモリ6から読み出されたデータ45Sをホストシステム1へ出力する。

【0054】

メモリコントローラ3は、ホストシステム1から読み出し要求(ステップS5)を受け付けた場合、図4の処理を開始する。アクセス制御部32が、読み出し要求に基づいて読み出し対象ページを決定し、メインメモリ4の読み出し対象ページからデータ45Mを読み出す(ステップS401)。ECC回路31は、読み出したデータ45Mに対してエラー検出処理を行う(ステップS402)。データ45Mからエラーが検出されなかった場合(ステップS402においてNo)、メモリコントローラ3は、データ45Mをホストシステム1へ出力する(ステップS407)。読み出し対象ページが複数である場合、ECC回路31は、各ページから読み出されたデータ45Mに対してエラー検出処理を行う。

【0055】

データ45Mからエラーが検出された場合(ステップS402においてYes)、ECC回路31は、検出されたエラーの訂正が可能であるか否かを確認する(ステップS403)。具体的には、ECC回路31のエラー訂正能力に基づいて、データ45Mのエラーの訂正が可能であるか否かが判断される。

【0056】

データ45Mのエラーを訂正できない場合(ステップS403においてNo)、メモリコントローラ3は、データ45Mをホストシステム1に出力することができない。このため、メモリコントローラ3は、メモリコントローラ5を介して、サブメモリからデータ45Sを取得する代替データ取得処理を実行する(ステップS411)。データ45M、45Sは、メインメモリ4及びサブメモリ6にそれぞれ書き込まれるときには、同一のデータである。すなわち、代替データ取得処理は、メモリ45Mに代わるデータとして、データ45Mと同一のデータを格納するページからデータ45Sを取得する処理である。代替データ取得処理の後に、メモリコントローラ3は、アクセス対象のメモリを切り替える(ステップS410)。ステップS410,S411の詳細は後述する。

【0057】

データ45Mのエラーの訂正が可能な場合(ステップS403においてYes)、ECC回路31は、データ45Mのエラーを訂正する(ステップS404)。訂正されたデータ45Mは、後述するように、ホストシステム1へ出力されるが(ステップS407)、メインメモリ4へ書き戻されることはない。これは、訂正されたデータ45Mをメインメモリ4に書き戻すことにより、メモリコントローラ3の負荷が大きくなることを防止するためである。データ45Mのエラーは、メインメモリ4がサブメモリに切り替えられた後に、メモリコントローラ5により訂正される。

【0058】

メモリコントローラ3は、エラーページを有するエラーブロックに関する情報を、エラー記録データ33として作成する(ステップS405)。エラーページは、データ45Mからエラーが検出されたページである。エラー記録データ33は、たとえば、メモリコントローラ3が備えるレジスタまたはメインメモリ4に格納される。

【0059】

図5は、エラー記録データ33の一例を示す図である。図5に示すように、エラー記録データ33は、データ45Mを格納するエラーブロックの論理アドレスと、データ45Mのエラービット数とを有する。メモリコントローラ3は、ホストシステム1からの読み出し要求に応じて、複数のページからデータ45Mを読み出すことがある。この場合、メモリコントローラ3は、複数のページの中から、エラービット数が最大のエラーページを特定する。メモリコントローラ3は、特定されたエラーページを有するブロックの論理アドレスと、特定されたエラーページのエラービット数とを対応付けて、エラー記録データ33に記録する。メモリコントローラ3は、エラー記録データ33をメモリコントローラ5へ出力することにより、エラーブロックの発生を通知する(ステップS406)。詳細は後述するが、メモリコントローラ5は、サブメモリ6のブロックのうち、エラーブロックに格納されたデータと同一のデータを格納するブロックを優先的に検査する。

【0060】

エラー記録データ33は、複数のエラーブロックを記録したデータであってもよい。たとえば、メモリコントローラ3は、10ブロック分のエラーブロックに関する情報を、エラー記録データ33として保持してもよい。この場合、メモリコントローラ3は、10ブロック分のエラーブロックがエラー記録データ33に記録された場合、エラー記録データ33をメモリコントローラ5に出力すればよい。また、エラー記録データ33は、エラーページの論理アドレスと、エラービット数とを対応付けたデータであってもよい。この場合、メモリコントローラ5が、エラーページの論理アドレスに基づいて、エラーブロックのアドレスを特定すればよい。

【0061】

再び、図1及び図4を参照する。ステップS406の後、または、データ45Mからエラーが検出されなかった場合(ステップS402においてNo)、メモリコントローラ3は、データ45Mをホストシステム1に出力する(ステップS407)。

【0062】

次に、メモリコントローラ3は、アクセス対象のメモリの切り替え条件が満たされているか否かを確認する。これは、メインメモリ4に格納されているデータのエラー訂正が不可能となる前にアクセス対象のメモリを切り替えることにより、データの信頼性を確保するためである。

【0063】

具体的には、メモリコントローラ3は、読み出し要求に基づいて読み出されたデータ45Mのエラービット数が切替基準値を超えているか否かを確認する(ステップS408)。複数のページからデータ45Mがそれぞれ読み出された場合、メモリコントローラ3は、エラービットが最も多いデータ45Mのエラービット数が、切替基準値を超えているか否かを確認する。切替基準値は、1ページあたりのビット数として設定される。データ45Mのエラービット数が切替基準値以上である場合(ステップS408においてYes)、メモリコントローラ3は、サブメモリ6の全ブロックの検査が終了したか否かを確認する(ステップS409)。動作指示部34は、メモリコントローラ5に対して、サブメモリ6の検査状況を問い合わせる。メモリコントローラ3は、サブメモリ6の全ブロックの検査終了を示す応答が入力された場合、サブメモリ6の検査が終了したと判定する。なお、メモリコントローラ5が、サブメモリ6の全ブロックの検査を終了していた場合、検査終了を通知するようにしてもよい。

【0064】

サブメモリ6の検査が終了していた場合(ステップS409においてYes)、メモリコントローラ3は、切り替え条件が満たされたと判断し、アクセス対象のメモリを切り替える(ステップS410)。具体的には、メモリコントローラ3は、アクセス対象のメモリを、メモリ6に変更する。ステップS410は、図3に示すステップS8に対応する。ステップS410の詳細は、後述する。

【0065】

ステップS408の説明に戻る。データ45Mのエラービット数が切替基準値よりも小さい場合(ステップS408においてNo)、メモリコントローラ3は、読み出し対象のメモリを切り替えることなく、図4に示す処理を終了する。同様に、サブメモリ6の検査が終了していない場合(ステップS409においてNo)、メモリコントローラ3は、読み出し対象のメモリを切り替えることなく、図4に示す処理を終了する。

【0066】

{4.2.代替データ取得処理(ステップS411)}

図6は、代替データ取得処理(ステップS411、図4参照)の流れを示すフローチャートである。上述したように、メモリコントローラ3は、メインメモリ4から読み出したデータ45Mのエラーを訂正できない場合(ステップS403においてNo)、サブメモリ6からデータ45Sを取得する。データ45M,45Sは、メインメモリ4、サブメモリ6において、同一の論理アドレスを有するページに格納されたデータである。

【0067】

メモリコントローラ3は、メモリコントローラ5に対して、サブメモリ6からのデータの読み出しを要求する(ステップS451)。具体的には、メモリコントローラ3は、エラー訂正できないデータ45Mが格納されたエラーページの論理アドレスを出力する。

【0068】

メモリコントローラ5は、メモリコントローラ3から入力した論理アドレスに基づいて、サブメモリ6からデータ45Sを読み出し、読み出したデータ45Sを出力する。データの読み出し要求を受け付けたときのメモリコントローラ5の動作の詳細は、後述する。メモリコントローラ3は、データ45Sがメモリコントローラ5から入力された場合(ステップS452においてYes)、データ45Mに代わる代替データとして、データ45Sをホストシステム1へ出力する(ステップS453)。このとき、アクセス制御部32は、データ45Sをメインメモリ4に書き戻さない。メインメモリ4のエラーは、メインメモリ4がサブメモリに切り替わった後に訂正される。

【0069】

図7は、ステップS451(図6参照)の読み出し要求を受け付けたときのメモリコントローラ5の動作を示すフローチャートである。

【0070】

メモリコントローラ5は、サブメモリ6から、データの読み出し要求をメモリコントローラ3から受け付けた場合(ステップS551においてYes)、エラーページの論理アドレスに基づいて、サブメモリ6からデータ45Sを読み出す(ステップS552)。すなわち、メモリコントローラ5は、メモリコントローラ3の要求に応じて、書き込み時にエラーページに格納されたデータと同一のデータを、サブメモリ6から読み出す。

【0071】

ECC回路51が、読み出したデータ45Sに対してエラー検出処理を行う(ステップS553)。データ45Sからエラーが検出されなかった場合(ステップS553においてNo)、メモリコントローラ5は、データ45Sをメモリコントローラ3へ出力する(ステップS556)。

【0072】

データ45Sからエラーが検出された場合(ステップS553においてYes)、ECC回路51は、検出されたエラーの訂正が可能であるか否かを確認する(ステップS554)。具体的には、ECC回路51のエラー訂正能力に基づいて、データ45Sのエラーの訂正が可能であるか否かが判断される。

【0073】

エラーの訂正が可能である場合(ステップS554においてYes)、ECC回路51は、読み出したデータ45Sのエラーを訂正する(ステップS555)。メモリコントローラ5は、訂正されたデータ45をメモリコントローラ3へ出力する(ステップS556。)

【0074】

データ45Sのエラーを訂正できない場合(ステップS554においてNo)、メモリコントローラ5は、メモリシステム2が故障したと判定する(ステップS557)。メインメモリ4から読み出されたデータ45M、及びサブメモリ6から読み出されたデータ45Sのエラーを訂正できないため、メモリシステム2は、ホストシステム1のデータ読み出し要求に応答することができない。メモリコントローラ5は、データ45Sのエラーを訂正できない旨をメモリコントローラ3に通知する。メモリコントローラ3は、データを出力することができないエラーメッセージをホストシステム1へ出力する。

【0075】

このように、サブメモリ6からのデータの読み出しは、ホストシステム1が読み出し要求を入力するたびに実行されない。サブメモリ6の読み出し負荷を軽減することができるため、サブメモリ6におけるリードディスターブの発生を抑制し、サブメモリ6に格納されたデータの信頼性を確保することができる。

【0076】

{5.サブメモリ6の検査}

以下、サブメモリ6を検査するときのメモリコントローラ5の動作について説明する。メモリコントローラ5は、メモリコントローラ3がホストシステム1からの読み出し要求に応答するのと並行して、サブメモリ6の各ブロックを検査する。これにより、バックアップ用のサブメモリ6に格納されたデータの信頼性を向上させる。

【0077】

図8は、検査管理テーブル54を示す図である。メモリコントローラ5は、検査管理テーブル54を参照しながら、サブメモリ6の各ページを検査する。

【0078】

図8に示すように、検査管理テーブル54は、サブメモリ6の各ブロックの論理アドレスと、検査状況と、エラービット数とを対応付けて記録する。検査状況には、「0」、「1」、「2」のいずれかの数値が設定される。「0」は、未検査のブロックであることを示す。「1」は、未検査のブロックであり、かつ、優先的に検査する必要がある優先検査ブロックであることを示す。「2」は、検査が既に終了したブロックであることを示す。

【0079】

エラービット数は、サブメモリ6の各ブロックで検出されたエラービット数ではない。検査管理テーブル54のエラービット数は、メインメモリ4の各ブロックにおいて、最も多くのエラービットを有するエラーページのエラービット数である。たとえば、メインメモリ4のブロック7Bに含まれるページのうち、ページ7Pのエラービット数「6」が最大である場合を考える。この場合、検査管理テーブル54において、ブロック7Bに対応するエラービット数として、「6」が記録される。

【0080】

図9は、サブメモリ6を検査するメモリコントローラ5の動作を示すフローチャートである。以下、図8及び図9を参照しながら、サブメモリ6の各ブロックの検査について詳しく説明する。

【0081】

メモリコントローラ5は、エラー記録データ33がメモリコントローラ3から入力された場合(ステップS501においてYes)、検査管理テーブル54を更新し、優先検査ブロックを設定する(ステップS502)。たとえば、メモリコントローラ3が、ブロック8B(図2参照)の論理アドレス「0x0514」と、エラービット数「9」とが記録されたエラー記録データ33をメモリコントローラ5へ出力した場合を考える。この場合、図8に示すように、検査管理テーブル54において、ブロック8Bのエラービット数が、「9」に更新される。ブロック8Bのエラービット数が既に記録されている場合、ブロック8Bのエラービット数は、エラー記録データ33に基づいて上書きされる。

【0082】

メモリコントローラ5は、検査管理テーブル54に記録されたブロック8Bのエラービット数と、優先検査基準値とに基づいて、ブロック8Bを優先検査ブロックに設定するか否かを判定する。優先検査基準値は、サブメモリ6の未検査のブロックの中で、優先検査ブロックとして設定するか否かを判定するためのしきい値であり、1ページあたりのエラービット数として設定される。これは、検査管理テーブル54のエラービット数が、ブロックの中でエラービットが最も多く発生しているページのエラービット数を示しているためである。

【0083】

検査管理テーブル54のブロック8Bにおいて、検査状況が「0」(未検査)に設定され、かつ、エラービット数が優先検査基準値を超えている場合、メモリコントローラ5は、ブロック8Bの検査状況を「1」に変更する。つまり、サブメモリ6のブロック8Bが、優先検査ブロックページに設定される。

【0084】

検査管理テーブル54のブロック8Bにおいて、検査状況が「0」(未検査)に設定され、かつ、エラービット数が優先検査基準値を超えていない場合、メモリコントローラ5は、ブロック8Bの検査状況を「0」のまま変更しない。これは、メインメモリ4のブロック8Bにおいて、リードディスターブが発生していないため、サブメモリ6のブロック8Bを優先的に検査する必要性が低いと考えられるためである。

【0085】

検査管理テーブル54のブロック8Bの検査状況が「2」(検査済み)に設定されている場合、メモリコントローラ5は、検査状況を「2」のまま変更しない。各ブロックの検査状況が「2」に設定された場合、検査状況が「0」または「1」に変更されることはない。これは、サブメモリ6のブロック8Bが既に検査されているため、サブメモリ6のブロック8Bに格納されたデータの信頼性が確保されているためである。この結果、検査済みのブロックのデータが繰り返し読み出されることを防止できる。

【0086】

再び、図9を参照する。検査領域決定部53は、検査管理テーブル54を参照して、検査対象のブロックを決定する(ステップS503〜S505)。優先検査ブロックが検査管理テーブル54に設定されている場合(ステップS503においてYes)、検査領域決定部53は、優先検査ブロックを検査対象として決定する(ステップS504)。複数の優先検査ブロックが検査管理テーブル54に設定されている場合、検査対象は、エラービット数の大きい順に決定されればよい。

【0087】

優先検査ブロックが検査管理テーブル54に設定されていない場合(ステップS503においてNo)、検査領域決定部53は、未検査のブロックの中から検査対象を決定する(ステップS505)。検査対象は、たとえば、論理アドレスの順に設定される。

【0088】

アクセス制御部52は、サブメモリ6の検査対象のブロックから、データ45Cを読み出す(ステップS506)。データ45Cは、検査用に読み出された、1ブロック分のデータである。データ45Cが検査対象のブロックにエラーなく記録されているか否かを確認するために、ECC回路51は、データ45Cに対するエラー検出処理を行う(ステップS507)。

【0089】

データ45Cからエラーが検出されなかった場合(ステップS507においてNo)、メモリコントローラ5は、検査対象のブロックの検査状況を、検査済みを示す「2」に変更する(ステップS511)。

【0090】

一方、データ45Cからエラーが検出された場合(ステップS507においてYes)、ECC回路51は、ステップS403(図4参照)と同様に、検出されたエラーの訂正が可能であるか否かを確認する(ステップS508)。

【0091】

検出されたエラーの訂正が不可能な場合(ステップS508においてNo)、メモリコントローラ3は、データ復旧処理を実行する(ステップS513)。データ復旧処理は、メインメモリ4に格納されたデータを、検査対象のブロックに書き戻す処理である。データ復旧処理の詳細は後述する。

【0092】

検出されたエラーの訂正が可能な場合(ステップS508においてYes)、ECC回路51は、データ45Cのエラーを訂正する(ステップS509)。アクセス制御部52は、訂正されたデータ45Cを検査対象のブロックに書き戻す(ステップS510)。

【0093】

なお、検査領域決定部53は、ページ単位でサブメモリ6を検査してもよい。この場合、検査対象のデータ45Cは、1ページ分のデータとなる。サブメモリ6がページ単位で検査される場合、訂正されたデータ45Cが書き戻されるタイミングは、エラー訂正直後でなくてもよい。これは、サブメモリ6に対するデータの書き戻しが、ブロック単位で行われるためである。たとえば、検査対象がページ8Pであり、かつ、ページ8Pのデータ45Cにエラーが検出された場合、アクセス制御部52は、ブロック7B(図2参照)に属する全てのページの検査が終了した後に、訂正されたデータ45Cをページ8Pに書き戻せばよい。この場合、訂正されたデータ45Cは、メモリコントローラ3により保持される。これにより、ページ8Pだけでなく、ブロック7Bに属する他のページで発生したエラーもリフレッシュすることができる。

【0094】

また、NANDフラッシュメモリの場合、データの書き込み時にエラービットが発生する可能性がある。このため、データ45Cのエラービット数が所定のしきい値よりも小さい場合、メモリコントローラ5は、サブメモリ6に対する負荷を軽減するために、データ45Cのエラー訂正及び再書き込みを実行しなくてもよい。

【0095】

訂正されたデータ45Cがサブメモリ6に書き戻された後に(ステップS510)、検査管理テーブル54が更新される(ステップS511)。具体的には、検査管理テーブル54において、検査対象のブロックの検査状況が、「2」に変更される。

【0096】

メモリコントローラ5は、サブメモリ6の全ブロックの検査が終了したか否かを確認する(ステップS512)。サブメモリ6の全ブロックの検査が終了した場合(ステップS512においてYes)、メモリコントローラ5は、図9の処理を終了する。サブメモリ6の全ブロックの検査が終了していない場合(ステップS512においてNo)、メモリコントローラ5は、未検査のブロックを検査するために、ステップS501に戻る。

【0097】

{6.データ復旧処理(ステップS513)}

図10は、データ復旧処理(ステップS513、図9参照)の流れを示すフローチャートである。上述したように、メモリコントローラ5は、検査対象のブロックから読み出したデータ45Cのエラーを訂正できない場合、メインメモリ4から書き戻し用のデータを取得する。

【0098】

メモリコントローラ5は、メモリコントローラ3に対して、データの読み出しを要求する(ステップS561)。具体的には、メモリコントローラ5は、検査対象のブロックの論理アドレスを出力する。メモリコントローラ3は、入力された論理アドレスに基づいて、検査対象のブロックに書き込まれたデータと同一のデータを、メインメモリ4から読み出し、読み出したデータをメモリコントローラ5へ出力する。このとき、メモリコントローラ3は、1ブロック分のデータを読み出す点を除き、図7に示す処理と同様の処理を実行する。

【0099】

メモリコントローラ3は、図7に示す処理を実行する際に、読み出したデータのエラー検出を行い(ステップS553)、エラー訂正が可能であるか否かを判定する(ステップS554)。読み出したデータから検出されたエラーの訂正ができない場合(ステップS554においてNo)、メモリコントローラ3は、メモリシステム2が故障したと判定する(ステップS557)。この場合、メモリコントローラ3は、検査対象のブロックに含まれるページの読み出し要求をホストシステム1から受け付けた際に、エラーメッセージをホストシステム1へ出力する。

【0100】

再び、図10を参照する。メモリコントローラ5は、読み出しデータがメモリコントローラ3から入力された場合(ステップS562においてYes)、入力されたデータを検査対象のブロックに書き戻す(ステップS563)。これにより、サブメモリ6においてエラー訂正できないデータ45Cが存在しても、サブメモリ6に記録されたデータ45Cを復旧することができる。

【0101】

{7.メモリ切替処理(ステップS410)}

以下、メモリコントローラ3が、アクセス対象をメモリ4からメモリ6へ切り替える処理(ステップS410、図4参照)について説明する。メモリコントローラ3は、読み出したデータ45Mのエラービット数が切替基準値よりも大きく(ステップS408においてYes)、かつ、サブメモリ6の検査が終了した場合(ステップS409においてYes)、アクセス対象のメモリを切り替える(ステップS410)。

【0102】

図11は、読み出し対象のメモリを切り替えるときのメモリコントローラ3の動作を示すフローチャートである。動作指示部34が、メモリコントローラ5に対して、アクセス対象のメモリをメモリ4からメモリ6へ切り替えることを指示する(ステップS461)。

【0103】

メモリコントローラ5は、アクセス対象の切り替え指示が入力された場合、検査管理テーブル54を初期化する。すなわち、検査管理テーブル54において、全ブロックの検査状況が「0」に設定され、エラービット数が消去される。メモリコントローラ5は、アクセス対象のメモリを、メモリ6からメモリ4へ切り替える。その後、メモリコントローラ5は、アクセス対象の切り替えが完了したことをメモリコントローラ3へ通知する。

【0104】

メモリコントローラ3は、切替完了の通知を受け付けた場合(ステップS462においてYes)、エラー記録データ33を消去する(ステップS463)。エラー記録データ33には、メインメモリ4におけるエラーページの情報が記録されているためである。メモリコントローラ3は、アクセス対象をメモリ4からメモリ6に切り替える(ステップS464)。これにより、アクセス対象の切り替え処理(ステップS410)が完了する。

【0105】

以後、メモリ6がメインメモリとして使用され、メモリ4がサブメモリとして使用される。そして、メモリの切り替え条件が満たされた場合、メモリコントローラ3は、再び、アクセス対象のメモリを切り替える。本実施の形態において、読み出し用のメインメモリと、バックアップ用のサブメモリとが切り替わることによって、メインメモリとして使用されるメモリの読み出し負荷が軽減される。また、メモリ4でリードディスターブが発生した場合であっても、メモリ4がサブメモリに切り替えられた後に、メモリ4のエラーを復旧することができる。したがって、メモリ4,6に格納されるデータの信頼性を確保することができる。

【0106】

{8.変形例}

上記実施の形態において、メモリコントローラ3は、アクセス対象のメモリの切り替え条件の一つとして、読み出したデータ45Mのエラービット数が切替基準値よりも大きいか否かを判定した(ステップS408)。しかし、メモリの切り替え条件は、これに限られない。

【0107】

図12は、メモリコントローラ3の変形例に係る機能ブロック図である。図12において、メモリコントローラ3は、リードカウンタ35を備える。リードカウンタ35は、メインメモリ4からのデータの読み出し回数をカウントする。読み出し回数は、メモリコントローラ3が各ページからデータを読み出すたびにカウントされる。メモリコントローラ3は、ステップS408の処理に代えて、リードカウンタ35のカウント数が読み出し上限値を超えているか否かを判定する。この場合、読み出し上限値は、リードディスターブが発生すると想定される読み出し回数よりも小さく設定されることが望ましい。これにより、メモリコントローラ3は、リードディスターブが実際に発生する前に、アクセス対象のメモリを切り替えることができるため、データの信頼性を確保することができる。

【0108】

また、リードカウンタ35は、メインメモリ4のページごとの読み出し回数をカウントしてもよい。この場合、メモリコントローラ3は、エラー記録データ33をメモリコントローラ5に出力しなくてもよい(ステップS406、図4参照)。メモリコントローラ3は、ステップS406に代えて、読み出し回数が所定の読み出し基準値を超えたページが発生した場合、そのページを有するブロックの論理アドレスをメモリコントローラ5へ通知する。たとえば、ページ7P(図2参照)の読み出し回数が所定の読み出し基準値を超えた場合、動作指示部34は、ブロック7Bの論理アドレスをメモリコントローラ5に出力する。メモリコントローラ5は、検査管理テーブル54において、ブロック7Bの検査状況を、優先検査を示す「1」に設定すればよい。

【0109】

上記実施の形態において、メモリコントローラ3,5が、メモリシステム2に搭載される構成を説明した。しかし、ホストシステム1が、メモリコントローラ3,5を備える構成であってもよい。また、ECC回路31,51は、メモリ4,6の内部にそれぞれ設けられてもよい。あるいは、ECC回路31,51は、メモリコントローラ3及びメモリコントローラ5の内部に設けられてもよい。

【0110】

上記実施の形態において、メモリシステム2が、メモリコントローラ3,5を備える構成を説明した。しかし、メモリシステム2において、メモリコントローラ3が、メモリ4,6の両者に対するアクセスを制御してもよい。この場合、メモリコントローラ3は、ホストシステム1の読み出し要求及び書き込み要求を優先的に処理する。メモリコントローラ3は、ホストシステム1からの要求がないときに、サブメモリ6の検査を行えばよい。

【0111】

本実施の形態において、メモリ4,6が同一の論理アドレス空間を有する例について説明した。しかし、メモリ4,6は、互いに異なる論理アドレス空間を有していてもよい。この場合、メモリコントローラ3,5のいずれかが、メモリ4の論理アドレスと、メモリ6の論理アドレスとの対応関係を示すアドレステーブルを保持すればよい。

【符号の説明】

【0112】

1 ホストシステム

2 メモリシステム

3,5 メモリコントローラ

4 メモリ(メインメモリ)

6 メモリ(サブメモリ)

31,51 ECC回路

32,52 アクセス制御部

33 エラー記録データ

34 動作指示部

35 リードカウンタ

53 検査領域決定部

54 検査管理テーブル

【特許請求の範囲】

【請求項1】

再書き込み可能な不揮発性メモリである第1メモリと、

再書き込み可能な不揮発性メモリであり、前記第1メモリのバックアップ用のメモリとして設定された第2メモリと、

前記第1メモリと前記第2メモリとにアクセスするメモリコントローラと、

を備え、

前記メモリコントローラは、

ホストから書き込み要求を受け付けた場合、前記第1メモリ及び前記第2メモリに対して同一のデータを書き込み、前記ホストから読み出し要求を受け付けた場合、前記第1メモリからデータを読み出すアクセス制御部と、

前記第2メモリが有するデータ領域のうちいずれかの領域を検査領域として決定する検査領域決定部と、

前記検査領域から読み出された検査対象データに対してエラー検出を行い、前記検査対象データからエラーが検出された場合、前記検査対象データのエラーを訂正するエラー訂正部と、

を備え、

前記アクセス制御部は、訂正された検査対象データを前記検査領域に再書き込みするメモリシステム。

【請求項2】

請求項1に記載のメモリシステムであって、

前記検査領域決定部は、前記第1メモリに含まれる第1領域が優先検査条件を満たした場合、前記第2メモリに含まれ、かつ、前記第1領域に格納されたデータと同一のデータを格納する第2領域を、優先的に前記検査領域として決定するメモリシステム。

【請求項3】

請求項1に記載のメモリシステムであって、

前記エラー訂正部は、前記検査対象データからエラーを検出した場合、前記検査対象データのエラーを訂正するか否かを判定し、

前記アクセス制御部は、エラーを訂正すると判定された場合、前記訂正された検査対象データを前記検査領域に再書き込みするメモリシステム。

【請求項4】

請求項2または請求項3に記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、

を備え、

前記優先検査条件は、前記第1メモリから読み出されたデータのエラービット数が予め設定された第1優先検査基準値を超えることであるメモリシステム。

【請求項5】

請求項2または請求項3に記載のメモリシステムであって、

前記メモリコントローラは、

前記第1メモリが有するデータ領域ごとに、データが読み出される回数をカウントするカウンタ、

を備え、

前記優先検査条件は、前記読み出し回数が予め設定された第2優先検査基準値を超えることであるメモリシステム。

【請求項6】

請求項2ないし請求項5のいずれかに記載のメモリシステムであって、

前記検査領域決定部は、前記第1領域が前記優先検査条件を満たし、かつ、前記第2領域が検査されていない場合、前記第2領域を優先的に前記検査領域として決定するメモリシステム。

【請求項7】

請求項1ないし請求項6のいずれかに記載のメモリシステムであって、

前記アクセス制御部は、前記エラー訂正部が前記検査対象データのエラーを訂正できない場合、前記第1メモリに含まれ、かつ、前記検査領域に格納されたデータと同一のデータを格納するデータ領域から復旧データを読み出し、前記復旧データを前記検査領域に再書き込みするメモリシステム。

【請求項8】

請求項1または請求項2に記載のメモリシステムであって、

前記アクセス制御部は、所定の切り替え条件が満たされた場合、前記読み出し要求を受け付けたときにデータを読み出すメモリを、前記第1メモリから前記第2メモリに切り替えるとともに、前記第2メモリのバックアップ用のメモリとして前記第1メモリを設定するメモリシステム。

【請求項9】

請求項8に記載のメモリシステムであって、

前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記読み出し要求に応じて前記第1メモリから読み出されたデータのエラービット数が予め設定された第1切替基準値を超えることであるメモリシステム。

【請求項10】

請求項8に記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリからのデータの読み出し回数をカウントするカウンタ、

を備え、

前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記第1メモリからのデータの読み出し回数が予め設定された第2切替基準値を超えることであるメモリシステム。

【請求項11】

請求項8ないし請求項10のいずれかに記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、

を備え、

前記切り替え条件は、前記第1メモリから読み出されたデータのエラーを訂正できないことであるメモリシステム。

【請求項12】

請求項1ないし請求項11のいずれかに記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリ及び前記第2メモリのうち、前記読み出し要求に基づいてデータが読み出されるメモリに対するアクセスを制御する第1メモリコントローラと、

前記第1メモリ及び前記第2メモリのうち、バックアップ用のメモリに対するアクセスを制御する第2メモリコントローラと、

を備えるメモリシステム。

【請求項1】

再書き込み可能な不揮発性メモリである第1メモリと、

再書き込み可能な不揮発性メモリであり、前記第1メモリのバックアップ用のメモリとして設定された第2メモリと、

前記第1メモリと前記第2メモリとにアクセスするメモリコントローラと、

を備え、

前記メモリコントローラは、

ホストから書き込み要求を受け付けた場合、前記第1メモリ及び前記第2メモリに対して同一のデータを書き込み、前記ホストから読み出し要求を受け付けた場合、前記第1メモリからデータを読み出すアクセス制御部と、

前記第2メモリが有するデータ領域のうちいずれかの領域を検査領域として決定する検査領域決定部と、

前記検査領域から読み出された検査対象データに対してエラー検出を行い、前記検査対象データからエラーが検出された場合、前記検査対象データのエラーを訂正するエラー訂正部と、

を備え、

前記アクセス制御部は、訂正された検査対象データを前記検査領域に再書き込みするメモリシステム。

【請求項2】

請求項1に記載のメモリシステムであって、

前記検査領域決定部は、前記第1メモリに含まれる第1領域が優先検査条件を満たした場合、前記第2メモリに含まれ、かつ、前記第1領域に格納されたデータと同一のデータを格納する第2領域を、優先的に前記検査領域として決定するメモリシステム。

【請求項3】

請求項1に記載のメモリシステムであって、

前記エラー訂正部は、前記検査対象データからエラーを検出した場合、前記検査対象データのエラーを訂正するか否かを判定し、

前記アクセス制御部は、エラーを訂正すると判定された場合、前記訂正された検査対象データを前記検査領域に再書き込みするメモリシステム。

【請求項4】

請求項2または請求項3に記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、

を備え、

前記優先検査条件は、前記第1メモリから読み出されたデータのエラービット数が予め設定された第1優先検査基準値を超えることであるメモリシステム。

【請求項5】

請求項2または請求項3に記載のメモリシステムであって、

前記メモリコントローラは、

前記第1メモリが有するデータ領域ごとに、データが読み出される回数をカウントするカウンタ、

を備え、

前記優先検査条件は、前記読み出し回数が予め設定された第2優先検査基準値を超えることであるメモリシステム。

【請求項6】

請求項2ないし請求項5のいずれかに記載のメモリシステムであって、

前記検査領域決定部は、前記第1領域が前記優先検査条件を満たし、かつ、前記第2領域が検査されていない場合、前記第2領域を優先的に前記検査領域として決定するメモリシステム。

【請求項7】

請求項1ないし請求項6のいずれかに記載のメモリシステムであって、

前記アクセス制御部は、前記エラー訂正部が前記検査対象データのエラーを訂正できない場合、前記第1メモリに含まれ、かつ、前記検査領域に格納されたデータと同一のデータを格納するデータ領域から復旧データを読み出し、前記復旧データを前記検査領域に再書き込みするメモリシステム。

【請求項8】

請求項1または請求項2に記載のメモリシステムであって、

前記アクセス制御部は、所定の切り替え条件が満たされた場合、前記読み出し要求を受け付けたときにデータを読み出すメモリを、前記第1メモリから前記第2メモリに切り替えるとともに、前記第2メモリのバックアップ用のメモリとして前記第1メモリを設定するメモリシステム。

【請求項9】

請求項8に記載のメモリシステムであって、

前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記読み出し要求に応じて前記第1メモリから読み出されたデータのエラービット数が予め設定された第1切替基準値を超えることであるメモリシステム。

【請求項10】

請求項8に記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリからのデータの読み出し回数をカウントするカウンタ、

を備え、

前記切り替え条件は、前記第2メモリの全データ領域に対するエラー検出処理を終了し、かつ、前記第1メモリからのデータの読み出し回数が予め設定された第2切替基準値を超えることであるメモリシステム。

【請求項11】

請求項8ないし請求項10のいずれかに記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリから読み出されたデータのエラーを検出するエラー検出部、

を備え、

前記切り替え条件は、前記第1メモリから読み出されたデータのエラーを訂正できないことであるメモリシステム。

【請求項12】

請求項1ないし請求項11のいずれかに記載のメモリシステムであって、

前記メモリコントローラは、さらに、

前記第1メモリ及び前記第2メモリのうち、前記読み出し要求に基づいてデータが読み出されるメモリに対するアクセスを制御する第1メモリコントローラと、

前記第1メモリ及び前記第2メモリのうち、バックアップ用のメモリに対するアクセスを制御する第2メモリコントローラと、

を備えるメモリシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−203642(P2012−203642A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−67510(P2011−67510)

【出願日】平成23年3月25日(2011.3.25)

【出願人】(591128453)株式会社メガチップス (322)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月25日(2011.3.25)

【出願人】(591128453)株式会社メガチップス (322)

【Fターム(参考)】

[ Back to top ]