メモリセルアレイを用いたIDチップおよびその生成方法

【課題】認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報を半導体メモリに予め搭載でき、セキュリティの向上を図れるIDチップおよびその生成方法を提供する。

【解決手段】本IDチップは、メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いた構成とされる。このメモリセルは、“0” または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”または“High”としてデータを生成する。そして、生成されたデータを用いて同一チップか否かを判別する。チップの判別は、メモリセルアレイのデータのハミング距離を測定し、ハミング距離が所定閾値以内の場合に同一チップと判別する。

【解決手段】本IDチップは、メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いた構成とされる。このメモリセルは、“0” または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”または“High”としてデータを生成する。そして、生成されたデータを用いて同一チップか否かを判別する。チップの判別は、メモリセルアレイのデータのハミング距離を測定し、ハミング距離が所定閾値以内の場合に同一チップと判別する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固有の識別情報を有するIDチップおよびその生成方法に関する技術である。

【背景技術】

【0002】

昨今の情報社会において、セキュリティの向上を図るべく、固有のID番号のような識別情報データを半導体集積回路(IC)本体に搭載する技術が研究されている。

特に、ICカードには個人情報等も記録されており、そのセキュリティの確保が重要となっている。また、ICカードの認証等において、搭載されたチップ毎に複製不可能な認証データを生成・保持することによって、更なるセキュリティの向上が求められている。

【0003】

従来、認証データを生成する方法としては、トランジスタのバラツキ特性を利用したものがある。トランジスタのバラツキを利用したID生成方法としては、トランジスタの電流値バラツキを用いるものや、遅延バラツキを利用するものや、ラッチを利用するものが知られている(例えば、特許文献1,非特許文献1を参照。)。

しかしながら、トランジスタの電流値バラツキを用いるものや、遅延バラツキを利用するものや、ラッチを利用するものは、SRAMのメモリセル構造をそのまま用いることはできず、専用の認証データ生成回路を作製する必要があった。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】再表02/045139号公報

【非特許文献】

【0005】

【非特許文献1】Ying Su, A Digital 1.6 pJ/bit Chip Identification CircuitUsing Process Variations, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, No. 1,JANUARY 2008, P.68−77.

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した如く、従来は、認証データ生成のための専用回路により事前に認証情報を作成し、その認証情報がユニークとなるように管理し、その上でメモリに記憶させる手順になる。

従って、認証データ生成用の専用回路を設ける必要があるといった問題がある。

【0007】

上記状況に鑑みて、本発明は、認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報を半導体メモリに予め搭載でき、セキュリティの向上を図れるIDチップおよびその生成方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明者らは、鋭意研究を重ねた結果、微細プロセスでのSRAMメモリセルにおいて、各メモリセルの特性が閾値電圧のバラツキによってチップごとに異なることを知見し、かかるチップごとに異なる特性のバラツキを利用したIDチップおよびその生成手法を完成した。本明細書において、IDチップは、固有の識別情報(ID)を有するチップの意味で用い、また、チップIDはチップ毎の固有の識別情報(ID)の意味で用いる。

【0009】

すなわち、上記目的を達成するため、本発明のIDチップは、メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いた構成とされる。

【0010】

かかる構成によれば、認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報を半導体メモリに予め搭載できる。また、メモリセルアレイに生成されたランダムなデータはチップごとに異なるため、複製不可能な情報となり、また、同一チップにおいては再現性のあるデータとなり、暗号生成で用いる秘密鍵として利用することが可能となる。

【0011】

また、上記IDチップにおけるメモリセルは、各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されることが好ましい態様である。

上記の構成は、SRAM等のメモリセルの典型的な回路構成である。インバータは、P型MOSトランジスタとN型MOSトランジスタで構成されるCMOSインバータが好適に用いられる。

【0012】

このメモリセルは、“0”

または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”としてデータ書き込みが行われたものである。

一般に、SRAM等のメモリセルへのデータ書込みの際には、2本のビット線のうち片側を“Low”、もう一方を“High”として目的のデータを書込む。これに対して、本発明のIDチップでは、両ビット線を同時に“Low”としてメモリセルにデータの書込みを行う。この時、閾値電圧のバラツキによってメモリセルに格納されるデータは、ランダムに決定される。この生成されるデータは、チップの閾値電圧のバラツキによって決定されるため、同一チップにおいては再現性あるデータとなる。また、生成されるデータは、チップ毎に異なるデータである。

なお、両ビット線に同時に“High”としてデータ書き込みを行う方法については、シミュレーションで確認を行ったところ、初期データ依存性が強く、閾値電圧のバラツキによってメモリセルにランダムなデータを生成させることは困難であるとの知見を得ている。これは、メモリセルのインバータカップルとビット線を接続するトランジスタがNMOSトランジスタで構成されていることから、“High”の電圧によってデータは反転し難く、初期データ依存性が強く現れたと推察する。

【0013】

また、上記メモリセルの一対のアクセストランジスタにおいて、相対的に、一方の閾値が低く、他方の閾値が高い場合、アクセストランジスタの閾値が低い側のインバータに“Low”が記憶されやすく、アクセストランジスタの閾値が高い側のインバータに“High”が記憶されやすい。

上記メモリセルは、6個のトランジスタで構成されるところ、クロスカップル接続された一対のインバータを構成する4個のトランジスタの閾値に起因する記憶データの傾向は見られず、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタの閾値にのみ記憶データに一定の傾向が見られることを、発明者らは実験により確認したのである。

【0014】

次に、本発明のIDチップの生成方法は、各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されるメモリセルがアレイ状に配置されたメモリセルアレイを用いて、下記(1)〜(5)の処理を行うものである。

【0015】

(1)全て或いは一部のメモリセルに対して、“0”

または“1”の初期データを書き込む。

(2)書き込みを行ったメモリセルに対して、データを読み出し、初期データであることを確認する。

(3)確認したメモリセルに対して、両ビット線を同時に“Low”としてランダムデータを生成する。

(4)メモリセルアレイのデータを読み出す。

(5)読み出したデータを固有の識別情報として記憶する。

【0016】

上記(1)の処理で、全て或いは一部のメモリセルに対してデータを書き込むことにしたのは、メモリセルアレイ全体(全行×全列)のデータを固有の識別情報として扱う場合や、メモリセルアレイの一部のブロック(一部の行×一部の列)のデータを固有の識別情報として扱う場合などを想定したものである。

また、上記(1)の処理で、“0”

または“1”の初期データは、オール“0” またはオール“1”のみならず、予め想定した0” と“1”で構成されるパターンに初期化しても構わない。

ここで、上記のIDチップの生成方法を用いて生成されたデータを用いて同一チップか否かを判別するIDチップ判別方法は、好ましくは、IDチップを構成するメモリセルアレイのデータのハミング距離を測定し、ハミング距離が所定閾値以内の場合に同一チップと判別する。ハミング距離とは、等しいビット数を持つ2つのビット列の中で、対応する位置にある異なったデータ(“0”,“1”)の個数である。

上記のIDチップの生成方法を用いて生成されたデータは、同一のメモリセルアレイの場合に再現性はあるが、生成されるデータが毎回完全に一致するものではない。そのため、ハミング距離の指標を用いて、同一チップか否かを判別することにしたのである。

【0017】

ハミング距離の所定閾値は、同一チップの最大ハミング距離と、異なるチップの最小ハミング距離との間の範囲に設定することが好ましい。例えば、同一チップの最大ハミング距離が5であり、異なるチップの最小ハミング距離50の場合、ハミング距離の所定閾値は6〜49の範囲に設定する。より好ましくは、ハミング距離の所定閾値は、同一チップの最大ハミング距離に近い値に設定する。上記の例では、ハミング距離の所定閾値は6〜49の範囲に設定するが、同一チップの最大ハミング距離の5に近い値に余裕を設けた6〜9にハミング距離の所定閾値を設定する。

【0018】

上述のIDチップの生成方法を用いることで、SRAMメモリセルの一部に固有の識別番号を生成することが可能となる。

本発明は、SRAMのメモリセル構造をそのまま用いているので、SRAMの一部のブロックまたは一部の行を識別情報データの格納領域と位置付け、そこに、メモリセル群の閾値電圧のバラツキを利用したチップ固有の識別情報データを生成・記録させるのである。

これにより、SRAMメモリセルを備える電子デバイスには、容易に固有の識別番号を持たせることができる。

【発明の効果】

【0019】

本発明によれば、認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報データを半導体メモリに予め搭載し、セキュリティの向上を図ることができる。

【図面の簡単な説明】

【0020】

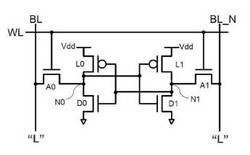

【図1】メモリセルの回路構成図

【図2】両ビット線を“Low”にして、ワード線の電位を降下させた場合のメモリセルの内部ノード(N0,N1)の電位の変移を示す図

【図3】ロードトランジスタ(L0,L1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図

【図4】ドライブトランジスタ(D0,D1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図

【図5】アクセストランジスタ(A0,A1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図

【図6】アクセストランジスタ(A0,A1)の閾値電位の分布グラフ

【図7】メモリセルの内部ノード(N0,N1)の格納データの説明図

【図8】同一チップの生成データの再現性の確認試験結果を示す図

【図9】異なるチップの生成データのバラツキ度合いの確認試験結果を示す図

【図10】チップIDの生成フロー図

【図11】チップIDの生成用回路の構成図

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施形態について、図面を参照しながら詳細に説明していく。なお、本発明の範囲は、以下の実施例や図示例に限定されるものではなく、幾多の変更及び変形が可能である。

【実施例1】

【0022】

図1は、メモリセルの回路構成図を示している。メモリセルは、各々の出力がメモリセルの列に対応して配置される一対のビット線(BL,BL_N)の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線(BL,BL_N)とインバータの出力との間に設けられた一対のアクセストランジスタ(A0,A1)と、アクセストランジスタ(A0,A1)の導通を制御する1本のワード線(WL)から構成される。ここで、一対のインバータは、P型MOSトランジスタのロードトランジスタ(L0,L1)とN型MOSトランジスタのドライブトランジスタ(D0,D1)で構成されるCMOSインバータである。

メモリセルの内部ノード(N0,N1)には、通常、2本のビット線(BL,BL_N)のうち片側を“Low”、もう一方を“High”として、“Low”又は“High”の電位が保持される。すなわち、メモリセルの内部ノード(N0,N1)は、“0”又は“1”のデータが書き込まれ、データを記憶することになる。

【0023】

本発明のIDチップでは、通常と異なり、両ビット線を同時に“Low”としてメモリセルにデータの書込みを行う。図2は、両ビット線を“Low”にして、ワード線の電位を降下させた場合のメモリセルの内部ノード(N0,N1)の電位の変移を示している。図2(1)に示すように、ワード線(WL)の電位を1.2Vから0Vに変化させた場合、メモリセルの内部ノード(N0)および内部ノード(N1)の電位は“Low”又は“High”のランダムな電位となり、“0”又は“1”のランダムなデータを記憶することが確認できる。

【0024】

このようなランダムな電位の傾向に関し、それぞれのトランジスタの閾値電位(Vth)との相関性について調査を行った。調査結果を図3〜5に示す。図3はロードトランジスタ(L0,L1)の閾値電位(Vth)の高低による内部ノード(N0,N1)の電位分布を示す図であり、図4はドライブトランジスタ(D0,D1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図であり、図5はアクセストランジスタ(A0,A1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図である。

図3と図4には、内部ノード(N0,N1)の電位の傾向に関して、特段、トランジスタの閾値電位(Vth)との相関性は見られなかった。

【0025】

しかしながら、図5には、内部ノード(N0,N1)の電位の傾向に関して、トランジスタの閾値電位(Vth)との相関性が顕著に見られた。アクセストランジスタ(A0,A1)の閾値電位の高低によって、内部ノード(N0,N1)の電位分布に傾向が見られたのである。すなわち、アクセストランジスタ(A0)の閾値が低く、アクセストランジスタ(A1)の閾値が高いほど、内部ノード(N0)に“Low”が記憶されやすい傾向があった。また、逆に、アクセストランジスタ(A0)の閾値が高く、アクセストランジスタ(A1)の閾値が低いほど、内部ノード(N1)に“High”が記憶されやすいという傾向があった。

【0026】

すなわち、図5の左上の領域は、アクセストランジスタ(A0)の閾値が、アクセストランジスタ(A1)よりも低い領域であり、アクセストランジスタ(A0)に接続された内部ノード(N0)にビット線から書き込まれる“Low”の電圧が記憶されやすい傾向を示している。一方、図5の右下の領域はアクセストランジスタ(A0)の閾値が、アクセストランジスタ(A1)よりも高い領域であり、アクセストランジスタ(A1)に接続された内部ノード(N1)にビット線から書き込まれる“Low”の電圧が記憶されやすく、内部ノード(N0)には逆の“Low”が記憶されやすいという傾向を示している。

【0027】

図6は、図5をヒストグラムとして表したものであり、アクセストランジスタ(A0,A1)の閾値電圧の分布とデータ依存性の関係を示したものである。

内部ノード(N0)が“Low”の状態を保持した場合は“0”,“High”の状態を保持した場合は“1”のデータを記憶した状態とする。

データが“0”の場合、アクセストランジスタ(A0)の閾値は低い傾向となり、バラツキを考慮していないモデルの閾値(全トランジスタの閾値の平均値)と比較して−0.0152V低い平均値を示しており、分布の中心が左にシフトしている。一方、アクセストランジスタ(A1)は、平均値が+0.0156V高い値となっている。

また、データが“1”の場合は、データが“0”の場合と逆の傾向を示している。

以上のことは、内部ノード(N0)に記憶されたデータが“Low”であるときと、“High”であるときとでは、アクセストランジスタ(A0,A1)の閾値電圧の分布が異なることを示しているのである。

従って、アクセストランジスタ(A0,A1)の閾値電圧のバラツキによって、メモリセルの内部ノード(N0,N1)に格納されるデータは、ランダムに決定されることになる。

【0028】

図7を参照して、メモリセルの内部ノード(N0,N1)の格納データの傾向について説明する。図7(1)は、アクセストランジスタ(A0)の閾値が低く、アクセストランジスタ(A1)の閾値が高いほど、内部ノード(N0)に“Low”が記憶されやすい傾向があることを示す図である。また、図7(2)は、アクセストランジスタ(A0)の閾値が高く、アクセストランジスタ(A1)の閾値が低いほど、内部ノード(N1)に“High”が記憶されやすいという傾向があることを示す図である。

ワード線(WL)を閉じた後に、メモリセルの内部ノード(N0,N1)に格納されるデータは、アクセストランジスタ(A0,A1)の閾値電圧のバラツキに最も影響を受け、閾値電圧のバラツキに応じてランダムになる。一方、ロードトランジスタ(L0,L1)やドライブトランジスタ(D0,D1)の閾値電圧の影響は少なく、内部ノード(N0,N1)に格納されるデータから、ロードトランジスタ(L0,L1)やドライブトランジスタ(D0,D1)の閾値の予測は困難である。

【0029】

このアクセストランジスタ(A0,A1)の閾値電圧のバラツキによって、128ビットのメモリセルアレイの保持データに固有のバラツキが存在するか否かの調査を実施した。

先ず、128ビットのメモリセルの全メモリセルに“0”データを書き込んだ。そして、“0”データの読み出しを行い、全メモリセルの保持データが初期化されたか否かを確認した。そして、全メモリセルの両ビット線を“Low”とした。全メモリセルの保持データを読み込み、生成されたデータを確認した。電源電圧は1.2Vを使用した。

上記の作業を1つのメモリセルアレイのチップに4回繰り返して、同一チップの生成データの再現性を確認した。結果を図8に示す。

また、上記の作業を異なる4つのメモリセルアレイのチップに対して行い、異なるチップの生成データのバラツキ度合いを確認した。結果を図9に示す。

【0030】

図8に示されるように、同一チップ(#1)に試行を4回繰り返した場合でも、生成データの分布、すなわち“0”と“1”のデータ分布に大きな変化は見られなかった。

一方、図9に示されるように、異なる4つのチップ(#1〜#4)に試行を行った場合は、生成データの分布、すなわち“0”と“1”のデータ分布は大きく相違することが確認できた。

【0031】

図8、図9の“0”と“1”のデータ分布のバラツキ度合いをハミング距離で評価した結果を下記表1にまとめる。

【0032】

【表1】

【0033】

上記の表1から、128ビットのメモリセルアレイにおいて、同一チップと異なるチップとでは、ハミング距離が10倍程度も異なることが確認できた。

すなわち、メモリセルアレイの個々のメモリセルの閾値電圧のバラツキによって決定され生成されるデータは、同一チップにおいては再現性あるデータとなり、また、チップ毎に異なるデータであることになる。

このことは、生成されるデータをチップの固有の識別情報(ID)として扱えることになる。また、ビット長を大きくすることで、生成データのユニーク性が向上し、大量のチップも十分に判別可能になる。

【0034】

図10は、チップIDの生成フローを示している。

(ステップS101)全て或いは一部のメモリセルに対して、“0”

または“1”の初期データを書き込む。

(ステップS103)書き込みを行ったメモリセルに対して、データを読み出し、初期データであることを確認する。

(ステップS105)確認したメモリセルに対して、両ビット線を同時に“Low”としてランダムデータを生成する。

(ステップS107)メモリセルアレイのデータを読み出す。

(ステップS109)読み出したデータをチップの固有の識別情報(チップID)として記憶する。

【0035】

図11は、チップIDの生成用回路の構成図である。

両ビット線“Low”書込みは、各ビット線に放電用のNMOSトランジスタを追加することで実現される。追加したNMOSトランジスタは、BLCTRL信号によって制御され、BLCTRL信号が“High”の時に、両ビット線を放電する。また、ビット線放電用のNMOSトランジスタは、各列にそれぞれ追加され、BLCTRL信号にて一斉に制御を行える構成にしている。

【産業上の利用可能性】

【0036】

本発明は、暗号生成で用いる秘密鍵として利用できる。

【符号の説明】

【0037】

A0,A1 アクセストランジスタ

L1,L2 ロードトランジスタ

D1,D2 ドライブトランジスタ

【技術分野】

【0001】

本発明は、固有の識別情報を有するIDチップおよびその生成方法に関する技術である。

【背景技術】

【0002】

昨今の情報社会において、セキュリティの向上を図るべく、固有のID番号のような識別情報データを半導体集積回路(IC)本体に搭載する技術が研究されている。

特に、ICカードには個人情報等も記録されており、そのセキュリティの確保が重要となっている。また、ICカードの認証等において、搭載されたチップ毎に複製不可能な認証データを生成・保持することによって、更なるセキュリティの向上が求められている。

【0003】

従来、認証データを生成する方法としては、トランジスタのバラツキ特性を利用したものがある。トランジスタのバラツキを利用したID生成方法としては、トランジスタの電流値バラツキを用いるものや、遅延バラツキを利用するものや、ラッチを利用するものが知られている(例えば、特許文献1,非特許文献1を参照。)。

しかしながら、トランジスタの電流値バラツキを用いるものや、遅延バラツキを利用するものや、ラッチを利用するものは、SRAMのメモリセル構造をそのまま用いることはできず、専用の認証データ生成回路を作製する必要があった。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】再表02/045139号公報

【非特許文献】

【0005】

【非特許文献1】Ying Su, A Digital 1.6 pJ/bit Chip Identification CircuitUsing Process Variations, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, No. 1,JANUARY 2008, P.68−77.

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した如く、従来は、認証データ生成のための専用回路により事前に認証情報を作成し、その認証情報がユニークとなるように管理し、その上でメモリに記憶させる手順になる。

従って、認証データ生成用の専用回路を設ける必要があるといった問題がある。

【0007】

上記状況に鑑みて、本発明は、認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報を半導体メモリに予め搭載でき、セキュリティの向上を図れるIDチップおよびその生成方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明者らは、鋭意研究を重ねた結果、微細プロセスでのSRAMメモリセルにおいて、各メモリセルの特性が閾値電圧のバラツキによってチップごとに異なることを知見し、かかるチップごとに異なる特性のバラツキを利用したIDチップおよびその生成手法を完成した。本明細書において、IDチップは、固有の識別情報(ID)を有するチップの意味で用い、また、チップIDはチップ毎の固有の識別情報(ID)の意味で用いる。

【0009】

すなわち、上記目的を達成するため、本発明のIDチップは、メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いた構成とされる。

【0010】

かかる構成によれば、認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報を半導体メモリに予め搭載できる。また、メモリセルアレイに生成されたランダムなデータはチップごとに異なるため、複製不可能な情報となり、また、同一チップにおいては再現性のあるデータとなり、暗号生成で用いる秘密鍵として利用することが可能となる。

【0011】

また、上記IDチップにおけるメモリセルは、各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されることが好ましい態様である。

上記の構成は、SRAM等のメモリセルの典型的な回路構成である。インバータは、P型MOSトランジスタとN型MOSトランジスタで構成されるCMOSインバータが好適に用いられる。

【0012】

このメモリセルは、“0”

または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”としてデータ書き込みが行われたものである。

一般に、SRAM等のメモリセルへのデータ書込みの際には、2本のビット線のうち片側を“Low”、もう一方を“High”として目的のデータを書込む。これに対して、本発明のIDチップでは、両ビット線を同時に“Low”としてメモリセルにデータの書込みを行う。この時、閾値電圧のバラツキによってメモリセルに格納されるデータは、ランダムに決定される。この生成されるデータは、チップの閾値電圧のバラツキによって決定されるため、同一チップにおいては再現性あるデータとなる。また、生成されるデータは、チップ毎に異なるデータである。

なお、両ビット線に同時に“High”としてデータ書き込みを行う方法については、シミュレーションで確認を行ったところ、初期データ依存性が強く、閾値電圧のバラツキによってメモリセルにランダムなデータを生成させることは困難であるとの知見を得ている。これは、メモリセルのインバータカップルとビット線を接続するトランジスタがNMOSトランジスタで構成されていることから、“High”の電圧によってデータは反転し難く、初期データ依存性が強く現れたと推察する。

【0013】

また、上記メモリセルの一対のアクセストランジスタにおいて、相対的に、一方の閾値が低く、他方の閾値が高い場合、アクセストランジスタの閾値が低い側のインバータに“Low”が記憶されやすく、アクセストランジスタの閾値が高い側のインバータに“High”が記憶されやすい。

上記メモリセルは、6個のトランジスタで構成されるところ、クロスカップル接続された一対のインバータを構成する4個のトランジスタの閾値に起因する記憶データの傾向は見られず、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタの閾値にのみ記憶データに一定の傾向が見られることを、発明者らは実験により確認したのである。

【0014】

次に、本発明のIDチップの生成方法は、各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されるメモリセルがアレイ状に配置されたメモリセルアレイを用いて、下記(1)〜(5)の処理を行うものである。

【0015】

(1)全て或いは一部のメモリセルに対して、“0”

または“1”の初期データを書き込む。

(2)書き込みを行ったメモリセルに対して、データを読み出し、初期データであることを確認する。

(3)確認したメモリセルに対して、両ビット線を同時に“Low”としてランダムデータを生成する。

(4)メモリセルアレイのデータを読み出す。

(5)読み出したデータを固有の識別情報として記憶する。

【0016】

上記(1)の処理で、全て或いは一部のメモリセルに対してデータを書き込むことにしたのは、メモリセルアレイ全体(全行×全列)のデータを固有の識別情報として扱う場合や、メモリセルアレイの一部のブロック(一部の行×一部の列)のデータを固有の識別情報として扱う場合などを想定したものである。

また、上記(1)の処理で、“0”

または“1”の初期データは、オール“0” またはオール“1”のみならず、予め想定した0” と“1”で構成されるパターンに初期化しても構わない。

ここで、上記のIDチップの生成方法を用いて生成されたデータを用いて同一チップか否かを判別するIDチップ判別方法は、好ましくは、IDチップを構成するメモリセルアレイのデータのハミング距離を測定し、ハミング距離が所定閾値以内の場合に同一チップと判別する。ハミング距離とは、等しいビット数を持つ2つのビット列の中で、対応する位置にある異なったデータ(“0”,“1”)の個数である。

上記のIDチップの生成方法を用いて生成されたデータは、同一のメモリセルアレイの場合に再現性はあるが、生成されるデータが毎回完全に一致するものではない。そのため、ハミング距離の指標を用いて、同一チップか否かを判別することにしたのである。

【0017】

ハミング距離の所定閾値は、同一チップの最大ハミング距離と、異なるチップの最小ハミング距離との間の範囲に設定することが好ましい。例えば、同一チップの最大ハミング距離が5であり、異なるチップの最小ハミング距離50の場合、ハミング距離の所定閾値は6〜49の範囲に設定する。より好ましくは、ハミング距離の所定閾値は、同一チップの最大ハミング距離に近い値に設定する。上記の例では、ハミング距離の所定閾値は6〜49の範囲に設定するが、同一チップの最大ハミング距離の5に近い値に余裕を設けた6〜9にハミング距離の所定閾値を設定する。

【0018】

上述のIDチップの生成方法を用いることで、SRAMメモリセルの一部に固有の識別番号を生成することが可能となる。

本発明は、SRAMのメモリセル構造をそのまま用いているので、SRAMの一部のブロックまたは一部の行を識別情報データの格納領域と位置付け、そこに、メモリセル群の閾値電圧のバラツキを利用したチップ固有の識別情報データを生成・記録させるのである。

これにより、SRAMメモリセルを備える電子デバイスには、容易に固有の識別番号を持たせることができる。

【発明の効果】

【0019】

本発明によれば、認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報データを半導体メモリに予め搭載し、セキュリティの向上を図ることができる。

【図面の簡単な説明】

【0020】

【図1】メモリセルの回路構成図

【図2】両ビット線を“Low”にして、ワード線の電位を降下させた場合のメモリセルの内部ノード(N0,N1)の電位の変移を示す図

【図3】ロードトランジスタ(L0,L1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図

【図4】ドライブトランジスタ(D0,D1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図

【図5】アクセストランジスタ(A0,A1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図

【図6】アクセストランジスタ(A0,A1)の閾値電位の分布グラフ

【図7】メモリセルの内部ノード(N0,N1)の格納データの説明図

【図8】同一チップの生成データの再現性の確認試験結果を示す図

【図9】異なるチップの生成データのバラツキ度合いの確認試験結果を示す図

【図10】チップIDの生成フロー図

【図11】チップIDの生成用回路の構成図

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施形態について、図面を参照しながら詳細に説明していく。なお、本発明の範囲は、以下の実施例や図示例に限定されるものではなく、幾多の変更及び変形が可能である。

【実施例1】

【0022】

図1は、メモリセルの回路構成図を示している。メモリセルは、各々の出力がメモリセルの列に対応して配置される一対のビット線(BL,BL_N)の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線(BL,BL_N)とインバータの出力との間に設けられた一対のアクセストランジスタ(A0,A1)と、アクセストランジスタ(A0,A1)の導通を制御する1本のワード線(WL)から構成される。ここで、一対のインバータは、P型MOSトランジスタのロードトランジスタ(L0,L1)とN型MOSトランジスタのドライブトランジスタ(D0,D1)で構成されるCMOSインバータである。

メモリセルの内部ノード(N0,N1)には、通常、2本のビット線(BL,BL_N)のうち片側を“Low”、もう一方を“High”として、“Low”又は“High”の電位が保持される。すなわち、メモリセルの内部ノード(N0,N1)は、“0”又は“1”のデータが書き込まれ、データを記憶することになる。

【0023】

本発明のIDチップでは、通常と異なり、両ビット線を同時に“Low”としてメモリセルにデータの書込みを行う。図2は、両ビット線を“Low”にして、ワード線の電位を降下させた場合のメモリセルの内部ノード(N0,N1)の電位の変移を示している。図2(1)に示すように、ワード線(WL)の電位を1.2Vから0Vに変化させた場合、メモリセルの内部ノード(N0)および内部ノード(N1)の電位は“Low”又は“High”のランダムな電位となり、“0”又は“1”のランダムなデータを記憶することが確認できる。

【0024】

このようなランダムな電位の傾向に関し、それぞれのトランジスタの閾値電位(Vth)との相関性について調査を行った。調査結果を図3〜5に示す。図3はロードトランジスタ(L0,L1)の閾値電位(Vth)の高低による内部ノード(N0,N1)の電位分布を示す図であり、図4はドライブトランジスタ(D0,D1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図であり、図5はアクセストランジスタ(A0,A1)の閾値電位の高低による内部ノード(N0,N1)の電位分布を示す図である。

図3と図4には、内部ノード(N0,N1)の電位の傾向に関して、特段、トランジスタの閾値電位(Vth)との相関性は見られなかった。

【0025】

しかしながら、図5には、内部ノード(N0,N1)の電位の傾向に関して、トランジスタの閾値電位(Vth)との相関性が顕著に見られた。アクセストランジスタ(A0,A1)の閾値電位の高低によって、内部ノード(N0,N1)の電位分布に傾向が見られたのである。すなわち、アクセストランジスタ(A0)の閾値が低く、アクセストランジスタ(A1)の閾値が高いほど、内部ノード(N0)に“Low”が記憶されやすい傾向があった。また、逆に、アクセストランジスタ(A0)の閾値が高く、アクセストランジスタ(A1)の閾値が低いほど、内部ノード(N1)に“High”が記憶されやすいという傾向があった。

【0026】

すなわち、図5の左上の領域は、アクセストランジスタ(A0)の閾値が、アクセストランジスタ(A1)よりも低い領域であり、アクセストランジスタ(A0)に接続された内部ノード(N0)にビット線から書き込まれる“Low”の電圧が記憶されやすい傾向を示している。一方、図5の右下の領域はアクセストランジスタ(A0)の閾値が、アクセストランジスタ(A1)よりも高い領域であり、アクセストランジスタ(A1)に接続された内部ノード(N1)にビット線から書き込まれる“Low”の電圧が記憶されやすく、内部ノード(N0)には逆の“Low”が記憶されやすいという傾向を示している。

【0027】

図6は、図5をヒストグラムとして表したものであり、アクセストランジスタ(A0,A1)の閾値電圧の分布とデータ依存性の関係を示したものである。

内部ノード(N0)が“Low”の状態を保持した場合は“0”,“High”の状態を保持した場合は“1”のデータを記憶した状態とする。

データが“0”の場合、アクセストランジスタ(A0)の閾値は低い傾向となり、バラツキを考慮していないモデルの閾値(全トランジスタの閾値の平均値)と比較して−0.0152V低い平均値を示しており、分布の中心が左にシフトしている。一方、アクセストランジスタ(A1)は、平均値が+0.0156V高い値となっている。

また、データが“1”の場合は、データが“0”の場合と逆の傾向を示している。

以上のことは、内部ノード(N0)に記憶されたデータが“Low”であるときと、“High”であるときとでは、アクセストランジスタ(A0,A1)の閾値電圧の分布が異なることを示しているのである。

従って、アクセストランジスタ(A0,A1)の閾値電圧のバラツキによって、メモリセルの内部ノード(N0,N1)に格納されるデータは、ランダムに決定されることになる。

【0028】

図7を参照して、メモリセルの内部ノード(N0,N1)の格納データの傾向について説明する。図7(1)は、アクセストランジスタ(A0)の閾値が低く、アクセストランジスタ(A1)の閾値が高いほど、内部ノード(N0)に“Low”が記憶されやすい傾向があることを示す図である。また、図7(2)は、アクセストランジスタ(A0)の閾値が高く、アクセストランジスタ(A1)の閾値が低いほど、内部ノード(N1)に“High”が記憶されやすいという傾向があることを示す図である。

ワード線(WL)を閉じた後に、メモリセルの内部ノード(N0,N1)に格納されるデータは、アクセストランジスタ(A0,A1)の閾値電圧のバラツキに最も影響を受け、閾値電圧のバラツキに応じてランダムになる。一方、ロードトランジスタ(L0,L1)やドライブトランジスタ(D0,D1)の閾値電圧の影響は少なく、内部ノード(N0,N1)に格納されるデータから、ロードトランジスタ(L0,L1)やドライブトランジスタ(D0,D1)の閾値の予測は困難である。

【0029】

このアクセストランジスタ(A0,A1)の閾値電圧のバラツキによって、128ビットのメモリセルアレイの保持データに固有のバラツキが存在するか否かの調査を実施した。

先ず、128ビットのメモリセルの全メモリセルに“0”データを書き込んだ。そして、“0”データの読み出しを行い、全メモリセルの保持データが初期化されたか否かを確認した。そして、全メモリセルの両ビット線を“Low”とした。全メモリセルの保持データを読み込み、生成されたデータを確認した。電源電圧は1.2Vを使用した。

上記の作業を1つのメモリセルアレイのチップに4回繰り返して、同一チップの生成データの再現性を確認した。結果を図8に示す。

また、上記の作業を異なる4つのメモリセルアレイのチップに対して行い、異なるチップの生成データのバラツキ度合いを確認した。結果を図9に示す。

【0030】

図8に示されるように、同一チップ(#1)に試行を4回繰り返した場合でも、生成データの分布、すなわち“0”と“1”のデータ分布に大きな変化は見られなかった。

一方、図9に示されるように、異なる4つのチップ(#1〜#4)に試行を行った場合は、生成データの分布、すなわち“0”と“1”のデータ分布は大きく相違することが確認できた。

【0031】

図8、図9の“0”と“1”のデータ分布のバラツキ度合いをハミング距離で評価した結果を下記表1にまとめる。

【0032】

【表1】

【0033】

上記の表1から、128ビットのメモリセルアレイにおいて、同一チップと異なるチップとでは、ハミング距離が10倍程度も異なることが確認できた。

すなわち、メモリセルアレイの個々のメモリセルの閾値電圧のバラツキによって決定され生成されるデータは、同一チップにおいては再現性あるデータとなり、また、チップ毎に異なるデータであることになる。

このことは、生成されるデータをチップの固有の識別情報(ID)として扱えることになる。また、ビット長を大きくすることで、生成データのユニーク性が向上し、大量のチップも十分に判別可能になる。

【0034】

図10は、チップIDの生成フローを示している。

(ステップS101)全て或いは一部のメモリセルに対して、“0”

または“1”の初期データを書き込む。

(ステップS103)書き込みを行ったメモリセルに対して、データを読み出し、初期データであることを確認する。

(ステップS105)確認したメモリセルに対して、両ビット線を同時に“Low”としてランダムデータを生成する。

(ステップS107)メモリセルアレイのデータを読み出す。

(ステップS109)読み出したデータをチップの固有の識別情報(チップID)として記憶する。

【0035】

図11は、チップIDの生成用回路の構成図である。

両ビット線“Low”書込みは、各ビット線に放電用のNMOSトランジスタを追加することで実現される。追加したNMOSトランジスタは、BLCTRL信号によって制御され、BLCTRL信号が“High”の時に、両ビット線を放電する。また、ビット線放電用のNMOSトランジスタは、各列にそれぞれ追加され、BLCTRL信号にて一斉に制御を行える構成にしている。

【産業上の利用可能性】

【0036】

本発明は、暗号生成で用いる秘密鍵として利用できる。

【符号の説明】

【0037】

A0,A1 アクセストランジスタ

L1,L2 ロードトランジスタ

D1,D2 ドライブトランジスタ

【特許請求の範囲】

【請求項1】

メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いたことを特徴とするIDチップ。

【請求項2】

前記メモリセルは、各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されることを特徴とする請求項1に記載のIDチップ。

【請求項3】

前記メモリセルは、“0”または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”としてデータ書き込みが行われたものであることを特徴とする請求項2に記載のIDチップ。

【請求項4】

前記一対のアクセストランジスタにおいて、相対的に、一方の閾値が低く、他方の閾値が高い場合、アクセストランジスタの閾値が低い側のインバータに“Low”が記憶されやすく、アクセストランジスタの閾値が高い側のインバータに“High”が記憶されやすいことを特徴とする請求項3に記載のIDチップ。

【請求項5】

各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されるメモリセルがアレイ状に配置されたメモリセルアレイを用いて、

1)全て或いは一部のメモリセルに対して、“0”

または“1”の初期データを書き込み、

2)書き込みを行ったメモリセルに対して、データを読み出し、初期データであることを確認し、

3)確認したメモリセルに対して、両ビット線を同時に“Low”としてデータを生成し、

4)メモリセルアレイのデータを読み出し、

5)読み出したデータを固有の識別情報として記憶する、

ことを特徴とするIDチップの生成方法。

【請求項6】

請求項5に記載のIDチップの生成方法を用いて生成された前記ランダムデータを用いて同一チップか否かを判別する方法であって、

IDチップを構成するメモリセルアレイのデータのハミング距離を測定し、

ハミング距離が所定閾値以内の場合に同一チップと判別するIDチップ判別方法。

【請求項7】

前記ハミング距離の所定閾値は、同一チップの最大ハミング距離と、異なるチップの最小ハミング距離との間の範囲に設定されることを特徴とする請求項6に記載のIDチップ判別方法。

【請求項8】

請求項5〜7のいずれかに記載のIDチップの生成方法を用いて、SRAMメモリセルの一部に固有の識別番号を生成すること。

【請求項1】

メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いたことを特徴とするIDチップ。

【請求項2】

前記メモリセルは、各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されることを特徴とする請求項1に記載のIDチップ。

【請求項3】

前記メモリセルは、“0”または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”としてデータ書き込みが行われたものであることを特徴とする請求項2に記載のIDチップ。

【請求項4】

前記一対のアクセストランジスタにおいて、相対的に、一方の閾値が低く、他方の閾値が高い場合、アクセストランジスタの閾値が低い側のインバータに“Low”が記憶されやすく、アクセストランジスタの閾値が高い側のインバータに“High”が記憶されやすいことを特徴とする請求項3に記載のIDチップ。

【請求項5】

各々の出力がメモリセルの列に対応して配置される一対のビット線の各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビット線とインバータの出力との間に設けられた一対のアクセストランジスタと、該アクセストランジスタの導通を制御する1本のワード線と、から少なくとも構成されるメモリセルがアレイ状に配置されたメモリセルアレイを用いて、

1)全て或いは一部のメモリセルに対して、“0”

または“1”の初期データを書き込み、

2)書き込みを行ったメモリセルに対して、データを読み出し、初期データであることを確認し、

3)確認したメモリセルに対して、両ビット線を同時に“Low”としてデータを生成し、

4)メモリセルアレイのデータを読み出し、

5)読み出したデータを固有の識別情報として記憶する、

ことを特徴とするIDチップの生成方法。

【請求項6】

請求項5に記載のIDチップの生成方法を用いて生成された前記ランダムデータを用いて同一チップか否かを判別する方法であって、

IDチップを構成するメモリセルアレイのデータのハミング距離を測定し、

ハミング距離が所定閾値以内の場合に同一チップと判別するIDチップ判別方法。

【請求項7】

前記ハミング距離の所定閾値は、同一チップの最大ハミング距離と、異なるチップの最小ハミング距離との間の範囲に設定されることを特徴とする請求項6に記載のIDチップ判別方法。

【請求項8】

請求項5〜7のいずれかに記載のIDチップの生成方法を用いて、SRAMメモリセルの一部に固有の識別番号を生成すること。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−73954(P2012−73954A)

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願番号】特願2010−219910(P2010−219910)

【出願日】平成22年9月29日(2010.9.29)

【出願人】(504150450)国立大学法人神戸大学 (421)

【Fターム(参考)】

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願日】平成22年9月29日(2010.9.29)

【出願人】(504150450)国立大学法人神戸大学 (421)

【Fターム(参考)】

[ Back to top ]