メモリデバイス

【課題】 より高いデータの著作権保護をもたらすメモリデバイスを提供する。

【解決手段】 メモリデバイスは、接続されているとホストデバイスと通信し、不揮発性の半導体メモリ31と、ホストデバイスからの要求に基づいて半導体メモリを制御するメモリ制御部72と、無線通信するための無線部22(62)と、管理部71と、を含む。管理部は、データを著作権保護のための手順に従ってメモリデバイスでデータを格納することを管理し、比較部74と更新部75とを含む。比較部は、著作権保護のための更新される可能性を有するパラメータの最新版を無線部を介して外部から取得し、メモリデバイスに保持されているパラメータを最新版のパラメータと比較する。更新部は、保持されているパラメータと最新版のパラメータとが一致していない場合に保持されているパラメータを最新版のパラメータに更新する。

【解決手段】 メモリデバイスは、接続されているとホストデバイスと通信し、不揮発性の半導体メモリ31と、ホストデバイスからの要求に基づいて半導体メモリを制御するメモリ制御部72と、無線通信するための無線部22(62)と、管理部71と、を含む。管理部は、データを著作権保護のための手順に従ってメモリデバイスでデータを格納することを管理し、比較部74と更新部75とを含む。比較部は、著作権保護のための更新される可能性を有するパラメータの最新版を無線部を介して外部から取得し、メモリデバイスに保持されているパラメータを最新版のパラメータと比較する。更新部は、保持されているパラメータと最新版のパラメータとが一致していない場合に保持されているパラメータを最新版のパラメータに更新する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、通信機能を有するメモリデバイスに関する。

【背景技術】

【0002】

データを保存するためのメディアとしてメモリデバイスがある。メモリデバイスによっては、不揮発性の半導体メモリとメモリを制御するためのコントローラとを含んでいる。そのようなメモリデバイスの具体例として、メモリカード、さらに具体的な例としてSDTMカードが挙げられる。このようなメモリカードおよびホストデバイスは、コンテンツデータの記録(書き込み)および再生(読み出し)を、データの著作権を保護するための仕組みに従って行なう。そのような仕組みとして、幾つかの機能が用意されている。しかしながら、そのうちの幾つかの機能は、その性質等に起因して十分に運用されていない場合がある。具体的には、ある特定の機能の運用にはユーザによる特定の処理や操作が必要であるのに対し、ユーザが自発的にそのような処理や操作を行なうことが考え難い。コンテンツデータの保護は、コンテンツホルダーが利益を享受するものであって、ユーザには何らのメリットももたらさないからである。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−28485号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

より高いデータの著作権保護をもたらすメモリデバイスを提供しようとするものである。

【課題を解決するための手段】

【0005】

一実施形態によるメモリデバイスは、メモリデバイスは、接続されているとホストデバイスと通信し、不揮発性の半導体メモリと、ホストデバイスからの要求に基づいて半導体メモリを制御するメモリ制御部と、無線通信するための無線部と、管理部と、を含む。管理部は、データを著作権保護のための手順に従ってメモリデバイスでデータを格納することを管理し、比較部と更新部とを含む。比較部は、著作権保護のための更新される可能性を有するパラメータの最新版を無線部を介して外部から取得し、メモリデバイスに保持されているパラメータを最新版のパラメータと比較する。更新部は、保持されているパラメータと最新版のパラメータとが一致していない場合に保持されているパラメータを最新版のパラメータに更新する。

【図面の簡単な説明】

【0006】

【図1】第1実施形態に係るメモリデバイスの構成を概略的に示している。

【図2】第1実施形態に係るメモリデバイスと管理サーバとの通信の様子を概略的に示している。

【図3】第1実施形態に係るメモリデバイスの別の例の構成を概略的に示している。

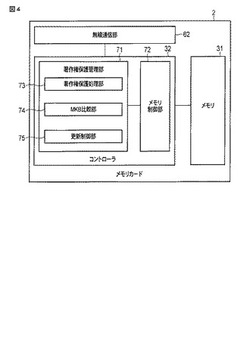

【図4】第1実施形態に係るメモリデバイスの機能ブロックを示している。

【図5】第1実施形態に係るコンテンツの著作権保護のためのキー管理および処理の流れを示している。

【図6】第1実施形態に係るデータ記録および再生のフローチャートである。

【図7】第2実施形態に係るメモリデバイスの機能ブロックを示している。

【図8】第2実施形態に係るデータ記録および再生のフローチャートである。

【図9】第3実施形態に係るメモリデバイスの機能ブロックを示している。

【図10】第3実施形態に係るデータ記録および再生のフローチャートである。

【発明を実施するための形態】

【0007】

メモリデバイスおよびホストデバイスを含んだメモリシステムによる著作権保護を提供するための仕組みとして、メディアバインド、リボケーション、ムーブというものが考えられる。

【0008】

メディアバインドでは、コンテンツデータを記録するホストデバイス(レコーダー)が生成したコンテンツキーを用いてコンデータが暗号化され、暗号化されたコンテンツデータ(以下、コンテンツデータを単にデータと称する場合がある)がメモリデバイスに書き込まれる。コンテンツキーはメディアに固有のID(identification)とホストデバイスに固有のデバイスキーとを用いて生成されるキーを用いて暗号化され、暗号化されたコンテンツキーがメモリデバイスに書き込まれる。メディアバインドされているデータは、別のメモリデバイスにコピーされても復号すなわち再生されることが不能である。コピーされたデータを保持するメモリデバイスからは、データの復号に必要なコンテンツキーを得られないからである。

【0009】

リボケーションとは、特定のデバイスキーを無効化するための仕組みである。ホストデバイスの外部に対して秘密とされているデバイスキーが暴露されると、このデバイスキーを用いて著作権保護機能が無効化される。マスターキーは、著作権保護手順に則ってホストデバイスがメモリデバイスにデータを記録したりデータを再生したりするのに必須である。デバイスキーは、データの復号を含むホストデバイスの内部処理に使用され、外部に対して秘匿されている。しかしながら、不正等によりデバイスキーが外部に暴露されることがある。暴露したデバイスキーを取得した悪意の第三者は、マスターキーの生成を通じて、コンテンツキーをも取得し、コンテンツキーを用いて平文のデータを入手できてしまう。これに対して、リボケーションは、暴露されたデバイスキーのみを無効化することにより、暴露されたデバイスキーを有するホストデバイスによるデータの記録および再生を禁止することができる。リボケーションをサポートするメモリデバイスは、メディアキーブロック(MKB)と称されるデータを保持している。リボケーションをサポートするホストデバイスは、メモリデバイスから読み出されたMKBと自身のデバイスキーとからマスターキーを生成する。デバイスキーが有効であれば、すなわち無効化されていなければ、ホストデバイスはマスターキーの再生に成功する。一方、MKBが、あるホストデバイスのデバイスキーを無効化するように構成されている場合、当該ホストデバイスはマスターキーを生成できず、データの記録および再生のための処理を続行できない。こうしてリボケーションが提供される。

【0010】

このように、リボケーションは、デバイスキーが暴露された際に、暴露されたデバイスキーを無効化することを通じで達成される。そのために、デバイスキーが暴露されたら、MKBを、対応するデバイスキーを無効化するように構成されたものに更新することが必要である。すなわち、MKBが最新に維持されることが重要である。MKBの更新後に製造されるメモリデバイスは、最新のMKBが記録されるので、リボケーションは有効に機能する。一方、流通しているメモリデバイスのMKBの更新は、ユーザがメモリデバイスを例えば公衆に設置されている特定の端末において更新することが考えられる。しかしながら、ユーザがMKBの更新を自発的に行なうことを期待することはできない。なぜなら、ユーザにとって何らのメリットもないからである。

【0011】

以下に、このような知見に基づいて構成された実施形態について図面を参照して説明する。以下の説明において、略同一の機能及び構成を有する構成要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0012】

また、以下に示す各実施形態は、実施形態の技術的思想を具体化するための装置や方法を例示するものであって、実施形態の技術的思想は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。実施形態の技術的思想は、特許請求の範囲において、種々の変更を加えることができる。

【0013】

各機能ブロックは、ハードウェア、コンピュータソフトウェアのいずれかまたは両者を組み合わせたものとして実現することができる。このため、各ブロックがこれらのいずれでもあることが明確となるように、概してそれらの機能の観点から以下に説明する。このような機能が、ハードウェアとして実行されるか、またはソフトウェアとして実行されるかは、具体的な実施態様またはシステム全体に課される設計制約に依存する。当業者は、具体的な実施態様ごとに、種々の方法でこれらの機能を実現し得るが、いずれの実現の手法も実施形態の範囲に含まれる。また、各機能ブロックが、以下の具体例のように区別されていることは必須ではない。例えば、一部の機能が以下の説明において例示されている機能ブロックとは別の機能ブロックによって実行されてもよい。さらに、例示の機能ブロックがさらに細かい機能サブブロックに分割されていてもよい。どの機能ブロックによって特定されるかによって実施形態が限定されるものではない。

【0014】

以下では、メモリデバイスとしてSDTMカードを例に取り説明する。しかしながら、いずれの実施形態も、これらの例に限られない。いずれの実施形態も、データ記録用のメディアであって、不揮発性のメモリと、メモリを制御するコントローラと、無線通信機能と、を有するメモリデバイスをカバーすることに留意されたい。

【0015】

(第1実施形態)

図1は、第1実施形態に係るメモリデバイスの構成を概略的に示している。図1は、また、メモリデバイスにアクセスするホストデバイスも示している。図1に示されているように、ホストデバイス(以下、ホストと称する)1は、MPU(micro processing unit)11、ROM(read only memory)12、RAM(random access memory)13、インターフェース14等を含んでいる。

【0016】

ROM12および(または)RAM13には、ホスト1の動作を実現するための、オペレーティングシステムおよび各種のアプリケーションを含むソフトウェア、ファイルシステム等の制御プログラム(命令)が格納されている。制御プログラムは、ホスト1が電源供給を受けた際等にRAM13上に読み出され、MPU11によって実行されることによりホスト1の全体または一部の動作が制御される。制御プログラムは、ユーザからの指示に従ってメモリカード2へのデータの書き込み、メモリカード2からのデータの読み出しおよびその再生等を行なう。インターフェース14は、ホスト1とメモリカード2との間のインターフェースを取るのに必要なハードウェア、ソフトウェアからなり、ハードウェア上の構成(ピンの配置、数等)を含み、またホスト1とメモリカード2とが準拠している種々の取り決めに則ったコマンドおよび手順を用いてホスト1とメモリカード2との間の通信を担う。インターフェース14のソフトウェア部分は、制御プログラムによってMPU11によって実行されてもよい。インターフェース14は、本例のようにSDTMカードの例については、SDインターフェースに相当する。

【0017】

メモリカード2は、メモリ部21および無線部22を有する。メモリ部21は、メモリ31、およびメモリ31を制御するためのコントローラ32を有する。メモリカード2は、ホスト1からの電源供給が開始すると、初期化動作を行い、次いでホスト1からのアクセスに応じた処理を行う。

【0018】

メモリ31は、データを不揮発に格納し、ページと呼ばれる単位でデータの書き込みおよび読み出しを行い、例えばNAND型フラッシュメモリからなる。ページは、複数の直列接続されたメモリセルの集合のメモリ空間からなり、固有の物理アドレスを割り当てられている。また、メモリ31は、連続する物理アドレスを有する複数のページからなるブロックと呼ばれる単位でデータの消去を行う。各メモリセルは、いわゆる積層ゲート構造のMOSFET(metal oxide semiconductor field effect transistor)からなる。各セルトランジスタは、浮遊ゲート電極に蓄えられる電子の数に応じて閾値電圧が変化し、この閾値電圧の違いに応じた情報を記憶する。セルトランジスタが2つ以上の閾値電圧の異なる状態を取り得る、つまりメモリセルが多値(多ビット)を記憶できるように、メモリ31が構成されていてもよい。

【0019】

コントローラ32は、メモリ31を制御するために設けられている。そのような制御には、メモリ31によるデータの格納状態を管理したり、メモリ31が直接的に実行できないホスト1からの要求をメモリ31に適する形で実現したりすることが含まれる。コントローラ32は、インターフェース41、MPU42、ROM43、RAM44、インターフェース54等を含んでいる。

【0020】

ROM43には、メモリカード2の動作を実現するためのファームウェア(制御プログラム(命令))が格納されている。ファームウェアは、メモリカード2が電源を供給されるとRAM44上に読み出され、MPU42によって実行されることによりホスト1の全体および一部の動作が制御される。そして、MPU42は、ファームウェアに従って所定の処理を実行する。ホスト1からのコマンドに従ってメモリ31に対する所定の処理を実行したりする。

【0021】

インターフェース41は、ホスト1とメモリカード2との間のインターフェースを取るのに必要なハードウェア、ソフトウェアからなる。インターフェース41は、インターフェース14と同様に、ハードウェア上の構成(ピンの配置、数等)を含み、またホスト1とメモリカード2とが準拠している種々の取り決めに則ったコマンドおよび手順を用いてホスト1とメモリカード2との間の通信を担う。より具体的には、インターフェース41は、コントローラ32の動作を司る制御プログラム等からのまたはそれらに向かう要求およびデータと、ホスト1とメモリカード2とが準拠した形態との間の変換を行なう。本例のようにSDTMカードの例については、SDインターフェースに相当する。

【0022】

また、インターフェース45は、コントローラ32とメモリ31との間のインターフェース処理を行う。すなわち、インターフェース54は、MPU42(制御プログラム)からのメモリ31に対する要求を、メモリ31が認識可能な形態を用いて実行する。

【0023】

無線部22は、図2に示されているように、ホスト1中のメモリカード2がMKB管理サーバ51と通信できるように構成されている。より具体的には、無線部22は、メモリカード2が、無線基地局52と無線通信することを可能にするように構成されている。無線基地局52はネットワーク53を介してMKB管理サーバ51と接続され、メモリカード2は無線基地局52およびネットワーク53を介してMKB管理サーバ51と通信する。

【0024】

図1に示されているように、無線部22は、少なくともアンテナ61を含んでいる。また、無線部22は、無線通信部62を含んでいる。無線通信部62は、メモリ部21と通信し、アンテナ61を制御する。より具体的には、無線通信部62は、メモリ部21からの要求に応じてデータ送信要求や問い合わせ等の通信内容を無線基地局52に送信するようにアンテナ61を制御する。また、アンテナ61は無線基地局52からのメモリカード2宛ての通信を受信し、無線通信部62に送る。無線通信部62は、受け取られた通信内容をメモリ部21に送る。無線通信部62は、例えば無線部22中のハードウェア、ソフトウェア、またはそれらの組合せにより実現される。または、無線通信部62は、ROM43に格納されていてRAM44上に読み出されたプログラムがMPU42によって実行されることによって実現されてもよい。

【0025】

また、アンテナ61は、メモリカード2中に設けられていなくてもよい。代わりに、ホスト1にアンテナが設けられていて、メモリカード2はホスト1に挿入されているとアンテナと通信可能に接続されるように構成される。図3は、メモリシステムの別の例を概略的に示している。図3に示されているように、メモリカード2の無線部22は、アンテナ61を含んでいない。一方、ホスト1はアンテナ63を含んでいる。無線通信部62は端子64と接続されており、ホスト1も端子65を有している。端子65は、アンテナ63と接続されており、メモリカード2がホスト1に挿入されると端子64と電気的に接続されるように構成されている。結果、無線通信部62は、ホスト1中のアンテナ63を用いて無線基地局52と無線通信を行なう。端子64および65は、インターフェース14および41に含まれていてもよいし、独立して設けられていてもよい。

【0026】

次に、図4を参照して、メモリカード2によるデータの著作権保護について説明する。図4は、メモリカード2の機能ブロックを示している。図4の各機能ブロックは、コントローラ32において実現され、上記のようにROM43および(または)RAM44上の制御プログラムがMPU42によって実行されることによって具現化される。または、専用のハードウェアや、ハードウェアとソフトウェアの組合せによって実現されてもよい。コントローラ32は、機能ブロックとして、著作権保護管理部71、およびメモリ制御部72を含んでいる。メモリ制御部72は、従来のメモリカード中のメモリコントローラが実行する、ホスト1からの要求を実行するのに必要なあらゆる処理を行なう。より具体的には、例えば、上記のファームウェアを含む各種制御プログラム、ホスト1またはメモリ31とのインターフェース等に関する処理が挙げられる。

【0027】

著作権保護管理部71は、メモリカード2がサポートする著作権保護(CPRM(Content Protection for Recordable Media))の規格に基づいてコンテンツデータを保護するため各種の処理の実行および全体の管理を行なう。このような処理には、少なくともリボケーションが含まれる。以下の説明では、リボケーションに加えて、メディアバインドもサポートする例について説明する。随意により、さらなる仕組みがサポートされていてもよい。著作権保護管理部71は、著作権保護処理部73、MKB比較部74、更新制御部75を有する。著作権保護処理部73、MKB比較部74、更新制御部75は、相互に通信可能に接続されている。

【0028】

著作権保護処理部73は、メモリカード2がサポートする著作権保護の規格に基づいてコンテンツデータを保護するため各種の処理を行なう。処理の具体例は、後に詳述する。MKB比較部72は、メモリカード2に格納されているMKBと、MKB管理サーバ51に格納されているMKBとを比較するための処理を担う。更新制御部73は、必要に応じて、メモリカード2中のMKBを更新するための処理を担う。

【0029】

次に、図5を参照して、著作権保護機能に則ったデータの記録および再生について説明する。図5は、コンテンツの著作権保護のためのキー管理、および処理の流れを示している。図5には、データ記録を行なうホスト(レコーダー)1aおよび再生を行なうホスト(プレイヤー)1bが描かれている。レコーダー1aおよびプレイヤー1bにおける処理は、ホスト1aおよび1b中の著作権保護に関する機能ブロックを用いて行なわれる。一方、レコーダー1aおよびプレイヤー1bとメモリカード2との間の通信に関する処理は、通信に関する機能ブロックにより行われる。このような各機能ブロックは、ホスト1中のMPU42、ROM43、RAM44により実現される。メモリカード2における処理は、メモリ部22により行なわれる。より具体的には、著作権保護に関する処理は著作権保護管理部71(より具体的には著作権保護処理部73)を用いて行なわれ、メモリ21への書き込みまたはメモリ21からの読み出しおよびホスト1との通信はメモリ制御部72を用いて行なわれる。

【0030】

メモリカード2へのデータの記録の開始にあたり、レコーダー1aは、メモリカード2にMKBの送信を要求する。MKBは、ホスト1が、マスターキーを生成するのに必要なデータ(パラメータ)である。マスターキーは、メモリシステムがサポートする著作権保護規格に則ったデータの記録および再生に必須である。レコーダー1aは、自身が保持している自身に固有のデバイスキーとMKBとを用いてマスターキーの生成を試みる。MKBは、特定のデバイスキーと組合せられた場合のみマスターキーが生成されないように構成されることが可能である。このような無効化されたデバイスキー以外のデバイスキーを有するホスト1は、当該MKBを用いてマスターキーを生成することができる。MKBは、メモリカード2に保持されており、メモリ31中のユーザがアクセスできない領域に格納されている。MKBは、後述の技術により最新のものであることが担保されている。MKB送信要求はメモリ制御部72により受け取られる。メモリ制御部72は、MKBをメモリ31から読み出し、これをレコーダー1aに送信する。なお、MKBは、メモリ31に限らず、メモリカード2中の任意の場所に格納されていて構わない。

【0031】

レコーダー1aは、取得されたMKBとデバイスキー(デバイスキー1)とを用いてMKB処理を行なう。レコーダー1aは、有効なデバイスキーを有していれば、MKB処理の結果としてマスターキーKMを得る。レコーダー1aは、以降、マスターキーKMを用いて、データの著作権保護手順に則ってデータをメモリカード2に記録する。より具体的には、レコーダー1aは、マスターキーを用いて、コンテンツデータの暗号化や、コンテンツデータの暗号化に用いたコンテンツキーの暗号化等を行う。マスターキーを用いた著作権保護として、任意のものが使用されることが可能である。しかしながら、以下では、本例に基づいて、SDTMカードの例について説明する。

【0032】

まず、レコーダー1aは、メモリカード2にメディアIDの送信を要求する。メディアIDは、メモリカード2中のユーザがアクセスできない領域に格納されている。メディアID送信要求はメモリ制御部72により受け取られる。メモリ制御部72は、メディアIDをメモリ31から読み出し、これをレコーダー1aに送信する。なお、メディアIDも、メモリ31に限らず、メモリカード2中の任意の場所に格納されていて構わない。レコーダー1aは、取得されたメディアIDとマスターキーKMとを用いて著作権保護手順に則った処理を行なう。図中のGは、メディアIDとマスターキーKMとを用いる特定の関数を表わす。関数Gの実行の結果、レコーダー1aは、メディアユニークキーKmuを得る。

【0033】

レコーダー1aは、また、データの記録に際してコンテンツキーKtを生成する。レコーダー1aは、コンテンツキーKtを用いてコンテンツデータを暗号化する。図中のEは、暗号化処理を意味する。暗号化されたデータは、メモリカード2に書き込まれる。そのために、レコーダー1aは、暗号化されたデータの書き込みをメモリカード2に要求する。要求および暗号化されたデータはメモリ制御部72によって受け取られる。メモリ制御部72は、要求に従ったデータ書き込みを遂行するための指示および書き込まれるデータをインターフェース45を通じてメモリ31に供給する。メモリ31は、指示に従って、供給されたデータを格納する。

【0034】

レコーダー1aは、さらに、コンテンツキーKtをメディアユニークキーKmuを用いて暗号化する。レコーダー1aは、暗号化されたコンテンツキーKteの書き込みをメモリカード2に要求する。メモリ制御部72は、暗号化されたコンテンツキーKteを、メモリ31中のユーザがアクセスできない領域に格納する。または、レコーダー1aは、暗号化されたコンテンツキーKteをさらに暗号化してもよい。その実行のために、メモリカード2は、メディアユニークキーKmuを、メモリ31中のユーザがアクセスできない領域に保持している。保持されているメディアユニークキーKmuは、ホスト1がマスターキーKMとメディアIDとから生成するメディアユニークキーKmuと同じである。レコーダー1aと著作権保護処理部73は、共通のメディアユニークキーKmuを用いてAKE(authentication and key exchange)処理を行なって、一時的な暗号化キーを生成する。レコーダー1aは、この一時キーを用いて、暗号化されたコンテンツキーKteをさらに暗号化する。レコーダー1aは、この2重暗号化されたコンテンツキーの書き込みをメモリカード2に要求する。

【0035】

メモリ制御部72は、2重暗号化されたコンテンツキーを受け取る。次いで、著作権保護処理部73は、一時キーを用いて、2重暗号化されたコンテンツキーを復号し、暗号化されたコンテンツキーKteを得る。図中のDは、復号を意味する。暗号化されたコンテンツキーKteは、メモリ制御部72の指示によって、メモリ31中のユーザがアクセスできない領域に格納される。こうして、著作権保護機能に基づいて暗号化されたデータおよび暗号化されたコンテンツキーKteがメモリカード2に書き込まれる。

【0036】

ホスト1によるメモリカード2からのデータの読み出しについても書き込みの場合と基本的な点は同様である。したがって、以下では、書き込みと異なる点に重点を置きながら概略的な説明にとどめる。プレイヤー(ホスト)1bは、データの書き込みの場合と同様に、メモリカード2からMKBを読み出す。次いで、プレイヤー1bは、自身が保持している自身に固有のデバイスキー(デバイスキー2)とMKBとを用いてマスターキーKMを生成する。デバイスキー2が無効化されていなければ、プレイヤー1bはマスターキーKMの生成に成功するはずである。得られたマスターキーKMは、レコーダー1bによって生成されるマスターキーKMと同じである。

【0037】

次いで、プレイヤー1bは、メモリカード2からメディアIDを読み出し、取得されたメディアIDとデバイスキーKMとからメディアユニークキーKmuを生成する。こうして生成されたメディアユニークキーKmuは、メモリカード2中のものと同じである。

【0038】

プレイヤー1bは、暗号化されたコンテンツキーKteの送信をメモリカード2に要求する。この要求がメモリ制御部72によって受け取られると、プレイヤー1bと著作権保護処理部73は、各々のメディアユニークキーKmuを用いてAKE処理を行なって、一時キーを生成する。著作権保護処理部73は、一時キーを用いて暗号化されたコンテンツキーKteをさらに暗号化する。2重暗号化されたコンテンツキーは、メモリ制御部72によってプレイヤー1bに送信される。プレイヤー1bは、2重暗号化されたコンテンツキーを一時キーを用いて復号して暗号化されたコンテンツキーKteを取得する。さらに、プレイヤー1bは、暗号化されたコンテンツキーKteをメディアユニークキーKmuを用いて復号してコンテンツキーKtを取得する。プレイヤー1bは、メモリカード2に暗号化されたデータの送信を要求する。この要求を受け取ると、メモリ制御部72は、メモリ42からデータを読み出し、プレイヤー1bに送信する。プレイヤー1bは、受け取られたデータをコンテンツキーKtを用いて復号して、平文のコンテンツデータを得る。

【0039】

次に、メモリカードへのデータ記録およびメモリカード中のデータの再生について、図6を参照してさらに説明する。図6は、第1実施形態に係るデータ記録および再生のフローチャートである。以下の説明では、メモリカード2はMKB管理サーバ51とオンライン接続されているものとする。MKBの管理は、著作権保護管理部71(または著作権保護処理部73)により制御される。メモリカード2は、メモリカード2がMKB管理サーバ51とオンライン接続している間に、自身のMKBが最新であるか否かを検査する。この検査は、ホスト2からの著作権保護手順に則ったメモリカード2へのデータ記録要求あるいはメモリカード2中のデータの再生要求の際に行われるようにすることが可能である。

【0040】

図6に示されているように、メモリ制御部72は、MKB送信要求を受信する(ステップS1)。メモリ制御部72は、送信要求を受信すると、著作権保護管理部71にMKBの検査を要求する。

【0041】

ステップS1に続いて、MKBの管理のためのステップS2〜S4が行なわれる。まず、ステップS2において、著作権保護処理部73(またはMKB比較部74)は、無線通信部62を通じてMKB管理サーバ51から最新のMKBを取得する。この取得のために、MKB比較部74は、MKB管理サーバ51に最新MKBの送信を要求する。送信要求は、無線通信部62に供給され、次いで無線通信部62の指示に従ってアンテナ61から送信される。送信要求は、さらに無線基地局およびネットワーク53を介してMKB管理サーバ51に送られる。MKB管理サーバ51は、送信要求を受け取ると、最新のMKBをネットワーク53および無線基地局52を介して、メモリカード2に送信する。最新MKBは、アンテナ61により受け取られ、無線通信部62を介してMKB比較部74により受け取られる。

【0042】

MKB比較部72は、最新のMKBとメモリカード2中のMKBを比較する(ステップS3)。両者が一致していれば、MKB比較部74は、一致の旨を著作権保護処理部73に通知し、MKB検査のための処理は終了する。一方、両者が不一致の場合、MKB比較部74は更新制御部75に結果を報告し、更新制御部75は、報告に応答して、メモリ制御部72を通じてメモリ31中のMKBを最新のMKBに更新する(ステップS4)。こうして、MKB検査のための処理は終了する。こうして、メモリカード2中のMKBが、MKB管理サーバ51中の最新のものと同期化されることが可能となっている。

【0043】

ステップS3またはステップS4に続いて、ステップS5が行なわれる。ステップS5において、メモリ制御部72は、MKB検査の終了を知得するとともにMKBをホストデバイス1に送信し、次いで、デバイスキーおよびMKBを用いて著作権保護手順に則ってデータ記録および再生が行なわれる。

【0044】

MKBの検査は、別のタイミングで行なわれてもよい。例えば、メモリカード2がMKB管理サーバ51とオンライン接続された後、および(または)その後定期的に行なわれるようにすることが可能である。検査のタイミングは、著作権保護管理部73により制御される。この例の場合、著作権保護管理部73の指示により、特定のタイミングで、ステップS2〜S4が実行される。

【0045】

以上説明したように、第1実施形態に係るメモリカードは、無線部22、MKB比較部74、更新制御部75を有する。MKB比較部74は、無線通信を通じて最新のMKBとメモリカード2中のMKBとを比較する。両者が不一致の場合、更新制御部75は、メモリ制御部72を通じて、メモリカード2中のMKBを最新のMKBに更新する。このように、メモリカード2中のMKBは最新のものに同期され、しかもこの同期はメモリカード2によって自律的に行なわれる。したがって、メモリカード2のユーザに頼ることなく、MKBが最新のものに維持される。結果、リボケーションの運用の実効性を高めることを通じてリボケーションを最大限に活用して、より強固な著作権保護を実現できる。

【0046】

(第2実施形態)

第2実施形態は、メモリカード2中のMKBの使用期限に関する。第2実施形態に係るメモリカード2は、第1実施形態と同じハードウェア構成(図1)を有する。ただし、このハードウェア構成によって具現化される機能ブロックは、第1、第2実施形態間で異なる。以下では、機能ブロックについて、第1実施形態と異なる点について説明する。一方、第2実施形態の説明で触れられていない点については、第1実施形態の記述が第2実施形態に全て適用されることに留意されたい。

【0047】

図7は、第2実施形態に係るメモリカード2の機能ブロックを示している。これらの機能ブロックも、コントローラ32において実現され、上記のようにROM43および(または)RAM44上の制御プログラムがMPU42によって実行されることによって具現化される。図7に示されているように、著作権保護管理部71は、第1実施形態で設けられている機能ブロックに加えて、期限比較部81、インターフェース制御部82を有する。

【0048】

期限比較部81は、メモリカード2中のMKBが最後に更新された時点からの経過時間を基準値と比較する。経過時間が基準値を超えている場合、その旨をインターフェース制御部82に通知する。経過時間の比較は、例えば、ホスト1がメモリカード2にMKBの送信を要求した際に行なわれる。インターフェース制御部82は、通知を受け取ると、メモリ制御部72がMKBを出力することを禁止する。

【0049】

次に、図8を参照して、メモリカードへのデータ記録およびメモリカード中のデータの再生について説明する。図8は、第2実施形態に係るデータ記録および再生のフローチャートである。図8に示されているように、メモリ制御部72は、ホスト1からMKBの送信要求を受信する(ステップS1)。ホスト1が、MKBの送信を要求するのは、例えば、ホスト1が著作権保護手順に則ってメモリカード1にデータを記録するときまたはメモリカード1中のデータを再生するときである。メモリ制御部72は、MKB送信要求を受け取ると、期限比較部81にMKB使用期限の検査を要求する。この要求を受けると期限比較部81は、メモリカード2中のMKBが最後に記録された(更新を含む)時刻からの経過時間が基準値を超えているかを検査する(ステップS11)。この基準値は、メモリカード2中(例えば期限比較部81中またはメモリ41中)に不揮発に記憶されている。経過時間が基準値を超えていない場合、メモリカード2中のMKBは使用期限が過ぎていないことを意味する。この結果、メモリ制御部72がMKBを送信することは許可され、メモリ制御部72はMKBをホスト1に送信する(ステップS12)。使用期限が過ぎていないことの通知は、例えば、期限比較部81および(または)インターフェース制御部82がメモリ制御部72に通知することを通じて行なわれる。次いで、デバイスキーおよびMKBを用いて著作権保護手順に則ってデータ記録および再生が行なわれる(ステップS5)。

【0050】

一方、ステップS11において、経過時間が閾値を超えている場合、メモリカード2中のMKBは使用期限が過ぎたことを意味する。そこで、期限比較部81は、MKBの使用期限が過ぎた旨をインターフェース制御部82に通知する。これを受けて、インターフェース制御部82は、メモリ制御部72がMKBを送信することを禁止する(ステップS13)。具体的には、例えばメモリ制御部72はMKBを送信しないか、送信拒否の旨のレスポンスを送信する。こうして、データの記録または再生処理は終了する。または、ステップS13の後に、メモリカード2がMKB管理サーバ51とオンライン接続されていれば、メモリカード2中のMKBの更新が第1実施形態に従って行なわれることが可能である。さらに、ステップS2〜S4は、ステップS13の後に限らず、第1実施形態と同様に、例えば、メモリカード2がMKB管理サーバ51とオンライン接続された後に、および(または)その後定期的に行なってもよい。

【0051】

また、ステップS11の検査は、ホスト1からのMKB送信要求に先立って予め行なわれていてもよい。すなわち、期限比較部81は、メモリカード2への電源供給の開始後および(または)一定の間隔で、メモリカード2中のMKBの最終記録時刻からの経過時間が基準値を超えているかを検査し、その結果のみを、メモリまたはレジスタ等に保持しておく。そして、期限比較部81は、この結果を参照することによってステップS11を実行する。

【0052】

メモリカード2がMKB管理サーバ51とオンライン接続されていれば、第1実施形態に従って、メモリカード2中のMKBは、最新版に自動で更新される。一方、メモリカード2が長きにわたってMKB管理サーバ51とオンライン接続されない状態でいると、MKBは更新されず、その使用期限が過ぎてしまう。そうすると、このメモリカード2は著作権保護手順に則ったデータの記録または再生に使用できないので、ユーザはメモリカード2を定期的にMKB管理サーバ51とオンライン接続する必要に迫られる。こうして、MKBが常に最新であることが担保される。なお、メモリカード2が常にMKB管理サーバ51とオンライン接続された状況で使用されれば、第1実施形態に従ってMKBは最新の状態に保たれるので、ユーザはMKBの使用期限を意識せずにメモリカード2を常に著作権保護手順に則って使用できる。

【0053】

第1実施形態に従ってMKBの自動更新が行なわれる際に、メモリカード2中のMKBが最新版であれば、更新は行なわれない。すると、メモリカード2中のMKBの最終記録時刻は維持され、メモリカード2の次回の使用の際に、MKBの使用期限が過ぎてしまっていることが起こり得る。これを避けるために、第2実施形態では、例えば、第1実施形態に従ってメモリカード2中のMKBが最新版であることが確認された場合でも、メモリカード2中のMKBの最終記録時刻を更新することが可能である。

【0054】

以上説明したように、第2実施形態に係るメモリカードは、第1実施形態の構成に加えて、期限比較部81、インターフェース制御部82を有する。期限比較部81は、メモリカード2中のMKBの最終記録時刻からの経過時刻を自動的に検査する。経過時刻がある基準値を超えていると、インターフェース制御82はメモリ制御部72によるMKBの送信を禁止する。したがって、基準値によって調整される使用期限を過ぎたMKBの使用が禁止される。結果、最新版でないMKBが使用される可能性が減じられ、リボケーションの機能を最大限に活用でき、より強固な著作権保護を実現できる。さらに、第1実施形態と同じ利点を得られる。

【0055】

(第3実施形態)

第3実施形態は、メモリカード2とMKB管理サーバ51とのオンライン接続に関する。第3実施形態に係るメモリカード2は、第1実施形態と同じハードウェア構成(図1)を有する。ただし、このハードウェア構成によって具現化される機能ブロックは、第1、第3実施形態間で異なる。以下では、機能ブロックについて、第1実施形態と異なる点について説明する。一方、第3実施形態の説明で触れられていない点については、第1実施形態の記述が第3実施形態に全て適用されることに留意されたい。

【0056】

図9は、第3実施形態に係るメモリカード2の機能ブロックを示している。これらの機能ブロックも、コントローラ32において実現され、上記のようにROM43および(または)RAM44上の制御プログラムがMPU42によって実行されることによって具現化される。図9に示されているように、著作権保護管理部71は、第1実施形態で設けられている機能ブロックに加えて、インターフェース制御部82、接続判断部91を有する。

【0057】

接続判断部91は、メモリカード2(無線部22)がMKB管理サーバ51とオンライン接続しているかを検査する。接続判断部91は、接続/非接続の状態をインターフェース制御部82に通知する。通知は、逐次的行なわれてもよいし、状態が変化した際に行なわれてもよい。インターフェース制御部82は、接続されている間のみ、メモリ制御部72がMKBをホスト1に送信することを許可する。一方、接続されていない間は、インターフェース制御部82は、メモリ制御部72がMKBをホスト1に送信することを禁止する。

【0058】

次に、図10を参照して、メモリカードへのデータ記録およびメモリカード中のデータの再生について説明する。図10は、第3実施形態に係るデータ記録および再生のフローチャートである。図10に示されているように、メモリ制御部72は、ホスト1からMKBの送信要求を受け取る(ステップS1)。ホスト1が、MKBの送信を要求するのは、例えば、ホスト1が著作権保護手順に則ってメモリカード1にデータを記録するときまたはメモリカード1中のデータを再生するときである。メモリ制御部72は、MKB送信要求を受け取ると、接続判断部91にメモリカード2とMKB管理サーバ51がオンライン接続しているかの検査を要求する。この要求を受けると接続判断部91は、メモリカード2とMKB管理サーバ51がオンライン接続しているかを検査する(ステップS21)。接続判断部91は、検査結果をインターフェース制御部82に通知する。

【0059】

インターフェース制御部82は、オンライン接続があれば、メモリ制御部72がMKBを送信することを許可し、メモリ制御部72はMKBをホスト1に送信する(ステップS12)。次いで、デバイスキーおよびMKBを用いて著作権保護手順に則ってデータ記録および再生が行なわれる(ステップS5)。

【0060】

一方、ステップS21においてオンライン接続がなければ、インターフェース制御部82は、メモリ制御部72がMKBを送信することを禁止する(ステップS13)。具体的には、例えばメモリ制御部72はMKBを送信しないか、送信拒否の旨のレスポンスを送信する。

【0061】

ステップS21の検査は、ホスト1からのMKB送信要求に先立って予め行なわれていてもよい。すなわち、接続判断部91は、メモリカード2への電源供給の開始後および(または)一定の間隔で、メモリカード2がオンライン接続しているかを検査し、その結果のみを、メモリまたはレジスタ等に保持しておく。そして、接続判断部91は、この結果を参照することによってステップS21を実行する。さらに、メモリカード2によるオンライン状態/オフライン状態が切り替わった際に、切り替わった後の状態が保持されるようにしてもよい。

【0062】

メモリカード2がMKB管理サーバ51とオンライン接続されていれば、第1実施形態に従って、メモリカード2中のMKBは、最新版に自動で更新される。一方、メモリカード2が長きにわたってMKB管理サーバ51とオンライン接続されていないと、メモリカード2はMKBをホスト1に送信しない。したがって、最新でないMKBが使用されることが防止される。

【0063】

第3実施形態に第2実施形態の技術が付加されていてもよい。

【0064】

以上説明したように、第3実施形態に係るメモリカードは、第1実施形態の構成に加えて、接続判断部91、インターフェース制御部82を有する。接続判断部91は、メモリカード2がMKB管理サーバ51とオンライン接続しているかを自動的に検査する。オンライン接続されていないと、インターフェース制御82はメモリ制御部72によるMKBの送信を禁じる。このため、メモリカード2中の最新版でないMKBが使用される可能性が排除される。結果、リボケーションの機能を最大限に活用でき、より強固な著作権保護を実現できる。さらに、第1実施形態と同じ利点を得られる。

【0065】

その他、各実施形態は、上記のものに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で、種々に変形することが可能である。さらに、上記実施形態には種々の段階が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の実施形態が抽出され得る。例えば、上記各実施形態に示される全構成要件から幾つかの構成要件が削除されても、この構成要件が削除された構成が実施形態として抽出され得る。

【符号の説明】

【0066】

1…ホストデバイス、2…メモリカード、11…MPU、12…ROM、13…RAM、14…インターフェース、21…メモリ部、22…無線部、31…メモリ、32…コントローラ、41…SDインターフェース、42…MPU、43…ROM、44…RAM、45…メモリ・インターフェース、51…MKB管理サーバ、52…無線基地局、53…ネットワーク、61…アンテナ、62…無線通信部、71…著作権保護管理部、72…メモリ制御部、73…著作権保護処理部、74…MKB比較部、75…更新制御部、81…期限比較部、82…インターフェース制御部、91…接続判断部。

【技術分野】

【0001】

本発明の実施形態は、通信機能を有するメモリデバイスに関する。

【背景技術】

【0002】

データを保存するためのメディアとしてメモリデバイスがある。メモリデバイスによっては、不揮発性の半導体メモリとメモリを制御するためのコントローラとを含んでいる。そのようなメモリデバイスの具体例として、メモリカード、さらに具体的な例としてSDTMカードが挙げられる。このようなメモリカードおよびホストデバイスは、コンテンツデータの記録(書き込み)および再生(読み出し)を、データの著作権を保護するための仕組みに従って行なう。そのような仕組みとして、幾つかの機能が用意されている。しかしながら、そのうちの幾つかの機能は、その性質等に起因して十分に運用されていない場合がある。具体的には、ある特定の機能の運用にはユーザによる特定の処理や操作が必要であるのに対し、ユーザが自発的にそのような処理や操作を行なうことが考え難い。コンテンツデータの保護は、コンテンツホルダーが利益を享受するものであって、ユーザには何らのメリットももたらさないからである。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−28485号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

より高いデータの著作権保護をもたらすメモリデバイスを提供しようとするものである。

【課題を解決するための手段】

【0005】

一実施形態によるメモリデバイスは、メモリデバイスは、接続されているとホストデバイスと通信し、不揮発性の半導体メモリと、ホストデバイスからの要求に基づいて半導体メモリを制御するメモリ制御部と、無線通信するための無線部と、管理部と、を含む。管理部は、データを著作権保護のための手順に従ってメモリデバイスでデータを格納することを管理し、比較部と更新部とを含む。比較部は、著作権保護のための更新される可能性を有するパラメータの最新版を無線部を介して外部から取得し、メモリデバイスに保持されているパラメータを最新版のパラメータと比較する。更新部は、保持されているパラメータと最新版のパラメータとが一致していない場合に保持されているパラメータを最新版のパラメータに更新する。

【図面の簡単な説明】

【0006】

【図1】第1実施形態に係るメモリデバイスの構成を概略的に示している。

【図2】第1実施形態に係るメモリデバイスと管理サーバとの通信の様子を概略的に示している。

【図3】第1実施形態に係るメモリデバイスの別の例の構成を概略的に示している。

【図4】第1実施形態に係るメモリデバイスの機能ブロックを示している。

【図5】第1実施形態に係るコンテンツの著作権保護のためのキー管理および処理の流れを示している。

【図6】第1実施形態に係るデータ記録および再生のフローチャートである。

【図7】第2実施形態に係るメモリデバイスの機能ブロックを示している。

【図8】第2実施形態に係るデータ記録および再生のフローチャートである。

【図9】第3実施形態に係るメモリデバイスの機能ブロックを示している。

【図10】第3実施形態に係るデータ記録および再生のフローチャートである。

【発明を実施するための形態】

【0007】

メモリデバイスおよびホストデバイスを含んだメモリシステムによる著作権保護を提供するための仕組みとして、メディアバインド、リボケーション、ムーブというものが考えられる。

【0008】

メディアバインドでは、コンテンツデータを記録するホストデバイス(レコーダー)が生成したコンテンツキーを用いてコンデータが暗号化され、暗号化されたコンテンツデータ(以下、コンテンツデータを単にデータと称する場合がある)がメモリデバイスに書き込まれる。コンテンツキーはメディアに固有のID(identification)とホストデバイスに固有のデバイスキーとを用いて生成されるキーを用いて暗号化され、暗号化されたコンテンツキーがメモリデバイスに書き込まれる。メディアバインドされているデータは、別のメモリデバイスにコピーされても復号すなわち再生されることが不能である。コピーされたデータを保持するメモリデバイスからは、データの復号に必要なコンテンツキーを得られないからである。

【0009】

リボケーションとは、特定のデバイスキーを無効化するための仕組みである。ホストデバイスの外部に対して秘密とされているデバイスキーが暴露されると、このデバイスキーを用いて著作権保護機能が無効化される。マスターキーは、著作権保護手順に則ってホストデバイスがメモリデバイスにデータを記録したりデータを再生したりするのに必須である。デバイスキーは、データの復号を含むホストデバイスの内部処理に使用され、外部に対して秘匿されている。しかしながら、不正等によりデバイスキーが外部に暴露されることがある。暴露したデバイスキーを取得した悪意の第三者は、マスターキーの生成を通じて、コンテンツキーをも取得し、コンテンツキーを用いて平文のデータを入手できてしまう。これに対して、リボケーションは、暴露されたデバイスキーのみを無効化することにより、暴露されたデバイスキーを有するホストデバイスによるデータの記録および再生を禁止することができる。リボケーションをサポートするメモリデバイスは、メディアキーブロック(MKB)と称されるデータを保持している。リボケーションをサポートするホストデバイスは、メモリデバイスから読み出されたMKBと自身のデバイスキーとからマスターキーを生成する。デバイスキーが有効であれば、すなわち無効化されていなければ、ホストデバイスはマスターキーの再生に成功する。一方、MKBが、あるホストデバイスのデバイスキーを無効化するように構成されている場合、当該ホストデバイスはマスターキーを生成できず、データの記録および再生のための処理を続行できない。こうしてリボケーションが提供される。

【0010】

このように、リボケーションは、デバイスキーが暴露された際に、暴露されたデバイスキーを無効化することを通じで達成される。そのために、デバイスキーが暴露されたら、MKBを、対応するデバイスキーを無効化するように構成されたものに更新することが必要である。すなわち、MKBが最新に維持されることが重要である。MKBの更新後に製造されるメモリデバイスは、最新のMKBが記録されるので、リボケーションは有効に機能する。一方、流通しているメモリデバイスのMKBの更新は、ユーザがメモリデバイスを例えば公衆に設置されている特定の端末において更新することが考えられる。しかしながら、ユーザがMKBの更新を自発的に行なうことを期待することはできない。なぜなら、ユーザにとって何らのメリットもないからである。

【0011】

以下に、このような知見に基づいて構成された実施形態について図面を参照して説明する。以下の説明において、略同一の機能及び構成を有する構成要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0012】

また、以下に示す各実施形態は、実施形態の技術的思想を具体化するための装置や方法を例示するものであって、実施形態の技術的思想は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。実施形態の技術的思想は、特許請求の範囲において、種々の変更を加えることができる。

【0013】

各機能ブロックは、ハードウェア、コンピュータソフトウェアのいずれかまたは両者を組み合わせたものとして実現することができる。このため、各ブロックがこれらのいずれでもあることが明確となるように、概してそれらの機能の観点から以下に説明する。このような機能が、ハードウェアとして実行されるか、またはソフトウェアとして実行されるかは、具体的な実施態様またはシステム全体に課される設計制約に依存する。当業者は、具体的な実施態様ごとに、種々の方法でこれらの機能を実現し得るが、いずれの実現の手法も実施形態の範囲に含まれる。また、各機能ブロックが、以下の具体例のように区別されていることは必須ではない。例えば、一部の機能が以下の説明において例示されている機能ブロックとは別の機能ブロックによって実行されてもよい。さらに、例示の機能ブロックがさらに細かい機能サブブロックに分割されていてもよい。どの機能ブロックによって特定されるかによって実施形態が限定されるものではない。

【0014】

以下では、メモリデバイスとしてSDTMカードを例に取り説明する。しかしながら、いずれの実施形態も、これらの例に限られない。いずれの実施形態も、データ記録用のメディアであって、不揮発性のメモリと、メモリを制御するコントローラと、無線通信機能と、を有するメモリデバイスをカバーすることに留意されたい。

【0015】

(第1実施形態)

図1は、第1実施形態に係るメモリデバイスの構成を概略的に示している。図1は、また、メモリデバイスにアクセスするホストデバイスも示している。図1に示されているように、ホストデバイス(以下、ホストと称する)1は、MPU(micro processing unit)11、ROM(read only memory)12、RAM(random access memory)13、インターフェース14等を含んでいる。

【0016】

ROM12および(または)RAM13には、ホスト1の動作を実現するための、オペレーティングシステムおよび各種のアプリケーションを含むソフトウェア、ファイルシステム等の制御プログラム(命令)が格納されている。制御プログラムは、ホスト1が電源供給を受けた際等にRAM13上に読み出され、MPU11によって実行されることによりホスト1の全体または一部の動作が制御される。制御プログラムは、ユーザからの指示に従ってメモリカード2へのデータの書き込み、メモリカード2からのデータの読み出しおよびその再生等を行なう。インターフェース14は、ホスト1とメモリカード2との間のインターフェースを取るのに必要なハードウェア、ソフトウェアからなり、ハードウェア上の構成(ピンの配置、数等)を含み、またホスト1とメモリカード2とが準拠している種々の取り決めに則ったコマンドおよび手順を用いてホスト1とメモリカード2との間の通信を担う。インターフェース14のソフトウェア部分は、制御プログラムによってMPU11によって実行されてもよい。インターフェース14は、本例のようにSDTMカードの例については、SDインターフェースに相当する。

【0017】

メモリカード2は、メモリ部21および無線部22を有する。メモリ部21は、メモリ31、およびメモリ31を制御するためのコントローラ32を有する。メモリカード2は、ホスト1からの電源供給が開始すると、初期化動作を行い、次いでホスト1からのアクセスに応じた処理を行う。

【0018】

メモリ31は、データを不揮発に格納し、ページと呼ばれる単位でデータの書き込みおよび読み出しを行い、例えばNAND型フラッシュメモリからなる。ページは、複数の直列接続されたメモリセルの集合のメモリ空間からなり、固有の物理アドレスを割り当てられている。また、メモリ31は、連続する物理アドレスを有する複数のページからなるブロックと呼ばれる単位でデータの消去を行う。各メモリセルは、いわゆる積層ゲート構造のMOSFET(metal oxide semiconductor field effect transistor)からなる。各セルトランジスタは、浮遊ゲート電極に蓄えられる電子の数に応じて閾値電圧が変化し、この閾値電圧の違いに応じた情報を記憶する。セルトランジスタが2つ以上の閾値電圧の異なる状態を取り得る、つまりメモリセルが多値(多ビット)を記憶できるように、メモリ31が構成されていてもよい。

【0019】

コントローラ32は、メモリ31を制御するために設けられている。そのような制御には、メモリ31によるデータの格納状態を管理したり、メモリ31が直接的に実行できないホスト1からの要求をメモリ31に適する形で実現したりすることが含まれる。コントローラ32は、インターフェース41、MPU42、ROM43、RAM44、インターフェース54等を含んでいる。

【0020】

ROM43には、メモリカード2の動作を実現するためのファームウェア(制御プログラム(命令))が格納されている。ファームウェアは、メモリカード2が電源を供給されるとRAM44上に読み出され、MPU42によって実行されることによりホスト1の全体および一部の動作が制御される。そして、MPU42は、ファームウェアに従って所定の処理を実行する。ホスト1からのコマンドに従ってメモリ31に対する所定の処理を実行したりする。

【0021】

インターフェース41は、ホスト1とメモリカード2との間のインターフェースを取るのに必要なハードウェア、ソフトウェアからなる。インターフェース41は、インターフェース14と同様に、ハードウェア上の構成(ピンの配置、数等)を含み、またホスト1とメモリカード2とが準拠している種々の取り決めに則ったコマンドおよび手順を用いてホスト1とメモリカード2との間の通信を担う。より具体的には、インターフェース41は、コントローラ32の動作を司る制御プログラム等からのまたはそれらに向かう要求およびデータと、ホスト1とメモリカード2とが準拠した形態との間の変換を行なう。本例のようにSDTMカードの例については、SDインターフェースに相当する。

【0022】

また、インターフェース45は、コントローラ32とメモリ31との間のインターフェース処理を行う。すなわち、インターフェース54は、MPU42(制御プログラム)からのメモリ31に対する要求を、メモリ31が認識可能な形態を用いて実行する。

【0023】

無線部22は、図2に示されているように、ホスト1中のメモリカード2がMKB管理サーバ51と通信できるように構成されている。より具体的には、無線部22は、メモリカード2が、無線基地局52と無線通信することを可能にするように構成されている。無線基地局52はネットワーク53を介してMKB管理サーバ51と接続され、メモリカード2は無線基地局52およびネットワーク53を介してMKB管理サーバ51と通信する。

【0024】

図1に示されているように、無線部22は、少なくともアンテナ61を含んでいる。また、無線部22は、無線通信部62を含んでいる。無線通信部62は、メモリ部21と通信し、アンテナ61を制御する。より具体的には、無線通信部62は、メモリ部21からの要求に応じてデータ送信要求や問い合わせ等の通信内容を無線基地局52に送信するようにアンテナ61を制御する。また、アンテナ61は無線基地局52からのメモリカード2宛ての通信を受信し、無線通信部62に送る。無線通信部62は、受け取られた通信内容をメモリ部21に送る。無線通信部62は、例えば無線部22中のハードウェア、ソフトウェア、またはそれらの組合せにより実現される。または、無線通信部62は、ROM43に格納されていてRAM44上に読み出されたプログラムがMPU42によって実行されることによって実現されてもよい。

【0025】

また、アンテナ61は、メモリカード2中に設けられていなくてもよい。代わりに、ホスト1にアンテナが設けられていて、メモリカード2はホスト1に挿入されているとアンテナと通信可能に接続されるように構成される。図3は、メモリシステムの別の例を概略的に示している。図3に示されているように、メモリカード2の無線部22は、アンテナ61を含んでいない。一方、ホスト1はアンテナ63を含んでいる。無線通信部62は端子64と接続されており、ホスト1も端子65を有している。端子65は、アンテナ63と接続されており、メモリカード2がホスト1に挿入されると端子64と電気的に接続されるように構成されている。結果、無線通信部62は、ホスト1中のアンテナ63を用いて無線基地局52と無線通信を行なう。端子64および65は、インターフェース14および41に含まれていてもよいし、独立して設けられていてもよい。

【0026】

次に、図4を参照して、メモリカード2によるデータの著作権保護について説明する。図4は、メモリカード2の機能ブロックを示している。図4の各機能ブロックは、コントローラ32において実現され、上記のようにROM43および(または)RAM44上の制御プログラムがMPU42によって実行されることによって具現化される。または、専用のハードウェアや、ハードウェアとソフトウェアの組合せによって実現されてもよい。コントローラ32は、機能ブロックとして、著作権保護管理部71、およびメモリ制御部72を含んでいる。メモリ制御部72は、従来のメモリカード中のメモリコントローラが実行する、ホスト1からの要求を実行するのに必要なあらゆる処理を行なう。より具体的には、例えば、上記のファームウェアを含む各種制御プログラム、ホスト1またはメモリ31とのインターフェース等に関する処理が挙げられる。

【0027】

著作権保護管理部71は、メモリカード2がサポートする著作権保護(CPRM(Content Protection for Recordable Media))の規格に基づいてコンテンツデータを保護するため各種の処理の実行および全体の管理を行なう。このような処理には、少なくともリボケーションが含まれる。以下の説明では、リボケーションに加えて、メディアバインドもサポートする例について説明する。随意により、さらなる仕組みがサポートされていてもよい。著作権保護管理部71は、著作権保護処理部73、MKB比較部74、更新制御部75を有する。著作権保護処理部73、MKB比較部74、更新制御部75は、相互に通信可能に接続されている。

【0028】

著作権保護処理部73は、メモリカード2がサポートする著作権保護の規格に基づいてコンテンツデータを保護するため各種の処理を行なう。処理の具体例は、後に詳述する。MKB比較部72は、メモリカード2に格納されているMKBと、MKB管理サーバ51に格納されているMKBとを比較するための処理を担う。更新制御部73は、必要に応じて、メモリカード2中のMKBを更新するための処理を担う。

【0029】

次に、図5を参照して、著作権保護機能に則ったデータの記録および再生について説明する。図5は、コンテンツの著作権保護のためのキー管理、および処理の流れを示している。図5には、データ記録を行なうホスト(レコーダー)1aおよび再生を行なうホスト(プレイヤー)1bが描かれている。レコーダー1aおよびプレイヤー1bにおける処理は、ホスト1aおよび1b中の著作権保護に関する機能ブロックを用いて行なわれる。一方、レコーダー1aおよびプレイヤー1bとメモリカード2との間の通信に関する処理は、通信に関する機能ブロックにより行われる。このような各機能ブロックは、ホスト1中のMPU42、ROM43、RAM44により実現される。メモリカード2における処理は、メモリ部22により行なわれる。より具体的には、著作権保護に関する処理は著作権保護管理部71(より具体的には著作権保護処理部73)を用いて行なわれ、メモリ21への書き込みまたはメモリ21からの読み出しおよびホスト1との通信はメモリ制御部72を用いて行なわれる。

【0030】

メモリカード2へのデータの記録の開始にあたり、レコーダー1aは、メモリカード2にMKBの送信を要求する。MKBは、ホスト1が、マスターキーを生成するのに必要なデータ(パラメータ)である。マスターキーは、メモリシステムがサポートする著作権保護規格に則ったデータの記録および再生に必須である。レコーダー1aは、自身が保持している自身に固有のデバイスキーとMKBとを用いてマスターキーの生成を試みる。MKBは、特定のデバイスキーと組合せられた場合のみマスターキーが生成されないように構成されることが可能である。このような無効化されたデバイスキー以外のデバイスキーを有するホスト1は、当該MKBを用いてマスターキーを生成することができる。MKBは、メモリカード2に保持されており、メモリ31中のユーザがアクセスできない領域に格納されている。MKBは、後述の技術により最新のものであることが担保されている。MKB送信要求はメモリ制御部72により受け取られる。メモリ制御部72は、MKBをメモリ31から読み出し、これをレコーダー1aに送信する。なお、MKBは、メモリ31に限らず、メモリカード2中の任意の場所に格納されていて構わない。

【0031】

レコーダー1aは、取得されたMKBとデバイスキー(デバイスキー1)とを用いてMKB処理を行なう。レコーダー1aは、有効なデバイスキーを有していれば、MKB処理の結果としてマスターキーKMを得る。レコーダー1aは、以降、マスターキーKMを用いて、データの著作権保護手順に則ってデータをメモリカード2に記録する。より具体的には、レコーダー1aは、マスターキーを用いて、コンテンツデータの暗号化や、コンテンツデータの暗号化に用いたコンテンツキーの暗号化等を行う。マスターキーを用いた著作権保護として、任意のものが使用されることが可能である。しかしながら、以下では、本例に基づいて、SDTMカードの例について説明する。

【0032】

まず、レコーダー1aは、メモリカード2にメディアIDの送信を要求する。メディアIDは、メモリカード2中のユーザがアクセスできない領域に格納されている。メディアID送信要求はメモリ制御部72により受け取られる。メモリ制御部72は、メディアIDをメモリ31から読み出し、これをレコーダー1aに送信する。なお、メディアIDも、メモリ31に限らず、メモリカード2中の任意の場所に格納されていて構わない。レコーダー1aは、取得されたメディアIDとマスターキーKMとを用いて著作権保護手順に則った処理を行なう。図中のGは、メディアIDとマスターキーKMとを用いる特定の関数を表わす。関数Gの実行の結果、レコーダー1aは、メディアユニークキーKmuを得る。

【0033】

レコーダー1aは、また、データの記録に際してコンテンツキーKtを生成する。レコーダー1aは、コンテンツキーKtを用いてコンテンツデータを暗号化する。図中のEは、暗号化処理を意味する。暗号化されたデータは、メモリカード2に書き込まれる。そのために、レコーダー1aは、暗号化されたデータの書き込みをメモリカード2に要求する。要求および暗号化されたデータはメモリ制御部72によって受け取られる。メモリ制御部72は、要求に従ったデータ書き込みを遂行するための指示および書き込まれるデータをインターフェース45を通じてメモリ31に供給する。メモリ31は、指示に従って、供給されたデータを格納する。

【0034】

レコーダー1aは、さらに、コンテンツキーKtをメディアユニークキーKmuを用いて暗号化する。レコーダー1aは、暗号化されたコンテンツキーKteの書き込みをメモリカード2に要求する。メモリ制御部72は、暗号化されたコンテンツキーKteを、メモリ31中のユーザがアクセスできない領域に格納する。または、レコーダー1aは、暗号化されたコンテンツキーKteをさらに暗号化してもよい。その実行のために、メモリカード2は、メディアユニークキーKmuを、メモリ31中のユーザがアクセスできない領域に保持している。保持されているメディアユニークキーKmuは、ホスト1がマスターキーKMとメディアIDとから生成するメディアユニークキーKmuと同じである。レコーダー1aと著作権保護処理部73は、共通のメディアユニークキーKmuを用いてAKE(authentication and key exchange)処理を行なって、一時的な暗号化キーを生成する。レコーダー1aは、この一時キーを用いて、暗号化されたコンテンツキーKteをさらに暗号化する。レコーダー1aは、この2重暗号化されたコンテンツキーの書き込みをメモリカード2に要求する。

【0035】

メモリ制御部72は、2重暗号化されたコンテンツキーを受け取る。次いで、著作権保護処理部73は、一時キーを用いて、2重暗号化されたコンテンツキーを復号し、暗号化されたコンテンツキーKteを得る。図中のDは、復号を意味する。暗号化されたコンテンツキーKteは、メモリ制御部72の指示によって、メモリ31中のユーザがアクセスできない領域に格納される。こうして、著作権保護機能に基づいて暗号化されたデータおよび暗号化されたコンテンツキーKteがメモリカード2に書き込まれる。

【0036】

ホスト1によるメモリカード2からのデータの読み出しについても書き込みの場合と基本的な点は同様である。したがって、以下では、書き込みと異なる点に重点を置きながら概略的な説明にとどめる。プレイヤー(ホスト)1bは、データの書き込みの場合と同様に、メモリカード2からMKBを読み出す。次いで、プレイヤー1bは、自身が保持している自身に固有のデバイスキー(デバイスキー2)とMKBとを用いてマスターキーKMを生成する。デバイスキー2が無効化されていなければ、プレイヤー1bはマスターキーKMの生成に成功するはずである。得られたマスターキーKMは、レコーダー1bによって生成されるマスターキーKMと同じである。

【0037】

次いで、プレイヤー1bは、メモリカード2からメディアIDを読み出し、取得されたメディアIDとデバイスキーKMとからメディアユニークキーKmuを生成する。こうして生成されたメディアユニークキーKmuは、メモリカード2中のものと同じである。

【0038】

プレイヤー1bは、暗号化されたコンテンツキーKteの送信をメモリカード2に要求する。この要求がメモリ制御部72によって受け取られると、プレイヤー1bと著作権保護処理部73は、各々のメディアユニークキーKmuを用いてAKE処理を行なって、一時キーを生成する。著作権保護処理部73は、一時キーを用いて暗号化されたコンテンツキーKteをさらに暗号化する。2重暗号化されたコンテンツキーは、メモリ制御部72によってプレイヤー1bに送信される。プレイヤー1bは、2重暗号化されたコンテンツキーを一時キーを用いて復号して暗号化されたコンテンツキーKteを取得する。さらに、プレイヤー1bは、暗号化されたコンテンツキーKteをメディアユニークキーKmuを用いて復号してコンテンツキーKtを取得する。プレイヤー1bは、メモリカード2に暗号化されたデータの送信を要求する。この要求を受け取ると、メモリ制御部72は、メモリ42からデータを読み出し、プレイヤー1bに送信する。プレイヤー1bは、受け取られたデータをコンテンツキーKtを用いて復号して、平文のコンテンツデータを得る。

【0039】

次に、メモリカードへのデータ記録およびメモリカード中のデータの再生について、図6を参照してさらに説明する。図6は、第1実施形態に係るデータ記録および再生のフローチャートである。以下の説明では、メモリカード2はMKB管理サーバ51とオンライン接続されているものとする。MKBの管理は、著作権保護管理部71(または著作権保護処理部73)により制御される。メモリカード2は、メモリカード2がMKB管理サーバ51とオンライン接続している間に、自身のMKBが最新であるか否かを検査する。この検査は、ホスト2からの著作権保護手順に則ったメモリカード2へのデータ記録要求あるいはメモリカード2中のデータの再生要求の際に行われるようにすることが可能である。

【0040】

図6に示されているように、メモリ制御部72は、MKB送信要求を受信する(ステップS1)。メモリ制御部72は、送信要求を受信すると、著作権保護管理部71にMKBの検査を要求する。

【0041】

ステップS1に続いて、MKBの管理のためのステップS2〜S4が行なわれる。まず、ステップS2において、著作権保護処理部73(またはMKB比較部74)は、無線通信部62を通じてMKB管理サーバ51から最新のMKBを取得する。この取得のために、MKB比較部74は、MKB管理サーバ51に最新MKBの送信を要求する。送信要求は、無線通信部62に供給され、次いで無線通信部62の指示に従ってアンテナ61から送信される。送信要求は、さらに無線基地局およびネットワーク53を介してMKB管理サーバ51に送られる。MKB管理サーバ51は、送信要求を受け取ると、最新のMKBをネットワーク53および無線基地局52を介して、メモリカード2に送信する。最新MKBは、アンテナ61により受け取られ、無線通信部62を介してMKB比較部74により受け取られる。

【0042】

MKB比較部72は、最新のMKBとメモリカード2中のMKBを比較する(ステップS3)。両者が一致していれば、MKB比較部74は、一致の旨を著作権保護処理部73に通知し、MKB検査のための処理は終了する。一方、両者が不一致の場合、MKB比較部74は更新制御部75に結果を報告し、更新制御部75は、報告に応答して、メモリ制御部72を通じてメモリ31中のMKBを最新のMKBに更新する(ステップS4)。こうして、MKB検査のための処理は終了する。こうして、メモリカード2中のMKBが、MKB管理サーバ51中の最新のものと同期化されることが可能となっている。

【0043】

ステップS3またはステップS4に続いて、ステップS5が行なわれる。ステップS5において、メモリ制御部72は、MKB検査の終了を知得するとともにMKBをホストデバイス1に送信し、次いで、デバイスキーおよびMKBを用いて著作権保護手順に則ってデータ記録および再生が行なわれる。

【0044】

MKBの検査は、別のタイミングで行なわれてもよい。例えば、メモリカード2がMKB管理サーバ51とオンライン接続された後、および(または)その後定期的に行なわれるようにすることが可能である。検査のタイミングは、著作権保護管理部73により制御される。この例の場合、著作権保護管理部73の指示により、特定のタイミングで、ステップS2〜S4が実行される。

【0045】

以上説明したように、第1実施形態に係るメモリカードは、無線部22、MKB比較部74、更新制御部75を有する。MKB比較部74は、無線通信を通じて最新のMKBとメモリカード2中のMKBとを比較する。両者が不一致の場合、更新制御部75は、メモリ制御部72を通じて、メモリカード2中のMKBを最新のMKBに更新する。このように、メモリカード2中のMKBは最新のものに同期され、しかもこの同期はメモリカード2によって自律的に行なわれる。したがって、メモリカード2のユーザに頼ることなく、MKBが最新のものに維持される。結果、リボケーションの運用の実効性を高めることを通じてリボケーションを最大限に活用して、より強固な著作権保護を実現できる。

【0046】

(第2実施形態)

第2実施形態は、メモリカード2中のMKBの使用期限に関する。第2実施形態に係るメモリカード2は、第1実施形態と同じハードウェア構成(図1)を有する。ただし、このハードウェア構成によって具現化される機能ブロックは、第1、第2実施形態間で異なる。以下では、機能ブロックについて、第1実施形態と異なる点について説明する。一方、第2実施形態の説明で触れられていない点については、第1実施形態の記述が第2実施形態に全て適用されることに留意されたい。

【0047】

図7は、第2実施形態に係るメモリカード2の機能ブロックを示している。これらの機能ブロックも、コントローラ32において実現され、上記のようにROM43および(または)RAM44上の制御プログラムがMPU42によって実行されることによって具現化される。図7に示されているように、著作権保護管理部71は、第1実施形態で設けられている機能ブロックに加えて、期限比較部81、インターフェース制御部82を有する。

【0048】

期限比較部81は、メモリカード2中のMKBが最後に更新された時点からの経過時間を基準値と比較する。経過時間が基準値を超えている場合、その旨をインターフェース制御部82に通知する。経過時間の比較は、例えば、ホスト1がメモリカード2にMKBの送信を要求した際に行なわれる。インターフェース制御部82は、通知を受け取ると、メモリ制御部72がMKBを出力することを禁止する。

【0049】

次に、図8を参照して、メモリカードへのデータ記録およびメモリカード中のデータの再生について説明する。図8は、第2実施形態に係るデータ記録および再生のフローチャートである。図8に示されているように、メモリ制御部72は、ホスト1からMKBの送信要求を受信する(ステップS1)。ホスト1が、MKBの送信を要求するのは、例えば、ホスト1が著作権保護手順に則ってメモリカード1にデータを記録するときまたはメモリカード1中のデータを再生するときである。メモリ制御部72は、MKB送信要求を受け取ると、期限比較部81にMKB使用期限の検査を要求する。この要求を受けると期限比較部81は、メモリカード2中のMKBが最後に記録された(更新を含む)時刻からの経過時間が基準値を超えているかを検査する(ステップS11)。この基準値は、メモリカード2中(例えば期限比較部81中またはメモリ41中)に不揮発に記憶されている。経過時間が基準値を超えていない場合、メモリカード2中のMKBは使用期限が過ぎていないことを意味する。この結果、メモリ制御部72がMKBを送信することは許可され、メモリ制御部72はMKBをホスト1に送信する(ステップS12)。使用期限が過ぎていないことの通知は、例えば、期限比較部81および(または)インターフェース制御部82がメモリ制御部72に通知することを通じて行なわれる。次いで、デバイスキーおよびMKBを用いて著作権保護手順に則ってデータ記録および再生が行なわれる(ステップS5)。

【0050】

一方、ステップS11において、経過時間が閾値を超えている場合、メモリカード2中のMKBは使用期限が過ぎたことを意味する。そこで、期限比較部81は、MKBの使用期限が過ぎた旨をインターフェース制御部82に通知する。これを受けて、インターフェース制御部82は、メモリ制御部72がMKBを送信することを禁止する(ステップS13)。具体的には、例えばメモリ制御部72はMKBを送信しないか、送信拒否の旨のレスポンスを送信する。こうして、データの記録または再生処理は終了する。または、ステップS13の後に、メモリカード2がMKB管理サーバ51とオンライン接続されていれば、メモリカード2中のMKBの更新が第1実施形態に従って行なわれることが可能である。さらに、ステップS2〜S4は、ステップS13の後に限らず、第1実施形態と同様に、例えば、メモリカード2がMKB管理サーバ51とオンライン接続された後に、および(または)その後定期的に行なってもよい。

【0051】

また、ステップS11の検査は、ホスト1からのMKB送信要求に先立って予め行なわれていてもよい。すなわち、期限比較部81は、メモリカード2への電源供給の開始後および(または)一定の間隔で、メモリカード2中のMKBの最終記録時刻からの経過時間が基準値を超えているかを検査し、その結果のみを、メモリまたはレジスタ等に保持しておく。そして、期限比較部81は、この結果を参照することによってステップS11を実行する。

【0052】

メモリカード2がMKB管理サーバ51とオンライン接続されていれば、第1実施形態に従って、メモリカード2中のMKBは、最新版に自動で更新される。一方、メモリカード2が長きにわたってMKB管理サーバ51とオンライン接続されない状態でいると、MKBは更新されず、その使用期限が過ぎてしまう。そうすると、このメモリカード2は著作権保護手順に則ったデータの記録または再生に使用できないので、ユーザはメモリカード2を定期的にMKB管理サーバ51とオンライン接続する必要に迫られる。こうして、MKBが常に最新であることが担保される。なお、メモリカード2が常にMKB管理サーバ51とオンライン接続された状況で使用されれば、第1実施形態に従ってMKBは最新の状態に保たれるので、ユーザはMKBの使用期限を意識せずにメモリカード2を常に著作権保護手順に則って使用できる。

【0053】

第1実施形態に従ってMKBの自動更新が行なわれる際に、メモリカード2中のMKBが最新版であれば、更新は行なわれない。すると、メモリカード2中のMKBの最終記録時刻は維持され、メモリカード2の次回の使用の際に、MKBの使用期限が過ぎてしまっていることが起こり得る。これを避けるために、第2実施形態では、例えば、第1実施形態に従ってメモリカード2中のMKBが最新版であることが確認された場合でも、メモリカード2中のMKBの最終記録時刻を更新することが可能である。

【0054】

以上説明したように、第2実施形態に係るメモリカードは、第1実施形態の構成に加えて、期限比較部81、インターフェース制御部82を有する。期限比較部81は、メモリカード2中のMKBの最終記録時刻からの経過時刻を自動的に検査する。経過時刻がある基準値を超えていると、インターフェース制御82はメモリ制御部72によるMKBの送信を禁止する。したがって、基準値によって調整される使用期限を過ぎたMKBの使用が禁止される。結果、最新版でないMKBが使用される可能性が減じられ、リボケーションの機能を最大限に活用でき、より強固な著作権保護を実現できる。さらに、第1実施形態と同じ利点を得られる。

【0055】

(第3実施形態)

第3実施形態は、メモリカード2とMKB管理サーバ51とのオンライン接続に関する。第3実施形態に係るメモリカード2は、第1実施形態と同じハードウェア構成(図1)を有する。ただし、このハードウェア構成によって具現化される機能ブロックは、第1、第3実施形態間で異なる。以下では、機能ブロックについて、第1実施形態と異なる点について説明する。一方、第3実施形態の説明で触れられていない点については、第1実施形態の記述が第3実施形態に全て適用されることに留意されたい。

【0056】

図9は、第3実施形態に係るメモリカード2の機能ブロックを示している。これらの機能ブロックも、コントローラ32において実現され、上記のようにROM43および(または)RAM44上の制御プログラムがMPU42によって実行されることによって具現化される。図9に示されているように、著作権保護管理部71は、第1実施形態で設けられている機能ブロックに加えて、インターフェース制御部82、接続判断部91を有する。

【0057】

接続判断部91は、メモリカード2(無線部22)がMKB管理サーバ51とオンライン接続しているかを検査する。接続判断部91は、接続/非接続の状態をインターフェース制御部82に通知する。通知は、逐次的行なわれてもよいし、状態が変化した際に行なわれてもよい。インターフェース制御部82は、接続されている間のみ、メモリ制御部72がMKBをホスト1に送信することを許可する。一方、接続されていない間は、インターフェース制御部82は、メモリ制御部72がMKBをホスト1に送信することを禁止する。

【0058】

次に、図10を参照して、メモリカードへのデータ記録およびメモリカード中のデータの再生について説明する。図10は、第3実施形態に係るデータ記録および再生のフローチャートである。図10に示されているように、メモリ制御部72は、ホスト1からMKBの送信要求を受け取る(ステップS1)。ホスト1が、MKBの送信を要求するのは、例えば、ホスト1が著作権保護手順に則ってメモリカード1にデータを記録するときまたはメモリカード1中のデータを再生するときである。メモリ制御部72は、MKB送信要求を受け取ると、接続判断部91にメモリカード2とMKB管理サーバ51がオンライン接続しているかの検査を要求する。この要求を受けると接続判断部91は、メモリカード2とMKB管理サーバ51がオンライン接続しているかを検査する(ステップS21)。接続判断部91は、検査結果をインターフェース制御部82に通知する。

【0059】

インターフェース制御部82は、オンライン接続があれば、メモリ制御部72がMKBを送信することを許可し、メモリ制御部72はMKBをホスト1に送信する(ステップS12)。次いで、デバイスキーおよびMKBを用いて著作権保護手順に則ってデータ記録および再生が行なわれる(ステップS5)。

【0060】

一方、ステップS21においてオンライン接続がなければ、インターフェース制御部82は、メモリ制御部72がMKBを送信することを禁止する(ステップS13)。具体的には、例えばメモリ制御部72はMKBを送信しないか、送信拒否の旨のレスポンスを送信する。

【0061】

ステップS21の検査は、ホスト1からのMKB送信要求に先立って予め行なわれていてもよい。すなわち、接続判断部91は、メモリカード2への電源供給の開始後および(または)一定の間隔で、メモリカード2がオンライン接続しているかを検査し、その結果のみを、メモリまたはレジスタ等に保持しておく。そして、接続判断部91は、この結果を参照することによってステップS21を実行する。さらに、メモリカード2によるオンライン状態/オフライン状態が切り替わった際に、切り替わった後の状態が保持されるようにしてもよい。

【0062】

メモリカード2がMKB管理サーバ51とオンライン接続されていれば、第1実施形態に従って、メモリカード2中のMKBは、最新版に自動で更新される。一方、メモリカード2が長きにわたってMKB管理サーバ51とオンライン接続されていないと、メモリカード2はMKBをホスト1に送信しない。したがって、最新でないMKBが使用されることが防止される。

【0063】

第3実施形態に第2実施形態の技術が付加されていてもよい。

【0064】

以上説明したように、第3実施形態に係るメモリカードは、第1実施形態の構成に加えて、接続判断部91、インターフェース制御部82を有する。接続判断部91は、メモリカード2がMKB管理サーバ51とオンライン接続しているかを自動的に検査する。オンライン接続されていないと、インターフェース制御82はメモリ制御部72によるMKBの送信を禁じる。このため、メモリカード2中の最新版でないMKBが使用される可能性が排除される。結果、リボケーションの機能を最大限に活用でき、より強固な著作権保護を実現できる。さらに、第1実施形態と同じ利点を得られる。

【0065】

その他、各実施形態は、上記のものに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で、種々に変形することが可能である。さらに、上記実施形態には種々の段階が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の実施形態が抽出され得る。例えば、上記各実施形態に示される全構成要件から幾つかの構成要件が削除されても、この構成要件が削除された構成が実施形態として抽出され得る。

【符号の説明】

【0066】

1…ホストデバイス、2…メモリカード、11…MPU、12…ROM、13…RAM、14…インターフェース、21…メモリ部、22…無線部、31…メモリ、32…コントローラ、41…SDインターフェース、42…MPU、43…ROM、44…RAM、45…メモリ・インターフェース、51…MKB管理サーバ、52…無線基地局、53…ネットワーク、61…アンテナ、62…無線通信部、71…著作権保護管理部、72…メモリ制御部、73…著作権保護処理部、74…MKB比較部、75…更新制御部、81…期限比較部、82…インターフェース制御部、91…接続判断部。

【特許請求の範囲】

【請求項1】

接続されているとホストデバイスと通信するメモリデバイスであって、

不揮発性の半導体メモリと、

前記ホストデバイスからの要求に基づいて前記半導体メモリを制御するメモリ制御部と、

無線通信するための無線部と、

データを著作権保護のための手順に従って前記メモリデバイスでデータを格納することを管理する管理部であって、著作権保護のための更新される可能性を有するパラメータの最新版を前記無線部を介して外部から取得し、前記メモリデバイスに保持されている前記パラメータを前記最新版の前記パラメータと比較する比較部を含み、前記保持されている前記パラメータと前記最新版の前記パラメータとが一致していない場合に前記保持されている前記パラメータを前記最新版の前記パラメータに更新する更新部を含む、管理部と、

を具備することを特徴とするメモリデバイス。

【請求項2】

前記管理部が、前記保持されている前記パラメータが最後に記録された時点からの経過時間と基準値を比較する期限比較部をさらに具備し、

前記管理部が、

前記保持されている前記パラメータが最後に記録された時点からの経過時間が前記基準値を超えている場合、前記パラメータの前記メモリデバイスの外部への送信要求に対して拒否し、前記保持されている前記パラメータが最後に記録された時点からの経過時間が前記基準値を超えていない場合、前記パラメータの前記メモリデバイスの外部へ送信する、

ことを特徴とする、請求項1のメモリデバイス。

【請求項3】

前記管理部が、前記無線部が外部とオンライン接続しているかを判断する接続判断部をさらに具備し、

前記接続判断部が、前記無線部が外部とオンライン接続していない場合、前記パラメータの前記メモリデバイスの外部への送信要求に対して拒否し、前記無線部が外部とオンライン接続している場合、前記パラメータの前記メモリデバイスの外部へ送信する、

ことを特徴とする、請求項1のメモリデバイス。

【請求項4】

前記手順が、前記手順に従って動作可能に構成されている複数のホストが保持する前記複数のホストの各々に固有の第1キーと前記パラメータとから第2キーとを生成することを含んでおり、

前記手順が、前記手順の実行に前記第2キーを必要とし、

前記パラメータが、複数の前記第1キーのうちの特定のものと組み合わされた場合に、前記第2キーの生成を不能にするように構成され、かつ前記メモリデバイスと通信するホストからの要求に応答して前記ホストに送信される、

ことを特徴とする、請求項1乃至3のいずれかの1項のメモリデバイス。

【請求項5】

前記パラメータが、CRPM規格におけるMKBである、

ことを特徴とする、請求項4のメモリデバイス。

【請求項1】

接続されているとホストデバイスと通信するメモリデバイスであって、

不揮発性の半導体メモリと、

前記ホストデバイスからの要求に基づいて前記半導体メモリを制御するメモリ制御部と、

無線通信するための無線部と、

データを著作権保護のための手順に従って前記メモリデバイスでデータを格納することを管理する管理部であって、著作権保護のための更新される可能性を有するパラメータの最新版を前記無線部を介して外部から取得し、前記メモリデバイスに保持されている前記パラメータを前記最新版の前記パラメータと比較する比較部を含み、前記保持されている前記パラメータと前記最新版の前記パラメータとが一致していない場合に前記保持されている前記パラメータを前記最新版の前記パラメータに更新する更新部を含む、管理部と、

を具備することを特徴とするメモリデバイス。

【請求項2】

前記管理部が、前記保持されている前記パラメータが最後に記録された時点からの経過時間と基準値を比較する期限比較部をさらに具備し、

前記管理部が、

前記保持されている前記パラメータが最後に記録された時点からの経過時間が前記基準値を超えている場合、前記パラメータの前記メモリデバイスの外部への送信要求に対して拒否し、前記保持されている前記パラメータが最後に記録された時点からの経過時間が前記基準値を超えていない場合、前記パラメータの前記メモリデバイスの外部へ送信する、

ことを特徴とする、請求項1のメモリデバイス。

【請求項3】

前記管理部が、前記無線部が外部とオンライン接続しているかを判断する接続判断部をさらに具備し、

前記接続判断部が、前記無線部が外部とオンライン接続していない場合、前記パラメータの前記メモリデバイスの外部への送信要求に対して拒否し、前記無線部が外部とオンライン接続している場合、前記パラメータの前記メモリデバイスの外部へ送信する、

ことを特徴とする、請求項1のメモリデバイス。

【請求項4】

前記手順が、前記手順に従って動作可能に構成されている複数のホストが保持する前記複数のホストの各々に固有の第1キーと前記パラメータとから第2キーとを生成することを含んでおり、

前記手順が、前記手順の実行に前記第2キーを必要とし、

前記パラメータが、複数の前記第1キーのうちの特定のものと組み合わされた場合に、前記第2キーの生成を不能にするように構成され、かつ前記メモリデバイスと通信するホストからの要求に応答して前記ホストに送信される、

ことを特徴とする、請求項1乃至3のいずれかの1項のメモリデバイス。

【請求項5】

前記パラメータが、CRPM規格におけるMKBである、

ことを特徴とする、請求項4のメモリデバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−11986(P2013−11986A)

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願番号】特願2011−143429(P2011−143429)

【出願日】平成23年6月28日(2011.6.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願日】平成23年6月28日(2011.6.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]