モジュール製造方法および装置、並びにプログラム

【課題】歩留まりを向上させる。

【解決手段】駆動制御部91は、アンテナ基板61を保持する下部ヘッド51と、アンテナ基板61に対向するように異方性導電膜64を保持する上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する位置に駆動させ、温度制御部92は、下部ヘッド51に設けられたヒータ72によって、アンテナ基板61に当接した異方性導電膜64が、アンテナ基板61に転写可能な温度に、異方性導電膜64を加熱させる。そして、アンテナ基板61と異方性導電膜64とが当接位置に駆動された状態で、異方性導電膜64がアンテナ基板61に転写可能な温度に加熱された後、駆動制御部91は、上部ヘッド52を、当接位置から開放するより先のタイミングで、下部ヘッド51をその位置から開放させる。本発明は、例えば、異方性導電膜により、ICチップと基板とを圧着して接合するモジュール製造方法に適用することができる。

【解決手段】駆動制御部91は、アンテナ基板61を保持する下部ヘッド51と、アンテナ基板61に対向するように異方性導電膜64を保持する上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する位置に駆動させ、温度制御部92は、下部ヘッド51に設けられたヒータ72によって、アンテナ基板61に当接した異方性導電膜64が、アンテナ基板61に転写可能な温度に、異方性導電膜64を加熱させる。そして、アンテナ基板61と異方性導電膜64とが当接位置に駆動された状態で、異方性導電膜64がアンテナ基板61に転写可能な温度に加熱された後、駆動制御部91は、上部ヘッド52を、当接位置から開放するより先のタイミングで、下部ヘッド51をその位置から開放させる。本発明は、例えば、異方性導電膜により、ICチップと基板とを圧着して接合するモジュール製造方法に適用することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、モジュール製造方法および装置、並びにプログラムに関し、特に、基板とICチップとを接合したモジュールの製造において、歩留まりを向上させることができるようにするモジュール製造方法および装置、並びにプログラムに関する。

【背景技術】

【0002】

従来、非接触型IC(Integrated Circuit)カード、または、これに実装されるモジュールの製造においては、異方性導電膜により、ICチップと、アンテナを構成するアンテナ基板とを圧着して接合することが行われている(例えば、特許文献1参照)。異方性導電膜は、熱硬化性を有する樹脂材料中に導電性粒子を分散させてなるものであり、加圧方向にのみ導電性を得ることができる機能性材料である。

【0003】

図1は、従来のICチップが搭載されるアンテナ基板のパターンの概略を示している。図1に示されるアンテナ基板上には、ICチップの3点の電極(バンプ)であるアンテナ端子La,Lb、およびグランド端子GNDに対応したランドおよび配線パターンが設けられている。

【0004】

図1に示されるようなアンテナ基板に、異方性導電膜により、ICチップを圧着、接合する際、まず、アンテナ基板側に異方性導電膜を転写させる、いわゆる仮貼りが行われる。

【0005】

仮貼りにおいては、可撓性を有するフィルム状のセパレータ(剥離フィルム)に剥離可能に接着された異方性導電膜と、アンテナ基板とを、それらを保持する上部ヘッドおよび下部ヘッドにより、所定の温度および荷重で、一定時間圧着させることで、アンテナ基板側に異方性導電膜が転写される。

【0006】

ところで、近年、ICチップとして、接触型ICチップと非接触型ICチップとを1チップ化したDual I/F(Interface) ICチップ(以下、単にDual ICチップという)が用いられるようになってきた。

【0007】

図2は、Dual ICチップが搭載されるアンテナ基板のパターンの概略を示している。図2に示されるアンテナ基板上には、Dual ICチップの9点のバンプ(La,Lb,GND,CLK,Vcc,Rst,I/O1,I/O2,Vpp)に対応したランドおよび配線パターンが設けられている。図2に示されるアンテナ基板においては、図1に示されるアンテナ基板と比べて、配線パターンのパターンピッチ(パターン間隔)が狭い。

【0008】

このため、図2に示されるようなアンテナ基板に異方性導電膜の仮貼りを行う際、上部ヘッドを引き上げて、セパレータから異方性導電膜を剥離するときに、配線パターン同士の間隙部分(基材表面)に異方性導電膜が転写されず、セパレータ側に剥離せず残ってしまうことがあった。

【0009】

そこで、パターンピッチの狭い配線パターンに対して仮貼りを行う際には、異方性導電膜の、温度が上昇するほど液状化する性質を利用して、異方性導電膜とアンテナ基板とを高温で圧着、転写させることが考えられた。

【0010】

【特許文献1】特開平11−282997号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、異方性導電膜の液状化が進むと、上部ヘッドを引き上げて、セパレータから異方性導電膜を剥離するときに、エッジ部分で異方性導電膜が捲れ上がり、異方性導電膜の厚さが不均一になってしまうことがあった。

【0012】

また、異方性導電膜とアンテナ基板との圧着時の温度が高すぎると、異方性導電膜は、Dual ICチップとアンテナ基板とを圧着(本圧着)する前に、熱硬化性を失ってしまい、本圧着時にDual ICチップのバンプとアンテナ基板のランドとを接合する機能を失ってしまう。

【0013】

そのため、Dual ICチップとアンテナ基板とを圧着する実装工程で接合不良が発生し、歩留まりが悪化する恐れがあった。

【0014】

本発明は、このような状況に鑑みてなされたものであり、歩留まりを向上させることができるようにするものである。

【課題を解決するための手段】

【0015】

本発明の一側面のモジュール製造方法は、基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造方法であって、前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動する駆動ステップと、前記駆動ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱ステップと、前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する開放ステップとを含む。

【0016】

前記導電膜は、セパレータに接着された異方性導電膜とされ、前記第2の保持部は、前記セパレータを介して、前記異方性導電膜を保持するものとされ、前記開放ステップにおいては、前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部に保持された前記セパレータから前記異方性導電膜を分離するより先のタイミングで、前記第1の保持部を前記当接位置から開放させることができる。

【0017】

前記基板は、アンテナ基板とされ、前記モジュールは、ICカードモジュールとされるようにできる。

【0018】

本発明の一側面のモジュール製造装置は、基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造装置であって、前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する第2の保持部と、前記第1の保持部と、前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御手段と、前記第1の保持部に設けられ、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱部とを備え、前記駆動手段により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記加熱部により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記駆動制御手段は、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する。

【0019】

本発明の一側面のプログラムは、基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールの製造を制御する処理をコンピュータに実行させるプログラムであって、前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御ステップと、前記駆動制御ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱するように制御する加熱制御ステップと、前記加熱制御ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を、前記当接位置から開放するより先のタイミングで、前記第1の保持部を、前記当接位置から開放するように制御する開放制御ステップとを含む処理をコンピュータに実行させる。

【0020】

本発明の一側面においては、基板を保持する第1の保持部と、基板に対向するように導電膜を保持する第2の保持部とが、基板と導電膜とが当接する当接位置に駆動され、基板と導電膜とが当接位置に駆動された状態で、第1の保持部に設けられた加熱部によって、基板に当接した導電膜が、基板に転写可能な温度に、導電膜が加熱され、導電膜が基板に転写可能な温度に加熱された後、第2の保持部を当接位置から開放するより先のタイミングで、第1の保持部が当接位置から開放される。

【発明の効果】

【0021】

本発明の一側面によれば、基板とICチップとを接合したモジュールの製造において、歩留まりを向上させることが可能となる。

【発明を実施するための最良の形態】

【0022】

以下、本発明の実施の形態について図を参照して説明する。

【0023】

[ICカード製造装置の構成例]

図3は、本発明を適用したモジュール製造装置の一実施の形態としてのICカード製造装置の構成例を示している。

【0024】

図3のICカード製造装置は、基板供給装置11、異方性導電膜貼着装置12、仮圧着装置13、ICチップ供給装置14、本圧着装置15、搬送装置16、および完成品搬出装置17から構成される。

【0025】

基板供給装置11は、接触/非接触型のICカード(Dual I/F ICカード)のアンテナ部を構成するアンテナ基板を送出し、搬送装置16を介して、異方性導電膜貼着装置12に供給する。

【0026】

異方性導電膜貼着装置12は、基板供給装置11から供給(搬送)されてきたアンテナ基板に異方性導電膜を転写する、仮貼り処理を行い、搬送装置16を介して、仮圧着装置13に供給する。

【0027】

仮圧着装置13は、異方性導電膜貼着装置12から供給(搬送)されてきた、異方性導電膜が仮貼りされたアンテナ基板に、ICチップ供給装置14から供給されてくるDual ICチップを仮圧着し、搬送装置16を介して、本圧着装置15に供給する。ICチップ供給装置14は、仮圧着装置13にDual ICチップを供給する。

【0028】

本圧着装置15は、仮圧着装置13から供給(搬送)されてきた、Dual ICチップが仮圧着されたアンテナ基板に対して、熱圧着により、アンテナ基板とDual ICチップとを本圧着する。

【0029】

搬送装置16は、基板供給装置11から送出されるアンテナ基板を、異方性導電膜貼着装置12から仮圧着装置13へ、仮圧着装置13から本圧着装置15へ、そして、本圧着装置15から完成品搬出装置17へと搬送する。

【0030】

完成品搬出装置17は、本圧着装置15から供給(搬送)されてきた、アンテナ基板とDual ICチップとが本圧着されたICモジュールに、保護シートや印刷層を重ね合わせて、ICカードを形成し、完成品として外部に搬出(送出)する。

【0031】

[異方性導電膜貼着装置の構成例]

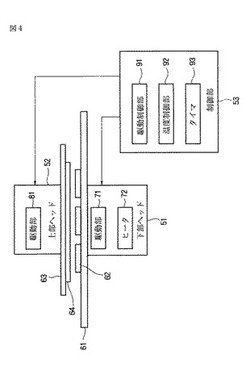

次に、図4を参照して、異方性導電膜貼着装置12の具体的な構成例について説明する。

【0032】

図4の異方性導電膜貼着装置12は、下部ヘッド51、上部ヘッド52、および制御部53から構成される。

【0033】

また、図4においては、基板供給装置11(図1)から搬送されてきた、アンテナ基板61が、配線パターン62のDual ICチップが圧着されない面で、下部ヘッド51により保持されている。また、セパレータ63に剥離可能に接着された異方性導電膜64が、セパレータ63を介して、上部ヘッド52により保持されている。

【0034】

下部ヘッド51は、アンテナ基板61を保持し、その状態で、制御部53の制御の下、図4中、上下方向に駆動する。

【0035】

下部ヘッド51は、駆動部71およびヒータ72を備えている。駆動部71は、制御部53の制御に基づいて、下部ヘッド51をアンテナ基板61とともに、図4中、上下方向に駆動させる。ヒータ72は、例えば、下部ヘッド51の、アンテナ基板61との接触面近傍に設けられ、制御部53の制御に基づいて、アンテナ基板61、および、アンテナ基板61に当接した異方性導電膜64を加熱する。

【0036】

上部ヘッド52は、異方性導電膜64が接着されたセパレータ63を保持し、その状態で、制御部53の制御の下、図4中、上下方向に駆動する。

【0037】

上部ヘッド52は、駆動部81を備えている。駆動部81は、制御部53の制御に基づいて、上部ヘッド52をセパレータ63とともに、図4中、上下方向に駆動させる。

【0038】

制御部53は、CPU(Central Processing Unit)、メモリなどから構成とされ、予め設定されたプログラムなどを実行することにより、異方性導電膜貼着装置12の各部の動作を制御する。

【0039】

制御部53は、駆動制御部91、温度制御部92、およびタイマ93を備えている。

【0040】

駆動制御部91は、下部ヘッド51の駆動部71、および、上部ヘッド52の駆動部81の駆動を制御する。具体的には、駆動制御部91は、下部ヘッド51と上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する当接位置に駆動するように、駆動部71および駆動部81を制御する。また、駆動制御部91は、タイマ93の計時動作に基づいて、下部ヘッド51と上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する当接位置から開放するように(遠ざけるように)、駆動部71および駆動部81を制御する。

【0041】

温度制御部92は、下部ヘッド51のヒータ72の温度を制御する。具体的には、温度制御部92は、アンテナ基板61に当接した異方性導電膜64が、アンテナ基板61に転写可能な温度になるように、ヒータ72の温度を80℃乃至110℃程度に制御する。

【0042】

タイマ93は、計時動作を行うようになされている。

【0043】

[ICカード製造装置のICチップ実装処理]

次に、図5のフローチャートを参照して、図3のICカード製造装置によるICチップ実装処理について説明する。

【0044】

ステップS11において、基板供給装置11は、アンテナ基板61を送出し、搬送装置16を介して、異方性導電膜貼着装置12に供給する。

【0045】

ステップS12において、異方性導電膜貼着装置12は、基板供給装置11から供給(搬送)されてきたアンテナ基板61に異方性導電膜を転写する、仮貼り処理を行う。

【0046】

[異方性導電膜貼着装置の仮貼り処理]

ここで、図6のフローチャートを参照して、異方性導電膜貼着装置12による仮貼り処理について説明する。

【0047】

ステップS31において、駆動制御部91は、駆動部71および駆動部81を制御することにより、下部ヘッド51と上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する当接位置(以下、圧着位置と称する)に駆動させる。

【0048】

ステップS32において、温度制御部92は、ヒータ72を制御することにより、アンテナ基板61の配線パターン62に当接した異方性導電膜64が、アンテナ基板61に転写可能な温度に、異方性導電膜64を加熱させる。

【0049】

以上の処理により、アンテナ基板61に異方性導電膜64が熱圧着される。

【0050】

ステップS33において、駆動制御部91は、駆動部71を制御することにより、所定の圧着時間経過後に、ヒータ72を備える下部ヘッド51を圧着位置から開放させる(遠ざける)。より具体的には、駆動制御部91は、タイマ93の計時動作に基づいて、下部ヘッド51と上部ヘッド52とが圧着位置に移動してから所定の時間が経過したことを検知する。そして、駆動制御部91は、駆動部71を制御することにより、下部ヘッド51を圧着位置から開放させる。

【0051】

ステップS34において、駆動制御部91は、タイマ93の計時動作に基づいて、下部ヘッド51が圧着位置から開放されてから、所定の時間が経過したか否かを判定する。

【0052】

ステップS34において、下部ヘッド51が圧着位置から開放されてから、所定の時間が経過していないと判定された場合、所定の時間が経過するまで、ステップS34の処理が繰り返される。

【0053】

一方、ステップS34において、下部ヘッド51が圧着位置から開放されてから、所定の時間が経過したと判定された場合、処理は、ステップS35に進む。

【0054】

ステップS35において、駆動制御部91は、駆動部81を制御することにより、上部ヘッド52を圧着位置から開放させる(遠ざける)。

【0055】

すなわち、従来のように、下部ヘッド51と上部ヘッド52が同時に開放された場合、異方性導電膜64は、ヒータ72による加熱で流動性が高い状態のままであるため、セパレータ63から異方性導電膜64を剥離するときに、異方性導電膜64が捲れ上がってしまう恐れがある。

【0056】

しかしながら、以上の処理によれば、ヒータ72を備える下部ヘッド51は、上部ヘッド52より先のタイミングで、圧着位置から開放されるので、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止され、その流動性を抑えることができ、異方性導電膜64が捲れ上がってしまうことを避けることができる。また、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止されるので、異方性導電膜64とアンテナ基板61との圧着時の温度が高くなりすぎず、異方性導電膜64は、Dual ICチップとアンテナ基板61とを本圧着する前に、熱硬化性を失ってしまうことを避けることができる。

【0057】

図7は、Dual ICチップの実装工程を示している。図7において、状態Aは、異方性導電膜64が仮貼りされた状態を示しており、状態Bは、状態AからDual ICチップ101が仮置きされた状態を示している。そして、状態Cは、状態BからDual ICチップ101が仮圧着され、さらに、圧着部111により本圧着される状態を示している。

【0058】

図6のフローチャートのステップS35の後、図7に示される状態Aのように、アンテナ基板61には、異方性導電膜64が仮貼りされた状態となり、アンテナ基板61は、搬送装置16を介して、仮圧着装置13に供給される。

【0059】

図5のフローチャートの説明に戻り、ステップS13において、仮圧着装置13は、異方性導電膜貼着装置12から供給(搬送)されてきたアンテナ基板61に、ICチップ供給装置14から供給されてくるDual ICチップ101を仮置きする。これにより、図7に示される状態Bのように、アンテナ基板61に仮貼りされた異方性導電膜64上に、Dual ICチップ101が仮置きされた状態となる。

【0060】

ステップS14において、仮圧着装置13は、図7の状態Bのように、アンテナ基板61に、仮置きされたDual ICチップ101を仮圧着し、搬送装置16を介して、本圧着装置15に供給する。

【0061】

ステップS15において、本圧着装置15は、仮圧着装置13から供給(搬送)されてきた、Dual ICチップ101が仮圧着されたアンテナ基板61に対して、熱圧着により、アンテナ基板61とDual ICチップ101とを本圧着する。すなわち、図7の状態Cのように、本圧着装置15は、アンテナ基板61に仮圧着されたDual ICチップ101を、圧着部111により加圧、加熱することで、アンテナ基板61とDual ICチップ101とを本圧着する。

【0062】

ステップS16において、完成品搬出装置17は、本圧着装置15から供給(搬送)されてきた、アンテナ基板とDual ICチップとが本圧着されたICモジュールに、保護シートや印刷層を重ね合わせて、ICカードを形成し、完成品として外部に搬出する。

【0063】

以上の処理によれば、異方性導電膜64の仮貼りにおいて、セパレータ63から異方性導電膜64を剥離するときに、異方性導電膜64が捲れ上がることを避けることができるので、異方性導電膜64の厚さを均一にすることができる。また、Dual ICチップ101とアンテナ基板61とを本圧着する前に、異方性導電膜64の熱硬化性を失ってしまうことを避けることができるので、本圧着時に、Dual ICチップ101のバンプとアンテナ基板61のランドとを接合する機能を失うことを避けることができる。したがって、Dual ICチップ101の実装工程における接合不良の発生を抑えることができ、歩留まりを向上させることが可能となる。

【0064】

以上においては、異方性導電膜64の仮貼り処理において、下部ヘッド51を、上部ヘッド52より先のタイミングで圧着位置から開放するために、下部ヘッド51が圧着位置から開放されてから所定時間経過後に上部ヘッド52を開放するようにしたが、下部ヘッド51が圧着位置から開放されてからの下部ヘッド51の位置に基づいて、上部ヘッド52を開放するようにしてもよい。

【0065】

[異方性導電膜貼着装置の他の構成例]

次に、図8を参照して、異方性導電膜貼着装置12の他の構成例について説明する。

【0066】

なお、図8の異方性導電膜貼着装置12において、図4の異方性導電膜貼着装置12に設けられたものと同様の機能を備える構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0067】

すなわち、図8の異方性導電膜貼着装置12において、図4の異方性導電膜貼着装置12と異なるのは、新たにセンサ201を設け、駆動制御部91に代えて駆動制御部202を設けた点である。

【0068】

センサ201は、下部ヘッド51の駆動方向(図中、上下方向)の位置を検知する位置センサであり、検知した下部ヘッド51の位置を示す位置情報を駆動制御部202に供給する。例えば、センサ201は、下部ヘッド51の駆動範囲内に設けられ、下部ヘッド51が、アンテナ基板61と異方性導電膜64との圧着位置から開放され、下部ヘッド51の下端部分がセンサ201近傍を通過したことを検知する。また、センサ201は、上述した形態に限らず、下部ヘッド51の駆動方向の位置を検知するものであればよい。

【0069】

駆動制御部202は、図4の駆動制御部91と同様の機能を備える他、センサ201からの位置情報に基づいて、上部ヘッド52を、圧着位置から開放するように(遠ざけるように)、駆動部81を制御する。

【0070】

[異方性導電膜貼着装置の仮貼り処理]

ここで、図9のフローチャートを参照して、図8の異方性導電膜貼着装置12による仮貼り処理について説明する。なお、図9のフローチャートにおけるステップS131乃至S133,S135の処理は、図6のフローチャートを参照して説明したステップS31乃至S33,S35の処理と同様であるので、その説明は省略するものとする。

【0071】

すなわち、ステップS134において、駆動制御部202は、センサ201からの位置情報を基に、下部ヘッド51が圧着位置から開放され、下部ヘッド51の位置が所定の位置になったか否かを判定する。

【0072】

ステップS134において、下部ヘッド51の位置が所定の位置になっていないと判定された場合、下部ヘッド51の位置が所定の位置になるまで、ステップS134の処理が繰り返される。

【0073】

一方、ステップS134において、下部ヘッド51の位置が所定の位置になったと判定された場合、処理は、ステップS135に進む。

【0074】

図6のフローチャートを参照して説明した処理と同様、以上の処理によれば、ヒータ72を備える下部ヘッド51は、上部ヘッド52より先のタイミングで、圧着位置から開放されるので、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止され、その流動性を抑えることができ、異方性導電膜64が捲れ上がってしまうことを避けることができる。また、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止されるので、異方性導電膜64とアンテナ基板61との圧着時の温度が高くなりすぎず、異方性導電膜64は、Dual ICチップ101とアンテナ基板61とを本圧着する前に、熱硬化性を失ってしまうことを避けることができる。

【0075】

したがって、異方性導電膜64の仮貼りにおいて、セパレータ63から異方性導電膜64を剥離するときに、異方性導電膜64が捲れ上がることを避けることができるので、異方性導電膜64の厚さを均一にすることができる。また、Dual ICチップ101とアンテナ基板61とを本圧着する前に、異方性導電膜64の熱硬化性を失ってしまうことを避けることができるので、本圧着時に、Dual ICチップ101のバンプとアンテナ基板61のランドとを接合する機能を失うことを避けることができる。すなわち、Dual ICチップ101の実装工程における接合不良の発生を抑えることができ、歩留まりを向上させることが可能となる。

【0076】

以上においては、ヒータを備える下部ヘッドを、上部ヘッドより先のタイミングで開放して異方性導電膜の仮貼りを行う構成について説明してきたが、アンテナ基板のパターンを改善したり、異方性導電膜の厚みを調整することで、異方性導電膜の仮貼りの信頼性を向上させるようにもできる。

【0077】

[仮貼りの信頼性向上の他の例]

まず、アンテナ基板のパターンの改善例について説明する。

【0078】

上述で説明してきたアンテナ基板は、PET(ポリエチレンテレフタレート)やPEN(ポリエチレンナフタレート)等のプラスチック製のシート状の基材上において、Cu(銅)やAl(アルミニウム)等の導体パターンをエッチングすることにより形成されている。

【0079】

ここで、上述したように、図2に示されるアンテナ基板上には、Dual ICチップの9点のバンプ(La,Lb,GND,CLK,Vcc,Rst,I/O1,I/O2,Vpp)に対応したランドが設けられているが、Dual ICチップにおいて、I/O2端子およびVpp端子は、実際には使用されていない。

【0080】

そこで、図10に、Dual ICチップにおいて、実際には使用されていない端子に対応するランドおよび配線パターンを形成しないアンテナ基板の例を示す。図10のアンテナ基板において、ランドP1乃至P7は、それぞれ、Dual ICチップのVcc端子、Rst端子、CLK端子、La端子、GND端子、I/O1端子、およびLb端子に対応する。

【0081】

図10に示されるように、Dual ICチップのI/O2端子およびVpp端子に対応するランドおよび配線パターンを形成しないことによって、パターンピッチを広くすることができる。

【0082】

このように、ICチップにおいて使用されない端子に対応するランドおよび配線パターンを、アンテナ基板上に形成しないようにすることで、パターンピッチを広くすることができ、異方性導電膜の仮貼りを行う際、パターン同士の間隙部分にも異方性導電膜を確実に転写することができる。したがって、異方性導電膜の仮貼りにおいて、異方性導電膜がセパレータ側に剥離し難くすることで、残り難くすることができる。結果として、異方性導電膜の仮貼りの信頼性を向上させることが可能となる。

【0083】

次に、異方性導電膜の厚みの調整例について説明する。

【0084】

従来、上述してきたようなDual ICチップの実装工程においては、例えば、厚みが15μmで、サイズが6mm×6mmの異方性導電膜が用いられていた。

【0085】

異方性導電膜に十分な厚みがない場合、パターンピッチが狭いアンテナ基板に異方性導電膜の仮貼りを行う際、アンテナ基板の基材表面と、配線パターンとの間の段差により生じるせん断力によって、異方性導電膜が剥がれやすくなっていた。

【0086】

そこで、異方性導電膜に厚みを持たせ、例えば、厚みを20μmにすることによって、アンテナ基板の基材表面と、配線パターンとの間の段差により生じるせん断力に対して耐久性を持たせることで、異方性導電膜が剥がれ難くなり、異方性導電膜の仮貼りの信頼性を向上させることが可能となる。

【0087】

以上のようにして、異方性導電膜の仮貼りの信頼性を向上することができるので、Dual ICチップの実装工程における接合不良の発生を抑えることができ、歩留まりを向上させることが可能となる。

【0088】

なお、上述した説明においては、Dual ICチップをアンテナ基板に圧着するICカード製造装置に、本発明を適用したが、これに限らず、複数の端子を有するICチップを配線パターン間のパターンピッチの狭い基板に圧着するモジュール製造装置に適用することができる。

【0089】

上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば汎用のパーソナルコンピュータ等に、プログラム記録媒体からインストールされる。

【0090】

図11は、上述した一連の処理をプログラムにより実行するコンピュータのハードウェアの構成例を示すブロック図である。

【0091】

コンピュータにおいて、制御部53に対応するCPU(Central Processing Unit)901,ROM(Read Only Memory)902,RAM(Random Access Memory)903は、バス904により相互に接続されている。

【0092】

バス904には、さらに、入出力インタフェース905が接続されている。入出力インタフェース905には、キーボード、マウス等よりなる入力部906、ディスプレイ、スピーカ等よりなる出力部907、ハードディスクや不揮発性のメモリ等よりなる記憶部908、ネットワークインタフェース等よりなる通信部909、磁気ディスク、光ディスク、光磁気ディスク、或いは半導体メモリ等のリムーバブルメディア911を駆動するドライブ910が接続されている。

【0093】

以上のように構成されるコンピュータでは、CPU901が、例えば、記憶部908に記憶されているプログラムを、入出力インタフェース905およびバス904を介して、RAM903にロードして実行することにより、上述した一連の処理が行われる。

【0094】

コンピュータ(CPU901)が実行するプログラムは、例えば、磁気ディスク(フレキシブルディスクを含む)、光ディスク(CD-ROM(Compact Disc-Read Only Memory),DVD(Digital Versatile Disc)等)、光磁気ディスク、もしくは半導体メモリ等よりなるパッケージメディアであるリムーバブルメディア911に記録して、あるいは、ローカルエリアネットワーク、インターネット、デジタル衛星放送といった、有線または無線の伝送媒体を介して提供される。

【0095】

そして、プログラムは、リムーバブルメディア911をドライブ910に装着することにより、入出力インタフェース905を介して、記憶部908にインストールすることができる。また、プログラムは、有線または無線の伝送媒体を介して、通信部909で受信し、記憶部908にインストールすることができる。その他、プログラムは、ROM902や記憶部908に、あらかじめインストールしておくことができる。

【0096】

なお、コンピュータが実行するプログラムは、本明細書で説明する順序に沿って時系列に処理が行われるプログラムであっても良いし、並列に、あるいは呼び出しが行われたとき等の必要なタイミングで処理が行われるプログラムであっても良い。

【0097】

また、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【図面の簡単な説明】

【0098】

【図1】従来のICチップが搭載されるアンテナ基板のパターンの概略図である。

【図2】Dual ICチップが搭載されるアンテナ基板のパターンの概略図である。

【図3】本発明を適用したモジュール製造装置の一実施の形態としてのICカード製造装置の構成例を示すブロック図である。

【図4】異方性導電膜貼着装置の具体的な構成例を示すブロック図である。

【図5】ICカード製造装置によるICチップ実装処理について説明するフローチャートである。

【図6】図4の異方性導電膜貼着装置による仮貼り処理について説明するフローチャートである。

【図7】Dual ICチップの実装工程を示す図である。

【図8】異方性導電膜貼着装置の他の構成例を示すブロック図である。

【図9】図8の異方性導電膜貼着装置による仮貼り処理について説明するフローチャートである。

【図10】アンテナ基板の例を示す図である。

【図11】コンピュータのハードウェアの構成例を示すブロック図である。

【符号の説明】

【0099】

12 異方性導電膜貼着装置, 51 下部ヘッド, 52 上部ヘッド, 53 制御部, 61 アンテナ基板, 62 配線パターン, 63 セパレータ, 64 異方性導電膜, 71 駆動部, 72 ヒータ, 81 駆動部, 91 駆動制御部, 92 温度制御部, 93 タイマ, 101 Dual ICチップ, 201 センサ, 202 駆動制御部

【技術分野】

【0001】

本発明は、モジュール製造方法および装置、並びにプログラムに関し、特に、基板とICチップとを接合したモジュールの製造において、歩留まりを向上させることができるようにするモジュール製造方法および装置、並びにプログラムに関する。

【背景技術】

【0002】

従来、非接触型IC(Integrated Circuit)カード、または、これに実装されるモジュールの製造においては、異方性導電膜により、ICチップと、アンテナを構成するアンテナ基板とを圧着して接合することが行われている(例えば、特許文献1参照)。異方性導電膜は、熱硬化性を有する樹脂材料中に導電性粒子を分散させてなるものであり、加圧方向にのみ導電性を得ることができる機能性材料である。

【0003】

図1は、従来のICチップが搭載されるアンテナ基板のパターンの概略を示している。図1に示されるアンテナ基板上には、ICチップの3点の電極(バンプ)であるアンテナ端子La,Lb、およびグランド端子GNDに対応したランドおよび配線パターンが設けられている。

【0004】

図1に示されるようなアンテナ基板に、異方性導電膜により、ICチップを圧着、接合する際、まず、アンテナ基板側に異方性導電膜を転写させる、いわゆる仮貼りが行われる。

【0005】

仮貼りにおいては、可撓性を有するフィルム状のセパレータ(剥離フィルム)に剥離可能に接着された異方性導電膜と、アンテナ基板とを、それらを保持する上部ヘッドおよび下部ヘッドにより、所定の温度および荷重で、一定時間圧着させることで、アンテナ基板側に異方性導電膜が転写される。

【0006】

ところで、近年、ICチップとして、接触型ICチップと非接触型ICチップとを1チップ化したDual I/F(Interface) ICチップ(以下、単にDual ICチップという)が用いられるようになってきた。

【0007】

図2は、Dual ICチップが搭載されるアンテナ基板のパターンの概略を示している。図2に示されるアンテナ基板上には、Dual ICチップの9点のバンプ(La,Lb,GND,CLK,Vcc,Rst,I/O1,I/O2,Vpp)に対応したランドおよび配線パターンが設けられている。図2に示されるアンテナ基板においては、図1に示されるアンテナ基板と比べて、配線パターンのパターンピッチ(パターン間隔)が狭い。

【0008】

このため、図2に示されるようなアンテナ基板に異方性導電膜の仮貼りを行う際、上部ヘッドを引き上げて、セパレータから異方性導電膜を剥離するときに、配線パターン同士の間隙部分(基材表面)に異方性導電膜が転写されず、セパレータ側に剥離せず残ってしまうことがあった。

【0009】

そこで、パターンピッチの狭い配線パターンに対して仮貼りを行う際には、異方性導電膜の、温度が上昇するほど液状化する性質を利用して、異方性導電膜とアンテナ基板とを高温で圧着、転写させることが考えられた。

【0010】

【特許文献1】特開平11−282997号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、異方性導電膜の液状化が進むと、上部ヘッドを引き上げて、セパレータから異方性導電膜を剥離するときに、エッジ部分で異方性導電膜が捲れ上がり、異方性導電膜の厚さが不均一になってしまうことがあった。

【0012】

また、異方性導電膜とアンテナ基板との圧着時の温度が高すぎると、異方性導電膜は、Dual ICチップとアンテナ基板とを圧着(本圧着)する前に、熱硬化性を失ってしまい、本圧着時にDual ICチップのバンプとアンテナ基板のランドとを接合する機能を失ってしまう。

【0013】

そのため、Dual ICチップとアンテナ基板とを圧着する実装工程で接合不良が発生し、歩留まりが悪化する恐れがあった。

【0014】

本発明は、このような状況に鑑みてなされたものであり、歩留まりを向上させることができるようにするものである。

【課題を解決するための手段】

【0015】

本発明の一側面のモジュール製造方法は、基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造方法であって、前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動する駆動ステップと、前記駆動ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱ステップと、前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する開放ステップとを含む。

【0016】

前記導電膜は、セパレータに接着された異方性導電膜とされ、前記第2の保持部は、前記セパレータを介して、前記異方性導電膜を保持するものとされ、前記開放ステップにおいては、前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部に保持された前記セパレータから前記異方性導電膜を分離するより先のタイミングで、前記第1の保持部を前記当接位置から開放させることができる。

【0017】

前記基板は、アンテナ基板とされ、前記モジュールは、ICカードモジュールとされるようにできる。

【0018】

本発明の一側面のモジュール製造装置は、基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造装置であって、前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する第2の保持部と、前記第1の保持部と、前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御手段と、前記第1の保持部に設けられ、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱部とを備え、前記駆動手段により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記加熱部により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記駆動制御手段は、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する。

【0019】

本発明の一側面のプログラムは、基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールの製造を制御する処理をコンピュータに実行させるプログラムであって、前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御ステップと、前記駆動制御ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱するように制御する加熱制御ステップと、前記加熱制御ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を、前記当接位置から開放するより先のタイミングで、前記第1の保持部を、前記当接位置から開放するように制御する開放制御ステップとを含む処理をコンピュータに実行させる。

【0020】

本発明の一側面においては、基板を保持する第1の保持部と、基板に対向するように導電膜を保持する第2の保持部とが、基板と導電膜とが当接する当接位置に駆動され、基板と導電膜とが当接位置に駆動された状態で、第1の保持部に設けられた加熱部によって、基板に当接した導電膜が、基板に転写可能な温度に、導電膜が加熱され、導電膜が基板に転写可能な温度に加熱された後、第2の保持部を当接位置から開放するより先のタイミングで、第1の保持部が当接位置から開放される。

【発明の効果】

【0021】

本発明の一側面によれば、基板とICチップとを接合したモジュールの製造において、歩留まりを向上させることが可能となる。

【発明を実施するための最良の形態】

【0022】

以下、本発明の実施の形態について図を参照して説明する。

【0023】

[ICカード製造装置の構成例]

図3は、本発明を適用したモジュール製造装置の一実施の形態としてのICカード製造装置の構成例を示している。

【0024】

図3のICカード製造装置は、基板供給装置11、異方性導電膜貼着装置12、仮圧着装置13、ICチップ供給装置14、本圧着装置15、搬送装置16、および完成品搬出装置17から構成される。

【0025】

基板供給装置11は、接触/非接触型のICカード(Dual I/F ICカード)のアンテナ部を構成するアンテナ基板を送出し、搬送装置16を介して、異方性導電膜貼着装置12に供給する。

【0026】

異方性導電膜貼着装置12は、基板供給装置11から供給(搬送)されてきたアンテナ基板に異方性導電膜を転写する、仮貼り処理を行い、搬送装置16を介して、仮圧着装置13に供給する。

【0027】

仮圧着装置13は、異方性導電膜貼着装置12から供給(搬送)されてきた、異方性導電膜が仮貼りされたアンテナ基板に、ICチップ供給装置14から供給されてくるDual ICチップを仮圧着し、搬送装置16を介して、本圧着装置15に供給する。ICチップ供給装置14は、仮圧着装置13にDual ICチップを供給する。

【0028】

本圧着装置15は、仮圧着装置13から供給(搬送)されてきた、Dual ICチップが仮圧着されたアンテナ基板に対して、熱圧着により、アンテナ基板とDual ICチップとを本圧着する。

【0029】

搬送装置16は、基板供給装置11から送出されるアンテナ基板を、異方性導電膜貼着装置12から仮圧着装置13へ、仮圧着装置13から本圧着装置15へ、そして、本圧着装置15から完成品搬出装置17へと搬送する。

【0030】

完成品搬出装置17は、本圧着装置15から供給(搬送)されてきた、アンテナ基板とDual ICチップとが本圧着されたICモジュールに、保護シートや印刷層を重ね合わせて、ICカードを形成し、完成品として外部に搬出(送出)する。

【0031】

[異方性導電膜貼着装置の構成例]

次に、図4を参照して、異方性導電膜貼着装置12の具体的な構成例について説明する。

【0032】

図4の異方性導電膜貼着装置12は、下部ヘッド51、上部ヘッド52、および制御部53から構成される。

【0033】

また、図4においては、基板供給装置11(図1)から搬送されてきた、アンテナ基板61が、配線パターン62のDual ICチップが圧着されない面で、下部ヘッド51により保持されている。また、セパレータ63に剥離可能に接着された異方性導電膜64が、セパレータ63を介して、上部ヘッド52により保持されている。

【0034】

下部ヘッド51は、アンテナ基板61を保持し、その状態で、制御部53の制御の下、図4中、上下方向に駆動する。

【0035】

下部ヘッド51は、駆動部71およびヒータ72を備えている。駆動部71は、制御部53の制御に基づいて、下部ヘッド51をアンテナ基板61とともに、図4中、上下方向に駆動させる。ヒータ72は、例えば、下部ヘッド51の、アンテナ基板61との接触面近傍に設けられ、制御部53の制御に基づいて、アンテナ基板61、および、アンテナ基板61に当接した異方性導電膜64を加熱する。

【0036】

上部ヘッド52は、異方性導電膜64が接着されたセパレータ63を保持し、その状態で、制御部53の制御の下、図4中、上下方向に駆動する。

【0037】

上部ヘッド52は、駆動部81を備えている。駆動部81は、制御部53の制御に基づいて、上部ヘッド52をセパレータ63とともに、図4中、上下方向に駆動させる。

【0038】

制御部53は、CPU(Central Processing Unit)、メモリなどから構成とされ、予め設定されたプログラムなどを実行することにより、異方性導電膜貼着装置12の各部の動作を制御する。

【0039】

制御部53は、駆動制御部91、温度制御部92、およびタイマ93を備えている。

【0040】

駆動制御部91は、下部ヘッド51の駆動部71、および、上部ヘッド52の駆動部81の駆動を制御する。具体的には、駆動制御部91は、下部ヘッド51と上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する当接位置に駆動するように、駆動部71および駆動部81を制御する。また、駆動制御部91は、タイマ93の計時動作に基づいて、下部ヘッド51と上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する当接位置から開放するように(遠ざけるように)、駆動部71および駆動部81を制御する。

【0041】

温度制御部92は、下部ヘッド51のヒータ72の温度を制御する。具体的には、温度制御部92は、アンテナ基板61に当接した異方性導電膜64が、アンテナ基板61に転写可能な温度になるように、ヒータ72の温度を80℃乃至110℃程度に制御する。

【0042】

タイマ93は、計時動作を行うようになされている。

【0043】

[ICカード製造装置のICチップ実装処理]

次に、図5のフローチャートを参照して、図3のICカード製造装置によるICチップ実装処理について説明する。

【0044】

ステップS11において、基板供給装置11は、アンテナ基板61を送出し、搬送装置16を介して、異方性導電膜貼着装置12に供給する。

【0045】

ステップS12において、異方性導電膜貼着装置12は、基板供給装置11から供給(搬送)されてきたアンテナ基板61に異方性導電膜を転写する、仮貼り処理を行う。

【0046】

[異方性導電膜貼着装置の仮貼り処理]

ここで、図6のフローチャートを参照して、異方性導電膜貼着装置12による仮貼り処理について説明する。

【0047】

ステップS31において、駆動制御部91は、駆動部71および駆動部81を制御することにより、下部ヘッド51と上部ヘッド52とを、アンテナ基板61と異方性導電膜64とが当接する当接位置(以下、圧着位置と称する)に駆動させる。

【0048】

ステップS32において、温度制御部92は、ヒータ72を制御することにより、アンテナ基板61の配線パターン62に当接した異方性導電膜64が、アンテナ基板61に転写可能な温度に、異方性導電膜64を加熱させる。

【0049】

以上の処理により、アンテナ基板61に異方性導電膜64が熱圧着される。

【0050】

ステップS33において、駆動制御部91は、駆動部71を制御することにより、所定の圧着時間経過後に、ヒータ72を備える下部ヘッド51を圧着位置から開放させる(遠ざける)。より具体的には、駆動制御部91は、タイマ93の計時動作に基づいて、下部ヘッド51と上部ヘッド52とが圧着位置に移動してから所定の時間が経過したことを検知する。そして、駆動制御部91は、駆動部71を制御することにより、下部ヘッド51を圧着位置から開放させる。

【0051】

ステップS34において、駆動制御部91は、タイマ93の計時動作に基づいて、下部ヘッド51が圧着位置から開放されてから、所定の時間が経過したか否かを判定する。

【0052】

ステップS34において、下部ヘッド51が圧着位置から開放されてから、所定の時間が経過していないと判定された場合、所定の時間が経過するまで、ステップS34の処理が繰り返される。

【0053】

一方、ステップS34において、下部ヘッド51が圧着位置から開放されてから、所定の時間が経過したと判定された場合、処理は、ステップS35に進む。

【0054】

ステップS35において、駆動制御部91は、駆動部81を制御することにより、上部ヘッド52を圧着位置から開放させる(遠ざける)。

【0055】

すなわち、従来のように、下部ヘッド51と上部ヘッド52が同時に開放された場合、異方性導電膜64は、ヒータ72による加熱で流動性が高い状態のままであるため、セパレータ63から異方性導電膜64を剥離するときに、異方性導電膜64が捲れ上がってしまう恐れがある。

【0056】

しかしながら、以上の処理によれば、ヒータ72を備える下部ヘッド51は、上部ヘッド52より先のタイミングで、圧着位置から開放されるので、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止され、その流動性を抑えることができ、異方性導電膜64が捲れ上がってしまうことを避けることができる。また、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止されるので、異方性導電膜64とアンテナ基板61との圧着時の温度が高くなりすぎず、異方性導電膜64は、Dual ICチップとアンテナ基板61とを本圧着する前に、熱硬化性を失ってしまうことを避けることができる。

【0057】

図7は、Dual ICチップの実装工程を示している。図7において、状態Aは、異方性導電膜64が仮貼りされた状態を示しており、状態Bは、状態AからDual ICチップ101が仮置きされた状態を示している。そして、状態Cは、状態BからDual ICチップ101が仮圧着され、さらに、圧着部111により本圧着される状態を示している。

【0058】

図6のフローチャートのステップS35の後、図7に示される状態Aのように、アンテナ基板61には、異方性導電膜64が仮貼りされた状態となり、アンテナ基板61は、搬送装置16を介して、仮圧着装置13に供給される。

【0059】

図5のフローチャートの説明に戻り、ステップS13において、仮圧着装置13は、異方性導電膜貼着装置12から供給(搬送)されてきたアンテナ基板61に、ICチップ供給装置14から供給されてくるDual ICチップ101を仮置きする。これにより、図7に示される状態Bのように、アンテナ基板61に仮貼りされた異方性導電膜64上に、Dual ICチップ101が仮置きされた状態となる。

【0060】

ステップS14において、仮圧着装置13は、図7の状態Bのように、アンテナ基板61に、仮置きされたDual ICチップ101を仮圧着し、搬送装置16を介して、本圧着装置15に供給する。

【0061】

ステップS15において、本圧着装置15は、仮圧着装置13から供給(搬送)されてきた、Dual ICチップ101が仮圧着されたアンテナ基板61に対して、熱圧着により、アンテナ基板61とDual ICチップ101とを本圧着する。すなわち、図7の状態Cのように、本圧着装置15は、アンテナ基板61に仮圧着されたDual ICチップ101を、圧着部111により加圧、加熱することで、アンテナ基板61とDual ICチップ101とを本圧着する。

【0062】

ステップS16において、完成品搬出装置17は、本圧着装置15から供給(搬送)されてきた、アンテナ基板とDual ICチップとが本圧着されたICモジュールに、保護シートや印刷層を重ね合わせて、ICカードを形成し、完成品として外部に搬出する。

【0063】

以上の処理によれば、異方性導電膜64の仮貼りにおいて、セパレータ63から異方性導電膜64を剥離するときに、異方性導電膜64が捲れ上がることを避けることができるので、異方性導電膜64の厚さを均一にすることができる。また、Dual ICチップ101とアンテナ基板61とを本圧着する前に、異方性導電膜64の熱硬化性を失ってしまうことを避けることができるので、本圧着時に、Dual ICチップ101のバンプとアンテナ基板61のランドとを接合する機能を失うことを避けることができる。したがって、Dual ICチップ101の実装工程における接合不良の発生を抑えることができ、歩留まりを向上させることが可能となる。

【0064】

以上においては、異方性導電膜64の仮貼り処理において、下部ヘッド51を、上部ヘッド52より先のタイミングで圧着位置から開放するために、下部ヘッド51が圧着位置から開放されてから所定時間経過後に上部ヘッド52を開放するようにしたが、下部ヘッド51が圧着位置から開放されてからの下部ヘッド51の位置に基づいて、上部ヘッド52を開放するようにしてもよい。

【0065】

[異方性導電膜貼着装置の他の構成例]

次に、図8を参照して、異方性導電膜貼着装置12の他の構成例について説明する。

【0066】

なお、図8の異方性導電膜貼着装置12において、図4の異方性導電膜貼着装置12に設けられたものと同様の機能を備える構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0067】

すなわち、図8の異方性導電膜貼着装置12において、図4の異方性導電膜貼着装置12と異なるのは、新たにセンサ201を設け、駆動制御部91に代えて駆動制御部202を設けた点である。

【0068】

センサ201は、下部ヘッド51の駆動方向(図中、上下方向)の位置を検知する位置センサであり、検知した下部ヘッド51の位置を示す位置情報を駆動制御部202に供給する。例えば、センサ201は、下部ヘッド51の駆動範囲内に設けられ、下部ヘッド51が、アンテナ基板61と異方性導電膜64との圧着位置から開放され、下部ヘッド51の下端部分がセンサ201近傍を通過したことを検知する。また、センサ201は、上述した形態に限らず、下部ヘッド51の駆動方向の位置を検知するものであればよい。

【0069】

駆動制御部202は、図4の駆動制御部91と同様の機能を備える他、センサ201からの位置情報に基づいて、上部ヘッド52を、圧着位置から開放するように(遠ざけるように)、駆動部81を制御する。

【0070】

[異方性導電膜貼着装置の仮貼り処理]

ここで、図9のフローチャートを参照して、図8の異方性導電膜貼着装置12による仮貼り処理について説明する。なお、図9のフローチャートにおけるステップS131乃至S133,S135の処理は、図6のフローチャートを参照して説明したステップS31乃至S33,S35の処理と同様であるので、その説明は省略するものとする。

【0071】

すなわち、ステップS134において、駆動制御部202は、センサ201からの位置情報を基に、下部ヘッド51が圧着位置から開放され、下部ヘッド51の位置が所定の位置になったか否かを判定する。

【0072】

ステップS134において、下部ヘッド51の位置が所定の位置になっていないと判定された場合、下部ヘッド51の位置が所定の位置になるまで、ステップS134の処理が繰り返される。

【0073】

一方、ステップS134において、下部ヘッド51の位置が所定の位置になったと判定された場合、処理は、ステップS135に進む。

【0074】

図6のフローチャートを参照して説明した処理と同様、以上の処理によれば、ヒータ72を備える下部ヘッド51は、上部ヘッド52より先のタイミングで、圧着位置から開放されるので、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止され、その流動性を抑えることができ、異方性導電膜64が捲れ上がってしまうことを避けることができる。また、セパレータ63から異方性導電膜64を剥離する前に、異方性導電膜64への加熱が停止されるので、異方性導電膜64とアンテナ基板61との圧着時の温度が高くなりすぎず、異方性導電膜64は、Dual ICチップ101とアンテナ基板61とを本圧着する前に、熱硬化性を失ってしまうことを避けることができる。

【0075】

したがって、異方性導電膜64の仮貼りにおいて、セパレータ63から異方性導電膜64を剥離するときに、異方性導電膜64が捲れ上がることを避けることができるので、異方性導電膜64の厚さを均一にすることができる。また、Dual ICチップ101とアンテナ基板61とを本圧着する前に、異方性導電膜64の熱硬化性を失ってしまうことを避けることができるので、本圧着時に、Dual ICチップ101のバンプとアンテナ基板61のランドとを接合する機能を失うことを避けることができる。すなわち、Dual ICチップ101の実装工程における接合不良の発生を抑えることができ、歩留まりを向上させることが可能となる。

【0076】

以上においては、ヒータを備える下部ヘッドを、上部ヘッドより先のタイミングで開放して異方性導電膜の仮貼りを行う構成について説明してきたが、アンテナ基板のパターンを改善したり、異方性導電膜の厚みを調整することで、異方性導電膜の仮貼りの信頼性を向上させるようにもできる。

【0077】

[仮貼りの信頼性向上の他の例]

まず、アンテナ基板のパターンの改善例について説明する。

【0078】

上述で説明してきたアンテナ基板は、PET(ポリエチレンテレフタレート)やPEN(ポリエチレンナフタレート)等のプラスチック製のシート状の基材上において、Cu(銅)やAl(アルミニウム)等の導体パターンをエッチングすることにより形成されている。

【0079】

ここで、上述したように、図2に示されるアンテナ基板上には、Dual ICチップの9点のバンプ(La,Lb,GND,CLK,Vcc,Rst,I/O1,I/O2,Vpp)に対応したランドが設けられているが、Dual ICチップにおいて、I/O2端子およびVpp端子は、実際には使用されていない。

【0080】

そこで、図10に、Dual ICチップにおいて、実際には使用されていない端子に対応するランドおよび配線パターンを形成しないアンテナ基板の例を示す。図10のアンテナ基板において、ランドP1乃至P7は、それぞれ、Dual ICチップのVcc端子、Rst端子、CLK端子、La端子、GND端子、I/O1端子、およびLb端子に対応する。

【0081】

図10に示されるように、Dual ICチップのI/O2端子およびVpp端子に対応するランドおよび配線パターンを形成しないことによって、パターンピッチを広くすることができる。

【0082】

このように、ICチップにおいて使用されない端子に対応するランドおよび配線パターンを、アンテナ基板上に形成しないようにすることで、パターンピッチを広くすることができ、異方性導電膜の仮貼りを行う際、パターン同士の間隙部分にも異方性導電膜を確実に転写することができる。したがって、異方性導電膜の仮貼りにおいて、異方性導電膜がセパレータ側に剥離し難くすることで、残り難くすることができる。結果として、異方性導電膜の仮貼りの信頼性を向上させることが可能となる。

【0083】

次に、異方性導電膜の厚みの調整例について説明する。

【0084】

従来、上述してきたようなDual ICチップの実装工程においては、例えば、厚みが15μmで、サイズが6mm×6mmの異方性導電膜が用いられていた。

【0085】

異方性導電膜に十分な厚みがない場合、パターンピッチが狭いアンテナ基板に異方性導電膜の仮貼りを行う際、アンテナ基板の基材表面と、配線パターンとの間の段差により生じるせん断力によって、異方性導電膜が剥がれやすくなっていた。

【0086】

そこで、異方性導電膜に厚みを持たせ、例えば、厚みを20μmにすることによって、アンテナ基板の基材表面と、配線パターンとの間の段差により生じるせん断力に対して耐久性を持たせることで、異方性導電膜が剥がれ難くなり、異方性導電膜の仮貼りの信頼性を向上させることが可能となる。

【0087】

以上のようにして、異方性導電膜の仮貼りの信頼性を向上することができるので、Dual ICチップの実装工程における接合不良の発生を抑えることができ、歩留まりを向上させることが可能となる。

【0088】

なお、上述した説明においては、Dual ICチップをアンテナ基板に圧着するICカード製造装置に、本発明を適用したが、これに限らず、複数の端子を有するICチップを配線パターン間のパターンピッチの狭い基板に圧着するモジュール製造装置に適用することができる。

【0089】

上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば汎用のパーソナルコンピュータ等に、プログラム記録媒体からインストールされる。

【0090】

図11は、上述した一連の処理をプログラムにより実行するコンピュータのハードウェアの構成例を示すブロック図である。

【0091】

コンピュータにおいて、制御部53に対応するCPU(Central Processing Unit)901,ROM(Read Only Memory)902,RAM(Random Access Memory)903は、バス904により相互に接続されている。

【0092】

バス904には、さらに、入出力インタフェース905が接続されている。入出力インタフェース905には、キーボード、マウス等よりなる入力部906、ディスプレイ、スピーカ等よりなる出力部907、ハードディスクや不揮発性のメモリ等よりなる記憶部908、ネットワークインタフェース等よりなる通信部909、磁気ディスク、光ディスク、光磁気ディスク、或いは半導体メモリ等のリムーバブルメディア911を駆動するドライブ910が接続されている。

【0093】

以上のように構成されるコンピュータでは、CPU901が、例えば、記憶部908に記憶されているプログラムを、入出力インタフェース905およびバス904を介して、RAM903にロードして実行することにより、上述した一連の処理が行われる。

【0094】

コンピュータ(CPU901)が実行するプログラムは、例えば、磁気ディスク(フレキシブルディスクを含む)、光ディスク(CD-ROM(Compact Disc-Read Only Memory),DVD(Digital Versatile Disc)等)、光磁気ディスク、もしくは半導体メモリ等よりなるパッケージメディアであるリムーバブルメディア911に記録して、あるいは、ローカルエリアネットワーク、インターネット、デジタル衛星放送といった、有線または無線の伝送媒体を介して提供される。

【0095】

そして、プログラムは、リムーバブルメディア911をドライブ910に装着することにより、入出力インタフェース905を介して、記憶部908にインストールすることができる。また、プログラムは、有線または無線の伝送媒体を介して、通信部909で受信し、記憶部908にインストールすることができる。その他、プログラムは、ROM902や記憶部908に、あらかじめインストールしておくことができる。

【0096】

なお、コンピュータが実行するプログラムは、本明細書で説明する順序に沿って時系列に処理が行われるプログラムであっても良いし、並列に、あるいは呼び出しが行われたとき等の必要なタイミングで処理が行われるプログラムであっても良い。

【0097】

また、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【図面の簡単な説明】

【0098】

【図1】従来のICチップが搭載されるアンテナ基板のパターンの概略図である。

【図2】Dual ICチップが搭載されるアンテナ基板のパターンの概略図である。

【図3】本発明を適用したモジュール製造装置の一実施の形態としてのICカード製造装置の構成例を示すブロック図である。

【図4】異方性導電膜貼着装置の具体的な構成例を示すブロック図である。

【図5】ICカード製造装置によるICチップ実装処理について説明するフローチャートである。

【図6】図4の異方性導電膜貼着装置による仮貼り処理について説明するフローチャートである。

【図7】Dual ICチップの実装工程を示す図である。

【図8】異方性導電膜貼着装置の他の構成例を示すブロック図である。

【図9】図8の異方性導電膜貼着装置による仮貼り処理について説明するフローチャートである。

【図10】アンテナ基板の例を示す図である。

【図11】コンピュータのハードウェアの構成例を示すブロック図である。

【符号の説明】

【0099】

12 異方性導電膜貼着装置, 51 下部ヘッド, 52 上部ヘッド, 53 制御部, 61 アンテナ基板, 62 配線パターン, 63 セパレータ, 64 異方性導電膜, 71 駆動部, 72 ヒータ, 81 駆動部, 91 駆動制御部, 92 温度制御部, 93 タイマ, 101 Dual ICチップ, 201 センサ, 202 駆動制御部

【特許請求の範囲】

【請求項1】

基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造方法において、

前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動する駆動ステップと、

前記駆動ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱ステップと、

前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する開放ステップと

を含むモジュール製造方法。

【請求項2】

前記導電膜は、セパレータに接着された異方性導電膜であり、

前記第2の保持部は、前記セパレータを介して、前記異方性導電膜を保持するものであり、

前記開放ステップにおいては、前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部に保持された前記セパレータから前記異方性導電膜を分離するより先のタイミングで、前記第1の保持部を前記当接位置から開放する

請求項1に記載のモジュール製造方法。

【請求項3】

前記基板は、アンテナ基板であり、

前記モジュールは、ICカードモジュールである

請求項1に記載のモジュール製造方法。

【請求項4】

基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造装置において、

前記基板を保持する第1の保持部と、

前記基板に対向するように前記導電膜を保持する第2の保持部と、

前記第1の保持部と、前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御手段と、

前記第1の保持部に設けられ、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱部と

を備え、

前記駆動手段により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記加熱部により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記駆動制御手段は、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する

モジュール製造装置。

【請求項5】

基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールの製造を制御する処理をコンピュータに実行させるプログラムにおいて、

前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御ステップと、

前記駆動制御ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱するように制御する加熱制御ステップと、

前記加熱制御ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を、前記当接位置から開放するより先のタイミングで、前記第1の保持部を、前記当接位置から開放するように制御する開放制御ステップと

を含む処理をコンピュータに実行させるプログラム。

【請求項1】

基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造方法において、

前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動する駆動ステップと、

前記駆動ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱ステップと、

前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する開放ステップと

を含むモジュール製造方法。

【請求項2】

前記導電膜は、セパレータに接着された異方性導電膜であり、

前記第2の保持部は、前記セパレータを介して、前記異方性導電膜を保持するものであり、

前記開放ステップにおいては、前記加熱ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部に保持された前記セパレータから前記異方性導電膜を分離するより先のタイミングで、前記第1の保持部を前記当接位置から開放する

請求項1に記載のモジュール製造方法。

【請求項3】

前記基板は、アンテナ基板であり、

前記モジュールは、ICカードモジュールである

請求項1に記載のモジュール製造方法。

【請求項4】

基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールを製造するモジュール製造装置において、

前記基板を保持する第1の保持部と、

前記基板に対向するように前記導電膜を保持する第2の保持部と、

前記第1の保持部と、前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御手段と、

前記第1の保持部に設けられ、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱する加熱部と

を備え、

前記駆動手段により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記加熱部により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記駆動制御手段は、前記第2の保持部を前記当接位置から開放するより先のタイミングで、前記第1の保持部を前記当接位置から開放する

モジュール製造装置。

【請求項5】

基板とIC(Integrated Circuit)チップとを熱圧着により接合するための導電膜が転写された前記基板に、前記ICチップを接合したモジュールの製造を制御する処理をコンピュータに実行させるプログラムにおいて、

前記基板を保持する第1の保持部と、前記基板に対向するように前記導電膜を保持する前記第2の保持部とを、前記基板と前記導電膜とが当接する当接位置に駆動するように制御する駆動制御ステップと、

前記駆動制御ステップの処理により、前記基板と前記導電膜とが前記当接位置に駆動された状態で、前記第1の保持部に設けられた加熱部によって、前記基板に当接した前記導電膜が、前記基板に転写可能な温度に、前記導電膜を加熱するように制御する加熱制御ステップと、

前記加熱制御ステップの処理により、前記導電膜が前記基板に転写可能な温度に加熱された後、前記第2の保持部を、前記当接位置から開放するより先のタイミングで、前記第1の保持部を、前記当接位置から開放するように制御する開放制御ステップと

を含む処理をコンピュータに実行させるプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−128880(P2010−128880A)

【公開日】平成22年6月10日(2010.6.10)

【国際特許分類】

【出願番号】特願2008−304167(P2008−304167)

【出願日】平成20年11月28日(2008.11.28)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成22年6月10日(2010.6.10)

【国際特許分類】

【出願日】平成20年11月28日(2008.11.28)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]