モノリシック集積回路及びデバイス

符号化されたデータをその中またはその上に配置された表面。符号化されたデータは、表面の上または中のめいめいの位置に配置された少なくとも1つのデータ部分と、表面の上または中に配置された位置合わせデータとを含み、位置合わせデータは、少なくとも2つのレジストレーション位置を少なくとも部分的に示す。レジストレーション位置は、表面に関する少なくとも1つのデータ部分の相対位置を少なくとも部分的に示し、これによって、データ部分を少なくとも部分的に復号することを可能にする。

Notice: Undefined index: DEJ in /mnt/www/gzt_disp.php on line 298

【特許請求の範囲】

【請求項1】

符号化されたデータをその中またはその上に配置された表面であって、前記符号化されたデータが、

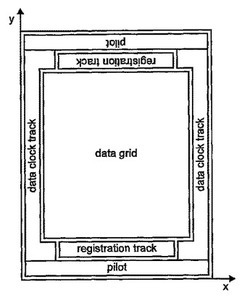

前記表面の上または中のめいめいの位置に配置された少なくとも1つのデータ部分と、

前記表面の上または中に配置された位置合わせデータであって、前記位置合わせデータが、少なくとも2つのレジストレーション位置を少なくとも部分的に示し、前記レジストレーション位置が、前記表面に関する前記少なくとも1つのデータ部分の相対位置を少なくとも部分的に示し、これによって、前記少なくとも1つのデータ部分を少なくとも部分的に復号することを可能にする、位置合わせデータと

を含む、表面。

【請求項2】

前記位置合わせデータが、

位置合わせ方向での前記符号化されたデータの位置を示す複数の基準点を示す第1レジストレーション構造と、

前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す複数の基準点を示す第2レジストレーション構造と

を含む、請求項1に記載の表面。

【請求項3】

前記第1レジストレーション構造が、

前記位置合わせ方向での前記符号化されたデータの粗位置を示す複数のマーカと、

前記位置合わせ方向での前記符号化されたデータの微細位置を示すクロックトラックと

を含む、請求項2に記載の表面。

【請求項4】

前記第2レジストレーション構造が、

前記位置合わせ方向に垂直な前記方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、

クロックトラックごとに2つの、前記位置合わせ方向での前記めいめいのクロックトラックの位置を示す、位置合わせ線と

を含む、請求項2に記載の表面。

【請求項5】

フォーマットが、少なくとも1つのデータブロックを含み、前記データブロックが、

複数の可能な値を定義するマークの配置と、

前記マークの位置を示す位置合わせデータと

を含む、請求項1に記載の表面。

【請求項6】

各データブロックが、

それ自体のパイロットトラックを設けられ、

それ自体のレジストレーション特徴を設けられ、

それ自体のクロッキング特徴を設けられ、

データ符号化区域の向かい合わせの側面に2つのクロッキング特徴を設けられ、

ビットストリームのフラグメントを符号化し、

データ符号化区域内でビットストリームのフラグメントを符号化し、

長方形データ符号化区域から形成される

のうちの少なくとも1つである、請求項5に記載の表面。

【請求項7】

データが、パラメータデータを使用して符号化され、各データブロックが、前記パラメータデータのうちの少なくともいくつかを符号化し、前記パラメータデータが、

前記符号化されたデータのサイズを示し、

インターリーブファクタを示し、

パラメータに関連するチェックサムと、

パラメータに関連するCRCチェックサムと、

パラメータに関連する冗長性データと、

パラメータに関連するリード−ソロモン冗長性データと、

パラメータの複製およびチェックサムと

のうちの少なくとも1つを使用してフォールトトレラントに符号化される

のうちの少なくとも1つである、請求項5に記載の表面。

【請求項8】

前記データが、フォールトトレラントにデータを符号化するために、複数のインターリーブされたコードワードを使用して符号化される、請求項1に記載の表面。

【請求項9】

前記位置合わせデータが、パイロット特徴を含み、前記パイロット特徴が、

フォールトトレラントに符号化され、

平行ラインの組から形成され、

2進パイロットシーケンスを符号化する平行ラインの組から形成され、

110101100100011と、

110010001111010と

のうちの少なくとも1つを符号化するパイロットシーケンスである

のうちの1つである、請求項1に記載の表面。

【請求項10】

符号化されたデータをその中またはその上に配置された表面であって、前記符号化されたデータが、

前記表面の上または中のめいめいの位置に配置された少なくとも1つのデータ部分であって、各データ部分が、位置合わせ方向に延びる、データ部分と、

前記表面の上または中に配置された位置合わせデータと

を含み、使用中に、スキャンライン方向に延びる感知領域内に供給されるデータを感知する感知デバイスが、

少なくとも2つの位置の前記位置合わせデータと、

前記複数のデータ部分のうちの少なくとも1つの少なくとも一部と

を感知し、

少なくとも2つのレジストレーション位置を使用して、前記スキャンライン方向と前記位置合わせ方向との間の位置合わせ角度を判定し、

少なくとも1つのレジストレーション位置および前記位置合わせ角度を使用して、前記感知領域に関する前記少なくとも1つの感知されたデータ部分の相対位置を判定し、

前記相対位置および前記位置合わせ角度を使用して、前記少なくとも1つのデータ部分を少なくとも部分的に復号する

ように動作する、表面。

【請求項11】

表面の上または中に設けられた符号化されたデータを復号するシステムであって、前記符号化されたデータが、

前記表面の上または中に配置された少なくとも1つのデータ部分と、

少なくとも1つのクロックインジケータを少なくとも部分的に示す位置合わせデータと

を含み、前記システムが、

感知領域内に供給されるデータを感知するセンサであって、

前記位置合わせデータの少なくとも一部と、

前記少なくとも1つのデータ部分の少なくとも一部と

を感知する、センサと、

デコーダであって、

前記感知された位置合わせデータ一部を使用して、前記クロックインジケータを判定し、

前記クロックインジケータを使用して、PLLを更新し、

前記PLLを使用して、前記感知領域と前記少なくとも1つの感知されたデータ部分との間の相対位置を判定し、

前記相対位置を使用して、前記少なくとも1つのデータ部分を少なくとも部分的に復号する

デコーダと

を含む、システム。

【請求項12】

前記デコーダが、

粗レジストレーションを判定するために少なくとも1つのマーカの位置を判定し、

前記粗レジストレーションを使用して、クロックトラック内のクロックインジケータを判定し、

前記クロックインジケータを使用して、位置合わせPLLを更新し、

前記位置合わせPLLを使用して、前記位置合わせ方向での前記符号化されたデータの微細レジストレーションを判定する

請求項11に記載のシステム。

【請求項13】

前記符号化されたデータが、レジストレーション構造を含み、前記レジストレーション構造が、前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、クロックトラックごとに2つの位置合わせ線とを含み、前記2つの位置合わせ線が、前記めいめいのクロックトラックの位置を示し、前記デコーダが、

位置合わせPLLを使用して、めいめいのクロックトラックの前記位置合わせ線の位置を判定し、

前記位置合わせ線の前記位置を使用して、各めいめいのクロックトラックの位置を判定し、

前記位置合わせPLLを更新する

請求項11に記載のシステム。

【請求項14】

前記デコーダが、

クロックトラックごとに、めいめいのデータクロックPLLを使用して、前記クロックトラック上のクロックインジケータの位置を判定し、

各クロックトラック上の前記クロックインジケータの前記位置を使用して、位置合わせ角度を判定し、

各データクロックPLLを更新する

請求項13に記載のシステム。

【請求項15】

前記デコーダが、

前記位置合わせデータを使用して、スキャンンラインの変換を判定することであって、前記変換が、前記データ部分内のビット符号化位置の座標を示す、判定することと、

前記変換を使用してビット値を検出することと

によって前記符号化されたデータを復号する、請求項11に記載のシステム。

【請求項16】

前記デコーダが、

前記ビット符号化位置の前記座標からサンプル値の座標を判定し、

2つの連続するスキャンラインからのサンプル値を補間することによってビット符号化値を判定する

請求項15に記載のシステム。

【請求項17】

前記デコーダが、

3つ以上の可能な値を有する復号されたビットストリームビットに一時値を割り当て、

前記ビットの2進値を、データ符号化区域内の周囲のビットの値に基づいて解決し、

解決された符号化されたビットストリームビット値をビットストリーム順でストレージデバイスに書き込む

請求項16に記載のシステム。

【請求項18】

前記デコーダが、

前記位置合わせデータ内でパイロット特徴を検出し、前記パイロット特徴が、少なくとも2つの位置で検出され、

前記パイロット特徴を使用して、

スキャンライン方向と位置合わせ方向との間の位置合わせ角度と、

前記位置合わせ方向に垂直な方向での初期レジストレーションと

を判定し、

前記位置合わせデータ内でレジストレーション特徴内のレジストレーションマーカを検出し、

前記レジストレーションマーカを使用して、前記位置合わせ方向での粗レジストレーションを判定し、

前記粗レジストレーションを使用して、前記位置合わせデータ内でレジストレーションクロックインジケータを検出し、

前記レジストレーションクロックインジケータを使用して、前記位置合わせ方向での微細レジストレーションを判定し、

前記微細レジストレーション、前記位置合わせ角度、および前記初期レジストレーションを使用して、少なくとも1つの位置合わせ線を検出し、

前記少なくとも1つの検出された位置合わせ線を使用して、前記微細レジストレーションを更新し、

前記更新された微細レジストレーションを使用して、前記位置合わせデータ内の2つのデータクロックトラックの位置を判定し、

前記データクロックトラックの前記位置を使用して、各データクロックトラック上のデータクロックインジケータを検出し、

各データクロックインジケータを使用して、更新された位置合わせ角度および前記位置合わせ方向に垂直な方向での更新されたレジストレーションを判定し、

前記少なくとも1つのデータ部分の少なくとも一部を検出し、

前記更新された位置合わせ角度、前記微細レジストレーション、および前記更新されたレジストレーションを使用して、前記少なくとも1つの検出されたデータ部分の少なくとも一部を復号する

請求項11に記載のシステム。

【請求項19】

前記デコーダが、繰り返して、

前記少なくとも1つの位置合わせ線を検出し、

前記微細レジストレーションを更新し、

前記更新された微細レジストレーションおよび前記更新されたレジストレーションを使用して、前記データクロックトラックの前記位置を判定し、

各データクロックトラック上のデータクロックインジケータを検出し、

前記更新された位置合わせ角度および前記更新されたレジストレーションを更新し、

これによって前記少なくとも1つのデータ部分を復号できるようにするために、前記少なくとも1つのデータ部分の少なくとも一部を検出する

請求項18に記載のシステム。

【請求項20】

前記デコーダが、

前記パイロット特徴の2つの位置でクロックインジケータを検出し、

これによって前記パイロット特徴を追跡するために、めいめいのパイロットPLLを各クロックインジケータに同期させ、

前記パイロットPLLを使用して、

前記位置合わせ角度と、

前記初期レジストレーションと

を判定し、

前記初期レジストレーションおよび前記位置合わせ角度を使用して、2つのデータクロックPLLを初期化し、

前記位置合わせデータ内の前記レジストレーションマーカを検出し、

前記レジストレーションマーカを使用して、前記粗レジストレーションを判定し、

これによって前記レジストレーション特徴を追跡するために、前記粗レジストレーションを使用して、レジストレーションPLLを前記位置合わせデータ内の前記レジストレーションクロックインジケータに同期させ、

前記レジストレーションPLLを使用して、前記微細レジストレーションを判定し、

前記微細レジストレーションを使用して、2つの位置合わせPLLを初期化し、

これによって前記データクロックトラックを追跡するために、前記位置合わせPLLを位置合わせマーカに同期させ、

前記位置合わせPLLを使用して、前記位置合わせデータ内の2つのデータクロックトラックの前記位置を判定し、

前記データクロックトラックの前記位置を使用して、各データクロックトラック上のデータクロックインジケータを検出し、

これによって前記位置合わせ方向に垂直な前記方向で前記データのレジストレーションを追跡するために、各データクロックPLLを対応するデータクロックインジケータに同期させ、

前記データクロックPLLを使用して、

前記更新された位置合わせ角度と、

前記表面上の符号化されたデータの前記位置と

のうちの少なくとも1つを判定する

請求項18に記載のシステム。

【請求項21】

表面の上または中でビットストリームを符号化するデータ保管フォーマットであって、

少なくとも1つのデータ部分であって、前記少なくとも1つのデータ部分が、前記ビットストリームとそれに続く対応する冗長性データとを含むデータシーケンスを符号化し、前記データシーケンスが、インターリーブされたコードワードを形成し、各コードワードが、前記ビットストリームの少なくとも一部と前記めいめいのビットストリーム一部に関連する冗長性データとを符号化する、少なくとも1つのデータ部分

を含むデータ保管フォーマット。

【請求項22】

前記フォーマットが、前記表面の上または中に配置された位置合わせデータを含み、前記位置合わせデータが、前記表面上の前記データ部分の位置を少なくとも部分的に示す、請求項21に記載のデータ保管フォーマット。

【請求項23】

前記位置合わせデータが、

位置合わせ方向での符号化されたデータの位置を示す複数の基準点を示す第1レジストレーション構造と、

前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す複数の基準点を示す第2レジストレーション構造と

を含む、請求項22に記載のデータ保管フォーマット。

【請求項24】

前記第1レジストレーション構造が、

前記位置合わせ方向での前記符号化されたデータの粗位置を示す複数のマーカと、

前記位置合わせ方向での前記符号化されたデータの微細位置を示すクロックトラックと

を含む、請求項23に記載のデータ保管フォーマット。

【請求項25】

前記第2レジストレーション構造が、

前記位置合わせ方向に垂直な前記方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、

クロックトラックごとに2つの、前記位置合わせ方向での前記めいめいのクロックトラックの位置を示す、位置合わせ線と

を含む、請求項23に記載のデータ保管フォーマット。

【請求項26】

前記フォーマットが、少なくとも1つのデータブロックを含み、前記データブロックが、

複数の可能な値を定義するマークの配置と、

前記マークの位置を示す位置合わせデータと

を含む、請求項21に記載のデータ保管フォーマット。

【請求項27】

各データブロックが、

それ自体のパイロットトラックを設けられ、

それ自体のレジストレーション特徴を設けられ、

それ自体のクロッキング特徴を設けられ、

データ符号化区域の向かい合わせの側面に2つのクロッキング特徴を設けられ、

ビットストリームのフラグメントを符号化し、

データ符号化区域内でビットストリームのフラグメントを符号化し、

長方形データ符号化区域から形成される

のうちの少なくとも1つである、請求項26に記載のデータ保管フォーマット。

【請求項28】

前記データが、フォールトトレラントにデータを符号化するために、複数のインターリーブされたコードワードを使用して符号化される、請求項21に記載のデータ保管フォーマット。

【請求項29】

前記フォーマットが、前記ビットストリームを符号化するのに使用される少なくとも1つのパラメータを少なくとも部分的に示すパラメータデータを含む、請求項21に記載のデータ保管フォーマット。

【請求項30】

前記ビットストリームの少なくとも一部が、少なくとも1つのデータブロックとして符号化され、前記データブロックが、少なくともいくつかのパラメータデータと少なくともいくつかの符号化されたデータとを符号化する、請求項29に記載のデータ保管フォーマット。

【請求項31】

各データブロックが、複数の可能な値を定義するマークの配置を定義するデータグリッドを含み、前記データグリッドの少なくとも第1列および最後の列が、前記パラメータデータを符号化するのに使用される、請求項30に記載のデータ保管フォーマット。

【請求項32】

前記パラメータデータが、

前記符号化されたデータのサイズを示し、

インターリーブファクタを示し、

パラメータに関連するチェックサムと、

パラメータに関連するCRCチェックサムと、

パラメータに関連する冗長性データと、

パラメータに関連するリード−ソロモン冗長性データと、

パラメータの複製およびチェックサムと

のうちの少なくとも1つを使用してフォールトトレラントに符号化される

のうちの少なくとも1つである、請求項29に記載のデータ保管フォーマット。

【請求項33】

前記位置合わせデータが、パイロット特徴を含み、前記パイロット特徴が、

フォールトトレラントに符号化され、

平行ラインの組から形成され、

2進パイロットシーケンスを符号化する平行ラインの組から形成され、

110101100100011と、

110010001111010と

のうちの少なくとも1つを符号化するパイロットシーケンスである

のうちの1つである、請求項22に記載のデータ保管フォーマット。

【請求項34】

符号化されたデータを復号するシステムであって、前記符号化されたデータが、

符号化されたビットストリームと、

前記ビットストリームに関連する冗長性データと

を含み、前記システムが、

前記符号化されたデータを保管するストアと、

デコーダであって、

前記符号化されたデータのコードワードフォーマットを判定し、

前記ストアから、前記判定されたフォーマットを使用して、符号化されたデータを読み取り、前記符号化されたデータが、前記符号化されたビットストリームおよび前記冗長性データを複数のコードワードのそれぞれにデインターリーブするために読み取られ、各コードワードが、ビットストリーム部分および対応する冗長性データを含み、

前記ビットストリーム部分および前記対応する冗長性データを使用して、前記符号化されたビットストリーム内の誤りを訂正し、

前記訂正されたデータを前記ストアに書き込む

デコーダと

を含む、システム。

【請求項35】

前記デコーダが、

前記位置合わせデータを使用して、各スキャンンラインの変換を判定することであって、前記変換が、前記データ部分内のビット符号化位置の座標を示す、判定することと、

前記変換を使用してビット値を検出することと

によって前記符号化されたデータを復号する、請求項34に記載のシステム。

【請求項36】

前記デコーダが、

前記ビット符号化位置の前記座標からサンプル値の座標を判定し、

2つの連続するサンプルラインからのサンプル値を補間することによってビット符号化値を判定する

請求項35に記載のシステム。

【請求項37】

前記デコーダが、

3つ以上の可能な値を有する復号されたビットストリームビットに一時値を割り当て、

前記ビットの2進値を、データ符号化区域内の周囲のビットの値に基づいて解決し、

解決された符号化されたビットストリームビット値をビットストリーム順でストレージデバイスに書き込む

請求項36に記載のシステム。

【請求項38】

前記デコーダが、

粗レジストレーションを判定するために少なくとも1つのマーカの位置を判定し、

前記粗レジストレーションを使用して、クロックトラック内のクロックインジケータを判定し、

前記クロックインジケータを使用して、位置合わせPLLを更新し、

前記位置合わせPLLを使用して、前記位置合わせ方向で前記符号化されたデータの微細レジストレーションを判定する

請求項34に記載のシステム。

【請求項39】

前記符号化されたデータが、レジストレーション構造を含み、前記レジストレーション構造が、前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、クロックトラックごとに2つの位置合わせ線とを含み、前記2つの位置合わせ線が、前記めいめいのクロックトラックの位置を示し、前記デコーダが、

位置合わせPLLを使用して、めいめいのクロックトラックの前記位置合わせ線の位置を判定し、

前記位置合わせ線の前記位置を使用して、各めいめいのトラックの位置を判定し、

前記位置合わせPLLを更新する

請求項34に記載のシステム。

【請求項40】

前記デコーダが、

クロックトラックごとに、めいめいのデータクロックPLLを使用して、前記クロックトラック上のクロックインジケータの位置を判定し、

各クロックトラック上の前記クロックインジケータの前記位置を使用して、位置合わせ角度を判定し、

各データクロックPLLを更新する

請求項39に記載のシステム。

【請求項41】

表面に印刷するノズルの少なくとも1つの行を有する細長い印字ヘッドと、

表面上のマーキングを感知する画素センサの少なくとも1つの行を有する細長いイメージセンサと

を含むモノリシック集積回路。

【請求項42】

前記回路が、

前記印字ヘッドを使用して、符号化されたデータを印刷することと、

前記イメージセンサを使用して、符号化されたデータを感知することと

のうちの少なくとも1つに使用される、請求項41に記載のモノリシック集積回路。

【請求項43】

前記符号化されたデータが、

少なくとも1つのデータ部分であって、前記少なくとも1つのデータ部分が、ビットストリームとそれに続く対応する冗長性データとを含むデータシーケンスを符号化し、前記データシーケンスが、インターリーブされたコードワードを形成し、各コードワードが、前記ビットストリームの少なくとも一部と前記めいめいのビットストリーム一部に関連する冗長性データとを符号化する、少なくとも1つのデータ部分

を含む、請求項42に記載のモノリシック集積回路。

【請求項44】

前記符号化されたデータが、

前記表面の上または中のめいめいの位置に配置された少なくとも1つのデータ部分と、

前記表面の上または中に配置された位置合わせデータであって、前記位置合わせデータが、少なくとも2つのレジストレーション位置を少なくとも部分的に示し、前記レジストレーション位置が、前記表面に関する前記少なくとも1つのデータ部分の相対位置を少なくとも部分的に示し、これによって、前記少なくとも1つのデータ部分を少なくとも部分的に復号することを可能にする、位置合わせデータと

を含む、請求項42に記載のモノリシック集積回路。

【請求項45】

前記印字ヘッドが、

各データ部分が位置合わせ方向に延び、少なくとも1つの第1データ部分が前記位置合わせ方向に垂直な第2方向で少なくとも1つの第2データ部分から変位されるように、前記表面の上または中に前記データ部分を印刷することと、

前記データ部分の少なくともいくつかの配置を示す位置合わせデータを印刷することと

によって前記符号化されたデータを印刷する、請求項42に記載のモノリシック集積回路。

【請求項46】

前記画素センサが、

少なくとも2つの位置の前記位置合わせデータの少なくとも一部を感知することであって、前記感知された位置合わせデータが、前記イメージセンサと前記位置合わせ方向との間の角度を判定するのに使用される、感知することと、

前記少なくとも1つの第1データ部分の少なくとも一部を感知することであって、前記感知されたデータ部分が、前記少なくとも1つの第2データ部分が感知される前に、前記判定された角度を使用して少なくとも部分的に復号された、前記少なくとも1つの感知された第1データ部分である、感知することと

によって前記符号化されたデータを感知する、請求項45に記載のモノリシック集積回路。

【請求項47】

前記符号化されたデータが、

位置合わせ方向での前記符号化されたデータの位置を示す複数の基準点を含む第1レジストレーション構造と、

前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す複数の基準点を含む第2レジストレーション構造と

のうちの少なくとも1つを含む、請求項45に記載のモノリシック集積回路。

【請求項48】

前記符号化されたデータが、少なくとも1つのデータブロックを含み、前記データブロックが、

複数の可能な値を定義するマークの配置と、

前記マークの位置を示す位置合わせデータと

を含む、請求項42に記載のモノリシック集積回路。

【請求項49】

各データブロックが、複数の可能な値を定義するマークの配置を定義するデータグリッドを含み、前記データグリッドの少なくとも第1列および最後の列が、符号化されたデータの生成に使用されるパラメータデータを符号化するのに使用される、請求項48に記載のモノリシック集積回路。

【請求項50】

前記データが、フォールトトレラントにデータを符号化するために、複数のインターリーブされたコードワードを使用して符号化される、請求項42に記載のモノリシック集積回路。

【請求項51】

前記印字ヘッドが、

インクジェット印字ヘッドと、

Memjet(商標)印字ヘッドと

のうちの少なくとも1つである、請求項41に記載のモノリシック集積回路。

【請求項52】

前記イメージセンサが、

アクティブ画素CMOSイメージセンサと、

CCDイメージセンサと

のうちの少なくとも1つである、請求項41に記載のモノリシック集積回路。

【請求項53】

前記印字ヘッドが、

実質的に不可視のインクを使用するフォーマットと、

赤外線吸収インクを使用するフォーマットと、

可視インクを使用する可視情報と、

媒体の実質的に同一の区域内の可視情報および前記実質的に不可視のフォーマットと、

実質的に同一の時の前記可視情報および前記実質的に不可視のフォーマットと、

netpage符号化されたデータと

のうちの少なくとも1つを印刷するように構成される、請求項41に記載のモノリシック集積回路。

【請求項54】

表面に印刷するノズルの少なくとも1つの行を有する細長い印字ヘッドと、

前記表面上のマーキングを感知する画素センサの少なくとも1つの行を有する細長いイメージセンサと

を含むモノリシック集積回路を組み込んだデバイス。

【請求項55】

搬送経路と、

ハウジングであって、

前記集積回路を含む空洞と、

前記搬送経路内に供給される媒体に小滴を置くことを可能にするための小滴吐出経路を画定するスロットと

を含むハウジングと、

少なくとも1つのインク供給と、

前記少なくとも1つのインク供給から前記モノリシック集積回路の表面に設けられた1つまたは複数の入口にンクを供給するインク供給モールディングと、

前記媒体を露光する少なくとも1つの放射源と、

前記媒体からの放射を前記画素センサにフォーカシングする少なくとも1つのフォーカシング要素と

を含む、請求項41に記載のデバイス。

【請求項56】

印刷される前記マーキングを示すデータを保管するドットシフトレジスタと、

前記ノズルの発射を制御するデータを保管する発射シフトレジスタと、

前記発射シフトレジスタにデータを保管するノズルタイミングおよび制御ブロックと

を含むコントローラを含む、請求項41に記載のデバイス。

【請求項57】

前記感知されたマーキングを示す信号を前記画素センサに出力させる画素制御ブロックと、

多重化された信号を形成するために前記信号を多重化するマルチプレクサと、

増幅された多重化された信号を形成するために前記多重化された信号を増幅する増幅器と、

前記増幅された多重化された信号を前記感知されたマーキングを示すデータに変換するアナログ−ディジタル変換器と

を含むコントローラを含む、請求項41に記載のデバイス。

【請求項58】

前記イメージセンサを通って前記媒体を搬送する少なくとも1つの搬送モータと、

ビットストリームデータを保管するストレージデバイスと、

前記媒体の存在を検出する少なくとも1つの媒体検出器と、

復号システムを制御するホストコントローラと

のうちの少なくとも1つを含む、請求項41に記載のデバイス。

【請求項59】

プリンタと、

リーダと、

復号システムと、

カメラと、

携帯電話機と

のうちの少なくとも1つを含む、請求項41に記載のデバイス。

【請求項60】

表面に符号化されたデータを印刷する印字ヘッドと、

前記表面上の符号化されたデータを感知するのに使用される感知デバイスと

を含むモノリシック集積回路であって、

使用中に、前記集積回路が、それぞれ符号化されたデータの印刷または感知のために前記印字ヘッドおよび前記感知デバイスを通って前記表面を移動できるようにするために搬送モジュールに隣接して設けられる

モノリシック集積回路。

【請求項1】

符号化されたデータをその中またはその上に配置された表面であって、前記符号化されたデータが、

前記表面の上または中のめいめいの位置に配置された少なくとも1つのデータ部分と、

前記表面の上または中に配置された位置合わせデータであって、前記位置合わせデータが、少なくとも2つのレジストレーション位置を少なくとも部分的に示し、前記レジストレーション位置が、前記表面に関する前記少なくとも1つのデータ部分の相対位置を少なくとも部分的に示し、これによって、前記少なくとも1つのデータ部分を少なくとも部分的に復号することを可能にする、位置合わせデータと

を含む、表面。

【請求項2】

前記位置合わせデータが、

位置合わせ方向での前記符号化されたデータの位置を示す複数の基準点を示す第1レジストレーション構造と、

前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す複数の基準点を示す第2レジストレーション構造と

を含む、請求項1に記載の表面。

【請求項3】

前記第1レジストレーション構造が、

前記位置合わせ方向での前記符号化されたデータの粗位置を示す複数のマーカと、

前記位置合わせ方向での前記符号化されたデータの微細位置を示すクロックトラックと

を含む、請求項2に記載の表面。

【請求項4】

前記第2レジストレーション構造が、

前記位置合わせ方向に垂直な前記方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、

クロックトラックごとに2つの、前記位置合わせ方向での前記めいめいのクロックトラックの位置を示す、位置合わせ線と

を含む、請求項2に記載の表面。

【請求項5】

フォーマットが、少なくとも1つのデータブロックを含み、前記データブロックが、

複数の可能な値を定義するマークの配置と、

前記マークの位置を示す位置合わせデータと

を含む、請求項1に記載の表面。

【請求項6】

各データブロックが、

それ自体のパイロットトラックを設けられ、

それ自体のレジストレーション特徴を設けられ、

それ自体のクロッキング特徴を設けられ、

データ符号化区域の向かい合わせの側面に2つのクロッキング特徴を設けられ、

ビットストリームのフラグメントを符号化し、

データ符号化区域内でビットストリームのフラグメントを符号化し、

長方形データ符号化区域から形成される

のうちの少なくとも1つである、請求項5に記載の表面。

【請求項7】

データが、パラメータデータを使用して符号化され、各データブロックが、前記パラメータデータのうちの少なくともいくつかを符号化し、前記パラメータデータが、

前記符号化されたデータのサイズを示し、

インターリーブファクタを示し、

パラメータに関連するチェックサムと、

パラメータに関連するCRCチェックサムと、

パラメータに関連する冗長性データと、

パラメータに関連するリード−ソロモン冗長性データと、

パラメータの複製およびチェックサムと

のうちの少なくとも1つを使用してフォールトトレラントに符号化される

のうちの少なくとも1つである、請求項5に記載の表面。

【請求項8】

前記データが、フォールトトレラントにデータを符号化するために、複数のインターリーブされたコードワードを使用して符号化される、請求項1に記載の表面。

【請求項9】

前記位置合わせデータが、パイロット特徴を含み、前記パイロット特徴が、

フォールトトレラントに符号化され、

平行ラインの組から形成され、

2進パイロットシーケンスを符号化する平行ラインの組から形成され、

110101100100011と、

110010001111010と

のうちの少なくとも1つを符号化するパイロットシーケンスである

のうちの1つである、請求項1に記載の表面。

【請求項10】

符号化されたデータをその中またはその上に配置された表面であって、前記符号化されたデータが、

前記表面の上または中のめいめいの位置に配置された少なくとも1つのデータ部分であって、各データ部分が、位置合わせ方向に延びる、データ部分と、

前記表面の上または中に配置された位置合わせデータと

を含み、使用中に、スキャンライン方向に延びる感知領域内に供給されるデータを感知する感知デバイスが、

少なくとも2つの位置の前記位置合わせデータと、

前記複数のデータ部分のうちの少なくとも1つの少なくとも一部と

を感知し、

少なくとも2つのレジストレーション位置を使用して、前記スキャンライン方向と前記位置合わせ方向との間の位置合わせ角度を判定し、

少なくとも1つのレジストレーション位置および前記位置合わせ角度を使用して、前記感知領域に関する前記少なくとも1つの感知されたデータ部分の相対位置を判定し、

前記相対位置および前記位置合わせ角度を使用して、前記少なくとも1つのデータ部分を少なくとも部分的に復号する

ように動作する、表面。

【請求項11】

表面の上または中に設けられた符号化されたデータを復号するシステムであって、前記符号化されたデータが、

前記表面の上または中に配置された少なくとも1つのデータ部分と、

少なくとも1つのクロックインジケータを少なくとも部分的に示す位置合わせデータと

を含み、前記システムが、

感知領域内に供給されるデータを感知するセンサであって、

前記位置合わせデータの少なくとも一部と、

前記少なくとも1つのデータ部分の少なくとも一部と

を感知する、センサと、

デコーダであって、

前記感知された位置合わせデータ一部を使用して、前記クロックインジケータを判定し、

前記クロックインジケータを使用して、PLLを更新し、

前記PLLを使用して、前記感知領域と前記少なくとも1つの感知されたデータ部分との間の相対位置を判定し、

前記相対位置を使用して、前記少なくとも1つのデータ部分を少なくとも部分的に復号する

デコーダと

を含む、システム。

【請求項12】

前記デコーダが、

粗レジストレーションを判定するために少なくとも1つのマーカの位置を判定し、

前記粗レジストレーションを使用して、クロックトラック内のクロックインジケータを判定し、

前記クロックインジケータを使用して、位置合わせPLLを更新し、

前記位置合わせPLLを使用して、前記位置合わせ方向での前記符号化されたデータの微細レジストレーションを判定する

請求項11に記載のシステム。

【請求項13】

前記符号化されたデータが、レジストレーション構造を含み、前記レジストレーション構造が、前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、クロックトラックごとに2つの位置合わせ線とを含み、前記2つの位置合わせ線が、前記めいめいのクロックトラックの位置を示し、前記デコーダが、

位置合わせPLLを使用して、めいめいのクロックトラックの前記位置合わせ線の位置を判定し、

前記位置合わせ線の前記位置を使用して、各めいめいのクロックトラックの位置を判定し、

前記位置合わせPLLを更新する

請求項11に記載のシステム。

【請求項14】

前記デコーダが、

クロックトラックごとに、めいめいのデータクロックPLLを使用して、前記クロックトラック上のクロックインジケータの位置を判定し、

各クロックトラック上の前記クロックインジケータの前記位置を使用して、位置合わせ角度を判定し、

各データクロックPLLを更新する

請求項13に記載のシステム。

【請求項15】

前記デコーダが、

前記位置合わせデータを使用して、スキャンンラインの変換を判定することであって、前記変換が、前記データ部分内のビット符号化位置の座標を示す、判定することと、

前記変換を使用してビット値を検出することと

によって前記符号化されたデータを復号する、請求項11に記載のシステム。

【請求項16】

前記デコーダが、

前記ビット符号化位置の前記座標からサンプル値の座標を判定し、

2つの連続するスキャンラインからのサンプル値を補間することによってビット符号化値を判定する

請求項15に記載のシステム。

【請求項17】

前記デコーダが、

3つ以上の可能な値を有する復号されたビットストリームビットに一時値を割り当て、

前記ビットの2進値を、データ符号化区域内の周囲のビットの値に基づいて解決し、

解決された符号化されたビットストリームビット値をビットストリーム順でストレージデバイスに書き込む

請求項16に記載のシステム。

【請求項18】

前記デコーダが、

前記位置合わせデータ内でパイロット特徴を検出し、前記パイロット特徴が、少なくとも2つの位置で検出され、

前記パイロット特徴を使用して、

スキャンライン方向と位置合わせ方向との間の位置合わせ角度と、

前記位置合わせ方向に垂直な方向での初期レジストレーションと

を判定し、

前記位置合わせデータ内でレジストレーション特徴内のレジストレーションマーカを検出し、

前記レジストレーションマーカを使用して、前記位置合わせ方向での粗レジストレーションを判定し、

前記粗レジストレーションを使用して、前記位置合わせデータ内でレジストレーションクロックインジケータを検出し、

前記レジストレーションクロックインジケータを使用して、前記位置合わせ方向での微細レジストレーションを判定し、

前記微細レジストレーション、前記位置合わせ角度、および前記初期レジストレーションを使用して、少なくとも1つの位置合わせ線を検出し、

前記少なくとも1つの検出された位置合わせ線を使用して、前記微細レジストレーションを更新し、

前記更新された微細レジストレーションを使用して、前記位置合わせデータ内の2つのデータクロックトラックの位置を判定し、

前記データクロックトラックの前記位置を使用して、各データクロックトラック上のデータクロックインジケータを検出し、

各データクロックインジケータを使用して、更新された位置合わせ角度および前記位置合わせ方向に垂直な方向での更新されたレジストレーションを判定し、

前記少なくとも1つのデータ部分の少なくとも一部を検出し、

前記更新された位置合わせ角度、前記微細レジストレーション、および前記更新されたレジストレーションを使用して、前記少なくとも1つの検出されたデータ部分の少なくとも一部を復号する

請求項11に記載のシステム。

【請求項19】

前記デコーダが、繰り返して、

前記少なくとも1つの位置合わせ線を検出し、

前記微細レジストレーションを更新し、

前記更新された微細レジストレーションおよび前記更新されたレジストレーションを使用して、前記データクロックトラックの前記位置を判定し、

各データクロックトラック上のデータクロックインジケータを検出し、

前記更新された位置合わせ角度および前記更新されたレジストレーションを更新し、

これによって前記少なくとも1つのデータ部分を復号できるようにするために、前記少なくとも1つのデータ部分の少なくとも一部を検出する

請求項18に記載のシステム。

【請求項20】

前記デコーダが、

前記パイロット特徴の2つの位置でクロックインジケータを検出し、

これによって前記パイロット特徴を追跡するために、めいめいのパイロットPLLを各クロックインジケータに同期させ、

前記パイロットPLLを使用して、

前記位置合わせ角度と、

前記初期レジストレーションと

を判定し、

前記初期レジストレーションおよび前記位置合わせ角度を使用して、2つのデータクロックPLLを初期化し、

前記位置合わせデータ内の前記レジストレーションマーカを検出し、

前記レジストレーションマーカを使用して、前記粗レジストレーションを判定し、

これによって前記レジストレーション特徴を追跡するために、前記粗レジストレーションを使用して、レジストレーションPLLを前記位置合わせデータ内の前記レジストレーションクロックインジケータに同期させ、

前記レジストレーションPLLを使用して、前記微細レジストレーションを判定し、

前記微細レジストレーションを使用して、2つの位置合わせPLLを初期化し、

これによって前記データクロックトラックを追跡するために、前記位置合わせPLLを位置合わせマーカに同期させ、

前記位置合わせPLLを使用して、前記位置合わせデータ内の2つのデータクロックトラックの前記位置を判定し、

前記データクロックトラックの前記位置を使用して、各データクロックトラック上のデータクロックインジケータを検出し、

これによって前記位置合わせ方向に垂直な前記方向で前記データのレジストレーションを追跡するために、各データクロックPLLを対応するデータクロックインジケータに同期させ、

前記データクロックPLLを使用して、

前記更新された位置合わせ角度と、

前記表面上の符号化されたデータの前記位置と

のうちの少なくとも1つを判定する

請求項18に記載のシステム。

【請求項21】

表面の上または中でビットストリームを符号化するデータ保管フォーマットであって、

少なくとも1つのデータ部分であって、前記少なくとも1つのデータ部分が、前記ビットストリームとそれに続く対応する冗長性データとを含むデータシーケンスを符号化し、前記データシーケンスが、インターリーブされたコードワードを形成し、各コードワードが、前記ビットストリームの少なくとも一部と前記めいめいのビットストリーム一部に関連する冗長性データとを符号化する、少なくとも1つのデータ部分

を含むデータ保管フォーマット。

【請求項22】

前記フォーマットが、前記表面の上または中に配置された位置合わせデータを含み、前記位置合わせデータが、前記表面上の前記データ部分の位置を少なくとも部分的に示す、請求項21に記載のデータ保管フォーマット。

【請求項23】

前記位置合わせデータが、

位置合わせ方向での符号化されたデータの位置を示す複数の基準点を示す第1レジストレーション構造と、

前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す複数の基準点を示す第2レジストレーション構造と

を含む、請求項22に記載のデータ保管フォーマット。

【請求項24】

前記第1レジストレーション構造が、

前記位置合わせ方向での前記符号化されたデータの粗位置を示す複数のマーカと、

前記位置合わせ方向での前記符号化されたデータの微細位置を示すクロックトラックと

を含む、請求項23に記載のデータ保管フォーマット。

【請求項25】

前記第2レジストレーション構造が、

前記位置合わせ方向に垂直な前記方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、

クロックトラックごとに2つの、前記位置合わせ方向での前記めいめいのクロックトラックの位置を示す、位置合わせ線と

を含む、請求項23に記載のデータ保管フォーマット。

【請求項26】

前記フォーマットが、少なくとも1つのデータブロックを含み、前記データブロックが、

複数の可能な値を定義するマークの配置と、

前記マークの位置を示す位置合わせデータと

を含む、請求項21に記載のデータ保管フォーマット。

【請求項27】

各データブロックが、

それ自体のパイロットトラックを設けられ、

それ自体のレジストレーション特徴を設けられ、

それ自体のクロッキング特徴を設けられ、

データ符号化区域の向かい合わせの側面に2つのクロッキング特徴を設けられ、

ビットストリームのフラグメントを符号化し、

データ符号化区域内でビットストリームのフラグメントを符号化し、

長方形データ符号化区域から形成される

のうちの少なくとも1つである、請求項26に記載のデータ保管フォーマット。

【請求項28】

前記データが、フォールトトレラントにデータを符号化するために、複数のインターリーブされたコードワードを使用して符号化される、請求項21に記載のデータ保管フォーマット。

【請求項29】

前記フォーマットが、前記ビットストリームを符号化するのに使用される少なくとも1つのパラメータを少なくとも部分的に示すパラメータデータを含む、請求項21に記載のデータ保管フォーマット。

【請求項30】

前記ビットストリームの少なくとも一部が、少なくとも1つのデータブロックとして符号化され、前記データブロックが、少なくともいくつかのパラメータデータと少なくともいくつかの符号化されたデータとを符号化する、請求項29に記載のデータ保管フォーマット。

【請求項31】

各データブロックが、複数の可能な値を定義するマークの配置を定義するデータグリッドを含み、前記データグリッドの少なくとも第1列および最後の列が、前記パラメータデータを符号化するのに使用される、請求項30に記載のデータ保管フォーマット。

【請求項32】

前記パラメータデータが、

前記符号化されたデータのサイズを示し、

インターリーブファクタを示し、

パラメータに関連するチェックサムと、

パラメータに関連するCRCチェックサムと、

パラメータに関連する冗長性データと、

パラメータに関連するリード−ソロモン冗長性データと、

パラメータの複製およびチェックサムと

のうちの少なくとも1つを使用してフォールトトレラントに符号化される

のうちの少なくとも1つである、請求項29に記載のデータ保管フォーマット。

【請求項33】

前記位置合わせデータが、パイロット特徴を含み、前記パイロット特徴が、

フォールトトレラントに符号化され、

平行ラインの組から形成され、

2進パイロットシーケンスを符号化する平行ラインの組から形成され、

110101100100011と、

110010001111010と

のうちの少なくとも1つを符号化するパイロットシーケンスである

のうちの1つである、請求項22に記載のデータ保管フォーマット。

【請求項34】

符号化されたデータを復号するシステムであって、前記符号化されたデータが、

符号化されたビットストリームと、

前記ビットストリームに関連する冗長性データと

を含み、前記システムが、

前記符号化されたデータを保管するストアと、

デコーダであって、

前記符号化されたデータのコードワードフォーマットを判定し、

前記ストアから、前記判定されたフォーマットを使用して、符号化されたデータを読み取り、前記符号化されたデータが、前記符号化されたビットストリームおよび前記冗長性データを複数のコードワードのそれぞれにデインターリーブするために読み取られ、各コードワードが、ビットストリーム部分および対応する冗長性データを含み、

前記ビットストリーム部分および前記対応する冗長性データを使用して、前記符号化されたビットストリーム内の誤りを訂正し、

前記訂正されたデータを前記ストアに書き込む

デコーダと

を含む、システム。

【請求項35】

前記デコーダが、

前記位置合わせデータを使用して、各スキャンンラインの変換を判定することであって、前記変換が、前記データ部分内のビット符号化位置の座標を示す、判定することと、

前記変換を使用してビット値を検出することと

によって前記符号化されたデータを復号する、請求項34に記載のシステム。

【請求項36】

前記デコーダが、

前記ビット符号化位置の前記座標からサンプル値の座標を判定し、

2つの連続するサンプルラインからのサンプル値を補間することによってビット符号化値を判定する

請求項35に記載のシステム。

【請求項37】

前記デコーダが、

3つ以上の可能な値を有する復号されたビットストリームビットに一時値を割り当て、

前記ビットの2進値を、データ符号化区域内の周囲のビットの値に基づいて解決し、

解決された符号化されたビットストリームビット値をビットストリーム順でストレージデバイスに書き込む

請求項36に記載のシステム。

【請求項38】

前記デコーダが、

粗レジストレーションを判定するために少なくとも1つのマーカの位置を判定し、

前記粗レジストレーションを使用して、クロックトラック内のクロックインジケータを判定し、

前記クロックインジケータを使用して、位置合わせPLLを更新し、

前記位置合わせPLLを使用して、前記位置合わせ方向で前記符号化されたデータの微細レジストレーションを判定する

請求項34に記載のシステム。

【請求項39】

前記符号化されたデータが、レジストレーション構造を含み、前記レジストレーション構造が、前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す少なくとも2つのクロックトラックと、クロックトラックごとに2つの位置合わせ線とを含み、前記2つの位置合わせ線が、前記めいめいのクロックトラックの位置を示し、前記デコーダが、

位置合わせPLLを使用して、めいめいのクロックトラックの前記位置合わせ線の位置を判定し、

前記位置合わせ線の前記位置を使用して、各めいめいのトラックの位置を判定し、

前記位置合わせPLLを更新する

請求項34に記載のシステム。

【請求項40】

前記デコーダが、

クロックトラックごとに、めいめいのデータクロックPLLを使用して、前記クロックトラック上のクロックインジケータの位置を判定し、

各クロックトラック上の前記クロックインジケータの前記位置を使用して、位置合わせ角度を判定し、

各データクロックPLLを更新する

請求項39に記載のシステム。

【請求項41】

表面に印刷するノズルの少なくとも1つの行を有する細長い印字ヘッドと、

表面上のマーキングを感知する画素センサの少なくとも1つの行を有する細長いイメージセンサと

を含むモノリシック集積回路。

【請求項42】

前記回路が、

前記印字ヘッドを使用して、符号化されたデータを印刷することと、

前記イメージセンサを使用して、符号化されたデータを感知することと

のうちの少なくとも1つに使用される、請求項41に記載のモノリシック集積回路。

【請求項43】

前記符号化されたデータが、

少なくとも1つのデータ部分であって、前記少なくとも1つのデータ部分が、ビットストリームとそれに続く対応する冗長性データとを含むデータシーケンスを符号化し、前記データシーケンスが、インターリーブされたコードワードを形成し、各コードワードが、前記ビットストリームの少なくとも一部と前記めいめいのビットストリーム一部に関連する冗長性データとを符号化する、少なくとも1つのデータ部分

を含む、請求項42に記載のモノリシック集積回路。

【請求項44】

前記符号化されたデータが、

前記表面の上または中のめいめいの位置に配置された少なくとも1つのデータ部分と、

前記表面の上または中に配置された位置合わせデータであって、前記位置合わせデータが、少なくとも2つのレジストレーション位置を少なくとも部分的に示し、前記レジストレーション位置が、前記表面に関する前記少なくとも1つのデータ部分の相対位置を少なくとも部分的に示し、これによって、前記少なくとも1つのデータ部分を少なくとも部分的に復号することを可能にする、位置合わせデータと

を含む、請求項42に記載のモノリシック集積回路。

【請求項45】

前記印字ヘッドが、

各データ部分が位置合わせ方向に延び、少なくとも1つの第1データ部分が前記位置合わせ方向に垂直な第2方向で少なくとも1つの第2データ部分から変位されるように、前記表面の上または中に前記データ部分を印刷することと、

前記データ部分の少なくともいくつかの配置を示す位置合わせデータを印刷することと

によって前記符号化されたデータを印刷する、請求項42に記載のモノリシック集積回路。

【請求項46】

前記画素センサが、

少なくとも2つの位置の前記位置合わせデータの少なくとも一部を感知することであって、前記感知された位置合わせデータが、前記イメージセンサと前記位置合わせ方向との間の角度を判定するのに使用される、感知することと、

前記少なくとも1つの第1データ部分の少なくとも一部を感知することであって、前記感知されたデータ部分が、前記少なくとも1つの第2データ部分が感知される前に、前記判定された角度を使用して少なくとも部分的に復号された、前記少なくとも1つの感知された第1データ部分である、感知することと

によって前記符号化されたデータを感知する、請求項45に記載のモノリシック集積回路。

【請求項47】

前記符号化されたデータが、

位置合わせ方向での前記符号化されたデータの位置を示す複数の基準点を含む第1レジストレーション構造と、

前記位置合わせ方向に垂直な方向での前記符号化されたデータの位置を示す複数の基準点を含む第2レジストレーション構造と

のうちの少なくとも1つを含む、請求項45に記載のモノリシック集積回路。

【請求項48】

前記符号化されたデータが、少なくとも1つのデータブロックを含み、前記データブロックが、

複数の可能な値を定義するマークの配置と、

前記マークの位置を示す位置合わせデータと

を含む、請求項42に記載のモノリシック集積回路。

【請求項49】

各データブロックが、複数の可能な値を定義するマークの配置を定義するデータグリッドを含み、前記データグリッドの少なくとも第1列および最後の列が、符号化されたデータの生成に使用されるパラメータデータを符号化するのに使用される、請求項48に記載のモノリシック集積回路。

【請求項50】

前記データが、フォールトトレラントにデータを符号化するために、複数のインターリーブされたコードワードを使用して符号化される、請求項42に記載のモノリシック集積回路。

【請求項51】

前記印字ヘッドが、

インクジェット印字ヘッドと、

Memjet(商標)印字ヘッドと

のうちの少なくとも1つである、請求項41に記載のモノリシック集積回路。

【請求項52】

前記イメージセンサが、

アクティブ画素CMOSイメージセンサと、

CCDイメージセンサと

のうちの少なくとも1つである、請求項41に記載のモノリシック集積回路。

【請求項53】

前記印字ヘッドが、

実質的に不可視のインクを使用するフォーマットと、

赤外線吸収インクを使用するフォーマットと、

可視インクを使用する可視情報と、

媒体の実質的に同一の区域内の可視情報および前記実質的に不可視のフォーマットと、

実質的に同一の時の前記可視情報および前記実質的に不可視のフォーマットと、

netpage符号化されたデータと

のうちの少なくとも1つを印刷するように構成される、請求項41に記載のモノリシック集積回路。

【請求項54】

表面に印刷するノズルの少なくとも1つの行を有する細長い印字ヘッドと、

前記表面上のマーキングを感知する画素センサの少なくとも1つの行を有する細長いイメージセンサと

を含むモノリシック集積回路を組み込んだデバイス。

【請求項55】

搬送経路と、

ハウジングであって、

前記集積回路を含む空洞と、

前記搬送経路内に供給される媒体に小滴を置くことを可能にするための小滴吐出経路を画定するスロットと

を含むハウジングと、

少なくとも1つのインク供給と、

前記少なくとも1つのインク供給から前記モノリシック集積回路の表面に設けられた1つまたは複数の入口にンクを供給するインク供給モールディングと、

前記媒体を露光する少なくとも1つの放射源と、

前記媒体からの放射を前記画素センサにフォーカシングする少なくとも1つのフォーカシング要素と

を含む、請求項41に記載のデバイス。

【請求項56】

印刷される前記マーキングを示すデータを保管するドットシフトレジスタと、

前記ノズルの発射を制御するデータを保管する発射シフトレジスタと、

前記発射シフトレジスタにデータを保管するノズルタイミングおよび制御ブロックと

を含むコントローラを含む、請求項41に記載のデバイス。

【請求項57】

前記感知されたマーキングを示す信号を前記画素センサに出力させる画素制御ブロックと、

多重化された信号を形成するために前記信号を多重化するマルチプレクサと、

増幅された多重化された信号を形成するために前記多重化された信号を増幅する増幅器と、

前記増幅された多重化された信号を前記感知されたマーキングを示すデータに変換するアナログ−ディジタル変換器と

を含むコントローラを含む、請求項41に記載のデバイス。

【請求項58】

前記イメージセンサを通って前記媒体を搬送する少なくとも1つの搬送モータと、

ビットストリームデータを保管するストレージデバイスと、

前記媒体の存在を検出する少なくとも1つの媒体検出器と、

復号システムを制御するホストコントローラと

のうちの少なくとも1つを含む、請求項41に記載のデバイス。

【請求項59】

プリンタと、

リーダと、

復号システムと、

カメラと、

携帯電話機と

のうちの少なくとも1つを含む、請求項41に記載のデバイス。

【請求項60】

表面に符号化されたデータを印刷する印字ヘッドと、

前記表面上の符号化されたデータを感知するのに使用される感知デバイスと

を含むモノリシック集積回路であって、

使用中に、前記集積回路が、それぞれ符号化されたデータの印刷または感知のために前記印字ヘッドおよび前記感知デバイスを通って前記表面を移動できるようにするために搬送モジュールに隣接して設けられる

モノリシック集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【公表番号】特表2007−538308(P2007−538308A)

【公表日】平成19年12月27日(2007.12.27)

【国際特許分類】

【出願番号】特願2007−505324(P2007−505324)

【出願日】平成17年3月21日(2005.3.21)

【国際出願番号】PCT/AU2005/000391

【国際公開番号】WO2005/096219

【国際公開日】平成17年10月13日(2005.10.13)

【出願人】(303024600)シルバーブルック リサーチ ピーティワイ リミテッド (150)

【Fターム(参考)】

【公表日】平成19年12月27日(2007.12.27)

【国際特許分類】

【出願日】平成17年3月21日(2005.3.21)

【国際出願番号】PCT/AU2005/000391

【国際公開番号】WO2005/096219

【国際公開日】平成17年10月13日(2005.10.13)

【出願人】(303024600)シルバーブルック リサーチ ピーティワイ リミテッド (150)

【Fターム(参考)】

[ Back to top ]