モータ速度制御装置、及び画像形成装置

【課題】安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供する。

【解決手段】本発明のモータ速度制御装置120は、tgt_frqに基づくrefclkを出力する基準クロック発生器101と、モータ107の所定回転角度ごとに所定数のfgを出力するエンコーダ108と、refpulseを出力する分周器102と、整数位相差ph_intとして出力する整数位相差検出器103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frcとして出力する小数位相差検出器104と、ph_intとph_frcを混合器105で所定の比率で加算してpherrとし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

【解決手段】本発明のモータ速度制御装置120は、tgt_frqに基づくrefclkを出力する基準クロック発生器101と、モータ107の所定回転角度ごとに所定数のfgを出力するエンコーダ108と、refpulseを出力する分周器102と、整数位相差ph_intとして出力する整数位相差検出器103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frcとして出力する小数位相差検出器104と、ph_intとph_frcを混合器105で所定の比率で加算してpherrとし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、モータ速度制御装置に関し、特に、PLL制御により回転制御されるモータの速度制御装置の回路構成に関するものである。

【背景技術】

【0002】

電子回路において、位相同期ループ(Phase Locked Loop:PLL)技術はよく知られている。一般にPLLは、外部から印加された制御電圧に比例した周波数で発振する電圧制御発振器(VCO)の出力パルス或いはその分周パルスと、基準周波数を持ったパルスとの位相差を検出して、検出した位相差をVCOにフィードバックすることで位相同期を実現している。

一方、所定の駆動電圧を印加することにより、当該電圧に比例した回転数で回転するモータ(DCモータ)もよく知られている。また、DCモータの回転軸に回転エンコーダを備えて、エンコーダパルス(FGパルス)を作ることもよく行われる。このようにすると、モータ駆動電圧からFGパルスまでをVCOに見立てることが可能である。即ち、PLLの手法によりモータの速度(回転数)をFGパルスにより検出して、所定の基準クロックにFGパルスが位相同期するようにモータ駆動電圧を制御してPLL制御を実現することができる。

何れのPLLでも、一般的な位相差検出器(位相比較器)は、位相差が1パルス周期(360度、あるいは2πラジアン)の範囲ではリニアな値を出力するが、その範囲を超えると折り返してしまい、位相同期状態から外れてしまう。

【0003】

モータ制御では、突発的な負荷変動や目標速度の変化が発生すると、過渡的に位相差が増大して1パルス周期を超えることがある。そうなると位相同期状態から外れてしまい、再び同期状態に戻るまでに時間を要する。また、再同期しても、1パルス位相以上の位置ずれを起こしたままになり、その後、修正されないという問題がある。

このような同期外れを避けるため、位相差検出器として基準パルス数とFGパルス数の差を用いる場合がある。こうすると位相差としてはパルス数単位になるので1パルス位相を超えても大局的な位相差は検出でき、位置ずれは生じない。しかしながら、分解能が1パルス単位と粗く、1パルス以内の精度では計測できないため精密な制御には向かないといった問題がある。

【0004】

従来技術として、特許文献1には、VCO(ここではデジタル値で制御される発振器)の位相を整数部と小数部の形式で出力させ、両方を位相差検出に用いる装置について開示されている。

また、特許文献2には、エンコーダ(FG)パルス数をカウントする位相カウンタで整数部を表現し、エンコーダ周期をクロックで計測することで速度を計測し、これを積分することで小数部を含んだ位相成分を求める可変速駆動装置について開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、特許文献1に開示されている従来技術は、駆動対象がデジタルVCOであれば小数部の出力が可能であるが、モータの場合はセンサ手段がFGパルスしかないので、FGパルス周期以下の位相量はそのままでは出力されないといった問題がある。

また、特許文献2に開示されている従来技術は、一般的なPLL制御に必要な基準周波数を持った基準パルスと、FGパルスとの間の位相差を小数部まで検出する位相差検出手段については開示されていない。

本発明は、かかる課題に鑑みてなされたものであり、安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明はかかる課題を解決するために、位相基準パルス数とモータの所定回転角度ごとに発生するFGパルス数との差を検出した整数位相差と、前記位相基準パルスのエッジと前記FGパルスのエッジとの時間差を検出して基準クロック単位で計測した小数位相差と、を所定の比率で加算して位相差とし、該位相差に応じて前記モータを駆動制御することを特徴とする。

【発明の効果】

【0007】

本発明によれば、整数位相差と小数位相差を所定の比率で加算して位相差とし、この位相差に応じてモータを駆動制御するようにしたので、1パルス周期を越える位相差を小数部まで含んで連続的に検出できる。したがって、安価な構成で、基準パルスと検出パルスの位相差を広範囲かつ精密に検出することができる。

【図面の簡単な説明】

【0008】

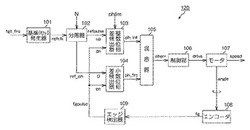

【図1】本発明の第1の実施形態に係るモータ速度制御装置の構成を示すブロック図である。

【図2】分周器の構成例を示す図である。

【図3】refclkとrefpulseおよびref_phの波形例を示す図である。

【図4】整数位相差検出器の構成例を示す図である。

【図5】カウンタの動作波形例を示す図である。

【図6】位相差とph_int、ph_frcおよぶpherrの関係を示す図である。

【図7】本発明の第2の実施形態に係るモータ速度制御装置の構成を示すブロック図である。

【図8】周期検出手段の構成例を示す図である。

【図9】周期検出手段の動作波形例を示す図である。

【図10】本発明のモータ速度制御装置を備えたデジタル複写機の概略構成図である。

【発明を実施するための形態】

【0009】

以下、本発明を図に示した実施形態を用いて詳細に説明する。但し、この実施形態に記載される構成要素、種類、組み合わせ、形状、その相対配置などは特定的な記載がない限り、この発明の範囲をそれのみに限定する主旨ではなく単なる説明例に過ぎない。

【0010】

図1は本発明の第1の実施形態に係るモータ速度制御装置の構成を示すブロック図である。本発明のモータ速度制御装置120は、tgt_frq(基準周波数)に基づくrefclk(基準クロック)を出力する基準クロック発生器(基準クロック発生手段)101と、モータ107の所定回転角度ごとに所定数のfg(FGパルス)を出力するエンコーダ(エンコーダ手段)108と、refclkをN分周してrefpulse(位相基準パルス)を出力する分周器(位相基準パルス生成手段)102と、refpulse数とfgpulse数の差を検出して整数位相差ph_intとして出力する整数位相差検出器(整数位相差検出手段)103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frc(小数位相差)として出力する小数位相差検出器(小数位相差検出手段)104と、ph_intとph_frcを混合器105で所定の比率で加算してpherr(位相差)とし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

本発明は、複写機、ファクシミリ装置、プリンタ、及びこれらの複合機に適用可能である。

【0011】

基準クロック発生器101は、目標周波数設定値tgt_frqの値に応じた周波数のクロックrefclkを発生させる。符号102はN分周器で、refclkを分周比設定値Nだけ分周した基準パルスrefpulseを出力する。尚、refpulseの周波数はrefclkの周波数の1/Nである。またこの分周過程で得られる基準位相値ref_phも出力する。

アップダウンカウンタを用いた整数位相差検出器103は、up入力パルスでアップ、dn入力パルスでダウンする。up入力には基準パルスrefpulseが接続される。dn入力には後述のモータ107のFGパルスfgpulseが接続される。整数位相差検出器103の出力ph_intはrepulseとfgpulseのそれぞれのパルス数の差、すなわち整数位相差を示す。ph_intが「1」の場合は1サイクルの位相差を示す。

ph_intは、fgpulseが到来してカウンタがダウンしたときの値が保持されて出力される。また整数位相差検出器103は、リミット設定値phlimより大きな値にはアップせず、−phlim(負の値)より小さな値にはダウンしないように構成されている。

【0012】

制御部106は、整数位相差ph_intと小数位相差ph_frcを所定の比率で加算して位相差pherrとし、この位相差pherrに基づいてモータ107を駆動制御する。即ち、アップダウンカウンタに限定せず、repulseとfgpulseのそれぞれのパルス数の差が得られればよい。例えば、それぞれをアップカウントして減算してもよい。ただし、アップカウンタ2個の差分では、後述の位相差リミットの実現が困難である。

整数位相差検出器103でアップダウンカウンタにすることで、1個のカウンタで実現できコストが安くなる。また、アップダウン条件の論理により簡単に位相差リミットが実現できる。

アップダウンカウント手段でアップダウン条件の論理でカウントリミットさせることにより、モータ起動時などrefpulseが多数到来してfgpulseがほとんど来ない状態でも位相差が過大にならないようにリミットできる。これにより起動後に位相差が収束する時間を短くできる。

【0013】

小数位相差検出器104は、モータ107のFGパルスエッジfgpulse(後述)が到来したときの分周器102が出力する基準位相値ref_phを保持する。保持結果ph_frcは、基準パルスref_pulseの1周期内でのfgpulse位相差を表しており、小数位相差と呼ぶことにする。小数位相差検出器104は具体的にはラッチ回路で実現できる。

なお小数位相差検出器104は、分周器102の基準位相ref_phをfgpulseでラッチする手段に限らず、refpulseエッジからfgpulseエッジまでの時間間隔を計測できればよい。たとえば、十分高速なクロックをカウントするカウンタを設け、このカウンタをrefpulseエッジでスタートさせてfgpulseエッジでストップさせ、その値を保持するようにしてもよい。

この実施形態のように、分周器102の基準位相ref_phをfgpulseでラッチすることにより、位相差測定用カウンタを別途設けなくても、基準クロック発生器101の分周カウンタを流用するので回路規模を小さくでき、安価になる。

【0014】

混合器(混合手段)105は、整数位相差ph_intと小数位相差ph_frcを所定の割合で加算して、位相差pherrを出力する。この加算割合はすくなくともph_intのほうを大きな比率で加算しておくのが好ましい。

位相差pherrは、混合器105の加算比率を、分周期102の分周比Nを用いて、整数位相差ph_intを小数位相差ph_frcのN倍の比率で加算する。このことにより、整数と小数が物理的に正しい比で加算され、pherrとして連続的な位相差データが得られるという効果がある。

【0015】

ここで、混合器105の処理を数式で書くと

pherr=N*ph_int+ph_frc ・・・(式1)

となる。

これは位相差1cycleをNとする量であるが、位相差1cycleを1とするには

pherr=ph_int+ph_frc/N ・・・(式2)

とすればよい(「*」は乗算、「/」は除算)。

いずれもph_intのほうがph_frcに対してN倍の比率になっている。

制御部106は、位相差pherrが0に近づくようにモータ駆動量driveを出力する。この処理は公知の制御理論等を用いることができる。通常、位相差だけを用いたモータ107の速度制御の場合は、位相差pherrに比例したゲイン処理と、位相差を微分した微分処理を加算して駆動量を算出することがよく行なわれる。いずれにせよ位相差pherrに応じてモータを駆動する手段である。

【0016】

DCモータ(以下、単にモータと呼ぶ)107は、駆動量driveに応じて回転する。driveは印加電圧相当でもよいし、電流相当でもよい。あるいはPWMなどのパルス駆動でもよい。

エンコーダ108は、モータ107の所定回転角ごとにパルスfgを出力する。通常、1周で50パルスから数1000パルスなど、応用分野により分解能は異なる。

エッジ検出器109は、fgパルスの立ち上がり、あるいは立ち下がり、あるいはその両方を検出してfgpulse信号を出力する。fgpulseは前述のように、整数位相差検出器103および小数位相差検出器104に接続されている。

このような構成で制御すると、結局基準パルスrefpulseとモータのFGパルスfgpulseの位相差が0に近づくように制御される。位相差が0でなくても一定値に制御されると、refpulseの周波数とfgpulseの周波数は等しくなり、したがってモータの回転速度は一定に制御される。

【0017】

図2は分周器の構成例を示す図である。カウンタ201は、refclkで1ずつアップする。カウンタの値が基準位相ref_phとして出力される。比較器202は、ref_phが設定値Nと等しくなると基準パルスrefpulseを出力する。このとき同時にカウンタ201をクリアする。このようにすると、ref_phが0からNまで増加して0に戻る動作を繰り返す。ref_phが0にもどるときにrefpulseを出力する。

【0018】

図3はrefclkとrefpulseおよびref_phの波形例を示す図である。ここでは基準クロックrefclkから基準パルスrefpulseの分周比Nを「10」としている。整数位相差を示すアップダウンカウンタ211の値phcntは、refpulseでアップ、fgpulseでダウンする。基準位相ref_phはrefpulseの間を0から10(厳密には9)まで増加してそれを繰り返す。fgpulseが到来したときのref_phをラッチして小数位相差ph_frcが生成される。また、fgpulseが到来してアップダウンカウンタ211がダウンしたときのphcntをラッチして整数位相差ph_intが生成される。「pherr=ph_int+ph_frc/N」として位相差pherrが計算される。

この例では全体として、最初はrefpulseのほうが速いので位相差は増大し、その後fgpulseのほうが速くなると位相差は減少する。位相差は「1」を越えても折り返されず、小数を含んで真の位相差が得られる。

【0019】

図4は整数位相差検出器の構成例を示す図である。アップダウンカウンタ211は、refpulse到来でアップ、fgpulse到来でダウンし、カウント値(正負)をphcntとして出力する。遅延器203は、fgpulseを1単位時間(基本クロック程度のごく短い時間。クロックは図示しない)だけ遅延させる。ラッチ手段212は、fgpulseによりカウンタ211が変化してから遅延器203の遅延量だけ遅れてphcntを保持する。つまり、fgpulseが到来してカウンタがダウンしたときの値が保持されて、ph_intが出力される。

カウンタ211は、位相差リミット設定値phlimにより正負リミットされる。すなわち、−phlimから+phlimの範囲で動作し、この範囲を越えてカウントしない。

【0020】

カウンタの動作ロジックは例えば以下のように記述できる(記述はC言語類似、説明のため記述ステップ番号s1−−s4を付与)。

s1:if(refpulse && fgpulse) phcnt=phcnt;

s2:else if ((refpulse)&&(phcnt<phlim)) phcnt=phcnt+1;

s3:else if ((fgpulse)&&(phcnt>−phlim) phcnt=phcnt−1;

s4:else phcnt=phcnt;

s1はrefpulseとfgpulseが同時の場合で、この場合はカウントせず保持。

s2はrefpulse到来時、正リミットphlimに達していなければカウントアップ。

s3はfgpulse到来時、負リミット−phlimに達していなければカウントダウン。

s4はそれ以外(両パルスとも来ない、あるいはリミットに達している)の場合で、カウントは保持。

【0021】

図5はカウンタの動作波形例を示す図である。

太い点線はphlimが十分大きい場合で、phcntはリミットされない。リミットしない場合はどちらかのパルスが来ないとphcntは大きくなり、再度0に近づくまで時間がかかる。これはモータ起動時に、位相差が非常に大きな状態になることを意味する。回転が立ち上がって位相差を0にもどすためには、repulseよりも短い周期でfgpulseが多数到来しなければならない。つまり、目標回転数より高い状態が長時間続き、回転数の収束(整定)に時間がかかる。太い実線がphlim=2の場合で、カウント値phcntは−2から+2に制限される。これにより、phcntが再度0に近づくのが速くなり、モータ起動後の回転数の収束(整定)時間を短くできる。

【0022】

図6は位相差とph_int、ph_frcおよぶpherrの関係を示す図である。

横軸はrefpulseとfgpulseの間の真の位相差、縦軸は検出された位相差である。いずれも1cycle(1周期分)を1としている。細い点線が小数位相差データph_frcをNで割ったもので、位相差が1だけ変化するごとに0−−1の間で循環し、ノコギリ上の関係になる。太い破線が整数位相差ph_intで、位相差が1だけ変化するごとに1だけ変化する。pherrは両者を加算したもので、Nが十分大きければほぼ連続的に変化するので、1cycleを越える広範囲で連続的に精密な位相差データが得られる。

【0023】

図7は、本発明の第2の実施形態に係るモータ速度制御装置の構成を示すブロック図である。同じ構成要素には図1と同じ参照番号を付し説明を省略する。本発明のモータ速度制御装置150がモータ速度制御装置100と異なる点は、周波数計測器110、速度差検出器111、混合器112が追加され、制御部106が制御部113に置き換わっている。本発明のモータ速度制御装置150は、FGパルスのエッジ周期を基準クロック単位で計測する周波数計測器(周期計測手段)110を備え、制御部113は、エッジ周期と分周比Nの差を速度差とし、この速度差と位相差を所定の比率で加算した結果に基づいてモータ107を駆動制御する。

本発明は、複写機、ファクシミリ装置、プリンタ、及びこれらの複合機に適用可能である。

【0024】

周波数計測器110は、fgpulseの周期を基準クロックrefclkで計数して周波数データfrqを出力する。

速度差検出器111は、frqから基準パルス分周比Nを減算して周波数差ferrを出力する。ferrはrefpulseとfgpulseの周波数差を反映した量になる。

混合器112は、位相差pherrと周波数差ferrを適当な割合で加算してmixerrを出力する。

制御部113は、mixerrに応じてモータ駆動量driveを出力する。最も簡単には制御部113は比例ゲインである。すなわち、「pherr+K*rferr」(Kは所定値)に比例してdriveを出力すればよい。

このように構成すると、速度差を加算することで制御ループが安定化され、制御器の機能が単純な比例ゲインでも構成可能になり、コストが安く精密な速度制御が可能になる。

また、Nは基準パルスrefpulseの分周比と同じであり、位相差検出系と共通化できるので、これも低コスト化の効果がある。

【0025】

図8は周期検出手段の構成例を示す図である。カウンタ221は、fgpulseが到来するとクリアされ、基準クロックrefclkでアップする。ラッチ手段222は、fgpulseが到来したときのカウンタ値fcntを保持する。保持されるのはカウンタ222がクリアされる直前の値である。したがって、fgpulseの到来間隔、すなわち周期が計測されてfrqとして出力される。

【0026】

図9は周期検出手段の動作波形例を示す図である。基準パルス分周比Nは図3と同じ「10」に設定している。容易にわかるように、repulseの間隔はちょうど「10*refclk周期」であるから、fgpulseの周波数がrepulseに等しい時、周期検出値frqは「10」になる。fgpulseがrefpulseよりも遅い(周波数が低い=周期が長い)ときはfrqは10より大きく、fgpulseがrefpulseよりも速い(周波数が高い=周期が短い)ときはfrqは10より小さくなる。したがって、「frq−N」を速度差ferrとして用いることができ、ferr=0でちょうど目標速度と等しく、ferr>0ならモータを加速、ferr<0ならモータを減速するように制御すればよい。

【0027】

図10は、本発明のモータ速度制御装置を備えたデジタル複写機の概略構成図である。この構成は、画像処理装置としての複写機100であり、この複写機100の上面にはコンタクトガラス6が設けられている。また、複写機100の上部には自動原稿送り装置(以下、単にADFという)1が設けられており、このADF1はコンタクトガラス6を開閉するように複写機100に図示しないヒンジ等を介して連結されている。このADF1は、複数の原稿からなる原稿束を載置可能な原稿載置台としての原稿トレイ2と、原稿トレイ2に載置された原稿束から原稿を1枚ずつ分離してコンタクトガラス6に向かって搬送する分離・搬送手段と、分離・搬送手段によってコンタクトガラス6に向かって搬送された原稿をコンタクトガラス6上の読取位置に搬送・停止させるとともに、コンタクトガラス6の下方に配設された複写機100の読取手段(公知の露光ランプ51、ミラー52、55、56、レンズ53、CCD54等)50により読み取りが終了した原稿をコンタクトガラス6から搬出する。給紙モータはコントローラからの出力信号によって駆動されるようになっており、コントローラは複写機100から給紙スタート信号が入力されると、給紙モータを正・逆転駆動するようになっている。給紙モータが正転駆動されると、給送ローラ3が時計方向に回転して原稿束から最上位に位置する原稿が給紙され、コンタクトガラス6に向かって搬送される。この原稿の先端が原稿セット検知センサ7によって検知されると、コントローラは原稿セット検知センサ7からの出力信号に基づいて給紙モータを逆転駆動させる。これにより、後続する原稿が進入するのを防止して分離されないようになっている。

【0028】

また、コントローラは原稿セット検知センサ7が原稿の後端を検知したとき、この検知時点からの搬送ベルトモータの回転パルスを計数し、回転パルスが所定値に達したときに、給送ベルト4の駆動を停止して給送ベルト4を停止することにより、原稿をコンタクトガラス6読取位置に停止させる。また、コントローラは原稿セット検知センサ7によって原稿の後端が検知された時点で、給紙モータを再び駆動し、後続する原稿を上述したように分離してコンタクトガラス6に向かって搬送し、この原稿が原稿セット検知センサ7によって検知された時点からの給紙モータのパルスが所定パルスに到達したときに、給紙モータを停止させて次原稿を先出し待機させる。そして、原稿がコンタクトガラス6の読取位置に停止したとき、複写機100によって原稿の読み取りおよび露光が行なわれる。この読み取りおよび露光が終了すると、コントローラには複写機100から信号が入力されるため、コントローラはこの信号が入力すると、搬送ベルトモータを正転駆動して、搬送ベルト16によって原稿をコンタクトガラス6から排送ローラ5に搬出する。

【0029】

上記のように、ADF1にある原稿トレイ2に原稿の画像面を上にして置かれた原稿束は、操作部上のプリントキーが押下されると、一番上の原稿からコンタクトガラス6上の所定の位置に給送される。給送された原稿は、読み取りユニット50によってコンタクトガラス6上の原稿の画像データを読み取り後、給送ベルト4および反転駆動コロによって排出口A(原稿反転排出時の排出口)に排出される。さらに、原稿トレイ2に次の原稿が有ることを検知した場合、前原稿と同様にコンタクトガラス6上に給送される。

第1トレイ8、第2トレイ9、第3トレイ10に積載された転写紙は、各々第1給紙ユニット11、第2給紙ユニット12、第3給紙ユニット13によって給紙され、縦搬送ユニット14によって感光体15に当接する位置まで搬送される。読み取りユニット50にて読み込まれた画像データは、書き込みユニット57からのレーザによって感光体15に書き込まれ、現像ユニット27を通過することによってトナー像が形成される。そして、転写紙は感光体15の回転と等速で搬送ベルト16によって搬送されながら、感光体15上のトナー像が転写される。その後、定着ユニット17にて画像を定着させ、排紙ユニット18に搬送される。排紙ユニット18に搬送された転写紙は、ステープルモードを行わない場合は、排紙トレイ19に排紙される。

【符号の説明】

【0030】

1 ADF、2 原稿トレイ、3 給送ローラ、4 給送ベルト、5 排紙ローラ、6 コンタクトガラス、7 原稿セット検知センサ、8 第1トレイ、9 第2トレイ、10 第3トレイ、11 第1給紙ユニット、12 第2給紙ユニット、13 第3給紙ユニット、14 縦搬送ユニット、15 感光体、16 搬送ベルト、51 露光ランプ、52、55、56、 ミラー、53 レンズ、54 CCD、100 複写機、101 基準クロック発生器、102 分周器、103 整数位相差検出器、104 少数位相差検出器、105 混合器、106 制御部、107 モータ、108 エンコーダ、109 エッジ検出器、110 周波数計測器、111 速度差検出器、112 混合器、120 第1の実施形態に係るモータ速度制御装置、150 第2の実施形態に係るモータ速度制御装置、201 アップダウンカウンタ、202 比較器、203 遅延器、211 アップダウンカウンタ、212 ラッチ回路、221 アップダウンカウンタ、222 ラッチ回路

【先行技術文献】

【特許文献】

【0031】

【特許文献1】特許第4377696号

【特許文献2】特開平9−247999号公報

【技術分野】

【0001】

本発明は、モータ速度制御装置に関し、特に、PLL制御により回転制御されるモータの速度制御装置の回路構成に関するものである。

【背景技術】

【0002】

電子回路において、位相同期ループ(Phase Locked Loop:PLL)技術はよく知られている。一般にPLLは、外部から印加された制御電圧に比例した周波数で発振する電圧制御発振器(VCO)の出力パルス或いはその分周パルスと、基準周波数を持ったパルスとの位相差を検出して、検出した位相差をVCOにフィードバックすることで位相同期を実現している。

一方、所定の駆動電圧を印加することにより、当該電圧に比例した回転数で回転するモータ(DCモータ)もよく知られている。また、DCモータの回転軸に回転エンコーダを備えて、エンコーダパルス(FGパルス)を作ることもよく行われる。このようにすると、モータ駆動電圧からFGパルスまでをVCOに見立てることが可能である。即ち、PLLの手法によりモータの速度(回転数)をFGパルスにより検出して、所定の基準クロックにFGパルスが位相同期するようにモータ駆動電圧を制御してPLL制御を実現することができる。

何れのPLLでも、一般的な位相差検出器(位相比較器)は、位相差が1パルス周期(360度、あるいは2πラジアン)の範囲ではリニアな値を出力するが、その範囲を超えると折り返してしまい、位相同期状態から外れてしまう。

【0003】

モータ制御では、突発的な負荷変動や目標速度の変化が発生すると、過渡的に位相差が増大して1パルス周期を超えることがある。そうなると位相同期状態から外れてしまい、再び同期状態に戻るまでに時間を要する。また、再同期しても、1パルス位相以上の位置ずれを起こしたままになり、その後、修正されないという問題がある。

このような同期外れを避けるため、位相差検出器として基準パルス数とFGパルス数の差を用いる場合がある。こうすると位相差としてはパルス数単位になるので1パルス位相を超えても大局的な位相差は検出でき、位置ずれは生じない。しかしながら、分解能が1パルス単位と粗く、1パルス以内の精度では計測できないため精密な制御には向かないといった問題がある。

【0004】

従来技術として、特許文献1には、VCO(ここではデジタル値で制御される発振器)の位相を整数部と小数部の形式で出力させ、両方を位相差検出に用いる装置について開示されている。

また、特許文献2には、エンコーダ(FG)パルス数をカウントする位相カウンタで整数部を表現し、エンコーダ周期をクロックで計測することで速度を計測し、これを積分することで小数部を含んだ位相成分を求める可変速駆動装置について開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、特許文献1に開示されている従来技術は、駆動対象がデジタルVCOであれば小数部の出力が可能であるが、モータの場合はセンサ手段がFGパルスしかないので、FGパルス周期以下の位相量はそのままでは出力されないといった問題がある。

また、特許文献2に開示されている従来技術は、一般的なPLL制御に必要な基準周波数を持った基準パルスと、FGパルスとの間の位相差を小数部まで検出する位相差検出手段については開示されていない。

本発明は、かかる課題に鑑みてなされたものであり、安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明はかかる課題を解決するために、位相基準パルス数とモータの所定回転角度ごとに発生するFGパルス数との差を検出した整数位相差と、前記位相基準パルスのエッジと前記FGパルスのエッジとの時間差を検出して基準クロック単位で計測した小数位相差と、を所定の比率で加算して位相差とし、該位相差に応じて前記モータを駆動制御することを特徴とする。

【発明の効果】

【0007】

本発明によれば、整数位相差と小数位相差を所定の比率で加算して位相差とし、この位相差に応じてモータを駆動制御するようにしたので、1パルス周期を越える位相差を小数部まで含んで連続的に検出できる。したがって、安価な構成で、基準パルスと検出パルスの位相差を広範囲かつ精密に検出することができる。

【図面の簡単な説明】

【0008】

【図1】本発明の第1の実施形態に係るモータ速度制御装置の構成を示すブロック図である。

【図2】分周器の構成例を示す図である。

【図3】refclkとrefpulseおよびref_phの波形例を示す図である。

【図4】整数位相差検出器の構成例を示す図である。

【図5】カウンタの動作波形例を示す図である。

【図6】位相差とph_int、ph_frcおよぶpherrの関係を示す図である。

【図7】本発明の第2の実施形態に係るモータ速度制御装置の構成を示すブロック図である。

【図8】周期検出手段の構成例を示す図である。

【図9】周期検出手段の動作波形例を示す図である。

【図10】本発明のモータ速度制御装置を備えたデジタル複写機の概略構成図である。

【発明を実施するための形態】

【0009】

以下、本発明を図に示した実施形態を用いて詳細に説明する。但し、この実施形態に記載される構成要素、種類、組み合わせ、形状、その相対配置などは特定的な記載がない限り、この発明の範囲をそれのみに限定する主旨ではなく単なる説明例に過ぎない。

【0010】

図1は本発明の第1の実施形態に係るモータ速度制御装置の構成を示すブロック図である。本発明のモータ速度制御装置120は、tgt_frq(基準周波数)に基づくrefclk(基準クロック)を出力する基準クロック発生器(基準クロック発生手段)101と、モータ107の所定回転角度ごとに所定数のfg(FGパルス)を出力するエンコーダ(エンコーダ手段)108と、refclkをN分周してrefpulse(位相基準パルス)を出力する分周器(位相基準パルス生成手段)102と、refpulse数とfgpulse数の差を検出して整数位相差ph_intとして出力する整数位相差検出器(整数位相差検出手段)103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frc(小数位相差)として出力する小数位相差検出器(小数位相差検出手段)104と、ph_intとph_frcを混合器105で所定の比率で加算してpherr(位相差)とし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

本発明は、複写機、ファクシミリ装置、プリンタ、及びこれらの複合機に適用可能である。

【0011】

基準クロック発生器101は、目標周波数設定値tgt_frqの値に応じた周波数のクロックrefclkを発生させる。符号102はN分周器で、refclkを分周比設定値Nだけ分周した基準パルスrefpulseを出力する。尚、refpulseの周波数はrefclkの周波数の1/Nである。またこの分周過程で得られる基準位相値ref_phも出力する。

アップダウンカウンタを用いた整数位相差検出器103は、up入力パルスでアップ、dn入力パルスでダウンする。up入力には基準パルスrefpulseが接続される。dn入力には後述のモータ107のFGパルスfgpulseが接続される。整数位相差検出器103の出力ph_intはrepulseとfgpulseのそれぞれのパルス数の差、すなわち整数位相差を示す。ph_intが「1」の場合は1サイクルの位相差を示す。

ph_intは、fgpulseが到来してカウンタがダウンしたときの値が保持されて出力される。また整数位相差検出器103は、リミット設定値phlimより大きな値にはアップせず、−phlim(負の値)より小さな値にはダウンしないように構成されている。

【0012】

制御部106は、整数位相差ph_intと小数位相差ph_frcを所定の比率で加算して位相差pherrとし、この位相差pherrに基づいてモータ107を駆動制御する。即ち、アップダウンカウンタに限定せず、repulseとfgpulseのそれぞれのパルス数の差が得られればよい。例えば、それぞれをアップカウントして減算してもよい。ただし、アップカウンタ2個の差分では、後述の位相差リミットの実現が困難である。

整数位相差検出器103でアップダウンカウンタにすることで、1個のカウンタで実現できコストが安くなる。また、アップダウン条件の論理により簡単に位相差リミットが実現できる。

アップダウンカウント手段でアップダウン条件の論理でカウントリミットさせることにより、モータ起動時などrefpulseが多数到来してfgpulseがほとんど来ない状態でも位相差が過大にならないようにリミットできる。これにより起動後に位相差が収束する時間を短くできる。

【0013】

小数位相差検出器104は、モータ107のFGパルスエッジfgpulse(後述)が到来したときの分周器102が出力する基準位相値ref_phを保持する。保持結果ph_frcは、基準パルスref_pulseの1周期内でのfgpulse位相差を表しており、小数位相差と呼ぶことにする。小数位相差検出器104は具体的にはラッチ回路で実現できる。

なお小数位相差検出器104は、分周器102の基準位相ref_phをfgpulseでラッチする手段に限らず、refpulseエッジからfgpulseエッジまでの時間間隔を計測できればよい。たとえば、十分高速なクロックをカウントするカウンタを設け、このカウンタをrefpulseエッジでスタートさせてfgpulseエッジでストップさせ、その値を保持するようにしてもよい。

この実施形態のように、分周器102の基準位相ref_phをfgpulseでラッチすることにより、位相差測定用カウンタを別途設けなくても、基準クロック発生器101の分周カウンタを流用するので回路規模を小さくでき、安価になる。

【0014】

混合器(混合手段)105は、整数位相差ph_intと小数位相差ph_frcを所定の割合で加算して、位相差pherrを出力する。この加算割合はすくなくともph_intのほうを大きな比率で加算しておくのが好ましい。

位相差pherrは、混合器105の加算比率を、分周期102の分周比Nを用いて、整数位相差ph_intを小数位相差ph_frcのN倍の比率で加算する。このことにより、整数と小数が物理的に正しい比で加算され、pherrとして連続的な位相差データが得られるという効果がある。

【0015】

ここで、混合器105の処理を数式で書くと

pherr=N*ph_int+ph_frc ・・・(式1)

となる。

これは位相差1cycleをNとする量であるが、位相差1cycleを1とするには

pherr=ph_int+ph_frc/N ・・・(式2)

とすればよい(「*」は乗算、「/」は除算)。

いずれもph_intのほうがph_frcに対してN倍の比率になっている。

制御部106は、位相差pherrが0に近づくようにモータ駆動量driveを出力する。この処理は公知の制御理論等を用いることができる。通常、位相差だけを用いたモータ107の速度制御の場合は、位相差pherrに比例したゲイン処理と、位相差を微分した微分処理を加算して駆動量を算出することがよく行なわれる。いずれにせよ位相差pherrに応じてモータを駆動する手段である。

【0016】

DCモータ(以下、単にモータと呼ぶ)107は、駆動量driveに応じて回転する。driveは印加電圧相当でもよいし、電流相当でもよい。あるいはPWMなどのパルス駆動でもよい。

エンコーダ108は、モータ107の所定回転角ごとにパルスfgを出力する。通常、1周で50パルスから数1000パルスなど、応用分野により分解能は異なる。

エッジ検出器109は、fgパルスの立ち上がり、あるいは立ち下がり、あるいはその両方を検出してfgpulse信号を出力する。fgpulseは前述のように、整数位相差検出器103および小数位相差検出器104に接続されている。

このような構成で制御すると、結局基準パルスrefpulseとモータのFGパルスfgpulseの位相差が0に近づくように制御される。位相差が0でなくても一定値に制御されると、refpulseの周波数とfgpulseの周波数は等しくなり、したがってモータの回転速度は一定に制御される。

【0017】

図2は分周器の構成例を示す図である。カウンタ201は、refclkで1ずつアップする。カウンタの値が基準位相ref_phとして出力される。比較器202は、ref_phが設定値Nと等しくなると基準パルスrefpulseを出力する。このとき同時にカウンタ201をクリアする。このようにすると、ref_phが0からNまで増加して0に戻る動作を繰り返す。ref_phが0にもどるときにrefpulseを出力する。

【0018】

図3はrefclkとrefpulseおよびref_phの波形例を示す図である。ここでは基準クロックrefclkから基準パルスrefpulseの分周比Nを「10」としている。整数位相差を示すアップダウンカウンタ211の値phcntは、refpulseでアップ、fgpulseでダウンする。基準位相ref_phはrefpulseの間を0から10(厳密には9)まで増加してそれを繰り返す。fgpulseが到来したときのref_phをラッチして小数位相差ph_frcが生成される。また、fgpulseが到来してアップダウンカウンタ211がダウンしたときのphcntをラッチして整数位相差ph_intが生成される。「pherr=ph_int+ph_frc/N」として位相差pherrが計算される。

この例では全体として、最初はrefpulseのほうが速いので位相差は増大し、その後fgpulseのほうが速くなると位相差は減少する。位相差は「1」を越えても折り返されず、小数を含んで真の位相差が得られる。

【0019】

図4は整数位相差検出器の構成例を示す図である。アップダウンカウンタ211は、refpulse到来でアップ、fgpulse到来でダウンし、カウント値(正負)をphcntとして出力する。遅延器203は、fgpulseを1単位時間(基本クロック程度のごく短い時間。クロックは図示しない)だけ遅延させる。ラッチ手段212は、fgpulseによりカウンタ211が変化してから遅延器203の遅延量だけ遅れてphcntを保持する。つまり、fgpulseが到来してカウンタがダウンしたときの値が保持されて、ph_intが出力される。

カウンタ211は、位相差リミット設定値phlimにより正負リミットされる。すなわち、−phlimから+phlimの範囲で動作し、この範囲を越えてカウントしない。

【0020】

カウンタの動作ロジックは例えば以下のように記述できる(記述はC言語類似、説明のため記述ステップ番号s1−−s4を付与)。

s1:if(refpulse && fgpulse) phcnt=phcnt;

s2:else if ((refpulse)&&(phcnt<phlim)) phcnt=phcnt+1;

s3:else if ((fgpulse)&&(phcnt>−phlim) phcnt=phcnt−1;

s4:else phcnt=phcnt;

s1はrefpulseとfgpulseが同時の場合で、この場合はカウントせず保持。

s2はrefpulse到来時、正リミットphlimに達していなければカウントアップ。

s3はfgpulse到来時、負リミット−phlimに達していなければカウントダウン。

s4はそれ以外(両パルスとも来ない、あるいはリミットに達している)の場合で、カウントは保持。

【0021】

図5はカウンタの動作波形例を示す図である。

太い点線はphlimが十分大きい場合で、phcntはリミットされない。リミットしない場合はどちらかのパルスが来ないとphcntは大きくなり、再度0に近づくまで時間がかかる。これはモータ起動時に、位相差が非常に大きな状態になることを意味する。回転が立ち上がって位相差を0にもどすためには、repulseよりも短い周期でfgpulseが多数到来しなければならない。つまり、目標回転数より高い状態が長時間続き、回転数の収束(整定)に時間がかかる。太い実線がphlim=2の場合で、カウント値phcntは−2から+2に制限される。これにより、phcntが再度0に近づくのが速くなり、モータ起動後の回転数の収束(整定)時間を短くできる。

【0022】

図6は位相差とph_int、ph_frcおよぶpherrの関係を示す図である。

横軸はrefpulseとfgpulseの間の真の位相差、縦軸は検出された位相差である。いずれも1cycle(1周期分)を1としている。細い点線が小数位相差データph_frcをNで割ったもので、位相差が1だけ変化するごとに0−−1の間で循環し、ノコギリ上の関係になる。太い破線が整数位相差ph_intで、位相差が1だけ変化するごとに1だけ変化する。pherrは両者を加算したもので、Nが十分大きければほぼ連続的に変化するので、1cycleを越える広範囲で連続的に精密な位相差データが得られる。

【0023】

図7は、本発明の第2の実施形態に係るモータ速度制御装置の構成を示すブロック図である。同じ構成要素には図1と同じ参照番号を付し説明を省略する。本発明のモータ速度制御装置150がモータ速度制御装置100と異なる点は、周波数計測器110、速度差検出器111、混合器112が追加され、制御部106が制御部113に置き換わっている。本発明のモータ速度制御装置150は、FGパルスのエッジ周期を基準クロック単位で計測する周波数計測器(周期計測手段)110を備え、制御部113は、エッジ周期と分周比Nの差を速度差とし、この速度差と位相差を所定の比率で加算した結果に基づいてモータ107を駆動制御する。

本発明は、複写機、ファクシミリ装置、プリンタ、及びこれらの複合機に適用可能である。

【0024】

周波数計測器110は、fgpulseの周期を基準クロックrefclkで計数して周波数データfrqを出力する。

速度差検出器111は、frqから基準パルス分周比Nを減算して周波数差ferrを出力する。ferrはrefpulseとfgpulseの周波数差を反映した量になる。

混合器112は、位相差pherrと周波数差ferrを適当な割合で加算してmixerrを出力する。

制御部113は、mixerrに応じてモータ駆動量driveを出力する。最も簡単には制御部113は比例ゲインである。すなわち、「pherr+K*rferr」(Kは所定値)に比例してdriveを出力すればよい。

このように構成すると、速度差を加算することで制御ループが安定化され、制御器の機能が単純な比例ゲインでも構成可能になり、コストが安く精密な速度制御が可能になる。

また、Nは基準パルスrefpulseの分周比と同じであり、位相差検出系と共通化できるので、これも低コスト化の効果がある。

【0025】

図8は周期検出手段の構成例を示す図である。カウンタ221は、fgpulseが到来するとクリアされ、基準クロックrefclkでアップする。ラッチ手段222は、fgpulseが到来したときのカウンタ値fcntを保持する。保持されるのはカウンタ222がクリアされる直前の値である。したがって、fgpulseの到来間隔、すなわち周期が計測されてfrqとして出力される。

【0026】

図9は周期検出手段の動作波形例を示す図である。基準パルス分周比Nは図3と同じ「10」に設定している。容易にわかるように、repulseの間隔はちょうど「10*refclk周期」であるから、fgpulseの周波数がrepulseに等しい時、周期検出値frqは「10」になる。fgpulseがrefpulseよりも遅い(周波数が低い=周期が長い)ときはfrqは10より大きく、fgpulseがrefpulseよりも速い(周波数が高い=周期が短い)ときはfrqは10より小さくなる。したがって、「frq−N」を速度差ferrとして用いることができ、ferr=0でちょうど目標速度と等しく、ferr>0ならモータを加速、ferr<0ならモータを減速するように制御すればよい。

【0027】

図10は、本発明のモータ速度制御装置を備えたデジタル複写機の概略構成図である。この構成は、画像処理装置としての複写機100であり、この複写機100の上面にはコンタクトガラス6が設けられている。また、複写機100の上部には自動原稿送り装置(以下、単にADFという)1が設けられており、このADF1はコンタクトガラス6を開閉するように複写機100に図示しないヒンジ等を介して連結されている。このADF1は、複数の原稿からなる原稿束を載置可能な原稿載置台としての原稿トレイ2と、原稿トレイ2に載置された原稿束から原稿を1枚ずつ分離してコンタクトガラス6に向かって搬送する分離・搬送手段と、分離・搬送手段によってコンタクトガラス6に向かって搬送された原稿をコンタクトガラス6上の読取位置に搬送・停止させるとともに、コンタクトガラス6の下方に配設された複写機100の読取手段(公知の露光ランプ51、ミラー52、55、56、レンズ53、CCD54等)50により読み取りが終了した原稿をコンタクトガラス6から搬出する。給紙モータはコントローラからの出力信号によって駆動されるようになっており、コントローラは複写機100から給紙スタート信号が入力されると、給紙モータを正・逆転駆動するようになっている。給紙モータが正転駆動されると、給送ローラ3が時計方向に回転して原稿束から最上位に位置する原稿が給紙され、コンタクトガラス6に向かって搬送される。この原稿の先端が原稿セット検知センサ7によって検知されると、コントローラは原稿セット検知センサ7からの出力信号に基づいて給紙モータを逆転駆動させる。これにより、後続する原稿が進入するのを防止して分離されないようになっている。

【0028】

また、コントローラは原稿セット検知センサ7が原稿の後端を検知したとき、この検知時点からの搬送ベルトモータの回転パルスを計数し、回転パルスが所定値に達したときに、給送ベルト4の駆動を停止して給送ベルト4を停止することにより、原稿をコンタクトガラス6読取位置に停止させる。また、コントローラは原稿セット検知センサ7によって原稿の後端が検知された時点で、給紙モータを再び駆動し、後続する原稿を上述したように分離してコンタクトガラス6に向かって搬送し、この原稿が原稿セット検知センサ7によって検知された時点からの給紙モータのパルスが所定パルスに到達したときに、給紙モータを停止させて次原稿を先出し待機させる。そして、原稿がコンタクトガラス6の読取位置に停止したとき、複写機100によって原稿の読み取りおよび露光が行なわれる。この読み取りおよび露光が終了すると、コントローラには複写機100から信号が入力されるため、コントローラはこの信号が入力すると、搬送ベルトモータを正転駆動して、搬送ベルト16によって原稿をコンタクトガラス6から排送ローラ5に搬出する。

【0029】

上記のように、ADF1にある原稿トレイ2に原稿の画像面を上にして置かれた原稿束は、操作部上のプリントキーが押下されると、一番上の原稿からコンタクトガラス6上の所定の位置に給送される。給送された原稿は、読み取りユニット50によってコンタクトガラス6上の原稿の画像データを読み取り後、給送ベルト4および反転駆動コロによって排出口A(原稿反転排出時の排出口)に排出される。さらに、原稿トレイ2に次の原稿が有ることを検知した場合、前原稿と同様にコンタクトガラス6上に給送される。

第1トレイ8、第2トレイ9、第3トレイ10に積載された転写紙は、各々第1給紙ユニット11、第2給紙ユニット12、第3給紙ユニット13によって給紙され、縦搬送ユニット14によって感光体15に当接する位置まで搬送される。読み取りユニット50にて読み込まれた画像データは、書き込みユニット57からのレーザによって感光体15に書き込まれ、現像ユニット27を通過することによってトナー像が形成される。そして、転写紙は感光体15の回転と等速で搬送ベルト16によって搬送されながら、感光体15上のトナー像が転写される。その後、定着ユニット17にて画像を定着させ、排紙ユニット18に搬送される。排紙ユニット18に搬送された転写紙は、ステープルモードを行わない場合は、排紙トレイ19に排紙される。

【符号の説明】

【0030】

1 ADF、2 原稿トレイ、3 給送ローラ、4 給送ベルト、5 排紙ローラ、6 コンタクトガラス、7 原稿セット検知センサ、8 第1トレイ、9 第2トレイ、10 第3トレイ、11 第1給紙ユニット、12 第2給紙ユニット、13 第3給紙ユニット、14 縦搬送ユニット、15 感光体、16 搬送ベルト、51 露光ランプ、52、55、56、 ミラー、53 レンズ、54 CCD、100 複写機、101 基準クロック発生器、102 分周器、103 整数位相差検出器、104 少数位相差検出器、105 混合器、106 制御部、107 モータ、108 エンコーダ、109 エッジ検出器、110 周波数計測器、111 速度差検出器、112 混合器、120 第1の実施形態に係るモータ速度制御装置、150 第2の実施形態に係るモータ速度制御装置、201 アップダウンカウンタ、202 比較器、203 遅延器、211 アップダウンカウンタ、212 ラッチ回路、221 アップダウンカウンタ、222 ラッチ回路

【先行技術文献】

【特許文献】

【0031】

【特許文献1】特許第4377696号

【特許文献2】特開平9−247999号公報

【特許請求の範囲】

【請求項1】

位相基準パルス数とモータの所定回転角度ごとに発生するFGパルス数との差を検出した整数位相差と、前記位相基準パルスのエッジと前記FGパルスのエッジとの時間差を検出して基準クロック単位で計測した小数位相差と、を所定の比率で加算して位相差とし、該位相差に応じて前記モータを駆動制御することを特徴とするモータ速度制御装置。

【請求項2】

基準周波数に基づく基準クロックを出力する基準クロック発生手段と、

前記モータの所定回転角度ごとに所定数のFGパルスを出力するエンコーダ手段と、

前記基準クロックをN分周して位相基準パルスを出力する位相基準パルス生成手段と、

前記位相基準パルス数と前記FGパルス数の差を検出して前記整数位相差として出力する整数位相差検出手段と、

前記位相基準パルスのエッジと前記FGパルスのエッジとの時間差を検出して前記基準クロック単位で計測して前記小数位相差として出力する小数位相差検出手段と、

前記整数位相差と前記小数位相差とを所定の比率で加算して位相差とし、該位相差に基づいて前記モータを駆動制御する制御部と、

を備えたことを特徴とする請求項1に記載のモータ速度制御装置。

【請求項3】

前記整数位相差検出手段は、前記位相基準パルスのエッジでアップ、又はダウンし、前記FGパルスのエッジでダウン、又はアップするアップダウンカウント手段のカウント出力を前記整数位相差とすることを特徴とする請求項2に記載のモータ速度制御装置。

【請求項4】

前記アップダウンカウント手段は、所定の正負リミット値を超えてカウントしないように制御するリミット手段を備えていることを特徴とする請求項3に記載のモータ速度制御装置。

【請求項5】

前記位相差は、分周比Nを用いて前記整数位相差を前記少数位相差のN倍の比率で加算した結果を用いることを特徴とする請求項1乃至4の何れか一項に記載のモータ速度制御装置。

【請求項6】

前記FGパルスのエッジ周期を前記基準クロック単位で計測する周期計測手段を備え、

前記制御部は、前記エッジ周期と前記分周比Nの差を速度差とし、該速度差と前記位相差を所定の比率で加算した結果に基づいて前記モータを駆動制御することを特徴とする請求項1乃至5の何れか一項に記載のモータ速度制御装置。

【請求項7】

請求項1乃至6の何れか一項に記載の速度制御装置を備えたことを特徴とする画像形成装置。

【請求項1】

位相基準パルス数とモータの所定回転角度ごとに発生するFGパルス数との差を検出した整数位相差と、前記位相基準パルスのエッジと前記FGパルスのエッジとの時間差を検出して基準クロック単位で計測した小数位相差と、を所定の比率で加算して位相差とし、該位相差に応じて前記モータを駆動制御することを特徴とするモータ速度制御装置。

【請求項2】

基準周波数に基づく基準クロックを出力する基準クロック発生手段と、

前記モータの所定回転角度ごとに所定数のFGパルスを出力するエンコーダ手段と、

前記基準クロックをN分周して位相基準パルスを出力する位相基準パルス生成手段と、

前記位相基準パルス数と前記FGパルス数の差を検出して前記整数位相差として出力する整数位相差検出手段と、

前記位相基準パルスのエッジと前記FGパルスのエッジとの時間差を検出して前記基準クロック単位で計測して前記小数位相差として出力する小数位相差検出手段と、

前記整数位相差と前記小数位相差とを所定の比率で加算して位相差とし、該位相差に基づいて前記モータを駆動制御する制御部と、

を備えたことを特徴とする請求項1に記載のモータ速度制御装置。

【請求項3】

前記整数位相差検出手段は、前記位相基準パルスのエッジでアップ、又はダウンし、前記FGパルスのエッジでダウン、又はアップするアップダウンカウント手段のカウント出力を前記整数位相差とすることを特徴とする請求項2に記載のモータ速度制御装置。

【請求項4】

前記アップダウンカウント手段は、所定の正負リミット値を超えてカウントしないように制御するリミット手段を備えていることを特徴とする請求項3に記載のモータ速度制御装置。

【請求項5】

前記位相差は、分周比Nを用いて前記整数位相差を前記少数位相差のN倍の比率で加算した結果を用いることを特徴とする請求項1乃至4の何れか一項に記載のモータ速度制御装置。

【請求項6】

前記FGパルスのエッジ周期を前記基準クロック単位で計測する周期計測手段を備え、

前記制御部は、前記エッジ周期と前記分周比Nの差を速度差とし、該速度差と前記位相差を所定の比率で加算した結果に基づいて前記モータを駆動制御することを特徴とする請求項1乃至5の何れか一項に記載のモータ速度制御装置。

【請求項7】

請求項1乃至6の何れか一項に記載の速度制御装置を備えたことを特徴とする画像形成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−253542(P2012−253542A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2011−124191(P2011−124191)

【出願日】平成23年6月2日(2011.6.2)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成23年6月2日(2011.6.2)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]