ランプ駆動制御装置および方法およびこれに組み込まれる信号処理回路および液晶バックライト駆動装置

【課題】

バックライト制御による画質の改善や消費電力低減の具現化に有効な手法を提供する。

【解決手段】

各ランプ電流は、弱平滑された後コンパレータで検出PWM化され、検出PWMはパルス幅カウンタで数値化された後、目標値から減算され、非線形特性付加後、入力誤差信号として出力され、ループフィルタ62によって積分され、定常時の閉ループによる制御信号が生成される。そして、この定常制御信号が駆動パルス生成部56内に点灯ブロックごとに設けられたソフト波形生成部350−1〜350−4に出力され、各ソフト波形生成部によってソフトスタート/ストップ波形が生成された後、出力振幅信号としてパルス変換部370−1〜370−4に出力される。このとき、ソフト波形生成部350−1〜350−4によって、定常状態への達成状況を示す定常達成信号がNOR回路344に出力され、非定常信号としてループフィルタ62に出力される。

バックライト制御による画質の改善や消費電力低減の具現化に有効な手法を提供する。

【解決手段】

各ランプ電流は、弱平滑された後コンパレータで検出PWM化され、検出PWMはパルス幅カウンタで数値化された後、目標値から減算され、非線形特性付加後、入力誤差信号として出力され、ループフィルタ62によって積分され、定常時の閉ループによる制御信号が生成される。そして、この定常制御信号が駆動パルス生成部56内に点灯ブロックごとに設けられたソフト波形生成部350−1〜350−4に出力され、各ソフト波形生成部によってソフトスタート/ストップ波形が生成された後、出力振幅信号としてパルス変換部370−1〜370−4に出力される。このとき、ソフト波形生成部350−1〜350−4によって、定常状態への達成状況を示す定常達成信号がNOR回路344に出力され、非定常信号としてループフィルタ62に出力される。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、ランプ駆動制御装置および方法およびこれに組み込まれる信号処理回路および液晶バックライト駆動装置に関し、特に、画質の改善や消費電力の低減に有効な手法に関する。

【背景技術】

【0002】

液晶TVに代表される液晶ディスプレイの動画性能を向上させる手法として、液晶バックライトの光源を複数のブロックに分割し、この分割したブロックごとに点灯タイミングを制御する手法が検討されている。この手法は、例えば、特許文献1に記載されている。

【0003】

この特許文献1には、同文献の図1に記載されたように、4つのブロックに分割されたバックライト32〜35が駆動回路28〜31によってそれぞれ独立に駆動される構成が示されている。

【0004】

一方で、液晶ディスプレイの消費電力を低減させる手法として、映像の平均輝度に応じてバックライトの輝度を制御するAPL−AGC(Average Picture Level Automatic Gain Control)という手法が知られている。この手法は、例えば、特許文献2乃至5

1下記の文献に記載されている。

【0005】

これらの文献には、映像シーンに連動させたバックライト制御の有効な手法が記載されているが、これらの手法を実際の製品で実現させるためには、LSIで構成された画像処理回路に変更を加える必要があり、バックライト駆動ユニットの構成や制御方法により対応が異なるため、画像処理LSI内でのバリエーション対応が困難であった。

【0006】

また、より消費電力を低減させるためには、バックライト制御手法そのものの高度化や多種類のバックライト制御手法を次々と組み合わせてゆく必要があり、莫大な開発費用のかかる大規模な画像処理回路内でのきめ細かい対応が困難である。

【0007】

また、複数のブロックに分割して制御する場合、従来のようなアナログ制御手段を用いると、ブロック間の電流バランス精度などにも困難が有り、そしてブロックの分割数に比例して制御回路規模も増大し、その分コストも増大するという問題が有った。また、ブロック間のキャリア同期や連動制御も複雑になり連動制御専用に別のデジタル制御回路が必要になった。

【特許文献1】特開2005−99367号公報

【特許文献2】特開2002−156951号公報

【特許文献3】特開2002−258401号公報

【特許文献4】特開2002−357810号公報

【特許文献5】特開2004−085961号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

そこで、本発明は、バックライト制御による画質の改善や消費電力低減の具現化に有効な手法を提供する。

【課題を解決するための手段】

【0009】

上記目的を達成するため、請求項1記載の発明は、ランプの駆動制御を行うランプ駆動制御装置において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記比較して得られた誤差成分に非線形特性を付加する手段と、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段とを具備することを特徴とする。

【0010】

また、請求項2記載の発明は、請求項1記載の発明において、前記非線形特性は、前記誤差成分が定常付近であるときの前記フィードバック制御のゲインを1としたときに、前記誤差成分が前記定常付近よりもマイナス側であるときの前記フィードバック制御のゲインを1よりも大きく設定し、前記誤差成分が前記定常付近よりもプラス側であるときの前記フィードバック制御のゲインを1よりも大きく設定することを特徴とする。

【0011】

また、請求項3記載の発明は、液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と、前記フィードバック制御手段に前記ランプに流す電流値のON/OFFを制御する信号を入力する手段と、前記ON/OFF信号の立ち上がりおよび/または立ち下がりに合わせて、前記ランプの制御量として複数種の傾斜値を適用する手段とを具備することを特徴とする。

【0012】

また、請求項4記載の発明は、請求項3記載の発明において、前記ON/OFF信号の立ち上がりおよび/または立ち下がりの直前および/または直後は、前記複数種の傾斜値のうち、緩やかな傾斜値が適用されることを特徴とする。

【0013】

また、請求項5記載の発明は、請求項3記載の発明において、前記液晶バックライトは、前記ランプを備えた複数の点灯ブロックから構成され、該各点灯ブロック内に設けられたランプに対する前記傾斜値の適用は、点灯ブロックごとに独立で行われることを特徴とする。

【0014】

また、請求項6記載の発明は、請求項3記載の発明において、前記ランプに電流が流れない低電圧範囲では、前記複数種の傾斜値のうち、急な傾斜値が選択されることを特徴とする。

【0015】

また、請求項7記載の発明は、請求項3記載の発明において、前記ON/OFF信号に基づく制御により、ランプがOFFとなった時には、該ランプに電流が流れない低電圧で前記ON/OFF信号のON状態を待機することを特徴とする。

【0016】

また、請求項8記載の発明は、請求項3記載の発明において、前記ON/OFF信号がON状態となる前に、前記ランプに電流が流れない低電圧で該ON状態を待機することを特徴とする。

【0017】

また、請求項9記載の発明は、ランプの駆動制御を行うランプ駆動制御方法において、前記ランプに流れる電流値を検出するステップと、前記検出した電流値を目標値と比較するステップと、前記比較して得られた誤差成分に非線形特性を付加するステップと、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行うステップとを具備することを特徴とする。

【0018】

また、請求項10記載の発明は、ランプの駆動制御を行うランプ駆動制御装置に組み込まれる信号処理回路において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記比較して得られた誤差成分に非線形特性を付加する手段と、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段とを具備することを特徴とする。

【0019】

また、請求項11記載の発明は、液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記比較して得られた誤差成分に非線形特性を付加する手段と、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段とを具備することを特徴とする。

【0020】

請求項1、2記載の発明によれば、フィードバック制御の誤差入力に非線形特性が付加され、例えば定常許容範囲より出力電流が低い時にゲインを高く設定することにより起動の高速化を図れ、また、回路異常や感電などにより、定常許容範囲より高い電流が流れた時にもゲインを高く設定することにより危険な電流からの保護の高速化を図れると共に定常状態での精度や安定性と両立させることができる。

【0021】

請求項3記載の発明によれば、フィードバックによる閉ループ制御に対して、ランプON/OFF時に複数種の傾斜値が出力に強制的に適用されるため、ループ応答特性とは無関係に好適なソフトスタート/ストップ・シーケンス制御を行うことができる。

【0022】

請求項4記載の発明によれば、点灯開始直後および、消灯完了直前に緩やかな傾斜が適用されるため、電流量の急変化による高周波成分が抑えられ、出力トランスなどの静音化を図ることができる。

【0023】

請求項5記載の発明によれば、複数チャンネルの一括電流制御の場合においても各チャンネルのスタート/ストップ・シーケンス制御を独立に行うことができるため、多チャンネル独立ON/OFF制御構成においても小規模回路で構成することができる。

【0024】

請求項6記載の発明によれば、ランプに電流が流れない低電圧範囲では急傾斜が適用されるため、ランプの電流が流れ始めるまでの無駄時間を短縮し、点灯遅れを小さくすることができる。

【0025】

請求項7記載の発明によれば、ランプに電流が流れない低電圧で待機する構成を有するため、ランプ以外に流れる電流、例えば配線や出力トランスの浮遊容量に流れる電流も含めて急な変化を抑えることができるため、静音化とランプの点灯遅れを小さくすることの両立に有効である。

【0026】

請求項8記載の発明によれば、ランプに電流が流れない低電圧で事前待機する構成を有するため、静音化とランプの点灯遅れを小さくすることの両立に有効でありながら、待機中に浮遊容量などに流れる電流やブリッジ回路のスイッチング・ロスによる無駄な電力消費も抑えることができる。

【発明の効果】

【0027】

以上説明したように、本発明によれば、バックライト制御による画質の改善や消費電力低減が安価な構成で期待できる。

【発明を実施するための最良の形態】

【0028】

以下、本発明の実施形態を添付図面を参照して詳細に説明する。尚、本発明は、以下説明する実施形態に限らず適宜変更可能である。

【0029】

図1は、本発明の実施形態に係る液晶バックライト駆動装置の構成を示す概念図である。同図(a)に示すように、本液晶バックライト駆動装置は、液晶パネル10の背面にバックライト光源として分割配置された点灯ブロックBL1〜BL4と、これら分割配置された各点灯ブロックを制御するバックライト制御部16で構成される。

【0030】

同図(a)において、画像処理部14は、所定のフレーム周期で入力される映像信号VDに基づいて所定の画像処理を行い、その結果として、液晶パネル10を駆動する信号を液晶駆動部12に出力し、点灯ブロックBL1〜BL4を制御する信号をバックライト制御部16に出力する。

【0031】

液晶駆動部12は、画像処理部14の出力信号に基づいて、液晶パネル10を構成する液晶素子の配向を制御することで、表示映像を構成する各画素の色彩や階調を設定し、バックライト制御部16は、画像処理部14の出力信号に基づいて、点灯ブロックBL1〜BL4の光量や点灯状態を制御することで、該当する表示領域の光量やバックライトのON/OFFを制御する。

【0032】

ここで、点灯ブロックBL1〜BL4は、液晶の走査方向に沿って4つのブロックに分割され、バックライト制御部16は、液晶駆動部12が駆動する液晶領域に対応する点灯ブロックの点灯状態を制御することで、例えば、液晶の遷移タイミングを避けたバックライトの順次点灯による疑似インパルス駆動型の動画改善が行われる。

【0033】

この分割された各点灯ブロックは、同図(b)に点灯ブロックBL1を代表として例示したように、光源となるランプL1を備え、このランプは、スイッチング素子Q1〜Q4で構成されたブリッジ回路とトランスTR1により駆動される。

【0034】

ここで、ブリッジ回路は、スイッチング素子Q1およびQ4で構成される正方向電流側(iP)のスイッチング部と、スイッチング素子Q3およびQ2で構成される負方向電流側(iN)のスイッチング部とで構成され、図中の点線iPおよびiNで示すように、正方向半サイクル電流iPは、スイッチング素子Q1、トランスTR1、スイッチング素子Q4の方向に流れ、負方向半サイクル電流iNは、スイッチング素子Q3、トランスTR1、スイッチング素子Q2の方向に流れ、その結果、負荷となるランプに対して交流電流が供給される。この動作は各点灯ブロックBL1〜BL4で同様である。

【0035】

図2は、図1に示した液晶バックライト駆動装置の全体構成を示す回路ブロック図である。同図に示すように、本装置では、ブリッジ回路と点灯ブロックとを含むアナログ回路部100がバックライト制御部16によって制御される。

【0036】

点灯ブロックBL1を駆動するブリッジ回路は、制御信号S1−1で駆動されるスイッチング素子対Q1、Q2と、制御信号S1−2で駆動されるスイッチング素子対Q3、Q4とで構成される。他の点灯ブロックBL2、BL3、BL4についても同様に構成される。

【0037】

バックライト制御部16には、ブリッジ回路の制御信号S1−1、S1−2、S2−1、S2−2、S3−1、S3−2、S4−1、S4−2に対応したポートP1〜P4が設けられ、これらのポートから各スイッチング素子対を制御する信号が出力される。

【0038】

また、各点灯ブロックBL1〜BL4には、ランプL1〜L4を流れる電流を検出するための抵抗R1〜R4が設けられ、検出された電流値は、バックライト制御部16の対応ポートP1〜P4に入力される。この入力された電流値に基づいて、点灯ブロックごとに調光制御が行われる。

【0039】

図3は、図2に示したブリッジ回路の動作例を示す回路図およびタイミングチャートである。同図(a)に示すように、ブリッジ回路を構成するスイッチング素子Q1〜Q4への制御入力をA〜Dとすると、これらA〜Dの制御信号の相対関係によって負荷LOADに供給される電力量が決定される。

【0040】

即ち、同図(b)に示すように、図中「Timing」で示したキャリアタイミングに同期させた出力PWM信号に基づいて、A〜Dのスイッチング波形を生成し、制御信号AがONの期間は負荷LOADに正方向の電流が供給され、制御信号CがONの期間は負荷LOADに負方向の電流が供給される。

【0041】

負荷LOADに供給する電力量は出力PWM波形のデューティによって制御され、負荷LOADに大きな電力を供給する場合は、出力PWM波形のデューティを大きくし、負荷LOADに小さな電力を供給する場合は、出力PWM波形のデューティを小さくする。

【0042】

このような電力供給量の制御を各点灯ブロックごとに検出した電流値に基づいて、点灯ブロックごとに行うことにより、点灯ブロック間の輝度バランスを調整する制御や、映像のシーンに応じて点灯ブロックごとに輝度を変化させるシーン制御を行うことができる。

【0043】

図4は、図2に示したブリッジ回路の他の動作例を示す回路図およびタイミングチャートである。同図(a)に示すように、ブリッジ回路を構成するスイッチング素子Q1〜Q4への制御入力をA〜Dとすると、これらA〜Dの制御信号の相対関係によって負荷LOADに供給される電力量が決定される。

【0044】

即ち、同図(b)および(c)に示すように、制御信号A〜Dのスイッチングデューティを一定条件とし、制御信号AとBのON状態を相補的に切り替えるとともに、制御信号CとDのON状態を相補的に切り替え、制御信号AとDの重なりによって負荷LOADに正方向の電流が供給され、制御信号BとCの重なりによって負荷LOADに負方向の電流が供給される。

【0045】

即ち、制御信号AとBのペアに対する制御信号CとDのペアの位相を変化させることで、負荷LOADに供給する電力量を制御することができる。負荷LOADに大きな電力を供給する場合は、同図(b)に示すように、両ペアの重なりを大きくすれば良く、負荷LOADに小さな電力を供給する場合は、同図(c)に示すように、両ペアの重なりを小さくすれば良い。

【0046】

このような電力供給量の制御を点灯ブロックごとに検出した電流値に基づいて、点灯ブロックごとに行うことにより、点灯ブロック間の輝度バランスを調整する制御や、映像のシーンに応じて点灯ブロックごとに輝度を変化させるシーン制御を行うことができる。

【0047】

図5は、図1に示した液晶バックライト駆動装置の制御構成を示す回路ブロック図である。同図に示すように、アナログ回路部100に設けられた点灯ブロックBL1〜BL4には、電源回路20からの直流電源が供給され、この直流電流がブリッジ回路によりスイッチング・昇圧されて高圧交流が生成される。

【0048】

ここで、バックライト制御部16は、デジタル回路によって構成され、点灯ブロックBL1〜BL4ごとに検出抵抗を介して検出されたランプ電流は、入力ポートP1〜P4からバックライト制御部16に入力される。

【0049】

この入力されたランプ電流情報は、点灯ブロックごとに、数値化部58でA/D変換された後、比較部60によって制御目標値と比較され、その結果得られた誤差情報がループフィルタ62で積分され、この積分結果が駆動パルス生成部56により処理されて、各点灯ブロックBL1〜BL4を駆動するための駆動パルスが生成される。

【0050】

これらの駆動パルスは、出力ポートP1〜P4からドライバ22を介して各点灯ブロックBL1〜BL4に出力され、このドライバ出力に基づいてブリッジ回路によるランプの点灯制御が行われる。

【0051】

数値化部58および駆動パルス生成部56には、タイミング発生部310で生成された波形生成の基本信号となるキャリアタイミングが供給され、このキャリアタイミングを利用して、数値化部58によるA/D変換と、駆動パルス生成部56による駆動パルスの生成が行われる。

【0052】

数値化部58により数値化されたデータは、点灯ブロックごとに、ランプのインピーダンス等のパラメータを検出するパラメータ検出部52に出力され、ここで検出されたパラメータに基づいて保護回路50による保護動作と起動制御部54によるランプの起動制御が行われる。

【0053】

保護回路50による保護動作としては、電源回路20の遮断、駆動パルスのデューティ低減、起動制御の停止等が、検出されたパラメータから判断された保護すべき程度に応じて適宜行われる。

【0054】

図6は、図5に示した数値化部および比較部の構成例を示す回路ブロック図である。同図では、点灯ブロックBL1のみを示すが他の点灯ブロックについても同様に構成される。同図に示すように、点灯ブロックのランプ電流情報は、検波部220によって検波され、この結果が平滑平均化RCフィルタ230によって強平滑または弱平滑平均化され、その結果がコンパレータ240によってリファレンス三角波と比較され、その結果が検出PWM信号として出力される。

【0055】

検出PWM信号は、入力パルス幅カウント回路322によってカウントされ、その結果が減算回路324によって目標値との差異が算出されて、その結果が非線形特性付加部326によって非線形処理されて入力誤差信号が生成される。

【0056】

図7は、検出PWM信号を生成する第1の例を示す回路ブロック図である。同図に示す例は、検出抵抗R1を介して検出したランプ電流を全波整流、強平滑平均化し、リファレンス三角波と比較することで検出PWM信号を生成する場合の例である。

【0057】

ここで、検波部220は、全波整流回路222とクリップ回路224によって構成され、このクリップ回路によって整流後の波形のゼロ値付近がクリップ整形される。

【0058】

平滑平均化RCフィルタ230は、強平滑平均化特性、即ち、長放電時定数を持たせたRC充放電回路によって構成され、リファレンス三角波生成部250は、リファレンスとなるパルス信号を平滑するRC回路によって構成され、このRC回路にキャリアタイミングや電流オフセットPWM信号等のリファレンスパルスが入力されることで、キャリアに同期した三角波が生成される。

【0059】

上記平滑平均化信号とリファレンス三角波がコンパレータ240により比較されて、ランプ電流情報がパルス信号として表現された検出PWM信号が生成される。

【0060】

尚、コンパレータ240に入力するリファレンス信号を変化させることにより、目標電流を可変とする構成としてもよい。例えば、同図のリファレンス三角波生成部250に入力するリファレンスパルスとしてキャリアタイミングを使用する場合には、該キャリアタイミングのデューティを変化させて目標電流を可変としてもよく、また、リファレンスパルスに別途電流オフセットPWMを供給して長時定数平滑フィルタ252によるDCを加算したり、リファレンスパルス自身を高速1ビット変調オフセット付き三角波、高速パルス密度変調PDM等を使用して所定のオフセットと波形を持ったリファレンス三角波を発生させて目標電流を可変としてもよく、また、図6内の入力パルス幅カウンタ322の初期ロード値を変化させたり、また図6内の減算回路324に供給する目標値を変化させて目標電流を可変としても良い。

【0061】

図8は、検出PWM信号を生成する第1の例に係るA/D変換動作を示す波形タイミングチャートである。同図(a)に示すように、検出抵抗で検出されたランプ電流は、実線で示した交流波形となり、この波形が全波整流されて同図(b)に示す整流波形となる。

【0062】

その後、同図(c)に示すように、整流後の波形のゼロ付近がクリップされて、その波形(薄い実線)が強平滑平均化されて振幅の小さな擬似三角波(濃い実線)が生成される。

【0063】

一方、同図(e)に示すように、キャリアタイミングに同期したリファレンス三角波(濃い実線)が強平滑平均化波形(薄い実線)と比較されて同図(f)に示したPWMパルス波形が生成される。

【0064】

図9は、検出PWM信号を生成する第2の例を示す回路ブロック図である。同図に示すように、トランスTR1が2出力型のツイントランスで構成され、一つのトランスに2本のランプL1−1、L1−2が接続される場合には、抵抗R1−1、R1−2で検出される波形の極性が反転することを利用して、半波整流回路221を用いた疑似全波整流を行う構成としても良い。

【0065】

ここで、検波部220は、半波整流回路222とクリップ回路224によって構成され、このクリップ回路によって整流後の波形のゼロ値付近がクリップ整形される。

【0066】

平滑平均化RCフィルタ230は、弱平滑平均化特性、即ち、短放電時定数を持たせたRC充放電回路によって構成され、リファレンス三角波生成部250は、リファレンスとなるパルス信号を平滑するRC回路によって構成され、このRC回路にリファレンスパルスが入力されることで、キャリアに同期した三角波が生成される。

【0067】

上記平滑平均化信号とリファレンス三角波がコンパレータ240により比較されて、ランプ電流情報がパルス信号として表現された検出PWM信号が生成される。

【0068】

図10は、検出PWM信号を生成する第2の例に係るA/D変換動作を示す波形タイミングチャートである。同図(a)に示すように、ランプ電流は実線と点線で示した極性の異なる電流が検出され、これらが半波整流されダイオードORにより合成されて同図(b)に示す整流波形となる。

【0069】

その後、同図(c)に示すように、整流後の波形のゼロ付近がクリップされて、その波形(薄い実線)が弱平滑平均化されて振幅の小さな擬似三角波(濃い実線)が生成される。

【0070】

一方、同図(e)に示すように、キャリアタイミングに同期したリファレンス三角波(濃い実線)が弱平滑平均化波形(薄い実線)と比較されて同図(f)に示した検出PWM波形が生成される。

【0071】

図11は、検出PWM信号を生成する第3の例を示す回路ブロック図である。同図に示す例は、コンパレータ240のリファレンスとして一定値を用いた場合の例であり、その他は前述の第2の例と同じである。

【0072】

図12は、検出PWM信号を生成する第3の例に係るA/D変換動作を示す波形タイミングチャートである。この例の場合は、同図(e)に示すように、一定値のリファレンス(濃い実線)が弱平滑平均化波形(薄い実線)と比較されて同図(f)に示したPWMパルス波形が生成される。その他は前述の第2の例と同じである。

【0073】

図13は、検出PWM信号を生成する第4の例を示す回路ブロック図である。同図に示す例は、同図に示す例は、検出抵抗R1を介して検出したランプ電流を全波整流、弱平滑平均化し、一定のリファレンスと比較することで検出PWM信号を生成する例であり、その他は前述の第1の例と同じである。

【0074】

図14は、検出PWM信号を生成する第4の例に係るA/D変換動作を示す波形タイミングチャートである。この例の場合は、同図(d)〜(f)に示すように、弱平滑平均化信号と一定のリファレンス値が比較されて検出PWM信号が生成される。その他は前述の第1の例と同じである。

【0075】

図15は、検出PWM信号を生成する第5の例を示す回路ブロック図である。同図に示す例は、リファレンス三角波生成フィルタ250に倍周波リファレンスパルスを供給して倍周波三角波を生成した例であり、その他は前述の第4の例と同じである。

【0076】

図16は、検出PWM信号を生成する第5の例に係るA/D変換動作を示す波形タイミングチャートである。この例の場合は、同図(e)に示すように、倍周波三角波リファレンス(濃い実線)が弱平滑平均化波形(薄い実線)と比較されて同図(f)に示したPWMパルス波形が生成される。その他は前述の第4の例と同じである。

【0077】

図17は、検出PWM信号を生成する第6の例を示す回路ブロック図である。この例は、同図(a)に示すように、図15の倍周波三角波生成部251にエッジ強調波形を適合させた場合の例である。この場合は、同図(b)に示すように、弱平滑平均化波形が実際は丸みを持っている部分をエッジ強調波形が適用された尖頭形状の三角波で吸収することができる。その他は前述の第5の例と同じである。

【0078】

図18は、検出PWM信号を生成せずに直に電流波形を高速AD変換してから平均電流値を得る場合の第6の例を示す回路ブロック図である。この例の場合は、同図に示すように、キャリアの8倍周波数の高速サンプリングクロックで電流波形を電圧化後そのままA/Dコンバータ360によりAD変換する。

【0079】

そして、波形の半サイクル毎の中ほど3サンプルをフリップフロップ362−1、362−2で取得し、加算器363によりデジタル加算した結果を絶対値演算回路364により絶対値化し、その後、平均値演算フリップフロップ366により、再度キャリアの2倍周波数、つまり、半サイクル毎の演算サンプリングクロックで再サンプリングして、半サイクル毎のゼロクロス近辺以外の数値化平均電流値を得る。以降、図5の比較回路60に入力され前述と同様の処理がなされる。

【0080】

図19は、図18に示した回路ブロックの処理のタイミングを示すタイミングチャートである。同図(a)および(b)に示すように、この例のA/Dコンバータでは、電流キャリア周波数の半サイクルに4回サンプリングされるが、同図(c)に示すように、その連続する3サンプル出力の合計値を半サイクルに1回、つまり4サンプルに1回の演算クロックで再サンプルして、同図(d)に示すように、1サイクル内の波形の同図(a)中のa〜iの内、ゼロクロス近辺のeとiを除いた「b+c+d」および「f+g+h」の平均値出力を得る。

【0081】

図20は、図6に示した非線形特性付加回路326で負荷する非線形特性の例を示す概念図である。同図に示すように、縦軸に示す誤差出力の値に応じて横軸に示すPWMデューティが決定される。ここで同図中「x2」で示す実線領域は、定常付近に達するまでは2倍ゲインにして速く立ち上げるための特性であり、同図中「x1」で示す実線領域のうちマイナス誤差定常範囲は、定常値近傍で定常ゲインに切り換えるための特性であり、同図中「x1」で示す実線領域のうちプラス誤差定常範囲は、一気に定常範囲を飛び越えて下がらないよう大きめに確保される特性であり、同図中「x8」で示す実線領域は、感電などの場合の危険な過電流は8倍ゲインにして急速に押さえるための特性である。

【0082】

図21は、図5に示したループフィルタの構成を示す回路ブロック図である。同図では、点灯ブロックBL1のみを示すが他の点灯ブロックについても同様に構成される。同図に示すように、ループフィルタ62は、加算回路332と、出力クリップ回路334と、フリップフロップ336によって構成され、このループフィルタによって非線形処理された入力誤差信号の積分処理が行われ、閉ループ制御信号が生成される。

【0083】

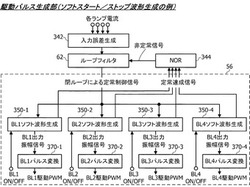

図22は、1ブロック共通単一電流制御でブロックごとに独立にソフトスタート/ストップ制御を行う場合の構成例を示す回路ブロック図である。

【0084】

図23は、図22に示した入力誤差生成部342の構成を示す回路ブロック図である。同図に示すように、各ブロックランプ電流の最大値選択兼全波整流回路を通って1本化された整流後電流波形は弱平滑された後コンパレータで検出PWM化される。検出PWMはパルス幅カウンタで数値化された後、目標値から減算され、非線形特性付加後、入力誤差信号として出力される。これらの構成および動作は図6と同様に行われる。

【0085】

上記のようにして生成された入力誤差信号は、図22に示したループフィルタ62によって積分され、定常時の閉ループによる制御信号が生成される。

【0086】

そして、この定常制御信号が駆動パルス生成部56内に点灯ブロックごとに設けられたソフト波形生成部350−1〜350−4に出力され、各ソフト波形生成部によってソフトスタート/ストップ波形が生成された後、出力振幅信号としてパルス変換部370−1〜370−4に出力される。このとき、ソフト波形生成部350−1〜350−4によって、定常状態への達成状況を示す定常達成信号がNOR回路344に出力され、非定常信号としてループフィルタ62に出力される。

【0087】

各点灯ブロックの出力振幅信号は、バルス変換部370−1〜370−4によって、振幅信号がパルス信号に変換され、各点灯ブロックの駆動PWM信号として、図5に示すバックライト制御部16の出力ポートP1〜P4からドライバ22を介して各点灯ブロックBL1〜BL4に出力される。

【0088】

図24は、図22に示したループフィルタの構成を示す回路ブロック図である。同図に示すように、ループフィルタ62は、加算回路332と、出力クリップ回路334と、フリップフロップ336と、AND回路338によって構成され、このループフィルタによって入力誤差信号の積分処理が行われる。

【0089】

AND回路338がフリップフロップ336に出力する信号は、非定常時の開ループ化による出力上昇を防止するためのホールド信号として出力され、出力クリップ回路346がAND回路348に出力する信号は、正の場合に定常制御値の上昇方向を示す。尚、このAND回路は必ずしも必要ではなく非定常時無条件でフリップフロップ336をホールドするようにしてもよい。

【0090】

図25は、図22に示したソフトスタート/ストップ波形生成部の構成を示す概念図である。同図では、点灯ブロックBL1のみを示すが他の点灯ブロックについても同様に構成される。同図に示すように、点灯ブロックごとに生成されたループフィルタ出力信号は、比較回路354および355、選択回路356に出力され、定常達成状態に応じて選択処理することでPWMデューティを示す出力振幅信号が生成される。

【0091】

ここで、比較回路354が出力するゼロ近傍または 定常値近傍を示す信号に基づいて、複数の傾斜値が傾斜値選択回路351によって選択され、この傾斜値が極性選択回路352によって点灯ブロックのON/OFF信号に基づく極性が適用され、その結果が加算回路353によって積分ループに加算され、強制カーブの生成が行われる。

【0092】

図26は、ソフトスタート/ストップ波形の例を示すタイミングチャートである。同図(a)は、点灯ブロックBL1のON/OFF信号を示し、同図(b)は、図25の傾斜値選択部351によって選択された出力振幅の電圧波形を示し、同図(c)は、ゼロ値近傍の傾斜部および定常値近傍の傾斜部に対応したタイミングを示し、同図(d)は点灯ブロックBL1が定常に達したタイミングを示し、同図(e)は、点灯ブロックBL2のON/OFF信号を示し、同図(f)は、図25の傾斜値選択部351によって選択された出力振幅の電圧波形を示し、同図(g)は、点灯ブロックBL1またはBL2が定常状態に達成するタイミングを示す。

【0093】

同図に示す制御の特徴としては、まず、閉ループのままスタート/ストップ時の出力のスルーレートを強制的に制限し、常時制御し続けたまま強制的に上昇および下降カーブを作ることで、ON/OFFをスムーズに切換える手法がある。

【0094】

この手法では、図5に示した制御構成、即ち、定常時の目標電流に対して誤差を検出し、この誤差成分をループフィルタを介して出力の自動制御を行う構成において、別途、図22に示した各点灯ブロックのON/OFF制御入力に合わせて、図26(b)に折れ線傾斜で図示したような、ON時上昇、OFF時下降の出力制御用強制カーブを生成する。この強制カーブの生成は、図25に示した傾斜値選択部351、極性選択部352、加算回路353により行われる。

【0095】

ここで、図25に示した比較回路354により、生成された強制カーブが上昇時に図26(b)の「閉ループ定常値」で示した自動制御値を超えようとした時には、図25の選択回路356により自動制御側の出力(同図中「閉ループによる定常制御信号」)を選択出力すると共に、その値を次の瞬間の強制カーブ出力用の現在値としても使用する。

【0096】

また、強制カーブで下降しようとする時は、その自動制御値から強制的に下降させて行き、自動制御値より小さい範囲では強制カーブ出力を選択出力する。下降してゼロその他所定の値以下になった時、その所定の値にクリップしその値を出力する。

【0097】

強制カーブが選択出力されている間は、自動制御値がオープンループとなって過上昇しないように、自動制御出力をホールドさせる。これにより自動制御と開始終了時の強制傾斜カーブとの高精度で連続的な移行が可能となり、静音化が図られる。

【0098】

上記に加え、スタート/ストップ直後やスタート/ストップ完了直前に傾斜を緩やかにしてより静音化を進める方法も有効である。例えば、強制カーブが自動制御値近傍にいる時や下限近傍にいる時には、より緩やかな傾斜値を選択することにより、上昇、下降のカーブを緩やかに構成してもよい。これにより定常値や下限値との切換えが滑らかになり、また電流量変化の高周波成分も抑えられ、さらに静音化される。

【0099】

また、スタートストップ時の強制カーブによる制御は、各点灯ブロック独立の多チャンネル制御で行うことにより、小規模な回路で独立に任意のタイミングでのON/OFF制御が可能になる。

【0100】

例えば、図22に示すように、各点灯ブロックそれぞれの定常電流値を共通の定常自動制御回路で制御し、スタート/ストップにより各点灯ブロックごと独立にON/OFFおよび出力の上昇および下降傾斜を付ける時、共通制御対象のどれか1チャンネルでも定常制御出力が選択されている時は、ホールドせず制御ループを有効にして、全てのチャンネルが定常制御出力選択状態から脱した時、定常制御をホールド状態にする。これにより各チャンネルの状態に依らず1組の定常自動制御回路で、安価に自動制御と独立スタート/ストップ傾斜カーブ生成が可能となる。

【0101】

図27は、ソフトスタート/ストップ波形の他の例を示すタイミングチャートである。同図(a)は、点灯ブロックBL1のON/OFF信号を示し、同図(b)〜(d)は、このON/OFF信号に対するソフトスタート/ストップの制御例を示す。

【0102】

同図(b)は、スタート/ストップ時に、ランプに電流が流れない低電圧出力範囲は、急傾斜で電圧の出力の上昇および下降を行い特に点灯時間までの時間を短縮する例であり、同図に示したゼロ点から放電開始電圧より少し下の切替閾値電圧までの間の傾斜が該当する部分である。

【0103】

同図(c)は、消灯時にはランプに電流が流れない範囲の低電圧でスタンバイしておき、スタート時の点灯開始までの時間短縮と静音化を図る例である。

【0104】

同図(d)は、同図(e)に示すような、ON/OFF信号より少し先行したスタンバイ開始信号により、ランプに電流が流れない範囲のスタンバイ電圧に事前待機し、スタート時の時間短縮と静音化を図りながらも、待機中に浮遊容量などに流れる電流やブリッジ回路のスイッチング・ロスによる、消灯時には不必要な消費電力の削減を図る例である。

【産業上の利用可能性】

【0105】

本発明によれば、より高度なバックライト制御が可能になるため、高画質化や消費電力の低減が要求される大型液晶ディスプレイへの適用が期待される。

【図面の簡単な説明】

【0106】

【図1】本発明の実施形態に係る液晶バックライト駆動装置の構成を示す概念図である。

【図2】図1に示した液晶バックライト駆動装置の全体構成を示す回路ブロック図である。

【図3】図2に示したブリッジ回路の動作例を示す回路図およびタイミングチャートである。

【図4】図2に示したブリッジ回路の他の動作例を示す回路図およびタイミングチャートである。

【図5】図1に示した液晶バックライト駆動装置の制御構成を示す回路ブロック図である。

【図6】図5に示した数値化部および比較部の構成例を示す回路ブロック図である。

【図7】検出PWM信号を生成する第1の例を示す回路ブロック図である。

【図8】検出PWM信号を生成する第1の例に係るA/D変換動作を示す波形タイミングチャートである。

【図9】検出PWM信号を生成する第2の例を示す回路ブロック図である。

【図10】検出PWM信号を生成する第2の例に係るA/D変換動作を示す波形タイミングチャートである。

【図11】検出PWM信号を生成する第3の例を示す回路ブロック図である。

【図12】検出PWM信号を生成する第3の例に係るA/D変換動作を示す波形タイミングチャートである。

【図13】検出PWM信号を生成する第4の例を示す回路ブロック図である。

【図14】検出PWM信号を生成する第4の例に係るA/D変換動作を示す波形タイミングチャートである。

【図15】検出PWM信号を生成する第5の例を示す回路ブロック図である。

【図16】検出PWM信号を生成する第5の例に係るA/D変換動作を示す波形タイミングチャートである。

【図17】検出PWM信号を生成する第6の例を示す回路ブロック図である。

【図18】検出PWM信号を生成せずに直に電流波形を高速AD変換してから平均電流値を得る場合の第6の例を示す回路ブロック図である。

【図19】図18に示した回路ブロックの処理のタイミングを示すタイミングチャートである。

【図20】図6に示した非線形特性付加回路326で負荷する非線形特性の例を示す概念図である。

【図21】図5に示したループフィルタの構成を示す回路ブロック図である。

【図22】1ブロック共通単一電流制御でブロックごとに独立にソフトスタート/ストップ制御を行う場合の構成例を示す回路ブロック図である。

【図23】図22に示した入力誤差生成部342の構成を示す回路ブロック図である。

【図24】図22に示したループフィルタの構成を示す回路ブロック図である。

【図25】図22に示したソフトスタート/ストップ波形生成部の構成を示す概念図である。

【図26】ソフトスタート/ストップ波形の例を示すタイミングチャートである。

【図27】ソフトスタート/ストップ波形の他の例を示すタイミングチャートである。

【符号の説明】

【0107】

10…液晶パネル、12…液晶駆動部、14…画像処理部、16…バックライト制御部、20…電源回路、22…ドライバ、50…保護回路、52…パラメータ検出部、54…起動制御部、56…駆動パルス生成部、58…数値化部、60…比較部、62…ループフィルタ、70…タイミング発生部、100…アナログ回路部、220…検波部、221…半波整流回路、222…全波整流回路、224…クリップ回路、230…平滑平均化RCフィルタ、240…コンパレータ、250…リファレンス三角波生成フィルタ、300…デジタル回路部、320…入力カウンタ、322…入力パルス幅カウント部、324…減算部、326…非線形特性付加部、330…ループフィルタ、332…加算部、334…出力クリップ部、336…フリップフロップ、340…最大値選択回路、344…NOR回路、348…AND回路、350…ソフト波形生成部、351…傾斜値選択部、352…極性選択部、353…加算回路、354…比較回路、355…比較回路、356…選択回路、357…レジスタ回路、360…A/Dコンバータ、362…フリップフロップ、363…加算器、364…絶対値演算回路、366…平均値演算フリップフロップ、370…バルス変換部

【技術分野】

【0001】

この発明は、ランプ駆動制御装置および方法およびこれに組み込まれる信号処理回路および液晶バックライト駆動装置に関し、特に、画質の改善や消費電力の低減に有効な手法に関する。

【背景技術】

【0002】

液晶TVに代表される液晶ディスプレイの動画性能を向上させる手法として、液晶バックライトの光源を複数のブロックに分割し、この分割したブロックごとに点灯タイミングを制御する手法が検討されている。この手法は、例えば、特許文献1に記載されている。

【0003】

この特許文献1には、同文献の図1に記載されたように、4つのブロックに分割されたバックライト32〜35が駆動回路28〜31によってそれぞれ独立に駆動される構成が示されている。

【0004】

一方で、液晶ディスプレイの消費電力を低減させる手法として、映像の平均輝度に応じてバックライトの輝度を制御するAPL−AGC(Average Picture Level Automatic Gain Control)という手法が知られている。この手法は、例えば、特許文献2乃至5

1下記の文献に記載されている。

【0005】

これらの文献には、映像シーンに連動させたバックライト制御の有効な手法が記載されているが、これらの手法を実際の製品で実現させるためには、LSIで構成された画像処理回路に変更を加える必要があり、バックライト駆動ユニットの構成や制御方法により対応が異なるため、画像処理LSI内でのバリエーション対応が困難であった。

【0006】

また、より消費電力を低減させるためには、バックライト制御手法そのものの高度化や多種類のバックライト制御手法を次々と組み合わせてゆく必要があり、莫大な開発費用のかかる大規模な画像処理回路内でのきめ細かい対応が困難である。

【0007】

また、複数のブロックに分割して制御する場合、従来のようなアナログ制御手段を用いると、ブロック間の電流バランス精度などにも困難が有り、そしてブロックの分割数に比例して制御回路規模も増大し、その分コストも増大するという問題が有った。また、ブロック間のキャリア同期や連動制御も複雑になり連動制御専用に別のデジタル制御回路が必要になった。

【特許文献1】特開2005−99367号公報

【特許文献2】特開2002−156951号公報

【特許文献3】特開2002−258401号公報

【特許文献4】特開2002−357810号公報

【特許文献5】特開2004−085961号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

そこで、本発明は、バックライト制御による画質の改善や消費電力低減の具現化に有効な手法を提供する。

【課題を解決するための手段】

【0009】

上記目的を達成するため、請求項1記載の発明は、ランプの駆動制御を行うランプ駆動制御装置において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記比較して得られた誤差成分に非線形特性を付加する手段と、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段とを具備することを特徴とする。

【0010】

また、請求項2記載の発明は、請求項1記載の発明において、前記非線形特性は、前記誤差成分が定常付近であるときの前記フィードバック制御のゲインを1としたときに、前記誤差成分が前記定常付近よりもマイナス側であるときの前記フィードバック制御のゲインを1よりも大きく設定し、前記誤差成分が前記定常付近よりもプラス側であるときの前記フィードバック制御のゲインを1よりも大きく設定することを特徴とする。

【0011】

また、請求項3記載の発明は、液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と、前記フィードバック制御手段に前記ランプに流す電流値のON/OFFを制御する信号を入力する手段と、前記ON/OFF信号の立ち上がりおよび/または立ち下がりに合わせて、前記ランプの制御量として複数種の傾斜値を適用する手段とを具備することを特徴とする。

【0012】

また、請求項4記載の発明は、請求項3記載の発明において、前記ON/OFF信号の立ち上がりおよび/または立ち下がりの直前および/または直後は、前記複数種の傾斜値のうち、緩やかな傾斜値が適用されることを特徴とする。

【0013】

また、請求項5記載の発明は、請求項3記載の発明において、前記液晶バックライトは、前記ランプを備えた複数の点灯ブロックから構成され、該各点灯ブロック内に設けられたランプに対する前記傾斜値の適用は、点灯ブロックごとに独立で行われることを特徴とする。

【0014】

また、請求項6記載の発明は、請求項3記載の発明において、前記ランプに電流が流れない低電圧範囲では、前記複数種の傾斜値のうち、急な傾斜値が選択されることを特徴とする。

【0015】

また、請求項7記載の発明は、請求項3記載の発明において、前記ON/OFF信号に基づく制御により、ランプがOFFとなった時には、該ランプに電流が流れない低電圧で前記ON/OFF信号のON状態を待機することを特徴とする。

【0016】

また、請求項8記載の発明は、請求項3記載の発明において、前記ON/OFF信号がON状態となる前に、前記ランプに電流が流れない低電圧で該ON状態を待機することを特徴とする。

【0017】

また、請求項9記載の発明は、ランプの駆動制御を行うランプ駆動制御方法において、前記ランプに流れる電流値を検出するステップと、前記検出した電流値を目標値と比較するステップと、前記比較して得られた誤差成分に非線形特性を付加するステップと、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行うステップとを具備することを特徴とする。

【0018】

また、請求項10記載の発明は、ランプの駆動制御を行うランプ駆動制御装置に組み込まれる信号処理回路において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記比較して得られた誤差成分に非線形特性を付加する手段と、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段とを具備することを特徴とする。

【0019】

また、請求項11記載の発明は、液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、前記ランプに流れる電流値を検出する手段と、前記検出した電流値を目標値と比較する手段と、前記比較して得られた誤差成分に非線形特性を付加する手段と、前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段とを具備することを特徴とする。

【0020】

請求項1、2記載の発明によれば、フィードバック制御の誤差入力に非線形特性が付加され、例えば定常許容範囲より出力電流が低い時にゲインを高く設定することにより起動の高速化を図れ、また、回路異常や感電などにより、定常許容範囲より高い電流が流れた時にもゲインを高く設定することにより危険な電流からの保護の高速化を図れると共に定常状態での精度や安定性と両立させることができる。

【0021】

請求項3記載の発明によれば、フィードバックによる閉ループ制御に対して、ランプON/OFF時に複数種の傾斜値が出力に強制的に適用されるため、ループ応答特性とは無関係に好適なソフトスタート/ストップ・シーケンス制御を行うことができる。

【0022】

請求項4記載の発明によれば、点灯開始直後および、消灯完了直前に緩やかな傾斜が適用されるため、電流量の急変化による高周波成分が抑えられ、出力トランスなどの静音化を図ることができる。

【0023】

請求項5記載の発明によれば、複数チャンネルの一括電流制御の場合においても各チャンネルのスタート/ストップ・シーケンス制御を独立に行うことができるため、多チャンネル独立ON/OFF制御構成においても小規模回路で構成することができる。

【0024】

請求項6記載の発明によれば、ランプに電流が流れない低電圧範囲では急傾斜が適用されるため、ランプの電流が流れ始めるまでの無駄時間を短縮し、点灯遅れを小さくすることができる。

【0025】

請求項7記載の発明によれば、ランプに電流が流れない低電圧で待機する構成を有するため、ランプ以外に流れる電流、例えば配線や出力トランスの浮遊容量に流れる電流も含めて急な変化を抑えることができるため、静音化とランプの点灯遅れを小さくすることの両立に有効である。

【0026】

請求項8記載の発明によれば、ランプに電流が流れない低電圧で事前待機する構成を有するため、静音化とランプの点灯遅れを小さくすることの両立に有効でありながら、待機中に浮遊容量などに流れる電流やブリッジ回路のスイッチング・ロスによる無駄な電力消費も抑えることができる。

【発明の効果】

【0027】

以上説明したように、本発明によれば、バックライト制御による画質の改善や消費電力低減が安価な構成で期待できる。

【発明を実施するための最良の形態】

【0028】

以下、本発明の実施形態を添付図面を参照して詳細に説明する。尚、本発明は、以下説明する実施形態に限らず適宜変更可能である。

【0029】

図1は、本発明の実施形態に係る液晶バックライト駆動装置の構成を示す概念図である。同図(a)に示すように、本液晶バックライト駆動装置は、液晶パネル10の背面にバックライト光源として分割配置された点灯ブロックBL1〜BL4と、これら分割配置された各点灯ブロックを制御するバックライト制御部16で構成される。

【0030】

同図(a)において、画像処理部14は、所定のフレーム周期で入力される映像信号VDに基づいて所定の画像処理を行い、その結果として、液晶パネル10を駆動する信号を液晶駆動部12に出力し、点灯ブロックBL1〜BL4を制御する信号をバックライト制御部16に出力する。

【0031】

液晶駆動部12は、画像処理部14の出力信号に基づいて、液晶パネル10を構成する液晶素子の配向を制御することで、表示映像を構成する各画素の色彩や階調を設定し、バックライト制御部16は、画像処理部14の出力信号に基づいて、点灯ブロックBL1〜BL4の光量や点灯状態を制御することで、該当する表示領域の光量やバックライトのON/OFFを制御する。

【0032】

ここで、点灯ブロックBL1〜BL4は、液晶の走査方向に沿って4つのブロックに分割され、バックライト制御部16は、液晶駆動部12が駆動する液晶領域に対応する点灯ブロックの点灯状態を制御することで、例えば、液晶の遷移タイミングを避けたバックライトの順次点灯による疑似インパルス駆動型の動画改善が行われる。

【0033】

この分割された各点灯ブロックは、同図(b)に点灯ブロックBL1を代表として例示したように、光源となるランプL1を備え、このランプは、スイッチング素子Q1〜Q4で構成されたブリッジ回路とトランスTR1により駆動される。

【0034】

ここで、ブリッジ回路は、スイッチング素子Q1およびQ4で構成される正方向電流側(iP)のスイッチング部と、スイッチング素子Q3およびQ2で構成される負方向電流側(iN)のスイッチング部とで構成され、図中の点線iPおよびiNで示すように、正方向半サイクル電流iPは、スイッチング素子Q1、トランスTR1、スイッチング素子Q4の方向に流れ、負方向半サイクル電流iNは、スイッチング素子Q3、トランスTR1、スイッチング素子Q2の方向に流れ、その結果、負荷となるランプに対して交流電流が供給される。この動作は各点灯ブロックBL1〜BL4で同様である。

【0035】

図2は、図1に示した液晶バックライト駆動装置の全体構成を示す回路ブロック図である。同図に示すように、本装置では、ブリッジ回路と点灯ブロックとを含むアナログ回路部100がバックライト制御部16によって制御される。

【0036】

点灯ブロックBL1を駆動するブリッジ回路は、制御信号S1−1で駆動されるスイッチング素子対Q1、Q2と、制御信号S1−2で駆動されるスイッチング素子対Q3、Q4とで構成される。他の点灯ブロックBL2、BL3、BL4についても同様に構成される。

【0037】

バックライト制御部16には、ブリッジ回路の制御信号S1−1、S1−2、S2−1、S2−2、S3−1、S3−2、S4−1、S4−2に対応したポートP1〜P4が設けられ、これらのポートから各スイッチング素子対を制御する信号が出力される。

【0038】

また、各点灯ブロックBL1〜BL4には、ランプL1〜L4を流れる電流を検出するための抵抗R1〜R4が設けられ、検出された電流値は、バックライト制御部16の対応ポートP1〜P4に入力される。この入力された電流値に基づいて、点灯ブロックごとに調光制御が行われる。

【0039】

図3は、図2に示したブリッジ回路の動作例を示す回路図およびタイミングチャートである。同図(a)に示すように、ブリッジ回路を構成するスイッチング素子Q1〜Q4への制御入力をA〜Dとすると、これらA〜Dの制御信号の相対関係によって負荷LOADに供給される電力量が決定される。

【0040】

即ち、同図(b)に示すように、図中「Timing」で示したキャリアタイミングに同期させた出力PWM信号に基づいて、A〜Dのスイッチング波形を生成し、制御信号AがONの期間は負荷LOADに正方向の電流が供給され、制御信号CがONの期間は負荷LOADに負方向の電流が供給される。

【0041】

負荷LOADに供給する電力量は出力PWM波形のデューティによって制御され、負荷LOADに大きな電力を供給する場合は、出力PWM波形のデューティを大きくし、負荷LOADに小さな電力を供給する場合は、出力PWM波形のデューティを小さくする。

【0042】

このような電力供給量の制御を各点灯ブロックごとに検出した電流値に基づいて、点灯ブロックごとに行うことにより、点灯ブロック間の輝度バランスを調整する制御や、映像のシーンに応じて点灯ブロックごとに輝度を変化させるシーン制御を行うことができる。

【0043】

図4は、図2に示したブリッジ回路の他の動作例を示す回路図およびタイミングチャートである。同図(a)に示すように、ブリッジ回路を構成するスイッチング素子Q1〜Q4への制御入力をA〜Dとすると、これらA〜Dの制御信号の相対関係によって負荷LOADに供給される電力量が決定される。

【0044】

即ち、同図(b)および(c)に示すように、制御信号A〜Dのスイッチングデューティを一定条件とし、制御信号AとBのON状態を相補的に切り替えるとともに、制御信号CとDのON状態を相補的に切り替え、制御信号AとDの重なりによって負荷LOADに正方向の電流が供給され、制御信号BとCの重なりによって負荷LOADに負方向の電流が供給される。

【0045】

即ち、制御信号AとBのペアに対する制御信号CとDのペアの位相を変化させることで、負荷LOADに供給する電力量を制御することができる。負荷LOADに大きな電力を供給する場合は、同図(b)に示すように、両ペアの重なりを大きくすれば良く、負荷LOADに小さな電力を供給する場合は、同図(c)に示すように、両ペアの重なりを小さくすれば良い。

【0046】

このような電力供給量の制御を点灯ブロックごとに検出した電流値に基づいて、点灯ブロックごとに行うことにより、点灯ブロック間の輝度バランスを調整する制御や、映像のシーンに応じて点灯ブロックごとに輝度を変化させるシーン制御を行うことができる。

【0047】

図5は、図1に示した液晶バックライト駆動装置の制御構成を示す回路ブロック図である。同図に示すように、アナログ回路部100に設けられた点灯ブロックBL1〜BL4には、電源回路20からの直流電源が供給され、この直流電流がブリッジ回路によりスイッチング・昇圧されて高圧交流が生成される。

【0048】

ここで、バックライト制御部16は、デジタル回路によって構成され、点灯ブロックBL1〜BL4ごとに検出抵抗を介して検出されたランプ電流は、入力ポートP1〜P4からバックライト制御部16に入力される。

【0049】

この入力されたランプ電流情報は、点灯ブロックごとに、数値化部58でA/D変換された後、比較部60によって制御目標値と比較され、その結果得られた誤差情報がループフィルタ62で積分され、この積分結果が駆動パルス生成部56により処理されて、各点灯ブロックBL1〜BL4を駆動するための駆動パルスが生成される。

【0050】

これらの駆動パルスは、出力ポートP1〜P4からドライバ22を介して各点灯ブロックBL1〜BL4に出力され、このドライバ出力に基づいてブリッジ回路によるランプの点灯制御が行われる。

【0051】

数値化部58および駆動パルス生成部56には、タイミング発生部310で生成された波形生成の基本信号となるキャリアタイミングが供給され、このキャリアタイミングを利用して、数値化部58によるA/D変換と、駆動パルス生成部56による駆動パルスの生成が行われる。

【0052】

数値化部58により数値化されたデータは、点灯ブロックごとに、ランプのインピーダンス等のパラメータを検出するパラメータ検出部52に出力され、ここで検出されたパラメータに基づいて保護回路50による保護動作と起動制御部54によるランプの起動制御が行われる。

【0053】

保護回路50による保護動作としては、電源回路20の遮断、駆動パルスのデューティ低減、起動制御の停止等が、検出されたパラメータから判断された保護すべき程度に応じて適宜行われる。

【0054】

図6は、図5に示した数値化部および比較部の構成例を示す回路ブロック図である。同図では、点灯ブロックBL1のみを示すが他の点灯ブロックについても同様に構成される。同図に示すように、点灯ブロックのランプ電流情報は、検波部220によって検波され、この結果が平滑平均化RCフィルタ230によって強平滑または弱平滑平均化され、その結果がコンパレータ240によってリファレンス三角波と比較され、その結果が検出PWM信号として出力される。

【0055】

検出PWM信号は、入力パルス幅カウント回路322によってカウントされ、その結果が減算回路324によって目標値との差異が算出されて、その結果が非線形特性付加部326によって非線形処理されて入力誤差信号が生成される。

【0056】

図7は、検出PWM信号を生成する第1の例を示す回路ブロック図である。同図に示す例は、検出抵抗R1を介して検出したランプ電流を全波整流、強平滑平均化し、リファレンス三角波と比較することで検出PWM信号を生成する場合の例である。

【0057】

ここで、検波部220は、全波整流回路222とクリップ回路224によって構成され、このクリップ回路によって整流後の波形のゼロ値付近がクリップ整形される。

【0058】

平滑平均化RCフィルタ230は、強平滑平均化特性、即ち、長放電時定数を持たせたRC充放電回路によって構成され、リファレンス三角波生成部250は、リファレンスとなるパルス信号を平滑するRC回路によって構成され、このRC回路にキャリアタイミングや電流オフセットPWM信号等のリファレンスパルスが入力されることで、キャリアに同期した三角波が生成される。

【0059】

上記平滑平均化信号とリファレンス三角波がコンパレータ240により比較されて、ランプ電流情報がパルス信号として表現された検出PWM信号が生成される。

【0060】

尚、コンパレータ240に入力するリファレンス信号を変化させることにより、目標電流を可変とする構成としてもよい。例えば、同図のリファレンス三角波生成部250に入力するリファレンスパルスとしてキャリアタイミングを使用する場合には、該キャリアタイミングのデューティを変化させて目標電流を可変としてもよく、また、リファレンスパルスに別途電流オフセットPWMを供給して長時定数平滑フィルタ252によるDCを加算したり、リファレンスパルス自身を高速1ビット変調オフセット付き三角波、高速パルス密度変調PDM等を使用して所定のオフセットと波形を持ったリファレンス三角波を発生させて目標電流を可変としてもよく、また、図6内の入力パルス幅カウンタ322の初期ロード値を変化させたり、また図6内の減算回路324に供給する目標値を変化させて目標電流を可変としても良い。

【0061】

図8は、検出PWM信号を生成する第1の例に係るA/D変換動作を示す波形タイミングチャートである。同図(a)に示すように、検出抵抗で検出されたランプ電流は、実線で示した交流波形となり、この波形が全波整流されて同図(b)に示す整流波形となる。

【0062】

その後、同図(c)に示すように、整流後の波形のゼロ付近がクリップされて、その波形(薄い実線)が強平滑平均化されて振幅の小さな擬似三角波(濃い実線)が生成される。

【0063】

一方、同図(e)に示すように、キャリアタイミングに同期したリファレンス三角波(濃い実線)が強平滑平均化波形(薄い実線)と比較されて同図(f)に示したPWMパルス波形が生成される。

【0064】

図9は、検出PWM信号を生成する第2の例を示す回路ブロック図である。同図に示すように、トランスTR1が2出力型のツイントランスで構成され、一つのトランスに2本のランプL1−1、L1−2が接続される場合には、抵抗R1−1、R1−2で検出される波形の極性が反転することを利用して、半波整流回路221を用いた疑似全波整流を行う構成としても良い。

【0065】

ここで、検波部220は、半波整流回路222とクリップ回路224によって構成され、このクリップ回路によって整流後の波形のゼロ値付近がクリップ整形される。

【0066】

平滑平均化RCフィルタ230は、弱平滑平均化特性、即ち、短放電時定数を持たせたRC充放電回路によって構成され、リファレンス三角波生成部250は、リファレンスとなるパルス信号を平滑するRC回路によって構成され、このRC回路にリファレンスパルスが入力されることで、キャリアに同期した三角波が生成される。

【0067】

上記平滑平均化信号とリファレンス三角波がコンパレータ240により比較されて、ランプ電流情報がパルス信号として表現された検出PWM信号が生成される。

【0068】

図10は、検出PWM信号を生成する第2の例に係るA/D変換動作を示す波形タイミングチャートである。同図(a)に示すように、ランプ電流は実線と点線で示した極性の異なる電流が検出され、これらが半波整流されダイオードORにより合成されて同図(b)に示す整流波形となる。

【0069】

その後、同図(c)に示すように、整流後の波形のゼロ付近がクリップされて、その波形(薄い実線)が弱平滑平均化されて振幅の小さな擬似三角波(濃い実線)が生成される。

【0070】

一方、同図(e)に示すように、キャリアタイミングに同期したリファレンス三角波(濃い実線)が弱平滑平均化波形(薄い実線)と比較されて同図(f)に示した検出PWM波形が生成される。

【0071】

図11は、検出PWM信号を生成する第3の例を示す回路ブロック図である。同図に示す例は、コンパレータ240のリファレンスとして一定値を用いた場合の例であり、その他は前述の第2の例と同じである。

【0072】

図12は、検出PWM信号を生成する第3の例に係るA/D変換動作を示す波形タイミングチャートである。この例の場合は、同図(e)に示すように、一定値のリファレンス(濃い実線)が弱平滑平均化波形(薄い実線)と比較されて同図(f)に示したPWMパルス波形が生成される。その他は前述の第2の例と同じである。

【0073】

図13は、検出PWM信号を生成する第4の例を示す回路ブロック図である。同図に示す例は、同図に示す例は、検出抵抗R1を介して検出したランプ電流を全波整流、弱平滑平均化し、一定のリファレンスと比較することで検出PWM信号を生成する例であり、その他は前述の第1の例と同じである。

【0074】

図14は、検出PWM信号を生成する第4の例に係るA/D変換動作を示す波形タイミングチャートである。この例の場合は、同図(d)〜(f)に示すように、弱平滑平均化信号と一定のリファレンス値が比較されて検出PWM信号が生成される。その他は前述の第1の例と同じである。

【0075】

図15は、検出PWM信号を生成する第5の例を示す回路ブロック図である。同図に示す例は、リファレンス三角波生成フィルタ250に倍周波リファレンスパルスを供給して倍周波三角波を生成した例であり、その他は前述の第4の例と同じである。

【0076】

図16は、検出PWM信号を生成する第5の例に係るA/D変換動作を示す波形タイミングチャートである。この例の場合は、同図(e)に示すように、倍周波三角波リファレンス(濃い実線)が弱平滑平均化波形(薄い実線)と比較されて同図(f)に示したPWMパルス波形が生成される。その他は前述の第4の例と同じである。

【0077】

図17は、検出PWM信号を生成する第6の例を示す回路ブロック図である。この例は、同図(a)に示すように、図15の倍周波三角波生成部251にエッジ強調波形を適合させた場合の例である。この場合は、同図(b)に示すように、弱平滑平均化波形が実際は丸みを持っている部分をエッジ強調波形が適用された尖頭形状の三角波で吸収することができる。その他は前述の第5の例と同じである。

【0078】

図18は、検出PWM信号を生成せずに直に電流波形を高速AD変換してから平均電流値を得る場合の第6の例を示す回路ブロック図である。この例の場合は、同図に示すように、キャリアの8倍周波数の高速サンプリングクロックで電流波形を電圧化後そのままA/Dコンバータ360によりAD変換する。

【0079】

そして、波形の半サイクル毎の中ほど3サンプルをフリップフロップ362−1、362−2で取得し、加算器363によりデジタル加算した結果を絶対値演算回路364により絶対値化し、その後、平均値演算フリップフロップ366により、再度キャリアの2倍周波数、つまり、半サイクル毎の演算サンプリングクロックで再サンプリングして、半サイクル毎のゼロクロス近辺以外の数値化平均電流値を得る。以降、図5の比較回路60に入力され前述と同様の処理がなされる。

【0080】

図19は、図18に示した回路ブロックの処理のタイミングを示すタイミングチャートである。同図(a)および(b)に示すように、この例のA/Dコンバータでは、電流キャリア周波数の半サイクルに4回サンプリングされるが、同図(c)に示すように、その連続する3サンプル出力の合計値を半サイクルに1回、つまり4サンプルに1回の演算クロックで再サンプルして、同図(d)に示すように、1サイクル内の波形の同図(a)中のa〜iの内、ゼロクロス近辺のeとiを除いた「b+c+d」および「f+g+h」の平均値出力を得る。

【0081】

図20は、図6に示した非線形特性付加回路326で負荷する非線形特性の例を示す概念図である。同図に示すように、縦軸に示す誤差出力の値に応じて横軸に示すPWMデューティが決定される。ここで同図中「x2」で示す実線領域は、定常付近に達するまでは2倍ゲインにして速く立ち上げるための特性であり、同図中「x1」で示す実線領域のうちマイナス誤差定常範囲は、定常値近傍で定常ゲインに切り換えるための特性であり、同図中「x1」で示す実線領域のうちプラス誤差定常範囲は、一気に定常範囲を飛び越えて下がらないよう大きめに確保される特性であり、同図中「x8」で示す実線領域は、感電などの場合の危険な過電流は8倍ゲインにして急速に押さえるための特性である。

【0082】

図21は、図5に示したループフィルタの構成を示す回路ブロック図である。同図では、点灯ブロックBL1のみを示すが他の点灯ブロックについても同様に構成される。同図に示すように、ループフィルタ62は、加算回路332と、出力クリップ回路334と、フリップフロップ336によって構成され、このループフィルタによって非線形処理された入力誤差信号の積分処理が行われ、閉ループ制御信号が生成される。

【0083】

図22は、1ブロック共通単一電流制御でブロックごとに独立にソフトスタート/ストップ制御を行う場合の構成例を示す回路ブロック図である。

【0084】

図23は、図22に示した入力誤差生成部342の構成を示す回路ブロック図である。同図に示すように、各ブロックランプ電流の最大値選択兼全波整流回路を通って1本化された整流後電流波形は弱平滑された後コンパレータで検出PWM化される。検出PWMはパルス幅カウンタで数値化された後、目標値から減算され、非線形特性付加後、入力誤差信号として出力される。これらの構成および動作は図6と同様に行われる。

【0085】

上記のようにして生成された入力誤差信号は、図22に示したループフィルタ62によって積分され、定常時の閉ループによる制御信号が生成される。

【0086】

そして、この定常制御信号が駆動パルス生成部56内に点灯ブロックごとに設けられたソフト波形生成部350−1〜350−4に出力され、各ソフト波形生成部によってソフトスタート/ストップ波形が生成された後、出力振幅信号としてパルス変換部370−1〜370−4に出力される。このとき、ソフト波形生成部350−1〜350−4によって、定常状態への達成状況を示す定常達成信号がNOR回路344に出力され、非定常信号としてループフィルタ62に出力される。

【0087】

各点灯ブロックの出力振幅信号は、バルス変換部370−1〜370−4によって、振幅信号がパルス信号に変換され、各点灯ブロックの駆動PWM信号として、図5に示すバックライト制御部16の出力ポートP1〜P4からドライバ22を介して各点灯ブロックBL1〜BL4に出力される。

【0088】

図24は、図22に示したループフィルタの構成を示す回路ブロック図である。同図に示すように、ループフィルタ62は、加算回路332と、出力クリップ回路334と、フリップフロップ336と、AND回路338によって構成され、このループフィルタによって入力誤差信号の積分処理が行われる。

【0089】

AND回路338がフリップフロップ336に出力する信号は、非定常時の開ループ化による出力上昇を防止するためのホールド信号として出力され、出力クリップ回路346がAND回路348に出力する信号は、正の場合に定常制御値の上昇方向を示す。尚、このAND回路は必ずしも必要ではなく非定常時無条件でフリップフロップ336をホールドするようにしてもよい。

【0090】

図25は、図22に示したソフトスタート/ストップ波形生成部の構成を示す概念図である。同図では、点灯ブロックBL1のみを示すが他の点灯ブロックについても同様に構成される。同図に示すように、点灯ブロックごとに生成されたループフィルタ出力信号は、比較回路354および355、選択回路356に出力され、定常達成状態に応じて選択処理することでPWMデューティを示す出力振幅信号が生成される。

【0091】

ここで、比較回路354が出力するゼロ近傍または 定常値近傍を示す信号に基づいて、複数の傾斜値が傾斜値選択回路351によって選択され、この傾斜値が極性選択回路352によって点灯ブロックのON/OFF信号に基づく極性が適用され、その結果が加算回路353によって積分ループに加算され、強制カーブの生成が行われる。

【0092】

図26は、ソフトスタート/ストップ波形の例を示すタイミングチャートである。同図(a)は、点灯ブロックBL1のON/OFF信号を示し、同図(b)は、図25の傾斜値選択部351によって選択された出力振幅の電圧波形を示し、同図(c)は、ゼロ値近傍の傾斜部および定常値近傍の傾斜部に対応したタイミングを示し、同図(d)は点灯ブロックBL1が定常に達したタイミングを示し、同図(e)は、点灯ブロックBL2のON/OFF信号を示し、同図(f)は、図25の傾斜値選択部351によって選択された出力振幅の電圧波形を示し、同図(g)は、点灯ブロックBL1またはBL2が定常状態に達成するタイミングを示す。

【0093】

同図に示す制御の特徴としては、まず、閉ループのままスタート/ストップ時の出力のスルーレートを強制的に制限し、常時制御し続けたまま強制的に上昇および下降カーブを作ることで、ON/OFFをスムーズに切換える手法がある。

【0094】

この手法では、図5に示した制御構成、即ち、定常時の目標電流に対して誤差を検出し、この誤差成分をループフィルタを介して出力の自動制御を行う構成において、別途、図22に示した各点灯ブロックのON/OFF制御入力に合わせて、図26(b)に折れ線傾斜で図示したような、ON時上昇、OFF時下降の出力制御用強制カーブを生成する。この強制カーブの生成は、図25に示した傾斜値選択部351、極性選択部352、加算回路353により行われる。

【0095】

ここで、図25に示した比較回路354により、生成された強制カーブが上昇時に図26(b)の「閉ループ定常値」で示した自動制御値を超えようとした時には、図25の選択回路356により自動制御側の出力(同図中「閉ループによる定常制御信号」)を選択出力すると共に、その値を次の瞬間の強制カーブ出力用の現在値としても使用する。

【0096】

また、強制カーブで下降しようとする時は、その自動制御値から強制的に下降させて行き、自動制御値より小さい範囲では強制カーブ出力を選択出力する。下降してゼロその他所定の値以下になった時、その所定の値にクリップしその値を出力する。

【0097】

強制カーブが選択出力されている間は、自動制御値がオープンループとなって過上昇しないように、自動制御出力をホールドさせる。これにより自動制御と開始終了時の強制傾斜カーブとの高精度で連続的な移行が可能となり、静音化が図られる。

【0098】

上記に加え、スタート/ストップ直後やスタート/ストップ完了直前に傾斜を緩やかにしてより静音化を進める方法も有効である。例えば、強制カーブが自動制御値近傍にいる時や下限近傍にいる時には、より緩やかな傾斜値を選択することにより、上昇、下降のカーブを緩やかに構成してもよい。これにより定常値や下限値との切換えが滑らかになり、また電流量変化の高周波成分も抑えられ、さらに静音化される。

【0099】

また、スタートストップ時の強制カーブによる制御は、各点灯ブロック独立の多チャンネル制御で行うことにより、小規模な回路で独立に任意のタイミングでのON/OFF制御が可能になる。

【0100】

例えば、図22に示すように、各点灯ブロックそれぞれの定常電流値を共通の定常自動制御回路で制御し、スタート/ストップにより各点灯ブロックごと独立にON/OFFおよび出力の上昇および下降傾斜を付ける時、共通制御対象のどれか1チャンネルでも定常制御出力が選択されている時は、ホールドせず制御ループを有効にして、全てのチャンネルが定常制御出力選択状態から脱した時、定常制御をホールド状態にする。これにより各チャンネルの状態に依らず1組の定常自動制御回路で、安価に自動制御と独立スタート/ストップ傾斜カーブ生成が可能となる。

【0101】

図27は、ソフトスタート/ストップ波形の他の例を示すタイミングチャートである。同図(a)は、点灯ブロックBL1のON/OFF信号を示し、同図(b)〜(d)は、このON/OFF信号に対するソフトスタート/ストップの制御例を示す。

【0102】

同図(b)は、スタート/ストップ時に、ランプに電流が流れない低電圧出力範囲は、急傾斜で電圧の出力の上昇および下降を行い特に点灯時間までの時間を短縮する例であり、同図に示したゼロ点から放電開始電圧より少し下の切替閾値電圧までの間の傾斜が該当する部分である。

【0103】

同図(c)は、消灯時にはランプに電流が流れない範囲の低電圧でスタンバイしておき、スタート時の点灯開始までの時間短縮と静音化を図る例である。

【0104】

同図(d)は、同図(e)に示すような、ON/OFF信号より少し先行したスタンバイ開始信号により、ランプに電流が流れない範囲のスタンバイ電圧に事前待機し、スタート時の時間短縮と静音化を図りながらも、待機中に浮遊容量などに流れる電流やブリッジ回路のスイッチング・ロスによる、消灯時には不必要な消費電力の削減を図る例である。

【産業上の利用可能性】

【0105】

本発明によれば、より高度なバックライト制御が可能になるため、高画質化や消費電力の低減が要求される大型液晶ディスプレイへの適用が期待される。

【図面の簡単な説明】

【0106】

【図1】本発明の実施形態に係る液晶バックライト駆動装置の構成を示す概念図である。

【図2】図1に示した液晶バックライト駆動装置の全体構成を示す回路ブロック図である。

【図3】図2に示したブリッジ回路の動作例を示す回路図およびタイミングチャートである。

【図4】図2に示したブリッジ回路の他の動作例を示す回路図およびタイミングチャートである。

【図5】図1に示した液晶バックライト駆動装置の制御構成を示す回路ブロック図である。

【図6】図5に示した数値化部および比較部の構成例を示す回路ブロック図である。

【図7】検出PWM信号を生成する第1の例を示す回路ブロック図である。

【図8】検出PWM信号を生成する第1の例に係るA/D変換動作を示す波形タイミングチャートである。

【図9】検出PWM信号を生成する第2の例を示す回路ブロック図である。

【図10】検出PWM信号を生成する第2の例に係るA/D変換動作を示す波形タイミングチャートである。

【図11】検出PWM信号を生成する第3の例を示す回路ブロック図である。

【図12】検出PWM信号を生成する第3の例に係るA/D変換動作を示す波形タイミングチャートである。

【図13】検出PWM信号を生成する第4の例を示す回路ブロック図である。

【図14】検出PWM信号を生成する第4の例に係るA/D変換動作を示す波形タイミングチャートである。

【図15】検出PWM信号を生成する第5の例を示す回路ブロック図である。

【図16】検出PWM信号を生成する第5の例に係るA/D変換動作を示す波形タイミングチャートである。

【図17】検出PWM信号を生成する第6の例を示す回路ブロック図である。

【図18】検出PWM信号を生成せずに直に電流波形を高速AD変換してから平均電流値を得る場合の第6の例を示す回路ブロック図である。

【図19】図18に示した回路ブロックの処理のタイミングを示すタイミングチャートである。

【図20】図6に示した非線形特性付加回路326で負荷する非線形特性の例を示す概念図である。

【図21】図5に示したループフィルタの構成を示す回路ブロック図である。

【図22】1ブロック共通単一電流制御でブロックごとに独立にソフトスタート/ストップ制御を行う場合の構成例を示す回路ブロック図である。

【図23】図22に示した入力誤差生成部342の構成を示す回路ブロック図である。

【図24】図22に示したループフィルタの構成を示す回路ブロック図である。

【図25】図22に示したソフトスタート/ストップ波形生成部の構成を示す概念図である。

【図26】ソフトスタート/ストップ波形の例を示すタイミングチャートである。

【図27】ソフトスタート/ストップ波形の他の例を示すタイミングチャートである。

【符号の説明】

【0107】

10…液晶パネル、12…液晶駆動部、14…画像処理部、16…バックライト制御部、20…電源回路、22…ドライバ、50…保護回路、52…パラメータ検出部、54…起動制御部、56…駆動パルス生成部、58…数値化部、60…比較部、62…ループフィルタ、70…タイミング発生部、100…アナログ回路部、220…検波部、221…半波整流回路、222…全波整流回路、224…クリップ回路、230…平滑平均化RCフィルタ、240…コンパレータ、250…リファレンス三角波生成フィルタ、300…デジタル回路部、320…入力カウンタ、322…入力パルス幅カウント部、324…減算部、326…非線形特性付加部、330…ループフィルタ、332…加算部、334…出力クリップ部、336…フリップフロップ、340…最大値選択回路、344…NOR回路、348…AND回路、350…ソフト波形生成部、351…傾斜値選択部、352…極性選択部、353…加算回路、354…比較回路、355…比較回路、356…選択回路、357…レジスタ回路、360…A/Dコンバータ、362…フリップフロップ、363…加算器、364…絶対値演算回路、366…平均値演算フリップフロップ、370…バルス変換部

【特許請求の範囲】

【請求項1】

ランプの駆動制御を行うランプ駆動制御装置において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記比較して得られた誤差成分に非線形特性を付加する手段と、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と

を具備することを特徴とするランプ駆動制御装置。

【請求項2】

前記非線形特性は、前記誤差成分が定常付近であるときの前記フィードバック制御のゲインを1としたときに、前記誤差成分が前記定常付近よりもマイナス側であるときの前記フィードバック制御のゲインを1よりも大きく設定し、前記誤差成分が前記定常付近よりもプラス側であるときの前記フィードバック制御のゲインを1よりも大きく設定することを特徴とする請求項1記載の液晶バックライト制御装置。

【請求項3】

液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と、

前記フィードバック制御手段に前記ランプに流す電流値のON/OFFを制御する信号を入力する手段と、

前記ON/OFF信号の立ち上がりおよび/または立ち下がりに合わせて、前記ランプの制御量として複数種の傾斜値を適用する手段と

を具備することを特徴とする液晶バックライト制御装置。

【請求項4】

前記ON/OFF信号の立ち上がりおよび/または立ち下がりの直前および/または直後は、前記複数種の傾斜値のうち、緩やかな傾斜値が適用されることを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項5】

前記液晶バックライトは、前記ランプを備えた複数の点灯ブロックから構成され、該各点灯ブロック内に設けられたランプに対する前記傾斜値の適用は、点灯ブロックごとに独立で行われることを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項6】

前記ランプに電流が流れない低電圧範囲では、前記複数種の傾斜値のうち、急な傾斜値が選択されることを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項7】

前記ON/OFF信号に基づく制御により、ランプがOFFとなった時には、該ランプに電流が流れない低電圧で前記ON/OFF信号のON状態を待機することを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項8】

前記ON/OFF信号がON状態となる前に、前記ランプに電流が流れない低電圧で該ON状態を待機することを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項9】

ランプの駆動制御を行うランプ駆動制御方法において、

前記ランプに流れる電流値を検出するステップと、

前記検出した電流値を目標値と比較するステップと、

前記比較して得られた誤差成分に非線形特性を付加するステップと、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行うステップと

を具備することを特徴とするランプ駆動制御方法。

【請求項10】

ランプの駆動制御を行うランプ駆動制御装置に組み込まれる信号処理回路において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記比較して得られた誤差成分に非線形特性を付加する手段と、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と

を具備することを特徴とする信号処理回路。

【請求項11】

液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記比較して得られた誤差成分に非線形特性を付加する手段と、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と

を具備することを特徴とする液晶バックライト制御装置。

【請求項1】

ランプの駆動制御を行うランプ駆動制御装置において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記比較して得られた誤差成分に非線形特性を付加する手段と、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と

を具備することを特徴とするランプ駆動制御装置。

【請求項2】

前記非線形特性は、前記誤差成分が定常付近であるときの前記フィードバック制御のゲインを1としたときに、前記誤差成分が前記定常付近よりもマイナス側であるときの前記フィードバック制御のゲインを1よりも大きく設定し、前記誤差成分が前記定常付近よりもプラス側であるときの前記フィードバック制御のゲインを1よりも大きく設定することを特徴とする請求項1記載の液晶バックライト制御装置。

【請求項3】

液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と、

前記フィードバック制御手段に前記ランプに流す電流値のON/OFFを制御する信号を入力する手段と、

前記ON/OFF信号の立ち上がりおよび/または立ち下がりに合わせて、前記ランプの制御量として複数種の傾斜値を適用する手段と

を具備することを特徴とする液晶バックライト制御装置。

【請求項4】

前記ON/OFF信号の立ち上がりおよび/または立ち下がりの直前および/または直後は、前記複数種の傾斜値のうち、緩やかな傾斜値が適用されることを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項5】

前記液晶バックライトは、前記ランプを備えた複数の点灯ブロックから構成され、該各点灯ブロック内に設けられたランプに対する前記傾斜値の適用は、点灯ブロックごとに独立で行われることを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項6】

前記ランプに電流が流れない低電圧範囲では、前記複数種の傾斜値のうち、急な傾斜値が選択されることを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項7】

前記ON/OFF信号に基づく制御により、ランプがOFFとなった時には、該ランプに電流が流れない低電圧で前記ON/OFF信号のON状態を待機することを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項8】

前記ON/OFF信号がON状態となる前に、前記ランプに電流が流れない低電圧で該ON状態を待機することを特徴とする請求項3記載の液晶バックライト制御装置。

【請求項9】

ランプの駆動制御を行うランプ駆動制御方法において、

前記ランプに流れる電流値を検出するステップと、

前記検出した電流値を目標値と比較するステップと、

前記比較して得られた誤差成分に非線形特性を付加するステップと、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行うステップと

を具備することを特徴とするランプ駆動制御方法。

【請求項10】

ランプの駆動制御を行うランプ駆動制御装置に組み込まれる信号処理回路において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記比較して得られた誤差成分に非線形特性を付加する手段と、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と

を具備することを特徴とする信号処理回路。

【請求項11】

液晶バックライトに設けられたランプの制御を行う液晶バックライト制御装置において、

前記ランプに流れる電流値を検出する手段と、

前記検出した電流値を目標値と比較する手段と、

前記比較して得られた誤差成分に非線形特性を付加する手段と、

前記非線形特性が付加された誤差成分に基づいて前記ランプに流す電流値のフィードバック制御を行う手段と

を具備することを特徴とする液晶バックライト制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【公開番号】特開2008−192492(P2008−192492A)

【公開日】平成20年8月21日(2008.8.21)

【国際特許分類】

【出願番号】特願2007−26709(P2007−26709)

【出願日】平成19年2月6日(2007.2.6)

【出願人】(000204284)太陽誘電株式会社 (964)

【出願人】(399091511)マイクロスペース株式会社 (15)

【公開日】平成20年8月21日(2008.8.21)

【国際特許分類】

【出願日】平成19年2月6日(2007.2.6)

【出願人】(000204284)太陽誘電株式会社 (964)

【出願人】(399091511)マイクロスペース株式会社 (15)

[ Back to top ]