リセスチャネル構造を有するセルトランジスタを含む半導体装置およびその製造方法

【課題】動作電圧の変動が少なく、正常に動作する半導体装置を提供すること。

【解決手段】表面チャネル型nMOSFET構造を備えたトランジスタ構造および表面チ

ャネル型pMOSFET構造を有備えたトランジスタ構造を有するデュアルゲート型周辺

トランジスタと、リセスチャネル構造を備えたnMOSFET構造を有するセルトランジ

スタと、を含む半導体装置であって、前記セルトランジスタ中のゲート電極を構成するN

型ポリシリコン層に含まれるN型不純物の濃度が、略一定である半導体装置。

【解決手段】表面チャネル型nMOSFET構造を備えたトランジスタ構造および表面チ

ャネル型pMOSFET構造を有備えたトランジスタ構造を有するデュアルゲート型周辺

トランジスタと、リセスチャネル構造を備えたnMOSFET構造を有するセルトランジ

スタと、を含む半導体装置であって、前記セルトランジスタ中のゲート電極を構成するN

型ポリシリコン層に含まれるN型不純物の濃度が、略一定である半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、リセス(溝)チャネル構造を有するセルトランジスタを含む半導体装置およ

びその製造方法に関し、

さらに詳しくは、リセスチャネル構造を有するセルトランジスタ、N型ポリシリコンを

含むゲート電極を備えたnMOSFET構造を有する周辺トランジスタ、およびP型ポリ

シリコンを含むゲート電極を備えたpMOSFET構造を有する周辺トランジスタを有す

る半導体装置およびその製造方法に関する。

【背景技術】

【0002】

図1に従来の半導体装置の模式的要部断面図を示す。

図1には、N型ポリシリコン層600を含むゲート電極6aがP型の半導体シリコン基

板1上に形成されたnMOSFET構造を有するトランジスタ200と、P型ポリシリコ

ン層601を含むゲート電極6bがNウエル領域360上に形成されたpMOSFET構

造を有するトランジスタ201を備えた半導体装置100が示されている。

【0003】

前記トランジスタ200は、ゲート絶縁膜5を介して半導体シリコン基板1上に形成さ

れたゲート電極6aと、前記ゲート電極6aに対応する一対のソース・ドレイン領域3を

有するものである。

前記ゲート電極6aは、N型ポリシリコン層600と金属シリサイド7とからなるもの

である。前記ゲート電極6aの上部と側壁には、それぞれ窒化シリコンからなる絶縁膜8

および9が設けられている。

【0004】

また前記トランジスタ201は、前記トランジスタ200と同様に、前記ゲート絶縁膜

5を介して前記半導体シリコン基板1中のNウエル領域360上に形成されたゲート電極

6bと、前記ゲート電極6bに対応する一対のソース・ドレイン領域4を有するものであ

る。

前記ゲート電極6bは、P型ポリシリコン層601と金属シリサイド7とからなるもの

である。前記ゲート電極6bの上部と側壁には、それぞれ窒化シリコンからなる絶縁膜8

および9が設けられている。

【0005】

さらに、前記トランジスタ200と前記トランジスタ201とは、素子間分離構造2に

より分離されている。

これらのトランジスタの組合せは相補型MOS(Complementary MOS、以下、「CMO

S」という。)構造と一般に呼ばれるものである。

【0006】

図1の前記トランジスタ200に対応するソース・ドレイン領域3はN型の不純物を含

み、また、前記トランジスタ201に対応するソース・ドレイン領域4はP型の不純物を

含む。

この様に、前記ゲート電極に含まれる不純物の導電型と、前記ソース・ドレイン領域に

含まれる不純物の導電型が一致するトランジスタは表面チャネル型トランジスタと呼ばれ

ている。

図1に示される前記CMOS構造を備えた半導体装置100は、前記トランジスタ20

0および201のそれぞれが表面チャネル型トランジスタから構成されている(特許文献

1)。

【0007】

一方、図2に他の従来の半導体装置の模式的要部断面図を示す。

図2には、P型ポリシリコン層を含むゲート電極611がN型エピタキシャル層1b上

に形成されたpMOSFET構造を有するトランジスタ202と、P型ポリシリコン層を

含むゲート電極612がPウエル領域340の上に形成されたnMOSFET構造を有す

るトランジスタ203と、リセスチャネル構造を有するP型ポリシリコン層610を含む

ゲート電極がPウエル領域340に形成されたpMOSFET構造を有するトランジスタ

204とを備えた半導体装置101が示されている。

【0008】

前記トランジスタ202に対応するソース・ドレイン領域301は、半導体シリコン基

板1a上に設けられたN型エピタキシャル層1bの表面領域のP型高濃度不純物層により

形成されている。

さらに前記ソース・ドレイン領域301に重ねて、P型低濃度不純物層310が設けら

れている。

【0009】

また前記トランジスタ203に対応するソース・ドレイン領域302は、前記Pウエル

領域340の表面領域のN型高濃度不純物層により形成されている。

さらに前記ソース・ドレイン領域302に重ねて、N型低濃度不純物層320が設けら

れている。

【0010】

前記トランジスタ204はリセスチャネル構造を有するものであるが、かかるトランジ

スタ204に対応するソース・ドレイン領域303は、N型ボディ領域341の表面領域

に設けられたP型高濃度不純物層により形成されている。

さらに前記ソース・ドレイン領域303に重ねて、P型低濃度不純物層330が設けら

れている。

前記N型ボディ領域341は前記Pウエル領域340内部に形成されていて、前記Pウ

エル領域340の下部にはP型埋め込み層370が設けられている。

【0011】

さらに前記リセスチャネル構造は、絶縁膜9、P型ポリシリコン層610、導電層70

0により充填されており、さらに前記導電層700の上部および側面には窒化シリコンか

らなる絶縁膜800および9が設けられている。

加えて、前記トランジスタ202、前記トランジスタ203および前記トランジスタ2

04は、それぞれ素子間分離構造2により分離されている。

【0012】

上記に説明した通り、前記トランジスタ202は、前記ゲート電極611がP型ポリシ

リコン層を含み、前記pMOSFET構造に対応するソース・ドレイン領域301がP型

の不純物を含むことから、表面チャネル型トランジスタである。

この一方、前記トランジスタ203は、前記ゲート電極612がP型ポリシリコン層を

含み、nMOSFET構造に対応するPウエルがP型不純物を含むことから、このタイプ

のトランジスタは、埋め込みチャネル型トランジスタと一般に呼ばれる。

この様に、表面チャネル型トランジスタ、埋め込みチャネル型トランジスタおよびリセ

スチャネル構造を有するトランジスタを備えた半導体装置101が知られている(特許文

献2)。

【特許文献1】特開平11−307729号公報

【特許文献2】特開2002−359294号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

しかしながら、上記の知見を新たにDRAM(Dynamic Random Access Memory)等の半

導体装置に適用しようとすると不具合が生じた。

【0014】

すなわち、表面チャネル型トランジスタのnMOSFET構造を有するトランジスタ構

造および表面チャネル型トランジスタのpMOSFET構造を有するトランジスタ構造を

有するデュアルゲート型周辺トランジスタと、リセスチャネル構造を備えたnMOSFE

T構造を有するセルトランジスタとを単に組み合わせただけでは、得られた半導体装置の

動作電圧の変動が大きい等、前記半導体装置が正常に動作しないという問題があった。

【0015】

本発明の目的は、表面チャネル型nMOSFET構造を備えたトランジスタ構造および

表面チャネル型pMOSFET構造を有備えたトランジスタ構造を有するデュアルゲート

型周辺トランジスタと、リセスチャネル構造を備えたnMOSFET構造を有するセルト

ランジスタと、を含む半導体装置であって、

動作電圧の変動が少なく、正常に動作する半導体装置を提供することにある。

【課題を解決するための手段】

【0016】

本発明者は、上記課題を解決すべく鋭意検討した結果、前記半導体装置の中でも、前記

セルトランジスタ中のゲート電極を構成するN型ポリシリコン層に含まれるN型不純物の

濃度が、略一定である半導体装置が上記課題を解決することを見出し、本発明を完成する

に至った。

すなわち本発明は、

【0017】

[1]半導体シリコン基板と、

前記半導体シリコン基板の所定の位置に設けられた素子間分離構造と、

前記素子間分離構造により区画された前記半導体シリコン基板の第一の領域に設けられ

たリセスチャネル構造を有するセルトランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第二の領域に設けられ

たnMOSFET構造を有する周辺トランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第三の領域に設けられ

たpMOSFET構造を有する周辺トランジスタと、

を備えた半導体装置であって、

(A)前記リセスチャネル構造を有するセルトランジスタは、下記(1)〜(4)を有し

、

(1)前記半導体シリコン基板の所定の位置に設けられたリセス

(2)前記リセス内部に接して設けられたゲート絶縁膜

(3)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

を含むゲート電極

(4)前記半導体シリコン基板の表面領域であって前記ゲート電極の両側に設けられた一

対のN型拡散層を含むソース・ドレイン領域

(B)前記第二の領域に設けられたnMOSFET構造を有する周辺トランジスタは、下

記(5)〜(7)を有し、

(5)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(6)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極

(7)前記半導体シリコン基板の表面領域であって、前記ゲート電極の両側に設けられた

一対のN型拡散層を含むソース・ドレイン領域

(C)前記第三の領域に設けられたpMOSFET構造を有する周辺トランジスタは、下

記(8)〜(10)を有し、

(8)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(9)前記ゲート絶縁膜に接して設けられたP型ポリシリコン層および前記P型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極、

(10)前記シリコン基板内部に設けられたNウエルの表面領域であって、前記ゲート電

極の両側に設けられた一対のP型拡散層を含むソース・ドレイン領域

かつ、上記に加えて前記セルトランジスタ中のN型ポリシリコン層に含まれるN型不純

物の濃度は、略一定であることを特徴とする半導体装置を提供するものであり、

【0018】

[2]前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられ、かつ前記リセス内部および前記リ

セス上部に設けられた導電層、

からなることを特徴とする上記[1]に記載の半導体装置を提供するものであり、

【0019】

[3]前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

前記N型ポリシリコン層内部に設けられた、不純物濃度が1.0×1020/cm3未

満の第二のポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする上記[1]に記載の半導体装置を提供するものであり、

【0020】

[4]前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して、前記リセス内部全てに設けられた前記N型ポリシリコン層

、

および前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする上記[1]に記載の半導体装置を提供するものであり、

【0021】

[5]前記リセスチャネル構造を有するセルトランジスタ中のN型ポリシリコン層に含ま

れるN型不純物の濃度は、1.0×1020〜1.0×1021/cm3の範囲であるこ

とを特徴とする上記[1]〜[4]のいずれかに記載の半導体装置を提供するものであり

、

【0022】

[6](1)半導体シリコン基板の所定の領域に素子間分離構造を形成し、前記半導体シ

リコン基板に前記素子間分離構造により区画された第一ないし第三の領域を形成する工程

と、

(2)前記素子間分離構造により区画された前記半導体シリコン基板の前記第一の領域に

リセスを形成する工程と、

(3)前記素子間分離構造により区画された前記半導体シリコン基板の前記第三の位置に

Nウエルを形成する工程と、

(4)前記半導体シリコン基板上面および前記リセス内部表面にゲート絶縁膜を形成する

工程と、

(5)前記ゲート絶縁膜のうち、前記半導体シリコン基板上面に該当する部分および前記

リセス内部表面に該当する部分の上面ならびに前記素子間分離構造上面に、不純物濃度が

1.0×1020/cm3未満のポリシリコン層を形成する工程と、

(6)前記第一および第二のそれぞれの所定の位置にある前記不純物濃度が1.0×10

20/cm3未満のポリシリコン層に対し、気相拡散法および固相拡散法からなる群より

選ばれる少なくとも一つの方法によりN型不純物を導入することによりN型ポリシリコン

層を形成する工程と、

(7)前記第三の所定の位置にある前記不純物濃度が1.0×1020/cm3未満のポ

リシリコン層に対し、P型不純物を導入することにより、P型ポリシリコン層を形成する

工程と、

(8)上記(6)および(7)の工程後、前記N型ポリシリコン層およびP型ポリシリコ

ン層の上に、金属シリサイド膜および金属膜からなる群より選ばれる少なくとも一つを形

成する工程と、

(9)エッチング工程により、前記第一および第二の領域に、それぞれN型ポリシリコン

層を含むゲート電極を形成し、かつ前記第三の領域にP型ポリシリコン層を含むゲート電

極を形成する工程と、

(10)前記第一および第二の領域にそれぞれ形成された前記ゲート電極の両側の半導体

シリコン基板表面領域に対し、N型不純物を注入することにより、前記第一の領域にリセ

スチャネル構造を有するセルトランジスタおよび前記第二の領域にnMOSFET構造を

形成する工程と、

(11)前記第三の領域に形成された前記ゲート電極の両側の半導体シリコン基板表面領

域に対し、P型不純物を注入することにより、前記第三の領域にpMOSFET構造を形

成する工程と、

を有することを特徴とする半導体装置の製造方法を提供するものであり、

【0023】

[7]前記工程(6)の前記N型ポリシリコン層を形成する方法は、PH3ガスを用いた

気相拡散法およびリン含有ガラスを用いた固相拡散法からなる群より選ばれる少なくとも

一つであることを特徴とする上記[6]に記載の半導体装置の製造方法を提供するもので

ある。

【発明の効果】

【0024】

本発明によれば、動作電圧の変動が少なく、正常に動作する半導体装置を提供すること

ができる。

【発明を実施するための最良の形態】

【0025】

本発明を実施するための最良の形態について、以下に図面を参照しつつ説明する。

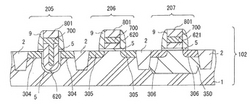

図3は、本発明の半導体装置の第一の実施態様を例示する模式的要部断面図である。

前記半導体装置102は、半導体シリコン基板1を備えるものである。

かかる半導体シリコン基板1に特に制限はなく、通常半導体用途に用いられるものを使

用することができる。本発明に使用する半導体シリコン基板1は、通常はホウ素等のP型

不純物を含有するシリコンウエハ等の市販品を使用することが可能である。

【0026】

また、本発明に使用する半導体シリコン基板1は、所定の位置に素子間分離構造2を備

えるものである。

前記素子間分離構造2の形成方法に限定はないが、例えば、前記半導体シリコン基板1

を用いて、高密度プラズマCVD等の方法を行なうことにより、酸化シリコン等からなる

前記素子間分離構造2を形成することができる。

【0027】

また本発明の半導体装置102は、前記素子間分離構造2により区画された前記半導体

シリコン基板1の第一の領域に設けられたリセスチャネル構造を有するセルトランジスタ

205を備えるものである。

図3に示す様に、前記リセスチャネル構造を有するセルトランジスタ205は前記シリ

コン基板1の所定の位置に設けられたリセス(溝)を有するものである。

前記リセスは、前記半導体シリコン基板1を用いて、リソグラフィー技術およびドライ

エッチング技術等の方法により設けることができる。

【0028】

前記リセスチャネル構造を有するセルトランジスタ205は、前記リセス内部に接して

設けられたゲート絶縁膜5を有するものである。

かかるゲート絶縁膜5は通常は酸化シリコン、窒化シリコン、シリコンオキシナイトラ

イド等の一種もしくは二種以上からなるものであるが、この様なゲート絶縁膜は、例えば

、酸化シリコンの場合であれば、前記半導体シリコン基板1表面のシリコンと、水や酸素

等とを高温下に反応させることにより得ることができる。

【0029】

また前記リセスチャネル構造を有するセルトランジスタ205は、前記ゲート絶縁膜5

に接して設けられたN型ポリシリコン層620および前記N型ポリシリコン層620に接

して設けられた導電層700を含むゲート電極を有するものである。

図3に例示される様に、前記N型ポリシリコン層620の断面はU字状の形状を有する

ものである。前記導電層700の一部は前記N型ポリシリコン層620のU字状の断面の

内部に接して設けられていて、前記導電層700の残りの部分は前記N型ポリシリコン層

620上部に接して設けられている。

【0030】

本発明に使用する前記N型ポリシリコン層620は、そのN型ポリシリコン層620に

含まれるN型不純物の濃度が略一定であることが必要である。

具体的には、N型ポリシリコン層620に含まれるN型不純物の濃度は、1.0×10

20〜1.0×1021/cm3の範囲である。

前記N型不純物の濃度が1.0×1020未満の場合には、得られた半導体装置の動作

電圧が一定せず、正常に動作しない。

また前記N型不純物の濃度が1.0×1021を超える場合には、不純物領域における

電気的短絡等の現象等により、得られた半導体装置が正常に動作しない。

【0031】

かかるN型不純物としては、例えば、リン、ヒ素等を挙げることができる。取り扱い性

の面ら前記N型不純物はリンであることが好ましい。

【0032】

前記N型不純物の濃度が略一定であるN型ポリシリコン層620は次の様にして得るこ

とができる。

すなわち、前記ゲート絶縁膜5に接して、不純物濃度が1.0×1020/cm3未満

のポリシリコン層を形成しておいてから、かかるポリシリコン層に対して、リン等のN型

不純物を気相拡散法、固相拡散法等の方法により導入することにより得ることができる。

前記気相拡散法としては、例えば、具体的には前記不純物を含有しないポリシリコン層

に対し、650〜750℃の温度範囲でPH3ガスを作用させる方法を挙げることができ

る。

また前記固相拡散法としては、例えば、具体的には前記不純物濃度が1.0×1020

/cm3未満のポリシリコン層に対し、リン含有ガラスを作用させる方法を挙げることが

できる。

かかるリン含有ガラスを使用する固相拡散法は、SiH4およびPOCl3を800〜

900℃の温度範囲で反応させ、前記不純物を含有しないポリシリコン層に作用させる方

法により実施することができる。

【0033】

また前記導電層700は、例えば、TiSi2、CoSi2、TaSi2、PtSi2

、NiSi2等の金属シリサイド、タングステン等の金属等の一種もしくは二種以上から

なるものである。

【0034】

さらに、前記N型ポリシリコン層620の側面、ならびに前記導電層700の側面およ

び上面には、窒化シリコン等からなる絶縁膜9および801が設けられている。

【0035】

また前記リセスチャネル構造を有するセルトランジスタ205は、前記半導体シリコン

基板1の表面領域であって前記ゲート電極の両側に設けられた一対のN型拡散層を含むソ

ース・ドレイン領域304を有するものである。

前記ソース・ドレイン領域304は、前記半導体シリコン基板1の表面領域に、先のゲ

ート電極を保護マスクとして、リン等のN型不純物をイオン注入する等の方法によりN型

高濃度不純物層として得ることができる。

【0036】

なお、前記ソース・ドレイン領域304には、図2の場合に説明した場合と同様、リン

等のN型高濃度不純物層に加えて、リン等のN型低濃度不純物層等を適宜追加することが

できる。

【0037】

次に本発明の半導体装置102は、前記素子間分離構造2により区画された前記半導体

シリコン基板1の第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ

206を備えるものである。

【0038】

図3に示す様に、第二の領域に設けられたnMOSFET構造を有する周辺トランジス

タ206は前記半導体シリコン基板1の所定の位置に設けられたゲート絶縁膜5を有する

ものである。

かかるゲート絶縁膜5は、先の第一の領域に設けられたリセスチャネル構造を有するセ

ルトランジスタ205の場合と同様、前記半導体シリコン基板1表面のシリコンと、水や

酸素等とを高温下に反応させる等の方法により得ることができる。

【0039】

また前記第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ206

は、前記ゲート絶縁膜5に接して設けられたN型ポリシリコン層620および前記N型ポ

リシリコン層620に接して設けられた導電層700からなるゲート電極を有するもので

ある。

このN型ポリシリコン層620は、先のリセスチャネル構造を有するセルトランジスタ

205の場合とは異なり、前記半導体シリコン基板1上に前記ゲート絶縁膜5を介して設

けられている。

【0040】

本発明に使用する前記N型ポリシリコン層620は、そのN型ポリシリコン層620に

含まれるN型不純物の濃度が略一定であることは先の場合と同様である。

前記N型ポリシリコン層620に接して前記導電層700が設けられている。前記導電

層700についても、前記リセスチャネル構造を有するセルトランジスタ205の場合と

同様である。

【0041】

さらに前記N型ポリシリコン層620の側面、ならびに前記導電層700の側面および

上面には、窒化シリコン等からなる絶縁膜9、801が設けられている。

【0042】

また第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ206は、

前記半導体シリコン基板1の表面領域であって、前記ゲート電極の両側に設けられた一対

のN型拡散層を含むソース・ドレイン領域305を有するものである。

前記ソース・ドレイン領域305は、前記半導体シリコン基板1の表面に、先のゲート

電極を保護マスクとして、リン等のN型不純物をイオン注入する等の方法により、N型高

濃度不純物層として得ることができる。

【0043】

なお、前記ソース・ドレイン領域305には、先の図2の場合に説明した場合と同様、

リン等の前記N型高濃度不純物層に加えて、リン等の前記N型低濃度不純物層等を適宜追

加することができる。

【0044】

次に、本発明の半導体装置102は、前記素子間分離構造2により区画された前記半導

体シリコン基板1の第三の領域に設けられたpMOSFET構造を有する周辺トランジス

タ207を備えるものである。

【0045】

図3に示す様に、第三の領域に設けられたpMOSFET構造を有する周辺トランジス

タ207は前記半導体シリコン基板1の所定の位置に設けられたゲート絶縁膜5を有する

ものである。

前記ゲート絶縁膜5を設ける方法等については先のセルトランジスタ205の場合と同

様である。

【0046】

また第三の領域に設けられたpMOSFET構造を有する周辺トランジスタ207は、

前記ゲート絶縁膜5に接して設けられたP型ポリシリコン層621および前記P型ポリシ

リコン層621に接して設けられた導電層700からなるゲート電極を有するものである

。

【0047】

先の第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ206のゲ

ート電極が前記N型ポリシリコン層620を有するのに対し、この第三の領域に設けられ

たpMOSFET構造を有する周辺トランジスタ207のゲート電極は、前記P型ポリシ

リコン層621を有する点が異なる。

すなわち、前記周辺トランジスタ206も前記周辺トランジスタ207も共に表面チャ

ネル型トランジスタである。

【0048】

前記P型ポリシリコン層621に含まれるP型不純物の濃度は、1.0×1020〜1

.0×1021/cm3の範囲であることが好ましい。

かかるP型不純物としては、例えば、ホウ素等を挙げることができる。

前記導電層700は、前記リセスチャネル構造を有するセルトランジスタ205の場合

と同様である。

【0049】

さらに前記P型ポリシリコン層621の側面、ならびに前記導電層700の側面および

上面には、窒化シリコン等からなる絶縁膜9、801が設けられている。

【0050】

また第三の領域に設けられたpMOSFET構造を有する周辺トランジスタ207は、

前記シリコン基板1内部に設けられたNウエル領域350の表面領域であって、前記ゲー

ト電極の両側に設けられた一対のN型拡散層を含むソース・ドレイン領域306を有する

ものである。

前記ソース・ドレイン領域306は、前記半導体シリコン基板1の表面に、先のゲート

電極をマスクとして、ホウ素等のP型不純物をイオン注入する等の方法によりP型高濃度

不純物層として得ることができる。

【0051】

なお、前記ソース・ドレイン領域306には、図2の場合に説明した場合と同様、ホウ

素等のP型高濃度不純物層に加えて、ホウ素等のP型低濃度不純物層等を適宜追加するこ

とができる。

【0052】

次に本発明の半導体装置の第二の実施態様について説明する。

図4は、本発明の半導体装置の第二の実施態様を例示する模式的要部断面図である。

【0053】

本発明の半導体装置103の構成は、図4における前記第一の領域に設けられたリセス

チャネル構造を有するセルトランジスタ208のゲート電極の構成と、前記第二の領域に

設けられたnMOSFET構造を有する周辺トランジスタ209のゲート電極の構成を除

き、図3の場合における本発明の半導体装置102の場合と同様である。

そこで前記第一の実施態様である半導体装置102と異なる点を中心に説明する。

【0054】

まず、先の図3の第一の実施態様である前記半導体装置102の前記リセスチャネル構

造を有するセルトランジスタ205の前記ゲート電極は、前記N型ポリシリコン層620

および前記導電層700からなるのに対し、

前記第二の実施態様である半導体装置103の前記リセスチャネル構造を有するセルト

ランジスタ208のゲート電極は、前記N型ポリシリコン層620、不純物濃度が1.0

×1020/cm3未満の第二のポリシリコン層630、第三のN型ポリシリコン層64

0および導電層700からなるものである。

前記半導体装置103の前記N型ポリシリコン層620および導電層700の構成等は

、先の半導体装置102の場合と同様である。

【0055】

図4に示す通り、前記不純物濃度が1.0×1020/cm3未満の第二のポリシリコ

ン層630は、前記N型ポリシリコン層620および前記第三のN型ポリシリコン層64

0との間に充填されている。

前記第二のポリシリコン層に含まれる不純物としては、例えば、リン等のP型不純物を

挙げることができる。

また、前記第三のN型ポリシリコン層640は、そのポリシリコン層にN型不純物を含

むものであるが、かかるN型不純物としては、例えばリン等を挙げることができる。

【0056】

次に、先の図3に示す半導体装置102の前記nMOSFET構造を有する周辺トラン

ジスタ206のゲート電極は、N型ポリシリコン層620および前記導電層700からな

るのに対し、

図4に示す前記第二の実施態様である半導体装置103の前記nMOSFET構造を有

する周辺トランジスタ209のゲート電極は、前記N型ポリシリコン層620、前記第三

のN型ポリシリコン層640、および前記導電層700からなるものである。

【0057】

前記N型ポリシリコン層620および前記第三のN型ポリシリコン層に640含まれる

N型不純物の濃度は、1.0×1020〜1.0×1021/cm3の範囲であることが

好ましい。

【0058】

前記第三のN型ポリシリコン層640に含まれるN型不純物の濃度は、先のN型ポリシ

リコン層620と必ずしも一致する必要はないが、前記濃度は一致していることが好まし

い。

【0059】

前記半導体装置102、103等により例示される本発明の半導体装置は、DRAM(

Dynamic Random Access Memory)等の用途に好適に使用することができる。

【0060】

次に実施例に基づき、本発明についてさらに詳細に説明する。

なお、本発明はこれらの実施例の態様により何ら限定されるものではない。

【実施例1】

【0061】

図5は、本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板

を示す模式的要部断面図である。

以下に本実施例の実施態様について、図面を参照しながら説明する。

【0062】

図5に示す通り、P型不純物を含有する前記半導体シリコン基板1に、前記素子間分離

構造2と前記Nウエル領域350を形成した後、リソグラフィー技術およびドライエッチ

ング技術等を用いて、溝幅90nm、深さ150nmのリセスを形成した。

【0063】

次に酸化シリコンからなるゲート絶縁膜5を前記半導体シリコン基板表面に10nmの

厚みにより形成した。

前記ゲート絶縁膜5は、シリコンオキシナイトライド膜、窒化シリコン膜等により形成

することも可能である。また、かかるゲート絶縁膜5は一種もしくは二種以上を形成する

ことができる。

【0064】

次にCVD法により、図6に示す通り、前記ゲート絶縁膜5の上に前記不純物濃度が1

.0×1020/cm3未満のポリシリコン層630を形成した。このポリシリコン層6

30の厚みは40nmであった。

前記ポリシリコン層630の厚みは、ゲート電極の側壁や導電層等が前記ゲート絶縁膜

5に及ぼす応力に応じて適宜決定されるが、40nm以上の範囲であれば好ましい。

【0065】

次に、CVD法により、前記ポリシリコン層630の上に保護酸化シリコン層500を

20nmの厚みで形成した後、さらにその上にフォトレジスト層900を形成した。前記

フォトレジスト層の不要な部分をリソグラフィー技術とドライエッチング技術とを用いて

除去した後、このフォトレジスト層900を保護マスクとして前記保護酸化シリコン層5

00の不要部分を、リソグラフィー技術とウエットエッチング技術とを用いて除去するこ

とにより、図7に示す様に、保護酸化膜500を形成した。

【0066】

次に前記フォトレジスト層900をドライエッチング、アッシング技術等により除去し

た後、前記保護酸化膜500を保護マスクとして、前記ポリシリコン層630に対し、温

度を700℃に設定した拡散炉中でPH3ガスを用いて気相拡散法を実施し、前記ポリシ

リコン層630のうち前記保護マスクのない部分にリンを導入した。この様にして図8に

示すN型ポリシリコン層620を形成した。

かかるN型ポリシリコン層620に含まれるN型不純物であるリンの濃度は、1.0×

1020〜1.0×1021/cm3の範囲であった。

【0067】

次に、図9に示す様に、前記N型ポリシリコン層620上に形成されたフォトレジスト

層900を保護マスクとして、前記ポリシリコン層630に対し、ホウ素をイオンとして

1.0×1015〜1.0×1016/cm2の範囲により注入してP型ポリシリコン層

621を形成した。

【0068】

前記フォトレジスト層900をドライエッチング、アッシング技術等により除去した後

、図10に示す様に、PVD法、CVD法等の方法により、導電層700を形成すること

ができる。

かかる導電層700としては、例えば、タングステンシリサイド、タングステン金属等

の一種もしくは二種以上からなるものを挙げることができる。

【0069】

前記ポリシリコン層620、621および630ならびに前記導電層700を、フォト

レジスト層(図示せず)を保護マスクとして、リソグラフィー技術とドライエッチング技

術等とを用いて除去することにより、図11に示す構造を形成することができる。

【0070】

次に、図11に示す構造の上に窒化シリコン等の絶縁膜を設けた後、異方性エッチング

の方法により、図12に示す様に、絶縁膜801からなる各ゲート電極上部構造および絶

縁膜9からなる各ゲート電極側壁を形成することができる。

【0071】

図12の各ゲート電極を保護マスクとして、リン等のN型不純物を前記半導体シリコン

基板1の表面領域にイオン注入することにより、前記高濃度N型不純物層からなる前記ソ

ース・ドレイン領域304および305をそれぞれ形成することができる。

【0072】

同様にホウ素等のP型不純物を前記Nウエル350の表面領域にイオン注入することに

より、前記高濃度P型それぞれ不純物層からなる前記ソース・ドレイン領域306を形成

することができる。

このようにして図3に示す本発明の実施例1の構造を得ることができる。

【0073】

なお、図3に示す通り、リセスチャネル構造を有するセルトランジスタ205の前記N

型不純物を含むポリシリコン層620と、前記導電層700とからなるゲート電極は、タ

ングステンシリサイド、タングステン金属等が埋め込まれているため、配線抵抗が小さい

という特徴がある。

【0074】

この様にして得られた半導体装置102は、動作電圧の変動が少なく、正常に動作する

ことから、DRAM(Dynamic Random Access memory)等の用途に好適に使用することが

できる。

【実施例2】

【0075】

本実施例2は、前記実施例1において、図8に示した製造方法の工程までは同様である

が、本実施例2に使用した前記半導体シリコン基板1に設けられたリセスの溝幅は70n

m、深さは150nmである点が異なる。

図15は、本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基

板の要部断面図である。

以下に本実施例の実施態様について、図面を参照しながら説明する。

【0076】

先の図8に示した保護酸化膜500を除去した後、前記ポリシリコン層620および6

30の全面に、不純物濃度が1.0×1020/cm3未満のポリシリコン層630を形

成することにより、図13に示した構造が得られる。

かかる不純物濃度が1.0×1020/cm3未満のポリシリコン層630の厚みは1

0〜20nmの範囲であった。

なお、前記不純物濃度が1.0×1020/cm3未満のポリシリコン層630の下の

前記ポリシリコン層620の厚みは30nmである。

【0077】

次に、図14に示す様に、前記Nウエル350上の対応する位置にフォトレジスト層9

00を設け、前記フォトレジスト層900を保護マスクとして、前記不純物を含有しない

ポリシリコン層630にリン等のN型不純物をイオン注入法により導入することにより、

第三のN型ポリシリコン層640を形成することができる。

【0078】

続いて、前記フォトレジスト層900を除去し、図15に示す様に、前記第三のN型ポ

リシリコン層640上に、新たにフォトレジスト層900を形成する。

前記フォトレジスト層900を保護マスクとして、前記Nウエル350上の対応する位

置にある、前記不純物濃度が1.0×1020/cm3未満のポリシリコン層630にホ

ウ素等のP型不純物をイオン注入法により導入することにより、前記P型ポリシリコン層

621を形成することができる。

【0079】

なお、前記第三のN型ポリシリコン層640を形成する際や前記P型ポリシリコン層6

21を形成する際等の場合に、前記イオン注入法によるエネルギーが強いと、それぞれ前

記リン等のN型不純物や前記ホウ素等のP型不純物が前記ポリシリコン層640等に留ま

らず、前記半導体シリコン基板1の表面領域にまで前記リン等のN型不純物や前記ホウ素

等のP型不純物の突き抜けが生じる。

この様な突き抜けが生じると、得られた半導体装置の閾値電圧の変動が生じ、正常に動

作しないという問題が生じる。

従って、前記ポリシリコン層640および前記半導体シリコン基板1表面より上部にあ

る前記ポリシリコン層620の合計の厚みが100nmの場合では、例えばリンの場合で

は10keV以下、ホウ素の場合では5KeV以下のエネルギーにより注入することが好

ましい。

【0080】

次に前記フォトレジスト層900をドライエッチング、アッシング技術等により除去し

、図16に示す様に、PVD法、CVD法等の方法により、導電層700を形成すること

ができる。

なお本実施例2に使用する導電層700の構成は、実施例1の場合と同様である。

【0081】

前記ポリシリコン層620、621および630ならびに前記導電層700を、フォト

レジスト層(図示せず)を保護マスクとして、リソグラフィー技術とドライエッチング、

アッシング技術等とを用いて除去することにより、図17に示す構造を形成することがで

きる。

【0082】

以下、実施例1の場合と同様の操作を実施することにより、図4に示す本発明の実施例

2の構造を得ることができる。

【0083】

なお、図4に示す通り、前記リセスチャネル構造を有するセルトランジスタ205中の

、前記N型不純物を含むポリシリコン層620、前記不純物濃度が1.0×1020/c

m3未満の第二のポリシリコン層630、前記第三のN型不純物を含むポリシリコン層6

40および前記導電層700とからなるゲート電極は、タングステンシリサイド、タング

ステン金属等が埋め込まれているため、配線抵抗が小さいという特徴がある。

ここで、前記リセスチャネル構造を有するセルトランジスタ208の前記N型ポリシリ

コン層620に含まれるN型不純物であるリンの濃度は、1.0×1020〜1.0×1

021/cm3の範囲であった。

【0084】

この様にして得られた半導体装置103は、動作電圧の変動が少なく、正常に動作する

ことから、DRAM(Dynamic Random Access Memory)等の用途に好適に使用することが

できる。

【実施例3】

【0085】

実施例2の場合で得られた、図4に示す半導体装置103のリセスチャネル構造を有す

るセルトランジスタ208のゲート電極を、温度650〜800℃の範囲で加熱処理する

ことにより、前記ゲート電極中の、前記N型不純物を含むポリシリコン層620、前記不

純物濃度が1.0×1020/cm3未満の第二のポリシリコン層630、および前記第

三のN型不純物を含むポリシリコン層640のそれぞれに含まれるリンは拡散し、それぞ

れの領域でリンの濃度を1.0×1020〜1.0×1021/cm3の範囲内で均一化

することができる。

前記温度が650℃未満の場合には、前記半導体シリコン基板1中のリンを活性化させ

ることができず、前記温度が800℃を超える場合には、前記周辺トランジスタ207の

ゲート電極中のP型ポリシリコンに含まれるホウ素等のP型不純物が前記半導体シリコン

基板1中に拡散し、前記半導体装置の正常な動作を妨げる。

【0086】

この様にして得られた半導体装置104(図示せず)は、動作電圧の変動が少なく、正

常に動作することから、DRAM(Dynamic Random Access memory)等の用途に好適に使

用することができる。

【0087】

[比較例1]

実施例1の図5の構造に対し、不純物濃度が1.0×1020/cm3未満のポリシリ

コン層630を設けた後、さらに前記Nウエル350上の対応する部分を除く前記半導体

シリコン基板1の上にフォトレジスト層900を設け、前記フォトレジスト層900を保

護マスクとして、前記Nウエル350上の対応する位置にある、前記不純物濃度が1.0

×1020/cm3未満の第二のポリシリコン層630にホウ素等のP型不純物をイオン

注入法により導入することにより、図18に示す様に前記P型ポリシリコン層621を形

成することができる。

【0088】

次に前記フォトレジスト層900を除去した後、図19に示す様に、前記P型ポリシリ

コン層621の上にフォトレジスト層900を設け、前記フォトレジスト層900を保護

マスクとして、前記ポリシリコン層630に対し、今度はリン等のN型不純物をイオン注

入法により導入することにより、図19に示す様に、前記N型ポリシリコン層620を形

成することができる。

このとき、前記リセス内部の最下部の前記ポリシリコン層630に含まれるリン等のN

型不純物濃度は、1.0×1020/cm3未満であった。

【0089】

次に、前記フォトレジスト900を除去した後、図20に示す様に、PVD法、CVD

法等の方法により、導電層700を形成することができる。

なお本比較例1に使用する導電層700の構成は、実施例1の場合と同様である。

前記ポリシリコン層620、621および630ならびに前記導電層700を、フォト

レジスト層(図示せず)を保護マスクとして、リソグラフィー技術とドライエッチング技

術とを用いて除去することにより、図21に示す構造を形成することができる。

【0090】

以下、実施例1の場合と同様の操作を実施することにより、図22に示す半導体装置を

得ることができる。

【0091】

図23に示す半導体装置は、リセスチャネル構造を有するセルトランジスタのゲート電

極には空乏層が存在するため、動作電圧の変動が大きく、正常に動作しなかった。

【図面の簡単な説明】

【0092】

【図1】従来の半導体装置を示す模式的要部断面図である。

【図2】従来の半導体装置を示す模式的要部断面図である。

【図3】本発明の半導体装置の第一の実施態様を例示する模式的要部断面図である。

【図4】本発明の半導体装置の第二の実施態様を例示する模式的要部断面図である。

【図5】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図6】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図7】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図8】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図9】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図10】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図11】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図12】本発明の半導体装置を例示する模式的要部断面図である(実施例1)。

【図13】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図14】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図15】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図16】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図17】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図18】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図19】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図20】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図21】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図22】比較例の半導体装置を例示する模式的要部断面図である(比較例1)。

【符号の説明】

【0093】

1、1a 半導体シリコン基板

1b N型エピタキシャル層

2 素子間分離構造

3、4、301〜306 ソース・ドレイン領域

5 ゲート絶縁膜

6a、6b、611、612 ゲート電極

7 金属シリサイド

8、9、800、801 絶縁膜

100、101、102、103 半導体装置

200 nMOSFET構造を有するトランジスタ

201、202、204、 207 pMOSFET構造を有するトランジスタ

203、206、209 nMOSFET構造を有するトランジスタ

205、208 リセスチャネル構造を有するセルトランジスタ

310、330 P型低濃度不純物層

320 N型低濃度不純物層

340 Pウエル領域

341 N型ボディ領域

350、360 Nウエル領域

370 P型埋め込み層

500 保護酸化シリコン層

600、620 N型ポリシリコン層

601、610、621 P型ポリシリコン層

630 不純物を含まないポリシリコン層

640 第二のN型ポリシリコン層

700 導電層

900 フォトレジスト層

【技術分野】

【0001】

本発明は、リセス(溝)チャネル構造を有するセルトランジスタを含む半導体装置およ

びその製造方法に関し、

さらに詳しくは、リセスチャネル構造を有するセルトランジスタ、N型ポリシリコンを

含むゲート電極を備えたnMOSFET構造を有する周辺トランジスタ、およびP型ポリ

シリコンを含むゲート電極を備えたpMOSFET構造を有する周辺トランジスタを有す

る半導体装置およびその製造方法に関する。

【背景技術】

【0002】

図1に従来の半導体装置の模式的要部断面図を示す。

図1には、N型ポリシリコン層600を含むゲート電極6aがP型の半導体シリコン基

板1上に形成されたnMOSFET構造を有するトランジスタ200と、P型ポリシリコ

ン層601を含むゲート電極6bがNウエル領域360上に形成されたpMOSFET構

造を有するトランジスタ201を備えた半導体装置100が示されている。

【0003】

前記トランジスタ200は、ゲート絶縁膜5を介して半導体シリコン基板1上に形成さ

れたゲート電極6aと、前記ゲート電極6aに対応する一対のソース・ドレイン領域3を

有するものである。

前記ゲート電極6aは、N型ポリシリコン層600と金属シリサイド7とからなるもの

である。前記ゲート電極6aの上部と側壁には、それぞれ窒化シリコンからなる絶縁膜8

および9が設けられている。

【0004】

また前記トランジスタ201は、前記トランジスタ200と同様に、前記ゲート絶縁膜

5を介して前記半導体シリコン基板1中のNウエル領域360上に形成されたゲート電極

6bと、前記ゲート電極6bに対応する一対のソース・ドレイン領域4を有するものであ

る。

前記ゲート電極6bは、P型ポリシリコン層601と金属シリサイド7とからなるもの

である。前記ゲート電極6bの上部と側壁には、それぞれ窒化シリコンからなる絶縁膜8

および9が設けられている。

【0005】

さらに、前記トランジスタ200と前記トランジスタ201とは、素子間分離構造2に

より分離されている。

これらのトランジスタの組合せは相補型MOS(Complementary MOS、以下、「CMO

S」という。)構造と一般に呼ばれるものである。

【0006】

図1の前記トランジスタ200に対応するソース・ドレイン領域3はN型の不純物を含

み、また、前記トランジスタ201に対応するソース・ドレイン領域4はP型の不純物を

含む。

この様に、前記ゲート電極に含まれる不純物の導電型と、前記ソース・ドレイン領域に

含まれる不純物の導電型が一致するトランジスタは表面チャネル型トランジスタと呼ばれ

ている。

図1に示される前記CMOS構造を備えた半導体装置100は、前記トランジスタ20

0および201のそれぞれが表面チャネル型トランジスタから構成されている(特許文献

1)。

【0007】

一方、図2に他の従来の半導体装置の模式的要部断面図を示す。

図2には、P型ポリシリコン層を含むゲート電極611がN型エピタキシャル層1b上

に形成されたpMOSFET構造を有するトランジスタ202と、P型ポリシリコン層を

含むゲート電極612がPウエル領域340の上に形成されたnMOSFET構造を有す

るトランジスタ203と、リセスチャネル構造を有するP型ポリシリコン層610を含む

ゲート電極がPウエル領域340に形成されたpMOSFET構造を有するトランジスタ

204とを備えた半導体装置101が示されている。

【0008】

前記トランジスタ202に対応するソース・ドレイン領域301は、半導体シリコン基

板1a上に設けられたN型エピタキシャル層1bの表面領域のP型高濃度不純物層により

形成されている。

さらに前記ソース・ドレイン領域301に重ねて、P型低濃度不純物層310が設けら

れている。

【0009】

また前記トランジスタ203に対応するソース・ドレイン領域302は、前記Pウエル

領域340の表面領域のN型高濃度不純物層により形成されている。

さらに前記ソース・ドレイン領域302に重ねて、N型低濃度不純物層320が設けら

れている。

【0010】

前記トランジスタ204はリセスチャネル構造を有するものであるが、かかるトランジ

スタ204に対応するソース・ドレイン領域303は、N型ボディ領域341の表面領域

に設けられたP型高濃度不純物層により形成されている。

さらに前記ソース・ドレイン領域303に重ねて、P型低濃度不純物層330が設けら

れている。

前記N型ボディ領域341は前記Pウエル領域340内部に形成されていて、前記Pウ

エル領域340の下部にはP型埋め込み層370が設けられている。

【0011】

さらに前記リセスチャネル構造は、絶縁膜9、P型ポリシリコン層610、導電層70

0により充填されており、さらに前記導電層700の上部および側面には窒化シリコンか

らなる絶縁膜800および9が設けられている。

加えて、前記トランジスタ202、前記トランジスタ203および前記トランジスタ2

04は、それぞれ素子間分離構造2により分離されている。

【0012】

上記に説明した通り、前記トランジスタ202は、前記ゲート電極611がP型ポリシ

リコン層を含み、前記pMOSFET構造に対応するソース・ドレイン領域301がP型

の不純物を含むことから、表面チャネル型トランジスタである。

この一方、前記トランジスタ203は、前記ゲート電極612がP型ポリシリコン層を

含み、nMOSFET構造に対応するPウエルがP型不純物を含むことから、このタイプ

のトランジスタは、埋め込みチャネル型トランジスタと一般に呼ばれる。

この様に、表面チャネル型トランジスタ、埋め込みチャネル型トランジスタおよびリセ

スチャネル構造を有するトランジスタを備えた半導体装置101が知られている(特許文

献2)。

【特許文献1】特開平11−307729号公報

【特許文献2】特開2002−359294号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

しかしながら、上記の知見を新たにDRAM(Dynamic Random Access Memory)等の半

導体装置に適用しようとすると不具合が生じた。

【0014】

すなわち、表面チャネル型トランジスタのnMOSFET構造を有するトランジスタ構

造および表面チャネル型トランジスタのpMOSFET構造を有するトランジスタ構造を

有するデュアルゲート型周辺トランジスタと、リセスチャネル構造を備えたnMOSFE

T構造を有するセルトランジスタとを単に組み合わせただけでは、得られた半導体装置の

動作電圧の変動が大きい等、前記半導体装置が正常に動作しないという問題があった。

【0015】

本発明の目的は、表面チャネル型nMOSFET構造を備えたトランジスタ構造および

表面チャネル型pMOSFET構造を有備えたトランジスタ構造を有するデュアルゲート

型周辺トランジスタと、リセスチャネル構造を備えたnMOSFET構造を有するセルト

ランジスタと、を含む半導体装置であって、

動作電圧の変動が少なく、正常に動作する半導体装置を提供することにある。

【課題を解決するための手段】

【0016】

本発明者は、上記課題を解決すべく鋭意検討した結果、前記半導体装置の中でも、前記

セルトランジスタ中のゲート電極を構成するN型ポリシリコン層に含まれるN型不純物の

濃度が、略一定である半導体装置が上記課題を解決することを見出し、本発明を完成する

に至った。

すなわち本発明は、

【0017】

[1]半導体シリコン基板と、

前記半導体シリコン基板の所定の位置に設けられた素子間分離構造と、

前記素子間分離構造により区画された前記半導体シリコン基板の第一の領域に設けられ

たリセスチャネル構造を有するセルトランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第二の領域に設けられ

たnMOSFET構造を有する周辺トランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第三の領域に設けられ

たpMOSFET構造を有する周辺トランジスタと、

を備えた半導体装置であって、

(A)前記リセスチャネル構造を有するセルトランジスタは、下記(1)〜(4)を有し

、

(1)前記半導体シリコン基板の所定の位置に設けられたリセス

(2)前記リセス内部に接して設けられたゲート絶縁膜

(3)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

を含むゲート電極

(4)前記半導体シリコン基板の表面領域であって前記ゲート電極の両側に設けられた一

対のN型拡散層を含むソース・ドレイン領域

(B)前記第二の領域に設けられたnMOSFET構造を有する周辺トランジスタは、下

記(5)〜(7)を有し、

(5)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(6)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極

(7)前記半導体シリコン基板の表面領域であって、前記ゲート電極の両側に設けられた

一対のN型拡散層を含むソース・ドレイン領域

(C)前記第三の領域に設けられたpMOSFET構造を有する周辺トランジスタは、下

記(8)〜(10)を有し、

(8)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(9)前記ゲート絶縁膜に接して設けられたP型ポリシリコン層および前記P型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極、

(10)前記シリコン基板内部に設けられたNウエルの表面領域であって、前記ゲート電

極の両側に設けられた一対のP型拡散層を含むソース・ドレイン領域

かつ、上記に加えて前記セルトランジスタ中のN型ポリシリコン層に含まれるN型不純

物の濃度は、略一定であることを特徴とする半導体装置を提供するものであり、

【0018】

[2]前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられ、かつ前記リセス内部および前記リ

セス上部に設けられた導電層、

からなることを特徴とする上記[1]に記載の半導体装置を提供するものであり、

【0019】

[3]前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

前記N型ポリシリコン層内部に設けられた、不純物濃度が1.0×1020/cm3未

満の第二のポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする上記[1]に記載の半導体装置を提供するものであり、

【0020】

[4]前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して、前記リセス内部全てに設けられた前記N型ポリシリコン層

、

および前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする上記[1]に記載の半導体装置を提供するものであり、

【0021】

[5]前記リセスチャネル構造を有するセルトランジスタ中のN型ポリシリコン層に含ま

れるN型不純物の濃度は、1.0×1020〜1.0×1021/cm3の範囲であるこ

とを特徴とする上記[1]〜[4]のいずれかに記載の半導体装置を提供するものであり

、

【0022】

[6](1)半導体シリコン基板の所定の領域に素子間分離構造を形成し、前記半導体シ

リコン基板に前記素子間分離構造により区画された第一ないし第三の領域を形成する工程

と、

(2)前記素子間分離構造により区画された前記半導体シリコン基板の前記第一の領域に

リセスを形成する工程と、

(3)前記素子間分離構造により区画された前記半導体シリコン基板の前記第三の位置に

Nウエルを形成する工程と、

(4)前記半導体シリコン基板上面および前記リセス内部表面にゲート絶縁膜を形成する

工程と、

(5)前記ゲート絶縁膜のうち、前記半導体シリコン基板上面に該当する部分および前記

リセス内部表面に該当する部分の上面ならびに前記素子間分離構造上面に、不純物濃度が

1.0×1020/cm3未満のポリシリコン層を形成する工程と、

(6)前記第一および第二のそれぞれの所定の位置にある前記不純物濃度が1.0×10

20/cm3未満のポリシリコン層に対し、気相拡散法および固相拡散法からなる群より

選ばれる少なくとも一つの方法によりN型不純物を導入することによりN型ポリシリコン

層を形成する工程と、

(7)前記第三の所定の位置にある前記不純物濃度が1.0×1020/cm3未満のポ

リシリコン層に対し、P型不純物を導入することにより、P型ポリシリコン層を形成する

工程と、

(8)上記(6)および(7)の工程後、前記N型ポリシリコン層およびP型ポリシリコ

ン層の上に、金属シリサイド膜および金属膜からなる群より選ばれる少なくとも一つを形

成する工程と、

(9)エッチング工程により、前記第一および第二の領域に、それぞれN型ポリシリコン

層を含むゲート電極を形成し、かつ前記第三の領域にP型ポリシリコン層を含むゲート電

極を形成する工程と、

(10)前記第一および第二の領域にそれぞれ形成された前記ゲート電極の両側の半導体

シリコン基板表面領域に対し、N型不純物を注入することにより、前記第一の領域にリセ

スチャネル構造を有するセルトランジスタおよび前記第二の領域にnMOSFET構造を

形成する工程と、

(11)前記第三の領域に形成された前記ゲート電極の両側の半導体シリコン基板表面領

域に対し、P型不純物を注入することにより、前記第三の領域にpMOSFET構造を形

成する工程と、

を有することを特徴とする半導体装置の製造方法を提供するものであり、

【0023】

[7]前記工程(6)の前記N型ポリシリコン層を形成する方法は、PH3ガスを用いた

気相拡散法およびリン含有ガラスを用いた固相拡散法からなる群より選ばれる少なくとも

一つであることを特徴とする上記[6]に記載の半導体装置の製造方法を提供するもので

ある。

【発明の効果】

【0024】

本発明によれば、動作電圧の変動が少なく、正常に動作する半導体装置を提供すること

ができる。

【発明を実施するための最良の形態】

【0025】

本発明を実施するための最良の形態について、以下に図面を参照しつつ説明する。

図3は、本発明の半導体装置の第一の実施態様を例示する模式的要部断面図である。

前記半導体装置102は、半導体シリコン基板1を備えるものである。

かかる半導体シリコン基板1に特に制限はなく、通常半導体用途に用いられるものを使

用することができる。本発明に使用する半導体シリコン基板1は、通常はホウ素等のP型

不純物を含有するシリコンウエハ等の市販品を使用することが可能である。

【0026】

また、本発明に使用する半導体シリコン基板1は、所定の位置に素子間分離構造2を備

えるものである。

前記素子間分離構造2の形成方法に限定はないが、例えば、前記半導体シリコン基板1

を用いて、高密度プラズマCVD等の方法を行なうことにより、酸化シリコン等からなる

前記素子間分離構造2を形成することができる。

【0027】

また本発明の半導体装置102は、前記素子間分離構造2により区画された前記半導体

シリコン基板1の第一の領域に設けられたリセスチャネル構造を有するセルトランジスタ

205を備えるものである。

図3に示す様に、前記リセスチャネル構造を有するセルトランジスタ205は前記シリ

コン基板1の所定の位置に設けられたリセス(溝)を有するものである。

前記リセスは、前記半導体シリコン基板1を用いて、リソグラフィー技術およびドライ

エッチング技術等の方法により設けることができる。

【0028】

前記リセスチャネル構造を有するセルトランジスタ205は、前記リセス内部に接して

設けられたゲート絶縁膜5を有するものである。

かかるゲート絶縁膜5は通常は酸化シリコン、窒化シリコン、シリコンオキシナイトラ

イド等の一種もしくは二種以上からなるものであるが、この様なゲート絶縁膜は、例えば

、酸化シリコンの場合であれば、前記半導体シリコン基板1表面のシリコンと、水や酸素

等とを高温下に反応させることにより得ることができる。

【0029】

また前記リセスチャネル構造を有するセルトランジスタ205は、前記ゲート絶縁膜5

に接して設けられたN型ポリシリコン層620および前記N型ポリシリコン層620に接

して設けられた導電層700を含むゲート電極を有するものである。

図3に例示される様に、前記N型ポリシリコン層620の断面はU字状の形状を有する

ものである。前記導電層700の一部は前記N型ポリシリコン層620のU字状の断面の

内部に接して設けられていて、前記導電層700の残りの部分は前記N型ポリシリコン層

620上部に接して設けられている。

【0030】

本発明に使用する前記N型ポリシリコン層620は、そのN型ポリシリコン層620に

含まれるN型不純物の濃度が略一定であることが必要である。

具体的には、N型ポリシリコン層620に含まれるN型不純物の濃度は、1.0×10

20〜1.0×1021/cm3の範囲である。

前記N型不純物の濃度が1.0×1020未満の場合には、得られた半導体装置の動作

電圧が一定せず、正常に動作しない。

また前記N型不純物の濃度が1.0×1021を超える場合には、不純物領域における

電気的短絡等の現象等により、得られた半導体装置が正常に動作しない。

【0031】

かかるN型不純物としては、例えば、リン、ヒ素等を挙げることができる。取り扱い性

の面ら前記N型不純物はリンであることが好ましい。

【0032】

前記N型不純物の濃度が略一定であるN型ポリシリコン層620は次の様にして得るこ

とができる。

すなわち、前記ゲート絶縁膜5に接して、不純物濃度が1.0×1020/cm3未満

のポリシリコン層を形成しておいてから、かかるポリシリコン層に対して、リン等のN型

不純物を気相拡散法、固相拡散法等の方法により導入することにより得ることができる。

前記気相拡散法としては、例えば、具体的には前記不純物を含有しないポリシリコン層

に対し、650〜750℃の温度範囲でPH3ガスを作用させる方法を挙げることができ

る。

また前記固相拡散法としては、例えば、具体的には前記不純物濃度が1.0×1020

/cm3未満のポリシリコン層に対し、リン含有ガラスを作用させる方法を挙げることが

できる。

かかるリン含有ガラスを使用する固相拡散法は、SiH4およびPOCl3を800〜

900℃の温度範囲で反応させ、前記不純物を含有しないポリシリコン層に作用させる方

法により実施することができる。

【0033】

また前記導電層700は、例えば、TiSi2、CoSi2、TaSi2、PtSi2

、NiSi2等の金属シリサイド、タングステン等の金属等の一種もしくは二種以上から

なるものである。

【0034】

さらに、前記N型ポリシリコン層620の側面、ならびに前記導電層700の側面およ

び上面には、窒化シリコン等からなる絶縁膜9および801が設けられている。

【0035】

また前記リセスチャネル構造を有するセルトランジスタ205は、前記半導体シリコン

基板1の表面領域であって前記ゲート電極の両側に設けられた一対のN型拡散層を含むソ

ース・ドレイン領域304を有するものである。

前記ソース・ドレイン領域304は、前記半導体シリコン基板1の表面領域に、先のゲ

ート電極を保護マスクとして、リン等のN型不純物をイオン注入する等の方法によりN型

高濃度不純物層として得ることができる。

【0036】

なお、前記ソース・ドレイン領域304には、図2の場合に説明した場合と同様、リン

等のN型高濃度不純物層に加えて、リン等のN型低濃度不純物層等を適宜追加することが

できる。

【0037】

次に本発明の半導体装置102は、前記素子間分離構造2により区画された前記半導体

シリコン基板1の第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ

206を備えるものである。

【0038】

図3に示す様に、第二の領域に設けられたnMOSFET構造を有する周辺トランジス

タ206は前記半導体シリコン基板1の所定の位置に設けられたゲート絶縁膜5を有する

ものである。

かかるゲート絶縁膜5は、先の第一の領域に設けられたリセスチャネル構造を有するセ

ルトランジスタ205の場合と同様、前記半導体シリコン基板1表面のシリコンと、水や

酸素等とを高温下に反応させる等の方法により得ることができる。

【0039】

また前記第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ206

は、前記ゲート絶縁膜5に接して設けられたN型ポリシリコン層620および前記N型ポ

リシリコン層620に接して設けられた導電層700からなるゲート電極を有するもので

ある。

このN型ポリシリコン層620は、先のリセスチャネル構造を有するセルトランジスタ

205の場合とは異なり、前記半導体シリコン基板1上に前記ゲート絶縁膜5を介して設

けられている。

【0040】

本発明に使用する前記N型ポリシリコン層620は、そのN型ポリシリコン層620に

含まれるN型不純物の濃度が略一定であることは先の場合と同様である。

前記N型ポリシリコン層620に接して前記導電層700が設けられている。前記導電

層700についても、前記リセスチャネル構造を有するセルトランジスタ205の場合と

同様である。

【0041】

さらに前記N型ポリシリコン層620の側面、ならびに前記導電層700の側面および

上面には、窒化シリコン等からなる絶縁膜9、801が設けられている。

【0042】

また第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ206は、

前記半導体シリコン基板1の表面領域であって、前記ゲート電極の両側に設けられた一対

のN型拡散層を含むソース・ドレイン領域305を有するものである。

前記ソース・ドレイン領域305は、前記半導体シリコン基板1の表面に、先のゲート

電極を保護マスクとして、リン等のN型不純物をイオン注入する等の方法により、N型高

濃度不純物層として得ることができる。

【0043】

なお、前記ソース・ドレイン領域305には、先の図2の場合に説明した場合と同様、

リン等の前記N型高濃度不純物層に加えて、リン等の前記N型低濃度不純物層等を適宜追

加することができる。

【0044】

次に、本発明の半導体装置102は、前記素子間分離構造2により区画された前記半導

体シリコン基板1の第三の領域に設けられたpMOSFET構造を有する周辺トランジス

タ207を備えるものである。

【0045】

図3に示す様に、第三の領域に設けられたpMOSFET構造を有する周辺トランジス

タ207は前記半導体シリコン基板1の所定の位置に設けられたゲート絶縁膜5を有する

ものである。

前記ゲート絶縁膜5を設ける方法等については先のセルトランジスタ205の場合と同

様である。

【0046】

また第三の領域に設けられたpMOSFET構造を有する周辺トランジスタ207は、

前記ゲート絶縁膜5に接して設けられたP型ポリシリコン層621および前記P型ポリシ

リコン層621に接して設けられた導電層700からなるゲート電極を有するものである

。

【0047】

先の第二の領域に設けられたnMOSFET構造を有する周辺トランジスタ206のゲ

ート電極が前記N型ポリシリコン層620を有するのに対し、この第三の領域に設けられ

たpMOSFET構造を有する周辺トランジスタ207のゲート電極は、前記P型ポリシ

リコン層621を有する点が異なる。

すなわち、前記周辺トランジスタ206も前記周辺トランジスタ207も共に表面チャ

ネル型トランジスタである。

【0048】

前記P型ポリシリコン層621に含まれるP型不純物の濃度は、1.0×1020〜1

.0×1021/cm3の範囲であることが好ましい。

かかるP型不純物としては、例えば、ホウ素等を挙げることができる。

前記導電層700は、前記リセスチャネル構造を有するセルトランジスタ205の場合

と同様である。

【0049】

さらに前記P型ポリシリコン層621の側面、ならびに前記導電層700の側面および

上面には、窒化シリコン等からなる絶縁膜9、801が設けられている。

【0050】

また第三の領域に設けられたpMOSFET構造を有する周辺トランジスタ207は、

前記シリコン基板1内部に設けられたNウエル領域350の表面領域であって、前記ゲー

ト電極の両側に設けられた一対のN型拡散層を含むソース・ドレイン領域306を有する

ものである。

前記ソース・ドレイン領域306は、前記半導体シリコン基板1の表面に、先のゲート

電極をマスクとして、ホウ素等のP型不純物をイオン注入する等の方法によりP型高濃度

不純物層として得ることができる。

【0051】

なお、前記ソース・ドレイン領域306には、図2の場合に説明した場合と同様、ホウ

素等のP型高濃度不純物層に加えて、ホウ素等のP型低濃度不純物層等を適宜追加するこ

とができる。

【0052】

次に本発明の半導体装置の第二の実施態様について説明する。

図4は、本発明の半導体装置の第二の実施態様を例示する模式的要部断面図である。

【0053】

本発明の半導体装置103の構成は、図4における前記第一の領域に設けられたリセス

チャネル構造を有するセルトランジスタ208のゲート電極の構成と、前記第二の領域に

設けられたnMOSFET構造を有する周辺トランジスタ209のゲート電極の構成を除

き、図3の場合における本発明の半導体装置102の場合と同様である。

そこで前記第一の実施態様である半導体装置102と異なる点を中心に説明する。

【0054】

まず、先の図3の第一の実施態様である前記半導体装置102の前記リセスチャネル構

造を有するセルトランジスタ205の前記ゲート電極は、前記N型ポリシリコン層620

および前記導電層700からなるのに対し、

前記第二の実施態様である半導体装置103の前記リセスチャネル構造を有するセルト

ランジスタ208のゲート電極は、前記N型ポリシリコン層620、不純物濃度が1.0

×1020/cm3未満の第二のポリシリコン層630、第三のN型ポリシリコン層64

0および導電層700からなるものである。

前記半導体装置103の前記N型ポリシリコン層620および導電層700の構成等は

、先の半導体装置102の場合と同様である。

【0055】

図4に示す通り、前記不純物濃度が1.0×1020/cm3未満の第二のポリシリコ

ン層630は、前記N型ポリシリコン層620および前記第三のN型ポリシリコン層64

0との間に充填されている。

前記第二のポリシリコン層に含まれる不純物としては、例えば、リン等のP型不純物を

挙げることができる。

また、前記第三のN型ポリシリコン層640は、そのポリシリコン層にN型不純物を含

むものであるが、かかるN型不純物としては、例えばリン等を挙げることができる。

【0056】

次に、先の図3に示す半導体装置102の前記nMOSFET構造を有する周辺トラン

ジスタ206のゲート電極は、N型ポリシリコン層620および前記導電層700からな

るのに対し、

図4に示す前記第二の実施態様である半導体装置103の前記nMOSFET構造を有

する周辺トランジスタ209のゲート電極は、前記N型ポリシリコン層620、前記第三

のN型ポリシリコン層640、および前記導電層700からなるものである。

【0057】

前記N型ポリシリコン層620および前記第三のN型ポリシリコン層に640含まれる

N型不純物の濃度は、1.0×1020〜1.0×1021/cm3の範囲であることが

好ましい。

【0058】

前記第三のN型ポリシリコン層640に含まれるN型不純物の濃度は、先のN型ポリシ

リコン層620と必ずしも一致する必要はないが、前記濃度は一致していることが好まし

い。

【0059】

前記半導体装置102、103等により例示される本発明の半導体装置は、DRAM(

Dynamic Random Access Memory)等の用途に好適に使用することができる。

【0060】

次に実施例に基づき、本発明についてさらに詳細に説明する。

なお、本発明はこれらの実施例の態様により何ら限定されるものではない。

【実施例1】

【0061】

図5は、本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板

を示す模式的要部断面図である。

以下に本実施例の実施態様について、図面を参照しながら説明する。

【0062】

図5に示す通り、P型不純物を含有する前記半導体シリコン基板1に、前記素子間分離

構造2と前記Nウエル領域350を形成した後、リソグラフィー技術およびドライエッチ

ング技術等を用いて、溝幅90nm、深さ150nmのリセスを形成した。

【0063】

次に酸化シリコンからなるゲート絶縁膜5を前記半導体シリコン基板表面に10nmの

厚みにより形成した。

前記ゲート絶縁膜5は、シリコンオキシナイトライド膜、窒化シリコン膜等により形成

することも可能である。また、かかるゲート絶縁膜5は一種もしくは二種以上を形成する

ことができる。

【0064】

次にCVD法により、図6に示す通り、前記ゲート絶縁膜5の上に前記不純物濃度が1

.0×1020/cm3未満のポリシリコン層630を形成した。このポリシリコン層6

30の厚みは40nmであった。

前記ポリシリコン層630の厚みは、ゲート電極の側壁や導電層等が前記ゲート絶縁膜

5に及ぼす応力に応じて適宜決定されるが、40nm以上の範囲であれば好ましい。

【0065】

次に、CVD法により、前記ポリシリコン層630の上に保護酸化シリコン層500を

20nmの厚みで形成した後、さらにその上にフォトレジスト層900を形成した。前記

フォトレジスト層の不要な部分をリソグラフィー技術とドライエッチング技術とを用いて

除去した後、このフォトレジスト層900を保護マスクとして前記保護酸化シリコン層5

00の不要部分を、リソグラフィー技術とウエットエッチング技術とを用いて除去するこ

とにより、図7に示す様に、保護酸化膜500を形成した。

【0066】

次に前記フォトレジスト層900をドライエッチング、アッシング技術等により除去し

た後、前記保護酸化膜500を保護マスクとして、前記ポリシリコン層630に対し、温

度を700℃に設定した拡散炉中でPH3ガスを用いて気相拡散法を実施し、前記ポリシ

リコン層630のうち前記保護マスクのない部分にリンを導入した。この様にして図8に

示すN型ポリシリコン層620を形成した。

かかるN型ポリシリコン層620に含まれるN型不純物であるリンの濃度は、1.0×

1020〜1.0×1021/cm3の範囲であった。

【0067】

次に、図9に示す様に、前記N型ポリシリコン層620上に形成されたフォトレジスト

層900を保護マスクとして、前記ポリシリコン層630に対し、ホウ素をイオンとして

1.0×1015〜1.0×1016/cm2の範囲により注入してP型ポリシリコン層

621を形成した。

【0068】

前記フォトレジスト層900をドライエッチング、アッシング技術等により除去した後

、図10に示す様に、PVD法、CVD法等の方法により、導電層700を形成すること

ができる。

かかる導電層700としては、例えば、タングステンシリサイド、タングステン金属等

の一種もしくは二種以上からなるものを挙げることができる。

【0069】

前記ポリシリコン層620、621および630ならびに前記導電層700を、フォト

レジスト層(図示せず)を保護マスクとして、リソグラフィー技術とドライエッチング技

術等とを用いて除去することにより、図11に示す構造を形成することができる。

【0070】

次に、図11に示す構造の上に窒化シリコン等の絶縁膜を設けた後、異方性エッチング

の方法により、図12に示す様に、絶縁膜801からなる各ゲート電極上部構造および絶

縁膜9からなる各ゲート電極側壁を形成することができる。

【0071】

図12の各ゲート電極を保護マスクとして、リン等のN型不純物を前記半導体シリコン

基板1の表面領域にイオン注入することにより、前記高濃度N型不純物層からなる前記ソ

ース・ドレイン領域304および305をそれぞれ形成することができる。

【0072】

同様にホウ素等のP型不純物を前記Nウエル350の表面領域にイオン注入することに

より、前記高濃度P型それぞれ不純物層からなる前記ソース・ドレイン領域306を形成

することができる。

このようにして図3に示す本発明の実施例1の構造を得ることができる。

【0073】

なお、図3に示す通り、リセスチャネル構造を有するセルトランジスタ205の前記N

型不純物を含むポリシリコン層620と、前記導電層700とからなるゲート電極は、タ

ングステンシリサイド、タングステン金属等が埋め込まれているため、配線抵抗が小さい

という特徴がある。

【0074】

この様にして得られた半導体装置102は、動作電圧の変動が少なく、正常に動作する

ことから、DRAM(Dynamic Random Access memory)等の用途に好適に使用することが

できる。

【実施例2】

【0075】

本実施例2は、前記実施例1において、図8に示した製造方法の工程までは同様である

が、本実施例2に使用した前記半導体シリコン基板1に設けられたリセスの溝幅は70n

m、深さは150nmである点が異なる。

図15は、本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基

板の要部断面図である。

以下に本実施例の実施態様について、図面を参照しながら説明する。

【0076】

先の図8に示した保護酸化膜500を除去した後、前記ポリシリコン層620および6

30の全面に、不純物濃度が1.0×1020/cm3未満のポリシリコン層630を形

成することにより、図13に示した構造が得られる。

かかる不純物濃度が1.0×1020/cm3未満のポリシリコン層630の厚みは1

0〜20nmの範囲であった。

なお、前記不純物濃度が1.0×1020/cm3未満のポリシリコン層630の下の

前記ポリシリコン層620の厚みは30nmである。

【0077】

次に、図14に示す様に、前記Nウエル350上の対応する位置にフォトレジスト層9

00を設け、前記フォトレジスト層900を保護マスクとして、前記不純物を含有しない

ポリシリコン層630にリン等のN型不純物をイオン注入法により導入することにより、

第三のN型ポリシリコン層640を形成することができる。

【0078】

続いて、前記フォトレジスト層900を除去し、図15に示す様に、前記第三のN型ポ

リシリコン層640上に、新たにフォトレジスト層900を形成する。

前記フォトレジスト層900を保護マスクとして、前記Nウエル350上の対応する位

置にある、前記不純物濃度が1.0×1020/cm3未満のポリシリコン層630にホ

ウ素等のP型不純物をイオン注入法により導入することにより、前記P型ポリシリコン層

621を形成することができる。

【0079】

なお、前記第三のN型ポリシリコン層640を形成する際や前記P型ポリシリコン層6

21を形成する際等の場合に、前記イオン注入法によるエネルギーが強いと、それぞれ前

記リン等のN型不純物や前記ホウ素等のP型不純物が前記ポリシリコン層640等に留ま

らず、前記半導体シリコン基板1の表面領域にまで前記リン等のN型不純物や前記ホウ素

等のP型不純物の突き抜けが生じる。

この様な突き抜けが生じると、得られた半導体装置の閾値電圧の変動が生じ、正常に動

作しないという問題が生じる。

従って、前記ポリシリコン層640および前記半導体シリコン基板1表面より上部にあ

る前記ポリシリコン層620の合計の厚みが100nmの場合では、例えばリンの場合で

は10keV以下、ホウ素の場合では5KeV以下のエネルギーにより注入することが好

ましい。

【0080】

次に前記フォトレジスト層900をドライエッチング、アッシング技術等により除去し

、図16に示す様に、PVD法、CVD法等の方法により、導電層700を形成すること

ができる。

なお本実施例2に使用する導電層700の構成は、実施例1の場合と同様である。

【0081】

前記ポリシリコン層620、621および630ならびに前記導電層700を、フォト

レジスト層(図示せず)を保護マスクとして、リソグラフィー技術とドライエッチング、

アッシング技術等とを用いて除去することにより、図17に示す構造を形成することがで

きる。

【0082】

以下、実施例1の場合と同様の操作を実施することにより、図4に示す本発明の実施例

2の構造を得ることができる。

【0083】

なお、図4に示す通り、前記リセスチャネル構造を有するセルトランジスタ205中の

、前記N型不純物を含むポリシリコン層620、前記不純物濃度が1.0×1020/c

m3未満の第二のポリシリコン層630、前記第三のN型不純物を含むポリシリコン層6

40および前記導電層700とからなるゲート電極は、タングステンシリサイド、タング

ステン金属等が埋め込まれているため、配線抵抗が小さいという特徴がある。

ここで、前記リセスチャネル構造を有するセルトランジスタ208の前記N型ポリシリ

コン層620に含まれるN型不純物であるリンの濃度は、1.0×1020〜1.0×1

021/cm3の範囲であった。

【0084】

この様にして得られた半導体装置103は、動作電圧の変動が少なく、正常に動作する

ことから、DRAM(Dynamic Random Access Memory)等の用途に好適に使用することが

できる。

【実施例3】

【0085】

実施例2の場合で得られた、図4に示す半導体装置103のリセスチャネル構造を有す

るセルトランジスタ208のゲート電極を、温度650〜800℃の範囲で加熱処理する

ことにより、前記ゲート電極中の、前記N型不純物を含むポリシリコン層620、前記不

純物濃度が1.0×1020/cm3未満の第二のポリシリコン層630、および前記第

三のN型不純物を含むポリシリコン層640のそれぞれに含まれるリンは拡散し、それぞ

れの領域でリンの濃度を1.0×1020〜1.0×1021/cm3の範囲内で均一化

することができる。

前記温度が650℃未満の場合には、前記半導体シリコン基板1中のリンを活性化させ

ることができず、前記温度が800℃を超える場合には、前記周辺トランジスタ207の

ゲート電極中のP型ポリシリコンに含まれるホウ素等のP型不純物が前記半導体シリコン

基板1中に拡散し、前記半導体装置の正常な動作を妨げる。

【0086】

この様にして得られた半導体装置104(図示せず)は、動作電圧の変動が少なく、正

常に動作することから、DRAM(Dynamic Random Access memory)等の用途に好適に使

用することができる。

【0087】

[比較例1]

実施例1の図5の構造に対し、不純物濃度が1.0×1020/cm3未満のポリシリ

コン層630を設けた後、さらに前記Nウエル350上の対応する部分を除く前記半導体

シリコン基板1の上にフォトレジスト層900を設け、前記フォトレジスト層900を保

護マスクとして、前記Nウエル350上の対応する位置にある、前記不純物濃度が1.0

×1020/cm3未満の第二のポリシリコン層630にホウ素等のP型不純物をイオン

注入法により導入することにより、図18に示す様に前記P型ポリシリコン層621を形

成することができる。

【0088】

次に前記フォトレジスト層900を除去した後、図19に示す様に、前記P型ポリシリ

コン層621の上にフォトレジスト層900を設け、前記フォトレジスト層900を保護

マスクとして、前記ポリシリコン層630に対し、今度はリン等のN型不純物をイオン注

入法により導入することにより、図19に示す様に、前記N型ポリシリコン層620を形

成することができる。

このとき、前記リセス内部の最下部の前記ポリシリコン層630に含まれるリン等のN

型不純物濃度は、1.0×1020/cm3未満であった。

【0089】

次に、前記フォトレジスト900を除去した後、図20に示す様に、PVD法、CVD

法等の方法により、導電層700を形成することができる。

なお本比較例1に使用する導電層700の構成は、実施例1の場合と同様である。

前記ポリシリコン層620、621および630ならびに前記導電層700を、フォト

レジスト層(図示せず)を保護マスクとして、リソグラフィー技術とドライエッチング技

術とを用いて除去することにより、図21に示す構造を形成することができる。

【0090】

以下、実施例1の場合と同様の操作を実施することにより、図22に示す半導体装置を

得ることができる。

【0091】

図23に示す半導体装置は、リセスチャネル構造を有するセルトランジスタのゲート電

極には空乏層が存在するため、動作電圧の変動が大きく、正常に動作しなかった。

【図面の簡単な説明】

【0092】

【図1】従来の半導体装置を示す模式的要部断面図である。

【図2】従来の半導体装置を示す模式的要部断面図である。

【図3】本発明の半導体装置の第一の実施態様を例示する模式的要部断面図である。

【図4】本発明の半導体装置の第二の実施態様を例示する模式的要部断面図である。

【図5】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図6】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図7】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図8】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図9】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図10】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図11】本発明の第一の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図12】本発明の半導体装置を例示する模式的要部断面図である(実施例1)。

【図13】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図14】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図15】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図16】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図17】本発明の第二の実施例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図18】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図19】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図20】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図21】比較例の製造方法の工程を説明するための半導体シリコン基板の模式的要部断面図である。

【図22】比較例の半導体装置を例示する模式的要部断面図である(比較例1)。

【符号の説明】

【0093】

1、1a 半導体シリコン基板

1b N型エピタキシャル層

2 素子間分離構造

3、4、301〜306 ソース・ドレイン領域

5 ゲート絶縁膜

6a、6b、611、612 ゲート電極

7 金属シリサイド

8、9、800、801 絶縁膜

100、101、102、103 半導体装置

200 nMOSFET構造を有するトランジスタ

201、202、204、 207 pMOSFET構造を有するトランジスタ

203、206、209 nMOSFET構造を有するトランジスタ

205、208 リセスチャネル構造を有するセルトランジスタ

310、330 P型低濃度不純物層

320 N型低濃度不純物層

340 Pウエル領域

341 N型ボディ領域

350、360 Nウエル領域

370 P型埋め込み層

500 保護酸化シリコン層

600、620 N型ポリシリコン層

601、610、621 P型ポリシリコン層

630 不純物を含まないポリシリコン層

640 第二のN型ポリシリコン層

700 導電層

900 フォトレジスト層

【特許請求の範囲】

【請求項1】

半導体シリコン基板と、

前記半導体シリコン基板の所定の位置に設けられた素子間分離構造と、

前記素子間分離構造により区画された前記半導体シリコン基板の第一の領域に設けられ

たリセスチャネル構造を有するセルトランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第二の領域に設けられ

たnMOSFET構造を有する周辺トランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第三の領域に設けられ

たpMOSFET構造を有する周辺トランジスタと、

を備えた半導体装置であって、

(A)前記リセスチャネル構造を有するセルトランジスタは、下記(1)〜(4)を有し

、

(1)前記半導体シリコン基板の所定の位置に設けられたリセス

(2)前記リセス内部に接して設けられたゲート絶縁膜

(3)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

を含むゲート電極

(4)前記半導体シリコン基板の表面領域であって前記ゲート電極の両側に設けられた一

対のN型拡散層を含むソース・ドレイン領域

(B)前記第二の領域に設けられたnMOSFET構造を有する周辺トランジスタは、下

記(5)〜(7)を有し、

(5)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(6)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極

(7)前記半導体シリコン基板の表面領域であって、前記ゲート電極の両側に設けられた

一対のN型拡散層を含むソース・ドレイン領域

(C)前記第三の領域に設けられたpMOSFET構造を有する周辺トランジスタは、下

記(8)〜(10)を有し、

(8)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(9)前記ゲート絶縁膜に接して設けられたP型ポリシリコン層および前記P型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極、

(10)前記シリコン基板内部に設けられたNウエルの表面領域であって、前記ゲート電

極の両側に設けられた一対のP型拡散層を含むソース・ドレイン領域

かつ、上記に加えて前記セルトランジスタ中のN型ポリシリコン層に含まれるN型不純

物の濃度は、略一定であることを特徴とする半導体装置。

【請求項2】

前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられ、かつ前記リセス内部および前記リ

セス上部に設けられた導電層、

からなることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

前記N型ポリシリコン層内部に設けられた、不純物濃度が1.0×1020/cm3未

満の第二のポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して、前記リセス内部全てに設けられた前記N型ポリシリコン層

、

および前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記リセスチャネル構造を有するセルトランジスタ中のN型ポリシリコン層に含まれる

N型不純物の濃度は、1.0×1020〜1.0×1021/cm3の範囲であることを

特徴とする請求項1〜4のいずれかに記載の半導体装置。

【請求項6】

(1)半導体シリコン基板の所定の領域に素子間分離構造を形成し、前記半導体シリコン

基板に前記素子間分離構造により区画された第一ないし第三の領域を形成する工程と、

(2)前記素子間分離構造により区画された前記半導体シリコン基板の前記第一の領域に

リセスを形成する工程と、

(3)前記素子間分離構造により区画された前記半導体シリコン基板の前記第三の位置に

Nウエルを形成する工程と、

(4)前記半導体シリコン基板上面および前記リセス内部表面にゲート絶縁膜を形成する

工程と、

(5)前記ゲート絶縁膜のうち、前記半導体シリコン基板上面に該当する部分および前記

リセス内部表面に該当する部分の上面ならびに前記素子間分離構造上面に、不純物濃度が

1.0×1020/cm3未満のポリシリコン層を形成する工程と、

(6)前記第一および第二のそれぞれの所定の位置にある前記不純物濃度が1.0×10

20/cm3未満のポリシリコン層に対し、気相拡散法および固相拡散法からなる群より

選ばれる少なくとも一つの方法によりN型不純物を導入することによりN型ポリシリコン

層を形成する工程と、

(7)前記第三の所定の位置にある前記不純物濃度が1.0×1020/cm3未満のポ

リシリコン層に対し、P型不純物を導入することにより、P型ポリシリコン層を形成する

工程と、

(8)上記(6)および(7)の工程後、前記N型ポリシリコン層およびP型ポリシリコ

ン層の上に、金属シリサイド膜および金属膜からなる群より選ばれる少なくとも一つを形

成する工程と、

(9)エッチング工程により、前記第一および第二の領域に、それぞれN型ポリシリコン

層を含むゲート電極を形成し、かつ前記第三の領域にP型ポリシリコン層を含むゲート電

極を形成する工程と、

(10)前記第一および第二の領域にそれぞれ形成された前記ゲート電極の両側の半導体

シリコン基板表面領域に対し、N型不純物を注入することにより、前記第一の領域にリセ

スチャネル構造を有するセルトランジスタおよび前記第二の領域にnMOSFET構造を

形成する工程と、

(11)前記第三の領域に形成された前記ゲート電極の両側の半導体シリコン基板表面領

域に対し、P型不純物を注入することにより、前記第三の領域にpMOSFET構造を形

成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記工程(6)の前記N型ポリシリコン層を形成する方法は、PH3ガスを用いた気相

拡散法およびリン含有ガラスを用いた固相拡散法からなる群より選ばれる少なくとも一つ

であることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項1】

半導体シリコン基板と、

前記半導体シリコン基板の所定の位置に設けられた素子間分離構造と、

前記素子間分離構造により区画された前記半導体シリコン基板の第一の領域に設けられ

たリセスチャネル構造を有するセルトランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第二の領域に設けられ

たnMOSFET構造を有する周辺トランジスタと、

前記素子間分離構造により区画された前記半導体シリコン基板の第三の領域に設けられ

たpMOSFET構造を有する周辺トランジスタと、

を備えた半導体装置であって、

(A)前記リセスチャネル構造を有するセルトランジスタは、下記(1)〜(4)を有し

、

(1)前記半導体シリコン基板の所定の位置に設けられたリセス

(2)前記リセス内部に接して設けられたゲート絶縁膜

(3)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

を含むゲート電極

(4)前記半導体シリコン基板の表面領域であって前記ゲート電極の両側に設けられた一

対のN型拡散層を含むソース・ドレイン領域

(B)前記第二の領域に設けられたnMOSFET構造を有する周辺トランジスタは、下

記(5)〜(7)を有し、

(5)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(6)前記ゲート絶縁膜に接して設けられたN型ポリシリコン層および前記N型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極

(7)前記半導体シリコン基板の表面領域であって、前記ゲート電極の両側に設けられた

一対のN型拡散層を含むソース・ドレイン領域

(C)前記第三の領域に設けられたpMOSFET構造を有する周辺トランジスタは、下

記(8)〜(10)を有し、

(8)前記半導体シリコン基板上の所定の位置に設けられたゲート絶縁膜

(9)前記ゲート絶縁膜に接して設けられたP型ポリシリコン層および前記P型ポリシリ

コン層に接して設けられた導電層、

からなるゲート電極、

(10)前記シリコン基板内部に設けられたNウエルの表面領域であって、前記ゲート電

極の両側に設けられた一対のP型拡散層を含むソース・ドレイン領域

かつ、上記に加えて前記セルトランジスタ中のN型ポリシリコン層に含まれるN型不純

物の濃度は、略一定であることを特徴とする半導体装置。

【請求項2】

前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられ、かつ前記リセス内部および前記リ

セス上部に設けられた導電層、

からなることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して設けられた前記N型ポリシリコン層、

前記N型ポリシリコン層内部に設けられた、不純物濃度が1.0×1020/cm3未

満の第二のポリシリコン層、

ならびに前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記リセスチャネル構造を有するセルトランジスタに含まれるゲート電極は、

前記ゲート絶縁膜に接して、前記リセス内部全てに設けられた前記N型ポリシリコン層

、

および前記N型ポリシリコン層に接して設けられた導電層、

からなることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記リセスチャネル構造を有するセルトランジスタ中のN型ポリシリコン層に含まれる

N型不純物の濃度は、1.0×1020〜1.0×1021/cm3の範囲であることを

特徴とする請求項1〜4のいずれかに記載の半導体装置。

【請求項6】

(1)半導体シリコン基板の所定の領域に素子間分離構造を形成し、前記半導体シリコン

基板に前記素子間分離構造により区画された第一ないし第三の領域を形成する工程と、

(2)前記素子間分離構造により区画された前記半導体シリコン基板の前記第一の領域に

リセスを形成する工程と、

(3)前記素子間分離構造により区画された前記半導体シリコン基板の前記第三の位置に

Nウエルを形成する工程と、

(4)前記半導体シリコン基板上面および前記リセス内部表面にゲート絶縁膜を形成する

工程と、

(5)前記ゲート絶縁膜のうち、前記半導体シリコン基板上面に該当する部分および前記

リセス内部表面に該当する部分の上面ならびに前記素子間分離構造上面に、不純物濃度が

1.0×1020/cm3未満のポリシリコン層を形成する工程と、

(6)前記第一および第二のそれぞれの所定の位置にある前記不純物濃度が1.0×10

20/cm3未満のポリシリコン層に対し、気相拡散法および固相拡散法からなる群より

選ばれる少なくとも一つの方法によりN型不純物を導入することによりN型ポリシリコン

層を形成する工程と、

(7)前記第三の所定の位置にある前記不純物濃度が1.0×1020/cm3未満のポ

リシリコン層に対し、P型不純物を導入することにより、P型ポリシリコン層を形成する

工程と、

(8)上記(6)および(7)の工程後、前記N型ポリシリコン層およびP型ポリシリコ

ン層の上に、金属シリサイド膜および金属膜からなる群より選ばれる少なくとも一つを形

成する工程と、

(9)エッチング工程により、前記第一および第二の領域に、それぞれN型ポリシリコン

層を含むゲート電極を形成し、かつ前記第三の領域にP型ポリシリコン層を含むゲート電

極を形成する工程と、

(10)前記第一および第二の領域にそれぞれ形成された前記ゲート電極の両側の半導体

シリコン基板表面領域に対し、N型不純物を注入することにより、前記第一の領域にリセ

スチャネル構造を有するセルトランジスタおよび前記第二の領域にnMOSFET構造を

形成する工程と、

(11)前記第三の領域に形成された前記ゲート電極の両側の半導体シリコン基板表面領

域に対し、P型不純物を注入することにより、前記第三の領域にpMOSFET構造を形

成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記工程(6)の前記N型ポリシリコン層を形成する方法は、PH3ガスを用いた気相

拡散法およびリン含有ガラスを用いた固相拡散法からなる群より選ばれる少なくとも一つ

であることを特徴とする請求項6に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2006−332211(P2006−332211A)

【公開日】平成18年12月7日(2006.12.7)

【国際特許分類】

【出願番号】特願2005−151641(P2005−151641)

【出願日】平成17年5月24日(2005.5.24)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成18年12月7日(2006.12.7)

【国際特許分類】

【出願日】平成17年5月24日(2005.5.24)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]