リフトオフ工程技術を用いたインターフェロメトリック変調器の製造方法

【課題】リフトオフ工程技術を用いたインターフェロメトリック変調器の製造方法

【解決手段】本開示の実施形態は、リフトオフ工程技術を用いてインターフェロメトリックデバイスを製造する方法を含む。光学的スタックまたは屈曲層などのインターフェロメトリック変調器の種々の層の製造においてリフトオフ工程を用いることは、各層に関連する複数の材料に関する個々の化学現象を有利に避けることができる。さらに、リフトオフ工程を使用することは、インターフェロメトリック変調器の製造に利用される材料及び施設の選択を増やすことを可能にする。

【解決手段】本開示の実施形態は、リフトオフ工程技術を用いてインターフェロメトリックデバイスを製造する方法を含む。光学的スタックまたは屈曲層などのインターフェロメトリック変調器の種々の層の製造においてリフトオフ工程を用いることは、各層に関連する複数の材料に関する個々の化学現象を有利に避けることができる。さらに、リフトオフ工程を使用することは、インターフェロメトリック変調器の製造に利用される材料及び施設の選択を増やすことを可能にする。

【発明の詳細な説明】

【技術分野】

【0001】

背景

発明の分野

本発明の分野は、インターフェロメトリックデバイスの製造の分野を含む、微小電気機械システム(MEMS)に関する。一実施形態において、本発明は、インターフェロメトリックデバイスの製造に用いることが可能な材料及び施設の数を拡張するのに用いられる製造工程技術に関する。

【背景技術】

【0002】

関連技術の記載

微小電気機械システム(MEMS)は、微少機械要素、アクチュエータ及び電子機器を含む。微少機械要素は、堆積、エッチング、及び又は、基板及び/又は堆積材料層の部分をエッチング除去し、あるいは、層を加えて電気素子及び電気機械素子を形成する他のミクロ機械加工プロセスを用いて形成することができる。MEMSデバイスの1つのタイプは、インターフェロメトリック変調器と称される。本明細書中で用いる場合、インターフェロメトリック変調器又はインターフェロメトリック光変調器とは、光学的干渉の原理を用いて光を選択的に吸収し及び/又は反射するデバイスを指す。ある実施形態において、インターフェロメトリック変調器は、一方又は両方が、この全体又は一部が透過性及び/又は反射性であってもよく、かつ適当な電気信号を印加したときに相対運動が可能な、1組の導電性プレートを備えてもよい。特定の実施形態において、一方のプレートは、基板上に堆積された固定層を備えてもよく、また他方のプレートは、この固定層からエアギャップだけ離れている金属膜を備えてもよい。本明細書に詳細に記載されているように、一方のプレートの他方に対する位置は、このインターフェロメトリック変調器に入射する光の光学的干渉を変えることができる。このようなデバイスは、広範囲の用途を有しており、これらのタイプのデバイスの特徴を利用し及び/又は変更することが当分野において有益であるため、現在ある製品を改良する際、及びまだ開発されていない新しい製品を考案する際に、これらの特徴を活かすことができる。

【発明の開示】

【課題を解決するための手段】

【0003】

ここに記述されるシステム、方法そしてデバイスはそれぞれいくつかの側面を備えているが、どの1つたりとも単にその望ましい属性を請け負うものではない。本発明の範囲を制限することなしに、より顕著な特徴について簡単に説明する。この議論を考慮した後に、特に“好ましい実施形態の詳細な説明”と称する部分を読めば、ここに記載した種々の実施形態がいかにして他の方法およびディスプレイ装置と比較して利点を提供するかを理解するであろう。

【0004】

一実施例は、インターフェロメトリック変調器の製造方法を提供するものであって、少なくとも第1のパターニング製造工程を用いて透明な基板上に光学的スタック(積層体)を形成することと、前記基板上に支持体構造を形成することとを含む。この実施形態において、前記方法はさらに、少なくとも第2のパターニング製造工程を用いて前記光学的スタック及び支持体構造上に上部ミラー層を形成することを含む。ここで、前記光学的スタック、前記支持体構造、前記上部ミラー層の少なくとも1つの表面に空洞部が形成され、前記上部ミラー層の前記空洞部への一部の移動は、前記支持体の表面から認識される光学特性を制御可能かつ予測可能な方法で変化させ、前記第1及び第2の製造工程の少なくとも1つはリフトオフ工程を具備する。他の実施形態は、そのような方法によって製造されたインターフェロメトリック変調器を提供する。

【0005】

他の実施形態は、インターフェロメトリック変調器の製造方法を提供するものであって、基板上にリフトオフステンシルを形成することと、前記リフトオフステンシルと前記基板上に第1の材料層を堆積することとを含む。この実施形態において、前記方法はさらに、前記第1の材料層上に第2の材料層を堆積することと、前記リフトオフステンシルを除去して、前記第1の材料層とその上に形成された前記第2の材料層とからなるパターニングされた領域を形成することとを含む。他の実施形態は、そのような方法によって製造されたインターフェロメトリック変調器を提供する。

【0006】

他の実施形態は、インターフェロメトリック変調器のアレイの製造方法を提供するものであって、リフトオフステンシルを用いて基板上に複数の正にパターニングされた光学的スタックと、複数の負にパターニングされたポスト領域とを形成することと、前記負にパターニングされたポスト領域内に複数のポスト構造を形成することとを含む。他の実施形態はそのような方法によって製造されたインターフェロメトリック変調器のアレイを提供する。

【0007】

他の実施形態は、ディスプレイ装置の製造方法を提供するものであって、第1のミラー層を堆積することと、前記第1のミラー層上に犠牲層を堆積することと、前記犠牲層上にリフトオフステンシルを形成することとを含む。この実施形態において、前記方法はさらに、前記リフトオフステンシル上に第2のミラー層を堆積することと、前記リフトオフステンシルを除去することによって、前記第2のミラー層のパターニングされた領域を形成して前記犠牲層の一部を露出することとを含む。他の実施形態は、そのような方法によって製造されたディスプレイ装置を提供する。

【0008】

他の実施形態は、上記の方法によって製造されるインターフェロメトリック変調器のアレイを含むディスプレイパネルを提供する。他の実施形態は、そのようなディスプレイパネルと、前記ディスプレイパネルと電気通信可能であって、イメージデータを処理するように構成されたプロセッサと、前記プロセッサと電気通信可能なメモリ装置とを含むディスプレイ装置を提供する。

【発明を実施するための最良の形態】

【0009】

以下の詳細な説明は、本発明の特定の実施形態を対象に記載している。しかしながら、複数の異なる方法によって実現可能である。ここでの説明では明細書全体にわたって図面を参照して説明がなされ、同一の部分には同一の参照符号が付与される。本実施形態は、動いていようと(例えば、ビデオ)、静止していようと(例えば、静止イメージ)、及びテキストであろうと写真であろうと、イメージを表示するように構成されているいかなるデバイスでも実施することができる。より具体的には、本実施形態を、限定するものではないが、移動電話、無線装置、PDA(personal data assistants)、ハンドヘルドコンピュータ又はポータブルコンピュータ、GPSレシーバ/ナビゲータ、カメラ、MP3プレーヤ、カムコーダー、ゲームコンソール、腕時計、時計、計算機、テレビモニタ、フラットパネルディスプレイ、コンピュータモニタ、オートディスプレイ(例えば、走行距離計等)、コックピット制御部及び/又はディスプレイ、カメラビューのディスプレイ(例えば、自動車のリアビューカメラのディスプレイ)、電子写真、電子掲示板又は電子サイン、プロジェクタ、建築構造物、パッケージング及び審美的構造(例えば、宝石に関するイメージの表示)等の様々な電子デバイスで、又は該様々な電子デバイスに付随して実施することができることが意図されている。また、本明細書中で説明したのと同様の構造のMEMSデバイスは、電子スイッチングデバイスにおける等の非表示用途で用いることもできる。

【0010】

好ましい実施形態は、インターフェロメトリック変調器の製造にリフトオフ工程方法を適用することを含む。

【0011】

インターフェロメトリックMEMSディスプレイ要素を備える1つのインターフェロメトリック変調ディスプレイの実施形態を図1に示す。これらのデバイスにおいて、画素は、明るい状態又は暗い状態のいずれかにある。この明るい(「オン」又は「オープン」)状態において、このディスプレイ要素は、入射可視光の大部分をユーザに対して反射させる。この暗い(「オフ」又は「クローズド」)状態の場合、このディスプレイ要素は、わずかな入射可視光を該ユーザに対して反射させる。実施形態によっては、これらの「オン」及び「オフ」状態の光反射特性は、逆にしてもよい。MEMS画素は、選択された色で主に反射するように構成することができ、黒及び白に加えてカラー表示を可能にする。

【0012】

図1は、ビジュアルディスプレイの一連の画素における隣接する2つの画素を示す等角図であり、各画素は、MEMSインターフェロメトリック変調器を備える。いくつかの実施形態においては、インターフェロメトリック変調ディスプレイは、これらのインターフェロメトリック変調器の行/列アレイを備える。各インターフェロメトリック変調器は、互いに可変かつ制御可能な距離をおいて配置され、少なくとも1つの可変寸法を有する光空洞部共振器を形成する1対の反射層を含む。一実施形態において、これらの反射層の一方は、2つの位置の間で移動することができる。本明細書において開放位置と称する第1の位置においては、この移動可能な反射層は、固定された部分的反射層から比較的大きな距離をおいて配置されている。本明細書において作動位置と称する第2の位置においては、この移動可能な反射層は、この部分的反射層により近接して配置されている。これらの2つの層から反射する入射光は、この移動可能な反射層の位置により、建設的に又は破壊的に干渉し、各画素に対して全体的反射状態又は非反射状態のいずれかをもたらす。

【0013】

図1の画素アレイの図示した部分は、隣接する2つのインターフェロメトリック変調器12a及び12bを含む。左側のインターフェロメトリック変調器12aにおいては、移動可能な高反射層14aが、部分的反射層を含む光学的スタック16aから所定の距離の開放位置に示されている。右側のインターフェロメトリック変調器12bにおいては、移動可能な反射層14bが、光学的スタック16bに隣接する作動位置に示されている。

【0014】

本明細書で言及されているような光学的スタック16a、16b(まとめて光学的スタック16と称する)は、典型的には、インジウムスズ酸化物(indium tin oxide;ITO)等の電子層、クロム等の部分的反射層、及び透明誘電体を含むことができるいくつかの融合層から構成される。このため、光学的スタック16は導電性であり、部分的に透明であり、かつ部分的に反射性であり、例えば、これらの層の1つ以上を透明基板20上に堆積させることにより製造することができる。いくつかの実施形態において、これらの層は、平行なストリップにパターン化され、また、以下にさらに説明するように、ディスプレイ装置に行電極を形成することができる。移動可能な反射層14a、14bは、ポスト18の上部に堆積させた(行電極16a、16bと直交する)堆積した1枚の金属層及び複数の金属層と、ポスト18の間に堆積させた介在犠牲材料とからなる一連の平行なストリップとして形成することができる。この犠牲材料がエッチング除去されると、移動可能な反射層14a、14bは、画定されたエアギャップ19だけ、光学的スタック16a、16bから分離される。アルミニウム等の高導電性及び反射性の材料は、反射層14に用いることができ、また、これらのストリップは、ディスプレイ装置内に列電極を形成してもよい。

【0015】

電圧を印加しない場合、空洞部19は、図1における画素12aによって示すように、移動可能な反射層14aが機械的に開放された状態で、移動可能な反射層14aと光学的スタック16aとの間に存続する。しかし、選択した行及び列に対して電位差を加えると、対応する画素におけるこの行及び列電極の交差部に形成されたキャパシタが充電されて、静電力がこれらの電極を一緒に引っ張る。この電圧が充分高い場合、移動可能な反射層14は変形し、かつ光学的スタック16に向かって押し込まれる。光学的スタック16内の(この図面には示されていない)誘電体層は、短絡を防止することができ、また、図1の右側の画素12bに示すように、層14と層16との間の隔離距離を制御することができる。この作用は、印加された電位差の極性に関係なく同じである。このように、反射性対非反射性の画素状態を制御することができる行/列動作は、従来のLCD及び他の表示技術で用いられるものと多くの点で似ている。

【0016】

図2〜図5Bは、表示用途において、インターフェロメトリック変調器のアレイを用いる1つの例示的なプロセス及びシステムを示す。

【0017】

図2は、本発明の態様を組み込んでもよい電子装置の一実施形態を示すシステムブロック図である。例示的な実施形態において、この電子装置は、ARM、Pentium(登録商標)、Pentium II(登録商標)、Pentium III(登録商標)、Pentium IV(登録商標)、Pentium Pro(登録商標)、8051、MIPS(登録商標)、Power PC(登録商標)、ALPHA(登録商標)等のどのような汎用の単一又はマルチチップマイクロプロセッサ、あるいは、ディジタル信号プロセッサ、マイクロコントローラ又はプログラマブルゲートアレイ等のどのような専用マイクロプロセッサであってもよいプロセッサ21を含む。従来技術と同様に、プロセッサ21は、1つ以上のソフトウェアモジュールを実行するように構成することができる。このプロセッサは、オペレーティングシステムを実行するのに加えて、ウェブブラウザ、電話アプリケーション、電子メールプログラム、又は他のソフトウェアアプリケーションを含む1つ以上のソフトウェアアプリケーションを実行するように構成することができる。

【0018】

一実施形態においては、プロセッサ21も、アレイドライバ22と通信するように構成されている。一実施形態において、アレイドライバ22は、信号を表示アレイ又はパネル30へ供給する行ドライバ回路24及び列ドライバ回路26を含む。図1に示すこのアレイの断面は、図2の線1−1によって示されている。MEMSインターフェロメトリック変調器の場合、この行/列作動プロトコルは、図3に示すそれらのデバイスのヒステリシス特性を利用してもよい。例えば、移動可能な層を、上記解放状態から作動状態に変形させるために、10ボルトの電位差を要求してもよい。しかし、この電圧がこの値から低下した場合、この移動可能な層は、この電圧が10ボルト以下に低下したときにその状態を維持する。図3の例示的な実施形態において、この移動可能な層は、この電圧が2ボルト以下に低下するまで、完全に解放されない。それに伴って、図3に示した実施例には、約3〜7Vの電圧範囲があり、この場合、その範囲内でこのデバイスが、この解放状態又は作動状態のいずれかで安定している印加電圧のウィンドウが存在する。本明細書では、これを「ヒステリシスウィンドウ」又は「安定ウィンドウ」と称する。図3のヒステリシス特性を有するディスプレイアレイの場合、上記行/列作動プロトコルは、行ストロービングの間、作動されるべきこのストローブされた行の画素が、約10ボルトの電圧差にさらされ、かつ解放されるべき画素が、0ボルトに近い電圧差にさらされるように設計することができる。このストローブの後、これらの画素は、どのような状態においても、行ストローブのままであるように、約5ボルトの定常電圧差にさらされる。書き込まれた後、各画素は、この実施例において3〜7Vの「安定ウィンドウ」内の電位差を参照する。この特徴は、図1に示す画素デザインを、作動又は解放先在状態のいずれかにおける同じ印加電圧条件の下で安定させる。上記インターフェロメトリック変調器の各画素は、作動状態であろうと解放状態であろうと、本質的に、固定された反射層と移動可能な層とによって形成されたキャパシタであるため、この安定状態は、ほとんど電力消失を伴わずに、このヒステリシスウィンドウ内の電圧で保持することができる。印加電位が固定されている場合、本質的に、電流はこの画素へは流れない。

【0019】

典型的な用途において、ディスプレイフレームは、第1の行における作動画素の所望のセットに従って、列電極のセットをアサートすることによって生成することができる。そして、行パルスは、行1電極に印加され、このアサートされた列ラインに対応する画素が作動される。次に、列電極のこのアサートされたセットは、第2の行の作動画素の所望のセットに対応させるため変化する。次いで、パルスが行2電極に印加され、このアサートされた列電極に従って、行2の適当な画素が作動される。行1画素は、行2パルスによる影響を受けず、行1パルスの間に設定された状態のままである。これは、フレームを生成するために、一連の行に対して繰り返すことができる。一般に、これらのフレームは、毎秒所望数のフレームにおいて、このプロセスを連続的に繰り返すことにより、新たな表示データに伴ってリフレッシュ及び/又は更新される。画素アレイの行及び列電極を駆動して表示フレームを生成する幅広いプロトコルもまた周知であり、本発明と共に用いることができる。

【0020】

図4、図5A及び図5Bは、図2の3×3アレイに表示フレームを生成する1つの可能な作動プロトコルを示す。図4は、図3のヒステリシス曲線を示す画素に用いることができる列及び行電圧レベルの可能なセットを示す。図4の実施形態において、画素を作動させることは、適当な行を−Vbiasに、適当な列を+ΔVに設定することを含み、これらはそれぞれ、−5V及び+5Vに相当する。画素を解放させることは、適当な行を+Vbiasに、適当な列を同じく+ΔVに設定して、この画素の両端に0Vの電位差を生じることにより実現される。行電圧が0Vに保持される行においては、これらの画素は、この列が+Vbias又は−Vbiasであることに関係なく、これらの画素が元々どのような状態にあろうとも安定している。図4にも示されているように、上述したもの以外の反対極性の電圧を用いることができること、例えば、画素を作動させることが、適当な列を+Vbiasに、及び適当な行を−ΔVに設定することを含むことができることは、正しく理解される。この実施形態において、画素を解放することは、適当な行を−Vbiasに、及び適当な行を同じく−ΔVに設定して、この画素の両端に0Vの電位差を生じさせることによって実現される。

【0021】

図5Bは、作動画素が非反射性である、図5Aに示す表示構成を生じる、図2の3×3アレイに印加される一連の行及び列信号を示すタイミング図である。図5Aに示すフレームに書き込む前に、画素は、どのような状態も可能であり、この実施例においては、全ての行が0Vであり、全ての列が+5Vである。これらの印加電圧によって、全ての画素は、これらの現在の作動又は解放状態において安定している。

【0022】

図5Aのフレームにおいては、画素(1,1)、(1,2)、(2,2)、(3,2)及び(3,3)が作動している。これを実現するため、行1のための「ラインタイム」の間には、列1及び列2が−5Vに設定され、かつ列3が+5Vに設定される。このことは、全ての画素が3〜7Vの安定ウィンドウに入ったままであるため、どの画素の状態も変えない。そして、行1は、0から5Vに上昇した後0に戻るパルスによってストローブされる。このことは、(1,1)及び(1,2)画素を作動させ、(1,3)画素を解放させる。このアレイ内の他の画素は影響を受けない。行2を要望通りに設定するため、列2は−5Vに設定され、列1及び列3は+5Vに設定される。次いで、行2に印加される同じストローブが画素(2,2)を作動させ、かつ画素(2,1)及び(2,3)を解放させる。ここでも、このアレイの他の画素は影響を受けない。行3は、列2及び列3を−5Vに、及び列1を+5Vに設定することにより、同様に設定される。行3のストローブは、行3の画素を図5Aに示すように設定する。このフレームを書き込んだ後、この行電位は0であり、この列電位は、+5又は−5Vのいずれかのままとすることができ、上記ディスプレイは、図5Aの構成において安定している。数十又は数百の行及び列のアレイに対して同じ処理手順を用いることができることは正しく認識される。また、行及び列の作動を実行するのに用いる電圧のタイミング、シーケンス及びレベルを、上述した包括的な原理の範囲内で大きく変化させることができること、及び上記の実施例が単に例示であり、どのような作動電圧方法も本明細書に記載したシステム及び方法と共に用いることができることは正しく認識される。

【0023】

図6A及び図6Bは、ディスプレイ装置40の実施形態を示すシステムブロック図である。ディスプレイ装置40は、例えば、携帯電話又は移動電話とすることができる。しかし、ディスプレイ装置40又は、そのわずかな変形例の同じ構成要素も、テレビ及びポータブルメディアプレーヤ等の様々なタイプのディスプレイ装置の例証である。

【0024】

ディスプレイ装置40は、ハウジング41と、ディスプレイ30と、アンテナ43と、スピーカ44と、入力装置48と、マイクロフォン46とを含む。ハウジング41は、一般に、射出成形及び真空成形を含む、当業者には周知の種々の製造プロセスのうちのいずれかによって形成されている。また、ハウジング41は、限定するものではないが、プラスチック、金属、ガラス、ゴム及びセラミック又はこれらの組み合わせを含む様々な材料のうちのいずれかから形成することができる。一実施形態において、ハウジング41は、異なる色の、又は、異なるロゴ、写真又はシンボルからなる他の取外し可能な部分と交換することができる取外し可能な部分(図示せず)を含む。

【0025】

例示的なディスプレイ装置40のディスプレイ30は、本明細書で説明したようなバイステイブルディスプレイを含む様々なディスプレイのうちのいずれかとすることができる。他の実施形態においては、ディスプレイ30は、上述したように、プラズマ、EL、OLED、STN LCD及びTFT LCD等のフラットパネルディスプレイ、あるいは、当業者には周知のCRT又は他のブラウン管装置等の非フラットパネルディスプレイを含む。しかし、本実施形態を説明するため、ディスプレイ30は、本明細書に記載したように、インターフェロメトリック変調ディスプレイを含む。

【0026】

例示的なディスプレイ装置40の一実施形態の構成要素を図6Bに概略的に示す。図示した例示的なディスプレイ装置40は、ハウジング41を含み、またこのハウジングの中に少なくとも部分的に閉じ込められた追加的な構成要素を含むことができる。例えば、一実施形態において、例示的なディスプレイ装置40は、トランシーバ47に結合されているアンテナ43を含むネットワークインタフェース27を含む。トランシーバ47はプロセッサ21に接続されており、このプロセッサは、調整ハードウェア52に接続されている。調整ハードウェア52は、信号を調整する(例えば、信号をフィルタリングする)ように構成してもよい。調整ハードウェア52は、スピーカ45及びマイクロフォン46に接続されている。また、プロセッサ21は、入力装置48及びドライバコントローラ29にも接続されている。ドライバコントローラ29は、フレームバッファ28及びアレイドライバ22に結合されており、このアレイドライバは、ディスプレイアレイ30にも結合されている。電源50は、特定の例示的なディスプレイ装置40デザインに要求される全ての構成要素に電力を供給する。

【0027】

ネットワークインタフェース27は、例示的なディスプレイ装置40が、ネットワークを介して1つ以上のデバイスと通信することができるように、アンテナ43及びトランシーバ47を含む。一実施形態において、ネットワークインタフェース27は、プロセッサ21の要求を軽減するためのいくつかの処理能力も有してもよい。アンテナ43は、当業者は既知である、信号を送受信する何らかのアンテナである。一実施形態において、このアンテナは、IEEE802.11(a)、(b)又は(g)を含むIEEE802.11規格に従ってRF信号を送受信する。別の実施形態においては、このアンテナは、ブルートゥース規格に従ってRF信号を送受信する。携帯電話の場合、このアンテナは、CDMA、GSM、AMPS、又は、無線セル電話ネットワーク内で通信するのに用いられる他の公知の信号を受信するように設計されている。トランシーバ47は、アンテナ43から受け取った信号をプロセッサ21によって受け取り、かつこのプロセッサによってさらに処理できるようにこの信号を前処理する。また、トランシーバ47は、プロセッサ21から受け取った信号を、アンテナ43を介して例示的なディスプレイ装置40から送信できるように、この信号を処理する。

【0028】

代替の実施形態においては、トランシーバ47は、レシーバと置き換えることができる。また別の代替の実施形態においては、ネットワークインタフェース27は、イメージソースと置き換えることができ、このイメージソースは、プロセッサ21へ送るべきイメージデータを格納又は生成することができる。例えば、このイメージソースは、イメージデータを含むDVD(digital video disc)又はハードディスクドライブ、あるいは、イメージデータを生成するソフトウェアモジュールとすることができる。

【0029】

プロセッサ21は、一般に、例示的なディスプレイ装置40の全体の動作を制御する。プロセッサ21は、ネットワークインタフェース27又はイメージソースからの圧縮されたイメージデータ等のデータを受け取り、このデータを処理して生イメージデータに、又は生イメージデータに容易に処理されるフォーマットにする。そして、プロセッサ21は、この処理されたデータをドライバコントローラ29に、又は格納のためにフレームバッファ28へ送る。生データとは、典型的には、イメージ内の各位置におけるイメージ特性を識別する情報を指す。例えば、このようなイメージ特性は、色、飽和及びグレースケールレベルを含むことができる。

【0030】

一実施形態において、プロセッサ21は、マイクロコントローラ、CPU、又は、例示的なディスプレイ装置40の動作を制御する論理ユニットを含む。調整ハードウェア52は、一般に、信号をスピーカ45へ転送し、かつマイクロフォン46から信号を受け取る増幅器及びフィルタを含む。調整ハードウェア52は、例示的なディスプレイ装置40内の個別の構成要素であってもよく、あるいは、プロセッサ21又は他の構成要素に組み込んでもよい。

【0031】

ドライバコントローラ29は、プロセッサ21によって生成された生イメージデータを、プロセッサ21から直接、又はフレームバッファ28から取得して、アレイドライバ22への高速転送に適した生イメージデータに再フォーマット化する。具体的には、ドライバコントローラ29は、表示アレイ30の全域を走査するのに適した時間順序を有するように、この生イメージデータを、ラスタ状フォーマットを有するデータフローに再フォーマット化する。そして、ドライバコントローラ29は、このフォーマット化した情報をアレイドライバ22へ送る。LCDコントローラ等のドライバコントローラ29は、独立型集積回路(IC)としてシステムプロセッサ21と関連付けられる場合があるが、このようなコントローラは、多くの方法で実施することができる。このコントローラは、ハードウェアとしてプロセッサ21に、ソフトウェアとしてプロセッサ21に埋め込んでもよく、又は、ハードウェア内で、アレイドライバ22と完全に一体化してもよい。

【0032】

典型的には、アレイドライバ22は、ドライバコントローラ29から上記フォーマット化された情報を受け取って、このビデオデータを、上記ディスプレイの画素のx−yマトリックスからくる何百及び時には何千ものリードに毎秒多数回印加される波形の並行セットに再フォーマット化する。

【0033】

一実施形態において、ドライバコントローラ29、アレイドライバ22及び表示アレイ30は、本明細書に記載したいずれかの種類のディスプレイに適している。例えば、一実施形態において、ドライバコントローラ29は、従来のディスプレイコントローラ又はバイステイブルディスプレイコントローラ(例えば、インターフェロメトリック変調コントローラ)である。別の実施形態においては、アレイドライバ22は、従来のドライバ又はバイステイブルディスプレイドライバ(例えば、インターフェロメトリック変調ディスプレイ)である。一実施形態において、ドライバコントローラ29は、アレイドライバ22と一体化されている。このような実施形態は、携帯電話、時計及び他の小面積ディスプレイ等の高度に一体化されたシステムにおいては共通である。また別の実施形態においては、表示アレイ30は、典型的な表示アレイ又はバイステイブルディスプレイアレイ(例えば、インターフェロメトリック変調器のアレイを含むディスプレイ)である。

【0034】

入力装置48は、ユーザが例示的なディスプレイ装置40の動作を制御できるようにする。一実施形態において、入力装置48は、QWERTYキーボード又は電話キーパッド、ボタン、スイッチ、タッチスクリーン、圧力又は熱センシティブ膜等のキーパッドを含む。一実施形態において、マイクロフォン46は、例示的なディスプレイ装置40のための入力装置である。マイクロフォン46を、この装置にデータを入力するのに使用する場合、例示的なディスプレイ装置40の動作を制御するために、ユーザがボイスコマンドを与えてもよい。

【0035】

電源50は、公知の様々なエネルギストレージデバイスを含むことができる。例えば、一実施形態において、電源50は、ニッケル−カドミウム電池又はリチウムイオン電池等の充電可能な電池である。別の実施形態において、電源50は、回復可能なエネルギ源、コンデンサ、又は、プラスチックソーラーセル及びソーラーセルペイントを含む太陽電池である。別の実施形態において、電源50は、壁コンセントから電力を受け取るように構成される。

【0036】

いくつかの実施においては、制御プログラム性は、上述したように、電子表示システムのいくつかの箇所に配置することができるドライバコントローラに存する。制御プログラム性は、アレイドライバ22に存する場合もある。当業者は、上述した最適化を、多数のハードウェア及び/又はソフトウェア構成要素のどれでも、及び様々な構成で実施することができることを正しく認識する。

【0037】

上記した原理に従って動作するインターフェロメトリック変調器の構成の詳細は種々の実施形態が考えられる。例えば、図7A−7Eは、可動反射層14及びその支持構造についての5つの異なる実施形態を示している。図7Aは、図1の実施形態の断面図であり、一片の金属材料14が垂直に延在する支持体18上に堆積されている。図7Bでは、可動反射層14は角部のみがテザー32を介して支持体に接続されている。図7Cでは、可動反射層14は、弾性をもつ金属からなる変形可能層34から吊り下げられている。変形可能層34は直接あるいは間接的に変形可能層34の周囲で基板20に接続する。この接続を以下では支持ポストと呼ぶ。図7Dに示す実施形態は、変形可能層34が設けられている支持ポストプラグ42を有する。可動反射層14は図7A−7Cに示すように、空洞部上に吊り下げられた状態を維持するが、変形可能層34は、変形可能層34と光学的スタック16との間の穴を満たすことによって支持ポストを形成しない。支持ポストは、支持ポストプラグ42を形成するのに用いられる平坦化(planarization)材料で形成されている。図7Eに示される実施形態は、図7Dに示す実施形態に基づいているが、図7A−7Cに示される実施形態の1つあるいは図示せぬ他の実施形態にも適用することが可能である。図7Eに示す実施形態において、バス構造44を形成するために、金属または他の導電材料からなる他の層が用いられる。この構成は、インターフェロメトリック変調器の背部に沿った信号経路が可能になるので、基板20上に形成しなければならない多数の電極を除去することが可能になる。

【0038】

図7に示す実施形態において、インターフェロメトリック変調器は、イメージが透明基板20の前面から見える直接的視認デバイスとして機能する。この前面は、変調器が配置される面に対向する。これらの実施形態において、反射層14は、基板20に対向する反射層の面に関して、変形可能層34を含む、インターフェロメトリック変調器の一部を光学的に遮蔽する。これによって、遮蔽領域を構成するとともにイメージ品質に悪影響を与えることなしに動作させることが可能となる。このような遮蔽により図7Eに示すバス構造44が可能となり、アドレシング及び該アドレシングに従った移動などの、変調器の電気機械的特性から変調器の光学特性を分離する能力を提供する。この分離可能な変調器アーキテクチャは、変調器の電気機械的側面と光学的側面に用いられる構造上の設計及び材料を選択するとともに、互いに独立して機能することを可能にする。さらに、図7C−7Eに示す実施形態は、変形可能層34によって実行される、反射層14の光学特性の機械的特性からの分離から得られるさらなる利点を有する。このことは、反射層14に用いられる構造設計と材料とを光学特性に関して最適化するとともに、変形可能層34に用いられる構造設計と材料とを所望の機械特性に関して最適化することを可能にする。

【0039】

ここで、(インターフェロメトリック変調器12a及び12bなどの)インターフェロメトリック変調器は概して光学装置であるが、当業界では、その製造工程において、一般的な半導体製造技術を用いる。すなわち、ある所望の金属あるいは他の層は、多くの材料除去技術に対して“異種”であるとみなされ、多くの異種のあるいは少なくとも異なる化学現象(chemistry)の使用に対応するものである。ときとして、所望の異種のすなわち他の材料に対応する除去のための新たな化学現象の導入は、製造工程において負の連鎖反応を引き起こすかあるいは単に多くの半導体製造施設において使用されないものである。

【0040】

従って、本開示の実施形態は、リフトオフ(離昇)工程技術を用いるインターフェロメトリックデバイスの方法を含む。術語“リフトオフ工程”は、金などのエッチングが困難な金属のパターンデザインに概して用いられる、(製品内に残る材料のエッチングを必要としないで)基板表面上のパターンの定義である製造工程を含む、広い意味での通常及び慣習上の意味を含む。リフトオフ工程において、材料は、(フォトレジストなどの)パターニングされた下層の材料上に堆積され、その後、下層の材料を溶解することによって選択された領域がリフトオフされる。リフトオフ工程において形成されるパターニングされた下層の材料は以下ではリフトオフパターンあるいはリフトオフステンシルと呼ぶ。

【0041】

実施形態によれば、図1の層16a、16bおよび/またはインターフェロメトリック変調器12a及び12bの可動層14a、14bの光学的スタックなどの、インターフェロメトリック変調器の種々の層の製造におけるリフトオフ工程の使用はそれぞれ、各層に関連する材料の堆積及びパターン定義に関連する個別化された化学現象を有利に避けることができる。リフトオフ工程の使用は、製造工程の数を低減して、コストの低減及び製造の複雑さの簡略化につなげることができる。さらに、リフトオフ工程の使用は、インターフェロメトリック変調器の製造で用いられる材料及び施設の選択においてはるかに大きな柔軟性を獲得する。

【0042】

図8は、例えば、図1のインターフェロメトリック変調器12a及び12bなどの、インターフェロメトリック変調器の少なくとも一部を製造するための製造工程200の一般的なフローチャートを示している。図8に示すように、製造工程200はブロック202を含み、リフトオフパターンは、種々の業者から入手可能な、好ましくは汚れの無い透明な基板アッセンブリ上に形成される。本実施形態では、基板はガラスであるが、プラスチックなどの他の基板も使用可能である。一実施形態において、リフトオフパターンは、ポリイミドリリース(polyimide release)層(PiRL)などの第1のリフトオフ材料を堆積することによって形成されるが、これは写真蝕刻されるかあるいは写真蝕刻されない。次に、堆積された第1のリフトオフ材料はフォトレジストにより包囲される。フォトレジストはパターン形状を提供し、第1のリフトオフ材料とフォトレジストとはリフトオフステンシルの形成に即してパターニングされる。他のフォトレジスト層の使用によってパターニングされるPiRL層を使用する工程技術は、例えばミズーリ州、ロラのBrewer Science社から入手可能である。しかしながら、当業者ならば、他のリフトオフ材料も使用可能であることをこの開示から認識するであろう。例えば、リフトオフパターンは、Futurex社から入手可能なパターニング可能なリフトオフ材料からなる単一層を用いて形成される。溶剤の接近(Solvent access)及びリフトオフステンシルの次の除去を達成するために、リフトオフステンシルの厚さは、好ましくは、リフトオフ材料の上に引き続き堆積される層よりも大きい。例えば、一実施形態においては、リフトオフステンシルの厚さは、約1500オングストロームから約50000オングストロームの範囲であり、他の実施形態では、約20000オングストロームから約30000オングストロームの範囲である。

【0043】

製造工程200はさらにブロック204を含み、ここで光学的スタックが形成される。一実施形態において、光学的スタックは基板アッセンブリ及びリフトオフステンシル上に1つまたはそれ以上の材料層を堆積することにより形成される。リフトオフ工程は、光学的スタック内に個々の層のそれぞれを別個に形成するために、あるいは好ましくは光学的スタック内に複数の層を形成するのに用いられる。例えば、図の実施形態において、光学的スタックは、導電層と、下部ミラー金属層と、誘電層とを含む。光学的スタック上に他の材料層を堆積してもよい。例えば、一実施形態において、犠牲層が光学的スタック上に堆積された後、光学的スタックに沿ってリフトオフ工程が施される。全体の積層体における各層(例えば光学的スタック及び犠牲層)の厚さは同じであるかあるいは以下に述べるように互いに異なっている。

【0044】

一実施形態において、導電層は実質的に透明な材料であり、好ましくはITO(インジウムすず酸化物)からなる。透明な導電層の厚さは概して、ディスプレイの行(ロー)に対する導電仕様や、材料の光学透過品質などを考慮して選択される。好ましい実施形態において、透明な導電層の厚さは約200オングストロームから約1000オングストロームの範囲である。例えば、図示の実施形態においては、透明な導電層は約500オングストロームの厚さをもつ。当業者ならばここでの開示から導電層を形成するために亜鉛酸化物を含む他の材料も有利に利用可能であることを認識するであろう。

【0045】

一実施形態において、下部ミラー金属層はクロム(Cr)層を備える。下部ミラー層の厚さは概して材料の光学透過度あるいは他の光学特性を考慮して選択される。同様にして、好ましい実施形態において、ミラー層の厚さは部分的に透過性を備えるように好ましくは約30オングストロームから約150オングストロームの範囲である。例えば、図示の実施形態において、ミラー層は約70オングストロームの厚さを有する。すなわち、本実施形態において、ITO透明導電層は(約500オングストローム)の厚さであり、クロムミラー層(約70オングストローム)の厚さよりも大きい。当業者ならばここでの開示から、下部ミラー金属層は、Crの代わりに、モリブデン(Mo)、チタン(Ti)、及び/またはタングステン(W)を含む他の材料からなることを認識するであろう。

【0046】

一実施形態において、誘電体層は二酸化シリコン(SiO2)層からなる。誘電体層の厚さは概して、バイアス位置における変調器の所望の色を考慮して選択される。すなわち、好ましい実施形態において、誘電体層の厚さは、約100オングストロームから約2500オングストロームの範囲である。例えば、図示の実施形態において、誘電体層は約700オングストロームの厚さをもつ。当業者ならばここでの開示から、誘電体層はここでは誘電体積層体と呼ばれる複数のサブレイヤを含むことを認識するであろう。誘電体層は窒化シリコン(SiN)、酸化アルミニウム(Al2O3)、酸化シリコン(SiOx)などの種々の誘電材料を単体であるいは組み合わせた形で含む(例えばサブレイヤ)。

【0047】

犠牲層は、図示の実施形態においてモリブデン(Mo)層からなる。犠牲層の厚さは概して、非作動位置における変調器の所望のカラーと、以下に述べるように、犠牲層を除去するために用いられる製造工程(例えばドライエッチ)とを考慮して選択される。犠牲層の厚さは好ましくは、約400オングストロームから約6000オングストロームの範囲である。例えば、図示の実施形態において、犠牲層は約2000オングストロームの厚さを有する。当業者ならばここでの開示から、犠牲層はモリブデンに加えてあるいはその代わりに、シリコン(Si)、チタン(Ti)、タングステン(W)、ゲルマニウム(G)などの1つまたはそれ以上の他の容易に除去可能な材料を含むことを認識するであろう。

【0048】

当業者ならばここでの開示から、前記したすべてのあるいは一部の光学的スタックは、少なくとも部分的には実質的に透明な基板への接着を考慮して及び/またはリフトオフパターンが形成された後に残る残渣の可能性を考慮して選択されることを認識するであろう。さらに、光学的スタックは、有機リフトオフ構造に実質的に悪影響を与えない温度で堆積可能な材料から選択される。例えば、一実施形態において、光学的スタックの材料は約250度あるいはそれ以下の温度で堆積される。

【0049】

製造工程200はブロック206を含み、ここでは光学的スタックがリフトオフ工程を用いてパターニングされる。ここに開示された技術により概して理解されるように、リフトオフ工程は一部あるいはすべてのリフトオフ材料と反応及び/または当該材料を溶解する化学現象を使用し、例えば光学的スタックの下にリフトオフステンシルを形成する。リフトオフ材料を除去することによって、リフトオフ材料の上の光学的スタックの材料はもはや付着せず、廃棄化学現象(waste chemistry)によって基板アッセンブリから浮遊あるいは離昇される。光学的スタック例えば犠牲層の上に形成された他の層は、光学的スタックに沿って離昇される。すなわち、リフトオフ工程は、既知の化学現象を用いて複数の異なる異種の層のパターニングを有利に提供する。リフトオフ材料の除去は種々の方法により達成される。例えば、もはや付着していない材料の除去のためのすすぎ工程に続いて、リフトオフ材料は、リフトオフ材料と反応する及び/または該材料を溶解する液状、ガス状あるいは蒸気のリフトオフ化学現象に対して露出される。リフトオフ化学現象は好ましくは液状で適用され、ここではウエットエッチリフトオフと呼ぶことにする。

【0050】

好ましい実施形態において、パターニングされた残りの層は、インターフェロメトリック変調器12a、12bなどの変調器のロー(行)電極、光学的スタックそして犠牲層を形成する。

【0051】

製造工程200はブロック208を含み、ここではポスト18などの支持体構造が形成される。例えば、例示された実施形態において、ポスト18の材料はパターニング可能あるいはパターニング不可の正あるいは負のフォトレジストからなる。一実施形態において、最上面のフォトレジストが堆積され、材料を最上面からパターニングするのに適切に配置されたレチクルが用いられる。化学的機械的平坦化(CMP)などの平坦化技術が、余分のフォトレジスト及び/または材料を除去するのに用いられる。一実施形態において、背面フォトレジストは背面露出(基板アッセンブリは好ましくは透明である)を用いてパターニングされ、光学的スタックパターンが適切なアライメント(マスク)を有利に形成する。一実施形態において、CMPは余分のフォトレジスト及び/または材料を除去するのに用いられる。

【0052】

当業者ならばここでの開示から、平坦化されたレジスト構造の形状を変更または改善するために特別なCMP工程が使用されることを認識するであろう。さらに、当業者ならば、スピンオンガラス(SOG)、有機平坦化材料などを含む、他の材料が一部あるいはすべてのポストを形成するのに用いられることを認識するであろう。当業者ならばここでの開示から、一部の材料または工程の使用は、CMP工程を低減または完全に除去することを認識するであろう。例えば、スピンオフガラスは、パターニングされて平坦化工程を経ずに単に残される。そのような工程はバンプを残すが、それは装置の動作または信頼性を実質的に変更するものではない。

【0053】

製造工程200はブロック210を含み、ここでは第2のリフトオフパターンが形成される。使用されるリフトオフ材料はブロック202及び第1のリフトオフパターンに関して上記した材料と同じかまたは異なっている。当業者ならばここでの開示から、リフトオフ材料は、ロー(行)電極層とのアライメントを確実にするように及び/またはリフトオフパターンの形成後に光学的スタックの清浄さを増大するように選択される。

【0054】

製造工程200はブロック212を含み、ここでは1つまたはそれ以上の屈曲(flex)層が形成される。一実施形態において、屈曲層は部分的に製造された変調器およびリフトオフ材料の上に1つまたはそれ以上の層を堆積することによって形成される。一実施形態において、屈曲層はミラー層と弾性をもつ金属導電層とからなる。一実施形態において、ミラー層はアルミニウム(AL)層からなる。ミラー層の厚さは概して材料の反射率及び材料構造の完全さを考慮して選択される。例えば、材料は独立しており、製造工程のステップと通常の動作におけるストレスに耐えるのに十分な厚さである。さらに、ミラー層は、例示的な実施形態において完全な反射性をもつのに十分な厚さである。一実施形態において、ミラー層の厚さは約80オングストロームから約1ミクロンの範囲である。例えば、例示的実施形態において、ミラー層は約300オングストロームの厚さを有する。当業者ならばここでの開示から、ミラー層はアルミニウムに加えてあるいはその代わりに、銀(Ag)または金(Au)などの1つまたはそれ以上の他の反射材料を含むことを認識するであろう。屈曲層は導電性、反射性及び/または弾性をもつ、すなわち、例えば、単一の構造は電極層、ミラー層そして変形可能な層として機能する。一部の実施形態において、例えば図7Cに示すように、反射層14は、変形可能な層34から吊り下げられ、両方が電極層として機能する。種々の他の構成が使用される。

【0055】

一実施形態において、屈曲層における弾性金属層はニッケル(Ni)層からなる。導電層の厚さは概して、材料構造の完全さと製造工程ステップに耐える能力とを考慮して選択される。一実施形態において、弾性金属導電層の厚さは約300オングストロームから約1ミクロンの範囲である。例えば、例示の実施形態において、屈曲層における導電層は、約1000オングストロームの厚さをもつ。当業者ならばここでの開示から、導電層は、ニッケルに加えてあるいはその代わりに、クロム、アルミニウム、及び/またはアルミニウム合金などの1つまたはそれ以上の他の導電材料を含むことを認識するであろう。導電層は金属酸化サンドイッチ構造などの複合構造を含む。

【0056】

当業者ならばここでの開示から、前記したすべてのあるいは一部の屈曲層は、少なくとも部分的には光学的スタックへの接着(あるいは接着の欠如)及び/または支持構造またはポスト層への接着を考慮して選択される。例えば、図1において、屈曲層14bの材料は好ましくは、インターフェロメトリック変調器12bの作動中における固定された部分的に反射性の層16bに対する接着力が最小になるように選択される。さらに、屈曲層の材料は、例えば導電層とミラー層との接着力が最大になるように互いの接着を考慮して選択される。

【0057】

製造工程200はブロック214を含み、ここで屈曲層はリフトオフ工程を用いてパターニングされる。好ましい実施形態において、残りのパターニングされた屈曲層は、インターフェロメトリック変調器12a、12bなどのインターフェロメトリック変調器の第2のミラー、カラム(列)電極そして機械的層を形成する。屈曲層は、例えば図7Cに示されるような構成を形成するために、ミラー層から別個にパターニングされる。リフトオフ工程は、比較的厚いミラー層のパターニングを有利に実現するために用いられる。屈曲層は好ましくは高導電性であり、引張応力内にある。屈曲層は好ましくは製造工程のストレスに耐えるためにかつ平坦化材料に接着するために内部的材料の完全さをもつ。

【0058】

一実施形態において、リフトオフステンシルの除去は好ましくは第2のミラーのパターニングされた領域を形成し、図14,15(以下に述べる)に示すように、下にある犠牲層の一部を露出する。この実施形態に示されるリフトオフ工程は、屈曲層の位置が、最終的な構造のために堆積材料をエッチングすることなしに(この場合、屈曲層を直接エッチングすることなしに)除去されることを可能にする。屈曲層の当該部分を従来の方法でエッチング除去することは、下にある犠牲層のエッチングが不十分になってしまうという問題を引き起こす。

【0059】

当業者ならばここでの開示から、種々の他の工程ステップにより、例えばインターフェロメトリック変調器12a(図1)の空洞部19などの空洞部を形成するために犠牲層を有利に除去できることを認識するであろう。さらに、上記したことに基づいて、当業者ならばここでの開示から、リフトオフ工程によって、エッチング両立性の問題、異なる新たな化学現象の問題を有利に避けながら、製造工程において特に上記した光学的スタックの製造におけるパターン形成を有利に強化するのに製造工程200が用いられることを認識するであろう。製造工程200は工程ステップを有利に減らすとともに変調器製造者のために層材料と製造施設の入手と選択の度合いを増大するのに用いられる。

【0060】

図9A及び9Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器300の平面図、断面図である。図に示すように、変調器300は、透明な基板アッセンブリ302と、パターニングされたリフトオフ材料PiRL304と、フォトレジスト306とを含み、全体でリフトオフステンシル308を形成している。図9Bに示すように、リフトオフ材料は、PiRL材料304を選択的にオーバエッチングすることによって逆さ台形または略T字形状を形成する。T字形状は、該T字形状の上部に堆積された材料が、T字形状の底部近くの基板上に堆積された材料から分離されるので、リフトオフを行うのに都合がよい。T字形状は、リフトオフステンシル308がリフトオフ化学現象に対して露出することを実現する。以下に詳述するように、ポスト602aは領域312内に形成され、(下部電極を互いに分離する)レール602bは図9Aに示すように領域310内に形成される。

【0061】

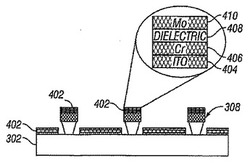

図10A及び10Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器400の平面図、断面図である。図に示すように、変調器400は、リフトオフステンシル308と基板302の上に形成された積層体402を含む。

【0062】

図10Bに示すように、積層体402は、ITO層404、Cr層406、誘電層408そして犠牲Mo層410を含む複数材料層からなる。図15を参照して後述するように、ITO層404、Cr層406、誘電層408は最終的に光学的スタック806に組み込まれる。上記したように、リフトオフステンシル308の厚さは好ましくは、リフトオフステンシル308を後で除去するために用いられる化学現象への縦方向のアクセスを可能にするために、積層体402の厚さよりも大きい。

【0063】

図11A及び11Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器500の平面図、断面図である。図に示すように、変調器500は、リフトオフ工程を行った後にパターニングされた積層体402を含み、この間に、リフトオフステンシル308は(図10Bに示すようにリフトオフステンシル308上に堆積された積層体402の一部とともに)除去される。パターニングされた積層体402は下に配置された光学的スタック404−408(図10B)を含む。光学的スタック404−408は(上に配置された犠牲層410とともに)、リフトオフの後に残る材料から形成されるという点において正にパターニングされる。同様にして、変調器500は、リフトオフステンシル308の除去によって形成され、基板302上に負にパターニングされた領域502a、502bを含む。

【0064】

図12Aは平面図であり、図12B、12Cは、本実施形態による部分的に製造されたインターフェロメトリック変調器600の断面図である。図に示すように、変調器600は、前面アライメント露出技術(図12B)あるいは背面自己整合露出技術(図12C)を用いて、放射606に対する露出によってレチクル604を通して形成された支持体構造602a(ポスト)及び602b(レール)を含む。ポスト602a及びレール602bはそれぞれ(図11A及び11B)、基板302上に負にパターニングされた領域502a、502b内に形成される。

【0065】

負にパターニングされた領域を形成するのにリフトオフ工程を使用することは、特に厚い層を除去する場合において、パターニングすべき材料を直接エッチングすることに比較して有利であることが見出された。例えば、直接的なエッチング工程により形成された負にパターニングされた領域は、エッチング剤がパターン材料をアンダーカットしやすいため、上に位置するパターン材料(例えばフォトレジスト)のサイズよりも幾分大きくなる傾向がある。ポスト構造が最小の空間を占有することが望ましい実施形態においては、リフトオフ工程の使用は、ポスト構造が形成される、所望のサイズに小さくされた負にパターニングされた領域の形成を確実にする。すなわち、好ましい実施形態においては、リフトオフ工程は、インターフェロメトリック変調器の製造中に負にパターニングされた領域を形成するために、より好ましくはポスト構造が後で形成される負にパターニングされた領域を形成するのに使用される。多くの実施形態において、ウエットエッチングリフトオフ工程は、インターフェロメトリック変調器の製造において負にパターニングされた領域を形成する場合に、直接エッチング(ウエット及び/またはドライ)と比較して特に有利である。

【0066】

リフトオフ工程の使用は、直接エッチング工程と比較して多数の材料層を除去する場合、特に比較的薄い層の下に位置する比較的厚い層を除去する場合に有利であることが見出された。材料が異なると直接エッチングの速度も異なる傾向があるので、多数の層を除去するために等方性のエッチング剤を使用するとしばしば側壁が不規則になる。これは種々の層において材料が異なることより縦方向のエッチング速度が異なるためである。例えば、より厚いITO層の上の薄いクロム層を含む積層体のウエットエッチングは、ITO層を除去するのに用いられるエッチング剤に対する露出が、厚いITO層の所望の程度のエッチングを獲得するために比較的長くなるために、クロム層のアンダーカットにつながる。すなわち、好ましい実施形態において、リフトオフ工程は、多数の材料層を除去するためにインターフェロメトリック変調器の製造において使用される。多くの実施形態において、ウエットエッチングリフトオフ工程は特に、インターフェロメトリック変調器の製造において多数の材料層を除去する場合に、直接エッチングと比較して有利である。

【0067】

図13A及び13Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器700の平面図、断面図である。断面図13Bは図12Bに示される線と異なる線に沿ったものであることに注意されたい。図に示すように、変調器700は、パターニングされたリフトオフ材料PiRL704と、フォトレジスト706とを含み、全体でリフトオフステンシル708を形成する。図13Bに示すように、リフトオフステンシル708は、リフトオフステンシル308の形成の場合に上記した方法と類似の方法によって積層体402上に略T字形状に形成される。

【0068】

図14A及び14Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器800の平面図、断面図である。図に示すように、変調器800は、積層体402上に形成された屈曲層802、リフトオフステンシル708、そしてポスト602aを含む。14Bに示すように、屈曲層802はAIミラー層804とNi導電層806とからなる。AIミラー層804とNi導電層806とは例えば物理気相成長法あるいはスパッタリング堆積などの種々の方法により形成される。

【0069】

図15Aは平面図であり、図15B、15Cは、本実施形態によるインターフェロメトリック変調器600の断面図である。図に示すように、変調器900は、リフトオフ工程が行われた(この間、リフトオフステンシル708が(図14Bに示すようにリフトオフステンシル708上に堆積された屈曲層802の一部とともに)除去された)後の、(AIミラー層804及びNi導電層806を含む)パターニングされた屈曲層802を含む。リフトオフステンシル708を除去すると、開口902、904が形成される。図15B及び15Cは積層体402からの犠牲層410の後工程による除去を示しており、ITO層404、Cr層406、誘電体層408を含む光学的スタック806を形成する。犠牲層410を除去すると、変調器900の空洞部19が形成される。ポスト602aはパターニングされた屈曲層802のための支持体構造であり、空洞部19を規定する役目をもつ。一実施形態において、除去は、Mo犠牲層410と化学的に反応させるために、開口902、904を通して流れるキセノンフッ化物(XeF2)に対して変調器800を露出することによって達成され、ドライエッチング工程によって犠牲層が除去されて空洞部19を形成する。

【0070】

インターフェロメトリック変調器の製造工程の前記の実施形態は好ましい実施形態の観点から記載されたが、当業者ならばここでの開示から他の実施形態を実現することも可能である。例えば、リフトオフ工程は、光学的スタックあるいは屈曲層の種々の層の1つまたは数個に有利に適用されるか、あるいは全く適用されない。さらに、種々のインターフェロメトリックデバイス構造及び形状は上記したリフトオフ工程を用いて形成される。例えば、ミラー機能は例えば屈曲層の機械的あるいは弾性を持つ機能から有利に分離され、これによって、実質的に硬いミラー層14が図7Cに示すように機械的層34から空洞部19の上方に吊り下げられる。そのような構造を製造するのに適切な方法は、定期的な実験によって決定され、例えば、ミラー層14の製造のための第1のリフトオフ工程及び機械的層34の製造のための第2のリフトオフ工程を含む。当業者ならば個々のインターフェロメトリック変調器の製造に適用可能であるとしてここに記述された方法は、インターフェロメトリック変調器アレイの製造にも適用可能であることを認識するであろう。同様にして、インターフェロメトリック変調器アレイの製造に適用可能であるとしてここに記述された方法は、個々のインターフェロメトリック変調器の製造にも適用可能である。

【0071】

当業者ならば多数及び種々の変形例が本発明の精神から逸脱することなしに実現可能であることが認識するであろう。したがって、本発明の形態は例示のみであり本発明の権利範囲を限定することを意図するものではないことが理解されるべきである。

【図面の簡単な説明】

【0072】

この発明のこれらおよび他の側面は、ある実施形態の図面を参照して説明される。図は一定の率で拡大縮小したものではなく、かつ本発明を例示的に説明するためのものであり、限定する意図で用いられるものではない。

【図1】図1は、第1のインターフェロメトリック変調器の移動可能な反射層が開放された(relaxed)位置にあり、第2のインターフェロメトリック変調器の移動可能な反射層が作動位置にあるインターフェロメトリック変調器ディスプレイの一実施形態の一部を示す等角図である。

【図2】図2は、3×3のインターフェロメトリック変調器ディスプレイを組み込んだ電子デバイスの一実施形態を示すシステムブロック図である。

【図3】図3は、図1のインターフェロメトリック変調器の例示的な実施形態における移動可能ミラー位置対印加電圧の図である。

【図4】図4は、インターフェロメトリック変調器ディスプレイを駆動するのに用いられる行及び列電圧の組を示す図である。

【図5A】図5Aは、図2の3×3のインターフェロメトリック変調器ディスプレイにおけるディスプレイデータの例示的なフレームを示す図である。

【図5B】図5Bは、図5Aのフレームに書き込むのに用いられる行及び列信号の例示的タイムチャートである。

【図6A】図6Aは、複数のインターフェロメトリック変調器を備えたビジュアルディスプレイ装置の一実施形態を示すシステムブロック図である。

【図6B】図6Bは、複数のインターフェロメトリック変調器を備えたビジュアルディスプレイ装置の一実施形態を示すシステムブロック図である。

【図7A】図7Aは、図1の装置の断面図である。

【図7B】図7Bは、インターフェロメトリック変調器の他の実施形態の断面図である。

【図7C】図7Cは、インターフェロメトリック変調器のさらに他の実施形態の断面図である。

【図7D】図7Dは、インターフェロメトリック変調器のさらに他の実施形態の断面図である。

【図7E】図7Eは、インターフェロメトリック変調器のさらに他の実施形態の断面図である。

【図8】図8は、一実施形態による、図1の変調器などのインターフェロメトリック変調器における製造工程の例示的フローチャートである。

【図9A】図9Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図9B】図9Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図10A】図10Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図10B】図10Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図11A】図11Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図11B】図11Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図12A】図12Aは図8の製造工程の実施形態を用いて一部製造された平面図である。

【図12B】図12Bは図8の製造工程の実施形態を用いて一部製造された断面図である。

【図12C】図12Cは図8の製造工程の実施形態を用いて一部製造された断面図である。

【図13A】図13Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図13B】図13Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図14A】図14Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図14B】図14Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図15A】図15Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図15B】図15Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図15C】図15Cは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【技術分野】

【0001】

背景

発明の分野

本発明の分野は、インターフェロメトリックデバイスの製造の分野を含む、微小電気機械システム(MEMS)に関する。一実施形態において、本発明は、インターフェロメトリックデバイスの製造に用いることが可能な材料及び施設の数を拡張するのに用いられる製造工程技術に関する。

【背景技術】

【0002】

関連技術の記載

微小電気機械システム(MEMS)は、微少機械要素、アクチュエータ及び電子機器を含む。微少機械要素は、堆積、エッチング、及び又は、基板及び/又は堆積材料層の部分をエッチング除去し、あるいは、層を加えて電気素子及び電気機械素子を形成する他のミクロ機械加工プロセスを用いて形成することができる。MEMSデバイスの1つのタイプは、インターフェロメトリック変調器と称される。本明細書中で用いる場合、インターフェロメトリック変調器又はインターフェロメトリック光変調器とは、光学的干渉の原理を用いて光を選択的に吸収し及び/又は反射するデバイスを指す。ある実施形態において、インターフェロメトリック変調器は、一方又は両方が、この全体又は一部が透過性及び/又は反射性であってもよく、かつ適当な電気信号を印加したときに相対運動が可能な、1組の導電性プレートを備えてもよい。特定の実施形態において、一方のプレートは、基板上に堆積された固定層を備えてもよく、また他方のプレートは、この固定層からエアギャップだけ離れている金属膜を備えてもよい。本明細書に詳細に記載されているように、一方のプレートの他方に対する位置は、このインターフェロメトリック変調器に入射する光の光学的干渉を変えることができる。このようなデバイスは、広範囲の用途を有しており、これらのタイプのデバイスの特徴を利用し及び/又は変更することが当分野において有益であるため、現在ある製品を改良する際、及びまだ開発されていない新しい製品を考案する際に、これらの特徴を活かすことができる。

【発明の開示】

【課題を解決するための手段】

【0003】

ここに記述されるシステム、方法そしてデバイスはそれぞれいくつかの側面を備えているが、どの1つたりとも単にその望ましい属性を請け負うものではない。本発明の範囲を制限することなしに、より顕著な特徴について簡単に説明する。この議論を考慮した後に、特に“好ましい実施形態の詳細な説明”と称する部分を読めば、ここに記載した種々の実施形態がいかにして他の方法およびディスプレイ装置と比較して利点を提供するかを理解するであろう。

【0004】

一実施例は、インターフェロメトリック変調器の製造方法を提供するものであって、少なくとも第1のパターニング製造工程を用いて透明な基板上に光学的スタック(積層体)を形成することと、前記基板上に支持体構造を形成することとを含む。この実施形態において、前記方法はさらに、少なくとも第2のパターニング製造工程を用いて前記光学的スタック及び支持体構造上に上部ミラー層を形成することを含む。ここで、前記光学的スタック、前記支持体構造、前記上部ミラー層の少なくとも1つの表面に空洞部が形成され、前記上部ミラー層の前記空洞部への一部の移動は、前記支持体の表面から認識される光学特性を制御可能かつ予測可能な方法で変化させ、前記第1及び第2の製造工程の少なくとも1つはリフトオフ工程を具備する。他の実施形態は、そのような方法によって製造されたインターフェロメトリック変調器を提供する。

【0005】

他の実施形態は、インターフェロメトリック変調器の製造方法を提供するものであって、基板上にリフトオフステンシルを形成することと、前記リフトオフステンシルと前記基板上に第1の材料層を堆積することとを含む。この実施形態において、前記方法はさらに、前記第1の材料層上に第2の材料層を堆積することと、前記リフトオフステンシルを除去して、前記第1の材料層とその上に形成された前記第2の材料層とからなるパターニングされた領域を形成することとを含む。他の実施形態は、そのような方法によって製造されたインターフェロメトリック変調器を提供する。

【0006】

他の実施形態は、インターフェロメトリック変調器のアレイの製造方法を提供するものであって、リフトオフステンシルを用いて基板上に複数の正にパターニングされた光学的スタックと、複数の負にパターニングされたポスト領域とを形成することと、前記負にパターニングされたポスト領域内に複数のポスト構造を形成することとを含む。他の実施形態はそのような方法によって製造されたインターフェロメトリック変調器のアレイを提供する。

【0007】

他の実施形態は、ディスプレイ装置の製造方法を提供するものであって、第1のミラー層を堆積することと、前記第1のミラー層上に犠牲層を堆積することと、前記犠牲層上にリフトオフステンシルを形成することとを含む。この実施形態において、前記方法はさらに、前記リフトオフステンシル上に第2のミラー層を堆積することと、前記リフトオフステンシルを除去することによって、前記第2のミラー層のパターニングされた領域を形成して前記犠牲層の一部を露出することとを含む。他の実施形態は、そのような方法によって製造されたディスプレイ装置を提供する。

【0008】

他の実施形態は、上記の方法によって製造されるインターフェロメトリック変調器のアレイを含むディスプレイパネルを提供する。他の実施形態は、そのようなディスプレイパネルと、前記ディスプレイパネルと電気通信可能であって、イメージデータを処理するように構成されたプロセッサと、前記プロセッサと電気通信可能なメモリ装置とを含むディスプレイ装置を提供する。

【発明を実施するための最良の形態】

【0009】

以下の詳細な説明は、本発明の特定の実施形態を対象に記載している。しかしながら、複数の異なる方法によって実現可能である。ここでの説明では明細書全体にわたって図面を参照して説明がなされ、同一の部分には同一の参照符号が付与される。本実施形態は、動いていようと(例えば、ビデオ)、静止していようと(例えば、静止イメージ)、及びテキストであろうと写真であろうと、イメージを表示するように構成されているいかなるデバイスでも実施することができる。より具体的には、本実施形態を、限定するものではないが、移動電話、無線装置、PDA(personal data assistants)、ハンドヘルドコンピュータ又はポータブルコンピュータ、GPSレシーバ/ナビゲータ、カメラ、MP3プレーヤ、カムコーダー、ゲームコンソール、腕時計、時計、計算機、テレビモニタ、フラットパネルディスプレイ、コンピュータモニタ、オートディスプレイ(例えば、走行距離計等)、コックピット制御部及び/又はディスプレイ、カメラビューのディスプレイ(例えば、自動車のリアビューカメラのディスプレイ)、電子写真、電子掲示板又は電子サイン、プロジェクタ、建築構造物、パッケージング及び審美的構造(例えば、宝石に関するイメージの表示)等の様々な電子デバイスで、又は該様々な電子デバイスに付随して実施することができることが意図されている。また、本明細書中で説明したのと同様の構造のMEMSデバイスは、電子スイッチングデバイスにおける等の非表示用途で用いることもできる。

【0010】

好ましい実施形態は、インターフェロメトリック変調器の製造にリフトオフ工程方法を適用することを含む。

【0011】

インターフェロメトリックMEMSディスプレイ要素を備える1つのインターフェロメトリック変調ディスプレイの実施形態を図1に示す。これらのデバイスにおいて、画素は、明るい状態又は暗い状態のいずれかにある。この明るい(「オン」又は「オープン」)状態において、このディスプレイ要素は、入射可視光の大部分をユーザに対して反射させる。この暗い(「オフ」又は「クローズド」)状態の場合、このディスプレイ要素は、わずかな入射可視光を該ユーザに対して反射させる。実施形態によっては、これらの「オン」及び「オフ」状態の光反射特性は、逆にしてもよい。MEMS画素は、選択された色で主に反射するように構成することができ、黒及び白に加えてカラー表示を可能にする。

【0012】

図1は、ビジュアルディスプレイの一連の画素における隣接する2つの画素を示す等角図であり、各画素は、MEMSインターフェロメトリック変調器を備える。いくつかの実施形態においては、インターフェロメトリック変調ディスプレイは、これらのインターフェロメトリック変調器の行/列アレイを備える。各インターフェロメトリック変調器は、互いに可変かつ制御可能な距離をおいて配置され、少なくとも1つの可変寸法を有する光空洞部共振器を形成する1対の反射層を含む。一実施形態において、これらの反射層の一方は、2つの位置の間で移動することができる。本明細書において開放位置と称する第1の位置においては、この移動可能な反射層は、固定された部分的反射層から比較的大きな距離をおいて配置されている。本明細書において作動位置と称する第2の位置においては、この移動可能な反射層は、この部分的反射層により近接して配置されている。これらの2つの層から反射する入射光は、この移動可能な反射層の位置により、建設的に又は破壊的に干渉し、各画素に対して全体的反射状態又は非反射状態のいずれかをもたらす。

【0013】

図1の画素アレイの図示した部分は、隣接する2つのインターフェロメトリック変調器12a及び12bを含む。左側のインターフェロメトリック変調器12aにおいては、移動可能な高反射層14aが、部分的反射層を含む光学的スタック16aから所定の距離の開放位置に示されている。右側のインターフェロメトリック変調器12bにおいては、移動可能な反射層14bが、光学的スタック16bに隣接する作動位置に示されている。

【0014】

本明細書で言及されているような光学的スタック16a、16b(まとめて光学的スタック16と称する)は、典型的には、インジウムスズ酸化物(indium tin oxide;ITO)等の電子層、クロム等の部分的反射層、及び透明誘電体を含むことができるいくつかの融合層から構成される。このため、光学的スタック16は導電性であり、部分的に透明であり、かつ部分的に反射性であり、例えば、これらの層の1つ以上を透明基板20上に堆積させることにより製造することができる。いくつかの実施形態において、これらの層は、平行なストリップにパターン化され、また、以下にさらに説明するように、ディスプレイ装置に行電極を形成することができる。移動可能な反射層14a、14bは、ポスト18の上部に堆積させた(行電極16a、16bと直交する)堆積した1枚の金属層及び複数の金属層と、ポスト18の間に堆積させた介在犠牲材料とからなる一連の平行なストリップとして形成することができる。この犠牲材料がエッチング除去されると、移動可能な反射層14a、14bは、画定されたエアギャップ19だけ、光学的スタック16a、16bから分離される。アルミニウム等の高導電性及び反射性の材料は、反射層14に用いることができ、また、これらのストリップは、ディスプレイ装置内に列電極を形成してもよい。

【0015】

電圧を印加しない場合、空洞部19は、図1における画素12aによって示すように、移動可能な反射層14aが機械的に開放された状態で、移動可能な反射層14aと光学的スタック16aとの間に存続する。しかし、選択した行及び列に対して電位差を加えると、対応する画素におけるこの行及び列電極の交差部に形成されたキャパシタが充電されて、静電力がこれらの電極を一緒に引っ張る。この電圧が充分高い場合、移動可能な反射層14は変形し、かつ光学的スタック16に向かって押し込まれる。光学的スタック16内の(この図面には示されていない)誘電体層は、短絡を防止することができ、また、図1の右側の画素12bに示すように、層14と層16との間の隔離距離を制御することができる。この作用は、印加された電位差の極性に関係なく同じである。このように、反射性対非反射性の画素状態を制御することができる行/列動作は、従来のLCD及び他の表示技術で用いられるものと多くの点で似ている。

【0016】

図2〜図5Bは、表示用途において、インターフェロメトリック変調器のアレイを用いる1つの例示的なプロセス及びシステムを示す。

【0017】

図2は、本発明の態様を組み込んでもよい電子装置の一実施形態を示すシステムブロック図である。例示的な実施形態において、この電子装置は、ARM、Pentium(登録商標)、Pentium II(登録商標)、Pentium III(登録商標)、Pentium IV(登録商標)、Pentium Pro(登録商標)、8051、MIPS(登録商標)、Power PC(登録商標)、ALPHA(登録商標)等のどのような汎用の単一又はマルチチップマイクロプロセッサ、あるいは、ディジタル信号プロセッサ、マイクロコントローラ又はプログラマブルゲートアレイ等のどのような専用マイクロプロセッサであってもよいプロセッサ21を含む。従来技術と同様に、プロセッサ21は、1つ以上のソフトウェアモジュールを実行するように構成することができる。このプロセッサは、オペレーティングシステムを実行するのに加えて、ウェブブラウザ、電話アプリケーション、電子メールプログラム、又は他のソフトウェアアプリケーションを含む1つ以上のソフトウェアアプリケーションを実行するように構成することができる。

【0018】

一実施形態においては、プロセッサ21も、アレイドライバ22と通信するように構成されている。一実施形態において、アレイドライバ22は、信号を表示アレイ又はパネル30へ供給する行ドライバ回路24及び列ドライバ回路26を含む。図1に示すこのアレイの断面は、図2の線1−1によって示されている。MEMSインターフェロメトリック変調器の場合、この行/列作動プロトコルは、図3に示すそれらのデバイスのヒステリシス特性を利用してもよい。例えば、移動可能な層を、上記解放状態から作動状態に変形させるために、10ボルトの電位差を要求してもよい。しかし、この電圧がこの値から低下した場合、この移動可能な層は、この電圧が10ボルト以下に低下したときにその状態を維持する。図3の例示的な実施形態において、この移動可能な層は、この電圧が2ボルト以下に低下するまで、完全に解放されない。それに伴って、図3に示した実施例には、約3〜7Vの電圧範囲があり、この場合、その範囲内でこのデバイスが、この解放状態又は作動状態のいずれかで安定している印加電圧のウィンドウが存在する。本明細書では、これを「ヒステリシスウィンドウ」又は「安定ウィンドウ」と称する。図3のヒステリシス特性を有するディスプレイアレイの場合、上記行/列作動プロトコルは、行ストロービングの間、作動されるべきこのストローブされた行の画素が、約10ボルトの電圧差にさらされ、かつ解放されるべき画素が、0ボルトに近い電圧差にさらされるように設計することができる。このストローブの後、これらの画素は、どのような状態においても、行ストローブのままであるように、約5ボルトの定常電圧差にさらされる。書き込まれた後、各画素は、この実施例において3〜7Vの「安定ウィンドウ」内の電位差を参照する。この特徴は、図1に示す画素デザインを、作動又は解放先在状態のいずれかにおける同じ印加電圧条件の下で安定させる。上記インターフェロメトリック変調器の各画素は、作動状態であろうと解放状態であろうと、本質的に、固定された反射層と移動可能な層とによって形成されたキャパシタであるため、この安定状態は、ほとんど電力消失を伴わずに、このヒステリシスウィンドウ内の電圧で保持することができる。印加電位が固定されている場合、本質的に、電流はこの画素へは流れない。

【0019】

典型的な用途において、ディスプレイフレームは、第1の行における作動画素の所望のセットに従って、列電極のセットをアサートすることによって生成することができる。そして、行パルスは、行1電極に印加され、このアサートされた列ラインに対応する画素が作動される。次に、列電極のこのアサートされたセットは、第2の行の作動画素の所望のセットに対応させるため変化する。次いで、パルスが行2電極に印加され、このアサートされた列電極に従って、行2の適当な画素が作動される。行1画素は、行2パルスによる影響を受けず、行1パルスの間に設定された状態のままである。これは、フレームを生成するために、一連の行に対して繰り返すことができる。一般に、これらのフレームは、毎秒所望数のフレームにおいて、このプロセスを連続的に繰り返すことにより、新たな表示データに伴ってリフレッシュ及び/又は更新される。画素アレイの行及び列電極を駆動して表示フレームを生成する幅広いプロトコルもまた周知であり、本発明と共に用いることができる。

【0020】

図4、図5A及び図5Bは、図2の3×3アレイに表示フレームを生成する1つの可能な作動プロトコルを示す。図4は、図3のヒステリシス曲線を示す画素に用いることができる列及び行電圧レベルの可能なセットを示す。図4の実施形態において、画素を作動させることは、適当な行を−Vbiasに、適当な列を+ΔVに設定することを含み、これらはそれぞれ、−5V及び+5Vに相当する。画素を解放させることは、適当な行を+Vbiasに、適当な列を同じく+ΔVに設定して、この画素の両端に0Vの電位差を生じることにより実現される。行電圧が0Vに保持される行においては、これらの画素は、この列が+Vbias又は−Vbiasであることに関係なく、これらの画素が元々どのような状態にあろうとも安定している。図4にも示されているように、上述したもの以外の反対極性の電圧を用いることができること、例えば、画素を作動させることが、適当な列を+Vbiasに、及び適当な行を−ΔVに設定することを含むことができることは、正しく理解される。この実施形態において、画素を解放することは、適当な行を−Vbiasに、及び適当な行を同じく−ΔVに設定して、この画素の両端に0Vの電位差を生じさせることによって実現される。

【0021】

図5Bは、作動画素が非反射性である、図5Aに示す表示構成を生じる、図2の3×3アレイに印加される一連の行及び列信号を示すタイミング図である。図5Aに示すフレームに書き込む前に、画素は、どのような状態も可能であり、この実施例においては、全ての行が0Vであり、全ての列が+5Vである。これらの印加電圧によって、全ての画素は、これらの現在の作動又は解放状態において安定している。

【0022】

図5Aのフレームにおいては、画素(1,1)、(1,2)、(2,2)、(3,2)及び(3,3)が作動している。これを実現するため、行1のための「ラインタイム」の間には、列1及び列2が−5Vに設定され、かつ列3が+5Vに設定される。このことは、全ての画素が3〜7Vの安定ウィンドウに入ったままであるため、どの画素の状態も変えない。そして、行1は、0から5Vに上昇した後0に戻るパルスによってストローブされる。このことは、(1,1)及び(1,2)画素を作動させ、(1,3)画素を解放させる。このアレイ内の他の画素は影響を受けない。行2を要望通りに設定するため、列2は−5Vに設定され、列1及び列3は+5Vに設定される。次いで、行2に印加される同じストローブが画素(2,2)を作動させ、かつ画素(2,1)及び(2,3)を解放させる。ここでも、このアレイの他の画素は影響を受けない。行3は、列2及び列3を−5Vに、及び列1を+5Vに設定することにより、同様に設定される。行3のストローブは、行3の画素を図5Aに示すように設定する。このフレームを書き込んだ後、この行電位は0であり、この列電位は、+5又は−5Vのいずれかのままとすることができ、上記ディスプレイは、図5Aの構成において安定している。数十又は数百の行及び列のアレイに対して同じ処理手順を用いることができることは正しく認識される。また、行及び列の作動を実行するのに用いる電圧のタイミング、シーケンス及びレベルを、上述した包括的な原理の範囲内で大きく変化させることができること、及び上記の実施例が単に例示であり、どのような作動電圧方法も本明細書に記載したシステム及び方法と共に用いることができることは正しく認識される。

【0023】

図6A及び図6Bは、ディスプレイ装置40の実施形態を示すシステムブロック図である。ディスプレイ装置40は、例えば、携帯電話又は移動電話とすることができる。しかし、ディスプレイ装置40又は、そのわずかな変形例の同じ構成要素も、テレビ及びポータブルメディアプレーヤ等の様々なタイプのディスプレイ装置の例証である。

【0024】

ディスプレイ装置40は、ハウジング41と、ディスプレイ30と、アンテナ43と、スピーカ44と、入力装置48と、マイクロフォン46とを含む。ハウジング41は、一般に、射出成形及び真空成形を含む、当業者には周知の種々の製造プロセスのうちのいずれかによって形成されている。また、ハウジング41は、限定するものではないが、プラスチック、金属、ガラス、ゴム及びセラミック又はこれらの組み合わせを含む様々な材料のうちのいずれかから形成することができる。一実施形態において、ハウジング41は、異なる色の、又は、異なるロゴ、写真又はシンボルからなる他の取外し可能な部分と交換することができる取外し可能な部分(図示せず)を含む。

【0025】

例示的なディスプレイ装置40のディスプレイ30は、本明細書で説明したようなバイステイブルディスプレイを含む様々なディスプレイのうちのいずれかとすることができる。他の実施形態においては、ディスプレイ30は、上述したように、プラズマ、EL、OLED、STN LCD及びTFT LCD等のフラットパネルディスプレイ、あるいは、当業者には周知のCRT又は他のブラウン管装置等の非フラットパネルディスプレイを含む。しかし、本実施形態を説明するため、ディスプレイ30は、本明細書に記載したように、インターフェロメトリック変調ディスプレイを含む。

【0026】

例示的なディスプレイ装置40の一実施形態の構成要素を図6Bに概略的に示す。図示した例示的なディスプレイ装置40は、ハウジング41を含み、またこのハウジングの中に少なくとも部分的に閉じ込められた追加的な構成要素を含むことができる。例えば、一実施形態において、例示的なディスプレイ装置40は、トランシーバ47に結合されているアンテナ43を含むネットワークインタフェース27を含む。トランシーバ47はプロセッサ21に接続されており、このプロセッサは、調整ハードウェア52に接続されている。調整ハードウェア52は、信号を調整する(例えば、信号をフィルタリングする)ように構成してもよい。調整ハードウェア52は、スピーカ45及びマイクロフォン46に接続されている。また、プロセッサ21は、入力装置48及びドライバコントローラ29にも接続されている。ドライバコントローラ29は、フレームバッファ28及びアレイドライバ22に結合されており、このアレイドライバは、ディスプレイアレイ30にも結合されている。電源50は、特定の例示的なディスプレイ装置40デザインに要求される全ての構成要素に電力を供給する。

【0027】

ネットワークインタフェース27は、例示的なディスプレイ装置40が、ネットワークを介して1つ以上のデバイスと通信することができるように、アンテナ43及びトランシーバ47を含む。一実施形態において、ネットワークインタフェース27は、プロセッサ21の要求を軽減するためのいくつかの処理能力も有してもよい。アンテナ43は、当業者は既知である、信号を送受信する何らかのアンテナである。一実施形態において、このアンテナは、IEEE802.11(a)、(b)又は(g)を含むIEEE802.11規格に従ってRF信号を送受信する。別の実施形態においては、このアンテナは、ブルートゥース規格に従ってRF信号を送受信する。携帯電話の場合、このアンテナは、CDMA、GSM、AMPS、又は、無線セル電話ネットワーク内で通信するのに用いられる他の公知の信号を受信するように設計されている。トランシーバ47は、アンテナ43から受け取った信号をプロセッサ21によって受け取り、かつこのプロセッサによってさらに処理できるようにこの信号を前処理する。また、トランシーバ47は、プロセッサ21から受け取った信号を、アンテナ43を介して例示的なディスプレイ装置40から送信できるように、この信号を処理する。

【0028】

代替の実施形態においては、トランシーバ47は、レシーバと置き換えることができる。また別の代替の実施形態においては、ネットワークインタフェース27は、イメージソースと置き換えることができ、このイメージソースは、プロセッサ21へ送るべきイメージデータを格納又は生成することができる。例えば、このイメージソースは、イメージデータを含むDVD(digital video disc)又はハードディスクドライブ、あるいは、イメージデータを生成するソフトウェアモジュールとすることができる。

【0029】

プロセッサ21は、一般に、例示的なディスプレイ装置40の全体の動作を制御する。プロセッサ21は、ネットワークインタフェース27又はイメージソースからの圧縮されたイメージデータ等のデータを受け取り、このデータを処理して生イメージデータに、又は生イメージデータに容易に処理されるフォーマットにする。そして、プロセッサ21は、この処理されたデータをドライバコントローラ29に、又は格納のためにフレームバッファ28へ送る。生データとは、典型的には、イメージ内の各位置におけるイメージ特性を識別する情報を指す。例えば、このようなイメージ特性は、色、飽和及びグレースケールレベルを含むことができる。

【0030】

一実施形態において、プロセッサ21は、マイクロコントローラ、CPU、又は、例示的なディスプレイ装置40の動作を制御する論理ユニットを含む。調整ハードウェア52は、一般に、信号をスピーカ45へ転送し、かつマイクロフォン46から信号を受け取る増幅器及びフィルタを含む。調整ハードウェア52は、例示的なディスプレイ装置40内の個別の構成要素であってもよく、あるいは、プロセッサ21又は他の構成要素に組み込んでもよい。

【0031】

ドライバコントローラ29は、プロセッサ21によって生成された生イメージデータを、プロセッサ21から直接、又はフレームバッファ28から取得して、アレイドライバ22への高速転送に適した生イメージデータに再フォーマット化する。具体的には、ドライバコントローラ29は、表示アレイ30の全域を走査するのに適した時間順序を有するように、この生イメージデータを、ラスタ状フォーマットを有するデータフローに再フォーマット化する。そして、ドライバコントローラ29は、このフォーマット化した情報をアレイドライバ22へ送る。LCDコントローラ等のドライバコントローラ29は、独立型集積回路(IC)としてシステムプロセッサ21と関連付けられる場合があるが、このようなコントローラは、多くの方法で実施することができる。このコントローラは、ハードウェアとしてプロセッサ21に、ソフトウェアとしてプロセッサ21に埋め込んでもよく、又は、ハードウェア内で、アレイドライバ22と完全に一体化してもよい。

【0032】

典型的には、アレイドライバ22は、ドライバコントローラ29から上記フォーマット化された情報を受け取って、このビデオデータを、上記ディスプレイの画素のx−yマトリックスからくる何百及び時には何千ものリードに毎秒多数回印加される波形の並行セットに再フォーマット化する。

【0033】

一実施形態において、ドライバコントローラ29、アレイドライバ22及び表示アレイ30は、本明細書に記載したいずれかの種類のディスプレイに適している。例えば、一実施形態において、ドライバコントローラ29は、従来のディスプレイコントローラ又はバイステイブルディスプレイコントローラ(例えば、インターフェロメトリック変調コントローラ)である。別の実施形態においては、アレイドライバ22は、従来のドライバ又はバイステイブルディスプレイドライバ(例えば、インターフェロメトリック変調ディスプレイ)である。一実施形態において、ドライバコントローラ29は、アレイドライバ22と一体化されている。このような実施形態は、携帯電話、時計及び他の小面積ディスプレイ等の高度に一体化されたシステムにおいては共通である。また別の実施形態においては、表示アレイ30は、典型的な表示アレイ又はバイステイブルディスプレイアレイ(例えば、インターフェロメトリック変調器のアレイを含むディスプレイ)である。

【0034】

入力装置48は、ユーザが例示的なディスプレイ装置40の動作を制御できるようにする。一実施形態において、入力装置48は、QWERTYキーボード又は電話キーパッド、ボタン、スイッチ、タッチスクリーン、圧力又は熱センシティブ膜等のキーパッドを含む。一実施形態において、マイクロフォン46は、例示的なディスプレイ装置40のための入力装置である。マイクロフォン46を、この装置にデータを入力するのに使用する場合、例示的なディスプレイ装置40の動作を制御するために、ユーザがボイスコマンドを与えてもよい。

【0035】

電源50は、公知の様々なエネルギストレージデバイスを含むことができる。例えば、一実施形態において、電源50は、ニッケル−カドミウム電池又はリチウムイオン電池等の充電可能な電池である。別の実施形態において、電源50は、回復可能なエネルギ源、コンデンサ、又は、プラスチックソーラーセル及びソーラーセルペイントを含む太陽電池である。別の実施形態において、電源50は、壁コンセントから電力を受け取るように構成される。

【0036】

いくつかの実施においては、制御プログラム性は、上述したように、電子表示システムのいくつかの箇所に配置することができるドライバコントローラに存する。制御プログラム性は、アレイドライバ22に存する場合もある。当業者は、上述した最適化を、多数のハードウェア及び/又はソフトウェア構成要素のどれでも、及び様々な構成で実施することができることを正しく認識する。

【0037】

上記した原理に従って動作するインターフェロメトリック変調器の構成の詳細は種々の実施形態が考えられる。例えば、図7A−7Eは、可動反射層14及びその支持構造についての5つの異なる実施形態を示している。図7Aは、図1の実施形態の断面図であり、一片の金属材料14が垂直に延在する支持体18上に堆積されている。図7Bでは、可動反射層14は角部のみがテザー32を介して支持体に接続されている。図7Cでは、可動反射層14は、弾性をもつ金属からなる変形可能層34から吊り下げられている。変形可能層34は直接あるいは間接的に変形可能層34の周囲で基板20に接続する。この接続を以下では支持ポストと呼ぶ。図7Dに示す実施形態は、変形可能層34が設けられている支持ポストプラグ42を有する。可動反射層14は図7A−7Cに示すように、空洞部上に吊り下げられた状態を維持するが、変形可能層34は、変形可能層34と光学的スタック16との間の穴を満たすことによって支持ポストを形成しない。支持ポストは、支持ポストプラグ42を形成するのに用いられる平坦化(planarization)材料で形成されている。図7Eに示される実施形態は、図7Dに示す実施形態に基づいているが、図7A−7Cに示される実施形態の1つあるいは図示せぬ他の実施形態にも適用することが可能である。図7Eに示す実施形態において、バス構造44を形成するために、金属または他の導電材料からなる他の層が用いられる。この構成は、インターフェロメトリック変調器の背部に沿った信号経路が可能になるので、基板20上に形成しなければならない多数の電極を除去することが可能になる。

【0038】

図7に示す実施形態において、インターフェロメトリック変調器は、イメージが透明基板20の前面から見える直接的視認デバイスとして機能する。この前面は、変調器が配置される面に対向する。これらの実施形態において、反射層14は、基板20に対向する反射層の面に関して、変形可能層34を含む、インターフェロメトリック変調器の一部を光学的に遮蔽する。これによって、遮蔽領域を構成するとともにイメージ品質に悪影響を与えることなしに動作させることが可能となる。このような遮蔽により図7Eに示すバス構造44が可能となり、アドレシング及び該アドレシングに従った移動などの、変調器の電気機械的特性から変調器の光学特性を分離する能力を提供する。この分離可能な変調器アーキテクチャは、変調器の電気機械的側面と光学的側面に用いられる構造上の設計及び材料を選択するとともに、互いに独立して機能することを可能にする。さらに、図7C−7Eに示す実施形態は、変形可能層34によって実行される、反射層14の光学特性の機械的特性からの分離から得られるさらなる利点を有する。このことは、反射層14に用いられる構造設計と材料とを光学特性に関して最適化するとともに、変形可能層34に用いられる構造設計と材料とを所望の機械特性に関して最適化することを可能にする。

【0039】

ここで、(インターフェロメトリック変調器12a及び12bなどの)インターフェロメトリック変調器は概して光学装置であるが、当業界では、その製造工程において、一般的な半導体製造技術を用いる。すなわち、ある所望の金属あるいは他の層は、多くの材料除去技術に対して“異種”であるとみなされ、多くの異種のあるいは少なくとも異なる化学現象(chemistry)の使用に対応するものである。ときとして、所望の異種のすなわち他の材料に対応する除去のための新たな化学現象の導入は、製造工程において負の連鎖反応を引き起こすかあるいは単に多くの半導体製造施設において使用されないものである。

【0040】

従って、本開示の実施形態は、リフトオフ(離昇)工程技術を用いるインターフェロメトリックデバイスの方法を含む。術語“リフトオフ工程”は、金などのエッチングが困難な金属のパターンデザインに概して用いられる、(製品内に残る材料のエッチングを必要としないで)基板表面上のパターンの定義である製造工程を含む、広い意味での通常及び慣習上の意味を含む。リフトオフ工程において、材料は、(フォトレジストなどの)パターニングされた下層の材料上に堆積され、その後、下層の材料を溶解することによって選択された領域がリフトオフされる。リフトオフ工程において形成されるパターニングされた下層の材料は以下ではリフトオフパターンあるいはリフトオフステンシルと呼ぶ。

【0041】

実施形態によれば、図1の層16a、16bおよび/またはインターフェロメトリック変調器12a及び12bの可動層14a、14bの光学的スタックなどの、インターフェロメトリック変調器の種々の層の製造におけるリフトオフ工程の使用はそれぞれ、各層に関連する材料の堆積及びパターン定義に関連する個別化された化学現象を有利に避けることができる。リフトオフ工程の使用は、製造工程の数を低減して、コストの低減及び製造の複雑さの簡略化につなげることができる。さらに、リフトオフ工程の使用は、インターフェロメトリック変調器の製造で用いられる材料及び施設の選択においてはるかに大きな柔軟性を獲得する。

【0042】

図8は、例えば、図1のインターフェロメトリック変調器12a及び12bなどの、インターフェロメトリック変調器の少なくとも一部を製造するための製造工程200の一般的なフローチャートを示している。図8に示すように、製造工程200はブロック202を含み、リフトオフパターンは、種々の業者から入手可能な、好ましくは汚れの無い透明な基板アッセンブリ上に形成される。本実施形態では、基板はガラスであるが、プラスチックなどの他の基板も使用可能である。一実施形態において、リフトオフパターンは、ポリイミドリリース(polyimide release)層(PiRL)などの第1のリフトオフ材料を堆積することによって形成されるが、これは写真蝕刻されるかあるいは写真蝕刻されない。次に、堆積された第1のリフトオフ材料はフォトレジストにより包囲される。フォトレジストはパターン形状を提供し、第1のリフトオフ材料とフォトレジストとはリフトオフステンシルの形成に即してパターニングされる。他のフォトレジスト層の使用によってパターニングされるPiRL層を使用する工程技術は、例えばミズーリ州、ロラのBrewer Science社から入手可能である。しかしながら、当業者ならば、他のリフトオフ材料も使用可能であることをこの開示から認識するであろう。例えば、リフトオフパターンは、Futurex社から入手可能なパターニング可能なリフトオフ材料からなる単一層を用いて形成される。溶剤の接近(Solvent access)及びリフトオフステンシルの次の除去を達成するために、リフトオフステンシルの厚さは、好ましくは、リフトオフ材料の上に引き続き堆積される層よりも大きい。例えば、一実施形態においては、リフトオフステンシルの厚さは、約1500オングストロームから約50000オングストロームの範囲であり、他の実施形態では、約20000オングストロームから約30000オングストロームの範囲である。

【0043】

製造工程200はさらにブロック204を含み、ここで光学的スタックが形成される。一実施形態において、光学的スタックは基板アッセンブリ及びリフトオフステンシル上に1つまたはそれ以上の材料層を堆積することにより形成される。リフトオフ工程は、光学的スタック内に個々の層のそれぞれを別個に形成するために、あるいは好ましくは光学的スタック内に複数の層を形成するのに用いられる。例えば、図の実施形態において、光学的スタックは、導電層と、下部ミラー金属層と、誘電層とを含む。光学的スタック上に他の材料層を堆積してもよい。例えば、一実施形態において、犠牲層が光学的スタック上に堆積された後、光学的スタックに沿ってリフトオフ工程が施される。全体の積層体における各層(例えば光学的スタック及び犠牲層)の厚さは同じであるかあるいは以下に述べるように互いに異なっている。

【0044】

一実施形態において、導電層は実質的に透明な材料であり、好ましくはITO(インジウムすず酸化物)からなる。透明な導電層の厚さは概して、ディスプレイの行(ロー)に対する導電仕様や、材料の光学透過品質などを考慮して選択される。好ましい実施形態において、透明な導電層の厚さは約200オングストロームから約1000オングストロームの範囲である。例えば、図示の実施形態においては、透明な導電層は約500オングストロームの厚さをもつ。当業者ならばここでの開示から導電層を形成するために亜鉛酸化物を含む他の材料も有利に利用可能であることを認識するであろう。

【0045】

一実施形態において、下部ミラー金属層はクロム(Cr)層を備える。下部ミラー層の厚さは概して材料の光学透過度あるいは他の光学特性を考慮して選択される。同様にして、好ましい実施形態において、ミラー層の厚さは部分的に透過性を備えるように好ましくは約30オングストロームから約150オングストロームの範囲である。例えば、図示の実施形態において、ミラー層は約70オングストロームの厚さを有する。すなわち、本実施形態において、ITO透明導電層は(約500オングストローム)の厚さであり、クロムミラー層(約70オングストローム)の厚さよりも大きい。当業者ならばここでの開示から、下部ミラー金属層は、Crの代わりに、モリブデン(Mo)、チタン(Ti)、及び/またはタングステン(W)を含む他の材料からなることを認識するであろう。

【0046】

一実施形態において、誘電体層は二酸化シリコン(SiO2)層からなる。誘電体層の厚さは概して、バイアス位置における変調器の所望の色を考慮して選択される。すなわち、好ましい実施形態において、誘電体層の厚さは、約100オングストロームから約2500オングストロームの範囲である。例えば、図示の実施形態において、誘電体層は約700オングストロームの厚さをもつ。当業者ならばここでの開示から、誘電体層はここでは誘電体積層体と呼ばれる複数のサブレイヤを含むことを認識するであろう。誘電体層は窒化シリコン(SiN)、酸化アルミニウム(Al2O3)、酸化シリコン(SiOx)などの種々の誘電材料を単体であるいは組み合わせた形で含む(例えばサブレイヤ)。

【0047】

犠牲層は、図示の実施形態においてモリブデン(Mo)層からなる。犠牲層の厚さは概して、非作動位置における変調器の所望のカラーと、以下に述べるように、犠牲層を除去するために用いられる製造工程(例えばドライエッチ)とを考慮して選択される。犠牲層の厚さは好ましくは、約400オングストロームから約6000オングストロームの範囲である。例えば、図示の実施形態において、犠牲層は約2000オングストロームの厚さを有する。当業者ならばここでの開示から、犠牲層はモリブデンに加えてあるいはその代わりに、シリコン(Si)、チタン(Ti)、タングステン(W)、ゲルマニウム(G)などの1つまたはそれ以上の他の容易に除去可能な材料を含むことを認識するであろう。

【0048】

当業者ならばここでの開示から、前記したすべてのあるいは一部の光学的スタックは、少なくとも部分的には実質的に透明な基板への接着を考慮して及び/またはリフトオフパターンが形成された後に残る残渣の可能性を考慮して選択されることを認識するであろう。さらに、光学的スタックは、有機リフトオフ構造に実質的に悪影響を与えない温度で堆積可能な材料から選択される。例えば、一実施形態において、光学的スタックの材料は約250度あるいはそれ以下の温度で堆積される。

【0049】

製造工程200はブロック206を含み、ここでは光学的スタックがリフトオフ工程を用いてパターニングされる。ここに開示された技術により概して理解されるように、リフトオフ工程は一部あるいはすべてのリフトオフ材料と反応及び/または当該材料を溶解する化学現象を使用し、例えば光学的スタックの下にリフトオフステンシルを形成する。リフトオフ材料を除去することによって、リフトオフ材料の上の光学的スタックの材料はもはや付着せず、廃棄化学現象(waste chemistry)によって基板アッセンブリから浮遊あるいは離昇される。光学的スタック例えば犠牲層の上に形成された他の層は、光学的スタックに沿って離昇される。すなわち、リフトオフ工程は、既知の化学現象を用いて複数の異なる異種の層のパターニングを有利に提供する。リフトオフ材料の除去は種々の方法により達成される。例えば、もはや付着していない材料の除去のためのすすぎ工程に続いて、リフトオフ材料は、リフトオフ材料と反応する及び/または該材料を溶解する液状、ガス状あるいは蒸気のリフトオフ化学現象に対して露出される。リフトオフ化学現象は好ましくは液状で適用され、ここではウエットエッチリフトオフと呼ぶことにする。

【0050】

好ましい実施形態において、パターニングされた残りの層は、インターフェロメトリック変調器12a、12bなどの変調器のロー(行)電極、光学的スタックそして犠牲層を形成する。

【0051】

製造工程200はブロック208を含み、ここではポスト18などの支持体構造が形成される。例えば、例示された実施形態において、ポスト18の材料はパターニング可能あるいはパターニング不可の正あるいは負のフォトレジストからなる。一実施形態において、最上面のフォトレジストが堆積され、材料を最上面からパターニングするのに適切に配置されたレチクルが用いられる。化学的機械的平坦化(CMP)などの平坦化技術が、余分のフォトレジスト及び/または材料を除去するのに用いられる。一実施形態において、背面フォトレジストは背面露出(基板アッセンブリは好ましくは透明である)を用いてパターニングされ、光学的スタックパターンが適切なアライメント(マスク)を有利に形成する。一実施形態において、CMPは余分のフォトレジスト及び/または材料を除去するのに用いられる。

【0052】

当業者ならばここでの開示から、平坦化されたレジスト構造の形状を変更または改善するために特別なCMP工程が使用されることを認識するであろう。さらに、当業者ならば、スピンオンガラス(SOG)、有機平坦化材料などを含む、他の材料が一部あるいはすべてのポストを形成するのに用いられることを認識するであろう。当業者ならばここでの開示から、一部の材料または工程の使用は、CMP工程を低減または完全に除去することを認識するであろう。例えば、スピンオフガラスは、パターニングされて平坦化工程を経ずに単に残される。そのような工程はバンプを残すが、それは装置の動作または信頼性を実質的に変更するものではない。

【0053】

製造工程200はブロック210を含み、ここでは第2のリフトオフパターンが形成される。使用されるリフトオフ材料はブロック202及び第1のリフトオフパターンに関して上記した材料と同じかまたは異なっている。当業者ならばここでの開示から、リフトオフ材料は、ロー(行)電極層とのアライメントを確実にするように及び/またはリフトオフパターンの形成後に光学的スタックの清浄さを増大するように選択される。

【0054】

製造工程200はブロック212を含み、ここでは1つまたはそれ以上の屈曲(flex)層が形成される。一実施形態において、屈曲層は部分的に製造された変調器およびリフトオフ材料の上に1つまたはそれ以上の層を堆積することによって形成される。一実施形態において、屈曲層はミラー層と弾性をもつ金属導電層とからなる。一実施形態において、ミラー層はアルミニウム(AL)層からなる。ミラー層の厚さは概して材料の反射率及び材料構造の完全さを考慮して選択される。例えば、材料は独立しており、製造工程のステップと通常の動作におけるストレスに耐えるのに十分な厚さである。さらに、ミラー層は、例示的な実施形態において完全な反射性をもつのに十分な厚さである。一実施形態において、ミラー層の厚さは約80オングストロームから約1ミクロンの範囲である。例えば、例示的実施形態において、ミラー層は約300オングストロームの厚さを有する。当業者ならばここでの開示から、ミラー層はアルミニウムに加えてあるいはその代わりに、銀(Ag)または金(Au)などの1つまたはそれ以上の他の反射材料を含むことを認識するであろう。屈曲層は導電性、反射性及び/または弾性をもつ、すなわち、例えば、単一の構造は電極層、ミラー層そして変形可能な層として機能する。一部の実施形態において、例えば図7Cに示すように、反射層14は、変形可能な層34から吊り下げられ、両方が電極層として機能する。種々の他の構成が使用される。

【0055】

一実施形態において、屈曲層における弾性金属層はニッケル(Ni)層からなる。導電層の厚さは概して、材料構造の完全さと製造工程ステップに耐える能力とを考慮して選択される。一実施形態において、弾性金属導電層の厚さは約300オングストロームから約1ミクロンの範囲である。例えば、例示の実施形態において、屈曲層における導電層は、約1000オングストロームの厚さをもつ。当業者ならばここでの開示から、導電層は、ニッケルに加えてあるいはその代わりに、クロム、アルミニウム、及び/またはアルミニウム合金などの1つまたはそれ以上の他の導電材料を含むことを認識するであろう。導電層は金属酸化サンドイッチ構造などの複合構造を含む。

【0056】

当業者ならばここでの開示から、前記したすべてのあるいは一部の屈曲層は、少なくとも部分的には光学的スタックへの接着(あるいは接着の欠如)及び/または支持構造またはポスト層への接着を考慮して選択される。例えば、図1において、屈曲層14bの材料は好ましくは、インターフェロメトリック変調器12bの作動中における固定された部分的に反射性の層16bに対する接着力が最小になるように選択される。さらに、屈曲層の材料は、例えば導電層とミラー層との接着力が最大になるように互いの接着を考慮して選択される。

【0057】

製造工程200はブロック214を含み、ここで屈曲層はリフトオフ工程を用いてパターニングされる。好ましい実施形態において、残りのパターニングされた屈曲層は、インターフェロメトリック変調器12a、12bなどのインターフェロメトリック変調器の第2のミラー、カラム(列)電極そして機械的層を形成する。屈曲層は、例えば図7Cに示されるような構成を形成するために、ミラー層から別個にパターニングされる。リフトオフ工程は、比較的厚いミラー層のパターニングを有利に実現するために用いられる。屈曲層は好ましくは高導電性であり、引張応力内にある。屈曲層は好ましくは製造工程のストレスに耐えるためにかつ平坦化材料に接着するために内部的材料の完全さをもつ。

【0058】

一実施形態において、リフトオフステンシルの除去は好ましくは第2のミラーのパターニングされた領域を形成し、図14,15(以下に述べる)に示すように、下にある犠牲層の一部を露出する。この実施形態に示されるリフトオフ工程は、屈曲層の位置が、最終的な構造のために堆積材料をエッチングすることなしに(この場合、屈曲層を直接エッチングすることなしに)除去されることを可能にする。屈曲層の当該部分を従来の方法でエッチング除去することは、下にある犠牲層のエッチングが不十分になってしまうという問題を引き起こす。

【0059】

当業者ならばここでの開示から、種々の他の工程ステップにより、例えばインターフェロメトリック変調器12a(図1)の空洞部19などの空洞部を形成するために犠牲層を有利に除去できることを認識するであろう。さらに、上記したことに基づいて、当業者ならばここでの開示から、リフトオフ工程によって、エッチング両立性の問題、異なる新たな化学現象の問題を有利に避けながら、製造工程において特に上記した光学的スタックの製造におけるパターン形成を有利に強化するのに製造工程200が用いられることを認識するであろう。製造工程200は工程ステップを有利に減らすとともに変調器製造者のために層材料と製造施設の入手と選択の度合いを増大するのに用いられる。

【0060】

図9A及び9Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器300の平面図、断面図である。図に示すように、変調器300は、透明な基板アッセンブリ302と、パターニングされたリフトオフ材料PiRL304と、フォトレジスト306とを含み、全体でリフトオフステンシル308を形成している。図9Bに示すように、リフトオフ材料は、PiRL材料304を選択的にオーバエッチングすることによって逆さ台形または略T字形状を形成する。T字形状は、該T字形状の上部に堆積された材料が、T字形状の底部近くの基板上に堆積された材料から分離されるので、リフトオフを行うのに都合がよい。T字形状は、リフトオフステンシル308がリフトオフ化学現象に対して露出することを実現する。以下に詳述するように、ポスト602aは領域312内に形成され、(下部電極を互いに分離する)レール602bは図9Aに示すように領域310内に形成される。

【0061】

図10A及び10Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器400の平面図、断面図である。図に示すように、変調器400は、リフトオフステンシル308と基板302の上に形成された積層体402を含む。

【0062】

図10Bに示すように、積層体402は、ITO層404、Cr層406、誘電層408そして犠牲Mo層410を含む複数材料層からなる。図15を参照して後述するように、ITO層404、Cr層406、誘電層408は最終的に光学的スタック806に組み込まれる。上記したように、リフトオフステンシル308の厚さは好ましくは、リフトオフステンシル308を後で除去するために用いられる化学現象への縦方向のアクセスを可能にするために、積層体402の厚さよりも大きい。

【0063】

図11A及び11Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器500の平面図、断面図である。図に示すように、変調器500は、リフトオフ工程を行った後にパターニングされた積層体402を含み、この間に、リフトオフステンシル308は(図10Bに示すようにリフトオフステンシル308上に堆積された積層体402の一部とともに)除去される。パターニングされた積層体402は下に配置された光学的スタック404−408(図10B)を含む。光学的スタック404−408は(上に配置された犠牲層410とともに)、リフトオフの後に残る材料から形成されるという点において正にパターニングされる。同様にして、変調器500は、リフトオフステンシル308の除去によって形成され、基板302上に負にパターニングされた領域502a、502bを含む。

【0064】

図12Aは平面図であり、図12B、12Cは、本実施形態による部分的に製造されたインターフェロメトリック変調器600の断面図である。図に示すように、変調器600は、前面アライメント露出技術(図12B)あるいは背面自己整合露出技術(図12C)を用いて、放射606に対する露出によってレチクル604を通して形成された支持体構造602a(ポスト)及び602b(レール)を含む。ポスト602a及びレール602bはそれぞれ(図11A及び11B)、基板302上に負にパターニングされた領域502a、502b内に形成される。

【0065】

負にパターニングされた領域を形成するのにリフトオフ工程を使用することは、特に厚い層を除去する場合において、パターニングすべき材料を直接エッチングすることに比較して有利であることが見出された。例えば、直接的なエッチング工程により形成された負にパターニングされた領域は、エッチング剤がパターン材料をアンダーカットしやすいため、上に位置するパターン材料(例えばフォトレジスト)のサイズよりも幾分大きくなる傾向がある。ポスト構造が最小の空間を占有することが望ましい実施形態においては、リフトオフ工程の使用は、ポスト構造が形成される、所望のサイズに小さくされた負にパターニングされた領域の形成を確実にする。すなわち、好ましい実施形態においては、リフトオフ工程は、インターフェロメトリック変調器の製造中に負にパターニングされた領域を形成するために、より好ましくはポスト構造が後で形成される負にパターニングされた領域を形成するのに使用される。多くの実施形態において、ウエットエッチングリフトオフ工程は、インターフェロメトリック変調器の製造において負にパターニングされた領域を形成する場合に、直接エッチング(ウエット及び/またはドライ)と比較して特に有利である。

【0066】

リフトオフ工程の使用は、直接エッチング工程と比較して多数の材料層を除去する場合、特に比較的薄い層の下に位置する比較的厚い層を除去する場合に有利であることが見出された。材料が異なると直接エッチングの速度も異なる傾向があるので、多数の層を除去するために等方性のエッチング剤を使用するとしばしば側壁が不規則になる。これは種々の層において材料が異なることより縦方向のエッチング速度が異なるためである。例えば、より厚いITO層の上の薄いクロム層を含む積層体のウエットエッチングは、ITO層を除去するのに用いられるエッチング剤に対する露出が、厚いITO層の所望の程度のエッチングを獲得するために比較的長くなるために、クロム層のアンダーカットにつながる。すなわち、好ましい実施形態において、リフトオフ工程は、多数の材料層を除去するためにインターフェロメトリック変調器の製造において使用される。多くの実施形態において、ウエットエッチングリフトオフ工程は特に、インターフェロメトリック変調器の製造において多数の材料層を除去する場合に、直接エッチングと比較して有利である。

【0067】

図13A及び13Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器700の平面図、断面図である。断面図13Bは図12Bに示される線と異なる線に沿ったものであることに注意されたい。図に示すように、変調器700は、パターニングされたリフトオフ材料PiRL704と、フォトレジスト706とを含み、全体でリフトオフステンシル708を形成する。図13Bに示すように、リフトオフステンシル708は、リフトオフステンシル308の形成の場合に上記した方法と類似の方法によって積層体402上に略T字形状に形成される。

【0068】

図14A及び14Bはそれぞれ、本実施形態による部分的に製造されたインターフェロメトリック変調器800の平面図、断面図である。図に示すように、変調器800は、積層体402上に形成された屈曲層802、リフトオフステンシル708、そしてポスト602aを含む。14Bに示すように、屈曲層802はAIミラー層804とNi導電層806とからなる。AIミラー層804とNi導電層806とは例えば物理気相成長法あるいはスパッタリング堆積などの種々の方法により形成される。

【0069】

図15Aは平面図であり、図15B、15Cは、本実施形態によるインターフェロメトリック変調器600の断面図である。図に示すように、変調器900は、リフトオフ工程が行われた(この間、リフトオフステンシル708が(図14Bに示すようにリフトオフステンシル708上に堆積された屈曲層802の一部とともに)除去された)後の、(AIミラー層804及びNi導電層806を含む)パターニングされた屈曲層802を含む。リフトオフステンシル708を除去すると、開口902、904が形成される。図15B及び15Cは積層体402からの犠牲層410の後工程による除去を示しており、ITO層404、Cr層406、誘電体層408を含む光学的スタック806を形成する。犠牲層410を除去すると、変調器900の空洞部19が形成される。ポスト602aはパターニングされた屈曲層802のための支持体構造であり、空洞部19を規定する役目をもつ。一実施形態において、除去は、Mo犠牲層410と化学的に反応させるために、開口902、904を通して流れるキセノンフッ化物(XeF2)に対して変調器800を露出することによって達成され、ドライエッチング工程によって犠牲層が除去されて空洞部19を形成する。

【0070】

インターフェロメトリック変調器の製造工程の前記の実施形態は好ましい実施形態の観点から記載されたが、当業者ならばここでの開示から他の実施形態を実現することも可能である。例えば、リフトオフ工程は、光学的スタックあるいは屈曲層の種々の層の1つまたは数個に有利に適用されるか、あるいは全く適用されない。さらに、種々のインターフェロメトリックデバイス構造及び形状は上記したリフトオフ工程を用いて形成される。例えば、ミラー機能は例えば屈曲層の機械的あるいは弾性を持つ機能から有利に分離され、これによって、実質的に硬いミラー層14が図7Cに示すように機械的層34から空洞部19の上方に吊り下げられる。そのような構造を製造するのに適切な方法は、定期的な実験によって決定され、例えば、ミラー層14の製造のための第1のリフトオフ工程及び機械的層34の製造のための第2のリフトオフ工程を含む。当業者ならば個々のインターフェロメトリック変調器の製造に適用可能であるとしてここに記述された方法は、インターフェロメトリック変調器アレイの製造にも適用可能であることを認識するであろう。同様にして、インターフェロメトリック変調器アレイの製造に適用可能であるとしてここに記述された方法は、個々のインターフェロメトリック変調器の製造にも適用可能である。

【0071】

当業者ならば多数及び種々の変形例が本発明の精神から逸脱することなしに実現可能であることが認識するであろう。したがって、本発明の形態は例示のみであり本発明の権利範囲を限定することを意図するものではないことが理解されるべきである。

【図面の簡単な説明】

【0072】

この発明のこれらおよび他の側面は、ある実施形態の図面を参照して説明される。図は一定の率で拡大縮小したものではなく、かつ本発明を例示的に説明するためのものであり、限定する意図で用いられるものではない。

【図1】図1は、第1のインターフェロメトリック変調器の移動可能な反射層が開放された(relaxed)位置にあり、第2のインターフェロメトリック変調器の移動可能な反射層が作動位置にあるインターフェロメトリック変調器ディスプレイの一実施形態の一部を示す等角図である。

【図2】図2は、3×3のインターフェロメトリック変調器ディスプレイを組み込んだ電子デバイスの一実施形態を示すシステムブロック図である。

【図3】図3は、図1のインターフェロメトリック変調器の例示的な実施形態における移動可能ミラー位置対印加電圧の図である。

【図4】図4は、インターフェロメトリック変調器ディスプレイを駆動するのに用いられる行及び列電圧の組を示す図である。

【図5A】図5Aは、図2の3×3のインターフェロメトリック変調器ディスプレイにおけるディスプレイデータの例示的なフレームを示す図である。

【図5B】図5Bは、図5Aのフレームに書き込むのに用いられる行及び列信号の例示的タイムチャートである。

【図6A】図6Aは、複数のインターフェロメトリック変調器を備えたビジュアルディスプレイ装置の一実施形態を示すシステムブロック図である。

【図6B】図6Bは、複数のインターフェロメトリック変調器を備えたビジュアルディスプレイ装置の一実施形態を示すシステムブロック図である。

【図7A】図7Aは、図1の装置の断面図である。

【図7B】図7Bは、インターフェロメトリック変調器の他の実施形態の断面図である。

【図7C】図7Cは、インターフェロメトリック変調器のさらに他の実施形態の断面図である。

【図7D】図7Dは、インターフェロメトリック変調器のさらに他の実施形態の断面図である。

【図7E】図7Eは、インターフェロメトリック変調器のさらに他の実施形態の断面図である。

【図8】図8は、一実施形態による、図1の変調器などのインターフェロメトリック変調器における製造工程の例示的フローチャートである。

【図9A】図9Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図9B】図9Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図10A】図10Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図10B】図10Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図11A】図11Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図11B】図11Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図12A】図12Aは図8の製造工程の実施形態を用いて一部製造された平面図である。

【図12B】図12Bは図8の製造工程の実施形態を用いて一部製造された断面図である。

【図12C】図12Cは図8の製造工程の実施形態を用いて一部製造された断面図である。

【図13A】図13Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図13B】図13Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図14A】図14Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図14B】図14Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図15A】図15Aは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の平面図である。

【図15B】図15Bは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【図15C】図15Cは、図8の製造工程の実施形態を用いて一部製造されたインターフェロメトリック変調器の断面図である。

【特許請求の範囲】

【請求項1】

インターフェロメトリック変調器の製造方法であって、

少なくとも第1のパターニング製造工程を用いて透明な基板上に光学的スタックを形成することと、

前記基板上に支持体構造を形成することと、

少なくとも第2のパターニング製造工程を用いて前記光学的スタック及び前記支持体構造上に上部ミラー層を形成することと、を具備し、

前記光学的スタック、前記支持体構造、前記上部ミラー層の少なくとも1つの表面に空洞部が形成され、前記上部ミラー層の前記空洞部への一部の移動は、前記基板の表面から認識される光学特性を制御可能かつ予測可能な方法で変化させ、前記第1及び第2の製造工程の少なくとも1つはリフトオフ工程を具備する方法。

【請求項2】

前記光学的スタックは導電層、下部ミラー金属層、誘電体層の少なくとも1つを具備する請求項1に記載の方法。

【請求項3】

前記光学的スタックは下部ミラー金属層を具備する請求項2に記載の方法。

【請求項4】

少なくとも前記下部ミラー金属層はロー(行)電極を形成する請求項3に記載の方法。

【請求項5】

前記光学的スタック上に前記上部ミラー層を形成することは、前記光学的スタックと前記上部ミラー層間に犠牲層を堆積することを具備する請求項1に記載の方法。

【請求項6】

前記空洞部を形成するために前記犠牲層の少なくとも一部を除去することをさらに具備する請求項5に記載の方法。

【請求項7】

前記リフトオフ工程は、前記犠牲層の少なくとも一部とともに前記光学的スタックの少なくとも一部を離昇することを具備する請求項5に記載の方法。

【請求項8】

前記上部ミラー層は弾性をもつ金属導電層を具備する請求項1に記載の方法。

【請求項9】

少なくとも前記上部ミラー層はカラム(列)電極を構成する請求項8に記載の方法。

【請求項10】

前記第1及び第2の製造工程は、リフトオフ工程を具備する請求項1に記載の方法。

【請求項11】

イメージングアプリケーションを形成することをさらに具備する請求項1に記載の方法。

【請求項12】

前記イメージングアプリケーションはフラットパネルディスプレイを具備する請求項11に記載の方法。

【請求項13】

前記フラットパネルディスプレイはモバイル電子デバイスの一部である請求項12に記載の方法。

【請求項14】

前記イメージングアプリケーションは、ハンドヘルドコンピュータ、パーソナルデジタルアシスタント、ラップトップコンピュータ、携帯電話、ハンドヘルドビデオゲームデバイス、家庭機器、テレビ、時計、キオスク、自動車計算装置の少なくとも1つを具備する請求項11に記載の方法。

【請求項15】

前記リフトオフ工程は概してT字形状のリフトオフステンシルを形成することを具備する請求項1に記載の方法。

【請求項16】

前記リフトオフ工程はリフトオフステンシルをパターニングすることを具備する請求項1に記載の方法。

【請求項17】

前記リフトオフステンシルのパターニングはポリマー上にフォトレジストを堆積することを具備する請求項16に記載の方法。

【請求項18】

前記リフトオフ工程は、リフトオフステンシルを除去するためのウエットエッチングを具備する請求項1に記載の方法。

【請求項19】

前記上部ミラー層上に変形可能な層を堆積することをさらに具備する請求項1に記載の方法。

【請求項20】

前記上部ミラー層は犠牲層の除去後、前記変形可能な層から吊り下げられる請求項19に記載の方法。

【請求項21】

請求項1の方法によって製造されるインターフェロメトリック変調器。

【請求項22】

請求項1の方法によって製造されるインターフェロメトリック変調器のアレイからなるディスプレイシステム。

【請求項23】

前記アレイと電気通信可能であり、イメージデータを処理するように構成されたプロセッサと、

前記プロセッサと電気通信可能なメモリ装置と、をさらに具備する請求項22に記載のディスプレイ装置。

【請求項24】

少なくとも1つの信号を前記アレイに送信するように構成された請求項23に記載のディスプレイ装置。

【請求項25】

前記イメージデータの少なくとも一部を前記駆動回路に送信するように構成されたコントローラをさらに具備する請求項24に記載のディスプレイ装置。

【請求項26】

前記イメージデータを前記プロセッサに送信するように構成されたイメージ源モジュールをさらに具備する請求項23に記載のディスプレイ装置。

【請求項27】

前記イメージ源モジュールは、受信機、トランシーバ、送信器の少なくとも1つを具備する請求項26に記載のディスプレイ装置。

【請求項28】

入力データを受信するとともに当該入力データを前記プロセッサに送信するように構成された入力装置をさらに具備する請求項23に記載のディスプレイ装置。

【請求項29】

インターフェロメトリック変調器の製造方法であって、

基板上にリフトオフステンシルを形成することと、

前記リフトオフステンシルと前記基板上に第1の材料層を堆積することと、

前記第1の材料層上に第2の材料層を堆積することと、

前記リフトオフステンシルを除去して、前記第2の材料層と前記第1の材料層とからなるパターニングされた領域を形成することと、を具備する方法。

【請求項30】

前記第1の材料層はITO(インジウムすず酸化物)であることを特徴とする請求項29に記載の方法。

【請求項31】

前記第2の材料層は、クロム、モリブデン、チタンからなる群から選択された少なくとも1つの金属を具備する請求項30に記載の方法。

【請求項32】

前記第2の材料層はモリブデンを具備する請求項31に記載の方法。

【請求項33】

前記第1の材料層は前記第2の材料層の厚さよりも大きい厚さをもつ請求項31に記載の方法。

【請求項34】

前記第2の材料層上に第3の材料層を堆積することをさらに具備する請求項29に記載の方法。

【請求項35】

前記第3の材料層は、誘電材料を具備する請求項34に記載の方法。

【請求項36】

前記第3の材料層上に第4の材料層を堆積することをさらに具備する請求項34に記載の方法。

【請求項37】

前記第4の材料層は、モリブデンを具備する請求項36に記載の方法。

【請求項38】

請求項29の方法によって製造されたインターフェロメトリック変調器。

【請求項39】

インターフェロメトリック変調器のアレイを製造する方法であって、

リフトオフステンシルを用いて基板上に複数の正にパターニングされた光学的スタックと、複数の負にパターニングされたポスト領域とを形成することと、

前記負にパターニングされたポスト領域内に複数のポスト構造を形成すること、とを具備する方法。

【請求項40】

請求項39の方法によって製造されたインターフェロメトリック変調器のアレイ。

【請求項41】

ディスプレイ装置の製造方法であって、

第1のミラー層を堆積することと、

前記第1のミラー層上に犠牲層を堆積することと、

前記犠牲層上にリフトオフステンシルを形成することと、

前記リフトオフステンシル上に第2のミラー層を堆積することと、

前記リフトオフステンシルを除去することによって、前記第2のミラー層のパターニングされた領域を形成して前記犠牲層の一部を露出することと、

を具備する方法。

【請求項42】

請求項41の方法によって製造されたディスプレイ装置。

【請求項1】

インターフェロメトリック変調器の製造方法であって、

少なくとも第1のパターニング製造工程を用いて透明な基板上に光学的スタックを形成することと、

前記基板上に支持体構造を形成することと、

少なくとも第2のパターニング製造工程を用いて前記光学的スタック及び前記支持体構造上に上部ミラー層を形成することと、を具備し、

前記光学的スタック、前記支持体構造、前記上部ミラー層の少なくとも1つの表面に空洞部が形成され、前記上部ミラー層の前記空洞部への一部の移動は、前記基板の表面から認識される光学特性を制御可能かつ予測可能な方法で変化させ、前記第1及び第2の製造工程の少なくとも1つはリフトオフ工程を具備する方法。

【請求項2】

前記光学的スタックは導電層、下部ミラー金属層、誘電体層の少なくとも1つを具備する請求項1に記載の方法。

【請求項3】

前記光学的スタックは下部ミラー金属層を具備する請求項2に記載の方法。

【請求項4】

少なくとも前記下部ミラー金属層はロー(行)電極を形成する請求項3に記載の方法。

【請求項5】

前記光学的スタック上に前記上部ミラー層を形成することは、前記光学的スタックと前記上部ミラー層間に犠牲層を堆積することを具備する請求項1に記載の方法。

【請求項6】

前記空洞部を形成するために前記犠牲層の少なくとも一部を除去することをさらに具備する請求項5に記載の方法。

【請求項7】

前記リフトオフ工程は、前記犠牲層の少なくとも一部とともに前記光学的スタックの少なくとも一部を離昇することを具備する請求項5に記載の方法。

【請求項8】

前記上部ミラー層は弾性をもつ金属導電層を具備する請求項1に記載の方法。

【請求項9】

少なくとも前記上部ミラー層はカラム(列)電極を構成する請求項8に記載の方法。

【請求項10】

前記第1及び第2の製造工程は、リフトオフ工程を具備する請求項1に記載の方法。

【請求項11】

イメージングアプリケーションを形成することをさらに具備する請求項1に記載の方法。

【請求項12】

前記イメージングアプリケーションはフラットパネルディスプレイを具備する請求項11に記載の方法。

【請求項13】

前記フラットパネルディスプレイはモバイル電子デバイスの一部である請求項12に記載の方法。

【請求項14】

前記イメージングアプリケーションは、ハンドヘルドコンピュータ、パーソナルデジタルアシスタント、ラップトップコンピュータ、携帯電話、ハンドヘルドビデオゲームデバイス、家庭機器、テレビ、時計、キオスク、自動車計算装置の少なくとも1つを具備する請求項11に記載の方法。

【請求項15】

前記リフトオフ工程は概してT字形状のリフトオフステンシルを形成することを具備する請求項1に記載の方法。

【請求項16】

前記リフトオフ工程はリフトオフステンシルをパターニングすることを具備する請求項1に記載の方法。

【請求項17】

前記リフトオフステンシルのパターニングはポリマー上にフォトレジストを堆積することを具備する請求項16に記載の方法。

【請求項18】

前記リフトオフ工程は、リフトオフステンシルを除去するためのウエットエッチングを具備する請求項1に記載の方法。

【請求項19】

前記上部ミラー層上に変形可能な層を堆積することをさらに具備する請求項1に記載の方法。

【請求項20】

前記上部ミラー層は犠牲層の除去後、前記変形可能な層から吊り下げられる請求項19に記載の方法。

【請求項21】

請求項1の方法によって製造されるインターフェロメトリック変調器。

【請求項22】

請求項1の方法によって製造されるインターフェロメトリック変調器のアレイからなるディスプレイシステム。

【請求項23】

前記アレイと電気通信可能であり、イメージデータを処理するように構成されたプロセッサと、

前記プロセッサと電気通信可能なメモリ装置と、をさらに具備する請求項22に記載のディスプレイ装置。

【請求項24】

少なくとも1つの信号を前記アレイに送信するように構成された請求項23に記載のディスプレイ装置。

【請求項25】

前記イメージデータの少なくとも一部を前記駆動回路に送信するように構成されたコントローラをさらに具備する請求項24に記載のディスプレイ装置。

【請求項26】

前記イメージデータを前記プロセッサに送信するように構成されたイメージ源モジュールをさらに具備する請求項23に記載のディスプレイ装置。

【請求項27】

前記イメージ源モジュールは、受信機、トランシーバ、送信器の少なくとも1つを具備する請求項26に記載のディスプレイ装置。

【請求項28】

入力データを受信するとともに当該入力データを前記プロセッサに送信するように構成された入力装置をさらに具備する請求項23に記載のディスプレイ装置。

【請求項29】

インターフェロメトリック変調器の製造方法であって、

基板上にリフトオフステンシルを形成することと、

前記リフトオフステンシルと前記基板上に第1の材料層を堆積することと、

前記第1の材料層上に第2の材料層を堆積することと、

前記リフトオフステンシルを除去して、前記第2の材料層と前記第1の材料層とからなるパターニングされた領域を形成することと、を具備する方法。

【請求項30】

前記第1の材料層はITO(インジウムすず酸化物)であることを特徴とする請求項29に記載の方法。

【請求項31】

前記第2の材料層は、クロム、モリブデン、チタンからなる群から選択された少なくとも1つの金属を具備する請求項30に記載の方法。

【請求項32】

前記第2の材料層はモリブデンを具備する請求項31に記載の方法。

【請求項33】

前記第1の材料層は前記第2の材料層の厚さよりも大きい厚さをもつ請求項31に記載の方法。

【請求項34】

前記第2の材料層上に第3の材料層を堆積することをさらに具備する請求項29に記載の方法。

【請求項35】

前記第3の材料層は、誘電材料を具備する請求項34に記載の方法。

【請求項36】

前記第3の材料層上に第4の材料層を堆積することをさらに具備する請求項34に記載の方法。

【請求項37】

前記第4の材料層は、モリブデンを具備する請求項36に記載の方法。

【請求項38】

請求項29の方法によって製造されたインターフェロメトリック変調器。

【請求項39】

インターフェロメトリック変調器のアレイを製造する方法であって、

リフトオフステンシルを用いて基板上に複数の正にパターニングされた光学的スタックと、複数の負にパターニングされたポスト領域とを形成することと、

前記負にパターニングされたポスト領域内に複数のポスト構造を形成すること、とを具備する方法。

【請求項40】

請求項39の方法によって製造されたインターフェロメトリック変調器のアレイ。

【請求項41】

ディスプレイ装置の製造方法であって、

第1のミラー層を堆積することと、

前記第1のミラー層上に犠牲層を堆積することと、

前記犠牲層上にリフトオフステンシルを形成することと、

前記リフトオフステンシル上に第2のミラー層を堆積することと、

前記リフトオフステンシルを除去することによって、前記第2のミラー層のパターニングされた領域を形成して前記犠牲層の一部を露出することと、

を具備する方法。

【請求項42】

請求項41の方法によって製造されたディスプレイ装置。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6A】

【図6B】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【図8】

【図9A】

【図9B】

【図10A】

【図10B】

【図11A】

【図11B】

【図12A】

【図12B】

【図12C】

【図13A】

【図13B】

【図14A】

【図14B】

【図15A】

【図15B】

【図15C】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6A】

【図6B】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【図8】

【図9A】

【図9B】

【図10A】

【図10B】

【図11A】

【図11B】

【図12A】

【図12B】

【図12C】

【図13A】

【図13B】

【図14A】

【図14B】

【図15A】

【図15B】

【図15C】

【公表番号】特表2008−514991(P2008−514991A)

【公表日】平成20年5月8日(2008.5.8)

【国際特許分類】

【出願番号】特願2007−533505(P2007−533505)

【出願日】平成17年9月2日(2005.9.2)

【国際出願番号】PCT/US2005/031693

【国際公開番号】WO2006/036470

【国際公開日】平成18年4月6日(2006.4.6)

【出願人】(505258472)アイディーシー、エルエルシー (122)

【Fターム(参考)】

【公表日】平成20年5月8日(2008.5.8)

【国際特許分類】

【出願日】平成17年9月2日(2005.9.2)

【国際出願番号】PCT/US2005/031693

【国際公開番号】WO2006/036470

【国際公開日】平成18年4月6日(2006.4.6)

【出願人】(505258472)アイディーシー、エルエルシー (122)

【Fターム(参考)】

[ Back to top ]