リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

【発明の詳細な説明】

【技術分野】

【0001】

この出願は、2011年11月23日に出願された米国特許出願第13/304,226に対して優先権を主張する。上記文献は、全体として本明細書において参照することによって援用される。

【背景技術】

【0002】

集積回路は、しばしば、揮発性メモリ要素を含む。一般的な揮発性メモリ要素は、交差連結されたインバータ(ラッチ)に基づく。集積回路が電力供給されている場合に限り、揮発性メモリ要素は、データを保持する。電力がなくなる場合、揮発性メモリ要素内のデータがなくなる。例えば、静的ランダムアクセスメモリ(SRAM)チップは、1つのタイプの揮発性メモリ要素であるSRAMセルを含む。揮発性メモリ要素は、プログラマブル論理デバイス集積回路においても使用され得る。

【0003】

揮発性メモリ要素は、ソフトエラーアップセットとして知られた現象の影響を受ける。ソフトエラーアップセットイベントは、宇宙線と、集積回路およびそれらのパッケージ内に埋め込まれた放射性不純物とによって引き起こされる。宇宙線および放射性不純物は、高エネルギー原子粒子(中性子およびアルファ粒子)を生成する。メモリ要素は、パターン化されたシリコン基板から形成されるトランジスタおよび他の部品を含む。原子粒子がメモリ要素内のシリコンと衝突する場合に、電子−正孔対が生成される。電子−正孔対は、メモリ要素内の充電されたノードが放電し、メモリ要素の状態が反転するようにし得る伝導経路を生成する。例えば、「1」がメモリ要素内に格納された場合に、ソフトエラーアップセットイベントは、「1」が「0」に変わるようにし得る。

【0004】

集積回路内のアップセットイベントは、メモリ要素内に格納されたデータを壊し、システム性能にとって重大な影響を有し得る。あるシステムアプリケーション(例えば、電気通信機器の遠隔インストレーション)において、欠点のある機器を修復することは、極めて負担となる。集積回路がソフトエラーアップセットイベントに対して優れた不感性をみせなければ、それらは、上記タイプのアプリケーションに対して不適切である。

【発明の概要】

【課題を解決するための手段】

【0005】

(要約)

メモリセルを有する集積回路が提供される。集積回路は、メモリセルアレイを制御するように動作可能な制御回路網を含み得る。制御回路網は、アドレシング回路網、データレジスタ回路網、書き込みドライバー回路網、読み取り感知回路網、および他の制御回路網のような回路網を含み得る。

【0006】

集積回路は、ナノ電気機械的(NEM)リレーテクノロジーを用いて形成されたデバイスを有する第1の部分と、相補型金属酸化物半導体(CMOS)テクノロジーを用いて形成されたデバイスを有する第2の部分とを有し得る。NEMデバイスは、CMOSデバイスの上に形成され得、NEMデバイスとCMOS回路網との間に配置されている誘電スタックのビアを通してCMOS回路網に連結され得る。メモリ回路網の少なくとも一部分は、第1の上部部分において形成され得、その一方で、非メモリ関連の回路網(例えば、論理回路および他の処理回路網)は、第2の下部部分において形成され得る。集積回路の第1および第2の部分の回路網は、それぞれの電源レベルを受け取り得る。

【0007】

本発明の1つの適切な実施形態において、メモリセルは、1対の電源ラインの間に直列に連結された第1および第2の不揮発性リレースイッチを含み得る。第1および第2のリレースイッチは、データの単一ビットがラッチされ得る中間ノードにおいて接続され得る。第1および第2の不揮発性リレースイッチは、各々、ゲートおよびバルク端子を含み得、たとえゲート−バルク電圧が低くても、それらの状態を保持し得る。ゲートおよびバルク電圧は、「1」または「0」をメモリセル内にロードするために、制御回路網を用いて個々に制御され得る。この方法で構成されたメモリセルは、不揮発性挙動、ソフトエラーアップセット不感性、およびゼロスタンバイ電流を示し得る。

【0008】

本発明の別の適切な実施形態において、メモリセルは、第1および第2の交差連結された反転回路を含み得る。第1の反転回路は、第1の対の電源ラインの間に第2のリレースイッチまたはnチャンネルトランジスタと直列に連結された少なくとも1つのリレースイッチを含み得、その一方で、第2の反転回路は、第2の対の電源ラインの間に直列に連結された2つのCMOSトランジスタを含み得る。第1の反転回路は、メモリセルに対して第1のデータストレージノードとして機能する出力を有し得、その一方で、第2の反転回路は、メモリセルに対して第2のデータストレージノードとして機能する出力を有し得る。少なくとも1つのアクセストランジスタは、データラインと第1および第2のデータストレージノードのうちの少なくとも1つとの間に連結され得る。アクセストランジスタは、メモリセルからデータを読み取るために、かつメモリセル内にデータを書き込むために使用され得る。この方法で構成されたメモリセルは、ソフトエラーアップセット不感性および低減された電力消費を示し得る。

【0009】

例えば、本発明は以下の項目を提供する。

(項目1)

集積回路であって、該集積回路は、

基板において形成された回路網と、

該回路網の上における複数の機械的リレーメモリ回路と

を含む、集積回路。

(項目2)

上記回路網と上記複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む、上記項目に記載の集積回路。

(項目3)

上記誘電スタックは、複数の金属ルーティング層およびビア層を含む、上記項目のいずれかに記載の集積回路。

(項目4)

上記回路網は、相補型金属酸化物半導体回路網を含む、上記項目のいずれかに記載の集積回路。

(項目5)

上記回路網は、上記複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である、上記項目のいずれかに記載の集積回路。

(項目6)

上記複数の機械的リレーメモリ回路のうちの少なくとも1つは、異なる電圧レベルを有する1対の電源ラインの間に直列に連結された1対の機械的リレースイッチを含む、上記項目のいずれかに記載の集積回路。

(項目7)

上記1対の機械的リレースイッチは、1対の不揮発性機械的リレースイッチを含む、上記項目のいずれかに記載の集積回路。

(項目8)

上記複数の機械的リレーメモリ回路は、少なくとも1つの機械的リレースイッチを含み、上記回路網は、双安定メモリ要素を形成するために該少なくとも1つの機械的リレースイッチに連結されているインバータを含む、上記項目のいずれかに記載の集積回路。

(項目9)

上記少なくとも1つの機械的リレースイッチは、揮発性機械的リレースイッチである、上記項目のいずれかに記載の集積回路。

(項目10)

上記集積回路は、ユーザーから構成データを受け取るように動作可能なプログラマブル集積回路を含み、上記複数の機械的リレーメモリ回路は、該構成データを格納するように動作可能である、上記項目のいずれかに記載の集積回路。

(項目11)

メモリ要素であって、該メモリ要素は、

直列に連結された少なくともnチャンネルトランジスタおよびpチャンネルトランジスタを有する第1の反転回路と、

少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含む、メモリ要素。

(項目12)

上記第1および第2の反転回路は、一緒に交差連結されている、上記項目のいずれかに記載のメモリ要素。

(項目13)

上記第2の反転回路は、上記少なくとも1つの機械的リレースイッチと直列に連結されている回路をさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目14)

上記回路は、機械的リレースイッチを含む、上記項目のいずれかに記載のメモリ要素。

(項目15)

上記回路は、金属酸化物半導体トランジスタを含む、上記項目のいずれかに記載のメモリ要素。

(項目16)

上記回路は、nチャンネルトランジスタを含む、上記項目のいずれかに記載のメモリ要素。

(項目17)

データラインと、

該データラインと上記第1の反転回路との間に連結された少なくとも1つのアクセストランジスタと

をさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目18)

メモリ要素であって、該メモリ要素は、

第1の電源電圧を供給するように動作可能な第1の電源ラインに連結されたpチャンネルトランジスタを有する第1の反転回路と、

該第1の電源ラインと異なる第2の電源ラインに連結された少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含み、

該第2の電源ラインは、該第1の電源電圧と異なる第2の電源電圧を供給するように動作可能である、メモリ要素。

(項目19)

上記第1および第2の反転回路は、一緒に交差連結されている、上記項目のいずれかに記載のメモリ要素。

(項目20)

第3の電源ラインと、

上記第1の電源ラインと該第3の電源ラインとの間に上記pチャンネルトランジスタと直列に連結された第1のnチャンネルトランジスタと

をさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目21)

上記第2の反転回路は、上記第2の電源ラインと上記第3の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された第2のnチャンネルトランジスタをさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目22)

第4の電源ラインをさらに含み、

上記第2の反転回路は、上記第2の電源ラインと該第4の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された追加の機械的リレースイッチをさらに含み、上記第3の電源ラインおよび該第4の電源ラインは、異なる電源電圧を供給するように動作可能である、上記項目のいずれかに記載のメモリ要素。

(項目23)

プログラマブル集積回路であって、該プログラマブル集積回路は、

少なくとも1つのnチャンネルトランジスタと少なくとも1つの機械的リレースイッチとを含む双安定メモリ要素を含み、

該双安定メモリ要素は、静的制御信号が提供される出力を有する、プログラマブル集積回路。

(項目24)

上記静的制御信号を受け取るように動作可能なゲートを有するパストランジスタをさらに含み、該パストランジスタは、上記プログラマブル集積回路上のプログラマブル論理回路網の一部を形成する、上記項目のいずれかに記載のプログラマブル集積回路。

(項目25)

上記双安定メモリ要素は、

上記少なくとも1つのnチャンネルトランジスタと直列に連結されているpチャンネルトランジスタと、

上記少なくとも1つの機械的リレースイッチと直列に連結されている追加の機械的リレースイッチと

をさらに含む、上記項目のいずれかに記載のプログラマブル集積回路。

(項目26)

基板と、

誘電層と、

該基板と該誘電層との間に配置された少なくとも1つの金属ルーティング層と

をさらに含み、

上記nチャンネルトランジスタは、基板において形成され、上記機械的リレースイッチは、誘電層において形成されている、上記項目のいずれかに記載のプログラマブル集積回路。

【0010】

(摘要)

メモリ要素を有する集積回路が提供される。集積回路は、相補型金属酸化物半導体(CMOS)デバイスを有する第1の部分において形成された論理回路網を含み得、ナノ電気機械的(NEM)リレーデバイスを有する第2の部分において形成されたメモリ要素および関連付けられたメモリ回路網の少なくとも一部を含み得る。NEMデバイスとCMOSデバイスとは、誘電スタックのビアを通して相互接続され得る。第1および第2の部分におけるデバイスは、それぞれの電源電圧を受け取り得る。1つの適切な配列において、メモリ要素は、不揮発性ストレージ特性およびソフトエラーアップセット不感性を提供する2つのリレースイッチを含み得る。別の適切な配列において、メモリ要素は、第1および第2の交差連結された反転回路を含み得る。第1の反転回路は、リレースイッチを含み得、その一方で、第2の反転回路は、CMOSトランジスタのみを含む。この方法で構成されたメモリ要素は、揮発性ストレージ特性およびSEU不感性を提供するために使用され得る。

【0011】

本発明のさらなる特徴、本発明の本質およびさまざまな利点は、添付の図面および以下の詳細な説明からより明白になる。

【図面の簡単な説明】

【0012】

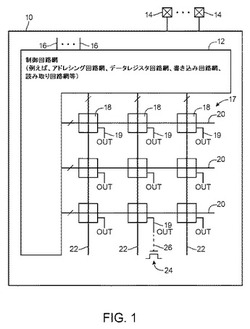

【図1】図1は、本発明の実施形態に従う例示的なメモリアレイ回路網のダイヤグラムである。

【図2】図2は、本発明の実施形態に従う、相補型金属酸化物半導体(CMOS)テクノロジーおよびナノ電気機械的(NEM)リレーテクノロジーを用いて形成された回路網を有する集積回路の断面側面図である。

【図3】図3は、本発明の実施形態に従う不揮発性リレースイッチのダイヤグラムである。

【図4】図4は、本発明の実施形態に従う図3のリレースイッチの状態ダイヤグラムである。

【図5】図5は、本発明の実施形態に従う図3および4に関連して示されたタイプのリレースイッチを用いて形成された例示的なメモリセルの回路ダイヤグラムである。

【図6】図6は、本発明の実施形態に従う図3のリレースイッチを動作させるための例示的な電圧バイアシング値の表である。

【図7】図7は、本発明の実施形態に従う揮発性リレースイッチのダイヤグラムである。

【図8】図8は、本発明の実施形態に従う図7のリレースイッチの動作を例示するビーム変位対ゲート−バルク電圧の図である。

【図9】図9は、本発明の実施形態に従う図7および8に関連して示されたタイプのリレースイッチを用いて形成された例示的なメモリセルの回路ダイヤグラムである。

【図10】図10は、本発明の実施形態に従って図9のメモリセルがソフトエラーアップセットに対してどのように不感であるかを示すタイミングダイヤグラムである。

【図11】図11は、本発明の実施形態に従う図7および8に関連して示されたタイプの少なくとも1つのリレースイッチを用いて形成された例示的なメモリセルの回路ダイヤグラムである。

【発明を実施するための形態】

【0013】

(詳細な説明)

本発明の実施形態は、ソフトエラーアップセットイベントに対して耐性のある集積回路メモリ要素に関する。メモリ要素は、メモリを使用する任意の適切な集積回路において使用され得る。これらの集積回路は、メモリチップ、メモリアレイを有するデジタル信号処理回路、マイクロプロセッサ、メモリアレイを有する特定用途の集積回路、プログラマブル集積回路(例えば、メモリ要素が構成メモリに対して使用されるプログラマブル論理デバイス集積回路)、または任意の他の適切な集積回路であり得る。

【0014】

集積回路(例えば、メモリチップまたはメモリが処理データを格納するために必要とされる他の回路)上において、メモリ要素は、揮発性メモリ要素(例えば、静的ランダムアクセスメモリセルのようなランダムアクセスメモリセル)、不揮発性メモリ要素(例えば、リレーデバイス、ヒューズ、アンチヒューズ、電気的プログラマブル読み取り専用のメモリ要素等)、または他のタイプのメモリ要素であり得る。プログラマブル集積回路の文脈において、メモリ要素は、構成データを格納するために使用され得、それ故、この文脈において、ときには構成メモリセルと呼ばれる。

【0015】

図1は、メモリセル18のアレイを含み得る集積回路を示す。任意の適切なメモリアレイ構造は、メモリセル18に対して使用され得る。1つの適切な配列が、図1に示される。図1の例示的なアレイにおいて3つの行および列のみのメモリセル18であるが、概してメモリアレイ17において数百または数千の行および列があり得る。アレイ17は、所与のデバイス10上の多くのアレイのうちの1つであり得、より大きなアレイの一部分であるサブアレイであり得、または任意の他の適切なグループのメモリセル18であり得る。

【0016】

各メモリ要素は、対応する出力経路19において対応する出力信号OUTを供給し得る。構成メモリアレイにおいて、各信号OUTは、対応する経路26を介して運搬され得、かつ対応するトランジスタ(例えば、関連付けられたプログラマブル論理回路内のトランジスタ24または他の回路)を構成することにおいて使用され得る静的出力制御信号である。

【0017】

集積回路10は、信号をメモリアレイ17に供給するための制御回路網12を有し得る。制御回路網12は、ピン14を用いて外部供給源から、および経路(例えば、経路16)を用いて内部供給源から電源電圧、データ、および他の信号を受け取り得る。制御回路網12は、アドレシング回路網、データレジスタ回路網、書き込み回路網、読み取り回路網等のような回路網を含み得る。制御回路網12は、ピン14によって供給される電源電圧を使用して、経路(例えば、経路20および22)上に所望の時間変動信号および固定信号を生成し得る。

【0018】

メモリ要素に供給される信号は、ときには、集合的に制御信号と呼ばれ得る。特定の文脈において、これらの信号の一部は、電力信号、クリア信号、データ信号、アドレス信号等と呼ばれ得る。これらの異なる信号タイプは、互いに排他的ではない。例えば、アレイ17に対するクリア信号は、アレイ17をクリアするために使用され得る制御(アドレス)信号のタイプとして機能し得る。このクリア信号は、セル18内のインバータのような回路網に電力を供給することによって、電力信号のタイプとしても機能し得る。同様に、クリアする動作がメモリセル18において論理0を配置するように機能するので、クリア信号は、データ信号のタイプとして機能し得る。

【0019】

概して、経路20および22に関連付けられた伝導ラインの適切な数が任意であり得る。例えば、アレイ17の各行は、(例として)経路20のうちのそれぞれの1つにおいて関連付けられたアドレスライン(例えば、真アドレスラインおよび補アドレスライン)と、関連付けられた読み取り/書き込みイネーブルラインを有し得る。アレイ17の各列は、データラインを含むそれぞれの経路22を有し得る。用語「行」および「列」は、メモリアレイ17内のセル18の特定のグループを指す1つの方法を示すに過ぎず、ときには相互交換可能に使用され得る。必要に応じて、他のパターンのラインは、経路20および22において使用され得る。例えば、異なる数の電源信号、データ信号、およびアドレス信号が使用され得る。

【0020】

クリア信号は、共通のクリアラインを介して同時に、アレイ17のすべてのセルへルーティングされ得る。クリアラインは、垂直に配向されることにより、各経路22のクリアラインのうちの1つの分岐があり得るか、またはクリアラインは、水平に配向されることにより、各経路20のクリアラインのうちの1つの分岐があり得る。クリアラインは、必ずしも必要とされない。

【0021】

電力もこのタイプのグローバル方式で配分され得る。例えば、正の電源電圧Vccは、共用の水平または垂直コンダクタのパターンを用いて各セル18に並列に供給され得る。同様に、グラウンド電圧Vssは、共用の水平または垂直ラインのパターンを用いてセル18に並列に供給され得る。制御ライン(例えば、アドレスラインおよびデータライン)は、一般的に互いに対して直交である(例えば、アドレスラインは、垂直であるが、データラインは、水平であり、またはその逆の場合もある)。

【0022】

正の電源電圧Vccは、正の電源ラインを介して提供され得る。グラウンド電圧Vssは、グラウンド電源ラインを介して提供され得る。任意の適切な値が、正の電源電圧Vccおよびグラウンド電圧Vssに対して使用され得る。例えば、正の電源電圧Vccは、1.2ボルト、1.1ボルト、1.0ボルト、0.9ボルト、0.9ボルトより低いボルト、または他の任意の適切なボルトであり得る。グラウンド電圧Vssは、(一例として)0ボルトであり得る。典型的な配列において、電源電圧Vccは、1.0ボルトであり得、Vssは0ボルトであり得、アドレス信号、データ信号、およびクリア信号に対する信号レベルは、(低い場合)0ボルトから(高い場合)1.0ボルトまでの範囲を有し得る。Vccが時間の関数として変動し、Vssが0ボルトより低く、および制御信号がオーバードライブされる(すなわち、制御信号がVcc−Vssより大きな信号強度を有する)配列も使用され得る。

【0023】

図2は、第2のタイプの回路10−2の上に形成された第1のタイプの回路網10−1を有する集積回路10の断面側面図である。図2において示されるように、回路網10−1は、機械的回路網(例えば、ナノ電気機械的(NEM)リレー回路32)を含み得るが、回路網10−2は、相補型金属酸化物半導体(CMOS)回路30および関連付けられた誘電スタック50を含み得る。

【0024】

例えば、CMOS回路30は、半導体基板40において形成されたnチャンネル金属酸化物半導体(NMOS)トランジスタおよびpチャンネル金属酸化物半導体(PMOS)トランジスタのような金属酸化物半導体電界効果トランジスタ(MOSFET)、基板40おいて1つのトランジスタと別のトランジスタと分離するための浅いトレンチ分離(STI)構造のような構造、ポリシリコン抵抗器、およびCMOSテクノロジーを用いて形成され得る他のタイプの電気デバイスを含み得る。誘電スタック50は、基板40の表面の上に形成され得る。誘電スタック50は、酸化シリコンまたは他の誘電体の層を含み得、それらの中に導電性構造が形成される。誘電スタック50は、金属相互接続層(ときには、金属層または金属ルーティング層と呼ばれる)およびビア層52を含み得る。

【0025】

導電性ルーティングライン(ときには、金属相互接続経路と呼ばれる)は、金属ルーティング層において形成され得る。ビア層52は、垂直の伝導する構造(例えば、タングステンビア、銅ビア、アルミニウムビア、または他の金属ビアのような導電性ビア)を含み得、伝導する構造は、各導電性ビアの両側の端部において形成された導電性ルーティングラインを接続するように構成されている。基板40に最も近い金属ルーティング層は、第1の金属ルーティング層M1と呼ばれる。連続する金属ルーティング層は、金属ルーティング層M2、M3、...、Mtopをその順番において含み得、金属ルーティング層M2が、層M1に最も近く、金属ルーティング層Mtopが、層M1から最も離れている(すなわち、金属ルーティング層M1は、誘電スタックの底面層を表し、その一方で、金属ルーティング層Mtopは、誘電スタックの最上層を表す)。誘電スタック50は、金属ルーティング層の各隣接する対がビア層52によって分離されている交互する配列で構成され得る。

【0026】

回路32は、NEMリレースイッチ(例えば、リレースイッチ60、不揮発性デバイス、およびNEM製造テクノロジーを用いて形成され得る他のタイプの電気機械的デバイス)を含み得る。リレースイッチ60は、静電作動の機械的スイッチであり得、その状態は、その端子において適用される電圧レベルに依存する。例えば、スイッチ60は、誘電体74(ときには、ボディー誘電材料と呼ばれる)の層の表面上に形成された第1および第2のソース−ドレイン端子68を含み得る。伝導性ブリッジ部品66(ときには、金属チャンネルと呼ばれる)は、第1のソース−ドレイン端子の上に延在する第1の突起する部分66−1と、第2のソース−ドレイン端子の上に延在する第2の突起する部分66−2とを有し得る。ブリッジ部品66は、ゲート部品62(例えば、ポリシリコンゲート構造または金属ゲート構造)によって支持され得る。ブリッジ部品66およびゲート部品62は、誘電材料64によって分離され得る。ゲート部品62は、関連付けられた第1および第2のソースドレイン領域68の間に位置するチャンネル領域の上に懸下されているビームとして機能し得る。ゲート部品62は、チャンネル領域の外側に位置する固定する構造(示されていない)を介して誘電体74に取り付けられ得る。導電性ボディー電極70は、ゲート部品62より下において誘電体74の表面内に形成され得る。

【0027】

リレースイッチ60の状態は、適切な電圧をゲート62およびボディー70に適用することによって制御され得る。一例として、スイッチ60のゲート端子とボディー端子との間の電圧差が、所定の電圧閾値レベルより大きい場合、スイッチ60は、オン状態に配置され得る(すなわち、ビーム62は、部分66−1および66−2を第1および第2のソース−ドレイン端子68と接触して配置することによってソース−ドレイン端子と接触するように低下され得る)。スイッチ60のゲート端子とボディー端子との間の電圧差が、所定の電圧閾値レベルより小さい場合、スイッチ60は、オフ状態に配置され得る(すなわち、ビーム62は、第1および第2のソース−ドレイン端子68が部分66−1および66−2と接触しないように上昇され得る)。スイッチ60がオフ状態に配置される場合に、ブリッジ部品66とソース−ドレイン構造68とは、(例として)空気によって分離され得る。

【0028】

本発明の1つの適切な配列において、メモリアレイ17、メモリアドレシング回路網、メモリデータレジスタ回路網、メモリ書き込みドライバー回路網、メモリ読み取り回路網、および他の周辺メモリ制御回路網は、部分10−1において形成され得、その一方で、構成可能な論理回路(例えば、パストランジスタ24、受動集積回路部品(例えば、集積回路抵抗器、キャパシタ、およびコンダクタ)、デジタルおよびアナログ処理ユニット、並びに他の非メモリ関連の回路網は、部分10−2において形成され得る(例えば、部分10−1が、部分10−2の上に形成され得る)。

【0029】

上部部分10−1のリレースイッチ60が構成メモリセル18の一部分を形成する図2の例を考察する。スイッチ60の第1のソース−ドレイン領域68は、出力19として機能し得、静的制御信号OUTが出力19において提供される(例えば、図1を参照)。静的制御信号OUTは、下部部分10−2において形成された対応するパストランジスタ24に供給され得る。図2において示されるように、パストランジスタ24は、基板40において形成されたソース−ドレイン領域46、ソース−ドレイン領域46間に位置するチャンネル領域の上に形成されたゲート42、ゲート42と関連付けられたチャンネル領域との間に配置されたゲート絶縁層44を含む。

【0030】

上部部分10−1のスイッチ60は、経路26を通して対応するパストランジスタ24に連結され得る。図2において示されるように、スイッチ60の第1のソース−ドレイン端子68は、誘電層74において形成されたビア69を通して、金属層M1−Mtopにおいて形成された金属スタブ56を通して、金属スタブ56を接続する金属ビア58を通して、そして金属ルーティング層M1の金属スタブ56をゲート42に接続する金属ビア58’を通してトランジスタ24に連結され得る。この例は、単なる例示に過ぎず、本発明の範囲を限定するものではない。必要に応じて、部分10−1の回路網と部分10−2の回路網との間の他の電気的接続が、この方法で作られ得る。例えば、部分10−2において形成された処理回路網30は、誘電スタック50を通る経路35を介して制御信号Vctrを部分10−1の回路網34に送信するように構成され得る。

【0031】

メモリ回路網がもはや論理および他の処理回路網と同じ平面上に形成される必要がないので、部分10−2の他のCMOS回路網の直接上に部分10−1のメモリ回路網を形成することは、実質的に貴重な集積回路の実領域を節約し得る。本発明の別の適切な配列において、回路網10−1は、第1の正電源電圧Vcc1をNEMリレー回路32に、および第2の正電源電圧Vcc2をCMOS回路30に提供するように動作可能な電源および制御回路網34を含み得る。回路網34は、NEMデバイスを用いて形成され得る。この配列を用いて提供された電力ドメイン分離は、部分10−1において動作するメモリ回路網が増大された性能のためにオーバードライブされることを可能にしながら、部分10−2において動作する回路網のための電力消費を低減させ得る。例えば、電源および制御回路網34は、上部部分10−1のメモリ回路網に電力を供給するために1.2ボルトを供給し、下部部分10−2の回路30に電力を供給するために0.85ボルトを供給し得る。

【0032】

図3は、第1のタイプのリレースイッチ60−1の概略的ダイヤグラムである。図3において示されるように、リレースイッチ60−1は、ソース−ドレイン端子SD1およびSD2、ゲート端子G、およびボディー(またはバルク)端子Bを有し得る。リレースイッチ60−1は、不揮発性挙動を示し得、この挙動において、たとえスイッチ60−1のゲートおよびボディー端子が任意の電力を供給されなくても、スイッチの状態が保存される。

【0033】

図4は、不揮発性リレースイッチ60−1の動作を例示する状態ダイヤグラムである。スイッチ60−1がオフ状態80(すなわち、SD1およびSD2が切断されている状態)にある場合、スイッチ60−1は、端子GとBとの間の電圧差(VGB)が所定のプルイン電圧閾値VPIを超えるように、端子GおよびBをバイアシングすることによってオンにされ得る。スイッチ60−1がオン状態82(すなわち、SD1およびSD2がブリッジ部品66を通して電気的かつ機械的に接続されている状態)にある場合、スイッチ60−2は、VGBが所定のプルアウト電圧閾値VPOより小さくなるように、端子GおよびBをバイアシングすることによってオフにされ得る。スイッチ60−1は、プルインの基準が満たされるまで(VGBがVPOより小さいか否かに関わらず)、オフ状態80のままであり得る。同様に、スイッチ60−2は、プルアウトの条件が満たされるまで(VGBがVPIより大きいか否かに関わらず)、オン状態82のままであり得る。(一例として)閾値VPIは、正の値を有し得、その一方で、VPOは、負の値を有し得る。

【0034】

例えば、デバイス10が電源オンにされており、かつスイッチ60−1が最初にオフ状態にあるシナリオを考察する。制御回路網は、スイッチ60−1をオン状態に配置するためにVGBがVPIを超えるように、スイッチ60−1をバイアシングするために使用され得る。次に、デバイス10が電源オフにされ得る。再びデバイス10に電力を供給すると、スイッチ60−1は、オン状態のままであり得る。デバイス10が電源オンにされており、かつスイッチ60−1が最初にオン状態にあるシナリオを考察する。制御回路網は、スイッチ60−1をオフ状態に配置するためにVGBがVPOより小さくなるように、スイッチ60−1をバイアシングするために使用され得る。次に、デバイス10が電源オフにされ得る。再びデバイス10に電力を供給すると、スイッチ60−1は、オフ状態のままであり得る。このような動作特性を有するリレースイッチ60−1は、不揮発性メモリ要素を形成するために使用され得る。

【0035】

図5は、例示的な不揮発性メモリセル18の回路ダイヤグラムである。図5において示されるように、リレースイッチ90および92は、正電源ライン84(例えば、正電源電圧Vcc1が提供される電源ライン)とグラウンド電源ライン86(例えば、グラウンド電源電圧Vssが提供されるグラウンドライン)との間のスイッチのソース−ドレイン端子を通して直列に連結され得る。スイッチ90および92は、図3および4に関連して説明されたタイプの不揮発性リレースイッチであり得る。スイッチ90の状態は、電圧VG1とVB1との相対的な大きさによって制御され得、その一方で、スイッチ92の状態は、電圧VG2とVB2との相対的な大きさによって制御され得る。図2に関連して説明された回路網34は、メモリセル18のスイッチ90および92に対するこれらの電圧を制御するために使用され得る。スイッチ90および92は、静的制御信号OUTが提供される中間ノードにおいて直列接続であり得る。

【0036】

図5のセル18は、不揮発性メモリ要素(すなわち、デバイス10が電力を供給されるか否かに関わらず、その状態を保持するメモリセル)であり得る。例えば、デバイス10が電源オンにされており、かつ所与のセル18が最初に「1」を格納している(すなわち、信号OUTが高である)シナリオを考察する。制御回路網は、「0」を所与のセル内に書き込むために、スイッチ90をオフにし、かつスイッチ92をオンにするように使用され得る。次に、デバイス10が電源オフにされ得る。再びデバイス10に電力を供給すると、所与のセルは、「0」を格納したままであり得る(すなわち、たとえスイッチ90および92が任意の電圧を供給されなくても、スイッチは、それらの状態を保持する)。デバイス10が電源オンにされており、かつ所与のセルが最初に「0」を格納している(すなわち、信号OUTが低である)別のシナリオを考察する。制御回路網は、「1」を所与のセル内に書き込むために、スイッチ90をオンにし、かつスイッチ92をオフにするように使用され得る。ゲート−バルク電圧VGB1およびVGB2は、デバイス10の通常動作中、0ボルトと等しい場合がある。たとえVGB1がVPIより小さく、かつVGB2がVPOより大きくても、所与のセルは、「1」を格納したままである(すなわち、プルイン/プルアウト条件が満たされない限り、スイッチ90および92は、それらの状態を保持する)。

【0037】

中間出力ノードに衝突する高エネルギー宇宙線がゲートおよびバルク端子に影響を与えないので、このタイプのメモリセル18も、ソフトエラーアップセット不感性を示す。たとえアルファ粒子がゲートおよびバルク端子のうちの1つに衝突したとしても、プルイン条件またはプルアウト条件が満たされ、セル18のスイッチ90および92のうちの1つの状態を反転するように、このイベントがVGBを駆動することは到底ありそうもない。

【0038】

図6は、図5のメモリセル18を動作させるための例示的な電圧バイアシング値の表である。「1」をセル内に書き込むために、VG1およびVB1は、プルアップリレースイッチ90をオンにするようにそれぞれ1.0ボルトおよび−1.0ボルトに駆動され得、その一方で、VG2およびVB2は、プルダウンリレースイッチ92をオフにするようにそれぞれ−1.0ボルトおよび1.0ボルトに駆動され得る。この例において、VPIは、1.5ボルトと等しく、VPOは、−1.5ボルトと等しい。プルアウト要求が満たされるまで(すなわち、VGBがVPOより小さくなるまで)、スイッチ90は、閉鎖状態に留まる。同様に、プルイン閾値が満たされるまで(すなわち、VGBがVPIより大きくなるまで)、スイッチ92は、開放状態に留まる。

【0039】

「0」をセル内に書き込むために、VG1およびVB1は、プルアップリレースイッチ90をオフにする(VGBがVPOより小さい)ようにそれぞれに−1.0ボルトおよび1.0ボルトに駆動され得、その一方で、VG2およびVB2は、プルダウンリレースイッチ92をオンにする(VGBがVPIより大きい)ようにそれぞれに1.0ボルトおよび−1.0ボルトに駆動され得る。プルイン要求が満たされるまで(すなわち、VGBがVPIより大きくなるまで)、スイッチ90は、開放状態に留まり、プルアウト閾値が満たされるまで(すなわち、VGBがVPOより小さくなるまで)、スイッチ92は、閉鎖状態に留まる。概して、セル18の状態は、ロード「1」またはロード「0」の条件が満たされるまでに変化されないままであり得る。VG1、VB1、VG2、およびVB2は、セル18の通常動作の中、接地され得る(例えは、VG1、VB1、VG2、およびVB2が0ボルトに駆動され、セル18が、その電流状態を保持する)。

【0040】

図7は、第2のタイプのリレースイッチ60−2の概略的ダイヤグラムである。図7に示されるように、リレースイッチ60−2は、ソース−ドレイン端子SD1およびSD2、ゲート端子G、並びにボディー(またはバルク)端子Bを有し得る。リレースイッチ60−2は、そのゲートおよびボディー端子が電力を供給されない場合に、スイッチ60−2の状態が失われる揮発性挙動を示し得る。スイッチ60−2のゲート部品がソース−ドレインコンダクタに向かって曲げられる量は、ビーム変位Xとして規定される。

【0041】

図8は、ビーム変位対ゲート−バルク電圧VGBのプロットである。図8において示されるように、ビーム変位Xは、VGBがプルアウト閾値VPOより小さい場合に最小である(すなわち、VGBがVPOより小さい場合に、スイッチ60−2がオフにされる)。ビーム変位は、VGBがプルイン閾値VPIより大きい場合に最大にされる(すなわち、VGBがVPIより大きい場合に、スイッチ60−2がオンにされる)。スイッチ60−2は、オン/オフの電圧遷移が異なる(例えば、オン/オフの遷移要求がスイッチ60−2の電流状態に依存する)ヒステリシス挙動を示し得る。

【0042】

例えば、スイッチ60−2が最初にオフ状態にあるシナリオを考察する。VGBが徐々に増大され場合に、ビーム変位Xは増大する。スイッチ60−2は、VGBがVPIを超える場合にオン状態に配置される(遷移100を参照)。次にVGBが徐々に減少される場合に、たとえVGBがVPI以下に落ちても(VGBがなおVPOより大きい限り)、スイッチ60−2はオン状態のままである。一旦VGBがVPO以下に低下されると、スイッチ60−2はオフにされる(遷移102を参照)。この例において、VPIは、VPOより大きい。図8は、単なる例示に過ぎず、本発明の範囲を限定するものではない。必要に応じて、VPIは、VPO以下であり得る。

【0043】

図9は、本発明の1つの実施形態に従う、CMOSトランジスタおよびNEMリレースイッチを含むメモリセル18の回路ダイヤグラムである。図9において示されるように、セル18は、第1および第2の交差連結された反転回路INV1およびINV2を含み得る。反転回路INV1は、第1の正電源ライン108(例えば、正電源電圧Vcc1が提供される電源ライン)と第1のグラウンドライン110(例えば、グラウンド電源電圧Vss1が提供される電源ライン)との間に直列に連結されたリレースイッチ112および114を含み得る。スイッチ112および114は、図7および8に関連して説明されたタイプの揮発性リレースイッチ60−2であり得る。スイッチ112のバルク端子は、電源ライン108に連結され得、その一方で、スイッチ110のバルク端子は、電源ライン110に連結され得る。

【0044】

反転回路INV2は、第2の正電源ライン104(例えば、正電源電圧Vcc2が提供される電源ライン)と第2のグラウンドライン106(例えば、グラウンド電源電圧Vss2が提供される電源ライン)との間に直列に連結されたpチャンネルプルアップトランジスタPU(例えば、pチャンネル金属酸化物半導体デバイス)およびnチャンネルプルダウントランジスタPD(例えば、nチャンネル金属酸化物半導体デバイス)を含み得る。この例において、リレースイッチ112および114に関連付けられたVcc1/Vss1は、COMSトランジスタPUおよびPDに関連付けられたVcc2/Vss2と等しい大きさかまたは異なる大きさであり得る(すなわち、リレーデバイスおよびCMOSデバイスが、別個の電源ラインを用いて電力を供給される)。

【0045】

反転回路INV1およびINV2は、各々、入力および出力を有し得る。INV1の出力は、INV2の入力に連結され得、メモリセル18に対して第1のデータストレージノードnOUTとして機能し得る。INV2の出力は、INV1の入力に連結され得、メモリセル18に対して第2のデータストレージノードOUTとして機能し得る。この方法で交差連結された反転回路INV1およびINV2は、単一データビットの真バーションおよび補バージョンを、それぞれ、データストレージノードnOUTおよびOUTにおいて格納するためのラッチとして使用され得る。例えば、セル18は、「0」を格納するために使用され得る(すなわち、ノードOUTが低であり、かつノードnOUTが高である)か、または「1」を格納するために使用され得る(すなわち、ノードOUTが高であり、かつノードnOUTが低である)。それ故、セル18のこの交差連結された部分は、ときには、双安定メモリ要素と呼ばれ得る。

【0046】

トランジスタAC1のような第1のアクセストランジスタは、データステージノードnOUTと第1のデータライン(例えば、真ビットライン信号BLが提供されるデータライン)との間に連結され得る。トランジスタAC2のような第2のアクセストランジスタは、データステージノードOUTと第2のデータライン(例えば、補ビットライン信号nBLが提供されるデータライン)との間に連結され得る。トランジスタAC1およびAC2のゲートは、対応するワードライン信号WLを用いて制御され得る。アクセストランジスタは、(例えば、WLをアサートし、ビットライン信号を適切な電圧レベルにバイアシングすることによって)、メモリセル18からデータを読み取るために、かつメモリセル18内にデータを書き込むために使用され得る。ワードライン信号WLは、ときにはアドレス信号と呼ばれ得、その一方で、トランジスタAC1およびAC2は、ときには、アドレストランジスタと呼ばれ得る。

【0047】

図9のセル18のリレースイッチ112および114は、上部デバイス部分10−1において形成され得(例えば、図2を参照)、その一方で、トランジスタPU、PD、AC1、およびAC2は、下部デバイス部分10−2において形成され得る。リレーインバータ回路INV1の入力および出力は、誘電スタック50のビア経路26を通して下へ、トランジスタAC1およびCMOSインバータ回路INV2に連結され得る。

【0048】

リレーデバイスの機械的スイッチング遅延が、セルが高エネルギー宇宙線によって引き起こされる妨害下にある時間よりはるかに長い期間である傾向を有するので、図9に関連して説明されたタイプのメモリセル18は、ソフトエラーアップセット不感性を示す。例えば、セル18が「0」を格納しており、侵入するアルファ粒子が時間t0において出力ノードOUTに衝突するシナリオを考察する(例えば、図10のタイミングダイヤグラムを参照)。(例として)このイベントは、結果としてノードOUTにおいて注入されるパルス状の電流IINJ_OUT(例えば、0.5μAのピークを有する電流パルス)を生じ得、ノードOUTでの電圧(VOUT)が1.2ボルトの正電源電圧に向かって上昇するようにし得る。VOUTにおいてこの一時的上昇は、スイッチ114をオンにし、かつスイッチ112をオフにすることを始動させる。しかしながら、スイッチ112および114のゲート部品にとってプルインまたはプルアウトまでかかる時間(例えば、時間t0からt2まで)が約ナノ秒であるが、注入されたノイズ電流の期間(例えば、時間t0からt1まで)が約ピコ秒であるので、ノードnOUTは、t1において高のままである。時間t1の後に、トランジスタPDは、オンであり、VOUTを放電し、グラウンドに戻るように機能する(すなわち、セル18は、その格納された「0」の値を保持する)。

【0049】

図11は、本発明の実施形態に従うメモリセル18の別の適切な配列を示す。図11において示されるように、セル18は、第1および第2の交差連結された反転回路INV1およびINV2を含み得る。反転回路INV1は、第1の正電源ライン108と共通グラウンドライン107(例えば、グラウンド電源電圧Vssが提供される電源ライン)との間に直列に連結されたリレースイッチ112およびnチャンネルトランジスタPD1を含み得る。スイッチ112は、図7および8に関連して説明されたタイプのリレースイッチ60−2であり得る。スイッチ112のバルク端子は、電源ライン108に連結され得る。

【0050】

反転回路INV2は、第2の正電源ライン104と共通グラウンドライン107との間に直列に連結されたpチャンネルプルアップトランジスタPUおよびnチャンネルプルダウントランジスタPD2を含み得る。この例において、INV1に関連付けられたVcc1は、INV2に関連付けられたVcc2と等しい大きさかまたは異な大きさであり得るが、Vssは、INV1およびINV2の両方に供給され得る。必要に応じて、INV1およびINV2は、それぞれのグラウンド電源ラインから異なるグラウンド電圧信号を受け取り得る。

【0051】

反転回路INV1およびINV2は、各々、入力および出力を有し得る。INV1の出力は、INV2の入力に連結され得、メモリセル18に対して第1のデータストレージノードnOUTとして機能し得る。INV2の出力は、INV1の入力に連結され得、メモリセル18に対して第2のデータストレージノードOUTとして機能し得る。第1のアクセストランジスタAC1は、データステージノードnOUTと第1のデータラインとの間に連結され得、その一方で、第2のアクセストランジスタAC2は、データステージノードOUTと第2のデータラインとの間に連結され得る。トランジスタAC1およびAC2のゲートは、対応するワードライン信号WLを用いて制御され得る。アクセストランジスタは、メモリセル18からデータを読み取るために、かつメモリセル18内にデータを書き込むために使用され得る。

【0052】

図11のセル18のリレースイッチ112は、上部デバイス部分10−1において形成され得(例えば、図1を参照)、その一方で、トランジスタPD1、PD2、PU、AC1、およびAC2は、標準CMOS製造技術を用いて下部デバイス部分10−2において形成され得る。リレースイッチ112は、誘電スタック50のビア経路26を通して下へ、トランジスタAC1、PD1、およびCMOSインバータ回路INV2に連結され得る。

【0053】

図11に関連して説明されたタイプのメモリセル18も、ソフトエラーアップセット不感性を示すために使用され得る。例えば、セル18が「0」を格納しており、(矢印200によって示されるように)侵入するアルファ粒子が出力ノードOUTに衝突するシナリオを考察する。これは、VOUTが高へ上昇するようにし、トランジスタPD1をオンにする。リレーデバイスの機械的スイッチングが、COMSトランジスタの電気的スイッチングに比べて比較的に遅いので、VOUTが高である期間に対してスイッチ112は、オンのままである。スイッチ112およびトランジスタPD1の両方がオンである場合に、スイッチ112のオンの抵抗がトランジスタPD1のオンの抵抗より実質的に低い(すなわち、リレーデバイスの機械的コンダクタンスが、CMOSトランジスタの電子的コンダクタンスより実質的に高い)ので、VnOUTは、比較的に高い状態(例えば、Vcc1の50%より大きい)に留まる。結果として、粒子200の影響がなくなる場合に、ノードnOUTでの高電圧は、PD2がノードOUTを放電し、グラウンドに戻ることを可能にする。

【0054】

セル18が「1」を格納しており、かつ侵入するアルファ粒子200は、VOUTが低に落ちるようにし、トランジスタPD1をオフにするように出力ノードOUTに衝突する別のシナリオを考察する。スイッチ112の遅い機械的スイッチングのため、スイッチ112は、VOUTが低である期間に対してオフのままである。スイッチ112およびトランジスタPD1の両方がオフである場合に、ノードnOUTは、浮動しており、それ故、VnOUTは、低に留まる。結果として、粒子200の影響がなくなる場合に、ノードnOUTでの低電圧は、トランジスタPUがOUTを充電し、Vcc2に戻ることを可能にする。

【0055】

図9および11のメモリセル構成は、単なる例示に過ぎず、本発明の範囲を限定するものではない。必要に応じて、リレースイッチは、6個より少ないスイッチングデバイスかまたは6個より多いスイッチングデバイスを有するメモリセル、多重ポートメモリセル、読み取りバッファー回路を有するメモリセル、2つより多い交差連結された反転回路を有するメモリセル、および他のタイプのメモリ要素において使用され得る。NEMリレーデバイスが、CMOSトランジスタに対して実質的により少ないソース−ドレイン漏れ電流を示すので、リレーデバイスを含むメモリセルはまた、低減された電力消費を示し得る。

【0056】

追加の実施形態:

(追加の実施形態1)

集積回路であって、該集積回路は、基板において形成された回路網と、該回路網の上における複数の機械的リレーメモリ回路とを含む、集積回路。

(追加の実施形態2)

上記回路網と上記複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む、追加の実施形態1に記載の集積回路。

(追加の実施形態3)

上記誘電スタックは、複数の金属ルーティング層およびビア層を含む、追加の実施形態2に記載の集積回路。

(追加の実施形態4)

上記回路網は、相補型金属酸化物半導体回路網を含む、追加の実施形態1に記載の集積回路。

(追加の実施形態5)

上記回路網は、上記複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である、追加の実施形態1に記載の集積回路。

(追加の実施形態6)

上記複数の機械的リレーメモリ回路のうちの少なくとも1つは、異なる電圧レベルを有する1対の電源ラインの間に直列に連結された1対の機械的リレースイッチを含む、追加の実施形態5に記載の集積回路。

(追加の実施形態7)

上記1対の機械的リレースイッチは、1対の不揮発性機械的リレースイッチを含む、追加の実施形態6に記載の集積回路。

(追加の実施形態8)

上記複数の機械的リレーメモリ回路は、少なくとも1つの機械的リレースイッチを含み、上記回路網は、双安定メモリ要素を形成するために該少なくとも1つの機械的リレースイッチに連結されているインバータを含む、追加の実施形態5に記載の集積回路。

(追加の実施形態9)

上記少なくとも1つの機械的リレースイッチは、揮発性機械的リレースイッチである、追加の実施形態8に記載の集積回路。

(追加の実施形態10)

上記集積回路は、ユーザーから構成データを受け取るように動作可能なプログラマブル集積回路を含み、上記複数の機械的リレーメモリ回路は、該構成データを格納するように動作可能である、追加の実施形態1に記載の集積回路。

(追加の実施形態11)

メモリ要素であって、該メモリ要素は、直列に連結された少なくともnチャンネルトランジスタおよびpチャンネルトランジスタを有する第1の反転回路と、少なくとも1つの機械的リレースイッチを有する第2の反転回路とを含む、メモリ要素。

(追加の実施形態12)

上記第1および第2の反転回路は、一緒に交差連結されている、追加の実施形態11に記載のメモリ要素。

(追加の実施形態13)

上記第2の反転回路は、上記少なくとも1つの機械的リレースイッチと直列に連結されている回路をさらに含む、追加の実施形態11に記載のメモリ要素。

(追加の実施形態14)

上記回路は、機械的リレースイッチを含む、追加の実施形態13に記載のメモリ要素。

(追加の実施形態15)

上記回路は、金属酸化物半導体トランジスタを含む、追加の実施形態13に記載のメモリ要素。

(追加の実施形態16)

上記回路は、nチャンネルトランジスタを含む、追加の実施形態15に記載のメモリ要素。

(追加の実施形態17)

データラインと、該データラインと上記第1の反転回路との間に連結された少なくとも1つのアクセストランジスタとをさらに含む、追加の実施形態16に記載のメモリ要素。

(追加の実施形態18)

メモリ要素であって、該メモリ要素は、第1の電源電圧を供給するように動作可能な第1の電源ラインに連結されたpチャンネルトランジスタを有する第1の反転回路と、該第1の電源ラインと異なる第2の電源ラインに連結された少なくとも1つの機械的リレースイッチを有する第2の反転回路とを含み、該第2の電源ラインは、該第1の電源電圧と異なる第2の電源電圧を供給するように動作可能である、メモリ要素。

(追加の実施形態19)

上記第1および第2の反転回路は、一緒に交差連結されている、追加の実施形態18に記載のメモリ要素。

(追加の実施形態20)

第3の電源ラインと、上記第1の電源ラインと該第3の電源ラインとの間に上記pチャンネルトランジスタと直列に連結された第1のnチャンネルトランジスタとをさらに含む、追加の実施形態18に記載のメモリ要素。

(追加の実施形態21)

上記第2の反転回路は、上記第2の電源ラインと上記第3の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された第2のnチャンネルトランジスタをさらに含む、追加の実施形態20に記載のメモリ要素。

(追加の実施形態22)

第4の電源ラインをさらに含み、上記第2の反転回路は、上記第2の電源ラインと該第4の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された追加の機械的リレースイッチをさらに含み、上記第3の電源ラインおよび該第4の電源ラインは、異なる電源電圧を供給するように動作可能である、追加の実施形態20に記載のメモリ要素。

(追加の実施形態23)

プログラマブル集積回路であって、該プログラマブル集積回路は、少なくとも1つのnチャンネルトランジスタと少なくとも1つの機械的リレースイッチとを含む双安定メモリ要素を含み、該双安定メモリ要素は、静的制御信号が提供される出力を有する、プログラマブル集積回路。

(追加の実施形態24)

上記静的制御信号を受け取るように動作可能なゲートを有するパストランジスタをさらに含み、該パストランジスタは、上記プログラマブル集積回路上のプログラマブル論理回路網の一部を形成する、追加の実施形態23に記載のプログラマブル集積回路。

(追加の実施形態25)

上記双安定メモリ要素は、上記少なくとも1つのnチャンネルトランジスタと直列に連結されているpチャンネルトランジスタと、上記少なくとも1つの機械的リレースイッチと直列に連結されている追加の機械的リレースイッチとをさらに含む、追加の実施形態23に記載のプログラマブル集積回路。

(追加の実施形態26)

基板と、誘電層と、該基板と該誘電層との間に配置された少なくとも1つの金属ルーティング層とをさらに含み、上記nチャンネルトランジスタは、基板において形成され、上記機械的リレースイッチは、誘電層において形成されている、追加の実施形態23に記載のプログラマブル集積回路。

【0057】

上記の内容は、単なる本発明の原理の例示に過ぎず、さまざまな改変が、本発明の範囲および精神から逸脱することなしに、当業者によって加えられ得る。上記実施形態は、単独も任意の組み合わせでも実装され得る。

【符号の説明】

【0058】

10 集積回路

12 制御回路網

14 ピン

16、20、22、26 経路

17 メモリアレイ

18 メモリセル

19 出力

24 パストランジスタ

【技術分野】

【0001】

この出願は、2011年11月23日に出願された米国特許出願第13/304,226に対して優先権を主張する。上記文献は、全体として本明細書において参照することによって援用される。

【背景技術】

【0002】

集積回路は、しばしば、揮発性メモリ要素を含む。一般的な揮発性メモリ要素は、交差連結されたインバータ(ラッチ)に基づく。集積回路が電力供給されている場合に限り、揮発性メモリ要素は、データを保持する。電力がなくなる場合、揮発性メモリ要素内のデータがなくなる。例えば、静的ランダムアクセスメモリ(SRAM)チップは、1つのタイプの揮発性メモリ要素であるSRAMセルを含む。揮発性メモリ要素は、プログラマブル論理デバイス集積回路においても使用され得る。

【0003】

揮発性メモリ要素は、ソフトエラーアップセットとして知られた現象の影響を受ける。ソフトエラーアップセットイベントは、宇宙線と、集積回路およびそれらのパッケージ内に埋め込まれた放射性不純物とによって引き起こされる。宇宙線および放射性不純物は、高エネルギー原子粒子(中性子およびアルファ粒子)を生成する。メモリ要素は、パターン化されたシリコン基板から形成されるトランジスタおよび他の部品を含む。原子粒子がメモリ要素内のシリコンと衝突する場合に、電子−正孔対が生成される。電子−正孔対は、メモリ要素内の充電されたノードが放電し、メモリ要素の状態が反転するようにし得る伝導経路を生成する。例えば、「1」がメモリ要素内に格納された場合に、ソフトエラーアップセットイベントは、「1」が「0」に変わるようにし得る。

【0004】

集積回路内のアップセットイベントは、メモリ要素内に格納されたデータを壊し、システム性能にとって重大な影響を有し得る。あるシステムアプリケーション(例えば、電気通信機器の遠隔インストレーション)において、欠点のある機器を修復することは、極めて負担となる。集積回路がソフトエラーアップセットイベントに対して優れた不感性をみせなければ、それらは、上記タイプのアプリケーションに対して不適切である。

【発明の概要】

【課題を解決するための手段】

【0005】

(要約)

メモリセルを有する集積回路が提供される。集積回路は、メモリセルアレイを制御するように動作可能な制御回路網を含み得る。制御回路網は、アドレシング回路網、データレジスタ回路網、書き込みドライバー回路網、読み取り感知回路網、および他の制御回路網のような回路網を含み得る。

【0006】

集積回路は、ナノ電気機械的(NEM)リレーテクノロジーを用いて形成されたデバイスを有する第1の部分と、相補型金属酸化物半導体(CMOS)テクノロジーを用いて形成されたデバイスを有する第2の部分とを有し得る。NEMデバイスは、CMOSデバイスの上に形成され得、NEMデバイスとCMOS回路網との間に配置されている誘電スタックのビアを通してCMOS回路網に連結され得る。メモリ回路網の少なくとも一部分は、第1の上部部分において形成され得、その一方で、非メモリ関連の回路網(例えば、論理回路および他の処理回路網)は、第2の下部部分において形成され得る。集積回路の第1および第2の部分の回路網は、それぞれの電源レベルを受け取り得る。

【0007】

本発明の1つの適切な実施形態において、メモリセルは、1対の電源ラインの間に直列に連結された第1および第2の不揮発性リレースイッチを含み得る。第1および第2のリレースイッチは、データの単一ビットがラッチされ得る中間ノードにおいて接続され得る。第1および第2の不揮発性リレースイッチは、各々、ゲートおよびバルク端子を含み得、たとえゲート−バルク電圧が低くても、それらの状態を保持し得る。ゲートおよびバルク電圧は、「1」または「0」をメモリセル内にロードするために、制御回路網を用いて個々に制御され得る。この方法で構成されたメモリセルは、不揮発性挙動、ソフトエラーアップセット不感性、およびゼロスタンバイ電流を示し得る。

【0008】

本発明の別の適切な実施形態において、メモリセルは、第1および第2の交差連結された反転回路を含み得る。第1の反転回路は、第1の対の電源ラインの間に第2のリレースイッチまたはnチャンネルトランジスタと直列に連結された少なくとも1つのリレースイッチを含み得、その一方で、第2の反転回路は、第2の対の電源ラインの間に直列に連結された2つのCMOSトランジスタを含み得る。第1の反転回路は、メモリセルに対して第1のデータストレージノードとして機能する出力を有し得、その一方で、第2の反転回路は、メモリセルに対して第2のデータストレージノードとして機能する出力を有し得る。少なくとも1つのアクセストランジスタは、データラインと第1および第2のデータストレージノードのうちの少なくとも1つとの間に連結され得る。アクセストランジスタは、メモリセルからデータを読み取るために、かつメモリセル内にデータを書き込むために使用され得る。この方法で構成されたメモリセルは、ソフトエラーアップセット不感性および低減された電力消費を示し得る。

【0009】

例えば、本発明は以下の項目を提供する。

(項目1)

集積回路であって、該集積回路は、

基板において形成された回路網と、

該回路網の上における複数の機械的リレーメモリ回路と

を含む、集積回路。

(項目2)

上記回路網と上記複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む、上記項目に記載の集積回路。

(項目3)

上記誘電スタックは、複数の金属ルーティング層およびビア層を含む、上記項目のいずれかに記載の集積回路。

(項目4)

上記回路網は、相補型金属酸化物半導体回路網を含む、上記項目のいずれかに記載の集積回路。

(項目5)

上記回路網は、上記複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である、上記項目のいずれかに記載の集積回路。

(項目6)

上記複数の機械的リレーメモリ回路のうちの少なくとも1つは、異なる電圧レベルを有する1対の電源ラインの間に直列に連結された1対の機械的リレースイッチを含む、上記項目のいずれかに記載の集積回路。

(項目7)

上記1対の機械的リレースイッチは、1対の不揮発性機械的リレースイッチを含む、上記項目のいずれかに記載の集積回路。

(項目8)

上記複数の機械的リレーメモリ回路は、少なくとも1つの機械的リレースイッチを含み、上記回路網は、双安定メモリ要素を形成するために該少なくとも1つの機械的リレースイッチに連結されているインバータを含む、上記項目のいずれかに記載の集積回路。

(項目9)

上記少なくとも1つの機械的リレースイッチは、揮発性機械的リレースイッチである、上記項目のいずれかに記載の集積回路。

(項目10)

上記集積回路は、ユーザーから構成データを受け取るように動作可能なプログラマブル集積回路を含み、上記複数の機械的リレーメモリ回路は、該構成データを格納するように動作可能である、上記項目のいずれかに記載の集積回路。

(項目11)

メモリ要素であって、該メモリ要素は、

直列に連結された少なくともnチャンネルトランジスタおよびpチャンネルトランジスタを有する第1の反転回路と、

少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含む、メモリ要素。

(項目12)

上記第1および第2の反転回路は、一緒に交差連結されている、上記項目のいずれかに記載のメモリ要素。

(項目13)

上記第2の反転回路は、上記少なくとも1つの機械的リレースイッチと直列に連結されている回路をさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目14)

上記回路は、機械的リレースイッチを含む、上記項目のいずれかに記載のメモリ要素。

(項目15)

上記回路は、金属酸化物半導体トランジスタを含む、上記項目のいずれかに記載のメモリ要素。

(項目16)

上記回路は、nチャンネルトランジスタを含む、上記項目のいずれかに記載のメモリ要素。

(項目17)

データラインと、

該データラインと上記第1の反転回路との間に連結された少なくとも1つのアクセストランジスタと

をさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目18)

メモリ要素であって、該メモリ要素は、

第1の電源電圧を供給するように動作可能な第1の電源ラインに連結されたpチャンネルトランジスタを有する第1の反転回路と、

該第1の電源ラインと異なる第2の電源ラインに連結された少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含み、

該第2の電源ラインは、該第1の電源電圧と異なる第2の電源電圧を供給するように動作可能である、メモリ要素。

(項目19)

上記第1および第2の反転回路は、一緒に交差連結されている、上記項目のいずれかに記載のメモリ要素。

(項目20)

第3の電源ラインと、

上記第1の電源ラインと該第3の電源ラインとの間に上記pチャンネルトランジスタと直列に連結された第1のnチャンネルトランジスタと

をさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目21)

上記第2の反転回路は、上記第2の電源ラインと上記第3の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された第2のnチャンネルトランジスタをさらに含む、上記項目のいずれかに記載のメモリ要素。

(項目22)

第4の電源ラインをさらに含み、

上記第2の反転回路は、上記第2の電源ラインと該第4の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された追加の機械的リレースイッチをさらに含み、上記第3の電源ラインおよび該第4の電源ラインは、異なる電源電圧を供給するように動作可能である、上記項目のいずれかに記載のメモリ要素。

(項目23)

プログラマブル集積回路であって、該プログラマブル集積回路は、

少なくとも1つのnチャンネルトランジスタと少なくとも1つの機械的リレースイッチとを含む双安定メモリ要素を含み、

該双安定メモリ要素は、静的制御信号が提供される出力を有する、プログラマブル集積回路。

(項目24)

上記静的制御信号を受け取るように動作可能なゲートを有するパストランジスタをさらに含み、該パストランジスタは、上記プログラマブル集積回路上のプログラマブル論理回路網の一部を形成する、上記項目のいずれかに記載のプログラマブル集積回路。

(項目25)

上記双安定メモリ要素は、

上記少なくとも1つのnチャンネルトランジスタと直列に連結されているpチャンネルトランジスタと、

上記少なくとも1つの機械的リレースイッチと直列に連結されている追加の機械的リレースイッチと

をさらに含む、上記項目のいずれかに記載のプログラマブル集積回路。

(項目26)

基板と、

誘電層と、

該基板と該誘電層との間に配置された少なくとも1つの金属ルーティング層と

をさらに含み、

上記nチャンネルトランジスタは、基板において形成され、上記機械的リレースイッチは、誘電層において形成されている、上記項目のいずれかに記載のプログラマブル集積回路。

【0010】

(摘要)

メモリ要素を有する集積回路が提供される。集積回路は、相補型金属酸化物半導体(CMOS)デバイスを有する第1の部分において形成された論理回路網を含み得、ナノ電気機械的(NEM)リレーデバイスを有する第2の部分において形成されたメモリ要素および関連付けられたメモリ回路網の少なくとも一部を含み得る。NEMデバイスとCMOSデバイスとは、誘電スタックのビアを通して相互接続され得る。第1および第2の部分におけるデバイスは、それぞれの電源電圧を受け取り得る。1つの適切な配列において、メモリ要素は、不揮発性ストレージ特性およびソフトエラーアップセット不感性を提供する2つのリレースイッチを含み得る。別の適切な配列において、メモリ要素は、第1および第2の交差連結された反転回路を含み得る。第1の反転回路は、リレースイッチを含み得、その一方で、第2の反転回路は、CMOSトランジスタのみを含む。この方法で構成されたメモリ要素は、揮発性ストレージ特性およびSEU不感性を提供するために使用され得る。

【0011】

本発明のさらなる特徴、本発明の本質およびさまざまな利点は、添付の図面および以下の詳細な説明からより明白になる。

【図面の簡単な説明】

【0012】

【図1】図1は、本発明の実施形態に従う例示的なメモリアレイ回路網のダイヤグラムである。

【図2】図2は、本発明の実施形態に従う、相補型金属酸化物半導体(CMOS)テクノロジーおよびナノ電気機械的(NEM)リレーテクノロジーを用いて形成された回路網を有する集積回路の断面側面図である。

【図3】図3は、本発明の実施形態に従う不揮発性リレースイッチのダイヤグラムである。

【図4】図4は、本発明の実施形態に従う図3のリレースイッチの状態ダイヤグラムである。

【図5】図5は、本発明の実施形態に従う図3および4に関連して示されたタイプのリレースイッチを用いて形成された例示的なメモリセルの回路ダイヤグラムである。

【図6】図6は、本発明の実施形態に従う図3のリレースイッチを動作させるための例示的な電圧バイアシング値の表である。

【図7】図7は、本発明の実施形態に従う揮発性リレースイッチのダイヤグラムである。

【図8】図8は、本発明の実施形態に従う図7のリレースイッチの動作を例示するビーム変位対ゲート−バルク電圧の図である。

【図9】図9は、本発明の実施形態に従う図7および8に関連して示されたタイプのリレースイッチを用いて形成された例示的なメモリセルの回路ダイヤグラムである。

【図10】図10は、本発明の実施形態に従って図9のメモリセルがソフトエラーアップセットに対してどのように不感であるかを示すタイミングダイヤグラムである。

【図11】図11は、本発明の実施形態に従う図7および8に関連して示されたタイプの少なくとも1つのリレースイッチを用いて形成された例示的なメモリセルの回路ダイヤグラムである。

【発明を実施するための形態】

【0013】

(詳細な説明)

本発明の実施形態は、ソフトエラーアップセットイベントに対して耐性のある集積回路メモリ要素に関する。メモリ要素は、メモリを使用する任意の適切な集積回路において使用され得る。これらの集積回路は、メモリチップ、メモリアレイを有するデジタル信号処理回路、マイクロプロセッサ、メモリアレイを有する特定用途の集積回路、プログラマブル集積回路(例えば、メモリ要素が構成メモリに対して使用されるプログラマブル論理デバイス集積回路)、または任意の他の適切な集積回路であり得る。

【0014】

集積回路(例えば、メモリチップまたはメモリが処理データを格納するために必要とされる他の回路)上において、メモリ要素は、揮発性メモリ要素(例えば、静的ランダムアクセスメモリセルのようなランダムアクセスメモリセル)、不揮発性メモリ要素(例えば、リレーデバイス、ヒューズ、アンチヒューズ、電気的プログラマブル読み取り専用のメモリ要素等)、または他のタイプのメモリ要素であり得る。プログラマブル集積回路の文脈において、メモリ要素は、構成データを格納するために使用され得、それ故、この文脈において、ときには構成メモリセルと呼ばれる。

【0015】

図1は、メモリセル18のアレイを含み得る集積回路を示す。任意の適切なメモリアレイ構造は、メモリセル18に対して使用され得る。1つの適切な配列が、図1に示される。図1の例示的なアレイにおいて3つの行および列のみのメモリセル18であるが、概してメモリアレイ17において数百または数千の行および列があり得る。アレイ17は、所与のデバイス10上の多くのアレイのうちの1つであり得、より大きなアレイの一部分であるサブアレイであり得、または任意の他の適切なグループのメモリセル18であり得る。

【0016】

各メモリ要素は、対応する出力経路19において対応する出力信号OUTを供給し得る。構成メモリアレイにおいて、各信号OUTは、対応する経路26を介して運搬され得、かつ対応するトランジスタ(例えば、関連付けられたプログラマブル論理回路内のトランジスタ24または他の回路)を構成することにおいて使用され得る静的出力制御信号である。

【0017】

集積回路10は、信号をメモリアレイ17に供給するための制御回路網12を有し得る。制御回路網12は、ピン14を用いて外部供給源から、および経路(例えば、経路16)を用いて内部供給源から電源電圧、データ、および他の信号を受け取り得る。制御回路網12は、アドレシング回路網、データレジスタ回路網、書き込み回路網、読み取り回路網等のような回路網を含み得る。制御回路網12は、ピン14によって供給される電源電圧を使用して、経路(例えば、経路20および22)上に所望の時間変動信号および固定信号を生成し得る。

【0018】

メモリ要素に供給される信号は、ときには、集合的に制御信号と呼ばれ得る。特定の文脈において、これらの信号の一部は、電力信号、クリア信号、データ信号、アドレス信号等と呼ばれ得る。これらの異なる信号タイプは、互いに排他的ではない。例えば、アレイ17に対するクリア信号は、アレイ17をクリアするために使用され得る制御(アドレス)信号のタイプとして機能し得る。このクリア信号は、セル18内のインバータのような回路網に電力を供給することによって、電力信号のタイプとしても機能し得る。同様に、クリアする動作がメモリセル18において論理0を配置するように機能するので、クリア信号は、データ信号のタイプとして機能し得る。

【0019】

概して、経路20および22に関連付けられた伝導ラインの適切な数が任意であり得る。例えば、アレイ17の各行は、(例として)経路20のうちのそれぞれの1つにおいて関連付けられたアドレスライン(例えば、真アドレスラインおよび補アドレスライン)と、関連付けられた読み取り/書き込みイネーブルラインを有し得る。アレイ17の各列は、データラインを含むそれぞれの経路22を有し得る。用語「行」および「列」は、メモリアレイ17内のセル18の特定のグループを指す1つの方法を示すに過ぎず、ときには相互交換可能に使用され得る。必要に応じて、他のパターンのラインは、経路20および22において使用され得る。例えば、異なる数の電源信号、データ信号、およびアドレス信号が使用され得る。

【0020】

クリア信号は、共通のクリアラインを介して同時に、アレイ17のすべてのセルへルーティングされ得る。クリアラインは、垂直に配向されることにより、各経路22のクリアラインのうちの1つの分岐があり得るか、またはクリアラインは、水平に配向されることにより、各経路20のクリアラインのうちの1つの分岐があり得る。クリアラインは、必ずしも必要とされない。

【0021】

電力もこのタイプのグローバル方式で配分され得る。例えば、正の電源電圧Vccは、共用の水平または垂直コンダクタのパターンを用いて各セル18に並列に供給され得る。同様に、グラウンド電圧Vssは、共用の水平または垂直ラインのパターンを用いてセル18に並列に供給され得る。制御ライン(例えば、アドレスラインおよびデータライン)は、一般的に互いに対して直交である(例えば、アドレスラインは、垂直であるが、データラインは、水平であり、またはその逆の場合もある)。

【0022】

正の電源電圧Vccは、正の電源ラインを介して提供され得る。グラウンド電圧Vssは、グラウンド電源ラインを介して提供され得る。任意の適切な値が、正の電源電圧Vccおよびグラウンド電圧Vssに対して使用され得る。例えば、正の電源電圧Vccは、1.2ボルト、1.1ボルト、1.0ボルト、0.9ボルト、0.9ボルトより低いボルト、または他の任意の適切なボルトであり得る。グラウンド電圧Vssは、(一例として)0ボルトであり得る。典型的な配列において、電源電圧Vccは、1.0ボルトであり得、Vssは0ボルトであり得、アドレス信号、データ信号、およびクリア信号に対する信号レベルは、(低い場合)0ボルトから(高い場合)1.0ボルトまでの範囲を有し得る。Vccが時間の関数として変動し、Vssが0ボルトより低く、および制御信号がオーバードライブされる(すなわち、制御信号がVcc−Vssより大きな信号強度を有する)配列も使用され得る。

【0023】

図2は、第2のタイプの回路10−2の上に形成された第1のタイプの回路網10−1を有する集積回路10の断面側面図である。図2において示されるように、回路網10−1は、機械的回路網(例えば、ナノ電気機械的(NEM)リレー回路32)を含み得るが、回路網10−2は、相補型金属酸化物半導体(CMOS)回路30および関連付けられた誘電スタック50を含み得る。

【0024】

例えば、CMOS回路30は、半導体基板40において形成されたnチャンネル金属酸化物半導体(NMOS)トランジスタおよびpチャンネル金属酸化物半導体(PMOS)トランジスタのような金属酸化物半導体電界効果トランジスタ(MOSFET)、基板40おいて1つのトランジスタと別のトランジスタと分離するための浅いトレンチ分離(STI)構造のような構造、ポリシリコン抵抗器、およびCMOSテクノロジーを用いて形成され得る他のタイプの電気デバイスを含み得る。誘電スタック50は、基板40の表面の上に形成され得る。誘電スタック50は、酸化シリコンまたは他の誘電体の層を含み得、それらの中に導電性構造が形成される。誘電スタック50は、金属相互接続層(ときには、金属層または金属ルーティング層と呼ばれる)およびビア層52を含み得る。

【0025】

導電性ルーティングライン(ときには、金属相互接続経路と呼ばれる)は、金属ルーティング層において形成され得る。ビア層52は、垂直の伝導する構造(例えば、タングステンビア、銅ビア、アルミニウムビア、または他の金属ビアのような導電性ビア)を含み得、伝導する構造は、各導電性ビアの両側の端部において形成された導電性ルーティングラインを接続するように構成されている。基板40に最も近い金属ルーティング層は、第1の金属ルーティング層M1と呼ばれる。連続する金属ルーティング層は、金属ルーティング層M2、M3、...、Mtopをその順番において含み得、金属ルーティング層M2が、層M1に最も近く、金属ルーティング層Mtopが、層M1から最も離れている(すなわち、金属ルーティング層M1は、誘電スタックの底面層を表し、その一方で、金属ルーティング層Mtopは、誘電スタックの最上層を表す)。誘電スタック50は、金属ルーティング層の各隣接する対がビア層52によって分離されている交互する配列で構成され得る。

【0026】

回路32は、NEMリレースイッチ(例えば、リレースイッチ60、不揮発性デバイス、およびNEM製造テクノロジーを用いて形成され得る他のタイプの電気機械的デバイス)を含み得る。リレースイッチ60は、静電作動の機械的スイッチであり得、その状態は、その端子において適用される電圧レベルに依存する。例えば、スイッチ60は、誘電体74(ときには、ボディー誘電材料と呼ばれる)の層の表面上に形成された第1および第2のソース−ドレイン端子68を含み得る。伝導性ブリッジ部品66(ときには、金属チャンネルと呼ばれる)は、第1のソース−ドレイン端子の上に延在する第1の突起する部分66−1と、第2のソース−ドレイン端子の上に延在する第2の突起する部分66−2とを有し得る。ブリッジ部品66は、ゲート部品62(例えば、ポリシリコンゲート構造または金属ゲート構造)によって支持され得る。ブリッジ部品66およびゲート部品62は、誘電材料64によって分離され得る。ゲート部品62は、関連付けられた第1および第2のソースドレイン領域68の間に位置するチャンネル領域の上に懸下されているビームとして機能し得る。ゲート部品62は、チャンネル領域の外側に位置する固定する構造(示されていない)を介して誘電体74に取り付けられ得る。導電性ボディー電極70は、ゲート部品62より下において誘電体74の表面内に形成され得る。

【0027】

リレースイッチ60の状態は、適切な電圧をゲート62およびボディー70に適用することによって制御され得る。一例として、スイッチ60のゲート端子とボディー端子との間の電圧差が、所定の電圧閾値レベルより大きい場合、スイッチ60は、オン状態に配置され得る(すなわち、ビーム62は、部分66−1および66−2を第1および第2のソース−ドレイン端子68と接触して配置することによってソース−ドレイン端子と接触するように低下され得る)。スイッチ60のゲート端子とボディー端子との間の電圧差が、所定の電圧閾値レベルより小さい場合、スイッチ60は、オフ状態に配置され得る(すなわち、ビーム62は、第1および第2のソース−ドレイン端子68が部分66−1および66−2と接触しないように上昇され得る)。スイッチ60がオフ状態に配置される場合に、ブリッジ部品66とソース−ドレイン構造68とは、(例として)空気によって分離され得る。

【0028】

本発明の1つの適切な配列において、メモリアレイ17、メモリアドレシング回路網、メモリデータレジスタ回路網、メモリ書き込みドライバー回路網、メモリ読み取り回路網、および他の周辺メモリ制御回路網は、部分10−1において形成され得、その一方で、構成可能な論理回路(例えば、パストランジスタ24、受動集積回路部品(例えば、集積回路抵抗器、キャパシタ、およびコンダクタ)、デジタルおよびアナログ処理ユニット、並びに他の非メモリ関連の回路網は、部分10−2において形成され得る(例えば、部分10−1が、部分10−2の上に形成され得る)。

【0029】

上部部分10−1のリレースイッチ60が構成メモリセル18の一部分を形成する図2の例を考察する。スイッチ60の第1のソース−ドレイン領域68は、出力19として機能し得、静的制御信号OUTが出力19において提供される(例えば、図1を参照)。静的制御信号OUTは、下部部分10−2において形成された対応するパストランジスタ24に供給され得る。図2において示されるように、パストランジスタ24は、基板40において形成されたソース−ドレイン領域46、ソース−ドレイン領域46間に位置するチャンネル領域の上に形成されたゲート42、ゲート42と関連付けられたチャンネル領域との間に配置されたゲート絶縁層44を含む。

【0030】

上部部分10−1のスイッチ60は、経路26を通して対応するパストランジスタ24に連結され得る。図2において示されるように、スイッチ60の第1のソース−ドレイン端子68は、誘電層74において形成されたビア69を通して、金属層M1−Mtopにおいて形成された金属スタブ56を通して、金属スタブ56を接続する金属ビア58を通して、そして金属ルーティング層M1の金属スタブ56をゲート42に接続する金属ビア58’を通してトランジスタ24に連結され得る。この例は、単なる例示に過ぎず、本発明の範囲を限定するものではない。必要に応じて、部分10−1の回路網と部分10−2の回路網との間の他の電気的接続が、この方法で作られ得る。例えば、部分10−2において形成された処理回路網30は、誘電スタック50を通る経路35を介して制御信号Vctrを部分10−1の回路網34に送信するように構成され得る。

【0031】

メモリ回路網がもはや論理および他の処理回路網と同じ平面上に形成される必要がないので、部分10−2の他のCMOS回路網の直接上に部分10−1のメモリ回路網を形成することは、実質的に貴重な集積回路の実領域を節約し得る。本発明の別の適切な配列において、回路網10−1は、第1の正電源電圧Vcc1をNEMリレー回路32に、および第2の正電源電圧Vcc2をCMOS回路30に提供するように動作可能な電源および制御回路網34を含み得る。回路網34は、NEMデバイスを用いて形成され得る。この配列を用いて提供された電力ドメイン分離は、部分10−1において動作するメモリ回路網が増大された性能のためにオーバードライブされることを可能にしながら、部分10−2において動作する回路網のための電力消費を低減させ得る。例えば、電源および制御回路網34は、上部部分10−1のメモリ回路網に電力を供給するために1.2ボルトを供給し、下部部分10−2の回路30に電力を供給するために0.85ボルトを供給し得る。

【0032】

図3は、第1のタイプのリレースイッチ60−1の概略的ダイヤグラムである。図3において示されるように、リレースイッチ60−1は、ソース−ドレイン端子SD1およびSD2、ゲート端子G、およびボディー(またはバルク)端子Bを有し得る。リレースイッチ60−1は、不揮発性挙動を示し得、この挙動において、たとえスイッチ60−1のゲートおよびボディー端子が任意の電力を供給されなくても、スイッチの状態が保存される。

【0033】

図4は、不揮発性リレースイッチ60−1の動作を例示する状態ダイヤグラムである。スイッチ60−1がオフ状態80(すなわち、SD1およびSD2が切断されている状態)にある場合、スイッチ60−1は、端子GとBとの間の電圧差(VGB)が所定のプルイン電圧閾値VPIを超えるように、端子GおよびBをバイアシングすることによってオンにされ得る。スイッチ60−1がオン状態82(すなわち、SD1およびSD2がブリッジ部品66を通して電気的かつ機械的に接続されている状態)にある場合、スイッチ60−2は、VGBが所定のプルアウト電圧閾値VPOより小さくなるように、端子GおよびBをバイアシングすることによってオフにされ得る。スイッチ60−1は、プルインの基準が満たされるまで(VGBがVPOより小さいか否かに関わらず)、オフ状態80のままであり得る。同様に、スイッチ60−2は、プルアウトの条件が満たされるまで(VGBがVPIより大きいか否かに関わらず)、オン状態82のままであり得る。(一例として)閾値VPIは、正の値を有し得、その一方で、VPOは、負の値を有し得る。

【0034】

例えば、デバイス10が電源オンにされており、かつスイッチ60−1が最初にオフ状態にあるシナリオを考察する。制御回路網は、スイッチ60−1をオン状態に配置するためにVGBがVPIを超えるように、スイッチ60−1をバイアシングするために使用され得る。次に、デバイス10が電源オフにされ得る。再びデバイス10に電力を供給すると、スイッチ60−1は、オン状態のままであり得る。デバイス10が電源オンにされており、かつスイッチ60−1が最初にオン状態にあるシナリオを考察する。制御回路網は、スイッチ60−1をオフ状態に配置するためにVGBがVPOより小さくなるように、スイッチ60−1をバイアシングするために使用され得る。次に、デバイス10が電源オフにされ得る。再びデバイス10に電力を供給すると、スイッチ60−1は、オフ状態のままであり得る。このような動作特性を有するリレースイッチ60−1は、不揮発性メモリ要素を形成するために使用され得る。

【0035】

図5は、例示的な不揮発性メモリセル18の回路ダイヤグラムである。図5において示されるように、リレースイッチ90および92は、正電源ライン84(例えば、正電源電圧Vcc1が提供される電源ライン)とグラウンド電源ライン86(例えば、グラウンド電源電圧Vssが提供されるグラウンドライン)との間のスイッチのソース−ドレイン端子を通して直列に連結され得る。スイッチ90および92は、図3および4に関連して説明されたタイプの不揮発性リレースイッチであり得る。スイッチ90の状態は、電圧VG1とVB1との相対的な大きさによって制御され得、その一方で、スイッチ92の状態は、電圧VG2とVB2との相対的な大きさによって制御され得る。図2に関連して説明された回路網34は、メモリセル18のスイッチ90および92に対するこれらの電圧を制御するために使用され得る。スイッチ90および92は、静的制御信号OUTが提供される中間ノードにおいて直列接続であり得る。

【0036】

図5のセル18は、不揮発性メモリ要素(すなわち、デバイス10が電力を供給されるか否かに関わらず、その状態を保持するメモリセル)であり得る。例えば、デバイス10が電源オンにされており、かつ所与のセル18が最初に「1」を格納している(すなわち、信号OUTが高である)シナリオを考察する。制御回路網は、「0」を所与のセル内に書き込むために、スイッチ90をオフにし、かつスイッチ92をオンにするように使用され得る。次に、デバイス10が電源オフにされ得る。再びデバイス10に電力を供給すると、所与のセルは、「0」を格納したままであり得る(すなわち、たとえスイッチ90および92が任意の電圧を供給されなくても、スイッチは、それらの状態を保持する)。デバイス10が電源オンにされており、かつ所与のセルが最初に「0」を格納している(すなわち、信号OUTが低である)別のシナリオを考察する。制御回路網は、「1」を所与のセル内に書き込むために、スイッチ90をオンにし、かつスイッチ92をオフにするように使用され得る。ゲート−バルク電圧VGB1およびVGB2は、デバイス10の通常動作中、0ボルトと等しい場合がある。たとえVGB1がVPIより小さく、かつVGB2がVPOより大きくても、所与のセルは、「1」を格納したままである(すなわち、プルイン/プルアウト条件が満たされない限り、スイッチ90および92は、それらの状態を保持する)。

【0037】

中間出力ノードに衝突する高エネルギー宇宙線がゲートおよびバルク端子に影響を与えないので、このタイプのメモリセル18も、ソフトエラーアップセット不感性を示す。たとえアルファ粒子がゲートおよびバルク端子のうちの1つに衝突したとしても、プルイン条件またはプルアウト条件が満たされ、セル18のスイッチ90および92のうちの1つの状態を反転するように、このイベントがVGBを駆動することは到底ありそうもない。

【0038】

図6は、図5のメモリセル18を動作させるための例示的な電圧バイアシング値の表である。「1」をセル内に書き込むために、VG1およびVB1は、プルアップリレースイッチ90をオンにするようにそれぞれ1.0ボルトおよび−1.0ボルトに駆動され得、その一方で、VG2およびVB2は、プルダウンリレースイッチ92をオフにするようにそれぞれ−1.0ボルトおよび1.0ボルトに駆動され得る。この例において、VPIは、1.5ボルトと等しく、VPOは、−1.5ボルトと等しい。プルアウト要求が満たされるまで(すなわち、VGBがVPOより小さくなるまで)、スイッチ90は、閉鎖状態に留まる。同様に、プルイン閾値が満たされるまで(すなわち、VGBがVPIより大きくなるまで)、スイッチ92は、開放状態に留まる。

【0039】

「0」をセル内に書き込むために、VG1およびVB1は、プルアップリレースイッチ90をオフにする(VGBがVPOより小さい)ようにそれぞれに−1.0ボルトおよび1.0ボルトに駆動され得、その一方で、VG2およびVB2は、プルダウンリレースイッチ92をオンにする(VGBがVPIより大きい)ようにそれぞれに1.0ボルトおよび−1.0ボルトに駆動され得る。プルイン要求が満たされるまで(すなわち、VGBがVPIより大きくなるまで)、スイッチ90は、開放状態に留まり、プルアウト閾値が満たされるまで(すなわち、VGBがVPOより小さくなるまで)、スイッチ92は、閉鎖状態に留まる。概して、セル18の状態は、ロード「1」またはロード「0」の条件が満たされるまでに変化されないままであり得る。VG1、VB1、VG2、およびVB2は、セル18の通常動作の中、接地され得る(例えは、VG1、VB1、VG2、およびVB2が0ボルトに駆動され、セル18が、その電流状態を保持する)。

【0040】

図7は、第2のタイプのリレースイッチ60−2の概略的ダイヤグラムである。図7に示されるように、リレースイッチ60−2は、ソース−ドレイン端子SD1およびSD2、ゲート端子G、並びにボディー(またはバルク)端子Bを有し得る。リレースイッチ60−2は、そのゲートおよびボディー端子が電力を供給されない場合に、スイッチ60−2の状態が失われる揮発性挙動を示し得る。スイッチ60−2のゲート部品がソース−ドレインコンダクタに向かって曲げられる量は、ビーム変位Xとして規定される。

【0041】

図8は、ビーム変位対ゲート−バルク電圧VGBのプロットである。図8において示されるように、ビーム変位Xは、VGBがプルアウト閾値VPOより小さい場合に最小である(すなわち、VGBがVPOより小さい場合に、スイッチ60−2がオフにされる)。ビーム変位は、VGBがプルイン閾値VPIより大きい場合に最大にされる(すなわち、VGBがVPIより大きい場合に、スイッチ60−2がオンにされる)。スイッチ60−2は、オン/オフの電圧遷移が異なる(例えば、オン/オフの遷移要求がスイッチ60−2の電流状態に依存する)ヒステリシス挙動を示し得る。

【0042】

例えば、スイッチ60−2が最初にオフ状態にあるシナリオを考察する。VGBが徐々に増大され場合に、ビーム変位Xは増大する。スイッチ60−2は、VGBがVPIを超える場合にオン状態に配置される(遷移100を参照)。次にVGBが徐々に減少される場合に、たとえVGBがVPI以下に落ちても(VGBがなおVPOより大きい限り)、スイッチ60−2はオン状態のままである。一旦VGBがVPO以下に低下されると、スイッチ60−2はオフにされる(遷移102を参照)。この例において、VPIは、VPOより大きい。図8は、単なる例示に過ぎず、本発明の範囲を限定するものではない。必要に応じて、VPIは、VPO以下であり得る。

【0043】

図9は、本発明の1つの実施形態に従う、CMOSトランジスタおよびNEMリレースイッチを含むメモリセル18の回路ダイヤグラムである。図9において示されるように、セル18は、第1および第2の交差連結された反転回路INV1およびINV2を含み得る。反転回路INV1は、第1の正電源ライン108(例えば、正電源電圧Vcc1が提供される電源ライン)と第1のグラウンドライン110(例えば、グラウンド電源電圧Vss1が提供される電源ライン)との間に直列に連結されたリレースイッチ112および114を含み得る。スイッチ112および114は、図7および8に関連して説明されたタイプの揮発性リレースイッチ60−2であり得る。スイッチ112のバルク端子は、電源ライン108に連結され得、その一方で、スイッチ110のバルク端子は、電源ライン110に連結され得る。

【0044】

反転回路INV2は、第2の正電源ライン104(例えば、正電源電圧Vcc2が提供される電源ライン)と第2のグラウンドライン106(例えば、グラウンド電源電圧Vss2が提供される電源ライン)との間に直列に連結されたpチャンネルプルアップトランジスタPU(例えば、pチャンネル金属酸化物半導体デバイス)およびnチャンネルプルダウントランジスタPD(例えば、nチャンネル金属酸化物半導体デバイス)を含み得る。この例において、リレースイッチ112および114に関連付けられたVcc1/Vss1は、COMSトランジスタPUおよびPDに関連付けられたVcc2/Vss2と等しい大きさかまたは異なる大きさであり得る(すなわち、リレーデバイスおよびCMOSデバイスが、別個の電源ラインを用いて電力を供給される)。

【0045】

反転回路INV1およびINV2は、各々、入力および出力を有し得る。INV1の出力は、INV2の入力に連結され得、メモリセル18に対して第1のデータストレージノードnOUTとして機能し得る。INV2の出力は、INV1の入力に連結され得、メモリセル18に対して第2のデータストレージノードOUTとして機能し得る。この方法で交差連結された反転回路INV1およびINV2は、単一データビットの真バーションおよび補バージョンを、それぞれ、データストレージノードnOUTおよびOUTにおいて格納するためのラッチとして使用され得る。例えば、セル18は、「0」を格納するために使用され得る(すなわち、ノードOUTが低であり、かつノードnOUTが高である)か、または「1」を格納するために使用され得る(すなわち、ノードOUTが高であり、かつノードnOUTが低である)。それ故、セル18のこの交差連結された部分は、ときには、双安定メモリ要素と呼ばれ得る。

【0046】

トランジスタAC1のような第1のアクセストランジスタは、データステージノードnOUTと第1のデータライン(例えば、真ビットライン信号BLが提供されるデータライン)との間に連結され得る。トランジスタAC2のような第2のアクセストランジスタは、データステージノードOUTと第2のデータライン(例えば、補ビットライン信号nBLが提供されるデータライン)との間に連結され得る。トランジスタAC1およびAC2のゲートは、対応するワードライン信号WLを用いて制御され得る。アクセストランジスタは、(例えば、WLをアサートし、ビットライン信号を適切な電圧レベルにバイアシングすることによって)、メモリセル18からデータを読み取るために、かつメモリセル18内にデータを書き込むために使用され得る。ワードライン信号WLは、ときにはアドレス信号と呼ばれ得、その一方で、トランジスタAC1およびAC2は、ときには、アドレストランジスタと呼ばれ得る。

【0047】

図9のセル18のリレースイッチ112および114は、上部デバイス部分10−1において形成され得(例えば、図2を参照)、その一方で、トランジスタPU、PD、AC1、およびAC2は、下部デバイス部分10−2において形成され得る。リレーインバータ回路INV1の入力および出力は、誘電スタック50のビア経路26を通して下へ、トランジスタAC1およびCMOSインバータ回路INV2に連結され得る。

【0048】

リレーデバイスの機械的スイッチング遅延が、セルが高エネルギー宇宙線によって引き起こされる妨害下にある時間よりはるかに長い期間である傾向を有するので、図9に関連して説明されたタイプのメモリセル18は、ソフトエラーアップセット不感性を示す。例えば、セル18が「0」を格納しており、侵入するアルファ粒子が時間t0において出力ノードOUTに衝突するシナリオを考察する(例えば、図10のタイミングダイヤグラムを参照)。(例として)このイベントは、結果としてノードOUTにおいて注入されるパルス状の電流IINJ_OUT(例えば、0.5μAのピークを有する電流パルス)を生じ得、ノードOUTでの電圧(VOUT)が1.2ボルトの正電源電圧に向かって上昇するようにし得る。VOUTにおいてこの一時的上昇は、スイッチ114をオンにし、かつスイッチ112をオフにすることを始動させる。しかしながら、スイッチ112および114のゲート部品にとってプルインまたはプルアウトまでかかる時間(例えば、時間t0からt2まで)が約ナノ秒であるが、注入されたノイズ電流の期間(例えば、時間t0からt1まで)が約ピコ秒であるので、ノードnOUTは、t1において高のままである。時間t1の後に、トランジスタPDは、オンであり、VOUTを放電し、グラウンドに戻るように機能する(すなわち、セル18は、その格納された「0」の値を保持する)。

【0049】

図11は、本発明の実施形態に従うメモリセル18の別の適切な配列を示す。図11において示されるように、セル18は、第1および第2の交差連結された反転回路INV1およびINV2を含み得る。反転回路INV1は、第1の正電源ライン108と共通グラウンドライン107(例えば、グラウンド電源電圧Vssが提供される電源ライン)との間に直列に連結されたリレースイッチ112およびnチャンネルトランジスタPD1を含み得る。スイッチ112は、図7および8に関連して説明されたタイプのリレースイッチ60−2であり得る。スイッチ112のバルク端子は、電源ライン108に連結され得る。

【0050】

反転回路INV2は、第2の正電源ライン104と共通グラウンドライン107との間に直列に連結されたpチャンネルプルアップトランジスタPUおよびnチャンネルプルダウントランジスタPD2を含み得る。この例において、INV1に関連付けられたVcc1は、INV2に関連付けられたVcc2と等しい大きさかまたは異な大きさであり得るが、Vssは、INV1およびINV2の両方に供給され得る。必要に応じて、INV1およびINV2は、それぞれのグラウンド電源ラインから異なるグラウンド電圧信号を受け取り得る。

【0051】

反転回路INV1およびINV2は、各々、入力および出力を有し得る。INV1の出力は、INV2の入力に連結され得、メモリセル18に対して第1のデータストレージノードnOUTとして機能し得る。INV2の出力は、INV1の入力に連結され得、メモリセル18に対して第2のデータストレージノードOUTとして機能し得る。第1のアクセストランジスタAC1は、データステージノードnOUTと第1のデータラインとの間に連結され得、その一方で、第2のアクセストランジスタAC2は、データステージノードOUTと第2のデータラインとの間に連結され得る。トランジスタAC1およびAC2のゲートは、対応するワードライン信号WLを用いて制御され得る。アクセストランジスタは、メモリセル18からデータを読み取るために、かつメモリセル18内にデータを書き込むために使用され得る。

【0052】

図11のセル18のリレースイッチ112は、上部デバイス部分10−1において形成され得(例えば、図1を参照)、その一方で、トランジスタPD1、PD2、PU、AC1、およびAC2は、標準CMOS製造技術を用いて下部デバイス部分10−2において形成され得る。リレースイッチ112は、誘電スタック50のビア経路26を通して下へ、トランジスタAC1、PD1、およびCMOSインバータ回路INV2に連結され得る。

【0053】

図11に関連して説明されたタイプのメモリセル18も、ソフトエラーアップセット不感性を示すために使用され得る。例えば、セル18が「0」を格納しており、(矢印200によって示されるように)侵入するアルファ粒子が出力ノードOUTに衝突するシナリオを考察する。これは、VOUTが高へ上昇するようにし、トランジスタPD1をオンにする。リレーデバイスの機械的スイッチングが、COMSトランジスタの電気的スイッチングに比べて比較的に遅いので、VOUTが高である期間に対してスイッチ112は、オンのままである。スイッチ112およびトランジスタPD1の両方がオンである場合に、スイッチ112のオンの抵抗がトランジスタPD1のオンの抵抗より実質的に低い(すなわち、リレーデバイスの機械的コンダクタンスが、CMOSトランジスタの電子的コンダクタンスより実質的に高い)ので、VnOUTは、比較的に高い状態(例えば、Vcc1の50%より大きい)に留まる。結果として、粒子200の影響がなくなる場合に、ノードnOUTでの高電圧は、PD2がノードOUTを放電し、グラウンドに戻ることを可能にする。

【0054】

セル18が「1」を格納しており、かつ侵入するアルファ粒子200は、VOUTが低に落ちるようにし、トランジスタPD1をオフにするように出力ノードOUTに衝突する別のシナリオを考察する。スイッチ112の遅い機械的スイッチングのため、スイッチ112は、VOUTが低である期間に対してオフのままである。スイッチ112およびトランジスタPD1の両方がオフである場合に、ノードnOUTは、浮動しており、それ故、VnOUTは、低に留まる。結果として、粒子200の影響がなくなる場合に、ノードnOUTでの低電圧は、トランジスタPUがOUTを充電し、Vcc2に戻ることを可能にする。

【0055】

図9および11のメモリセル構成は、単なる例示に過ぎず、本発明の範囲を限定するものではない。必要に応じて、リレースイッチは、6個より少ないスイッチングデバイスかまたは6個より多いスイッチングデバイスを有するメモリセル、多重ポートメモリセル、読み取りバッファー回路を有するメモリセル、2つより多い交差連結された反転回路を有するメモリセル、および他のタイプのメモリ要素において使用され得る。NEMリレーデバイスが、CMOSトランジスタに対して実質的により少ないソース−ドレイン漏れ電流を示すので、リレーデバイスを含むメモリセルはまた、低減された電力消費を示し得る。

【0056】

追加の実施形態:

(追加の実施形態1)

集積回路であって、該集積回路は、基板において形成された回路網と、該回路網の上における複数の機械的リレーメモリ回路とを含む、集積回路。

(追加の実施形態2)

上記回路網と上記複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む、追加の実施形態1に記載の集積回路。

(追加の実施形態3)

上記誘電スタックは、複数の金属ルーティング層およびビア層を含む、追加の実施形態2に記載の集積回路。

(追加の実施形態4)

上記回路網は、相補型金属酸化物半導体回路網を含む、追加の実施形態1に記載の集積回路。

(追加の実施形態5)

上記回路網は、上記複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である、追加の実施形態1に記載の集積回路。

(追加の実施形態6)

上記複数の機械的リレーメモリ回路のうちの少なくとも1つは、異なる電圧レベルを有する1対の電源ラインの間に直列に連結された1対の機械的リレースイッチを含む、追加の実施形態5に記載の集積回路。

(追加の実施形態7)

上記1対の機械的リレースイッチは、1対の不揮発性機械的リレースイッチを含む、追加の実施形態6に記載の集積回路。

(追加の実施形態8)

上記複数の機械的リレーメモリ回路は、少なくとも1つの機械的リレースイッチを含み、上記回路網は、双安定メモリ要素を形成するために該少なくとも1つの機械的リレースイッチに連結されているインバータを含む、追加の実施形態5に記載の集積回路。

(追加の実施形態9)

上記少なくとも1つの機械的リレースイッチは、揮発性機械的リレースイッチである、追加の実施形態8に記載の集積回路。

(追加の実施形態10)

上記集積回路は、ユーザーから構成データを受け取るように動作可能なプログラマブル集積回路を含み、上記複数の機械的リレーメモリ回路は、該構成データを格納するように動作可能である、追加の実施形態1に記載の集積回路。

(追加の実施形態11)

メモリ要素であって、該メモリ要素は、直列に連結された少なくともnチャンネルトランジスタおよびpチャンネルトランジスタを有する第1の反転回路と、少なくとも1つの機械的リレースイッチを有する第2の反転回路とを含む、メモリ要素。

(追加の実施形態12)

上記第1および第2の反転回路は、一緒に交差連結されている、追加の実施形態11に記載のメモリ要素。

(追加の実施形態13)

上記第2の反転回路は、上記少なくとも1つの機械的リレースイッチと直列に連結されている回路をさらに含む、追加の実施形態11に記載のメモリ要素。

(追加の実施形態14)

上記回路は、機械的リレースイッチを含む、追加の実施形態13に記載のメモリ要素。

(追加の実施形態15)

上記回路は、金属酸化物半導体トランジスタを含む、追加の実施形態13に記載のメモリ要素。

(追加の実施形態16)

上記回路は、nチャンネルトランジスタを含む、追加の実施形態15に記載のメモリ要素。

(追加の実施形態17)

データラインと、該データラインと上記第1の反転回路との間に連結された少なくとも1つのアクセストランジスタとをさらに含む、追加の実施形態16に記載のメモリ要素。

(追加の実施形態18)

メモリ要素であって、該メモリ要素は、第1の電源電圧を供給するように動作可能な第1の電源ラインに連結されたpチャンネルトランジスタを有する第1の反転回路と、該第1の電源ラインと異なる第2の電源ラインに連結された少なくとも1つの機械的リレースイッチを有する第2の反転回路とを含み、該第2の電源ラインは、該第1の電源電圧と異なる第2の電源電圧を供給するように動作可能である、メモリ要素。

(追加の実施形態19)

上記第1および第2の反転回路は、一緒に交差連結されている、追加の実施形態18に記載のメモリ要素。

(追加の実施形態20)

第3の電源ラインと、上記第1の電源ラインと該第3の電源ラインとの間に上記pチャンネルトランジスタと直列に連結された第1のnチャンネルトランジスタとをさらに含む、追加の実施形態18に記載のメモリ要素。

(追加の実施形態21)

上記第2の反転回路は、上記第2の電源ラインと上記第3の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された第2のnチャンネルトランジスタをさらに含む、追加の実施形態20に記載のメモリ要素。

(追加の実施形態22)

第4の電源ラインをさらに含み、上記第2の反転回路は、上記第2の電源ラインと該第4の電源ラインとの間に上記少なくとも1つの機械的リレースイッチと直列に連結された追加の機械的リレースイッチをさらに含み、上記第3の電源ラインおよび該第4の電源ラインは、異なる電源電圧を供給するように動作可能である、追加の実施形態20に記載のメモリ要素。

(追加の実施形態23)

プログラマブル集積回路であって、該プログラマブル集積回路は、少なくとも1つのnチャンネルトランジスタと少なくとも1つの機械的リレースイッチとを含む双安定メモリ要素を含み、該双安定メモリ要素は、静的制御信号が提供される出力を有する、プログラマブル集積回路。

(追加の実施形態24)

上記静的制御信号を受け取るように動作可能なゲートを有するパストランジスタをさらに含み、該パストランジスタは、上記プログラマブル集積回路上のプログラマブル論理回路網の一部を形成する、追加の実施形態23に記載のプログラマブル集積回路。

(追加の実施形態25)

上記双安定メモリ要素は、上記少なくとも1つのnチャンネルトランジスタと直列に連結されているpチャンネルトランジスタと、上記少なくとも1つの機械的リレースイッチと直列に連結されている追加の機械的リレースイッチとをさらに含む、追加の実施形態23に記載のプログラマブル集積回路。

(追加の実施形態26)

基板と、誘電層と、該基板と該誘電層との間に配置された少なくとも1つの金属ルーティング層とをさらに含み、上記nチャンネルトランジスタは、基板において形成され、上記機械的リレースイッチは、誘電層において形成されている、追加の実施形態23に記載のプログラマブル集積回路。

【0057】

上記の内容は、単なる本発明の原理の例示に過ぎず、さまざまな改変が、本発明の範囲および精神から逸脱することなしに、当業者によって加えられ得る。上記実施形態は、単独も任意の組み合わせでも実装され得る。

【符号の説明】

【0058】

10 集積回路

12 制御回路網

14 ピン

16、20、22、26 経路

17 メモリアレイ

18 メモリセル

19 出力

24 パストランジスタ

【特許請求の範囲】

【請求項1】

集積回路であって、該集積回路は、

基板において形成された回路網と、

該回路網の上における複数の機械的リレーメモリ回路と

を含む、集積回路。

【請求項2】

前記回路網と前記複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む、請求項1に記載の集積回路。

【請求項3】

前記誘電スタックは、複数の金属ルーティング層およびビア層を含む、請求項2に記載の集積回路。

【請求項4】

前記回路網は、相補型金属酸化物半導体回路網を含む、請求項1に記載の集積回路。

【請求項5】

前記回路網は、前記複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である、請求項1に記載の集積回路。

【請求項6】

前記複数の機械的リレーメモリ回路のうちの少なくとも1つは、異なる電圧レベルを有する1対の電源ラインの間に直列に連結された1対の機械的リレースイッチを含む、請求項5に記載の集積回路。

【請求項7】

前記1対の機械的リレースイッチは、1対の不揮発性機械的リレースイッチを含む、請求項6に記載の集積回路。

【請求項8】

前記複数の機械的リレーメモリ回路は、少なくとも1つの機械的リレースイッチを含み、前記回路網は、双安定メモリ要素を形成するために該少なくとも1つの機械的リレースイッチに連結されているインバータを含む、請求項5に記載の集積回路。

【請求項9】

前記少なくとも1つの機械的リレースイッチは、揮発性機械的リレースイッチである、請求項8に記載の集積回路。

【請求項10】

前記集積回路は、ユーザーから構成データを受け取るように動作可能なプログラマブル集積回路を含み、前記複数の機械的リレーメモリ回路は、該構成データを格納するように動作可能である、請求項1に記載の集積回路。

【請求項11】

メモリ要素であって、該メモリ要素は、

直列に連結された少なくともnチャンネルトランジスタおよびpチャンネルトランジスタを有する第1の反転回路と、

少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含む、メモリ要素。

【請求項12】

前記第1および第2の反転回路は、一緒に交差連結されている、請求項11に記載のメモリ要素。

【請求項13】

前記第2の反転回路は、前記少なくとも1つの機械的リレースイッチと直列に連結されている回路をさらに含む、請求項11に記載のメモリ要素。

【請求項14】

前記回路は、機械的リレースイッチを含む、請求項13に記載のメモリ要素。

【請求項15】

前記回路は、金属酸化物半導体トランジスタを含む、請求項13に記載のメモリ要素。

【請求項16】

前記回路は、nチャンネルトランジスタを含む、請求項15に記載のメモリ要素。

【請求項17】

データラインと、

該データラインと前記第1の反転回路との間に連結された少なくとも1つのアクセストランジスタと

をさらに含む、請求項16に記載のメモリ要素。

【請求項18】

メモリ要素であって、該メモリ要素は、

第1の電源電圧を供給するように動作可能な第1の電源ラインに連結されたpチャンネルトランジスタを有する第1の反転回路と、

該第1の電源ラインと異なる第2の電源ラインに連結された少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含み、

該第2の電源ラインは、該第1の電源電圧と異なる第2の電源電圧を供給するように動作可能である、メモリ要素。

【請求項19】

前記第1および第2の反転回路は、一緒に交差連結されている、請求項18に記載のメモリ要素。

【請求項20】

第3の電源ラインと、

前記第1の電源ラインと該第3の電源ラインとの間に前記pチャンネルトランジスタと直列に連結された第1のnチャンネルトランジスタと

をさらに含む、請求項18に記載のメモリ要素。

【請求項21】

前記第2の反転回路は、前記第2の電源ラインと前記第3の電源ラインとの間に前記少なくとも1つの機械的リレースイッチと直列に連結された第2のnチャンネルトランジスタをさらに含む、請求項20に記載のメモリ要素。

【請求項22】

第4の電源ラインをさらに含み、

前記第2の反転回路は、前記第2の電源ラインと該第4の電源ラインとの間に前記少なくとも1つの機械的リレースイッチと直列に連結された追加の機械的リレースイッチをさらに含み、前記第3の電源ラインおよび該第4の電源ラインは、異なる電源電圧を供給するように動作可能である、請求項20に記載のメモリ要素。

【請求項23】

プログラマブル集積回路であって、該プログラマブル集積回路は、

少なくとも1つのnチャンネルトランジスタと少なくとも1つの機械的リレースイッチとを含む双安定メモリ要素を含み、

該双安定メモリ要素は、静的制御信号が提供される出力を有する、プログラマブル集積回路。

【請求項24】

前記静的制御信号を受け取るように動作可能なゲートを有するパストランジスタをさらに含み、該パストランジスタは、前記プログラマブル集積回路上のプログラマブル論理回路網の一部を形成する、請求項23に記載のプログラマブル集積回路。

【請求項25】

前記双安定メモリ要素は、

前記少なくとも1つのnチャンネルトランジスタと直列に連結されているpチャンネルトランジスタと、

前記少なくとも1つの機械的リレースイッチと直列に連結されている追加の機械的リレースイッチと

をさらに含む、請求項23に記載のプログラマブル集積回路。

【請求項26】

基板と、

誘電層と、

該基板と該誘電層との間に配置された少なくとも1つの金属ルーティング層と

をさらに含み、

前記nチャンネルトランジスタは、基板において形成され、前記機械的リレースイッチは、誘電層において形成されている、請求項23に記載のプログラマブル集積回路。

【請求項1】

集積回路であって、該集積回路は、

基板において形成された回路網と、

該回路網の上における複数の機械的リレーメモリ回路と

を含む、集積回路。

【請求項2】

前記回路網と前記複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む、請求項1に記載の集積回路。

【請求項3】

前記誘電スタックは、複数の金属ルーティング層およびビア層を含む、請求項2に記載の集積回路。

【請求項4】

前記回路網は、相補型金属酸化物半導体回路網を含む、請求項1に記載の集積回路。

【請求項5】

前記回路網は、前記複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である、請求項1に記載の集積回路。

【請求項6】

前記複数の機械的リレーメモリ回路のうちの少なくとも1つは、異なる電圧レベルを有する1対の電源ラインの間に直列に連結された1対の機械的リレースイッチを含む、請求項5に記載の集積回路。

【請求項7】

前記1対の機械的リレースイッチは、1対の不揮発性機械的リレースイッチを含む、請求項6に記載の集積回路。

【請求項8】

前記複数の機械的リレーメモリ回路は、少なくとも1つの機械的リレースイッチを含み、前記回路網は、双安定メモリ要素を形成するために該少なくとも1つの機械的リレースイッチに連結されているインバータを含む、請求項5に記載の集積回路。

【請求項9】

前記少なくとも1つの機械的リレースイッチは、揮発性機械的リレースイッチである、請求項8に記載の集積回路。

【請求項10】

前記集積回路は、ユーザーから構成データを受け取るように動作可能なプログラマブル集積回路を含み、前記複数の機械的リレーメモリ回路は、該構成データを格納するように動作可能である、請求項1に記載の集積回路。

【請求項11】

メモリ要素であって、該メモリ要素は、

直列に連結された少なくともnチャンネルトランジスタおよびpチャンネルトランジスタを有する第1の反転回路と、

少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含む、メモリ要素。

【請求項12】

前記第1および第2の反転回路は、一緒に交差連結されている、請求項11に記載のメモリ要素。

【請求項13】

前記第2の反転回路は、前記少なくとも1つの機械的リレースイッチと直列に連結されている回路をさらに含む、請求項11に記載のメモリ要素。

【請求項14】

前記回路は、機械的リレースイッチを含む、請求項13に記載のメモリ要素。

【請求項15】

前記回路は、金属酸化物半導体トランジスタを含む、請求項13に記載のメモリ要素。

【請求項16】

前記回路は、nチャンネルトランジスタを含む、請求項15に記載のメモリ要素。

【請求項17】

データラインと、

該データラインと前記第1の反転回路との間に連結された少なくとも1つのアクセストランジスタと

をさらに含む、請求項16に記載のメモリ要素。

【請求項18】

メモリ要素であって、該メモリ要素は、

第1の電源電圧を供給するように動作可能な第1の電源ラインに連結されたpチャンネルトランジスタを有する第1の反転回路と、

該第1の電源ラインと異なる第2の電源ラインに連結された少なくとも1つの機械的リレースイッチを有する第2の反転回路と

を含み、

該第2の電源ラインは、該第1の電源電圧と異なる第2の電源電圧を供給するように動作可能である、メモリ要素。

【請求項19】

前記第1および第2の反転回路は、一緒に交差連結されている、請求項18に記載のメモリ要素。

【請求項20】

第3の電源ラインと、

前記第1の電源ラインと該第3の電源ラインとの間に前記pチャンネルトランジスタと直列に連結された第1のnチャンネルトランジスタと

をさらに含む、請求項18に記載のメモリ要素。

【請求項21】

前記第2の反転回路は、前記第2の電源ラインと前記第3の電源ラインとの間に前記少なくとも1つの機械的リレースイッチと直列に連結された第2のnチャンネルトランジスタをさらに含む、請求項20に記載のメモリ要素。

【請求項22】

第4の電源ラインをさらに含み、

前記第2の反転回路は、前記第2の電源ラインと該第4の電源ラインとの間に前記少なくとも1つの機械的リレースイッチと直列に連結された追加の機械的リレースイッチをさらに含み、前記第3の電源ラインおよび該第4の電源ラインは、異なる電源電圧を供給するように動作可能である、請求項20に記載のメモリ要素。

【請求項23】

プログラマブル集積回路であって、該プログラマブル集積回路は、

少なくとも1つのnチャンネルトランジスタと少なくとも1つの機械的リレースイッチとを含む双安定メモリ要素を含み、

該双安定メモリ要素は、静的制御信号が提供される出力を有する、プログラマブル集積回路。

【請求項24】

前記静的制御信号を受け取るように動作可能なゲートを有するパストランジスタをさらに含み、該パストランジスタは、前記プログラマブル集積回路上のプログラマブル論理回路網の一部を形成する、請求項23に記載のプログラマブル集積回路。

【請求項25】

前記双安定メモリ要素は、

前記少なくとも1つのnチャンネルトランジスタと直列に連結されているpチャンネルトランジスタと、

前記少なくとも1つの機械的リレースイッチと直列に連結されている追加の機械的リレースイッチと

をさらに含む、請求項23に記載のプログラマブル集積回路。

【請求項26】

基板と、

誘電層と、

該基板と該誘電層との間に配置された少なくとも1つの金属ルーティング層と

をさらに含み、

前記nチャンネルトランジスタは、基板において形成され、前記機械的リレースイッチは、誘電層において形成されている、請求項23に記載のプログラマブル集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−110409(P2013−110409A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2012−246307(P2012−246307)

【出願日】平成24年11月8日(2012.11.8)

【出願人】(597154922)アルテラ コーポレイション (163)

【氏名又は名称原語表記】Altera Corporation

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成24年11月8日(2012.11.8)

【出願人】(597154922)アルテラ コーポレイション (163)

【氏名又は名称原語表記】Altera Corporation

【Fターム(参考)】

[ Back to top ]