レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はマイコンのテスト設計とレイアウト設計、特にゼロディフェクトが要求される車載用半導体の設計に関する。

【背景技術】

【0002】

高度な情報化社会の発展に伴い、半導体基板上に形成した複数の半導体素子を集積して機能的回路を構成した、演算用集積回路、記憶素子、および、それらを混載させた所謂システムオンチップ(System on Chip:SoC)といった半導体製品には、更なる高性能化の要求とともに、品質向上の要求がなされている。

【0003】

半導体製品の製造段階における個々の工程は、必然的に、一定の割合で不良発生の可能性を含むものである。数多くの素子、および、素子を結線する多層の配線で発生する短絡、開放などの不良は、電気的なテストプログラムで不良とする。

【0004】

しかし、電気的なテストで全ての不良を検出することは不可能である。そして、電気的なテストで未検出の不良が残留し、市場での不良のポテンシャルとなる。特に、車載用の半導体製品では、ゼロディフェクトの要求が強く、実質上、サブppmの不良率が要求されている。

【0005】

特開2000−315223号公報(特許文献1)には、半導体製造時のシステム検証を階層化し、各階層におけるシステム検証のためのテストクラスタを設計用データベースに設けることにより、特に設計中における検証を行なう際における利用性の高い設計用データベースを提供する集積回路の設計方法が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−315223号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1の集積回路の設計方法では要求仕様段階から始まる評価を必要としている。回路設計終了後のパターンの配線段階のみでの不良率の改善には適さない。

【0008】

また、半導体製品のテスト検出率は通常、テストモデルごとに計算されており、各々のテストの検出率の向上を行っている。また、テストによる未検出を対策するために、テスト上の改善も行われている。しかし、半導体製品の大規模化、複雑化により同一モデルのテストであれば、検出率が100%に近づくほどテスト時間が急増する。従って、未検出箇所をゼロにすることは実質的に不可能である。

【0009】

本発明の目的は、効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供することにある。

【0010】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次の通りである。

【0012】

本発明の代表的な実施の形態に関わるレイアウト修正・ライブラリセル置換モジュールは、半導体装置の更新前のレイアウト設計データと、未検出領域の情報と、未検出領域の致命率・不良率の情報を入力することで、実製品製造時の障害の検出率・致命率・不良率を改善し、レイアウト設計データの修正を行い、更新後のレイアウト設計データを出力する。

【0013】

このレイアウト修正・ライブラリセル置換モジュールは、電源電位のダミー配線またはグランド電位のダミー配線を追加することで、更新前のレイアウト設計データよりも更新後のレイアウト設計データの障害検出率を向上することを特徴とする。

【0014】

このレイアウト修正・ライブラリセル置換モジュールは、併走する信号線の間隔を調整することで、半導体装置の欠陥の致命率・不良率を低下させることを特徴とする。また、このレイアウト修正・ライブラリセル置換モジュールは、併走する信号線は双方とも同じ信号を流すことを特徴とする。

【0015】

このレイアウト修正・ライブラリセル置換モジュールは、併走する信号線は異なる信号を流すことを特徴とする。

【0016】

本発明に関わる半導体装置設計用EDAツールは、上記のレイアウト修正・ライブラリセル置換モジュールを含み、未検出領域の情報を出力するテスト未検出領域抽出モジュールと、未検出領域の致命率・不良率の情報を出力する致命率・不良率検出モジュールと、を有することを特徴とする。

【0017】

この半導体装置設計用EDAツールにおいて、レイアウト修正・ライブラリセル置換モジュールの出力する更新後のレイアウト設計データをテスト未検出領域抽出モジュールに帰還することを特徴とする。

【0018】

この半導体装置設計用EDAツールにおいて、未検出領域の情報が致命率・不良率検出モジュールにも入力されることを特徴としても良い。

【発明の効果】

【0019】

本発明に関わるレイアウト修正・ライブラリセル置換モジュール及びそれを含む半導体装置設計用EDAツールを用いる事で、不良率の高い領域の検出率・不良率・致命率を低下させることが可能となる。

【0020】

また、本発明に関わるレイアウト修正・ライブラリセル置換モジュール及びそれを含む半導体装置設計用EDAツールを用いる事で、lddqテストなどで不良が検出できない箇所について事前の措置を採り、不良率・致命率の低下を図ることが可能となる。

【図面の簡単な説明】

【0021】

【図1】テスト未検出領域抽出モジュールの入力と出力に関わる概念図である。

【図2】致命率・不良率検出モジュールの入力と出力に関わる概念図である。

【図3】テストパターン追加・削除モジュールの入力と出力に関わる概念図である。

【図4】レイアウト修正・ライブラリセル置換モジュールの入力と出力に関わる概念図である。

【図5】各モジュールの接続関係を表す図である。

【図6】各モジュールの別の接続関係を表す図である。

【図7】致命率・不良率検出モジュールで取り扱う検出率・不良率・致命率についての概念図である。

【図8】レイアウト修正・ライブラリセル置換モジュールにおけるレイアウトの修正についての概念図である。

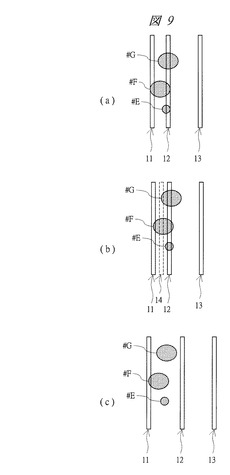

【図9】本発明における配線の修正例に付いての概念図である。

【図10】本発明における配線の修正例に付いての別の概念図である。

【発明を実施するための形態】

【0022】

以下の実施の形態においては、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明する。しかし、特に明示した場合を除き、それは互いに無関係なものではなく、一方は他方の一部又は全部の変形例、詳細、補足説明などの関係にある。また、以下の実施の形態において、要素の数など(個数、数値、量、範囲などを含む)に言及する場合、特に明示した場合及び原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものでなく、特定の数以上でも以下でも良い。

【0023】

さらに、以下の実施の形態において、その構成要素は、特に明示した場合及び原理的に明らかに必須であると考えられる場合を除き、必ずしも必須のものでないことは言うまでもない。

【0024】

以下、図を用いて本発明の実施の形態を説明する。

【0025】

(第1の実施の形態)

本発明に関わる評価システムは、1)テスト未検出領域抽出モジュール、2)致命率・不良率検出モジュール、3)テストパターン追加・削除モジュール、4)レイアウト修正・ライブラリセル置換モジュール、の4つのソフトウェアモジュールを含む。この評価システムは一般的なワークステーションまたはパーソナルコンピュータ上で動作することを想定している。

【0026】

図1は、テスト未検出領域抽出モジュールの入力と出力に関わる概念図である。図2は致命率・不良率検出モジュールの入力と出力に関わる概念図である。図3は、テストパターン追加・削除モジュールの入力と出力に関わる概念図である。図4は、レイアウト修正・ライブラリセル置換モジュールの入力と出力に関わる概念図である。

【0027】

本発明における1)テスト未検出領域抽出モジュールは、半導体装置の欠陥確認用のテストの未検出領域の抽出を行うソフトウェアモジュールである。半導体装置に対しては、スキャンテスト、IDDQテスト、LSBテストなどの各種評価が行われるが、テスト未検出領域抽出モジュールは、これらの結果から未検出領域を洗い出す。

【0028】

テスト未検出領域抽出モジュールの入力としては、A)テスト設計結果からの未検出リスト、B)レイアウト設計データ、の2つが存在する。一方出力としては、C)未検出配線、ライブラリセルの未検出ノードの情報、D)レイアウト上の未検出部表示用のデータとなる。

【0029】

A)テスト設計結果からの未検出リストは、スキャンテスト、IDDQテスト、LSBテストの設計結果から想定されるテスト結果から、半導体装置全体の中での未検出箇所を表すリストである。この入力データはテスト設計仕様から求められるものである。このテスト設計結果からの未検出リストは、RS−232C、USBなどの外部インターフェースやワークステーション等に備えられているリムーバブルディスクなどからテスト未検出領域抽出モジュールに入力される。また、3)テストパターン追加・削除モジュールからの出力として、このテスト設計結果からの未検出領域が列挙されたリスト(=未検出リスト)が出力され、反復して評価することも可能な構成とする。

【0030】

B)レイアウト設計データは、評価対象の半導体装置のレイアウト情報を記載したデータである。このデータは、A)テスト設計結果からの未検出リスト同様に、外部から入力されることを想定する。また、4)レイアウト修正・ライブラリセル置換モジュールの出力を利用することも想定している。

【0031】

C)未検出配線、ライブラリセルの未検出ノードの情報は、上記各種の評価では欠陥の確認を行えない箇所(未検出ノード)を特定するデータである。このデータは、2)致命率・不良率検出モジュールの入力信号となる。

【0032】

D)レイアウト上の未検出部表示用のデータは、上記C)未検出配線、ライブラリセルの未検出ノードの情報を可視化するための表示用データである。

【0033】

2)致命率・不良率検出モジュールは、上記C)未検出配線、ライブラリセルの未検出ノードの情報及びE)製造工程の欠陥密度サイズ分布情報を利用して、上記の未検出領域における致命的な欠陥の発生確率、及び、不良発生率を導出するソフトウェアモジュールである。

【0034】

2)致命率・不良率検出モジュールの入力には、先ほど述べたC)未検出配線、ライブラリセルの未検出ノードの情報の他に、E)製造工程の欠陥密度サイズ分布情報が存在する。

【0035】

E)製造工程の欠陥密度サイズ分布情報は、製造工程・製造ラインに依拠する欠陥の発生密度、及び半導体装置のウエハの大きさに関する情報である。この情報は、A)テスト設計結果からの未検出リスト同様に、RS−232C、USBなどの外部インターフェースやワークステーション等に備えられているリムーバブルディスクなどから入力される。

【0036】

2)致命率・不良率検出モジュールは、F)各未検出領域の致命率・不良率の情報を出力する。

【0037】

この、F)各未検出領域の致命率・不良率の情報は、未検出配線、ライブラリセルの未検出ノードの情報で列記された未検出領域(=未検出配線、ライブラリセルの未検出ノード)毎の致命率・不良率を列記した情報である。

【0038】

この致命率・不良率検出モジュールの処理結果は、3)テストパターン追加・削除モジュールに出力される。

【0039】

図7は、致命率・不良率検出モジュールで取り扱う検出率・不良率・致命率についての概念図である。

【0040】

本図において、正規の接続関係にあるトレンチは同じハッチングが掛けてある。

【0041】

配線(1)の組と配線(2)の組を検討する。

【0042】

配線(1)の組と配線(2)の組は、トレンチの長さが相違する。(1)の組の方が長く、(2)の組は短い。

【0043】

また、(1)の組は接続関係の異なる配線が近接・併走した位置に配置されている。

【0044】

この条件下で、(1)の組と(2)の組の検出率は後者の方が高くなる。単純に配線長が長いとショートの可能性が高くなること、併走する配線との間でのショート発生時に明確に識別可能であること(図7#B)がその理由である。

【0045】

一方、不良率・致命率という点では、(2)の組の方が明らかに低くなる。(2)の組の場合、図7#C#Dの双方が発生した場合でも、電気的な動作にほとんど影響は無い。これに対し、(1)の組の場合には、#Bの場合には回路の動作が期待できない。

【0046】

このように検出率と、致命率・不良率には差異がある。この両者を可能な限り良好なものとする(検出率を上げる一方で致命率は落とす)ように、2)致命率・不良率検出モジュールは動作する。

【0047】

2)致命率・不良率検出モジュールによって致命率・不良率が明確となると、4)レイアウト修正・ライブラリセル置換モジュールが検出しづらい箇所のパターンを不良が発生し易い回路配線パターンに変更することで、実製品完成後の評価での不良検出率を向上することが可能となる。これが本発明の主題である。

【0048】

3)テストパターン追加・削除モジュールは上記F)各未検出領域の致命率・不良率の情報や、未検出配線、ライブラリセルの未検出ノードの情報などを参酌して、テストパターンの追加および削除を行うソフトウェアモジュールである。

【0049】

3)テストパターン追加・削除モジュールの入力としては、1)テスト未検出領域抽出モジュールから出力されるC)未検出配線、ライブラリセルの未検出ノードの情報、2)致命率・不良率検出モジュールから出力されるF)各未検出領域の致命率・不良率の情報、のほかに、G)テスト設計データが必要となる。

【0050】

G)テスト設計データは、A)テスト設計結果からの未検出リストを求める際、および実際の評価で使用するスキャンテストなどの設計仕様を定義したデータである。このG)テスト設計データの内容を追加、削除することが3)テストパターン追加・削除モジュールの処理となる。

【0051】

3)テストパターン追加・削除モジュールの出力は、A)テスト設計結果からの未検出リスト、H)テスト設計結果を出力する。

【0052】

H)テスト設計結果は、G)テスト設計データに対して追加・削除された後のテスト設計データである。当然、記載のフォーマットなどはG)テスト設計データと同一の物となる。

【0053】

4)レイアウト修正・ライブラリセル置換モジュールは、上記の3つのモジュールの出力結果から、半導体装置に実装する際のレイアウトの修正及びセルのライブラリを置き換える処理を行うソフトウェアモジュールである。

【0054】

4)レイアウト修正・ライブラリセル置換モジュールには、B)レイアウト設計データ(更新前)、C)未検出配線、ライブラリセルの未検出ノードの情報、F)各未検出領域の致命率・不良率の情報、が入力される。これらの入力信号を元に回路モジュールの再配置、配線の取り回しの変更を行う。

【0055】

これらの処理が終わった後、4)レイアウト修正・ライブラリセル置換モジュールはB)レイアウト設計データ(更新後)を出力する。この更新後のB)レイアウト設計データを1)テスト未検出領域抽出モジュールに帰還することで、より不良発見率の高いテスト設計を行うことを可能とする。

【0056】

次に、これらの各モジュールの関係を俯瞰する。

【0057】

図5は、各モジュールの接続関係を表す図である。

【0058】

このように、3)テストパターン追加・削除モジュールから出力されるA)テスト設計結果からの未検出リスト、および4)レイアウト修正・ライブラリセル置換モジュールから出力されるB)レイアウト設計データを帰還し、反復して評価することで、不良率の最小化を図ることが可能となる。

【0059】

また図6は、各モジュールの別の接続関係を表す図である。

【0060】

この場合、1)テスト未検出領域抽出モジュール及び2)致命率・不良率検出モジュールを2セット用意する。そして1)テスト未検出領域抽出モジュールのスキャンテストなどのセッティングを変えて実行する。

【0061】

この2つの1)テスト未検出領域抽出モジュールそれぞれの出力であるC)未検出配線、ライブラリセルの未検出ノードの情報から、2)致命率・不良率検出モジュールの出力を導出する。

【0062】

そして、これら4つのモジュールの出力を3)テストパターン追加・削除モジュールに入力する際に、不良率が最小になる組み合わせを選択する。図上では2つのスイッチで表しているが、実装時にはこの選択はワークステーションなどのCPUが行うこととなろう。

【0063】

このようにすることで、図5と異なり反復作業を要することなく不良率の最小化を図ることが可能となる。

【0064】

(第2の実施の形態)

次に、本発明の第2の実施の形態に付いて図を用いて説明する。

【0065】

第1の実施の形態は、ソフトウェアモジュールの構成について説明した。これに対し、本実施の形態では、4)レイアウト修正・ライブラリセル置換モジュールの動作について検討する。

【0066】

図8は、4)レイアウト修正・ライブラリセル置換モジュールにおけるレイアウトの修正についての概念図である。この図ではMOSFETによるRAM(ランダムアクセスメモリ)を想定している。

【0067】

図8(a)はレイアウト修正前のものであり、図8(b)は修正後のものである。

【0068】

図8(a)で欠陥9が発生していた場合、ダミーポリシリコン(ダミー配線)1とアクティブ領域4との間でショートが発生する。修正前の場合、完成品の性能の低下は起こるものの、欠陥が検出されない不具合が生ずる。

【0069】

これに対し、4)レイアウト修正・ライブラリセル置換モジュールが図8(b)のようにダミーポリシリコン1と電源VSS7、ダミーポリシリコン3と電源Vcc6をコンタクトで接続したとする。この場合には、図8(a)のような欠陥が発生した場合にアクティブ領域4、5の動作は不調をきたし、結果RAMとしての動作は望めなくなる。しかし、検出は確実に行うことが可能となり、市場に不良品が出回ることを防止することが可能となる。

【0070】

このように、検出しづらい箇所の不良発生率を意図的に向上させることで、出荷製品の良品率を向上させることが可能となる。

【0071】

なお、上記ではダミーポリシリコン1と電源VSS7、ダミーポリシリコン3と電源Vcc6を接続するとした。電源の代わりに、ダミーポリシリコン1とグランド電位、ダミーポリシリコン3とグランド電位を接続しても良い。

【0072】

次に、実際の配線の修正方法について検討する。

【0073】

図9は、本発明における配線の修正例に付いての概念図である。

【0074】

図9(a)は、修正前の配線を表す。図9(b)は、検出性向上を狙った修正後の配線を示す。図9(c)は、致命性低下を狙った修正後の配線を示す。

【0075】

まず図9(a)で障害の性質を説明する。

【0076】

本図の回路は、3本の配線11、12、13が平行して配置されているものを想定する。配線11と配線12の間は狭く、配線12と配線13の間は広い。

【0077】

本図上の障害としては3つ存在する。#Eは配線12に発生したものの致命的なものでない障害を表す。#Fは配線11及び配線12の間にまたがった、致命的な障害を表す。#Gは配線12に致命的なものでない障害でかつ#Eよりも規模の大きいものを表す。

【0078】

次に図9(b)について説明する。

【0079】

この図では、配線11と配線12の間に、電源電位又はグランド電位の配線14を追加する。このように配線を追加することで、#Gの障害の検出の可能性を上げることができる。確かに#Eの障害は検出できないものの、このような検出専用の配線を追加することで、相当数の障害を事前に検出することが可能となる。

【0080】

一方、図9(c)は別のアプローチを採る。

【0081】

こちらは、配線11と配線12の配線間距離を拠り大きく取ることで、#Fの障害について図9(a)並みに致命性を低下させることが可能となる。

【0082】

また、図10は、本発明における配線の修正例に付いての別の概念図である。図10(a)は、修正前の配線を表す。図10(b)は、致命性の低減を狙った修正後の配線を示す。

【0083】

この図では正常な状態で、配線22と配線23は接続されている。一方配線21と配線22は別系統である。

【0084】

この場合、配線21と配線22の間にまたがる欠陥である#Iは検出性を有する。一方で、配線22と配線23の間で生じた障害である#H及び#Jについては検出性を有しない。

【0085】

そこで図10(b)のように、配線23を配線22から離す。これにより、不良率・致命率を低下させることが可能となる。

【0086】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更が可能であることは言うまでもない。

【産業上の利用可能性】

【0087】

本発明は、半導体回路の設計段階におけるテスト可能性の検討に用いられる。またこれに使用されるEDA(Electric Degsign Automation)ツールに適用することも可能である。

【符号の説明】

【0088】

1、2、3…ダミーポリシリコン、4、5…アクティブ領域、

6…第1層メタル(電源Vcc)、7…第1層メタル(電源Vss)、

8…コンタクト、9…欠陥、

11、12、13、14、21、22、23、24…配線。

【技術分野】

【0001】

本発明はマイコンのテスト設計とレイアウト設計、特にゼロディフェクトが要求される車載用半導体の設計に関する。

【背景技術】

【0002】

高度な情報化社会の発展に伴い、半導体基板上に形成した複数の半導体素子を集積して機能的回路を構成した、演算用集積回路、記憶素子、および、それらを混載させた所謂システムオンチップ(System on Chip:SoC)といった半導体製品には、更なる高性能化の要求とともに、品質向上の要求がなされている。

【0003】

半導体製品の製造段階における個々の工程は、必然的に、一定の割合で不良発生の可能性を含むものである。数多くの素子、および、素子を結線する多層の配線で発生する短絡、開放などの不良は、電気的なテストプログラムで不良とする。

【0004】

しかし、電気的なテストで全ての不良を検出することは不可能である。そして、電気的なテストで未検出の不良が残留し、市場での不良のポテンシャルとなる。特に、車載用の半導体製品では、ゼロディフェクトの要求が強く、実質上、サブppmの不良率が要求されている。

【0005】

特開2000−315223号公報(特許文献1)には、半導体製造時のシステム検証を階層化し、各階層におけるシステム検証のためのテストクラスタを設計用データベースに設けることにより、特に設計中における検証を行なう際における利用性の高い設計用データベースを提供する集積回路の設計方法が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−315223号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1の集積回路の設計方法では要求仕様段階から始まる評価を必要としている。回路設計終了後のパターンの配線段階のみでの不良率の改善には適さない。

【0008】

また、半導体製品のテスト検出率は通常、テストモデルごとに計算されており、各々のテストの検出率の向上を行っている。また、テストによる未検出を対策するために、テスト上の改善も行われている。しかし、半導体製品の大規模化、複雑化により同一モデルのテストであれば、検出率が100%に近づくほどテスト時間が急増する。従って、未検出箇所をゼロにすることは実質的に不可能である。

【0009】

本発明の目的は、効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供することにある。

【0010】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次の通りである。

【0012】

本発明の代表的な実施の形態に関わるレイアウト修正・ライブラリセル置換モジュールは、半導体装置の更新前のレイアウト設計データと、未検出領域の情報と、未検出領域の致命率・不良率の情報を入力することで、実製品製造時の障害の検出率・致命率・不良率を改善し、レイアウト設計データの修正を行い、更新後のレイアウト設計データを出力する。

【0013】

このレイアウト修正・ライブラリセル置換モジュールは、電源電位のダミー配線またはグランド電位のダミー配線を追加することで、更新前のレイアウト設計データよりも更新後のレイアウト設計データの障害検出率を向上することを特徴とする。

【0014】

このレイアウト修正・ライブラリセル置換モジュールは、併走する信号線の間隔を調整することで、半導体装置の欠陥の致命率・不良率を低下させることを特徴とする。また、このレイアウト修正・ライブラリセル置換モジュールは、併走する信号線は双方とも同じ信号を流すことを特徴とする。

【0015】

このレイアウト修正・ライブラリセル置換モジュールは、併走する信号線は異なる信号を流すことを特徴とする。

【0016】

本発明に関わる半導体装置設計用EDAツールは、上記のレイアウト修正・ライブラリセル置換モジュールを含み、未検出領域の情報を出力するテスト未検出領域抽出モジュールと、未検出領域の致命率・不良率の情報を出力する致命率・不良率検出モジュールと、を有することを特徴とする。

【0017】

この半導体装置設計用EDAツールにおいて、レイアウト修正・ライブラリセル置換モジュールの出力する更新後のレイアウト設計データをテスト未検出領域抽出モジュールに帰還することを特徴とする。

【0018】

この半導体装置設計用EDAツールにおいて、未検出領域の情報が致命率・不良率検出モジュールにも入力されることを特徴としても良い。

【発明の効果】

【0019】

本発明に関わるレイアウト修正・ライブラリセル置換モジュール及びそれを含む半導体装置設計用EDAツールを用いる事で、不良率の高い領域の検出率・不良率・致命率を低下させることが可能となる。

【0020】

また、本発明に関わるレイアウト修正・ライブラリセル置換モジュール及びそれを含む半導体装置設計用EDAツールを用いる事で、lddqテストなどで不良が検出できない箇所について事前の措置を採り、不良率・致命率の低下を図ることが可能となる。

【図面の簡単な説明】

【0021】

【図1】テスト未検出領域抽出モジュールの入力と出力に関わる概念図である。

【図2】致命率・不良率検出モジュールの入力と出力に関わる概念図である。

【図3】テストパターン追加・削除モジュールの入力と出力に関わる概念図である。

【図4】レイアウト修正・ライブラリセル置換モジュールの入力と出力に関わる概念図である。

【図5】各モジュールの接続関係を表す図である。

【図6】各モジュールの別の接続関係を表す図である。

【図7】致命率・不良率検出モジュールで取り扱う検出率・不良率・致命率についての概念図である。

【図8】レイアウト修正・ライブラリセル置換モジュールにおけるレイアウトの修正についての概念図である。

【図9】本発明における配線の修正例に付いての概念図である。

【図10】本発明における配線の修正例に付いての別の概念図である。

【発明を実施するための形態】

【0022】

以下の実施の形態においては、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明する。しかし、特に明示した場合を除き、それは互いに無関係なものではなく、一方は他方の一部又は全部の変形例、詳細、補足説明などの関係にある。また、以下の実施の形態において、要素の数など(個数、数値、量、範囲などを含む)に言及する場合、特に明示した場合及び原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものでなく、特定の数以上でも以下でも良い。

【0023】

さらに、以下の実施の形態において、その構成要素は、特に明示した場合及び原理的に明らかに必須であると考えられる場合を除き、必ずしも必須のものでないことは言うまでもない。

【0024】

以下、図を用いて本発明の実施の形態を説明する。

【0025】

(第1の実施の形態)

本発明に関わる評価システムは、1)テスト未検出領域抽出モジュール、2)致命率・不良率検出モジュール、3)テストパターン追加・削除モジュール、4)レイアウト修正・ライブラリセル置換モジュール、の4つのソフトウェアモジュールを含む。この評価システムは一般的なワークステーションまたはパーソナルコンピュータ上で動作することを想定している。

【0026】

図1は、テスト未検出領域抽出モジュールの入力と出力に関わる概念図である。図2は致命率・不良率検出モジュールの入力と出力に関わる概念図である。図3は、テストパターン追加・削除モジュールの入力と出力に関わる概念図である。図4は、レイアウト修正・ライブラリセル置換モジュールの入力と出力に関わる概念図である。

【0027】

本発明における1)テスト未検出領域抽出モジュールは、半導体装置の欠陥確認用のテストの未検出領域の抽出を行うソフトウェアモジュールである。半導体装置に対しては、スキャンテスト、IDDQテスト、LSBテストなどの各種評価が行われるが、テスト未検出領域抽出モジュールは、これらの結果から未検出領域を洗い出す。

【0028】

テスト未検出領域抽出モジュールの入力としては、A)テスト設計結果からの未検出リスト、B)レイアウト設計データ、の2つが存在する。一方出力としては、C)未検出配線、ライブラリセルの未検出ノードの情報、D)レイアウト上の未検出部表示用のデータとなる。

【0029】

A)テスト設計結果からの未検出リストは、スキャンテスト、IDDQテスト、LSBテストの設計結果から想定されるテスト結果から、半導体装置全体の中での未検出箇所を表すリストである。この入力データはテスト設計仕様から求められるものである。このテスト設計結果からの未検出リストは、RS−232C、USBなどの外部インターフェースやワークステーション等に備えられているリムーバブルディスクなどからテスト未検出領域抽出モジュールに入力される。また、3)テストパターン追加・削除モジュールからの出力として、このテスト設計結果からの未検出領域が列挙されたリスト(=未検出リスト)が出力され、反復して評価することも可能な構成とする。

【0030】

B)レイアウト設計データは、評価対象の半導体装置のレイアウト情報を記載したデータである。このデータは、A)テスト設計結果からの未検出リスト同様に、外部から入力されることを想定する。また、4)レイアウト修正・ライブラリセル置換モジュールの出力を利用することも想定している。

【0031】

C)未検出配線、ライブラリセルの未検出ノードの情報は、上記各種の評価では欠陥の確認を行えない箇所(未検出ノード)を特定するデータである。このデータは、2)致命率・不良率検出モジュールの入力信号となる。

【0032】

D)レイアウト上の未検出部表示用のデータは、上記C)未検出配線、ライブラリセルの未検出ノードの情報を可視化するための表示用データである。

【0033】

2)致命率・不良率検出モジュールは、上記C)未検出配線、ライブラリセルの未検出ノードの情報及びE)製造工程の欠陥密度サイズ分布情報を利用して、上記の未検出領域における致命的な欠陥の発生確率、及び、不良発生率を導出するソフトウェアモジュールである。

【0034】

2)致命率・不良率検出モジュールの入力には、先ほど述べたC)未検出配線、ライブラリセルの未検出ノードの情報の他に、E)製造工程の欠陥密度サイズ分布情報が存在する。

【0035】

E)製造工程の欠陥密度サイズ分布情報は、製造工程・製造ラインに依拠する欠陥の発生密度、及び半導体装置のウエハの大きさに関する情報である。この情報は、A)テスト設計結果からの未検出リスト同様に、RS−232C、USBなどの外部インターフェースやワークステーション等に備えられているリムーバブルディスクなどから入力される。

【0036】

2)致命率・不良率検出モジュールは、F)各未検出領域の致命率・不良率の情報を出力する。

【0037】

この、F)各未検出領域の致命率・不良率の情報は、未検出配線、ライブラリセルの未検出ノードの情報で列記された未検出領域(=未検出配線、ライブラリセルの未検出ノード)毎の致命率・不良率を列記した情報である。

【0038】

この致命率・不良率検出モジュールの処理結果は、3)テストパターン追加・削除モジュールに出力される。

【0039】

図7は、致命率・不良率検出モジュールで取り扱う検出率・不良率・致命率についての概念図である。

【0040】

本図において、正規の接続関係にあるトレンチは同じハッチングが掛けてある。

【0041】

配線(1)の組と配線(2)の組を検討する。

【0042】

配線(1)の組と配線(2)の組は、トレンチの長さが相違する。(1)の組の方が長く、(2)の組は短い。

【0043】

また、(1)の組は接続関係の異なる配線が近接・併走した位置に配置されている。

【0044】

この条件下で、(1)の組と(2)の組の検出率は後者の方が高くなる。単純に配線長が長いとショートの可能性が高くなること、併走する配線との間でのショート発生時に明確に識別可能であること(図7#B)がその理由である。

【0045】

一方、不良率・致命率という点では、(2)の組の方が明らかに低くなる。(2)の組の場合、図7#C#Dの双方が発生した場合でも、電気的な動作にほとんど影響は無い。これに対し、(1)の組の場合には、#Bの場合には回路の動作が期待できない。

【0046】

このように検出率と、致命率・不良率には差異がある。この両者を可能な限り良好なものとする(検出率を上げる一方で致命率は落とす)ように、2)致命率・不良率検出モジュールは動作する。

【0047】

2)致命率・不良率検出モジュールによって致命率・不良率が明確となると、4)レイアウト修正・ライブラリセル置換モジュールが検出しづらい箇所のパターンを不良が発生し易い回路配線パターンに変更することで、実製品完成後の評価での不良検出率を向上することが可能となる。これが本発明の主題である。

【0048】

3)テストパターン追加・削除モジュールは上記F)各未検出領域の致命率・不良率の情報や、未検出配線、ライブラリセルの未検出ノードの情報などを参酌して、テストパターンの追加および削除を行うソフトウェアモジュールである。

【0049】

3)テストパターン追加・削除モジュールの入力としては、1)テスト未検出領域抽出モジュールから出力されるC)未検出配線、ライブラリセルの未検出ノードの情報、2)致命率・不良率検出モジュールから出力されるF)各未検出領域の致命率・不良率の情報、のほかに、G)テスト設計データが必要となる。

【0050】

G)テスト設計データは、A)テスト設計結果からの未検出リストを求める際、および実際の評価で使用するスキャンテストなどの設計仕様を定義したデータである。このG)テスト設計データの内容を追加、削除することが3)テストパターン追加・削除モジュールの処理となる。

【0051】

3)テストパターン追加・削除モジュールの出力は、A)テスト設計結果からの未検出リスト、H)テスト設計結果を出力する。

【0052】

H)テスト設計結果は、G)テスト設計データに対して追加・削除された後のテスト設計データである。当然、記載のフォーマットなどはG)テスト設計データと同一の物となる。

【0053】

4)レイアウト修正・ライブラリセル置換モジュールは、上記の3つのモジュールの出力結果から、半導体装置に実装する際のレイアウトの修正及びセルのライブラリを置き換える処理を行うソフトウェアモジュールである。

【0054】

4)レイアウト修正・ライブラリセル置換モジュールには、B)レイアウト設計データ(更新前)、C)未検出配線、ライブラリセルの未検出ノードの情報、F)各未検出領域の致命率・不良率の情報、が入力される。これらの入力信号を元に回路モジュールの再配置、配線の取り回しの変更を行う。

【0055】

これらの処理が終わった後、4)レイアウト修正・ライブラリセル置換モジュールはB)レイアウト設計データ(更新後)を出力する。この更新後のB)レイアウト設計データを1)テスト未検出領域抽出モジュールに帰還することで、より不良発見率の高いテスト設計を行うことを可能とする。

【0056】

次に、これらの各モジュールの関係を俯瞰する。

【0057】

図5は、各モジュールの接続関係を表す図である。

【0058】

このように、3)テストパターン追加・削除モジュールから出力されるA)テスト設計結果からの未検出リスト、および4)レイアウト修正・ライブラリセル置換モジュールから出力されるB)レイアウト設計データを帰還し、反復して評価することで、不良率の最小化を図ることが可能となる。

【0059】

また図6は、各モジュールの別の接続関係を表す図である。

【0060】

この場合、1)テスト未検出領域抽出モジュール及び2)致命率・不良率検出モジュールを2セット用意する。そして1)テスト未検出領域抽出モジュールのスキャンテストなどのセッティングを変えて実行する。

【0061】

この2つの1)テスト未検出領域抽出モジュールそれぞれの出力であるC)未検出配線、ライブラリセルの未検出ノードの情報から、2)致命率・不良率検出モジュールの出力を導出する。

【0062】

そして、これら4つのモジュールの出力を3)テストパターン追加・削除モジュールに入力する際に、不良率が最小になる組み合わせを選択する。図上では2つのスイッチで表しているが、実装時にはこの選択はワークステーションなどのCPUが行うこととなろう。

【0063】

このようにすることで、図5と異なり反復作業を要することなく不良率の最小化を図ることが可能となる。

【0064】

(第2の実施の形態)

次に、本発明の第2の実施の形態に付いて図を用いて説明する。

【0065】

第1の実施の形態は、ソフトウェアモジュールの構成について説明した。これに対し、本実施の形態では、4)レイアウト修正・ライブラリセル置換モジュールの動作について検討する。

【0066】

図8は、4)レイアウト修正・ライブラリセル置換モジュールにおけるレイアウトの修正についての概念図である。この図ではMOSFETによるRAM(ランダムアクセスメモリ)を想定している。

【0067】

図8(a)はレイアウト修正前のものであり、図8(b)は修正後のものである。

【0068】

図8(a)で欠陥9が発生していた場合、ダミーポリシリコン(ダミー配線)1とアクティブ領域4との間でショートが発生する。修正前の場合、完成品の性能の低下は起こるものの、欠陥が検出されない不具合が生ずる。

【0069】

これに対し、4)レイアウト修正・ライブラリセル置換モジュールが図8(b)のようにダミーポリシリコン1と電源VSS7、ダミーポリシリコン3と電源Vcc6をコンタクトで接続したとする。この場合には、図8(a)のような欠陥が発生した場合にアクティブ領域4、5の動作は不調をきたし、結果RAMとしての動作は望めなくなる。しかし、検出は確実に行うことが可能となり、市場に不良品が出回ることを防止することが可能となる。

【0070】

このように、検出しづらい箇所の不良発生率を意図的に向上させることで、出荷製品の良品率を向上させることが可能となる。

【0071】

なお、上記ではダミーポリシリコン1と電源VSS7、ダミーポリシリコン3と電源Vcc6を接続するとした。電源の代わりに、ダミーポリシリコン1とグランド電位、ダミーポリシリコン3とグランド電位を接続しても良い。

【0072】

次に、実際の配線の修正方法について検討する。

【0073】

図9は、本発明における配線の修正例に付いての概念図である。

【0074】

図9(a)は、修正前の配線を表す。図9(b)は、検出性向上を狙った修正後の配線を示す。図9(c)は、致命性低下を狙った修正後の配線を示す。

【0075】

まず図9(a)で障害の性質を説明する。

【0076】

本図の回路は、3本の配線11、12、13が平行して配置されているものを想定する。配線11と配線12の間は狭く、配線12と配線13の間は広い。

【0077】

本図上の障害としては3つ存在する。#Eは配線12に発生したものの致命的なものでない障害を表す。#Fは配線11及び配線12の間にまたがった、致命的な障害を表す。#Gは配線12に致命的なものでない障害でかつ#Eよりも規模の大きいものを表す。

【0078】

次に図9(b)について説明する。

【0079】

この図では、配線11と配線12の間に、電源電位又はグランド電位の配線14を追加する。このように配線を追加することで、#Gの障害の検出の可能性を上げることができる。確かに#Eの障害は検出できないものの、このような検出専用の配線を追加することで、相当数の障害を事前に検出することが可能となる。

【0080】

一方、図9(c)は別のアプローチを採る。

【0081】

こちらは、配線11と配線12の配線間距離を拠り大きく取ることで、#Fの障害について図9(a)並みに致命性を低下させることが可能となる。

【0082】

また、図10は、本発明における配線の修正例に付いての別の概念図である。図10(a)は、修正前の配線を表す。図10(b)は、致命性の低減を狙った修正後の配線を示す。

【0083】

この図では正常な状態で、配線22と配線23は接続されている。一方配線21と配線22は別系統である。

【0084】

この場合、配線21と配線22の間にまたがる欠陥である#Iは検出性を有する。一方で、配線22と配線23の間で生じた障害である#H及び#Jについては検出性を有しない。

【0085】

そこで図10(b)のように、配線23を配線22から離す。これにより、不良率・致命率を低下させることが可能となる。

【0086】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更が可能であることは言うまでもない。

【産業上の利用可能性】

【0087】

本発明は、半導体回路の設計段階におけるテスト可能性の検討に用いられる。またこれに使用されるEDA(Electric Degsign Automation)ツールに適用することも可能である。

【符号の説明】

【0088】

1、2、3…ダミーポリシリコン、4、5…アクティブ領域、

6…第1層メタル(電源Vcc)、7…第1層メタル(電源Vss)、

8…コンタクト、9…欠陥、

11、12、13、14、21、22、23、24…配線。

【特許請求の範囲】

【請求項1】

半導体装置の更新前のレイアウト設計データと、未検出領域の情報と、前記未検出領域の致命率・不良率の情報を入力することで、実製品製造時の障害の検出率・致命率・不良率を改善し、レイアウト設計データの修正を行い、更新後のレイアウト設計データを出力するレイアウト修正・ライブラリセル置換モジュール。

【請求項2】

請求項1に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

電源電位のダミー配線またはグランド電位のダミー配線を追加することで、前記更新前のレイアウト設計データよりも前記更新後のレイアウト設計データの障害検出率を向上することを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項3】

請求項1に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

併走する信号線の間隔を調整することで、前記半導体装置の欠陥の致命率・不良率を低下させることを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項4】

請求項3に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

前記併走する信号線は双方とも同じ信号を流すことを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項5】

請求項3に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

前記併走する信号線は異なる信号を流すことを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項6】

請求項1に記載のレイアウト修正・ライブラリセル置換モジュールを含み、

前記未検出領域の情報を出力するテスト未検出領域抽出モジュールと、

前記未検出領域の致命率・不良率の情報を出力する致命率・不良率検出モジュールと、を有することを特徴とする半導体装置設計用EDAツール。

【請求項7】

請求項6に記載の半導体装置設計用EDAツールにおいて、前記レイアウト修正・ライブラリセル置換モジュールの出力する更新後のレイアウト設計データを前記テスト未検出領域抽出モジュールに帰還することを特徴とする半導体装置設計用EDAツール。

【請求項8】

請求項6または7に記載の半導体装置設計用EDAツールにおいて、前記未検出領域の情報が前記致命率・不良率検出モジュールにも入力されることを特徴とする半導体装置設計用EDAツール。

【請求項1】

半導体装置の更新前のレイアウト設計データと、未検出領域の情報と、前記未検出領域の致命率・不良率の情報を入力することで、実製品製造時の障害の検出率・致命率・不良率を改善し、レイアウト設計データの修正を行い、更新後のレイアウト設計データを出力するレイアウト修正・ライブラリセル置換モジュール。

【請求項2】

請求項1に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

電源電位のダミー配線またはグランド電位のダミー配線を追加することで、前記更新前のレイアウト設計データよりも前記更新後のレイアウト設計データの障害検出率を向上することを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項3】

請求項1に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

併走する信号線の間隔を調整することで、前記半導体装置の欠陥の致命率・不良率を低下させることを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項4】

請求項3に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

前記併走する信号線は双方とも同じ信号を流すことを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項5】

請求項3に記載のレイアウト修正・ライブラリセル置換モジュールにおいて、

前記併走する信号線は異なる信号を流すことを特徴とするレイアウト修正・ライブラリセル置換モジュール。

【請求項6】

請求項1に記載のレイアウト修正・ライブラリセル置換モジュールを含み、

前記未検出領域の情報を出力するテスト未検出領域抽出モジュールと、

前記未検出領域の致命率・不良率の情報を出力する致命率・不良率検出モジュールと、を有することを特徴とする半導体装置設計用EDAツール。

【請求項7】

請求項6に記載の半導体装置設計用EDAツールにおいて、前記レイアウト修正・ライブラリセル置換モジュールの出力する更新後のレイアウト設計データを前記テスト未検出領域抽出モジュールに帰還することを特徴とする半導体装置設計用EDAツール。

【請求項8】

請求項6または7に記載の半導体装置設計用EDAツールにおいて、前記未検出領域の情報が前記致命率・不良率検出モジュールにも入力されることを特徴とする半導体装置設計用EDAツール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−164022(P2012−164022A)

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願番号】特願2011−22005(P2011−22005)

【出願日】平成23年2月3日(2011.2.3)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願日】平成23年2月3日(2011.2.3)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]