レベルシフタ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路の最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路を提供する。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、レベルシフタ回路、走査回路、表示装置、及び、電子機器に関する。

【背景技術】

【0002】

平面型(フラットパネル型)の表示装置の一つとして、デバイスに流れる電流値に応じて発光輝度が変化する、所謂、電流駆動型の電気光学素子を画素の発光部(発光素子)として用いた表示装置がある。電流駆動型の電気光学素子としては、例えば、有機材料のエレクトロルミネッセンス(Electro Luminescence:EL)を利用し、有機薄膜に電界をかけると発光する現象を用いた有機EL素子が知られている。

【0003】

画素の発光部として有機EL素子を用いた有機EL表示装置は次のような特長を持っている。すなわち、有機EL素子は、10V以下の印加電圧で駆動できるために低消費電力である。有機EL素子は自発光素子であるために、液晶表示装置に比べて、画像の視認性が高く、しかも、バックライト等の照明部材を必要としないために軽量化及び薄型化が容易である。更に、有機EL素子は、応答速度が数μsec程度と非常に高速であるために動画表示時の残像が発生しない。

【0004】

この有機EL表示装置に代表される平面型の表示装置は、電気光学素子の他に、書込みトランジスタ、保持容量、及び、駆動トランジスタを少なくとも有する画素が行列状に2次元配置された構成となっている(例えば、特許文献1参照)。

【0005】

この種の表示装置において、書込みトランジスタは、画素行毎に配線される制御線(走査線)を通して走査回路(走査部)から与えられる制御パルス(走査パルス)によって駆動されることで、信号線を通して供給される映像信号の信号電圧を画素内に書き込む。保持容量は、書込みトランジスタが書き込んだ信号電圧を保持する。駆動トランジスタは、保持容量が保持した信号電圧に応じて電気光学素子を駆動する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−310311号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、一般的に、表示パネルを大型化した場合、走査回路から書込みトランジスタに制御パルスを伝送する制御線の負荷が大きくなるため、その負荷の影響で制御パルスの波形が大きく鈍ってしまう。負荷の影響を抑えるには、走査回路の最終段のインバータ回路を構成するトランジスタのサイズを大きくし、当該インバータ回路の抵抗を小さくすることが考えられる。しかし、トランジスタのサイズを大きくすると、走査回路、ひいては、当該走査回路を含む周辺回路の回路規模が大きくなるため、表示パネルの狭額縁化の妨げとなる。

【0008】

このため、走査回路の最終段のインバータ回路を構成するトランジスタのサイズをそのままにして、即ち、トランジスタのサイズを大きくすることなく、最終段のインバータ回路の抵抗(インバータ回路を構成するトランジスタのオン抵抗)を小さくすることが必要となる。一般に、トランジスタの抵抗値は、トランジスタのサイズとゲート−ソース間電圧に依存する。従って、最終段のインバータ回路を構成するトランジスタのサイズを大きくしないのであれば、当該トランジスタのゲート−ソース間電圧を上げる、即ち、最終段のインバータ回路の入力電圧の振幅を増大させる必要がある。

【0009】

最終段のインバータ回路の入力電圧の振幅を増大させるには、最終段のインバータ回路の前段の回路に与える電源電圧を入力電圧よりも高くする必要がある。しかし、単純に、前段の回路に与える電源電圧を入力電圧よりも高くすると、前段の回路を構成するトランジスタにかかるソース−ドレイン間電圧が高くなってしまい、所定のソース−ドレイン耐圧を超えてしまう。

【0010】

一般に、トランジスタのソース−ドレイン耐圧はゲート−ソース耐圧よりも小さい(低い)。従って、前段の回路を構成するトランジスタにかかるソース−ドレイン耐圧が、当該トランジスタの所定のソース−ドレイン耐圧を超えると、当該トランジスタの信頼性が著しく低下してしまう。

【0011】

そこで、本開示は、回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路における最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路、当該レベルシフタ回路を用いる走査回路、当該走査回路を搭載した表示装置、及び、当該表示装置を有する電子機器を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記の目的を達成するために、本開示のレベルシフタ回路は、

第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

ことを特徴としている。

【0013】

本開示のレベルシフタ回路は、最終段にインバータ回路を有する走査回路において、最終段のインバータ回路の前段の回路として用いることができる。また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段の回路として用いる走査回路は、画素が行列状に配置されて成る表示装置、あるいは、固体撮像装置において、各画素を走査する走査回路として搭載することができる。また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段の回路として用いる走査回路を搭載する表示装置は、表示部を備える各種の電子機器において、その表示部として用いることができる。

【0014】

上記構成のレベルシフタ回路において、第1トランジスタ回路と第2トランジスタ回路とが第1固定電源と第2固定電源との間に直列に接続されていることで、一方の電源側のトランジスタ回路である例えば第1トランジスタ回路が動作状態になると、出力端の電圧が第1固定電源の電圧になる。同様に、第3トランジスタ回路と第4トランジスタ回路とが第1固定電源と第2固定電源との間に直列に接続されていることで、一方の電源側のトランジスタ回路である例えば第3トランジスタ回路が動作状態になると、出力端の電圧が第1固定電源の電圧になる。これにより、第2,第4トランジスタ回路には、第1固定電源の電圧と第2固定電源の電圧とが与えられることになる。

【0015】

このとき、他方の電源側の2つのトランジスタ回路である例えば第2,第4トランジスタ回路のダブルゲートトランジスタの共通接続ノードには、スイッチ素子によって第3固定電源の電圧が与えられる。これにより、ダブルゲート構造を構成する2つのトランジスタの各ソース−ドレイン間には、第1固定電源−第2固定電源間の電圧ではなく、第1固定電源−第3固定電源間の電圧と、第3固定電源−第2固定電源間の電圧とが与えられることになる。

【0016】

ここで、第1固定電源−第3固定電源間の電圧、及び、第3固定電源−第2固定電源間の電圧が、第1〜第4トランジスタ回路を構成する各トランジスタのソース−ドレイン耐圧の範囲内の電圧とする。これにより、トランジスタに与えられるソース−ドレイン間電圧がその耐圧の範囲内となり、尚且つ、入力電圧の振幅よりも大きい振幅の出力電圧を導出することができる。

【発明の効果】

【0017】

本開示によれば、トランジスタのソース−ドレイン間電圧をその耐圧の範囲内とし、入力電圧の振幅よりも大きい振幅の出力電圧を導出することができるため、トランジスタのソース−ドレイン耐圧を維持したまま、走査回路における最終段のインバータ回路の入力電圧の振幅を増大させることができる。

【図面の簡単な説明】

【0018】

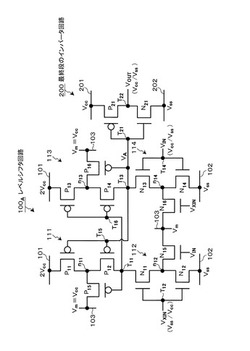

【図1】本開示の第1実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【図2】一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccの場合の、第1実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図3】一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の、第1実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図4】第1実施形態に係るレベルシフタ回路における2つの入力電圧VIN,VXIN、レベルシフタ回路の出力電圧VA、及び、最終段のインバータ回路の出力電圧VOUTの各波形を示す波形図である。

【図5】本開示の第2実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【図6】一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の、第2実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図7】一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccの場合の、第2実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図8】第2実施形態に係るレベルシフタ回路における2つの入力電圧VIN,VXIN、レベルシフタ回路の出力電圧VA、及び、最終段のインバータ回路の出力電圧VOUTの各波形を示す波形図である。

【図9】本開示の第3実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【図10】第3実施形態に係るレベルシフタ回路における入力電圧VIN、1段目のレベルシフタ回路の出力電圧VA、2段目のレベルシフタ回路の出力電圧VB、及び、最終段のインバータ回路の出力電圧VOUTの各波形を示す波形図である。

【図11】本開示の有機EL表示装置の構成の概略を示すシステム構成図である。

【図12】画素(画素回路)の具体的な回路構成の一例を示す回路図である。

【図13】書込み走査回路の構成の一例を示すブロック図である。

【発明を実施するための形態】

【0019】

以下、本開示の技術を実施するための形態(以下、「実施形態」と記述する)について図面を用いて詳細に説明する。本開示は実施形態に限定されるものではない。以下の説明において、同一要素又は同一機能を有する要素には同一符号を用いることとし、重複する説明は省略する。尚、説明は以下の順序で行う。

1.本開示のレベルシフタ回路、全般に関する説明

2.第1実施形態に係るレベルシフタ回路

2−1.回路構成

2−2.回路動作

2−3.作用、効果

3.第2実施形態に係るレベルシフタ回路

3−1.回路構成

3−2.回路動作

3−3.作用、効果

4.第3実施形態に係るレベルシフタ回路

5.表示装置(有機EL表示装置)

5−1.システム構成

5−2.画素回路

5−3.走査回路

5−4.その他

6.電子機器

7.本開示の構成

【0020】

<1.本開示のレベルシフタ回路、全般に関する説明>

本開示のレベルシフタ回路は、第1導電型のトランジスタから成る第1,第3トランジスタ回路と、第2導電型のトランジスタから成る第2,第4トランジスタ回路とを有する構成となっている。第1トランジスタ回路と第2トランジスタ回路とは、第1固定電源と第2固定電源との間に直列に接続されている。第3トランジスタ回路と第4トランジスタ回路とは、第1固定電源と第2固定電源との間に直列に接続されている。

【0021】

第1トランジスタ回路と第2トランジスタ回路との共通接続ノードは、これらトランジスタ回路の出力端となる。また、第3トランジスタ回路と第4トランジスタ回路との共通接続ノードは、これらトランジスタ回路の出力端となる。そして、第2トランジスタ回路の入力端には第1入力電圧が与えられ、第4トランジスタ回路の入力端には第2入力電圧が与えられる。第1入力電圧と第2入力電圧とを、逆相の電圧とすることができる。第1トランジスタ回路の入力端が第3,第4トランジスタ回路の共通接続ノードに接続され、第3トランジスタ回路の入力端が第1,第2トランジスタ回路の共通接続ノードに接続されている。

【0022】

そして、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路は、ダブルゲート構造のトランジスタ、即ち、ダブルゲートトランジスタから成る。ここで、第1固定電源側の2つのトランジスタ回路とは第1,第3トランジスタ回路のことであり、第2固定電源側の2つのトランジスタ回路とは第2,第4トランジスタ回路のことである。

【0023】

本開示のレベルシフタ回路は、大きくは、2つの回路形態を採ることができる。第1の回路形態は、第1固定電源が正側電源、第2固定電源が負側電源、第1導電型のトランジスタがPチャネル型のトランジスタ、第2導電型のトランジスタがNチャネル型のトランジスタの形態である。第2の回路形態は、第1固定電源が負側電源、第2固定電源が正側電源、第1導電型のトランジスタがNチャネル型のトランジスタ、第2導電型のトランジスタがPチャネル型のトランジスタの形態である。

【0024】

第1の回路形態を採るときは、第1固定電源の電圧を第1,第2入力電圧の高電圧側の電圧よりも高く設定し、第2固定電源の電圧を第1,第2入力電圧の低電圧側の電圧以下に設定するのが好ましい。また、第2の回路形態を採るときは、第1固定電源の電圧を第1,第2入力電圧の低電圧側の電圧よりも低く設定し、第2固定電源の電圧を第1,第2入力電圧の高電圧側の電圧以上に設定するのが好ましい。

【0025】

本開示のレベルシフタ回路は、第3,第4トランジスタ回路の共通接続ノードに接続される最終段のインバータ回路との組合せで用いることができる。この場合、第1の回路形態では、第1固定電源の電圧を最終段のインバータ回路の正側電源の電圧よりも高く設定し、第2固定電源の電圧を最終段のインバータ回路の負側電源の電圧以下に設定するのが好ましい。また、第2の回路形態では、第1固定電源の電圧を最終段のインバータ回路の負側電源の電圧よりも低く設定し、第2固定電源の電圧を最終段のインバータ回路の正側電源の電圧以上に設定するのが好ましい。

【0026】

そして、本開示のレベルシフタ回路は、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに対して、第3固定電源の電圧を与えるスイッチ素子を有することを特徴としている。

【0027】

第3固定電源の電圧は、第1,第2固定電源の各電圧の間の値、好ましくは、第1,第2固定電源の各電圧の平均値とするのが望ましい。この第3固定電源の電圧を選択的に与えるスイッチ素子は、他方の電源側の2つのトランジスタ回路を構成するトランジスタと同導電型のトランジスタとすることができる。この同導電型のトランジスタは、第1入力電圧または第2入力電圧をゲート入力とする。

【0028】

ここで、第1固定電源−第3固定電源間の電圧、及び、第3固定電源−第2固定電源間の電圧が、第1〜第4トランジスタ回路を構成する各トランジスタのソース−ドレイン耐圧の範囲内の電圧とするのが好ましい。このような電圧設定を行うことにより、第1〜第4トランジスタ回路を構成する各トランジスタに与えられるソース−ドレイン間電圧がその耐圧の範囲内となり、尚且つ、第1,第2入力電圧の振幅よりも大きい振幅の出力電圧を導出することができる。

【0029】

本開示のレベルシフタ回路は、その用途が限定されるものではなく、一般的なレベルシフタ回路として種々の用途に用いることができる。一例として、本開示のレベルシフタ回路は、最終段にインバータ回路を有し、行列状に配置された画素を走査する走査信号を出力する走査回路において、最終段のインバータ回路の前段の回路として用いることができる。

【0030】

また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段回路として用いる走査回路は、電気光学素子を含む画素が行列状に配置されて成る表示装置、あるいは、光電変換素子を含む画素が行列状に配置されて成る固体撮像装置において、各画素を走査する走査回路として用いることができる。この場合、走査回路は、表示パネル上に搭載する形態をとることもできるし、あるいは、ドライバICとして表示パネル外に配する形態をとることもできる。また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段回路として用いる走査回路を搭載する表示装置は、表示部を備える各種の電子機器において、その表示部として用いることができる。

【0031】

以下に、本開示の具体的な実施形態に係るレベルシフタ回路について説明する。

【0032】

<2.第1実施形態>

[2−1.回路構成]

図1は、本開示の第1実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。第1実施形態に係るレベルシフタ回路100Aは、前に述べた第1の回路形態を採っている。すなわち、第1固定電源101を正側電源、第2固定電源102を負側電源とし、第1導電型のトランジスタとしてPチャネル型のトランジスタ(以下、「Pチャネルトランジスタ」と記述する)を用い、第2導電型のトランジスタとしてNチャネル型のトランジスタ(以下、「Nチャネルトランジスタ」と記述する)を用いる。

【0033】

図1において、第1実施形態に係るレベルシフタ回路100Aは、第1トランジスタ回路111、第2トランジスタ回路112、第3トランジスタ回路113、及び、第4トランジスタ回路114の4つのトランジスタ回路から構成されている。第1トランジスタ回路111と第2トランジスタ回路112とは、正側電源である第1固定電源101と負側電源である第2固定電源102との間に直列に接続されている。同様に、第3トランジスタ回路113と第4トランジスタ回路114とは、第1固定電源101と第2固定電源102との間に直列に接続されている。

【0034】

第1固定電源101側の2つのトランジスタ回路、即ち、第1トランジスタ回路111及び第3トランジスタ回路113は、Pチャネルトランジスタから成る。第2固定電源102側の2つのトランジスタ回路、即ち、第2トランジスタ回路112及び第4トランジスタ回路114は、Nチャネルトランジスタから成る。そして、第1固定電源101側の2つのトランジスタ回路111,113、及び、第2固定電源102側の2つのトランジスタ回路112,114が共に、ダブルゲート構造のトランジスタ、即ち、ダブルゲートトランジスタから成る。

【0035】

但し、これは一例に過ぎず、第1固定電源101側の2つのトランジスタ回路111,113及び第2固定電源102側の2つのトランジスタ回路112,114の一方側の2つのトランジスタ回路のみが、ダブルゲートトランジスタから成る構成を採ることも可能である。このように、一方側の2つのトランジスタ回路のみがダブルゲートトランジスタから成るときは、他方側の2つのトランジスタ回路はシングルゲートトランジスタから成る。

【0036】

第1トランジスタ回路111は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP11,P12から成る。PチャネルトランジスタP11のソース電極は、第1固定電源101に接続されている。PチャネルトランジスタP11のドレイン電極とPチャネルトランジスタP12のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P11,P12)の共通接続ノードn11となっている。PチャネルトランジスタP12のドレイン電極は、第1トランジスタ回路111の出力端T11となっている。

【0037】

第2トランジスタ回路112は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN11,N12から成る。NチャネルトランジスタN11のドレイン電極は、第2トランジスタ回路112の出力端T11となっている。第2トランジスタ回路112の出力端T11は、第1トランジスタ回路111の出力端T11でもある。すなわち、PチャネルトランジスタP12のドレイン電極とNチャネルトランジスタN11のドレイン電極とが共通に接続されて第1,第2トランジスタ回路111,112の出力端T11となっている。

【0038】

2つのNチャネルトランジスタN11,N12の共通に接続されたゲート電極は、第2トランジスタ回路112の入力端T12となっている。NチャネルトランジスタN11のソース電極とNチャネルトランジスタN12のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N11,N12)の共通接続ノードn12となっている。NチャネルトランジスタN12のソース電極は、第2固定電源102に接続されている。

【0039】

第3トランジスタ回路113は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP13,P14から成る。PチャネルトランジスタP13のソース電極は、第1固定電源101に接続されている。PチャネルトランジスタP13のドレイン電極とPチャネルトランジスタP14のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P13,P14)の共通接続ノードn13となっている。PチャネルトランジスタP14のドレイン電極は、第3トランジスタ回路113の出力端T13となっている。

【0040】

第4トランジスタ回路114は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN13,N14から成る。NチャネルトランジスタN13のドレイン電極は、第4トランジスタ回路114の出力端T13となっている。第4トランジスタ回路114の出力端T13は、第3トランジスタ回路113の出力端T13でもある。すなわち、PチャネルトランジスタP14のドレイン電極とNチャネルトランジスタN13のドレイン電極とが共通に接続されて第3,第4トランジスタ回路113,114の出力端T13となっている。また、第3,第4トランジスタ回路113,114の出力端T13は、本レベルシフタ回路100Aの出力端でもある。

【0041】

2つのNチャネルトランジスタN13,N14の共通に接続されたゲート電極は、第4トランジスタ回路114の入力端T14となっている。NチャネルトランジスタN13のソース電極とNチャネルトランジスタN14のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N13,N14)の共通接続ノードn14となっている。NチャネルトランジスタN14のソース電極は、第2固定電源102に接続されている。

【0042】

上記構成のレベルシフタ回路100Aにおいて、第2固定電源102側の2つのトランジスタ回路、即ち、第2,第4トランジスタ112,114の各入力端T12,T14には、第1,第2入力電圧VXIN,VINが与えられる。第1,第2入力電圧VXIN,VINは、高電圧側の電圧(高レベル)がVcc、低電圧側の電圧(低レベル)がVssの、互いに逆相の電圧である。

【0043】

この第1,第2入力電圧VXIN,VINに対して、第1固定電源101の電圧は、高電圧側の電圧Vccよりも高い電圧、例えば2Vccに設定され、第2固定電源102の電圧は、低電圧側の電圧Vss以下の電圧、例えば、等しい電圧に設定されている。尚、ここでは、レベルシフタ回路100A、即ち、第1〜第4トランジスタ回路111〜114を構成する各トランジスタのソース−ドレイン耐圧を(Vcc−Vss)として考える。

【0044】

第1トランジスタ回路111の入力端T15、即ち、ダブルゲートトランジスタ(P11,P12)のゲート電極は、第3,第4トランジスタ回路113,114の出力端T13に接続されている。また、第3トランジスタ回路113の入力端T16、即ち、ダブルゲートトランジスタ(P13,P14)のゲート電極は、第1,第2トランジスタ回路111,112の出力端T11に接続されている。

【0045】

上述したように、本実施形態に係るレベルシフタ回路100Aは、第1トランジスタ回路111、第2トランジスタ回路112、第3トランジスタ回路113、及び、第4トランジスタ回路114の4つのトランジスタ回路がダブルゲートトランジスタから成る特徴に加えて、次の点を特徴としている。

【0046】

第1トランジスタ回路111を構成するダブルゲートトランジスタ(P11,P12)の共通接続ノードn11と第3固定電源103との間には、スイッチ素子、例えば、第1トランジスタ回路111を構成するトランジスタと同導電型であるPチャネルトランジスタP15が接続されている。PチャネルトランジスタP15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P11,P12)の共通接続ノードn11に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0047】

PチャネルトランジスタP15は、ゲート電極が第1,第2スイッチ回路111,112の出力端T11に接続されている。そして、PチャネルトランジスタP15は、第2トランジスタ回路112が動作状態のときに、導通(オン)状態となって第3固定電源103の電圧Vmを、第1トランジスタ回路111のダブルゲートトランジスタ(P11,P12)の共通接続ノードn11に与える。ここで、「第2トランジスタ回路112が動作状態のとき」とは、第2トランジスタ回路112を構成するNチャネルトランジスタN11,N12が導通状態のときを言う。

【0048】

第2トランジスタ回路112を構成するダブルゲートトランジスタ(N11,N12)の共通接続ノードn12と第3固定電源103との間には、スイッチ素子、例えば、第2トランジスタ回路112を構成するトランジスタと同導電型であるNチャネルトランジスタN15が接続されている。NチャネルトランジスタN15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N11,N12)の共通接続ノードn12に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0049】

NチャネルトランジスタN15は、ゲート電極に第2入力電圧VINが与えられる。そして、NチャネルトランジスタN15は、第1トランジスタ回路111が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第2トランジスタ回路112のダブルゲートトランジスタ(N11,N12)の共通接続ノードn12に与える。ここで、「第1トランジスタ回路111が動作状態のとき」とは、第1トランジスタ回路111を構成するPチャネルトランジスタP11,P12が導通状態のときを言う。

【0050】

第3トランジスタ回路113を構成するダブルゲートトランジスタ(P13,P14)の共通接続ノードn13と第3固定電源103との間には、スイッチ素子、例えば、第3トランジスタ回路113を構成するトランジスタと同導電型であるPチャネルトランジスタP16が接続されている。PチャネルトランジスタP16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P13,P14)の共通接続ノードn13に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0051】

PチャネルトランジスタP16は、第3,第4スイッチ回路113,114の出力端T13に接続されている。そして、PチャネルトランジスタP16は、第4トランジスタ回路114が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第3トランジスタ回路113のダブルゲートトランジスタ(P13,P14)の共通接続ノードn13に与える。ここで、「第4トランジスタ回路114が動作状態のとき」とは、第4トランジスタ回路114を構成するNチャネルトランジスタN13,N14が導通状態のときを言う。

【0052】

第4トランジスタ回路114を構成するダブルゲートトランジスタ(N13,N14)の共通接続ノードn14と第3固定電源103との間には、スイッチ素子、例えば、第4トランジスタ回路114を構成するトランジスタと同導電型であるNチャネルトランジスタN16が接続されている。NチャネルトランジスタN16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N13,N14)の共通接続ノードn14に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0053】

NチャネルトランジスタN16は、ゲート電極に第1入力電圧VXINが与えられる。そして、NチャネルトランジスタN16は、第3トランジスタ回路113が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第4トランジスタ回路114のダブルゲートトランジスタ(N13,N14)の共通接続ノードn14に与える。ここで、「第3トランジスタ回路113が動作状態のとき」とは、第3トランジスタ回路113を構成するPチャネルトランジスタP13,P14が導通状態のときを言う。

【0054】

ここで、第3固定電源103の電圧Vmとして、第1,第2固定電源101,102の各電圧の間の値、好ましくは、第1,第2固定電源101,102の各電圧2Vcc,Vssの平均値を用いる。本例の場合、Vm=Vccとする。また、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧を、第1〜第4トランジスタ回路111〜114を構成する各トランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内の電圧とする。

【0055】

上記構成のレベルシフタ回路100Aは、その出力端T13、即ち、第3,第4トランジスタ回路113,114の出力端T13に入力端が接続される最終段のインバータ回路200との組合せで用いるのが好ましい。最終段のインバータ回路200は、PチャネルトランジスタP21及びNチャネルトランジスタN21から成るCMOSインバータ回路構成となっている。すなわち、PチャネルトランジスタP21及びNチャネルトランジスタN21は、正側電源201と負側電源202との間に直列に接続されている。

【0056】

そして、本例の場合には、正側電源201の電圧が入力電圧VIN,VXINの高電圧側と同じ電圧Vccに、負側電源202の電圧が入力電圧VIN,VXINの低電圧側と同じ電圧Vssにそれぞれ設定されている。これにより、前段のレベルシフタ回路100Aの第1固定電源101の電圧2Vccは、最終段のインバータ回路200の正側電源201の電圧Vccよりも高く、第2固定電源102の電圧Vssは、最終段のインバータ回路200の負側電源102の電圧Vssと等しくなる。

【0057】

PチャネルトランジスタP21及びNチャネルトランジスタN21のゲート電極同士は、共通に接続されて本インバータ回路200の入力端T21となり、前段のレベルシフタ回路100Aの出力端T13に接続されている。また、PチャネルトランジスタP21及びNチャネルトランジスタN21のドレイン電極同士は、共通に接続されて本インバータ回路200の出力端T22となっている。そして、この出力端T22から、振幅がVcc−Vss、即ち、高電圧側がVcc、低電圧側がVssの出力電圧VOUTが導出される。

【0058】

[2−2.回路動作]

続いて、上記構成の第1実施形態に係るレベルシフタ回路100Aの回路動作について、図2及び図3を用いて説明する。尚、図4には、互いに逆相の2つの入力電圧VIN,VXIN、レベルシフタ回路100Aの出力電圧VA、及び、最終段のインバータ回路200の出力電圧VOUTの各波形を示す。

【0059】

先ず、一方の入力電圧VINが低電圧(低レベル)Vss、他方の入力電圧VXINが高電圧(高レベル)Vccの場合の回路動作について、図2の動作説明図を用いて説明する。

【0060】

一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccのとき、第2トランジスタ回路112のNチャネルトランジスタN11,N12及び第4トランジスタ回路114側のNチャネルトランジスタN16が導通(オン)状態になる。これにより、第3トランジスタ回路113のPチャネルトランジスタP13,P14及び第1トランジスタ回路111側のPチャネルトランジスタP15の各ゲート電位が低レベルVssとなる。

【0061】

この動作により、第3トランジスタ回路113のPチャネルトランジスタP13,P14及び第1トランジスタ回路111側のPチャネルトランジスタP15が導通状態になるため、本レベルシフタ回路100Aの出力電圧VAは第1固定電源101の電圧2Vccになる。このとき、Vm=Vccであることから、第1トランジスタ回路111のダブルゲートトランジスタ(P11,P12)の共通接続ノードn11の電位はVccとなる。また、NチャネルトランジスタN16の閾値電圧をVthとすると、第4トランジスタ回路114のダブルゲートトランジスタ(N13,N14)の共通接続ノードn14の電位はVcc−Vthという値となる。

【0062】

次に、一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の回路動作について、図3の動作説明図を用いて説明する。

【0063】

一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssのとき、第4トランジスタ回路114のNチャネルトランジスタN13,N14及び第2トランジスタ回路112側のNチャネルトランジスタN15が導通状態になる。これにより、第1トランジスタ回路111のPチャネルトランジスタP11,P12及び第3トランジスタ回路113側のPチャネルトランジスタP16の各ゲート電位(本レベルシフタ回路100Aの出力電圧でもある)VAが第1固定電源101の電圧2Vccから第2固定電源102の電圧Vssへと遷移する。

【0064】

第1トランジスタ回路111のPチャネルトランジスタP11,P12のゲート電位が低レベルVssになることで、これらPチャネルトランジスタP11,P12が導通状態になる。これにより、第3トランジスタ回路113のPチャネルトランジスタP13,P14のゲート電位が第1固定電源101の電圧2Vccになるため、これらPチャネルトランジスタP13,P14が非導通(オフ)状態になる。このとき、第3トランジスタ回路113のダブルゲートトランジスタ(P13,P14)の共通接続ノードn13の電位はVccとなる。また、NチャネルトランジスタN15の閾値電圧をVthとすると、第2トランジスタ回路112のダブルゲートトランジスタ(N11,N12)の共通接続ノードn12の電位はVcc−Vthとなる。

【0065】

ここで、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン間電圧について考える。各トランジスタにかかるソース−ドレイン間電圧は、第1固定電源101の電圧2Vcc、第2固定電源102の電圧Vss、及び、第3固定電源103の電圧Vm(=Vcc)の各値によって決定される。そして、前述したように、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧が、各トランジスタのソース−ドレイン耐圧(本例では、Vcc−Vss)の範囲内の電圧となるように各電源電圧の値が設定されている。

【0066】

このような条件の下で上述した回路動作を行うことで、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えつつ、2Vcc−Vssの振幅の出力電圧VAを得ることができる。

【0067】

[2−3.第1実施形態の作用、効果]

第1実施形態に係るレベルシフタ回路100Aは、入力電圧VIN,VXINを高くなる方向にレベルシフト(レベル変換)する作用を為す。そして、このレベルシフタ回路100Aを最終段のインバータ回路200の前段の回路として配する。これにより、最終段のインバータ回路200の抵抗を下げるに当たって、当該インバータ回路200を構成するトランジスタP21,N21のサイズを大きくすることなく、これらトランジスタP21,N21のゲート−ソース間電圧を上げることができる、即ち、インバータ回路200の入力電圧の振幅を増大させることができる。

【0068】

また、第1〜第4トランジスタ回路111〜114をダブルゲートトランジスタによって構成し、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源103の電圧Vmを与えるようにした。

【0069】

具体的には、第2トランジスタ回路112が動作状態のとき、第1トランジスタ回路111のダブルゲートトランジスタ(P11,P12)の共通接続ノードn11に、PチャネルトランジスタP15を介して第3固定電源103の電圧Vmを与える。また、第4トランジスタ回路114が動作状態のとき、第3トランジスタ回路113のダブルゲートトランジスタ(P13,P14)の共通接続ノードn13に、PチャネルトランジスタP16を介して第3固定電源103の電圧Vmを与える。

【0070】

このようにすることで、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えることができる。従って、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。

【0071】

この場合、最終段のインバータ回路200に入力される波形の振幅が(2Vcc−Vss)となり、最終段のインバータ回路200を構成するトランジスタP21,N21のゲート−ソース間には、ソース−ドレイン耐圧(Vcc−Vss)を超える電圧がかかることになる。しかし、一般に、トランジスタのゲート−ソース耐圧は、ソース−ドレイン耐圧よりも大きい(高い)。従って、トランジスタP21,N21のゲート−ソース間に、ソース−ドレイン耐圧を超える電圧を印加することができる。そして、トランジスタP21,N21のゲート−ソース間電圧を上げる、即ち、最終段のインバータ回路200の入力電圧の振幅を増大させることによって当該インバータ回路200の抵抗を下げることができる。

【0072】

上述したように、第1実施形態に係るレベルシフタ回路100Aによれば、当該レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。また、最終段のインバータ回路200の入力電圧の振幅をより増大させることにより、当該インバータ200を構成するトランジスタP21,N21のサイズを小さくすることが可能になる。更に、定常状態において貫通電流が流れないため、低消費電力化も可能となる。

【0073】

<3.第2実施形態>

[3−1.回路構成]

図5は、本開示の第2実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。第2実施形態に係るレベルシフタ回路100Bは、前に述べた第2の回路形態を採っている。すなわち、第1固定電源101を負側電源、第2固定電源102を正側電源とし、第1導電型のトランジスタとしてNチャネルトランジスタを用い、第2導電型のトランジスタとしてPチャネルトランジスタを用いる。

【0074】

図5において、第2実施形態に係るレベルシフタ回路100Bは、第1トランジスタ回路211、第2トランジスタ回路212、第3トランジスタ回路213、及び、第4トランジスタ回路214の4つのトランジスタ回路から構成されている。第1トランジスタ回路211と第2トランジスタ回路212とは、負側電源である第1固定電源101と正側電源である第2固定電源102との間に直列に接続されている。同様に、第3トランジスタ回路213と第4トランジスタ回路214とは、第1固定電源101と第2固定電源102との間に直列に接続されている。

【0075】

第1固定電源101側の2つのトランジスタ回路、即ち、第1トランジスタ回路211及び第3トランジスタ回路213は、Nチャネルトランジスタから成る。第2固定電源102側の2つのトランジスタ回路、即ち、第2トランジスタ回路212及び第4トランジスタ回路214は、Nチャネルトランジスタから成る。そして、第1固定電源101側の2つのトランジスタ回路211,213、及び、第2固定電源102側の2つのトランジスタ回路212,214が共に、ダブルゲートトランジスタから成る。

【0076】

但し、これは一例に過ぎず、第1固定電源101側の2つのトランジスタ回路211,213及び第2固定電源102側の2つのトランジスタ回路212,214の一方側の2つのトランジスタ回路のみが、ダブルゲートトランジスタから成る構成を採ることも可能である。一方側の2つのトランジスタ回路のみがダブルゲートトランジスタから成るときは、他方側の2つのトランジスタ回路はシングルゲートトランジスタから成る。

【0077】

第1トランジスタ回路211は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN11,N12から成る。NチャネルトランジスタN11のドレイン電極は、第1トランジスタ回路211の出力端T11となっている。NチャネルトランジスタN11のソース電極とNチャネルトランジスタN12のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N11,N12)の共通接続ノードn11となっている。NチャネルトランジスタN12のソース電極は、第1固定電源101に接続されている。

【0078】

第2トランジスタ回路212は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP11,P12から成る。2つのPチャネルトランジスタP11,P12の共通に接続されたゲート電極は、第2トランジスタ回路212の入力端T12となっている。PチャネルトランジスタP11のソース電極は、第2固定電源102に接続されている。PチャネルトランジスタP11のドレイン電極とPチャネルトランジスタP12のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P11,P12)の共通接続ノードn12となっている。

【0079】

PチャネルトランジスタP12のドレイン電極は、第2トランジスタ回路212の出力端T11となっている。第2トランジスタ回路212の出力端T11は、第1トランジスタ回路211の出力端T11でもある。すなわち、PチャネルトランジスタP12のドレイン電極とNチャネルトランジスタN11のドレイン電極とが共通に接続されて第1,第2トランジスタ回路211,212の出力端T11となっている。

【0080】

第3トランジスタ回路213は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN13,N14から成る。NチャネルトランジスタN13のドレイン電極は、第3トランジスタ回路213の出力端T13となっている。NチャネルトランジスタN13のソース電極とNチャネルトランジスタN14のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N13,N14)の共通接続ノードn13となっている。NチャネルトランジスタN14のソース電極は、第1固定電源101に接続されている。

【0081】

第4トランジスタ回路214は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP13,P14から成る。2つのPチャネルトランジスタP13,P14の共通に接続されたゲート電極は、第4トランジスタ回路214の入力端T14となっている。PチャネルトランジスタP13のソース電極は、第2固定電源102に接続されている。PチャネルトランジスタP13のドレイン電極とPチャネルトランジスタP14のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P13,P14)の共通接続ノードn14となっている。

【0082】

PチャネルトランジスタP14のドレイン電極は、第4トランジスタ回路214の出力端T13となっている。第4トランジスタ回路214の出力端T13は、第3トランジスタ回路213の出力端T13でもある。すなわち、PチャネルトランジスタP14のドレイン電極とNチャネルトランジスタN13のドレイン電極とが共通に接続されて第3,第4トランジスタ回路213,214の出力端T13となっている。また、第3,第4トランジスタ回路213,214の出力端T13は、本レベルシフタ回路100Bの出力端でもある。

【0083】

上記構成のレベルシフタ回路100Bにおいて、第2固定電源102側の2つのトランジスタ回路、即ち、第2,第4トランジスタ212,214の各入力端T12,T14には、第1,第2入力電圧VXIN,VINが与えられる。第1,第2入力電圧VXIN,VINは、高レベルがVcc、低レベルがVssの、互いに逆相の電圧である。

【0084】

この第1,第2入力電圧VXIN,VINに対して、第1固定電源101の電圧は、低電圧側の電圧Vssよりも低い電圧、例えば2Vssに設定され、第2固定電源102の電圧は、高電圧側の電圧Vcc以上の電圧、例えば、等しい電圧に設定されている。尚、ここでは、レベルシフタ回路100B、即ち、第1〜第4トランジスタ回路211〜214を構成する各トランジスタのソース−ドレイン耐圧を(Vcc−Vss)として考える。

【0085】

第1トランジスタ回路211の入力端T15、即ち、ダブルゲートトランジスタ(N11,N12)のゲート電極は、第3,第4トランジスタ回路213,214の出力端T13に接続されている。また、第3トランジスタ回路213の入力端T16、即ち、ダブルゲートトランジスタ(N13,N14)のゲート電極は、第1,第2トランジスタ回路211,212の出力端T11に接続されている。

【0086】

上述したように、本実施形態に係るレベルシフタ回路100Bは、第1トランジスタ回路211、第2トランジスタ回路212、第3トランジスタ回路213、及び、第4トランジスタ回路214の4つのトランジスタ回路がダブルゲートトランジスタから成る特徴に加えて、次の点を特徴としている。

【0087】

第1トランジスタ回路211を構成するダブルゲートトランジスタ(N11,N12)の共通接続ノードn11と第3固定電源103との間には、スイッチ素子、例えば、第1トランジスタ回路211を構成するトランジスタと同導電型であるNチャネルトランジスタN15が接続されている。NチャネルトランジスタN15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N11,N12)の共通接続ノードn11に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0088】

NチャネルトランジスタN15は、ゲート電極が出力端T11に接続されている。そして、NチャネルトランジスタN15は、第2トランジスタ回路212が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第1トランジスタ回路211のダブルゲートトランジスタ(N11,N12)の共通接続ノードn11に与える。ここで、「第2トランジスタ回路212が動作状態のとき」とは、第2トランジスタ回路212を構成するPチャネルトランジスタP11,P12が導通状態のときを言う。

【0089】

第2トランジスタ回路212を構成するダブルゲートトランジスタ(P11,P12)の共通接続ノードn12と第3固定電源103との間には、スイッチ素子、例えば、第2トランジスタ回路212を構成するトランジスタと同導電型であるPチャネルトランジスタP15が接続されている。PチャネルトランジスタP15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P11,P12)の共通接続ノードn12に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0090】

PチャネルトランジスタP15は、ゲート電極に第2入力電圧VINが与えられる。そして、PチャネルトランジスタP15は、第1トランジスタ回路211が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第2トランジスタ回路212のダブルゲートトランジスタ(P11,P12)の共通接続ノードn12に与える。ここで、「第1トランジスタ回路211が動作状態のとき」とは、第1トランジスタ回路211を構成するNチャネルトランジスタN11,N12が導通状態のときを言う。

【0091】

第3トランジスタ回路213を構成するダブルゲートトランジスタ(N13,N14)の共通接続ノードn13と第3固定電源103との間には、スイッチ素子、例えば、第3トランジスタ回路213を構成するトランジスタと同導電型であるNチャネルトランジスタN16が接続されている。NチャネルトランジスタN16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N13,N14)の共通接続ノードn13に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0092】

NチャネルトランジスタN16は、ゲート電極が出力端T13に接続されている。そして、NチャネルトランジスタN16は、第4トランジスタ回路214が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第3トランジスタ回路213のダブルゲートトランジスタ(N13,N14)の共通接続ノードn13に与える。ここで、「第4トランジスタ回路214が動作状態のとき」とは、第4トランジスタ回路214を構成するPチャネルトランジスタP13,P14が導通状態のときを言う。

【0093】

第4トランジスタ回路214を構成するダブルゲートトランジスタ(P13,P14)の共通接続ノードn14と第3固定電源103との間には、スイッチ素子、例えば、第4トランジスタ回路214を構成するトランジスタと同導電型であるPチャネルトランジスタP16が接続されている。PチャネルトランジスタP16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P13,P14)の共通接続ノードn14に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0094】

PチャネルトランジスタP16は、ゲート電極に第1入力電圧VXINが与えられる。そして、PチャネルトランジスタP16は、第3トランジスタ回路213が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第4トランジスタ回路214のダブルゲートトランジスタ(P13,P14)の共通接続ノードn14に与える。ここで、「第3トランジスタ回路213が動作状態のとき」とは、第3トランジスタ回路213を構成するNチャネルトランジスタN13,N14が導通状態のときを言う。

【0095】

ここで、第3固定電源103の電圧Vmとして、第1,第2固定電源101,102の各電圧の間の値、好ましくは、第1,第2固定電源101,102の各電圧Vcc,2Vssの平均値を用いる。本例の場合、Vm=Vssとする。また、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧を、第1〜第4トランジスタ回路211〜214を構成する各トランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内の電圧とする。

【0096】

上記構成のレベルシフタ回路100Bは、第1実施形態の場合と同様に、最終段のインバータ回路200との組合せで用いるのが好ましい。最終段のインバータ回路200は、正側電源201の電圧が入力電圧VIN,VXINの高電圧側と同じ電圧Vccに、負側電源202の電圧が入力電圧VIN,VXINの低電圧側と同じ電圧Vssにそれぞれ設定されている。従って、前段のレベルシフタ回路100Bの第1固定電源101の電圧2Vssは、最終段のインバータ回路200の負側電源102の電圧Vssよりも低く、第2固定電源102の電圧Vccは、最終段のインバータ回路200の正側電源201の電圧Vccと等しくなる。

【0097】

[3−2.回路動作]

続いて、上記構成の第2実施形態に係るレベルシフタ回路100Bの回路動作について、図6及び図7を用いて説明する。尚、図8には、互いに逆相の2つの入力電圧VIN,VXIN、レベルシフタ回路100Bの出力電圧VB、及び、最終段のインバータ回路200の出力電圧VOUTの各波形を示す。

【0098】

先ず、一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の回路動作について、図6の動作説明図を用いて説明する。

【0099】

一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssのとき、第2トランジスタ回路212のPチャネルトランジスタP11,P12及び第4トランジスタ回路214側のPチャネルトランジスタP16が導通状態になる。これにより、第3トランジスタ回路213のNチャネルトランジスタN13,N14及び第1トランジスタ回路211側のNチャネルトランジスタN15の各ゲート電位が高レベルVccとなる。

【0100】

この動作により、第3トランジスタ回路213のNチャネルトランジスタN13,N14及び第1トランジスタ回路211側のNチャネルトランジスタN15が導通状態になるため、本レベルシフタ回路100Bの出力電圧VBは第1固定電源101の電圧2Vssになる。このとき、Vm=Vssであることから、第1トランジスタ回路211のダブルゲートトランジスタ(N11,N12)の共通接続ノードn11の電位はVssとなる。また、PチャネルトランジスタP16の閾値電圧をVthとすると、第4トランジスタ回路214のダブルゲートトランジスタ(P13,P14)の共通接続ノードn14の電位はVss+Vthという値となる。

【0101】

次に、一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccの場合の回路動作について、図7の動作説明図を用いて説明する。

【0102】

一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccのとき、第4トランジスタ回路214のPチャネルトランジスタP13,P14及び第2トランジスタ回路212側のPチャネルトランジスタP15が導通状態になる。これにより、第1トランジスタ回路211のNチャネルトランジスタN11,P12及び第3トランジスタ回路213側のNチャネルトランジスタN16の各ゲート電位(本レベルシフタ回路100Bの出力電圧でもある)VBが第1固定電源101の電圧2Vssから第2固定電源102の電圧Vccへと遷移する。

【0103】

第1トランジスタ回路211のNチャネルトランジスタN11,N12のゲート電位が高レベルVccになることで、これらNチャネルトランジスタN11,N12が導通状態になる。これにより、第3トランジスタ回路213のNチャネルトランジスタN13,N14のゲート電位が第1固定電源101の電圧2Vssになるため、これらNチャネルトランジスタN13,N14が非導通状態になる。このとき、第3トランジスタ回路213のダブルゲートトランジスタ(N13,N14)の共通接続ノードn13の電位はVssとなる。また、PチャネルトランジスタP15の閾値電圧をVthとすると、第2トランジスタ回路212のダブルゲートトランジスタ(P11,P12)の共通接続ノードn12の電位はVss+Vthとなる。

【0104】

ここで、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン間電圧について考える。各トランジスタにかかるソース−ドレイン間電圧は、第1固定電源101の電圧2Vss、第2固定電源102の電圧Vcc、及び、第3固定電源103の電圧Vm(=Vss)の各値によって決定される。そして、前述したように、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧が、各トランジスタのソース−ドレイン耐圧(本例では、Vcc−Vss)の範囲内の電圧となるように各電源電圧の値が設定されている。

【0105】

このような条件の下で上述した回路動作を行うことで、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えつつ、2Vss−Vccの振幅の出力電圧VAを得ることができる。

【0106】

[3−3.第2実施形態の作用、効果]

第2実施形態に係るレベルシフタ回路100Bは、基本的に、第1実施形態に係るレベルシフタ回路100Aと同様の作用、効果を得ることができる。すなわち、最終段のインバータ回路200を構成するトランジスタP21,N21のサイズを大きくすることなく、尚且つ、各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。

【0107】

回路動作上では、次の点で第1実施形態に係るレベルシフタ回路100Aと異なるものの、得られる作用、効果は同じである。

【0108】

具体的には、第2トランジスタ回路212が動作状態のとき、第1トランジスタ回路211のダブルゲートトランジスタ(N11,N12)の共通接続ノードn11に、NチャネルトランジスタN15を介して第3固定電源103の電圧Vmを与える。また、第4トランジスタ回路214が動作状態のとき、第3トランジスタ回路213のダブルゲートトランジスタ(N13,N14)の共通接続ノードn13に、NチャネルトランジスタN16を介して第3固定電源103の電圧Vmを与える。

【0109】

このようにすることで、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えることができる。従って、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。

【0110】

上述したように、第2実施形態に係るレベルシフタ回路100Bによれば、第1実施形態に係るレベルシフタ回路100Aと同様の作用、効果を得ることができる。すなわち、レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。また、最終段のインバータ回路200の入力電圧の振幅をより増大させることにより、当該インバータ200を構成するトランジスタP21,N21のサイズを小さくすることが可能になる。更に、定常状態において貫通電流が流れないため、低消費電力化も可能となる。

【0111】

<4.第3実施形態>

図9は、本開示の第3実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【0112】

図9に示すように、第3実施形態に係るレベルシフタ回路100Cは、第1実施形態に係るレベルシフタ回路100Aと第2実施形態に係るレベルシフタ回路100Bとの組合せから成る。レベルシフタ回路100A及びレベルシフタ回路100Bの配置の順番は任意であるが、本例では、レベルシフタ回路100Aを前段側(1段目)に、レベルシフタ回路100Bを後段側(2段目)に配置する構成を採っている。また、第3実施形態に係るレベルシフタ回路100Cについても、第1,第2実施形態の場合と同様に、最終段のインバータ回路200との組合せで用いるのが好ましい。

【0113】

1段目のレベルシフタ回路100Aでは、正側電源の電圧を2Vccに設定し、負側電源の電圧をVssに設定している。これにより、1段目のレベルシフタ回路100Aの出力電圧VAとして、2Vcc−Vssの振幅の電圧が導出される。また、2段目のレベルシフタ回路100Bでは、正側電源の電圧を2Vccに設定し、負側電源の電圧を2Vssに設定している。これにより、1段目のレベルシフタ回路100Bの出力電圧VBとして、2Vcc−2Vssの振幅の電圧が導出される。

【0114】

図10に、入力電圧VIN、1段目のレベルシフタ回路100Aの出力電圧VA、2段目のレベルシフタ回路100Bの出力電圧VB、及び、最終段のインバータ回路200の出力電圧VOUTの各波形を示す。

【0115】

上述したように、レベルシフタ回路100Cを複数段(本例では、2段)縦続接続の構成とすることで、当該レベルシフタ回路100Cを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅をより増大させることができる。これにより、最終段のインバータ回路200を構成するトランジスタP21,N21のサイズをより小さくすることが可能になる。また、定常状態において、貫通電流をより確実に抑えることができる、より低消費電力化を図ることができる。

【0116】

以上説明した、各実施形態に係るレベルシフタ回路100A,100B,100Cは、一般的なレベルシフタ回路として種々の用途に用いることができる他、例えば、最終段にインバータ回路を有する走査回路において、最終段のインバータ回路の前段回路として用いることができる。また、これらレベルシフタ回路100A,100B,100Cを最終段のインバータ回路の前段回路として走査回路(本開示の走査回路)は、電気光学素子を含む画素が行列状に配置されて成る表示装置、あるいは、光電変換素子を含む画素が行列状に配置されて成る固体撮像装置において、各画素を走査する走査回路として用いることができる。

【0117】

以下では、第1,第2,第3実施形態に係るレベルシフタ回路100A,100B,100Cを、最終段のインバータ回路の前段回路として走査回路を搭載する表示装置を本開示の表示装置として説明する。

【0118】

<3.表示装置>

[3−1.システム構成]

図11は、本開示の表示装置、例えば、アクティブマトリクス型表示装置の構成の概略を示すシステム構成図である。

【0119】

アクティブマトリクス型表示装置は、電気光学素子に流れる電流を、当該電気光学素子と同じ画素内に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタによって制御する表示装置である。絶縁ゲート型電界効果トランジスタとしては、典型的には、TFT(Thin Film Transistor:薄膜トランジスタ)が用いられる。

【0120】

ここでは、一例として、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子、例えば有機EL素子を、画素(画素回路)の発光素子として用いるアクティブマトリクス型有機EL表示装置の場合を例に挙げて説明する。

【0121】

図11に示すように、本例に係る有機EL表示装置10は、有機EL素子を含む複数の画素20が行列状に2次元配置されてなる画素アレイ部30と、当該画素アレイ部30の周辺に配置される駆動回路部とを有する構成となっている。駆動回路部は、書込み走査回路40、電源供給走査回路50、及び、信号出力回路60等から成り、画素アレイ部30の各画素20を駆動する。

【0122】

ここで、有機EL表示装置10がカラー表示対応の場合は、カラー画像を形成する単位となる1つの画素(単位画素)は複数の副画素(サブピクセル)から構成され、この副画素の各々が図11の画素20に相当することになる。より具体的には、カラー表示対応の表示装置では、1つの画素は、例えば、赤色(Red;R)光を発光する副画素、緑色(Green;G)光を発光する副画素、青色(Blue;B)光を発光する副画素の3つの副画素から構成される。

【0123】

但し、1つの画素としては、RGBの3原色の副画素の組み合わせに限られるものではなく、3原色の副画素に更に1色あるいは複数色の副画素を加えて1つの画素を構成することも可能である。より具体的には、例えば、輝度向上のために白色(White;W)光を発光する副画素を加えて1つの画素を構成したり、色再現範囲を拡大するために補色光を発光する少なくとも1つの副画素を加えて1つの画素を構成したりすることも可能である。

【0124】

画素アレイ部30には、m行n列の画素20の配列に対して、行方向(画素行に沿った方向/画素行の画素の配列方向)に沿って走査線311〜31mと電源供給線321〜32mとが画素行毎に配線されている。更に、m行n列の画素20の配列に対して、列方向(画素列に沿った方向/画素列の画素の配列方向)に沿って信号線331〜33nが画素列毎に配線されている。

【0125】

走査線311〜31mは、書込み走査回路40の対応する行の出力端にそれぞれ接続されている。電源供給線321〜32mは、電源供給走査回路50の対応する行の出力端にそれぞれ接続されている。信号線331〜33nは、信号出力回路60の対応する列の出力端にそれぞれ接続されている。

【0126】

画素アレイ部30は、通常、ガラス基板などの透明絶縁基板上に形成されている。これにより、有機EL表示装置10は、平面型(フラット型)のパネル構造となっている。画素アレイ部30の各画素20の駆動回路は、アモルファスシリコンTFTまたは低温ポリシリコンTFTを用いて形成することができる。

【0127】

書込み走査回路40は、クロックパルスckに同期してスタートパルスspを順にシフト(転送)するシフトレジスタ回路等によって構成されている。この書込み走査回路40は、画素アレイ部30の各画素20への映像信号の信号電圧の書込みに際し、走査線31(311〜31m)に対して書込み走査信号WS(WS1〜WS m)を順次供給することによって画素アレイ部30の各画素20を行単位で順番に走査(線順次走査)する。

【0128】

電源供給走査回路50は、クロックパルスckに同期してスタートパルスspを順にシフトするシフトレジスタ回路等によって構成されている。この電源供給走査回路50は、書込み走査回路40による線順次走査に同期して、第1電源電位Vccpと当該第1電源電位Vccpよりも低い第2電源電位Viniとで切り替わることが可能な電源電位DS(DS1〜DSm)を電源供給線32(321〜32m)に供給する。電源電位DSのVccp/Viniの切替えにより、画素20の発光/非発光の制御が行なわれる。

【0129】

信号出力回路60は、信号供給源(図示せず)から供給される輝度情報に応じた映像信号の信号電圧(以下、単に「信号電圧」と記述する場合もある)Vsigと基準電圧Vofsとを選択的に出力する。ここで、基準電圧Vofsは、映像信号の信号電圧Vsigの基準となる電位(例えば、映像信号の黒レベルに相当する電位)である。

【0130】

信号出力回路60から出力される信号電圧Vsig/基準電圧Vofsは、信号線33(331〜33n)を介して画素アレイ部30の各画素20に対して、書込み走査回路40による走査によって選択された画素行の単位で書き込まれる。すなわち、信号出力回路60は、信号電圧Vsigを行(ライン)単位で書き込む線順次書込みの駆動形態を採っている。

【0131】

[3−2.画素回路]

図12は、画素(画素回路)20の具体的な回路構成の一例を示す回路図である。画素20の発光部は、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子である有機EL素子21から成る。

【0132】

図12に示すように、画素20は、有機EL素子21と、有機EL素子21に電流を流すことによって当該有機EL素子21を駆動する駆動回路とによって構成されている。有機EL素子21は、全ての画素20に対して共通に配線された共通電源供給線34にカソード電極が接続されている。

【0133】

有機EL素子21を駆動する駆動回路は、駆動トランジスタ22、書込みトランジスタ23、及び、保持容量24を有する構成となっている。駆動トランジスタ22及び書込みトランジスタ23としてNチャネル型のTFTを用いることができる。但し、ここで示した、駆動トランジスタ22及び書込みトランジスタ23の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。

【0134】

駆動トランジスタ22は、一方の電極(ソース/ドレイン電極)が有機EL素子21のアノード電極に接続され、他方の電極(ソース/ドレイン電極)が電源供給線32(321〜32m)に接続されている。

【0135】

書込みトランジスタ23は、一方の電極(ソース/ドレイン電極)が信号線33(331〜33n)に接続され、他方の電極(ソース/ドレイン電極)が駆動トランジスタ22のゲート電極に接続されている。また、書込みトランジスタ23のゲート電極は、走査線31(311〜31m)に接続されている。

【0136】

駆動トランジスタ22及び書込みトランジスタ23において、一方の電極とは、ソース/ドレイン領域に電気的に接続された金属配線を言い、他方の電極とは、ドレイン/ソース領域に電気的に接続された金属配線を言う。また、一方の電極と他方の電極との電位関係によって一方の電極がソース電極ともなればドレイン電極ともなり、他方の電極がドレイン電極ともなればソース電極ともなる。

【0137】

保持容量24は、一方の電極が駆動トランジスタ22のゲート電極に接続され、他方の電極が駆動トランジスタ22の他方の電極、及び、有機EL素子21のアノード電極に接続されている。

【0138】

上記構成の画素20において、書込みトランジスタ23は、書込み走査回路40から走査線31を通してゲート電極に印加されるHighアクティブの書込み走査信号WSに応答して導通状態となる。これにより、書込みトランジスタ23は、信号線33を通して信号出力回路60から供給される、輝度情報に応じた映像信号の信号電圧Vsigまたは基準電圧Vofsをサンプリングして画素20内に書き込む。書込みトランジスタ23によって書き込まれた信号電圧Vsigまたは基準電圧Vofsは、駆動トランジスタ22のゲート電極に印加されるとともに保持容量24に保持される。

【0139】

駆動トランジスタ22は、電源供給線32(321〜32m)の電源電位DSが第1電源電位Vccpにあるときには、一方の電極がドレイン電極、他方の電極がソース電極となって飽和領域で動作する。これにより、駆動トランジスタ22は、電源供給線32から電流の供給を受けて有機EL素子21を電流駆動にて発光駆動する。より具体的には、駆動トランジスタ22は、飽和領域で動作することにより、保持容量24に保持された信号電圧Vsigの電圧値に応じた電流値の駆動電流を有機EL素子21に供給し、当該有機EL素子21を電流駆動することによって発光させる。

【0140】

駆動トランジスタ22は更に、電源電位DSが第1電源電位Vccpから第2電源電位Viniに切り替わったときには、一方の電極がソース電極、他方の電極がドレイン電極となってスイッチングトランジスタとして動作する。これにより、駆動トランジスタ22は、有機EL素子21への駆動電流の供給を停止し、有機EL素子21を非発光状態にする。すなわち、駆動トランジスタ22は、有機EL素子21の発光/非発光を制御するトランジスタとしての機能をも併せ持っている。

【0141】

この駆動トランジスタ22のスイッチング動作により、有機EL素子21が非発光状態となる期間(非発光期間)を設け、有機EL素子21の発光期間と非発光期間の割合(デューティ)を制御することができる。このデューティ制御により、1表示フレーム期間に亘って画素が発光することに伴う残像ボケを低減できるために、特に、動画の画品位をより優れたものとすることができる。

【0142】

電源供給走査回路50から電源供給線32を通して選択的に供給される第1,第2電源電位Vccp,Viniのうち、第1電源電位Vccpは有機EL素子21を発光駆動する駆動電流を駆動トランジスタ22に供給するための電源電位である。また、第2電源電位Viniは、有機EL素子21に対して逆バイアスを掛けるための電源電位である。この第2電源電位Viniは、基準電圧Vofsよりも低い電位、例えば、駆動トランジスタ22の閾値電圧をVthとするときVofs−Vthよりも低い電位、好ましくは、Vofs−Vthよりも十分に低い電位に設定される。

【0143】

[3−3.走査回路]

以上説明した有機EL表示装置10において、画素アレイ部30の周辺回路である書込み走査回路40や電源供給走査回路50の最終段のインバータ回路の前段回路として、先述した第1,第2,第3実施形態に係るレベルシフタ回路100A,100B,100Cを用いることができる。

【0144】

ここでは、一例として、第1,第2,第3実施形態に係るレベルシフタ回路100A,100B,100Cを、書込み走査回路40の最終段のインバータ回路の前段回路として用いる場合を例に挙げて説明する。

【0145】

図13は、書込み走査回路40の構成の一例を示すブロック図である。

【0146】

図13に示すように、書込み走査回路40は、例えば、シフトレジスタ回路41、ロジック回路群42、レベルシフタ回路群43、及び、最終段のインバータ回路群44によって構成されている。シフトレジスタ回路41は、画素アレイ部30の行数mに対応した段数のシフト段(転送段/単位回路)が縦続接続された構成となっており、クロックパルスckに同期してスタートパルスspを順にシフトし、各シフト段から順次シフトパルスを出力する。

【0147】

ロジック回路群42、レベルシフタ回路群43、及び、インバータ回路群44は各々、画素アレイ部30の行数mに対応した数のロジック回路421〜42m、レベルシフタ回路431〜43m、及び、最終段のインバータ回路441〜44mから成る。

【0148】

ロジック回路群42の各ロジック回路421〜42mは、シフトレジスタ回路41の対応するシフト段から出力されるシフトパルスを、所定のタイミングの走査パルスにタイミング調整する。レベルシフタ回路群43の各レベルシフタ回路431〜43mは、論理レベルの走査パルスを、それよりも高いレベルの走査パルスにレベルシフト(レベル変換)する。最終段のインバータ回路群44の各インバータ回路441〜44mは、レベルシフト後の走査パルスを、極性反転して書込み走査信号(パルス)WS1〜WS mとして画素アレイ部30の走査線311〜31 mに供給する。

【0149】

上記構成の書込み走査回路40において、その最終段段のインバータ回路群44のインバータ回路441〜44mの各々として、先述した各実施形態に係るレベルシフタ回路100A,100B,100Cを用いることができる。これらレベルシフタ回路100A,100B,100Cは、先述したように、当該レベルシフタ回路を構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200に入力する電圧の振幅を増大させることができる。

【0150】

そして、最終段のインバータ回路200を構成するトランジスタP21,N21のゲート−ソース間電圧を上げ、最終段のインバータ回路200の抵抗(即ち、トランジスタP21,N21のオン抵抗)を下げることで、表示パネル70の大型化が可能になる。より具体的には、表示パネル70の大型化によって走査線311〜31mの負荷が大きくなり、その負荷の影響で書込み走査パルスWS1〜WS mの波形が鈍ってしまう訳であるが、最終段のインバータ回路200の抵抗が下がることにより、負荷の影響を最小限に抑えることができる。従って、表示パネル70の大型化が可能になる。

【0151】

また、最終段のインバータ回路200の入力電圧の振幅をより増大させることで、当該インバータ200を構成するトランジスタP21,N21のサイズを小さくすることが可能になる。これにより、レベルシフタ回路100A,100B,100Cの回路規模、ひいては、これらレベルシフタ回路100A,100B,100Cを画素アレイ部30の画素行の行数分を有する書込み走査回路40や電源供給走査回路50の回路規模の縮小化を図ることができる。

【0152】

その結果、書込み走査回路40や電源供給走査回路50を、例えば図11に示すように、画素アレイ部30と同じ表示パネル70上に搭載して成る有機EL表示装置にあっては、表示パネル70の狭額縁化が可能になる。また、書込み走査回路40や電源供給走査回路50をドライバICとして表示パネル70外に配する構成を採る有機EL表示装置にあっては、当該ドライバICの小型化を図ることができる。

【0153】

[3−4.その他]

上述した有機EL表示装置では、画素20が2つのNチャネルのトランジスタ22,23及び1つの保持容量24から成る回路構成の場合を例に挙げて説明したが、画素20としてはこの回路構成のものに限られるものではない。すなわち、例えば、駆動トランジスタ22としてPチャネル型のTFTを用いた回路構成や、有機EL素子21の容量不足分を補い、保持容量24に対する映像信号の書込みゲインを高めるための補助容量を有する回路構成の画素20であってもよい。更には、基準電圧Vofsや第2電源電位Viniを選択的に書き込むためのスイッチングトランジスタなどを別途有する回路構成の画素20などであってもよい。

【0154】

また、上記の適用例では、画素20の電気光学素子として、有機EL素子を用いた有機EL表示装置に適用した場合を例に挙げて説明したが、本開示の技術はこの適用例に限られるものではない。具体的には、本開示の技術は、無機EL素子、LED素子、半導体レーザー素子など、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子(発光素子)を用いた表示装置の他、液晶表示装置やプラズマ表示装置など、走査回路を有する表示装置全般に対して適用可能である。更には、表示装置に限らず、固体撮像装置など、走査回路を有する装置全般に対して適用可能である。

【0155】

<4.電子機器>

以上説明した本開示のバッファ回路を出力段に用いる走査回路を搭載する表示装置は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示部(表示装置)として用いることが可能である。

【0156】

先述した各実施形態の説明から明らかなように、本開示のレベルシフタ回路を最終段のインバータ回路の前段回路として用いる走査回路は、例えば、画素アレイ部と同じ表示パネルに搭載される表示装置にあっては、表示パネルの狭額縁化を図ることができる。従って、表示部を有するあらゆる分野の電子機器において、その表示部として、本開示のレベルシフタ回路を最終段のインバータ回路の前段回路として用いる走査回路を搭載する表示装置を用いることで、電子機器本体の小型化を図ることができる。

【0157】

これらの電子機器としては、例えば、テレビジョンセット、デジタルカメラ、ビデオカメラ等の他、PDA(Personal Digital Assistant)、ゲーム機、ノート型パーソナルコンピュータ、電子書籍等の携帯情報機器、携帯電話機等の携帯通信機器などを例示することができる。

【0158】

<5.本開示の構成>

尚、本開示は以下のような構成を採ることができる。

(1)第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

レベルシフタ回路。

(2)第1固定電源−第3固定電源間の電圧及び第3固定電源−第2固定電源間の電圧は、前記第1乃至第4トランジスタ回路を構成する各トランジスタのソース−ドレイン耐圧の範囲内の電圧である

前記(1)に記載のレベルシフタ回路。

(3)第1入力電圧と第2入力電圧とは互いに逆相の電圧である

前記(1)または前記(2)に記載のレベルシフタ回路。

(4)第3固定電源の電圧は、第1固定電源及び第2固定電源の各電圧の間の値である

前記(1)から前記(3)のいずれかに記載のレベルシフタ回路。

(5)第3固定電源の電圧は、第1固定電源及び第2固定電源の各電圧の平均値である

前記(4)に記載のレベルシフタ回路。

(6)前記スイッチ素子は、前記他方の電源側の2つのトランジスタ回路を構成するトランジスタと同導電型のトランジスタである

前記(1)から前記(5)のいずれかに記載のレベルシフタ回路。

(7)前記スイッチ素子は、第1入力電圧または第2入力電圧をゲート入力とする

前記(1)から前記(6)のいずれかに記載のレベルシフタ回路。

(8)前記第3,第4トランジスタ回路の共通接続ノードには最終段のインバータ回路が接続されている

前記(1)から前記(7)のいずれかに記載のレベルシフタ回路。

(9)第1固定電源は正側電源、第2固定電源は負側電源であり、

第1導電型のトランジスタはPチャネル型のトランジスタ、第2導電型のトランジスタはNチャネル型のトランジスタである

前記(1)から前記(8)のいずれかに記載のレベルシフタ回路。

(10)第1固定電源の電圧は、第1,第2入力電圧の高電圧側の電圧よりも高く、

第2固定電源の電圧は、第1,第2入力電圧の低電圧側の電圧以下である

前記(9)に記載のレベルシフタ回路。

(11)第1固定電源の電圧は、前記最終段のインバータ回路の正側電源の電圧よりも高く、

第2固定電源の電圧は、前記最終段のインバータ回路の負側電源の電圧と等しい

前記(9)に記載のレベルシフタ回路。

(12)第1固定電源は負側電源、第2固定電源は正側電源であり、

第1導電型のトランジスタはNチャネル型のトランジスタ、第2導電型のトランジスタはPチャネル型のトランジスタである

前記(1)から前記(8)のいずれかに記載のレベルシフタ回路。

(13)第1固定電源の電圧は、第1,第2入力電圧の低電圧側の電圧よりも低く、

第2固定電源の電圧は、第1,第2入力電圧の高電圧側の電圧以上である

前記(12)に記載のレベルシフタ回路。

(14)第1固定電源の電圧は、前記最終段のインバータ回路の負側電源の電圧よりも低く、

第2固定電源の電圧は、前記最終段のインバータ回路の正側電源の電圧と等しい

前記(12)に記載のレベルシフタ回路。

(15)最終段にインバータ回路を、当該インバータ回路の前段にレベルシフタ回路を有し、

前記レベルシフタ回路は、

第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

走査回路。

(16)電気光学素子を含む画素が行列状に配置されて成る画素アレイ部と、

最終段にインバータ回路を、当該インバータ回路の前段にレベルシフタ回路を有し、前記画素アレイ部の各画素を走査する走査回路と

を備え、

前記レベルシフタ回路は、

第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

表示装置。

(17)電気光学素子を含む画素が行列状に配置されて成る画素アレイ部と、

最終段にインバータ回路を、当該インバータ回路の前段にレベルシフタ回路を有し、前記画素アレイ部の各画素を走査する走査回路と

を備え、

前記レベルシフタ回路は、

第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

表示装置を有する電子機器。

【符号の説明】

【0159】

10・・・有機EL表示装置、20・・・画素、21・・・有機EL素子、22・・・駆動トランジスタ、23・・・書込みトランジスタ、24・・・保持容量、30・・・画素アレイ部、40・・・書込み走査回路、41・・・シフトレジスタ回路、42・・・ロジック回路群、43・・・レベルシフタ回路群、44・・・インバータ回路群、50・・・電源供給走査回路、60・・・信号出力回路、100A,100B,100C・・・レベルシフタ回路、200・・・最終段のインバータ回路

【技術分野】

【0001】

本開示は、レベルシフタ回路、走査回路、表示装置、及び、電子機器に関する。

【背景技術】

【0002】

平面型(フラットパネル型)の表示装置の一つとして、デバイスに流れる電流値に応じて発光輝度が変化する、所謂、電流駆動型の電気光学素子を画素の発光部(発光素子)として用いた表示装置がある。電流駆動型の電気光学素子としては、例えば、有機材料のエレクトロルミネッセンス(Electro Luminescence:EL)を利用し、有機薄膜に電界をかけると発光する現象を用いた有機EL素子が知られている。

【0003】

画素の発光部として有機EL素子を用いた有機EL表示装置は次のような特長を持っている。すなわち、有機EL素子は、10V以下の印加電圧で駆動できるために低消費電力である。有機EL素子は自発光素子であるために、液晶表示装置に比べて、画像の視認性が高く、しかも、バックライト等の照明部材を必要としないために軽量化及び薄型化が容易である。更に、有機EL素子は、応答速度が数μsec程度と非常に高速であるために動画表示時の残像が発生しない。

【0004】

この有機EL表示装置に代表される平面型の表示装置は、電気光学素子の他に、書込みトランジスタ、保持容量、及び、駆動トランジスタを少なくとも有する画素が行列状に2次元配置された構成となっている(例えば、特許文献1参照)。

【0005】

この種の表示装置において、書込みトランジスタは、画素行毎に配線される制御線(走査線)を通して走査回路(走査部)から与えられる制御パルス(走査パルス)によって駆動されることで、信号線を通して供給される映像信号の信号電圧を画素内に書き込む。保持容量は、書込みトランジスタが書き込んだ信号電圧を保持する。駆動トランジスタは、保持容量が保持した信号電圧に応じて電気光学素子を駆動する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−310311号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、一般的に、表示パネルを大型化した場合、走査回路から書込みトランジスタに制御パルスを伝送する制御線の負荷が大きくなるため、その負荷の影響で制御パルスの波形が大きく鈍ってしまう。負荷の影響を抑えるには、走査回路の最終段のインバータ回路を構成するトランジスタのサイズを大きくし、当該インバータ回路の抵抗を小さくすることが考えられる。しかし、トランジスタのサイズを大きくすると、走査回路、ひいては、当該走査回路を含む周辺回路の回路規模が大きくなるため、表示パネルの狭額縁化の妨げとなる。

【0008】

このため、走査回路の最終段のインバータ回路を構成するトランジスタのサイズをそのままにして、即ち、トランジスタのサイズを大きくすることなく、最終段のインバータ回路の抵抗(インバータ回路を構成するトランジスタのオン抵抗)を小さくすることが必要となる。一般に、トランジスタの抵抗値は、トランジスタのサイズとゲート−ソース間電圧に依存する。従って、最終段のインバータ回路を構成するトランジスタのサイズを大きくしないのであれば、当該トランジスタのゲート−ソース間電圧を上げる、即ち、最終段のインバータ回路の入力電圧の振幅を増大させる必要がある。

【0009】

最終段のインバータ回路の入力電圧の振幅を増大させるには、最終段のインバータ回路の前段の回路に与える電源電圧を入力電圧よりも高くする必要がある。しかし、単純に、前段の回路に与える電源電圧を入力電圧よりも高くすると、前段の回路を構成するトランジスタにかかるソース−ドレイン間電圧が高くなってしまい、所定のソース−ドレイン耐圧を超えてしまう。

【0010】

一般に、トランジスタのソース−ドレイン耐圧はゲート−ソース耐圧よりも小さい(低い)。従って、前段の回路を構成するトランジスタにかかるソース−ドレイン耐圧が、当該トランジスタの所定のソース−ドレイン耐圧を超えると、当該トランジスタの信頼性が著しく低下してしまう。

【0011】

そこで、本開示は、回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路における最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路、当該レベルシフタ回路を用いる走査回路、当該走査回路を搭載した表示装置、及び、当該表示装置を有する電子機器を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記の目的を達成するために、本開示のレベルシフタ回路は、

第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

ことを特徴としている。

【0013】

本開示のレベルシフタ回路は、最終段にインバータ回路を有する走査回路において、最終段のインバータ回路の前段の回路として用いることができる。また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段の回路として用いる走査回路は、画素が行列状に配置されて成る表示装置、あるいは、固体撮像装置において、各画素を走査する走査回路として搭載することができる。また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段の回路として用いる走査回路を搭載する表示装置は、表示部を備える各種の電子機器において、その表示部として用いることができる。

【0014】

上記構成のレベルシフタ回路において、第1トランジスタ回路と第2トランジスタ回路とが第1固定電源と第2固定電源との間に直列に接続されていることで、一方の電源側のトランジスタ回路である例えば第1トランジスタ回路が動作状態になると、出力端の電圧が第1固定電源の電圧になる。同様に、第3トランジスタ回路と第4トランジスタ回路とが第1固定電源と第2固定電源との間に直列に接続されていることで、一方の電源側のトランジスタ回路である例えば第3トランジスタ回路が動作状態になると、出力端の電圧が第1固定電源の電圧になる。これにより、第2,第4トランジスタ回路には、第1固定電源の電圧と第2固定電源の電圧とが与えられることになる。

【0015】

このとき、他方の電源側の2つのトランジスタ回路である例えば第2,第4トランジスタ回路のダブルゲートトランジスタの共通接続ノードには、スイッチ素子によって第3固定電源の電圧が与えられる。これにより、ダブルゲート構造を構成する2つのトランジスタの各ソース−ドレイン間には、第1固定電源−第2固定電源間の電圧ではなく、第1固定電源−第3固定電源間の電圧と、第3固定電源−第2固定電源間の電圧とが与えられることになる。

【0016】

ここで、第1固定電源−第3固定電源間の電圧、及び、第3固定電源−第2固定電源間の電圧が、第1〜第4トランジスタ回路を構成する各トランジスタのソース−ドレイン耐圧の範囲内の電圧とする。これにより、トランジスタに与えられるソース−ドレイン間電圧がその耐圧の範囲内となり、尚且つ、入力電圧の振幅よりも大きい振幅の出力電圧を導出することができる。

【発明の効果】

【0017】

本開示によれば、トランジスタのソース−ドレイン間電圧をその耐圧の範囲内とし、入力電圧の振幅よりも大きい振幅の出力電圧を導出することができるため、トランジスタのソース−ドレイン耐圧を維持したまま、走査回路における最終段のインバータ回路の入力電圧の振幅を増大させることができる。

【図面の簡単な説明】

【0018】

【図1】本開示の第1実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【図2】一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccの場合の、第1実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図3】一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の、第1実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図4】第1実施形態に係るレベルシフタ回路における2つの入力電圧VIN,VXIN、レベルシフタ回路の出力電圧VA、及び、最終段のインバータ回路の出力電圧VOUTの各波形を示す波形図である。

【図5】本開示の第2実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【図6】一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の、第2実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図7】一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccの場合の、第2実施形態に係るレベルシフタ回路の回路動作の説明に供する動作説明図である。

【図8】第2実施形態に係るレベルシフタ回路における2つの入力電圧VIN,VXIN、レベルシフタ回路の出力電圧VA、及び、最終段のインバータ回路の出力電圧VOUTの各波形を示す波形図である。

【図9】本開示の第3実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【図10】第3実施形態に係るレベルシフタ回路における入力電圧VIN、1段目のレベルシフタ回路の出力電圧VA、2段目のレベルシフタ回路の出力電圧VB、及び、最終段のインバータ回路の出力電圧VOUTの各波形を示す波形図である。

【図11】本開示の有機EL表示装置の構成の概略を示すシステム構成図である。

【図12】画素(画素回路)の具体的な回路構成の一例を示す回路図である。

【図13】書込み走査回路の構成の一例を示すブロック図である。

【発明を実施するための形態】

【0019】

以下、本開示の技術を実施するための形態(以下、「実施形態」と記述する)について図面を用いて詳細に説明する。本開示は実施形態に限定されるものではない。以下の説明において、同一要素又は同一機能を有する要素には同一符号を用いることとし、重複する説明は省略する。尚、説明は以下の順序で行う。

1.本開示のレベルシフタ回路、全般に関する説明

2.第1実施形態に係るレベルシフタ回路

2−1.回路構成

2−2.回路動作

2−3.作用、効果

3.第2実施形態に係るレベルシフタ回路

3−1.回路構成

3−2.回路動作

3−3.作用、効果

4.第3実施形態に係るレベルシフタ回路

5.表示装置(有機EL表示装置)

5−1.システム構成

5−2.画素回路

5−3.走査回路

5−4.その他

6.電子機器

7.本開示の構成

【0020】

<1.本開示のレベルシフタ回路、全般に関する説明>

本開示のレベルシフタ回路は、第1導電型のトランジスタから成る第1,第3トランジスタ回路と、第2導電型のトランジスタから成る第2,第4トランジスタ回路とを有する構成となっている。第1トランジスタ回路と第2トランジスタ回路とは、第1固定電源と第2固定電源との間に直列に接続されている。第3トランジスタ回路と第4トランジスタ回路とは、第1固定電源と第2固定電源との間に直列に接続されている。

【0021】

第1トランジスタ回路と第2トランジスタ回路との共通接続ノードは、これらトランジスタ回路の出力端となる。また、第3トランジスタ回路と第4トランジスタ回路との共通接続ノードは、これらトランジスタ回路の出力端となる。そして、第2トランジスタ回路の入力端には第1入力電圧が与えられ、第4トランジスタ回路の入力端には第2入力電圧が与えられる。第1入力電圧と第2入力電圧とを、逆相の電圧とすることができる。第1トランジスタ回路の入力端が第3,第4トランジスタ回路の共通接続ノードに接続され、第3トランジスタ回路の入力端が第1,第2トランジスタ回路の共通接続ノードに接続されている。

【0022】

そして、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路は、ダブルゲート構造のトランジスタ、即ち、ダブルゲートトランジスタから成る。ここで、第1固定電源側の2つのトランジスタ回路とは第1,第3トランジスタ回路のことであり、第2固定電源側の2つのトランジスタ回路とは第2,第4トランジスタ回路のことである。

【0023】

本開示のレベルシフタ回路は、大きくは、2つの回路形態を採ることができる。第1の回路形態は、第1固定電源が正側電源、第2固定電源が負側電源、第1導電型のトランジスタがPチャネル型のトランジスタ、第2導電型のトランジスタがNチャネル型のトランジスタの形態である。第2の回路形態は、第1固定電源が負側電源、第2固定電源が正側電源、第1導電型のトランジスタがNチャネル型のトランジスタ、第2導電型のトランジスタがPチャネル型のトランジスタの形態である。

【0024】

第1の回路形態を採るときは、第1固定電源の電圧を第1,第2入力電圧の高電圧側の電圧よりも高く設定し、第2固定電源の電圧を第1,第2入力電圧の低電圧側の電圧以下に設定するのが好ましい。また、第2の回路形態を採るときは、第1固定電源の電圧を第1,第2入力電圧の低電圧側の電圧よりも低く設定し、第2固定電源の電圧を第1,第2入力電圧の高電圧側の電圧以上に設定するのが好ましい。

【0025】

本開示のレベルシフタ回路は、第3,第4トランジスタ回路の共通接続ノードに接続される最終段のインバータ回路との組合せで用いることができる。この場合、第1の回路形態では、第1固定電源の電圧を最終段のインバータ回路の正側電源の電圧よりも高く設定し、第2固定電源の電圧を最終段のインバータ回路の負側電源の電圧以下に設定するのが好ましい。また、第2の回路形態では、第1固定電源の電圧を最終段のインバータ回路の負側電源の電圧よりも低く設定し、第2固定電源の電圧を最終段のインバータ回路の正側電源の電圧以上に設定するのが好ましい。

【0026】

そして、本開示のレベルシフタ回路は、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに対して、第3固定電源の電圧を与えるスイッチ素子を有することを特徴としている。

【0027】

第3固定電源の電圧は、第1,第2固定電源の各電圧の間の値、好ましくは、第1,第2固定電源の各電圧の平均値とするのが望ましい。この第3固定電源の電圧を選択的に与えるスイッチ素子は、他方の電源側の2つのトランジスタ回路を構成するトランジスタと同導電型のトランジスタとすることができる。この同導電型のトランジスタは、第1入力電圧または第2入力電圧をゲート入力とする。

【0028】

ここで、第1固定電源−第3固定電源間の電圧、及び、第3固定電源−第2固定電源間の電圧が、第1〜第4トランジスタ回路を構成する各トランジスタのソース−ドレイン耐圧の範囲内の電圧とするのが好ましい。このような電圧設定を行うことにより、第1〜第4トランジスタ回路を構成する各トランジスタに与えられるソース−ドレイン間電圧がその耐圧の範囲内となり、尚且つ、第1,第2入力電圧の振幅よりも大きい振幅の出力電圧を導出することができる。

【0029】

本開示のレベルシフタ回路は、その用途が限定されるものではなく、一般的なレベルシフタ回路として種々の用途に用いることができる。一例として、本開示のレベルシフタ回路は、最終段にインバータ回路を有し、行列状に配置された画素を走査する走査信号を出力する走査回路において、最終段のインバータ回路の前段の回路として用いることができる。

【0030】

また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段回路として用いる走査回路は、電気光学素子を含む画素が行列状に配置されて成る表示装置、あるいは、光電変換素子を含む画素が行列状に配置されて成る固体撮像装置において、各画素を走査する走査回路として用いることができる。この場合、走査回路は、表示パネル上に搭載する形態をとることもできるし、あるいは、ドライバICとして表示パネル外に配する形態をとることもできる。また、本開示のレベルシフタ回路を、最終段のインバータ回路の前段回路として用いる走査回路を搭載する表示装置は、表示部を備える各種の電子機器において、その表示部として用いることができる。

【0031】

以下に、本開示の具体的な実施形態に係るレベルシフタ回路について説明する。

【0032】

<2.第1実施形態>

[2−1.回路構成]

図1は、本開示の第1実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。第1実施形態に係るレベルシフタ回路100Aは、前に述べた第1の回路形態を採っている。すなわち、第1固定電源101を正側電源、第2固定電源102を負側電源とし、第1導電型のトランジスタとしてPチャネル型のトランジスタ(以下、「Pチャネルトランジスタ」と記述する)を用い、第2導電型のトランジスタとしてNチャネル型のトランジスタ(以下、「Nチャネルトランジスタ」と記述する)を用いる。

【0033】

図1において、第1実施形態に係るレベルシフタ回路100Aは、第1トランジスタ回路111、第2トランジスタ回路112、第3トランジスタ回路113、及び、第4トランジスタ回路114の4つのトランジスタ回路から構成されている。第1トランジスタ回路111と第2トランジスタ回路112とは、正側電源である第1固定電源101と負側電源である第2固定電源102との間に直列に接続されている。同様に、第3トランジスタ回路113と第4トランジスタ回路114とは、第1固定電源101と第2固定電源102との間に直列に接続されている。

【0034】

第1固定電源101側の2つのトランジスタ回路、即ち、第1トランジスタ回路111及び第3トランジスタ回路113は、Pチャネルトランジスタから成る。第2固定電源102側の2つのトランジスタ回路、即ち、第2トランジスタ回路112及び第4トランジスタ回路114は、Nチャネルトランジスタから成る。そして、第1固定電源101側の2つのトランジスタ回路111,113、及び、第2固定電源102側の2つのトランジスタ回路112,114が共に、ダブルゲート構造のトランジスタ、即ち、ダブルゲートトランジスタから成る。

【0035】

但し、これは一例に過ぎず、第1固定電源101側の2つのトランジスタ回路111,113及び第2固定電源102側の2つのトランジスタ回路112,114の一方側の2つのトランジスタ回路のみが、ダブルゲートトランジスタから成る構成を採ることも可能である。このように、一方側の2つのトランジスタ回路のみがダブルゲートトランジスタから成るときは、他方側の2つのトランジスタ回路はシングルゲートトランジスタから成る。

【0036】

第1トランジスタ回路111は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP11,P12から成る。PチャネルトランジスタP11のソース電極は、第1固定電源101に接続されている。PチャネルトランジスタP11のドレイン電極とPチャネルトランジスタP12のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P11,P12)の共通接続ノードn11となっている。PチャネルトランジスタP12のドレイン電極は、第1トランジスタ回路111の出力端T11となっている。

【0037】

第2トランジスタ回路112は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN11,N12から成る。NチャネルトランジスタN11のドレイン電極は、第2トランジスタ回路112の出力端T11となっている。第2トランジスタ回路112の出力端T11は、第1トランジスタ回路111の出力端T11でもある。すなわち、PチャネルトランジスタP12のドレイン電極とNチャネルトランジスタN11のドレイン電極とが共通に接続されて第1,第2トランジスタ回路111,112の出力端T11となっている。

【0038】

2つのNチャネルトランジスタN11,N12の共通に接続されたゲート電極は、第2トランジスタ回路112の入力端T12となっている。NチャネルトランジスタN11のソース電極とNチャネルトランジスタN12のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N11,N12)の共通接続ノードn12となっている。NチャネルトランジスタN12のソース電極は、第2固定電源102に接続されている。

【0039】

第3トランジスタ回路113は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP13,P14から成る。PチャネルトランジスタP13のソース電極は、第1固定電源101に接続されている。PチャネルトランジスタP13のドレイン電極とPチャネルトランジスタP14のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P13,P14)の共通接続ノードn13となっている。PチャネルトランジスタP14のドレイン電極は、第3トランジスタ回路113の出力端T13となっている。

【0040】

第4トランジスタ回路114は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN13,N14から成る。NチャネルトランジスタN13のドレイン電極は、第4トランジスタ回路114の出力端T13となっている。第4トランジスタ回路114の出力端T13は、第3トランジスタ回路113の出力端T13でもある。すなわち、PチャネルトランジスタP14のドレイン電極とNチャネルトランジスタN13のドレイン電極とが共通に接続されて第3,第4トランジスタ回路113,114の出力端T13となっている。また、第3,第4トランジスタ回路113,114の出力端T13は、本レベルシフタ回路100Aの出力端でもある。

【0041】

2つのNチャネルトランジスタN13,N14の共通に接続されたゲート電極は、第4トランジスタ回路114の入力端T14となっている。NチャネルトランジスタN13のソース電極とNチャネルトランジスタN14のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N13,N14)の共通接続ノードn14となっている。NチャネルトランジスタN14のソース電極は、第2固定電源102に接続されている。

【0042】

上記構成のレベルシフタ回路100Aにおいて、第2固定電源102側の2つのトランジスタ回路、即ち、第2,第4トランジスタ112,114の各入力端T12,T14には、第1,第2入力電圧VXIN,VINが与えられる。第1,第2入力電圧VXIN,VINは、高電圧側の電圧(高レベル)がVcc、低電圧側の電圧(低レベル)がVssの、互いに逆相の電圧である。

【0043】

この第1,第2入力電圧VXIN,VINに対して、第1固定電源101の電圧は、高電圧側の電圧Vccよりも高い電圧、例えば2Vccに設定され、第2固定電源102の電圧は、低電圧側の電圧Vss以下の電圧、例えば、等しい電圧に設定されている。尚、ここでは、レベルシフタ回路100A、即ち、第1〜第4トランジスタ回路111〜114を構成する各トランジスタのソース−ドレイン耐圧を(Vcc−Vss)として考える。

【0044】

第1トランジスタ回路111の入力端T15、即ち、ダブルゲートトランジスタ(P11,P12)のゲート電極は、第3,第4トランジスタ回路113,114の出力端T13に接続されている。また、第3トランジスタ回路113の入力端T16、即ち、ダブルゲートトランジスタ(P13,P14)のゲート電極は、第1,第2トランジスタ回路111,112の出力端T11に接続されている。

【0045】

上述したように、本実施形態に係るレベルシフタ回路100Aは、第1トランジスタ回路111、第2トランジスタ回路112、第3トランジスタ回路113、及び、第4トランジスタ回路114の4つのトランジスタ回路がダブルゲートトランジスタから成る特徴に加えて、次の点を特徴としている。

【0046】

第1トランジスタ回路111を構成するダブルゲートトランジスタ(P11,P12)の共通接続ノードn11と第3固定電源103との間には、スイッチ素子、例えば、第1トランジスタ回路111を構成するトランジスタと同導電型であるPチャネルトランジスタP15が接続されている。PチャネルトランジスタP15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P11,P12)の共通接続ノードn11に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0047】

PチャネルトランジスタP15は、ゲート電極が第1,第2スイッチ回路111,112の出力端T11に接続されている。そして、PチャネルトランジスタP15は、第2トランジスタ回路112が動作状態のときに、導通(オン)状態となって第3固定電源103の電圧Vmを、第1トランジスタ回路111のダブルゲートトランジスタ(P11,P12)の共通接続ノードn11に与える。ここで、「第2トランジスタ回路112が動作状態のとき」とは、第2トランジスタ回路112を構成するNチャネルトランジスタN11,N12が導通状態のときを言う。

【0048】

第2トランジスタ回路112を構成するダブルゲートトランジスタ(N11,N12)の共通接続ノードn12と第3固定電源103との間には、スイッチ素子、例えば、第2トランジスタ回路112を構成するトランジスタと同導電型であるNチャネルトランジスタN15が接続されている。NチャネルトランジスタN15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N11,N12)の共通接続ノードn12に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0049】

NチャネルトランジスタN15は、ゲート電極に第2入力電圧VINが与えられる。そして、NチャネルトランジスタN15は、第1トランジスタ回路111が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第2トランジスタ回路112のダブルゲートトランジスタ(N11,N12)の共通接続ノードn12に与える。ここで、「第1トランジスタ回路111が動作状態のとき」とは、第1トランジスタ回路111を構成するPチャネルトランジスタP11,P12が導通状態のときを言う。

【0050】

第3トランジスタ回路113を構成するダブルゲートトランジスタ(P13,P14)の共通接続ノードn13と第3固定電源103との間には、スイッチ素子、例えば、第3トランジスタ回路113を構成するトランジスタと同導電型であるPチャネルトランジスタP16が接続されている。PチャネルトランジスタP16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P13,P14)の共通接続ノードn13に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0051】

PチャネルトランジスタP16は、第3,第4スイッチ回路113,114の出力端T13に接続されている。そして、PチャネルトランジスタP16は、第4トランジスタ回路114が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第3トランジスタ回路113のダブルゲートトランジスタ(P13,P14)の共通接続ノードn13に与える。ここで、「第4トランジスタ回路114が動作状態のとき」とは、第4トランジスタ回路114を構成するNチャネルトランジスタN13,N14が導通状態のときを言う。

【0052】

第4トランジスタ回路114を構成するダブルゲートトランジスタ(N13,N14)の共通接続ノードn14と第3固定電源103との間には、スイッチ素子、例えば、第4トランジスタ回路114を構成するトランジスタと同導電型であるNチャネルトランジスタN16が接続されている。NチャネルトランジスタN16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N13,N14)の共通接続ノードn14に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0053】

NチャネルトランジスタN16は、ゲート電極に第1入力電圧VXINが与えられる。そして、NチャネルトランジスタN16は、第3トランジスタ回路113が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第4トランジスタ回路114のダブルゲートトランジスタ(N13,N14)の共通接続ノードn14に与える。ここで、「第3トランジスタ回路113が動作状態のとき」とは、第3トランジスタ回路113を構成するPチャネルトランジスタP13,P14が導通状態のときを言う。

【0054】

ここで、第3固定電源103の電圧Vmとして、第1,第2固定電源101,102の各電圧の間の値、好ましくは、第1,第2固定電源101,102の各電圧2Vcc,Vssの平均値を用いる。本例の場合、Vm=Vccとする。また、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧を、第1〜第4トランジスタ回路111〜114を構成する各トランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内の電圧とする。

【0055】

上記構成のレベルシフタ回路100Aは、その出力端T13、即ち、第3,第4トランジスタ回路113,114の出力端T13に入力端が接続される最終段のインバータ回路200との組合せで用いるのが好ましい。最終段のインバータ回路200は、PチャネルトランジスタP21及びNチャネルトランジスタN21から成るCMOSインバータ回路構成となっている。すなわち、PチャネルトランジスタP21及びNチャネルトランジスタN21は、正側電源201と負側電源202との間に直列に接続されている。

【0056】

そして、本例の場合には、正側電源201の電圧が入力電圧VIN,VXINの高電圧側と同じ電圧Vccに、負側電源202の電圧が入力電圧VIN,VXINの低電圧側と同じ電圧Vssにそれぞれ設定されている。これにより、前段のレベルシフタ回路100Aの第1固定電源101の電圧2Vccは、最終段のインバータ回路200の正側電源201の電圧Vccよりも高く、第2固定電源102の電圧Vssは、最終段のインバータ回路200の負側電源102の電圧Vssと等しくなる。

【0057】

PチャネルトランジスタP21及びNチャネルトランジスタN21のゲート電極同士は、共通に接続されて本インバータ回路200の入力端T21となり、前段のレベルシフタ回路100Aの出力端T13に接続されている。また、PチャネルトランジスタP21及びNチャネルトランジスタN21のドレイン電極同士は、共通に接続されて本インバータ回路200の出力端T22となっている。そして、この出力端T22から、振幅がVcc−Vss、即ち、高電圧側がVcc、低電圧側がVssの出力電圧VOUTが導出される。

【0058】

[2−2.回路動作]

続いて、上記構成の第1実施形態に係るレベルシフタ回路100Aの回路動作について、図2及び図3を用いて説明する。尚、図4には、互いに逆相の2つの入力電圧VIN,VXIN、レベルシフタ回路100Aの出力電圧VA、及び、最終段のインバータ回路200の出力電圧VOUTの各波形を示す。

【0059】

先ず、一方の入力電圧VINが低電圧(低レベル)Vss、他方の入力電圧VXINが高電圧(高レベル)Vccの場合の回路動作について、図2の動作説明図を用いて説明する。

【0060】

一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccのとき、第2トランジスタ回路112のNチャネルトランジスタN11,N12及び第4トランジスタ回路114側のNチャネルトランジスタN16が導通(オン)状態になる。これにより、第3トランジスタ回路113のPチャネルトランジスタP13,P14及び第1トランジスタ回路111側のPチャネルトランジスタP15の各ゲート電位が低レベルVssとなる。

【0061】

この動作により、第3トランジスタ回路113のPチャネルトランジスタP13,P14及び第1トランジスタ回路111側のPチャネルトランジスタP15が導通状態になるため、本レベルシフタ回路100Aの出力電圧VAは第1固定電源101の電圧2Vccになる。このとき、Vm=Vccであることから、第1トランジスタ回路111のダブルゲートトランジスタ(P11,P12)の共通接続ノードn11の電位はVccとなる。また、NチャネルトランジスタN16の閾値電圧をVthとすると、第4トランジスタ回路114のダブルゲートトランジスタ(N13,N14)の共通接続ノードn14の電位はVcc−Vthという値となる。

【0062】

次に、一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の回路動作について、図3の動作説明図を用いて説明する。

【0063】

一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssのとき、第4トランジスタ回路114のNチャネルトランジスタN13,N14及び第2トランジスタ回路112側のNチャネルトランジスタN15が導通状態になる。これにより、第1トランジスタ回路111のPチャネルトランジスタP11,P12及び第3トランジスタ回路113側のPチャネルトランジスタP16の各ゲート電位(本レベルシフタ回路100Aの出力電圧でもある)VAが第1固定電源101の電圧2Vccから第2固定電源102の電圧Vssへと遷移する。

【0064】

第1トランジスタ回路111のPチャネルトランジスタP11,P12のゲート電位が低レベルVssになることで、これらPチャネルトランジスタP11,P12が導通状態になる。これにより、第3トランジスタ回路113のPチャネルトランジスタP13,P14のゲート電位が第1固定電源101の電圧2Vccになるため、これらPチャネルトランジスタP13,P14が非導通(オフ)状態になる。このとき、第3トランジスタ回路113のダブルゲートトランジスタ(P13,P14)の共通接続ノードn13の電位はVccとなる。また、NチャネルトランジスタN15の閾値電圧をVthとすると、第2トランジスタ回路112のダブルゲートトランジスタ(N11,N12)の共通接続ノードn12の電位はVcc−Vthとなる。

【0065】

ここで、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン間電圧について考える。各トランジスタにかかるソース−ドレイン間電圧は、第1固定電源101の電圧2Vcc、第2固定電源102の電圧Vss、及び、第3固定電源103の電圧Vm(=Vcc)の各値によって決定される。そして、前述したように、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧が、各トランジスタのソース−ドレイン耐圧(本例では、Vcc−Vss)の範囲内の電圧となるように各電源電圧の値が設定されている。

【0066】

このような条件の下で上述した回路動作を行うことで、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えつつ、2Vcc−Vssの振幅の出力電圧VAを得ることができる。

【0067】

[2−3.第1実施形態の作用、効果]

第1実施形態に係るレベルシフタ回路100Aは、入力電圧VIN,VXINを高くなる方向にレベルシフト(レベル変換)する作用を為す。そして、このレベルシフタ回路100Aを最終段のインバータ回路200の前段の回路として配する。これにより、最終段のインバータ回路200の抵抗を下げるに当たって、当該インバータ回路200を構成するトランジスタP21,N21のサイズを大きくすることなく、これらトランジスタP21,N21のゲート−ソース間電圧を上げることができる、即ち、インバータ回路200の入力電圧の振幅を増大させることができる。

【0068】

また、第1〜第4トランジスタ回路111〜114をダブルゲートトランジスタによって構成し、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源103の電圧Vmを与えるようにした。

【0069】

具体的には、第2トランジスタ回路112が動作状態のとき、第1トランジスタ回路111のダブルゲートトランジスタ(P11,P12)の共通接続ノードn11に、PチャネルトランジスタP15を介して第3固定電源103の電圧Vmを与える。また、第4トランジスタ回路114が動作状態のとき、第3トランジスタ回路113のダブルゲートトランジスタ(P13,P14)の共通接続ノードn13に、PチャネルトランジスタP16を介して第3固定電源103の電圧Vmを与える。

【0070】

このようにすることで、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えることができる。従って、本レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。

【0071】

この場合、最終段のインバータ回路200に入力される波形の振幅が(2Vcc−Vss)となり、最終段のインバータ回路200を構成するトランジスタP21,N21のゲート−ソース間には、ソース−ドレイン耐圧(Vcc−Vss)を超える電圧がかかることになる。しかし、一般に、トランジスタのゲート−ソース耐圧は、ソース−ドレイン耐圧よりも大きい(高い)。従って、トランジスタP21,N21のゲート−ソース間に、ソース−ドレイン耐圧を超える電圧を印加することができる。そして、トランジスタP21,N21のゲート−ソース間電圧を上げる、即ち、最終段のインバータ回路200の入力電圧の振幅を増大させることによって当該インバータ回路200の抵抗を下げることができる。

【0072】

上述したように、第1実施形態に係るレベルシフタ回路100Aによれば、当該レベルシフタ回路100Aを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。また、最終段のインバータ回路200の入力電圧の振幅をより増大させることにより、当該インバータ200を構成するトランジスタP21,N21のサイズを小さくすることが可能になる。更に、定常状態において貫通電流が流れないため、低消費電力化も可能となる。

【0073】

<3.第2実施形態>

[3−1.回路構成]

図5は、本開示の第2実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。第2実施形態に係るレベルシフタ回路100Bは、前に述べた第2の回路形態を採っている。すなわち、第1固定電源101を負側電源、第2固定電源102を正側電源とし、第1導電型のトランジスタとしてNチャネルトランジスタを用い、第2導電型のトランジスタとしてPチャネルトランジスタを用いる。

【0074】

図5において、第2実施形態に係るレベルシフタ回路100Bは、第1トランジスタ回路211、第2トランジスタ回路212、第3トランジスタ回路213、及び、第4トランジスタ回路214の4つのトランジスタ回路から構成されている。第1トランジスタ回路211と第2トランジスタ回路212とは、負側電源である第1固定電源101と正側電源である第2固定電源102との間に直列に接続されている。同様に、第3トランジスタ回路213と第4トランジスタ回路214とは、第1固定電源101と第2固定電源102との間に直列に接続されている。

【0075】

第1固定電源101側の2つのトランジスタ回路、即ち、第1トランジスタ回路211及び第3トランジスタ回路213は、Nチャネルトランジスタから成る。第2固定電源102側の2つのトランジスタ回路、即ち、第2トランジスタ回路212及び第4トランジスタ回路214は、Nチャネルトランジスタから成る。そして、第1固定電源101側の2つのトランジスタ回路211,213、及び、第2固定電源102側の2つのトランジスタ回路212,214が共に、ダブルゲートトランジスタから成る。

【0076】

但し、これは一例に過ぎず、第1固定電源101側の2つのトランジスタ回路211,213及び第2固定電源102側の2つのトランジスタ回路212,214の一方側の2つのトランジスタ回路のみが、ダブルゲートトランジスタから成る構成を採ることも可能である。一方側の2つのトランジスタ回路のみがダブルゲートトランジスタから成るときは、他方側の2つのトランジスタ回路はシングルゲートトランジスタから成る。

【0077】

第1トランジスタ回路211は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN11,N12から成る。NチャネルトランジスタN11のドレイン電極は、第1トランジスタ回路211の出力端T11となっている。NチャネルトランジスタN11のソース電極とNチャネルトランジスタN12のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N11,N12)の共通接続ノードn11となっている。NチャネルトランジスタN12のソース電極は、第1固定電源101に接続されている。

【0078】

第2トランジスタ回路212は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP11,P12から成る。2つのPチャネルトランジスタP11,P12の共通に接続されたゲート電極は、第2トランジスタ回路212の入力端T12となっている。PチャネルトランジスタP11のソース電極は、第2固定電源102に接続されている。PチャネルトランジスタP11のドレイン電極とPチャネルトランジスタP12のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P11,P12)の共通接続ノードn12となっている。

【0079】

PチャネルトランジスタP12のドレイン電極は、第2トランジスタ回路212の出力端T11となっている。第2トランジスタ回路212の出力端T11は、第1トランジスタ回路211の出力端T11でもある。すなわち、PチャネルトランジスタP12のドレイン電極とNチャネルトランジスタN11のドレイン電極とが共通に接続されて第1,第2トランジスタ回路211,212の出力端T11となっている。

【0080】

第3トランジスタ回路213は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのNチャネルトランジスタN13,N14から成る。NチャネルトランジスタN13のドレイン電極は、第3トランジスタ回路213の出力端T13となっている。NチャネルトランジスタN13のソース電極とNチャネルトランジスタN14のドレイン電極とは共通に接続されて、ダブルゲートトランジスタ(N13,N14)の共通接続ノードn13となっている。NチャネルトランジスタN14のソース電極は、第1固定電源101に接続されている。

【0081】

第4トランジスタ回路214は、ゲート電極同士が共通に接続されたダブルゲート構造の2つのPチャネルトランジスタP13,P14から成る。2つのPチャネルトランジスタP13,P14の共通に接続されたゲート電極は、第4トランジスタ回路214の入力端T14となっている。PチャネルトランジスタP13のソース電極は、第2固定電源102に接続されている。PチャネルトランジスタP13のドレイン電極とPチャネルトランジスタP14のソース電極とは共通に接続されて、ダブルゲートトランジスタ(P13,P14)の共通接続ノードn14となっている。

【0082】

PチャネルトランジスタP14のドレイン電極は、第4トランジスタ回路214の出力端T13となっている。第4トランジスタ回路214の出力端T13は、第3トランジスタ回路213の出力端T13でもある。すなわち、PチャネルトランジスタP14のドレイン電極とNチャネルトランジスタN13のドレイン電極とが共通に接続されて第3,第4トランジスタ回路213,214の出力端T13となっている。また、第3,第4トランジスタ回路213,214の出力端T13は、本レベルシフタ回路100Bの出力端でもある。

【0083】

上記構成のレベルシフタ回路100Bにおいて、第2固定電源102側の2つのトランジスタ回路、即ち、第2,第4トランジスタ212,214の各入力端T12,T14には、第1,第2入力電圧VXIN,VINが与えられる。第1,第2入力電圧VXIN,VINは、高レベルがVcc、低レベルがVssの、互いに逆相の電圧である。

【0084】

この第1,第2入力電圧VXIN,VINに対して、第1固定電源101の電圧は、低電圧側の電圧Vssよりも低い電圧、例えば2Vssに設定され、第2固定電源102の電圧は、高電圧側の電圧Vcc以上の電圧、例えば、等しい電圧に設定されている。尚、ここでは、レベルシフタ回路100B、即ち、第1〜第4トランジスタ回路211〜214を構成する各トランジスタのソース−ドレイン耐圧を(Vcc−Vss)として考える。

【0085】

第1トランジスタ回路211の入力端T15、即ち、ダブルゲートトランジスタ(N11,N12)のゲート電極は、第3,第4トランジスタ回路213,214の出力端T13に接続されている。また、第3トランジスタ回路213の入力端T16、即ち、ダブルゲートトランジスタ(N13,N14)のゲート電極は、第1,第2トランジスタ回路211,212の出力端T11に接続されている。

【0086】

上述したように、本実施形態に係るレベルシフタ回路100Bは、第1トランジスタ回路211、第2トランジスタ回路212、第3トランジスタ回路213、及び、第4トランジスタ回路214の4つのトランジスタ回路がダブルゲートトランジスタから成る特徴に加えて、次の点を特徴としている。

【0087】

第1トランジスタ回路211を構成するダブルゲートトランジスタ(N11,N12)の共通接続ノードn11と第3固定電源103との間には、スイッチ素子、例えば、第1トランジスタ回路211を構成するトランジスタと同導電型であるNチャネルトランジスタN15が接続されている。NチャネルトランジスタN15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N11,N12)の共通接続ノードn11に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0088】

NチャネルトランジスタN15は、ゲート電極が出力端T11に接続されている。そして、NチャネルトランジスタN15は、第2トランジスタ回路212が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第1トランジスタ回路211のダブルゲートトランジスタ(N11,N12)の共通接続ノードn11に与える。ここで、「第2トランジスタ回路212が動作状態のとき」とは、第2トランジスタ回路212を構成するPチャネルトランジスタP11,P12が導通状態のときを言う。

【0089】

第2トランジスタ回路212を構成するダブルゲートトランジスタ(P11,P12)の共通接続ノードn12と第3固定電源103との間には、スイッチ素子、例えば、第2トランジスタ回路212を構成するトランジスタと同導電型であるPチャネルトランジスタP15が接続されている。PチャネルトランジスタP15は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P11,P12)の共通接続ノードn12に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0090】

PチャネルトランジスタP15は、ゲート電極に第2入力電圧VINが与えられる。そして、PチャネルトランジスタP15は、第1トランジスタ回路211が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第2トランジスタ回路212のダブルゲートトランジスタ(P11,P12)の共通接続ノードn12に与える。ここで、「第1トランジスタ回路211が動作状態のとき」とは、第1トランジスタ回路211を構成するNチャネルトランジスタN11,N12が導通状態のときを言う。

【0091】

第3トランジスタ回路213を構成するダブルゲートトランジスタ(N13,N14)の共通接続ノードn13と第3固定電源103との間には、スイッチ素子、例えば、第3トランジスタ回路213を構成するトランジスタと同導電型であるNチャネルトランジスタN16が接続されている。NチャネルトランジスタN16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(N13,N14)の共通接続ノードn13に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0092】

NチャネルトランジスタN16は、ゲート電極が出力端T13に接続されている。そして、NチャネルトランジスタN16は、第4トランジスタ回路214が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第3トランジスタ回路213のダブルゲートトランジスタ(N13,N14)の共通接続ノードn13に与える。ここで、「第4トランジスタ回路214が動作状態のとき」とは、第4トランジスタ回路214を構成するPチャネルトランジスタP13,P14が導通状態のときを言う。

【0093】

第4トランジスタ回路214を構成するダブルゲートトランジスタ(P13,P14)の共通接続ノードn14と第3固定電源103との間には、スイッチ素子、例えば、第4トランジスタ回路214を構成するトランジスタと同導電型であるPチャネルトランジスタP16が接続されている。PチャネルトランジスタP16は、一方のソース/ドレイン電極がダブルゲートトランジスタ(P13,P14)の共通接続ノードn14に接続され、他方のソース/ドレイン電極が第3固定電源103に接続されている。

【0094】

PチャネルトランジスタP16は、ゲート電極に第1入力電圧VXINが与えられる。そして、PチャネルトランジスタP16は、第3トランジスタ回路213が動作状態のときに、導通状態となって第3固定電源103の電圧Vmを、第4トランジスタ回路214のダブルゲートトランジスタ(P13,P14)の共通接続ノードn14に与える。ここで、「第3トランジスタ回路213が動作状態のとき」とは、第3トランジスタ回路213を構成するNチャネルトランジスタN13,N14が導通状態のときを言う。

【0095】

ここで、第3固定電源103の電圧Vmとして、第1,第2固定電源101,102の各電圧の間の値、好ましくは、第1,第2固定電源101,102の各電圧Vcc,2Vssの平均値を用いる。本例の場合、Vm=Vssとする。また、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧を、第1〜第4トランジスタ回路211〜214を構成する各トランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内の電圧とする。

【0096】

上記構成のレベルシフタ回路100Bは、第1実施形態の場合と同様に、最終段のインバータ回路200との組合せで用いるのが好ましい。最終段のインバータ回路200は、正側電源201の電圧が入力電圧VIN,VXINの高電圧側と同じ電圧Vccに、負側電源202の電圧が入力電圧VIN,VXINの低電圧側と同じ電圧Vssにそれぞれ設定されている。従って、前段のレベルシフタ回路100Bの第1固定電源101の電圧2Vssは、最終段のインバータ回路200の負側電源102の電圧Vssよりも低く、第2固定電源102の電圧Vccは、最終段のインバータ回路200の正側電源201の電圧Vccと等しくなる。

【0097】

[3−2.回路動作]

続いて、上記構成の第2実施形態に係るレベルシフタ回路100Bの回路動作について、図6及び図7を用いて説明する。尚、図8には、互いに逆相の2つの入力電圧VIN,VXIN、レベルシフタ回路100Bの出力電圧VB、及び、最終段のインバータ回路200の出力電圧VOUTの各波形を示す。

【0098】

先ず、一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssの場合の回路動作について、図6の動作説明図を用いて説明する。

【0099】

一方の入力電圧VINが高レベルVcc、他方の入力電圧VXINが低レベルVssのとき、第2トランジスタ回路212のPチャネルトランジスタP11,P12及び第4トランジスタ回路214側のPチャネルトランジスタP16が導通状態になる。これにより、第3トランジスタ回路213のNチャネルトランジスタN13,N14及び第1トランジスタ回路211側のNチャネルトランジスタN15の各ゲート電位が高レベルVccとなる。

【0100】

この動作により、第3トランジスタ回路213のNチャネルトランジスタN13,N14及び第1トランジスタ回路211側のNチャネルトランジスタN15が導通状態になるため、本レベルシフタ回路100Bの出力電圧VBは第1固定電源101の電圧2Vssになる。このとき、Vm=Vssであることから、第1トランジスタ回路211のダブルゲートトランジスタ(N11,N12)の共通接続ノードn11の電位はVssとなる。また、PチャネルトランジスタP16の閾値電圧をVthとすると、第4トランジスタ回路214のダブルゲートトランジスタ(P13,P14)の共通接続ノードn14の電位はVss+Vthという値となる。

【0101】

次に、一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccの場合の回路動作について、図7の動作説明図を用いて説明する。

【0102】

一方の入力電圧VINが低レベルVss、他方の入力電圧VXINが高レベルVccのとき、第4トランジスタ回路214のPチャネルトランジスタP13,P14及び第2トランジスタ回路212側のPチャネルトランジスタP15が導通状態になる。これにより、第1トランジスタ回路211のNチャネルトランジスタN11,P12及び第3トランジスタ回路213側のNチャネルトランジスタN16の各ゲート電位(本レベルシフタ回路100Bの出力電圧でもある)VBが第1固定電源101の電圧2Vssから第2固定電源102の電圧Vccへと遷移する。

【0103】

第1トランジスタ回路211のNチャネルトランジスタN11,N12のゲート電位が高レベルVccになることで、これらNチャネルトランジスタN11,N12が導通状態になる。これにより、第3トランジスタ回路213のNチャネルトランジスタN13,N14のゲート電位が第1固定電源101の電圧2Vssになるため、これらNチャネルトランジスタN13,N14が非導通状態になる。このとき、第3トランジスタ回路213のダブルゲートトランジスタ(N13,N14)の共通接続ノードn13の電位はVssとなる。また、PチャネルトランジスタP15の閾値電圧をVthとすると、第2トランジスタ回路212のダブルゲートトランジスタ(P11,P12)の共通接続ノードn12の電位はVss+Vthとなる。

【0104】

ここで、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン間電圧について考える。各トランジスタにかかるソース−ドレイン間電圧は、第1固定電源101の電圧2Vss、第2固定電源102の電圧Vcc、及び、第3固定電源103の電圧Vm(=Vss)の各値によって決定される。そして、前述したように、第1固定電源101−第3固定電源103間の電圧、及び、第3固定電源103−第2固定電源102間の電圧が、各トランジスタのソース−ドレイン耐圧(本例では、Vcc−Vss)の範囲内の電圧となるように各電源電圧の値が設定されている。

【0105】

このような条件の下で上述した回路動作を行うことで、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えつつ、2Vss−Vccの振幅の出力電圧VAを得ることができる。

【0106】

[3−3.第2実施形態の作用、効果]

第2実施形態に係るレベルシフタ回路100Bは、基本的に、第1実施形態に係るレベルシフタ回路100Aと同様の作用、効果を得ることができる。すなわち、最終段のインバータ回路200を構成するトランジスタP21,N21のサイズを大きくすることなく、尚且つ、各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。

【0107】

回路動作上では、次の点で第1実施形態に係るレベルシフタ回路100Aと異なるものの、得られる作用、効果は同じである。

【0108】

具体的には、第2トランジスタ回路212が動作状態のとき、第1トランジスタ回路211のダブルゲートトランジスタ(N11,N12)の共通接続ノードn11に、NチャネルトランジスタN15を介して第3固定電源103の電圧Vmを与える。また、第4トランジスタ回路214が動作状態のとき、第3トランジスタ回路213のダブルゲートトランジスタ(N13,N14)の共通接続ノードn13に、NチャネルトランジスタN16を介して第3固定電源103の電圧Vmを与える。

【0109】

このようにすることで、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン間電圧を、これらトランジスタのソース−ドレイン耐圧(Vcc−Vss)の範囲内に抑えることができる。従って、本レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。

【0110】

上述したように、第2実施形態に係るレベルシフタ回路100Bによれば、第1実施形態に係るレベルシフタ回路100Aと同様の作用、効果を得ることができる。すなわち、レベルシフタ回路100Bを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅を増大させることができる。また、最終段のインバータ回路200の入力電圧の振幅をより増大させることにより、当該インバータ200を構成するトランジスタP21,N21のサイズを小さくすることが可能になる。更に、定常状態において貫通電流が流れないため、低消費電力化も可能となる。

【0111】

<4.第3実施形態>

図9は、本開示の第3実施形態に係るレベルシフタ回路の構成の一例を示す回路図である。

【0112】

図9に示すように、第3実施形態に係るレベルシフタ回路100Cは、第1実施形態に係るレベルシフタ回路100Aと第2実施形態に係るレベルシフタ回路100Bとの組合せから成る。レベルシフタ回路100A及びレベルシフタ回路100Bの配置の順番は任意であるが、本例では、レベルシフタ回路100Aを前段側(1段目)に、レベルシフタ回路100Bを後段側(2段目)に配置する構成を採っている。また、第3実施形態に係るレベルシフタ回路100Cについても、第1,第2実施形態の場合と同様に、最終段のインバータ回路200との組合せで用いるのが好ましい。

【0113】

1段目のレベルシフタ回路100Aでは、正側電源の電圧を2Vccに設定し、負側電源の電圧をVssに設定している。これにより、1段目のレベルシフタ回路100Aの出力電圧VAとして、2Vcc−Vssの振幅の電圧が導出される。また、2段目のレベルシフタ回路100Bでは、正側電源の電圧を2Vccに設定し、負側電源の電圧を2Vssに設定している。これにより、1段目のレベルシフタ回路100Bの出力電圧VBとして、2Vcc−2Vssの振幅の電圧が導出される。

【0114】

図10に、入力電圧VIN、1段目のレベルシフタ回路100Aの出力電圧VA、2段目のレベルシフタ回路100Bの出力電圧VB、及び、最終段のインバータ回路200の出力電圧VOUTの各波形を示す。

【0115】

上述したように、レベルシフタ回路100Cを複数段(本例では、2段)縦続接続の構成とすることで、当該レベルシフタ回路100Cを構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200の入力電圧の振幅をより増大させることができる。これにより、最終段のインバータ回路200を構成するトランジスタP21,N21のサイズをより小さくすることが可能になる。また、定常状態において、貫通電流をより確実に抑えることができる、より低消費電力化を図ることができる。

【0116】

以上説明した、各実施形態に係るレベルシフタ回路100A,100B,100Cは、一般的なレベルシフタ回路として種々の用途に用いることができる他、例えば、最終段にインバータ回路を有する走査回路において、最終段のインバータ回路の前段回路として用いることができる。また、これらレベルシフタ回路100A,100B,100Cを最終段のインバータ回路の前段回路として走査回路(本開示の走査回路)は、電気光学素子を含む画素が行列状に配置されて成る表示装置、あるいは、光電変換素子を含む画素が行列状に配置されて成る固体撮像装置において、各画素を走査する走査回路として用いることができる。

【0117】

以下では、第1,第2,第3実施形態に係るレベルシフタ回路100A,100B,100Cを、最終段のインバータ回路の前段回路として走査回路を搭載する表示装置を本開示の表示装置として説明する。

【0118】

<3.表示装置>

[3−1.システム構成]

図11は、本開示の表示装置、例えば、アクティブマトリクス型表示装置の構成の概略を示すシステム構成図である。

【0119】

アクティブマトリクス型表示装置は、電気光学素子に流れる電流を、当該電気光学素子と同じ画素内に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタによって制御する表示装置である。絶縁ゲート型電界効果トランジスタとしては、典型的には、TFT(Thin Film Transistor:薄膜トランジスタ)が用いられる。

【0120】

ここでは、一例として、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子、例えば有機EL素子を、画素(画素回路)の発光素子として用いるアクティブマトリクス型有機EL表示装置の場合を例に挙げて説明する。

【0121】

図11に示すように、本例に係る有機EL表示装置10は、有機EL素子を含む複数の画素20が行列状に2次元配置されてなる画素アレイ部30と、当該画素アレイ部30の周辺に配置される駆動回路部とを有する構成となっている。駆動回路部は、書込み走査回路40、電源供給走査回路50、及び、信号出力回路60等から成り、画素アレイ部30の各画素20を駆動する。

【0122】

ここで、有機EL表示装置10がカラー表示対応の場合は、カラー画像を形成する単位となる1つの画素(単位画素)は複数の副画素(サブピクセル)から構成され、この副画素の各々が図11の画素20に相当することになる。より具体的には、カラー表示対応の表示装置では、1つの画素は、例えば、赤色(Red;R)光を発光する副画素、緑色(Green;G)光を発光する副画素、青色(Blue;B)光を発光する副画素の3つの副画素から構成される。

【0123】

但し、1つの画素としては、RGBの3原色の副画素の組み合わせに限られるものではなく、3原色の副画素に更に1色あるいは複数色の副画素を加えて1つの画素を構成することも可能である。より具体的には、例えば、輝度向上のために白色(White;W)光を発光する副画素を加えて1つの画素を構成したり、色再現範囲を拡大するために補色光を発光する少なくとも1つの副画素を加えて1つの画素を構成したりすることも可能である。

【0124】

画素アレイ部30には、m行n列の画素20の配列に対して、行方向(画素行に沿った方向/画素行の画素の配列方向)に沿って走査線311〜31mと電源供給線321〜32mとが画素行毎に配線されている。更に、m行n列の画素20の配列に対して、列方向(画素列に沿った方向/画素列の画素の配列方向)に沿って信号線331〜33nが画素列毎に配線されている。

【0125】

走査線311〜31mは、書込み走査回路40の対応する行の出力端にそれぞれ接続されている。電源供給線321〜32mは、電源供給走査回路50の対応する行の出力端にそれぞれ接続されている。信号線331〜33nは、信号出力回路60の対応する列の出力端にそれぞれ接続されている。

【0126】

画素アレイ部30は、通常、ガラス基板などの透明絶縁基板上に形成されている。これにより、有機EL表示装置10は、平面型(フラット型)のパネル構造となっている。画素アレイ部30の各画素20の駆動回路は、アモルファスシリコンTFTまたは低温ポリシリコンTFTを用いて形成することができる。

【0127】

書込み走査回路40は、クロックパルスckに同期してスタートパルスspを順にシフト(転送)するシフトレジスタ回路等によって構成されている。この書込み走査回路40は、画素アレイ部30の各画素20への映像信号の信号電圧の書込みに際し、走査線31(311〜31m)に対して書込み走査信号WS(WS1〜WS m)を順次供給することによって画素アレイ部30の各画素20を行単位で順番に走査(線順次走査)する。

【0128】

電源供給走査回路50は、クロックパルスckに同期してスタートパルスspを順にシフトするシフトレジスタ回路等によって構成されている。この電源供給走査回路50は、書込み走査回路40による線順次走査に同期して、第1電源電位Vccpと当該第1電源電位Vccpよりも低い第2電源電位Viniとで切り替わることが可能な電源電位DS(DS1〜DSm)を電源供給線32(321〜32m)に供給する。電源電位DSのVccp/Viniの切替えにより、画素20の発光/非発光の制御が行なわれる。

【0129】

信号出力回路60は、信号供給源(図示せず)から供給される輝度情報に応じた映像信号の信号電圧(以下、単に「信号電圧」と記述する場合もある)Vsigと基準電圧Vofsとを選択的に出力する。ここで、基準電圧Vofsは、映像信号の信号電圧Vsigの基準となる電位(例えば、映像信号の黒レベルに相当する電位)である。

【0130】

信号出力回路60から出力される信号電圧Vsig/基準電圧Vofsは、信号線33(331〜33n)を介して画素アレイ部30の各画素20に対して、書込み走査回路40による走査によって選択された画素行の単位で書き込まれる。すなわち、信号出力回路60は、信号電圧Vsigを行(ライン)単位で書き込む線順次書込みの駆動形態を採っている。

【0131】

[3−2.画素回路]

図12は、画素(画素回路)20の具体的な回路構成の一例を示す回路図である。画素20の発光部は、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子である有機EL素子21から成る。

【0132】

図12に示すように、画素20は、有機EL素子21と、有機EL素子21に電流を流すことによって当該有機EL素子21を駆動する駆動回路とによって構成されている。有機EL素子21は、全ての画素20に対して共通に配線された共通電源供給線34にカソード電極が接続されている。

【0133】

有機EL素子21を駆動する駆動回路は、駆動トランジスタ22、書込みトランジスタ23、及び、保持容量24を有する構成となっている。駆動トランジスタ22及び書込みトランジスタ23としてNチャネル型のTFTを用いることができる。但し、ここで示した、駆動トランジスタ22及び書込みトランジスタ23の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。

【0134】

駆動トランジスタ22は、一方の電極(ソース/ドレイン電極)が有機EL素子21のアノード電極に接続され、他方の電極(ソース/ドレイン電極)が電源供給線32(321〜32m)に接続されている。

【0135】

書込みトランジスタ23は、一方の電極(ソース/ドレイン電極)が信号線33(331〜33n)に接続され、他方の電極(ソース/ドレイン電極)が駆動トランジスタ22のゲート電極に接続されている。また、書込みトランジスタ23のゲート電極は、走査線31(311〜31m)に接続されている。

【0136】

駆動トランジスタ22及び書込みトランジスタ23において、一方の電極とは、ソース/ドレイン領域に電気的に接続された金属配線を言い、他方の電極とは、ドレイン/ソース領域に電気的に接続された金属配線を言う。また、一方の電極と他方の電極との電位関係によって一方の電極がソース電極ともなればドレイン電極ともなり、他方の電極がドレイン電極ともなればソース電極ともなる。

【0137】

保持容量24は、一方の電極が駆動トランジスタ22のゲート電極に接続され、他方の電極が駆動トランジスタ22の他方の電極、及び、有機EL素子21のアノード電極に接続されている。

【0138】

上記構成の画素20において、書込みトランジスタ23は、書込み走査回路40から走査線31を通してゲート電極に印加されるHighアクティブの書込み走査信号WSに応答して導通状態となる。これにより、書込みトランジスタ23は、信号線33を通して信号出力回路60から供給される、輝度情報に応じた映像信号の信号電圧Vsigまたは基準電圧Vofsをサンプリングして画素20内に書き込む。書込みトランジスタ23によって書き込まれた信号電圧Vsigまたは基準電圧Vofsは、駆動トランジスタ22のゲート電極に印加されるとともに保持容量24に保持される。

【0139】

駆動トランジスタ22は、電源供給線32(321〜32m)の電源電位DSが第1電源電位Vccpにあるときには、一方の電極がドレイン電極、他方の電極がソース電極となって飽和領域で動作する。これにより、駆動トランジスタ22は、電源供給線32から電流の供給を受けて有機EL素子21を電流駆動にて発光駆動する。より具体的には、駆動トランジスタ22は、飽和領域で動作することにより、保持容量24に保持された信号電圧Vsigの電圧値に応じた電流値の駆動電流を有機EL素子21に供給し、当該有機EL素子21を電流駆動することによって発光させる。

【0140】

駆動トランジスタ22は更に、電源電位DSが第1電源電位Vccpから第2電源電位Viniに切り替わったときには、一方の電極がソース電極、他方の電極がドレイン電極となってスイッチングトランジスタとして動作する。これにより、駆動トランジスタ22は、有機EL素子21への駆動電流の供給を停止し、有機EL素子21を非発光状態にする。すなわち、駆動トランジスタ22は、有機EL素子21の発光/非発光を制御するトランジスタとしての機能をも併せ持っている。

【0141】

この駆動トランジスタ22のスイッチング動作により、有機EL素子21が非発光状態となる期間(非発光期間)を設け、有機EL素子21の発光期間と非発光期間の割合(デューティ)を制御することができる。このデューティ制御により、1表示フレーム期間に亘って画素が発光することに伴う残像ボケを低減できるために、特に、動画の画品位をより優れたものとすることができる。

【0142】

電源供給走査回路50から電源供給線32を通して選択的に供給される第1,第2電源電位Vccp,Viniのうち、第1電源電位Vccpは有機EL素子21を発光駆動する駆動電流を駆動トランジスタ22に供給するための電源電位である。また、第2電源電位Viniは、有機EL素子21に対して逆バイアスを掛けるための電源電位である。この第2電源電位Viniは、基準電圧Vofsよりも低い電位、例えば、駆動トランジスタ22の閾値電圧をVthとするときVofs−Vthよりも低い電位、好ましくは、Vofs−Vthよりも十分に低い電位に設定される。

【0143】

[3−3.走査回路]

以上説明した有機EL表示装置10において、画素アレイ部30の周辺回路である書込み走査回路40や電源供給走査回路50の最終段のインバータ回路の前段回路として、先述した第1,第2,第3実施形態に係るレベルシフタ回路100A,100B,100Cを用いることができる。

【0144】

ここでは、一例として、第1,第2,第3実施形態に係るレベルシフタ回路100A,100B,100Cを、書込み走査回路40の最終段のインバータ回路の前段回路として用いる場合を例に挙げて説明する。

【0145】

図13は、書込み走査回路40の構成の一例を示すブロック図である。

【0146】

図13に示すように、書込み走査回路40は、例えば、シフトレジスタ回路41、ロジック回路群42、レベルシフタ回路群43、及び、最終段のインバータ回路群44によって構成されている。シフトレジスタ回路41は、画素アレイ部30の行数mに対応した段数のシフト段(転送段/単位回路)が縦続接続された構成となっており、クロックパルスckに同期してスタートパルスspを順にシフトし、各シフト段から順次シフトパルスを出力する。

【0147】

ロジック回路群42、レベルシフタ回路群43、及び、インバータ回路群44は各々、画素アレイ部30の行数mに対応した数のロジック回路421〜42m、レベルシフタ回路431〜43m、及び、最終段のインバータ回路441〜44mから成る。

【0148】

ロジック回路群42の各ロジック回路421〜42mは、シフトレジスタ回路41の対応するシフト段から出力されるシフトパルスを、所定のタイミングの走査パルスにタイミング調整する。レベルシフタ回路群43の各レベルシフタ回路431〜43mは、論理レベルの走査パルスを、それよりも高いレベルの走査パルスにレベルシフト(レベル変換)する。最終段のインバータ回路群44の各インバータ回路441〜44mは、レベルシフト後の走査パルスを、極性反転して書込み走査信号(パルス)WS1〜WS mとして画素アレイ部30の走査線311〜31 mに供給する。

【0149】

上記構成の書込み走査回路40において、その最終段段のインバータ回路群44のインバータ回路441〜44mの各々として、先述した各実施形態に係るレベルシフタ回路100A,100B,100Cを用いることができる。これらレベルシフタ回路100A,100B,100Cは、先述したように、当該レベルシフタ回路を構成する各トランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路200に入力する電圧の振幅を増大させることができる。

【0150】

そして、最終段のインバータ回路200を構成するトランジスタP21,N21のゲート−ソース間電圧を上げ、最終段のインバータ回路200の抵抗(即ち、トランジスタP21,N21のオン抵抗)を下げることで、表示パネル70の大型化が可能になる。より具体的には、表示パネル70の大型化によって走査線311〜31mの負荷が大きくなり、その負荷の影響で書込み走査パルスWS1〜WS mの波形が鈍ってしまう訳であるが、最終段のインバータ回路200の抵抗が下がることにより、負荷の影響を最小限に抑えることができる。従って、表示パネル70の大型化が可能になる。

【0151】

また、最終段のインバータ回路200の入力電圧の振幅をより増大させることで、当該インバータ200を構成するトランジスタP21,N21のサイズを小さくすることが可能になる。これにより、レベルシフタ回路100A,100B,100Cの回路規模、ひいては、これらレベルシフタ回路100A,100B,100Cを画素アレイ部30の画素行の行数分を有する書込み走査回路40や電源供給走査回路50の回路規模の縮小化を図ることができる。

【0152】

その結果、書込み走査回路40や電源供給走査回路50を、例えば図11に示すように、画素アレイ部30と同じ表示パネル70上に搭載して成る有機EL表示装置にあっては、表示パネル70の狭額縁化が可能になる。また、書込み走査回路40や電源供給走査回路50をドライバICとして表示パネル70外に配する構成を採る有機EL表示装置にあっては、当該ドライバICの小型化を図ることができる。

【0153】

[3−4.その他]

上述した有機EL表示装置では、画素20が2つのNチャネルのトランジスタ22,23及び1つの保持容量24から成る回路構成の場合を例に挙げて説明したが、画素20としてはこの回路構成のものに限られるものではない。すなわち、例えば、駆動トランジスタ22としてPチャネル型のTFTを用いた回路構成や、有機EL素子21の容量不足分を補い、保持容量24に対する映像信号の書込みゲインを高めるための補助容量を有する回路構成の画素20であってもよい。更には、基準電圧Vofsや第2電源電位Viniを選択的に書き込むためのスイッチングトランジスタなどを別途有する回路構成の画素20などであってもよい。

【0154】

また、上記の適用例では、画素20の電気光学素子として、有機EL素子を用いた有機EL表示装置に適用した場合を例に挙げて説明したが、本開示の技術はこの適用例に限られるものではない。具体的には、本開示の技術は、無機EL素子、LED素子、半導体レーザー素子など、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子(発光素子)を用いた表示装置の他、液晶表示装置やプラズマ表示装置など、走査回路を有する表示装置全般に対して適用可能である。更には、表示装置に限らず、固体撮像装置など、走査回路を有する装置全般に対して適用可能である。

【0155】

<4.電子機器>

以上説明した本開示のバッファ回路を出力段に用いる走査回路を搭載する表示装置は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示部(表示装置)として用いることが可能である。

【0156】

先述した各実施形態の説明から明らかなように、本開示のレベルシフタ回路を最終段のインバータ回路の前段回路として用いる走査回路は、例えば、画素アレイ部と同じ表示パネルに搭載される表示装置にあっては、表示パネルの狭額縁化を図ることができる。従って、表示部を有するあらゆる分野の電子機器において、その表示部として、本開示のレベルシフタ回路を最終段のインバータ回路の前段回路として用いる走査回路を搭載する表示装置を用いることで、電子機器本体の小型化を図ることができる。

【0157】

これらの電子機器としては、例えば、テレビジョンセット、デジタルカメラ、ビデオカメラ等の他、PDA(Personal Digital Assistant)、ゲーム機、ノート型パーソナルコンピュータ、電子書籍等の携帯情報機器、携帯電話機等の携帯通信機器などを例示することができる。

【0158】

<5.本開示の構成>

尚、本開示は以下のような構成を採ることができる。

(1)第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

レベルシフタ回路。

(2)第1固定電源−第3固定電源間の電圧及び第3固定電源−第2固定電源間の電圧は、前記第1乃至第4トランジスタ回路を構成する各トランジスタのソース−ドレイン耐圧の範囲内の電圧である

前記(1)に記載のレベルシフタ回路。

(3)第1入力電圧と第2入力電圧とは互いに逆相の電圧である

前記(1)または前記(2)に記載のレベルシフタ回路。

(4)第3固定電源の電圧は、第1固定電源及び第2固定電源の各電圧の間の値である

前記(1)から前記(3)のいずれかに記載のレベルシフタ回路。

(5)第3固定電源の電圧は、第1固定電源及び第2固定電源の各電圧の平均値である

前記(4)に記載のレベルシフタ回路。

(6)前記スイッチ素子は、前記他方の電源側の2つのトランジスタ回路を構成するトランジスタと同導電型のトランジスタである

前記(1)から前記(5)のいずれかに記載のレベルシフタ回路。

(7)前記スイッチ素子は、第1入力電圧または第2入力電圧をゲート入力とする

前記(1)から前記(6)のいずれかに記載のレベルシフタ回路。

(8)前記第3,第4トランジスタ回路の共通接続ノードには最終段のインバータ回路が接続されている

前記(1)から前記(7)のいずれかに記載のレベルシフタ回路。

(9)第1固定電源は正側電源、第2固定電源は負側電源であり、

第1導電型のトランジスタはPチャネル型のトランジスタ、第2導電型のトランジスタはNチャネル型のトランジスタである

前記(1)から前記(8)のいずれかに記載のレベルシフタ回路。

(10)第1固定電源の電圧は、第1,第2入力電圧の高電圧側の電圧よりも高く、

第2固定電源の電圧は、第1,第2入力電圧の低電圧側の電圧以下である

前記(9)に記載のレベルシフタ回路。

(11)第1固定電源の電圧は、前記最終段のインバータ回路の正側電源の電圧よりも高く、

第2固定電源の電圧は、前記最終段のインバータ回路の負側電源の電圧と等しい

前記(9)に記載のレベルシフタ回路。

(12)第1固定電源は負側電源、第2固定電源は正側電源であり、

第1導電型のトランジスタはNチャネル型のトランジスタ、第2導電型のトランジスタはPチャネル型のトランジスタである

前記(1)から前記(8)のいずれかに記載のレベルシフタ回路。

(13)第1固定電源の電圧は、第1,第2入力電圧の低電圧側の電圧よりも低く、

第2固定電源の電圧は、第1,第2入力電圧の高電圧側の電圧以上である

前記(12)に記載のレベルシフタ回路。

(14)第1固定電源の電圧は、前記最終段のインバータ回路の負側電源の電圧よりも低く、

第2固定電源の電圧は、前記最終段のインバータ回路の正側電源の電圧と等しい

前記(12)に記載のレベルシフタ回路。

(15)最終段にインバータ回路を、当該インバータ回路の前段にレベルシフタ回路を有し、

前記レベルシフタ回路は、

第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

走査回路。

(16)電気光学素子を含む画素が行列状に配置されて成る画素アレイ部と、

最終段にインバータ回路を、当該インバータ回路の前段にレベルシフタ回路を有し、前記画素アレイ部の各画素を走査する走査回路と

を備え、

前記レベルシフタ回路は、

第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、第1導電型のトランジスタから成る第3トランジスタ回路と第2導電型のトランジスタから成る第4トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続されており、

前記第2トランジスタ回路の入力端には第1入力電圧が与えられ、前記第4トランジスタ回路の入力端には第2入力電圧が与えられ、

前記第1トランジスタ回路の入力端が前記第3,第4トランジスタ回路の出力端に接続され、前記第3トランジスタ回路の入力端が前記第1,第2トランジスタ回路の出力端に接続されており、

第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成り、

一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路の前記ダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を有する

表示装置。