レーダビデオ表示装置

【課題】本発明の課題は、レーダビデオの特性上必要なビデオデータの減光処理、高輝度の点を優先的に描画する為の処理をGPU処理で行うことにより、CPU処理の負荷を大幅に軽減したレーダビデオ表示装置を提供することにある。

【解決手段】本発明は、CPUにより受信したアジマス分のデータをメインメモリからテクスチャメモリに送る処理をし、GPUにおいて、テクスチャメモリから座標、輝度、更新時間の描画頂点情報が入力され、更新時間と現在時間の差で輝度に対して減光計算を行い、減光計算を行った1レンジ分解能分のデータの輝度の階調情報を座標軸のZとして3次元化すると共に、描画頂点情報の3次元の座標値と輝度からレンダリング処理を行って2次元の画像データに変換する処理をする。

【解決手段】本発明は、CPUにより受信したアジマス分のデータをメインメモリからテクスチャメモリに送る処理をし、GPUにおいて、テクスチャメモリから座標、輝度、更新時間の描画頂点情報が入力され、更新時間と現在時間の差で輝度に対して減光計算を行い、減光計算を行った1レンジ分解能分のデータの輝度の階調情報を座標軸のZとして3次元化すると共に、描画頂点情報の3次元の座標値と輝度からレンダリング処理を行って2次元の画像データに変換する処理をする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンピュータグラフィックスによってレーダビデオの描画を行うレーダビデオ表示装置に関する。

【背景技術】

【0002】

近年、コンピュータ・グラフィックス・システムの発展により、レーダビデオの描画処理をソフトウェア制御で高速に行うことが可能になっているが、レーダビデオの特性上必要な、描画したビデオデータの減光処理、高輝度の点を優先的に描画する為の処理、レーダ位置からの極座標で扱われるビデオデータの画面画素へ対応させる座標変換処理などをソフトウェアによるCPU(Central Processing Unit:演算処理装置)処理にて行う必要があった。この為、CPU処理の負荷が発生していた。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−134224号公報

【特許文献2】特開2009−156709号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来技術では、レーダビデオ表示装置をソフトウェアを使用してCPUで実現した場合、減光処理、高輝度の点を優先的に描画する表示処理を行う為にCPU処理の負荷が発生していた。その為に表示分解能を下げて処理を行ったり、専用のハードウェアを使用して処理を行う必要があった。

【0005】

そこで、本発明の課題は、レーダビデオの特性上必要なビデオデータの減光処理、高輝度の点を優先的に描画する為の処理をGPU(Graphics Processing Unit:描画処理装置)処理で行うことにより、CPU処理の負荷を大幅に軽減した描画を可能とするレーダビデオ表示装置を提供することにある。

【課題を解決するための手段】

【0006】

上記の課題を解決するために、本発明のレーダビデオ表示装置は、レーダ装置からのアナログデータを信号処理装置で変換したデジタルデータが受信される送受信モジュールと、前記送受信モジュールに接続され、座標、輝度の描画頂点情報が初期化されるメインメモリと、前記メインメモリに接続され、座標、輝度、更新時間の描画頂点情報が初期化されるテクスチャメモリと、前記メインメモリ上の該当するアジマスの描画頂点情報の各レンジの輝度情報を前記送受信モジュールで受信したデジタルデータの輝度値を使用して更新すると共に、前記メインメモリの輝度の描画頂点情報を取り出して更新時間を付加して対応する前記テクスチャメモリ上の輝度、更新時間の描画頂点情報を更新するCPUと、前記テクスチャメモリから座標、輝度、更新時間の描画頂点情報が入力され、更新時間と現在時間の差で輝度に対して減光計算を行い、減光計算を行った1レンジ分解能分のデータの輝度の階調情報を座標軸のZとして3次元化すると共に、描画頂点情報の3次元の座標値と輝度からレンダリング処理を行って2次元の画像データに変換するGPUと、前記GPUから2次元の画像データが書き込まれるフレームメモリと、前記フレームメモリからの2次元の画像データが入力され、レーダビデオの映像が表示されるモニタとを具備することを特徴とするものである。

【発明の効果】

【0007】

本発明のレーダビデオ表示装置は、ソフトウェア処理によるCPU負荷を発生させることなく、コンピュータグラフィックスにおいて減光処理、高輝度の点を優先的に描画する為の処理をGPU処理で実現したレーダ表示を行うことを可能とする。

【図面の簡単な説明】

【0008】

【図1】本発明の実施形態に係るレーダビデオ表示システムを示す構成説明図である。

【図2】本発明の実施形態に係るレーダビデオ表示装置を示す構成説明図である。

【図3】本発明の実施形態に係る頂点データの定義方法を示す説明図である。

【図4】本発明の実施形態に係るモニタの表示画面のピクセル数とレンジ分解能を示す説明図である。

【図5】本発明の実施形態に係る頂点データを示す説明図であり、(a)は頂点データの集合体、(b)は(a)のB部の1アジマス分解能分のデータ、(c)は(a)のC部の1アジマス分解能分のデータである。

【図6】本発明の実施形態に係るレーダビデオ表示装置の初期化を示す構成説明図である。

【図7】本発明の実施形態に係るレーダビデオ表示装置のデータ受信、メインメモリ更新処理を示す構成説明図である。

【図8】本発明の実施形態に係るレーダビデオ表示装置のテクスチャメモリ更新処理を示す構成説明図である。

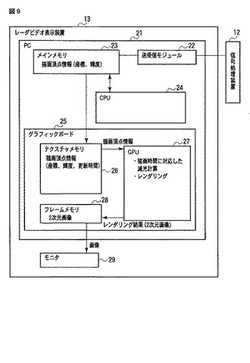

【図9】本発明の実施形態に係るレーダビデオ表示装置の描画更新処理を示す構成説明図である。

【発明を実施するための形態】

【0009】

以下、本発明の実施の形態について、詳細に説明する。図中、同一部分は同一符号を付して説明する。

【0010】

図1は本発明の実施形態に係るレーダビデオ表示システムを示す構成説明図である。図において、11はレーダ装置、12は信号処理装置、13はレーダビデオ表示装置である。

【0011】

図1に示すように、レーダ装置11はレーダアンテナ14がアジマス方向に回転しながら定期的に走査を行い、それぞれのレンジ方向と、距離によるゲイン値のアナログデータを信号処理装置12に出力する。信号処理装置12はレーダ装置11から入力されたアナログデータをデジタルデータに変換してレーダビデオ表示装置13に出力する。レーダビデオ表示装置13は信号処理装置12から入力されたデジタルデータを受信しながらアジマス単位で更新して表示する。また、レーダビデオ表示装置13は描画時間経過と共に減光させる減光処理、高輝度の点を優先的に描画する表示処理を実現する。

【0012】

図2は本発明の実施形態に係るレーダビデオ表示装置を示す構成説明図である。図において、21はPC(パソコン)、22は送受信モジュール、23はメインメモリ、24はCPU、25はグラフィックボード、26はテクスチャメモリ、27はGPU、28はフレームメモリ、29はモニタである。

【0013】

すなわち、信号処理装置12には送受信モジュール22を介してメインメモリ23が接続され、メインメモリ23にはCPU24及びテクスチャメモリ26が接続される。テクスチャメモリ26はGPU27に接続され、GPU27はフレームメモリ28を介してモニタ29に接続される。テクスチャメモリ26、GPU27、フレームメモリ28はグラフィックボード25に搭載され、グラフィックボード25、送受信モジュール22、メインメモリ23、CPU24はPC21を構成し、PC21、モニタ29はレーダビデオ表示装置13を構成する。

【0014】

図3は本発明の実施形態に係る頂点データの定義方法を示す説明図である。図3(a)はレーダ装置11においてレーダアンテナ14の走査を示し、アナログデータが得られる。図3(b)はレーダ装置11で得られたアナログデータをデジタルデータに変換したデジタルデータを示し、各ゲイン値を最終的に輝度として表示する。図3(c)はアジマス、レンジで分割されたデータを頂点の集合体として定義する。図3(d)は図3(c)の1アジマス分解能分のデータである。アジマス分解能はアジマス方向の分割数である。図3(e)は図3(d)の1レンジ分解能分のデータ(ポリゴンデータ)である。レンジ分解能はレンジ方向の分割数である。

【0015】

図4は本発明の実施形態に係るモニタの表示画面のピクセル数とレンジ分解能を示す説明図である。図4に示すように、縦方向のピクセル数をP、横方向のピクセル数をWとし、レンジ分解能RをR>P,R>Wと設定することにより、1レンジ分解能分の長さが最終的な表示で1ピクセル以内に収まるので、1レンジ分解能分のデータを直線として扱っても、抜けの無い画像として処理できる。すなわち、レンジ分解能Rを画面のピクセル数より細かく設定することで、レンジ間で描画抜けが発生することが無い。

【0016】

図5は本発明の実施形態に係る頂点データを示す説明図であり、(a)は図3(c)と同じ頂点データの集合体、(b)は(a)のB部の1アジマス分解能分のデータ、(c)は(a)のC部の1アジマス分解能分のデータである。図5において、各頂点が保持するデータを以下のように定義する。

【0017】

座標(X[a][r][p],Y[a][r][p])

輝度G[a][r]

更新時間T[a]

a=(0〜A−1)

r=(0〜R−1)

p=(0〜1)

ここで、Aはアジマス分解能、Rはレンジ分解能である。

【0018】

すなわち、それぞれの頂点データに輝度情報、更新時間情報を保持させる。1レンジ分解能分のデータを構成する各頂点データは、共通の輝度情報と更新時間情報を保持させる。

【0019】

図6は本発明の実施形態に係るレーダビデオ表示装置の初期化を示す構成説明図である。すなわち、CPU24は、レーダビデオ表示装置13を含むシステムの初期化時に、メインメモリ23に描画頂点情報(座標、輝度)、テクスチャメモリ26に描画頂点情報(座標、輝度、更新時間)のバッファを確保して初期化した後、CPU24で描画頂点座標の座標位置の計算を行ってメインメモリ23、テクスチャメモリ26の描画頂点情報の座標を更新する。このように、CPU24は初期化時に描画頂点情報の設定処理をする。

【0020】

図7は本発明の実施形態に係るレーダビデオ表示装置のデータ受信、メインメモリ更新処理を示す構成説明図である。すなわち、信号処理装置12は、レーダ装置11のレーダ走査毎にアジマス単位でデジタルデータを定期的にレーダビデオ表示装置13へ送信する。レーダビデオ表示装置13は、送受信モジュール22でアジマス単位に分割されたデジタルデータを受信して、CPU24によってメインメモリ23上の該当するアジマスの描画頂点情報の各レンジの輝度情報を、前記送受信モジュール22で受信したデジタルデータの輝度値を使用して更新する。このように、CPU24は描画頂点毎の輝度情報を設定する処理をする。

【0021】

図8は本発明の実施形態に係るレーダビデオ表示装置のテクスチャメモリ更新処理を示す構成説明図である。すなわち、CPU24によって定期的にテクスチャメモリ26の更新処理を行い、前回のテクスチャメモリ26の更新処理を行った時から変更された分のメインメモリ23の描画頂点情報(輝度)を取り出して更新時間を付加し、対応するテクスチャメモリ26上の描画頂点情報(輝度、更新時間)を更新する。このように、CPU24は描画頂点毎にデータ更新時間を設定する処理をし、レーダ装置11のレーダ走査のスイープが通過した場所の輝度情報と更新時間を保持させる。

【0022】

図9は本発明の実施形態に係るレーダビデオ表示装置の描画更新処理を示す構成説明図である。すなわち、CPU24で定期的に描画更新処理を行い、グラフィックボード25上にあるOpenGLとシェーダ言語を利用したGPU27にはテクスチャメモリ26から描画頂点情報(座標、輝度、更新時間)が入力される。グラフィックボード25上にあるOpenGLとシェーダ言語を利用したGPU27によって、レーダ装置11のレーダ走査のスイープが通過した時の更新時間と現在時間の差(経過時間)を計算して、輝度に対して経過時間に対応した減光量の計算を行う。減光計算を行った輝度を階調情報として1レンジ分解能分のデータ(ポリゴンデータ)に輝度として設定する。同様に1レンジ分解能分のデータ(ポリゴンデータ)の輝度の階調情報を座標値のZとして設定して3次元化する。

【0023】

描画頂点情報の3次元の座標値と輝度から、グラフィックボード25上にあるOpenGLとシェーダ言語を利用したGPU27によってレンダリング処理を行って2次元の画像データに変換してフレームメモリ28へ書き込む。フレームメモリ28から2次元の画像データがモニタ29へ出力されることで、レーダビデオの映像がモニタ29に表示される。このように、GPU27でのレンダリング処理により、3次元空間での表示を2次元空間へ射影する。また、モニタ29は減光処理、高輝度の点を優先的に描画する処理を実現してレーダビデオ表示する。

【0024】

以上のように、CPU24の行う処理は、受信したアジマス分のデータをメインメモリ23からテクスチャメモリ26に送るだけであり、全データに対する減光処理、2次元画像への変換処理は全てGPU27で行うこととなる。これによりCPU24の処理負荷を抑えてレーダビデオの表示を行うことが出来る。

【0025】

また、GPU27により輝度の階調情報を座標値のZとして設定して3次元化することにより、輝度の高い1レンジ分解能分のデータ(ポリゴンデータ)が手前に見えるようになる。それを2次元に変換することにより輝度の高い1レンジ分解能分のデータ(ポリゴンデータ)が優先的に描画されるようになり、輝度の高いデータが暗いデータに上書きされて消えてしまうことを回避できる。

【0026】

以上説明したように本発明によれば、ビデオデータの1分解能分のデータをOpenGLの頂点で囲まれるポリゴンデータとして扱い、それぞれのポリゴンデータにOpenGLで設定した座標系の3次元の座標(位置)情報、輝度情報、更新(描画)時間情報を保持させる。

【0027】

また、CPU側ではレーダ装置のレーダ走査のスイープが通過した場所の各ポリゴンデータの輝度情報、更新(描画)時間を更新する。描画した時間経過によってGPU側で減光させて表示を行うことによって、CPU側での処理負荷無しに減光処理を実現する。

【0028】

さらに、各ポリゴンデータは直線の集合体として定義しておくことによって、描画抜けの無い映像を作成することができ、実際の画面上の画素へ対応させる処理は、GPU側のレンダリング処理で実現することによって、CPU側での処理負荷無しに座標変換処理を実現する。

【0029】

また、各ポリゴンデータ値の輝度情報を高さ方向として扱うことで、輝度の高いデータを前面に表示することが可能となり、高輝度の点を優先的に描画する為のソフトウェアによる比較処理を行う必要がなくなる。これによりCPU側での処理負荷無しに高輝度の点を優先的に描画する処理を実現する。

【0030】

なお、本発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてもよい。

【符号の説明】

【0031】

11…レーダ装置、12…信号処理装置、13…レーダビデオ表示装置、21…PC(パソコン)、22…送受信モジュール、23…メインメモリ、24…CPU、25…グラフィックボード、26…テクスチャメモリ、27…GPU、28…フレームメモリ、29…モニタ。

【技術分野】

【0001】

本発明は、コンピュータグラフィックスによってレーダビデオの描画を行うレーダビデオ表示装置に関する。

【背景技術】

【0002】

近年、コンピュータ・グラフィックス・システムの発展により、レーダビデオの描画処理をソフトウェア制御で高速に行うことが可能になっているが、レーダビデオの特性上必要な、描画したビデオデータの減光処理、高輝度の点を優先的に描画する為の処理、レーダ位置からの極座標で扱われるビデオデータの画面画素へ対応させる座標変換処理などをソフトウェアによるCPU(Central Processing Unit:演算処理装置)処理にて行う必要があった。この為、CPU処理の負荷が発生していた。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−134224号公報

【特許文献2】特開2009−156709号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来技術では、レーダビデオ表示装置をソフトウェアを使用してCPUで実現した場合、減光処理、高輝度の点を優先的に描画する表示処理を行う為にCPU処理の負荷が発生していた。その為に表示分解能を下げて処理を行ったり、専用のハードウェアを使用して処理を行う必要があった。

【0005】

そこで、本発明の課題は、レーダビデオの特性上必要なビデオデータの減光処理、高輝度の点を優先的に描画する為の処理をGPU(Graphics Processing Unit:描画処理装置)処理で行うことにより、CPU処理の負荷を大幅に軽減した描画を可能とするレーダビデオ表示装置を提供することにある。

【課題を解決するための手段】

【0006】

上記の課題を解決するために、本発明のレーダビデオ表示装置は、レーダ装置からのアナログデータを信号処理装置で変換したデジタルデータが受信される送受信モジュールと、前記送受信モジュールに接続され、座標、輝度の描画頂点情報が初期化されるメインメモリと、前記メインメモリに接続され、座標、輝度、更新時間の描画頂点情報が初期化されるテクスチャメモリと、前記メインメモリ上の該当するアジマスの描画頂点情報の各レンジの輝度情報を前記送受信モジュールで受信したデジタルデータの輝度値を使用して更新すると共に、前記メインメモリの輝度の描画頂点情報を取り出して更新時間を付加して対応する前記テクスチャメモリ上の輝度、更新時間の描画頂点情報を更新するCPUと、前記テクスチャメモリから座標、輝度、更新時間の描画頂点情報が入力され、更新時間と現在時間の差で輝度に対して減光計算を行い、減光計算を行った1レンジ分解能分のデータの輝度の階調情報を座標軸のZとして3次元化すると共に、描画頂点情報の3次元の座標値と輝度からレンダリング処理を行って2次元の画像データに変換するGPUと、前記GPUから2次元の画像データが書き込まれるフレームメモリと、前記フレームメモリからの2次元の画像データが入力され、レーダビデオの映像が表示されるモニタとを具備することを特徴とするものである。

【発明の効果】

【0007】

本発明のレーダビデオ表示装置は、ソフトウェア処理によるCPU負荷を発生させることなく、コンピュータグラフィックスにおいて減光処理、高輝度の点を優先的に描画する為の処理をGPU処理で実現したレーダ表示を行うことを可能とする。

【図面の簡単な説明】

【0008】

【図1】本発明の実施形態に係るレーダビデオ表示システムを示す構成説明図である。

【図2】本発明の実施形態に係るレーダビデオ表示装置を示す構成説明図である。

【図3】本発明の実施形態に係る頂点データの定義方法を示す説明図である。

【図4】本発明の実施形態に係るモニタの表示画面のピクセル数とレンジ分解能を示す説明図である。

【図5】本発明の実施形態に係る頂点データを示す説明図であり、(a)は頂点データの集合体、(b)は(a)のB部の1アジマス分解能分のデータ、(c)は(a)のC部の1アジマス分解能分のデータである。

【図6】本発明の実施形態に係るレーダビデオ表示装置の初期化を示す構成説明図である。

【図7】本発明の実施形態に係るレーダビデオ表示装置のデータ受信、メインメモリ更新処理を示す構成説明図である。

【図8】本発明の実施形態に係るレーダビデオ表示装置のテクスチャメモリ更新処理を示す構成説明図である。

【図9】本発明の実施形態に係るレーダビデオ表示装置の描画更新処理を示す構成説明図である。

【発明を実施するための形態】

【0009】

以下、本発明の実施の形態について、詳細に説明する。図中、同一部分は同一符号を付して説明する。

【0010】

図1は本発明の実施形態に係るレーダビデオ表示システムを示す構成説明図である。図において、11はレーダ装置、12は信号処理装置、13はレーダビデオ表示装置である。

【0011】

図1に示すように、レーダ装置11はレーダアンテナ14がアジマス方向に回転しながら定期的に走査を行い、それぞれのレンジ方向と、距離によるゲイン値のアナログデータを信号処理装置12に出力する。信号処理装置12はレーダ装置11から入力されたアナログデータをデジタルデータに変換してレーダビデオ表示装置13に出力する。レーダビデオ表示装置13は信号処理装置12から入力されたデジタルデータを受信しながらアジマス単位で更新して表示する。また、レーダビデオ表示装置13は描画時間経過と共に減光させる減光処理、高輝度の点を優先的に描画する表示処理を実現する。

【0012】

図2は本発明の実施形態に係るレーダビデオ表示装置を示す構成説明図である。図において、21はPC(パソコン)、22は送受信モジュール、23はメインメモリ、24はCPU、25はグラフィックボード、26はテクスチャメモリ、27はGPU、28はフレームメモリ、29はモニタである。

【0013】

すなわち、信号処理装置12には送受信モジュール22を介してメインメモリ23が接続され、メインメモリ23にはCPU24及びテクスチャメモリ26が接続される。テクスチャメモリ26はGPU27に接続され、GPU27はフレームメモリ28を介してモニタ29に接続される。テクスチャメモリ26、GPU27、フレームメモリ28はグラフィックボード25に搭載され、グラフィックボード25、送受信モジュール22、メインメモリ23、CPU24はPC21を構成し、PC21、モニタ29はレーダビデオ表示装置13を構成する。

【0014】

図3は本発明の実施形態に係る頂点データの定義方法を示す説明図である。図3(a)はレーダ装置11においてレーダアンテナ14の走査を示し、アナログデータが得られる。図3(b)はレーダ装置11で得られたアナログデータをデジタルデータに変換したデジタルデータを示し、各ゲイン値を最終的に輝度として表示する。図3(c)はアジマス、レンジで分割されたデータを頂点の集合体として定義する。図3(d)は図3(c)の1アジマス分解能分のデータである。アジマス分解能はアジマス方向の分割数である。図3(e)は図3(d)の1レンジ分解能分のデータ(ポリゴンデータ)である。レンジ分解能はレンジ方向の分割数である。

【0015】

図4は本発明の実施形態に係るモニタの表示画面のピクセル数とレンジ分解能を示す説明図である。図4に示すように、縦方向のピクセル数をP、横方向のピクセル数をWとし、レンジ分解能RをR>P,R>Wと設定することにより、1レンジ分解能分の長さが最終的な表示で1ピクセル以内に収まるので、1レンジ分解能分のデータを直線として扱っても、抜けの無い画像として処理できる。すなわち、レンジ分解能Rを画面のピクセル数より細かく設定することで、レンジ間で描画抜けが発生することが無い。

【0016】

図5は本発明の実施形態に係る頂点データを示す説明図であり、(a)は図3(c)と同じ頂点データの集合体、(b)は(a)のB部の1アジマス分解能分のデータ、(c)は(a)のC部の1アジマス分解能分のデータである。図5において、各頂点が保持するデータを以下のように定義する。

【0017】

座標(X[a][r][p],Y[a][r][p])

輝度G[a][r]

更新時間T[a]

a=(0〜A−1)

r=(0〜R−1)

p=(0〜1)

ここで、Aはアジマス分解能、Rはレンジ分解能である。

【0018】

すなわち、それぞれの頂点データに輝度情報、更新時間情報を保持させる。1レンジ分解能分のデータを構成する各頂点データは、共通の輝度情報と更新時間情報を保持させる。

【0019】

図6は本発明の実施形態に係るレーダビデオ表示装置の初期化を示す構成説明図である。すなわち、CPU24は、レーダビデオ表示装置13を含むシステムの初期化時に、メインメモリ23に描画頂点情報(座標、輝度)、テクスチャメモリ26に描画頂点情報(座標、輝度、更新時間)のバッファを確保して初期化した後、CPU24で描画頂点座標の座標位置の計算を行ってメインメモリ23、テクスチャメモリ26の描画頂点情報の座標を更新する。このように、CPU24は初期化時に描画頂点情報の設定処理をする。

【0020】

図7は本発明の実施形態に係るレーダビデオ表示装置のデータ受信、メインメモリ更新処理を示す構成説明図である。すなわち、信号処理装置12は、レーダ装置11のレーダ走査毎にアジマス単位でデジタルデータを定期的にレーダビデオ表示装置13へ送信する。レーダビデオ表示装置13は、送受信モジュール22でアジマス単位に分割されたデジタルデータを受信して、CPU24によってメインメモリ23上の該当するアジマスの描画頂点情報の各レンジの輝度情報を、前記送受信モジュール22で受信したデジタルデータの輝度値を使用して更新する。このように、CPU24は描画頂点毎の輝度情報を設定する処理をする。

【0021】

図8は本発明の実施形態に係るレーダビデオ表示装置のテクスチャメモリ更新処理を示す構成説明図である。すなわち、CPU24によって定期的にテクスチャメモリ26の更新処理を行い、前回のテクスチャメモリ26の更新処理を行った時から変更された分のメインメモリ23の描画頂点情報(輝度)を取り出して更新時間を付加し、対応するテクスチャメモリ26上の描画頂点情報(輝度、更新時間)を更新する。このように、CPU24は描画頂点毎にデータ更新時間を設定する処理をし、レーダ装置11のレーダ走査のスイープが通過した場所の輝度情報と更新時間を保持させる。

【0022】

図9は本発明の実施形態に係るレーダビデオ表示装置の描画更新処理を示す構成説明図である。すなわち、CPU24で定期的に描画更新処理を行い、グラフィックボード25上にあるOpenGLとシェーダ言語を利用したGPU27にはテクスチャメモリ26から描画頂点情報(座標、輝度、更新時間)が入力される。グラフィックボード25上にあるOpenGLとシェーダ言語を利用したGPU27によって、レーダ装置11のレーダ走査のスイープが通過した時の更新時間と現在時間の差(経過時間)を計算して、輝度に対して経過時間に対応した減光量の計算を行う。減光計算を行った輝度を階調情報として1レンジ分解能分のデータ(ポリゴンデータ)に輝度として設定する。同様に1レンジ分解能分のデータ(ポリゴンデータ)の輝度の階調情報を座標値のZとして設定して3次元化する。

【0023】

描画頂点情報の3次元の座標値と輝度から、グラフィックボード25上にあるOpenGLとシェーダ言語を利用したGPU27によってレンダリング処理を行って2次元の画像データに変換してフレームメモリ28へ書き込む。フレームメモリ28から2次元の画像データがモニタ29へ出力されることで、レーダビデオの映像がモニタ29に表示される。このように、GPU27でのレンダリング処理により、3次元空間での表示を2次元空間へ射影する。また、モニタ29は減光処理、高輝度の点を優先的に描画する処理を実現してレーダビデオ表示する。

【0024】

以上のように、CPU24の行う処理は、受信したアジマス分のデータをメインメモリ23からテクスチャメモリ26に送るだけであり、全データに対する減光処理、2次元画像への変換処理は全てGPU27で行うこととなる。これによりCPU24の処理負荷を抑えてレーダビデオの表示を行うことが出来る。

【0025】

また、GPU27により輝度の階調情報を座標値のZとして設定して3次元化することにより、輝度の高い1レンジ分解能分のデータ(ポリゴンデータ)が手前に見えるようになる。それを2次元に変換することにより輝度の高い1レンジ分解能分のデータ(ポリゴンデータ)が優先的に描画されるようになり、輝度の高いデータが暗いデータに上書きされて消えてしまうことを回避できる。

【0026】

以上説明したように本発明によれば、ビデオデータの1分解能分のデータをOpenGLの頂点で囲まれるポリゴンデータとして扱い、それぞれのポリゴンデータにOpenGLで設定した座標系の3次元の座標(位置)情報、輝度情報、更新(描画)時間情報を保持させる。

【0027】

また、CPU側ではレーダ装置のレーダ走査のスイープが通過した場所の各ポリゴンデータの輝度情報、更新(描画)時間を更新する。描画した時間経過によってGPU側で減光させて表示を行うことによって、CPU側での処理負荷無しに減光処理を実現する。

【0028】

さらに、各ポリゴンデータは直線の集合体として定義しておくことによって、描画抜けの無い映像を作成することができ、実際の画面上の画素へ対応させる処理は、GPU側のレンダリング処理で実現することによって、CPU側での処理負荷無しに座標変換処理を実現する。

【0029】

また、各ポリゴンデータ値の輝度情報を高さ方向として扱うことで、輝度の高いデータを前面に表示することが可能となり、高輝度の点を優先的に描画する為のソフトウェアによる比較処理を行う必要がなくなる。これによりCPU側での処理負荷無しに高輝度の点を優先的に描画する処理を実現する。

【0030】

なお、本発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてもよい。

【符号の説明】

【0031】

11…レーダ装置、12…信号処理装置、13…レーダビデオ表示装置、21…PC(パソコン)、22…送受信モジュール、23…メインメモリ、24…CPU、25…グラフィックボード、26…テクスチャメモリ、27…GPU、28…フレームメモリ、29…モニタ。

【特許請求の範囲】

【請求項1】

レーダ装置からのアナログデータを信号処理装置で変換したデジタルデータが受信される送受信モジュールと、

前記送受信モジュールに接続され、座標、輝度の描画頂点情報が初期化されるメインメモリと、

前記メインメモリに接続され、座標、輝度、更新時間の描画頂点情報が初期化されるテクスチャメモリと、

前記メインメモリ上の該当するアジマスの描画頂点情報の各レンジの輝度情報を前記送受信モジュールで受信したデジタルデータの輝度値を使用して更新すると共に、前記メインメモリの輝度の描画頂点情報を取り出して更新時間を付加して対応する前記テクスチャメモリ上の輝度、更新時間の描画頂点情報を更新するCPUと、

前記テクスチャメモリから座標、輝度、更新時間の描画頂点情報が入力され、更新時間と現在時間の差で輝度に対して減光計算を行い、減光計算を行った1レンジ分解能分のデータの輝度の階調情報を座標軸のZとして3次元化すると共に、描画頂点情報の3次元の座標値と輝度からレンダリング処理を行って2次元の画像データに変換するGPUと、

前記GPUから2次元の画像データが書き込まれるフレームメモリと、

前記フレームメモリからの2次元の画像データが入力され、レーダビデオの映像が表示されるモニタと

を具備することを特徴とするレーダビデオ表示装置。

【請求項1】

レーダ装置からのアナログデータを信号処理装置で変換したデジタルデータが受信される送受信モジュールと、

前記送受信モジュールに接続され、座標、輝度の描画頂点情報が初期化されるメインメモリと、

前記メインメモリに接続され、座標、輝度、更新時間の描画頂点情報が初期化されるテクスチャメモリと、

前記メインメモリ上の該当するアジマスの描画頂点情報の各レンジの輝度情報を前記送受信モジュールで受信したデジタルデータの輝度値を使用して更新すると共に、前記メインメモリの輝度の描画頂点情報を取り出して更新時間を付加して対応する前記テクスチャメモリ上の輝度、更新時間の描画頂点情報を更新するCPUと、

前記テクスチャメモリから座標、輝度、更新時間の描画頂点情報が入力され、更新時間と現在時間の差で輝度に対して減光計算を行い、減光計算を行った1レンジ分解能分のデータの輝度の階調情報を座標軸のZとして3次元化すると共に、描画頂点情報の3次元の座標値と輝度からレンダリング処理を行って2次元の画像データに変換するGPUと、

前記GPUから2次元の画像データが書き込まれるフレームメモリと、

前記フレームメモリからの2次元の画像データが入力され、レーダビデオの映像が表示されるモニタと

を具備することを特徴とするレーダビデオ表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−123603(P2011−123603A)

【公開日】平成23年6月23日(2011.6.23)

【国際特許分類】

【出願番号】特願2009−279660(P2009−279660)

【出願日】平成21年12月9日(2009.12.9)

【出願人】(000221155)東芝電波プロダクツ株式会社 (62)

【Fターム(参考)】

【公開日】平成23年6月23日(2011.6.23)

【国際特許分類】

【出願日】平成21年12月9日(2009.12.9)

【出願人】(000221155)東芝電波プロダクツ株式会社 (62)

【Fターム(参考)】

[ Back to top ]