ロバストディジタル制御を適用した力率改善装置および電源装置

【課題】簡素な構成の制御器で高速応答とロバスト性の両立を実現可能な力率改善装置およびそれを備えた電源装置を提供する。

【解決手段】例えば、昇圧コンバータ部BSTCを制御対象とする電流制御器ICMPと、BSTCおよびICMPを制御対象とする電圧制御器VCMPを備える。ICMPは、BSTCの極を設定するための状態フィードバック部FBBKと、目標値制御に対する応答と外乱(qv,qy)制御に対する応答とを個別に設定できるようにするためのロバスト補償器RTCMiを備える。VCMPは、状態フィードバック部を備えずに、ICMPと同様のロバスト補償器RTCMvを備える。

【解決手段】例えば、昇圧コンバータ部BSTCを制御対象とする電流制御器ICMPと、BSTCおよびICMPを制御対象とする電圧制御器VCMPを備える。ICMPは、BSTCの極を設定するための状態フィードバック部FBBKと、目標値制御に対する応答と外乱(qv,qy)制御に対する応答とを個別に設定できるようにするためのロバスト補償器RTCMiを備える。VCMPは、状態フィードバック部を備えずに、ICMPと同様のロバスト補償器RTCMvを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、力率改善装置およびそれを備えた電源装置に関し、特にディジタル制御によって力率改善を行う力率改善装置およびそれを備えたAC−DCコンバータ(電源装置)に適用して有益な技術に関するものである。

【背景技術】

【0002】

例えば、特許文献1には、制御対象の伝達関数を外乱や遅れ要素を含む二次近似のモデル伝達関数に定め、当該モデル伝達関数に対して当該モデル伝達関数の逆関数と動的補償器とを結合した系を構成し、この系を等価変換して得た積分形制御系を実現する制御補償手段を備えたロバストディジタル制御器が示されている。ここで、制御対象は、DC−DCコンバータとなっている。また、二次近似のモデル伝達関数に定める際には、状態フィードバック則および状態フィードフォワード則が適用される。非特許文献1には、ディジタル制御を行うPFC(power factor correction)コントローラを備えたAC−DCコンバータが示されている。PFCコントローラには、離散時間系のPI(P:比例、I:積分)制御器が用いられる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第4341753号明細書

【非特許文献】

【0004】

【非特許文献1】「トランジスタ技術」、2009年9月号、p.145−153

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、スイッチング電源装置の制御方式として、従来のアナログ制御方式に変わってディジタル制御方式を適用する技術が注目されている。ディジタル制御方式を用いることで、例えば、制御アルゴリズムの変更がソフトウエアの変更によって容易に可能となったり、あるいは、高度な制御理論を用いて電源制御の高精度化が見込めるなど、様々なメリットが得られる。このようなスイッチング電源装置の一つとして、AC−DCコンバータが挙げられる。AC−DCコンバータの中には、外部電源ラインからのAC入力電力の力率を改善し、外部電源ラインに重畳する高調波電流を低減するための力率改善装置(PFC)を備えたものが多く存在する。

【0006】

力率改善装置にディジタル制御方式を適用する場合、例えば、非特許文献1に示されるようなPI(P:比例、I:積分)制御器、あるいはこれに微分(D)を加えたPID制御器を用いることが考えられる。しかしながら、PID制御器では、高速応答とロバスト性の両立が困難となる恐れがある。スイッチング電源装置において、ロバスト性とは、系を安定させた上で、制御量を目標値に精度よく追従させること、外乱の悪影響を除去・抑制すること、入力急変や負荷急変等のパラメータ変動に対して不感であること、をそれぞれ満たすことを言う。高速応答のため入出力特性の帯域を広げると外乱に対する感度が上がり過ぎ、逆にロバスト性を保つため外乱に対する感度を下げると入出力特性の応答性が低下する。

【0007】

そこで、特許文献1の技術を用いることが考えられる。特許文献1の技術を用いると、前述した制御補償手段によって、入力に対する応答と外乱に対する応答を個別に制御することが可能になる(すなわち近似的2自由度制御が可能になる)。これによって、PID制御器において困難であった高速応答とロバスト性の両立が図れる。ただし、特許文献1では、電圧ループで構成されるDC−DCコンバータに近似的2自由度制御を適用する技術が示されているが、これを単純に力率改善装置(PFC)に応用することは容易でない。PFCは、電流ループと電圧ループの二重ループの構成が必要であるが、特許文献1の技術をPFCの各ループにそのまま適用すると、演算及び係数決定が非常に複雑となり、その演算時間がDC−DCコンバータの場合の2倍程度必要となる恐れがある。

【0008】

本発明は、このようなことを鑑みてなされたものであり、その目的の一つは、簡素な構成で高速応答とロバスト性の両立を実現可能な力率改善装置およびそれを備えた電源装置を提供することにある。本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち、代表的な実施の形態の概要を簡単に説明すれば、次のとおりである。

【0010】

本実施の形態による力率改善装置は、昇圧コンバータ部を制御対象とし、アナログ・ディジタル変換器と、電流ループと、電圧ループとを備える。制御対象となる昇圧コンバータ部(BSTC)は、インダクタ(L0)、容量(C0)、負荷(RL)、ダイオード(D0)およびスイッチ用トランジスタ(Q0)を含み、交流入力電圧(vi)が入力される整流器(RCT1)の出力電圧(Vi)を受けて所定の直流電圧値を持つ第1出力電圧(vo)を生成する。アナログ・ディジタル変換器(ADC)は、交流入力電圧を反映した第1目標信号(vac)、インダクタに流れるインダクタ電流(iL)、第1出力電圧(vo)をそれぞれディジタル信号に変換し、第1目標信号に対応する第1ディジタル信号(r)、インダクタ電流に対応する第2ディジタル信号(iL)、第1出力電圧に対応する第3ディジタル信号(vo)を出力する。電流ループは、第1および第2ディジタル信号を受けて、インダクタ電流を交流入力電圧に追従させるための第1操作量(v)を生成し、第1操作量に基づくデューティ比を持つPWM信号をスイッチ用トランジスタに向けて出力する。電圧ループは、第3ディジタル信号を受けて、第1出力電圧を予め定められた目標電圧(rv)に設定するための第2操作量(uv)を生成し、第2操作量を第1目標信号に反映させる。また、交流入力電圧の振幅変動に対応するため、第2ディジタル信号を平均値計算器(AVG)に入力し、平均値(vavg)を生成し、この逆数を第1目標信号に反映させる。ここで、電流ループは、昇圧コンバータ部の極を定めるための状態フィードバック部(FBBK)と、第1ロバスト補償器(RTCMi)とを有する。第1ロバスト補償器(RTCMi)は、状態フィードバック部を含めた昇圧コンバータ部の第1伝達関数(Wry)に対する近似的な第1逆伝達関数(Wm−1)ならびに第1ディジタルロウパスフィルタ(K(z))を含み、電流ループの目標値制御に対する応答(Wry)と外乱制御に対する応答(WQy)とを個別に設定するためものである。

【0011】

このように、電流ループと電圧ループを備え、電流ループに対して状態フィードバック部とロバスト補償器を設けることで、電流ループにおいて高速応答とロバスト性の両立が実現可能となり、その結果、電流ループを制御対象とする電圧ループにおいても当該効果を十分に得ることが可能になる。また、当該電流ループの構成によって電流ループを含めた昇圧コンバータ部を低次の伝達関数に近似することができ、その結果、電圧ループの構成を簡素化することが可能になる。特に、当該伝達関数を1次に近似することで、電圧ループの構成をより簡素化することができ、更に、電圧ループを電流ループと同様なロバスト補償器で構成することで、高速応答とロバスト性の両立をより図ることが可能になる。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的な実施の形態によって得られる効果を簡単に説明すると、力率改善装置およびそれを備えた電源装置において、簡素な構成の制御器で高速応答とロバスト性の両立が実現可能となる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施の形態1による電源装置において、その構成の一例を示すブロック図である。

【図2】図1の電源装置において、その制御器のマイクロコントローラユニットの機能概要を示すブロック図である。

【図3】(a)は、図2の電源装置における昇圧コンバータ部の回路モデルの一例を示す図であり、(b)は、(a)に対応する状態方程式のブロック線図モデルの一例を示す図である。

【図4】(a)は、図3(b)を離散状態方程式で表したブロック線図モデルの一例を示す図であり、(b)は、図4(a)を簡略表示した図である。

【図5】図4(a)、(b)を対象に状態フィードバック則を適用した後のブロック線図モデルの一例を示す図である。

【図6】(a)は、本発明の実施の形態1による電源装置において、電流ループに対するロバスト補償器のブロック線図モデルの一例を示す図であり、(b)は、(a)を等価変換したブロック線図モデルの一例を示す図である。

【図7】図6(b)のブロック線図モデルに図5のブロック線図モデルを適用した電流制御器を示す図である。

【図8】図7のブロック線図モデルを等価変換した電流制御器のブロック線図モデルの一例を示す図である。

【図9】本発明の実施の形態1による電源装置において、その電流制御器のパラメータ決定に伴う根軌跡の例を示す説明図である。

【図10】図8の電流制御器に乗算器を接続したブロック線図モデルの一例を示す図である。

【図11】(a)は、図10のブロック線図モデルに基づき生成した新たな制御対象のブロック線図モデルの一例を示す図であり、(b)は、(a)を近似的に表現した図である。

【図12】本発明の実施の形態1による電源装置において、電圧ループに対するロバスト補償器のブロック線図モデルの一例を示す図である。

【図13】図12のブロック線図モデルを等価変換すると共に図11(a)のブロック線図モデルを適用した電圧制御器のブロック線図モデルの一例を示す図である。

【図14】本発明の実施の形態1による電源装置において、その昇圧コンバータ部の回路モデルの一例を纏めた説明図である。

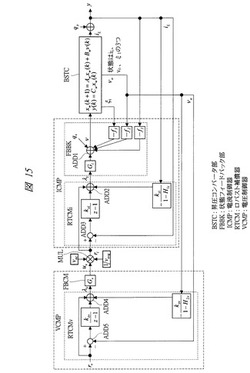

【図15】本発明の実施の形態1による電源装置において、その構成例を纏めたブロック線図である。

【図16】図15を等価変換したブロック線図である。

【図17】本発明の実施の形態1による電源装置において、その比較例として検討した電源装置の構成例を示すブロック線図である。

【図18】(a)、(b)は、動特性変化に対する出力電圧と入力電流の変化を検証した結果を示すものであり、(a)は図15又は図16の構成例を用いた場合の結果であり、(b)はその比較例となる図17の構成例を用いた場合の結果である。

【図19】図15又は図16の構成例を用いた場合の力率改善効果を検証した結果を示す図である。

【図20】本発明の実施の形態2による電源装置において、その構成例を纏めたブロック線図である。

【図21】本発明の実施の形態3による電源装置において、その構成例を纏めたブロック線図である。

【図22】本発明の実施の形態4による電源装置において、その構成の一例を示すブロック図である。

【発明を実施するための形態】

【0014】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0015】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0016】

また、実施の形態の各機能ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0017】

(実施の形態1)

《(1)電源装置の全体構成》

図1は、本発明の実施の形態1による電源装置において、その構成の一例を示すブロック図である。図1に示す電源装置は、整流回路RCT1,RCT2、フィルタFLT1,FLT2、容量CI,C0、電流検出回路IDET、インダクタL0、ダイオードD0、スイッチ用トランジスタQ0、ドライバ回路DRV、負荷RL、およびマイクロコントローラユニットMCU等を備える。このうち、C0,IDET,L0,D0,Q0,DRV,RLは昇圧コンバータ部BSTCを構成する。整流回路RCT1は、外部交流電源VACからの商用の交流入力電圧viおよび交流入力電流iacを受け、内部のダイオードブリッジ等を用いて全波整流を行う。同様に、整流回路RCT2は、交流入力電圧viおよび交流入力電流iacを受けて全波整流を行い、全波整流後の入力電圧vacを出力する。

【0018】

容量CIは、容量値Ciを持ち、RCT1の出力を平滑化することで、基準電源ノードの電圧を基準として略直流の入力電圧Viを生成する。インダクタL0は、インダクタンスL0を持ち、一端に入力電圧Viが印加される。スイッチ用トランジスタQ0は、ソースが基準電源ノードに、ドレインがL0の他端にそれぞれ接続され、ゲートがドライバ回路DRVによって制御される。ダイオードD0は、アノードがL0の他端に接続され、カソードが容量値C0を持つ容量C0の一端に接続される。

【0019】

容量C0は、他端が基準電源ノードに接続され、D0からの出力電流ioに伴う電荷を蓄えることで出力電圧voを生成する。この出力電圧voおよび出力電流ioは、抵抗値RLを持つ負荷RLに供給される。電流検出回路IDETは、インダクタL0に流れるインダクタ電流iLを検出する。フィルタFLT1は、整流回路RCT2からの全波整流後の入力電圧vacとIDETからのインダクタ電流iLをフィルタリングしたのち、マイクロコントローラユニットMCUに出力する。フィルタFLT2は、出力電圧voをフィルタリングしたのち、MCUに出力する。

【0020】

マイクロコントローラユニット(力率改善装置の一部となる制御器)MCUは、例えば一つの半導体チップで実現され、アナログ・ディジタル変換回路ADCと、制御回路CTLと、PWM(Pulse Width Modulation)信号生成回路PWMGを備えている。ADCは、前述したフィルタFTL1,FTL2を介して出力された全波整流後の入力電圧vac、インダクタ電流iL、および出力電圧voをそれぞれディジタル信号に変換する。CTLは、当該ディジタル信号を受けて、出力電圧voが予め定めた所定の目標電圧となり、かつ交流入力電流iacが交流入力電圧viと同様の正弦波となるようにPWMデューティ比の演算を行う。PWMGは、このPWMデューティ比の演算結果を受けてPWM信号を生成する。前述したドライバ回路DRVは、このPWMGからのPWM信号に基づいてスイッチ用トランジスタQ0のオン・オフを制御する。

【0021】

このような構成により、昇圧コンバータ部BSTCでは、スイッチ用トランジスタQ0がオンの場合には、ダイオードD0がオフになると共にインダクタL0に電力が蓄積され、Q0がオフとなった際にはD0がオンになると共にL0の蓄積電力がD0を介して容量C0および負荷RLに供給される。特に限定はされないが、本実施の形態では、例えば、交流入力電圧viは100[Vrms]、Ciは1[μF]、L0は150[μH]、RLは292[Ω]、C0は940[μF]、Viは140[V]、voは385[V]を用いる。

【0022】

図2は、図1の電源装置において、その制御器を構成するマイクロコントローラユニットの機能概要を示すブロック図である。図2に示すMCUは、主に図1の制御回路CTLの部分の詳細を示したものであり、電流制御器ICMP、電圧制御器VCMP、乗算器MUL、平均値計算器AVGを備えている。CTLは、具体的には、DSP(Digital Signal Processor)等のプロセッサである。力率改善を行いながら、出力電圧voを安定化させるためには、出力電圧vo、インダクタ電流iL、全波整流後の入力電圧vacをフィードバックして演算に使用する必要がある。ここでは、ディジタル制御を使用するため、vo,iL,vacが、それぞれフィルタを通して、アナログ・ディジタル変換回路ADCでディジタル値に変換されている。また、PWM信号は、0〜1のデューティ比をPWM信号生成回路PWMGが備えるPWMタイマカウンタに入力することで生成される。

【0023】

図2においては、まず、デューティ比vを入力、インダクタ電流iLを出力とする系を制御対象とする電流制御器ICMPが設けられる。ICMPは、目標信号rにインダクタ電流iLが追従するようにデューティ比vを定める。ここで、目標信号rは、全波整流後の入力電圧vacとその平均値の逆数1/vavgに基づいて定められる。これによって、入力電流iacは入力電圧viに追従することになり、力率が改善され、高調波特性が改善される。さらに、乗算器MULの入力となる制御信号uvを入力、出力電圧voを出力とする系を新たな制御対象として、電圧制御器VCMPが設けられる。MULは、全波整流後の入力電圧vacとその平均値の逆数1/vavgの積に制御信号uvを乗算することで前述した目標信号rを生成する。VCMPは、出力電圧voが所定の目標電圧rvと一致するように制御信号uvを生成する。これによって、入力電流iacは入力電圧viに追従したまま、出力電圧voを所定の目標電圧rvに保つようにデューティ比vの平均値を操作するような処理が行われる。

【0024】

《(2)電流制御器の詳細》

《(2−1)昇圧コンバータ部の状態方程式の導出と離散化》

図3(a)は、図2の電源装置における昇圧コンバータ部の回路モデルの一例を示す図であり、図3(b)は、図3(a)に対応する状態方程式のブロック線図モデルの一例を示す図である。図4(a)は、図3(b)を離散状態方程式で表したブロック線図モデルの一例を示す図であり、図4(b)は、図4(a)を簡略表示した図である。

【0025】

ここでは、図2に示す電流制御器ICMPを設計することを目的として、図3(a)に示す回路モデルを用いて、デューティ比μを入力、インダクタ電流iLを出力として、昇圧コンバータ部BSTCの回路状態方程式を導出する。図3(a)において、R0はインダクタンスL0を持つインダクタ(L0)とスイッチ用トランジスタQ0の等価直列抵抗である。また、μはデューティ比で、μはμの平均値μsとμの微小変動Δμの和で表される(μ=μs+Δμ)。voおよびiLも、同様に、平均値VsおよびIsと、微小変動ΔvOおよびΔiLの和で表される(vo=Vs+ΔvO、iL=Is+ΔiL)。

【0026】

動作点近傍においては、平均値はそれぞれ動作点を定める定数であり、微小変動が変数となる。Vs、Isは、それぞれμsに依存し、式(1)、式(2)で表される。特に限定はされないが、本実施の形態では、例えば、R0=1.8[Ω]、μs=0.651(Vsがvoの仕様385[V]になる点)を用いる。

【0027】

【数1】

【0028】

【数2】

【0029】

インダクタ電流ΔiLを第1の状態変数、出力電圧ΔvOを第2の状態変数とし、所謂状態平均化法を用いて、動作点近傍における線形近似された状態方程式を導出すると、式(3)となる。ただし、式(3)において、Ac,Bc,x(t),u(t),Ccは、それぞれ式(4)で与えられる。また、Ac,Bcは、前述した各数値例を代入すると、式(5)となる。

【0030】

【数3】

【0031】

【数4】

【0032】

【数5】

【0033】

ここで、式(3)の状態方程式をブロック線図モデルに書き直すと、図3(b)のようになる。但し、Ac(i,j),Bc(i,j)は行列Ac,Bcの行列要素である。このモデルをディジタル制御器で扱うために、特許文献1と同様な方式を用いて、入力に時間遅れを持たせながら、離散時間モデル(差分方程式)に変換すると、離散化された状態方程式モデルは式(6)となる。ただし、式(6)において、Aw,Bwはそれぞれ式(7)で与えられ、xw(k),v(k),Cwは、それぞれ式(8)で与えられる。式(7)において、Tはサンプリング周期、Ldは入力の遅れ時間である。

【0034】

【数6】

【0035】

【数7】

【0036】

【数8】

【0037】

ここで、動作点やパラメータ変化が生じた場合を考える。動作点変化は、負荷抵抗RLの抵抗値RL、デューティ比μ、ならびに入力電圧Viの変化と、それらに伴うVs、Isの変化になるので、AcとBcの全ての要素の変動となる。これらのパラメータ変動は、前述した時間遅れ考慮の制御対象の入出力に入る等価外乱qv,qyに置き換えることができる。図4(a)は、この等価外乱qv,qyを含めて式(6)をブロック線図モデルで表したものであり、図4(b)は、その簡易表示となる。但し、aij,bijは行列Aw,Bwの行列要素である。

【0038】

特に限定はされないが、本実施の形態では、例えば、サンプリング周波数fs=100[kHz]、サンプリング周期Ts=10[μs]、遅れ時間Ld=0.99Tsを用いる。この際には、式(7)は式(9)となる。また、式(6)の状態方程式を伝達関数Gw(z)に変換し、各零点n1,n2および各極p1,p2を求めると、式(10)のようになる。

【0039】

【数9】

【0040】

【数10】

【0041】

《(2−2)状態フィードバック則の適用》

次に、図4(a)、(b)の構成例を対象に所謂状態フィードバック則を適用し、制御対象の応答特性(極)を任意のものに変更する。図5は、図4(a)、(b)を対象に状態フィードバック則を適用した後のブロック線図モデルの一例を示す図である。状態フィードバック則を適用する場合、図5に示されるように、まず、Aw−BwFの固有値(極)がベクトルP=[H1 H2 H3]で指定される固有値となる状態フィードバック行列F=[f1 f2 f3]を計算する。次いで、入力から出力までのゲインを1とするようなゲインGを計算して、v(k)=−Fxw(k)+Gr(k)となるようにフィードバックを形成する。このような状態フィードバック則を適用すると、入力rから出力y(iL)までの応答特性(伝達関数)Wryを式(11)のように変更することができる。また、ゲインGは式(12)で表される。ただしIは3行3列の単位行列である。

【0042】

【数11】

【0043】

【数12】

【0044】

ここで、式(11)の導出方法について説明する。式(11)において、(z−n1)(z−n2)は制御対象の元々の零点であり、(z−H1)(z−H2)(z−H3)は極配置後の極である。ここで、1次遅れ系(1/(z−H1))を考える。連続システムの1次遅れ系Gc(s)は、直流ゲインGdcと時定数τdを用いて式(13)で表記される。

【0045】

【数13】

【0046】

この1次遅れ系のステップ応答は、ステップ入力のラプラス変換(1/s)をかけて、式(14)となる。これをサンプリング周期Tsでz変換すると、式(15)となり、ステップ入力のz変換(z/(z−1))を除くと、離散1次遅れ系のパルス伝達関数は式(16)で表される。ただしexp(−Ts/τd)=H1である。

【0047】

【数14】

【0048】

【数15】

【0049】

【数16】

【0050】

式(16)より、離散システムでは、極をH1においた場合、直流ゲインとしてGdcの他に(1−H1)が必要であることがわかる。そこで、全ての極・零点に対して、Gdc=1とし、同様の直流ゲインを追加すると、Wryは式(11)のようになる。

【0051】

また、式(12)の導出方法について説明する。まず、前述した式(6)の状態方程式の直流ゲインを求める。この状態方程式は、1入力1出力の伝達関数に置き換えると、Gw=Cw(zI−Aw)−1Bwとなる。当該伝達関数の直流ゲインは、z=1の場合に相当する。したがって、伝達関数Gwにz=1を代入すると、直流ゲインGwdcは式(17)となる。

【0052】

【数17】

【0053】

ここで、状態フィードバックは、状態フィードバックゲインFを使って、系のA行列を(A−BF)に変えることで、A行列の固有値(極)を移動する手法であるから、状態フィードバックを適用した系の直流ゲインは、式(17)における直流ゲインのA行列を(A−BF)に置き換えたものとなる。よって、状態フィードバック則(v(k)=−Fxw(k)+r)を適用した系の直流ゲインGwfdcは、式(18)であり、これを打ち消して、直流ゲインを1とするためのゲインGは、その逆数となる式(12)で与えられる。

【0054】

【数18】

【0055】

式(11)において、一般的に、零点n1,n2は応答特性に与える影響が小さく、例えば極を、H1>>H2,H3となるように指定することで、Wryを1次モデルに近似することができる。この近似された特性を式(19)に示すようにWmとおく。

【0056】

【数19】

【0057】

しかしながら、昇圧コンバータの場合、負荷の抵抗とキャパシタンスによって零点n1の位置が大きく変化し、応答特性に影響を与えることがある。昇圧コンバータの電流特性において、時定数τ=RLC0が小さい場合、零点n1は単位円の中心近くに、時定数τが大きい場合、零点n1は単位円内の単位円付近にそれぞれ存在する。離散システムにおいては、零点aが単位円内にあり、単位円に近い場合、オーバーシュートを生じ、aが単位円に近いほど、それが大きくなり、またaが単位円より遠い位置にある場合は、影響は無視して良いほど小さく、零点は単なるゲイン的要素となることが知られている。よって、昇圧コンバータの電流特性では、時定数τが大きい場合に、応答特性にオーバーシュートを生じることがわかる。オーバーシュートを抑えるには、時定数τ=RLC0を小さくする必要があるが、負荷抵抗RLを小さくすると出力電圧のリプルが増え、容量C0を増やしてそれを抑える必要が出るため、通常の使用で、τを小さくすることは難しく、零点n1の影響が無視できない。

【0058】

このように、零点n1が、単位円内の単位円近くに存在するものとし、もう一つの零点n2は無視しても構わないものとすると、零点n1を除去しないと安定した特性が得られないため、本実施の形態では、Hパラメータの指定手法を変更し、H2で零点n1を打ち消すようにする。すなわち、H2=n1とし、残りの極に関しては、H1>>H3と定める。こうすると、式(11)に示したr−y伝達関数Wryは式(20)のようになり、式(19)の場合と同様に、Wryを1次モデルで近似することができる。

【0059】

【数20】

【0060】

《(2−3)ロバスト補償器の接続》

続いて、図5に示したモデルに対してロバスト補償器を接続する。図6(a)は、本発明の実施の形態1による電源装置において、ロバスト補償器のブロック線図モデルの一例を示す図であり、図6(b)は、図6(a)を等価変換したブロック線図モデルの一例を示す図である。図5に示したモデルに、2自由度制御を適用するため、図6(a)に示すようなロバスト補償器RTCMiを接続する。図6(a)に示すWryは、図5の式(20)に示した伝達関数Wryに対応する。RTCMiは、逆システムとなるWm−1とロウパスフィルタとして機能するK(z)を備え、Wm−1は式(20)の逆数となる式(21)で与えられ、K(z)は、式(22)で与えられる。また、前述した等価外乱qv,qyは、図6(a)における等価外乱ベクトルQ=[qv qy]Tで示され、その伝達関数がWQyである。

【0061】

【数21】

【0062】

【数22】

【0063】

ただし、図6(a)に示すロバスト補償器RTCMiは、分子の次数が分母よりも大きい逆システムを持つため、そのままでは実現が困難である。そのため、条件を定めて、その条件下で、実現できる形に等価変換することが望ましい。この等価変換に際し、まず、図6(a)より式(23)が得られる。式(23)を変形して(z)を省略すると式(24)となる。

【0064】

【数23】

【0065】

【数24】

【0066】

次いで、式(24)においてWm−1とKに式(21)および式(22)を代入すると、式(25)が得られる。式(25)を変形すると式(26)が得られ、さらに、式(26)における左辺の括弧内を右辺に移して整理すると式(27)が得られる。Wryの入力λが式(27)で表されることをブロック線図にしたものが図6(b)である。

【0067】

【数25】

【0068】

【数26】

【0069】

【数27】

【0070】

図7は、図6(b)のブロック線図モデルに図5のブロック線図モデルを適用した電流制御器を示す図である。図8は、図7のブロック線図モデルを等価変換したブロック線図モデルの一例を示す図である。図8は、図7にブロック線図モデルを式(28)の係数を使用して等価変換したものである。図8において、目標信号rおよびインダクタ電流iLを入力とし、デューティ比vを出力する部分が図2の電流制御器ICMPに該当する。

【0071】

【数28】

【0072】

ここで、図6(a)を例とすると、r→yの伝達関数は式(29)で与えられ、Q→yの伝達関数は式(30)で与えられる。ただし、式(30)におけるWQy(z)は、式(31)で与えられ、式(29)および式(30)におけるWs(z)は式(20)のWryと式(21)のWm−1の積(WryWm−1)を用いて式(32)で与えられる。

【0073】

【数29】

【0074】

【数30】

【0075】

【数31】

【0076】

【数32】

【0077】

式(29)を算出する際にはQ→yの特性は関係ないためQ=0とし、式(30)を算出する際にはr→yの特性は関係ないためr=0とする。例えば、式(30)を算出するにあたりr=0とした場合、図6(a)より、λは式(33)となる。また、図6(a)より、y=Wryλ+WQyQであるため、これを変形すると、式(34)が得られる。式(34)よりyを求め、それを変形すると式(30)が得られる。

【0078】

【数33】

【0079】

【数34】

【0080】

式(29)および式(30)において、Ws(z)≒1であれば式(35)となる。これにより、r→yの伝達特性はH1のみで定めることができ、Q→yの伝達特性はkzで定めることができる。すなわち、通常の入力(r)に対する応答と、外乱(Q)に対する応答をそれぞれ独立に制御できる近似的2自由度制御が実現可能になる。

【0081】

【数35】

【0082】

《(2−4)パラメータの決定》

前述した項目(2−2)及び(2−3)より、電流制御器ICMPのパラメータの決定に際しては、以下の条件があることがわかる。

(条件1)極の一つであるH2は、単位円内の零点n1と近い値にして打ち消す。

(条件2)電流制御器のr−y特性を決める代表極H1をもう一つの極H3より十分大きくする。

(条件3)H1はH2に対して速く(H2>>H1)にする。

(条件4)Ws(z)≒1とし、近似度を良くする。

(条件5)kzを上げ、外乱の影響を小さくする。

【0083】

ここで、外乱の影響を小さくするためにはkzを大きくする必要があるが、kzを大きくすると、式(29)における(z−1+kzWs(z))の極pz1,pz2が代表極H1に近づき、近似度が悪くなる可能性がある。図9は、本発明の実施の形態1による電源装置において、その電流制御器のパラメータ決定に伴う根軌跡の例を示す説明図である。図9では、kzを0から増加させた時のpz1,pz2の根軌跡の例が示されている。図9において、根は1,H3から出発し、点線に沿って移動していく。ここから、kzが十分大きな値の時に、|H1|>>|H3|,|pz1|,|pz2|、かつH2≒n1を満たすように、H1,H2,H3,kzを決めれば良いことがわかる。

【0084】

特に限定はされないが、本実施の形態では、例えば、式(10)に基づきH2=n1=0.999927とし、また、H1=0.5、H3=−0.2、kz=0.35とする。この場合、図5で述べたF行列[f1 f2 f3]は、F=[0.017372 −0.0014308 0.58241]となり、ゲインGは式(12)より、G=0.024809となり、r−y伝達関数Wryは、式(10)の零点n2を用いて式(36)となる。

【0085】

【数36】

【0086】

また、図8における電流制御器ICMPの各係数をそれぞれ計算すると、式(28)より、k1=−0.034738、k2=0.0014308、k3=−0.58241、ki=0.0086831、kr=0.024809となる。さらに移動後の極は、pz1=0.39777+0.24106i、pz2=0.39777−0.24106iとなり、条件を満たすものとなる。

【0087】

《(3)電圧制御器の詳細(本実施の形態の主要な特徴)》

《(3−1)乗算器の接続》

図10は、図8の電流制御器に乗算器を接続したブロック線図モデルの一例を示す図である。前述した図2においては、インダクタ電流iLの平均値が、入力電流iacを全波整流したものになる。そのため、iLを、整流後の入力電圧vacに追従させれば、入力電流iacは、入力電圧viに追従することになり、力率が改善され、高調波特性が改善される。このため、図10に示すように乗算器にvacを入力することで電流の目標信号rを生成し、iLをvacに追従させるようにする。また、そのままでは目標信号rが大きくなりすぎてしまうため、vacの平均値vavgの逆数も同時に乗算器に入力する。

【0088】

《(3−2)新たな制御対象の定義》

図10において、制御信号uvを入力、出力電圧vOを出力yvとおいた、新たな制御対象を考え、それを用いて図2の電圧制御器VCMPを設計する。この新たな制御対象は、昇圧コンバータ部の離散化モデルにおける3次に電流制御器の1次を加えた計4次のシステムとなるが、これに対して、前述した電流制御器の場合と同様にして、再度状態フィードバック則を適用すると、システムが複雑になる。そこで、本実施の形態では、新たな制御対象を1次(低次)のモデルに近似し、それに対してロバスト補償器を接続する手法で電圧制御器を構成することが主要な特徴となっている。

【0089】

まず、新たな制御対象の特性を1次モデルに近似する手法を考える。電圧を制御するため、式(6)〜式(8)に示した昇圧コンバータ部の離散化状態方程式において、状態変数であるvOとiLとを入れ替える。この場合、電流と電圧の特性の違いを考えると、式(6)に示した離散化状態方程式の状態変数xw(k)をxw’(k)=[vo(k) iL(k) ξ1(k)]Tと置き換えても、Aw行列の固有値は変わらず、それは状態フィードバックをかけたAw−BwFの場合も同様である。

【0090】

再度、この状態変数で伝達関数Gw’を求めると、式(37)となり、前述した式(10)と比較すると、極は共通し、零点と直流ゲインが変化するのみである。そのため、新たな制御対象の伝達特性は、電流制御器を設計する際の状態フィードバックとロバスト補償器に大きく依存することになる。

【0091】

【数37】

【0092】

したがって、デューティ比をμとして、μ→iLに対して、μ→voは零点と直流ゲインのみ変化したものと捉えると、新たな制御対象のuv→voの伝達特性は、式(38)で表される。ただし、Grivはインダクタ電流から出力電圧までの直流ゲインである。

【0093】

【数38】

【0094】

式(38)において、vacに関して、入力電圧の変化全てを考慮することは困難であるため、vacをピーク値Viとし、Grivを展開すると、式(39)が得られる。ただし、Guiは式(40)で与えられる。

【0095】

【数39】

【0096】

【数40】

【0097】

ここで、式(38)〜式(40)は、次のようにして導出される。まず、uv→voの伝達関数は、前述した式(37)と式(10)との比較から、式(11)のWryに対して、零点n1とn2がn1vとn2vに変化したものとなる。また、それに伴い、電流制御器では打ち消されていた極H2が、打ち消されずに残ることになる。さらに、極H3と、ロバスト補償器によって追加された極が、kzによってpz1,pz2に変化する。極H1はそのまま残る。以上のことから、極・零点をそれぞれ書き出し、式(11)の場合と同様にして直流ゲインを付加すると式(41)となる。

【0098】

【数41】

【0099】

ただし、式(41)の直流ゲインはr→iLのものを前提としているため、さらにiL→voの直流ゲインを追加する必要がある。インダクタ電流iLから出力電圧voまでの直流ゲインGrivは、図4(a)にz=1を代入することで得られる。図4(a)、(b)のブロック線図モデルの状態方程式を展開し、z=1、つまり、x(k+1)=x(k)を適用すると、式(42)が得られる。

【0100】

【数42】

【0101】

また、前述した式(12)の場合と同様にして求めたvからiLまでの直流ゲインGui(式(40))を使って式(42)を変形すると式(43)となり、その結果、式(44)のGrivが得られる。そして、この式(44)を用いて前述した式(39)が得られる。

【0102】

【数43】

【0103】

【数44】

【0104】

図11(a)は、図10のブロック線図モデルに基づき生成した新たな制御対象のブロック線図モデルの一例を示す図であり、図11(b)は、図11(a)を近似的に表現した図である。前述した式(39)において、零点n1v,n2vはz平面での単位円外の遠くに配置されるため、伝達特性には大きな影響を与えない。そこで、図11(a)に示すように、図10に対して直流ゲインを打ち消して「1」とするゲインGv=vavg/(ViGriv)を追加し、新たな入力rvおよび出力yv(=v0)を設けてその伝達特性を考える。この場合、入力rvからの伝達特性は、式(39)よりH1,H2,H3,kz(H3,kzによって値が決まるpz1,pz2)によって決定される。一般に電流制御器ICMPの零点n1は単位円に近い位置にあり、|H2|>>|H1|となるため、項目(2−4)で述べたパラメータ決定法から、同時に|H2|>>|H3|,|pz1|,|pz2|となる。これによって、rv−yv(=v0)の伝達関数Wryvは、式(45)および図11(b)に示す1次モデルWmvに近似される。特に限定はされないが、本実施の形態では、例えば、Griv=48.375、Gv=0.01316とする。

【0105】

【数45】

【0106】

ここで、前述した|H2|>>|H1|となる理由および条件について補足する。2重ループの制御器においては、内側ループ(今回は電流制御器)の制御性能に外ループ(電圧制御器)が影響せぬよう、内側ループの制御帯域幅を、外側より広く取る必要がある。一般にPFC制御器においては、電流ループの制御帯域は、100[Hz]の整流sin波に追従するため2[kHz]〜10[kHz]程度、電圧ループの制御帯域は〜10[Hz]程度とされる。本実施の形態では、項目(2−4)で述べたように零点n1=0.9999あたりになるので、これを打ち消す極H2=n1を電圧ループの目標特性とすると、その制御帯域は、サンプリング周波数Fs=100[kHz]において1.57[Hz]となる。電流ループは、電流の追従性を高めるために目標特性の極H1が例えば0.88191〜0.53349(制御帯域1[kHz]〜10[kHz])程度であるため、|H2|>>|H1|となる。

【0107】

《(3−3)ロバスト補償器の接続》

図11(b)に示したように、入力rv−出力voの伝達関数が1次モデルに近似されたので、このモデルに対して、前述した項目(2−3)の場合と同様にして、ロバスト補償器を接続する。図12は、本発明の実施の形態1による電源装置において、電圧ループに対するロバスト補償器のブロック線図モデルの一例を示す図である。図12において、Wryvは、式(45)に示した伝達関数Wryvに対応する。ロバスト補償器RTCMvは、逆システムとなるWmv−1とロウパスフィルタとして機能するKv(z)を備える。Wmv−1は式(45)に基づいてWmv−1=(z−H2)/(1−H2)で与えられ、Kv(z)は、式(22)と同様に、Kv(z)=kzv/(z−1+kzv)で与えられる。また、等価外乱qv,qyからyvまでの伝達関数WQyvは、WQyv(z)=[Wqvyv(z) Wqyyv(z)]である。

【0108】

図13は、図12のブロック線図モデルを等価変換すると共に図11(a)のブロック線図モデルを適用した電圧制御器のブロック線図モデルの一例を示す図である。すなわち、図13は、図12に対して、前述した図6(a)、(b)の場合と同様の等価変換を行い、更に、伝達関数Wryv,WQyvの部分に図11(a)のモデルを適用したものである。ここで、等価変換に伴い追加された各係数は、式(46)で与えられる。

【0109】

【数46】

【0110】

図13において、rv,voを入力とし、uvを出力する部分が、図2における電圧補償器VCMPに該当する。ここで、図12を例とすると、rv→yvの伝達関数は、式(29)と同様に式(47)で与えられ、Q→yvの伝達関数は式(30)と同様に式(48)で与えられる。ただし、式(47)および式(48)におけるWsvは、式(45)のWryvと式(45)のWmv−1の積(WryvWmv−1)を用いて式(49)で与えられる。

【0111】

【数47】

【0112】

【数48】

【0113】

【数49】

【0114】

式(47)および式(48)において、Wsv(z)≒1であれば式(50)となる。これにより、rv→yvの伝達特性はH2のみで定めることができ、Q→yvの伝達特性はkzvで定めることができる。すなわち、通常の入力(rv)に対する応答と、外乱(Q)に対する応答をそれぞれ独立に制御できる近似的2自由度制御が実現可能になる。

【0115】

【数50】

【0116】

特に限定はされないが、本実施の形態では、電流制御器の場合と同様にして、根軌跡から、kzvが変化したときに移動する極の値が全てH2より十分小さくなるよう、例えばkzv=0.25とする。この場合、図13の電圧制御器VCMPの各係数は、式(46)により、それぞれ、krv=0.01316、kf=−45.069、kiv=0.00329となる。

【0117】

《(4)電源装置(力率改善装置)の主要な構成および効果の纏め》

図14は、本発明の実施の形態1による電源装置において、その昇圧コンバータ部の回路モデルの一例を纏めた説明図である。項目(2−1)で述べたように、本実施の形態による電源装置では、制御対象となる昇圧コンバータ部BSTCをディジタル制御するために、BSTCを図14に示すような状態方程式によってモデル化する。この際には、まず、PFC用昇圧コンバータの等価回路(S101)を基に連続時間の状態方程式を求め(S102)、この連続時間の状態方程式を離散化された状態方程式に変換する(S103)。更に、アナログ・ディジタル変換回路の変換時間やプロセッサの演算時間等の遅延時間を考慮し、これを反映した状態ξ1を追加し、遅延時間をシステムの入力遅延時間Ld=0.99Tsとして、S103における制御対象の離散化された状態方程式に反映させる(S104)。その結果、操作量(デューティ比)vを入力とし、インダクタ電流iL、出力電圧vo、およびシステム入力遅延時間ξ1を状態とする離散化された状態方程式が得られる。

【0118】

図15は、本発明の実施の形態1による電源装置において、その構成例を纏めたブロック線図である。図15においては、昇圧コンバータ部BSTCと、電流制御器ICMPと、電圧制御器VCMPと、乗算器MULが示されている。このうち、ICMP,VCMP,MULが図2で述べたように力率改善装置(PFC)の一部を構成する制御器に該当する。力率改善装置(PFC)(制御器)は、図14で説明した昇圧コンバータ部BSTCの回路モデルに基づいてその内部構成が定められる。ICMPは、状態フィードバック部FBBKとロバスト補償器RTCMiを備えている。

【0119】

状態フィードバック部FBBKは、項目(2−2)で述べたように、状態フィードバックゲインF=[f1 f2 f3]と、直流ゲインを補償する(λi→iLの直流ゲインを1にする)ためのフィードフォワードゲインGiと、加算器(減算器)ADD1を備える。ロバスト補償器RTCMiは、項目(2−3)で述べたように、BSTCおよびFBBKを制御対象として、当該制御対象を1次で近似した際の逆システムとロウパスフィルタとを備えている。ただし、前述したように、当該逆システムおよびロウパスフィルタは等価変換されることで、RTCMiは、係数(−kzi/(1−H1i))と、係数および積分器(kzi/(z−1))と、加算器(減算器)ADD2,ADD3を備える。なお、パラメータzは、サンプリング周期をTとしてejωTに等しい。

【0120】

電圧制御器VCMPは、状態フィードバック補償部FBCMとロバスト補償器RTCMvを備えている。FBCMは、項目(3−2)で述べたように、直流ゲインを補償する(λv→voの直流ゲインを1にする)ためのフィードフォワードゲインGvを備える。RTCMvは、項目(3−3)で述べたように、BSTC,FBBK,RTCMi,MULを制御対象として、当該制御対象を1次で近似した際の逆システムとロウパスフィルタとを備えている。ただし、前述したように、当該逆システムおよびロウパスフィルタは等価変換されることで、RTCMvは、係数(−kzv/(1−H2v))と、係数および積分器(kzv/(z−1))と、加算器(減算器)ADD4,ADD5を備える。

【0121】

以上のように、本実施の形態による電源装置(力率改善装置(PFC))は、PFCを電流ループと電圧ループから構成する。電流ループでは、制御対象に状態フィードバック則を適用し、更に近似的な逆システムとロウパスフィルタで構成されるロバスト補償器を加えることで2自由度制御が行われる。一方、電圧ループでは、簡素化のため新たに状態フィードバック則の適用は行わずに、電流ループ全体の簡易的(近似的)な逆システムとロウパスフィルタで構成されるロバスト補償器を備えることで2自由度制御が行われる。電流ループ、電圧ループ共に2自由度制御が行われるため、目標値制御に対する応答と外乱制御に対する応答を独立に設定でき、入力電流に対する応答と負荷変動などの動特性に対する応答を同時に改善できる。すなわち、高速応答とロバスト性の両立が実現可能になる。

【0122】

更に、電圧ループは、電流ループのような状態フィードバック則の適用を行わずに、ロバスト補償器を備えた簡素な構成で実現している。これにより、設計の容易化が図れ、また、電圧ループに状態フィードバック則の適用を行った場合と比較して積和演算回数等が減るため、PFCの実動作における演算時間の短縮等が可能となる。なお、図15には、構成を判り易くするため、図7に示したような等価変換前のブロック線図が示されているが、勿論、これに対して図8に示したような等価変換を行い、これに基づいてPFCを構成することも可能である。

【0123】

図16は、図15を等価変換したブロック線図である。図16のブロック線図は、前述した図13のブロック線図と同一のものである。図16において、電流制御器ICMPは、フィードバック係数k1,k2,k3と、フィードフォワード係数krと、積分器(1/(z−1))と、係数kiと、加算器(減算器)ADD6,ADD7を備える。一方、電圧制御器VCMPは、フィードバック係数kfと、フィードフォワード係数krvと、積分器(1/(z−1))と、係数kivと、加算器(減算器)ADD8,ADD9を備える。

【0124】

《(5)比較例との対比ならびに検証結果》

図17は、本発明の実施の形態1による電源装置において、その比較例として検討した電源装置の構成例を示すブロック線図である。図17に示す電源装置は、例えば、前述した非特許文献1に示されるようなPI(P:比例、I:積分)制御器を備えている。電流ループのPI制御器IPIは、係数kpiからなるP部と、(1/(z−1))および係数kiiからなるI部を備え、その外側に位置する電圧ループのPI制御器VPIは、係数kpvからなるP部と、(1/(z−1))および係数kivからなるI部を備える。

【0125】

図18(a)、(b)は、動特性変化に対する出力電圧と入力電流の変化を検証した結果を示すものであり、図18(a)は図15又は図16の構成例を用いた場合の結果であり、図18(b)はその比較例となる図17の構成例を用いた場合の結果である。図18(a)、(b)から判るように、図15又は図16の構成例を用いることで、図17の構成例と比較して外乱に対する出力電圧および入力電流の変動を抑制することが可能になる。例えば、図18(b)では、外乱に対して20V程度の出力電圧変動が生じているが、図18(a)では、それが7V程度に抑制されている。すなわち、図15又は図16の構成例を用いることで、図17の構成例と比較してロバスト性を向上させることができる。図19は、図15又は図16の構成例を用いた場合の力率改善効果を検証した結果を示す図である。ここでは、出力電圧vo=385V、RL=300Ωとして、0.994程度の力率が得られている。

【0126】

以上、本実施の形態1による力率改善装置および電源装置を用いることで、代表的には簡素な構成で高速応答とロバスト性の両立が実現可能となる。

【0127】

(実施の形態2)

図20は、本発明の実施の形態2による電源装置において、その構成例を纏めたブロック線図である。図20に示す電源装置は、前述した図16の変形例となっており、図16のVCMPが図20の電圧制御器VCMPaに変更され、図16のICMPが図20の電流制御器ICMPaに変更された構成となっている。VCMPaは、図16のVCMPからフィードフォワード係数Krvが削除された構成を備えており、ICMPaは、図16のVCMPからフィードフォワード係数Krが削除された構成を備えている。

【0128】

例えば前述した図7の構成例において、係数kzが十分に大きく、「(z−1+kz)/(z−1+kz)≒kz/(z−1+kz)」と近似できる場合、図7におけるrからλへのフィードフォワード経路を近似的に削除することができる。この場合、図8の電流制御器ICMPにおけるkrのフィードフォワード経路は必ずしも必要ではなくなる。すなわち、図15の構成例において、kziが十分に大きい場合には図15のICMPにおけるriからλiへのフィードフォワード経路を近似的に削除することができ、図16のICMPにおけるkrのフィードフォワード経路は必ずしも必要ではなくなる。これと同様に、図16の電圧制御器VCMPにおいても、図15の係数kzvが十分に大きい場合には図16の係数Krvのフィードフォワード経路は必ずしも必要ではなくなる。

【0129】

このように、フォードフォワード経路の削除を行うことで、力率改善装置(PFC)の構成をより簡素化することができ、また、PFCの動作に伴う演算時間をより短縮することが可能になる。

【0130】

(実施の形態3)

図21は、本発明の実施の形態3による電源装置において、その構成例を纏めたブロック線図である。図21に示す電源装置は、前述した図16の変形例となっており、図16のVCMPが図20の電圧ループ用PI制御器VPIに変更された構成となっている。VPIは、図17の場合と同様に、係数kpvからなるP(比例)部と、積分器(1/(z−1))および係数kivからなるI(積分)部と、2個の加算器(減算器)ADD10,ADD11を備える。

【0131】

前述したように、電流ループに関しては、電流制御器ICMPによって高いロバスト性が実現できると共に、電流ループ全体を十分に近似度の高い1次モデルで近似することができる。このため、図21に示すように、電圧制御器を一般的なPI制御器VPI等で構成した場合でも、簡素な構成で、ある程度十分な高速応答とロバスト性の両立が実現可能となる。

【0132】

(実施の形態4)

図22は、本発明の実施の形態4による電源装置において、その構成の一例を示すブロック図である。図22に示す電源装置は、前述した図1の電源装置の変形例となっており、図1と比較して昇圧コンバータ部の構成が異なっている。図22の昇圧コンバータ部BSTCaは、図1のBSTCに対して、インダクタL1、ダイオードD1、スイッチ用トランジスタQ1、およびドライバ回路DRV2が追加されている。L1およびD1は直列接続され、当該直列接続回路が前述したインダクタL0およびダイオードD0からなる直列接続回路と並列に接続される。Q1は、ソースが基準電源ノードに、ドレインがL1とD1の接続ノード(D1のアノード側)にそれぞれ接続され、ゲートがDRV2によって制御される。DRV2は、マイクロコントローラユニット(力率改善装置の一部を構成する制御器)MCU内のPWM信号生成回路PWMGから出力されたPWM信号を入力として動作する。

【0133】

ドライバ回路DRV2のPWM信号は、ドライバ回路DRV1のPWM信号のサイクルを基準としてそこから半サイクルずれるタイミングで生成される。これによって、スイッチ用トランジスタQ0,Q1では、インターリーブ方式によるスイッチングが行われる。このようなインターリーブ方式を適用することで、スイッチングによって生じるL0,L1のインダクタ電流io0,io1のリプル成分を低減できるため、結果的に、図1の場合と比較して入力電流iacに生じる高調波成分をより低減することが可能になる。力率改善装置の制御器は実施の形態1、2または3と同様の構成に、インターリーブ制御を加えた構成である。

【0134】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

【産業上の利用可能性】

【0135】

本実施の形態による力率改善装置および電源装置は、特に、マイクロコンピュータ(又はディジタルシグナルプロセッサ(DSP))等によるディジタル演算処理を用いて力率改善を行うAC−DCコンバータに適用して有益なものであり、これに限らず、PFC機能を備えたAC−DCコンバータ全般に広く適用可能である。

【符号の説明】

【0136】

ADC アナログ・ディジタル変換回路

ADD 加算器(減算器)

AVG 平均値計算器

BSTC 昇圧コンバータ部

CI,CO 容量

CTL 制御回路

D ダイオード

DRV ドライバ回路

FLT フィルタ

ICMP 電流制御器

IDET 電流検出回路

IPI,VPI PI制御器

L インダクタ

MCU マイクロコントローラユニット

MUL 乗算器

PWMG PWM信号生成回路

Q スイッチ用トランジスタ

RCT 整流回路

RL 負荷

RTCM ロバスト補償器

VAC 外部交流電源

VCMP 電圧制御器

【技術分野】

【0001】

本発明は、力率改善装置およびそれを備えた電源装置に関し、特にディジタル制御によって力率改善を行う力率改善装置およびそれを備えたAC−DCコンバータ(電源装置)に適用して有益な技術に関するものである。

【背景技術】

【0002】

例えば、特許文献1には、制御対象の伝達関数を外乱や遅れ要素を含む二次近似のモデル伝達関数に定め、当該モデル伝達関数に対して当該モデル伝達関数の逆関数と動的補償器とを結合した系を構成し、この系を等価変換して得た積分形制御系を実現する制御補償手段を備えたロバストディジタル制御器が示されている。ここで、制御対象は、DC−DCコンバータとなっている。また、二次近似のモデル伝達関数に定める際には、状態フィードバック則および状態フィードフォワード則が適用される。非特許文献1には、ディジタル制御を行うPFC(power factor correction)コントローラを備えたAC−DCコンバータが示されている。PFCコントローラには、離散時間系のPI(P:比例、I:積分)制御器が用いられる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第4341753号明細書

【非特許文献】

【0004】

【非特許文献1】「トランジスタ技術」、2009年9月号、p.145−153

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、スイッチング電源装置の制御方式として、従来のアナログ制御方式に変わってディジタル制御方式を適用する技術が注目されている。ディジタル制御方式を用いることで、例えば、制御アルゴリズムの変更がソフトウエアの変更によって容易に可能となったり、あるいは、高度な制御理論を用いて電源制御の高精度化が見込めるなど、様々なメリットが得られる。このようなスイッチング電源装置の一つとして、AC−DCコンバータが挙げられる。AC−DCコンバータの中には、外部電源ラインからのAC入力電力の力率を改善し、外部電源ラインに重畳する高調波電流を低減するための力率改善装置(PFC)を備えたものが多く存在する。

【0006】

力率改善装置にディジタル制御方式を適用する場合、例えば、非特許文献1に示されるようなPI(P:比例、I:積分)制御器、あるいはこれに微分(D)を加えたPID制御器を用いることが考えられる。しかしながら、PID制御器では、高速応答とロバスト性の両立が困難となる恐れがある。スイッチング電源装置において、ロバスト性とは、系を安定させた上で、制御量を目標値に精度よく追従させること、外乱の悪影響を除去・抑制すること、入力急変や負荷急変等のパラメータ変動に対して不感であること、をそれぞれ満たすことを言う。高速応答のため入出力特性の帯域を広げると外乱に対する感度が上がり過ぎ、逆にロバスト性を保つため外乱に対する感度を下げると入出力特性の応答性が低下する。

【0007】

そこで、特許文献1の技術を用いることが考えられる。特許文献1の技術を用いると、前述した制御補償手段によって、入力に対する応答と外乱に対する応答を個別に制御することが可能になる(すなわち近似的2自由度制御が可能になる)。これによって、PID制御器において困難であった高速応答とロバスト性の両立が図れる。ただし、特許文献1では、電圧ループで構成されるDC−DCコンバータに近似的2自由度制御を適用する技術が示されているが、これを単純に力率改善装置(PFC)に応用することは容易でない。PFCは、電流ループと電圧ループの二重ループの構成が必要であるが、特許文献1の技術をPFCの各ループにそのまま適用すると、演算及び係数決定が非常に複雑となり、その演算時間がDC−DCコンバータの場合の2倍程度必要となる恐れがある。

【0008】

本発明は、このようなことを鑑みてなされたものであり、その目的の一つは、簡素な構成で高速応答とロバスト性の両立を実現可能な力率改善装置およびそれを備えた電源装置を提供することにある。本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち、代表的な実施の形態の概要を簡単に説明すれば、次のとおりである。

【0010】

本実施の形態による力率改善装置は、昇圧コンバータ部を制御対象とし、アナログ・ディジタル変換器と、電流ループと、電圧ループとを備える。制御対象となる昇圧コンバータ部(BSTC)は、インダクタ(L0)、容量(C0)、負荷(RL)、ダイオード(D0)およびスイッチ用トランジスタ(Q0)を含み、交流入力電圧(vi)が入力される整流器(RCT1)の出力電圧(Vi)を受けて所定の直流電圧値を持つ第1出力電圧(vo)を生成する。アナログ・ディジタル変換器(ADC)は、交流入力電圧を反映した第1目標信号(vac)、インダクタに流れるインダクタ電流(iL)、第1出力電圧(vo)をそれぞれディジタル信号に変換し、第1目標信号に対応する第1ディジタル信号(r)、インダクタ電流に対応する第2ディジタル信号(iL)、第1出力電圧に対応する第3ディジタル信号(vo)を出力する。電流ループは、第1および第2ディジタル信号を受けて、インダクタ電流を交流入力電圧に追従させるための第1操作量(v)を生成し、第1操作量に基づくデューティ比を持つPWM信号をスイッチ用トランジスタに向けて出力する。電圧ループは、第3ディジタル信号を受けて、第1出力電圧を予め定められた目標電圧(rv)に設定するための第2操作量(uv)を生成し、第2操作量を第1目標信号に反映させる。また、交流入力電圧の振幅変動に対応するため、第2ディジタル信号を平均値計算器(AVG)に入力し、平均値(vavg)を生成し、この逆数を第1目標信号に反映させる。ここで、電流ループは、昇圧コンバータ部の極を定めるための状態フィードバック部(FBBK)と、第1ロバスト補償器(RTCMi)とを有する。第1ロバスト補償器(RTCMi)は、状態フィードバック部を含めた昇圧コンバータ部の第1伝達関数(Wry)に対する近似的な第1逆伝達関数(Wm−1)ならびに第1ディジタルロウパスフィルタ(K(z))を含み、電流ループの目標値制御に対する応答(Wry)と外乱制御に対する応答(WQy)とを個別に設定するためものである。

【0011】

このように、電流ループと電圧ループを備え、電流ループに対して状態フィードバック部とロバスト補償器を設けることで、電流ループにおいて高速応答とロバスト性の両立が実現可能となり、その結果、電流ループを制御対象とする電圧ループにおいても当該効果を十分に得ることが可能になる。また、当該電流ループの構成によって電流ループを含めた昇圧コンバータ部を低次の伝達関数に近似することができ、その結果、電圧ループの構成を簡素化することが可能になる。特に、当該伝達関数を1次に近似することで、電圧ループの構成をより簡素化することができ、更に、電圧ループを電流ループと同様なロバスト補償器で構成することで、高速応答とロバスト性の両立をより図ることが可能になる。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的な実施の形態によって得られる効果を簡単に説明すると、力率改善装置およびそれを備えた電源装置において、簡素な構成の制御器で高速応答とロバスト性の両立が実現可能となる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施の形態1による電源装置において、その構成の一例を示すブロック図である。

【図2】図1の電源装置において、その制御器のマイクロコントローラユニットの機能概要を示すブロック図である。

【図3】(a)は、図2の電源装置における昇圧コンバータ部の回路モデルの一例を示す図であり、(b)は、(a)に対応する状態方程式のブロック線図モデルの一例を示す図である。

【図4】(a)は、図3(b)を離散状態方程式で表したブロック線図モデルの一例を示す図であり、(b)は、図4(a)を簡略表示した図である。

【図5】図4(a)、(b)を対象に状態フィードバック則を適用した後のブロック線図モデルの一例を示す図である。

【図6】(a)は、本発明の実施の形態1による電源装置において、電流ループに対するロバスト補償器のブロック線図モデルの一例を示す図であり、(b)は、(a)を等価変換したブロック線図モデルの一例を示す図である。

【図7】図6(b)のブロック線図モデルに図5のブロック線図モデルを適用した電流制御器を示す図である。

【図8】図7のブロック線図モデルを等価変換した電流制御器のブロック線図モデルの一例を示す図である。

【図9】本発明の実施の形態1による電源装置において、その電流制御器のパラメータ決定に伴う根軌跡の例を示す説明図である。

【図10】図8の電流制御器に乗算器を接続したブロック線図モデルの一例を示す図である。

【図11】(a)は、図10のブロック線図モデルに基づき生成した新たな制御対象のブロック線図モデルの一例を示す図であり、(b)は、(a)を近似的に表現した図である。

【図12】本発明の実施の形態1による電源装置において、電圧ループに対するロバスト補償器のブロック線図モデルの一例を示す図である。

【図13】図12のブロック線図モデルを等価変換すると共に図11(a)のブロック線図モデルを適用した電圧制御器のブロック線図モデルの一例を示す図である。

【図14】本発明の実施の形態1による電源装置において、その昇圧コンバータ部の回路モデルの一例を纏めた説明図である。

【図15】本発明の実施の形態1による電源装置において、その構成例を纏めたブロック線図である。

【図16】図15を等価変換したブロック線図である。

【図17】本発明の実施の形態1による電源装置において、その比較例として検討した電源装置の構成例を示すブロック線図である。

【図18】(a)、(b)は、動特性変化に対する出力電圧と入力電流の変化を検証した結果を示すものであり、(a)は図15又は図16の構成例を用いた場合の結果であり、(b)はその比較例となる図17の構成例を用いた場合の結果である。

【図19】図15又は図16の構成例を用いた場合の力率改善効果を検証した結果を示す図である。

【図20】本発明の実施の形態2による電源装置において、その構成例を纏めたブロック線図である。

【図21】本発明の実施の形態3による電源装置において、その構成例を纏めたブロック線図である。

【図22】本発明の実施の形態4による電源装置において、その構成の一例を示すブロック図である。

【発明を実施するための形態】

【0014】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0015】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0016】

また、実施の形態の各機能ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0017】

(実施の形態1)

《(1)電源装置の全体構成》

図1は、本発明の実施の形態1による電源装置において、その構成の一例を示すブロック図である。図1に示す電源装置は、整流回路RCT1,RCT2、フィルタFLT1,FLT2、容量CI,C0、電流検出回路IDET、インダクタL0、ダイオードD0、スイッチ用トランジスタQ0、ドライバ回路DRV、負荷RL、およびマイクロコントローラユニットMCU等を備える。このうち、C0,IDET,L0,D0,Q0,DRV,RLは昇圧コンバータ部BSTCを構成する。整流回路RCT1は、外部交流電源VACからの商用の交流入力電圧viおよび交流入力電流iacを受け、内部のダイオードブリッジ等を用いて全波整流を行う。同様に、整流回路RCT2は、交流入力電圧viおよび交流入力電流iacを受けて全波整流を行い、全波整流後の入力電圧vacを出力する。

【0018】

容量CIは、容量値Ciを持ち、RCT1の出力を平滑化することで、基準電源ノードの電圧を基準として略直流の入力電圧Viを生成する。インダクタL0は、インダクタンスL0を持ち、一端に入力電圧Viが印加される。スイッチ用トランジスタQ0は、ソースが基準電源ノードに、ドレインがL0の他端にそれぞれ接続され、ゲートがドライバ回路DRVによって制御される。ダイオードD0は、アノードがL0の他端に接続され、カソードが容量値C0を持つ容量C0の一端に接続される。

【0019】

容量C0は、他端が基準電源ノードに接続され、D0からの出力電流ioに伴う電荷を蓄えることで出力電圧voを生成する。この出力電圧voおよび出力電流ioは、抵抗値RLを持つ負荷RLに供給される。電流検出回路IDETは、インダクタL0に流れるインダクタ電流iLを検出する。フィルタFLT1は、整流回路RCT2からの全波整流後の入力電圧vacとIDETからのインダクタ電流iLをフィルタリングしたのち、マイクロコントローラユニットMCUに出力する。フィルタFLT2は、出力電圧voをフィルタリングしたのち、MCUに出力する。

【0020】

マイクロコントローラユニット(力率改善装置の一部となる制御器)MCUは、例えば一つの半導体チップで実現され、アナログ・ディジタル変換回路ADCと、制御回路CTLと、PWM(Pulse Width Modulation)信号生成回路PWMGを備えている。ADCは、前述したフィルタFTL1,FTL2を介して出力された全波整流後の入力電圧vac、インダクタ電流iL、および出力電圧voをそれぞれディジタル信号に変換する。CTLは、当該ディジタル信号を受けて、出力電圧voが予め定めた所定の目標電圧となり、かつ交流入力電流iacが交流入力電圧viと同様の正弦波となるようにPWMデューティ比の演算を行う。PWMGは、このPWMデューティ比の演算結果を受けてPWM信号を生成する。前述したドライバ回路DRVは、このPWMGからのPWM信号に基づいてスイッチ用トランジスタQ0のオン・オフを制御する。

【0021】

このような構成により、昇圧コンバータ部BSTCでは、スイッチ用トランジスタQ0がオンの場合には、ダイオードD0がオフになると共にインダクタL0に電力が蓄積され、Q0がオフとなった際にはD0がオンになると共にL0の蓄積電力がD0を介して容量C0および負荷RLに供給される。特に限定はされないが、本実施の形態では、例えば、交流入力電圧viは100[Vrms]、Ciは1[μF]、L0は150[μH]、RLは292[Ω]、C0は940[μF]、Viは140[V]、voは385[V]を用いる。

【0022】

図2は、図1の電源装置において、その制御器を構成するマイクロコントローラユニットの機能概要を示すブロック図である。図2に示すMCUは、主に図1の制御回路CTLの部分の詳細を示したものであり、電流制御器ICMP、電圧制御器VCMP、乗算器MUL、平均値計算器AVGを備えている。CTLは、具体的には、DSP(Digital Signal Processor)等のプロセッサである。力率改善を行いながら、出力電圧voを安定化させるためには、出力電圧vo、インダクタ電流iL、全波整流後の入力電圧vacをフィードバックして演算に使用する必要がある。ここでは、ディジタル制御を使用するため、vo,iL,vacが、それぞれフィルタを通して、アナログ・ディジタル変換回路ADCでディジタル値に変換されている。また、PWM信号は、0〜1のデューティ比をPWM信号生成回路PWMGが備えるPWMタイマカウンタに入力することで生成される。

【0023】

図2においては、まず、デューティ比vを入力、インダクタ電流iLを出力とする系を制御対象とする電流制御器ICMPが設けられる。ICMPは、目標信号rにインダクタ電流iLが追従するようにデューティ比vを定める。ここで、目標信号rは、全波整流後の入力電圧vacとその平均値の逆数1/vavgに基づいて定められる。これによって、入力電流iacは入力電圧viに追従することになり、力率が改善され、高調波特性が改善される。さらに、乗算器MULの入力となる制御信号uvを入力、出力電圧voを出力とする系を新たな制御対象として、電圧制御器VCMPが設けられる。MULは、全波整流後の入力電圧vacとその平均値の逆数1/vavgの積に制御信号uvを乗算することで前述した目標信号rを生成する。VCMPは、出力電圧voが所定の目標電圧rvと一致するように制御信号uvを生成する。これによって、入力電流iacは入力電圧viに追従したまま、出力電圧voを所定の目標電圧rvに保つようにデューティ比vの平均値を操作するような処理が行われる。

【0024】

《(2)電流制御器の詳細》

《(2−1)昇圧コンバータ部の状態方程式の導出と離散化》

図3(a)は、図2の電源装置における昇圧コンバータ部の回路モデルの一例を示す図であり、図3(b)は、図3(a)に対応する状態方程式のブロック線図モデルの一例を示す図である。図4(a)は、図3(b)を離散状態方程式で表したブロック線図モデルの一例を示す図であり、図4(b)は、図4(a)を簡略表示した図である。

【0025】

ここでは、図2に示す電流制御器ICMPを設計することを目的として、図3(a)に示す回路モデルを用いて、デューティ比μを入力、インダクタ電流iLを出力として、昇圧コンバータ部BSTCの回路状態方程式を導出する。図3(a)において、R0はインダクタンスL0を持つインダクタ(L0)とスイッチ用トランジスタQ0の等価直列抵抗である。また、μはデューティ比で、μはμの平均値μsとμの微小変動Δμの和で表される(μ=μs+Δμ)。voおよびiLも、同様に、平均値VsおよびIsと、微小変動ΔvOおよびΔiLの和で表される(vo=Vs+ΔvO、iL=Is+ΔiL)。

【0026】

動作点近傍においては、平均値はそれぞれ動作点を定める定数であり、微小変動が変数となる。Vs、Isは、それぞれμsに依存し、式(1)、式(2)で表される。特に限定はされないが、本実施の形態では、例えば、R0=1.8[Ω]、μs=0.651(Vsがvoの仕様385[V]になる点)を用いる。

【0027】

【数1】

【0028】

【数2】

【0029】

インダクタ電流ΔiLを第1の状態変数、出力電圧ΔvOを第2の状態変数とし、所謂状態平均化法を用いて、動作点近傍における線形近似された状態方程式を導出すると、式(3)となる。ただし、式(3)において、Ac,Bc,x(t),u(t),Ccは、それぞれ式(4)で与えられる。また、Ac,Bcは、前述した各数値例を代入すると、式(5)となる。

【0030】

【数3】

【0031】

【数4】

【0032】

【数5】

【0033】

ここで、式(3)の状態方程式をブロック線図モデルに書き直すと、図3(b)のようになる。但し、Ac(i,j),Bc(i,j)は行列Ac,Bcの行列要素である。このモデルをディジタル制御器で扱うために、特許文献1と同様な方式を用いて、入力に時間遅れを持たせながら、離散時間モデル(差分方程式)に変換すると、離散化された状態方程式モデルは式(6)となる。ただし、式(6)において、Aw,Bwはそれぞれ式(7)で与えられ、xw(k),v(k),Cwは、それぞれ式(8)で与えられる。式(7)において、Tはサンプリング周期、Ldは入力の遅れ時間である。

【0034】

【数6】

【0035】

【数7】

【0036】

【数8】

【0037】

ここで、動作点やパラメータ変化が生じた場合を考える。動作点変化は、負荷抵抗RLの抵抗値RL、デューティ比μ、ならびに入力電圧Viの変化と、それらに伴うVs、Isの変化になるので、AcとBcの全ての要素の変動となる。これらのパラメータ変動は、前述した時間遅れ考慮の制御対象の入出力に入る等価外乱qv,qyに置き換えることができる。図4(a)は、この等価外乱qv,qyを含めて式(6)をブロック線図モデルで表したものであり、図4(b)は、その簡易表示となる。但し、aij,bijは行列Aw,Bwの行列要素である。

【0038】

特に限定はされないが、本実施の形態では、例えば、サンプリング周波数fs=100[kHz]、サンプリング周期Ts=10[μs]、遅れ時間Ld=0.99Tsを用いる。この際には、式(7)は式(9)となる。また、式(6)の状態方程式を伝達関数Gw(z)に変換し、各零点n1,n2および各極p1,p2を求めると、式(10)のようになる。

【0039】

【数9】

【0040】

【数10】

【0041】

《(2−2)状態フィードバック則の適用》

次に、図4(a)、(b)の構成例を対象に所謂状態フィードバック則を適用し、制御対象の応答特性(極)を任意のものに変更する。図5は、図4(a)、(b)を対象に状態フィードバック則を適用した後のブロック線図モデルの一例を示す図である。状態フィードバック則を適用する場合、図5に示されるように、まず、Aw−BwFの固有値(極)がベクトルP=[H1 H2 H3]で指定される固有値となる状態フィードバック行列F=[f1 f2 f3]を計算する。次いで、入力から出力までのゲインを1とするようなゲインGを計算して、v(k)=−Fxw(k)+Gr(k)となるようにフィードバックを形成する。このような状態フィードバック則を適用すると、入力rから出力y(iL)までの応答特性(伝達関数)Wryを式(11)のように変更することができる。また、ゲインGは式(12)で表される。ただしIは3行3列の単位行列である。

【0042】

【数11】

【0043】

【数12】

【0044】

ここで、式(11)の導出方法について説明する。式(11)において、(z−n1)(z−n2)は制御対象の元々の零点であり、(z−H1)(z−H2)(z−H3)は極配置後の極である。ここで、1次遅れ系(1/(z−H1))を考える。連続システムの1次遅れ系Gc(s)は、直流ゲインGdcと時定数τdを用いて式(13)で表記される。

【0045】

【数13】

【0046】

この1次遅れ系のステップ応答は、ステップ入力のラプラス変換(1/s)をかけて、式(14)となる。これをサンプリング周期Tsでz変換すると、式(15)となり、ステップ入力のz変換(z/(z−1))を除くと、離散1次遅れ系のパルス伝達関数は式(16)で表される。ただしexp(−Ts/τd)=H1である。

【0047】

【数14】

【0048】

【数15】

【0049】

【数16】

【0050】

式(16)より、離散システムでは、極をH1においた場合、直流ゲインとしてGdcの他に(1−H1)が必要であることがわかる。そこで、全ての極・零点に対して、Gdc=1とし、同様の直流ゲインを追加すると、Wryは式(11)のようになる。

【0051】

また、式(12)の導出方法について説明する。まず、前述した式(6)の状態方程式の直流ゲインを求める。この状態方程式は、1入力1出力の伝達関数に置き換えると、Gw=Cw(zI−Aw)−1Bwとなる。当該伝達関数の直流ゲインは、z=1の場合に相当する。したがって、伝達関数Gwにz=1を代入すると、直流ゲインGwdcは式(17)となる。

【0052】

【数17】

【0053】

ここで、状態フィードバックは、状態フィードバックゲインFを使って、系のA行列を(A−BF)に変えることで、A行列の固有値(極)を移動する手法であるから、状態フィードバックを適用した系の直流ゲインは、式(17)における直流ゲインのA行列を(A−BF)に置き換えたものとなる。よって、状態フィードバック則(v(k)=−Fxw(k)+r)を適用した系の直流ゲインGwfdcは、式(18)であり、これを打ち消して、直流ゲインを1とするためのゲインGは、その逆数となる式(12)で与えられる。

【0054】

【数18】

【0055】

式(11)において、一般的に、零点n1,n2は応答特性に与える影響が小さく、例えば極を、H1>>H2,H3となるように指定することで、Wryを1次モデルに近似することができる。この近似された特性を式(19)に示すようにWmとおく。

【0056】

【数19】

【0057】

しかしながら、昇圧コンバータの場合、負荷の抵抗とキャパシタンスによって零点n1の位置が大きく変化し、応答特性に影響を与えることがある。昇圧コンバータの電流特性において、時定数τ=RLC0が小さい場合、零点n1は単位円の中心近くに、時定数τが大きい場合、零点n1は単位円内の単位円付近にそれぞれ存在する。離散システムにおいては、零点aが単位円内にあり、単位円に近い場合、オーバーシュートを生じ、aが単位円に近いほど、それが大きくなり、またaが単位円より遠い位置にある場合は、影響は無視して良いほど小さく、零点は単なるゲイン的要素となることが知られている。よって、昇圧コンバータの電流特性では、時定数τが大きい場合に、応答特性にオーバーシュートを生じることがわかる。オーバーシュートを抑えるには、時定数τ=RLC0を小さくする必要があるが、負荷抵抗RLを小さくすると出力電圧のリプルが増え、容量C0を増やしてそれを抑える必要が出るため、通常の使用で、τを小さくすることは難しく、零点n1の影響が無視できない。

【0058】

このように、零点n1が、単位円内の単位円近くに存在するものとし、もう一つの零点n2は無視しても構わないものとすると、零点n1を除去しないと安定した特性が得られないため、本実施の形態では、Hパラメータの指定手法を変更し、H2で零点n1を打ち消すようにする。すなわち、H2=n1とし、残りの極に関しては、H1>>H3と定める。こうすると、式(11)に示したr−y伝達関数Wryは式(20)のようになり、式(19)の場合と同様に、Wryを1次モデルで近似することができる。

【0059】

【数20】

【0060】

《(2−3)ロバスト補償器の接続》

続いて、図5に示したモデルに対してロバスト補償器を接続する。図6(a)は、本発明の実施の形態1による電源装置において、ロバスト補償器のブロック線図モデルの一例を示す図であり、図6(b)は、図6(a)を等価変換したブロック線図モデルの一例を示す図である。図5に示したモデルに、2自由度制御を適用するため、図6(a)に示すようなロバスト補償器RTCMiを接続する。図6(a)に示すWryは、図5の式(20)に示した伝達関数Wryに対応する。RTCMiは、逆システムとなるWm−1とロウパスフィルタとして機能するK(z)を備え、Wm−1は式(20)の逆数となる式(21)で与えられ、K(z)は、式(22)で与えられる。また、前述した等価外乱qv,qyは、図6(a)における等価外乱ベクトルQ=[qv qy]Tで示され、その伝達関数がWQyである。

【0061】

【数21】

【0062】

【数22】

【0063】

ただし、図6(a)に示すロバスト補償器RTCMiは、分子の次数が分母よりも大きい逆システムを持つため、そのままでは実現が困難である。そのため、条件を定めて、その条件下で、実現できる形に等価変換することが望ましい。この等価変換に際し、まず、図6(a)より式(23)が得られる。式(23)を変形して(z)を省略すると式(24)となる。

【0064】

【数23】

【0065】

【数24】

【0066】

次いで、式(24)においてWm−1とKに式(21)および式(22)を代入すると、式(25)が得られる。式(25)を変形すると式(26)が得られ、さらに、式(26)における左辺の括弧内を右辺に移して整理すると式(27)が得られる。Wryの入力λが式(27)で表されることをブロック線図にしたものが図6(b)である。

【0067】

【数25】

【0068】

【数26】

【0069】

【数27】

【0070】

図7は、図6(b)のブロック線図モデルに図5のブロック線図モデルを適用した電流制御器を示す図である。図8は、図7のブロック線図モデルを等価変換したブロック線図モデルの一例を示す図である。図8は、図7にブロック線図モデルを式(28)の係数を使用して等価変換したものである。図8において、目標信号rおよびインダクタ電流iLを入力とし、デューティ比vを出力する部分が図2の電流制御器ICMPに該当する。

【0071】

【数28】

【0072】

ここで、図6(a)を例とすると、r→yの伝達関数は式(29)で与えられ、Q→yの伝達関数は式(30)で与えられる。ただし、式(30)におけるWQy(z)は、式(31)で与えられ、式(29)および式(30)におけるWs(z)は式(20)のWryと式(21)のWm−1の積(WryWm−1)を用いて式(32)で与えられる。

【0073】

【数29】

【0074】

【数30】

【0075】

【数31】

【0076】

【数32】

【0077】

式(29)を算出する際にはQ→yの特性は関係ないためQ=0とし、式(30)を算出する際にはr→yの特性は関係ないためr=0とする。例えば、式(30)を算出するにあたりr=0とした場合、図6(a)より、λは式(33)となる。また、図6(a)より、y=Wryλ+WQyQであるため、これを変形すると、式(34)が得られる。式(34)よりyを求め、それを変形すると式(30)が得られる。

【0078】

【数33】

【0079】

【数34】

【0080】

式(29)および式(30)において、Ws(z)≒1であれば式(35)となる。これにより、r→yの伝達特性はH1のみで定めることができ、Q→yの伝達特性はkzで定めることができる。すなわち、通常の入力(r)に対する応答と、外乱(Q)に対する応答をそれぞれ独立に制御できる近似的2自由度制御が実現可能になる。

【0081】

【数35】

【0082】

《(2−4)パラメータの決定》

前述した項目(2−2)及び(2−3)より、電流制御器ICMPのパラメータの決定に際しては、以下の条件があることがわかる。

(条件1)極の一つであるH2は、単位円内の零点n1と近い値にして打ち消す。

(条件2)電流制御器のr−y特性を決める代表極H1をもう一つの極H3より十分大きくする。

(条件3)H1はH2に対して速く(H2>>H1)にする。

(条件4)Ws(z)≒1とし、近似度を良くする。

(条件5)kzを上げ、外乱の影響を小さくする。

【0083】

ここで、外乱の影響を小さくするためにはkzを大きくする必要があるが、kzを大きくすると、式(29)における(z−1+kzWs(z))の極pz1,pz2が代表極H1に近づき、近似度が悪くなる可能性がある。図9は、本発明の実施の形態1による電源装置において、その電流制御器のパラメータ決定に伴う根軌跡の例を示す説明図である。図9では、kzを0から増加させた時のpz1,pz2の根軌跡の例が示されている。図9において、根は1,H3から出発し、点線に沿って移動していく。ここから、kzが十分大きな値の時に、|H1|>>|H3|,|pz1|,|pz2|、かつH2≒n1を満たすように、H1,H2,H3,kzを決めれば良いことがわかる。

【0084】

特に限定はされないが、本実施の形態では、例えば、式(10)に基づきH2=n1=0.999927とし、また、H1=0.5、H3=−0.2、kz=0.35とする。この場合、図5で述べたF行列[f1 f2 f3]は、F=[0.017372 −0.0014308 0.58241]となり、ゲインGは式(12)より、G=0.024809となり、r−y伝達関数Wryは、式(10)の零点n2を用いて式(36)となる。

【0085】

【数36】

【0086】

また、図8における電流制御器ICMPの各係数をそれぞれ計算すると、式(28)より、k1=−0.034738、k2=0.0014308、k3=−0.58241、ki=0.0086831、kr=0.024809となる。さらに移動後の極は、pz1=0.39777+0.24106i、pz2=0.39777−0.24106iとなり、条件を満たすものとなる。

【0087】

《(3)電圧制御器の詳細(本実施の形態の主要な特徴)》

《(3−1)乗算器の接続》

図10は、図8の電流制御器に乗算器を接続したブロック線図モデルの一例を示す図である。前述した図2においては、インダクタ電流iLの平均値が、入力電流iacを全波整流したものになる。そのため、iLを、整流後の入力電圧vacに追従させれば、入力電流iacは、入力電圧viに追従することになり、力率が改善され、高調波特性が改善される。このため、図10に示すように乗算器にvacを入力することで電流の目標信号rを生成し、iLをvacに追従させるようにする。また、そのままでは目標信号rが大きくなりすぎてしまうため、vacの平均値vavgの逆数も同時に乗算器に入力する。

【0088】

《(3−2)新たな制御対象の定義》

図10において、制御信号uvを入力、出力電圧vOを出力yvとおいた、新たな制御対象を考え、それを用いて図2の電圧制御器VCMPを設計する。この新たな制御対象は、昇圧コンバータ部の離散化モデルにおける3次に電流制御器の1次を加えた計4次のシステムとなるが、これに対して、前述した電流制御器の場合と同様にして、再度状態フィードバック則を適用すると、システムが複雑になる。そこで、本実施の形態では、新たな制御対象を1次(低次)のモデルに近似し、それに対してロバスト補償器を接続する手法で電圧制御器を構成することが主要な特徴となっている。

【0089】

まず、新たな制御対象の特性を1次モデルに近似する手法を考える。電圧を制御するため、式(6)〜式(8)に示した昇圧コンバータ部の離散化状態方程式において、状態変数であるvOとiLとを入れ替える。この場合、電流と電圧の特性の違いを考えると、式(6)に示した離散化状態方程式の状態変数xw(k)をxw’(k)=[vo(k) iL(k) ξ1(k)]Tと置き換えても、Aw行列の固有値は変わらず、それは状態フィードバックをかけたAw−BwFの場合も同様である。

【0090】

再度、この状態変数で伝達関数Gw’を求めると、式(37)となり、前述した式(10)と比較すると、極は共通し、零点と直流ゲインが変化するのみである。そのため、新たな制御対象の伝達特性は、電流制御器を設計する際の状態フィードバックとロバスト補償器に大きく依存することになる。

【0091】

【数37】

【0092】

したがって、デューティ比をμとして、μ→iLに対して、μ→voは零点と直流ゲインのみ変化したものと捉えると、新たな制御対象のuv→voの伝達特性は、式(38)で表される。ただし、Grivはインダクタ電流から出力電圧までの直流ゲインである。

【0093】

【数38】

【0094】

式(38)において、vacに関して、入力電圧の変化全てを考慮することは困難であるため、vacをピーク値Viとし、Grivを展開すると、式(39)が得られる。ただし、Guiは式(40)で与えられる。

【0095】

【数39】

【0096】

【数40】

【0097】

ここで、式(38)〜式(40)は、次のようにして導出される。まず、uv→voの伝達関数は、前述した式(37)と式(10)との比較から、式(11)のWryに対して、零点n1とn2がn1vとn2vに変化したものとなる。また、それに伴い、電流制御器では打ち消されていた極H2が、打ち消されずに残ることになる。さらに、極H3と、ロバスト補償器によって追加された極が、kzによってpz1,pz2に変化する。極H1はそのまま残る。以上のことから、極・零点をそれぞれ書き出し、式(11)の場合と同様にして直流ゲインを付加すると式(41)となる。

【0098】

【数41】

【0099】

ただし、式(41)の直流ゲインはr→iLのものを前提としているため、さらにiL→voの直流ゲインを追加する必要がある。インダクタ電流iLから出力電圧voまでの直流ゲインGrivは、図4(a)にz=1を代入することで得られる。図4(a)、(b)のブロック線図モデルの状態方程式を展開し、z=1、つまり、x(k+1)=x(k)を適用すると、式(42)が得られる。

【0100】

【数42】

【0101】

また、前述した式(12)の場合と同様にして求めたvからiLまでの直流ゲインGui(式(40))を使って式(42)を変形すると式(43)となり、その結果、式(44)のGrivが得られる。そして、この式(44)を用いて前述した式(39)が得られる。

【0102】

【数43】

【0103】

【数44】

【0104】

図11(a)は、図10のブロック線図モデルに基づき生成した新たな制御対象のブロック線図モデルの一例を示す図であり、図11(b)は、図11(a)を近似的に表現した図である。前述した式(39)において、零点n1v,n2vはz平面での単位円外の遠くに配置されるため、伝達特性には大きな影響を与えない。そこで、図11(a)に示すように、図10に対して直流ゲインを打ち消して「1」とするゲインGv=vavg/(ViGriv)を追加し、新たな入力rvおよび出力yv(=v0)を設けてその伝達特性を考える。この場合、入力rvからの伝達特性は、式(39)よりH1,H2,H3,kz(H3,kzによって値が決まるpz1,pz2)によって決定される。一般に電流制御器ICMPの零点n1は単位円に近い位置にあり、|H2|>>|H1|となるため、項目(2−4)で述べたパラメータ決定法から、同時に|H2|>>|H3|,|pz1|,|pz2|となる。これによって、rv−yv(=v0)の伝達関数Wryvは、式(45)および図11(b)に示す1次モデルWmvに近似される。特に限定はされないが、本実施の形態では、例えば、Griv=48.375、Gv=0.01316とする。

【0105】

【数45】

【0106】

ここで、前述した|H2|>>|H1|となる理由および条件について補足する。2重ループの制御器においては、内側ループ(今回は電流制御器)の制御性能に外ループ(電圧制御器)が影響せぬよう、内側ループの制御帯域幅を、外側より広く取る必要がある。一般にPFC制御器においては、電流ループの制御帯域は、100[Hz]の整流sin波に追従するため2[kHz]〜10[kHz]程度、電圧ループの制御帯域は〜10[Hz]程度とされる。本実施の形態では、項目(2−4)で述べたように零点n1=0.9999あたりになるので、これを打ち消す極H2=n1を電圧ループの目標特性とすると、その制御帯域は、サンプリング周波数Fs=100[kHz]において1.57[Hz]となる。電流ループは、電流の追従性を高めるために目標特性の極H1が例えば0.88191〜0.53349(制御帯域1[kHz]〜10[kHz])程度であるため、|H2|>>|H1|となる。

【0107】

《(3−3)ロバスト補償器の接続》

図11(b)に示したように、入力rv−出力voの伝達関数が1次モデルに近似されたので、このモデルに対して、前述した項目(2−3)の場合と同様にして、ロバスト補償器を接続する。図12は、本発明の実施の形態1による電源装置において、電圧ループに対するロバスト補償器のブロック線図モデルの一例を示す図である。図12において、Wryvは、式(45)に示した伝達関数Wryvに対応する。ロバスト補償器RTCMvは、逆システムとなるWmv−1とロウパスフィルタとして機能するKv(z)を備える。Wmv−1は式(45)に基づいてWmv−1=(z−H2)/(1−H2)で与えられ、Kv(z)は、式(22)と同様に、Kv(z)=kzv/(z−1+kzv)で与えられる。また、等価外乱qv,qyからyvまでの伝達関数WQyvは、WQyv(z)=[Wqvyv(z) Wqyyv(z)]である。

【0108】

図13は、図12のブロック線図モデルを等価変換すると共に図11(a)のブロック線図モデルを適用した電圧制御器のブロック線図モデルの一例を示す図である。すなわち、図13は、図12に対して、前述した図6(a)、(b)の場合と同様の等価変換を行い、更に、伝達関数Wryv,WQyvの部分に図11(a)のモデルを適用したものである。ここで、等価変換に伴い追加された各係数は、式(46)で与えられる。

【0109】

【数46】

【0110】

図13において、rv,voを入力とし、uvを出力する部分が、図2における電圧補償器VCMPに該当する。ここで、図12を例とすると、rv→yvの伝達関数は、式(29)と同様に式(47)で与えられ、Q→yvの伝達関数は式(30)と同様に式(48)で与えられる。ただし、式(47)および式(48)におけるWsvは、式(45)のWryvと式(45)のWmv−1の積(WryvWmv−1)を用いて式(49)で与えられる。

【0111】

【数47】

【0112】

【数48】

【0113】

【数49】

【0114】

式(47)および式(48)において、Wsv(z)≒1であれば式(50)となる。これにより、rv→yvの伝達特性はH2のみで定めることができ、Q→yvの伝達特性はkzvで定めることができる。すなわち、通常の入力(rv)に対する応答と、外乱(Q)に対する応答をそれぞれ独立に制御できる近似的2自由度制御が実現可能になる。

【0115】

【数50】

【0116】

特に限定はされないが、本実施の形態では、電流制御器の場合と同様にして、根軌跡から、kzvが変化したときに移動する極の値が全てH2より十分小さくなるよう、例えばkzv=0.25とする。この場合、図13の電圧制御器VCMPの各係数は、式(46)により、それぞれ、krv=0.01316、kf=−45.069、kiv=0.00329となる。

【0117】

《(4)電源装置(力率改善装置)の主要な構成および効果の纏め》

図14は、本発明の実施の形態1による電源装置において、その昇圧コンバータ部の回路モデルの一例を纏めた説明図である。項目(2−1)で述べたように、本実施の形態による電源装置では、制御対象となる昇圧コンバータ部BSTCをディジタル制御するために、BSTCを図14に示すような状態方程式によってモデル化する。この際には、まず、PFC用昇圧コンバータの等価回路(S101)を基に連続時間の状態方程式を求め(S102)、この連続時間の状態方程式を離散化された状態方程式に変換する(S103)。更に、アナログ・ディジタル変換回路の変換時間やプロセッサの演算時間等の遅延時間を考慮し、これを反映した状態ξ1を追加し、遅延時間をシステムの入力遅延時間Ld=0.99Tsとして、S103における制御対象の離散化された状態方程式に反映させる(S104)。その結果、操作量(デューティ比)vを入力とし、インダクタ電流iL、出力電圧vo、およびシステム入力遅延時間ξ1を状態とする離散化された状態方程式が得られる。

【0118】

図15は、本発明の実施の形態1による電源装置において、その構成例を纏めたブロック線図である。図15においては、昇圧コンバータ部BSTCと、電流制御器ICMPと、電圧制御器VCMPと、乗算器MULが示されている。このうち、ICMP,VCMP,MULが図2で述べたように力率改善装置(PFC)の一部を構成する制御器に該当する。力率改善装置(PFC)(制御器)は、図14で説明した昇圧コンバータ部BSTCの回路モデルに基づいてその内部構成が定められる。ICMPは、状態フィードバック部FBBKとロバスト補償器RTCMiを備えている。

【0119】

状態フィードバック部FBBKは、項目(2−2)で述べたように、状態フィードバックゲインF=[f1 f2 f3]と、直流ゲインを補償する(λi→iLの直流ゲインを1にする)ためのフィードフォワードゲインGiと、加算器(減算器)ADD1を備える。ロバスト補償器RTCMiは、項目(2−3)で述べたように、BSTCおよびFBBKを制御対象として、当該制御対象を1次で近似した際の逆システムとロウパスフィルタとを備えている。ただし、前述したように、当該逆システムおよびロウパスフィルタは等価変換されることで、RTCMiは、係数(−kzi/(1−H1i))と、係数および積分器(kzi/(z−1))と、加算器(減算器)ADD2,ADD3を備える。なお、パラメータzは、サンプリング周期をTとしてejωTに等しい。

【0120】

電圧制御器VCMPは、状態フィードバック補償部FBCMとロバスト補償器RTCMvを備えている。FBCMは、項目(3−2)で述べたように、直流ゲインを補償する(λv→voの直流ゲインを1にする)ためのフィードフォワードゲインGvを備える。RTCMvは、項目(3−3)で述べたように、BSTC,FBBK,RTCMi,MULを制御対象として、当該制御対象を1次で近似した際の逆システムとロウパスフィルタとを備えている。ただし、前述したように、当該逆システムおよびロウパスフィルタは等価変換されることで、RTCMvは、係数(−kzv/(1−H2v))と、係数および積分器(kzv/(z−1))と、加算器(減算器)ADD4,ADD5を備える。

【0121】

以上のように、本実施の形態による電源装置(力率改善装置(PFC))は、PFCを電流ループと電圧ループから構成する。電流ループでは、制御対象に状態フィードバック則を適用し、更に近似的な逆システムとロウパスフィルタで構成されるロバスト補償器を加えることで2自由度制御が行われる。一方、電圧ループでは、簡素化のため新たに状態フィードバック則の適用は行わずに、電流ループ全体の簡易的(近似的)な逆システムとロウパスフィルタで構成されるロバスト補償器を備えることで2自由度制御が行われる。電流ループ、電圧ループ共に2自由度制御が行われるため、目標値制御に対する応答と外乱制御に対する応答を独立に設定でき、入力電流に対する応答と負荷変動などの動特性に対する応答を同時に改善できる。すなわち、高速応答とロバスト性の両立が実現可能になる。

【0122】

更に、電圧ループは、電流ループのような状態フィードバック則の適用を行わずに、ロバスト補償器を備えた簡素な構成で実現している。これにより、設計の容易化が図れ、また、電圧ループに状態フィードバック則の適用を行った場合と比較して積和演算回数等が減るため、PFCの実動作における演算時間の短縮等が可能となる。なお、図15には、構成を判り易くするため、図7に示したような等価変換前のブロック線図が示されているが、勿論、これに対して図8に示したような等価変換を行い、これに基づいてPFCを構成することも可能である。

【0123】

図16は、図15を等価変換したブロック線図である。図16のブロック線図は、前述した図13のブロック線図と同一のものである。図16において、電流制御器ICMPは、フィードバック係数k1,k2,k3と、フィードフォワード係数krと、積分器(1/(z−1))と、係数kiと、加算器(減算器)ADD6,ADD7を備える。一方、電圧制御器VCMPは、フィードバック係数kfと、フィードフォワード係数krvと、積分器(1/(z−1))と、係数kivと、加算器(減算器)ADD8,ADD9を備える。

【0124】

《(5)比較例との対比ならびに検証結果》

図17は、本発明の実施の形態1による電源装置において、その比較例として検討した電源装置の構成例を示すブロック線図である。図17に示す電源装置は、例えば、前述した非特許文献1に示されるようなPI(P:比例、I:積分)制御器を備えている。電流ループのPI制御器IPIは、係数kpiからなるP部と、(1/(z−1))および係数kiiからなるI部を備え、その外側に位置する電圧ループのPI制御器VPIは、係数kpvからなるP部と、(1/(z−1))および係数kivからなるI部を備える。

【0125】

図18(a)、(b)は、動特性変化に対する出力電圧と入力電流の変化を検証した結果を示すものであり、図18(a)は図15又は図16の構成例を用いた場合の結果であり、図18(b)はその比較例となる図17の構成例を用いた場合の結果である。図18(a)、(b)から判るように、図15又は図16の構成例を用いることで、図17の構成例と比較して外乱に対する出力電圧および入力電流の変動を抑制することが可能になる。例えば、図18(b)では、外乱に対して20V程度の出力電圧変動が生じているが、図18(a)では、それが7V程度に抑制されている。すなわち、図15又は図16の構成例を用いることで、図17の構成例と比較してロバスト性を向上させることができる。図19は、図15又は図16の構成例を用いた場合の力率改善効果を検証した結果を示す図である。ここでは、出力電圧vo=385V、RL=300Ωとして、0.994程度の力率が得られている。

【0126】

以上、本実施の形態1による力率改善装置および電源装置を用いることで、代表的には簡素な構成で高速応答とロバスト性の両立が実現可能となる。

【0127】

(実施の形態2)

図20は、本発明の実施の形態2による電源装置において、その構成例を纏めたブロック線図である。図20に示す電源装置は、前述した図16の変形例となっており、図16のVCMPが図20の電圧制御器VCMPaに変更され、図16のICMPが図20の電流制御器ICMPaに変更された構成となっている。VCMPaは、図16のVCMPからフィードフォワード係数Krvが削除された構成を備えており、ICMPaは、図16のVCMPからフィードフォワード係数Krが削除された構成を備えている。

【0128】

例えば前述した図7の構成例において、係数kzが十分に大きく、「(z−1+kz)/(z−1+kz)≒kz/(z−1+kz)」と近似できる場合、図7におけるrからλへのフィードフォワード経路を近似的に削除することができる。この場合、図8の電流制御器ICMPにおけるkrのフィードフォワード経路は必ずしも必要ではなくなる。すなわち、図15の構成例において、kziが十分に大きい場合には図15のICMPにおけるriからλiへのフィードフォワード経路を近似的に削除することができ、図16のICMPにおけるkrのフィードフォワード経路は必ずしも必要ではなくなる。これと同様に、図16の電圧制御器VCMPにおいても、図15の係数kzvが十分に大きい場合には図16の係数Krvのフィードフォワード経路は必ずしも必要ではなくなる。

【0129】

このように、フォードフォワード経路の削除を行うことで、力率改善装置(PFC)の構成をより簡素化することができ、また、PFCの動作に伴う演算時間をより短縮することが可能になる。

【0130】

(実施の形態3)

図21は、本発明の実施の形態3による電源装置において、その構成例を纏めたブロック線図である。図21に示す電源装置は、前述した図16の変形例となっており、図16のVCMPが図20の電圧ループ用PI制御器VPIに変更された構成となっている。VPIは、図17の場合と同様に、係数kpvからなるP(比例)部と、積分器(1/(z−1))および係数kivからなるI(積分)部と、2個の加算器(減算器)ADD10,ADD11を備える。

【0131】

前述したように、電流ループに関しては、電流制御器ICMPによって高いロバスト性が実現できると共に、電流ループ全体を十分に近似度の高い1次モデルで近似することができる。このため、図21に示すように、電圧制御器を一般的なPI制御器VPI等で構成した場合でも、簡素な構成で、ある程度十分な高速応答とロバスト性の両立が実現可能となる。

【0132】

(実施の形態4)

図22は、本発明の実施の形態4による電源装置において、その構成の一例を示すブロック図である。図22に示す電源装置は、前述した図1の電源装置の変形例となっており、図1と比較して昇圧コンバータ部の構成が異なっている。図22の昇圧コンバータ部BSTCaは、図1のBSTCに対して、インダクタL1、ダイオードD1、スイッチ用トランジスタQ1、およびドライバ回路DRV2が追加されている。L1およびD1は直列接続され、当該直列接続回路が前述したインダクタL0およびダイオードD0からなる直列接続回路と並列に接続される。Q1は、ソースが基準電源ノードに、ドレインがL1とD1の接続ノード(D1のアノード側)にそれぞれ接続され、ゲートがDRV2によって制御される。DRV2は、マイクロコントローラユニット(力率改善装置の一部を構成する制御器)MCU内のPWM信号生成回路PWMGから出力されたPWM信号を入力として動作する。

【0133】

ドライバ回路DRV2のPWM信号は、ドライバ回路DRV1のPWM信号のサイクルを基準としてそこから半サイクルずれるタイミングで生成される。これによって、スイッチ用トランジスタQ0,Q1では、インターリーブ方式によるスイッチングが行われる。このようなインターリーブ方式を適用することで、スイッチングによって生じるL0,L1のインダクタ電流io0,io1のリプル成分を低減できるため、結果的に、図1の場合と比較して入力電流iacに生じる高調波成分をより低減することが可能になる。力率改善装置の制御器は実施の形態1、2または3と同様の構成に、インターリーブ制御を加えた構成である。

【0134】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

【産業上の利用可能性】

【0135】

本実施の形態による力率改善装置および電源装置は、特に、マイクロコンピュータ(又はディジタルシグナルプロセッサ(DSP))等によるディジタル演算処理を用いて力率改善を行うAC−DCコンバータに適用して有益なものであり、これに限らず、PFC機能を備えたAC−DCコンバータ全般に広く適用可能である。

【符号の説明】

【0136】

ADC アナログ・ディジタル変換回路

ADD 加算器(減算器)

AVG 平均値計算器

BSTC 昇圧コンバータ部

CI,CO 容量

CTL 制御回路

D ダイオード

DRV ドライバ回路

FLT フィルタ

ICMP 電流制御器

IDET 電流検出回路

IPI,VPI PI制御器

L インダクタ

MCU マイクロコントローラユニット

MUL 乗算器

PWMG PWM信号生成回路

Q スイッチ用トランジスタ

RCT 整流回路

RL 負荷

RTCM ロバスト補償器

VAC 外部交流電源

VCMP 電圧制御器

【特許請求の範囲】

【請求項1】

インダクタ、ダイオードおよびスイッチ用トランジスタを含み、交流入力電圧が入力される整流器の出力電圧を受けて所定の直流電圧値を持つ第1出力電圧を生成する昇圧コンバータ部を制御対象とし、

前記交流入力電圧を反映した第1目標信号、前記インダクタに流れるインダクタ電流、前記第1出力電圧をそれぞれディジタル信号に変換し、前記第1目標信号に対応する第1ディジタル信号、前記インダクタ電流に対応する第2ディジタル信号、前記第1出力電圧に対応する第3ディジタル信号を出力するアナログ・ディジタル変換器と、

前記第1および第2ディジタル信号を受けて、前記インダクタ電流を前記交流入力電圧に追従させるための第1操作量を生成し、前記第1操作量に基づくデューティ比を持つPWM信号を前記スイッチ用トランジスタに向けて出力する電流ループと、

前記第3ディジタル信号を受けて、前記第1出力電圧を予め定められた目標電圧に設定するための第2操作量を生成し、前記第2操作量を前記第1目標信号に反映させる電圧ループとを備え、

前記電流ループは、

前記昇圧コンバータ部の極を定めるための状態フィードバック部と、

前記状態フィードバック部を含めた前記昇圧コンバータ部の第1伝達関数に対する近似的な第1逆伝達関数ならびに第1ディジタルロウパスフィルタを含み、前記電流ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第1ロバスト補償器とを有することを特徴とする力率改善装置。

【請求項2】

請求項1記載の力率改善装置において、

前記電圧ループは、前記電流ループを含めた前記昇圧コンバータ部の第2伝達関数に対する近似的な第2逆伝達関数ならびに第2ディジタルロウパスフィルタを含み、前記電圧ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第2ロバスト補償器を有することを特徴とする力率改善装置。

【請求項3】

請求項2記載の力率改善装置において、

前記第1逆伝達関数は、前記第1伝達関数を1次近似した関数に基づいて設定され、

前記第2逆伝達関数は、前記第2伝達関数を1次近似した関数に基づいて設定されることを特徴とする力率改善装置。

【請求項4】

請求項3記載の力率改善装置において、

前記第1および第2ディジタルロウパスフィルタのそれぞれの伝達関数K(z)は、係数kzおよびパラメータz(=exp(jωT))を用いて、

K(z)=kz/(z−1+kz)

で定められることを特徴とする力率改善装置。

【請求項5】

請求項4記載の力率改善装置において、

前記第1逆伝達関数は、前記第1伝達関数の出力を入力とし、

前記第1ディジタルロウパスフィルタは、前記第1伝達関数の入力から前記第1逆伝達関数の出力を減算した値を入力とし、出力を前記第1伝達関数の入力に帰還し、

前記第2逆伝達関数は、前記第2伝達関数の出力を入力とし、

前記第2ディジタルロウパスフィルタは、前記第2伝達関数の入力から前記第2逆伝達関数の出力を減算した値を入力とし、出力を前記第2伝達関数の入力に帰還することを特徴とする力率改善装置。

【請求項6】

請求項3記載の力率改善装置において、

前記昇圧コンバータ部は、デューティ比を操作量とし、前記インダクタ電流と、前記第1出力電圧と、前記アナログ・ディジタル変換器の遅延を含めたシステム遅延時間とを状態変数とする離散化された状態方程式で表され、

前記状態フィードバック部は、前記インダクタ電流を前記デューティ比に反映させるための第1フィードバックゲインと、前記第1出力電圧を前記デューティ比に反映させるための第2フィードバックゲインと、前記システム遅延時間を前記デューティ比に反映させるための第3フィードバックゲインとを備えることを特徴とする力率改善装置。

【請求項7】

請求項3記載の力率改善装置において、

前記第1伝達関数は、代表極となる第1極によって1次近似され、

前記第1伝達関数における前記第1極とは異なる第2極は、前記第1伝達関数の零点の一つを打ち消す値に設定され、

前記第2伝達関数は、前記第2極によって1次近似されることを特徴とする力率改善装置。

【請求項8】

請求項2記載の力率改善装置において、

前記電流ループおよび前記電圧ループは、プロセッサによる演算処理で実現されることを特徴とする力率改善装置。

【請求項9】

交流入力電圧を整流する整流器と、

昇圧コンバータ部と、

プロセッサを含んだ力率改善装置とを備え、

前記昇圧コンバータ部は、

一端が前記整流器の出力に結合される第1インダクタと、

アノードが前記第1インダクタの他端に結合される第1ダイオードと、

一端が前記第1ダイオードのカソードに結合され、他端が基準電圧ノードに結合され、両端間に第1出力電圧を生成する出力容量と、

前記第1ダイオードのアノードと前記基準電圧ノードの間に結合される第1スイッチ用トランジスタと、

第1PWM信号が入力され、前記第1PWM信号に基づいて前記第1スイッチ用トランジスタのオン・オフを制御する第1ドライバ回路とを備え、

前記力率改善装置は、

前記交流入力電圧を反映した第1目標信号、前記第1インダクタに流れるインダクタ電流、前記第1出力電圧をそれぞれディジタル信号に変換し、前記第1目標信号に対応する第1ディジタル信号、前記インダクタ電流に対応する第2ディジタル信号、前記第1出力電圧に対応する第3ディジタル信号を出力するアナログ・ディジタル変換器と、

前記第1および第2ディジタル信号を受けて、前記インダクタ電流を前記交流入力電圧に追従させるための第1操作量を生成し、前記第1操作量に基づくデューティ比を持つ前記第1PWM信号を前記第1ドライバ回路に向けて出力する電流ループと、

前記第3ディジタル信号を受けて、前記第1出力電圧を予め定められた目標電圧に設定するための第2操作量を生成し、前記第2操作量を前記第1目標信号に反映させる電圧ループとを備え、

前記電流ループは、

前記昇圧コンバータ部の極を定めるための状態フィードバック部と、

前記状態フィードバック部を含めた前記昇圧コンバータ部の第1伝達関数に対する近似的な第1逆伝達関数ならびに第1ディジタルロウパスフィルタを含み、前記電流ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第1ロバスト補償器とを有することを特徴とする電源装置。

【請求項10】

請求項9記載の電源装置において、

前記電圧ループは、前記電流ループを含めた前記昇圧コンバータ部の第2伝達関数に対する近似的な第2逆伝達関数ならびに第2ディジタルロウパスフィルタを含み、前記電圧ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第2ロバスト補償器を有することを特徴とする電源装置。

【請求項11】

請求項10記載の電源装置において、

前記第1逆伝達関数は、前記第1伝達関数を1次近似した関数に基づいて設定され、

前記第2逆伝達関数は、前記第2伝達関数を1次近似した関数に基づいて設定されることを特徴とする電源装置。

【請求項12】

請求項11記載の電源装置において、

前記第1および第2ディジタルロウパスフィルタのそれぞれの伝達関数K(z)は、係数kzおよびパラメータz(=exp(jωT))を用いて、

K(z)=kz/(z−1+kz)

で定められることを特徴とする電源装置。

【請求項13】

請求項12記載の電源装置において、

前記第1逆伝達関数は、前記第1伝達関数の出力を入力とし、

前記第1ディジタルロウパスフィルタは、前記第1伝達関数の入力から前記第1逆伝達関数の出力を減算した値を入力とし、出力を前記第1伝達関数の入力に帰還し、

前記第2逆伝達関数は、前記第2伝達関数の出力を入力とし、

前記第2ディジタルロウパスフィルタは、前記第2伝達関数の入力から前記第2逆伝達関数の出力を減算した値を入力とし、出力を前記第2伝達関数の入力に帰還することを特徴とする電源装置。

【請求項14】

請求項11記載の電源装置において、

前記昇圧コンバータ部は、デューティ比を操作量とし、前記インダクタ電流と、前記第1出力電圧と、前記アナログ・ディジタル変換器の遅延を含めたシステム遅延時間とを状態変数とする離散化された状態方程式で表され、

前記状態フィードバック部は、前記インダクタ電流を前記デューティ比に反映させるための第1フィードバックゲインと、前記第1出力電圧を前記デューティ比に反映させるための第2フィードバックゲインと、前記システム遅延時間を前記デューティ比に反映させるための第3フィードバックゲインとを備えることを特徴とする電源装置。

【請求項15】

請求項11記載の電源装置において、

前記第1伝達関数は、代表極となる第1極によって1次近似され、

前記第1伝達関数における前記第1極とは異なる第2極は、前記第1伝達関数の零点の一つを打ち消す値に設定され、

前記第2伝達関数は、前記第2極によって1次近似されることを特徴とする電源装置。

【請求項16】

請求項11記載の電源装置において、

前記昇圧コンバータ部は、さらに、

一端が前記整流器の出力に結合される第2インダクタと、

アノードが前記第2インダクタの他端に結合され、カソードが前記第1ダイオードのカソードに結合される第2ダイオードと、

前記第2ダイオードのアノードと前記基準電圧ノードの間に結合される第2スイッチ用トランジスタと、

第2PWM信号が入力され、前記第2PWM信号に基づいて前記第2スイッチ用トランジスタのオン・オフを制御する第2ドライバ回路とを備え、

前記力率改善装置は、さらに、前記第1PWM信号のサイクルから半サイクルずれるタイミングで前記第2ドライバ回路に向けて前記第2PWM信号を出力することを特徴とする電源装置。

【請求項1】

インダクタ、ダイオードおよびスイッチ用トランジスタを含み、交流入力電圧が入力される整流器の出力電圧を受けて所定の直流電圧値を持つ第1出力電圧を生成する昇圧コンバータ部を制御対象とし、

前記交流入力電圧を反映した第1目標信号、前記インダクタに流れるインダクタ電流、前記第1出力電圧をそれぞれディジタル信号に変換し、前記第1目標信号に対応する第1ディジタル信号、前記インダクタ電流に対応する第2ディジタル信号、前記第1出力電圧に対応する第3ディジタル信号を出力するアナログ・ディジタル変換器と、

前記第1および第2ディジタル信号を受けて、前記インダクタ電流を前記交流入力電圧に追従させるための第1操作量を生成し、前記第1操作量に基づくデューティ比を持つPWM信号を前記スイッチ用トランジスタに向けて出力する電流ループと、

前記第3ディジタル信号を受けて、前記第1出力電圧を予め定められた目標電圧に設定するための第2操作量を生成し、前記第2操作量を前記第1目標信号に反映させる電圧ループとを備え、

前記電流ループは、

前記昇圧コンバータ部の極を定めるための状態フィードバック部と、

前記状態フィードバック部を含めた前記昇圧コンバータ部の第1伝達関数に対する近似的な第1逆伝達関数ならびに第1ディジタルロウパスフィルタを含み、前記電流ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第1ロバスト補償器とを有することを特徴とする力率改善装置。

【請求項2】

請求項1記載の力率改善装置において、

前記電圧ループは、前記電流ループを含めた前記昇圧コンバータ部の第2伝達関数に対する近似的な第2逆伝達関数ならびに第2ディジタルロウパスフィルタを含み、前記電圧ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第2ロバスト補償器を有することを特徴とする力率改善装置。

【請求項3】

請求項2記載の力率改善装置において、

前記第1逆伝達関数は、前記第1伝達関数を1次近似した関数に基づいて設定され、

前記第2逆伝達関数は、前記第2伝達関数を1次近似した関数に基づいて設定されることを特徴とする力率改善装置。

【請求項4】

請求項3記載の力率改善装置において、

前記第1および第2ディジタルロウパスフィルタのそれぞれの伝達関数K(z)は、係数kzおよびパラメータz(=exp(jωT))を用いて、

K(z)=kz/(z−1+kz)

で定められることを特徴とする力率改善装置。

【請求項5】

請求項4記載の力率改善装置において、

前記第1逆伝達関数は、前記第1伝達関数の出力を入力とし、

前記第1ディジタルロウパスフィルタは、前記第1伝達関数の入力から前記第1逆伝達関数の出力を減算した値を入力とし、出力を前記第1伝達関数の入力に帰還し、

前記第2逆伝達関数は、前記第2伝達関数の出力を入力とし、

前記第2ディジタルロウパスフィルタは、前記第2伝達関数の入力から前記第2逆伝達関数の出力を減算した値を入力とし、出力を前記第2伝達関数の入力に帰還することを特徴とする力率改善装置。

【請求項6】

請求項3記載の力率改善装置において、

前記昇圧コンバータ部は、デューティ比を操作量とし、前記インダクタ電流と、前記第1出力電圧と、前記アナログ・ディジタル変換器の遅延を含めたシステム遅延時間とを状態変数とする離散化された状態方程式で表され、

前記状態フィードバック部は、前記インダクタ電流を前記デューティ比に反映させるための第1フィードバックゲインと、前記第1出力電圧を前記デューティ比に反映させるための第2フィードバックゲインと、前記システム遅延時間を前記デューティ比に反映させるための第3フィードバックゲインとを備えることを特徴とする力率改善装置。

【請求項7】

請求項3記載の力率改善装置において、

前記第1伝達関数は、代表極となる第1極によって1次近似され、

前記第1伝達関数における前記第1極とは異なる第2極は、前記第1伝達関数の零点の一つを打ち消す値に設定され、

前記第2伝達関数は、前記第2極によって1次近似されることを特徴とする力率改善装置。

【請求項8】

請求項2記載の力率改善装置において、

前記電流ループおよび前記電圧ループは、プロセッサによる演算処理で実現されることを特徴とする力率改善装置。

【請求項9】

交流入力電圧を整流する整流器と、

昇圧コンバータ部と、

プロセッサを含んだ力率改善装置とを備え、

前記昇圧コンバータ部は、

一端が前記整流器の出力に結合される第1インダクタと、

アノードが前記第1インダクタの他端に結合される第1ダイオードと、

一端が前記第1ダイオードのカソードに結合され、他端が基準電圧ノードに結合され、両端間に第1出力電圧を生成する出力容量と、

前記第1ダイオードのアノードと前記基準電圧ノードの間に結合される第1スイッチ用トランジスタと、

第1PWM信号が入力され、前記第1PWM信号に基づいて前記第1スイッチ用トランジスタのオン・オフを制御する第1ドライバ回路とを備え、

前記力率改善装置は、

前記交流入力電圧を反映した第1目標信号、前記第1インダクタに流れるインダクタ電流、前記第1出力電圧をそれぞれディジタル信号に変換し、前記第1目標信号に対応する第1ディジタル信号、前記インダクタ電流に対応する第2ディジタル信号、前記第1出力電圧に対応する第3ディジタル信号を出力するアナログ・ディジタル変換器と、

前記第1および第2ディジタル信号を受けて、前記インダクタ電流を前記交流入力電圧に追従させるための第1操作量を生成し、前記第1操作量に基づくデューティ比を持つ前記第1PWM信号を前記第1ドライバ回路に向けて出力する電流ループと、

前記第3ディジタル信号を受けて、前記第1出力電圧を予め定められた目標電圧に設定するための第2操作量を生成し、前記第2操作量を前記第1目標信号に反映させる電圧ループとを備え、

前記電流ループは、

前記昇圧コンバータ部の極を定めるための状態フィードバック部と、

前記状態フィードバック部を含めた前記昇圧コンバータ部の第1伝達関数に対する近似的な第1逆伝達関数ならびに第1ディジタルロウパスフィルタを含み、前記電流ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第1ロバスト補償器とを有することを特徴とする電源装置。

【請求項10】

請求項9記載の電源装置において、

前記電圧ループは、前記電流ループを含めた前記昇圧コンバータ部の第2伝達関数に対する近似的な第2逆伝達関数ならびに第2ディジタルロウパスフィルタを含み、前記電圧ループの目標値制御に対する応答と外乱制御に対する応答とを個別に設定するための第2ロバスト補償器を有することを特徴とする電源装置。

【請求項11】

請求項10記載の電源装置において、

前記第1逆伝達関数は、前記第1伝達関数を1次近似した関数に基づいて設定され、

前記第2逆伝達関数は、前記第2伝達関数を1次近似した関数に基づいて設定されることを特徴とする電源装置。

【請求項12】

請求項11記載の電源装置において、

前記第1および第2ディジタルロウパスフィルタのそれぞれの伝達関数K(z)は、係数kzおよびパラメータz(=exp(jωT))を用いて、

K(z)=kz/(z−1+kz)

で定められることを特徴とする電源装置。

【請求項13】

請求項12記載の電源装置において、

前記第1逆伝達関数は、前記第1伝達関数の出力を入力とし、

前記第1ディジタルロウパスフィルタは、前記第1伝達関数の入力から前記第1逆伝達関数の出力を減算した値を入力とし、出力を前記第1伝達関数の入力に帰還し、

前記第2逆伝達関数は、前記第2伝達関数の出力を入力とし、

前記第2ディジタルロウパスフィルタは、前記第2伝達関数の入力から前記第2逆伝達関数の出力を減算した値を入力とし、出力を前記第2伝達関数の入力に帰還することを特徴とする電源装置。

【請求項14】

請求項11記載の電源装置において、

前記昇圧コンバータ部は、デューティ比を操作量とし、前記インダクタ電流と、前記第1出力電圧と、前記アナログ・ディジタル変換器の遅延を含めたシステム遅延時間とを状態変数とする離散化された状態方程式で表され、

前記状態フィードバック部は、前記インダクタ電流を前記デューティ比に反映させるための第1フィードバックゲインと、前記第1出力電圧を前記デューティ比に反映させるための第2フィードバックゲインと、前記システム遅延時間を前記デューティ比に反映させるための第3フィードバックゲインとを備えることを特徴とする電源装置。

【請求項15】

請求項11記載の電源装置において、

前記第1伝達関数は、代表極となる第1極によって1次近似され、

前記第1伝達関数における前記第1極とは異なる第2極は、前記第1伝達関数の零点の一つを打ち消す値に設定され、

前記第2伝達関数は、前記第2極によって1次近似されることを特徴とする電源装置。

【請求項16】

請求項11記載の電源装置において、

前記昇圧コンバータ部は、さらに、

一端が前記整流器の出力に結合される第2インダクタと、

アノードが前記第2インダクタの他端に結合され、カソードが前記第1ダイオードのカソードに結合される第2ダイオードと、

前記第2ダイオードのアノードと前記基準電圧ノードの間に結合される第2スイッチ用トランジスタと、

第2PWM信号が入力され、前記第2PWM信号に基づいて前記第2スイッチ用トランジスタのオン・オフを制御する第2ドライバ回路とを備え、

前記力率改善装置は、さらに、前記第1PWM信号のサイクルから半サイクルずれるタイミングで前記第2ドライバ回路に向けて前記第2PWM信号を出力することを特徴とする電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図20】

【図21】

【図22】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図20】

【図21】

【図22】

【図18】

【図19】

【公開番号】特開2013−59141(P2013−59141A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−194547(P2011−194547)

【出願日】平成23年9月7日(2011.9.7)

【出願人】(504133110)国立大学法人電気通信大学 (383)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月7日(2011.9.7)

【出願人】(504133110)国立大学法人電気通信大学 (383)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]