ワンダ測定装置及びワンダ測定方法

【課題】簡単な回路構成で高精度なワンダ測定が行える。

【解決手段】正弦波生成部4a,4bは、クロック信号からなる被測定信号と基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力する。位相復調部6は、2つの正弦波電圧信号u1(t),u2(t)を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力する。制御部8は、予め設定される被測定信号の公称周波数と基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を1組の正弦波生成部4a,4bに設定して2つの正弦波電圧信号u1(t),u2(t)の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する。

【解決手段】正弦波生成部4a,4bは、クロック信号からなる被測定信号と基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力する。位相復調部6は、2つの正弦波電圧信号u1(t),u2(t)を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力する。制御部8は、予め設定される被測定信号の公称周波数と基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を1組の正弦波生成部4a,4bに設定して2つの正弦波電圧信号u1(t),u2(t)の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パルス状の被測定信号のパルス間隔の変動(ゆれ)のうち、特に長期位相変動であるワンダを測定するワンダ測定装置及びワンダ測定方法に関する。

【背景技術】

【0002】

例えばSDH/SONETやOTNと呼ばれる長距離伝送方式では、同期式が広く使用されている。そして、系全体が同期している通信ネットワークにおいて、同期式変換器や伝送装置から出力される信号(データやクロック)を被測定信号とし、この被測定信号のワンダを測定するワンダ測定装置が知られている。

【0003】

図5は特許文献1に開示されるジッタ/ワンダ解析装置の概略構成を示すブロック図である。なお、図5では、特許文献1の図1における測定信号生成回路、連続周期測定回路、バッファメモリをまとめてタイムインターバルカウンタ53として図示している。

【0004】

図5のジッタ/ワンダ解析装置51では、異なる周波数の入力信号(被測定信号、基準信号)をそれぞれ分周器52(52a,52b)で分周し、一組の同一周波数を持つクロック信号(又は繰り返しパルス信号)に変換している。この変換後の周波数は、8kHzや4kHzが使用されることが多い。その理由は、SDH/SONETやOTNに使用される伝送レートや基準信号の周波数が必ず8kHzの倍数で表されるためである。

【0005】

なお、ワンダは、10Hz以下の位相変動成分と一般的に定義されているため、8kHzや4kHzに分周しても検出可能である。

【0006】

そして、タイムインターバルカウンタ53は、一組の同一周波数を持つクロック信号が入力されると、両者の時間差系列x(n)をワンダ計算部54に出力する。その後、ワンダ計算部54は、タイムインターバルカウンタ53からのx(n)を用いて、MTIEやTDEVと呼ばれるワンダ量を計算し、この計算した結果が表示部55に表示される。

【0007】

ところで、被測定信号と基準信号をそれぞれ分周器52a,52bで分周した際、両者を同一周波数にしないと、タイムインターバルカウンタ53で測定される時間差系列x(n)には、周波数差(オフセット周波数)に起因する測定誤差が加算されてしまう。

【0008】

タイムインターバルカウンタ53には、様々な回路方式があるが、基本的には、基準信号に対する被測定信号の時間差変動を測るため、入力信号間のパルスの時間差を一定間隔で測定している。そして、この入力信号間のパルスの時間差と位相差は、φ(t)=2πf0×x(t)…式(1)を用いて相互に変換可能である。

【0009】

上記式(1)において、φ(t)は時刻tにおける瞬時位相差(単位はラジアン)、x(t)は時刻tにおける時間差、f0は入力信号周波数であり、連続量x(t)を一定間隔のサンプル系列で表したものがx(n)(n=0,1,2,・・・)である。

【0010】

なお、タイムインターバルカウンタ53については、本発明とは直接関係ないので、ここでは詳説しない(具体的には、特許文献1を参照)。

【0011】

ところで、ITU−T等で規定されるSDH/SONET伝送装置のワンダは、一般的にns(ナノ秒)オーダーで表される。このため、特許文献1の方式を採用したタイムインターバルカウンタは、その1/10である0.1ns程度の測定精度を持たなければならない。

【0012】

仮に、0.1nsの時間分解能のタイムインターバルカウンタ53を実現するためには、入力信号間のパルスの時間差を一定間隔でカウントする単純なカウンタ方式では、10GHzのカウンタが必要になる。しかし、そのような動作で複雑な回路を動作させるのは難しく、部品コストも増大するという課題がある。

【0013】

このため、特許文献1に開示されるように、カウンタ周波数には100MHzを使用して10nsの分解能で時間計測をする一方、それ以上の時間精度を得るために、端数時間電圧変換器(特許文献1の図14)を用いて、時間分解能を向上させている。

【0014】

このように、タイムインターバルカウンタ53は、論理回路だけで実現することができず、端数時間電圧変換器のようなアナログ回路が必要になる。その結果、回路を小型化できず、またアナログ回路の部品ばらつきを補正するために、校正手段が別途必要になるという課題が生じる。

【0015】

図6は特許文献2に開示される周波数安定度測定装置の概略構成を示すブロック図である。なお、図6では、特許文献1の図5における第1のHPF、第2のHPF、第1の90度移相器、第2の90度移相器、演算回路、移送検波器を位相復調部、ワンダ計算部として図示している。

【0016】

図6の測定装置61では、入力信号として、同一又は異なる周波数の正弦波信号S1(t),S2(t)を入力し、周波数変換部62により、同一周波数の正弦波電圧u1(t),u2(t)信号に変換している。ADC(A/D変換器)63(63a,63b)では、周波数変換部62からの2つの正弦波信号u1(t),u2(t)を一定周期でサンプリングし、系列u1(n),u2(n)(n=0,1,2,・・・)として出力する。そして、位相復調部64では、ADC63a,63bからのu1(n),u2(n)間の瞬時位相の差φ(n)を位相復調方式によって検出している。位相復調方式は、例えば特許文献2が従来技術として挙げている直交検波方式(特許文献2の図10)でも良いし、特許文献2に開示される方式でも良い。そして、位相復調部64は、瞬時位相の差φ(n)から時間差系列x(n)をx(n)=φ(n)/2πf0…式(2)を用いて算出している。但し、f0はADCの入力周波数である。そして、ワンダ計算部65は、位相復調部64からのx(n)を用いて、MTIEやTDEVと呼ばれるワンダ量を計算し、この計算した結果が表示部66に表示される。

【0017】

この特許文献2の測定装置61の特徴は、周波数変換部62以降が、市販の低速ADCとプロセッサで実現可能な演算回路だけで構築できる点にある。つまり、前述したタイムインターバルカウンタ53のような校正を必要とするアナログ回路が不要である。また、回路の動作速度も数10k〜数100kHz程度となるため、タイムインターバルカウンタ53のような高速動作する回路が不要であり、回路に高額な高周波部品を使用せずに済む。

【0018】

ところで、特許文献2では、周波数変換部62として、(a)ミキサ方式、(b)分周器方式、(c)PLL方式の3つの方式を挙げている。

【0019】

図7(a),(b),(c)は上記3つの方式による周波数変換部62(62A,62B,62C)の各構成例を示している。図7(a)はミキサ方式の周波数変換部62Aの構成例を示している。図7(a)のミキサ方式の周波数変換部62Aは、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が等しい場合(f1≒f2)に使用される方式であり、最も高精度な測定が実現できる。

【0020】

すなわち、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が等しい場合、ローカル発振器62aが持つ固有の位相変動成分に起因する時間誤差成分は、LPF(ローパスフィルタ)62b,62bから出力される正弦波電圧信号u1(t),u2(t)に等しく含まれる。このため、後段の演算過程において上記時間誤差成分を相殺することができる。また、被測定信号S1(t)と基準信号S2(t)との間の時間差x(t)は、ミキサ62c,62cによって周波数変換比だけ増幅される。

【0021】

これらの結果、図7(a)のミキサ方式の周波数変換部62Aによれば、時間差x(n)の測定精度が大幅に向上する。しかしながら、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が異なる場合(f1≠f2)は使用できないという課題がある。

【0022】

図7(b)の分周器方式の周波数変換部62Bは、2つの分周器62d,62dの分周比を異なる値に設定すれば、被測定信号S1(t)の周波数f1と基準信号S2(n)の周波数f2が異なる場合(f1≠f2)であっても、正弦波電圧信号u1(t),u2(t)の周波数を等しくできる。なお、特許文献2の図7には示されていないが、通常、分周器から出力される信号は矩形波のため、図7(b)に示すようなLPF(又はBPF)62e,62eを介して正弦波に変換することが必要である。

【0023】

ところで、先述のように、本発明で対象とする被測定信号は、ITU−Tで定められた伝送レートが8kHzの倍数であるため、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2の最大公約数が8kHzになることが多い。この結果、正弦波電圧信号u1(t)とu2(t)の周波数は8kHzや、8KHzの整数分の1(4kHz、2kHz)が適している。

【0024】

図7(c)のPLL方式の周波数変換部62Cは、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が等しい場合(f1=f2)、異なる場合(f1≠f2)の何れの場合であっても、高精度の測定には向いていない。その理由は、PLL62f,62fに使用されているVCO62g,62gがそれぞれ固有の位相雑音(位相変動)を持っており、その差分が測定誤差になってしまうためである。

【0025】

以上の結果、被測定信号S1(t)と基準信号S2(t)の周波数f1≠f2の条件下では、図7(b)の分周器方式の周波数変換部62Bが有効である。

【先行技術文献】

【特許文献】

【0026】

【特許文献1】特開平7−83980号公報

【特許文献2】特許第3845573号公報

【発明の概要】

【発明が解決しようとする課題】

【0027】

しかしながら、上述した図7(b)の分周器方式の周波数変換部62Bを用いた構成では、0.1nsの測定精度を実現する上で問題点がある。

【0028】

例えば、正弦波電圧信号u1(t),u2(t)の周波数が8kHzとなるように分周器の分周比を設定した場合、ADCのサンプリングレートは、サンプリング定理から2倍の16kサンプル/s以上であれば良い。このような比較的低速なADCであれば、現在24bit分解能のADCが市販されている。

【0029】

但し、24bitのADCと言っても、ADC内部の回路雑音等の影響によって、実質的な分解能(ENOB)は19bit程度であることが多い。

【0030】

この実質的な分解能ENOBから求まる正弦波電圧信号u1(t),u2(t)の信号対雑音比(SNR)に起因する測定装置のx(n)に対する測定誤差を、SNR=6.02×ENOB+1.76[dB]、測定誤差ε=1/(2πf0×10SNR/20)[s](実効値)…式(3)から概算することができる。

【0031】

例えばENOB=19[bit]の時、SNR≒116[dB]、ε≒31[ps](実効値)となる。誤差ε=31[ps]は実効値のため、そのpeak−to−peak値は、ADCの内部ノイズがガウシアンノイズだと仮定すると、実効値の10〜14倍程度になる。すなわち、31×14=434ps(=0.434ns)。これでは、0.1nsの精度を実現できない。

【0032】

上述した式(3)に基づくと、測定精度を向上させるには、ADCのSNRを向上させるか、正弦波電圧信号u1(t),u2(t)の周波数f0を高くするかのどちらかである。

【0033】

まず、ADCのSNRを向上させるには、例えば2M 個のADCを用いてその出力を加算平均すれば、原理的に3×M[dB]だけSNRが向上する。仮にM=4として、16個のADCの出力を加算すれば、SNRは12dB向上する。この結果、εは1/4倍になって0.1ns程度になる。但し、この場合、ADCが16×2ch=32個となって、回路規模が増大するという課題がある。

【0034】

これに対し、周波数f0を高くする方法は、前述した図7(c)の分周器方式を用いる方法では難しい。これは、前述のように、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2の公約数が8kHz以上にならない場合があるためである。

【0035】

例えば、SDHのSTM−256で規定されている伝送レートは、39.81312Gbpsであり、このデータ信号から変換されたクロック信号(39.81312GHz)を被測定信号とし、SDHで広く使用されている同期クロック(1.544MHz)を基準信号とした場合、39.81312GHz÷4976640=8.0kHz、1.544MHz÷193=8.0kHzとなり、これらの周波数の最大公約数は8kHzである。

【0036】

したがって、分周器による分周後の周波数f0を同一にする場合、f0を8kHz以上にできない。

【0037】

そこで、周波数f0を高くするため、分周器による分周後の周波数を同一にしない場合を考えると、例えば分周後の周波数として、被測定信号:3.981312GHz÷497664=80.0kHz、基準信号:1.544MHz÷19≒81.26315789kHzとし、80kHz前後になるようにする。

【0038】

この場合、f0は約80kHzなので、測定装置のSNRに起因する測定誤差は先の例の10倍向上して、約0.04nsとなり、目標の精度0.1nsを満足する。その反面、分周後の周波数の差(周波数オフセット)に起因する測定誤差が新たに発生するという課題がある。

【0039】

ここで、分周器による分周後の周波数に差がない場合、検出される時間差x(n)は、図8(a)に示すように、長時間測定してもその値が発散しない。これに対し、分周後の周波数に差がある場合は、図8(b)に示すように、測定時間とともにx(n)の値が増大または減少する(最終的には、経過時間とともに、+∞または−∞に発散する)。

【0040】

そして、x(n)の値が大きくなると、x(n)の数値精度(ビット数)の制限から、やがてアンダーフローが生じて、測定対象であるx(n)の測定分解能が悪化する。

【0041】

例えば前述したように、分周後に1kHz程度の周波数オフセットがある場合、周波数オフセットに起因する測定誤差は、経過時間t(s)とともに、(1k/80k)×tの割合で増加する。この測定誤差は予測可能であるから、経過時間tとともに差し引けば良い。但し、ここで注意すべきことは、要求される精度0.1nsに対して、差し引く誤差が極めて大きい(t=10000sの時、125s)ので、x(n)がアンダーフローを生じずに0.1ns精度を維持するためにはx(n)のビット幅として41bit程度必要になる。

【0042】

ところが、ワンダ計算部をFPGAやDSP等で構成した場合には、ハードウェアのリソースの都合上、ビット幅には制限があり、測定時間を短く制限するか、測定精度の悪化を許容する必要が生じる。

【0043】

そこで、本発明は上記問題点に鑑みてなされたものであって、簡単な回路構成で高精度なワンダ測定が行えるワンダ測定装置及びワンダ測定方法を提供することを目的としている。

【課題を解決するための手段】

【0044】

上記目的を達成するため、本発明の請求項1に記載されたワンダ測定装置は、クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力する1組の正弦波生成部4a,4bと、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力する位相復調部6と、

前記時間差系列に基づいてワンダ量を計算するワンダ計算部9と、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を前記1組の正弦波生成部に設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する制御部8とを備えたことを特徴とする。

【0045】

請求項2に記載されたワンダ測定装置は、請求項1のワンダ測定装置において、

前記制御部8は、前記周波数チューニング・ワードの設定に基づく前記正弦波電圧信号u1(t),u2(t)の出力周波数の差を周波数オフセットΔfとして算出し、

前記周波数オフセットを用いて前記位相復調部6から出力される時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧する周波数オフセット補正部を更に備えたことを特徴とする。

【0046】

請求項3に記載されたワンダ測定方法は、クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力するステップと、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力するステップと、

前記時間差系列に基づいてワンダ量を計算するステップと、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧するステップとを含むことを特徴とする。

【0047】

請求項4に記載されたワンダ測定方法は、請求項3のワンダ測定方法において、

前記周波数チューニング・ワードの設定に基づく前記2つの正弦波電圧信号の出力周波数の差を周波数オフセットΔfとして算出するステップと、

前記周波数オフセットを用いて前記時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧するステップとを更に含むことを特徴とする。

【発明の効果】

【0048】

本発明によれば、特許文献1のタイムインターバルカウンタのような複雑で校正が必要となる高速アナログ回路を必要とせず、簡単な回路構成で回路雑音に起因する測定誤差を抑圧して高精度なワンダ測定を行うことができる。

【0049】

また、予測可能な周波数オフセットΔfに起因する測定誤差を後段の周波数オフセット補正部で除去することができる。その際、正弦波生成部としてDDSを用いたことにより、周波数オフセットΔfに起因する測定誤差は、従来の分周器方式よりも大幅に小さくなり、演算回路は少ないリソースで実現することができる。その結果、簡単な構成で高精度のワンダ測定装置を実現することができる。

【図面の簡単な説明】

【0050】

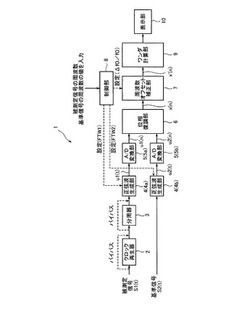

【図1】本発明に係るワンダ測定装置のブロック構成図である。

【図2】本発明に係るワンダ測定装置の概要を示すブロック図である。

【図3】本発明に係るワンダ測定装置のクロック再生器の内部構成の一例を示す図である。

【図4】(a),(b) 本発明に係るワンダ測定装置の正弦波生成部の内部構成の各例を示す図である。

【図5】特許文献1に開示されるジッタ/ワンダ解析装置の概略ブロック構成図である。

【図6】特許文献2に開示される周波数安定度測定装置の概略ブロック構成図である。

【図7】(a)〜(c) 特許文献2の周波数変換部の内部構成の各例を示す図である。

【図8】(a),(b) 分周後の周波数に差がない場合とある場合にそれぞれ検出される時間差の特性の一例を示す図である。

【発明を実施するための形態】

【0051】

以下、本発明を実施するための形態について、添付した図面を参照しながら詳細に説明する。尚、この実施の形態によりこの発明が限定されるものではなく、この形態に基づいて当業者などによりなされる実施可能な他の形態、実施例及び運用技術などはすべて本発明の範疇に含まれる。

【0052】

図1は本発明に係るワンダ測定装置のブロック構成図、図2は本発明に係るワンダ測定装置の概要を示すブロック図、図3は本発明に係るワンダ測定装置のクロック再生器の内部構成の一例を示す図、図4(a),(b)は本発明に係るワンダ測定装置の正弦波生成部の内部構成の各例を示す図である。

【0053】

図2に示すように、本発明に係るワンダ測定装置1は、例えば同期式変換器や伝送装置などの測定対象物Wから出力されるデータ信号やクロック信号による被測定信号と、基準信号とを入力として、被測定信号のワンダを測定するものである。

【0054】

なお、ITU−T勧告では、クロック信号やデータ信号による被測定信号に含まれる成分のうち、10Hz以上の位相変動成分をジッタと定義し、10Hz以下の位相変動成分をワンダと定義してそれぞれを区別している。

【0055】

また、本発明に係るワンダ測定装置に入力される被測定信号としては、具体的に、1.544MHz、2.048MHz、5MHz、10MHzの電気信号によるクロック信号の他、2.5Gbps、10Gbps、40Gbps、43Gbpsなどの光信号によるNRZデータ信号やRZデータ信号などがある。以下、本発明に係るワンダ測定装置の構成について説明する。

【0056】

図1に示すように、本例のワンダ測定装置1は、クロック再生器2、分周器3、正弦波生成部4、A/D変換部5、位相復調部6、周波数オフセット補正部7、制御部8、ワンダ計算部9、表示部10を備えて概略構成される。

【0057】

クロック再生器2は、測定対象物Wからの被測定信号がNRZ式やRZ式などのデータ信号の場合、このデータ信号を一定周期のクロック信号に変換している。具体的に、例えば40Gbpsのデータ信号が被測定信号として測定対象物Wから入力されると、この40Gbpsのデータ信号を40GHzのクロック信号に変換している。

【0058】

クロック再生器2は、例えばBPF方式の構成を採用することができる。BPF方式のクロック再生器2は、図3に示すように、遅延回路2a、排他的論理回路(XOR)2b、バンドパスフィルタ(BPF)2cを備えて概略構成される。このクロック再生器2では、遅延回路2aによって入力信号(被測定信号)を時間Δxだけ遅延させて排他的論理回路2bに入力している。その際、Δxは、最大入力ビットレートの逆数の1/2以下にする。排他的論理回路2bには、被測定信号と、この被測定信号を遅延回路2aによりΔxだけ遅延した遅延信号とが入力され、両信号の位相がずれた箇所だけ信号として出力される。この排他的論理回路2bの出力には、ビットレート相当の周波数の基本波成分が含まれるので、この基本波成分を後段のバンドパスフィルタ2cで抽出している。この際、バンドパスフィルタ2cの通過帯域は、測定対象となるワンダの周波数成分よりも十分に広くする。

【0059】

なお、被測定信号は、クロック信号の場合、クロック再生器2に入力されず、後段の分周器3にバイパスされる。また、被測定信号は、光信号の場合、クロック再生器2の前段に光電変換器(不図示)が接続され、光信号から電気信号に変換される。

【0060】

分周器3は、入力されるクロック信号の周波数を、後段の正弦波生成部4が動作可能な周波数まで分周して下げている。具体的に、分周器3に入力されるクロック信号の入力周波数が100MHz〜50GHzの場合、正弦波生成部4の最大動作周波数が1GHzであれば、分周器3の分周比を1/64に固定すれば、出力周波数が1.56MHz〜781MHzになり、常に正弦波生成部4を駆動できる周波数になる。

【0061】

なお、正弦波生成部4が動作可能な周波数のクロック信号が被測定信号の場合には、分周器3に入力されず、後段の正弦波生成部4にバイパスされる。すなわち、正弦波生成部4が動作可能な周波数のクロック信号(電気信号)が被測定信号の場合には、クロック再生器2、分周器3、光電変換器を経由せず正弦波生成部4に直接入力される。

【0062】

正弦波生成部4は、被測定信号側の第1正弦波生成部4aと、基準信号側の第2正弦波生成部4bとを1組として構成される。第1正弦波生成部4aは、分周器3側からのクロック信号(被測定信号)を動作クロックとし、正弦波電圧信号u1(t)を出力している。また、第2正弦波生成部4bは、基準信号を動作クロックとし、正弦波電圧信号u2(t)を出力している。

【0063】

なお、基準信号は、SDH/SONETで規定される高精度の周波数の信号である。基準信号は、具体的に、1.544MHz、2.048MHz、5MHz、10MHzの電気信号であることが多く、外部から入力される他、ワンダ測定装置1内部の水晶発振器による発振信号を用いることもできる。

【0064】

第1正弦波生成部4a及び第2正弦波生成部4bは、それぞれの入力クロック周波数が異なっていても、互いにほぼ等しい周波数を出力するように、制御部8により周波数チューニング・ワード(FTW)を設定して出力周波数f0が制御される。

【0065】

正弦波生成部4(4a,4b)は、市販ICのDDS(Direct Digital Synthesizer:ダイレクト・デジタル・シンセサイザ) やFPGA(Field-Programmable Gate Array) とDAC(digital to analog converter:デジタルーアナログ変換回路) の組み合わせで構成することができる。市販ICのDDSで構成された正弦波生成部4として、例えばFTWのビット数k=48bitの場合、f0=(FTW/2k )×f1…式(4)から出力周波数f0を設定することができる。なお、FTWは正の整数(1〜248)である。

【0066】

また、FPGAとDACの組み合わせで構成された正弦波生成部4は、FPGA内部で正弦波系列を発生し、DACで正弦波系列を電圧信号に変換している。この構成によれば、FPGAの設計次第により、周波数チューニング・ワードFTWのビット幅を48bit以上に大きく設定することが可能である。

【0067】

本例では、この正弦波生成部4(4a,4b)の正弦波電圧信号u1(t),u2(t)の出力周波数を高くすることにより、回路雑音に起因する測定誤差を抑圧している。これにより、被測定信号と基準信号との2つの出力周波数の差(周波数オフセット)は、従来の分周器方式に比べて、大幅に小さくできる。

【0068】

例えばFTWのビット数kbitのDDSを正弦波生成部4として用いた場合、入力クロック周波数f1に対する出力周波数の分解能Δfは、Δf=f1/2k である。この結果、周波数Δfを高くしても、周波数オフセットに起因する測定誤差を大幅に小さくできる。

【0069】

A/D変換部5は、正弦波生成部4(4a,4b)からの2つの正弦波電圧信号u1(t),u2(t)を一定周期でサンプリングし、系列u1(n),u2(n)(但し、n=0,1,2,・・・)として出力している。

【0070】

位相復調部6は、A/D変換部5からの系列u1(n),u2(n)間の瞬時位相の差φ(n)を検出し、この検出した瞬時位相の差φ(n)から時間差系列x(n)=φ(n)/2πf0(但し、f0:A/D変換部5の入力周波数)を算出している。

【0071】

なお、位相復調部6は、例えば特許文献2に従来技術として図6に開示される直交検波方式や特許文献2の図6に開示される方式などを採用することができ、特に構成や方式が限定されるものではない。

【0072】

周波数オフセット補正部7は、位相復調部6から入力される時間差系列x(n)を用いて、ワンダ測定装置1で発生する周波数オフセットΔf0に起因する測定誤差を減算除去して補正し、この補正した時間差系列x’(n)=x(n)−(Δf0/f0)×(n/Fs)を出力している(但し、n=0,1,2,・・・)。なお、Fsはx(n)のサンプリングレートであり、A/D変換部5のサンプリング周波数に等しい。また、Δf0は制御部8から入力される周波数オフセット量(数値パラメータ)である。

【0073】

制御部8は、予め設定される被測定信号の公称周波数(f1)と基準信号の公称周波数(f2)に応じて、第1正弦波生成部4a及び第2正弦波生成部4bの出力周波数が規定の値に近づくように、第1正弦波生成部4a及び第2正弦波生成部4bにそれぞれFTW(周波数チューニング・ワード)を設定している。このFTWの決定及び設定の手順については後述する。また、制御部8は、第1正弦波生成部4a及び第2正弦波生成部4bの出力周波数f0(f0’,f0’’)から周波数オフセット量Δf0を算出し、この算出した周波数オフセット量Δf0を周波数オフセット補正部7に設定している。この周波数オフセット量Δf0の算出及び設定の手順については後述する。

【0074】

ワンダ計算部9は、周波数オフセット補正部7により補正された時間差系列x’(n)を用いて、MTIE(マキシマムタイムインターバルエラー)、TDEV(タイムデビエーション)と呼ばれるワンダ量を計算している。

【0075】

表示部10は、例えば液晶表示器などで構成され、ワンダ計算部9によって計算されたワンダ量、すなわちMTIEやTDEVなどを表示している。

【0076】

次に、上記のように構成されたワンダ測定装置1のワンダ測定方法の手順について説明する。

【0077】

まず、ワンダ測定装置1を用いる装置使用者は、被測定信号の公称周波数f1、基準信号の公称周波数f2の値を制御部8に予め設定しておく。ワンダ測定の開始が指示されると、第1正弦波生成部4aに被測定信号が入力され、第2正弦波生成部4bに基準信号が入力される。この際、被測定信号側の第1正弦波生成部4aに入力される周波数は、分周器3の分周比をNとすると、f1/Nになる。

【0078】

そして、制御部8は、第1正弦波生成部4aから出力される周波数が、予め定められた第1正弦波生成部4aの出力周波数f0に最も近づくように、FTW1=[(f0/f1)×N×2k ]…式(5)を用いて第1正弦波生成部4aの周波数チューニング・ワードFTW1を決定する。なお、f0:正弦波生成部の出力周波数の理想値(装置側の都合で決めて良い値)、f1:被測定信号の公称周波数、N:分周器3の分周比(固定値)、k:第1正弦波生成部4aのビット数、[]:[]内の値を超えない最大の整数である。

【0079】

そして、制御部8は、上記式(5)を用いて決定した周波数チューニング・ワードFTW1を被測定信号側の第1正弦波生成部4aに設定する。この時、実際に第1正弦波生成部4aから出力される周波数f0’は、f0’=(FTW1/2k )×f1…式(6)で表される。

【0080】

また、制御部8は、基準信号側の第2正弦波生成部4bの出力が、予め定められた第2正弦波生成部4bの出力周波数f0’に最も近づくように、FTW2=[(f0’/f2)×2k ]…式(7)を用いて第2正弦波生成部4bのFTW2を決定する。

【0081】

そして、制御部8は、上記式を(7)を用いて決定した周波数チューニング・ワードFTW2を基準信号側の第2正弦波生成部4bに設定する。この時、実際に第2正弦波生成部4bから出力される周波数f0’’は、f0’’=(FTW2/2k )×f2…式(8)で表される。

【0082】

これにより、2つの正弦波生成部4a,4bの出力周波数の差(周波数オフセット)Δf0は、上記式(6),(8)からΔf0=f0’−f0’’=(FTW1×f1−FTW2×f2)/2k …式(9)で表される。

【0083】

そして、制御部8は、Δf0/f0(出力周波数の誤差の比率)を補正値として、周波数オフセット補正部7に入力する。

【0084】

続いて、周波数オフセット補正部7は、制御部8から補正値が入力されると、x’(n)=x(n)−(Δf0/f0)×(n/Fs)…式(10)を用いて、周波数オフセットに起因する測定誤差を除去し、補正後の時間差系列x’(n)を出力する。なお、n=0,1,2,・・・、Fsは時間差系列x(n)のサンプリングレート(A/D変換部5のサンプリング周波数に等しい)である。

【0085】

次に、上記構成によるワンダ測定装置1の具体的な動作例について数値を示して説明する。

【0086】

被測定信号がSDHのSTM−256伝送レート、基準信号が1.544MHzのクロック信号の場合、1/64で分周したクロック信号の周波数は622.08MHzになる。この周波数622.08MHzを第1正弦波生成部4aとしてのDDSのクロック信号として、80kHz近傍の周波数を出力した場合、A/D変換部5のSNR(=116dB)に起因する測定誤差のpeak−to−peakは0.04nsとなる。

【0087】

そして、正弦波生成部4(4a,4b)としてのDDSが48bitの時、DDSの出力間の周波数オフセットΔf0は、Δf0≦622.08M/248≒2.21×10-6[Hz]になる。この値であれば、経過時間10000sでも0.1nsの測定分解能を保つためには、時間差系列x(n)のビット数は12bitで良いため、従来技術(41bit)に比べて大幅に回路リソースが少なくて済む。

【0088】

さらに、周波数オフセット補正部7によって周波数オフセットΔfをほぼ0でき、この周波数オフセットΔfに起因する測定誤差を抑圧でき、その影響を実質的に無視して高精度な測定が可能になる。

【0089】

このように、本発明のワンダ測定装置及びワンダ測定方法によれば、特許文献1のタイムインターバルカウンタのような複雑で校正が必要となる高速アナログ回路を必要とせず、簡単な回路構成で回路雑音に起因する測定誤差を抑圧して高精度なワンダ測定を行うことができる。

【0090】

また、特許文献2の分周器を用いた方式では、被測定信号と基準信号の周波数が異なる場合、分周器の出力周波数を一致させるため、出力周波数を低くしていた。このため、回路雑音に起因する測定誤差が小さくならず、高精度化が困難であった。

【0091】

これに対し、本発明によれば、正弦波生成部4としてDDSを用いることにより、A/D変換部5の入力周波数を高くして回路雑音に起因する測定誤差を抑圧することができる。しかも、予測可能な周波数オフセットΔfに起因する測定誤差を後段の演算回路(周波数オフセット補正部7)で除去することができる。その際、正弦波生成部4としてDDSを用いたことにより、周波数オフセットΔfに起因する測定誤差は、従来の分周器方式よりも大幅に小さくなり、演算回路は少ないリソースで実現することができる。その結果、簡単な構成で高精度のワンダ測定装置を実現することができる。

【符号の説明】

【0092】

1 ワンダ測定装置

2 クロック再生器

3 分周器

4(4a,4b) 正弦波生成部

5 A/D変換部

6 位相復調部

7 周波数オフセット補正部

8 制御部

9 ワンダ計算部

10 表示部

【技術分野】

【0001】

本発明は、パルス状の被測定信号のパルス間隔の変動(ゆれ)のうち、特に長期位相変動であるワンダを測定するワンダ測定装置及びワンダ測定方法に関する。

【背景技術】

【0002】

例えばSDH/SONETやOTNと呼ばれる長距離伝送方式では、同期式が広く使用されている。そして、系全体が同期している通信ネットワークにおいて、同期式変換器や伝送装置から出力される信号(データやクロック)を被測定信号とし、この被測定信号のワンダを測定するワンダ測定装置が知られている。

【0003】

図5は特許文献1に開示されるジッタ/ワンダ解析装置の概略構成を示すブロック図である。なお、図5では、特許文献1の図1における測定信号生成回路、連続周期測定回路、バッファメモリをまとめてタイムインターバルカウンタ53として図示している。

【0004】

図5のジッタ/ワンダ解析装置51では、異なる周波数の入力信号(被測定信号、基準信号)をそれぞれ分周器52(52a,52b)で分周し、一組の同一周波数を持つクロック信号(又は繰り返しパルス信号)に変換している。この変換後の周波数は、8kHzや4kHzが使用されることが多い。その理由は、SDH/SONETやOTNに使用される伝送レートや基準信号の周波数が必ず8kHzの倍数で表されるためである。

【0005】

なお、ワンダは、10Hz以下の位相変動成分と一般的に定義されているため、8kHzや4kHzに分周しても検出可能である。

【0006】

そして、タイムインターバルカウンタ53は、一組の同一周波数を持つクロック信号が入力されると、両者の時間差系列x(n)をワンダ計算部54に出力する。その後、ワンダ計算部54は、タイムインターバルカウンタ53からのx(n)を用いて、MTIEやTDEVと呼ばれるワンダ量を計算し、この計算した結果が表示部55に表示される。

【0007】

ところで、被測定信号と基準信号をそれぞれ分周器52a,52bで分周した際、両者を同一周波数にしないと、タイムインターバルカウンタ53で測定される時間差系列x(n)には、周波数差(オフセット周波数)に起因する測定誤差が加算されてしまう。

【0008】

タイムインターバルカウンタ53には、様々な回路方式があるが、基本的には、基準信号に対する被測定信号の時間差変動を測るため、入力信号間のパルスの時間差を一定間隔で測定している。そして、この入力信号間のパルスの時間差と位相差は、φ(t)=2πf0×x(t)…式(1)を用いて相互に変換可能である。

【0009】

上記式(1)において、φ(t)は時刻tにおける瞬時位相差(単位はラジアン)、x(t)は時刻tにおける時間差、f0は入力信号周波数であり、連続量x(t)を一定間隔のサンプル系列で表したものがx(n)(n=0,1,2,・・・)である。

【0010】

なお、タイムインターバルカウンタ53については、本発明とは直接関係ないので、ここでは詳説しない(具体的には、特許文献1を参照)。

【0011】

ところで、ITU−T等で規定されるSDH/SONET伝送装置のワンダは、一般的にns(ナノ秒)オーダーで表される。このため、特許文献1の方式を採用したタイムインターバルカウンタは、その1/10である0.1ns程度の測定精度を持たなければならない。

【0012】

仮に、0.1nsの時間分解能のタイムインターバルカウンタ53を実現するためには、入力信号間のパルスの時間差を一定間隔でカウントする単純なカウンタ方式では、10GHzのカウンタが必要になる。しかし、そのような動作で複雑な回路を動作させるのは難しく、部品コストも増大するという課題がある。

【0013】

このため、特許文献1に開示されるように、カウンタ周波数には100MHzを使用して10nsの分解能で時間計測をする一方、それ以上の時間精度を得るために、端数時間電圧変換器(特許文献1の図14)を用いて、時間分解能を向上させている。

【0014】

このように、タイムインターバルカウンタ53は、論理回路だけで実現することができず、端数時間電圧変換器のようなアナログ回路が必要になる。その結果、回路を小型化できず、またアナログ回路の部品ばらつきを補正するために、校正手段が別途必要になるという課題が生じる。

【0015】

図6は特許文献2に開示される周波数安定度測定装置の概略構成を示すブロック図である。なお、図6では、特許文献1の図5における第1のHPF、第2のHPF、第1の90度移相器、第2の90度移相器、演算回路、移送検波器を位相復調部、ワンダ計算部として図示している。

【0016】

図6の測定装置61では、入力信号として、同一又は異なる周波数の正弦波信号S1(t),S2(t)を入力し、周波数変換部62により、同一周波数の正弦波電圧u1(t),u2(t)信号に変換している。ADC(A/D変換器)63(63a,63b)では、周波数変換部62からの2つの正弦波信号u1(t),u2(t)を一定周期でサンプリングし、系列u1(n),u2(n)(n=0,1,2,・・・)として出力する。そして、位相復調部64では、ADC63a,63bからのu1(n),u2(n)間の瞬時位相の差φ(n)を位相復調方式によって検出している。位相復調方式は、例えば特許文献2が従来技術として挙げている直交検波方式(特許文献2の図10)でも良いし、特許文献2に開示される方式でも良い。そして、位相復調部64は、瞬時位相の差φ(n)から時間差系列x(n)をx(n)=φ(n)/2πf0…式(2)を用いて算出している。但し、f0はADCの入力周波数である。そして、ワンダ計算部65は、位相復調部64からのx(n)を用いて、MTIEやTDEVと呼ばれるワンダ量を計算し、この計算した結果が表示部66に表示される。

【0017】

この特許文献2の測定装置61の特徴は、周波数変換部62以降が、市販の低速ADCとプロセッサで実現可能な演算回路だけで構築できる点にある。つまり、前述したタイムインターバルカウンタ53のような校正を必要とするアナログ回路が不要である。また、回路の動作速度も数10k〜数100kHz程度となるため、タイムインターバルカウンタ53のような高速動作する回路が不要であり、回路に高額な高周波部品を使用せずに済む。

【0018】

ところで、特許文献2では、周波数変換部62として、(a)ミキサ方式、(b)分周器方式、(c)PLL方式の3つの方式を挙げている。

【0019】

図7(a),(b),(c)は上記3つの方式による周波数変換部62(62A,62B,62C)の各構成例を示している。図7(a)はミキサ方式の周波数変換部62Aの構成例を示している。図7(a)のミキサ方式の周波数変換部62Aは、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が等しい場合(f1≒f2)に使用される方式であり、最も高精度な測定が実現できる。

【0020】

すなわち、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が等しい場合、ローカル発振器62aが持つ固有の位相変動成分に起因する時間誤差成分は、LPF(ローパスフィルタ)62b,62bから出力される正弦波電圧信号u1(t),u2(t)に等しく含まれる。このため、後段の演算過程において上記時間誤差成分を相殺することができる。また、被測定信号S1(t)と基準信号S2(t)との間の時間差x(t)は、ミキサ62c,62cによって周波数変換比だけ増幅される。

【0021】

これらの結果、図7(a)のミキサ方式の周波数変換部62Aによれば、時間差x(n)の測定精度が大幅に向上する。しかしながら、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が異なる場合(f1≠f2)は使用できないという課題がある。

【0022】

図7(b)の分周器方式の周波数変換部62Bは、2つの分周器62d,62dの分周比を異なる値に設定すれば、被測定信号S1(t)の周波数f1と基準信号S2(n)の周波数f2が異なる場合(f1≠f2)であっても、正弦波電圧信号u1(t),u2(t)の周波数を等しくできる。なお、特許文献2の図7には示されていないが、通常、分周器から出力される信号は矩形波のため、図7(b)に示すようなLPF(又はBPF)62e,62eを介して正弦波に変換することが必要である。

【0023】

ところで、先述のように、本発明で対象とする被測定信号は、ITU−Tで定められた伝送レートが8kHzの倍数であるため、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2の最大公約数が8kHzになることが多い。この結果、正弦波電圧信号u1(t)とu2(t)の周波数は8kHzや、8KHzの整数分の1(4kHz、2kHz)が適している。

【0024】

図7(c)のPLL方式の周波数変換部62Cは、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2が等しい場合(f1=f2)、異なる場合(f1≠f2)の何れの場合であっても、高精度の測定には向いていない。その理由は、PLL62f,62fに使用されているVCO62g,62gがそれぞれ固有の位相雑音(位相変動)を持っており、その差分が測定誤差になってしまうためである。

【0025】

以上の結果、被測定信号S1(t)と基準信号S2(t)の周波数f1≠f2の条件下では、図7(b)の分周器方式の周波数変換部62Bが有効である。

【先行技術文献】

【特許文献】

【0026】

【特許文献1】特開平7−83980号公報

【特許文献2】特許第3845573号公報

【発明の概要】

【発明が解決しようとする課題】

【0027】

しかしながら、上述した図7(b)の分周器方式の周波数変換部62Bを用いた構成では、0.1nsの測定精度を実現する上で問題点がある。

【0028】

例えば、正弦波電圧信号u1(t),u2(t)の周波数が8kHzとなるように分周器の分周比を設定した場合、ADCのサンプリングレートは、サンプリング定理から2倍の16kサンプル/s以上であれば良い。このような比較的低速なADCであれば、現在24bit分解能のADCが市販されている。

【0029】

但し、24bitのADCと言っても、ADC内部の回路雑音等の影響によって、実質的な分解能(ENOB)は19bit程度であることが多い。

【0030】

この実質的な分解能ENOBから求まる正弦波電圧信号u1(t),u2(t)の信号対雑音比(SNR)に起因する測定装置のx(n)に対する測定誤差を、SNR=6.02×ENOB+1.76[dB]、測定誤差ε=1/(2πf0×10SNR/20)[s](実効値)…式(3)から概算することができる。

【0031】

例えばENOB=19[bit]の時、SNR≒116[dB]、ε≒31[ps](実効値)となる。誤差ε=31[ps]は実効値のため、そのpeak−to−peak値は、ADCの内部ノイズがガウシアンノイズだと仮定すると、実効値の10〜14倍程度になる。すなわち、31×14=434ps(=0.434ns)。これでは、0.1nsの精度を実現できない。

【0032】

上述した式(3)に基づくと、測定精度を向上させるには、ADCのSNRを向上させるか、正弦波電圧信号u1(t),u2(t)の周波数f0を高くするかのどちらかである。

【0033】

まず、ADCのSNRを向上させるには、例えば2M 個のADCを用いてその出力を加算平均すれば、原理的に3×M[dB]だけSNRが向上する。仮にM=4として、16個のADCの出力を加算すれば、SNRは12dB向上する。この結果、εは1/4倍になって0.1ns程度になる。但し、この場合、ADCが16×2ch=32個となって、回路規模が増大するという課題がある。

【0034】

これに対し、周波数f0を高くする方法は、前述した図7(c)の分周器方式を用いる方法では難しい。これは、前述のように、被測定信号S1(t)の周波数f1と基準信号S2(t)の周波数f2の公約数が8kHz以上にならない場合があるためである。

【0035】

例えば、SDHのSTM−256で規定されている伝送レートは、39.81312Gbpsであり、このデータ信号から変換されたクロック信号(39.81312GHz)を被測定信号とし、SDHで広く使用されている同期クロック(1.544MHz)を基準信号とした場合、39.81312GHz÷4976640=8.0kHz、1.544MHz÷193=8.0kHzとなり、これらの周波数の最大公約数は8kHzである。

【0036】

したがって、分周器による分周後の周波数f0を同一にする場合、f0を8kHz以上にできない。

【0037】

そこで、周波数f0を高くするため、分周器による分周後の周波数を同一にしない場合を考えると、例えば分周後の周波数として、被測定信号:3.981312GHz÷497664=80.0kHz、基準信号:1.544MHz÷19≒81.26315789kHzとし、80kHz前後になるようにする。

【0038】

この場合、f0は約80kHzなので、測定装置のSNRに起因する測定誤差は先の例の10倍向上して、約0.04nsとなり、目標の精度0.1nsを満足する。その反面、分周後の周波数の差(周波数オフセット)に起因する測定誤差が新たに発生するという課題がある。

【0039】

ここで、分周器による分周後の周波数に差がない場合、検出される時間差x(n)は、図8(a)に示すように、長時間測定してもその値が発散しない。これに対し、分周後の周波数に差がある場合は、図8(b)に示すように、測定時間とともにx(n)の値が増大または減少する(最終的には、経過時間とともに、+∞または−∞に発散する)。

【0040】

そして、x(n)の値が大きくなると、x(n)の数値精度(ビット数)の制限から、やがてアンダーフローが生じて、測定対象であるx(n)の測定分解能が悪化する。

【0041】

例えば前述したように、分周後に1kHz程度の周波数オフセットがある場合、周波数オフセットに起因する測定誤差は、経過時間t(s)とともに、(1k/80k)×tの割合で増加する。この測定誤差は予測可能であるから、経過時間tとともに差し引けば良い。但し、ここで注意すべきことは、要求される精度0.1nsに対して、差し引く誤差が極めて大きい(t=10000sの時、125s)ので、x(n)がアンダーフローを生じずに0.1ns精度を維持するためにはx(n)のビット幅として41bit程度必要になる。

【0042】

ところが、ワンダ計算部をFPGAやDSP等で構成した場合には、ハードウェアのリソースの都合上、ビット幅には制限があり、測定時間を短く制限するか、測定精度の悪化を許容する必要が生じる。

【0043】

そこで、本発明は上記問題点に鑑みてなされたものであって、簡単な回路構成で高精度なワンダ測定が行えるワンダ測定装置及びワンダ測定方法を提供することを目的としている。

【課題を解決するための手段】

【0044】

上記目的を達成するため、本発明の請求項1に記載されたワンダ測定装置は、クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力する1組の正弦波生成部4a,4bと、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力する位相復調部6と、

前記時間差系列に基づいてワンダ量を計算するワンダ計算部9と、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を前記1組の正弦波生成部に設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する制御部8とを備えたことを特徴とする。

【0045】

請求項2に記載されたワンダ測定装置は、請求項1のワンダ測定装置において、

前記制御部8は、前記周波数チューニング・ワードの設定に基づく前記正弦波電圧信号u1(t),u2(t)の出力周波数の差を周波数オフセットΔfとして算出し、

前記周波数オフセットを用いて前記位相復調部6から出力される時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧する周波数オフセット補正部を更に備えたことを特徴とする。

【0046】

請求項3に記載されたワンダ測定方法は、クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力するステップと、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力するステップと、

前記時間差系列に基づいてワンダ量を計算するステップと、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧するステップとを含むことを特徴とする。

【0047】

請求項4に記載されたワンダ測定方法は、請求項3のワンダ測定方法において、

前記周波数チューニング・ワードの設定に基づく前記2つの正弦波電圧信号の出力周波数の差を周波数オフセットΔfとして算出するステップと、

前記周波数オフセットを用いて前記時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧するステップとを更に含むことを特徴とする。

【発明の効果】

【0048】

本発明によれば、特許文献1のタイムインターバルカウンタのような複雑で校正が必要となる高速アナログ回路を必要とせず、簡単な回路構成で回路雑音に起因する測定誤差を抑圧して高精度なワンダ測定を行うことができる。

【0049】

また、予測可能な周波数オフセットΔfに起因する測定誤差を後段の周波数オフセット補正部で除去することができる。その際、正弦波生成部としてDDSを用いたことにより、周波数オフセットΔfに起因する測定誤差は、従来の分周器方式よりも大幅に小さくなり、演算回路は少ないリソースで実現することができる。その結果、簡単な構成で高精度のワンダ測定装置を実現することができる。

【図面の簡単な説明】

【0050】

【図1】本発明に係るワンダ測定装置のブロック構成図である。

【図2】本発明に係るワンダ測定装置の概要を示すブロック図である。

【図3】本発明に係るワンダ測定装置のクロック再生器の内部構成の一例を示す図である。

【図4】(a),(b) 本発明に係るワンダ測定装置の正弦波生成部の内部構成の各例を示す図である。

【図5】特許文献1に開示されるジッタ/ワンダ解析装置の概略ブロック構成図である。

【図6】特許文献2に開示される周波数安定度測定装置の概略ブロック構成図である。

【図7】(a)〜(c) 特許文献2の周波数変換部の内部構成の各例を示す図である。

【図8】(a),(b) 分周後の周波数に差がない場合とある場合にそれぞれ検出される時間差の特性の一例を示す図である。

【発明を実施するための形態】

【0051】

以下、本発明を実施するための形態について、添付した図面を参照しながら詳細に説明する。尚、この実施の形態によりこの発明が限定されるものではなく、この形態に基づいて当業者などによりなされる実施可能な他の形態、実施例及び運用技術などはすべて本発明の範疇に含まれる。

【0052】

図1は本発明に係るワンダ測定装置のブロック構成図、図2は本発明に係るワンダ測定装置の概要を示すブロック図、図3は本発明に係るワンダ測定装置のクロック再生器の内部構成の一例を示す図、図4(a),(b)は本発明に係るワンダ測定装置の正弦波生成部の内部構成の各例を示す図である。

【0053】

図2に示すように、本発明に係るワンダ測定装置1は、例えば同期式変換器や伝送装置などの測定対象物Wから出力されるデータ信号やクロック信号による被測定信号と、基準信号とを入力として、被測定信号のワンダを測定するものである。

【0054】

なお、ITU−T勧告では、クロック信号やデータ信号による被測定信号に含まれる成分のうち、10Hz以上の位相変動成分をジッタと定義し、10Hz以下の位相変動成分をワンダと定義してそれぞれを区別している。

【0055】

また、本発明に係るワンダ測定装置に入力される被測定信号としては、具体的に、1.544MHz、2.048MHz、5MHz、10MHzの電気信号によるクロック信号の他、2.5Gbps、10Gbps、40Gbps、43Gbpsなどの光信号によるNRZデータ信号やRZデータ信号などがある。以下、本発明に係るワンダ測定装置の構成について説明する。

【0056】

図1に示すように、本例のワンダ測定装置1は、クロック再生器2、分周器3、正弦波生成部4、A/D変換部5、位相復調部6、周波数オフセット補正部7、制御部8、ワンダ計算部9、表示部10を備えて概略構成される。

【0057】

クロック再生器2は、測定対象物Wからの被測定信号がNRZ式やRZ式などのデータ信号の場合、このデータ信号を一定周期のクロック信号に変換している。具体的に、例えば40Gbpsのデータ信号が被測定信号として測定対象物Wから入力されると、この40Gbpsのデータ信号を40GHzのクロック信号に変換している。

【0058】

クロック再生器2は、例えばBPF方式の構成を採用することができる。BPF方式のクロック再生器2は、図3に示すように、遅延回路2a、排他的論理回路(XOR)2b、バンドパスフィルタ(BPF)2cを備えて概略構成される。このクロック再生器2では、遅延回路2aによって入力信号(被測定信号)を時間Δxだけ遅延させて排他的論理回路2bに入力している。その際、Δxは、最大入力ビットレートの逆数の1/2以下にする。排他的論理回路2bには、被測定信号と、この被測定信号を遅延回路2aによりΔxだけ遅延した遅延信号とが入力され、両信号の位相がずれた箇所だけ信号として出力される。この排他的論理回路2bの出力には、ビットレート相当の周波数の基本波成分が含まれるので、この基本波成分を後段のバンドパスフィルタ2cで抽出している。この際、バンドパスフィルタ2cの通過帯域は、測定対象となるワンダの周波数成分よりも十分に広くする。

【0059】

なお、被測定信号は、クロック信号の場合、クロック再生器2に入力されず、後段の分周器3にバイパスされる。また、被測定信号は、光信号の場合、クロック再生器2の前段に光電変換器(不図示)が接続され、光信号から電気信号に変換される。

【0060】

分周器3は、入力されるクロック信号の周波数を、後段の正弦波生成部4が動作可能な周波数まで分周して下げている。具体的に、分周器3に入力されるクロック信号の入力周波数が100MHz〜50GHzの場合、正弦波生成部4の最大動作周波数が1GHzであれば、分周器3の分周比を1/64に固定すれば、出力周波数が1.56MHz〜781MHzになり、常に正弦波生成部4を駆動できる周波数になる。

【0061】

なお、正弦波生成部4が動作可能な周波数のクロック信号が被測定信号の場合には、分周器3に入力されず、後段の正弦波生成部4にバイパスされる。すなわち、正弦波生成部4が動作可能な周波数のクロック信号(電気信号)が被測定信号の場合には、クロック再生器2、分周器3、光電変換器を経由せず正弦波生成部4に直接入力される。

【0062】

正弦波生成部4は、被測定信号側の第1正弦波生成部4aと、基準信号側の第2正弦波生成部4bとを1組として構成される。第1正弦波生成部4aは、分周器3側からのクロック信号(被測定信号)を動作クロックとし、正弦波電圧信号u1(t)を出力している。また、第2正弦波生成部4bは、基準信号を動作クロックとし、正弦波電圧信号u2(t)を出力している。

【0063】

なお、基準信号は、SDH/SONETで規定される高精度の周波数の信号である。基準信号は、具体的に、1.544MHz、2.048MHz、5MHz、10MHzの電気信号であることが多く、外部から入力される他、ワンダ測定装置1内部の水晶発振器による発振信号を用いることもできる。

【0064】

第1正弦波生成部4a及び第2正弦波生成部4bは、それぞれの入力クロック周波数が異なっていても、互いにほぼ等しい周波数を出力するように、制御部8により周波数チューニング・ワード(FTW)を設定して出力周波数f0が制御される。

【0065】

正弦波生成部4(4a,4b)は、市販ICのDDS(Direct Digital Synthesizer:ダイレクト・デジタル・シンセサイザ) やFPGA(Field-Programmable Gate Array) とDAC(digital to analog converter:デジタルーアナログ変換回路) の組み合わせで構成することができる。市販ICのDDSで構成された正弦波生成部4として、例えばFTWのビット数k=48bitの場合、f0=(FTW/2k )×f1…式(4)から出力周波数f0を設定することができる。なお、FTWは正の整数(1〜248)である。

【0066】

また、FPGAとDACの組み合わせで構成された正弦波生成部4は、FPGA内部で正弦波系列を発生し、DACで正弦波系列を電圧信号に変換している。この構成によれば、FPGAの設計次第により、周波数チューニング・ワードFTWのビット幅を48bit以上に大きく設定することが可能である。

【0067】

本例では、この正弦波生成部4(4a,4b)の正弦波電圧信号u1(t),u2(t)の出力周波数を高くすることにより、回路雑音に起因する測定誤差を抑圧している。これにより、被測定信号と基準信号との2つの出力周波数の差(周波数オフセット)は、従来の分周器方式に比べて、大幅に小さくできる。

【0068】

例えばFTWのビット数kbitのDDSを正弦波生成部4として用いた場合、入力クロック周波数f1に対する出力周波数の分解能Δfは、Δf=f1/2k である。この結果、周波数Δfを高くしても、周波数オフセットに起因する測定誤差を大幅に小さくできる。

【0069】

A/D変換部5は、正弦波生成部4(4a,4b)からの2つの正弦波電圧信号u1(t),u2(t)を一定周期でサンプリングし、系列u1(n),u2(n)(但し、n=0,1,2,・・・)として出力している。

【0070】

位相復調部6は、A/D変換部5からの系列u1(n),u2(n)間の瞬時位相の差φ(n)を検出し、この検出した瞬時位相の差φ(n)から時間差系列x(n)=φ(n)/2πf0(但し、f0:A/D変換部5の入力周波数)を算出している。

【0071】

なお、位相復調部6は、例えば特許文献2に従来技術として図6に開示される直交検波方式や特許文献2の図6に開示される方式などを採用することができ、特に構成や方式が限定されるものではない。

【0072】

周波数オフセット補正部7は、位相復調部6から入力される時間差系列x(n)を用いて、ワンダ測定装置1で発生する周波数オフセットΔf0に起因する測定誤差を減算除去して補正し、この補正した時間差系列x’(n)=x(n)−(Δf0/f0)×(n/Fs)を出力している(但し、n=0,1,2,・・・)。なお、Fsはx(n)のサンプリングレートであり、A/D変換部5のサンプリング周波数に等しい。また、Δf0は制御部8から入力される周波数オフセット量(数値パラメータ)である。

【0073】

制御部8は、予め設定される被測定信号の公称周波数(f1)と基準信号の公称周波数(f2)に応じて、第1正弦波生成部4a及び第2正弦波生成部4bの出力周波数が規定の値に近づくように、第1正弦波生成部4a及び第2正弦波生成部4bにそれぞれFTW(周波数チューニング・ワード)を設定している。このFTWの決定及び設定の手順については後述する。また、制御部8は、第1正弦波生成部4a及び第2正弦波生成部4bの出力周波数f0(f0’,f0’’)から周波数オフセット量Δf0を算出し、この算出した周波数オフセット量Δf0を周波数オフセット補正部7に設定している。この周波数オフセット量Δf0の算出及び設定の手順については後述する。

【0074】

ワンダ計算部9は、周波数オフセット補正部7により補正された時間差系列x’(n)を用いて、MTIE(マキシマムタイムインターバルエラー)、TDEV(タイムデビエーション)と呼ばれるワンダ量を計算している。

【0075】

表示部10は、例えば液晶表示器などで構成され、ワンダ計算部9によって計算されたワンダ量、すなわちMTIEやTDEVなどを表示している。

【0076】

次に、上記のように構成されたワンダ測定装置1のワンダ測定方法の手順について説明する。

【0077】

まず、ワンダ測定装置1を用いる装置使用者は、被測定信号の公称周波数f1、基準信号の公称周波数f2の値を制御部8に予め設定しておく。ワンダ測定の開始が指示されると、第1正弦波生成部4aに被測定信号が入力され、第2正弦波生成部4bに基準信号が入力される。この際、被測定信号側の第1正弦波生成部4aに入力される周波数は、分周器3の分周比をNとすると、f1/Nになる。

【0078】

そして、制御部8は、第1正弦波生成部4aから出力される周波数が、予め定められた第1正弦波生成部4aの出力周波数f0に最も近づくように、FTW1=[(f0/f1)×N×2k ]…式(5)を用いて第1正弦波生成部4aの周波数チューニング・ワードFTW1を決定する。なお、f0:正弦波生成部の出力周波数の理想値(装置側の都合で決めて良い値)、f1:被測定信号の公称周波数、N:分周器3の分周比(固定値)、k:第1正弦波生成部4aのビット数、[]:[]内の値を超えない最大の整数である。

【0079】

そして、制御部8は、上記式(5)を用いて決定した周波数チューニング・ワードFTW1を被測定信号側の第1正弦波生成部4aに設定する。この時、実際に第1正弦波生成部4aから出力される周波数f0’は、f0’=(FTW1/2k )×f1…式(6)で表される。

【0080】

また、制御部8は、基準信号側の第2正弦波生成部4bの出力が、予め定められた第2正弦波生成部4bの出力周波数f0’に最も近づくように、FTW2=[(f0’/f2)×2k ]…式(7)を用いて第2正弦波生成部4bのFTW2を決定する。

【0081】

そして、制御部8は、上記式を(7)を用いて決定した周波数チューニング・ワードFTW2を基準信号側の第2正弦波生成部4bに設定する。この時、実際に第2正弦波生成部4bから出力される周波数f0’’は、f0’’=(FTW2/2k )×f2…式(8)で表される。

【0082】

これにより、2つの正弦波生成部4a,4bの出力周波数の差(周波数オフセット)Δf0は、上記式(6),(8)からΔf0=f0’−f0’’=(FTW1×f1−FTW2×f2)/2k …式(9)で表される。

【0083】

そして、制御部8は、Δf0/f0(出力周波数の誤差の比率)を補正値として、周波数オフセット補正部7に入力する。

【0084】

続いて、周波数オフセット補正部7は、制御部8から補正値が入力されると、x’(n)=x(n)−(Δf0/f0)×(n/Fs)…式(10)を用いて、周波数オフセットに起因する測定誤差を除去し、補正後の時間差系列x’(n)を出力する。なお、n=0,1,2,・・・、Fsは時間差系列x(n)のサンプリングレート(A/D変換部5のサンプリング周波数に等しい)である。

【0085】

次に、上記構成によるワンダ測定装置1の具体的な動作例について数値を示して説明する。

【0086】

被測定信号がSDHのSTM−256伝送レート、基準信号が1.544MHzのクロック信号の場合、1/64で分周したクロック信号の周波数は622.08MHzになる。この周波数622.08MHzを第1正弦波生成部4aとしてのDDSのクロック信号として、80kHz近傍の周波数を出力した場合、A/D変換部5のSNR(=116dB)に起因する測定誤差のpeak−to−peakは0.04nsとなる。

【0087】

そして、正弦波生成部4(4a,4b)としてのDDSが48bitの時、DDSの出力間の周波数オフセットΔf0は、Δf0≦622.08M/248≒2.21×10-6[Hz]になる。この値であれば、経過時間10000sでも0.1nsの測定分解能を保つためには、時間差系列x(n)のビット数は12bitで良いため、従来技術(41bit)に比べて大幅に回路リソースが少なくて済む。

【0088】

さらに、周波数オフセット補正部7によって周波数オフセットΔfをほぼ0でき、この周波数オフセットΔfに起因する測定誤差を抑圧でき、その影響を実質的に無視して高精度な測定が可能になる。

【0089】

このように、本発明のワンダ測定装置及びワンダ測定方法によれば、特許文献1のタイムインターバルカウンタのような複雑で校正が必要となる高速アナログ回路を必要とせず、簡単な回路構成で回路雑音に起因する測定誤差を抑圧して高精度なワンダ測定を行うことができる。

【0090】

また、特許文献2の分周器を用いた方式では、被測定信号と基準信号の周波数が異なる場合、分周器の出力周波数を一致させるため、出力周波数を低くしていた。このため、回路雑音に起因する測定誤差が小さくならず、高精度化が困難であった。

【0091】

これに対し、本発明によれば、正弦波生成部4としてDDSを用いることにより、A/D変換部5の入力周波数を高くして回路雑音に起因する測定誤差を抑圧することができる。しかも、予測可能な周波数オフセットΔfに起因する測定誤差を後段の演算回路(周波数オフセット補正部7)で除去することができる。その際、正弦波生成部4としてDDSを用いたことにより、周波数オフセットΔfに起因する測定誤差は、従来の分周器方式よりも大幅に小さくなり、演算回路は少ないリソースで実現することができる。その結果、簡単な構成で高精度のワンダ測定装置を実現することができる。

【符号の説明】

【0092】

1 ワンダ測定装置

2 クロック再生器

3 分周器

4(4a,4b) 正弦波生成部

5 A/D変換部

6 位相復調部

7 周波数オフセット補正部

8 制御部

9 ワンダ計算部

10 表示部

【特許請求の範囲】

【請求項1】

クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号(u1(t),u2(t))を出力する1組の正弦波生成部(4a,4b)と、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列(u1(n),u2(n))間の瞬時位相の差に基づく時間差系列(x(n))を出力する位相復調部(6)と、

前記時間差系列に基づいてワンダ量を計算するワンダ計算部(9)と、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数(f0)に最も近づく周波数チューニング・ワード(FTW1,FTW2)を前記1組の正弦波生成部に設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する制御部(8)とを備えたことを特徴とするワンダ測定装置。

【請求項2】

前記制御部(8)は、前記周波数チューニング・ワードの設定に基づく前記正弦波電圧信号(u1(t),u2(t))の出力周波数の差を周波数オフセット(Δf)として算出し、

前記周波数オフセットを用いて前記位相復調部(6)から出力される時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧する周波数オフセット補正部を更に備えたことを特徴とする請求項1記載のワンダ測定装置。

【請求項3】

クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号(u1(t),u2(t))を出力するステップと、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列(u1(n),u2(n))間の瞬時位相の差に基づく時間差系列(x(n))を出力するステップと、

前記時間差系列に基づいてワンダ量を計算するステップと、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数(f0)に最も近づく周波数チューニング・ワード(FTW1,FTW2)を設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧するステップとを含むことを特徴とするワンダ測定方法。

【請求項4】

前記周波数チューニング・ワードの設定に基づく前記2つの正弦波電圧信号の出力周波数の差を周波数オフセット(Δf)として算出するステップと、

前記周波数オフセットを用いて前記時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧するステップとを更に含むことを特徴とする請求項3記載のワンダ測定方法。

【請求項1】

クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号(u1(t),u2(t))を出力する1組の正弦波生成部(4a,4b)と、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列(u1(n),u2(n))間の瞬時位相の差に基づく時間差系列(x(n))を出力する位相復調部(6)と、

前記時間差系列に基づいてワンダ量を計算するワンダ計算部(9)と、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数(f0)に最も近づく周波数チューニング・ワード(FTW1,FTW2)を前記1組の正弦波生成部に設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する制御部(8)とを備えたことを特徴とするワンダ測定装置。

【請求項2】

前記制御部(8)は、前記周波数チューニング・ワードの設定に基づく前記正弦波電圧信号(u1(t),u2(t))の出力周波数の差を周波数オフセット(Δf)として算出し、

前記周波数オフセットを用いて前記位相復調部(6)から出力される時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧する周波数オフセット補正部を更に備えたことを特徴とする請求項1記載のワンダ測定装置。

【請求項3】

クロック信号による被測定信号と、クロック信号による基準信号とを動作クロックとしてそれぞれ正弦波電圧信号(u1(t),u2(t))を出力するステップと、

前記2つの正弦波電圧信号を一定周期でサンプリングして得られる系列(u1(n),u2(n))間の瞬時位相の差に基づく時間差系列(x(n))を出力するステップと、

前記時間差系列に基づいてワンダ量を計算するステップと、

予め設定される前記被測定信号の公称周波数と前記基準信号の公称周波数とに基づき、規定の出力周波数(f0)に最も近づく周波数チューニング・ワード(FTW1,FTW2)を設定して前記2つの正弦波電圧信号の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧するステップとを含むことを特徴とするワンダ測定方法。

【請求項4】

前記周波数チューニング・ワードの設定に基づく前記2つの正弦波電圧信号の出力周波数の差を周波数オフセット(Δf)として算出するステップと、

前記周波数オフセットを用いて前記時間差系列を補正し、前記周波数オフセットに起因する測定誤差を抑圧するステップとを更に含むことを特徴とする請求項3記載のワンダ測定方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−88312(P2013−88312A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−229831(P2011−229831)

【出願日】平成23年10月19日(2011.10.19)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月19日(2011.10.19)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

[ Back to top ]