下位互換性を有するインタフェースおよび方法

【課題】異なる転送プロトコルと互換性を有するインタフェース及び方法を提供する。

【解決手段】インタフェースは、パッドの組と通信するために選択的にイネーブルされる第1及び第2のタイプの物理インタフェースを含む。第1の転送プロトコル回路は第1のモードにおいて第1のタイプの物理インタフェースと協働して動作可能であり、第2の転送プロトコル回路は第2のモードにおいて第2のタイプの物理インタフェースと協働して動作可能である。モードコントローラは、動作モードを示すモード値に基づいて一方の物理インタフェース及び対応する転送プロトコルをイネーブルする。第1のモードがデフォルトのモードであり、モードコントローラは第2のモードへの動的な遷移をイネーブルする。第1のモードに戻る動的な遷移のために、第2のモード中にエスケープ指示がイネーブルされる。プログラム可能なタイミング値がモード遷移を容易にするために使用される。

【解決手段】インタフェースは、パッドの組と通信するために選択的にイネーブルされる第1及び第2のタイプの物理インタフェースを含む。第1の転送プロトコル回路は第1のモードにおいて第1のタイプの物理インタフェースと協働して動作可能であり、第2の転送プロトコル回路は第2のモードにおいて第2のタイプの物理インタフェースと協働して動作可能である。モードコントローラは、動作モードを示すモード値に基づいて一方の物理インタフェース及び対応する転送プロトコルをイネーブルする。第1のモードがデフォルトのモードであり、モードコントローラは第2のモードへの動的な遷移をイネーブルする。第1のモードに戻る動的な遷移のために、第2のモード中にエスケープ指示がイネーブルされる。プログラム可能なタイミング値がモード遷移を容易にするために使用される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般的には電子インタフェースに関し、より詳細には、下位互換性を有する、複数の異なる転送プロトコル間のインタフェースおよび方法に関する。

【背景技術】

【0002】

実際面において、複数の用途のために構成され、または事実上の業界標準に準拠して実装されるいくつかの従来の電子デバイスまたは回路インタフェースは、現在のまたは新たな用途に対して適切な帯域幅を有しない場合がある。例えば、IEEE 1149.1標準規格に準拠するジョイント・テスト・アクション・グループ(JTAG)のバウンダリスキャンは、デバッグ(例えば、ソフトウェアデバッグ)、テスト(例えば、ビルトイン・セルフ・テスト・プロシージャ)、電子機械較正、バウンダリスキャンなどのような、さまざまな目的に使用される、1つのこのような事実上の業界標準である。従来のJTAGインタフェースは、約25メガヘルツ(MHz)のような比較的低い帯域幅において動作する比較的高いシングルエンド電圧レベル信号を使用する。ほとんどの低コストツールが従来のJTAGインタフェースを使用している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許第7593411号明細書

【特許文献2】米国特許第6850660号明細書

【特許文献3】米国特許第6825698号明細書

【図面の簡単な説明】

【0004】

【図1】一実施形態による物理インタフェースを含むインタフェースシステムの簡略ブロック図である。

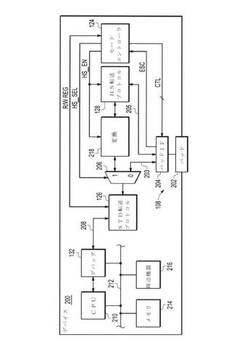

【図2】図1のデバイスの一実施形態に従って実装されるデバイスのより詳細なブロック図である。

【図3】一実施形態に従って実装される図1および2のモードコントローラの簡略ブロック図である。

【図4】パッドの一部およびパッドIF回路の対応する部分を含む図2の物理インタフェースの代表的な部分の簡略ブロック図である。

【図5】標準モードから高速モードへの遷移の間の、図2のパッドの状態および図2のデバイスのESC指示検出のステータスを示す表である。

【図6】高速モードから標準モードへの遷移の間の、図2のパッドの状態および図2のデバイスのESC指示検出のステータスを示す表である。

【図7】標準モードと高速モードとの間の遷移に関する、図2のデバイスの動作の状態を示す簡略状態図である。

【発明を実施するための形態】

【0005】

以下の説明は、当業者が本発明を、特定の用途およびその要件の文脈内で提供されるように作成および使用することを可能にするために提示される。しかしながら、好ましい実施形態に対するさまざまな改変が当業者には明らかであり、本明細書において定義される一般原則は他の実施形態にも適用され得る。それゆえ、本発明は、本明細書において示され説明される特定の実施形態に限定されることは意図されておらず、本明細書において開示される原則および新規の特徴と一致する最も広い範囲に従うべきである。

【0006】

集積回路(IC)の内部データ変数のランタイム可視性のためのもののような、より高い帯域幅を提供する、より高速の開発プロトコルインタフェースを提供することが望ましい。最新のプロトコルインタフェースは、最大300MHzまたはそれを超えるような著しく高い帯域幅を提供する低電圧差動シグナリングを用いて動作するように設計されている。既存のまたは従来のプロトコルとの下位互換性を維持しながら、より高速の開発プロトコルインタフェースを利用することが望ましい。「インフライト」の間、即ち実行している間により低速のモードとより高速のモードとの間で遷移することも望ましい。既存のインタフェースは遅すぎるか、静的であるかまたは他の様態で既存の構成と互換性がない。

【0007】

図1は、一実施形態による物理インタフェースを含むインタフェースシステム100の簡略ブロック図である。物理インタフェースは入力および出力インタフェースであることができ、ただし、物理インタフェースは単独で入力インタフェースまたは単独で出力インタフェースであることが理解される。インタフェースシステム100は、通信リンク106を介してホスト104に接続されるデバイス102を含む。一実施形態において、デバイス102およびホスト104は各々集積回路(IC)として実装され、各々システム・オン・チップ(SOC)構成に従って構成される。ホスト104とデバイス102との間のインタフェースは、デバッグ、テスト、較正、バウンダリスキャンなどのようなさまざまな機能または目的のうちのいずれか1つのためのものである。通信リンク106は、デバイス102とホスト104との間で対応する信号を伝送するために、複数の導電性経路、ワイヤ、配線などを組み組むコネクタ、ケーブル、導電性配線などのような任意の適切な様式で実装される。デバイス102は物理インタフェース(IF)108を含み、ホスト104は、デバイス102とホスト104との間の通信を可能にするために、通信リンク106に物理的かつ電気的に接続するための同様の物理インタフェース110を含む。

【0008】

簡略化された構成において、ホスト104は、インタフェースのセット、即ち、物理インタフェース110をモードコントローラ114、標準(STD)転送プロトコル回路116、および高速(HS)転送プロトコル回路118に接続するバス112を含んで示されている。ホストロジック120は、ホスト104とデバイス102との間の通信を設定および制御するために含まれることができ、ただし、代替的な実施態様が意図される。ホストロジック120は、バス112に接続されることができ、或いは、別個にモードコントローラ114、STD転送プロトコル回路116、およびHS転送プロトコル回路118のうちの1つまたは複数に接続される。バス112は、データや制御信号を伝送するために複数の導電性配線などを用いて従来の様式で実装される。バス112は、代替的な方法に従って実装されることができ、当業者に理解されるようなインタフェース、制御デバイス、またはその両方をさらに含んでもよい。

【0009】

モードコントローラ114は、イネーブル信号STD_ENをSTD転送プロトコル回路116に提供し、別のイネーブル信号HS_ENをHS転送プロトコル回路118に提供する。一般的に、モードコントローラ114は、独立して、またはホストロジック120の制御下で、デバイス102と通信するためにSTD転送プロトコル回路116またはHS転送プロトコル回路118をイネーブルする。モードコントローラ114は、1つまたは複数の制御(CTL)信号を、STD転送プロトコル回路116またはHS転送プロトコル回路118のうちの動作しているものに従って物理インタフェース110を制御、イネーブル、またはその両方を行うために提供する。

【0010】

デバイス102は、同様の構成で、インタフェースのセット、即ち、物理インタフェース108を、モードコントローラ124、STD転送プロトコル回路126、およびHS転送プロトコル回路128に接続するバス122を含んで示されている。STD転送プロトコル回路126およびHS転送プロトコル回路128は、各々、データおよび制御信号を含むバス130を介して1つまたは複数のデバッグブロック132にさらに接続される。ホスト104の場合と同様に、モードコントローラ124は、イネーブル信号STD_ENをSTD転送プロトコル回路126に提供し、別のイネーブル信号HS_ENをHS転送プロトコル回路128に提供する。モードコントローラ124は、ホスト104と通信するために、STD転送プロトコル回路126またはHS転送プロトコル回路128をイネーブルする。モードコントローラ124は、1つまたは複数の制御(CTL)信号を、STD転送プロトコル回路126またはHS転送プロトコル回路128のうちの動作しているものに従って物理インタフェース108を制御、イネーブル、またはその両方を行うために提供する。

【0011】

本明細書においてさらに説明されるように、物理インタフェース108および110の各々は、外部から提供される通信リンク106と物理的および電気的に相互作用するためのパッドの組(例えば、図2の202)を含む。物理インタフェース108および110の各々は、パッドを対応する内部接続(例えば、112、122)を介してSTD転送プロトコルまたはHS転送プロトコルのうちのイネーブルされているものに対して相互作用するための、対応するパッドインタフェース(IF)回路(例えば、図2の204)をさらに含む。

【0012】

一実施形態において、パワーオンまたはリセット(POR)されると、デバイス102およびホスト104は、最初は「標準」モードで動作し、当該モードにおいて、ホスト104のSTD転送プロトコル回路116およびデバイス102のSTD転送プロトコル回路126が通信を確立するために最初にイネーブルされている。ホスト104は、「オンザフライ」または「インフライト」を高速モードに動的に切り替えるためのコマンドや通信パラメータをデバイス102に送り、当該高速モードにおいて、モードコントローラ124は、デバイス102内のHS転送プロトコル回路128をイネーブルすることによって動作をHSモードに遷移させる。同様に、モードコントローラ114は、ホスト104内のHS転送プロトコル回路118をイネーブルすることによって、動作をHSモードに遷移させる。遷移が完了した後、デバイス102およびホスト104は著しく高い帯域幅パフォーマンスのための高速動作に従って、はるかに高速で情報を通信することができる。

【0013】

ホスト104は、より低速の標準モードに戻すように動的に遷移するための別のコマンドや通信パラメータをデバイス102に送ることができる。このようにして、デバイス102およびホスト104は両方とも高速動作のために構成され、両方とも最初は標準モードとの下位互換性のために構成される。

【0014】

一実施形態において、エスケープ指示の検出をイネーブルすることによって、外部擾乱などに起因してより高速のシグナリングモードにおいて通信が可能性として損失することから回復することが可能となる。高速モードの間、ホスト104は何らかの理由によるデバイス102との通信の損失を検出すると、通信を再確立するために、デバイス102に標準モードに切り替え戻させるためのエスケープ指示などをアサートすることができる。一実施形態において、ホスト104は、物理インタフェース108のパッド202のうちの1つまたは複数を、信号を強制的に0ボルト(V)または接地などにするように、差分共通モード範囲などを脱して駆動するように構成され、物理インタフェース108は、差分範囲外信号を検出するとともにエスケープ信号などを内部アサートするように構成される。モードコントローラ124は、アサートされたエスケープ信号を検出し、動作を標準モードに戻すように遷移する。

【0015】

一実施形態において、物理インタフェース108は、第1のタイプの物理インタフェース(標準モード)から第2のタイプの物理インタフェース(高速モード)に動的に遷移され、必要または所望に応じて再び戻る。一実施形態において、第1のタイプの物理インタフェースはシングルエンドシグナリングを採用し、一方で第2のタイプの物理インタフェースは、より高い帯域幅パフォーマンスのために低電圧差動シグナリングを採用する。より具体的な実施形態において、第1のタイプの物理インタフェースは、JTAG IEEE 1149.1標準規格に準拠して実装されることができ、ただし、シリアル周辺機器インタフェース(SPI)などのような他のタイプの標準規格が考慮される。JTAGは、約10〜30MHzの通信帯域幅において動作する。第2のタイプの物理インタフェースは、より高い帯域幅パフォーマンスのために低電圧差動シグナリング(LVDS)に準拠して実装される。LVDSは、約1.2Vの共通モード電圧を用いる電気デジタル・シグナリング・システムであり、最大300MHzまたはさらに高い通信帯域幅において動作することができる。

【0016】

一実施形態において、ホスト104は、デバイス102に、レジスタなどにおいて高速イネーブルビットを設定するコマンドパケットなどを送り、当該高速イネーブルビットは、モードコントローラ124に、高速モードに遷移させる。ホスト104は、1つまたは複数のプログラム可能なタイミング値をさらに送信することができ、当該タイミング値は、デバイス102によって、本明細書においてさらに説明されるようなスイッチ回路遅延および信号の整定に充てるための対応する期間(複数の場合もあり)を確立するために使用される。

【0017】

図2は、デバイス102の一実施形態に従って実装されるデバイス200のより詳細なブロック図である。物理インタフェース108は、通信リンク106に接続するためのパッド202の組と、パッド202に接続される対応するパッドIF回路204とを含む。パッドIF回路204は選択的に、STD転送プロトコル回路126を信号線203の組および選択ロジック206を介して相互作用するように、またはHS転送プロトコル回路128を信号線205の組を介して相互作用するように、構成される。パッドIF回路204はさらに、少なくとも1つのエスケープ(ESC)信号をモードコントローラ124に提供し、当該モードコントローラは、CTL信号を提供して、動作モードに応じてパッドIF回路204の構成を制御する。

【0018】

この構成において、STD転送プロトコル回路126は、別個のインタフェース208を介してデバッグブロック132に接続される。デバッグロジック132はさらに、デバイス200の中央処理装置(CPU)210に接続される。CPU210はさらに、システムバス212を介してメモリ214および1つまたは複数の周辺機器216に接続される。デバッグロジック132も、メモリ操作のためにシステムバス212に接続される。一実施形態において、デバッグブロック132は、CPU210の動作をモニタリングする。STD転送プロトコル回路126は、デバッグブロック132を介して、CPU210のバウンダリスキャン動作、デバッグ動作、較正動作などを実行することができる。

【0019】

HS転送プロトコル回路128は、STD転送プロトコル回路126と同様にしてデバッグロジック132に接続されることができ、ここで、動作モードに応じて1度に一方がイネーブルされる。例示されている実施形態において、STD転送プロトコル回路126は内部では、HS転送プロトコル回路128の高速動作に対処するのに十分高速で動作する。しかしながら、標準モードで動作しているとき、物理インタフェース108は、標準通信のための構成されるはるかに低い帯域幅で動作する。高速動作モードにおいて、HS転送プロトコル回路128は、高速通信のために構成される物理インタフェース108を介してホスト104と通信し、変換ロジック218が、STD転送プロトコル回路126と互換性であるように通信を変換するために提供される。変換ロジック218は、選択ロジック206の一方の入力を通じてSTD転送プロトコル回路126の入力に接続される。例示されている実施形態において、選択ロジック206は、モードコントローラ124によって提供される選択信号HS_SELによって指示される動作モードに応じて信号線203または変換ロジック218を選択するためのマルチプレクサ(MUX)として実装される。

【0020】

PORされると、デバイス200はデフォルトで標準動作モードに設定される。モードコントローラ124は、CTL信号をアサートしてパッドIF回路204を標準モードのために制御する。これは、標準プロトコルしかサポートしていない場合があるホストに対する下位互換性を可能にする。モードコントローラ124は、HS_EN信号をローでアサートして(またはローでネゲートされて)HS転送プロトコル回路128および変換ロジック218をディセーブルし、HS_SEL信号をアサートして選択ロジック206を、信号線203を選択するように制御する。従って、パッド202はパッドIF回路204を介してSTD転送プロトコル回路126に、選択ロジック206を介して接続される。ホスト104は、標準モードにおいても構成され、従来の構成と同様にしてSTD転送プロトコル回路116を使用して通信する。

【0021】

ホスト104は、高速モードに遷移するためのコマンドなどをデバイス200のSTD転送プロトコル回路126に送る。STD転送プロトコル回路126は、モードコントローラ124内の制御レジスタ(例えば、図3の302)を、リード/ライトレジスタ(R/W REG)パスを介してモード値MODE_HS(図3)を設定するようにプログラムし、さらに、遷移を容易にするために選択された値にプログラムされる1つまたは複数のタイミング値を送ることができる。R/W REGパスは、STD転送プロトコル回路126とモードコントローラ124との間の通信を容易にするための1つまたは複数の信号を含む。モードコントローラ124は、CTL信号をアサートしてパッドIF回路204を信号線205のために遷移させることによって応答する。モードコントローラ124は、HS_EN信号をハイでアサートしてHS転送プロトコル回路128をイネーブルし、HS_SELをアサートして選択ロジック206を変換ロジック218を選択するように切り替える。遷移が完了すると、同様に高速モードに遷移しているホスト200は、パッドIF回路204および信号線205を介してHS転送プロトコル回路128と通信する。通信は、変換ロジック218によって変換され、それによって、ホスト104はSTD転送プロトコル回路126と間接的に通信する。なお、高速モードに構成されるパッドIF回路204、信号線205、HS転送プロトコル回路128および変換ロジック218を介する高速通信経路は、標準モードのために構成されるパッドIF回路204および信号線203を介する標準通信経路よりも大幅に速い。

【0022】

図3は、一実施形態に従って実装されるモードコントローラ124の簡略ブロック図である。モードコントローラ124は、制御レジスタ302と、1つまたは複数のカウンタ304と、スイッチロジック306と、パッドコントローラ308とを含む。制御レジスタ302は、任意の適切なタイプのプログラム可能メモリデバイスを使用して実装される。スイッチロジック306およびカウンタ304は、バス310(または信号線の適切な組)を介して制御レジスタ302に接続され、カウンタ304、スイッチロジック306およびパッドコントローラ308は、動作モード間の制御および遷移のために互いに接続されて示されている。R/W REGパスは制御レジスタ302と相互作用する。ESC信号がスイッチロジック306に提供され、当該スイッチロジックはHS_EN信号およびHS_SEL信号を提供する。パッドコントローラ308は、パッドIF回路204を制御するためのCTL信号を提供する。

【0023】

制御レジスタ302は、動作モード間の制御および遷移のためのいくつかの2値通信パラメータを記憶する。図示されるように、制御レジスタ302は、モード制御値MODE_HSならびに2つのタイマ値TIMER1およびTIMER2を記憶する。MODE_HSは、標準モードのためにクリア(ロー)されるか、高速モードのために設定(ハイ)されるか、またはその逆である、単一ビットである。TIMER1値は第1のタイムアウトTIMEOUT1によって示される第1の期間を判定するためにカウンタ304内に読み出され、TIMER2値は第2のタイムアウトTIMEOUT2によって示される第2の期間を判定するためにカウンタ304内に読み出される。

【0024】

PORされると、MODE_HS値は最初は標準モードを示すためにローにクリアされている。ホスト104は、第1および第2の期間をプログラムするとともにMODE_HSをハイに設定して高速モードに遷移するためにTIMER1およびTIMER2内にさらに値を記憶するための1つまたは複数の通信またはコマンドを送る。スイッチロジック306は、ハイに設定されたMODE_HSを検出してパッドコントローラ308に高速モードに遷移させるよう指示する。パッドコントローラ308は、CTL信号をアサートして、物理インタフェース108を下記にさらに説明されるような中間安全モードにするようにパッドIF回路204を制御することによって応答する。スイッチロジック306も、HS_EN信号をハイでアサートしてHS転送プロトコル回路128をイネーブルし、高速モードへの遷移を開始する。第1の期間を開始するためにTIMER1値がカウンタ304内に読み出される。

【0025】

TIMEOUT1を受けた第1の期間の後、スイッチロジック306はパッドコントローラ308に、パッドIF回路204をイネーブルして高速インタフェースをイネーブルさせるように指示する。スイッチロジック306は、変換ロジック218を選択するためにHS_SEL信号もアサートする。カウンタ304はリセットされ、第2の期間を開始するためにTIMER2値がカウンタ304内に読み出される。TIMEOUT2を受けた第2の期間の満了後、スイッチロジック306はパッドIF回路204によるエスケープ指示の検出をイネーブルする。エスケープ指示が検出されると、パッドIF回路204は標準モードに戻る遷移を始めるためにESC信号をアサートする。この期間は、デバイス102およびホスト104が両方とも高速モードに移行することを可能にする。

【0026】

高速モードの間、MODE_HS値がクリアされる場合、またはESC信号がスイッチロジック306によってアサートされているものとして検出される場合、パッドコントローラ308はパッドIF回路204を中間安全モードに遷移させ、第1の期間を開始するためにTIMER1がカウンタ304内に読み出される。標準モードに遷移して戻るために、ESC指示の検出が抑制され、HS_ENがネゲートされる。TIMEOUT1を受けた第1の期間の後、パッドコントローラ308は、物理インタフェース108を標準モードにイネーブルするためにCTL信号をアサートし、信号線203を選択するためにHS_SELがアサートされる。

【0027】

図4は、パッド202の一部およびパッドIF回路204の対応する部分を含む物理インタフェース108の代表的な部分の簡略ブロック図である。追加のパッドおよび対応する回路が含まれてもよいが、図示されてはいない。パッド202は、通信リンク106などを介するなどして外部デバイスと相互作用するためのパッドP1〜P4を含む。パッドIF回路204は、共通のパッド202の組を共有する第1のタイプの物理インタフェース401と、第2のタイプの物理インタフェース411とに分割される。第1のタイプの物理インタフェース401は、標準モード(それぞれSTD1、STD2、STD3およびSTD4)で動作する4つのパッドIFブロック402、404、406および408を含む。第2のタイプの物理インタフェース411は、パッドIFブロック412および414(それぞれHS1およびHS2)のペアを含む。パッドIFブロック402、404、406、408、412および414の各々を制御するために、イネーブル信号、安全モード信号などを含むような、CTL信号が提供される。

【0028】

標準モードにおいて、第2のタイプの物理インタフェース411のパッドIFブロック412および414はディセーブルされており、第1のタイプの物理インタフェース401のパッドIFブロック402、404、406および408はイネーブルされている。イネーブルされると、パッドIFブロック402および408は、外部シングルエンド信号S1およびS4を受け取るとともにS1およびS4を信号線203を介してSTD転送プロトコル回路126に伝送するための入力パッドとして構成される。イネーブルされると、パッドIFブロック404および406は、内部シングルエンド信号S2およびS3をSTD転送プロトコル回路126から対応するパッドP2およびP3を介して外部デバイスに伝送するための出力パッドとして構成される。追加のパッドおよび対応する回路が、具体的な実施態様に応じて追加の入力、出力または入出力(I/O)信号のために含まれてもよい。

【0029】

高速モードにおいては、パッドIFブロック412および414がイネーブルされており、パッドIFブロック402、404、406および408はディセーブルされている。イネーブルされると、パッドIFブロック412は、パッドP1およびP2に提供される差動入力信号S5を受け取り、信号線205を介してHS転送プロトコル回路128に伝送するための差動入力パッドIFブロックとして構成される。図示されるように、パッドP1は差動入力信号S5の正(+)極性として構成され、パッドP2は負(−)極性として構成される。イネーブルされると、パッドIFブロック414は、HS転送プロトコル回路128からの差動出力信号S6をパッドP3およびP4に伝送するための差動出力パッドとして構成される。図示されるように、パッドP3は差動出力信号S6の正(+)極性として構成され、パッドP4は負(−)極性として構成される。ここでも、追加のパッドおよび回路が、追加の入力、出力またはI/O信号のために含まれてもよい。高速モードにおいて、追加の信号は差動またはシングルエンドである場合がある。例えば、高速クロック信号が追加のHSパッドおよび対応するパッド上で伝送される場合がある。

【0030】

パッドIFブロック412および414は各々ESC信号を提供するように示されている。ESC信号は複数のパッドIFブロックのうちの任意の1つによって提供されてもよいし、または1つの選択されるパッドIFブロックによって提供されてもよい。標準モードの間は、パッドIFブロック412および414がディセーブルされ、ESC信号は任意の動作上の効果をもたらすことを事実上抑制される。高速モードの間は、デバイス102とホスト104との間の通常通信動作の間ESC信号はローでアサートされる(またはネゲートされる)。外部擾乱のような何らかの理由により高速モードの間にデバイス102とホスト104との間の通信が損失すると、ホスト104はエスケープ指示を、パッドIFブロック412によって検出されるパッドP1およびP2のうちの一方または両方に提供する。代替的に、または加えて、ホスト104はエスケープ指示を、パッドIFブロック414によって検出される、パッドP3およびP4のうちの一方または両方に提供する。

【0031】

一例として、パッドIFブロック412および414は両方とも、既知のまたは他の様態で許容可能な差動共通モード電圧範囲を有する差動共通モード電圧内で差動モードで動作し、ここで、パッドP3およびP4に接続される信号も差動共通モード電圧範囲を有する。ホスト104はパッドP1もしくはP2(またはP3もしくはP4)に提供される信号に対してはシングルエンド信号を、あるいは両方に対して通常の共通モード範囲から外れる差動信号を生成することができる。一例として、ホスト104は、パッドP1およびP2に提供される信号を強制的に0V(または接地)にし得、それによって、通常共通モード電圧仕様に事実上違反する。パッドIFブロック412は、共通モード電圧範囲違反を検出し、ESC信号をモードコントローラ124にアサートし、これは、動作を高速モードから標準動作モードに戻すように遷移する。

【0032】

標準モードと高速モードとの間の遷移期間の間、パッドIF回路204のIFブロックのうちの1つまたは複数および対応するパッド202は、遷移を容易にするために「安全」モードなどに設定可能である。従って、パッドIFブロックは、外部信号(対応するパッドを介する)および内部信号の一方または両方を、「HI−Z」状態と称される高インピーダンス状態にすることができる。加えてまたは代替形態において、外部信号(およびパッド)および内部信号の一方または両方が、論理0または論理1のような既知の状態または信号レベルになってもよい。一例として、標準モードから高速モードへの遷移の間、パッドIFブロック402はパッドP1を、内部バッファなどをディセーブルすることなどによってHI−Z状態にすることができ、信号S1を、論理1、論理0またはHI−Zのような任意の適切なまたはそれ以外の所定の値にアサートすることができる。このような遷移動作はスプリアス信号または電圧/電流ノイズを抑制または他の様態で低減し、動作モード間の円滑な遷移を容易にする。

【0033】

図5は、標準モードから高速モードへの遷移の間の、パッド202の状態およびデバイス102のESC指示検出のステータスを示す表500である。第1のタイプの物理インタフェース401と第2のタイプの物理インタフェース411との間の遷移の間、パッド202の各々の状態が、パッドIF回路204のステータスによって判定されるか、または他の様態で当該状態を反映する。この場合、標準モードはJTAGとして定義され、第1のタイプの物理インタフェース401は、JTAGに準拠するシグナリングを含み、高速モードは高速クロック出力HSCLKを用いるLVDSシグナリングを使用して定義される。一実施形態において、高速モードの間にHSCLKはデバイス200上で生成され、パッド202に提供される。

【0034】

表500は、列501〜505を含み、ここで、第1の列501は例示的なパッドP1〜P5およびESCを列挙している。第2の列502は標準状態に関するP1〜P5の機能を列挙しており、これは例示されている実施形態においてはJTAGについて特に定義されており、ただし、他の標準インタフェース方法が考慮されることが留意される。この場合、第1のタイプの物理インタフェース401がイネーブルされ(パッドIFブロック402、404をイネーブルするなどして)、デバイス102のパッドP1〜P5はそれぞれ、テスト・データ・イン(Test Data In)(TDI)、テストモード選択(Test Mode Select)(TMS)、テスト・データ・アウト(Test Data Out)(TDO)、テストリセット(TRST)、およびテストクロック(Test Clock)(TCLK)として定義される。標準モードの間、ホスト104がインタフェースのためのテストクロック信号を提供するため、TCLKはデバイス102に対する入力として定義され、一方で、ホスト104のための対応するパッドは出力である。ESC指示検出は標準モードにおいては抑制され、それによって、ESC信号の状態は無視される。

【0035】

第3の列503は、モードコントローラ124が、制御レジスタ302内のMODE_HS値(またはビット)が設定されるかまたは他の様態で設定されているものとして検出されることを検出するときに入る標準安全(STD_SAFE)モードである。モードコントローラ124は、第1のタイプの物理インタフェース401を安全モードにするためにCTL信号をアサートし、当該モードにおいて、パッドP1〜P5はHI−Z(高インピーダンス)状態になる。ESC指示検出は抑制されたままである。TIMER1値がカウンタ304内に読み出され、(適切なカウンタ304の動作を開始することなどによって)第1の期間が開始される。

【0036】

第4の列504は、第1の期間が完了した(例えば、カウンタ304のTIMER1カウントの完了)後TIMEOUT1を受けて入るスイッチモードである。HS転送プロトコル回路128がイネーブルされて、第2のタイプの物理インタフェース411をイネーブルするためにCTL信号がアサートされ、それによって、パッド202が高速モードのために定義される。パッドP1およびP2はまとめて、P1に対する正極性TXPおよびP2に対する負極性TXNを含む差動LVDS送信信号として定義される。なお、遷移の間、差動LVDS送信信号は使用されない場合があり、それによって、これらのパッドは代替的にHI−Z状態のままである場合がある。パッドP3およびP4はまとめて、P3に対する正極性RXPおよびP4に対する負極性RXNを含む差動LVDS受信信号として定義される。P5は、デバイス102から出力される高速クロックHSCLKを、高速動作のタイミングを制御するためにホスト104に提供する。ESC指示検出は抑制されたままである。TIMER2値がカウンタ304内に読み出され、第2の期間が開始される。

【0037】

第5の列505は、第2の期間が完了した後TIMEOUT2を受けて入る高速(HS)モードである。この時点において、ESC指示検出がイネーブルされ、フェイルセーフ機構として完全に機能し、パッド202は高速モードのために完全に動作可能である。

【0038】

図6は、高速モードから標準モードへの遷移の間の、パッド202の状態およびデバイス102のESC指示検出のステータスを示す表600である。第1の列601は列501と同じであり、パッドおよびESC指示検出のステータスを列挙している。第2の列602は列505と同じであり、HSモードが動作可能でありイネーブルされていることを示す。第3の列603は、MODE_HS値がクリアされているかまたはESC信号がアサートされているときの標準モードへの遷移のための高速安全モード(HS_SAFE)である。HS_SAFEモードにおいて、第2のタイプの物理インタフェース411は安全モードになり、それによって、パッドP1〜P5はHI−Z状態になり、ESC指示検出が抑制される。さらに、TIMER1値がカウンタ304内に読み出され、第1の期間が開始される。第4の列604は、第1の期間が満了した後TIMEOUT1を受けて再び入る標準モードである。ESC指示検出は、標準動作モードの間は抑制されたままである。

【0039】

図7は、標準モードと高速モードとの間の遷移に関する、デバイス102の動作の状態を示す簡略状態図である。PORされると、動作は初めは状態702によって示されるように標準モードにある(表500の列502)。動作はMODE_HS値が設定されるまで標準モードのままである。

【0040】

MODE_HSが設定されていると検出されると、動作は最終的に、HSモードに遷移するために、状態704によって示されるような(および、表500の列503によって示されるような)STD_SAFEモードに進む。HS転送プロトコル回路128および変換ロジック218をイネーブルするために、HS_EN信号がアサートされる。TIMER1値がカウンタ304内に読み出され、第1の期間が開始される。

【0041】

TIMEOUT1(第1の期間の満了)を受けて、動作は最終的に、状態706(表500の列504)によって示されるようなSWITCHモードに進む。HS転送プロトコル回路128および変換ロジック218がイネーブルされて動作可能になる。第2のタイプの物理インタフェース411がイネーブルされて動作可能になり、高速動作をイネーブルするためにHS_SEL信号がアサートされる。TIMER2値がカウンタ304内に読み出され、第2の期間が開始される。

【0042】

TIMEOUT2を受けて、動作は最終的に、状態708によって示されるような、ならびに表500の列505および表600の列602によって示されるような、高速動作モードに遷移する。ESC信号を介してエスケープ指示を検出するために、エスケープ指示がイネーブルされる。MODE_HSが設定されたままであり、かつESCバーによって示されるようにESC信号がネゲートされたままである間、動作は高速モードのままである。

【0043】

MODE_HS値がクリアとして検出されるか、またはESC信号がハイでアサートされるといつでも、動作は標準モードに戻るべく遷移するために、状態710によって示されるような、および表600の列603によって示されるようなHS_SAFEモードに遷移する。TIMER1値がカウンタ304内に読み出され、第1の期間が開始される。TIMEOUT1を受けて、動作は、表600の列604によって示されるように、状態702における標準モードに戻る。

【0044】

物理インタフェースと、第1の転送プロトコル回路および第2の転送プロトコル回路と、メモリと、モードコントローラとを含むインタフェース。物理インタフェースは、第1のタイプの物理インタフェースと、それと異なる第2のタイプの物理インタフェースとを含み、これらは両方とも共通のパッドの組と相互作用するために選択的にイネーブルされる。第1の転送プロトコル回路は第1の動作モードにおいて第1のタイプの物理インタフェースと協働して動作可能であり、第2の転送プロトコル回路は第2の動作モードにおいて第2のタイプの物理インタフェースと協働して動作可能である。メモリは、第1の動作モードおよび第2の動作モードのうちの一方を示すモード値を記憶する。モードコントローラは、電源投入またはリセットされると、第1の動作モードにおいて第1の転送プロトコルを用いて動作するために第1のタイプの物理インタフェースをイネーブルし、モード値が第2の動作モードを示すとき第2の転送プロトコルを用いて動作するために、第1のタイプの物理インタフェースをディセーブルするとともに第2のタイプの物理インタフェースをイネーブルすることによって、第2の動作モードに動的に遷移する。

【0045】

さまざまな実施形態において、モードコントローラは、モード値が第1の動作モードを示すとき第1の転送プロトコルを用いて動作するために、第2のタイプの物理インタフェースをディセーブルするとともに第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに動作を戻すように動的に遷移する。第1の動作モードと第2の動作モードとの間の遷移のためにプログラム可能な時間値が使用される。モード値および1つまたは複数のプログラム可能なタイミング値は、プログラム可能な期間を提供するためにメモリ内に記憶される。

【0046】

通信の損失の場合などにおいて、第1の動作モードに戻る遷移をイネーブルするために、エスケープ指示が提供される。一実施形態において、例えば、第2のタイプの物理インタフェースは所定の電圧範囲内で動作することができ、所定の電圧範囲を超えるとエスケープ信号をアサートまたは他の様態で提供するように構成される。エスケープ機構は第1の動作モードにおいては抑制され、第2の動作モードにおいてはイネーブルされる。

【0047】

一実施形態において、動作モード間の遷移のために安全モードが使用される。一実施形態において、例えば、第1の物理インタフェースおよび第2の物理インタフェースは、動作モード間で遷移しながら、共通のパッドの組を高インピーダンス状態またはそれ以外の既知の論理状態にするように構成される。より具体的な実施形態において、モードコントローラが、物理インタフェースを動的に安全モードにして、第1の期間を開始し、第1の期間が満了すると第2の転送プロトコルを用いて動作するために第2のタイプの物理インタフェースをイネーブルし、第2の期間を開始し、第2の期間が満了するとエスケープ信号の検出をイネーブルする。

【0048】

モードコントローラは、モード値によってまたはエスケープ信号によって指示されると、第1の転送プロトコルを用いて動作するために、第2のタイプの物理インタフェースをディセーブルするとともに第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに動作を戻すように動的に遷移することができる。

【0049】

第1のタイプの物理インタフェースは、共通のパッドの組を介する第1の帯域幅におけるシングルエンドシグナリングのために構成されることができ、第2のタイプの物理インタフェースは、共通のパッドの組を介する第2のより高い帯域幅における低電圧差動シグナリングのために構成される。第1の動作モードは、JTAGなどのような事実上の業界標準に準拠する。

【0050】

一実施形態によるインタフェースの動作方法は、初めに、第1の転送プロトコルに従って動作するために、共通のパッドの組に接続される第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードで動作する工程と、第1の動作モードおよび第2の動作モードのうちの一方を示すモード値をモニタリングする工程と、モード値によって指示されると、第2の転送プロトコルによって動作するために、共通のパッドの組に接続される第2のタイプの物理インタフェースをイネーブルすることによって、第2の動作モードに動的に遷移する工程とを備える。

【0051】

本方法は、モード値によって指示されると、第1の転送プロトコルを用いて動作するために、第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに戻すように動的に遷移する工程を備える。

【0052】

第2の動作モードに動的に遷移する工程は、第1のタイプの物理インタフェースを安全モードにする工程と、第2の転送プロトコルによる動作をイネーブルする工程と、第2の転送プロトコル動作がイネーブルされると第2のタイプの物理インタフェースを使用して第2の転送プロトコルに動作を切り替える工程とを備える。

【0053】

本方法は、安全モード中に所定期間を開始する工程と、当該期間の満了後に第2のタイプの物理インタフェースを使用して第2の転送プロトコルに動作を切り替える工程とをさらに備える。本方法は、第1の動作モードで動作している間に、第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備えることができ、ここで、コマンドは期間を示す時間値を含む。

【0054】

本方法は、安全モード中に第1の期間を開始する工程と、第1の期間の満了後に第2のタイプの物理インタフェースを使用して第2の転送プロトコルに動作を切り替える工程と、イネーブルされると第2のタイプの物理インタフェースによって、範囲外状態をモニタリングするとともに、範囲外状態が検出されるとエスケープ信号を提供する工程と、第1の期間の満了後に第2の期間を開始する工程と、第2の期間の満了後にエスケープ信号の検出をイネーブルする工程とをさらに備える。

【0055】

本方法は、第1の動作モードで動作している間に、第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備えることができ、ここで、コマンドは第1の期間を示す第1の時間値と、第2の期間を示す第2の時間値とを含む。

【0056】

本方法は、モード値によって指示されると、またはエスケープ信号が検出されると、第1の転送プロトコルに従って動作するために、第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに動的に遷移し戻す工程をさらに備える。本方法は、第2の動作モードにある間に、第1の転送プロトコルと第2の転送プロトコルとの間で変換する工程をさらに備える。

【0057】

別の実施形態による、インタフェースの動作方法は、第1の転送プロトコルおよび第2の転送プロトコルのうちの一方を示すモード値をモニタリングする工程と、モード値が第1の転送プロトコルを示すとき、第1の転送プロトコルに従って動作するために、パッドに接続される第1のタイプの物理インタフェースをイネーブルする工程と、モード値が第2の転送プロトコルを示すとき、当該転送プロトコルに従って動作するために、パッドに接続される第2のタイプの物理インタフェースをイネーブルする工程と、第2の転送プロトコルに従って動作しているときに、パッド上で範囲外条件が検出されると、第1の転送プロトコルに従って動作するように動的に戻すように切り替える工程とを備える。

【0058】

本発明をその特定の好ましいバージョンを参照して相当に詳細に説明してきたが、他のバージョンおよび変形形態が可能であり考慮される。当業者は、添付の特許請求の範囲によって定義されているような本発明の精神および範囲から逸脱することなく、本発明の同じ目的を実行するための他の構造を設計または改変するための基礎として、開示されている概念および具体的な実施形態を容易に使用することができることを理解すべきである。

【符号の説明】

【0059】

100…インタフェースシステム、108,110,401,411…物理インタフェース、114…モードコントローラ、116…標準転送プロトコル回路、118…高速転送プロトコル回路、202…パッド、204…パッドIF回路、208…インタフェース、210…中央処理装置、214…メモリ。

【技術分野】

【0001】

本発明は一般的には電子インタフェースに関し、より詳細には、下位互換性を有する、複数の異なる転送プロトコル間のインタフェースおよび方法に関する。

【背景技術】

【0002】

実際面において、複数の用途のために構成され、または事実上の業界標準に準拠して実装されるいくつかの従来の電子デバイスまたは回路インタフェースは、現在のまたは新たな用途に対して適切な帯域幅を有しない場合がある。例えば、IEEE 1149.1標準規格に準拠するジョイント・テスト・アクション・グループ(JTAG)のバウンダリスキャンは、デバッグ(例えば、ソフトウェアデバッグ)、テスト(例えば、ビルトイン・セルフ・テスト・プロシージャ)、電子機械較正、バウンダリスキャンなどのような、さまざまな目的に使用される、1つのこのような事実上の業界標準である。従来のJTAGインタフェースは、約25メガヘルツ(MHz)のような比較的低い帯域幅において動作する比較的高いシングルエンド電圧レベル信号を使用する。ほとんどの低コストツールが従来のJTAGインタフェースを使用している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許第7593411号明細書

【特許文献2】米国特許第6850660号明細書

【特許文献3】米国特許第6825698号明細書

【図面の簡単な説明】

【0004】

【図1】一実施形態による物理インタフェースを含むインタフェースシステムの簡略ブロック図である。

【図2】図1のデバイスの一実施形態に従って実装されるデバイスのより詳細なブロック図である。

【図3】一実施形態に従って実装される図1および2のモードコントローラの簡略ブロック図である。

【図4】パッドの一部およびパッドIF回路の対応する部分を含む図2の物理インタフェースの代表的な部分の簡略ブロック図である。

【図5】標準モードから高速モードへの遷移の間の、図2のパッドの状態および図2のデバイスのESC指示検出のステータスを示す表である。

【図6】高速モードから標準モードへの遷移の間の、図2のパッドの状態および図2のデバイスのESC指示検出のステータスを示す表である。

【図7】標準モードと高速モードとの間の遷移に関する、図2のデバイスの動作の状態を示す簡略状態図である。

【発明を実施するための形態】

【0005】

以下の説明は、当業者が本発明を、特定の用途およびその要件の文脈内で提供されるように作成および使用することを可能にするために提示される。しかしながら、好ましい実施形態に対するさまざまな改変が当業者には明らかであり、本明細書において定義される一般原則は他の実施形態にも適用され得る。それゆえ、本発明は、本明細書において示され説明される特定の実施形態に限定されることは意図されておらず、本明細書において開示される原則および新規の特徴と一致する最も広い範囲に従うべきである。

【0006】

集積回路(IC)の内部データ変数のランタイム可視性のためのもののような、より高い帯域幅を提供する、より高速の開発プロトコルインタフェースを提供することが望ましい。最新のプロトコルインタフェースは、最大300MHzまたはそれを超えるような著しく高い帯域幅を提供する低電圧差動シグナリングを用いて動作するように設計されている。既存のまたは従来のプロトコルとの下位互換性を維持しながら、より高速の開発プロトコルインタフェースを利用することが望ましい。「インフライト」の間、即ち実行している間により低速のモードとより高速のモードとの間で遷移することも望ましい。既存のインタフェースは遅すぎるか、静的であるかまたは他の様態で既存の構成と互換性がない。

【0007】

図1は、一実施形態による物理インタフェースを含むインタフェースシステム100の簡略ブロック図である。物理インタフェースは入力および出力インタフェースであることができ、ただし、物理インタフェースは単独で入力インタフェースまたは単独で出力インタフェースであることが理解される。インタフェースシステム100は、通信リンク106を介してホスト104に接続されるデバイス102を含む。一実施形態において、デバイス102およびホスト104は各々集積回路(IC)として実装され、各々システム・オン・チップ(SOC)構成に従って構成される。ホスト104とデバイス102との間のインタフェースは、デバッグ、テスト、較正、バウンダリスキャンなどのようなさまざまな機能または目的のうちのいずれか1つのためのものである。通信リンク106は、デバイス102とホスト104との間で対応する信号を伝送するために、複数の導電性経路、ワイヤ、配線などを組み組むコネクタ、ケーブル、導電性配線などのような任意の適切な様式で実装される。デバイス102は物理インタフェース(IF)108を含み、ホスト104は、デバイス102とホスト104との間の通信を可能にするために、通信リンク106に物理的かつ電気的に接続するための同様の物理インタフェース110を含む。

【0008】

簡略化された構成において、ホスト104は、インタフェースのセット、即ち、物理インタフェース110をモードコントローラ114、標準(STD)転送プロトコル回路116、および高速(HS)転送プロトコル回路118に接続するバス112を含んで示されている。ホストロジック120は、ホスト104とデバイス102との間の通信を設定および制御するために含まれることができ、ただし、代替的な実施態様が意図される。ホストロジック120は、バス112に接続されることができ、或いは、別個にモードコントローラ114、STD転送プロトコル回路116、およびHS転送プロトコル回路118のうちの1つまたは複数に接続される。バス112は、データや制御信号を伝送するために複数の導電性配線などを用いて従来の様式で実装される。バス112は、代替的な方法に従って実装されることができ、当業者に理解されるようなインタフェース、制御デバイス、またはその両方をさらに含んでもよい。

【0009】

モードコントローラ114は、イネーブル信号STD_ENをSTD転送プロトコル回路116に提供し、別のイネーブル信号HS_ENをHS転送プロトコル回路118に提供する。一般的に、モードコントローラ114は、独立して、またはホストロジック120の制御下で、デバイス102と通信するためにSTD転送プロトコル回路116またはHS転送プロトコル回路118をイネーブルする。モードコントローラ114は、1つまたは複数の制御(CTL)信号を、STD転送プロトコル回路116またはHS転送プロトコル回路118のうちの動作しているものに従って物理インタフェース110を制御、イネーブル、またはその両方を行うために提供する。

【0010】

デバイス102は、同様の構成で、インタフェースのセット、即ち、物理インタフェース108を、モードコントローラ124、STD転送プロトコル回路126、およびHS転送プロトコル回路128に接続するバス122を含んで示されている。STD転送プロトコル回路126およびHS転送プロトコル回路128は、各々、データおよび制御信号を含むバス130を介して1つまたは複数のデバッグブロック132にさらに接続される。ホスト104の場合と同様に、モードコントローラ124は、イネーブル信号STD_ENをSTD転送プロトコル回路126に提供し、別のイネーブル信号HS_ENをHS転送プロトコル回路128に提供する。モードコントローラ124は、ホスト104と通信するために、STD転送プロトコル回路126またはHS転送プロトコル回路128をイネーブルする。モードコントローラ124は、1つまたは複数の制御(CTL)信号を、STD転送プロトコル回路126またはHS転送プロトコル回路128のうちの動作しているものに従って物理インタフェース108を制御、イネーブル、またはその両方を行うために提供する。

【0011】

本明細書においてさらに説明されるように、物理インタフェース108および110の各々は、外部から提供される通信リンク106と物理的および電気的に相互作用するためのパッドの組(例えば、図2の202)を含む。物理インタフェース108および110の各々は、パッドを対応する内部接続(例えば、112、122)を介してSTD転送プロトコルまたはHS転送プロトコルのうちのイネーブルされているものに対して相互作用するための、対応するパッドインタフェース(IF)回路(例えば、図2の204)をさらに含む。

【0012】

一実施形態において、パワーオンまたはリセット(POR)されると、デバイス102およびホスト104は、最初は「標準」モードで動作し、当該モードにおいて、ホスト104のSTD転送プロトコル回路116およびデバイス102のSTD転送プロトコル回路126が通信を確立するために最初にイネーブルされている。ホスト104は、「オンザフライ」または「インフライト」を高速モードに動的に切り替えるためのコマンドや通信パラメータをデバイス102に送り、当該高速モードにおいて、モードコントローラ124は、デバイス102内のHS転送プロトコル回路128をイネーブルすることによって動作をHSモードに遷移させる。同様に、モードコントローラ114は、ホスト104内のHS転送プロトコル回路118をイネーブルすることによって、動作をHSモードに遷移させる。遷移が完了した後、デバイス102およびホスト104は著しく高い帯域幅パフォーマンスのための高速動作に従って、はるかに高速で情報を通信することができる。

【0013】

ホスト104は、より低速の標準モードに戻すように動的に遷移するための別のコマンドや通信パラメータをデバイス102に送ることができる。このようにして、デバイス102およびホスト104は両方とも高速動作のために構成され、両方とも最初は標準モードとの下位互換性のために構成される。

【0014】

一実施形態において、エスケープ指示の検出をイネーブルすることによって、外部擾乱などに起因してより高速のシグナリングモードにおいて通信が可能性として損失することから回復することが可能となる。高速モードの間、ホスト104は何らかの理由によるデバイス102との通信の損失を検出すると、通信を再確立するために、デバイス102に標準モードに切り替え戻させるためのエスケープ指示などをアサートすることができる。一実施形態において、ホスト104は、物理インタフェース108のパッド202のうちの1つまたは複数を、信号を強制的に0ボルト(V)または接地などにするように、差分共通モード範囲などを脱して駆動するように構成され、物理インタフェース108は、差分範囲外信号を検出するとともにエスケープ信号などを内部アサートするように構成される。モードコントローラ124は、アサートされたエスケープ信号を検出し、動作を標準モードに戻すように遷移する。

【0015】

一実施形態において、物理インタフェース108は、第1のタイプの物理インタフェース(標準モード)から第2のタイプの物理インタフェース(高速モード)に動的に遷移され、必要または所望に応じて再び戻る。一実施形態において、第1のタイプの物理インタフェースはシングルエンドシグナリングを採用し、一方で第2のタイプの物理インタフェースは、より高い帯域幅パフォーマンスのために低電圧差動シグナリングを採用する。より具体的な実施形態において、第1のタイプの物理インタフェースは、JTAG IEEE 1149.1標準規格に準拠して実装されることができ、ただし、シリアル周辺機器インタフェース(SPI)などのような他のタイプの標準規格が考慮される。JTAGは、約10〜30MHzの通信帯域幅において動作する。第2のタイプの物理インタフェースは、より高い帯域幅パフォーマンスのために低電圧差動シグナリング(LVDS)に準拠して実装される。LVDSは、約1.2Vの共通モード電圧を用いる電気デジタル・シグナリング・システムであり、最大300MHzまたはさらに高い通信帯域幅において動作することができる。

【0016】

一実施形態において、ホスト104は、デバイス102に、レジスタなどにおいて高速イネーブルビットを設定するコマンドパケットなどを送り、当該高速イネーブルビットは、モードコントローラ124に、高速モードに遷移させる。ホスト104は、1つまたは複数のプログラム可能なタイミング値をさらに送信することができ、当該タイミング値は、デバイス102によって、本明細書においてさらに説明されるようなスイッチ回路遅延および信号の整定に充てるための対応する期間(複数の場合もあり)を確立するために使用される。

【0017】

図2は、デバイス102の一実施形態に従って実装されるデバイス200のより詳細なブロック図である。物理インタフェース108は、通信リンク106に接続するためのパッド202の組と、パッド202に接続される対応するパッドIF回路204とを含む。パッドIF回路204は選択的に、STD転送プロトコル回路126を信号線203の組および選択ロジック206を介して相互作用するように、またはHS転送プロトコル回路128を信号線205の組を介して相互作用するように、構成される。パッドIF回路204はさらに、少なくとも1つのエスケープ(ESC)信号をモードコントローラ124に提供し、当該モードコントローラは、CTL信号を提供して、動作モードに応じてパッドIF回路204の構成を制御する。

【0018】

この構成において、STD転送プロトコル回路126は、別個のインタフェース208を介してデバッグブロック132に接続される。デバッグロジック132はさらに、デバイス200の中央処理装置(CPU)210に接続される。CPU210はさらに、システムバス212を介してメモリ214および1つまたは複数の周辺機器216に接続される。デバッグロジック132も、メモリ操作のためにシステムバス212に接続される。一実施形態において、デバッグブロック132は、CPU210の動作をモニタリングする。STD転送プロトコル回路126は、デバッグブロック132を介して、CPU210のバウンダリスキャン動作、デバッグ動作、較正動作などを実行することができる。

【0019】

HS転送プロトコル回路128は、STD転送プロトコル回路126と同様にしてデバッグロジック132に接続されることができ、ここで、動作モードに応じて1度に一方がイネーブルされる。例示されている実施形態において、STD転送プロトコル回路126は内部では、HS転送プロトコル回路128の高速動作に対処するのに十分高速で動作する。しかしながら、標準モードで動作しているとき、物理インタフェース108は、標準通信のための構成されるはるかに低い帯域幅で動作する。高速動作モードにおいて、HS転送プロトコル回路128は、高速通信のために構成される物理インタフェース108を介してホスト104と通信し、変換ロジック218が、STD転送プロトコル回路126と互換性であるように通信を変換するために提供される。変換ロジック218は、選択ロジック206の一方の入力を通じてSTD転送プロトコル回路126の入力に接続される。例示されている実施形態において、選択ロジック206は、モードコントローラ124によって提供される選択信号HS_SELによって指示される動作モードに応じて信号線203または変換ロジック218を選択するためのマルチプレクサ(MUX)として実装される。

【0020】

PORされると、デバイス200はデフォルトで標準動作モードに設定される。モードコントローラ124は、CTL信号をアサートしてパッドIF回路204を標準モードのために制御する。これは、標準プロトコルしかサポートしていない場合があるホストに対する下位互換性を可能にする。モードコントローラ124は、HS_EN信号をローでアサートして(またはローでネゲートされて)HS転送プロトコル回路128および変換ロジック218をディセーブルし、HS_SEL信号をアサートして選択ロジック206を、信号線203を選択するように制御する。従って、パッド202はパッドIF回路204を介してSTD転送プロトコル回路126に、選択ロジック206を介して接続される。ホスト104は、標準モードにおいても構成され、従来の構成と同様にしてSTD転送プロトコル回路116を使用して通信する。

【0021】

ホスト104は、高速モードに遷移するためのコマンドなどをデバイス200のSTD転送プロトコル回路126に送る。STD転送プロトコル回路126は、モードコントローラ124内の制御レジスタ(例えば、図3の302)を、リード/ライトレジスタ(R/W REG)パスを介してモード値MODE_HS(図3)を設定するようにプログラムし、さらに、遷移を容易にするために選択された値にプログラムされる1つまたは複数のタイミング値を送ることができる。R/W REGパスは、STD転送プロトコル回路126とモードコントローラ124との間の通信を容易にするための1つまたは複数の信号を含む。モードコントローラ124は、CTL信号をアサートしてパッドIF回路204を信号線205のために遷移させることによって応答する。モードコントローラ124は、HS_EN信号をハイでアサートしてHS転送プロトコル回路128をイネーブルし、HS_SELをアサートして選択ロジック206を変換ロジック218を選択するように切り替える。遷移が完了すると、同様に高速モードに遷移しているホスト200は、パッドIF回路204および信号線205を介してHS転送プロトコル回路128と通信する。通信は、変換ロジック218によって変換され、それによって、ホスト104はSTD転送プロトコル回路126と間接的に通信する。なお、高速モードに構成されるパッドIF回路204、信号線205、HS転送プロトコル回路128および変換ロジック218を介する高速通信経路は、標準モードのために構成されるパッドIF回路204および信号線203を介する標準通信経路よりも大幅に速い。

【0022】

図3は、一実施形態に従って実装されるモードコントローラ124の簡略ブロック図である。モードコントローラ124は、制御レジスタ302と、1つまたは複数のカウンタ304と、スイッチロジック306と、パッドコントローラ308とを含む。制御レジスタ302は、任意の適切なタイプのプログラム可能メモリデバイスを使用して実装される。スイッチロジック306およびカウンタ304は、バス310(または信号線の適切な組)を介して制御レジスタ302に接続され、カウンタ304、スイッチロジック306およびパッドコントローラ308は、動作モード間の制御および遷移のために互いに接続されて示されている。R/W REGパスは制御レジスタ302と相互作用する。ESC信号がスイッチロジック306に提供され、当該スイッチロジックはHS_EN信号およびHS_SEL信号を提供する。パッドコントローラ308は、パッドIF回路204を制御するためのCTL信号を提供する。

【0023】

制御レジスタ302は、動作モード間の制御および遷移のためのいくつかの2値通信パラメータを記憶する。図示されるように、制御レジスタ302は、モード制御値MODE_HSならびに2つのタイマ値TIMER1およびTIMER2を記憶する。MODE_HSは、標準モードのためにクリア(ロー)されるか、高速モードのために設定(ハイ)されるか、またはその逆である、単一ビットである。TIMER1値は第1のタイムアウトTIMEOUT1によって示される第1の期間を判定するためにカウンタ304内に読み出され、TIMER2値は第2のタイムアウトTIMEOUT2によって示される第2の期間を判定するためにカウンタ304内に読み出される。

【0024】

PORされると、MODE_HS値は最初は標準モードを示すためにローにクリアされている。ホスト104は、第1および第2の期間をプログラムするとともにMODE_HSをハイに設定して高速モードに遷移するためにTIMER1およびTIMER2内にさらに値を記憶するための1つまたは複数の通信またはコマンドを送る。スイッチロジック306は、ハイに設定されたMODE_HSを検出してパッドコントローラ308に高速モードに遷移させるよう指示する。パッドコントローラ308は、CTL信号をアサートして、物理インタフェース108を下記にさらに説明されるような中間安全モードにするようにパッドIF回路204を制御することによって応答する。スイッチロジック306も、HS_EN信号をハイでアサートしてHS転送プロトコル回路128をイネーブルし、高速モードへの遷移を開始する。第1の期間を開始するためにTIMER1値がカウンタ304内に読み出される。

【0025】

TIMEOUT1を受けた第1の期間の後、スイッチロジック306はパッドコントローラ308に、パッドIF回路204をイネーブルして高速インタフェースをイネーブルさせるように指示する。スイッチロジック306は、変換ロジック218を選択するためにHS_SEL信号もアサートする。カウンタ304はリセットされ、第2の期間を開始するためにTIMER2値がカウンタ304内に読み出される。TIMEOUT2を受けた第2の期間の満了後、スイッチロジック306はパッドIF回路204によるエスケープ指示の検出をイネーブルする。エスケープ指示が検出されると、パッドIF回路204は標準モードに戻る遷移を始めるためにESC信号をアサートする。この期間は、デバイス102およびホスト104が両方とも高速モードに移行することを可能にする。

【0026】

高速モードの間、MODE_HS値がクリアされる場合、またはESC信号がスイッチロジック306によってアサートされているものとして検出される場合、パッドコントローラ308はパッドIF回路204を中間安全モードに遷移させ、第1の期間を開始するためにTIMER1がカウンタ304内に読み出される。標準モードに遷移して戻るために、ESC指示の検出が抑制され、HS_ENがネゲートされる。TIMEOUT1を受けた第1の期間の後、パッドコントローラ308は、物理インタフェース108を標準モードにイネーブルするためにCTL信号をアサートし、信号線203を選択するためにHS_SELがアサートされる。

【0027】

図4は、パッド202の一部およびパッドIF回路204の対応する部分を含む物理インタフェース108の代表的な部分の簡略ブロック図である。追加のパッドおよび対応する回路が含まれてもよいが、図示されてはいない。パッド202は、通信リンク106などを介するなどして外部デバイスと相互作用するためのパッドP1〜P4を含む。パッドIF回路204は、共通のパッド202の組を共有する第1のタイプの物理インタフェース401と、第2のタイプの物理インタフェース411とに分割される。第1のタイプの物理インタフェース401は、標準モード(それぞれSTD1、STD2、STD3およびSTD4)で動作する4つのパッドIFブロック402、404、406および408を含む。第2のタイプの物理インタフェース411は、パッドIFブロック412および414(それぞれHS1およびHS2)のペアを含む。パッドIFブロック402、404、406、408、412および414の各々を制御するために、イネーブル信号、安全モード信号などを含むような、CTL信号が提供される。

【0028】

標準モードにおいて、第2のタイプの物理インタフェース411のパッドIFブロック412および414はディセーブルされており、第1のタイプの物理インタフェース401のパッドIFブロック402、404、406および408はイネーブルされている。イネーブルされると、パッドIFブロック402および408は、外部シングルエンド信号S1およびS4を受け取るとともにS1およびS4を信号線203を介してSTD転送プロトコル回路126に伝送するための入力パッドとして構成される。イネーブルされると、パッドIFブロック404および406は、内部シングルエンド信号S2およびS3をSTD転送プロトコル回路126から対応するパッドP2およびP3を介して外部デバイスに伝送するための出力パッドとして構成される。追加のパッドおよび対応する回路が、具体的な実施態様に応じて追加の入力、出力または入出力(I/O)信号のために含まれてもよい。

【0029】

高速モードにおいては、パッドIFブロック412および414がイネーブルされており、パッドIFブロック402、404、406および408はディセーブルされている。イネーブルされると、パッドIFブロック412は、パッドP1およびP2に提供される差動入力信号S5を受け取り、信号線205を介してHS転送プロトコル回路128に伝送するための差動入力パッドIFブロックとして構成される。図示されるように、パッドP1は差動入力信号S5の正(+)極性として構成され、パッドP2は負(−)極性として構成される。イネーブルされると、パッドIFブロック414は、HS転送プロトコル回路128からの差動出力信号S6をパッドP3およびP4に伝送するための差動出力パッドとして構成される。図示されるように、パッドP3は差動出力信号S6の正(+)極性として構成され、パッドP4は負(−)極性として構成される。ここでも、追加のパッドおよび回路が、追加の入力、出力またはI/O信号のために含まれてもよい。高速モードにおいて、追加の信号は差動またはシングルエンドである場合がある。例えば、高速クロック信号が追加のHSパッドおよび対応するパッド上で伝送される場合がある。

【0030】

パッドIFブロック412および414は各々ESC信号を提供するように示されている。ESC信号は複数のパッドIFブロックのうちの任意の1つによって提供されてもよいし、または1つの選択されるパッドIFブロックによって提供されてもよい。標準モードの間は、パッドIFブロック412および414がディセーブルされ、ESC信号は任意の動作上の効果をもたらすことを事実上抑制される。高速モードの間は、デバイス102とホスト104との間の通常通信動作の間ESC信号はローでアサートされる(またはネゲートされる)。外部擾乱のような何らかの理由により高速モードの間にデバイス102とホスト104との間の通信が損失すると、ホスト104はエスケープ指示を、パッドIFブロック412によって検出されるパッドP1およびP2のうちの一方または両方に提供する。代替的に、または加えて、ホスト104はエスケープ指示を、パッドIFブロック414によって検出される、パッドP3およびP4のうちの一方または両方に提供する。

【0031】

一例として、パッドIFブロック412および414は両方とも、既知のまたは他の様態で許容可能な差動共通モード電圧範囲を有する差動共通モード電圧内で差動モードで動作し、ここで、パッドP3およびP4に接続される信号も差動共通モード電圧範囲を有する。ホスト104はパッドP1もしくはP2(またはP3もしくはP4)に提供される信号に対してはシングルエンド信号を、あるいは両方に対して通常の共通モード範囲から外れる差動信号を生成することができる。一例として、ホスト104は、パッドP1およびP2に提供される信号を強制的に0V(または接地)にし得、それによって、通常共通モード電圧仕様に事実上違反する。パッドIFブロック412は、共通モード電圧範囲違反を検出し、ESC信号をモードコントローラ124にアサートし、これは、動作を高速モードから標準動作モードに戻すように遷移する。

【0032】

標準モードと高速モードとの間の遷移期間の間、パッドIF回路204のIFブロックのうちの1つまたは複数および対応するパッド202は、遷移を容易にするために「安全」モードなどに設定可能である。従って、パッドIFブロックは、外部信号(対応するパッドを介する)および内部信号の一方または両方を、「HI−Z」状態と称される高インピーダンス状態にすることができる。加えてまたは代替形態において、外部信号(およびパッド)および内部信号の一方または両方が、論理0または論理1のような既知の状態または信号レベルになってもよい。一例として、標準モードから高速モードへの遷移の間、パッドIFブロック402はパッドP1を、内部バッファなどをディセーブルすることなどによってHI−Z状態にすることができ、信号S1を、論理1、論理0またはHI−Zのような任意の適切なまたはそれ以外の所定の値にアサートすることができる。このような遷移動作はスプリアス信号または電圧/電流ノイズを抑制または他の様態で低減し、動作モード間の円滑な遷移を容易にする。

【0033】

図5は、標準モードから高速モードへの遷移の間の、パッド202の状態およびデバイス102のESC指示検出のステータスを示す表500である。第1のタイプの物理インタフェース401と第2のタイプの物理インタフェース411との間の遷移の間、パッド202の各々の状態が、パッドIF回路204のステータスによって判定されるか、または他の様態で当該状態を反映する。この場合、標準モードはJTAGとして定義され、第1のタイプの物理インタフェース401は、JTAGに準拠するシグナリングを含み、高速モードは高速クロック出力HSCLKを用いるLVDSシグナリングを使用して定義される。一実施形態において、高速モードの間にHSCLKはデバイス200上で生成され、パッド202に提供される。

【0034】

表500は、列501〜505を含み、ここで、第1の列501は例示的なパッドP1〜P5およびESCを列挙している。第2の列502は標準状態に関するP1〜P5の機能を列挙しており、これは例示されている実施形態においてはJTAGについて特に定義されており、ただし、他の標準インタフェース方法が考慮されることが留意される。この場合、第1のタイプの物理インタフェース401がイネーブルされ(パッドIFブロック402、404をイネーブルするなどして)、デバイス102のパッドP1〜P5はそれぞれ、テスト・データ・イン(Test Data In)(TDI)、テストモード選択(Test Mode Select)(TMS)、テスト・データ・アウト(Test Data Out)(TDO)、テストリセット(TRST)、およびテストクロック(Test Clock)(TCLK)として定義される。標準モードの間、ホスト104がインタフェースのためのテストクロック信号を提供するため、TCLKはデバイス102に対する入力として定義され、一方で、ホスト104のための対応するパッドは出力である。ESC指示検出は標準モードにおいては抑制され、それによって、ESC信号の状態は無視される。

【0035】

第3の列503は、モードコントローラ124が、制御レジスタ302内のMODE_HS値(またはビット)が設定されるかまたは他の様態で設定されているものとして検出されることを検出するときに入る標準安全(STD_SAFE)モードである。モードコントローラ124は、第1のタイプの物理インタフェース401を安全モードにするためにCTL信号をアサートし、当該モードにおいて、パッドP1〜P5はHI−Z(高インピーダンス)状態になる。ESC指示検出は抑制されたままである。TIMER1値がカウンタ304内に読み出され、(適切なカウンタ304の動作を開始することなどによって)第1の期間が開始される。

【0036】

第4の列504は、第1の期間が完了した(例えば、カウンタ304のTIMER1カウントの完了)後TIMEOUT1を受けて入るスイッチモードである。HS転送プロトコル回路128がイネーブルされて、第2のタイプの物理インタフェース411をイネーブルするためにCTL信号がアサートされ、それによって、パッド202が高速モードのために定義される。パッドP1およびP2はまとめて、P1に対する正極性TXPおよびP2に対する負極性TXNを含む差動LVDS送信信号として定義される。なお、遷移の間、差動LVDS送信信号は使用されない場合があり、それによって、これらのパッドは代替的にHI−Z状態のままである場合がある。パッドP3およびP4はまとめて、P3に対する正極性RXPおよびP4に対する負極性RXNを含む差動LVDS受信信号として定義される。P5は、デバイス102から出力される高速クロックHSCLKを、高速動作のタイミングを制御するためにホスト104に提供する。ESC指示検出は抑制されたままである。TIMER2値がカウンタ304内に読み出され、第2の期間が開始される。

【0037】

第5の列505は、第2の期間が完了した後TIMEOUT2を受けて入る高速(HS)モードである。この時点において、ESC指示検出がイネーブルされ、フェイルセーフ機構として完全に機能し、パッド202は高速モードのために完全に動作可能である。

【0038】

図6は、高速モードから標準モードへの遷移の間の、パッド202の状態およびデバイス102のESC指示検出のステータスを示す表600である。第1の列601は列501と同じであり、パッドおよびESC指示検出のステータスを列挙している。第2の列602は列505と同じであり、HSモードが動作可能でありイネーブルされていることを示す。第3の列603は、MODE_HS値がクリアされているかまたはESC信号がアサートされているときの標準モードへの遷移のための高速安全モード(HS_SAFE)である。HS_SAFEモードにおいて、第2のタイプの物理インタフェース411は安全モードになり、それによって、パッドP1〜P5はHI−Z状態になり、ESC指示検出が抑制される。さらに、TIMER1値がカウンタ304内に読み出され、第1の期間が開始される。第4の列604は、第1の期間が満了した後TIMEOUT1を受けて再び入る標準モードである。ESC指示検出は、標準動作モードの間は抑制されたままである。

【0039】

図7は、標準モードと高速モードとの間の遷移に関する、デバイス102の動作の状態を示す簡略状態図である。PORされると、動作は初めは状態702によって示されるように標準モードにある(表500の列502)。動作はMODE_HS値が設定されるまで標準モードのままである。

【0040】

MODE_HSが設定されていると検出されると、動作は最終的に、HSモードに遷移するために、状態704によって示されるような(および、表500の列503によって示されるような)STD_SAFEモードに進む。HS転送プロトコル回路128および変換ロジック218をイネーブルするために、HS_EN信号がアサートされる。TIMER1値がカウンタ304内に読み出され、第1の期間が開始される。

【0041】

TIMEOUT1(第1の期間の満了)を受けて、動作は最終的に、状態706(表500の列504)によって示されるようなSWITCHモードに進む。HS転送プロトコル回路128および変換ロジック218がイネーブルされて動作可能になる。第2のタイプの物理インタフェース411がイネーブルされて動作可能になり、高速動作をイネーブルするためにHS_SEL信号がアサートされる。TIMER2値がカウンタ304内に読み出され、第2の期間が開始される。

【0042】

TIMEOUT2を受けて、動作は最終的に、状態708によって示されるような、ならびに表500の列505および表600の列602によって示されるような、高速動作モードに遷移する。ESC信号を介してエスケープ指示を検出するために、エスケープ指示がイネーブルされる。MODE_HSが設定されたままであり、かつESCバーによって示されるようにESC信号がネゲートされたままである間、動作は高速モードのままである。

【0043】

MODE_HS値がクリアとして検出されるか、またはESC信号がハイでアサートされるといつでも、動作は標準モードに戻るべく遷移するために、状態710によって示されるような、および表600の列603によって示されるようなHS_SAFEモードに遷移する。TIMER1値がカウンタ304内に読み出され、第1の期間が開始される。TIMEOUT1を受けて、動作は、表600の列604によって示されるように、状態702における標準モードに戻る。

【0044】

物理インタフェースと、第1の転送プロトコル回路および第2の転送プロトコル回路と、メモリと、モードコントローラとを含むインタフェース。物理インタフェースは、第1のタイプの物理インタフェースと、それと異なる第2のタイプの物理インタフェースとを含み、これらは両方とも共通のパッドの組と相互作用するために選択的にイネーブルされる。第1の転送プロトコル回路は第1の動作モードにおいて第1のタイプの物理インタフェースと協働して動作可能であり、第2の転送プロトコル回路は第2の動作モードにおいて第2のタイプの物理インタフェースと協働して動作可能である。メモリは、第1の動作モードおよび第2の動作モードのうちの一方を示すモード値を記憶する。モードコントローラは、電源投入またはリセットされると、第1の動作モードにおいて第1の転送プロトコルを用いて動作するために第1のタイプの物理インタフェースをイネーブルし、モード値が第2の動作モードを示すとき第2の転送プロトコルを用いて動作するために、第1のタイプの物理インタフェースをディセーブルするとともに第2のタイプの物理インタフェースをイネーブルすることによって、第2の動作モードに動的に遷移する。

【0045】

さまざまな実施形態において、モードコントローラは、モード値が第1の動作モードを示すとき第1の転送プロトコルを用いて動作するために、第2のタイプの物理インタフェースをディセーブルするとともに第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに動作を戻すように動的に遷移する。第1の動作モードと第2の動作モードとの間の遷移のためにプログラム可能な時間値が使用される。モード値および1つまたは複数のプログラム可能なタイミング値は、プログラム可能な期間を提供するためにメモリ内に記憶される。

【0046】

通信の損失の場合などにおいて、第1の動作モードに戻る遷移をイネーブルするために、エスケープ指示が提供される。一実施形態において、例えば、第2のタイプの物理インタフェースは所定の電圧範囲内で動作することができ、所定の電圧範囲を超えるとエスケープ信号をアサートまたは他の様態で提供するように構成される。エスケープ機構は第1の動作モードにおいては抑制され、第2の動作モードにおいてはイネーブルされる。

【0047】

一実施形態において、動作モード間の遷移のために安全モードが使用される。一実施形態において、例えば、第1の物理インタフェースおよび第2の物理インタフェースは、動作モード間で遷移しながら、共通のパッドの組を高インピーダンス状態またはそれ以外の既知の論理状態にするように構成される。より具体的な実施形態において、モードコントローラが、物理インタフェースを動的に安全モードにして、第1の期間を開始し、第1の期間が満了すると第2の転送プロトコルを用いて動作するために第2のタイプの物理インタフェースをイネーブルし、第2の期間を開始し、第2の期間が満了するとエスケープ信号の検出をイネーブルする。

【0048】

モードコントローラは、モード値によってまたはエスケープ信号によって指示されると、第1の転送プロトコルを用いて動作するために、第2のタイプの物理インタフェースをディセーブルするとともに第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに動作を戻すように動的に遷移することができる。

【0049】

第1のタイプの物理インタフェースは、共通のパッドの組を介する第1の帯域幅におけるシングルエンドシグナリングのために構成されることができ、第2のタイプの物理インタフェースは、共通のパッドの組を介する第2のより高い帯域幅における低電圧差動シグナリングのために構成される。第1の動作モードは、JTAGなどのような事実上の業界標準に準拠する。

【0050】

一実施形態によるインタフェースの動作方法は、初めに、第1の転送プロトコルに従って動作するために、共通のパッドの組に接続される第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードで動作する工程と、第1の動作モードおよび第2の動作モードのうちの一方を示すモード値をモニタリングする工程と、モード値によって指示されると、第2の転送プロトコルによって動作するために、共通のパッドの組に接続される第2のタイプの物理インタフェースをイネーブルすることによって、第2の動作モードに動的に遷移する工程とを備える。

【0051】

本方法は、モード値によって指示されると、第1の転送プロトコルを用いて動作するために、第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに戻すように動的に遷移する工程を備える。

【0052】

第2の動作モードに動的に遷移する工程は、第1のタイプの物理インタフェースを安全モードにする工程と、第2の転送プロトコルによる動作をイネーブルする工程と、第2の転送プロトコル動作がイネーブルされると第2のタイプの物理インタフェースを使用して第2の転送プロトコルに動作を切り替える工程とを備える。

【0053】

本方法は、安全モード中に所定期間を開始する工程と、当該期間の満了後に第2のタイプの物理インタフェースを使用して第2の転送プロトコルに動作を切り替える工程とをさらに備える。本方法は、第1の動作モードで動作している間に、第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備えることができ、ここで、コマンドは期間を示す時間値を含む。

【0054】

本方法は、安全モード中に第1の期間を開始する工程と、第1の期間の満了後に第2のタイプの物理インタフェースを使用して第2の転送プロトコルに動作を切り替える工程と、イネーブルされると第2のタイプの物理インタフェースによって、範囲外状態をモニタリングするとともに、範囲外状態が検出されるとエスケープ信号を提供する工程と、第1の期間の満了後に第2の期間を開始する工程と、第2の期間の満了後にエスケープ信号の検出をイネーブルする工程とをさらに備える。

【0055】

本方法は、第1の動作モードで動作している間に、第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備えることができ、ここで、コマンドは第1の期間を示す第1の時間値と、第2の期間を示す第2の時間値とを含む。

【0056】

本方法は、モード値によって指示されると、またはエスケープ信号が検出されると、第1の転送プロトコルに従って動作するために、第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードに動的に遷移し戻す工程をさらに備える。本方法は、第2の動作モードにある間に、第1の転送プロトコルと第2の転送プロトコルとの間で変換する工程をさらに備える。

【0057】

別の実施形態による、インタフェースの動作方法は、第1の転送プロトコルおよび第2の転送プロトコルのうちの一方を示すモード値をモニタリングする工程と、モード値が第1の転送プロトコルを示すとき、第1の転送プロトコルに従って動作するために、パッドに接続される第1のタイプの物理インタフェースをイネーブルする工程と、モード値が第2の転送プロトコルを示すとき、当該転送プロトコルに従って動作するために、パッドに接続される第2のタイプの物理インタフェースをイネーブルする工程と、第2の転送プロトコルに従って動作しているときに、パッド上で範囲外条件が検出されると、第1の転送プロトコルに従って動作するように動的に戻すように切り替える工程とを備える。

【0058】

本発明をその特定の好ましいバージョンを参照して相当に詳細に説明してきたが、他のバージョンおよび変形形態が可能であり考慮される。当業者は、添付の特許請求の範囲によって定義されているような本発明の精神および範囲から逸脱することなく、本発明の同じ目的を実行するための他の構造を設計または改変するための基礎として、開示されている概念および具体的な実施形態を容易に使用することができることを理解すべきである。

【符号の説明】

【0059】

100…インタフェースシステム、108,110,401,411…物理インタフェース、114…モードコントローラ、116…標準転送プロトコル回路、118…高速転送プロトコル回路、202…パッド、204…パッドIF回路、208…インタフェース、210…中央処理装置、214…メモリ。

【特許請求の範囲】

【請求項1】

インタフェースであって、

両方とも共通のパッドの組と相互作用するために選択的にイネーブルされる第1のタイプの物理インタフェース、および、それと異なる第2のタイプの物理インタフェースを含む物理インタフェースと、

第1の動作モードにおいて前記第1のタイプの物理インタフェースと協働して動作可能である第1の転送プロトコル回路と、

第2の動作モードにおいて前記第2のタイプの物理インタフェースと協働して動作可能である第2の転送プロトコル回路と、

前記第1の動作モードおよび前記第2の動作モードのうちの一方を示すモード値を記憶するメモリと、

電源投入またはリセットされると、前記第1の動作モードにおいて前記第1の転送プロトコル回路と協働して動作するために前記第1のタイプの物理インタフェースをイネーブルし、前記モード値が前記第2の動作モードを示すとき前記第2の転送プロトコル回路と協働して動作するために、前記第1のタイプの物理インタフェースをディセーブルするとともに前記第2のタイプの物理インタフェースをイネーブルすることによって、前記第2の動作モードに動的に遷移するモードコントローラとを備える、インタフェース。

【請求項2】

前記モードコントローラは、前記モード値が前記第1の動作モードを示すとき前記第1の転送プロトコル回路と協働して動作するために、前記第2のタイプの物理インタフェースをディセーブルするとともに前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻るように動的に遷移する、請求項1に記載のインタフェース。

【請求項3】

前記メモリはプログラム可能な時間値を記憶し、

前記モードコントローラは、前記物理インタフェースを安全モードにすることによって、および、前記プログラム可能な時間値に基づく期間が満了すると、前記第1の転送プロトコル回路を用いて動作するために前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻すように動的に遷移する、請求項2に記載のインタフェース。

【請求項4】

前記メモリはプログラム可能な時間値を記憶し、

前記モードコントローラは、前記物理インタフェースを安全モードにすることによって、および、前記プログラム可能な時間値に基づく期間が満了すると、前記第2の転送プロトコル回路と協働して動作するために前記第2のタイプの物理インタフェースをイネーブルすることによって、前記第2の動作モードに動的に遷移する、請求項1に記載のインタフェース。

【請求項5】

前記メモリはプログラム可能な時間値を記憶し、

前記モードコントローラは、前記第2のタイプの物理インタフェースをイネーブルすると、前記プログラム可能な時間値に基づいて少なくとも1つの期間を開始するために前記第2の動作モードに動的に遷移し、前記少なくとも1つの期間が満了するとエスケープ信号の検出をイネーブルし、

前記エスケープ信号は、前記第1の動作モードに戻る遷移を示すように構成される、請求項1に記載のインタフェース。

【請求項6】

前記メモリは第1のプログラム可能な時間値および第2のプログラム可能な時間値をさらに記憶し、

前記第2のタイプの物理インタフェースは所定の電圧範囲内で動作するとともに、該所定の電圧範囲を超えるとエスケープ信号をアサートし、

前記モードコントローラは、前記物理インタフェースを安全モードにすることによって、前記第1のプログラム可能な時間値に基づいて第1の期間を開始することによって、該第1の期間が満了すると前記第2の転送プロトコル回路を用いて動作するために前記第2のタイプの物理インタフェースをイネーブルすることによって、前記第2のプログラム可能な時間値に基づく第2の期間を開始することによって、および、該第2の期間が満了すると前記エスケープ信号の検出をイネーブルすることによって、前記第2の動作モードに動的に遷移する、請求項1に記載のインタフェース。

【請求項7】

前記モードコントローラは、前記モード値が前記第1の動作モードを示すとき、または前記エスケープ信号が前記第1の動作モードを示すとき、前記第1の転送プロトコル回路を用いて動作するために、前記第2のタイプの物理インタフェースをディセーブルするとともに前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻すように動的に遷移する、請求項6に記載のインタフェース。

【請求項8】

前記第1のタイプの物理インタフェースおよび前記第1の転送プロトコル回路は第1の帯域幅においてシングルエンドシグナリングを用いるJTAGに準拠して動作し、前記第2のタイプの物理インタフェースおよび前記第2の転送プロトコル回路は前記第1の帯域幅よりも高い第2の帯域幅において低電圧差動シグナリングを使用して動作する、請求項1に記載のインタフェース。

【請求項9】

前記第1のタイプの物理インタフェースは前記共通のパッドの組を介する第1の帯域幅におけるシングルエンドシグナリングのために構成される第1のブロックの組を備え、前記第2のタイプの物理インタフェースは前記共通のパッドの組を介する前記第1の帯域幅よりも高い第2の帯域幅における低電圧差動シグナリングのために構成される第2のブロックの組を備える、請求項1に記載のインタフェース。

【請求項10】

前記第2の動作モードの間に、前記第1の転送プロトコル回路と前記第2の転送プロトコル回路との間で変換する変換ロジックをさらに備える、請求項1に記載のインタフェース。

【請求項11】

インタフェースの動作方法であって、

初めに、第1の転送プロトコルに従って動作するために、共通のパッドの組に接続される第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードで動作する工程と、

前記第1の動作モードおよび第2の動作モードのうちの一方を示すモード値をモニタリングする工程と、

前記モード値によって指示されると、第2の転送プロトコルに従って動作するために、前記共通のパッドの組に接続される第2のタイプの物理インタフェースをイネーブルすることによって、前記第2の動作モードに動的に遷移する工程とを備える、方法。

【請求項12】

前記モード値によって指示されると、前記第1の転送プロトコルを用いて動作するために、前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻るように動的に遷移する工程をさらに備える、請求項11に記載の方法。

【請求項13】

前記第2の動作モードに前記動的に遷移する工程は、

前記第1のタイプの物理インタフェースを安全モードにする工程と、

前記第2の転送プロトコルによる動作をイネーブルする工程と、

前記第2の転送プロトコルの動作がイネーブルされると前記第2のタイプの物理インタフェースを使用して前記第2の転送プロトコルに動作を切り替える工程とを含む、請求項11に記載の方法。

【請求項14】

安全モード中に所定期間を開始する工程と、

前記切り替えることが、前記期間の満了後に前記第2のタイプの物理インタフェースを使用して前記第2の転送プロトコルに動作を切り替える工程とをさらに備える、請求項13に記載の方法。

【請求項15】

前記第1の動作モードで動作している間に、前記第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備える、該コマンドは前記期間を示す時間値を含む、請求項14に記載の方法。

【請求項16】

前記安全モード中に第1の期間を開始する工程と、

前記切り替える工程が、前記第1の期間の満了後に前記第2のタイプの物理インタフェースを使用して前記第2の転送プロトコルに動作を切り替える工程を含むことと、

前記第2のタイプの物理インタフェースによって、範囲外状態をモニタリングするとともに、該範囲外状態が検出されるとエスケープ信号を提供する工程と、

前記第1の期間の前記満了後に第2の期間を開始する工程と、

前記第2の期間の満了後に前記エスケープ信号の検出をイネーブルする工程とをさらに備える、請求項13に記載の方法。

【請求項17】

前記第1の動作モードで動作している間に、前記第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備え、該コマンドは前記第1の期間を示す第1の時間値、および前記第2の期間を示す第2の時間値を含む、請求項16に記載の方法。

【請求項18】

前記モード値によって指示されるとき、または前記エスケープ信号が検出されるとき、前記第1の転送プロトコルに従って動作するために、前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻るように動的に遷移する工程をさらに備える、請求項16に記載の方法。

【請求項19】

前記第2の動作モード中に、前記第1の転送プロトコルと前記第2の転送プロトコルとの間で動作を変換する工程をさらに備える、請求項11に記載の方法。

【請求項20】

インタフェースの動作方法であって、

第1の転送プロトコルおよび第2の転送プロトコルのうちの一方を示すモード値をモニタリングする工程と、

前記モード値が前記第1の転送プロトコルを示すとき、前記第1の転送プロトコルに従って動作するために、複数のパッドに接続される第1のタイプの物理インタフェースをイネーブルする工程と、

前記モード値が前記第2の転送プロトコルを示すとき、前記転送プロトコルに従って動作するために、前記複数のパッドに接続される第2のタイプの物理インタフェースをイネーブルする工程と、

前記第2の転送プロトコルに従って動作しているときに、前記複数のパッドのうちの少なくとも1つのパッド上で範囲外条件が検出されると、前記第1の転送プロトコルに従って動作するように動的に戻すように切り替える工程とを備える、方法。

【請求項21】

前記第2の転送プロトコルに従って動作しているときに、前記複数のパッドのうちの少なくとも1つを共通モード電圧範囲に従って動作させる工程と、前記複数のパッドのうちの前記少なくとも1つの電圧が前記共通モード電圧範囲を外れるときを検出する工程とをさらに備える、請求項20に記載の方法。

【請求項1】

インタフェースであって、

両方とも共通のパッドの組と相互作用するために選択的にイネーブルされる第1のタイプの物理インタフェース、および、それと異なる第2のタイプの物理インタフェースを含む物理インタフェースと、

第1の動作モードにおいて前記第1のタイプの物理インタフェースと協働して動作可能である第1の転送プロトコル回路と、

第2の動作モードにおいて前記第2のタイプの物理インタフェースと協働して動作可能である第2の転送プロトコル回路と、

前記第1の動作モードおよび前記第2の動作モードのうちの一方を示すモード値を記憶するメモリと、

電源投入またはリセットされると、前記第1の動作モードにおいて前記第1の転送プロトコル回路と協働して動作するために前記第1のタイプの物理インタフェースをイネーブルし、前記モード値が前記第2の動作モードを示すとき前記第2の転送プロトコル回路と協働して動作するために、前記第1のタイプの物理インタフェースをディセーブルするとともに前記第2のタイプの物理インタフェースをイネーブルすることによって、前記第2の動作モードに動的に遷移するモードコントローラとを備える、インタフェース。

【請求項2】

前記モードコントローラは、前記モード値が前記第1の動作モードを示すとき前記第1の転送プロトコル回路と協働して動作するために、前記第2のタイプの物理インタフェースをディセーブルするとともに前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻るように動的に遷移する、請求項1に記載のインタフェース。

【請求項3】

前記メモリはプログラム可能な時間値を記憶し、

前記モードコントローラは、前記物理インタフェースを安全モードにすることによって、および、前記プログラム可能な時間値に基づく期間が満了すると、前記第1の転送プロトコル回路を用いて動作するために前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻すように動的に遷移する、請求項2に記載のインタフェース。

【請求項4】

前記メモリはプログラム可能な時間値を記憶し、

前記モードコントローラは、前記物理インタフェースを安全モードにすることによって、および、前記プログラム可能な時間値に基づく期間が満了すると、前記第2の転送プロトコル回路と協働して動作するために前記第2のタイプの物理インタフェースをイネーブルすることによって、前記第2の動作モードに動的に遷移する、請求項1に記載のインタフェース。

【請求項5】

前記メモリはプログラム可能な時間値を記憶し、

前記モードコントローラは、前記第2のタイプの物理インタフェースをイネーブルすると、前記プログラム可能な時間値に基づいて少なくとも1つの期間を開始するために前記第2の動作モードに動的に遷移し、前記少なくとも1つの期間が満了するとエスケープ信号の検出をイネーブルし、

前記エスケープ信号は、前記第1の動作モードに戻る遷移を示すように構成される、請求項1に記載のインタフェース。

【請求項6】

前記メモリは第1のプログラム可能な時間値および第2のプログラム可能な時間値をさらに記憶し、

前記第2のタイプの物理インタフェースは所定の電圧範囲内で動作するとともに、該所定の電圧範囲を超えるとエスケープ信号をアサートし、

前記モードコントローラは、前記物理インタフェースを安全モードにすることによって、前記第1のプログラム可能な時間値に基づいて第1の期間を開始することによって、該第1の期間が満了すると前記第2の転送プロトコル回路を用いて動作するために前記第2のタイプの物理インタフェースをイネーブルすることによって、前記第2のプログラム可能な時間値に基づく第2の期間を開始することによって、および、該第2の期間が満了すると前記エスケープ信号の検出をイネーブルすることによって、前記第2の動作モードに動的に遷移する、請求項1に記載のインタフェース。

【請求項7】

前記モードコントローラは、前記モード値が前記第1の動作モードを示すとき、または前記エスケープ信号が前記第1の動作モードを示すとき、前記第1の転送プロトコル回路を用いて動作するために、前記第2のタイプの物理インタフェースをディセーブルするとともに前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻すように動的に遷移する、請求項6に記載のインタフェース。

【請求項8】

前記第1のタイプの物理インタフェースおよび前記第1の転送プロトコル回路は第1の帯域幅においてシングルエンドシグナリングを用いるJTAGに準拠して動作し、前記第2のタイプの物理インタフェースおよび前記第2の転送プロトコル回路は前記第1の帯域幅よりも高い第2の帯域幅において低電圧差動シグナリングを使用して動作する、請求項1に記載のインタフェース。

【請求項9】

前記第1のタイプの物理インタフェースは前記共通のパッドの組を介する第1の帯域幅におけるシングルエンドシグナリングのために構成される第1のブロックの組を備え、前記第2のタイプの物理インタフェースは前記共通のパッドの組を介する前記第1の帯域幅よりも高い第2の帯域幅における低電圧差動シグナリングのために構成される第2のブロックの組を備える、請求項1に記載のインタフェース。

【請求項10】

前記第2の動作モードの間に、前記第1の転送プロトコル回路と前記第2の転送プロトコル回路との間で変換する変換ロジックをさらに備える、請求項1に記載のインタフェース。

【請求項11】

インタフェースの動作方法であって、

初めに、第1の転送プロトコルに従って動作するために、共通のパッドの組に接続される第1のタイプの物理インタフェースをイネーブルすることによって、第1の動作モードで動作する工程と、

前記第1の動作モードおよび第2の動作モードのうちの一方を示すモード値をモニタリングする工程と、

前記モード値によって指示されると、第2の転送プロトコルに従って動作するために、前記共通のパッドの組に接続される第2のタイプの物理インタフェースをイネーブルすることによって、前記第2の動作モードに動的に遷移する工程とを備える、方法。

【請求項12】

前記モード値によって指示されると、前記第1の転送プロトコルを用いて動作するために、前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻るように動的に遷移する工程をさらに備える、請求項11に記載の方法。

【請求項13】

前記第2の動作モードに前記動的に遷移する工程は、

前記第1のタイプの物理インタフェースを安全モードにする工程と、

前記第2の転送プロトコルによる動作をイネーブルする工程と、

前記第2の転送プロトコルの動作がイネーブルされると前記第2のタイプの物理インタフェースを使用して前記第2の転送プロトコルに動作を切り替える工程とを含む、請求項11に記載の方法。

【請求項14】

安全モード中に所定期間を開始する工程と、

前記切り替えることが、前記期間の満了後に前記第2のタイプの物理インタフェースを使用して前記第2の転送プロトコルに動作を切り替える工程とをさらに備える、請求項13に記載の方法。

【請求項15】

前記第1の動作モードで動作している間に、前記第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備える、該コマンドは前記期間を示す時間値を含む、請求項14に記載の方法。

【請求項16】

前記安全モード中に第1の期間を開始する工程と、

前記切り替える工程が、前記第1の期間の満了後に前記第2のタイプの物理インタフェースを使用して前記第2の転送プロトコルに動作を切り替える工程を含むことと、

前記第2のタイプの物理インタフェースによって、範囲外状態をモニタリングするとともに、該範囲外状態が検出されるとエスケープ信号を提供する工程と、

前記第1の期間の前記満了後に第2の期間を開始する工程と、

前記第2の期間の満了後に前記エスケープ信号の検出をイネーブルする工程とをさらに備える、請求項13に記載の方法。

【請求項17】

前記第1の動作モードで動作している間に、前記第2の動作モードへの遷移を指示するコマンドを受け取る工程をさらに備え、該コマンドは前記第1の期間を示す第1の時間値、および前記第2の期間を示す第2の時間値を含む、請求項16に記載の方法。

【請求項18】

前記モード値によって指示されるとき、または前記エスケープ信号が検出されるとき、前記第1の転送プロトコルに従って動作するために、前記第1のタイプの物理インタフェースをイネーブルすることによって、前記第1の動作モードに戻るように動的に遷移する工程をさらに備える、請求項16に記載の方法。

【請求項19】

前記第2の動作モード中に、前記第1の転送プロトコルと前記第2の転送プロトコルとの間で動作を変換する工程をさらに備える、請求項11に記載の方法。

【請求項20】

インタフェースの動作方法であって、

第1の転送プロトコルおよび第2の転送プロトコルのうちの一方を示すモード値をモニタリングする工程と、

前記モード値が前記第1の転送プロトコルを示すとき、前記第1の転送プロトコルに従って動作するために、複数のパッドに接続される第1のタイプの物理インタフェースをイネーブルする工程と、

前記モード値が前記第2の転送プロトコルを示すとき、前記転送プロトコルに従って動作するために、前記複数のパッドに接続される第2のタイプの物理インタフェースをイネーブルする工程と、

前記第2の転送プロトコルに従って動作しているときに、前記複数のパッドのうちの少なくとも1つのパッド上で範囲外条件が検出されると、前記第1の転送プロトコルに従って動作するように動的に戻すように切り替える工程とを備える、方法。

【請求項21】

前記第2の転送プロトコルに従って動作しているときに、前記複数のパッドのうちの少なくとも1つを共通モード電圧範囲に従って動作させる工程と、前記複数のパッドのうちの前記少なくとも1つの電圧が前記共通モード電圧範囲を外れるときを検出する工程とをさらに備える、請求項20に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−78115(P2013−78115A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2012−190978(P2012−190978)

【出願日】平成24年8月31日(2012.8.31)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成24年8月31日(2012.8.31)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

[ Back to top ]