不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、不揮発性プログラマブルスイッチに関する。

【背景技術】

【0002】

一般に、プログラマブルスイッチは、スイッチとして機能するパストランジスタのゲートにメモリを接続して、メモリの保持データに応じてパストランジスタのオン/オフ状態を切り換え制御するものである。典型的なFPGA(Field Programmable Gate Array)は複数のロジック素子と、プログラマブルスイッチのアレーとで構成されている。各プログラマブルスイッチはロジック素子を選択的に接続する役割を担う。

【0003】

不揮発性プログラマブルスイッチを、2つの不揮発性メモリトランジスタと、1つのパストランジスタとで構成する方式が知られている。この方式においては、不揮発性メモリトランジスタとしては、例えばフローティングゲート型の不揮発性メモリトランジスタが用いられる。2つの不揮発性メモリトランジスタのいずれかを介して、パストランジスタのゲートには電源電圧もしくは0Vが入力される。不揮発性メモリトランジスタの書込を、FN(Fowler-Nordheim)トンネル電流書込方式(以下、FN方式ともいう)で行う場合は、二つの不揮発性メモリトランジスタの内の一方を選択して書き込む、選択書込が行われる。このため、二つの不揮発性メモリトランジスタのそれぞれのゲートは異なるワードラインに接続する必要がある。

【0004】

また、プログラマブルロジックスイッチを、2つの不揮発性メモリトランジスタと、1つのパストランジスタと、1つのアクセストランジスタとで構成する他の方式が知られている。不揮発性メモリトランジスタとしては、例えばフローティングゲート型メモリトランジスタが用いられる。2つの不揮発性メモリトランジスタのいずれかを介して、パストランジスタのゲートには電源電圧もしくは0Vが入力される。この他の方式においては、2つの不揮発性メモリトランジスタのゲートは共通のワードラインに接続され、選択書込は、チャネルホットエレクトロン書込方式(以下、CHE方式ともいう)で行う。

【0005】

書込可能なメモリトランジスタの限界サイズは、一般にFN方式の場合の方がCHE方式の場合よりも小さい。CHE方式は、ソース/ドレイン間の電位差によって発生した熱電子を、ゲートに印加した電圧によって電荷蓄積膜に注入する。一般に、熱電子の注入効率はトランジスタのゲート長が100nm以下の領域ではゲート長が短くなるほど低下する。

【0006】

プログラマブルスイッチのセル面積は、セル当たりのワードライン数の少ない方が、またメモリトランジスタの寸法の小さい方が、小さくなる。セル面積が小さい方が、同一チップ面積でより多くの回路要素を搭載でき高性能なFPGAを実現できる。または、同一数の回路要素をより小さいチップ面積に搭載できチップ当たりコストを低減できる。

【0007】

従って、より小さい面積を有する不揮発性プログラマブルスイッチを実現するためには、FN方式が適応可能で且つセルあたりのワード線が1本のセル構造が望まれる。しかし、その方法については現在知られていない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】米国特許第5812450号明細書

【特許文献2】米国特許第6002610号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

本実施形態は、セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【課題を解決するための手段】

【0010】

本実施形態による不揮発性プログラマブルスイッチは、第1配線に接続される第1端子と、第2配線に接続される第2端子と、第3配線に接続される第3端子と、を有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と、前記第2配線に接続される第5端子と、前記第3配線に接続される第6端子と、を有し、前記第1不揮発性メモリトランジスタと同じ導電型の第2不揮発性メモリトランジスタと、前記第2配線にゲート電極が接続されたパストランジスタと、を備え、前記第1配線および前記第4配線が第1電源に接続され、前記第3配線が前記第1電源の電圧よりも高い電圧の第2電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が増加し、前記第2不揮発性メモリトランジスタの閾値電圧が低下し、前記第1配線および前記第4配線が前記第1電源に接続され、前記第3配線が前記第1電源の電圧よりも低い電圧の第3電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が低下し、前記第2不揮発性メモリトランジスタの閾値電圧が増加すること、を特徴とする。

【図面の簡単な説明】

【0011】

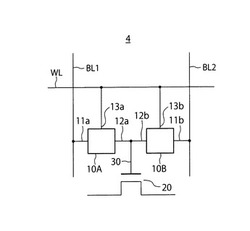

【図1】第1実施形態によるセルを示す回路図。

【図2】図2(a)、2(b)は、第1実施形態によるセルの動作を説明する回路図。

【図3】図3(a)、3(b)は、第1メモリトランジスタの第1具体例を示す図。

【図4】図4(a)、4(b)は、第1メモリトランジスタの書込電圧を示す図。

【図5】第1メモリトランジスタのId−Vgs特性を示す図。

【図6】図6(a)、6(b)は、第2メモリトランジスタの第1具体例を示す図。

【図7】図7(a)、7(b)は、第2メモリトランジスタの書込電圧を示す図。

【図8】第2メモリトランジスタのId−Vgs特性を示す図。

【図9】第1実施形態によるセルの第1具体例を示す回路図。

【図10】第2実施形態によるMUXを示す回路図。

【図11】第2実施形態のMUXの動作を説明する図。

【図12】第2実施形態のMUXの動作を説明する図。

【図13】第2実施形態のMUXの動作を説明する図。

【図14】第3実施形態によるセルを示す回路図。

【図15】図15(a)、15(b)は、pチャネルメモリトランジスタを示す図。

【図16】図16(a)、16(b)は、pチャネルメモリトランジスタの書込電圧を示す図。

【図17】pチャネルメモリトランジスタのId−Vgs特性を示す図。

【図18】第3実施形態の第1変形例によるセルを示す回路図。

【図19】第4実施形態によるセルを示す回路図。

【図20】図20(a)、20(b)は、pチャネルメモリトランジスタを示す図。

【図21】図21(a)、21(b)は、pチャネルメモリトランジスタの書込電圧を示す図。

【図22】図22は、pチャネルメモリトランジスタのId−Vgs特性を示す図。

【図23】第4実施形態の第1変形例によるセルを示す回路図。

【図24】第5実施形態によるセルを示す回路図。

【図25】図25(a)、25(b)は、nチャネルメモリトランジスタを示す断面図。

【図26】図26(a)、26(b)は、nチャネルメモリトランジスタを示す断面図。

【図27】図27(a)、27(b)は、nチャネルメモリトランジスタの書込電圧を示す図。

【図28】nチャネルメモリトランジスタのId−Vgs特性を示す図。

【図29】図29(a)、29(b)は、nチャネルメモリトランジスタの書込電圧を示す図。

【図30】nチャネルメモリトランジスタのId−Vgs特性を示す図。

【図31】第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図32】図32(a)、32(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図33】図33(a)、33(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図34】図34(a)、34(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図35】図35(a)、35(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図36】図36(a)、36(b)は、第5実施形態に係るメモリトランジスタの形成方法の他の例を示す断面図。

【発明を実施するための形態】

【0012】

以下、図面を参照しながら、実施形態を説明する。

【0013】

(第1実施形態)

図1に第1実施形態による不揮発性プログラマブルスイッチを示す。この不揮発性プログラマブルスイッチ4は、第1および第2不揮発性メモリトランジスタ(以下、メモリトランジスタともいう)10A、10Bと、パストランジスタ20と、配線30と、を備え、一つのセルを構成する。不揮発性プログラマブルスイッチ4を以下、スイッチ4またはセル4ともいう。

【0014】

第1メモリトランジスタ10Aは、配線BL1に接続される第1端子11aと、配線30に接続される第2端子12aと、配線WLに接続される第3端子13aと、を備えている。第1メモリトランジスタ10Aにおいては、例えば第1端子11aがソース/ドレインの一方であり、第2端子12aがソース/ドレインの他方であり、第3端子13aがゲートである。また、同様に、第2メモリトランジスタ10Bは、配線BL2に接続される第1端子11bと、配線30に接続される第2端子12bと、配線WLに接続される第3端子13bと、を備えている。第2メモリトランジスタ10Bにおいては、例えば第1端子11bがソース/ドレインの一方であり、第2端子12bがソース/ドレインの他方であり、第3端子13bがゲート電極である。

【0015】

パストランジスタ20は、ゲート電極が配線30に接続され、ソース/ドレインがそれぞれ外部の配線に接続される。

【0016】

したがって、第1および第2メモリトランジスタ10A、10Bは、第3端子13a、13bが同じ配線WLに接続され、第2端子12a、12bが配線30を介してパストランジスタ20のゲート電極に接続される。

【0017】

そしてこのように構成されたスイッチ4においては、配線WLに第1書込電圧Vprg1を印加したときには、第1メモリトランジスタ10Aの閾値電圧(単に、閾値ともいう)Vthの絶対値が増加し、第2メモリトランジスタ10Bの閾値電圧Vthの絶対値が減少する(図2(a)参照)。また、配線WLに第1書込電圧Vprg1よりも低い第2書込電圧Vprg2(<Vprg1)を印加したときには、第1メモリトランジスタ10Aの閾値電圧Vthの絶対値が減少し、第2メモリトランジスタ10Bの閾値電圧Vthの絶対値が増加する(図2(b)参照)。

【0018】

次に、第1メモリトランジスタ10Aの第1具体例の構成を図3(a)に示す。図3(a)に示すように、この第1具体例のメモリトランジスタ10aは、p型半導体領域(例えばpウェル)101aに形成されたnチャネルトランジスタであって、pウェル101aに離間して形成されたn型のソース/ドレイン102aと、ソース/ドレイン102a間のpウェル101aの領域(チャネル)上に形成されたゲート構造110aとを備えている。なお、p型半導体領域としてはpウェルの他にp型半導体基板とすることができる。ゲート構造110aは、絶縁膜(トンネル膜)111aと、電荷蓄積膜112aと、絶縁膜(ブロック膜)113aと、ゲート電極114aとがこの順序で積層された構造を有している。ソース/ドレイン102aの一方が図1に示す配線BL1に接続され、他方が配線30に接続される。また、ゲート電極114aが配線WLに接続される。そして、絶縁膜111aの膜厚が絶縁膜113aの膜厚よりも薄いか、もしくは絶縁膜111aの平均比誘電率が絶縁膜113aの平均比誘電率よりも小さくなるように構成されている。ここで、絶縁膜の平均比誘電率εaveは、絶縁膜がn(≧1)個の層から構成され、i(n≧i≧1)番目の層の物理層厚をTi、比誘電率をεiとしたとき、以下の式で表される。

【数1】

また、この第1具体例のメモリトランジスタ10aは、本明細書では、図3(b)に示す記号で表す。

【0019】

第1具体例のメモリトランジスタ10aでは例えば、絶縁膜111aはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層構造とし、電荷蓄積膜112aはSiN(5nm)とし、絶縁膜113aはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とする。ここで記号「A/B」はAが上層でBが下層であることを意味し、括弧内の数値は層厚を示す。したがって、絶縁膜111aの膜厚は6nmとなり、絶縁膜113aの膜厚は10.5nmとなり、絶縁膜111aの膜厚は絶縁膜113aの膜厚よりも薄い。また、SiO2の比誘電率が3.9で、SiNの比誘電率が8であるので、絶縁膜111aの平均比誘電率は4.26、絶縁膜113aの平均比誘電率は4.70となる。すなわち、絶縁膜111aの平均比誘電率は絶縁膜113aの平均比誘電率よりも小さい。

【0020】

なお、絶縁膜111a、113a、電荷蓄積膜112a、およびゲート電極114aの膜厚、材料および組成は、メモリトランジスタ10aから該当部分を、FIB(Focused Ion Beam)を用いたピックアップ法で切り出し、その断面を高分解能透過電子顕微鏡(HRTEM)で撮像するか、若しくはエネルギー分散型X線分析(EDX(Energy Dispersive X-ray Analysis))、若しくは電子エネルギー損失分光法(EELS(Electron Energy-Loss Spectroscopy))で分析すれば、明らかにすることができる。

【0021】

図4(a)、4(b)に、第1具体例の第1メモリトランジスタ10aの書込電圧を示す。第1具体例の第1メモリトランジスタ10aにおいて、例えば第1書込電圧Vprg1を+18V、第2書込電圧Vprg2を−18Vとする。第1メモリトランジスタ10aにおいて、図4(a)に示すように、ソース/ドレイン102aおよびpウェル101aに印加する電圧を0Vとし、ゲート電極に第1書込電圧Vprg1(+18V)を印加した場合、チャネルの電子は絶縁膜111aをトンネル現象(FNトンネル電流)により通過し、電荷蓄積膜112aに注入され、電荷蓄積膜112aでトラップされ蓄積される。絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚いので、電荷蓄積膜112aからゲート電極114aへの電子の流出量はチャネルから電荷蓄積膜113aへの流入量よりも小さくなる。すなわち、電荷蓄積膜112aにトラップされた電荷(電子)量が増大する。

【0022】

また、絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、絶縁膜113aに印加される電界は絶縁膜111aに印加される電界よりも小さくなる。このため、電荷蓄積膜112aからゲート電極114aへの電子の流出量はチャネルから電荷蓄積膜112aへの流入量よりも小さくなる。

【0023】

第1具体例の第1メモリトランジスタ10aでは、絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚く、且つ、絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、電荷蓄積膜112aからゲート電極114aへの電子の流出量はチャネルから電荷蓄積膜112aへの流入量よりも大幅に小さくなる。

【0024】

このようにして電荷蓄積膜112aに蓄えられた負電荷(電子)はnチャネルメモリトランジスタ10aの閾値電圧を上昇させ、高閾値となる。この高閾値は例えば4Vである。

【0025】

次に、図4(b)に示すように、第1メモリトランジスタ10aが高閾値状態であるときに、ソース/ドレイン102aおよびpウェル101aに印加する電圧を0Vとし、ゲート電極104aに第2書込電圧Vprg2(−18V)を印加した場合、電荷蓄積膜112aに蓄えられた電子は絶縁膜111aをトンネル現象により通過しチャネルへ放出される。このとき、絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚いので、ゲート電極114aから電荷蓄積膜112aへの電子の流入量は電荷蓄積膜112aからチャネルへの電子の流出量よりも小さくなる。また、絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、絶縁膜113aに印加される電界は絶縁膜111aに印加される電界よりも小さくなる。このため、ゲート電極114aから電荷蓄積膜112aへの電子の流入量は電荷蓄積膜112aからチャネルへの電子の流出量よりも小さくなる。

【0026】

第1具体例の第1メモリトランジスタ10aでは、絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚く、且つ絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、ゲート電極114aから電荷蓄積膜112aへの電子の流入量は電荷蓄積膜112aからチャネルへの電子の流出量よりも大幅に小さくなる。

【0027】

このように、電荷蓄積膜112aに電荷が蓄えられている状態(高閾値状態)で、第2書込電圧Vprg2(−18V)を印加することにより、電荷蓄積膜112aは元の中性状態に戻るので閾値は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112aに電荷が蓄えられていない状態(低閾値状態)で、第1メモリトランジスタ10aに第2書込電圧Vprg2(−18V)を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0028】

図5に、第1メモリトランジスタ10aが高閾値状態(例えばデータ“1”状態)と、低閾値状態(例えばデータ“0”状態)にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性をそれぞれ示す。なお、高閾値状態をデータ“0”状態に対応させ、低閾値状態をデータ“1”状態に対応させてもよい。

【0029】

次に、第2メモリトランジスタ10Bの第1具体例の構成を図6(a)に示す。図6(a)に示すように、この第1具体例のメモリトランジスタ10bは、p型半導体領域(例えばpウェル)101bに形成されたnチャネルトランジスタであって、pウェル101bに離間して形成されたn型のソース/ドレイン102bと、ソース/ドレイン102b間のpウェル101bの領域(チャネル)上に形成されたゲート構造110bとを備えている。なお、p型半導体領域としては、pウェルの他にp型半導体基板とすることもできる。このゲート構造110bは、絶縁膜(ブロック膜)111bと、電荷蓄積膜112bと、絶縁膜(トンネル膜)113bと、ゲート電極114bとがこの順序で積層された構造を有している。ソース/ドレイン102bの一方が図1に示す配線BL2に接続され、他方が配線30に接続される。また、ゲート電極114bが配線WLに接続される。そして、絶縁膜111bの膜厚が絶縁膜113bの膜厚よりも厚いか、もしくは絶縁膜111bの平均比誘電率が絶縁膜113bの平均比誘電率よりも大きくなるように構成されている。

【0030】

第1具体例の第2メモリトランジスタ10bでは例えば、絶縁膜111bはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とし、電荷蓄積膜112bはSiN(5nm)とし、絶縁膜113bはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層構造とする。したがって、絶縁膜111bの膜厚は10.5nm、絶縁膜113bの膜厚は6nmとなり、絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚い。また、絶縁膜111bの平均比誘電率は4.70、絶縁膜113bの平均比誘電率は4.26となり、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きい。

【0031】

図7(a)、7(b)に、第1具体例の第2メモリトランジスタ10bの書込電圧を示す。第1具体例の第2不揮発性メモリトランジスタ10bにおいて、図7(a)に示すように、ソース/ドレイン102bおよびpウェル101bに印加する電圧を0Vとし、ゲートに第2書込電圧Vprg2(−18V)を印加した場合、ゲート電極114bの電子は絶縁膜113bをトンネル現象により通過し電荷蓄積膜112bに注入され、電荷蓄積膜112bで捕獲される。絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚いので、電荷蓄積膜112bからチャネルへの電子の流出量はゲート電極114bから電荷蓄積膜112bへの電子の流入量よりも小さくなる。

【0032】

また、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、絶縁膜111bに印加される電界は絶縁膜113bに印加される電界よりも小さくなる。このため、電荷蓄積膜112bからチャネルへの電子の流出量はゲート電極114bから電荷蓄積膜112bへの流入量よりも小さくなる。

【0033】

この第1具体例の第2メモリトランジスタ10bでは、絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚く、且つ、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、電荷蓄積膜112bからチャネルへの電子の流出量はゲート電極114bから電荷蓄積膜112bへの電子の流入量よりも大幅に小さくなる。これにより、電荷蓄積膜112bに蓄えられた負電荷はnチャネルトランジスタの閾値を上昇させる。この高閾値は例えば4Vである。

【0034】

次に、第1具体例の第2メモリトランジスタ10bが高閾値状態にあるときに、図7(b)に示すように、ソース/ドレイン102bおよびpウェル101bに印加する電圧を0Vとし、ゲート電極104bに第1書込電圧Vprg1(+18V)を印加した場合、電荷蓄積膜112bに蓄えられた負電荷(電子)は絶縁膜113bをトンネル現象により通過しゲート電極114bへ放出される。絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚いので、チャネルから電荷蓄積膜112bへの電子の流入量は電荷蓄積膜112bからゲート電極114bへの電子の流出量よりも小さくなる。また、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、絶縁膜111bに印加される電界は絶縁膜113bに印加される電界よりも小さくなる。このため、チャネルから電荷蓄積膜112bへの電子の流入量は電荷蓄積膜112bからゲート電極114bへの電子の流出量よりも小さくなる。

【0035】

第1具体例の第2メモリトランジスタ10bでは、絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚く、且つ、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、チャネルから電荷蓄積膜112bへの電子の流入量は電荷蓄積膜112bからゲート電極114bへの電子の流出量よりも大幅に小さくなる。これにより、電荷蓄積膜112bは元の中性状態に戻るので閾値は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112bに電荷が蓄えられていない状態(低閾値状態)で、第2メモリトランジスタ10bに第1書込電圧Vprg1を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0036】

図8に、第1具体例の第2メモリトランジスタ10bが高閾値状態(例えばデータ“1”状態)と、低閾値状態(例えばデータ“0”状態)にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性をそれぞれ示す。

【0037】

なお、第1具体例の第1および第2メモリトランジスタは、電荷蓄積膜112a、112bが電荷をトラップするトラップ絶縁膜であるMONOS(Metal-Oxide-Nitride- Oxide-Semiconductor)型不揮発性メモリトランジスタであった。このトラップ絶縁膜の代わりに、ポリシリコン、もしくはn型不純物がドープされたポリシリコン、もしくはp型不純物がドープされたポリシリコンを用いても良い。この場合、第1および第2メモリトランジスタは、フローティングゲート型(FG型)の不揮発性メモリトランジスタとなる。また、電荷蓄積膜112a、112bは、ポリシリコンとSiN膜との積層構造であっても良い。更に、電荷蓄積膜112a、112bは、メタルもしくは半導体からなる微粒子(ドット)を含有する層を有していても良い。

【0038】

また、第1具体例の第1および第2メモリトランジスタにおいては、絶縁膜113aおよび絶縁膜111bは、SiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造を有していた。この積層構造の代わりに、比誘電率の高い材料で構成しても良い。この比誘電率の高い材料としては、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOなどを使用できる。

【0039】

また、第1具体例の第1および第2メモリトランジスタ10a、10bにおいては、絶縁膜113aおよび絶縁膜111bは電子の通過をブロックする性能(ブロック性能)が重要である。電子親和力をχとする。電子親和力χが低い絶縁材料の方がブロック性能は高くなる。低χ材料層/高χ材料層/低χ材料層の積層構造とすれば帯電効果によりブロック性能を向上できる。ここで帯電効果とは、(1)イニシャルの書込時に低χ材料層に挟まれた高χ材料層に電子がトラップされ、高χ材料層が負に帯電する、(2)負の帯電により高χ材料層の実効χが低下し、ブロック性能が高まる、という効果を言う。多くの場合、材料の比誘電率εとχは比例する傾向にある。したがって、高χ材料は高ε材料であり、低χ材料は低ε材料となる。そして、高χ材料層(高ε材料層)を低χ材料層(低ε材料層)で挟み込んだ積層構造は、平均比誘電率εavgは高く且つ実効的なχを低くすることが可能となり、これにより、高いブロック性能を持つことができる。SiO2の電子親和力χは0.95eVであり、化学量論組成のSiN(Si3N4)の電子親和力χは1.32eVであり、トラップ密度を増加させるためにSiリッチ組成としたSiN(SiNx:x<1.33)の電子親和力χは1.32eV以上では組成比xの低下とともに電子親和力χが大きくなる。例えば、x=1.20でχ=2.01eV、x=1.07でχ=2.70eVである。第1具体例の第1および第2メモリトランジスタ10a、10bにおける絶縁膜113aおよび絶縁膜111bはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)であり、低χ材料層/高χ材料層/低χ材料層の積層膜になっている。Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOを、SiO2もしくはSiNで挟み込んだ積層構造を使用しても良い。

【0040】

第1実施形態による第1具体例のスイッチ4Aを図9に示す。この第1具体例のスイッチ4Aは、第1および第2メモリトランジスタ10A、10Bとしてそれぞれ図3(a)、図6(a)に示す第1具体例のメモリトランジスタ10a、10bを用いた構成となっている。この第1具体例のスイッチ4Aにおいて、上述したように、配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流による書込により、第1メモリトランジスタ10aの閾値電圧を増加させ、第2メモリトランジスタ10bの閾値電圧を低下させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、第1メモリトランジスタの閾値電圧を低下させ、第2メモリトランジスタの閾値電圧を増大させることができる。

【0041】

以上説明したように、第1実施形態によれば、FN電流による書込が可能であり、且つ共通の配線WLにより2つのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0042】

また、第1実施形態においては、第1および第2メモリトランジスタ10A、10Bをnチャネルトランジスタで構成したことにより、同じ導電型のウェルで形成することが可能となり、素子分離領域、例えばSTI(Shallow Trench Isolation)領域を形成する必要がない。このため、第1および第2メモリトランジスタがnチャネルおよびpチャネルトランジスタであって異なる導電型のウェルで形成する場合に比べて、セル面積をより小さくすることができる。

【0043】

(第2実施形態)

次に、第2実施形態によるマルチプレクサ(以下、MUXともいう)を図10に示す。この実施形態のMUX1は、3個のセル41、42、43を備えている。各セル4i(i=1,2,3)は、図1に示すスイッチ4と同じ構成を有し、第1および第2メモリトランジスタ10A、10Bと、パストランジスタ20と、配線30とを備えている。各セル4i(i=1,2,3)においては、第1メモリトランジスタ10Aのソース/ドレインの一方が配線BL1iに接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続された構成となっている。また、各セル4i(i=1,2,3)においては、第2メモリトランジスタ10Bのソース/ドレインの一方が配線BL2iに接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続された構成となっている。すなわち、配線WLは、各セル4i(i=1,2,3)に対して共通の配線となっている。また、各セル4i(i=1,2,3)においては、パストランジスタ20のゲート電極が配線30に接続され、ソース/ドレインの一方が入力信号線INiに接続され、ソース/ドレインの他方が出力信号線OUT1に接続された構成となっている。したがって。第2実施形態のMUX1は、3つの入力信号線IN1、IN2、IN3に入力された3つの入力信号のうち、予めプログラムされた1つを選択して出力信号線OUT1に出力する構成となっている。第2実施形態のMUX1は不揮発性FPGAの基本回路の一つである。

【0044】

次に、第2実施形態のMUX1の動作、即ち、初期化、書込選択、MUX動作(FPGA動作)について図11乃至図13を参照して説明する。この説明の例では、入力信号線IN1の入力が選択されて出力信号線OUT1から出力され、入力信号線IN2、IN3の入力は遮断されるようにMUX1をプログラムする。即ち、セル41においてはパストランジスタ20がONとなるように、セル42、43においてはパストランジスタ20がOFFとなるようにプログラムする。

【0045】

初期化動作を図11に示す。配線WLには第2書込電圧Vprg2(−18V)を印加し、配線BL1i(i=1,2,3)、BL2i(i=1,2,3)には0Vを印加する。この結果、すべてのセル41、42、43の第1メモリトランジスタ10Aの閾値は低く(“0”状態)なり、すべてのセル41、42、43の第2メモリトランジスタ10Bの閾値は高く(“1”状態)なる。

【0046】

選択書込動作を図12に示す。配線WLには第1書込電圧Vprg1(+18V)を印加し、選択セルであるセル41の配線BL11、BL21には0Vを印加し、非選択セルであるセル42、43の配線BL12、BL22、BL13、BL23には書込阻止電圧Vinhibitを印加する。第2実施形態においては、書込阻止電圧Vinhibitは例えば6Vである。この結果、セル41の第1メモリトランジスタ10Aの閾値は高くなり(“1”状態)、セル41の第2メモリトランジスタ10Bの閾値は低くなる(“0”状態)。選択セル41のチャネルとゲート電極との間の印加電圧は18Vであるのに対して、非選択セル42、43のチャネルとゲート電極間の印加電圧は12Vと低い。このため、非選択セル42、43においてFN電流注入による書込は起こらない。

【0047】

MUX動作(FPGA動作)を図13に示す。各セル4i(i=1,2,3)の第1メモリトランジスタ10Aが接続される配線BL1iにはVss(0V)を、第2メモリトランジスタ10Bが接続される配線BL2iにはVdd(例えば、2V)を印加する。配線WLには読出電圧Vread(例えば、2V)を印加する。図5に示すように、ゲートにVread(2V)を印加された第1メモリトランジスタ10Aが低閾値状態(“0”状態)にあるならばソース/ドレイン間の抵抗が低くなり、第1メモリトランジスタ10Aは入力された信号を通過させる。一方、第1メモリトランジスタ10Aが高閾値状態(“1”状態)にあるならばソース/ドレイン間の抵抗が高くなり、第1メモリトランジスタ10Aは入力された信号を遮断する。同様に図8に示すように、ゲートにVread(2V)を印加された第2メモリトランジスタ10Bが低閾値状態(“0”状態)にあるならばソース/ドレイン間の抵抗が低くなり、第2メモリトランジスタ10Bは入力された信号を通過させる。一方、第2メモリトランジスタ10Bが高閾値状態(“1”状態)にあるならばソース/ドレイン間の抵抗が高くなり、第2メモリトランジスタ10Bは入力された信号を遮断する。セル41のパストランジスタ20のゲートには低閾値状態にある第2メモリトランジスタ10Bを経由してVddが印加され、パストランジスタ20はON状態となる。一方、セル42、43のパストランジスタ20のゲート電極には低閾値状態にある第1メモリトランジスタ10Aを経由してVss(0V)が印加され、パストランジスタ20はOFF状態となる。IN1に入力された信号はセル41のパストランジスタを経由してOUT1に出力される。一方、入力信号線IN2、IN3に入力された信号はセル42、43のパストランジスタ20によってそれぞれ遮断される。

【0048】

上述したように、第2実施形態においては、書込電圧の印加時に閾値のシフト方向が異なるメモリトランジスタ10A、10Bのペアと、パストランジスタ20とを組み合わせたセル構造を有しているので、FN電流による書込が可能であり、且つ共通の配線WLにより各セルのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0049】

さらに加えて、第2実施形態によれば、選択書込回数を大幅に減少することができる。この第2実施形態のMUXをFPGAに用いれば、FPGAの書込時間を、大幅に減少することができる。n入力1出力のMUXをプログラミングするのに必要な選択書込回数は、第1実施形態の不揮発性プログマブルスイッチをMUXに用いた場合は1回である。一方、従来の不揮発性プログラマブルスイッチをMUXに用いた場合はN回必要となる。ここでは、第1および第2メモリトランジスタの閾値状態を、(0/0)、(0/1)、(1/0)、(1/1)で表す。例えば、状態(0/1)は、第1メモリトランジスタの閾値が“0”状態で、第2メモリトランジスタの閾値が“1”状態であることを意味する。

【0050】

第2実施形態のMUXでは、初期化において共通の配線WLには第2書込電圧Vprg2(−18V)を印加することによって、すべてのセル41、42、43は状態(0/1)に一括でプログラミングされる。これはすべてのパストランジスタ30がMUX動作(FPGA動作)時にOFFする状態である。選択書込動作においては1つの選択セルのみを状態(1/0)になるよう書込を実施すればよい。この結果、選択セルのパストランジスタ30のみがONする。

【0051】

一方、従来の不揮発性プログラマブルスイッチは初期化(消去動作)においてすべての不揮発性プログラマブルスイッチは(0/0)にリセットされる。状態(0/0)はパストランジスタの状態が不定になり、不揮発性プログラマブルスイッチの動作時には使用しない。選択書込動作においてはすべてのセルに対して書込動作を行い、状態(1/0)か状態(0/1)を書込む必要がある。

【0052】

即ち、第2実施形態のMUXでは、セル内の不揮発性メモリトランジスタペアの状態が(0/1)と(1/0)のみであり、状態(0/0)と状態(1/1)が不要である点に着眼し、書込電圧の印加時に閾値のシフト方向が異なる不揮発性メモリトランジスタのペアを組み合わせることにより、FPGAの書込時間を大幅に短縮することも可能にしている。

【0053】

(第3実施形態)

図14に第3実施形態による不揮発性プログラマブルスイッチ(以下、スイッチまたはセルともいう)を示す。この第3実施形態のセル4Bは、図9に示す第1実施形態による第1具体例のセル4Aにおいて、第2メモリトランジスタとして、nチャネルメモリトランジスタ10bをpチャネルメモリトランジスタ10cに置き換えた構成となっている。

【0054】

このメモリトランジスタ10cの構成を図15(a)に示す。図15(a)に示すように、このメモリトランジスタ10cは、n型半導体領域(例えばnウェル)101cに形成されたpチャネルトランジスタであって、nウェル101cに離間して形成されたp型のソース/ドレイン102cと、ソース/ドレイン102c間のnウェル101cの領域(チャネル)上に形成されたゲート構造110cとを備えている。なお、n型半導体領域としてはnウェルの他にn型半導体基板とすることができる。ゲート構造110cは、絶縁膜111cと、電荷蓄積膜112cと、絶縁膜113cと、ゲート電極114cとがこの順序で積層された構造を有している。ソース/ドレイン102cの一方が図14に示す配線BL2に接続され、他方が配線30に接続される。また、ゲート電極114cが配線WLに接続される。そして、絶縁膜111cの膜厚が絶縁膜113cの膜厚よりも薄いか、もしくは絶縁膜111cの平均比誘電率が絶縁膜113cの平均比誘電率よりも小さくなるように構成されている。また、このメモリトランジスタ10cは、本明細書では、図15(b)に示す記号で表す。

【0055】

メモリトランジスタ10cでは例えば、絶縁膜111cはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層構造とし、電荷蓄積膜112cはSiN(5nm)とし、絶縁膜113cはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とする。すなわち、絶縁膜111cの膜厚は6nm、絶縁膜113cの膜厚は10.5nmとなり、絶縁膜111cの膜厚は絶縁膜113cの膜厚よりも薄い。また、SiO2の比誘電率が3.9で、SiNの比誘電率が8であるので、絶縁膜111cの平均比誘電率は4.26、絶縁膜113cの平均比誘電率は4.70となる。すなわち、絶縁膜111cの平均比誘電率は絶縁膜113cの平均比誘電率よりも小さい。

【0056】

なお、メモリトランジスタ10cは、電荷蓄積膜112cが電荷をトラップするトラップ絶縁膜であるMONOS型不揮発性メモリトランジスタであった。このトラップ絶縁膜の代わりに、ポリシリコン、もしくはn型不純物がドープされたポリシリコン、もしくはp型不純物がドープされたポリシリコンを用いても良い。この場合、メモリトランジスタ10cは、フローティングゲート型の不揮発性メモリトランジスタとなる。また、電荷蓄積膜112cは、ポリシリコンとSiN膜との積層構造であっても良い。更に、電荷蓄積膜112cは、メタルもしくは半導体からなる微粒子(ドット)を含有する層を有していても良い。

【0057】

また、メモリトランジスタ10cにおいては、絶縁膜113cは、SiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造を有していた。この積層構造の代わりに、比誘電率の高い材料で構成しても良い。この比誘電率の高い材料としては、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOなどを使用できる。

【0058】

また、メモリトランジスタ10cにおいては、絶縁膜113cは電子の通過をブロックする性能(ブロック性能)が重要である。このため、第1実施形態と同様に、低χ材料層/高χ材料層/低χ材料層の積層膜を用いてもよい。また、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOを、SiO2もしくはSiNで挟み込んだ積層構造を使用しても良い。

【0059】

図16(a)、16(b)にメモリトランジスタ10cの書込電圧を示す。メモリトランジスタ10cにおいて、例えば第1書込電圧Vprg1を+18V、第2書込電圧Vprg2を−18Vとする。このメモリトランジスタ10cにおいて、図16(a)に示すように、ソース/ドレイン102cおよびnウェル101cに印加する電圧を0Vとし、ゲート電極114cに第1書込電圧Vprg1(+18V)を印加した場合、チャネルの電子は絶縁膜111cをトンネル現象により通過し電荷蓄積膜112cに注入され、電荷蓄積膜112cでトラップされ蓄積される。絶縁膜113cの平均比誘電率は絶縁膜111cの平均比誘電率よりも大きいので、電荷蓄積膜112cからゲート電極114cへの電子の移動は起こらない。電荷蓄積膜112cに蓄えられた負電荷(電子)はpチャネルメモリトランジスタ10cの閾値電圧(Vth)を正方向にシフトさせる。これはpチャネルメモリトランジスタ10cの閾値電圧を低下させることに相当する。この低閾値は例えば+2Vである。なお、pチャネルメモリトランジスタ10cにおいては、閾値Vthが負の場合はその絶対値が大きいほど、もしくは閾値Vthが正の場合はその絶対値が小さいほど閾値が高いと表現する。逆に、pチャネルメモリトランジスタ10cにおいては、閾値Vthが負の場合はその絶対値が小さいほど、もしくは閾値Vthが正の場合はその絶対値が大きいほど閾値が低いと表現する。

【0060】

次に、図16(b)に示すように、メモリトランジスタ10cが低閾値状態であるときに、ソース/ドレイン102cおよびnウェル101cに印加する電圧を0Vとし、ゲート電極114cに第2書込電圧Vprg2(−18V)を印加した場合、電荷蓄積膜112cに蓄えられた電子は絶縁膜111cをトンネル現象により通過しチャネルへ放出される。絶縁膜113cの平均比誘電率は絶縁膜111cの平均比誘電率よりも大きいので、ゲート電極114cから電荷蓄積膜112cへの電子の移動は起こらない。メモリトランジスタ10cにおいては、閾値は元の高閾値に戻る。この高閾値は例えば−2Vである。もし、電荷蓄積膜111cに電荷が蓄えられていない状態(高閾値状態)で、メモリトランジスタ10cに第2書込電圧Vprg2を印加した場合は、電荷の移動は起こらず高閾値状態が保持される。

【0061】

図17に、メモリトランジスタ10cが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性をそれぞれ示す。

【0062】

図14に示す第3実施形態のセル4Bにおいては、配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流の書込により、nチャネルメモリトランジスタ10aの閾値電圧を増加させ、pチャネルメモリトランジスタ10cの閾値電圧を低下させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、nチャネルメモリトランジスタ10aの閾値電圧を低下させ、pチャネルメモリトランジスタ10cの閾値電圧を増大させることができる。すなわち、セル4Bの読出動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの一方がON状態となり、他方がOFF状態となる。また、書込動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができる。

【0063】

(第1変形例)

第3実施形態の第1変形例によるセル4Cを図18に示す。この第1変形例によるセル4Cは、図14に示す第3実施形態のセル4Bにおいて、nチャネルメモリトランジスタ10aの電荷蓄積膜112aと、pチャネルメモリトランジスタ10cの電荷蓄積膜112cとを接続した構成となっている。例えば、nチャネルメモリトランジスタ10aの電荷蓄積膜112aと、pチャネルメモリトランジスタ10cの電荷蓄積膜112cとを共有化した構成となっている。第1変形例によるセル4Cにおいては、例えばSiNからなる電荷蓄積膜を、nチャネルメモリトランジスタ10aの電荷蓄積膜112aと、pチャネルメモリトランジスタ10cの電荷蓄積膜112cに分離する加工が必ずしも必要でなくなり、このことは、特に微細なセルの作成を容易にする。

【0064】

この第1変形例のセル4Cにおいては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cはともに、MONOS型のメモリトランジスタとなる。この第1変形例のセルCにおいても、図14に示す第3実施形態のセル4Bと同様に、セル4Cの動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの一方がON状態となり、他方がOFF状態となる。また、書込動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができる。

【0065】

これに対して、比較例のセルとして、第1変形例にセル4Cにおいて、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cをFG型のメモリトランジスタとしたものを形成する。この比較例のセルにおいては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができない。すなわち、一方のメモリトランジスタの閾値を変化させれば、他方のメモリトランジスタの閾値も従属して変化する。したがって、この比較例のセルにおいては、書込動作時に、一方のメモリトランジスタがONとなり、他方のメモリトランジスタがOFFとなるような読み出し電圧Vreadを設定できない場合がある。

【0066】

この比較例のセルにおいて、共通にされたFG(電荷蓄積膜)をnチャネルメモリトランジスタと、pチャネルメモリトランジスタで分離する加工を施せば、チャネル不純物とゲート電極の不純物濃度の調整によりΔVthの独立制御が可能となる。しかしこの場合、FG(電荷蓄積膜)が厚いために分離加工する際の加工マージンが必要となる。即ち、必要なセル面積が大きくなる。FG型メモリトランジスタのトンネル膜、電荷蓄積膜(FG)、ブロック膜の典型的な厚さの一例は、7nm、90nm、9nmであり、合計して116nmの厚さがある。

【0067】

第3実施形態およびその第1変形例のセル4B、4Cで使用するMONOS型メモリトランジスタの場合、SiNの電荷蓄積膜の厚さが薄いため分離加工する場合の加工マージンが小さい。MONOS型メモリトランジスタのトンネル膜、電荷蓄積膜、ブロック膜の厚さは、第3実施形態のセルにおいては、従えば、6nm、5nm、10.5nmであり、合計して、21.5nmである。

【0068】

また、MONOS型メモリトランジスタの場合、第1変形例のようにnチャネルメモリトランジスタとpチャネルメモリトランジスタで、SiNの電荷蓄積膜を共有する場合でもΔVthの独立制御が可能となる。これは、比較例のようにFGに注入された電子は可動(mobile)キャリアとなり、FG中の電位が均一になるように再配置するのに対して、SiNの電荷蓄積膜に注入されトラップされた電子は不動(immobile)化/局在化するためである。SiNの電荷蓄積膜を共有すれば分離加工のプロセスコストや、分離加工のための大きなセル面積も必要なく、nチャネルメモリトランジスタとpチャネルメモリトランジスタでΔVthの独立制御が可能になる。

【0069】

第3実施形態の第1変形例のセル4Cに用いられるMONOS型メモリトランジスタの電荷蓄積膜がSiNで構成される場合を考える。この場合、電荷蓄積膜を構成するSiNx膜の組成xは、0.67<x≦1.33の範囲にあることが望ましい。SiNx膜の化学量論的組成はSi3N4であり、その場合のSiに対するNのモル比はx=1.33となる。x<1.33のSiNx膜は、Siの組成比が大きいSiリッチな組成となり、Siの未結合手に由来する電子トラップ量が増大する。このため、より大きなΔVthを実現できる。x=0.67は平均的に、Siの4つの結合手の内2つが未結合手となるが、隣接Siと共有結合を形成する組成に相当する。この場合、共有結合が大量に存在することになり、トラップされた電子が広範囲に拡散するようになる。この場合、nチャネルメモリトランジスタとpチャネルメモリトランジスタでΔVthの独立制御が難しくなる。

【0070】

第2実施形態のMUXを構成するセル4として、第1実施形態の第1具体例のセル4A、第3実施形態およびその第1変形例によるセル4B、4Cを用いてMUXを構成しても、第2実施形態のMUXと同じ手続きで初期化、選択書込、FPGA動作が可能である。例えば、第3実施形態のセル4Bを用いた場合、FPGA動作においては、配線WLに読出電圧Vread(+2V)を印加すると、第1メモリトランジスタであるnチャネルメモリトランジスタ10aのソース−ゲート電圧Vgsは、Vgs=Vread−Vssであるから、Vgs=+2Vとなる。ここで、Vssはソースに印加される電圧でVss=0Vである(図13参照)。一方、第2メモリトランジスタであるpチャネルメモリトランジスタ10cのソース−ゲート電圧VgsはVgs=Vread−Vddであるから、Vgs=0Vとなる。ここで、Vddはpチャネルメモリトランジスタ10cのソースに印加される電圧(例えば、+2V(図13参照))である。したがって、図8と図17を参照すれば明らかなように、nチャネルメモリトランジスタ10aとpチャネルメモリトランジスタ10cはともに閾値が低い/高いに応じてON/OFF状態が決定される。

【0071】

第1実施形態の第1具体例のセル4Aに対して第3実施形態およびその第1変形例のセル4B、4Cは次の2つの利点を有している。第1の利点は、第3実施形態では、第1メモリトランジスタ10aと第2メモリトランジスタ10cのゲート積層構造を共通にすることが可能であり、ゲート部の作成工程数を低減させることができる。第2の利点は、第3実施形態では、FPGA動作においてVssを転送する第1メモリトランジスタとしてnチャネルメモリトランジスタ10aを使用し、一方、Vddを転送する第2メモリトランジスタにpチャネルメモリトランジスタ10cを使用することができる。一般に、Vssを転送するにはnチャネルメモリトランジスタが有利であり、一方Vddを転送するにはpチャネルメモリトランジスタが有利である。これは、nチャネルメモリトランジスタを使用してVddを転送する場合、閾値電圧分の電圧降下を伴うからである。

【0072】

以上説明したように、第3実施形態およびその第1変形例によれば、第1実施形態と同様に、FN電流による書込が可能であり、且つ共通の配線WLにより2つのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0073】

(第4実施形態)

図19に第4実施形態による不揮発性プログラマブルスイッチ(以下、セル4Dともいう)を示す。この第4実施形態のセル4Dは、図14に示す第3実施形態のセル4Bにおいて、第1メモリトランジスタとしてnチャネルメモリトランジスタ10aを図6(a)に示すnチャネルメモリトランジスタ10bに置き換えるとともに、第2メモリトランジスタとしてpチャネルメモリトランジスタ10cをpチャネルメモリトランジスタ10dに置き換えた構成となっている。

【0074】

このセル4Dにおいては、nチャネルメモリトランジスタ10dは、ソース/ドレインの一方が配線BL1に接続され、他方が配線30に接続され、ゲート電極が配線WLに接続される。

【0075】

pチャネルメモリトランジスタ10dの構成を図20(a)に示す。図20(a)に示すように、このメモリトランジスタ10dは、n型半導体領域(例えばnウェル)101dに形成されたpチャネルトランジスタであって、nウェル101dに離間して形成されたp型のソース/ドレイン102dと、ソース/ドレイン102d間のnウェル101dの領域(チャネル)上に形成されたゲート構造110dとを備えている。なお、n型半導体領域としてはnウェルの他にn型半導体基板とすることができる。ゲート構造110dは、絶縁膜111dと、電荷蓄積膜112dと、絶縁膜113dと、ゲート電極114dとがこの順序で積層された構造を有している。ソース/ドレイン102dの一方が図19に示す配線BL2に接続され、他方が配線30に接続される。また、ゲート電極114dが配線WLに接続される。そして、絶縁膜111dの膜厚が絶縁膜113dの膜厚よりも厚いか、もしくは絶縁膜111dの平均比誘電率が絶縁膜113cの平均比誘電率よりも大きくなるように構成されている。また、このメモリトランジスタ10dは、本明細書では、図20(b)に示す記号で表す。

【0076】

メモリトランジスタ10dでは例えば、絶縁膜111dはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とし、電荷蓄積膜112dはSiN(5nm)とし、絶縁膜113dはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層とする。すなわち、絶縁膜111dの膜厚は10.5nm、絶縁膜113dの膜厚は6nmとなり、絶縁膜111dの膜厚は絶縁膜113dの膜厚よりも厚い。また、SiO2の比誘電率が3.9で、SiNの比誘電率が8であるので、絶縁膜111dの平均比誘電率は4.70、絶縁膜113dの平均比誘電率は4.26となる。すなわち、絶縁膜111dの平均比誘電率は絶縁膜113dの平均比誘電率よりも大きい。

【0077】

なお、メモリトランジスタ10dは、電荷蓄積膜112dが電荷をトラップするトラップ絶縁膜であるMONOS型不揮発性メモリトランジスタであった。このトラップ絶縁膜の代わりに、ポリシリコン、もしくはn型不純物がドープされたポリシリコン、もしくはp型不純物がドープされたポリシリコンを用いても良い。この場合、メモリトランジスタ10dは、フローティングゲート型の不揮発性メモリトランジスタとなる。また、電荷蓄積膜112dは、ポリシリコンとSiN膜との積層構造であっても良い。更に、電荷蓄積膜112dは、メタルもしくは半導体からなる微粒子(ドット)を含有する層を有していても良い。

【0078】

また、メモリトランジスタ10dにおいては、絶縁膜111dは、SiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造を有していた。この積層構造の代わりに、比誘電率の高い材料で構成しても良い。この比誘電率の高い材料としては、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOなどを使用できる。

【0079】

また、メモリトランジスタ10dにおいては、絶縁膜111dは電子の通過をブロックする性能(ブロック性能)が重要である。このため、第1実施形態と同様に、低χ材料層/高χ材料層/低χ材料層の積層膜を用いてもよい。また、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOを、SiO2もしくはSiNで挟み込んだ積層構造を使用しても良い。

【0080】

図21(a)、21(b)にメモリトランジスタ10dの書込電圧を示す。メモリトランジスタ10dにおいて、図21(a)に示すように、ソース/ドレイン102dおよびnウェル101dに印加する電圧を0Vとし、ゲート電極114dに第2書込電圧Vprg2(−18V)を印加した場合、ゲート電極114dの電子は絶縁膜113dをトンネル現象により通過し電荷蓄積膜112dに注入され、電荷蓄積膜112dでトラップされて蓄積される。絶縁膜111dの平均比誘電率は絶縁膜113dの平均比誘電率よりも大きいので、電荷蓄積膜112dからチャネルへの電子の移動は起こらない。電荷蓄積膜112dに蓄えられた負電荷はpチャネルメモリトランジスタ10dの閾値電圧(Vth)を低下させ、低閾値となる。この低閾値は例えば+2Vである。

【0081】

次に、図21(b)に示すように、メモリトランジスタ10dが低閾値状態であるときに、ソース/ドレイン102dおよびnウェル101dに印加する電圧を0Vとし、ゲート電極114dに第1書込電圧Vprg1(+18V)を印加した場合、電荷蓄積膜112dに蓄えられた負電荷(電子)は絶縁膜113dをトンネル現象により通過し、ゲート電極114dへ放出される。絶縁膜111dの平均比誘電率は絶縁膜113dの平均比誘電率よりも大きいので、チャネルから電荷蓄積膜112dへの電子の移動は起こらない。電荷蓄積膜112dは元の中性状態に戻るので、pチャネルメモリトランジスタ10dの閾値は元の高閾値に戻る。この高閾値は例えば−2Vである。もし、電荷蓄積膜112dに電荷が蓄えられていない状態(高閾値状態)で、メモリトランジスタ10dに第1書込電圧Vprg1を印加した場合は、電荷の移動は起こらず高閾値状態が保持される。

【0082】

図22に、メモリトランジスタ10dが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性を示す。

【0083】

図19に示す第4実施形態のセル4Dにおいては、配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流の書込により、nチャネルメモリトランジスタ10bの閾値電圧を低下させ、pチャネルメモリトランジスタ10dの閾値電圧を増大させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、nチャネルメモリトランジスタ10bの閾値電圧を増大させ、pチャネルメモリトランジスタ10dの閾値電圧を低下させることができる。

【0084】

(第1変形例)

次に、第4実施形態の第1変形例によるセル4Eを図23に示す。このセル4Eは、図19に示す第4実施形態のセル4Dにおいて、nチャネルメモリトランジスタ10bの電荷蓄積膜112bと、pチャネルメモリトランジスタ10dの電荷蓄積膜112dを接続した構成となっている。例えば、nチャネルメモリトランジスタ10bとpチャネルメモリトランジスタ10dが一つの電荷蓄積膜を共有してもよい。この第1変形例によるセル4Eにおいては、電荷蓄積膜を分離する加工が必ずしも必要では無い。これは、特に微細なセルの作成を容易にする。

【0085】

この第1変形例のセル4Eにおいては、nチャネルメモリトランジスタ10bおよびpチャネルメモリトランジスタ10dはともに、MONOS型のメモリトランジスタとなる。この第1変形例のセルEにおいても、図14に示す第3実施形態のセル4Bと同様に、セル4Eの動作時においては、nチャネルメモリトランジスタ10bおよびpチャネルメモリトランジスタ10dの一方がON状態となり、他方がOFF状態となる。また、書込動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができる。

【0086】

第4実施形態またはその変形例によるセル4D、4Eを、第2実施形態のMUXを構成するセルとして用いることができる。この場合、次の点を除いて、第2実施形態と同じ手続きで初期化、選択書込、FPGA動作が可能である。第4実施形態または変形例によるセル4D、4Eを用いた場合には、初期化の際には配線WLに第1書込電圧Vprg1(+18V)を印加し、選択書込の際には配線WLに第2書込電圧Vprg2(−18V)を印加する。

【0087】

第1実施形態に対する第4実施形態の利点は、既に述べた第1実施形態に対する第3実施形態の利点と同じである。第3実施形態に対する第4実施形態の利点は、p型トランジスタのΔVthがチャネルと電荷蓄積膜の間の電子授受によるのではなく、ゲート電極と電荷蓄積膜との間の電子授受によることにより、電荷の注入効率が高くなる場合があることである。

【0088】

以上説明したように、第4実施形態およびその第1変形例によれば、第1実施形態と同様に、FN電流による書込が可能であり、且つ共通の配線WLにより2つのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0089】

(第5実施形態)

図24に、第5実施形態による不揮発性プログラマブルスイッチ(以下、セル4Fともいう)を示す。この第5実施形態によるセル4Fは、図9に示す第1実施形態の第1具体例のセル4Aにおいて、nチャネルメモリトランジスタ10a、10bをnチャネルメモリトランジスタ10e、10fにそれぞれ置き換えた構成となっている。メモリトランジスタ10eは、ソース/ドレインの一方が配線BL1に接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続される。また、メモリトランジスタ10fは、ソース/ドレインの一方が配線BL2に接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続される。

【0090】

nチャネルメモリトランジスタ10eの構成を図25(a)、25(b)に示す。図25(a)はゲート長方向(ソースからドレインに向かう方向)の断面図であり、図25(b)はゲート長方向に直交する方向の断面図である。このメモリトランジスタ10eは、図25(a)に示すように、p型半導体領域(例えばpウェル)101eに形成されたnチャネルトランジスタであって、pウェル101eに離間して形成されたn型のソース/ドレイン102eと、ソース/ドレイン102e間のpウェル101eの領域(チャネル)上に形成されたゲート構造110eとを備えている。なお、p型半導体領域としてはpウェルの他にp型半導体基板とすることができる。ゲート構造110eは、絶縁膜(トンネル膜)111eと、電荷蓄積膜112eと、絶縁膜(ブロック膜)113eと、ゲート電極114eとがこの順序で積層された構造を有している。図25(b)に示すように、絶縁膜113eは電荷蓄積膜112eの上面と側面の一部を覆うように設けられ、ゲート電極114eは絶縁膜113eの上面および側面を覆うように設けられている。

【0091】

nチャネルメモリトランジスタ10fの構成を図26(a)、26(b)に示す。図26(a)はゲート長方向(ソースからドレインに向かう方向)の断面図であり、図26(b)はゲート長方向に直交する方向の断面図である。このメモリトランジスタ10fは、図26(a)に示すように、p型半導体領域(例えばpウェル)101fに形成されたnチャネルトランジスタであって、pウェル101fに離間して形成されたn型のソース/ドレイン102fと、ソース/ドレイン102f間のpウェル101fの領域(チャネル)上に形成されたゲート構造110fとを備えている。なお、p型半導体領域としてはpウェルの他にp型半導体基板とすることができる。ゲート構造110fは、絶縁膜(トンネル膜)111fと、電荷蓄積膜112fと、絶縁膜(ブロック膜)113fと、ゲート電極114fとがこの順序で積層された構造を有している。図26(b)に示すように、絶縁膜113fは、電荷蓄積膜112fと接触する面積よりも、ゲート電極114fと接触する面積が大きくなるように設けられている。また、図26(b)に示すように、絶縁膜113fの下面の面積が電荷蓄積膜112fの上面の面積よりも大きく、絶縁膜113fの上面の面積は、ゲート電極114fの下面の面積以下となるように設けられている。なお、メモリトランジスタ10e、10fは、MONOS型不揮発性メモリトランジスタであっても、FG型不揮発性メモリトランジスタであってもよい。

【0092】

第5実施形態においては、メモリトランジスタ10eの電荷蓄積膜112eに対する絶縁膜113eを挟んで対向するゲート電極114eの対向面積(重なり合う面積)が、メモリトランジスタ10fの電荷蓄積膜112fに対する絶縁膜113fを挟んで対向するゲート電極114fの対向面積(重なり合う面積)よりも大きくなるように構成されている。電荷蓄積膜に対するゲート電極の対向面積の違いは、ゲート電極に電圧を印加した場合のウェル(基板)から見た電荷蓄積膜の電位の違いを生じ、対向面積が大きいほど、電荷蓄積膜の電位が高くなる。具体的には、ゲート電極に印加する電圧をVcg、電荷蓄積膜の電位をVct、電荷蓄積膜とウェルとの容量をC1、ゲート電極と電荷蓄積膜との間の容量をC2とすると、

Vcg=(C2/(C1+C2))×Vct

の関係がある。したがって、上述した対向面積はその間の容量C2に関わる。ここでC2/(C1+C2)はカップリング比(Coupling Ratio)と呼称される。カップリング比が異なれば、同じ電圧をゲート電極に印加した場合にも、メモリ動作は異なるものとなる。ここで、絶縁膜を挟んで対向する2つの電極の対向面積をS、上記絶縁膜の厚さをt、上記絶縁膜の誘電率をεとすると、容量Cは

C=(S/t)×ε

となる。この場合、図25(b)示す構成においては、容量C1に関する対向面積は、容量C2に関する対向面積よりも小さいため、容量C2が大きく、すなわち絶縁膜111eを介した電荷のやり取りを促進させることができる。

【0093】

一方、図26(b)に示す構成においては、図25(b)に示す構成に比べ、容量C1と容量C2との間に対向面積Sの差を生じさせにくい。この場合、電荷のやり取りを促進させるためには、絶縁膜の厚さtを変える必要がある。このため、図26(b)に示す構成においては、絶縁膜113fを介した電荷のやり取りを促進させるためには、絶縁膜111fよりも絶縁膜113fを薄くする必要がある。

【0094】

図27(a)、27(b)に、メモリトランジスタ10eの書込電圧を示す。第5実施形態では、例えば第1書込電圧Vprg1を+18V、第2書込電圧Vprg2を−18Vとする。図27(a)に示すように、メモリトランジスタ10eのソース/ドレイン102eおよびpウェル101eに印加する電圧を0Vとし、ゲート電極114eに第1書込電圧Vprg1(+18V)を印加した場合、チャネルの電子は絶縁膜111eをトンネル現象(FNトンネル電流)により通過して電荷蓄積膜112eに注入される。注入された電子は電荷蓄積膜112eでトラップされ、蓄積される。このとき、メモリトランジスタ10eにおいては、電荷蓄積膜112eに対するゲート電極114eの対向面積が、電荷蓄積膜112eに対するチャネルの対向面積よりも大きいため、電荷蓄積膜112eから絶縁膜113eを介してゲート電極114eへの電子の流出量はチャネルから電荷蓄積膜112eへの注入量に比べて少ない。

【0095】

電荷蓄積膜112eに蓄えられた負電荷(電子)はnチャネルメモリトランジスタ10eの閾値電圧(Vth)を上昇させ、高閾値となる。この高閾値は例えば4Vである。

【0096】

次に、メモリトランジスタ10eが高閾値状態にあるときに、メモリトランジスタ10eのソース/ドレイン102eおよびpウェル101eに印加する電圧を0Vとし、ゲート電極114eに第2書込電圧Vprg2(−18V)を印加した場合、電荷蓄積膜112eに蓄えられた電子は絶縁膜111eをトンネル現象により通過しチャネルへ放出される。このとき、メモリトランジスタ10eにおいては、電荷蓄積膜112eに対するゲート電極の対向面積が、電荷蓄積膜112eに対するチャネルの対向面積よりも大きいため、ゲート電極114eから電荷蓄積膜112eへの電子の注入量は電荷蓄積膜112eからチャネルへの流出量に比べて少ない。これにより、電荷蓄積膜112eは元の中性状態に戻るのでメモリトランジスタ10eの閾値は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112eに電荷が蓄えられていない状態(低閾値状態)で、メモリトランジスタ10eに第2書込電圧Vprg2を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0097】

図28に、メモリトランジスタ10eが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性を示す。

【0098】

図29(a)、29(b)に、メモリトランジスタ10fの書込電圧を示す。図29(a)に示すように、メモリトランジスタ10fにおいて、ソース/ドレイン102fおよびpウェル101fに印加する電圧を0Vとし、ゲート電極114fに第2書込電圧Vprg2(−18V)を印加した場合、ゲート電極114fの電子は絶縁膜113fをトンネル現象により通過し電荷蓄積膜112fに注入され、そこでトラップされ蓄積される。このとき、メモリトランジスタ10fにおいては、電荷蓄積膜112fに対するゲート電極114fの対向面積が、電荷蓄積膜112fに対するチャネルの対向面積よりも小さいため、電荷蓄積膜112fからチャネルへの電子の流出量はゲート電極114fからの注入量に比べて少ない。電荷蓄積膜112fに蓄えられた負電荷はnチャネルメモリトランジスタ10fの閾値電圧(Vth)を上昇させ高閾値となる。この高閾値は例えば4Vである。

【0099】

次に、メモリトランジスタ10fが高閾値状態にあるときに、図29(b)に示すように、ソース/ドレイン102fおよびpウェル101fに印加する電圧を0Vとし、ゲート電極114fに第1書込電圧Vprg1(+18V)を印加した場合、電荷蓄積膜112fに蓄えられた負電荷(電子)は絶縁膜113fをトンネル現象により通過し、ゲート電極114fへ放出される。このとき、メモリトランジスタ10fにおいては、電荷蓄積膜112fに対するゲート電極114fの対向面積が、電荷蓄積膜112fに対するゲーチャネルの対向面積よりも小さいため、チャネルから電荷蓄積膜112fへの電子の流入量は、電荷蓄積膜112fからゲート電極114fへの流出量に比べて少ない。これにより電荷蓄積膜112fは元の中性状態に戻るので閾値電圧は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112fに電荷が蓄えられていない状態(低閾値状態)で、メモリトランジスタ10fに第1書込電圧Vprg1を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0100】

図30に、メモリトランジスタ10fが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性を示す。

【0101】

図24に示した第5実施形態におけるセル4Fの動作としては、例えば図4に示す第1実施形態の第1具体例のセル4Aと等価である。配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流の書込により、メモリトランジスタ10eの閾値電圧を増加させ、メモリトランジスタ10fの閾値電圧を低下させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、メモリトランジスタ10eの閾値電圧を低下させ、メモリトランジスタ10fの閾値電圧を増大させることができる。

【0102】

次に、メモリトランジスタ10e、10fの製造方法を図31乃至図36(b)を参照して説明する。図31乃至図36(b)は、メモリトランジスタ10e、10fの製造方法を説明する断面図である。

【0103】

まず、図31に示すように、半導体基板のpウェル101の上に絶縁膜111を形成し、絶縁膜111上に電荷蓄積膜112を形成する。

【0104】

次いで、例えばPEP(Photo Engraving Process)によるパターニングの後、異方性ドライエッチングを施すことにより、電荷蓄積膜112、絶縁膜111、およびウェル101を分断加工する。これにより、ウェル101は、メモリトランジスタ10eの形成領域101eと、メモリトランジスタ10fの形成領域101fに分断される。そして、ウェル101e上には絶縁膜111e、および電荷蓄積膜112eが残置され、ウェル101f上には絶縁膜111f、および電荷蓄積膜112fが残置される。続いて、分断加工により電荷蓄積膜112、絶縁膜111、およびウェル領域101が除去された領域に、例えばシリコン酸化膜(SiO2)などの絶縁膜130を埋め込み、例えばCMP(Chemical Mechanical Polishing)を用いて平坦化処理を行う(図32(a)、32(b))。この時、必要であれば、例えばSiNなどのハードマスク135をPEP前に電荷蓄積膜112の上に堆積しても良い。この状態を図32(a)32(b)に示す。この直後および後に続く工程において、ハードマスク135は、例えばウェットエッチングを施すことにより除去される。

【0105】

次いで、例えばPEPによるパターニングの後、異方性ドライエッチングを施すことによりメモリトランジスタ10eの形成領域における埋め込み絶縁膜130を加工する。この状態を図33(a)、33(b)に示す。この時、メモリトランジスタ10fの形成領域における埋め込み絶縁膜130はパターニングにより保護されており、加工されない。

【0106】

次いで、例えば等方性ウェットエッチングを施すことにより、電荷蓄積膜112e、112fを加工する。その際、メモリトランジスタ10eの形成領域においては、埋め込み絶縁膜130が加工されているため、ウェル101eに垂直な方向だけでなく、ウェル101eに平行な方向へのサイドエッチングが入る。この状態を図34(a)、34(b)に示す。このとき、メモリトランジスタ10fの形成領域においては、ウェル101fに垂直な方向にのみエッチングされる。

【0107】

次いで、図35(a)、35(b)に示すように、縁膜113を形成した後、ゲート電極114を形成する。

【0108】

次いで、例えばPEPによるパターニングの後、異方性ドライエッチングを施すことにより図35(a)、35(b)の奥行き方向に対して垂直方向にゲート電極114、絶縁膜113と、電荷蓄積膜112e、112fと、絶縁膜111e、111fとを加工し、ゲート電極114をゲート電極114e、114fに分断するとともに、絶縁膜113を絶縁膜113e、113fに分断する。これにより、メモリトランジスタ10eと、メモリトランジスタ10fが形成される。なお、絶縁膜113は、必要に応じて分断しなくても良い。

【0109】

第1実施形態の第1具体例によるセル4A、第3実施形態のセル4B、および第4実施形態のセル4Eに対する第5実施形態のセル4Fの利点は、メモリトランジスタ10eおよびメモリトランジスタ10fの作り分けにおいて、標準的なプロセスに対してPEPを行う1工程のみを追加すれば良く、低コストで形成可能なことである。この場合、第5実施形態におけるメモリトランジスタ10eおよびメモリトランジスタ10fは第1実施形態、第3および第4実施形態に示すいずれの構造でも良い。また、第5実施形態のセルはメモリトランジスタ10fとして、nチャネルメモリトランジスタを用いて構成したが、例えばメモリトランジスタ10dとして説明したpチャネルメモリトランジスタを用いて構成した場合においても、図17に示したようにスイッチ動作は可能である。

【0110】

一方、メモリトランジスタ10eおよびメモリトランジスタ10fの両者を異なった構造とした場合、例えば、メモリトランジスタ10eとしてメモリトランジスタ10aと同構造、メモリトランジスタ10fとしてメモリトランジスタ10bと同構造とすることで、同一書込電圧に対する両者の動作の差が開く方向となり、図28および図30に示したスイッチ動作をより際立たせることが出来る。

【0111】

また、第5実施形態の特徴としては、メモリトランジスタ10eおよびメモリトランジスタ10fの両者で、電荷蓄積膜に対するゲート電極の接触面積が異なることが特徴であるので、図25(a)、25(b)および図26(a)、26(b)で示した構造でなくても良い。例えば、図33(a)、33(b)の状態から図34(a)、34(b)におけるエッチング処理を省略し、図35(a)、35(b)の成膜を行うことで形成される構造を図36(a)、36(b)に示す。この構造は、電荷蓄積膜に対するゲート電極の接触面積の両者間における差は、図25(a)、25(b)および図26(a)、26(b)で示した構造と比べると小さくなるが、エッチング工程を省略できる分、製造コストを抑えることができる。一方、図34(a)、34(b)で示したエッチングを行うことで、絶縁膜113および電極114を形成する祭、ウェル分断領域を介して隣接するセル間が狭くなった場合にも埋め込みを行うことができる。これにより隣接する電荷蓄積膜間が容量を持ってしまうような干渉効果を抑制することが可能となり、高集積化を進める上で有利となる。

【0112】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これらの実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0113】

1 MUX

4〜4F 不揮発性プログラマブルスイッチ(セル)

10A 第1不揮発性メモリトランジスタ(第1メモリトランジスタ)

10B 第2不揮発性メモリトランジスタ(第2メモリトランジスタ)

10a、10b nチャネルメモリトランジスタ

10c、10d pチャネルメモリトランジスタ

11a、11b 第1端子

12a、12b 第2端子

13a、13b 第3端子

20 パストランジスタ

30 配線

BL1 配線

BL2 配線

WL 配線

【技術分野】

【0001】

本発明の実施形態は、不揮発性プログラマブルスイッチに関する。

【背景技術】

【0002】

一般に、プログラマブルスイッチは、スイッチとして機能するパストランジスタのゲートにメモリを接続して、メモリの保持データに応じてパストランジスタのオン/オフ状態を切り換え制御するものである。典型的なFPGA(Field Programmable Gate Array)は複数のロジック素子と、プログラマブルスイッチのアレーとで構成されている。各プログラマブルスイッチはロジック素子を選択的に接続する役割を担う。

【0003】

不揮発性プログラマブルスイッチを、2つの不揮発性メモリトランジスタと、1つのパストランジスタとで構成する方式が知られている。この方式においては、不揮発性メモリトランジスタとしては、例えばフローティングゲート型の不揮発性メモリトランジスタが用いられる。2つの不揮発性メモリトランジスタのいずれかを介して、パストランジスタのゲートには電源電圧もしくは0Vが入力される。不揮発性メモリトランジスタの書込を、FN(Fowler-Nordheim)トンネル電流書込方式(以下、FN方式ともいう)で行う場合は、二つの不揮発性メモリトランジスタの内の一方を選択して書き込む、選択書込が行われる。このため、二つの不揮発性メモリトランジスタのそれぞれのゲートは異なるワードラインに接続する必要がある。

【0004】

また、プログラマブルロジックスイッチを、2つの不揮発性メモリトランジスタと、1つのパストランジスタと、1つのアクセストランジスタとで構成する他の方式が知られている。不揮発性メモリトランジスタとしては、例えばフローティングゲート型メモリトランジスタが用いられる。2つの不揮発性メモリトランジスタのいずれかを介して、パストランジスタのゲートには電源電圧もしくは0Vが入力される。この他の方式においては、2つの不揮発性メモリトランジスタのゲートは共通のワードラインに接続され、選択書込は、チャネルホットエレクトロン書込方式(以下、CHE方式ともいう)で行う。

【0005】

書込可能なメモリトランジスタの限界サイズは、一般にFN方式の場合の方がCHE方式の場合よりも小さい。CHE方式は、ソース/ドレイン間の電位差によって発生した熱電子を、ゲートに印加した電圧によって電荷蓄積膜に注入する。一般に、熱電子の注入効率はトランジスタのゲート長が100nm以下の領域ではゲート長が短くなるほど低下する。

【0006】

プログラマブルスイッチのセル面積は、セル当たりのワードライン数の少ない方が、またメモリトランジスタの寸法の小さい方が、小さくなる。セル面積が小さい方が、同一チップ面積でより多くの回路要素を搭載でき高性能なFPGAを実現できる。または、同一数の回路要素をより小さいチップ面積に搭載できチップ当たりコストを低減できる。

【0007】

従って、より小さい面積を有する不揮発性プログラマブルスイッチを実現するためには、FN方式が適応可能で且つセルあたりのワード線が1本のセル構造が望まれる。しかし、その方法については現在知られていない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】米国特許第5812450号明細書

【特許文献2】米国特許第6002610号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

本実施形態は、セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【課題を解決するための手段】

【0010】

本実施形態による不揮発性プログラマブルスイッチは、第1配線に接続される第1端子と、第2配線に接続される第2端子と、第3配線に接続される第3端子と、を有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と、前記第2配線に接続される第5端子と、前記第3配線に接続される第6端子と、を有し、前記第1不揮発性メモリトランジスタと同じ導電型の第2不揮発性メモリトランジスタと、前記第2配線にゲート電極が接続されたパストランジスタと、を備え、前記第1配線および前記第4配線が第1電源に接続され、前記第3配線が前記第1電源の電圧よりも高い電圧の第2電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が増加し、前記第2不揮発性メモリトランジスタの閾値電圧が低下し、前記第1配線および前記第4配線が前記第1電源に接続され、前記第3配線が前記第1電源の電圧よりも低い電圧の第3電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が低下し、前記第2不揮発性メモリトランジスタの閾値電圧が増加すること、を特徴とする。

【図面の簡単な説明】

【0011】

【図1】第1実施形態によるセルを示す回路図。

【図2】図2(a)、2(b)は、第1実施形態によるセルの動作を説明する回路図。

【図3】図3(a)、3(b)は、第1メモリトランジスタの第1具体例を示す図。

【図4】図4(a)、4(b)は、第1メモリトランジスタの書込電圧を示す図。

【図5】第1メモリトランジスタのId−Vgs特性を示す図。

【図6】図6(a)、6(b)は、第2メモリトランジスタの第1具体例を示す図。

【図7】図7(a)、7(b)は、第2メモリトランジスタの書込電圧を示す図。

【図8】第2メモリトランジスタのId−Vgs特性を示す図。

【図9】第1実施形態によるセルの第1具体例を示す回路図。

【図10】第2実施形態によるMUXを示す回路図。

【図11】第2実施形態のMUXの動作を説明する図。

【図12】第2実施形態のMUXの動作を説明する図。

【図13】第2実施形態のMUXの動作を説明する図。

【図14】第3実施形態によるセルを示す回路図。

【図15】図15(a)、15(b)は、pチャネルメモリトランジスタを示す図。

【図16】図16(a)、16(b)は、pチャネルメモリトランジスタの書込電圧を示す図。

【図17】pチャネルメモリトランジスタのId−Vgs特性を示す図。

【図18】第3実施形態の第1変形例によるセルを示す回路図。

【図19】第4実施形態によるセルを示す回路図。

【図20】図20(a)、20(b)は、pチャネルメモリトランジスタを示す図。

【図21】図21(a)、21(b)は、pチャネルメモリトランジスタの書込電圧を示す図。

【図22】図22は、pチャネルメモリトランジスタのId−Vgs特性を示す図。

【図23】第4実施形態の第1変形例によるセルを示す回路図。

【図24】第5実施形態によるセルを示す回路図。

【図25】図25(a)、25(b)は、nチャネルメモリトランジスタを示す断面図。

【図26】図26(a)、26(b)は、nチャネルメモリトランジスタを示す断面図。

【図27】図27(a)、27(b)は、nチャネルメモリトランジスタの書込電圧を示す図。

【図28】nチャネルメモリトランジスタのId−Vgs特性を示す図。

【図29】図29(a)、29(b)は、nチャネルメモリトランジスタの書込電圧を示す図。

【図30】nチャネルメモリトランジスタのId−Vgs特性を示す図。

【図31】第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図32】図32(a)、32(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図33】図33(a)、33(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図34】図34(a)、34(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図35】図35(a)、35(b)は、第5実施形態に係るメモリトランジスタの形成方法を示す断面図。

【図36】図36(a)、36(b)は、第5実施形態に係るメモリトランジスタの形成方法の他の例を示す断面図。

【発明を実施するための形態】

【0012】

以下、図面を参照しながら、実施形態を説明する。

【0013】

(第1実施形態)

図1に第1実施形態による不揮発性プログラマブルスイッチを示す。この不揮発性プログラマブルスイッチ4は、第1および第2不揮発性メモリトランジスタ(以下、メモリトランジスタともいう)10A、10Bと、パストランジスタ20と、配線30と、を備え、一つのセルを構成する。不揮発性プログラマブルスイッチ4を以下、スイッチ4またはセル4ともいう。

【0014】

第1メモリトランジスタ10Aは、配線BL1に接続される第1端子11aと、配線30に接続される第2端子12aと、配線WLに接続される第3端子13aと、を備えている。第1メモリトランジスタ10Aにおいては、例えば第1端子11aがソース/ドレインの一方であり、第2端子12aがソース/ドレインの他方であり、第3端子13aがゲートである。また、同様に、第2メモリトランジスタ10Bは、配線BL2に接続される第1端子11bと、配線30に接続される第2端子12bと、配線WLに接続される第3端子13bと、を備えている。第2メモリトランジスタ10Bにおいては、例えば第1端子11bがソース/ドレインの一方であり、第2端子12bがソース/ドレインの他方であり、第3端子13bがゲート電極である。

【0015】

パストランジスタ20は、ゲート電極が配線30に接続され、ソース/ドレインがそれぞれ外部の配線に接続される。

【0016】

したがって、第1および第2メモリトランジスタ10A、10Bは、第3端子13a、13bが同じ配線WLに接続され、第2端子12a、12bが配線30を介してパストランジスタ20のゲート電極に接続される。

【0017】

そしてこのように構成されたスイッチ4においては、配線WLに第1書込電圧Vprg1を印加したときには、第1メモリトランジスタ10Aの閾値電圧(単に、閾値ともいう)Vthの絶対値が増加し、第2メモリトランジスタ10Bの閾値電圧Vthの絶対値が減少する(図2(a)参照)。また、配線WLに第1書込電圧Vprg1よりも低い第2書込電圧Vprg2(<Vprg1)を印加したときには、第1メモリトランジスタ10Aの閾値電圧Vthの絶対値が減少し、第2メモリトランジスタ10Bの閾値電圧Vthの絶対値が増加する(図2(b)参照)。

【0018】

次に、第1メモリトランジスタ10Aの第1具体例の構成を図3(a)に示す。図3(a)に示すように、この第1具体例のメモリトランジスタ10aは、p型半導体領域(例えばpウェル)101aに形成されたnチャネルトランジスタであって、pウェル101aに離間して形成されたn型のソース/ドレイン102aと、ソース/ドレイン102a間のpウェル101aの領域(チャネル)上に形成されたゲート構造110aとを備えている。なお、p型半導体領域としてはpウェルの他にp型半導体基板とすることができる。ゲート構造110aは、絶縁膜(トンネル膜)111aと、電荷蓄積膜112aと、絶縁膜(ブロック膜)113aと、ゲート電極114aとがこの順序で積層された構造を有している。ソース/ドレイン102aの一方が図1に示す配線BL1に接続され、他方が配線30に接続される。また、ゲート電極114aが配線WLに接続される。そして、絶縁膜111aの膜厚が絶縁膜113aの膜厚よりも薄いか、もしくは絶縁膜111aの平均比誘電率が絶縁膜113aの平均比誘電率よりも小さくなるように構成されている。ここで、絶縁膜の平均比誘電率εaveは、絶縁膜がn(≧1)個の層から構成され、i(n≧i≧1)番目の層の物理層厚をTi、比誘電率をεiとしたとき、以下の式で表される。

【数1】

また、この第1具体例のメモリトランジスタ10aは、本明細書では、図3(b)に示す記号で表す。

【0019】

第1具体例のメモリトランジスタ10aでは例えば、絶縁膜111aはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層構造とし、電荷蓄積膜112aはSiN(5nm)とし、絶縁膜113aはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とする。ここで記号「A/B」はAが上層でBが下層であることを意味し、括弧内の数値は層厚を示す。したがって、絶縁膜111aの膜厚は6nmとなり、絶縁膜113aの膜厚は10.5nmとなり、絶縁膜111aの膜厚は絶縁膜113aの膜厚よりも薄い。また、SiO2の比誘電率が3.9で、SiNの比誘電率が8であるので、絶縁膜111aの平均比誘電率は4.26、絶縁膜113aの平均比誘電率は4.70となる。すなわち、絶縁膜111aの平均比誘電率は絶縁膜113aの平均比誘電率よりも小さい。

【0020】

なお、絶縁膜111a、113a、電荷蓄積膜112a、およびゲート電極114aの膜厚、材料および組成は、メモリトランジスタ10aから該当部分を、FIB(Focused Ion Beam)を用いたピックアップ法で切り出し、その断面を高分解能透過電子顕微鏡(HRTEM)で撮像するか、若しくはエネルギー分散型X線分析(EDX(Energy Dispersive X-ray Analysis))、若しくは電子エネルギー損失分光法(EELS(Electron Energy-Loss Spectroscopy))で分析すれば、明らかにすることができる。

【0021】

図4(a)、4(b)に、第1具体例の第1メモリトランジスタ10aの書込電圧を示す。第1具体例の第1メモリトランジスタ10aにおいて、例えば第1書込電圧Vprg1を+18V、第2書込電圧Vprg2を−18Vとする。第1メモリトランジスタ10aにおいて、図4(a)に示すように、ソース/ドレイン102aおよびpウェル101aに印加する電圧を0Vとし、ゲート電極に第1書込電圧Vprg1(+18V)を印加した場合、チャネルの電子は絶縁膜111aをトンネル現象(FNトンネル電流)により通過し、電荷蓄積膜112aに注入され、電荷蓄積膜112aでトラップされ蓄積される。絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚いので、電荷蓄積膜112aからゲート電極114aへの電子の流出量はチャネルから電荷蓄積膜113aへの流入量よりも小さくなる。すなわち、電荷蓄積膜112aにトラップされた電荷(電子)量が増大する。

【0022】

また、絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、絶縁膜113aに印加される電界は絶縁膜111aに印加される電界よりも小さくなる。このため、電荷蓄積膜112aからゲート電極114aへの電子の流出量はチャネルから電荷蓄積膜112aへの流入量よりも小さくなる。

【0023】

第1具体例の第1メモリトランジスタ10aでは、絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚く、且つ、絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、電荷蓄積膜112aからゲート電極114aへの電子の流出量はチャネルから電荷蓄積膜112aへの流入量よりも大幅に小さくなる。

【0024】

このようにして電荷蓄積膜112aに蓄えられた負電荷(電子)はnチャネルメモリトランジスタ10aの閾値電圧を上昇させ、高閾値となる。この高閾値は例えば4Vである。

【0025】

次に、図4(b)に示すように、第1メモリトランジスタ10aが高閾値状態であるときに、ソース/ドレイン102aおよびpウェル101aに印加する電圧を0Vとし、ゲート電極104aに第2書込電圧Vprg2(−18V)を印加した場合、電荷蓄積膜112aに蓄えられた電子は絶縁膜111aをトンネル現象により通過しチャネルへ放出される。このとき、絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚いので、ゲート電極114aから電荷蓄積膜112aへの電子の流入量は電荷蓄積膜112aからチャネルへの電子の流出量よりも小さくなる。また、絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、絶縁膜113aに印加される電界は絶縁膜111aに印加される電界よりも小さくなる。このため、ゲート電極114aから電荷蓄積膜112aへの電子の流入量は電荷蓄積膜112aからチャネルへの電子の流出量よりも小さくなる。

【0026】

第1具体例の第1メモリトランジスタ10aでは、絶縁膜113aの膜厚は絶縁膜111aの膜厚よりも厚く、且つ絶縁膜113aの平均比誘電率は絶縁膜111aの平均比誘電率よりも大きいので、ゲート電極114aから電荷蓄積膜112aへの電子の流入量は電荷蓄積膜112aからチャネルへの電子の流出量よりも大幅に小さくなる。

【0027】

このように、電荷蓄積膜112aに電荷が蓄えられている状態(高閾値状態)で、第2書込電圧Vprg2(−18V)を印加することにより、電荷蓄積膜112aは元の中性状態に戻るので閾値は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112aに電荷が蓄えられていない状態(低閾値状態)で、第1メモリトランジスタ10aに第2書込電圧Vprg2(−18V)を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0028】

図5に、第1メモリトランジスタ10aが高閾値状態(例えばデータ“1”状態)と、低閾値状態(例えばデータ“0”状態)にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性をそれぞれ示す。なお、高閾値状態をデータ“0”状態に対応させ、低閾値状態をデータ“1”状態に対応させてもよい。

【0029】

次に、第2メモリトランジスタ10Bの第1具体例の構成を図6(a)に示す。図6(a)に示すように、この第1具体例のメモリトランジスタ10bは、p型半導体領域(例えばpウェル)101bに形成されたnチャネルトランジスタであって、pウェル101bに離間して形成されたn型のソース/ドレイン102bと、ソース/ドレイン102b間のpウェル101bの領域(チャネル)上に形成されたゲート構造110bとを備えている。なお、p型半導体領域としては、pウェルの他にp型半導体基板とすることもできる。このゲート構造110bは、絶縁膜(ブロック膜)111bと、電荷蓄積膜112bと、絶縁膜(トンネル膜)113bと、ゲート電極114bとがこの順序で積層された構造を有している。ソース/ドレイン102bの一方が図1に示す配線BL2に接続され、他方が配線30に接続される。また、ゲート電極114bが配線WLに接続される。そして、絶縁膜111bの膜厚が絶縁膜113bの膜厚よりも厚いか、もしくは絶縁膜111bの平均比誘電率が絶縁膜113bの平均比誘電率よりも大きくなるように構成されている。

【0030】

第1具体例の第2メモリトランジスタ10bでは例えば、絶縁膜111bはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とし、電荷蓄積膜112bはSiN(5nm)とし、絶縁膜113bはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層構造とする。したがって、絶縁膜111bの膜厚は10.5nm、絶縁膜113bの膜厚は6nmとなり、絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚い。また、絶縁膜111bの平均比誘電率は4.70、絶縁膜113bの平均比誘電率は4.26となり、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きい。

【0031】

図7(a)、7(b)に、第1具体例の第2メモリトランジスタ10bの書込電圧を示す。第1具体例の第2不揮発性メモリトランジスタ10bにおいて、図7(a)に示すように、ソース/ドレイン102bおよびpウェル101bに印加する電圧を0Vとし、ゲートに第2書込電圧Vprg2(−18V)を印加した場合、ゲート電極114bの電子は絶縁膜113bをトンネル現象により通過し電荷蓄積膜112bに注入され、電荷蓄積膜112bで捕獲される。絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚いので、電荷蓄積膜112bからチャネルへの電子の流出量はゲート電極114bから電荷蓄積膜112bへの電子の流入量よりも小さくなる。

【0032】

また、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、絶縁膜111bに印加される電界は絶縁膜113bに印加される電界よりも小さくなる。このため、電荷蓄積膜112bからチャネルへの電子の流出量はゲート電極114bから電荷蓄積膜112bへの流入量よりも小さくなる。

【0033】

この第1具体例の第2メモリトランジスタ10bでは、絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚く、且つ、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、電荷蓄積膜112bからチャネルへの電子の流出量はゲート電極114bから電荷蓄積膜112bへの電子の流入量よりも大幅に小さくなる。これにより、電荷蓄積膜112bに蓄えられた負電荷はnチャネルトランジスタの閾値を上昇させる。この高閾値は例えば4Vである。

【0034】

次に、第1具体例の第2メモリトランジスタ10bが高閾値状態にあるときに、図7(b)に示すように、ソース/ドレイン102bおよびpウェル101bに印加する電圧を0Vとし、ゲート電極104bに第1書込電圧Vprg1(+18V)を印加した場合、電荷蓄積膜112bに蓄えられた負電荷(電子)は絶縁膜113bをトンネル現象により通過しゲート電極114bへ放出される。絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚いので、チャネルから電荷蓄積膜112bへの電子の流入量は電荷蓄積膜112bからゲート電極114bへの電子の流出量よりも小さくなる。また、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、絶縁膜111bに印加される電界は絶縁膜113bに印加される電界よりも小さくなる。このため、チャネルから電荷蓄積膜112bへの電子の流入量は電荷蓄積膜112bからゲート電極114bへの電子の流出量よりも小さくなる。

【0035】

第1具体例の第2メモリトランジスタ10bでは、絶縁膜111bの膜厚は絶縁膜113bの膜厚よりも厚く、且つ、絶縁膜111bの平均比誘電率は絶縁膜113bの平均比誘電率よりも大きいので、チャネルから電荷蓄積膜112bへの電子の流入量は電荷蓄積膜112bからゲート電極114bへの電子の流出量よりも大幅に小さくなる。これにより、電荷蓄積膜112bは元の中性状態に戻るので閾値は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112bに電荷が蓄えられていない状態(低閾値状態)で、第2メモリトランジスタ10bに第1書込電圧Vprg1を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0036】

図8に、第1具体例の第2メモリトランジスタ10bが高閾値状態(例えばデータ“1”状態)と、低閾値状態(例えばデータ“0”状態)にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性をそれぞれ示す。

【0037】

なお、第1具体例の第1および第2メモリトランジスタは、電荷蓄積膜112a、112bが電荷をトラップするトラップ絶縁膜であるMONOS(Metal-Oxide-Nitride- Oxide-Semiconductor)型不揮発性メモリトランジスタであった。このトラップ絶縁膜の代わりに、ポリシリコン、もしくはn型不純物がドープされたポリシリコン、もしくはp型不純物がドープされたポリシリコンを用いても良い。この場合、第1および第2メモリトランジスタは、フローティングゲート型(FG型)の不揮発性メモリトランジスタとなる。また、電荷蓄積膜112a、112bは、ポリシリコンとSiN膜との積層構造であっても良い。更に、電荷蓄積膜112a、112bは、メタルもしくは半導体からなる微粒子(ドット)を含有する層を有していても良い。

【0038】

また、第1具体例の第1および第2メモリトランジスタにおいては、絶縁膜113aおよび絶縁膜111bは、SiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造を有していた。この積層構造の代わりに、比誘電率の高い材料で構成しても良い。この比誘電率の高い材料としては、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOなどを使用できる。

【0039】

また、第1具体例の第1および第2メモリトランジスタ10a、10bにおいては、絶縁膜113aおよび絶縁膜111bは電子の通過をブロックする性能(ブロック性能)が重要である。電子親和力をχとする。電子親和力χが低い絶縁材料の方がブロック性能は高くなる。低χ材料層/高χ材料層/低χ材料層の積層構造とすれば帯電効果によりブロック性能を向上できる。ここで帯電効果とは、(1)イニシャルの書込時に低χ材料層に挟まれた高χ材料層に電子がトラップされ、高χ材料層が負に帯電する、(2)負の帯電により高χ材料層の実効χが低下し、ブロック性能が高まる、という効果を言う。多くの場合、材料の比誘電率εとχは比例する傾向にある。したがって、高χ材料は高ε材料であり、低χ材料は低ε材料となる。そして、高χ材料層(高ε材料層)を低χ材料層(低ε材料層)で挟み込んだ積層構造は、平均比誘電率εavgは高く且つ実効的なχを低くすることが可能となり、これにより、高いブロック性能を持つことができる。SiO2の電子親和力χは0.95eVであり、化学量論組成のSiN(Si3N4)の電子親和力χは1.32eVであり、トラップ密度を増加させるためにSiリッチ組成としたSiN(SiNx:x<1.33)の電子親和力χは1.32eV以上では組成比xの低下とともに電子親和力χが大きくなる。例えば、x=1.20でχ=2.01eV、x=1.07でχ=2.70eVである。第1具体例の第1および第2メモリトランジスタ10a、10bにおける絶縁膜113aおよび絶縁膜111bはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)であり、低χ材料層/高χ材料層/低χ材料層の積層膜になっている。Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOを、SiO2もしくはSiNで挟み込んだ積層構造を使用しても良い。

【0040】

第1実施形態による第1具体例のスイッチ4Aを図9に示す。この第1具体例のスイッチ4Aは、第1および第2メモリトランジスタ10A、10Bとしてそれぞれ図3(a)、図6(a)に示す第1具体例のメモリトランジスタ10a、10bを用いた構成となっている。この第1具体例のスイッチ4Aにおいて、上述したように、配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流による書込により、第1メモリトランジスタ10aの閾値電圧を増加させ、第2メモリトランジスタ10bの閾値電圧を低下させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、第1メモリトランジスタの閾値電圧を低下させ、第2メモリトランジスタの閾値電圧を増大させることができる。

【0041】

以上説明したように、第1実施形態によれば、FN電流による書込が可能であり、且つ共通の配線WLにより2つのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0042】

また、第1実施形態においては、第1および第2メモリトランジスタ10A、10Bをnチャネルトランジスタで構成したことにより、同じ導電型のウェルで形成することが可能となり、素子分離領域、例えばSTI(Shallow Trench Isolation)領域を形成する必要がない。このため、第1および第2メモリトランジスタがnチャネルおよびpチャネルトランジスタであって異なる導電型のウェルで形成する場合に比べて、セル面積をより小さくすることができる。

【0043】

(第2実施形態)

次に、第2実施形態によるマルチプレクサ(以下、MUXともいう)を図10に示す。この実施形態のMUX1は、3個のセル41、42、43を備えている。各セル4i(i=1,2,3)は、図1に示すスイッチ4と同じ構成を有し、第1および第2メモリトランジスタ10A、10Bと、パストランジスタ20と、配線30とを備えている。各セル4i(i=1,2,3)においては、第1メモリトランジスタ10Aのソース/ドレインの一方が配線BL1iに接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続された構成となっている。また、各セル4i(i=1,2,3)においては、第2メモリトランジスタ10Bのソース/ドレインの一方が配線BL2iに接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続された構成となっている。すなわち、配線WLは、各セル4i(i=1,2,3)に対して共通の配線となっている。また、各セル4i(i=1,2,3)においては、パストランジスタ20のゲート電極が配線30に接続され、ソース/ドレインの一方が入力信号線INiに接続され、ソース/ドレインの他方が出力信号線OUT1に接続された構成となっている。したがって。第2実施形態のMUX1は、3つの入力信号線IN1、IN2、IN3に入力された3つの入力信号のうち、予めプログラムされた1つを選択して出力信号線OUT1に出力する構成となっている。第2実施形態のMUX1は不揮発性FPGAの基本回路の一つである。

【0044】

次に、第2実施形態のMUX1の動作、即ち、初期化、書込選択、MUX動作(FPGA動作)について図11乃至図13を参照して説明する。この説明の例では、入力信号線IN1の入力が選択されて出力信号線OUT1から出力され、入力信号線IN2、IN3の入力は遮断されるようにMUX1をプログラムする。即ち、セル41においてはパストランジスタ20がONとなるように、セル42、43においてはパストランジスタ20がOFFとなるようにプログラムする。

【0045】

初期化動作を図11に示す。配線WLには第2書込電圧Vprg2(−18V)を印加し、配線BL1i(i=1,2,3)、BL2i(i=1,2,3)には0Vを印加する。この結果、すべてのセル41、42、43の第1メモリトランジスタ10Aの閾値は低く(“0”状態)なり、すべてのセル41、42、43の第2メモリトランジスタ10Bの閾値は高く(“1”状態)なる。

【0046】

選択書込動作を図12に示す。配線WLには第1書込電圧Vprg1(+18V)を印加し、選択セルであるセル41の配線BL11、BL21には0Vを印加し、非選択セルであるセル42、43の配線BL12、BL22、BL13、BL23には書込阻止電圧Vinhibitを印加する。第2実施形態においては、書込阻止電圧Vinhibitは例えば6Vである。この結果、セル41の第1メモリトランジスタ10Aの閾値は高くなり(“1”状態)、セル41の第2メモリトランジスタ10Bの閾値は低くなる(“0”状態)。選択セル41のチャネルとゲート電極との間の印加電圧は18Vであるのに対して、非選択セル42、43のチャネルとゲート電極間の印加電圧は12Vと低い。このため、非選択セル42、43においてFN電流注入による書込は起こらない。

【0047】

MUX動作(FPGA動作)を図13に示す。各セル4i(i=1,2,3)の第1メモリトランジスタ10Aが接続される配線BL1iにはVss(0V)を、第2メモリトランジスタ10Bが接続される配線BL2iにはVdd(例えば、2V)を印加する。配線WLには読出電圧Vread(例えば、2V)を印加する。図5に示すように、ゲートにVread(2V)を印加された第1メモリトランジスタ10Aが低閾値状態(“0”状態)にあるならばソース/ドレイン間の抵抗が低くなり、第1メモリトランジスタ10Aは入力された信号を通過させる。一方、第1メモリトランジスタ10Aが高閾値状態(“1”状態)にあるならばソース/ドレイン間の抵抗が高くなり、第1メモリトランジスタ10Aは入力された信号を遮断する。同様に図8に示すように、ゲートにVread(2V)を印加された第2メモリトランジスタ10Bが低閾値状態(“0”状態)にあるならばソース/ドレイン間の抵抗が低くなり、第2メモリトランジスタ10Bは入力された信号を通過させる。一方、第2メモリトランジスタ10Bが高閾値状態(“1”状態)にあるならばソース/ドレイン間の抵抗が高くなり、第2メモリトランジスタ10Bは入力された信号を遮断する。セル41のパストランジスタ20のゲートには低閾値状態にある第2メモリトランジスタ10Bを経由してVddが印加され、パストランジスタ20はON状態となる。一方、セル42、43のパストランジスタ20のゲート電極には低閾値状態にある第1メモリトランジスタ10Aを経由してVss(0V)が印加され、パストランジスタ20はOFF状態となる。IN1に入力された信号はセル41のパストランジスタを経由してOUT1に出力される。一方、入力信号線IN2、IN3に入力された信号はセル42、43のパストランジスタ20によってそれぞれ遮断される。

【0048】

上述したように、第2実施形態においては、書込電圧の印加時に閾値のシフト方向が異なるメモリトランジスタ10A、10Bのペアと、パストランジスタ20とを組み合わせたセル構造を有しているので、FN電流による書込が可能であり、且つ共通の配線WLにより各セルのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0049】

さらに加えて、第2実施形態によれば、選択書込回数を大幅に減少することができる。この第2実施形態のMUXをFPGAに用いれば、FPGAの書込時間を、大幅に減少することができる。n入力1出力のMUXをプログラミングするのに必要な選択書込回数は、第1実施形態の不揮発性プログマブルスイッチをMUXに用いた場合は1回である。一方、従来の不揮発性プログラマブルスイッチをMUXに用いた場合はN回必要となる。ここでは、第1および第2メモリトランジスタの閾値状態を、(0/0)、(0/1)、(1/0)、(1/1)で表す。例えば、状態(0/1)は、第1メモリトランジスタの閾値が“0”状態で、第2メモリトランジスタの閾値が“1”状態であることを意味する。

【0050】

第2実施形態のMUXでは、初期化において共通の配線WLには第2書込電圧Vprg2(−18V)を印加することによって、すべてのセル41、42、43は状態(0/1)に一括でプログラミングされる。これはすべてのパストランジスタ30がMUX動作(FPGA動作)時にOFFする状態である。選択書込動作においては1つの選択セルのみを状態(1/0)になるよう書込を実施すればよい。この結果、選択セルのパストランジスタ30のみがONする。

【0051】

一方、従来の不揮発性プログラマブルスイッチは初期化(消去動作)においてすべての不揮発性プログラマブルスイッチは(0/0)にリセットされる。状態(0/0)はパストランジスタの状態が不定になり、不揮発性プログラマブルスイッチの動作時には使用しない。選択書込動作においてはすべてのセルに対して書込動作を行い、状態(1/0)か状態(0/1)を書込む必要がある。

【0052】

即ち、第2実施形態のMUXでは、セル内の不揮発性メモリトランジスタペアの状態が(0/1)と(1/0)のみであり、状態(0/0)と状態(1/1)が不要である点に着眼し、書込電圧の印加時に閾値のシフト方向が異なる不揮発性メモリトランジスタのペアを組み合わせることにより、FPGAの書込時間を大幅に短縮することも可能にしている。

【0053】

(第3実施形態)

図14に第3実施形態による不揮発性プログラマブルスイッチ(以下、スイッチまたはセルともいう)を示す。この第3実施形態のセル4Bは、図9に示す第1実施形態による第1具体例のセル4Aにおいて、第2メモリトランジスタとして、nチャネルメモリトランジスタ10bをpチャネルメモリトランジスタ10cに置き換えた構成となっている。

【0054】

このメモリトランジスタ10cの構成を図15(a)に示す。図15(a)に示すように、このメモリトランジスタ10cは、n型半導体領域(例えばnウェル)101cに形成されたpチャネルトランジスタであって、nウェル101cに離間して形成されたp型のソース/ドレイン102cと、ソース/ドレイン102c間のnウェル101cの領域(チャネル)上に形成されたゲート構造110cとを備えている。なお、n型半導体領域としてはnウェルの他にn型半導体基板とすることができる。ゲート構造110cは、絶縁膜111cと、電荷蓄積膜112cと、絶縁膜113cと、ゲート電極114cとがこの順序で積層された構造を有している。ソース/ドレイン102cの一方が図14に示す配線BL2に接続され、他方が配線30に接続される。また、ゲート電極114cが配線WLに接続される。そして、絶縁膜111cの膜厚が絶縁膜113cの膜厚よりも薄いか、もしくは絶縁膜111cの平均比誘電率が絶縁膜113cの平均比誘電率よりも小さくなるように構成されている。また、このメモリトランジスタ10cは、本明細書では、図15(b)に示す記号で表す。

【0055】

メモリトランジスタ10cでは例えば、絶縁膜111cはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層構造とし、電荷蓄積膜112cはSiN(5nm)とし、絶縁膜113cはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とする。すなわち、絶縁膜111cの膜厚は6nm、絶縁膜113cの膜厚は10.5nmとなり、絶縁膜111cの膜厚は絶縁膜113cの膜厚よりも薄い。また、SiO2の比誘電率が3.9で、SiNの比誘電率が8であるので、絶縁膜111cの平均比誘電率は4.26、絶縁膜113cの平均比誘電率は4.70となる。すなわち、絶縁膜111cの平均比誘電率は絶縁膜113cの平均比誘電率よりも小さい。

【0056】

なお、メモリトランジスタ10cは、電荷蓄積膜112cが電荷をトラップするトラップ絶縁膜であるMONOS型不揮発性メモリトランジスタであった。このトラップ絶縁膜の代わりに、ポリシリコン、もしくはn型不純物がドープされたポリシリコン、もしくはp型不純物がドープされたポリシリコンを用いても良い。この場合、メモリトランジスタ10cは、フローティングゲート型の不揮発性メモリトランジスタとなる。また、電荷蓄積膜112cは、ポリシリコンとSiN膜との積層構造であっても良い。更に、電荷蓄積膜112cは、メタルもしくは半導体からなる微粒子(ドット)を含有する層を有していても良い。

【0057】

また、メモリトランジスタ10cにおいては、絶縁膜113cは、SiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造を有していた。この積層構造の代わりに、比誘電率の高い材料で構成しても良い。この比誘電率の高い材料としては、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOなどを使用できる。

【0058】

また、メモリトランジスタ10cにおいては、絶縁膜113cは電子の通過をブロックする性能(ブロック性能)が重要である。このため、第1実施形態と同様に、低χ材料層/高χ材料層/低χ材料層の積層膜を用いてもよい。また、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOを、SiO2もしくはSiNで挟み込んだ積層構造を使用しても良い。

【0059】

図16(a)、16(b)にメモリトランジスタ10cの書込電圧を示す。メモリトランジスタ10cにおいて、例えば第1書込電圧Vprg1を+18V、第2書込電圧Vprg2を−18Vとする。このメモリトランジスタ10cにおいて、図16(a)に示すように、ソース/ドレイン102cおよびnウェル101cに印加する電圧を0Vとし、ゲート電極114cに第1書込電圧Vprg1(+18V)を印加した場合、チャネルの電子は絶縁膜111cをトンネル現象により通過し電荷蓄積膜112cに注入され、電荷蓄積膜112cでトラップされ蓄積される。絶縁膜113cの平均比誘電率は絶縁膜111cの平均比誘電率よりも大きいので、電荷蓄積膜112cからゲート電極114cへの電子の移動は起こらない。電荷蓄積膜112cに蓄えられた負電荷(電子)はpチャネルメモリトランジスタ10cの閾値電圧(Vth)を正方向にシフトさせる。これはpチャネルメモリトランジスタ10cの閾値電圧を低下させることに相当する。この低閾値は例えば+2Vである。なお、pチャネルメモリトランジスタ10cにおいては、閾値Vthが負の場合はその絶対値が大きいほど、もしくは閾値Vthが正の場合はその絶対値が小さいほど閾値が高いと表現する。逆に、pチャネルメモリトランジスタ10cにおいては、閾値Vthが負の場合はその絶対値が小さいほど、もしくは閾値Vthが正の場合はその絶対値が大きいほど閾値が低いと表現する。

【0060】

次に、図16(b)に示すように、メモリトランジスタ10cが低閾値状態であるときに、ソース/ドレイン102cおよびnウェル101cに印加する電圧を0Vとし、ゲート電極114cに第2書込電圧Vprg2(−18V)を印加した場合、電荷蓄積膜112cに蓄えられた電子は絶縁膜111cをトンネル現象により通過しチャネルへ放出される。絶縁膜113cの平均比誘電率は絶縁膜111cの平均比誘電率よりも大きいので、ゲート電極114cから電荷蓄積膜112cへの電子の移動は起こらない。メモリトランジスタ10cにおいては、閾値は元の高閾値に戻る。この高閾値は例えば−2Vである。もし、電荷蓄積膜111cに電荷が蓄えられていない状態(高閾値状態)で、メモリトランジスタ10cに第2書込電圧Vprg2を印加した場合は、電荷の移動は起こらず高閾値状態が保持される。

【0061】

図17に、メモリトランジスタ10cが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性をそれぞれ示す。

【0062】

図14に示す第3実施形態のセル4Bにおいては、配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流の書込により、nチャネルメモリトランジスタ10aの閾値電圧を増加させ、pチャネルメモリトランジスタ10cの閾値電圧を低下させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、nチャネルメモリトランジスタ10aの閾値電圧を低下させ、pチャネルメモリトランジスタ10cの閾値電圧を増大させることができる。すなわち、セル4Bの読出動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの一方がON状態となり、他方がOFF状態となる。また、書込動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができる。

【0063】

(第1変形例)

第3実施形態の第1変形例によるセル4Cを図18に示す。この第1変形例によるセル4Cは、図14に示す第3実施形態のセル4Bにおいて、nチャネルメモリトランジスタ10aの電荷蓄積膜112aと、pチャネルメモリトランジスタ10cの電荷蓄積膜112cとを接続した構成となっている。例えば、nチャネルメモリトランジスタ10aの電荷蓄積膜112aと、pチャネルメモリトランジスタ10cの電荷蓄積膜112cとを共有化した構成となっている。第1変形例によるセル4Cにおいては、例えばSiNからなる電荷蓄積膜を、nチャネルメモリトランジスタ10aの電荷蓄積膜112aと、pチャネルメモリトランジスタ10cの電荷蓄積膜112cに分離する加工が必ずしも必要でなくなり、このことは、特に微細なセルの作成を容易にする。

【0064】

この第1変形例のセル4Cにおいては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cはともに、MONOS型のメモリトランジスタとなる。この第1変形例のセルCにおいても、図14に示す第3実施形態のセル4Bと同様に、セル4Cの動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの一方がON状態となり、他方がOFF状態となる。また、書込動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができる。

【0065】

これに対して、比較例のセルとして、第1変形例にセル4Cにおいて、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cをFG型のメモリトランジスタとしたものを形成する。この比較例のセルにおいては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができない。すなわち、一方のメモリトランジスタの閾値を変化させれば、他方のメモリトランジスタの閾値も従属して変化する。したがって、この比較例のセルにおいては、書込動作時に、一方のメモリトランジスタがONとなり、他方のメモリトランジスタがOFFとなるような読み出し電圧Vreadを設定できない場合がある。

【0066】

この比較例のセルにおいて、共通にされたFG(電荷蓄積膜)をnチャネルメモリトランジスタと、pチャネルメモリトランジスタで分離する加工を施せば、チャネル不純物とゲート電極の不純物濃度の調整によりΔVthの独立制御が可能となる。しかしこの場合、FG(電荷蓄積膜)が厚いために分離加工する際の加工マージンが必要となる。即ち、必要なセル面積が大きくなる。FG型メモリトランジスタのトンネル膜、電荷蓄積膜(FG)、ブロック膜の典型的な厚さの一例は、7nm、90nm、9nmであり、合計して116nmの厚さがある。

【0067】

第3実施形態およびその第1変形例のセル4B、4Cで使用するMONOS型メモリトランジスタの場合、SiNの電荷蓄積膜の厚さが薄いため分離加工する場合の加工マージンが小さい。MONOS型メモリトランジスタのトンネル膜、電荷蓄積膜、ブロック膜の厚さは、第3実施形態のセルにおいては、従えば、6nm、5nm、10.5nmであり、合計して、21.5nmである。

【0068】

また、MONOS型メモリトランジスタの場合、第1変形例のようにnチャネルメモリトランジスタとpチャネルメモリトランジスタで、SiNの電荷蓄積膜を共有する場合でもΔVthの独立制御が可能となる。これは、比較例のようにFGに注入された電子は可動(mobile)キャリアとなり、FG中の電位が均一になるように再配置するのに対して、SiNの電荷蓄積膜に注入されトラップされた電子は不動(immobile)化/局在化するためである。SiNの電荷蓄積膜を共有すれば分離加工のプロセスコストや、分離加工のための大きなセル面積も必要なく、nチャネルメモリトランジスタとpチャネルメモリトランジスタでΔVthの独立制御が可能になる。

【0069】

第3実施形態の第1変形例のセル4Cに用いられるMONOS型メモリトランジスタの電荷蓄積膜がSiNで構成される場合を考える。この場合、電荷蓄積膜を構成するSiNx膜の組成xは、0.67<x≦1.33の範囲にあることが望ましい。SiNx膜の化学量論的組成はSi3N4であり、その場合のSiに対するNのモル比はx=1.33となる。x<1.33のSiNx膜は、Siの組成比が大きいSiリッチな組成となり、Siの未結合手に由来する電子トラップ量が増大する。このため、より大きなΔVthを実現できる。x=0.67は平均的に、Siの4つの結合手の内2つが未結合手となるが、隣接Siと共有結合を形成する組成に相当する。この場合、共有結合が大量に存在することになり、トラップされた電子が広範囲に拡散するようになる。この場合、nチャネルメモリトランジスタとpチャネルメモリトランジスタでΔVthの独立制御が難しくなる。

【0070】

第2実施形態のMUXを構成するセル4として、第1実施形態の第1具体例のセル4A、第3実施形態およびその第1変形例によるセル4B、4Cを用いてMUXを構成しても、第2実施形態のMUXと同じ手続きで初期化、選択書込、FPGA動作が可能である。例えば、第3実施形態のセル4Bを用いた場合、FPGA動作においては、配線WLに読出電圧Vread(+2V)を印加すると、第1メモリトランジスタであるnチャネルメモリトランジスタ10aのソース−ゲート電圧Vgsは、Vgs=Vread−Vssであるから、Vgs=+2Vとなる。ここで、Vssはソースに印加される電圧でVss=0Vである(図13参照)。一方、第2メモリトランジスタであるpチャネルメモリトランジスタ10cのソース−ゲート電圧VgsはVgs=Vread−Vddであるから、Vgs=0Vとなる。ここで、Vddはpチャネルメモリトランジスタ10cのソースに印加される電圧(例えば、+2V(図13参照))である。したがって、図8と図17を参照すれば明らかなように、nチャネルメモリトランジスタ10aとpチャネルメモリトランジスタ10cはともに閾値が低い/高いに応じてON/OFF状態が決定される。

【0071】

第1実施形態の第1具体例のセル4Aに対して第3実施形態およびその第1変形例のセル4B、4Cは次の2つの利点を有している。第1の利点は、第3実施形態では、第1メモリトランジスタ10aと第2メモリトランジスタ10cのゲート積層構造を共通にすることが可能であり、ゲート部の作成工程数を低減させることができる。第2の利点は、第3実施形態では、FPGA動作においてVssを転送する第1メモリトランジスタとしてnチャネルメモリトランジスタ10aを使用し、一方、Vddを転送する第2メモリトランジスタにpチャネルメモリトランジスタ10cを使用することができる。一般に、Vssを転送するにはnチャネルメモリトランジスタが有利であり、一方Vddを転送するにはpチャネルメモリトランジスタが有利である。これは、nチャネルメモリトランジスタを使用してVddを転送する場合、閾値電圧分の電圧降下を伴うからである。

【0072】

以上説明したように、第3実施形態およびその第1変形例によれば、第1実施形態と同様に、FN電流による書込が可能であり、且つ共通の配線WLにより2つのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0073】

(第4実施形態)

図19に第4実施形態による不揮発性プログラマブルスイッチ(以下、セル4Dともいう)を示す。この第4実施形態のセル4Dは、図14に示す第3実施形態のセル4Bにおいて、第1メモリトランジスタとしてnチャネルメモリトランジスタ10aを図6(a)に示すnチャネルメモリトランジスタ10bに置き換えるとともに、第2メモリトランジスタとしてpチャネルメモリトランジスタ10cをpチャネルメモリトランジスタ10dに置き換えた構成となっている。

【0074】

このセル4Dにおいては、nチャネルメモリトランジスタ10dは、ソース/ドレインの一方が配線BL1に接続され、他方が配線30に接続され、ゲート電極が配線WLに接続される。

【0075】

pチャネルメモリトランジスタ10dの構成を図20(a)に示す。図20(a)に示すように、このメモリトランジスタ10dは、n型半導体領域(例えばnウェル)101dに形成されたpチャネルトランジスタであって、nウェル101dに離間して形成されたp型のソース/ドレイン102dと、ソース/ドレイン102d間のnウェル101dの領域(チャネル)上に形成されたゲート構造110dとを備えている。なお、n型半導体領域としてはnウェルの他にn型半導体基板とすることができる。ゲート構造110dは、絶縁膜111dと、電荷蓄積膜112dと、絶縁膜113dと、ゲート電極114dとがこの順序で積層された構造を有している。ソース/ドレイン102dの一方が図19に示す配線BL2に接続され、他方が配線30に接続される。また、ゲート電極114dが配線WLに接続される。そして、絶縁膜111dの膜厚が絶縁膜113dの膜厚よりも厚いか、もしくは絶縁膜111dの平均比誘電率が絶縁膜113cの平均比誘電率よりも大きくなるように構成されている。また、このメモリトランジスタ10dは、本明細書では、図20(b)に示す記号で表す。

【0076】

メモリトランジスタ10dでは例えば、絶縁膜111dはSiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造とし、電荷蓄積膜112dはSiN(5nm)とし、絶縁膜113dはSiO2(2.5nm)/SiN(1nm)/SiO2(2.5nm)の積層とする。すなわち、絶縁膜111dの膜厚は10.5nm、絶縁膜113dの膜厚は6nmとなり、絶縁膜111dの膜厚は絶縁膜113dの膜厚よりも厚い。また、SiO2の比誘電率が3.9で、SiNの比誘電率が8であるので、絶縁膜111dの平均比誘電率は4.70、絶縁膜113dの平均比誘電率は4.26となる。すなわち、絶縁膜111dの平均比誘電率は絶縁膜113dの平均比誘電率よりも大きい。

【0077】

なお、メモリトランジスタ10dは、電荷蓄積膜112dが電荷をトラップするトラップ絶縁膜であるMONOS型不揮発性メモリトランジスタであった。このトラップ絶縁膜の代わりに、ポリシリコン、もしくはn型不純物がドープされたポリシリコン、もしくはp型不純物がドープされたポリシリコンを用いても良い。この場合、メモリトランジスタ10dは、フローティングゲート型の不揮発性メモリトランジスタとなる。また、電荷蓄積膜112dは、ポリシリコンとSiN膜との積層構造であっても良い。更に、電荷蓄積膜112dは、メタルもしくは半導体からなる微粒子(ドット)を含有する層を有していても良い。

【0078】

また、メモリトランジスタ10dにおいては、絶縁膜111dは、SiO2(3.5nm)/SiN(3.5nm)/SiO2(3.5nm)の積層構造を有していた。この積層構造の代わりに、比誘電率の高い材料で構成しても良い。この比誘電率の高い材料としては、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOなどを使用できる。

【0079】

また、メモリトランジスタ10dにおいては、絶縁膜111dは電子の通過をブロックする性能(ブロック性能)が重要である。このため、第1実施形態と同様に、低χ材料層/高χ材料層/低χ材料層の積層膜を用いてもよい。また、Hf酸化物、Zr酸化物、Ta酸化物、Ti酸化物、La酸化物、Al酸化物および、それらの混合物、LaAlOを、SiO2もしくはSiNで挟み込んだ積層構造を使用しても良い。

【0080】

図21(a)、21(b)にメモリトランジスタ10dの書込電圧を示す。メモリトランジスタ10dにおいて、図21(a)に示すように、ソース/ドレイン102dおよびnウェル101dに印加する電圧を0Vとし、ゲート電極114dに第2書込電圧Vprg2(−18V)を印加した場合、ゲート電極114dの電子は絶縁膜113dをトンネル現象により通過し電荷蓄積膜112dに注入され、電荷蓄積膜112dでトラップされて蓄積される。絶縁膜111dの平均比誘電率は絶縁膜113dの平均比誘電率よりも大きいので、電荷蓄積膜112dからチャネルへの電子の移動は起こらない。電荷蓄積膜112dに蓄えられた負電荷はpチャネルメモリトランジスタ10dの閾値電圧(Vth)を低下させ、低閾値となる。この低閾値は例えば+2Vである。

【0081】

次に、図21(b)に示すように、メモリトランジスタ10dが低閾値状態であるときに、ソース/ドレイン102dおよびnウェル101dに印加する電圧を0Vとし、ゲート電極114dに第1書込電圧Vprg1(+18V)を印加した場合、電荷蓄積膜112dに蓄えられた負電荷(電子)は絶縁膜113dをトンネル現象により通過し、ゲート電極114dへ放出される。絶縁膜111dの平均比誘電率は絶縁膜113dの平均比誘電率よりも大きいので、チャネルから電荷蓄積膜112dへの電子の移動は起こらない。電荷蓄積膜112dは元の中性状態に戻るので、pチャネルメモリトランジスタ10dの閾値は元の高閾値に戻る。この高閾値は例えば−2Vである。もし、電荷蓄積膜112dに電荷が蓄えられていない状態(高閾値状態)で、メモリトランジスタ10dに第1書込電圧Vprg1を印加した場合は、電荷の移動は起こらず高閾値状態が保持される。

【0082】

図22に、メモリトランジスタ10dが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性を示す。

【0083】

図19に示す第4実施形態のセル4Dにおいては、配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流の書込により、nチャネルメモリトランジスタ10bの閾値電圧を低下させ、pチャネルメモリトランジスタ10dの閾値電圧を増大させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、nチャネルメモリトランジスタ10bの閾値電圧を増大させ、pチャネルメモリトランジスタ10dの閾値電圧を低下させることができる。

【0084】

(第1変形例)

次に、第4実施形態の第1変形例によるセル4Eを図23に示す。このセル4Eは、図19に示す第4実施形態のセル4Dにおいて、nチャネルメモリトランジスタ10bの電荷蓄積膜112bと、pチャネルメモリトランジスタ10dの電荷蓄積膜112dを接続した構成となっている。例えば、nチャネルメモリトランジスタ10bとpチャネルメモリトランジスタ10dが一つの電荷蓄積膜を共有してもよい。この第1変形例によるセル4Eにおいては、電荷蓄積膜を分離する加工が必ずしも必要では無い。これは、特に微細なセルの作成を容易にする。

【0085】

この第1変形例のセル4Eにおいては、nチャネルメモリトランジスタ10bおよびpチャネルメモリトランジスタ10dはともに、MONOS型のメモリトランジスタとなる。この第1変形例のセルEにおいても、図14に示す第3実施形態のセル4Bと同様に、セル4Eの動作時においては、nチャネルメモリトランジスタ10bおよびpチャネルメモリトランジスタ10dの一方がON状態となり、他方がOFF状態となる。また、書込動作時においては、nチャネルメモリトランジスタ10aおよびpチャネルメモリトランジスタ10cの閾値の変化量ΔVthを独立に制御することができる。

【0086】

第4実施形態またはその変形例によるセル4D、4Eを、第2実施形態のMUXを構成するセルとして用いることができる。この場合、次の点を除いて、第2実施形態と同じ手続きで初期化、選択書込、FPGA動作が可能である。第4実施形態または変形例によるセル4D、4Eを用いた場合には、初期化の際には配線WLに第1書込電圧Vprg1(+18V)を印加し、選択書込の際には配線WLに第2書込電圧Vprg2(−18V)を印加する。

【0087】

第1実施形態に対する第4実施形態の利点は、既に述べた第1実施形態に対する第3実施形態の利点と同じである。第3実施形態に対する第4実施形態の利点は、p型トランジスタのΔVthがチャネルと電荷蓄積膜の間の電子授受によるのではなく、ゲート電極と電荷蓄積膜との間の電子授受によることにより、電荷の注入効率が高くなる場合があることである。

【0088】

以上説明したように、第4実施形態およびその第1変形例によれば、第1実施形態と同様に、FN電流による書込が可能であり、且つ共通の配線WLにより2つのメモリトランジスタが駆動されるため、セル面積を小さくすることができる。

【0089】

(第5実施形態)

図24に、第5実施形態による不揮発性プログラマブルスイッチ(以下、セル4Fともいう)を示す。この第5実施形態によるセル4Fは、図9に示す第1実施形態の第1具体例のセル4Aにおいて、nチャネルメモリトランジスタ10a、10bをnチャネルメモリトランジスタ10e、10fにそれぞれ置き換えた構成となっている。メモリトランジスタ10eは、ソース/ドレインの一方が配線BL1に接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続される。また、メモリトランジスタ10fは、ソース/ドレインの一方が配線BL2に接続され、ソース/ドレインの他方が配線30に接続され、ゲート電極が配線WLに接続される。

【0090】

nチャネルメモリトランジスタ10eの構成を図25(a)、25(b)に示す。図25(a)はゲート長方向(ソースからドレインに向かう方向)の断面図であり、図25(b)はゲート長方向に直交する方向の断面図である。このメモリトランジスタ10eは、図25(a)に示すように、p型半導体領域(例えばpウェル)101eに形成されたnチャネルトランジスタであって、pウェル101eに離間して形成されたn型のソース/ドレイン102eと、ソース/ドレイン102e間のpウェル101eの領域(チャネル)上に形成されたゲート構造110eとを備えている。なお、p型半導体領域としてはpウェルの他にp型半導体基板とすることができる。ゲート構造110eは、絶縁膜(トンネル膜)111eと、電荷蓄積膜112eと、絶縁膜(ブロック膜)113eと、ゲート電極114eとがこの順序で積層された構造を有している。図25(b)に示すように、絶縁膜113eは電荷蓄積膜112eの上面と側面の一部を覆うように設けられ、ゲート電極114eは絶縁膜113eの上面および側面を覆うように設けられている。

【0091】

nチャネルメモリトランジスタ10fの構成を図26(a)、26(b)に示す。図26(a)はゲート長方向(ソースからドレインに向かう方向)の断面図であり、図26(b)はゲート長方向に直交する方向の断面図である。このメモリトランジスタ10fは、図26(a)に示すように、p型半導体領域(例えばpウェル)101fに形成されたnチャネルトランジスタであって、pウェル101fに離間して形成されたn型のソース/ドレイン102fと、ソース/ドレイン102f間のpウェル101fの領域(チャネル)上に形成されたゲート構造110fとを備えている。なお、p型半導体領域としてはpウェルの他にp型半導体基板とすることができる。ゲート構造110fは、絶縁膜(トンネル膜)111fと、電荷蓄積膜112fと、絶縁膜(ブロック膜)113fと、ゲート電極114fとがこの順序で積層された構造を有している。図26(b)に示すように、絶縁膜113fは、電荷蓄積膜112fと接触する面積よりも、ゲート電極114fと接触する面積が大きくなるように設けられている。また、図26(b)に示すように、絶縁膜113fの下面の面積が電荷蓄積膜112fの上面の面積よりも大きく、絶縁膜113fの上面の面積は、ゲート電極114fの下面の面積以下となるように設けられている。なお、メモリトランジスタ10e、10fは、MONOS型不揮発性メモリトランジスタであっても、FG型不揮発性メモリトランジスタであってもよい。

【0092】

第5実施形態においては、メモリトランジスタ10eの電荷蓄積膜112eに対する絶縁膜113eを挟んで対向するゲート電極114eの対向面積(重なり合う面積)が、メモリトランジスタ10fの電荷蓄積膜112fに対する絶縁膜113fを挟んで対向するゲート電極114fの対向面積(重なり合う面積)よりも大きくなるように構成されている。電荷蓄積膜に対するゲート電極の対向面積の違いは、ゲート電極に電圧を印加した場合のウェル(基板)から見た電荷蓄積膜の電位の違いを生じ、対向面積が大きいほど、電荷蓄積膜の電位が高くなる。具体的には、ゲート電極に印加する電圧をVcg、電荷蓄積膜の電位をVct、電荷蓄積膜とウェルとの容量をC1、ゲート電極と電荷蓄積膜との間の容量をC2とすると、

Vcg=(C2/(C1+C2))×Vct

の関係がある。したがって、上述した対向面積はその間の容量C2に関わる。ここでC2/(C1+C2)はカップリング比(Coupling Ratio)と呼称される。カップリング比が異なれば、同じ電圧をゲート電極に印加した場合にも、メモリ動作は異なるものとなる。ここで、絶縁膜を挟んで対向する2つの電極の対向面積をS、上記絶縁膜の厚さをt、上記絶縁膜の誘電率をεとすると、容量Cは

C=(S/t)×ε

となる。この場合、図25(b)示す構成においては、容量C1に関する対向面積は、容量C2に関する対向面積よりも小さいため、容量C2が大きく、すなわち絶縁膜111eを介した電荷のやり取りを促進させることができる。

【0093】

一方、図26(b)に示す構成においては、図25(b)に示す構成に比べ、容量C1と容量C2との間に対向面積Sの差を生じさせにくい。この場合、電荷のやり取りを促進させるためには、絶縁膜の厚さtを変える必要がある。このため、図26(b)に示す構成においては、絶縁膜113fを介した電荷のやり取りを促進させるためには、絶縁膜111fよりも絶縁膜113fを薄くする必要がある。

【0094】

図27(a)、27(b)に、メモリトランジスタ10eの書込電圧を示す。第5実施形態では、例えば第1書込電圧Vprg1を+18V、第2書込電圧Vprg2を−18Vとする。図27(a)に示すように、メモリトランジスタ10eのソース/ドレイン102eおよびpウェル101eに印加する電圧を0Vとし、ゲート電極114eに第1書込電圧Vprg1(+18V)を印加した場合、チャネルの電子は絶縁膜111eをトンネル現象(FNトンネル電流)により通過して電荷蓄積膜112eに注入される。注入された電子は電荷蓄積膜112eでトラップされ、蓄積される。このとき、メモリトランジスタ10eにおいては、電荷蓄積膜112eに対するゲート電極114eの対向面積が、電荷蓄積膜112eに対するチャネルの対向面積よりも大きいため、電荷蓄積膜112eから絶縁膜113eを介してゲート電極114eへの電子の流出量はチャネルから電荷蓄積膜112eへの注入量に比べて少ない。

【0095】

電荷蓄積膜112eに蓄えられた負電荷(電子)はnチャネルメモリトランジスタ10eの閾値電圧(Vth)を上昇させ、高閾値となる。この高閾値は例えば4Vである。

【0096】

次に、メモリトランジスタ10eが高閾値状態にあるときに、メモリトランジスタ10eのソース/ドレイン102eおよびpウェル101eに印加する電圧を0Vとし、ゲート電極114eに第2書込電圧Vprg2(−18V)を印加した場合、電荷蓄積膜112eに蓄えられた電子は絶縁膜111eをトンネル現象により通過しチャネルへ放出される。このとき、メモリトランジスタ10eにおいては、電荷蓄積膜112eに対するゲート電極の対向面積が、電荷蓄積膜112eに対するチャネルの対向面積よりも大きいため、ゲート電極114eから電荷蓄積膜112eへの電子の注入量は電荷蓄積膜112eからチャネルへの流出量に比べて少ない。これにより、電荷蓄積膜112eは元の中性状態に戻るのでメモリトランジスタ10eの閾値は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112eに電荷が蓄えられていない状態(低閾値状態)で、メモリトランジスタ10eに第2書込電圧Vprg2を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0097】

図28に、メモリトランジスタ10eが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性を示す。

【0098】

図29(a)、29(b)に、メモリトランジスタ10fの書込電圧を示す。図29(a)に示すように、メモリトランジスタ10fにおいて、ソース/ドレイン102fおよびpウェル101fに印加する電圧を0Vとし、ゲート電極114fに第2書込電圧Vprg2(−18V)を印加した場合、ゲート電極114fの電子は絶縁膜113fをトンネル現象により通過し電荷蓄積膜112fに注入され、そこでトラップされ蓄積される。このとき、メモリトランジスタ10fにおいては、電荷蓄積膜112fに対するゲート電極114fの対向面積が、電荷蓄積膜112fに対するチャネルの対向面積よりも小さいため、電荷蓄積膜112fからチャネルへの電子の流出量はゲート電極114fからの注入量に比べて少ない。電荷蓄積膜112fに蓄えられた負電荷はnチャネルメモリトランジスタ10fの閾値電圧(Vth)を上昇させ高閾値となる。この高閾値は例えば4Vである。

【0099】

次に、メモリトランジスタ10fが高閾値状態にあるときに、図29(b)に示すように、ソース/ドレイン102fおよびpウェル101fに印加する電圧を0Vとし、ゲート電極114fに第1書込電圧Vprg1(+18V)を印加した場合、電荷蓄積膜112fに蓄えられた負電荷(電子)は絶縁膜113fをトンネル現象により通過し、ゲート電極114fへ放出される。このとき、メモリトランジスタ10fにおいては、電荷蓄積膜112fに対するゲート電極114fの対向面積が、電荷蓄積膜112fに対するゲーチャネルの対向面積よりも小さいため、チャネルから電荷蓄積膜112fへの電子の流入量は、電荷蓄積膜112fからゲート電極114fへの流出量に比べて少ない。これにより電荷蓄積膜112fは元の中性状態に戻るので閾値電圧は元の低閾値に戻る。この低閾値は例えば0Vである。もし、電荷蓄積膜112fに電荷が蓄えられていない状態(低閾値状態)で、メモリトランジスタ10fに第1書込電圧Vprg1を印加した場合は、電荷の移動は起こらず低閾値状態が保持される。

【0100】

図30に、メモリトランジスタ10fが高閾値状態と、低閾値状態にある場合におけるドレイン電流(Id)−ゲート電圧(Vgs)特性を示す。

【0101】

図24に示した第5実施形態におけるセル4Fの動作としては、例えば図4に示す第1実施形態の第1具体例のセル4Aと等価である。配線WLに第1書込電圧Vprg1(+18V)を印加すれば、FNトンネル電流の書込により、メモリトランジスタ10eの閾値電圧を増加させ、メモリトランジスタ10fの閾値電圧を低下させることができる。また、配線WLに第2書込電圧Vprg2(−18V)を印加すれば、メモリトランジスタ10eの閾値電圧を低下させ、メモリトランジスタ10fの閾値電圧を増大させることができる。

【0102】

次に、メモリトランジスタ10e、10fの製造方法を図31乃至図36(b)を参照して説明する。図31乃至図36(b)は、メモリトランジスタ10e、10fの製造方法を説明する断面図である。

【0103】

まず、図31に示すように、半導体基板のpウェル101の上に絶縁膜111を形成し、絶縁膜111上に電荷蓄積膜112を形成する。

【0104】

次いで、例えばPEP(Photo Engraving Process)によるパターニングの後、異方性ドライエッチングを施すことにより、電荷蓄積膜112、絶縁膜111、およびウェル101を分断加工する。これにより、ウェル101は、メモリトランジスタ10eの形成領域101eと、メモリトランジスタ10fの形成領域101fに分断される。そして、ウェル101e上には絶縁膜111e、および電荷蓄積膜112eが残置され、ウェル101f上には絶縁膜111f、および電荷蓄積膜112fが残置される。続いて、分断加工により電荷蓄積膜112、絶縁膜111、およびウェル領域101が除去された領域に、例えばシリコン酸化膜(SiO2)などの絶縁膜130を埋め込み、例えばCMP(Chemical Mechanical Polishing)を用いて平坦化処理を行う(図32(a)、32(b))。この時、必要であれば、例えばSiNなどのハードマスク135をPEP前に電荷蓄積膜112の上に堆積しても良い。この状態を図32(a)32(b)に示す。この直後および後に続く工程において、ハードマスク135は、例えばウェットエッチングを施すことにより除去される。

【0105】

次いで、例えばPEPによるパターニングの後、異方性ドライエッチングを施すことによりメモリトランジスタ10eの形成領域における埋め込み絶縁膜130を加工する。この状態を図33(a)、33(b)に示す。この時、メモリトランジスタ10fの形成領域における埋め込み絶縁膜130はパターニングにより保護されており、加工されない。

【0106】

次いで、例えば等方性ウェットエッチングを施すことにより、電荷蓄積膜112e、112fを加工する。その際、メモリトランジスタ10eの形成領域においては、埋め込み絶縁膜130が加工されているため、ウェル101eに垂直な方向だけでなく、ウェル101eに平行な方向へのサイドエッチングが入る。この状態を図34(a)、34(b)に示す。このとき、メモリトランジスタ10fの形成領域においては、ウェル101fに垂直な方向にのみエッチングされる。

【0107】

次いで、図35(a)、35(b)に示すように、縁膜113を形成した後、ゲート電極114を形成する。

【0108】

次いで、例えばPEPによるパターニングの後、異方性ドライエッチングを施すことにより図35(a)、35(b)の奥行き方向に対して垂直方向にゲート電極114、絶縁膜113と、電荷蓄積膜112e、112fと、絶縁膜111e、111fとを加工し、ゲート電極114をゲート電極114e、114fに分断するとともに、絶縁膜113を絶縁膜113e、113fに分断する。これにより、メモリトランジスタ10eと、メモリトランジスタ10fが形成される。なお、絶縁膜113は、必要に応じて分断しなくても良い。

【0109】

第1実施形態の第1具体例によるセル4A、第3実施形態のセル4B、および第4実施形態のセル4Eに対する第5実施形態のセル4Fの利点は、メモリトランジスタ10eおよびメモリトランジスタ10fの作り分けにおいて、標準的なプロセスに対してPEPを行う1工程のみを追加すれば良く、低コストで形成可能なことである。この場合、第5実施形態におけるメモリトランジスタ10eおよびメモリトランジスタ10fは第1実施形態、第3および第4実施形態に示すいずれの構造でも良い。また、第5実施形態のセルはメモリトランジスタ10fとして、nチャネルメモリトランジスタを用いて構成したが、例えばメモリトランジスタ10dとして説明したpチャネルメモリトランジスタを用いて構成した場合においても、図17に示したようにスイッチ動作は可能である。

【0110】

一方、メモリトランジスタ10eおよびメモリトランジスタ10fの両者を異なった構造とした場合、例えば、メモリトランジスタ10eとしてメモリトランジスタ10aと同構造、メモリトランジスタ10fとしてメモリトランジスタ10bと同構造とすることで、同一書込電圧に対する両者の動作の差が開く方向となり、図28および図30に示したスイッチ動作をより際立たせることが出来る。

【0111】

また、第5実施形態の特徴としては、メモリトランジスタ10eおよびメモリトランジスタ10fの両者で、電荷蓄積膜に対するゲート電極の接触面積が異なることが特徴であるので、図25(a)、25(b)および図26(a)、26(b)で示した構造でなくても良い。例えば、図33(a)、33(b)の状態から図34(a)、34(b)におけるエッチング処理を省略し、図35(a)、35(b)の成膜を行うことで形成される構造を図36(a)、36(b)に示す。この構造は、電荷蓄積膜に対するゲート電極の接触面積の両者間における差は、図25(a)、25(b)および図26(a)、26(b)で示した構造と比べると小さくなるが、エッチング工程を省略できる分、製造コストを抑えることができる。一方、図34(a)、34(b)で示したエッチングを行うことで、絶縁膜113および電極114を形成する祭、ウェル分断領域を介して隣接するセル間が狭くなった場合にも埋め込みを行うことができる。これにより隣接する電荷蓄積膜間が容量を持ってしまうような干渉効果を抑制することが可能となり、高集積化を進める上で有利となる。

【0112】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これらの実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0113】

1 MUX

4〜4F 不揮発性プログラマブルスイッチ(セル)

10A 第1不揮発性メモリトランジスタ(第1メモリトランジスタ)

10B 第2不揮発性メモリトランジスタ(第2メモリトランジスタ)

10a、10b nチャネルメモリトランジスタ

10c、10d pチャネルメモリトランジスタ

11a、11b 第1端子

12a、12b 第2端子

13a、13b 第3端子

20 パストランジスタ

30 配線

BL1 配線

BL2 配線

WL 配線

【特許請求の範囲】

【請求項1】

第1配線に接続される第1端子と、第2配線に接続される第2端子と、第3配線に接続される第3端子と、を有する第1不揮発性メモリトランジスタと、

第4配線に接続される第4端子と、前記第2配線に接続される第5端子と、前記第3配線に接続される第6端子と、を有し、前記第1不揮発性メモリトランジスタと同じ導電型の第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備え、

前記第1配線および前記第4配線が第1電源に接続され、前記第3配線が前記第1電源の電圧よりも高い電圧の第2電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が増加し、前記第2不揮発性メモリトランジスタの閾値電圧が低下し、

前記第1配線および前記第4配線が前記第1電源に接続され、前記第3配線が前記第1電源の電圧よりも低い電圧の第3電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が低下し、前記第2不揮発性メモリトランジスタの閾値電圧が増加すること、

を特徴とする不揮発性プログラマブルスイッチ。

【請求項2】

前記第1不揮発性メモリトランジスタは、半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも物理膜厚が厚い第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造を有し、前記第1ソース/ドレインの一方が前記第1端子であり、前記第1ソース/ドレインの他方が前記第2端子であり、前記第1ゲート電極が前記第3端子であり、

前記第2不揮発性メモリトランジスタは、前記半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも物理膜厚が薄い第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造を有し、前記第2ソース/ドレインの一方が前記第4端子であり、前記第2ソース/ドレインの他方が前記第5端子であり、前記第2ゲート電極が前記第6端子であること、

を特徴とする請求項1記載の不揮発性プログラマブルスイッチ。

【請求項3】

前記第1不揮発性メモリトランジスタは、半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも平均比誘電率が大きい第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造を有し、前記第1ソース/ドレインの一方が前記第1端子であり、前記第1ソース/ドレインの他方が前記第2端子であり、前記第1ゲート電極が前記第3端子であり、

前記第2不揮発性メモリトランジスタは、前記半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも平均比誘電率が小さい第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造を有し、前記第2ソース/ドレインの一方が前記第4端子であり、前記第2ソース/ドレインの他方が前記第5端子であり、前記第2ゲート電極が前記第6端子であること、

を特徴とする請求項1記載の不揮発性プログラマブルスイッチ。

【請求項4】

前記第2絶縁膜および前記第3絶縁膜は、第1材料層を、前記第1材料層よりも電子親和力の低い第2材料層で挟んだ積層構造を有していることを特徴とする請求項2または3に記載の不揮発性プログラマブルスイッチ。

【請求項5】

前記第1不揮発性メモリトランジスタは、半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記半導体領域上に、第1絶縁膜、第1電荷蓄積膜、第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造を有し、前記第1ソース/ドレインの一方が前記第1端子であり、前記第1ソース/ドレインの他方が前記第2端子であり、前記第1ゲート電極が前記第3端子であり、

前記第2不揮発性メモリトランジスタは、前記半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記半導体領域上に、第3絶縁膜、第2電荷蓄積膜、第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造を有し、前記第2ソース/ドレインの一方が前記第4端子であり、前記第2ソース/ドレインの他方が前記第5端子であり、前記第2ゲート電極が前記第6端子であり、

前記第1不揮発性メモリトランジスタにおいて第1電荷蓄積膜に対する第2絶縁膜を挟んで対向する第1ゲート電極の対向面積が、第2不揮発性メモリトランジスタにおいて第2電荷蓄積膜に対する第2絶縁膜を挟んで対向する第2ゲート電極の対向面積よりも大きいこと、

を特徴とする請求項1記載の不揮発性プログラマブルスイッチ。

【請求項6】

前記第2絶縁膜は前記第1電荷蓄積膜の上面および一部の側面を覆い、前記第1ゲート電極は前記第2絶縁膜の上面および側面を覆うことを特徴とする請求項5記載の不揮発性プログラマブルスイッチ。

【請求項7】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも物理膜厚が厚い第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも物理膜厚が厚い第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項8】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも平均比誘電率が大きい第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも平均比誘電率が大きい第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項9】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも物理膜厚が薄い第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも物理膜厚が薄い第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項10】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも平均比誘電率が小さい第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも平均比誘電率が小さい第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項11】

前記第1および第2電荷蓄積膜はトラップ絶縁膜であり、前記第1および第2電荷蓄積膜は接続されていることを特徴とする請求項7乃至10のいずれかに記載の不揮発性プログラマブルスイッチ。

【請求項12】

前記第1配線および前記第4配線が第1電源に接続され、前記第3配線が前記第1電源の電圧よりも高い電圧の第2電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が増加し、前記第2不揮発性メモリトランジスタの閾値電圧が低下し、

前記第1配線および前記第4配線が前記第1電源に接続され、前記第3配線が前記第1電源の電圧よりも低い電圧の第3電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が低下し、前記第2不揮発性メモリトランジスタの閾値電圧が増加すること、

を特徴とする請求項7乃至11のいずれかに記載の不揮発性プログラマブルスイッチ。

【請求項13】

前記第1配線および前記第4配線が前記第1電源の電圧よりも大きい電圧の前記第4電源に接続されているときに、前記第3配線が前記第2電源または第3電源に接続されても、前記第1および第2不揮発性メモリトランジスタの閾値電圧は変化しないことを特徴とする請求項1乃至12のいずれかに記載の不揮発性プログラマブルスイッチ。

【請求項1】

第1配線に接続される第1端子と、第2配線に接続される第2端子と、第3配線に接続される第3端子と、を有する第1不揮発性メモリトランジスタと、

第4配線に接続される第4端子と、前記第2配線に接続される第5端子と、前記第3配線に接続される第6端子と、を有し、前記第1不揮発性メモリトランジスタと同じ導電型の第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備え、

前記第1配線および前記第4配線が第1電源に接続され、前記第3配線が前記第1電源の電圧よりも高い電圧の第2電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が増加し、前記第2不揮発性メモリトランジスタの閾値電圧が低下し、

前記第1配線および前記第4配線が前記第1電源に接続され、前記第3配線が前記第1電源の電圧よりも低い電圧の第3電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が低下し、前記第2不揮発性メモリトランジスタの閾値電圧が増加すること、

を特徴とする不揮発性プログラマブルスイッチ。

【請求項2】

前記第1不揮発性メモリトランジスタは、半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも物理膜厚が厚い第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造を有し、前記第1ソース/ドレインの一方が前記第1端子であり、前記第1ソース/ドレインの他方が前記第2端子であり、前記第1ゲート電極が前記第3端子であり、

前記第2不揮発性メモリトランジスタは、前記半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも物理膜厚が薄い第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造を有し、前記第2ソース/ドレインの一方が前記第4端子であり、前記第2ソース/ドレインの他方が前記第5端子であり、前記第2ゲート電極が前記第6端子であること、

を特徴とする請求項1記載の不揮発性プログラマブルスイッチ。

【請求項3】

前記第1不揮発性メモリトランジスタは、半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも平均比誘電率が大きい第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造を有し、前記第1ソース/ドレインの一方が前記第1端子であり、前記第1ソース/ドレインの他方が前記第2端子であり、前記第1ゲート電極が前記第3端子であり、

前記第2不揮発性メモリトランジスタは、前記半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも平均比誘電率が小さい第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造を有し、前記第2ソース/ドレインの一方が前記第4端子であり、前記第2ソース/ドレインの他方が前記第5端子であり、前記第2ゲート電極が前記第6端子であること、

を特徴とする請求項1記載の不揮発性プログラマブルスイッチ。

【請求項4】

前記第2絶縁膜および前記第3絶縁膜は、第1材料層を、前記第1材料層よりも電子親和力の低い第2材料層で挟んだ積層構造を有していることを特徴とする請求項2または3に記載の不揮発性プログラマブルスイッチ。

【請求項5】

前記第1不揮発性メモリトランジスタは、半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記半導体領域上に、第1絶縁膜、第1電荷蓄積膜、第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造を有し、前記第1ソース/ドレインの一方が前記第1端子であり、前記第1ソース/ドレインの他方が前記第2端子であり、前記第1ゲート電極が前記第3端子であり、

前記第2不揮発性メモリトランジスタは、前記半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記半導体領域上に、第3絶縁膜、第2電荷蓄積膜、第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造を有し、前記第2ソース/ドレインの一方が前記第4端子であり、前記第2ソース/ドレインの他方が前記第5端子であり、前記第2ゲート電極が前記第6端子であり、

前記第1不揮発性メモリトランジスタにおいて第1電荷蓄積膜に対する第2絶縁膜を挟んで対向する第1ゲート電極の対向面積が、第2不揮発性メモリトランジスタにおいて第2電荷蓄積膜に対する第2絶縁膜を挟んで対向する第2ゲート電極の対向面積よりも大きいこと、

を特徴とする請求項1記載の不揮発性プログラマブルスイッチ。

【請求項6】

前記第2絶縁膜は前記第1電荷蓄積膜の上面および一部の側面を覆い、前記第1ゲート電極は前記第2絶縁膜の上面および側面を覆うことを特徴とする請求項5記載の不揮発性プログラマブルスイッチ。

【請求項7】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも物理膜厚が厚い第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも物理膜厚が厚い第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項8】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも平均比誘電率が大きい第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも平均比誘電率が大きい第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項9】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも物理膜厚が薄い第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも物理膜厚が薄い第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項10】

第1半導体領域に離間して形成された第1ソース/ドレインと、前記第1ソース/ドレイン間の前記第1半導体領域上に、第1絶縁膜、第1電荷蓄積膜、前記第1絶縁膜よりも平均比誘電率が小さい第2絶縁膜、および第1ゲート電極がこの順序で積層された第1ゲート構造と、を有し、前記第1ソース/ドレインの一方が第1配線に接続され、前記第1ソース/ドレインの他方が第2配線に接続され、前記第1ゲート電極が第3配線に接続される第1不揮発性メモリトランジスタと、

前記第1半導体領域と導電型が異なる第2半導体領域に離間して形成された第2ソース/ドレインと、前記第2ソース/ドレイン間の前記第2半導体領域上に、第3絶縁膜、第2電荷蓄積膜、前記第3絶縁膜よりも平均比誘電率が小さい第4絶縁膜、および第2ゲート電極がこの順序で積層された第2ゲート構造と、を有し、前記第2ソース/ドレインの一方が第4配線に接続され、前記第2ソース/ドレインの他方が前記第2配線に接続され、前記第2ゲート電極が前記第3配線に接続される第2不揮発性メモリトランジスタと、

前記第2配線にゲート電極が接続されたパストランジスタと、

を備えていることを特徴とする不揮発性プログラマブルスイッチ。

【請求項11】

前記第1および第2電荷蓄積膜はトラップ絶縁膜であり、前記第1および第2電荷蓄積膜は接続されていることを特徴とする請求項7乃至10のいずれかに記載の不揮発性プログラマブルスイッチ。

【請求項12】

前記第1配線および前記第4配線が第1電源に接続され、前記第3配線が前記第1電源の電圧よりも高い電圧の第2電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が増加し、前記第2不揮発性メモリトランジスタの閾値電圧が低下し、

前記第1配線および前記第4配線が前記第1電源に接続され、前記第3配線が前記第1電源の電圧よりも低い電圧の第3電源に接続されるときに前記第1不揮発性メモリトランジスタの閾値電圧が低下し、前記第2不揮発性メモリトランジスタの閾値電圧が増加すること、

を特徴とする請求項7乃至11のいずれかに記載の不揮発性プログラマブルスイッチ。

【請求項13】