不揮発性メモリおよび改善された部分的ページプログラミング機能を備えた制御処理

【課題】2以上のシーケンシャルなプログラミングパス時にメモリセルのプログラミングが行われるプログラミング方式において、メモリセルのうちの少なくともいくつかのメモリセルを第2のパス中にプログラムするのに不十分なホストデータしか存在しないとき、誤ったプログラミングが生じない方式を提供する。

【解決手段】プログラミング方式を変更することによって、誤ったプログラミングの防止が可能となる。第2のプログラミングパス中、誤ったしきい値電圧に合わせたプログラミングをこのメモリセルに行わせないようにするコード構成を選択することにより、エラーを含む状態に合わせたプログラミングをこのセルに行わせないようにする代替データに基づいてこのメモリセルのプログラミングを行う。

【解決手段】プログラミング方式を変更することによって、誤ったプログラミングの防止が可能となる。第2のプログラミングパス中、誤ったしきい値電圧に合わせたプログラミングをこのメモリセルに行わせないようにするコード構成を選択することにより、エラーを含む状態に合わせたプログラミングをこのセルに行わせないようにする代替データに基づいてこのメモリセルのプログラミングを行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に、電気的に消去可能でプログラム可能なリードオンリメモリ(EEPROM)およびフラッシュEEPROMのような不揮発性半導体メモリに関し、特に、改善された部分的ページプログラミング機能を備えた不揮発性半導体メモリに関する。

【背景技術】

【0002】

不揮発性の電荷蓄積能力を有する固体メモリデバイス、特に、小形のファクタカードとしてパッケージ化されたEEPROMおよびフラッシュEEPROMの形の固体メモリデバイスは、最近、様々な移動用デバイスや携帯用デバイス(特に情報機器および消費者用電子製品)において選好されるメモリデバイスになっている。内蔵形カードおよび取り外し可能カードの双方の形のフラッシュメモリは、その小形サイズ、少ない消費電力、高速性、並びに、高い信頼性という特徴のために移動環境や携帯環境で理想的に好ましいメモリデバイスである。

【0003】

EEPROMは、ソース領域とドレイン領域間の、半導体基板のチャネル領域にわたって配置される電界効果トランジスタ構造内のフローティング(接続されていない)導電性ゲートを利用するものである。このフローティングゲートにわたってコントロールゲートが設けられる。トランジスタのしきい値電圧特性はこのフローティングゲートに保持されている電荷量により制御される。すなわち、フローティングゲートの所定の電荷レベルに対して、そのソース領域とドレイン領域間の導通を可能にするためにトランジスタを“オン”に転換する前に、コントロールゲートに印加しなければならない対応する電圧(しきい値)が生じる。

【0004】

このフローティングゲートは電荷範囲の保持が可能であり、したがって、しきい値電圧ウィンドウ内の任意のしきい値電圧レベルにセットしてプログラミングを行うことが可能となる。しきい値電圧ウィンドウのサイズはデバイスの最小しきい値レベルと最大しきい値レベルとによって画定され、この最小および最大しきい値レベルがフローティングゲート上へのプログラム可能な電荷範囲に対応するしきい値レベルとなる。このしきい値ウィンドウは、一般にメモリデバイスの特性、動作条件および履歴に依って決まる。原則として、このウィンドウ内の個別の分解可能な各しきい値電圧レベルの範囲を用いて、セルの明確に限定されたメモリ状態を示すことが可能となる。

【0005】

メモリセルとして機能するトランジスタは典型的には2つのメカニズムのうちの一方によって“プログラム”状態へプログラムされる。“熱い電子注入”時に、ドレインに印加される高い電圧により電子は基板チャネル領域の両端にわたって加速される。同時に、コントロールゲートに印加される高い電圧によって熱い電子は薄いゲート誘電体の中を通ってフローティングゲート上へ引っ張られる。“トンネリング”注入時に、基板に対して相対的に高い電圧がコントロールゲートに印加される。このようにして、電子は基板から中間に介在するフローティングゲートへ引っ張られることになる。

【0006】

複数のメカニズムによってメモリデバイスを消去することも可能である。EEPROMの場合、コントロールゲートに対して相対的に高い電圧を基板に印加することによってメモリセルを電気的に消去し、基板チャネル領域(すなわち、ファウラー−ノードルハイム (Fowler-Nordheim)のトンネリング)までフローティングゲート内の電子を誘導して薄い酸化膜を貫通するようにすることが可能である。典型的には、EEPROMはバイト毎に消去可能である。フラッシュEEPROMの場合、一度にすべてか、1回につき1以上のブロックかのいずれかのメモリの電気的消去が可能であり、その場合、512バイトまたはそれ以上のメモリからブロックを構成することも可能である。

【0007】

不揮発性メモリセルの例

メモリデバイスはカードに装着可能な1以上のメモリチップを通常備えている。個々のメモリチップはメモリセルからなるアレイを備え、これらのメモリセルは、デコーダ並びに消去回路、書き込み回路および読み出し回路のような周辺回路によってサポートされている。インテリジェントで、より高いレベルのメモリ処理とインターフェイスとを実行するコントローラを備えたさらに複雑なメモリデバイスも出現している。今日利用されている多くの商業的に成功を納めた不揮発性固体メモリデバイスが存在する。これらのメモリデバイスは異なるタイプのメモリセルを採用することも可能であり、これら個々のタイプは1以上の電荷蓄積素子を含むものであってもよい。

【0008】

図1A〜図1Eは、不揮発性メモリセルの様々な例を概略的に示す。

図1Aは、電荷を蓄積するためのフローティングゲートを備えたEEPROMセルの形で不揮発性メモリを概略的に示す。電気的に消去可能でプログラム可能なリードオンリメモリ(EEPROM)は類似の対応する構造を有しているが、さらにこれに加えて、このリードオンリメモリは、UV輻射線に曝す必要なく、適当な電圧の印加時に電荷をロードしたり、そのフローティングゲートから電気的に電荷を除去したりするメカニズムを提供するものである。米国特許第5,595,924号(特許文献1)にこのようなセル並びにこれらのセルの製造方法の例についての記載がある。

【0009】

図1Bは、選択ゲートとコントロールゲート(ステアリングゲート)の双方のゲートを備えたフラッシュEEPROMセルを概略的に示す。メモリセル10はソース拡散部14とドレイン拡散部16との間に“分割チャネル”12を有している。2つのトランジスタT1とT2とを直列に備えたセルが効率良く形成される。T1は、フローティングゲート20とコントロールゲート30とを備えたメモリトランジスタとして機能する。フローティングゲートは選択可能な電荷量の蓄積が可能である。チャネルのT1部分を通って流れることが可能な電流量は、コントロールゲート30にかかる電圧と、間に介在するフローティングゲート20に存在する電荷量とに依存して決まる。T2は、選択ゲート40を備えた選択トランジスタとして機能する。選択ゲート40において或る電圧によりT2をオンに転換すると、T2によって、チャネルのT1部分の電流がソースとドレイン間を通ることが可能となる。選択トランジスタはコントロールゲート側での電圧に依存しないソースドレインチャネルに沿ったスイッチを提供する。1つの利点として、これを用いて、セルのフローティングゲート側でのこのセルの(正の)電荷空乏に起因して生じるゼロコントロールゲート電圧でも、まだ導通を行っているセルをオフに転換することができるという点が挙げられる。別の利点として、これによってソース側注入プログラミングのさらに容易な実現が可能となる。

【0010】

分割チャネルメモリセルの1つの単純な実施形態として、図1Bに示されている点線によって概略的に示すように選択ゲートとコントロールゲートとを同じワードラインと接続する実施形態がある。この接続は、チャネルの一方の部分にわたって電荷蓄積素子(フローティングゲート)を配置させ、チャネルの他方の部分にわたって、並びに、電荷蓄積素子にわたって(ワードラインの一部である)コントロールゲート構造を配置させることにより達成される。この結果、2つのトランジスタ、すなわち、電荷蓄積素子にかかる電荷量と、チャネルのトランジスタの部分の中を通って流れることができる電流量の制御を行うワードラインにかかる電圧との組み合わせを有する一方のトランジスタ(メモリトランジスタ)、並びに、トランジスタのゲートの例として単独で機能しているワードラインを有する他方のトランジスタ(選択トランジスタ)を直列に備えたセルが形成される。このようなセルのいくつかの例、メモリシステムにおけるこれらセルの利用およびこれらセルの製造方法については、米国特許第5,070,032号(特許文献2)、第5,095,344号(特許文献3)、第5,315,541号(特許文献4)、第5,343,063号(特許文献5)、第5,661,053号(特許文献6)に記載されている。

【0011】

図1Bに示されているさらに改善された分割チャネルセルの実施形態として、選択ゲートとコントロールゲートとが独立し、このゲート間が点線によって接続されない場合の実施形態がある。1つの実施構成は、ワードラインに対して垂直に伸びる制御(ステアリング)ラインと接続されたセルアレイ内に1列のコントロールゲートを有する。この結果、選択されたセルの読み出しまたはプログラミングの際に、2つの機能を同時に実行する必要性からワードラインは解放されることになる。2つの機能とは、(1)選択トランジスタのゲートとしての機能であり、したがって、選択トランジスタをオン/オフに転換するための適当な電圧を必要とする機能と、(2)ワードラインと電荷蓄積素子間での電界(容量性)結合を通じて電荷蓄積素子の電圧を所望のレベルに合わせて駆動する機能である。単一の電圧を用いて最適の態様でこの機能の双方を実行することはしばしば困難となる。コントロールゲートと選択ゲートとを独立に制御すれば、追加の制御ラインが機能(2)を実行している間、ワードラインは機能(1)を実行するだけで十分となる。この能力は、より高い性能のプログラミング設計をサポートするものとなり、その場合、プログラミング電圧は目標データに適合されることになる。フラッシュEEPROMアレイにおける独立したコントロール(すなわち、ステアリング)ゲートの利用については、例えば、米国特許第5,313,421号(特許文献7)および第6,222,762号(特許文献8)に記載されている。

【0012】

図1Cは、デュアルフローティングゲートと、独立した選択ゲートとコントロールゲートとを備えた別のフラッシュEEPROMセルを概略的に示す。メモリセル10は、直列の3つのトランジスタを効率良く備えていることを除いて、図1Bのメモリセルと同様のメモリセルである。このタイプのセルでは、2つの蓄積素子(すなわち、T1左とT1右の蓄積素子)がそのチャネルを介してソースとドレイン拡散部との間に選択トランジスタT1を備えて設けられる。これらのメモリトランジスタは、フローティングゲート20と20’と、コントロールゲート30、30’とをそれぞれ有している。選択トランジスタT2は選択ゲート40によって制御される。任意の時点で、このメモリトランジスタのうちの一方だけが読み出しまたは書き込みのためにアクセスされる。記憶ユニットT1左がアクセスされているとき、T2とT1右の双方がオンに転換されて、チャネルのT1左の部分の電流がソースとドレインとの間を通ることが可能になる。同様に、記憶ユニットT1右がアクセスされているとき、T2とT1左がオンに転換される。フローティングゲートの近傍に選択ゲートのポリシリコンの一部を設けることにより消去が行われ、さらに、フローティングゲート内に蓄積された電子を選択ゲートのポリシリコンまでトンネリングすることができるように、極めて大きな正の電圧(例えば、20Vなど)が選択ゲートに印加される。

【0013】

図1Dは、NANDセルに編成された一連のメモリセルを概略的に示す。NANDセル50は、一連のメモリトランジスタM1、M2、...Mnのソースとドレインとによってデイジチェーンされた一連のメモリトランジスタM1、M2、...Mn(n=4、8、16またはこれよりも大きな数)から構成される。NANDセルのソース側端子54およびドレイン側端子56を介して、一対の選択トランジスタS1、S2が、このメモリトランジスタチェーンの外部との接続を制御する。メモリアレイにおいて、ソース選択トランジスタS1がオンに転換されると、ソース側端子はソースラインと結合される。同様に、ドレイン選択トランジスタS2がオンに転換されると、NANDセルのドレイン側端子はメモリアレイのビットラインと結合される。チェーンの形でつながれた個々のメモリトランジスタは、意図するメモリ状態を表すために所定の電荷量を蓄積する電荷蓄積素子を有している。個々のメモリトランジスタのコントロールゲートは、読み出し処理および書き込み処理に対する制御を行う。選択トランジスタS1、S2の各々のコントロールゲートは、それぞれ、そのソース側端子54およびドレイン側端子56を介してNANDセルに対するアクセスを制御する。

【0014】

NANDセル内のアドレス指定したメモリトランジスタがプログラミング中に読み出され、検証されると、そのコントロールゲートには適当な電圧が供給される。同時に、NANDセル50内の残りのアドレス指定されていないメモリトランジスタは、このメモリトランジスタのコントロールゲートにかけられる十分な電圧の印加によって全部オンに転換される。このようにして、導電経路は個々のメモリトランジスタのソースからNANDセルのソース側端子54まで、そして同様に、個々のメモリトランジスタのドレイン用として、セルのドレイン側端子56まで効率的に形成される。このようなNANDセル構造を備えたメモリデバイスについては、米国特許第5,570,315号(特許文献9)、第5,903,495号(特許文献10)、第6,046,935号(特許文献11)に記載されている。

【0015】

図1Eは、電荷を蓄積する誘電体層を含む不揮発性メモリを概略的に示す。前述した導電性フローティングゲート素子の代わりに、誘電体層の個別領域が電荷蓄積素子として利用される。誘電体記憶素子を利用するこのようなメモリデバイスについては、エイタンらによる“NROM:新規の局在化トラッピング、2ビット不揮発性メモリセル”,IEEE電子デバイスレターズ,第21巻,第11号,2000年11月,543〜545ページ (Eitan et al., “NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol.21, no.11, November 2000, pp.543-545) (非特許文献1)に記載されている。ONO誘電体層はソースおよびドレイン拡散部の間のチャネルの両端にわたって延在する。1データビット用の電荷がドレインに隣接して誘電体層内に局在化され、さらに別のデータビット用の電荷がソースに隣接して誘電体層内に局在化される。例えば、米国特許第5,768,192号(特許文献12)および第6,011,725号(特許文献13)に2つのシリコン二酸化物層の間に挟まれるトラッピング誘電体を有する不揮発性メモリセルについての開示がある。多状態データ蓄積は、誘電体内で空間的に分離された電荷蓄積領域の2進状態を別々に読み出すことにより実現される。

【0016】

メモリアレイ

典型的には、メモリデバイスには、行と列とで構成され、ワードラインとビットラインとによってアドレス可能な2次元アレイのメモリセルが含まれる。このアレイはNOR形またはNAND形アーキテクチャに従って形成することができる。

【0017】

NORアレイ

図2は、NORメモリセルのアレイの一例を示す。NOR形アーキテクチャを備えたメモリデバイスは図1Bまたは図1Cに例示するタイプのセルにより実現される。個々のメモリセル行はそのソースとドレインとによってデイジチェーンで接続される。この設計を仮想接地設計 (virtual ground design)と呼ぶことがしばしばある。個々のメモリセル10は、ソース14と、ドレイン16と、コントロールゲート30と、選択ゲート40とを備えている。1行のセルにはワードライン42と接続されたこのセルの選択ゲートが設けられる。1列のセルはそのソースとドレインとを備え、これらのセルはそれぞれ選択済みのビットライン34と36と接続している。メモリセルがそのコントロールゲートと選択ゲートとを独立に制御させる実施形態によっては、ステアリングライン36が1列のセルのコントロールゲートを接続するものもある。

【0018】

多くのフラッシュEEPROMデバイスが、そのコントロールゲートと選択ゲートとを一体に接続して個々に形成されたメモリセルにより実現される。この場合、ステアリングラインを必要とせず、単にワードラインがセルのすべてのコントロールゲートと選択ゲートとを個々の行に沿って接続するだけでよい。これらの設計例が、米国特許第5,172,338号(特許文献14)および第5,418,752号(特許文献15)に開示されている。この設計では、ワードラインにより実質的に2つの機能(すなわち、行選択機能と、読み出しやプログラミングを行うための、行のすべてのセルへのコントロールゲート電圧の供給機能)とが実行される。

【0019】

NANDアレイ

図3は、図1Dに示されている例のようなメモリセルのNANDアレイの一例を示す。個々のNANDセルの列に沿って、ビットラインが個々のNANDセルのドレイン側端子56と結合される。NANDセルの個々の行に沿って、ソースラインがすべてのNANDセルのソース側端子54を接続するようにしてもよい。また、行に沿ったNANDセルのコントロールゲートも一連の対応するワードラインと接続される。接続されたワードラインを介して、この対の選択トランジスタのコントロールゲートに適当な電圧をかけて、この対の選択トランジスタをオンに転換することによりNANDセルの行全体のアドレス指定を行うことができる(図1Dを参照されたい)。NANDセルのチェーン内のメモリトランジスタが読み出されると、チェーン内の残りのメモリトランジスタが、このメモリトランジスタの関連するワードラインを介して強くオンに転換され、それによってチェーンの中を流れる電流は、読み込まれているセルに蓄積された電荷のレベルによって実質的に依存して決められることになる。メモリシステムの一部としてのNAND形アーキテクチャのアレイの一例並びにその処理は、米国特許第5,570,315号(特許文献9)と、第5,774,397号(特許文献16)と、第6,046,935号(特許文献11)とに見られる。

【0020】

ブロック消去

電荷記憶メモリデバイスのプログラミングの結果として、専ら電荷記憶メモリデバイスの電荷蓄積素子に対するさらに多くの電荷の付加が可能となる。したがって、プログラミング処理を行う前に、電荷蓄積素子内の既存の電荷を除去(または消去)する必要がある。1以上のメモリセルブロックを消去する消去回路(図示せず)が設けられる。セルアレイ全体またはアレイの大きなセルグループが電気的に一括して(すなわち、フラッシュで)消去される場合、EEPROMのような不揮発性メモリは“フラッシュ”EEPROMと呼ばれる。消去されるとすぐに、セルグループの再プログラミングが可能となる。一括消去可能なセルグループは1以上のアドレス可能な消去単位から構成することも可能である。消去単位または消去ブロックが典型的には1以上のデータページを蓄積し、このページがプログラミングおよび読み出しの単位となるが、単一の処理時に2以上のページがプログラミングや読み出しを行うようにすることも可能である。個々のページは、典型的には1以上のデータセクタを蓄積し、このセクタのサイズはホストシステムにより画定される。一例として、磁気ディスク駆動装置に関する基準規格に従う512バイトのユーザデータセクタがあり、これに加えてユーザデータおよび/またはユーザデータが蓄積されているブロックに関する或る数バイトのオーバーヘッド情報がある。

【0021】

読み出し/書き込み回路

通常の2状態EEPROMセルでは、少なくとも1つのブレークポイントレベルが確定され、導通ウィンドウの分割が行われて、2つの領域がつくられる。ブレークポイントに対する相対的なセル状態が、“電流”の検知か、“電圧”の検知かのいずれかを利用して通常決定される。電流検知を利用して、所定の固定電圧と、セルのゲートと、ソースと、ドレインとを印加することによりセルが読み出され、結果として生じる電流が、絶対値か、或いは2つの極値間の中間値に計画的にセットされたしきい値を有する同様のセルから取得される値かのいずれかの値と比較される。読み出された電流の方がブレークポイントレベルの電流よりも高い場合、セルは、1つの論理状態(例えば“0”状態など)をなすように設定される。一方、電流がブレークポイントレベルの電流よりも低い場合、セルはもう一方の論理状態(例えば“1”状態など)をなすように設定される。したがって、このような2状態セルによって1ビットのデジタル情報の蓄積が行われることになる。基準電流のソースは、外部でプログラムすることも可能ではあるが、ブレークポイントレベル電流を生成するメモリシステムの一部として提供されることも多い。

【0022】

メモリ容量を上げることを目的として、フラッシュEEPROMデバイスは、半導体技術の進歩に伴ってますます高密度になる記録密度で製造されている。記憶容量を上げる別の方法として、各メモリセルに3以上の状態を蓄積させる方法がある。

【0023】

マルチ状態またはマルチレベルEEPROMメモリセル用として、導通ウィンドウは2以上のブレークポイントにより3以上の領域に分割されるので、各セルが1ビット以上のデータを蓄積する能力を持つことができるようになる。与えられたEEPROMアレイが蓄積できる情報は、このようにして各セルが蓄積することができる状態数を用いて増やされる。マルチ状態すなわちマルチレベル・メモリセルを持つEEPROMまたはフラッシュEEPROMについては、米国特許第5,172,338号(特許文献14)に記載されている。

【0024】

実際には、セルのメモリ状態は、読み出しレベルがコントロールゲートに印加されるときのセルのソース電極とドレイン電極の両端にわたる導通電流の検知により通常読み出される。したがって、セルのフローティングゲートの各々の所定の電荷について、一定の基準コントロールゲート電圧に関連して、対応する導通電流の検出が可能となる。同様に、フローティングゲート上へのプログラム可能な電荷範囲により、対応するしきい値電圧用ウィンドウや対応する導通電流ウィンドウが画定される。

【0025】

これとは別に、仕切られた電流ウィンドウ間での導通電流の検出(電流検知)の代わりに、コントロールゲートにおけるテスト中に所定のメモリ状態用のしきい値電圧をセットし、この導通電流がしきい値電流(電圧検知)よりも低いか高いかの検出を行うことが可能である。1つの実施構成では、ビットラインの静電容量を通じる導通電流の放電レートによってチェックを行うことにより、しきい値電流を基準とする相対的な導通電流の検出が行われる。セルがプログラムされている(ゲート電圧を基準として相対的に高いしきい値である)場合、放電電流が非常に小さくなるため、ビットラインの相対的に大きな静電容量が著しく放電されることはなく、センスアンプは“0”状態に戻ることになる。

【0026】

米国特許第4,357,685号(特許文献17)に2状態EPROMのプログラミング方法が開示され、この方法では、セルは、所定の状態にセットされてプログラムされると、連続するプログラミング電圧パルスを受け、その度に増分する電荷がフローティングゲートに加えられる。パルス間で、ブレークポイントレベルと比較して、セルのソース・ドレイン電流を測定するためにセルのリードバック(検証)が行われる。電流状態が所望の状態に達したことが検証されたときプログラミングは停止する。使用するプログラミングパルス列が、増加する周期や振幅を持つ場合もある。

【0027】

従来技術によるプログラミング回路は単に、プログラミングパルスを印加して、しきい値ウィンドウを通って消去状態または接地状態から目標状態に達するまで1ステップずつ進むようにする回路にすぎない。実際に、適当な精度を可能にするには、個々の分割領域すなわち画定領域が、少なくともおよそ5つの越えるべきプログラミングステップを必要とする。その性能は2状態メモリセル用として容認することができるものである。しかし、マルチ状態セルの場合、所要なステップ数は分割の数と共に増加するため、プログラミングの精度すなわち精密さも高める必要がある。例えば、16個の状態セルでは、目標状態にセットしてプログラムするのに平均して少なくとも40個のプログラミングパルスが必要となる場合もある。

【0028】

メモリアレイ100は行デコーダおよび列デコーダを介して読み出し/書き込み回路によりアクセスを行うことが可能である。図2および図3に示されているように、メモリアレイ100内のメモリセルのメモリトランジスタは1組の選択ワードラインとビットラインとを介してアドレス可能である。行デコーダは1以上のワードラインを選択し、列デコーダは1以上のビットラインを選択して、アドレス指定したメモリトランジスタのそれぞれのゲートに対する適当な電圧の印加を図るようにする。アドレス指定したメモリトランジスタのメモリ状態の読み出しまたは書き込み(プログラム)を行うための読み出し/書き込み回路が設けられる。読み出し/書き込み回路は、ビットラインを介してアレイ内の記憶素子と接続可能な複数の読み出し/書き込みモジュールを備える。

【0029】

読み出し中または検証中に、センスアンプは、選択ビットラインを介して接続されたアドレス指定済みのメモリトランジスタのドレインの中を流れる電流を決定する。この電流はメモリトランジスタに蓄積された電荷およびこのメモリトランジスタのコントロールゲート電圧に依存して決められる。例えば、多状態EEPROMセルでは、複数の異なるレベルのうちの1つレベルに合わせてこのセルのフローティングゲートを荷電することが可能となる。4レベルセルの場合、2ビットデータを蓄積することができる。センスアンプによって検出されたレベルはレベルからビットへの変換論理回路によって1組のデータビットへ変換されて、データラッチに蓄積される。

【0030】

読み出し/書き込み性能および精度に影響を与える諸要因

読み出しおよびプログラミング性能の改善を目的として、アレイ内の複数の電荷蓄積素子またはメモリトランジスタの同時読み出しや、同時プログラミングが行われる。したがって、記憶素子の論理“ページ”の一括読み出しや、一括プログラミングが行われることになる。既存のメモリアーキテクチャにおいて、複数のインタリーブされたページは典型的には行の中に含まれる。ページのすべての記憶素子はまとめて読み出されたり、まとめてプログラムされたりすることになる。列デコーダは、インタリーブされたページの個々のページを、対応する個数の読み出し/書き込みモジュールと選択的に接続することになる。例えば、1つの実施構成では、メモリアレイは532バイト(512バイト+20バイトのオーバーヘッド)のページサイズを有するように設計される。個々の列がドレインビットラインを含み、かつ、行当たり2つのインタリーブ済みのページが存在する場合、これによって、個々のページが4256列と関連づけられて8512列に達することになる。すべての偶数番号のビットラインまたは奇数番号のビットラインのいずれかと同時に読み出しまたは書き込みを行えるように接続可能な4256個のセンスモジュールが存在することになる。このようにして、4256ビット(すなわち、532バイト)のデータページが同時に記憶素子のページから読み出されたり、或いは記憶素子のページの中へプログラムされたりする。読み出し/書き込み回路を形成する読み出し/書き込みモジュールを構成して種々のアーキテクチャに変えることも可能である。

【0031】

非常にコンパクトでかつ高性能の不揮発性メモリおよび制御方法については、“非常にコンパクトな不揮発性メモリおよびその方法”という2002年9月24日に出願されたラウル−エイドリアン・セルニアによる米国特許出願第10/254,483号(特許文献18)に記載されている。この特許出願は、その全体が本願明細書において参照により援用されている。

【0032】

図4Aと図4Bとに、前述したタイプのアレイ内の4状態NANDメモリセルのプログラミングの特定の現行技術を例示する。これら2つの図およびプログラミング処理についての添付の説明は、米国特許第6,522,580号(特許文献19)から採られたものであり、この特許は、その全体が本願明細書において参照により援用されている。

【0033】

図4Aと図4Bには、前述したタイプのアレイにおける4状態NANDメモリセルのしきい値電圧の分布状態を示し、このメモリセルにはアレイ内のセルのフローティングゲートによって2ビットデータ、すなわち個々のセル内の4つのデータ状態が蓄積される。曲線Eは、消去状態(“11”データ状態)にあるアレイ内のセルのしきい値レベルVT(負のしきい値電圧レベルにある)の分布状態を表す曲線である。セルの初期状態として、セルが前述した消去状態以外の状態にセットされた場合、本願で用いるような曲線Eもこのような状態を表すことになる。さらに一般的に言えば、消去状態を含むすべてのこのような状態を本願では“リセット状態”と呼ぶことにする。“10”と“00”のユーザデータをそれぞれ蓄積する蓄積素子のしきい値電圧の分布状態AとBとは、それぞれ0ボルトと1ボルトとの間、並びに、1ボルトと2ボルトとの間にはいるように示される。曲線Cは、“01”データ状態に合わせてプログラムされたメモリセルの分布状態を示し、最高のしきい値電圧レベルが、読み出された過去の電圧のうち2ボルトよりも大きく、かつ、4.5ボルトよりも小さいレベルとなる。“ユーザデータ”および“ホストデータ”という用語は本願では交換可能に用いられる。

【0034】

単一メモリセルに蓄積された2つのビットの各々は別の論理ページから得られ、異なる時刻にプログラムすることも可能である。2つのビットの各々は、互いから得られる別の論理ページアドレスを担持する。単一メモリセルに蓄積されたこれら2つのビットは、順序づけられた1組の2進値変数または一対の2進値変数(有意性のより高いビットおよび有意性のより低いビット)を形成する。下位ページのアドレスが入力されると、ユーザデータすなわちホストデータ“11”、“10”、“00”、“01”内のこの有意性のより低い方のビットがアクセスされる。上位ページアドレスが入力されると、ユーザデータすなわちホストデータの有意性のより高い方のビットがアクセスされる。蓄積データが3以上のビットを含む場合、順序づけられたセットの蓄積値は3以上の変数を含むものであってもよい。論理ページの指定は、偶数/奇数ページ指定またはインタリーブされたページ指定とは異なるものとなる。このようなページ指定は、メモリアレイにおけるメモリセルの物理的構成に関する指定である。しきい値ウィンドウを4状態よりも多くの状態にさらに細かく分割して、セル当たり3以上のデータビットを表すためにセルに蓄積することが可能となるところまで論理ページの指定を拡張することも可能である。これによって3以上のページが利用されるようになり、その場合、これらのページは、単に第1、第2、第3ページなどの数値として参照することも可能となる。

【0035】

前述したように、プログラム処理に先立って、1以上のメモリセルブロック(本願では電荷蓄積素子とも呼ばれる)が一括して電気的に消去されて、消去状態“11”となる。次いで、データバッファ内のユーザデータすなわちホストデータを利用して、電荷蓄積レベルまたは電荷蓄積素子のしきい値レベルがセットされる。第1のプログラミングパス時に、セルのしきい値レベルはデータバッファ内の下位の論理ページから得られるビットに従ってセットされる。このビットが“1”の場合、何も行われない。というのは、以前に消去された結果としてセルが消去状態となるからである。しかし、このビットが“0”の場合、セルのレベルは第1のプログラミング済み状態まで上げられる。この処理によって第1のプログラミングパスは終了する。

【0036】

第2のプログラミングパス時に、セルのしきい値レベルは、上位論理ページからデータバッファに蓄積されるビットに従ってセットされる。このセルのしきい値レベルが“1”の場合、プログラミングは行われない。というのは、このセルは、下位ページのビットのプログラミングに対応して状態Eまたは状態Aのうちの一方の状態にあるからである。これらの状態の双方は上位ページビット“1”を担持する。しかし、上位ページのビットが“0”であれば、セルは2回目にプログラムされる。第1のパスの結果、セルが消去状態Eのままとなれば、上向きの矢印によって図4Bに示されているようにセルはその状態から最高の状態Cへプログラムされることになる。しかし、セルがプログラムされて状態Aになった場合、第1のプログラミングパスの結果、下向きの矢印によって図4Bに示されているように、セルは、第2のパス時にその状態から状態Bへさらにプログラムされることになる。この第2のパスの結果、下位ページのビットの第1のパスプログラミングの結果を変えることなく、上位ページから“0”を蓄積するように指定される状態へセルをプログラムすることになる。

【0037】

上位ページのビットが“0”となる第2のプログラミングパス中に、図4Bの上下の矢印に従って、消去状態Eから最高の状態Cへセルをプログラムするか、または状態Aから状態Bへセルをプログラムするかのいずれかのプログラミングを行うことが望ましい。プログラミングを上向きの矢印に従って行うか、下向きの矢印に従って行うかを決定するために、セルがEの状態にあるのか、またはAの状態にあるのかを第1に判定する必要がある。デバイスによっては、この判定が、内部読み出しまたは内部データロードとして公知の処理プロセスにより行われるものもあり、その場合、第1のプログラミングパス中にプログラムされるセルによって、そのしきい値レベルが状態Eまたは状態Aのいずれの状態に対応するかの判定が読み出される。

【0038】

前述したタイプのメモリアレイにおける、セルからなる隣接フローティングゲート間での電界効果結合については、ジアン・チェンとユーピン・フォングによる米国特許第5,867,429号(特許文献20)に記載されている。この特許は、その全体が本願明細書において参照により援用されている。集積回路の製造技術の改善の結果、この結合のレベルは、メモリセルアレイのサイズの縮小に伴って必然的に上昇することになる。この問題は、異なる時点にプログラムされた2組の隣接セル間で最も顕著に発生するものである。1組のセルをプログラムして、1組のデータに対応する電荷レベルがフローティングゲートに加えられる。第2の組のデータを用いて第2の組のセルをプログラムした後、第1の組のセルのフローティングゲートから読み出された電荷レベルが、第1の組のフローティングゲートと結合されている第2の組のフローティングゲートに対する電荷の影響に起因して、プログラムされた電荷レベルとは異なっているように見えることが頻繁に生じる。これはユーピン効果として知られているものである。

【0039】

後続してプログラムされる第2の組のセルのフローティングゲートが、第1の組のセルのフローティングゲートのしきい値レベルよりもずっと高いしきい値レベルに合わせてプログラムされているとき、前述したユーピン効果は特に顕著になる。図4Bから観察されることとして、第2の組のセルのフローティングゲートが消去状態から最高の状態Cへプログラムされると、しきい値電圧の変動が相対的に大きくなることに起因して、ユーピン効果が最も顕著になるということが挙げられる。ユーピン効果を小さくする1つのアプローチとして、後続のワードラインのプログラミング後、この状態の最終値に合わせてこの状態をプログラムするアプローチがある。このアプローチについては、“隣接するメモリセル行の蓄積素子間における結合の影響を低減する技術”という2002年9月6日にラウル−エイドリアン・セルニアにより出願された米国特許出願第10/237,426号(特許文献21)に記載されている。この特許出願は、その全体が本願明細書において参照により援用されている。本願は個々のページ内に“フラグ”セルというコンセプトを導入するものであり、このコンセプトは、そのページの状態(中間状態または最終状態)のプログラミングを示すものである。

【0040】

ユーピン効果を低減する別のアプローチとして、図4Aと図4Bとに示されているアプローチ以外の、シバタらによる米国特許第6,657,891号(特許文献22)に提案されているような別のコード構成を利用するものがある。この特許は、その全体が本願明細書において参照により援用されている。シバタらによって提案されているコード構成は図5A〜図5Cに示されているものである。図5A〜図5Cでは、メモリセルのしきい値電圧レベルによって表すことができる3以上の論理ページデータの存在も可能であることが予見され、この理由のために、図5A〜図5Cでは前述した下位の論理ページは第1のページと呼ばれ、前述した上位の論理ページは第2のページと呼ばれている。前述したように、メモリセルの中へ書き込むべき第1のページデータが“1”の場合、プログラミングは実行されず、セルは消去状態Eのまま残ることになる。第1のページデータが“0”の場合、メモリセルのしきい値電圧が図5Aに示されている分布状態すなわち状態B’で1まで上昇するようにプログラミングは構成される。これは、第1のページデータの“0”値が状態Aに合わせてセルにプログラムさせる図4Aでの処理プロセスとは対照的である。図5Bに示されているように、第2のページデータを利用してセルをプログラムする前に、状態B’に予めプログラムされているメモリセルに隣接するメモリセルへデータは書き込まれる。後続してプログラムされる隣接するセルのフローティングゲートにかかる電荷に起因して生じるユーピン効果の結果、図5Bに示されているしきい値電圧の分布状態B’は、図5Aのものよりも幅が広く、大きな面積のものになっている。図4A/Bまたは図5Cの最終分布状態Bよりも値の点では常に低いものの、図5Aの初期の分布状態B’の方が、図4A/Bまたは図5Cの最終分布状態Bよりもずっと幅が広いことに留意されたい。

【0041】

第2のページデータが書き込まれると、当初消去状態Eにあったセルは状態Aへプログラムされ、当初状態B’にあったセルは状態Cへプログラムされる。このコード構成には異なる時点にプログラムされた隣接するセルの電荷レベル間での電位差、したがって、隣接するフローティングゲート間での電界効果結合を小さくする効果があり、したがってユーピン効果が生じることになる。

【0042】

隣接するフローティングゲート内での電界効果結合を小さくするためには、図5Aと図5Cとを参照する前述したコード構成は利点を有するものであるかもしれないが、以下に説明するようにページの充填を行うユーザデータが不十分な場合、このようなコード構成を用いると、誤った状態に合わせてユーザデータがプログラムされる可能性がある。

【0043】

不揮発性メモリアレイによっては、ページ当たり2048バイトを有するものもある。このことは、或いは読み出し処理または書き込み処理時に単一の単位として2048バイトが読み出されたり、或いはプログラムされたりすることを意味する。不揮発性メモリシステムのシステムプログラミングは、512バイトのような2048バイトよりも少ないバイトを単位としてそのまま処理することも可能である。したがって、第1および第2の(下位および上位などの)ページの各ページは、4つのセクタのような複数のセクタを含むことになる場合がある。言い換えれば、ホストがデータ転送の終了へ向かってユーザデータをメモリアレイへ転送するとき、ページ内のメモリセルのすべてを完全にプログラムするにはユーザデータが不足する場合がある。したがって、個々のページが2048バイトを有する場合、第1のページと、1、2、3セクタのみを充填するのに十分なデータが存在するかもしれないが、第2のページの4つのセクタすべてを充填するにはデータが不十分となることが考えられる。メモリアレイ内のメモリセル行が、前述したタイプのインタリーブされたページ(偶数番号のビットラインによって制御される偶数ページには行内のメモリセルのすべてが含まれ、奇数番号のビットラインによって制御される奇数ページには行内のメモリセルのすべてが含まれる)を含む場合には、これは真であり、メモリアレイ内のメモリセル行には単一のページが含まれることになる。したがって、2048個のメモリセルの個々の行が、奇数ページと偶数ページのような2つのインタリーブされたページに分割され、個々のページが1024バイトを含むようになっている場合、偶数または奇数の第1のページと、偶数または奇数の第2のページの一方のセクタを充填するには適切なまたは十分なデータが存在するかもしれないが、偶数または奇数の第2のページの双方のセクタを充填するには適切なまたは十分なデータが存在しないことが考えられる。図4Aと図4Bに例示するタイプのコード構成の場合、このような状況によって問題が生じることはない。しかし、前述した図5A、5B、5Cに示されているような別のコード構成を利用する場合、このような状況が以下に例示するように問題となる場合がある。

【0044】

この問題が図6Aおよび図6Bの例で示されている。この例では、メモリアレイ内の行には、2048バイトのデータを蓄積するための16,384個のメモリセルが含まれ、このメモリセルが1ページを構成することになる。メモリアレイへまたはメモリアレイからデータを転送するコンピュータホストシステムは、各ブロックが512バイトを有する4つのブロック内でデータの転送を行う。したがって、図6Aに示されているように、アレイ内のメモリセル行は4つのセクタ、すなわちグループ112、114、116、118に分割され、個々のグループ内のセルの各々は第1の(下位)ページデータおよび第2の(上位)ページデータを蓄積することになる。本願明細書で以後使用するように、“セクタ”および“グループ”という用語は交換可能に用いられる。図6Aに示されているように、第1のページすなわち下位ページを充填するのに十分なホストデータが存在し、そのため4つの第1のページすなわち下位ページセクタは、下位ページセクタであることを示すために“L”とマークされることになる。プログラム対象のユーザデータすなわちホストデータのブロックの終端部へ向かって、4つのセクタの下位ページすなわち第1のページをプログラムするのに十分なデータのみが存在するようにしてもよく、そして、グループ112のセルの第2のページすなわち上位ページの第1のセクタのみが存在するようにしてもよい。この上位ページは上位ページであることを示すために図6Aでは“U”とマークされる。この結果、図6Aのセクタすなわちグループ114、116、118には、セルの上位ページすなわち第2のページをプログラムするために残されたデータが存在しなくなり、このセクタすなわちグループは、上位ページであることを示す“U”のマーカーなしでブランクのままに放置されることになる。

【0045】

異なるグループでメモリセルをプログラムするためにユーザデータを使用する前に、このデータは対応するデータバッファまたはラッチの中へ第1にロードされる(図7、図8A、図8Bを参照されたい)。次いで、データラッチに蓄積されたユーザデータはメモリセルのプログラミングのために利用される。図6Bは、図6Aのメモリセルの4つの対応するセクタすなわちグループ112、114、116、118をプログラムするための4つのデータブロック112’、114’、116’、118’の第1および第2のページを蓄積するためのデータラッチの機能を例示する機能ブロック図である。ブロックを消去した後で、かつ、4つのグループ内でセルをプログラムするためにユーザデータすなわちホストデータをデータラッチの中へロードする前に、データラッチのすべては“1”で最初にロードされる。この例では、このユーザデータはこの4つのグループのメモリセルのうちの下位ページすなわち第1のページおよびグループ112内のセルの上位ページのみのプログラミング用としては十分である。したがって、図6Bに示されているように、ブロック114’、116’、118’用のデータを蓄積するためのデータラッチの上位ページすなわち第2のページは“1”でロードされ、“1”を含み続けることになる。図6Bに示されているように、例えば、3つのデータブロック114’、116’、118’内の下位ページすなわち第1のページの中へロードされたユーザデータに依存して、3つのセクタ内のデータラッチ内のデータが値“11”を有する場合、(データ130’、132’、134’、136’、138’でプログラムされたメモリセルなどの)メモリセルのうちのいくつかはプログラムされないことになる。しかし、3つのブロック114’、116’、118’内のデータが(データ122’、124’、126’、128’などの)値“10”を有する場合、しきい値電圧すなわち蓄積レベルがコード構成に従って状態“10”に対応するようになるまで、セクタすなわちグループ114、116、118内の対応するメモリセルはプログラムされることになる。

【0046】

次いで、ユーザデータすなわちホストデータの別のブロックを後続してロードして、ブロック114’、116’、118’を蓄積するデータラッチ内でデフォルト値“1”を変位するとき、このようなデータは、典型的にはすべてが値“1”であるとはかぎらず、いくつかの値が“0”となるものもある。したがって、状態“10”に合わせてプログラムされたグループ114、116、118内の(データ122’〜128’を含むセルなどの)このメモリセルのうちのいくつかのメモリセルの場合、後続ブロックのユーザデータすなわちホストデータが、このようなメモリセル用として“1”ではなく“0”を第2のページデータすなわち上位ページデータとして対応するデータラッチの中へロードする場合、代わりにこのようなセルを状態“00”に合わせてプログラムする必要がある場合もある。図5Cから、状態“10”の蓄積レベルが最高レベルCであることが観察される。既存のプログラミング技法がブロック消去処理から離れて個々のメモリセルの蓄積レベルのしきい値電圧の低下を許さないため、図5A〜5Cのコード構成を用いる場合、状態“10”から状態“00”へのこのようなメモリセルの再プログラムは実行不能となり、その結果セルは誤った状態へプログラムされることになる。図5A〜5Cでコード構成を使用するとき、本願ではこれを部分的ページプログラム問題と呼ぶことにする。

【先行技術文献】

【特許文献】

【0047】

【特許文献1】米国特許第5,595,924号

【特許文献2】米国特許第5,070,032号

【特許文献3】米国特許第5,095,344号

【特許文献4】米国特許第5,315,541号

【特許文献5】米国特許第5,343,063号

【特許文献6】米国特許第5,661,053号

【特許文献7】米国特許第5,313,421号

【特許文献8】米国特許第6,222,762号

【特許文献9】米国特許第5,570,315号

【特許文献10】米国特許第5,903,495号

【特許文献11】米国特許第6,046,935号

【特許文献12】米国特許第5,768,192号

【特許文献13】米国特許第6,011,725号

【特許文献14】米国特許第5,172,338号

【特許文献15】米国特許第5,418,752号

【特許文献16】米国特許第5,774,397号

【特許文献17】米国特許第4,357,685号

【特許文献18】米国特許出願第10/254,483号

【特許文献19】米国特許第6,522,580号

【特許文献20】米国特許第5,867,429号

【特許文献21】米国特許出願第10/237,426号

【特許文献22】米国特許第6,657,891号

【非特許文献】

【0048】

【非特許文献1】エイタンらによる“NROM:新規の局在化トラッピング、2ビット不揮発性メモリセル”,IEEE電子デバイスレターズ,第21巻,第11号,2000年11月,543〜545ページ

【発明の概要】

【0049】

本願発明者らは、たとえメモリセルのうちのいくつかが第1のプログラミングパス時に、ユーピン効果を小さくする従来方式によるコード構成の下での状態よりも高い状態(状態Bなど)へプログラムされても、ホストデータが不十分な第2のプログラミングパス中に(最高の状態などの)誤った状態へメモリセルすなわち電荷蓄積素子がプログラムされるのを防ぐように不揮発性半導体メモリシステムが設計されている場合、この部分的ページプログラム問題は完全に回避可能であることを認識した。例えば、(第1のプログラミングパスの結果として)第2のプログラミングパス中に素子をプログラムして、このようなより高い状態にある素子を電荷レベルで(最高の状態などの)エラーを含むさらに高い状態よりも低い状態になるようにすることが可能である。このようにして、後続するホストデータすなわちユーザデータに従うメモリセルのプログラミングは、前述した部分的ページプログラム問題の結果として妨害を受けることはなくなる。

【0050】

1つの実施形態では、第1のプログラミングパスの後で、かつ、第2のプログラミングパスよりも前に、十分な上位ページデータすなわち第2のページデータを用いることなくセルをプログラムするために、データラッチの中へ適当なデータをロードすることによりこの効果の達成は可能となり、これによって、第2のプログラミング中にプログラミングを行うとき、(第1のプログラミングパスの結果としての)より高い状態でプログラミング電圧が素子やセルと結合されることはなくなる。別の実施形態では、図5Cに示されているコード構成をわずかに変更することによってこの効果は達成可能となり、その結果、部分的ページプログラム問題は生じなくなる。

【0051】

本発明の別の態様によれば、フラグデータを蓄積するフラグセルを用いて、ホストデータすなわちユーザデータの終了のようなホストデータすなわちユーザデータの境界を示すことが可能であり、それによって部分的プログラム問題はエラーを含む結果が生じなくなる。1つの実施形態では、素子はグループ化されて、複数のセクタすなわちグループに変えられ、個々のグループには、ホストデータが不十分な第2のパス時に、このようなグループの素子がプログラムされたものであるかどうかを示すフラグデータを蓄積するための少なくとも1つの対応するフラグ電荷蓄積セルが含まれる。複数のグループのうちの少なくとも2つのグループが共通のワードラインによって制御される。少なくとも2つのグループのうちの少なくとも1つのグループではあるが、すべてのグループではないグループのプログラミングを第2のパス中に行うのに十分なホストデータが存在するとき、フラグデータは少なくとも2つのグループのうちの少なくとも一方のフラグ電荷蓄積セルに蓄積されるか、このような(単複の)フラグセルに蓄積されたフラグデータが変更されて、ホストデータの境界が示されることになる。

【0052】

説明を簡略にするために、本願では同一の構成要素には同じ参照番号が付されている。

【図面の簡単な説明】

【0053】

【図1A】不揮発性メモリセルの異なる例を概略的に示す。

【図1B】不揮発性メモリセルの異なる例を概略的に示す。

【図1C】不揮発性メモリセルの異なる例を概略的に示す。

【図1D】不揮発性メモリセルの異なる例を概略的に示す。

【図1E】不揮発性メモリセルの異なる例を概略的に示す。

【図2】NORメモリセルのアレイの一例を示す。

【図3】図1Dに示されているようなメモリセルのNANDアレイの一例を示す。

【図4A】図3のメモリセルアレイをプログラムする現行技術を示す電圧しきい値レベルの分布状態である。

【図4B】図3のメモリセルアレイをプログラムする現行技術を示す電圧しきい値レベルの分布状態である。

【図5A】図3のメモリセルアレイをプログラムする別の現行技術を示す電圧しきい値レベルの分布状態である。

【図5B】図3のメモリセルアレイをプログラムする別の現行技術を示す電圧しきい値レベルの分布状態である。

【図5C】図3のメモリセルアレイをプログラムする別の現行技術を示す電圧しきい値レベルの分布状態である。

【図6A】メモリセル行の概略ブロック図であり、部分的ページプログラム問題の例示に役立つ図である。

【図6B】図6Aでメモリセルをプログラムするための4つのデータブロックの概念図であり、部分的ページプログラム問題の例示に役立つ図である。

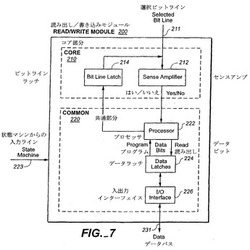

【図7】本発明の1つの実施形態を例示するための、コア部分と共通部分とに分割された個々の読み出し/書き込みモジュールの概略ブロック図である。

【図8A】仕切られた読み出し/書き込みスタックのバンクを有するコンパクトなメモリデバイスを概略的に例示し、本発明の1つの実施形態の例示に役立つ図である。

【図8B】図7に示されているコンパクトなメモリデバイスの別の配置構成を例示する。

【図9】図7の読み出し/書き込みモジュールの構成要素の概略ブロック図であり、本発明の1つの実施形態を例示するために構成要素の動作をさらに詳細に示す。

【図10A】本発明の1つの実施形態を例示するための、電圧しきい値レベルの分布状態およびメモリセルの電圧しきい値レベルを読み出す技法を示す例である。

【図10B】本発明の1つの実施形態を例示するための、電圧しきい値レベルの分布状態およびメモリセルの電圧しきい値レベルを読み出す技法を示す例である。

【図11A】第1および第2の(下位および上位)ページの読み出しを表すテーブルであり、図10Aに例示されている電圧しきい値レベルを読み出す方法の例示に役立つ図である。

【図11B】第1および第2の(下位および上位)ページの読み出しを表すテーブルであり、図10Bに例示されている電圧しきい値レベルを読み出す方法の例示に役立つ図である。

【図12】電圧しきい値レベルの分布状態およびコード構成の関連づけられた値を示す例であり、本発明の別の実施形態を例示する。

【発明を実施するための形態】

【0054】

不揮発性メモリシステムの例

図7は、本発明の好ましい実施形態に従ってコア部分210と共通部分220とに分割された個々の読み出し/書き込みモジュール200の概略ブロック図である。コア部分210は接続されたビットライン211内の導通電流が所定のしきい値レベル以上か未満かを判定するセンスアンプ212を備えている。前述したように、接続されたビットライン211はアレイ内のアドレス指定されたメモリセルのドレインへのアクセスを可能にする。

【0055】

1つの実施形態では、コア部分210もビットラインラッチ214を備えている。このビットラインラッチを利用して接続されたビットライン211にかかる電圧条件がセットされる。1つの実施構成では、ビットラインラッチでラッチされた所定の状態はプログラムの禁止を指定する(Vddなどの)状態へ引っ張られる接続ビットライン211を結果として生じることになる。以下説明するようにこの特徴はプログラム禁止用として利用される。

【0056】

共通部分220は、プロセッサ222と、データラッチセット224およびデータラッチセット224とデータバス231間で結合された入出力インターフェイス226とを備える。プロセッサ222は計算を実行する。例えば、プロセッサ222の機能の1つとして、検知されたメモリセルのメモリ状態の判定などがあり、判定されたデータはデータラッチセットの中へ蓄積される。背景技術の欄で説明したように、メモリセルは電荷範囲を保持することが可能であり、したがって、しきい値電圧ウィンドウ内の任意のしきい値電圧レベル(すなわち、所定の導通電流に合わせてセルをオンに転換したばかりのコントロールゲート電圧)に合わせてプログラミングを行うことが可能となる。データラッチセット224を利用して、読み出し処理中にセンスアンプが検知した電流から、プロセッサにより判定されたデータビットが蓄積される。このデータラッチセット224は、データバス231からインポートされたユーザデータビットをプログラム処理中にホスト(図示せず)から蓄積するためにも用いられる。これらのインポートされたデータビットは、メモリの中へプログラムされたデータの書き込みを意図した書き込みデータを表すものである。入出力インターフェイス226はデータラッチセット224とデータバス231間のインターフェイスを提供する。

【0057】

読み出し中や検知中、処理は、アドレス指定したセルへの異なるコントロールゲート電圧の供給を基本的に制御し、種々のデータラッチに対して適当なロードを行うようにプロセッサに指図し、センスアンプを付勢する状態マシン(図示せず)の制御下にある。メモリがサポートしている種々のメモリ状態に対応する種々の予め定義されたコントロールゲート電圧を通って、処理がステップするにつれて、センスアンプ212はこれらの電圧のうちの1つの電圧でトリップすることになる。その時点で、プロセッサ222は、センスアンプのトリッピングイベント、並びに、状態マシンからの入力ライン223を介して印加されたコントロールゲート電圧に関する情報を考慮することにより、結果として生じるメモリ状態を決定する。次いで、プロセッサ222は、メモリ状態用の2進符号化を計算し、結果として生じるデータビットをデータラッチセット224の中へ蓄積する。状態マシンはモジュール200内の回路ブロックのすべての回路ブロックと通信を行う。

【0058】

SA/ビットラインラッチ214は、センスアンプ212の出力をラッチするラッチとして、および、図7と関連して説明したビットラインラッチとしての2つの任務の双方の役割を果たすことが可能である。したがって、SA/ビットラインラッチ214は、センスアンプか、プロセッサかのいずれかによってセットすることが可能となる。好ましい実施構成では、SA/ビットラインラッチ214からの信号はドライバ(図示せず)により駆動されて、選択したビットライン211の電圧によりセットされる。

【0059】

図7を参照してわかるように、プログラム中または検証中、プログラム対象データはデータバス231からデータラッチセット224の中へ入力される。状態マシンの制御下にあるプログラム処理には、アドレス指定されたセルのコントロールゲートに印加された一連のプログラミング電圧パルスが含まれる。個々のプログラミングパルスの後に、セルが所望のメモリ状態にプログラムされたかどうかを判定するリードバックが後続する。プロセッサ222は、所望のメモリ状態と比較しながらメモリ状態のリードバックをモニタする。2つのメモリ状態が一致すると、プロセッサ222はビットラインラッチ214をセットして、プログラミングの禁止を指定する状態へビットラインを引っ張らせるようにする。こうすることによって、たとえ、プログラミングパルスがセルのコントロールゲート上に生じたとしても、セルと結合したビットラインのさらなるプログラミングは禁止されることになる。

【0060】

入出力インターフェイス226は、データラッチのセット224の中で、または、データラッチのセット224の中からデータのトランスポートを可能にする。図8Aと図8Bでわかるように、読み出し/書き込みモジュールのブロックはメモリデバイスの中で同時に使用されて、一度にデータブロックを読み出したり、プログラムしたりする。典型的には、読み出し/書き込みモジュールのブロックには、シフトレジスタの形成のために合成されたモジュールの個々のセットのデータラッチが含まれ、読み出し/書き込みモジュールのブロックによりラッチされたデータをデータバス231へ連続的に転送して外へ出力できるようになっている。同様に、読み出し/書き込みモジュールのブロック用のプログラミングデータをデータバス231から連続的に入力し、それぞれのデータラッチセットの中へラッチすることができる。

【0061】

コンパクトな読み出し/書き込み回路

このアーキテクチャの1つの注目すべき特徴として、同時に動作している読み出し/書き込みモジュールのブロックの場合、個々のモジュールを分割して、コア部分と共通部分とに変え、コア部分のブロックに、共通部分の数よりも実質的に少数のブロックを動作させ、共通部分の数よりも実質的に少数のブロックを共有させるようにするという特徴がある。このアーキテクチャにより、個々の読み出し/書き込みモジュールの間の複製回路の構成要素の一部を取り除くことが可能となり、それによって空間および電力の節減が行われる。高密度のメモリチップ設計では、メモリアレイ用の読み出し/書き込み回路全体の50%程度まで空間の節減を行うことが可能となる。こうすることによって読み出し/書き込みモジュールを高密度でパックすることが可能となり、その結果、読み出し/書き込みモジュールはメモリアレイの隣接した切れ目なく連続するメモリセル行として機能することが可能となり、それによって行内のセルのすべての同時プログラミングまたは読み出しが可能となる。

【0062】

図8Aは、仕切られた読み出し/書き込みスタックのバンクを有するコンパクトなメモリデバイスを本発明の1つの実施形態に従って概略的に示す。メモリデバイスは、メモリセル300の2次元アレイと、制御回路310と、読み出し/書き込み回路370とを備える。メモリアレイ300は行デコーダ330を介してワードラインにより、並びに、列デコーダ360を介してビットラインによりアドレス可能である。読み出し/書き込み回路370は仕切られた読み出し/書き込みスタック400のバンクとして実現され、メモリセルのブロックの同時読み出しまたは同時プログラミングが可能となる。1つの実施形態では、メモリセル行はマルチブロックに分割され、ブロックマルチプレクサ350が設けられて、個々のブロックへの読み出し/書き込み回路370の多重化が行われる。読み出し/書き込みスタック400間の通信がスタックバスによって行われ、さらにスタックバスコントローラ430によって制御される。

【0063】

制御回路310は、メモリアレイ300でメモリ処理を実行するために読み出し/書き込み回路370と一体に動作する。制御回路310は状態マシン312、チップアドレスデコーダ314およびパワー制御モジュール316を備える。状態マシン312はメモリ処理のチップレベル制御を行う。オンチップアドレスデコーダ314は、ホストが使用するアドレスインターフェイスまたはデコーダ330と370とが使用するハードウェアアドレスとつながるメモリコントローラを提供する。パワー制御モジュール316は、メモリ処理中にワードラインとビットラインとへ供給される電力および電圧を制御する。

【0064】

図8Bは、図8Aに示されているコンパクトなメモリデバイスの好ましい配置構成を例示する。種々の周辺回路によるメモリアレイ300へのアクセスがアレイの対向する側に左右対称に実現され、それによって個々の側部のアクセスラインと回路とが半分に減少するようになっている。この結果、行デコーダは行デコーダ330Aと330Bとに分割され、列デコーダは列デコーダ360Aと360Bとに分割されることになる。メモリセル行がマルチブロックに分割された実施形態では、ブロックマルチプレクサ350はブロックマルチプレクサ350Aと350Bとに分割される。同様に、読み出し/書き込み回路は、最下部からビットラインと接続する読み出し/書き込み回路370Aと、アレイ300の最上部からビットラインと接続する読み出し/書き込み回路370Bとに分割される。このようにして、読み出し/書き込みモジュールの記録密度、したがって、仕切られた読み出し/書き込みスタック400の記録密度は、個々の仕切られた読み出し/書き込みスタック400によって1/2に実質的に低減することになる。

【0065】

図8Aまたは図8Bの個々の仕切られた読み出し/書き込みスタック400には、k個のメモリセルからなるセグメントとして同時に機能する読み出し/書き込みモジュールのスタックが実質的に含まれる。個々のスタックは、図7に示されている態様でコアスタック部分と共通のスタック部分とに分割される。個々の読み出し/書き込みスタック400間の通信はスタックバス(図示せず)による相互接続によって行われ、スタックバスコントローラ430によって制御される。制御ライン(図示せず)は、スタックバスコントローラ430から読み出し/書き込みスタックのコア部分の各々へ制御信号とクロック信号とを出力する。同様に、制御ライン(図示せず)は、スタックバスコントローラ430から読み出し/書き込みスタック400の共通部分の各々へ制御信号とクロック信号とを出力する。

【0066】

同時に動作している仕切られた読み出し/書き込みスタック400のバンク全体によって行に沿うp個のセルブロックの同時読み出しまたはプログラミングが可能となる。例えば、rがバンク内のスタック数であれば、p=r*kとなる。1つの例示のメモリアレイが、p=512バイト(512×8ビット)、k=8、したがってr=512を有する場合もある。この好ましい実施形態では、ブロックは一続きのセル行全体である。別の実施形態では、ブロックは行内のセルのサブセットである。例えば、セルのサブセットは行全体の1/2若しくは行全体の1/4になることも考えられる。セルのサブセットは、切れ目なく連続する一続きのセルや、1個おきのセル、或いは1個おきの所定数のセルとなる場合も考えられる。

【0067】

図8Aに示されている実施形態では、p個のセルの各々に対してp個の数の読み出し/書き込みモジュールが存在することになる。個々のスタックがk個のメモリセルとして機能しているとき、バンク内の読み出し/書き込みスタックの総数はr=p/kによって示される。p=512バイトおよびk=8の場合の例では、rは512となる。

【0068】

前述したように、高密度でかつ高性能のメモリにおいて遭遇する1つの問題として、隣接した切れ目なく連続するセル行のブロックの同時読み出しと同時プログラミングを行う必要性と、すべてのセルに対する読み出し/書き込みモジュールを適合させる際の困難とが存在する。

【0069】

この適合化問題は、メモリアレイの対向する側に周辺回路が形成される図8Bに示されている好ましい実施形態によって多少とも解決される。読み出し/書き込み回路370A、370Bがメモリアレイ300の対向する側に形成されるとき、p個のセルブロックの1/2が最上部側からアクセスされ、別の1/2がアレイの底部側からアクセスされることになる。したがって、p/2個の数の読み出し/書き込みモジュールが個々の側部に存在することになる。この当然の結果として、個々の側部にある読み出し/書き込みスタック400はp/2個の数のビットラインまたはメモリセルとして同時に機能するだけで十分となり、したがって、バンク内の読み出し/書き込みスタックの総数はr=p/2kによって与えられることになる。p=512バイトでk=8の例では、rは256となる。このことは、図8Aに示されている実施形態と比べて、メモリアレイの個々の側部には読み出し/書き込みスタック400の個数の1/2の個数しか必要でないことを意味することになる。

【0070】

別の実施形態では、この適合化問題や別の考慮事項によって、さらに低い記録密度が決定され、セル行は2以上のインタリービングなセルブロックに分割されることになる。例えば、一方のセルブロックは偶数番号の列から得られるセルから構成され、他方のセルブロックは奇数番号の列から得られるセルから構成される。図8Aと図8Bとに示されているように、ブロックマルチプレクサ350すなわち350Aと350Bとは、偶数または奇数のブロックのいずれかのブロックへ仕切られた読み出し/書き込みスタックのバンクの切替えに利用されることになる。図8Bに示されている実施形態では、p/4個の数の読み出し/書き込みモジュールがアレイの個々の側部に設けられることになる。この場合、対向する側部の各側部にある読み出し/書き込みスタックの個数はr=p/4k個になる。したがって、さらに多くの余地が与えられて、より少数の読み出し/書き込みモジュールをぴったり適合できるようにはなるが、これは性能の低下により行われるものであり、読み出し/書き込みブロックはもはや隣接した切れ目なく連続するブロックではなくなる。

【0071】

部分的プログラム問題を解決する実施形態

前述したように、部分的プログラム問題は、図5A〜5Cおよび図10A、10Bのコード構成のようなコード構成を用いてメモリセルのプログラミングを行う際に、そして、第2のプログラミングパス中にセルのプログラミングを行うのにユーザデータすなわちホストデータが不十分なときに、状態Bに対して生じるものである。このようなイベント時にデータラッチ内の第2の(上位)ページデータがデフォルト“1”の値になるため、以下に説明するようにデフォルト“1”の値になるイベントの発生が妨げられなければ、このようなセルは、図5A〜5C、10A、10Bのコード構成の下で状態Cにプログラムされることになる。次のプログラミング処理時の後続するユーザデータすなわちホストデータによって、このようなセルが状態Bにプログラムされた状態のままであることが求められる場合、そのような状態のままであることはあり得ない。というのは、ブロック消去処理を除いてほとんどの設計がしきい値レベルの低下を許さないからである。

【0072】

本発明の1つの実施形態は、ユーザすなわちホストの上位ページデータが含まれないメモリセルの場合、プログラミング処理時の第1のプログラミングパスの後であって、しかも、第2のプログラミングパスよりも前に、このようなメモリセルのプログラミングに用いられるデータラッチ内の下位ページデータは、適当な代替データによって変位され、第2のプログラミングパス時にこのようなメモリセルのプログラミングを妨げるようにするという認識に基づくものである。この結果、この実施形態の1つの実施構成では、消去状態すなわちリセット状態Eがデータ“11”を表すか、或いはデータ“11”に対応する場合、内部データロード処理時に、このようなメモリセルから読み出されたデータラッチ内の第1のページデータすなわち下位ページデータは“1”によって変位される。このことが以下に参照する図9にさらに詳細に示されている。

【0073】

図9は、図7の回路ブロックのデータラッチの構造をさらに詳細に示す概略ブロック図である。図9に示されているように、図7のデータラッチ224は、少なくとも3つのラッチ224a、224b、224cを備えている。この例のうちの1つの例では、スタックによって使用中のk個のセル間での読み出し/書き込みスタック400内のモジュール200は、対応するメモリセルの読み出しおよび書き込み制御のために用いられる。したがって、ラッチ224a〜224cは個々に1ビットのラッチであってもよい。プログラミング処理中、ユーザデータすなわちホストデータはデータバス231と入出力インターフェイス226とを通ってラッチ内へロードされる。1つの実施形態では、第1のデータビットすなわち下位のデータビットはバス231とインターフェイス226とを介してラッチ224aの中へ第1にロードされる。このロードは、図7、図8A、図8Bのスタックのバンク内のスタック400の各スタック内の読み出し/書き込みモジュール200のすべてによって同時に行われて、ページ全体のプログラミングが意図されることになる。ページ全体は1つの行内のメモリアレイ300の中のメモリセルのすべてから構成することも可能である。これとは別に、ページ全体は、1つのセル行内のインタリーブされたページの場合、奇数ページまたは偶数ページのようなメモリアレイ300内の行の一部のメモリセルから構成されるものであってもよい。

【0074】

次いで、ページ内のメモリセルは、スタック400のバンク内のモジュール200のすべてのモジュール内のデータラッチ224a内の下位ページデータすなわち第1のページデータを用いてプログラムされる。ラッチ224a内の第1のページデータすなわち下位ページデータを用いてページ内のメモリセルをプログラムした後、第2のページデータすなわち上位ページデータがバス231とインターフェイス226とを介してラッチ224a内へロードされる。このデータはプロセッサ222によって、メモリセルの第2のパスプログラミングに備えてラッチ224cへシフトされる。前述したように、第2のパスプログラミングを行うより前に、第1のプログラミングパスの後に、第2のパスプログラミングのためのメモリセルのしきい値電圧すなわちしきい値レベルを知っている必要がある。1つの実施形態では、これは内部データロード処理によって行われ、この内部データロード処理時に、ページ内のメモリセル内の電流がスタック400のバンク内モジュール200内のセンスアンプ212により検知される。このようなセルのしきい値電圧すなわち蓄積レベル、並びに、このようなセルに対応するデータはモジュール内のプロセッサ222により判定され、次いで、モジュール内のラッチ224aに蓄積される。第2のパスプログラミング内のページをプログラムするのに十分な上位ページデータすなわち第2のページデータが存在する場合、ラッチ224aに蓄積されたデータ、並びに、ラッチ224c内のユーザすなわちホストの上位ページデータすなわち第2のページデータは、第2のパスプログラミング時のページ内のメモリセルをプログラムするために使用される。これは、以下の例で図6Aのセクタ112内のセルをプログラムする場合である。

【0075】

しかし、ページ全体をプログラムするのに上位ページデータすなわち第2のページデータが不十分な場合、これは制御回路310によって第1に検出される。図6Aおよび図6Bに例示されている例では、メモリセルの第1のページすなわち下位ページをプログラムするのに十分なデータが存在している間、第1のセクタ112用の十分なデータのみが存在することになる。したがって、ホストデータすなわちユーザデータはこのようなセクタで終了し、セクタ114、116、118用の上位ページデータすなわち第2のページデータはそれ以上存在しなくなる。このようなイベント時に、並びに、本発明の1つの実施形態では、この場合データを変位するために、状態マシン312は、メモリセルの読み出しから内部データロード処理の結果生じる代替データをラッチ224aの中へロードさせる。代替データによって内部にロードされた下位ページデータすなわち第1のページデータの変位は、不十分な上位ページデータすなわち第2のページデータが存在するメモリセルのプログラミングを制御するモジュールのデータラッチ用としてのみ生じることになる。図6Aおよび図6Bの例では、この変位は、セクタ114、116、118内のメモリセル用として行われる。セクタ112内のメモリセルのプログラミングを制御するためのモジュール内のデータラッチ224a用として、ラッチ224a内のデータは、前述した内部データのロード処理の結果として生じるデータであり続ける。したがって、データブロック112’、114’、116’、118’間の境界を追跡することによって、そして、これらのセクタのうちのどのセクタがユーザデータすなわちホストデータを有しているかいないかを追跡することによって、内部データロード時に読み出されたデータを置き換える代替データのロード処理が、第2のページデータすなわち上位ページデータを有していないページのセクタ内のセル専用として行われることになる。1つの実施形態では、ページの境界はメモリセルのプログラミングを制御するために、コントローラ回路310によってモニタされる。以下さらに詳細に説明するように、コントローラ回路すなわち回路310は適当なフラグデータを蓄積し、対応するセクタのフラグ電荷蓄積セルの中でフラグデータを適当に変更して、ホストデータが不十分な行のセクタを示すようにする。

【0076】

この実施形態では、対応するセルをプログラムするための第2のデータすなわち上位ページデータが不十分なとき、異なるモジュール内のラッチ224a内へロードされるデータを交換するために代替データが利用される。しかし、第1のプログラミングパス中にB’状態へプログラムされたセルに対してのみ部分的ページプログラム問題が生じることが知られている。第1のプログラミングパスの後、消去状態Eのまま残るセルについては、これらのセルを正確に状態Aへプログラムするか、第2のプログラミングパスの結果として正確に状態Eのまま残るようにするかのいずれかが可能である。したがって、この実施形態では、状態B’にあるセルのプログラミングを行うために代替データ“1”をラッチ224aの中へのみロードする必要がある。そして、このロードは第1のプログラミングパスの後の状態Eのセルに対しては行われない。このことは、第2のパス中、プログラミング電圧が状態B’のセルと結合するのを防ぐという効果を有するものである。これは、B’の分布状態がBの分布状態の中へさらに移行することを禁止するという効果も有するものであり、セクタ114、116、118の各セクタに対して、後続する上位ページデータが利用可能となる場合、個々のセクタは、状態EまたはB’のいずれかからプログラミングを開始することになる。このようなセルに対して、或いは、対応する第2のページデータすなわち上位ページデータを含まない、すべてのセルの代替セルとして、データラッチの中へ“1”をロードして、これらのセルをプログラムするようにすることにより、内部ロード処理の交換を行うことも可能となる。このような変形例およびその他の変形例は本発明の範囲に含まれるものである。この実施形態は、消去状態Eがデータ“11”を表す方式に限定されるものでもない。

【0077】

図5Aと図5Bに関連する前述した場合と同様、この実施形態では、たとえ第2のページデータすなわち上位ページデータを含まないセルのB’の分布状態が広範にわたるユーピン効果に起因して広がったかもしれない場合であっても、後続して隣接するセルをプログラムするとき、このような広がったB’の状態の電荷レベルは次のより高い状態Cの電荷レベル未満のままとなる。

【0078】

ラッチ224aの中へ前述したようにデータをロードして、メモリセルを読み出すことによって、内部データロードの結果として生じるデータの変位を行うことは、状態マシン312を備えた制御回路310によって、ユーザすなわちホストにとって透過的に行うことも可能である。これとは別に、プログラムシーケンスを変えることによってこのような処理の達成が可能である。プログラムアルゴリズムの中に新たなコマンドを追加せずに、ユーザすなわちホストによってどのゾーンまたはセクタがプログラムされているかをゾーン検出回路を用いて検出して、残りの1または複数のセクタまたはゾーンを選択し、包括的なリセット時にラッチ224aと224cの双方にデータ“11”を充填するようにしてもよい。すべてのこのような変形例は本発明の範囲に属するものである。

【0079】

読み出し処理

ページの境界で部分的にプログラムされたページを読み出す際に、読み出しアルゴリズムの修正を行う必要がある場合もある。というのは、完全にプログラムされたメモリセルの読み出しレベルが、完全にはプログラムされなかったメモリセルの読み出しレベルと異なる場合もあるからである。この状況は図10Aと図10Bとに図示されている。図10Aは、図6Aに例示され、前述したメモリアレイ内のメモリセル行のグループすなわちセクタ112におけるしきい値電圧レベルのメモリセルの分布状態を示す図例である。このような例では、グループすなわちセクタ112内のメモリセルのすべては第1および第2のプログラミングパス中にプログラムされたものであり、それによってこれらのセルのしきい値電圧は図5Cと図10Aの分布状態E、A、B、Cを有するようになる。しかし、セクタ114、116、118内のメモリセルの場合、これらのメモリセルは、図5A、図5Bまたは図10Bの状態EまたはB’のいずれかの状態になる。すべての4つのセクタ112、114、116、118内のセルのしきい値電圧によって表される上位ページデータすなわち第2のページデータを得るために、メモリセルが2つの異なる読み出しレベルVaおよびVcで読み出され、電圧検知モードが想定されることになる。図5Cと図10Aに示されている“1001”の上位ページすなわち第2のページ用のコード構成を得ることを意図して、読み出しレベルVaを採用する際の規定は、Vcが使用される読み出しレベルを用いる際の規定とは異なる(そして実際には正反対の)ものとなる。したがって、図11Aを参照すると、読み出しレベルVaを用いるとき、セルのしきい値電圧がVa未満(またはVaよりも大きな負の値)であれば、このようなしきい値電圧に対応する上位ページ値は“1”となる。しかし、読み出しレベルVcの場合には、この読み出しレベルVaの場合とは正反対の事実となる。したがって、読み出しレベルVcの場合、メモリセルのしきい値電圧がVc以上であれば、このようなしきい値電圧は上位ページすなわち第2のページ値“1”に対応することになるが、しきい値がVc未満であれば、このようなしきい値電圧は上位ページすなわち第2のページ値“0”に対応することになる。このような規定を用いる場合の、状態E、A、B、Cに対応する上位ページすなわち第2のページ値が図11Aに示されている。読み出しレベルVaおよびVcを含む2つの読み出し値の結果生じる2つの値が論理和の形で組み合わされると、その組み合わせによって、図5Cと図10Aに例示されている第2のページすなわち上位ページ用のコード構成“1001”が産みだされる。したがって、状態EおよびC用の2つの値の組み合わせの結果生じる2つの読み出し値によって、上位ページすなわち第2のページ値“1”が結果として生じることになり、一方、状態AおよびBの結果生じる2つの読み出し値の組み合わせによって、上位ページすなわち第2のページ値“0”が結果として生じることになる。

【0080】

グループすなわちセクタ112内のメモリセルを読み出すための前述した規定と同じ規定も適用して、グループすなわちセクタ114、116、118において部分的にプログラムされたメモリセルを読み出し、それによって通常行われるアルゴリズムを用いて、選択ワードラインに沿ったすべてのセルを同時に読み出すことが可能となる。次いで、読み出し値が論理和で同様に組み合わされ、図11Aに例示されているように上位ページすなわち第2のページ値の出力処理が行われる。次いで、このような上位ページすなわち第2のページ値はラッチ224cに蓄積され、図9のプロセッサ222によって、入出力インターフェイス226を通ってラッチ224aとバス231とへシフトされる。これから観察されることとして、メモリセルが完全にプログラムされているか、単に部分的にのみプログラムされているかにかかわらず、すべてのメモリセル値の上位ページすなわち第2のページの読み出しを行うために、同じ組の読み出しレベル(VaおよびVc)を利用することも可能であるということが挙げられる。

【0081】

しかし、下位ページすなわち第1のページ値を読み出すとき、ページ内のすべてのメモリセルが完全にプログラムされているか否かに応じて、その結果は異なるものとなる。したがって、グループすなわちセクタ112内のメモリセルの場合、図10Aに示されているようにセルのすべては状態E、A、B、Cへプログラムされ、それによって印加すべき読み出しレベルはVbとなる。グループすなわちセクタ114、116、118内のメモリセルは第1のプログラミングパス時にのみプログラムされ、第2のプログラミングパス時にはプログラムされない。その結果、メモリセルのしきい値電圧の分布状態は図5A、図5Bまたは図10Bに示されているようになる。図5Bを参照して前述したように、図5Bと図10Bの分布状態B’はユーピン効果に起因して広がっている。下位ページデータすなわち第1のページデータがグループすなわちセクタ114、116、118内のセルから読み出されるとき、読み出しレベルはVbではなくVaとすることが望ましい。

【0082】

1つの実施形態では、すべてのセクタ112、114、116、118内のメモリセルは、すべて読み出しレベルVbと共にシーケンシャルに読み出され、次いで、読み出しレベルVaと共に読み出され、図11Bに示されている結果が得られることになる。このVaとVb双方の読み出しの際に用いる規定は、下位ページすなわち第1のページのしきい値電圧がVb未満であれば、ビット値は“1”とし、下位ページすなわち第1のページのしきい値電圧がVb以上であれば、ビット値は“0”とするというものである。図11Bから観察されるように、グループすなわちセクタ112内のメモリセルを読み出す場合、読み出しレベルVbを用いる読み出しのみが有効となり、グループすなわちセクタ114、116、118のうちの任意の1つのメモリセルを読み出す場合、読み出しレベルVaを用いる読み出しが有効となる。1つの実施形態では、2つの異なる読み出しレベルを用いて2つの読み出し処理を容易にするために、読み出し電圧Vbを用いる読み出し処理の結果生じる下位ページすなわち第1のページ値はラッチ224cに蓄積され、そして読み出しレベルVaを用いて得られる下位ページすなわち第1のページ値はラッチ224bに蓄積されることになる。次いで、読み出し中のメモリセルが完全にプログラムされたかあるいは単に部分的にのみプログラムされたかに応じて、2つのラッチ224bと224cのうちの一方の値は、このようなセルから読み出された下位ページすなわち第1のページ値として、ラッチ224aへシフトされ、次いで、インターフェイス226を通ってデータバス231へ送信されることになる。

【0083】

完全にプログラムされたセルと、単に部分的にプログラムされたセルとを区別することができるようにするために、フラグ電荷蓄積セルが利用される。前に参照した米国特許出願第10/237,426号(特許文献21)並びに、シバタらの米国特許第6,657,891号(特許文献22)に開示されているように、フラグセルはメモリアレイ内のメモリセル行の中に組み込まれ、これらのフラグセルは読み出し処理時にメモリセルと共に読み出される。したがって、米国特許第6,657,891号(特許文献22)に記載されているアーキテクチャ(図3に関して記載したものなど)と同じアーキテクチャを採用して、メモリアレイ300内の少なくともいくつかの行の各々の中に対応するフラグ電荷蓄積セルを組み込むようにしてもよい。セクタの各々には少なくとも1つの対応するフラグ電荷蓄積セルが含まれる。セクタ112、114、116、118内の対応するフラグセルの位置は図6Aの矢印FCによって示されている。シバタらの特許に記載されているような1つの実施構成では、第1のプログラミングパス中にフラグセルの第1のページすなわち下位ページビットは状態“1”のまま残り、“0”へ変えられることはない。第2のページをプログラムする第2のプログラミングパス中、フラグセルの第2のページすなわち上位ページビットは“1”から“0”へ変えられて、第2のプログラミングパスが行われたことが示される。前述したように、第2のプログラミングパス中、メモリセルが読み出されて、この内部データのロード処理時に下位ページのビット値が得られることになる。好ましくは、この内部データのロード処理中、下位のすなわち第1のフラグビットも“1”から“0”へ変えられることが望ましい。したがって、第2のプログラミングパスの終了後、上位および下位の(第2および第1の)フラグセルのフラグビットの双方は“11”から“00”へ変えられている。1つの実施形態では、第1および第2の(下位および上位)ページのビット値の変動は制御回路310によって実行することも可能である。或いは、適当なビット値を(単複の)フラグセルに制御回路310により蓄積することも可能である。

【0084】

フラグデータの値を用いて、ホストデータすなわちユーザデータの終端部のようなホストデータすなわちユーザデータの境界にマークを付すことも可能である。前述した例では、第2のパス中にプログラムされた(単複の)フラグセルのセクタすなわちグループ内のフラグデータが値“00”を有することになるのに対して、第2のパス中のプログラムされなかったフラグセルのセクタすなわちグループ内のフラグデータは値“11”を有することになる。次いで、(単複の)フラグセルの2つの隣接するセクタすなわちグループのビット値が“11”と“00”の間で変わるとき、2つの隣接するセクタすなわちグループ内の電荷蓄積素子に蓄積されたホストデータすなわちユーザデータの境界が示されることになる。(共通のワードラインによって制御される複数のセクタすなわちグループ間の2つのような)2つの隣接するセクタすなわちグループ間の連結部でホストデータすなわちユーザデータの終端部を示すようにすることも可能であり、これらの隣接セクタすなわちグループのフラグデータは連結部の両端にわたって“11”から“00”へ変化する。フラグデータの値を追跡することによって、以下に説明するような電荷蓄積素子の読み出しのようなエラーを含む結果の防止を図ることが可能となる。

【0085】

読み出し処理時に、読み出しレベルは、読み出し対象のメモリセルが完全にプログラムされているか、或いは単に部分的にプログラムされているかに依って決められる。このことは、読み出し対象のメモリセル行内に組み込まれたフラグビットの読み出しにより確かめることが可能となる。前述したように、第2のプログラミングパスの内部データロードの処理中に、下位のフラグビットすなわち第1のフラグビットも“1”から“0”へ変更される。したがって、この下位のフラグビットすなわち第1のフラグビットの読み出しの際に、正確な読み出しレベルの決定が可能となる。すなわち、このビットが“1”であれば、読み出しレベルはVaとなるが、このビットが“0”であれば、読み出しレベルはVbとなる。これは、ページが単に部分的にプログラムされているページの境界を除いて、すべてのメモリセルが完全にプログラムされているメモリアレイ300内の行のほとんどでメモリセルの読み出しを行う場合にも真となる。したがって、2つのフラグビットの各々を“0”にセットすることによって、ページ内のメモリセルから読み出される、読み出しレベルVbを含むページ用の下位ページすなわち第1のページを第1のすなわち下位のフラグビットの読み出しと共に終了することが可能となる。したがって、ページ全体が完全にプログラムされたほとんどのインスタンスでは、フラグビットの検知および状態マシンの調整が可能となり、その結果読み出しレベルVaを用いて第2の読み出し処理を行う必要性がなくなることになる。したがって、フラグデータの読み出し結果に依存して、下位ページすなわち第1のページ値をセルから読み出すための読み出しレベルの別のシーケンスを印加することも可能となる。ページ内のセルのすべてが完全にプログラムされていることがフラグデータによって示された場合、読み出しレベルVbを伴う1回だけの読み出し処理で充分となるのに対して、ページ内のセルのすべてが完全にプログラムされているわけではないことがフラグデータによって示された場合、読み出しレベルVbの後に読み出しレベルVaを伴う2回の読み出し処理が必要とになる。この結果、異なる読み出しシーケンスが利用可能となり、読み出されたフラグデータの値に応じて適当なシーケンスが選択され、利用されることになる。

【0086】

前述したことから、部分的にプログラムされたページを読み出すにはさらに多くの時間が必要となることは明らかである。というのは、完全にはプログラムされていないページ内のセクタ用の2つの異なる読み出しレベルで下位のすなわち第1のページデータがシーケンシャルに読み出されるからである。この目的のために、図8Aおよび図8Bの制御回路310内の状態マシン312は、ページを充填するのにデータが不十分であると判定されると、バス301内の読み出し/話中信号ライン(個々には図示せず)を介して話中信号をホストコントローラへ送信する。次いで、この状態マシンはそのタイミング信号を調整して、完全にはプログラムされていないメモリセルの読み出し処理用としてさらに多くの時間を許可することになる。制御回路310は、フラッシュメモリからデータの読み出しを行う際にさらに多くの呼出し時間があることをユーザに認知させるように順次ホストコントローラに通知する。

【0087】

ダミーの時間を用いてキャッシュタイミングと共にしきい値電圧または蓄積レベルを読み出す場合、“11”から“00”へのフラグビットの変更が検出されると、制御回路310内の状態マシンはしきい値電圧の蓄積レベルを読み出すためのダミーの時間を長くして、2つの異なる読み出しレベル用としてシーケンシャルに読み出しを行うためのさらに多くの時間を許可するようにする。

【0088】

図12は、しきい値電圧の分布状態、並びに、新規の代替のコード構成に従ってこの分布状態により表されたデータの例であり、本発明の別の実施形態を例示するものである。図10Aおよび図12の比較によって、これら2つのコード構成が、図12の新たなコード構成では、しきい値電圧の分布状態Bが“10”を表し、しきい値電圧の分布状態Cが“00”を表すという点で異なるものであることは明らかでる。これに対して、図10Aのコード構成では、分布状態Bは“00”を表し、分布状態Cは“10”を表している。図10Aおよび図12の比較によって、双方のコード構成における4つの異なる分布状態E、A、B、Cが同じ下位ページすなわち第1のページ値“1100”を有するものであることも明らかになる。第1のプログラミングパス中に図12の新たなコード構成を用いる場合、メモリセルはプログラムされず、その結果、このメモリセルは、ホストデータが“1”の場合の状態Eのままとなるか、またはホストデータが“0”の場合の分布状態B’にプログラムされるかのいずれかとなる。第2のプログラミングパス中、上位ページすなわち第2のページのビット値が“1”であれば、メモリセルはプログラムされず、その結果、このメモリセルは分布状態Eのままとなるか、或いは分布状態Bへ狭められた状態になる。ユーザデータが“0”であれば、第1のプログラミングパスの後に、メモリセルの初期分布状態に応じてメモリセルは分布状態AまたはCにプログラムされる。この結果、図5Cおよび図10Aのコード構成のユーピン効果の場合と類似して、図12の新たなコード構成もユーピン効果を小さくすることになる。

【0089】

図12から、第1のプログラミングパスにおける上位ページすなわち第2のページの状態EおよびBの値の双方が“1”であることが明らかである。このことは、ホストデータすなわちユーザデータがページ全体を充填するのに不十分な場合、データラッチ内のユーザデータを利用して第2のプログラミングパス時にメモリセルをプログラムする際、上位ページデータすなわち第2のページデータが不十分なメモリセルが、エラーを含む分布状態へプログラムされないことを意味することになる。これは、図5Cおよび図10Aのコード構成を使用する状況とは異なり、セルが状態Eまたは状態B’であるかどうかにかかわらず真である。ホストデータが第1のページすなわち下位ページ用のデータ“0”を有し、しかも、位置122’用の第2のページすなわち上位ページ用のデータが存在しない場合の図6Bの例を再度参照すると、この位置用の第2のページすなわち上位ページ用のデフォルト値は“1”となり、その結果位置122’は値“10”で充填されることになる。この値は、図10Aではコード構成に従う分布状態Cへのプログラミングを必要とするが、図12ではコード構成に従う分布状態Bへのプログラミングを必要とする。ホストデータの下位ページすなわち第1のページ値が“0”であるため、セクタ114内の対応するメモリセルは第1のプログラミングパス時に状態B’へすでにプログラムされていて、状態Bの方へほんのわずかこのメモリセルを動かす必要がある。個々のセクタ114、116、118が状態EまたはB’の状態のまま残っている従来の実施形態とは対照的に、この実施形態では、上位ページデータを用いて第1のセクタ112をプログラムするとすぐに、以前状態B’にあったそのページの他のすべてのセルが状態Bへ動かされることに留意されたい。したがって、新たなホストデータが、ページのセクタ114、116、118内のメモリセルの第2のページすなわち上位ページをプログラムするのに再び利用可能になると、これらのセクタ内のメモリセルはすでに正確なしきい値電圧の分布状態にあることになる。

【0090】

図12に例示するコード構成を利用することによって、前述した部分的ページプログラミングは生じなくなることが観察される。第1のプログラミングパスの後の第2のページすなわち上位ページの同じ値によって、セルに対する2つの可能な蓄積レベルを表す場合、同じ文脈で図12のコード構成とは異なるコード構成を用いて、部分的ページプログラム問題の解決を図ることが可能となる。2つの可能な状態が、図5Cと図10Aの消去(すなわち、リセット)状態で、かつ、B状態である場合、双方の状態の第2のページ値は同じとなることが望ましい。この場合、部分的ページプログラム問題は生じなくなる。

【0091】

図12ではコード構成に関して部分的ページプログラム問題が生じないため、ページの個々のセクタ用として別個のフラグ記憶セルを設ける必要はなくなる。上位および下位の(第1および第2の)ページビット値の双方の値が、図12のコード構成では分布状態AとBとの間で変動し、その結果、コード構成はグレーコードとはならないことも図12から明らかである。このことは、(例えば当業で周知の種々の種類の妨害メカニズムを通じて)分布状態がBからAへドリフトした場合、ビットエラーが論理データの2つのページで検知され、次いで、このコード構成を利用する場合、さらに多くの誤り訂正(ECC)ビットが望ましくなる場合が生じることを意味する。さらに、上位すなわち第2のページ値情報をメモリセルから得るために、3つの異なる読み出しレベルで読み出しを行う必要がある場合もある。その結果、この場合の読み出し時間の方が図10Aのコード構成を採用する場合の読み出し時間と比べて長くなる。しかし、図12のコード構成は、図9のデータラッチ224bのような追加のデータラッチを必要としないという点で利点がある。

【0092】

この設計に対する1つの可能な代替例として、独立に制御される読み出し/書き込みモジュールによって、図6Aの4つのセルグループ112、114、116、118を制御することができるようにする例が挙げられる。この代替例は、部分的ページプログラム問題を解決する際にさらなる柔軟性を与えることになるものではあるが、メモリデバイスのダイサイズを大きくするものとなる。図10および図12の双方の方式の1つの利点として、読み出し/書き込みモジュールを簡単に制御することができるため、ダイサイズが大きくならないという利点、或いは、少量だけ増えるという利点が挙げられる。

【0093】

以上、種々の実施形態を参照しながら本発明について説明してきたが、添付の請求項並びにこれらの請求項と均等なものによって画定される本発明の範囲から逸脱することなく、変更並びに修正を行うことも可能であることを理解されたい。例えば、実施形態はNANDアレイでの動作を参照しながら説明することもできるが、この実施形態はNORアレイに対しても同様に適用可能であり、このような変形例およびその他の変形例は本発明の範囲に含まれるものとする。4つのセクタに個々にグループ化されたメモリセル行を参照しながら本発明を例示したが、これらのメモリセル行はさらに多数のまたはさらに少数のセクタにグループ化することも可能であり、このような異なるグループ化方式の場合にも本願明細書で説明した利点と同じ利点を利用することが可能となる。本願明細書で参照したすべての参考文献は参照により援用されている。

【技術分野】

【0001】

本発明は一般に、電気的に消去可能でプログラム可能なリードオンリメモリ(EEPROM)およびフラッシュEEPROMのような不揮発性半導体メモリに関し、特に、改善された部分的ページプログラミング機能を備えた不揮発性半導体メモリに関する。

【背景技術】

【0002】

不揮発性の電荷蓄積能力を有する固体メモリデバイス、特に、小形のファクタカードとしてパッケージ化されたEEPROMおよびフラッシュEEPROMの形の固体メモリデバイスは、最近、様々な移動用デバイスや携帯用デバイス(特に情報機器および消費者用電子製品)において選好されるメモリデバイスになっている。内蔵形カードおよび取り外し可能カードの双方の形のフラッシュメモリは、その小形サイズ、少ない消費電力、高速性、並びに、高い信頼性という特徴のために移動環境や携帯環境で理想的に好ましいメモリデバイスである。

【0003】

EEPROMは、ソース領域とドレイン領域間の、半導体基板のチャネル領域にわたって配置される電界効果トランジスタ構造内のフローティング(接続されていない)導電性ゲートを利用するものである。このフローティングゲートにわたってコントロールゲートが設けられる。トランジスタのしきい値電圧特性はこのフローティングゲートに保持されている電荷量により制御される。すなわち、フローティングゲートの所定の電荷レベルに対して、そのソース領域とドレイン領域間の導通を可能にするためにトランジスタを“オン”に転換する前に、コントロールゲートに印加しなければならない対応する電圧(しきい値)が生じる。

【0004】

このフローティングゲートは電荷範囲の保持が可能であり、したがって、しきい値電圧ウィンドウ内の任意のしきい値電圧レベルにセットしてプログラミングを行うことが可能となる。しきい値電圧ウィンドウのサイズはデバイスの最小しきい値レベルと最大しきい値レベルとによって画定され、この最小および最大しきい値レベルがフローティングゲート上へのプログラム可能な電荷範囲に対応するしきい値レベルとなる。このしきい値ウィンドウは、一般にメモリデバイスの特性、動作条件および履歴に依って決まる。原則として、このウィンドウ内の個別の分解可能な各しきい値電圧レベルの範囲を用いて、セルの明確に限定されたメモリ状態を示すことが可能となる。

【0005】

メモリセルとして機能するトランジスタは典型的には2つのメカニズムのうちの一方によって“プログラム”状態へプログラムされる。“熱い電子注入”時に、ドレインに印加される高い電圧により電子は基板チャネル領域の両端にわたって加速される。同時に、コントロールゲートに印加される高い電圧によって熱い電子は薄いゲート誘電体の中を通ってフローティングゲート上へ引っ張られる。“トンネリング”注入時に、基板に対して相対的に高い電圧がコントロールゲートに印加される。このようにして、電子は基板から中間に介在するフローティングゲートへ引っ張られることになる。

【0006】

複数のメカニズムによってメモリデバイスを消去することも可能である。EEPROMの場合、コントロールゲートに対して相対的に高い電圧を基板に印加することによってメモリセルを電気的に消去し、基板チャネル領域(すなわち、ファウラー−ノードルハイム (Fowler-Nordheim)のトンネリング)までフローティングゲート内の電子を誘導して薄い酸化膜を貫通するようにすることが可能である。典型的には、EEPROMはバイト毎に消去可能である。フラッシュEEPROMの場合、一度にすべてか、1回につき1以上のブロックかのいずれかのメモリの電気的消去が可能であり、その場合、512バイトまたはそれ以上のメモリからブロックを構成することも可能である。

【0007】

不揮発性メモリセルの例

メモリデバイスはカードに装着可能な1以上のメモリチップを通常備えている。個々のメモリチップはメモリセルからなるアレイを備え、これらのメモリセルは、デコーダ並びに消去回路、書き込み回路および読み出し回路のような周辺回路によってサポートされている。インテリジェントで、より高いレベルのメモリ処理とインターフェイスとを実行するコントローラを備えたさらに複雑なメモリデバイスも出現している。今日利用されている多くの商業的に成功を納めた不揮発性固体メモリデバイスが存在する。これらのメモリデバイスは異なるタイプのメモリセルを採用することも可能であり、これら個々のタイプは1以上の電荷蓄積素子を含むものであってもよい。

【0008】

図1A〜図1Eは、不揮発性メモリセルの様々な例を概略的に示す。

図1Aは、電荷を蓄積するためのフローティングゲートを備えたEEPROMセルの形で不揮発性メモリを概略的に示す。電気的に消去可能でプログラム可能なリードオンリメモリ(EEPROM)は類似の対応する構造を有しているが、さらにこれに加えて、このリードオンリメモリは、UV輻射線に曝す必要なく、適当な電圧の印加時に電荷をロードしたり、そのフローティングゲートから電気的に電荷を除去したりするメカニズムを提供するものである。米国特許第5,595,924号(特許文献1)にこのようなセル並びにこれらのセルの製造方法の例についての記載がある。

【0009】

図1Bは、選択ゲートとコントロールゲート(ステアリングゲート)の双方のゲートを備えたフラッシュEEPROMセルを概略的に示す。メモリセル10はソース拡散部14とドレイン拡散部16との間に“分割チャネル”12を有している。2つのトランジスタT1とT2とを直列に備えたセルが効率良く形成される。T1は、フローティングゲート20とコントロールゲート30とを備えたメモリトランジスタとして機能する。フローティングゲートは選択可能な電荷量の蓄積が可能である。チャネルのT1部分を通って流れることが可能な電流量は、コントロールゲート30にかかる電圧と、間に介在するフローティングゲート20に存在する電荷量とに依存して決まる。T2は、選択ゲート40を備えた選択トランジスタとして機能する。選択ゲート40において或る電圧によりT2をオンに転換すると、T2によって、チャネルのT1部分の電流がソースとドレイン間を通ることが可能となる。選択トランジスタはコントロールゲート側での電圧に依存しないソースドレインチャネルに沿ったスイッチを提供する。1つの利点として、これを用いて、セルのフローティングゲート側でのこのセルの(正の)電荷空乏に起因して生じるゼロコントロールゲート電圧でも、まだ導通を行っているセルをオフに転換することができるという点が挙げられる。別の利点として、これによってソース側注入プログラミングのさらに容易な実現が可能となる。

【0010】

分割チャネルメモリセルの1つの単純な実施形態として、図1Bに示されている点線によって概略的に示すように選択ゲートとコントロールゲートとを同じワードラインと接続する実施形態がある。この接続は、チャネルの一方の部分にわたって電荷蓄積素子(フローティングゲート)を配置させ、チャネルの他方の部分にわたって、並びに、電荷蓄積素子にわたって(ワードラインの一部である)コントロールゲート構造を配置させることにより達成される。この結果、2つのトランジスタ、すなわち、電荷蓄積素子にかかる電荷量と、チャネルのトランジスタの部分の中を通って流れることができる電流量の制御を行うワードラインにかかる電圧との組み合わせを有する一方のトランジスタ(メモリトランジスタ)、並びに、トランジスタのゲートの例として単独で機能しているワードラインを有する他方のトランジスタ(選択トランジスタ)を直列に備えたセルが形成される。このようなセルのいくつかの例、メモリシステムにおけるこれらセルの利用およびこれらセルの製造方法については、米国特許第5,070,032号(特許文献2)、第5,095,344号(特許文献3)、第5,315,541号(特許文献4)、第5,343,063号(特許文献5)、第5,661,053号(特許文献6)に記載されている。

【0011】

図1Bに示されているさらに改善された分割チャネルセルの実施形態として、選択ゲートとコントロールゲートとが独立し、このゲート間が点線によって接続されない場合の実施形態がある。1つの実施構成は、ワードラインに対して垂直に伸びる制御(ステアリング)ラインと接続されたセルアレイ内に1列のコントロールゲートを有する。この結果、選択されたセルの読み出しまたはプログラミングの際に、2つの機能を同時に実行する必要性からワードラインは解放されることになる。2つの機能とは、(1)選択トランジスタのゲートとしての機能であり、したがって、選択トランジスタをオン/オフに転換するための適当な電圧を必要とする機能と、(2)ワードラインと電荷蓄積素子間での電界(容量性)結合を通じて電荷蓄積素子の電圧を所望のレベルに合わせて駆動する機能である。単一の電圧を用いて最適の態様でこの機能の双方を実行することはしばしば困難となる。コントロールゲートと選択ゲートとを独立に制御すれば、追加の制御ラインが機能(2)を実行している間、ワードラインは機能(1)を実行するだけで十分となる。この能力は、より高い性能のプログラミング設計をサポートするものとなり、その場合、プログラミング電圧は目標データに適合されることになる。フラッシュEEPROMアレイにおける独立したコントロール(すなわち、ステアリング)ゲートの利用については、例えば、米国特許第5,313,421号(特許文献7)および第6,222,762号(特許文献8)に記載されている。

【0012】

図1Cは、デュアルフローティングゲートと、独立した選択ゲートとコントロールゲートとを備えた別のフラッシュEEPROMセルを概略的に示す。メモリセル10は、直列の3つのトランジスタを効率良く備えていることを除いて、図1Bのメモリセルと同様のメモリセルである。このタイプのセルでは、2つの蓄積素子(すなわち、T1左とT1右の蓄積素子)がそのチャネルを介してソースとドレイン拡散部との間に選択トランジスタT1を備えて設けられる。これらのメモリトランジスタは、フローティングゲート20と20’と、コントロールゲート30、30’とをそれぞれ有している。選択トランジスタT2は選択ゲート40によって制御される。任意の時点で、このメモリトランジスタのうちの一方だけが読み出しまたは書き込みのためにアクセスされる。記憶ユニットT1左がアクセスされているとき、T2とT1右の双方がオンに転換されて、チャネルのT1左の部分の電流がソースとドレインとの間を通ることが可能になる。同様に、記憶ユニットT1右がアクセスされているとき、T2とT1左がオンに転換される。フローティングゲートの近傍に選択ゲートのポリシリコンの一部を設けることにより消去が行われ、さらに、フローティングゲート内に蓄積された電子を選択ゲートのポリシリコンまでトンネリングすることができるように、極めて大きな正の電圧(例えば、20Vなど)が選択ゲートに印加される。

【0013】

図1Dは、NANDセルに編成された一連のメモリセルを概略的に示す。NANDセル50は、一連のメモリトランジスタM1、M2、...Mnのソースとドレインとによってデイジチェーンされた一連のメモリトランジスタM1、M2、...Mn(n=4、8、16またはこれよりも大きな数)から構成される。NANDセルのソース側端子54およびドレイン側端子56を介して、一対の選択トランジスタS1、S2が、このメモリトランジスタチェーンの外部との接続を制御する。メモリアレイにおいて、ソース選択トランジスタS1がオンに転換されると、ソース側端子はソースラインと結合される。同様に、ドレイン選択トランジスタS2がオンに転換されると、NANDセルのドレイン側端子はメモリアレイのビットラインと結合される。チェーンの形でつながれた個々のメモリトランジスタは、意図するメモリ状態を表すために所定の電荷量を蓄積する電荷蓄積素子を有している。個々のメモリトランジスタのコントロールゲートは、読み出し処理および書き込み処理に対する制御を行う。選択トランジスタS1、S2の各々のコントロールゲートは、それぞれ、そのソース側端子54およびドレイン側端子56を介してNANDセルに対するアクセスを制御する。

【0014】

NANDセル内のアドレス指定したメモリトランジスタがプログラミング中に読み出され、検証されると、そのコントロールゲートには適当な電圧が供給される。同時に、NANDセル50内の残りのアドレス指定されていないメモリトランジスタは、このメモリトランジスタのコントロールゲートにかけられる十分な電圧の印加によって全部オンに転換される。このようにして、導電経路は個々のメモリトランジスタのソースからNANDセルのソース側端子54まで、そして同様に、個々のメモリトランジスタのドレイン用として、セルのドレイン側端子56まで効率的に形成される。このようなNANDセル構造を備えたメモリデバイスについては、米国特許第5,570,315号(特許文献9)、第5,903,495号(特許文献10)、第6,046,935号(特許文献11)に記載されている。

【0015】

図1Eは、電荷を蓄積する誘電体層を含む不揮発性メモリを概略的に示す。前述した導電性フローティングゲート素子の代わりに、誘電体層の個別領域が電荷蓄積素子として利用される。誘電体記憶素子を利用するこのようなメモリデバイスについては、エイタンらによる“NROM:新規の局在化トラッピング、2ビット不揮発性メモリセル”,IEEE電子デバイスレターズ,第21巻,第11号,2000年11月,543〜545ページ (Eitan et al., “NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol.21, no.11, November 2000, pp.543-545) (非特許文献1)に記載されている。ONO誘電体層はソースおよびドレイン拡散部の間のチャネルの両端にわたって延在する。1データビット用の電荷がドレインに隣接して誘電体層内に局在化され、さらに別のデータビット用の電荷がソースに隣接して誘電体層内に局在化される。例えば、米国特許第5,768,192号(特許文献12)および第6,011,725号(特許文献13)に2つのシリコン二酸化物層の間に挟まれるトラッピング誘電体を有する不揮発性メモリセルについての開示がある。多状態データ蓄積は、誘電体内で空間的に分離された電荷蓄積領域の2進状態を別々に読み出すことにより実現される。

【0016】

メモリアレイ

典型的には、メモリデバイスには、行と列とで構成され、ワードラインとビットラインとによってアドレス可能な2次元アレイのメモリセルが含まれる。このアレイはNOR形またはNAND形アーキテクチャに従って形成することができる。

【0017】

NORアレイ

図2は、NORメモリセルのアレイの一例を示す。NOR形アーキテクチャを備えたメモリデバイスは図1Bまたは図1Cに例示するタイプのセルにより実現される。個々のメモリセル行はそのソースとドレインとによってデイジチェーンで接続される。この設計を仮想接地設計 (virtual ground design)と呼ぶことがしばしばある。個々のメモリセル10は、ソース14と、ドレイン16と、コントロールゲート30と、選択ゲート40とを備えている。1行のセルにはワードライン42と接続されたこのセルの選択ゲートが設けられる。1列のセルはそのソースとドレインとを備え、これらのセルはそれぞれ選択済みのビットライン34と36と接続している。メモリセルがそのコントロールゲートと選択ゲートとを独立に制御させる実施形態によっては、ステアリングライン36が1列のセルのコントロールゲートを接続するものもある。

【0018】

多くのフラッシュEEPROMデバイスが、そのコントロールゲートと選択ゲートとを一体に接続して個々に形成されたメモリセルにより実現される。この場合、ステアリングラインを必要とせず、単にワードラインがセルのすべてのコントロールゲートと選択ゲートとを個々の行に沿って接続するだけでよい。これらの設計例が、米国特許第5,172,338号(特許文献14)および第5,418,752号(特許文献15)に開示されている。この設計では、ワードラインにより実質的に2つの機能(すなわち、行選択機能と、読み出しやプログラミングを行うための、行のすべてのセルへのコントロールゲート電圧の供給機能)とが実行される。

【0019】

NANDアレイ

図3は、図1Dに示されている例のようなメモリセルのNANDアレイの一例を示す。個々のNANDセルの列に沿って、ビットラインが個々のNANDセルのドレイン側端子56と結合される。NANDセルの個々の行に沿って、ソースラインがすべてのNANDセルのソース側端子54を接続するようにしてもよい。また、行に沿ったNANDセルのコントロールゲートも一連の対応するワードラインと接続される。接続されたワードラインを介して、この対の選択トランジスタのコントロールゲートに適当な電圧をかけて、この対の選択トランジスタをオンに転換することによりNANDセルの行全体のアドレス指定を行うことができる(図1Dを参照されたい)。NANDセルのチェーン内のメモリトランジスタが読み出されると、チェーン内の残りのメモリトランジスタが、このメモリトランジスタの関連するワードラインを介して強くオンに転換され、それによってチェーンの中を流れる電流は、読み込まれているセルに蓄積された電荷のレベルによって実質的に依存して決められることになる。メモリシステムの一部としてのNAND形アーキテクチャのアレイの一例並びにその処理は、米国特許第5,570,315号(特許文献9)と、第5,774,397号(特許文献16)と、第6,046,935号(特許文献11)とに見られる。

【0020】

ブロック消去

電荷記憶メモリデバイスのプログラミングの結果として、専ら電荷記憶メモリデバイスの電荷蓄積素子に対するさらに多くの電荷の付加が可能となる。したがって、プログラミング処理を行う前に、電荷蓄積素子内の既存の電荷を除去(または消去)する必要がある。1以上のメモリセルブロックを消去する消去回路(図示せず)が設けられる。セルアレイ全体またはアレイの大きなセルグループが電気的に一括して(すなわち、フラッシュで)消去される場合、EEPROMのような不揮発性メモリは“フラッシュ”EEPROMと呼ばれる。消去されるとすぐに、セルグループの再プログラミングが可能となる。一括消去可能なセルグループは1以上のアドレス可能な消去単位から構成することも可能である。消去単位または消去ブロックが典型的には1以上のデータページを蓄積し、このページがプログラミングおよび読み出しの単位となるが、単一の処理時に2以上のページがプログラミングや読み出しを行うようにすることも可能である。個々のページは、典型的には1以上のデータセクタを蓄積し、このセクタのサイズはホストシステムにより画定される。一例として、磁気ディスク駆動装置に関する基準規格に従う512バイトのユーザデータセクタがあり、これに加えてユーザデータおよび/またはユーザデータが蓄積されているブロックに関する或る数バイトのオーバーヘッド情報がある。

【0021】

読み出し/書き込み回路

通常の2状態EEPROMセルでは、少なくとも1つのブレークポイントレベルが確定され、導通ウィンドウの分割が行われて、2つの領域がつくられる。ブレークポイントに対する相対的なセル状態が、“電流”の検知か、“電圧”の検知かのいずれかを利用して通常決定される。電流検知を利用して、所定の固定電圧と、セルのゲートと、ソースと、ドレインとを印加することによりセルが読み出され、結果として生じる電流が、絶対値か、或いは2つの極値間の中間値に計画的にセットされたしきい値を有する同様のセルから取得される値かのいずれかの値と比較される。読み出された電流の方がブレークポイントレベルの電流よりも高い場合、セルは、1つの論理状態(例えば“0”状態など)をなすように設定される。一方、電流がブレークポイントレベルの電流よりも低い場合、セルはもう一方の論理状態(例えば“1”状態など)をなすように設定される。したがって、このような2状態セルによって1ビットのデジタル情報の蓄積が行われることになる。基準電流のソースは、外部でプログラムすることも可能ではあるが、ブレークポイントレベル電流を生成するメモリシステムの一部として提供されることも多い。

【0022】

メモリ容量を上げることを目的として、フラッシュEEPROMデバイスは、半導体技術の進歩に伴ってますます高密度になる記録密度で製造されている。記憶容量を上げる別の方法として、各メモリセルに3以上の状態を蓄積させる方法がある。

【0023】

マルチ状態またはマルチレベルEEPROMメモリセル用として、導通ウィンドウは2以上のブレークポイントにより3以上の領域に分割されるので、各セルが1ビット以上のデータを蓄積する能力を持つことができるようになる。与えられたEEPROMアレイが蓄積できる情報は、このようにして各セルが蓄積することができる状態数を用いて増やされる。マルチ状態すなわちマルチレベル・メモリセルを持つEEPROMまたはフラッシュEEPROMについては、米国特許第5,172,338号(特許文献14)に記載されている。

【0024】

実際には、セルのメモリ状態は、読み出しレベルがコントロールゲートに印加されるときのセルのソース電極とドレイン電極の両端にわたる導通電流の検知により通常読み出される。したがって、セルのフローティングゲートの各々の所定の電荷について、一定の基準コントロールゲート電圧に関連して、対応する導通電流の検出が可能となる。同様に、フローティングゲート上へのプログラム可能な電荷範囲により、対応するしきい値電圧用ウィンドウや対応する導通電流ウィンドウが画定される。

【0025】

これとは別に、仕切られた電流ウィンドウ間での導通電流の検出(電流検知)の代わりに、コントロールゲートにおけるテスト中に所定のメモリ状態用のしきい値電圧をセットし、この導通電流がしきい値電流(電圧検知)よりも低いか高いかの検出を行うことが可能である。1つの実施構成では、ビットラインの静電容量を通じる導通電流の放電レートによってチェックを行うことにより、しきい値電流を基準とする相対的な導通電流の検出が行われる。セルがプログラムされている(ゲート電圧を基準として相対的に高いしきい値である)場合、放電電流が非常に小さくなるため、ビットラインの相対的に大きな静電容量が著しく放電されることはなく、センスアンプは“0”状態に戻ることになる。

【0026】

米国特許第4,357,685号(特許文献17)に2状態EPROMのプログラミング方法が開示され、この方法では、セルは、所定の状態にセットされてプログラムされると、連続するプログラミング電圧パルスを受け、その度に増分する電荷がフローティングゲートに加えられる。パルス間で、ブレークポイントレベルと比較して、セルのソース・ドレイン電流を測定するためにセルのリードバック(検証)が行われる。電流状態が所望の状態に達したことが検証されたときプログラミングは停止する。使用するプログラミングパルス列が、増加する周期や振幅を持つ場合もある。

【0027】

従来技術によるプログラミング回路は単に、プログラミングパルスを印加して、しきい値ウィンドウを通って消去状態または接地状態から目標状態に達するまで1ステップずつ進むようにする回路にすぎない。実際に、適当な精度を可能にするには、個々の分割領域すなわち画定領域が、少なくともおよそ5つの越えるべきプログラミングステップを必要とする。その性能は2状態メモリセル用として容認することができるものである。しかし、マルチ状態セルの場合、所要なステップ数は分割の数と共に増加するため、プログラミングの精度すなわち精密さも高める必要がある。例えば、16個の状態セルでは、目標状態にセットしてプログラムするのに平均して少なくとも40個のプログラミングパルスが必要となる場合もある。

【0028】

メモリアレイ100は行デコーダおよび列デコーダを介して読み出し/書き込み回路によりアクセスを行うことが可能である。図2および図3に示されているように、メモリアレイ100内のメモリセルのメモリトランジスタは1組の選択ワードラインとビットラインとを介してアドレス可能である。行デコーダは1以上のワードラインを選択し、列デコーダは1以上のビットラインを選択して、アドレス指定したメモリトランジスタのそれぞれのゲートに対する適当な電圧の印加を図るようにする。アドレス指定したメモリトランジスタのメモリ状態の読み出しまたは書き込み(プログラム)を行うための読み出し/書き込み回路が設けられる。読み出し/書き込み回路は、ビットラインを介してアレイ内の記憶素子と接続可能な複数の読み出し/書き込みモジュールを備える。

【0029】

読み出し中または検証中に、センスアンプは、選択ビットラインを介して接続されたアドレス指定済みのメモリトランジスタのドレインの中を流れる電流を決定する。この電流はメモリトランジスタに蓄積された電荷およびこのメモリトランジスタのコントロールゲート電圧に依存して決められる。例えば、多状態EEPROMセルでは、複数の異なるレベルのうちの1つレベルに合わせてこのセルのフローティングゲートを荷電することが可能となる。4レベルセルの場合、2ビットデータを蓄積することができる。センスアンプによって検出されたレベルはレベルからビットへの変換論理回路によって1組のデータビットへ変換されて、データラッチに蓄積される。

【0030】

読み出し/書き込み性能および精度に影響を与える諸要因

読み出しおよびプログラミング性能の改善を目的として、アレイ内の複数の電荷蓄積素子またはメモリトランジスタの同時読み出しや、同時プログラミングが行われる。したがって、記憶素子の論理“ページ”の一括読み出しや、一括プログラミングが行われることになる。既存のメモリアーキテクチャにおいて、複数のインタリーブされたページは典型的には行の中に含まれる。ページのすべての記憶素子はまとめて読み出されたり、まとめてプログラムされたりすることになる。列デコーダは、インタリーブされたページの個々のページを、対応する個数の読み出し/書き込みモジュールと選択的に接続することになる。例えば、1つの実施構成では、メモリアレイは532バイト(512バイト+20バイトのオーバーヘッド)のページサイズを有するように設計される。個々の列がドレインビットラインを含み、かつ、行当たり2つのインタリーブ済みのページが存在する場合、これによって、個々のページが4256列と関連づけられて8512列に達することになる。すべての偶数番号のビットラインまたは奇数番号のビットラインのいずれかと同時に読み出しまたは書き込みを行えるように接続可能な4256個のセンスモジュールが存在することになる。このようにして、4256ビット(すなわち、532バイト)のデータページが同時に記憶素子のページから読み出されたり、或いは記憶素子のページの中へプログラムされたりする。読み出し/書き込み回路を形成する読み出し/書き込みモジュールを構成して種々のアーキテクチャに変えることも可能である。

【0031】

非常にコンパクトでかつ高性能の不揮発性メモリおよび制御方法については、“非常にコンパクトな不揮発性メモリおよびその方法”という2002年9月24日に出願されたラウル−エイドリアン・セルニアによる米国特許出願第10/254,483号(特許文献18)に記載されている。この特許出願は、その全体が本願明細書において参照により援用されている。

【0032】

図4Aと図4Bとに、前述したタイプのアレイ内の4状態NANDメモリセルのプログラミングの特定の現行技術を例示する。これら2つの図およびプログラミング処理についての添付の説明は、米国特許第6,522,580号(特許文献19)から採られたものであり、この特許は、その全体が本願明細書において参照により援用されている。

【0033】

図4Aと図4Bには、前述したタイプのアレイにおける4状態NANDメモリセルのしきい値電圧の分布状態を示し、このメモリセルにはアレイ内のセルのフローティングゲートによって2ビットデータ、すなわち個々のセル内の4つのデータ状態が蓄積される。曲線Eは、消去状態(“11”データ状態)にあるアレイ内のセルのしきい値レベルVT(負のしきい値電圧レベルにある)の分布状態を表す曲線である。セルの初期状態として、セルが前述した消去状態以外の状態にセットされた場合、本願で用いるような曲線Eもこのような状態を表すことになる。さらに一般的に言えば、消去状態を含むすべてのこのような状態を本願では“リセット状態”と呼ぶことにする。“10”と“00”のユーザデータをそれぞれ蓄積する蓄積素子のしきい値電圧の分布状態AとBとは、それぞれ0ボルトと1ボルトとの間、並びに、1ボルトと2ボルトとの間にはいるように示される。曲線Cは、“01”データ状態に合わせてプログラムされたメモリセルの分布状態を示し、最高のしきい値電圧レベルが、読み出された過去の電圧のうち2ボルトよりも大きく、かつ、4.5ボルトよりも小さいレベルとなる。“ユーザデータ”および“ホストデータ”という用語は本願では交換可能に用いられる。

【0034】

単一メモリセルに蓄積された2つのビットの各々は別の論理ページから得られ、異なる時刻にプログラムすることも可能である。2つのビットの各々は、互いから得られる別の論理ページアドレスを担持する。単一メモリセルに蓄積されたこれら2つのビットは、順序づけられた1組の2進値変数または一対の2進値変数(有意性のより高いビットおよび有意性のより低いビット)を形成する。下位ページのアドレスが入力されると、ユーザデータすなわちホストデータ“11”、“10”、“00”、“01”内のこの有意性のより低い方のビットがアクセスされる。上位ページアドレスが入力されると、ユーザデータすなわちホストデータの有意性のより高い方のビットがアクセスされる。蓄積データが3以上のビットを含む場合、順序づけられたセットの蓄積値は3以上の変数を含むものであってもよい。論理ページの指定は、偶数/奇数ページ指定またはインタリーブされたページ指定とは異なるものとなる。このようなページ指定は、メモリアレイにおけるメモリセルの物理的構成に関する指定である。しきい値ウィンドウを4状態よりも多くの状態にさらに細かく分割して、セル当たり3以上のデータビットを表すためにセルに蓄積することが可能となるところまで論理ページの指定を拡張することも可能である。これによって3以上のページが利用されるようになり、その場合、これらのページは、単に第1、第2、第3ページなどの数値として参照することも可能となる。

【0035】

前述したように、プログラム処理に先立って、1以上のメモリセルブロック(本願では電荷蓄積素子とも呼ばれる)が一括して電気的に消去されて、消去状態“11”となる。次いで、データバッファ内のユーザデータすなわちホストデータを利用して、電荷蓄積レベルまたは電荷蓄積素子のしきい値レベルがセットされる。第1のプログラミングパス時に、セルのしきい値レベルはデータバッファ内の下位の論理ページから得られるビットに従ってセットされる。このビットが“1”の場合、何も行われない。というのは、以前に消去された結果としてセルが消去状態となるからである。しかし、このビットが“0”の場合、セルのレベルは第1のプログラミング済み状態まで上げられる。この処理によって第1のプログラミングパスは終了する。

【0036】

第2のプログラミングパス時に、セルのしきい値レベルは、上位論理ページからデータバッファに蓄積されるビットに従ってセットされる。このセルのしきい値レベルが“1”の場合、プログラミングは行われない。というのは、このセルは、下位ページのビットのプログラミングに対応して状態Eまたは状態Aのうちの一方の状態にあるからである。これらの状態の双方は上位ページビット“1”を担持する。しかし、上位ページのビットが“0”であれば、セルは2回目にプログラムされる。第1のパスの結果、セルが消去状態Eのままとなれば、上向きの矢印によって図4Bに示されているようにセルはその状態から最高の状態Cへプログラムされることになる。しかし、セルがプログラムされて状態Aになった場合、第1のプログラミングパスの結果、下向きの矢印によって図4Bに示されているように、セルは、第2のパス時にその状態から状態Bへさらにプログラムされることになる。この第2のパスの結果、下位ページのビットの第1のパスプログラミングの結果を変えることなく、上位ページから“0”を蓄積するように指定される状態へセルをプログラムすることになる。

【0037】

上位ページのビットが“0”となる第2のプログラミングパス中に、図4Bの上下の矢印に従って、消去状態Eから最高の状態Cへセルをプログラムするか、または状態Aから状態Bへセルをプログラムするかのいずれかのプログラミングを行うことが望ましい。プログラミングを上向きの矢印に従って行うか、下向きの矢印に従って行うかを決定するために、セルがEの状態にあるのか、またはAの状態にあるのかを第1に判定する必要がある。デバイスによっては、この判定が、内部読み出しまたは内部データロードとして公知の処理プロセスにより行われるものもあり、その場合、第1のプログラミングパス中にプログラムされるセルによって、そのしきい値レベルが状態Eまたは状態Aのいずれの状態に対応するかの判定が読み出される。

【0038】

前述したタイプのメモリアレイにおける、セルからなる隣接フローティングゲート間での電界効果結合については、ジアン・チェンとユーピン・フォングによる米国特許第5,867,429号(特許文献20)に記載されている。この特許は、その全体が本願明細書において参照により援用されている。集積回路の製造技術の改善の結果、この結合のレベルは、メモリセルアレイのサイズの縮小に伴って必然的に上昇することになる。この問題は、異なる時点にプログラムされた2組の隣接セル間で最も顕著に発生するものである。1組のセルをプログラムして、1組のデータに対応する電荷レベルがフローティングゲートに加えられる。第2の組のデータを用いて第2の組のセルをプログラムした後、第1の組のセルのフローティングゲートから読み出された電荷レベルが、第1の組のフローティングゲートと結合されている第2の組のフローティングゲートに対する電荷の影響に起因して、プログラムされた電荷レベルとは異なっているように見えることが頻繁に生じる。これはユーピン効果として知られているものである。

【0039】

後続してプログラムされる第2の組のセルのフローティングゲートが、第1の組のセルのフローティングゲートのしきい値レベルよりもずっと高いしきい値レベルに合わせてプログラムされているとき、前述したユーピン効果は特に顕著になる。図4Bから観察されることとして、第2の組のセルのフローティングゲートが消去状態から最高の状態Cへプログラムされると、しきい値電圧の変動が相対的に大きくなることに起因して、ユーピン効果が最も顕著になるということが挙げられる。ユーピン効果を小さくする1つのアプローチとして、後続のワードラインのプログラミング後、この状態の最終値に合わせてこの状態をプログラムするアプローチがある。このアプローチについては、“隣接するメモリセル行の蓄積素子間における結合の影響を低減する技術”という2002年9月6日にラウル−エイドリアン・セルニアにより出願された米国特許出願第10/237,426号(特許文献21)に記載されている。この特許出願は、その全体が本願明細書において参照により援用されている。本願は個々のページ内に“フラグ”セルというコンセプトを導入するものであり、このコンセプトは、そのページの状態(中間状態または最終状態)のプログラミングを示すものである。

【0040】

ユーピン効果を低減する別のアプローチとして、図4Aと図4Bとに示されているアプローチ以外の、シバタらによる米国特許第6,657,891号(特許文献22)に提案されているような別のコード構成を利用するものがある。この特許は、その全体が本願明細書において参照により援用されている。シバタらによって提案されているコード構成は図5A〜図5Cに示されているものである。図5A〜図5Cでは、メモリセルのしきい値電圧レベルによって表すことができる3以上の論理ページデータの存在も可能であることが予見され、この理由のために、図5A〜図5Cでは前述した下位の論理ページは第1のページと呼ばれ、前述した上位の論理ページは第2のページと呼ばれている。前述したように、メモリセルの中へ書き込むべき第1のページデータが“1”の場合、プログラミングは実行されず、セルは消去状態Eのまま残ることになる。第1のページデータが“0”の場合、メモリセルのしきい値電圧が図5Aに示されている分布状態すなわち状態B’で1まで上昇するようにプログラミングは構成される。これは、第1のページデータの“0”値が状態Aに合わせてセルにプログラムさせる図4Aでの処理プロセスとは対照的である。図5Bに示されているように、第2のページデータを利用してセルをプログラムする前に、状態B’に予めプログラムされているメモリセルに隣接するメモリセルへデータは書き込まれる。後続してプログラムされる隣接するセルのフローティングゲートにかかる電荷に起因して生じるユーピン効果の結果、図5Bに示されているしきい値電圧の分布状態B’は、図5Aのものよりも幅が広く、大きな面積のものになっている。図4A/Bまたは図5Cの最終分布状態Bよりも値の点では常に低いものの、図5Aの初期の分布状態B’の方が、図4A/Bまたは図5Cの最終分布状態Bよりもずっと幅が広いことに留意されたい。

【0041】

第2のページデータが書き込まれると、当初消去状態Eにあったセルは状態Aへプログラムされ、当初状態B’にあったセルは状態Cへプログラムされる。このコード構成には異なる時点にプログラムされた隣接するセルの電荷レベル間での電位差、したがって、隣接するフローティングゲート間での電界効果結合を小さくする効果があり、したがってユーピン効果が生じることになる。

【0042】

隣接するフローティングゲート内での電界効果結合を小さくするためには、図5Aと図5Cとを参照する前述したコード構成は利点を有するものであるかもしれないが、以下に説明するようにページの充填を行うユーザデータが不十分な場合、このようなコード構成を用いると、誤った状態に合わせてユーザデータがプログラムされる可能性がある。

【0043】

不揮発性メモリアレイによっては、ページ当たり2048バイトを有するものもある。このことは、或いは読み出し処理または書き込み処理時に単一の単位として2048バイトが読み出されたり、或いはプログラムされたりすることを意味する。不揮発性メモリシステムのシステムプログラミングは、512バイトのような2048バイトよりも少ないバイトを単位としてそのまま処理することも可能である。したがって、第1および第2の(下位および上位などの)ページの各ページは、4つのセクタのような複数のセクタを含むことになる場合がある。言い換えれば、ホストがデータ転送の終了へ向かってユーザデータをメモリアレイへ転送するとき、ページ内のメモリセルのすべてを完全にプログラムするにはユーザデータが不足する場合がある。したがって、個々のページが2048バイトを有する場合、第1のページと、1、2、3セクタのみを充填するのに十分なデータが存在するかもしれないが、第2のページの4つのセクタすべてを充填するにはデータが不十分となることが考えられる。メモリアレイ内のメモリセル行が、前述したタイプのインタリーブされたページ(偶数番号のビットラインによって制御される偶数ページには行内のメモリセルのすべてが含まれ、奇数番号のビットラインによって制御される奇数ページには行内のメモリセルのすべてが含まれる)を含む場合には、これは真であり、メモリアレイ内のメモリセル行には単一のページが含まれることになる。したがって、2048個のメモリセルの個々の行が、奇数ページと偶数ページのような2つのインタリーブされたページに分割され、個々のページが1024バイトを含むようになっている場合、偶数または奇数の第1のページと、偶数または奇数の第2のページの一方のセクタを充填するには適切なまたは十分なデータが存在するかもしれないが、偶数または奇数の第2のページの双方のセクタを充填するには適切なまたは十分なデータが存在しないことが考えられる。図4Aと図4Bに例示するタイプのコード構成の場合、このような状況によって問題が生じることはない。しかし、前述した図5A、5B、5Cに示されているような別のコード構成を利用する場合、このような状況が以下に例示するように問題となる場合がある。

【0044】

この問題が図6Aおよび図6Bの例で示されている。この例では、メモリアレイ内の行には、2048バイトのデータを蓄積するための16,384個のメモリセルが含まれ、このメモリセルが1ページを構成することになる。メモリアレイへまたはメモリアレイからデータを転送するコンピュータホストシステムは、各ブロックが512バイトを有する4つのブロック内でデータの転送を行う。したがって、図6Aに示されているように、アレイ内のメモリセル行は4つのセクタ、すなわちグループ112、114、116、118に分割され、個々のグループ内のセルの各々は第1の(下位)ページデータおよび第2の(上位)ページデータを蓄積することになる。本願明細書で以後使用するように、“セクタ”および“グループ”という用語は交換可能に用いられる。図6Aに示されているように、第1のページすなわち下位ページを充填するのに十分なホストデータが存在し、そのため4つの第1のページすなわち下位ページセクタは、下位ページセクタであることを示すために“L”とマークされることになる。プログラム対象のユーザデータすなわちホストデータのブロックの終端部へ向かって、4つのセクタの下位ページすなわち第1のページをプログラムするのに十分なデータのみが存在するようにしてもよく、そして、グループ112のセルの第2のページすなわち上位ページの第1のセクタのみが存在するようにしてもよい。この上位ページは上位ページであることを示すために図6Aでは“U”とマークされる。この結果、図6Aのセクタすなわちグループ114、116、118には、セルの上位ページすなわち第2のページをプログラムするために残されたデータが存在しなくなり、このセクタすなわちグループは、上位ページであることを示す“U”のマーカーなしでブランクのままに放置されることになる。

【0045】

異なるグループでメモリセルをプログラムするためにユーザデータを使用する前に、このデータは対応するデータバッファまたはラッチの中へ第1にロードされる(図7、図8A、図8Bを参照されたい)。次いで、データラッチに蓄積されたユーザデータはメモリセルのプログラミングのために利用される。図6Bは、図6Aのメモリセルの4つの対応するセクタすなわちグループ112、114、116、118をプログラムするための4つのデータブロック112’、114’、116’、118’の第1および第2のページを蓄積するためのデータラッチの機能を例示する機能ブロック図である。ブロックを消去した後で、かつ、4つのグループ内でセルをプログラムするためにユーザデータすなわちホストデータをデータラッチの中へロードする前に、データラッチのすべては“1”で最初にロードされる。この例では、このユーザデータはこの4つのグループのメモリセルのうちの下位ページすなわち第1のページおよびグループ112内のセルの上位ページのみのプログラミング用としては十分である。したがって、図6Bに示されているように、ブロック114’、116’、118’用のデータを蓄積するためのデータラッチの上位ページすなわち第2のページは“1”でロードされ、“1”を含み続けることになる。図6Bに示されているように、例えば、3つのデータブロック114’、116’、118’内の下位ページすなわち第1のページの中へロードされたユーザデータに依存して、3つのセクタ内のデータラッチ内のデータが値“11”を有する場合、(データ130’、132’、134’、136’、138’でプログラムされたメモリセルなどの)メモリセルのうちのいくつかはプログラムされないことになる。しかし、3つのブロック114’、116’、118’内のデータが(データ122’、124’、126’、128’などの)値“10”を有する場合、しきい値電圧すなわち蓄積レベルがコード構成に従って状態“10”に対応するようになるまで、セクタすなわちグループ114、116、118内の対応するメモリセルはプログラムされることになる。

【0046】

次いで、ユーザデータすなわちホストデータの別のブロックを後続してロードして、ブロック114’、116’、118’を蓄積するデータラッチ内でデフォルト値“1”を変位するとき、このようなデータは、典型的にはすべてが値“1”であるとはかぎらず、いくつかの値が“0”となるものもある。したがって、状態“10”に合わせてプログラムされたグループ114、116、118内の(データ122’〜128’を含むセルなどの)このメモリセルのうちのいくつかのメモリセルの場合、後続ブロックのユーザデータすなわちホストデータが、このようなメモリセル用として“1”ではなく“0”を第2のページデータすなわち上位ページデータとして対応するデータラッチの中へロードする場合、代わりにこのようなセルを状態“00”に合わせてプログラムする必要がある場合もある。図5Cから、状態“10”の蓄積レベルが最高レベルCであることが観察される。既存のプログラミング技法がブロック消去処理から離れて個々のメモリセルの蓄積レベルのしきい値電圧の低下を許さないため、図5A〜5Cのコード構成を用いる場合、状態“10”から状態“00”へのこのようなメモリセルの再プログラムは実行不能となり、その結果セルは誤った状態へプログラムされることになる。図5A〜5Cでコード構成を使用するとき、本願ではこれを部分的ページプログラム問題と呼ぶことにする。

【先行技術文献】

【特許文献】

【0047】

【特許文献1】米国特許第5,595,924号

【特許文献2】米国特許第5,070,032号

【特許文献3】米国特許第5,095,344号

【特許文献4】米国特許第5,315,541号

【特許文献5】米国特許第5,343,063号

【特許文献6】米国特許第5,661,053号

【特許文献7】米国特許第5,313,421号

【特許文献8】米国特許第6,222,762号

【特許文献9】米国特許第5,570,315号

【特許文献10】米国特許第5,903,495号

【特許文献11】米国特許第6,046,935号

【特許文献12】米国特許第5,768,192号

【特許文献13】米国特許第6,011,725号

【特許文献14】米国特許第5,172,338号

【特許文献15】米国特許第5,418,752号

【特許文献16】米国特許第5,774,397号

【特許文献17】米国特許第4,357,685号

【特許文献18】米国特許出願第10/254,483号

【特許文献19】米国特許第6,522,580号

【特許文献20】米国特許第5,867,429号

【特許文献21】米国特許出願第10/237,426号

【特許文献22】米国特許第6,657,891号

【非特許文献】

【0048】

【非特許文献1】エイタンらによる“NROM:新規の局在化トラッピング、2ビット不揮発性メモリセル”,IEEE電子デバイスレターズ,第21巻,第11号,2000年11月,543〜545ページ

【発明の概要】

【0049】

本願発明者らは、たとえメモリセルのうちのいくつかが第1のプログラミングパス時に、ユーピン効果を小さくする従来方式によるコード構成の下での状態よりも高い状態(状態Bなど)へプログラムされても、ホストデータが不十分な第2のプログラミングパス中に(最高の状態などの)誤った状態へメモリセルすなわち電荷蓄積素子がプログラムされるのを防ぐように不揮発性半導体メモリシステムが設計されている場合、この部分的ページプログラム問題は完全に回避可能であることを認識した。例えば、(第1のプログラミングパスの結果として)第2のプログラミングパス中に素子をプログラムして、このようなより高い状態にある素子を電荷レベルで(最高の状態などの)エラーを含むさらに高い状態よりも低い状態になるようにすることが可能である。このようにして、後続するホストデータすなわちユーザデータに従うメモリセルのプログラミングは、前述した部分的ページプログラム問題の結果として妨害を受けることはなくなる。

【0050】

1つの実施形態では、第1のプログラミングパスの後で、かつ、第2のプログラミングパスよりも前に、十分な上位ページデータすなわち第2のページデータを用いることなくセルをプログラムするために、データラッチの中へ適当なデータをロードすることによりこの効果の達成は可能となり、これによって、第2のプログラミング中にプログラミングを行うとき、(第1のプログラミングパスの結果としての)より高い状態でプログラミング電圧が素子やセルと結合されることはなくなる。別の実施形態では、図5Cに示されているコード構成をわずかに変更することによってこの効果は達成可能となり、その結果、部分的ページプログラム問題は生じなくなる。

【0051】

本発明の別の態様によれば、フラグデータを蓄積するフラグセルを用いて、ホストデータすなわちユーザデータの終了のようなホストデータすなわちユーザデータの境界を示すことが可能であり、それによって部分的プログラム問題はエラーを含む結果が生じなくなる。1つの実施形態では、素子はグループ化されて、複数のセクタすなわちグループに変えられ、個々のグループには、ホストデータが不十分な第2のパス時に、このようなグループの素子がプログラムされたものであるかどうかを示すフラグデータを蓄積するための少なくとも1つの対応するフラグ電荷蓄積セルが含まれる。複数のグループのうちの少なくとも2つのグループが共通のワードラインによって制御される。少なくとも2つのグループのうちの少なくとも1つのグループではあるが、すべてのグループではないグループのプログラミングを第2のパス中に行うのに十分なホストデータが存在するとき、フラグデータは少なくとも2つのグループのうちの少なくとも一方のフラグ電荷蓄積セルに蓄積されるか、このような(単複の)フラグセルに蓄積されたフラグデータが変更されて、ホストデータの境界が示されることになる。

【0052】

説明を簡略にするために、本願では同一の構成要素には同じ参照番号が付されている。

【図面の簡単な説明】

【0053】

【図1A】不揮発性メモリセルの異なる例を概略的に示す。

【図1B】不揮発性メモリセルの異なる例を概略的に示す。

【図1C】不揮発性メモリセルの異なる例を概略的に示す。

【図1D】不揮発性メモリセルの異なる例を概略的に示す。

【図1E】不揮発性メモリセルの異なる例を概略的に示す。

【図2】NORメモリセルのアレイの一例を示す。

【図3】図1Dに示されているようなメモリセルのNANDアレイの一例を示す。

【図4A】図3のメモリセルアレイをプログラムする現行技術を示す電圧しきい値レベルの分布状態である。

【図4B】図3のメモリセルアレイをプログラムする現行技術を示す電圧しきい値レベルの分布状態である。

【図5A】図3のメモリセルアレイをプログラムする別の現行技術を示す電圧しきい値レベルの分布状態である。

【図5B】図3のメモリセルアレイをプログラムする別の現行技術を示す電圧しきい値レベルの分布状態である。

【図5C】図3のメモリセルアレイをプログラムする別の現行技術を示す電圧しきい値レベルの分布状態である。

【図6A】メモリセル行の概略ブロック図であり、部分的ページプログラム問題の例示に役立つ図である。

【図6B】図6Aでメモリセルをプログラムするための4つのデータブロックの概念図であり、部分的ページプログラム問題の例示に役立つ図である。

【図7】本発明の1つの実施形態を例示するための、コア部分と共通部分とに分割された個々の読み出し/書き込みモジュールの概略ブロック図である。

【図8A】仕切られた読み出し/書き込みスタックのバンクを有するコンパクトなメモリデバイスを概略的に例示し、本発明の1つの実施形態の例示に役立つ図である。

【図8B】図7に示されているコンパクトなメモリデバイスの別の配置構成を例示する。

【図9】図7の読み出し/書き込みモジュールの構成要素の概略ブロック図であり、本発明の1つの実施形態を例示するために構成要素の動作をさらに詳細に示す。

【図10A】本発明の1つの実施形態を例示するための、電圧しきい値レベルの分布状態およびメモリセルの電圧しきい値レベルを読み出す技法を示す例である。

【図10B】本発明の1つの実施形態を例示するための、電圧しきい値レベルの分布状態およびメモリセルの電圧しきい値レベルを読み出す技法を示す例である。

【図11A】第1および第2の(下位および上位)ページの読み出しを表すテーブルであり、図10Aに例示されている電圧しきい値レベルを読み出す方法の例示に役立つ図である。

【図11B】第1および第2の(下位および上位)ページの読み出しを表すテーブルであり、図10Bに例示されている電圧しきい値レベルを読み出す方法の例示に役立つ図である。

【図12】電圧しきい値レベルの分布状態およびコード構成の関連づけられた値を示す例であり、本発明の別の実施形態を例示する。

【発明を実施するための形態】

【0054】

不揮発性メモリシステムの例

図7は、本発明の好ましい実施形態に従ってコア部分210と共通部分220とに分割された個々の読み出し/書き込みモジュール200の概略ブロック図である。コア部分210は接続されたビットライン211内の導通電流が所定のしきい値レベル以上か未満かを判定するセンスアンプ212を備えている。前述したように、接続されたビットライン211はアレイ内のアドレス指定されたメモリセルのドレインへのアクセスを可能にする。

【0055】

1つの実施形態では、コア部分210もビットラインラッチ214を備えている。このビットラインラッチを利用して接続されたビットライン211にかかる電圧条件がセットされる。1つの実施構成では、ビットラインラッチでラッチされた所定の状態はプログラムの禁止を指定する(Vddなどの)状態へ引っ張られる接続ビットライン211を結果として生じることになる。以下説明するようにこの特徴はプログラム禁止用として利用される。

【0056】

共通部分220は、プロセッサ222と、データラッチセット224およびデータラッチセット224とデータバス231間で結合された入出力インターフェイス226とを備える。プロセッサ222は計算を実行する。例えば、プロセッサ222の機能の1つとして、検知されたメモリセルのメモリ状態の判定などがあり、判定されたデータはデータラッチセットの中へ蓄積される。背景技術の欄で説明したように、メモリセルは電荷範囲を保持することが可能であり、したがって、しきい値電圧ウィンドウ内の任意のしきい値電圧レベル(すなわち、所定の導通電流に合わせてセルをオンに転換したばかりのコントロールゲート電圧)に合わせてプログラミングを行うことが可能となる。データラッチセット224を利用して、読み出し処理中にセンスアンプが検知した電流から、プロセッサにより判定されたデータビットが蓄積される。このデータラッチセット224は、データバス231からインポートされたユーザデータビットをプログラム処理中にホスト(図示せず)から蓄積するためにも用いられる。これらのインポートされたデータビットは、メモリの中へプログラムされたデータの書き込みを意図した書き込みデータを表すものである。入出力インターフェイス226はデータラッチセット224とデータバス231間のインターフェイスを提供する。

【0057】

読み出し中や検知中、処理は、アドレス指定したセルへの異なるコントロールゲート電圧の供給を基本的に制御し、種々のデータラッチに対して適当なロードを行うようにプロセッサに指図し、センスアンプを付勢する状態マシン(図示せず)の制御下にある。メモリがサポートしている種々のメモリ状態に対応する種々の予め定義されたコントロールゲート電圧を通って、処理がステップするにつれて、センスアンプ212はこれらの電圧のうちの1つの電圧でトリップすることになる。その時点で、プロセッサ222は、センスアンプのトリッピングイベント、並びに、状態マシンからの入力ライン223を介して印加されたコントロールゲート電圧に関する情報を考慮することにより、結果として生じるメモリ状態を決定する。次いで、プロセッサ222は、メモリ状態用の2進符号化を計算し、結果として生じるデータビットをデータラッチセット224の中へ蓄積する。状態マシンはモジュール200内の回路ブロックのすべての回路ブロックと通信を行う。

【0058】

SA/ビットラインラッチ214は、センスアンプ212の出力をラッチするラッチとして、および、図7と関連して説明したビットラインラッチとしての2つの任務の双方の役割を果たすことが可能である。したがって、SA/ビットラインラッチ214は、センスアンプか、プロセッサかのいずれかによってセットすることが可能となる。好ましい実施構成では、SA/ビットラインラッチ214からの信号はドライバ(図示せず)により駆動されて、選択したビットライン211の電圧によりセットされる。

【0059】

図7を参照してわかるように、プログラム中または検証中、プログラム対象データはデータバス231からデータラッチセット224の中へ入力される。状態マシンの制御下にあるプログラム処理には、アドレス指定されたセルのコントロールゲートに印加された一連のプログラミング電圧パルスが含まれる。個々のプログラミングパルスの後に、セルが所望のメモリ状態にプログラムされたかどうかを判定するリードバックが後続する。プロセッサ222は、所望のメモリ状態と比較しながらメモリ状態のリードバックをモニタする。2つのメモリ状態が一致すると、プロセッサ222はビットラインラッチ214をセットして、プログラミングの禁止を指定する状態へビットラインを引っ張らせるようにする。こうすることによって、たとえ、プログラミングパルスがセルのコントロールゲート上に生じたとしても、セルと結合したビットラインのさらなるプログラミングは禁止されることになる。

【0060】

入出力インターフェイス226は、データラッチのセット224の中で、または、データラッチのセット224の中からデータのトランスポートを可能にする。図8Aと図8Bでわかるように、読み出し/書き込みモジュールのブロックはメモリデバイスの中で同時に使用されて、一度にデータブロックを読み出したり、プログラムしたりする。典型的には、読み出し/書き込みモジュールのブロックには、シフトレジスタの形成のために合成されたモジュールの個々のセットのデータラッチが含まれ、読み出し/書き込みモジュールのブロックによりラッチされたデータをデータバス231へ連続的に転送して外へ出力できるようになっている。同様に、読み出し/書き込みモジュールのブロック用のプログラミングデータをデータバス231から連続的に入力し、それぞれのデータラッチセットの中へラッチすることができる。

【0061】

コンパクトな読み出し/書き込み回路

このアーキテクチャの1つの注目すべき特徴として、同時に動作している読み出し/書き込みモジュールのブロックの場合、個々のモジュールを分割して、コア部分と共通部分とに変え、コア部分のブロックに、共通部分の数よりも実質的に少数のブロックを動作させ、共通部分の数よりも実質的に少数のブロックを共有させるようにするという特徴がある。このアーキテクチャにより、個々の読み出し/書き込みモジュールの間の複製回路の構成要素の一部を取り除くことが可能となり、それによって空間および電力の節減が行われる。高密度のメモリチップ設計では、メモリアレイ用の読み出し/書き込み回路全体の50%程度まで空間の節減を行うことが可能となる。こうすることによって読み出し/書き込みモジュールを高密度でパックすることが可能となり、その結果、読み出し/書き込みモジュールはメモリアレイの隣接した切れ目なく連続するメモリセル行として機能することが可能となり、それによって行内のセルのすべての同時プログラミングまたは読み出しが可能となる。

【0062】

図8Aは、仕切られた読み出し/書き込みスタックのバンクを有するコンパクトなメモリデバイスを本発明の1つの実施形態に従って概略的に示す。メモリデバイスは、メモリセル300の2次元アレイと、制御回路310と、読み出し/書き込み回路370とを備える。メモリアレイ300は行デコーダ330を介してワードラインにより、並びに、列デコーダ360を介してビットラインによりアドレス可能である。読み出し/書き込み回路370は仕切られた読み出し/書き込みスタック400のバンクとして実現され、メモリセルのブロックの同時読み出しまたは同時プログラミングが可能となる。1つの実施形態では、メモリセル行はマルチブロックに分割され、ブロックマルチプレクサ350が設けられて、個々のブロックへの読み出し/書き込み回路370の多重化が行われる。読み出し/書き込みスタック400間の通信がスタックバスによって行われ、さらにスタックバスコントローラ430によって制御される。

【0063】

制御回路310は、メモリアレイ300でメモリ処理を実行するために読み出し/書き込み回路370と一体に動作する。制御回路310は状態マシン312、チップアドレスデコーダ314およびパワー制御モジュール316を備える。状態マシン312はメモリ処理のチップレベル制御を行う。オンチップアドレスデコーダ314は、ホストが使用するアドレスインターフェイスまたはデコーダ330と370とが使用するハードウェアアドレスとつながるメモリコントローラを提供する。パワー制御モジュール316は、メモリ処理中にワードラインとビットラインとへ供給される電力および電圧を制御する。

【0064】

図8Bは、図8Aに示されているコンパクトなメモリデバイスの好ましい配置構成を例示する。種々の周辺回路によるメモリアレイ300へのアクセスがアレイの対向する側に左右対称に実現され、それによって個々の側部のアクセスラインと回路とが半分に減少するようになっている。この結果、行デコーダは行デコーダ330Aと330Bとに分割され、列デコーダは列デコーダ360Aと360Bとに分割されることになる。メモリセル行がマルチブロックに分割された実施形態では、ブロックマルチプレクサ350はブロックマルチプレクサ350Aと350Bとに分割される。同様に、読み出し/書き込み回路は、最下部からビットラインと接続する読み出し/書き込み回路370Aと、アレイ300の最上部からビットラインと接続する読み出し/書き込み回路370Bとに分割される。このようにして、読み出し/書き込みモジュールの記録密度、したがって、仕切られた読み出し/書き込みスタック400の記録密度は、個々の仕切られた読み出し/書き込みスタック400によって1/2に実質的に低減することになる。

【0065】

図8Aまたは図8Bの個々の仕切られた読み出し/書き込みスタック400には、k個のメモリセルからなるセグメントとして同時に機能する読み出し/書き込みモジュールのスタックが実質的に含まれる。個々のスタックは、図7に示されている態様でコアスタック部分と共通のスタック部分とに分割される。個々の読み出し/書き込みスタック400間の通信はスタックバス(図示せず)による相互接続によって行われ、スタックバスコントローラ430によって制御される。制御ライン(図示せず)は、スタックバスコントローラ430から読み出し/書き込みスタックのコア部分の各々へ制御信号とクロック信号とを出力する。同様に、制御ライン(図示せず)は、スタックバスコントローラ430から読み出し/書き込みスタック400の共通部分の各々へ制御信号とクロック信号とを出力する。

【0066】

同時に動作している仕切られた読み出し/書き込みスタック400のバンク全体によって行に沿うp個のセルブロックの同時読み出しまたはプログラミングが可能となる。例えば、rがバンク内のスタック数であれば、p=r*kとなる。1つの例示のメモリアレイが、p=512バイト(512×8ビット)、k=8、したがってr=512を有する場合もある。この好ましい実施形態では、ブロックは一続きのセル行全体である。別の実施形態では、ブロックは行内のセルのサブセットである。例えば、セルのサブセットは行全体の1/2若しくは行全体の1/4になることも考えられる。セルのサブセットは、切れ目なく連続する一続きのセルや、1個おきのセル、或いは1個おきの所定数のセルとなる場合も考えられる。

【0067】

図8Aに示されている実施形態では、p個のセルの各々に対してp個の数の読み出し/書き込みモジュールが存在することになる。個々のスタックがk個のメモリセルとして機能しているとき、バンク内の読み出し/書き込みスタックの総数はr=p/kによって示される。p=512バイトおよびk=8の場合の例では、rは512となる。

【0068】

前述したように、高密度でかつ高性能のメモリにおいて遭遇する1つの問題として、隣接した切れ目なく連続するセル行のブロックの同時読み出しと同時プログラミングを行う必要性と、すべてのセルに対する読み出し/書き込みモジュールを適合させる際の困難とが存在する。

【0069】

この適合化問題は、メモリアレイの対向する側に周辺回路が形成される図8Bに示されている好ましい実施形態によって多少とも解決される。読み出し/書き込み回路370A、370Bがメモリアレイ300の対向する側に形成されるとき、p個のセルブロックの1/2が最上部側からアクセスされ、別の1/2がアレイの底部側からアクセスされることになる。したがって、p/2個の数の読み出し/書き込みモジュールが個々の側部に存在することになる。この当然の結果として、個々の側部にある読み出し/書き込みスタック400はp/2個の数のビットラインまたはメモリセルとして同時に機能するだけで十分となり、したがって、バンク内の読み出し/書き込みスタックの総数はr=p/2kによって与えられることになる。p=512バイトでk=8の例では、rは256となる。このことは、図8Aに示されている実施形態と比べて、メモリアレイの個々の側部には読み出し/書き込みスタック400の個数の1/2の個数しか必要でないことを意味することになる。

【0070】

別の実施形態では、この適合化問題や別の考慮事項によって、さらに低い記録密度が決定され、セル行は2以上のインタリービングなセルブロックに分割されることになる。例えば、一方のセルブロックは偶数番号の列から得られるセルから構成され、他方のセルブロックは奇数番号の列から得られるセルから構成される。図8Aと図8Bとに示されているように、ブロックマルチプレクサ350すなわち350Aと350Bとは、偶数または奇数のブロックのいずれかのブロックへ仕切られた読み出し/書き込みスタックのバンクの切替えに利用されることになる。図8Bに示されている実施形態では、p/4個の数の読み出し/書き込みモジュールがアレイの個々の側部に設けられることになる。この場合、対向する側部の各側部にある読み出し/書き込みスタックの個数はr=p/4k個になる。したがって、さらに多くの余地が与えられて、より少数の読み出し/書き込みモジュールをぴったり適合できるようにはなるが、これは性能の低下により行われるものであり、読み出し/書き込みブロックはもはや隣接した切れ目なく連続するブロックではなくなる。

【0071】

部分的プログラム問題を解決する実施形態

前述したように、部分的プログラム問題は、図5A〜5Cおよび図10A、10Bのコード構成のようなコード構成を用いてメモリセルのプログラミングを行う際に、そして、第2のプログラミングパス中にセルのプログラミングを行うのにユーザデータすなわちホストデータが不十分なときに、状態Bに対して生じるものである。このようなイベント時にデータラッチ内の第2の(上位)ページデータがデフォルト“1”の値になるため、以下に説明するようにデフォルト“1”の値になるイベントの発生が妨げられなければ、このようなセルは、図5A〜5C、10A、10Bのコード構成の下で状態Cにプログラムされることになる。次のプログラミング処理時の後続するユーザデータすなわちホストデータによって、このようなセルが状態Bにプログラムされた状態のままであることが求められる場合、そのような状態のままであることはあり得ない。というのは、ブロック消去処理を除いてほとんどの設計がしきい値レベルの低下を許さないからである。

【0072】

本発明の1つの実施形態は、ユーザすなわちホストの上位ページデータが含まれないメモリセルの場合、プログラミング処理時の第1のプログラミングパスの後であって、しかも、第2のプログラミングパスよりも前に、このようなメモリセルのプログラミングに用いられるデータラッチ内の下位ページデータは、適当な代替データによって変位され、第2のプログラミングパス時にこのようなメモリセルのプログラミングを妨げるようにするという認識に基づくものである。この結果、この実施形態の1つの実施構成では、消去状態すなわちリセット状態Eがデータ“11”を表すか、或いはデータ“11”に対応する場合、内部データロード処理時に、このようなメモリセルから読み出されたデータラッチ内の第1のページデータすなわち下位ページデータは“1”によって変位される。このことが以下に参照する図9にさらに詳細に示されている。

【0073】

図9は、図7の回路ブロックのデータラッチの構造をさらに詳細に示す概略ブロック図である。図9に示されているように、図7のデータラッチ224は、少なくとも3つのラッチ224a、224b、224cを備えている。この例のうちの1つの例では、スタックによって使用中のk個のセル間での読み出し/書き込みスタック400内のモジュール200は、対応するメモリセルの読み出しおよび書き込み制御のために用いられる。したがって、ラッチ224a〜224cは個々に1ビットのラッチであってもよい。プログラミング処理中、ユーザデータすなわちホストデータはデータバス231と入出力インターフェイス226とを通ってラッチ内へロードされる。1つの実施形態では、第1のデータビットすなわち下位のデータビットはバス231とインターフェイス226とを介してラッチ224aの中へ第1にロードされる。このロードは、図7、図8A、図8Bのスタックのバンク内のスタック400の各スタック内の読み出し/書き込みモジュール200のすべてによって同時に行われて、ページ全体のプログラミングが意図されることになる。ページ全体は1つの行内のメモリアレイ300の中のメモリセルのすべてから構成することも可能である。これとは別に、ページ全体は、1つのセル行内のインタリーブされたページの場合、奇数ページまたは偶数ページのようなメモリアレイ300内の行の一部のメモリセルから構成されるものであってもよい。

【0074】

次いで、ページ内のメモリセルは、スタック400のバンク内のモジュール200のすべてのモジュール内のデータラッチ224a内の下位ページデータすなわち第1のページデータを用いてプログラムされる。ラッチ224a内の第1のページデータすなわち下位ページデータを用いてページ内のメモリセルをプログラムした後、第2のページデータすなわち上位ページデータがバス231とインターフェイス226とを介してラッチ224a内へロードされる。このデータはプロセッサ222によって、メモリセルの第2のパスプログラミングに備えてラッチ224cへシフトされる。前述したように、第2のパスプログラミングを行うより前に、第1のプログラミングパスの後に、第2のパスプログラミングのためのメモリセルのしきい値電圧すなわちしきい値レベルを知っている必要がある。1つの実施形態では、これは内部データロード処理によって行われ、この内部データロード処理時に、ページ内のメモリセル内の電流がスタック400のバンク内モジュール200内のセンスアンプ212により検知される。このようなセルのしきい値電圧すなわち蓄積レベル、並びに、このようなセルに対応するデータはモジュール内のプロセッサ222により判定され、次いで、モジュール内のラッチ224aに蓄積される。第2のパスプログラミング内のページをプログラムするのに十分な上位ページデータすなわち第2のページデータが存在する場合、ラッチ224aに蓄積されたデータ、並びに、ラッチ224c内のユーザすなわちホストの上位ページデータすなわち第2のページデータは、第2のパスプログラミング時のページ内のメモリセルをプログラムするために使用される。これは、以下の例で図6Aのセクタ112内のセルをプログラムする場合である。

【0075】

しかし、ページ全体をプログラムするのに上位ページデータすなわち第2のページデータが不十分な場合、これは制御回路310によって第1に検出される。図6Aおよび図6Bに例示されている例では、メモリセルの第1のページすなわち下位ページをプログラムするのに十分なデータが存在している間、第1のセクタ112用の十分なデータのみが存在することになる。したがって、ホストデータすなわちユーザデータはこのようなセクタで終了し、セクタ114、116、118用の上位ページデータすなわち第2のページデータはそれ以上存在しなくなる。このようなイベント時に、並びに、本発明の1つの実施形態では、この場合データを変位するために、状態マシン312は、メモリセルの読み出しから内部データロード処理の結果生じる代替データをラッチ224aの中へロードさせる。代替データによって内部にロードされた下位ページデータすなわち第1のページデータの変位は、不十分な上位ページデータすなわち第2のページデータが存在するメモリセルのプログラミングを制御するモジュールのデータラッチ用としてのみ生じることになる。図6Aおよび図6Bの例では、この変位は、セクタ114、116、118内のメモリセル用として行われる。セクタ112内のメモリセルのプログラミングを制御するためのモジュール内のデータラッチ224a用として、ラッチ224a内のデータは、前述した内部データのロード処理の結果として生じるデータであり続ける。したがって、データブロック112’、114’、116’、118’間の境界を追跡することによって、そして、これらのセクタのうちのどのセクタがユーザデータすなわちホストデータを有しているかいないかを追跡することによって、内部データロード時に読み出されたデータを置き換える代替データのロード処理が、第2のページデータすなわち上位ページデータを有していないページのセクタ内のセル専用として行われることになる。1つの実施形態では、ページの境界はメモリセルのプログラミングを制御するために、コントローラ回路310によってモニタされる。以下さらに詳細に説明するように、コントローラ回路すなわち回路310は適当なフラグデータを蓄積し、対応するセクタのフラグ電荷蓄積セルの中でフラグデータを適当に変更して、ホストデータが不十分な行のセクタを示すようにする。

【0076】

この実施形態では、対応するセルをプログラムするための第2のデータすなわち上位ページデータが不十分なとき、異なるモジュール内のラッチ224a内へロードされるデータを交換するために代替データが利用される。しかし、第1のプログラミングパス中にB’状態へプログラムされたセルに対してのみ部分的ページプログラム問題が生じることが知られている。第1のプログラミングパスの後、消去状態Eのまま残るセルについては、これらのセルを正確に状態Aへプログラムするか、第2のプログラミングパスの結果として正確に状態Eのまま残るようにするかのいずれかが可能である。したがって、この実施形態では、状態B’にあるセルのプログラミングを行うために代替データ“1”をラッチ224aの中へのみロードする必要がある。そして、このロードは第1のプログラミングパスの後の状態Eのセルに対しては行われない。このことは、第2のパス中、プログラミング電圧が状態B’のセルと結合するのを防ぐという効果を有するものである。これは、B’の分布状態がBの分布状態の中へさらに移行することを禁止するという効果も有するものであり、セクタ114、116、118の各セクタに対して、後続する上位ページデータが利用可能となる場合、個々のセクタは、状態EまたはB’のいずれかからプログラミングを開始することになる。このようなセルに対して、或いは、対応する第2のページデータすなわち上位ページデータを含まない、すべてのセルの代替セルとして、データラッチの中へ“1”をロードして、これらのセルをプログラムするようにすることにより、内部ロード処理の交換を行うことも可能となる。このような変形例およびその他の変形例は本発明の範囲に含まれるものである。この実施形態は、消去状態Eがデータ“11”を表す方式に限定されるものでもない。

【0077】

図5Aと図5Bに関連する前述した場合と同様、この実施形態では、たとえ第2のページデータすなわち上位ページデータを含まないセルのB’の分布状態が広範にわたるユーピン効果に起因して広がったかもしれない場合であっても、後続して隣接するセルをプログラムするとき、このような広がったB’の状態の電荷レベルは次のより高い状態Cの電荷レベル未満のままとなる。

【0078】

ラッチ224aの中へ前述したようにデータをロードして、メモリセルを読み出すことによって、内部データロードの結果として生じるデータの変位を行うことは、状態マシン312を備えた制御回路310によって、ユーザすなわちホストにとって透過的に行うことも可能である。これとは別に、プログラムシーケンスを変えることによってこのような処理の達成が可能である。プログラムアルゴリズムの中に新たなコマンドを追加せずに、ユーザすなわちホストによってどのゾーンまたはセクタがプログラムされているかをゾーン検出回路を用いて検出して、残りの1または複数のセクタまたはゾーンを選択し、包括的なリセット時にラッチ224aと224cの双方にデータ“11”を充填するようにしてもよい。すべてのこのような変形例は本発明の範囲に属するものである。

【0079】

読み出し処理