不揮発性メモリの正常性情報を取得して使用するためのシステム及び方法

【課題】不揮発性メモリ(「NVM」)の正常性情報を取得して使用するためのシステム及び方法を提供する。

【解決手段】正常性情報は、NVMの一部で検出されたエラー数、又は不揮発性メモリの一部から読み取りを行うために又はこのメモリの一部をプログラムするために必要な時間量などの、NVM装置の一部の性能及び信頼性に関連する様々な情報を含むことができる。動作中、ホスト装置上にアドレス固有の正常性情報を受動的に記憶し、コマンドの一部としてメモリコントローラに提供することができる。メモリコントローラは、このコマンドから正常性情報を抽出し、この情報を使用してアクセス要求を実行することができる。アクセス要求の完了後、メモリコントローラは正常性情報を更新し、この情報をホスト装置へ返送することができる。

【解決手段】正常性情報は、NVMの一部で検出されたエラー数、又は不揮発性メモリの一部から読み取りを行うために又はこのメモリの一部をプログラムするために必要な時間量などの、NVM装置の一部の性能及び信頼性に関連する様々な情報を含むことができる。動作中、ホスト装置上にアドレス固有の正常性情報を受動的に記憶し、コマンドの一部としてメモリコントローラに提供することができる。メモリコントローラは、このコマンドから正常性情報を抽出し、この情報を使用してアクセス要求を実行することができる。アクセス要求の完了後、メモリコントローラは正常性情報を更新し、この情報をホスト装置へ返送することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本文献は、不揮発性メモリの正常性(health)情報を取得して使用するためのシステム及び方法に関する。

【背景技術】

【0002】

大容量記憶装置には、フラッシュメモリ(例えば、NANDフラッシュメモリ及びNORフラッシュメモリ)などの、様々な種類の不揮発性メモリ(「NVM」)を使用することができる。例えば、(ポータブルメディアプレーヤなどの)消費者向け電子機器は、音楽、ビデオ、画像、及びその他のメディア又はタイプの情報を含むデータを記憶するためにフラッシュメモリを使用する。

【0003】

一部のフラッシュメモリシステムでは、ホストシステムが論理ブロックアドレス(LBA)の読み取り動作及びプログラム動作を要求し、このLBAがフラッシュメモリの物理ブロックアドレスにマッピング又は変換される。このマッピングにより、ホストオペレーティングシステムが、ディスクドライブと同様の方法でフラッシュメモリにアクセスできるようになる。フラッシュメモリは、ランダムアクセス方式で一度に1バイト又は1ワードを読み取り又はプログラムすることができるが、通常は一度に1ブロックが消去される。新たに消去されたブロックから開始して、このブロック内のあらゆるバイトをプログラムすることができる。バイトは、一旦プログラムされると、通常はブロック全体が消去されるまで再プログラムすることができない。フラッシュメモリの消去プログラムのサイクル数には限りがあるので、フラッシュメモリの寿命を引き延ばすには、消去プログラムのサイクル数を最小にすることが望ましい。

【発明の概要】

【発明が解決しようとする課題】

【0004】

上述したフラッシュメモリの固有の特性を背景として、フラッシュメモリ及びその他のNVMの正常性情報を効率的に取得して使用できるシステム、方法及び装置が必要とされている。

【課題を解決するための手段】

【0005】

不揮発性フラッシュメモリ(NVM)の正常性(health)情報を取得して使用するためのシステム及び方法を開示する。本発明の実施形態は、ホスト及び不揮発性メモリパッケージを有するシステムで動作することができる。ホストは揮発性メモリを含み、論理対物理マッピングの維持、プログラムの発行、NVMパッケージに対するコマンドの読み取り又は消去、及びウェアレベリング及びガベージコレクションの実行などの不揮発性メモリの機能を実行することができる。ホストは、本発明の実施形態による正常性データベースを維持することもできる。NVMパッケージは、ホストに通信可能に結合され、メモリコントローラ及び(NANDフラッシュなどの)不揮発性メモリを含むことができる。いくつかの実施形態では、NVMパッケージが、誤り訂正符号エンジンを含むこともできる。

【0006】

正常性データベースは、NVMに関する情報を記憶することができる。すなわち、NVM内の(ページ又はブロックなどの)物理的位置ごとに、この物理的位置に特有の正常性情報がデータベースに記憶される。データベースに記憶される正常性情報は、NVMの特定のアドレス位置にアクセスするために使用する様々なソフトウェア及び/又はハードウェアパラメータを指定するアドレス固有の正常性情報とすることができる。正常性情報は、例えば、ページの正確性、閾値電圧、読み取り、プログラム及び消去を行うために必要なサイクル時間及び/又はサイクル数、使用する誤り訂正符号などを含むことができる。正常性情報は、メモリコントローラにより生成することができるが、ホストによって保持されるデータベースに記憶される。正常性情報をホスト上に記憶することはできるが、ホストは、NVMを管理するために正常性情報を解釈し、修正し、又は使用することは決してない。

【0007】

ホストは、NVMにアクセスしたいと望む場合、(読み取りコマンド又はプログラムコマンドなどの)アクセスコマンド、アドレス及びアドレス固有の正常性情報を含むコマンドパケットを構築し、このコマンドパケットをメモリコントローラに提供することができる。ホストは、正常性情報データベースにアクセスして、コマンドパケットに含めるためのアドレスに基づいてアドレス固有の正常性情報を取り出す。メモリコントローラは、コマンドパケットを受け取ると正常性情報を抽出し、NVM内のアクセスされる物理的位置に対して指定されたソフトウェア及び/又はハードウェアパラメータに従ってアクセス要求を実行することができる。

【0008】

コマンドが実行された後、メモリコントローラは、アクセス要求を実行するために1又はそれ以上の動作パラメータに変更が必要であったかどうかを判定することができる。変更が必要であった場合、メモリコントローラは正常性情報を更新し、この更新した正常性情報及びNVMアドレスをホスト装置へ送信することができる。その後、ホストは、更新した正常性情報をデータベースに記憶することができる。

【0009】

全体を通じて同じ参照番号が同じ部分を示す添付図面とともに以下の詳細な説明を検討すれば、本発明の上記の及びその他の態様、その特質及び様々な特徴がより明らかになるであろう。

【図面の簡単な説明】

【0010】

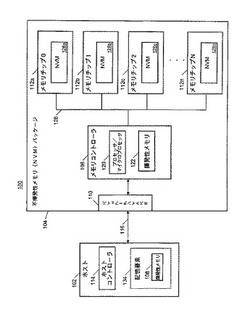

【図1】本発明の様々な実施形態による、ホストとメモリコントローラを有するNVMパッケージとを含む例示的なシステムを示す図である。

【図2】本発明の様々な実施形態による例示的なシステムを示す図である。

【図3】本発明の様々な実施形態による例示的なデータ構造を示す図である。

【図4】本発明のいくつかの実施形態による、正常性情報を取得して使用する例示的な処理を示すフローチャートである。

【発明を実施するための形態】

【0011】

図1は、NVMパッケージ104及びホスト102を含むシステム100を示す図である。ホスト102は、メモリコントローラ106と、ホストインターフェイス110と、対応するNVMs128a〜nを有するメモリチップ112a〜nとを含むことができるNVMパッケージ104に正常性情報を提供するように構成することができる。例えば、システム例100に示すように、ホスト102は、NVMパッケージ104に正常性情報を提供することができ、NVMパッケージ104は、この正常性情報を使用して(読み取り動作、プログラム動作、消去動作などの)アクセス要求及び(ウェアレベリング及びガベージコレクションなどの)メモリ管理機能を実行し、これによりシステム100の性能、信頼性及び/又は電力使用を改善することができる。NVMパッケージ104は正常性情報を更新し、これをホスト102に戻して正常性情報データベースに記憶されるようにすることもできる。

【0012】

ホスト102は、ポータブルメディアプレーヤ、携帯電話機、ポケットサイズパーソナルコンピュータ、携帯情報端末(「PDA」)、デスクトップコンピュータ、ラップトップコンピュータ、及び/又はタブレットコンピュータ装置などの様々なホスト装置及び/又はシステムのいずれかとすることができる。NVMパッケージ104は、(例えば、メモリチップ112a〜n内に)NVM128a〜nを含むことができ、ボールグリッドアレイパッケージ又はその他の好適な種類の集積回路(「IC」)パッケージとすることができる。NVMパッケージ104は、ホスト102の一部であっても、及び/又はこれとは別個のものであってもよい。例えば、ホスト102を基板レベルの装置とし、NVMパッケージ104を、この基板レベルの装置上に取り付けられたメモリサブシステムとすることができる。他の実施形態では、NVMパッケージ104を、(SATAなどの)有線インターフェイス又は(Bluetooth(登録商標)などの)無線インターフェイスを使用してホスト102に結合することができる。

【0013】

ホスト102は、NVMパッケージ104と相互作用するように構成されたホストコントローラ114を含むことができる。例えば、ホスト102は、読み取り動作、プログラム動作及び消去動作などの様々なアクセス要求をNVMパッケージ104に送信することができる。ホストコントローラ114は、ソフトウェア及び/又はファームウェア命令の実行に基づいて動作を行うように構成された1又はそれ以上のプロセッサ及び/又はマイクロプロセッサを含むことができる。これに加えて及び/又はこれとは別に、ホストコントローラ114は、様々な動作を行うように構成された特定用途向け集積回路(「ASIC」)などのハードウェアベースの構成要素を含むこともできる。ホストコントローラ114は、NVMパッケージ104に送信する(コマンド、データなどの)情報を、ホスト102とNVMパッケージ104の間で共用される通信プロトコルに従ってフォーマットすることができる。

【0014】

ホスト102は、揮発性メモリ108を含む記憶要素134を含むことができる。揮発性メモリ108は、キャッシュメモリ又はRAMなどの様々な揮発性メモリタイプのいずれかとすることができる。ホスト102は、揮発性メモリ108を使用して、メモリ動作を実行し、及び/又はNVMパッケージ104から読み取っている及び/又はNVMパッケージ104に書き込んでいるデータを一時的に記憶することができる。例えば、揮発性メモリ108は、NVMパッケージ104に送信するメモリ動作の待ち行列を一時的に記憶すること、又はNVMパッケージ104から受け取ったデータを記憶することができる。また、揮発性メモリ108は、本発明の実施形態による正常性情報データベースを記憶することもできる。ホストコントローラ114は、正常性情報データベースにアクセスして、メモリコントローラ106に出すコマンドに含めるためのアドレス固有の正常性情報を取り出すことができる。十分な量の揮発性メモリをNVMパッケージ104内に保持するとコストが掛かり過ぎるので、NVMパッケージ104上の揮発性メモリとは対照的に、一般的にはホスト102上の揮発性メモリ内に正常性情報データベースを保持することが必要である。

【0015】

ホスト102は、通信チャネル116を介して、ホストインターフェイス110及びメモリコントローラ106を使用してNVMパッケージ104と通信することができる。通信チャネル116は、双方向通信に適したいずれのバスであってもよい。通信チャネル116は、固定式であっても、着脱式であっても、又は無線方式であってもよい。例えば、通信チャネル116は、ユニバーサルシリアルバス(USB)、シリアルアドバンスドテクノロジ(SATA)バス、又はその他のあらゆる好適なバスとすることができる。

【0016】

メモリコントローラ106は、ソフトウェア命令及び/又はファームウェア命令の実行に基づいて動作を行うように構成された1又はそれ以上のプロセッサ及び/又はマイクロプロセッサ120を含むことができる。これに加えて及び/又はこれとは別に、メモリコントローラ106は、様々な動作を行うように構成されたASICなどのハードウェアベースの構成要素を含むこともできる。メモリコントローラ106は、ホスト102によって出されたコマンドを実行することなどの様々な動作を行うことができる。

【0017】

ホストコントローラ114及びメモリコントローラ106は、単独で又は組み合わせて、ガベージコレクション及びウェアレベリングなどの様々なメモリ管理機能を実行することができる。メモリコントローラ106が少なくともいくつかのメモリ管理機能を実行するように構成された実施構成では、NVMパッケージ104を、「managed NVM」(又はNANDフラッシュメモリの場合には「managed NAND」)と呼ぶことができる。これは、NVNパッケージ104の外部にあるホストコントローラ114がNVMパッケージ104のメモリ管理機能を実行する「raw NVM」(又はNANDフラッシュメモリの場合には「raw NAND」)とは対照的なものとすることができる。

【0018】

いくつかの実施形態では、メモリコントローラ106を、メモリチップ112a〜nと同じパッケージに組み込むことができる。他の実施形態では、メモリコントローラ106を、ホスト102と別個の又は同じパッケージ内に物理的に配置することができる。いくつかの実施形態では、メモリコントローラ106を省き、通常はメモリコントローラ106によって行われる(ガベージコレクション及びウェアレベリングなどの)全てのメモリ管理機能を(ホストコントローラ114などの)ホストコントローラによって行うことができる。

【0019】

メモリコントローラ106は、揮発性メモリ122を含むことができる。揮発性メモリ122は、キャッシュメモリ又はRAMなどの様々な揮発性メモリタイプのいずれかとすることができる。メモリコントローラ106は、揮発性メモリ122を使用して、アクセス要求を実行し、及び/又はメモリチップ112a〜n内のNVM128a〜nから読み取っているデータ及びここに書き込んでいるデータを一時的に記憶することができる。例えば、揮発性メモリ122はファームウェアを記憶することができ、メモリコントローラ106は、このファームウェアを使用して、NVMパッケージ104上の(読み取り/プログラム動作などの)動作を行うことができる。揮発性メモリ122は、NVMパッケージ104内のNVMに関連する正常性情報を一時的に記憶することもできる。メモリコントローラ106は、NVM128a〜nを使用して、デバッグログ、命令、及びNVMパッケージ104が動作するために使用するファームウェアなどの様々な情報を永続的に記憶することができる。

【0020】

メモリコントローラ106は、永続的データ記憶に使用できるNVMs128a〜nに、共有内部バス126を使用してアクセスすることができる。NVMパッケージ104内には1つの共有内部バス126しか示していないが、NVMパッケージは、1つよりも多くの共有内部バスを含むことができる。各内部バスは、メモリチップ112a〜nに関して示すように(2個、3個、4個、8個、32個などの)複数のメモリチップに接続することができる。メモリチップ112a〜nは、積層構成を含む様々な構成で物理的に配置することができ、いくつかの実施形態によれば集積回路(IC)チップとすることができる。

【0021】

NVM128a〜nは、フローティングゲート技術又は電荷トラップ技術に基づくNANDフラッシュメモリ、NORフラッシュメモリ、消去可能プログラム可能読み取り専用メモリ(「EPROM」)、電気的消去可能プログラム可能読み取り専用メモリ(「EEPROM」)、強誘電性RAM(「FRAM(登録商標)」)、磁気抵抗性RAM(「MRAM」)、相変化メモリ(「PCM」)などの様々なNVMのいずれか、又はこれらのいずれかの組み合わせとすることができる。

【0022】

図2は、電子装置200のブロック図であり、この図には、様々な実施形態によるシステム100(図1)のファームウェア、ソフトウェア及び/又はハードウェア構成要素のいくつかをより詳細に示すことができる。電子装置200は、図1に関連して上述した特徴及び機能のいずれかを有することができ、逆もまた同様である。図示のように、破線で層の境界を定めている。どの構成要素が境界線内に入るかについての描写は例示にすぎず、1又はそれ以上の構成要素が異なる層に属することもできると理解されたい。

【0023】

電子装置200は、ファイルシステム210、ホストコントローラ212、NVMバスコントローラ216、メモリコントローラ220、及びNVM230を含むことができる。いくつかの実施形態では、ファイルシステム210及びホストコントローラ212をソフトウェア又はファームウェアモジュールとすることができ、NVMバスコントローラ216、メモリコントローラ220及びNVM230をハードウェアモジュールとすることができる。従って、これらの実施形態では、ホストコントローラ212が、NVMインターフェイス218のソフトウェア又はファームウェアの側面を表すことができ、NVMバスコントローラ216が、NVMインターフェイス218のハードウェアの側面を表すことができる。

【0024】

ファイルシステム210は、ファイルアロケーションテーブル(「FAT」)ファイルシステム又は階層型ファイルシステムプラス(「HFS+」)などのいずれかの好適な種類のファイルシステムを含むことができ、電子装置200のオペレーティングシステムの一部(例えば、図1のSoC制御回路112の一部)とすることもできる。いくつかの実施形態では、ファイルシステム210が、ページの論理対物理マッピングを行うフラッシュファイルシステムを含むことができる。これらの実施形態では、ファイルシステム210が、以下で説明するホストコントローラ212の機能の一部又は全部を実行することができ、従ってファイルシステム210とホストコントローラ212は、別個のモジュールであっても又はそうでなくてもよい。

【0025】

ファイルシステム210は、アプリケーション及びオペレーティングシステムのファイル及びフォルダ構造を管理することができる。ファイルシステム210は、電子装置200上で実行されるアプリケーション又はオペレーティングシステムの制御下で動作することができ、このアプリケーション又はオペレーティングシステムが、NVM230から情報を読み取ること又はNVM230に情報を記憶することを要求した場合、ホストコントローラ212に書き込み及び読み取りコマンドを提供することができる。ファイルシステム210は、各書き込み又は読み取りコマンドとともに、ユーザデータをどこから読み取るべきか又はどこに書き込むべきかを示すための、論理ページアドレス及びページをオフセットしたLBAなどの論理アドレスを提供することができる。

【0026】

ファイルシステム210は、NVMと直接的に互換性がない読み取り及び書き込み要求をホストコントローラ212に提供することができる。例えば、論理アドレスには、ハードドライブベースのシステムに特有の規則又はプロトコルを使用することができる。ハードドライブベースのシステムは、フラッシュメモリとは異なり、最初にブロックの消去を行わずに記憶域を上書きすることができる。さらに、ハードドライブは、装置の寿命を延ばすためにウェアレベリングを必要としなくてよい。従って、NVMインターフェイス218は、メモリ固有の、ベンダー固有の、又はこれらの両方のあらゆる機能を実行して、ファイルシステム要求の処理及びその他の管理機能をNVMに適した形で行うことができる。

【0027】

ホストコントローラ212は、トランスレーションレイヤ214を含むことができる。いくつかの実施形態では、トランスレーションレイヤ214をフラッシュトランスレーションレイヤ(「FTL」)とすることができ、又はこのFTLを含むことができる。書き込みコマンド時には、トランスレーションレイヤ214が、提供された論理アドレスを、NVM上の空いている消去済みの物理的位置にマッピングすることができる。読み取りコマンド時には、トランスレーションレイヤ214が、提供された論理アドレスを使用して、要求されるデータが記憶されている場所の物理アドレスを特定することができる。各NVMは、NVMのサイズ又はベンダーに応じて異なるレイアウトを有することができるので、このマッピング動作は、メモリ及び/又はベンダー固有のものとなり得る。トランスレーションレイヤ214は、論理対物理アドレスマッピングに加え、他のあらゆる好適な機能を実行することもできる。例えば、トランスレーションレイヤ214は、ガベージコレクション(「GC」)及びウェアレベリングなどの、フラッシュトランスレーションレイヤに特有のものとすることができる他の機能のいずれかを実行することができる。

【0028】

例えば、トランスレーションレイヤ214は、ガベージコレクションを実行して、NVM230のプログラム済みブロックを消去のために解放することができる。解放され消去されると、このメモリ位置を使用して、例えばファイルシステム210から受け取った新たなユーザデータを記憶することができる。場合によっては、GCプロセスが、プログラム済みブロックから消去済みのメモリ位置を有する別のブロックに有効なデータをコピーして、これによりプログラム済みブロック内の有効データを無効化することに関与することができる。プログラム済みブロック内のメモリ位置が全て無効になると、トランスレーションレイヤ214は、NVMバスコントローラ216に、これらのプログラム済みブロック上で消去動作を行うように指示することができる。本明細書で使用する「有効なデータ」とは、(LBAなどの)1又はそれ以上の論理アドレスに対応する直近の書き込み要求に応答してプログラムされたユーザデータを意味することができ、従って1又はそれ以上の論理アドレスに対応する有効なバージョンのユーザデータとすることができる。

【0029】

ホストコントローラ212は、アドレス固有の正常性情報を記憶するための正常性データベース215を含むことができる。正常性データベース215は、NVM230内の物理的位置に対応する情報の参照テーブルを含むことができる。ファイルシステム210が、ホストコントローラ212にコマンド及び論理アドレスを送ると、トランスレーションレイヤ214が、NVM230内の物理的位置を特定し、ホストコントローラ212が、この物理的位置を使用して、正常性データベース215からアドレス固有の正常性情報を取得する。いくつかの実施形態では、ホストコントローラ212が、メモリコントローラ220に提供するコマンドパケットに、正常性データベース215から取得した正常性情報を含める。この実施形態では、ホストコントローラ212が、データ検索エージェントとして機能し、正常性情報を使用してNVMの管理上の決定を行うことはない。ホストコントローラ212は、メモリコントローラ220から受け取った正常性情報を使用して正常性データベース215を更新することにより、データ投入エージェントとして機能することもできる。

【0030】

メモリコントローラ220は、正常性情報を生成し、これを正常性データベース215に記憶する。この結果、メモリコントローラ220のみが正常性情報を解釈して使用することができる。ホストコントローラ212は、正常性情報をデータベース215に記憶することはできるが、これを使用してNVMの管理上の決定を行うことはできない。

【0031】

(図1の揮発性メモリ108内に存在できる)正常性データベースに記憶された正常性情報は、NVMインターフェイス218又はホストインターフェイス110の下流のソフトウェア及び/又はハードウェア構成要素が、NVM230のあらゆる特定の物理的位置に対するコマンド要求をより効率的に処理できるようにする情報とすることができる。例えば、正常性情報は、例えばNVMパッケージ104上に存在するECCエンジンがいずれの誤り訂正符号を実施すべきかを指定することができる。別の例として、正常性情報は、プログラム電圧、プログラム/検証サイクルの数、及びNVM内の特定の物理的位置に必要なプログラム分解能などの、メモリコントローラハードウェアの設定を記憶することができる。

【0032】

正常性情報は、NVMの一部の劣化及び/又は障害の可能性を示すあらゆるデータを含むことができる。一般に、正常性情報は、NVMの効率的かつ信頼できる使用に関する決定を行うために使用できる、NVMに関するあらゆるデータを含むことができる。メモリコントローラ106又は220は、重要な性能及び較正パラメータを記憶することにより、コマンド要求を実行する方法を、不必要な待ち時間及びデータ破損を避けるように変更することができる。

【0033】

1つの特定の例では、正常性情報を使用して、ホストにより開始される読み取り動作を事前に補正することができる。ホストは、NVMの(ブロックなどの)特定の部分の読み取り動作を開始することができる。メモリコントローラは、この読み取り動作を受け取って、NVMの(ブロック又はページなどの)物理アドレスに関連する正常性情報を調べることができる。正常性情報は、ブロックを読み取った最後の時間、及び読み取り動作に複数の読み取りサイクルが必要であったことを示すことができる。例えば、読み取り動作に8回の読み取りサイクルを要し、使用した各読み取りサイクルで徐々に読み取り条件を変更した(例えば、閾値電圧値を徐々にシフトさせた)かもしれない。この正常性情報に基づいて、メモリコントローラは、最後の既知の成功した(単複の)読み取り条件を使用して、要求される物理的位置上の読み取り動作を実行すると決定することができる。読み取り動作がうまくいった場合、メモリコントローラは、その物理的位置(ブロックなど)に関する正常性情報をそのままホストに戻すことができる。しかしながら、読み取り動作にさらなる読み取りサイクルが必要であった場合、メモリコントローラは、その物理的位置(ブロックなど)に関する正常性情報を更新し、この更新した正常性情報をホストに戻すことができる。

【0034】

別の例では、正常性情報を使用して、ホストがプログラム動作を開始した時にNVMの一部をより効率的にプログラムすることができる。(NANDフラッシュメモリなどの)NVMは、時間、使用(読み取り/プログラムサイクル数など)、及び動作温度とともに劣化する傾向にある。この劣化は、例えばメモリセルの閾値電圧の変位の形で表れることがある。従って、正常性情報は、NVMの一部のこれらの重要なパラメータを追跡することができる。メモリコントローラ106は、NVM128a〜nの特定部分にデータをプログラムする要求をホスト102から受け取ると、このメモリ部分に関する正常性情報を参照して、プログラム済みのセルがどれほどの程度及びどれほど速く劣化しそうであるかを判断することができる。例えば、ホスト102が、(例えば、正常性情報内の時間、温度、及びサイクルデータによって示される)すぐに劣化しそうなメモリ部分に対してプログラム動作を開始した場合、メモリコントローラ106は、プログラム電圧を、予想閾値電圧ドリフトを補償するように変化させるよう決定することができる。

【0035】

いくつかの実施形態による、取得して使用できる正常性情報のさらなる例として、NVMの一部における不良ビット数、DLLタイミング設定、及び/又はデータのプログラム又は読み取りに必要なサイクル時間又はサイクル数を反映するビット誤り率データを挙げることができる。検出されたエラーを補正するためのメモリ装置の容量を示すことができるページの正確性に関して正常性情報を蓄積することもできる。例えば、エラーの訂正に必要な誤り訂正符号(「ECC」)サイクルの数、又は(高ビットフリップECC、低ビットフリップECC、ソフトウェアECCなどの)使用するECC技術が、NVMの一部の正常性を示すことができる。

【0036】

ホストコントローラ212は、(プログラム、読み取り及び消去コマンドなどの)NVMアクセスコマンドを完了するために、NVMバスコントローラ216と相互連結することができる。NVMバスコントローラ216は、メモリコントローラ220へのハードウェアインターフェイスとして機能し、バスプロトコル、データ転送率及びその他の仕様を使用してメモリコントローラ220と通信することができる。

【0037】

NVMインターフェイス218は、本明細書では「メタデータ」と呼ぶこともあるメモリ管理データに基づいてNVM230を管理することができる。このメタデータは、ホストコントローラ212によって生成することも、又はホストコントローラ212の制御下で動作するモジュールによって生成することもできる。例えば、メタデータは、論理アドレスと物理アドレスの間のマッピング、不良ブロック管理、ウェアレベリング、データエラーを検出又は訂正するために使用する誤り訂正符号(「ECC」)データ、又はこれらのいずれかの組み合わせを管理するために使用するあらゆる情報を含むことができる。メタデータは、ファイルシステム210により提供されるデータ、及び論理アドレスなどのユーザデータを含むことができる。従って、一般に「メタデータ」は、ユーザデータについての又はユーザデータに関する、或いは不揮発メモリの動作及びメモリ位置を管理するために一般的に使用されるあらゆる情報を意味することができる。いくつかの実施形態では、メタデータ及び正常性情報が互いに排他的である。

【0038】

NVMインターフェイス218は、NVM230にメタデータを記憶するように構成することができる。いくつかの実施形態では、NVMインターフェイス218が、ユーザデータに関連するメタデータを、ユーザデータが記憶されているメモリ位置と同じメモリ位置(ページなど)に記憶することができる。例えば、NVMインターフェイス218は、ユーザデータ、その関連する論理アドレス、及びユーザデータのためのECCデータをNVM230の1又はそれ以上のメモリ位置に記憶することができる。NVMインターフェイス218は、ユーザデータに関する他の種類のメタデータを同じメモリ位置に記憶することもできる。

【0039】

NVMインターフェイス218は、NVM230に正常性情報を記憶することもできる。NVMインターフェイス218は、正常性データベース215のコンテンツをNVM230に定期的に、又は電源切断イベント中(例えば装置をオフにした時)に記憶することができる。NVM230に正常性情報を記憶した場合、電源投入中にこの情報を取り出して正常性データベース215に投入することができる。

【0040】

NVMインターフェイス218は論理アドレスを記憶して、NVM230の電源投入時又はNVM230の動作中に、電子装置200がその位置にどのようなデータが存在するかを判断できるようにすることができる。具体的に言えば、ファイルシステム210は、ユーザデータをその物理的位置ではなくその論理的位置に従って参照できるので、NVMインターフェイス218は、ユーザデータと論理アドレスをともに記憶してこれらの関連性を維持することができる。このようにして、たとえNVM230内の物理対論理マッピングを維持するインデックステーブルが期限切れになっても、NVMインターフェイス218は、例えば電子装置200の電源投入時又は再起動時に依然として正しいマッピングを判断することができる。

【0041】

図3は、(図1のホスト102などの)ホスト装置と(図1のメモリコントローラ106などの)メモリコントローラの間で転送できるコマンドパケット300の例示的な図である。コマンドパケット300は、コマンドアクセス要求331、アドレス333、正常性情報335、データ337、及びメタデータ339を含むことができる。コマンドアクセス要求331は、例えば読み取り要求、プログラム要求又は消去要求などの、ホスト装置によってメモリコントローラに提供されるあらゆる好適な命令とすることができる。アドレス333は、アクセスされるNVM内の(単複の)物理アドレスとすることができる。例えば、この(単複の)アドレスは、(トランスレーションレイヤ214などの)トランスレーションレイヤから導出することができる。

【0042】

コマンドパケットは、正常性情報335を含むこともできる。正常性情報335は、アドレス333に関連付けることができ、従って本明細書ではアドレス固有の正常性情報と呼ぶことができる。ホストコントローラは、このアドレス固有の正常性情報を(正常性データベース215などの)正常性データベースから取り出して、これをコマンドパケット300に含めることができる。メモリコントローラは、コマンドパケット300を受け取ると、正常性情報335を抽出し、これを処理し、これに応じてコマンドアクセス要求331を実行することができる。いくつかの実施形態によれば、正常性情報335が、ページの正確性、閾値電圧、NVMの該当部分を読み取り、プログラムし、又は消去するために必要なサイクル時間及び/又はサイクル数などの、アドレス固有のNVM正常性インジケータを含むことができる。他の実施形態では、正常性情報335を正常性等級とすることができ、この正常性等級は、個々のNVM正常性インジケータから計算したNVMの一般化した正常性指示とすることができる。正常性情報335は、メモリコントローラ220に特有のものとすることができ、従ってメモリコントローラのみがこれを解釈して使用することができる。従って、どのメーカーがメモリコントローラ及びNVMを生産したかに関わらず、メモリコントローラは、コマンドパケット300に含まれる正常性情報を受け取り、これを処理して使用することができる。さらに、ホストコントローラは、正常性情報の内容については全く知ることができない。

【0043】

データ構造330は、データ337及びメタデータ339を含むこともできる。例えば、アクセス要求がプログラム要求である場合、データ337は、NVMに対してプログラムされたデータであることができる。データ337は、あらゆる好適な種類のデータとすることができる。ホスト装置がメディアプレーヤである実施形態では、データ337が、(楽曲、ビデオ、画像、eブックなどの)1又はそれ以上のメディアファイルを表すことができる。メタデータ339は、論理アドレスと物理アドレスの間のマッピング管理、不良ブロック管理、ウェアレベリング、データエラーを検出して補正するために使用される誤り訂正符号(「ECC」)データ、又はこれらのいずれかの組み合わせを管理するために使用されるあらゆる情報を含むことができる。

【0044】

例示的なコマンドプログラム要求では、メモリコントローラが、最初のバスサイクルで(図1の通信チャネル116などの)通信チャネルを介してホスト装置からプログラムコマンドパケットを受け取り、これをコマンドレジスタ(揮発性メモリ122など)に記憶することができる。次に、1又はそれ以上のバスサイクルを使用して、揮発性メモリのアドレスレジスタにアドレス333を入力することができる。次に、ページバッファ内にデータ337及びメタデータ339をロードして、アドレスレジスタに記憶されたNVMのアドレスにプログラムすることができる。

【0045】

例示的なコマンド読み取り要求では、メモリコントローラが、最初のバスサイクルで通信チャネルを介してホスト装置からコマンド読み取りパケットを取り出してコマンドレジスタに記憶することができる。1又はそれ以上のバスサイクルを使用して、アドレスレジスタにアドレス333を入力することができる。次に、NVMのアドレス333に記憶されたデータをページバッファに転送し、バスの準備ができたらホストに転送することができる。

【0046】

図4は、本発明の実施形態による、システムが正常性情報をどのように使用するかについてのステップを示す例示的なフローチャートである。このシステムは、とりわけ(ホスト102などの)ホスト装置、(メモリコントローラ106などの)メモリコントローラ、及び(NVM128などの)NVMを含むことができる。ステップ410において、NVMの正常性情報データベースが少なくとも1つの記憶要素内に保持される。この少なくとも1つの記憶要素は、ホスト装置に付随する揮発性メモリとすることができる。正常性情報データベースは、物理アドレス固有の正常性情報を記憶する。

【0047】

ステップ420において、メモリコントローラにコマンドが提供され、各コマンドは、コマンドアクセス要求、アドレス、及びアドレス固有の正常性情報を含む。ホスト装置は、(トランスレーションレイヤ214などの)トランスレーションレイヤから物理アドレスを取得することによってコマンドをパッケージ化し、この物理アドレスを使用して正常性情報データベースからアドレス固有の正常性情報を取り出すことができる。このホストにより編成されるコマンドパケットは、図3に関連して上述したコマンドパケットと同様のものとすることができる。

【0048】

ステップ430において、メモリコントローラが、コマンドからアドレス固有の正常性情報を抽出することができる。ステップ440において、メモリコントローラが、このアドレス固有の正常性情報に従ってアクセス要求を実行することができる。例えば、メモリコントローラは、NVMの物理アドレスに対するコマンドを実行する際に、アドレス固有の正常性情報内に存在するあらゆるハードウェア及び/又はソフトウェアパラメータを考慮する。プログラムコマンドが実行されている場合、正常性情報は、プログラミングをどれほど細かく調整すべきかを指定することができ、又は所与の位置に関するプログラム時間又は最終的なプログラム電圧レベルをどのようにすべきかを指定することができる。コントローラは、この情報を使用して、その意図される位置に最も適した形でデータをプログラムすることができる。

【0049】

ステップ450において、アドレス固有の正常性情報に従ってアクセス要求が実行されたかどうかを判定する。アドレス固有の正常性情報に従ってアクセス要求が実行された場合、プロセスはステップ480において終了する。アドレス固有の正常性情報に従ってアクセス要求が実行されなかった場合、プロセスはステップ460へ進む。例えば、アドレス固有の正常性情報に含まれているパラメータとは異なるソフトウェア及び/又はハードウェアパラメータがアクセス要求の実行に必要な場合に、プロセスはステップ460へ進むことができる。例えば、メモリコントローラは、使用した実際のパラメータを正常性情報が示唆するパラメータと比較することができる。

【0050】

ステップ460において、メモリコントローラは、変更した(単複の)パラメータをパケット内にパッケージ化することによって正常性情報を更新し、これをホスト装置に提供することができる。パケットは、アドレス及び更新済みの正常性情報を含むことができる。ステップ470において、ホスト装置は、メモリコントローラから受け取った変更済みの(単複の)パラメータを使用して、正常性情報データベース内の正常性情報を更新することができる。

【0051】

図4に示すステップは例示にすぎず、既存のステップを修正又は省略すること、追加のステップを加えること、いくつかのステップの順序を変更することができると理解されたい。

【0052】

不揮発性メモリの正常性情報を取得して使用するためのシステム及び方法について説明したが、本発明の思想及び範囲から逸脱することなく多くの変更を行うことができると理解されたい。既知のものではなくすなわち後から考案される、当業者から見た本主題からのわずかな変化も、同等に特許請求の範囲に含まれることが明確に企図される。従って、現在当業者に公知の、及び将来的に当業者に知られる明白な置換は、規定の構成要素の範囲に含まれると定義される。

【0053】

説明した本発明の実施形態は、限定ではなく例示目的で示したものである。

【技術分野】

【0001】

本文献は、不揮発性メモリの正常性(health)情報を取得して使用するためのシステム及び方法に関する。

【背景技術】

【0002】

大容量記憶装置には、フラッシュメモリ(例えば、NANDフラッシュメモリ及びNORフラッシュメモリ)などの、様々な種類の不揮発性メモリ(「NVM」)を使用することができる。例えば、(ポータブルメディアプレーヤなどの)消費者向け電子機器は、音楽、ビデオ、画像、及びその他のメディア又はタイプの情報を含むデータを記憶するためにフラッシュメモリを使用する。

【0003】

一部のフラッシュメモリシステムでは、ホストシステムが論理ブロックアドレス(LBA)の読み取り動作及びプログラム動作を要求し、このLBAがフラッシュメモリの物理ブロックアドレスにマッピング又は変換される。このマッピングにより、ホストオペレーティングシステムが、ディスクドライブと同様の方法でフラッシュメモリにアクセスできるようになる。フラッシュメモリは、ランダムアクセス方式で一度に1バイト又は1ワードを読み取り又はプログラムすることができるが、通常は一度に1ブロックが消去される。新たに消去されたブロックから開始して、このブロック内のあらゆるバイトをプログラムすることができる。バイトは、一旦プログラムされると、通常はブロック全体が消去されるまで再プログラムすることができない。フラッシュメモリの消去プログラムのサイクル数には限りがあるので、フラッシュメモリの寿命を引き延ばすには、消去プログラムのサイクル数を最小にすることが望ましい。

【発明の概要】

【発明が解決しようとする課題】

【0004】

上述したフラッシュメモリの固有の特性を背景として、フラッシュメモリ及びその他のNVMの正常性情報を効率的に取得して使用できるシステム、方法及び装置が必要とされている。

【課題を解決するための手段】

【0005】

不揮発性フラッシュメモリ(NVM)の正常性(health)情報を取得して使用するためのシステム及び方法を開示する。本発明の実施形態は、ホスト及び不揮発性メモリパッケージを有するシステムで動作することができる。ホストは揮発性メモリを含み、論理対物理マッピングの維持、プログラムの発行、NVMパッケージに対するコマンドの読み取り又は消去、及びウェアレベリング及びガベージコレクションの実行などの不揮発性メモリの機能を実行することができる。ホストは、本発明の実施形態による正常性データベースを維持することもできる。NVMパッケージは、ホストに通信可能に結合され、メモリコントローラ及び(NANDフラッシュなどの)不揮発性メモリを含むことができる。いくつかの実施形態では、NVMパッケージが、誤り訂正符号エンジンを含むこともできる。

【0006】

正常性データベースは、NVMに関する情報を記憶することができる。すなわち、NVM内の(ページ又はブロックなどの)物理的位置ごとに、この物理的位置に特有の正常性情報がデータベースに記憶される。データベースに記憶される正常性情報は、NVMの特定のアドレス位置にアクセスするために使用する様々なソフトウェア及び/又はハードウェアパラメータを指定するアドレス固有の正常性情報とすることができる。正常性情報は、例えば、ページの正確性、閾値電圧、読み取り、プログラム及び消去を行うために必要なサイクル時間及び/又はサイクル数、使用する誤り訂正符号などを含むことができる。正常性情報は、メモリコントローラにより生成することができるが、ホストによって保持されるデータベースに記憶される。正常性情報をホスト上に記憶することはできるが、ホストは、NVMを管理するために正常性情報を解釈し、修正し、又は使用することは決してない。

【0007】

ホストは、NVMにアクセスしたいと望む場合、(読み取りコマンド又はプログラムコマンドなどの)アクセスコマンド、アドレス及びアドレス固有の正常性情報を含むコマンドパケットを構築し、このコマンドパケットをメモリコントローラに提供することができる。ホストは、正常性情報データベースにアクセスして、コマンドパケットに含めるためのアドレスに基づいてアドレス固有の正常性情報を取り出す。メモリコントローラは、コマンドパケットを受け取ると正常性情報を抽出し、NVM内のアクセスされる物理的位置に対して指定されたソフトウェア及び/又はハードウェアパラメータに従ってアクセス要求を実行することができる。

【0008】

コマンドが実行された後、メモリコントローラは、アクセス要求を実行するために1又はそれ以上の動作パラメータに変更が必要であったかどうかを判定することができる。変更が必要であった場合、メモリコントローラは正常性情報を更新し、この更新した正常性情報及びNVMアドレスをホスト装置へ送信することができる。その後、ホストは、更新した正常性情報をデータベースに記憶することができる。

【0009】

全体を通じて同じ参照番号が同じ部分を示す添付図面とともに以下の詳細な説明を検討すれば、本発明の上記の及びその他の態様、その特質及び様々な特徴がより明らかになるであろう。

【図面の簡単な説明】

【0010】

【図1】本発明の様々な実施形態による、ホストとメモリコントローラを有するNVMパッケージとを含む例示的なシステムを示す図である。

【図2】本発明の様々な実施形態による例示的なシステムを示す図である。

【図3】本発明の様々な実施形態による例示的なデータ構造を示す図である。

【図4】本発明のいくつかの実施形態による、正常性情報を取得して使用する例示的な処理を示すフローチャートである。

【発明を実施するための形態】

【0011】

図1は、NVMパッケージ104及びホスト102を含むシステム100を示す図である。ホスト102は、メモリコントローラ106と、ホストインターフェイス110と、対応するNVMs128a〜nを有するメモリチップ112a〜nとを含むことができるNVMパッケージ104に正常性情報を提供するように構成することができる。例えば、システム例100に示すように、ホスト102は、NVMパッケージ104に正常性情報を提供することができ、NVMパッケージ104は、この正常性情報を使用して(読み取り動作、プログラム動作、消去動作などの)アクセス要求及び(ウェアレベリング及びガベージコレクションなどの)メモリ管理機能を実行し、これによりシステム100の性能、信頼性及び/又は電力使用を改善することができる。NVMパッケージ104は正常性情報を更新し、これをホスト102に戻して正常性情報データベースに記憶されるようにすることもできる。

【0012】

ホスト102は、ポータブルメディアプレーヤ、携帯電話機、ポケットサイズパーソナルコンピュータ、携帯情報端末(「PDA」)、デスクトップコンピュータ、ラップトップコンピュータ、及び/又はタブレットコンピュータ装置などの様々なホスト装置及び/又はシステムのいずれかとすることができる。NVMパッケージ104は、(例えば、メモリチップ112a〜n内に)NVM128a〜nを含むことができ、ボールグリッドアレイパッケージ又はその他の好適な種類の集積回路(「IC」)パッケージとすることができる。NVMパッケージ104は、ホスト102の一部であっても、及び/又はこれとは別個のものであってもよい。例えば、ホスト102を基板レベルの装置とし、NVMパッケージ104を、この基板レベルの装置上に取り付けられたメモリサブシステムとすることができる。他の実施形態では、NVMパッケージ104を、(SATAなどの)有線インターフェイス又は(Bluetooth(登録商標)などの)無線インターフェイスを使用してホスト102に結合することができる。

【0013】

ホスト102は、NVMパッケージ104と相互作用するように構成されたホストコントローラ114を含むことができる。例えば、ホスト102は、読み取り動作、プログラム動作及び消去動作などの様々なアクセス要求をNVMパッケージ104に送信することができる。ホストコントローラ114は、ソフトウェア及び/又はファームウェア命令の実行に基づいて動作を行うように構成された1又はそれ以上のプロセッサ及び/又はマイクロプロセッサを含むことができる。これに加えて及び/又はこれとは別に、ホストコントローラ114は、様々な動作を行うように構成された特定用途向け集積回路(「ASIC」)などのハードウェアベースの構成要素を含むこともできる。ホストコントローラ114は、NVMパッケージ104に送信する(コマンド、データなどの)情報を、ホスト102とNVMパッケージ104の間で共用される通信プロトコルに従ってフォーマットすることができる。

【0014】

ホスト102は、揮発性メモリ108を含む記憶要素134を含むことができる。揮発性メモリ108は、キャッシュメモリ又はRAMなどの様々な揮発性メモリタイプのいずれかとすることができる。ホスト102は、揮発性メモリ108を使用して、メモリ動作を実行し、及び/又はNVMパッケージ104から読み取っている及び/又はNVMパッケージ104に書き込んでいるデータを一時的に記憶することができる。例えば、揮発性メモリ108は、NVMパッケージ104に送信するメモリ動作の待ち行列を一時的に記憶すること、又はNVMパッケージ104から受け取ったデータを記憶することができる。また、揮発性メモリ108は、本発明の実施形態による正常性情報データベースを記憶することもできる。ホストコントローラ114は、正常性情報データベースにアクセスして、メモリコントローラ106に出すコマンドに含めるためのアドレス固有の正常性情報を取り出すことができる。十分な量の揮発性メモリをNVMパッケージ104内に保持するとコストが掛かり過ぎるので、NVMパッケージ104上の揮発性メモリとは対照的に、一般的にはホスト102上の揮発性メモリ内に正常性情報データベースを保持することが必要である。

【0015】

ホスト102は、通信チャネル116を介して、ホストインターフェイス110及びメモリコントローラ106を使用してNVMパッケージ104と通信することができる。通信チャネル116は、双方向通信に適したいずれのバスであってもよい。通信チャネル116は、固定式であっても、着脱式であっても、又は無線方式であってもよい。例えば、通信チャネル116は、ユニバーサルシリアルバス(USB)、シリアルアドバンスドテクノロジ(SATA)バス、又はその他のあらゆる好適なバスとすることができる。

【0016】

メモリコントローラ106は、ソフトウェア命令及び/又はファームウェア命令の実行に基づいて動作を行うように構成された1又はそれ以上のプロセッサ及び/又はマイクロプロセッサ120を含むことができる。これに加えて及び/又はこれとは別に、メモリコントローラ106は、様々な動作を行うように構成されたASICなどのハードウェアベースの構成要素を含むこともできる。メモリコントローラ106は、ホスト102によって出されたコマンドを実行することなどの様々な動作を行うことができる。

【0017】

ホストコントローラ114及びメモリコントローラ106は、単独で又は組み合わせて、ガベージコレクション及びウェアレベリングなどの様々なメモリ管理機能を実行することができる。メモリコントローラ106が少なくともいくつかのメモリ管理機能を実行するように構成された実施構成では、NVMパッケージ104を、「managed NVM」(又はNANDフラッシュメモリの場合には「managed NAND」)と呼ぶことができる。これは、NVNパッケージ104の外部にあるホストコントローラ114がNVMパッケージ104のメモリ管理機能を実行する「raw NVM」(又はNANDフラッシュメモリの場合には「raw NAND」)とは対照的なものとすることができる。

【0018】

いくつかの実施形態では、メモリコントローラ106を、メモリチップ112a〜nと同じパッケージに組み込むことができる。他の実施形態では、メモリコントローラ106を、ホスト102と別個の又は同じパッケージ内に物理的に配置することができる。いくつかの実施形態では、メモリコントローラ106を省き、通常はメモリコントローラ106によって行われる(ガベージコレクション及びウェアレベリングなどの)全てのメモリ管理機能を(ホストコントローラ114などの)ホストコントローラによって行うことができる。

【0019】

メモリコントローラ106は、揮発性メモリ122を含むことができる。揮発性メモリ122は、キャッシュメモリ又はRAMなどの様々な揮発性メモリタイプのいずれかとすることができる。メモリコントローラ106は、揮発性メモリ122を使用して、アクセス要求を実行し、及び/又はメモリチップ112a〜n内のNVM128a〜nから読み取っているデータ及びここに書き込んでいるデータを一時的に記憶することができる。例えば、揮発性メモリ122はファームウェアを記憶することができ、メモリコントローラ106は、このファームウェアを使用して、NVMパッケージ104上の(読み取り/プログラム動作などの)動作を行うことができる。揮発性メモリ122は、NVMパッケージ104内のNVMに関連する正常性情報を一時的に記憶することもできる。メモリコントローラ106は、NVM128a〜nを使用して、デバッグログ、命令、及びNVMパッケージ104が動作するために使用するファームウェアなどの様々な情報を永続的に記憶することができる。

【0020】

メモリコントローラ106は、永続的データ記憶に使用できるNVMs128a〜nに、共有内部バス126を使用してアクセスすることができる。NVMパッケージ104内には1つの共有内部バス126しか示していないが、NVMパッケージは、1つよりも多くの共有内部バスを含むことができる。各内部バスは、メモリチップ112a〜nに関して示すように(2個、3個、4個、8個、32個などの)複数のメモリチップに接続することができる。メモリチップ112a〜nは、積層構成を含む様々な構成で物理的に配置することができ、いくつかの実施形態によれば集積回路(IC)チップとすることができる。

【0021】

NVM128a〜nは、フローティングゲート技術又は電荷トラップ技術に基づくNANDフラッシュメモリ、NORフラッシュメモリ、消去可能プログラム可能読み取り専用メモリ(「EPROM」)、電気的消去可能プログラム可能読み取り専用メモリ(「EEPROM」)、強誘電性RAM(「FRAM(登録商標)」)、磁気抵抗性RAM(「MRAM」)、相変化メモリ(「PCM」)などの様々なNVMのいずれか、又はこれらのいずれかの組み合わせとすることができる。

【0022】

図2は、電子装置200のブロック図であり、この図には、様々な実施形態によるシステム100(図1)のファームウェア、ソフトウェア及び/又はハードウェア構成要素のいくつかをより詳細に示すことができる。電子装置200は、図1に関連して上述した特徴及び機能のいずれかを有することができ、逆もまた同様である。図示のように、破線で層の境界を定めている。どの構成要素が境界線内に入るかについての描写は例示にすぎず、1又はそれ以上の構成要素が異なる層に属することもできると理解されたい。

【0023】

電子装置200は、ファイルシステム210、ホストコントローラ212、NVMバスコントローラ216、メモリコントローラ220、及びNVM230を含むことができる。いくつかの実施形態では、ファイルシステム210及びホストコントローラ212をソフトウェア又はファームウェアモジュールとすることができ、NVMバスコントローラ216、メモリコントローラ220及びNVM230をハードウェアモジュールとすることができる。従って、これらの実施形態では、ホストコントローラ212が、NVMインターフェイス218のソフトウェア又はファームウェアの側面を表すことができ、NVMバスコントローラ216が、NVMインターフェイス218のハードウェアの側面を表すことができる。

【0024】

ファイルシステム210は、ファイルアロケーションテーブル(「FAT」)ファイルシステム又は階層型ファイルシステムプラス(「HFS+」)などのいずれかの好適な種類のファイルシステムを含むことができ、電子装置200のオペレーティングシステムの一部(例えば、図1のSoC制御回路112の一部)とすることもできる。いくつかの実施形態では、ファイルシステム210が、ページの論理対物理マッピングを行うフラッシュファイルシステムを含むことができる。これらの実施形態では、ファイルシステム210が、以下で説明するホストコントローラ212の機能の一部又は全部を実行することができ、従ってファイルシステム210とホストコントローラ212は、別個のモジュールであっても又はそうでなくてもよい。

【0025】

ファイルシステム210は、アプリケーション及びオペレーティングシステムのファイル及びフォルダ構造を管理することができる。ファイルシステム210は、電子装置200上で実行されるアプリケーション又はオペレーティングシステムの制御下で動作することができ、このアプリケーション又はオペレーティングシステムが、NVM230から情報を読み取ること又はNVM230に情報を記憶することを要求した場合、ホストコントローラ212に書き込み及び読み取りコマンドを提供することができる。ファイルシステム210は、各書き込み又は読み取りコマンドとともに、ユーザデータをどこから読み取るべきか又はどこに書き込むべきかを示すための、論理ページアドレス及びページをオフセットしたLBAなどの論理アドレスを提供することができる。

【0026】

ファイルシステム210は、NVMと直接的に互換性がない読み取り及び書き込み要求をホストコントローラ212に提供することができる。例えば、論理アドレスには、ハードドライブベースのシステムに特有の規則又はプロトコルを使用することができる。ハードドライブベースのシステムは、フラッシュメモリとは異なり、最初にブロックの消去を行わずに記憶域を上書きすることができる。さらに、ハードドライブは、装置の寿命を延ばすためにウェアレベリングを必要としなくてよい。従って、NVMインターフェイス218は、メモリ固有の、ベンダー固有の、又はこれらの両方のあらゆる機能を実行して、ファイルシステム要求の処理及びその他の管理機能をNVMに適した形で行うことができる。

【0027】

ホストコントローラ212は、トランスレーションレイヤ214を含むことができる。いくつかの実施形態では、トランスレーションレイヤ214をフラッシュトランスレーションレイヤ(「FTL」)とすることができ、又はこのFTLを含むことができる。書き込みコマンド時には、トランスレーションレイヤ214が、提供された論理アドレスを、NVM上の空いている消去済みの物理的位置にマッピングすることができる。読み取りコマンド時には、トランスレーションレイヤ214が、提供された論理アドレスを使用して、要求されるデータが記憶されている場所の物理アドレスを特定することができる。各NVMは、NVMのサイズ又はベンダーに応じて異なるレイアウトを有することができるので、このマッピング動作は、メモリ及び/又はベンダー固有のものとなり得る。トランスレーションレイヤ214は、論理対物理アドレスマッピングに加え、他のあらゆる好適な機能を実行することもできる。例えば、トランスレーションレイヤ214は、ガベージコレクション(「GC」)及びウェアレベリングなどの、フラッシュトランスレーションレイヤに特有のものとすることができる他の機能のいずれかを実行することができる。

【0028】

例えば、トランスレーションレイヤ214は、ガベージコレクションを実行して、NVM230のプログラム済みブロックを消去のために解放することができる。解放され消去されると、このメモリ位置を使用して、例えばファイルシステム210から受け取った新たなユーザデータを記憶することができる。場合によっては、GCプロセスが、プログラム済みブロックから消去済みのメモリ位置を有する別のブロックに有効なデータをコピーして、これによりプログラム済みブロック内の有効データを無効化することに関与することができる。プログラム済みブロック内のメモリ位置が全て無効になると、トランスレーションレイヤ214は、NVMバスコントローラ216に、これらのプログラム済みブロック上で消去動作を行うように指示することができる。本明細書で使用する「有効なデータ」とは、(LBAなどの)1又はそれ以上の論理アドレスに対応する直近の書き込み要求に応答してプログラムされたユーザデータを意味することができ、従って1又はそれ以上の論理アドレスに対応する有効なバージョンのユーザデータとすることができる。

【0029】

ホストコントローラ212は、アドレス固有の正常性情報を記憶するための正常性データベース215を含むことができる。正常性データベース215は、NVM230内の物理的位置に対応する情報の参照テーブルを含むことができる。ファイルシステム210が、ホストコントローラ212にコマンド及び論理アドレスを送ると、トランスレーションレイヤ214が、NVM230内の物理的位置を特定し、ホストコントローラ212が、この物理的位置を使用して、正常性データベース215からアドレス固有の正常性情報を取得する。いくつかの実施形態では、ホストコントローラ212が、メモリコントローラ220に提供するコマンドパケットに、正常性データベース215から取得した正常性情報を含める。この実施形態では、ホストコントローラ212が、データ検索エージェントとして機能し、正常性情報を使用してNVMの管理上の決定を行うことはない。ホストコントローラ212は、メモリコントローラ220から受け取った正常性情報を使用して正常性データベース215を更新することにより、データ投入エージェントとして機能することもできる。

【0030】

メモリコントローラ220は、正常性情報を生成し、これを正常性データベース215に記憶する。この結果、メモリコントローラ220のみが正常性情報を解釈して使用することができる。ホストコントローラ212は、正常性情報をデータベース215に記憶することはできるが、これを使用してNVMの管理上の決定を行うことはできない。

【0031】

(図1の揮発性メモリ108内に存在できる)正常性データベースに記憶された正常性情報は、NVMインターフェイス218又はホストインターフェイス110の下流のソフトウェア及び/又はハードウェア構成要素が、NVM230のあらゆる特定の物理的位置に対するコマンド要求をより効率的に処理できるようにする情報とすることができる。例えば、正常性情報は、例えばNVMパッケージ104上に存在するECCエンジンがいずれの誤り訂正符号を実施すべきかを指定することができる。別の例として、正常性情報は、プログラム電圧、プログラム/検証サイクルの数、及びNVM内の特定の物理的位置に必要なプログラム分解能などの、メモリコントローラハードウェアの設定を記憶することができる。

【0032】

正常性情報は、NVMの一部の劣化及び/又は障害の可能性を示すあらゆるデータを含むことができる。一般に、正常性情報は、NVMの効率的かつ信頼できる使用に関する決定を行うために使用できる、NVMに関するあらゆるデータを含むことができる。メモリコントローラ106又は220は、重要な性能及び較正パラメータを記憶することにより、コマンド要求を実行する方法を、不必要な待ち時間及びデータ破損を避けるように変更することができる。

【0033】

1つの特定の例では、正常性情報を使用して、ホストにより開始される読み取り動作を事前に補正することができる。ホストは、NVMの(ブロックなどの)特定の部分の読み取り動作を開始することができる。メモリコントローラは、この読み取り動作を受け取って、NVMの(ブロック又はページなどの)物理アドレスに関連する正常性情報を調べることができる。正常性情報は、ブロックを読み取った最後の時間、及び読み取り動作に複数の読み取りサイクルが必要であったことを示すことができる。例えば、読み取り動作に8回の読み取りサイクルを要し、使用した各読み取りサイクルで徐々に読み取り条件を変更した(例えば、閾値電圧値を徐々にシフトさせた)かもしれない。この正常性情報に基づいて、メモリコントローラは、最後の既知の成功した(単複の)読み取り条件を使用して、要求される物理的位置上の読み取り動作を実行すると決定することができる。読み取り動作がうまくいった場合、メモリコントローラは、その物理的位置(ブロックなど)に関する正常性情報をそのままホストに戻すことができる。しかしながら、読み取り動作にさらなる読み取りサイクルが必要であった場合、メモリコントローラは、その物理的位置(ブロックなど)に関する正常性情報を更新し、この更新した正常性情報をホストに戻すことができる。

【0034】

別の例では、正常性情報を使用して、ホストがプログラム動作を開始した時にNVMの一部をより効率的にプログラムすることができる。(NANDフラッシュメモリなどの)NVMは、時間、使用(読み取り/プログラムサイクル数など)、及び動作温度とともに劣化する傾向にある。この劣化は、例えばメモリセルの閾値電圧の変位の形で表れることがある。従って、正常性情報は、NVMの一部のこれらの重要なパラメータを追跡することができる。メモリコントローラ106は、NVM128a〜nの特定部分にデータをプログラムする要求をホスト102から受け取ると、このメモリ部分に関する正常性情報を参照して、プログラム済みのセルがどれほどの程度及びどれほど速く劣化しそうであるかを判断することができる。例えば、ホスト102が、(例えば、正常性情報内の時間、温度、及びサイクルデータによって示される)すぐに劣化しそうなメモリ部分に対してプログラム動作を開始した場合、メモリコントローラ106は、プログラム電圧を、予想閾値電圧ドリフトを補償するように変化させるよう決定することができる。

【0035】

いくつかの実施形態による、取得して使用できる正常性情報のさらなる例として、NVMの一部における不良ビット数、DLLタイミング設定、及び/又はデータのプログラム又は読み取りに必要なサイクル時間又はサイクル数を反映するビット誤り率データを挙げることができる。検出されたエラーを補正するためのメモリ装置の容量を示すことができるページの正確性に関して正常性情報を蓄積することもできる。例えば、エラーの訂正に必要な誤り訂正符号(「ECC」)サイクルの数、又は(高ビットフリップECC、低ビットフリップECC、ソフトウェアECCなどの)使用するECC技術が、NVMの一部の正常性を示すことができる。

【0036】

ホストコントローラ212は、(プログラム、読み取り及び消去コマンドなどの)NVMアクセスコマンドを完了するために、NVMバスコントローラ216と相互連結することができる。NVMバスコントローラ216は、メモリコントローラ220へのハードウェアインターフェイスとして機能し、バスプロトコル、データ転送率及びその他の仕様を使用してメモリコントローラ220と通信することができる。

【0037】

NVMインターフェイス218は、本明細書では「メタデータ」と呼ぶこともあるメモリ管理データに基づいてNVM230を管理することができる。このメタデータは、ホストコントローラ212によって生成することも、又はホストコントローラ212の制御下で動作するモジュールによって生成することもできる。例えば、メタデータは、論理アドレスと物理アドレスの間のマッピング、不良ブロック管理、ウェアレベリング、データエラーを検出又は訂正するために使用する誤り訂正符号(「ECC」)データ、又はこれらのいずれかの組み合わせを管理するために使用するあらゆる情報を含むことができる。メタデータは、ファイルシステム210により提供されるデータ、及び論理アドレスなどのユーザデータを含むことができる。従って、一般に「メタデータ」は、ユーザデータについての又はユーザデータに関する、或いは不揮発メモリの動作及びメモリ位置を管理するために一般的に使用されるあらゆる情報を意味することができる。いくつかの実施形態では、メタデータ及び正常性情報が互いに排他的である。

【0038】

NVMインターフェイス218は、NVM230にメタデータを記憶するように構成することができる。いくつかの実施形態では、NVMインターフェイス218が、ユーザデータに関連するメタデータを、ユーザデータが記憶されているメモリ位置と同じメモリ位置(ページなど)に記憶することができる。例えば、NVMインターフェイス218は、ユーザデータ、その関連する論理アドレス、及びユーザデータのためのECCデータをNVM230の1又はそれ以上のメモリ位置に記憶することができる。NVMインターフェイス218は、ユーザデータに関する他の種類のメタデータを同じメモリ位置に記憶することもできる。

【0039】

NVMインターフェイス218は、NVM230に正常性情報を記憶することもできる。NVMインターフェイス218は、正常性データベース215のコンテンツをNVM230に定期的に、又は電源切断イベント中(例えば装置をオフにした時)に記憶することができる。NVM230に正常性情報を記憶した場合、電源投入中にこの情報を取り出して正常性データベース215に投入することができる。

【0040】

NVMインターフェイス218は論理アドレスを記憶して、NVM230の電源投入時又はNVM230の動作中に、電子装置200がその位置にどのようなデータが存在するかを判断できるようにすることができる。具体的に言えば、ファイルシステム210は、ユーザデータをその物理的位置ではなくその論理的位置に従って参照できるので、NVMインターフェイス218は、ユーザデータと論理アドレスをともに記憶してこれらの関連性を維持することができる。このようにして、たとえNVM230内の物理対論理マッピングを維持するインデックステーブルが期限切れになっても、NVMインターフェイス218は、例えば電子装置200の電源投入時又は再起動時に依然として正しいマッピングを判断することができる。

【0041】

図3は、(図1のホスト102などの)ホスト装置と(図1のメモリコントローラ106などの)メモリコントローラの間で転送できるコマンドパケット300の例示的な図である。コマンドパケット300は、コマンドアクセス要求331、アドレス333、正常性情報335、データ337、及びメタデータ339を含むことができる。コマンドアクセス要求331は、例えば読み取り要求、プログラム要求又は消去要求などの、ホスト装置によってメモリコントローラに提供されるあらゆる好適な命令とすることができる。アドレス333は、アクセスされるNVM内の(単複の)物理アドレスとすることができる。例えば、この(単複の)アドレスは、(トランスレーションレイヤ214などの)トランスレーションレイヤから導出することができる。

【0042】

コマンドパケットは、正常性情報335を含むこともできる。正常性情報335は、アドレス333に関連付けることができ、従って本明細書ではアドレス固有の正常性情報と呼ぶことができる。ホストコントローラは、このアドレス固有の正常性情報を(正常性データベース215などの)正常性データベースから取り出して、これをコマンドパケット300に含めることができる。メモリコントローラは、コマンドパケット300を受け取ると、正常性情報335を抽出し、これを処理し、これに応じてコマンドアクセス要求331を実行することができる。いくつかの実施形態によれば、正常性情報335が、ページの正確性、閾値電圧、NVMの該当部分を読み取り、プログラムし、又は消去するために必要なサイクル時間及び/又はサイクル数などの、アドレス固有のNVM正常性インジケータを含むことができる。他の実施形態では、正常性情報335を正常性等級とすることができ、この正常性等級は、個々のNVM正常性インジケータから計算したNVMの一般化した正常性指示とすることができる。正常性情報335は、メモリコントローラ220に特有のものとすることができ、従ってメモリコントローラのみがこれを解釈して使用することができる。従って、どのメーカーがメモリコントローラ及びNVMを生産したかに関わらず、メモリコントローラは、コマンドパケット300に含まれる正常性情報を受け取り、これを処理して使用することができる。さらに、ホストコントローラは、正常性情報の内容については全く知ることができない。

【0043】

データ構造330は、データ337及びメタデータ339を含むこともできる。例えば、アクセス要求がプログラム要求である場合、データ337は、NVMに対してプログラムされたデータであることができる。データ337は、あらゆる好適な種類のデータとすることができる。ホスト装置がメディアプレーヤである実施形態では、データ337が、(楽曲、ビデオ、画像、eブックなどの)1又はそれ以上のメディアファイルを表すことができる。メタデータ339は、論理アドレスと物理アドレスの間のマッピング管理、不良ブロック管理、ウェアレベリング、データエラーを検出して補正するために使用される誤り訂正符号(「ECC」)データ、又はこれらのいずれかの組み合わせを管理するために使用されるあらゆる情報を含むことができる。

【0044】

例示的なコマンドプログラム要求では、メモリコントローラが、最初のバスサイクルで(図1の通信チャネル116などの)通信チャネルを介してホスト装置からプログラムコマンドパケットを受け取り、これをコマンドレジスタ(揮発性メモリ122など)に記憶することができる。次に、1又はそれ以上のバスサイクルを使用して、揮発性メモリのアドレスレジスタにアドレス333を入力することができる。次に、ページバッファ内にデータ337及びメタデータ339をロードして、アドレスレジスタに記憶されたNVMのアドレスにプログラムすることができる。

【0045】

例示的なコマンド読み取り要求では、メモリコントローラが、最初のバスサイクルで通信チャネルを介してホスト装置からコマンド読み取りパケットを取り出してコマンドレジスタに記憶することができる。1又はそれ以上のバスサイクルを使用して、アドレスレジスタにアドレス333を入力することができる。次に、NVMのアドレス333に記憶されたデータをページバッファに転送し、バスの準備ができたらホストに転送することができる。

【0046】

図4は、本発明の実施形態による、システムが正常性情報をどのように使用するかについてのステップを示す例示的なフローチャートである。このシステムは、とりわけ(ホスト102などの)ホスト装置、(メモリコントローラ106などの)メモリコントローラ、及び(NVM128などの)NVMを含むことができる。ステップ410において、NVMの正常性情報データベースが少なくとも1つの記憶要素内に保持される。この少なくとも1つの記憶要素は、ホスト装置に付随する揮発性メモリとすることができる。正常性情報データベースは、物理アドレス固有の正常性情報を記憶する。

【0047】

ステップ420において、メモリコントローラにコマンドが提供され、各コマンドは、コマンドアクセス要求、アドレス、及びアドレス固有の正常性情報を含む。ホスト装置は、(トランスレーションレイヤ214などの)トランスレーションレイヤから物理アドレスを取得することによってコマンドをパッケージ化し、この物理アドレスを使用して正常性情報データベースからアドレス固有の正常性情報を取り出すことができる。このホストにより編成されるコマンドパケットは、図3に関連して上述したコマンドパケットと同様のものとすることができる。

【0048】

ステップ430において、メモリコントローラが、コマンドからアドレス固有の正常性情報を抽出することができる。ステップ440において、メモリコントローラが、このアドレス固有の正常性情報に従ってアクセス要求を実行することができる。例えば、メモリコントローラは、NVMの物理アドレスに対するコマンドを実行する際に、アドレス固有の正常性情報内に存在するあらゆるハードウェア及び/又はソフトウェアパラメータを考慮する。プログラムコマンドが実行されている場合、正常性情報は、プログラミングをどれほど細かく調整すべきかを指定することができ、又は所与の位置に関するプログラム時間又は最終的なプログラム電圧レベルをどのようにすべきかを指定することができる。コントローラは、この情報を使用して、その意図される位置に最も適した形でデータをプログラムすることができる。

【0049】

ステップ450において、アドレス固有の正常性情報に従ってアクセス要求が実行されたかどうかを判定する。アドレス固有の正常性情報に従ってアクセス要求が実行された場合、プロセスはステップ480において終了する。アドレス固有の正常性情報に従ってアクセス要求が実行されなかった場合、プロセスはステップ460へ進む。例えば、アドレス固有の正常性情報に含まれているパラメータとは異なるソフトウェア及び/又はハードウェアパラメータがアクセス要求の実行に必要な場合に、プロセスはステップ460へ進むことができる。例えば、メモリコントローラは、使用した実際のパラメータを正常性情報が示唆するパラメータと比較することができる。

【0050】

ステップ460において、メモリコントローラは、変更した(単複の)パラメータをパケット内にパッケージ化することによって正常性情報を更新し、これをホスト装置に提供することができる。パケットは、アドレス及び更新済みの正常性情報を含むことができる。ステップ470において、ホスト装置は、メモリコントローラから受け取った変更済みの(単複の)パラメータを使用して、正常性情報データベース内の正常性情報を更新することができる。

【0051】

図4に示すステップは例示にすぎず、既存のステップを修正又は省略すること、追加のステップを加えること、いくつかのステップの順序を変更することができると理解されたい。

【0052】

不揮発性メモリの正常性情報を取得して使用するためのシステム及び方法について説明したが、本発明の思想及び範囲から逸脱することなく多くの変更を行うことができると理解されたい。既知のものではなくすなわち後から考案される、当業者から見た本主題からのわずかな変化も、同等に特許請求の範囲に含まれることが明確に企図される。従って、現在当業者に公知の、及び将来的に当業者に知られる明白な置換は、規定の構成要素の範囲に含まれると定義される。

【0053】

説明した本発明の実施形態は、限定ではなく例示目的で示したものである。

【特許請求の範囲】

【請求項1】

不揮発性メモリ(NVM)と、

前記NVMに第1のバスを介して通信可能に結合されたメモリコントローラと、

前記メモリコントローラに第2のバスを介して通信可能に結合された、少なくとも1つの記憶要素を有するホスト装置と、を備え、

前記ホスト装置が、

前記少なくとも1つの記憶要素内に、アドレス固有の正常性情報を記憶した前記NVMの正常性情報データベースを保持し、

各々がアクセス要求、アドレス及びアドレス固有の正常性情報を含むコマンドを、前記第2のバスを介して前記メモリコントローラに提供し、

前記メモリコントローラが、

前記コマンドから前記アドレス固有の正常性情報を抽出し、

前記アドレス固有の正常性情報に従って前記アクセス要求を実行する、ことを特徴とするシステム。

【請求項2】

前記不揮発性メモリが、NANDフラッシュメモリを含む、ことを特徴とする請求項1に記載のシステム。

【請求項3】

前記メモリコントローラがさらに、前記アドレス固有の正常性情報を更新し、該更新したアドレス固有の正常性情報を前記ホスト装置に提供する、ことを特徴とする請求項1に記載のシステム。

【請求項4】

前記ホスト装置が、さらに、前記更新したアドレス固有の正常性情報を前記正常性情報データベースに記憶する、ことを特徴とする請求項3に記載のシステム。

【請求項5】

前記ホスト装置が、前記正常性情報データベースに記憶されたいずれのアドレス固有の正常性情報とも関係なく動作する、ことを特徴とする請求項1に記載のシステム。

【請求項6】

前記ホスト装置が、前記正常性情報データベース内のいずれのアドレス固有の正常性情報も単独で修正しない、ことを特徴とする請求項1に記載のシステム。

【請求項7】

前記アドレス固有の正常性情報が、誤り訂正パラメータ、プログラムパラメータ、読み取りパラメータ、又はこれらのあらゆる組み合わせを含む、ことを特徴とする請求項1に記載のシステム。

【請求項8】

前記ホスト装置が、さらに、

ファイルシステムからファイルシステムコマンドを受け取り、

前記ファイルシステムコマンドから、アクセスすべき物理アドレスを判断し、

前記正常性情報データベースにアクセスして、前記物理アドレスに対応するアドレス固有の正常性情報を取り出し、

前記取り出したアドレス固有の正常性情報及び前記物理アドレスを、前記NVMコントローラに提供する前記コマンドに組み入れる、ことを特徴とする請求項1に記載のシステム。

【請求項9】

不揮発性メモリ(NVM)と通信するメモリコントローラにより実施される方法であって、

アクセス要求と、

アドレスと、

前記アドレスに関連するアドレス固有の正常性情報と、

を含むコマンドをメモリコントローラにおいてホスト装置から受け取るステップと、

前記アドレス固有の正常性情報を処理して少なくとも1つのNVM動作パラメータを取得するステップと、

前記少なくとも1つのNVM動作パラメータに従って前記アクセス要求を実行するステップと、を含むことを特徴とする方法。

【請求項10】

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったかどうかを判定するステップと、

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったと判定された場合、前記少なくとも1つの動作パラメータに前記変更を含めるように前記正常性情報を更新するステップと、

前記更新した正常性情報及び前記アドレスを前記ホスト装置に送信するステップと、をさらに含むことを特徴とする請求項9に記載の方法。

【請求項11】

前記少なくとも1つのNVM動作パラメータが、誤り訂正符号(ECC)パラメータを含む、ことを特徴とする請求項9に記載の方法。

【請求項12】

前記少なくとも1つのNVM動作パラメータが、読み取りパラメータを含む、ことを特徴とする請求項9に記載の方法。

【請求項13】

前記少なくとも1つのNVM動作パラメータが、プログラムパラメータを含む、ことを特徴とする請求項9に記載の方法。

【請求項14】

前記アクセス要求が、読み取り要求又はプログラム要求である、ことを特徴とする請求項9に記載の方法。

【請求項15】

ホストと通信するためのインターフェイスと、

不揮発性メモリ(NVM)と、

前記インターフェイス及び前記NVMに結合されたコントローラと、を含み、

前記コントローラが、

前記インターフェイスから、アクセス要求、アドレス及び正常性情報を含むコマンドを受け取り、

前記正常性情報を処理して少なくとも1つのNVM動作パラメータを取得し、

前記少なくとも1つのNVM動作パラメータに従って前記アクセス要求を実行する、ことを特徴とする不揮発性メモリパッケージ。

【請求項16】

前記コントローラが、さらに、

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったかどうかを判定し、

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったと判定された場合、前記少なくとも1つの動作パラメータに前記変更を含めるように前記正常性情報を更新し、

前記更新した正常性情報及び前記アドレスを前記インターフェイスに送信する、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項17】

前記少なくとも1つのNVM動作パラメータが、誤り訂正符号(ECC)パラメータを含む、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項18】

前記少なくとも1つのNVM動作パラメータが、読み取りパラメータを含む、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項19】

前記少なくとも1つのNVM動作パラメータが、プログラムパラメータを含む、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項20】

前記メモリコントローラに結合された誤り訂正符号(ECC)エンジンをさらに含み、前記メモリコントローラが、前記ECCエンジンに前記ECCパラメータを使用するように指示する、ことを特徴とする請求項17に記載の不揮発性メモリパッケージ。

【請求項1】

不揮発性メモリ(NVM)と、

前記NVMに第1のバスを介して通信可能に結合されたメモリコントローラと、

前記メモリコントローラに第2のバスを介して通信可能に結合された、少なくとも1つの記憶要素を有するホスト装置と、を備え、

前記ホスト装置が、

前記少なくとも1つの記憶要素内に、アドレス固有の正常性情報を記憶した前記NVMの正常性情報データベースを保持し、

各々がアクセス要求、アドレス及びアドレス固有の正常性情報を含むコマンドを、前記第2のバスを介して前記メモリコントローラに提供し、

前記メモリコントローラが、

前記コマンドから前記アドレス固有の正常性情報を抽出し、

前記アドレス固有の正常性情報に従って前記アクセス要求を実行する、ことを特徴とするシステム。

【請求項2】

前記不揮発性メモリが、NANDフラッシュメモリを含む、ことを特徴とする請求項1に記載のシステム。

【請求項3】

前記メモリコントローラがさらに、前記アドレス固有の正常性情報を更新し、該更新したアドレス固有の正常性情報を前記ホスト装置に提供する、ことを特徴とする請求項1に記載のシステム。

【請求項4】

前記ホスト装置が、さらに、前記更新したアドレス固有の正常性情報を前記正常性情報データベースに記憶する、ことを特徴とする請求項3に記載のシステム。

【請求項5】

前記ホスト装置が、前記正常性情報データベースに記憶されたいずれのアドレス固有の正常性情報とも関係なく動作する、ことを特徴とする請求項1に記載のシステム。

【請求項6】

前記ホスト装置が、前記正常性情報データベース内のいずれのアドレス固有の正常性情報も単独で修正しない、ことを特徴とする請求項1に記載のシステム。

【請求項7】

前記アドレス固有の正常性情報が、誤り訂正パラメータ、プログラムパラメータ、読み取りパラメータ、又はこれらのあらゆる組み合わせを含む、ことを特徴とする請求項1に記載のシステム。

【請求項8】

前記ホスト装置が、さらに、

ファイルシステムからファイルシステムコマンドを受け取り、

前記ファイルシステムコマンドから、アクセスすべき物理アドレスを判断し、

前記正常性情報データベースにアクセスして、前記物理アドレスに対応するアドレス固有の正常性情報を取り出し、

前記取り出したアドレス固有の正常性情報及び前記物理アドレスを、前記NVMコントローラに提供する前記コマンドに組み入れる、ことを特徴とする請求項1に記載のシステム。

【請求項9】

不揮発性メモリ(NVM)と通信するメモリコントローラにより実施される方法であって、

アクセス要求と、

アドレスと、

前記アドレスに関連するアドレス固有の正常性情報と、

を含むコマンドをメモリコントローラにおいてホスト装置から受け取るステップと、

前記アドレス固有の正常性情報を処理して少なくとも1つのNVM動作パラメータを取得するステップと、

前記少なくとも1つのNVM動作パラメータに従って前記アクセス要求を実行するステップと、を含むことを特徴とする方法。

【請求項10】

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったかどうかを判定するステップと、

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったと判定された場合、前記少なくとも1つの動作パラメータに前記変更を含めるように前記正常性情報を更新するステップと、

前記更新した正常性情報及び前記アドレスを前記ホスト装置に送信するステップと、をさらに含むことを特徴とする請求項9に記載の方法。

【請求項11】

前記少なくとも1つのNVM動作パラメータが、誤り訂正符号(ECC)パラメータを含む、ことを特徴とする請求項9に記載の方法。

【請求項12】

前記少なくとも1つのNVM動作パラメータが、読み取りパラメータを含む、ことを特徴とする請求項9に記載の方法。

【請求項13】

前記少なくとも1つのNVM動作パラメータが、プログラムパラメータを含む、ことを特徴とする請求項9に記載の方法。

【請求項14】

前記アクセス要求が、読み取り要求又はプログラム要求である、ことを特徴とする請求項9に記載の方法。

【請求項15】

ホストと通信するためのインターフェイスと、

不揮発性メモリ(NVM)と、

前記インターフェイス及び前記NVMに結合されたコントローラと、を含み、

前記コントローラが、

前記インターフェイスから、アクセス要求、アドレス及び正常性情報を含むコマンドを受け取り、

前記正常性情報を処理して少なくとも1つのNVM動作パラメータを取得し、

前記少なくとも1つのNVM動作パラメータに従って前記アクセス要求を実行する、ことを特徴とする不揮発性メモリパッケージ。

【請求項16】

前記コントローラが、さらに、

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったかどうかを判定し、

前記アクセス要求を実行するために前記少なくとも1つの動作パラメータに変更が必要であったと判定された場合、前記少なくとも1つの動作パラメータに前記変更を含めるように前記正常性情報を更新し、

前記更新した正常性情報及び前記アドレスを前記インターフェイスに送信する、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項17】

前記少なくとも1つのNVM動作パラメータが、誤り訂正符号(ECC)パラメータを含む、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項18】

前記少なくとも1つのNVM動作パラメータが、読み取りパラメータを含む、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項19】

前記少なくとも1つのNVM動作パラメータが、プログラムパラメータを含む、ことを特徴とする請求項15に記載の不揮発性メモリパッケージ。

【請求項20】

前記メモリコントローラに結合された誤り訂正符号(ECC)エンジンをさらに含み、前記メモリコントローラが、前記ECCエンジンに前記ECCパラメータを使用するように指示する、ことを特徴とする請求項17に記載の不揮発性メモリパッケージ。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−97789(P2013−97789A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−230293(P2012−230293)

【出願日】平成24年9月28日(2012.9.28)

【出願人】(503260918)アップル インコーポレイテッド (568)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2012−230293(P2012−230293)

【出願日】平成24年9月28日(2012.9.28)

【出願人】(503260918)アップル インコーポレイテッド (568)

【Fターム(参考)】

[ Back to top ]