不揮発性メモリ装置および暗号キー生成方法

【課題】メモリ側の情報を用いて暗号キーを安全に生成することができる暗号キー生成方法およびそれを用いた不揮発性メモリ装置を提供する。

【解決手段】電気的に書き換え可能なメモリセルアレイ(101)を有し、メモリセルアレイの予め定められた複数のメモリセルから各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出部(104、201、202)手段と、複数のメモリセルの各々の複数ビットのデジタル値に基づいて暗号キー(K)を生成する暗号キー生成部(203、204)と、を有する。

【解決手段】電気的に書き換え可能なメモリセルアレイ(101)を有し、メモリセルアレイの予め定められた複数のメモリセルから各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出部(104、201、202)手段と、複数のメモリセルの各々の複数ビットのデジタル値に基づいて暗号キー(K)を生成する暗号キー生成部(203、204)と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は電気的に書き換え可能な不揮発性の半導体メモリを搭載したメモリ装置に係り、特に記録する情報の暗号化に用いる暗号キーの生成方法に関する。

【背景技術】

【0002】

記憶媒体に格納されたデータの不正コピーを防止する方法が種々提案されている。たとえば特許文献1に開示されたメモリシステムは、NANDフラッシュメモリの先頭ブロックに記録されたCIS識別情報(通常は外部から書き換えできない)とファイル中の識別子とを読み出して比較し、不一致であれば不正コピーされたものと判断して以降の処理を中止する。

【0003】

また特許文献2に開示された記録方法では、コンテンツデータを鍵情報を用いて暗号化し、その鍵情報を含む管理情報と共に記録媒体に記録する。これにより、コンテンツをコピーしても鍵情報がないとコンテンツを復号できない。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−112824号公報

【特許文献2】国際公開第WO2005/122165号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記特許文献1に開示されたCIS識別情報は、工場生産時に書き込まれる記憶装置ごとに異なる固定値であり、出荷後に変更することができない。また特許文献2も不正使用を防止するために暗号鍵を導入しており、この鍵情報を書き換えることは想定されていない。

【0006】

しかしながら、一般にパスワードや暗号鍵などの秘密情報は、ある程度の時間が経過すれば更新する方が安全である。特に、パスワードや暗号鍵を別の英数字に更新するだけでなく、セキュリティレベルを上げるために暗号鍵のビット長を長くすることも有効である。上記特許文献に開示された方法では、不正使用を防止する目的で設けられた識別情報や鍵情報などが既に与えられたものであって、安全に変更する手段がないために、十分に高いセキュリティを得ることができないという課題があった。

【0007】

そこで、本発明の目的は、メモリ側の情報を用いて暗号キーを安全に生成することができる暗号キー生成方法およびそれを用いた不揮発性メモリ装置を提供することにある。

【課題を解決するための手段】

【0008】

本発明による不揮発性メモリ装置は、電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置であって、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出手段と、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する暗号キー生成手段と、を有することを特徴とする。

【0009】

本発明による暗号キー生成方法は、電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置における暗号キー生成方法であって、検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出し、暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する、ことを特徴とする。

【発明の効果】

【0010】

本発明により、メモリ側の情報を用いて暗号キーを安全に生成することができる。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の一実施形態による不揮発性メモリ装置におけるメモリセルのしきい値電圧のばらつき分布を模式的に示すグラフである。

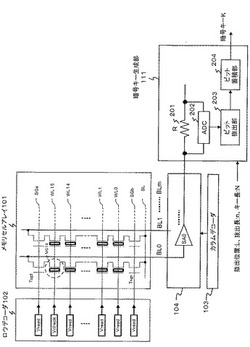

【図2】図2は、本発明の一実施形態による不揮発性メモリ装置であるメモリカードの内部回路の機能構成を示すブロック図である。

【図3】図3は、本発明の第1実施例による不揮発性メモリ装置における暗号キー生成部の機能構成および動作を説明するためにメモリカードの関連回路部分だけを示すブロック図である。

【図4】図4は、本実施例による暗号キー生成方法におけるセル選択方法の一例を示すメモリセルアレイの模式図である。

【図5】図5は、本実施例による暗号キー生成方法を示すフローチャートである。

【図6】図6は、図4に示すセル選択方法により選択されたセルのしきい値から抜き出されるビットの一例を示す模式図である。

【図7】図7は、図6に示す抜出ビットの値を用いた暗号キー生成の一例を示す模式図である。

【図8】図8は、本発明の第2実施例におけるメモリセルのしきい値電圧のばらつき分布と暗号キー生成方法の一例を模式的に示すグラフである。

【図9】図9は、本発明の第2実施例による不揮発性メモリ装置における暗号キー生成部の機能構成および動作を説明するためにメモリカードの関連回路部分だけを示すブロック図である。

【図10】図10(A)は本発明によるメモリカードのコンテンツ書き込み時の使用例、図10(B)は読み出し時の使用例をそれぞれ示すシーケンス図である。

【発明を実施するための形態】

【0012】

本発明の一実施形態によるメモリカードは電気的に書き換え可能な不揮発性メモリを有し、メモリセルのしきい値電圧がセルごとにばらついていることを利用して暗号キーを生成する。以下、本発明の一実施形態について詳細に説明するが、本発明はこの実施形態に限定されるものではなく、測定可能な電気的性質にばらつきがある不揮発性メモリを用いたメモリ装置であれば適用可能である。

【0013】

1.不揮発性メモリ

一般に、フローティングゲートに電荷を蓄積する絶縁ゲート型の不揮発性メモリでは、ソース・ドレイン間電流が流れ始めるしきい値電圧にばらつきがある。たとえば、同一シリコン基板上のメモリチップであっても、書き込み時の条件(温度、電圧)や製造時のゲート酸化膜の厚さ、加工精度のばらつき、書き込み・消去に伴なうゲート酸化膜の劣化等により、蓄積される電荷量はメモリセルごとに異なっている。このために、書き込まれているデータが同じであってもメモリセルが取り得るしきい値電圧はある分布を持ってばらついている。

【0014】

1つのメモリセルに2値データを記憶する2値型NANDフラッシュメモリを例にとると、図1に示すように、記憶データごとに、メモリセルのしきい値電圧がある範囲で分布している。ここで、図1のグラフの横軸はメモリセルのしきい値電圧、縦軸はセル数である。2値型のNANDフラッシュメモリにおけるメモリセルのしきい値電圧の分布は、消去状態とされるデータ「1」を表わすしきい値電圧の分布Aと、プログラム状態とされるデータ「0」を表わすしきい値電圧の分布Bがある。このような分布を有するフラッシュメモリであれば、分布Bを十分に超えるゲート電圧Vreadを印加することで、当該メモリセルを導通状態にすることができる。また分布Aと分布Bとの間のゲート電圧Vcheckを印加した場合、当該メモリセルの書き込みデータが「1」であれば導通状態、書き込みデータが「0」であれば非導通状態となり、当該メモリセルのソース・ドレイン電流を検出することで書き込みデータの判定が可能である。4値型NANDフラッシュメモリであれば、それぞれのデータ00/01/10/11に対応して4つのしきい値電圧の分布があり、分布間のゲート電圧を印加することで書き込まれたデータを同様に判定可能である。

【0015】

このような不揮発性メモリにおいて、消去・書き込み時に外部からの操作でしきい値電圧をある一意の値にすることは困難である。そこで、個々のセルのしきい値電圧を測定できれば、その測定値のばらつきを利用して暗号キーの離散性・固有性を高めることができる。

【0016】

2.メモリカード

図2を参照すると、本発明の一実施形態によるメモリカード100には、電気的書き換え可能な不揮発性半導体メモリを配列したメモリセルアレイ101が設けられている。メモリセルアレイ101にはNAND型フラッシュメモリが用いられ、各メモリセルはフローティングゲートに電荷を蓄積する絶縁ゲート型の半導体メモリデバイスからなる。より詳しくは、メモリセルアレイ100は複数のスタックド・ゲート構造の電気的書き換え可能な不揮発性メモリセルから構成され、各メモリセルのフローティングゲートに蓄積されている電荷量でデータの記憶を行なう。メモリセルは、図1に示すような2値型であってもよいし、多値型(たとえば、上述した4値型)であってもよい。

【0017】

メモリセルアレイ100は、ロウデコーダ102、カラムデコーダ103および書き換え/読み出し回路104により、個々のセルの選択および情報の書込/読み出しが行われる。後述するように、ロウデコーダ102は、ページ単位でセルのゲート電極に接続されたワード線を選択し、カラムデコーダ103はビット線を選択する。メモリセルアレイ101では、ページ単位でデータ書き込みおよび読み出しが実行されるので、書き換え/読み出し回路104にはビット線ごとにセンスアンプ回路およびラッチ回路が設けられている(以下、ページバッファと呼ぶ)。

【0018】

アドレスレジスタ105は、ロウデコーダ102およびカラムデコーダ103へ指定されたアドレスを出力し、ロウデコーダ102およびカラムデコーダ103は当該アドレスをデコードして対応するワード線およびビット線を選択する。

【0019】

電圧制御回路106は制御回路107により制御され、データ書き換え、消去、読み出し時に用いられる高電圧や中間電圧を発生し、メモリアレイ101やロウデコーダ102などへ供給する。ロウデコーダ102は、選択されたワード線の電圧をデータ読出、書込あるいは消去の動作に応じて変化させる。後述するように、制御回路107はデータ書き込み、消去および読み出しのシーケンス制御を行なう。

【0020】

ロジックコントロール回路108は、外部からチップイネーブル信号CEB、コマンドラッチイネーブル信号CLE、アドレスラッチイネーブル信号ALE、書き込みイネーブル信号WEB、読み出しイネーブル信号REB、ライトプロテクト信号WPBなどの外部制御信号を取り込み、動作モードに応じて内部制御信号を発生して制御回路107へ出力する。

【0021】

入出力バッファ109は、外部回路との間でデータの入出力およびアドレス信号の入力を行うために用いられる。すなわち、入出力バッファ109を通して入出力端子I/O0〜7と書き換え/読み出し回路104との間でデータが転送され、入出力端子I/O0〜7から入力されるアドレス信号はアドレスレジスタ105に蓄積され、動作制御コマンドはデコードされてコマンドレジスタ110に蓄積される。制御回路107は、コマンドレジスタ110の内容に従ってメモリカードの制御を行なう。内部制御信号は入出力バッファ109でのデータラッチ、転送などの制御に用いられ、またロジックコントロール回路108から生成された内部制御信号は制御回路107に送られ、それに従って制御回路107は動作制御を行う。

【0022】

さらに、本実施形態によるメモリカード100は暗号キー生成部111を有する。暗号キー生成部111は、後述するように、書き換え/読み出し回路104により読み出された複数の選択セルからの出力信号から暗号キーを生成し、制御回路107へ出力する。制御回路107は書き換え/読み出し回路104を通して暗号キーをメモリセルアレイ101に書き込む。暗号キー生成部111の構成及び動作については後述する。

【0023】

なお、制御回路107および暗号キー生成部111は機能的に分かれていればよく、別々のハードウエア回路で実現することもできる。また、それぞれの機能プログラムを図示しないメモリに格納しておき、これらのプログラムをCPU(中央処理装置)等のプログラム制御プロセッサ上で実行することで、制御回路107および暗号キー生成部111と同等の機能を実現することも可能である。

【0024】

3.第1実施例

本発明の第1実施例によれば、読み出されたメモリセルのしきい値電圧を所定解像度のアナログ−デジタル変換器(ADC)を用いてデジタル化し、そのビットデータを用いて暗号キーを生成する。以下、図3〜図7を参照しながら本発明の第1実施例を詳細に説明する。

【0025】

3.1)構成

図3において、NAND型フラッシュメモリのメモリセルアレイ101には複数のメモリセルMCがワード線WL0−WL15およびビット線BL0−BLmに沿って配列されているものとする。具体的には、所定数m個のメモリセルMCの制御電極(ゲート電極)がワード線WL0−WL15の各々に接続され、ワード線WL0−WL15にはロウデコーダ102によりそれぞれ選択された電圧(Vread、Vcheck、または0)が印加される。

【0026】

さらに、所定数m個の選択トランジスタTsgdのゲート電極は選択線SGaに接続され、各選択トランジスタTsgdのドレイン電極は対応するビット線に接続されている。また所定数m個の選択トランジスタTsgsのゲート電極は選択線SGbに、ソース電極は共通ソース線SLにそれぞれ接続されている。選択線SGaおよびSGbには、ロウデコーダ102によりそれぞれ選択された電圧(Vreadあるいは0)が印加される。

【0027】

また、各ビット線方向の選択トランジスタTsgdと選択トランジスタTsgsとの間には16個のメモリセルMCが直列接続されている。したがって、各ビット線と共通ソース線SLとは、対応する選択トランジスタTsgd、16個のメモリセルMCおよび選択トランジスタTsgsからなる直接回路を通して接続されている。上述したように、ワート線および選択線に電圧Vreadが印加されると、対応する選択トランジスタおよびメモリセルは導通状態となる。したがって、ビット線方向の16個のメモリセルのうち、チェック電圧Vcheckが印加されたメモリセルの蓄積電荷量に対応した電流が当該ビット線に流れることとなり、選択されたメモリセルのデータ読み出しあるいはしきい値電圧測定が可能となる。

【0028】

ビット線BL0−BLmは書き換え/読み出し回路104のセンスアンプSA0−SAmにそれぞれ接続されている。カラムデコーダ103で選択されたビット線を流れる電流は、対応するセンスアンプSAにより増幅され、後段のデータ判定あるいは暗号キー生成が実行される。

【0029】

暗号キー生成部111は、抵抗器201およびADC202からなる検出部と、ビット抜出部203およびビット蓄積部204からなる生成部とを含み、制御回路107の制御下で暗号キーの生成プロセスを実行する。まず、書き換え/読み出し回路104から出力された選択セルのチェック出力電流により抵抗器201の両端に電圧が発生し、それをADC202が所定ビット数でデジタル変換する。ADC202の分解能は任意である。ADC202のデジタル出力は、ビット抜出部203により所定の抜出位置Lの所定数nのビットが抜き出され、ビット蓄積部204により所定キー長Nになるまで蓄積されることで所定長の暗号キーが生成される。

【0030】

なお、抵抗器201およびADC202以外のビット抜出部203およびビット蓄積部204は、プログラム制御プロセッサ上でプログラムを実行することにより実現可能である。また、ビットの抜出位置L、抜き出しビット数nおよびキー長Nの設定は、工場出荷時に決定されてもよいが、ホストコンピュータから暗号キーを要求された時あるいはユーザ指定で任意に決定することも可能である。

【0031】

3.2)動作

以下、図4〜図7を参照しながら、暗号キー生成方法について詳細に説明する。

【0032】

先ず、図4に示すように、制御回路107には、暗号キーを作成するために使用するメモリセルが予め決められている。一例として、16個のメモリセルを用いる場合には、ブロックBlock0におけるページPage0の先頭16ビットを構成する16個のメモリセルMCを先頭から順に使うようにしておけばよい。あるいは、すでに値が書き込まれているページの任意のメモリセル16個を選択して使用することもできる。

【0033】

また、暗号キー長さ(N)は任意であるが、以下の説明ではN=64ビット長の暗号キーを作成するものとし、ADC202の分解能は8ビットであるものとする。また、後述するように、ビット抜出部203によるビット抜出位置Lおよび抜き出されるビット数nは、MSBを除く上位4ビット分であるものとする。したがって、1つのメモリセルから4ビット分の値が生成されるので、64ビットの暗号キーを生成するために全部で16個のメモリセルが使用される。

【0034】

制御回路107は、外部機器から制御信号(CEB/CLE/ALE/WEB/REB/WPB)および入出力端子I/O0〜7により暗号キー生成要求を受信すると、暗号キー生成プロセスを開始する。この暗号キー生成要求は外部機器が著作権保護したいデータを書き込む場合、具体的には工場での生産時、メモリカード100の初期化を行う時、あるいはメモリセルアレイ101に暗号キーが存在しない時などである。

【0035】

図5において、暗号キー生成プロセスが開始されると、制御回路107はロウデコーダ102およびカラムデコーダ103を制御して所定の暗号生成用メモリセルを選択する(ステップS401)。たとえば、図3に示すようにメモリセルMC15が選択されたとすれば、ロウデコーダ102はそのワード線WL15にチェック用電圧Vcheckを出力すると共に、それ以外のワード線WL0〜WL14、選択線SGDおよびSDSには導通ゲート電圧Vreadを出力して導通状態にする。チェック用電圧Vcheckは、図1に示すように分布Aと分布Bの間にあるので、データ「0」のメモリセルでは非導通であるが、データ「1」のメモリセルではそのしきい値電圧と電圧Vcheckとの電位差に応じたソース・ドレイン電流を得ることができる。

【0036】

チェック用電圧Vcheckがワード線WL15に印加されると、ワード線WL15に接続されたメモリセルMCのうちデータ「1」を記憶したメモリセルにおいてしきい値電圧に応じたソース・ドレイン電流が流れる状態となる。図3に例示するようにカラムデコーダ103によってビットラインBL0のみが選択されると、センスアンプSA0から出力される電流にはメモリセルMC15のフローティングゲートに蓄積される電荷量が反映されている。図1に示すように、メモリセルMC15のしきい値電圧が分布Aのなかで比較的高い場合には、チェック用電圧Vcheckとの電位差が小さいので検出されるビット線の電流量は小さく、逆にしきい値電圧が比較的低い場合には電流量は大きくなる。

【0037】

こうしてメモリセルMC15の蓄積電荷量に対応した電流が書き換え/読み出し回路104のセンスアンプSA0から読み出されると(ステップS402)、ADC202は抵抗器201の両端の電圧を8ビットのデジタルデータに変換し(ステップS403)、ビット抜出部203へ出力する。

【0038】

ビット抜出部203は、予め設定されたビット抜出位置Lおよび抜出ビット数nに従って、8ビットデータから4ビット分を抜き出しビット蓄積部204へ出力する(ステップS404)。ここでは、図6に示すように、ADC202が出力する8ビットのAD変換値から最上位ビット(MSB)のbit7と下位3ビット(bit0〜2)を削除したbit3〜6を抜き出し、ビット蓄積部204に蓄積する。

【0039】

ビット蓄積部204は、図7に示すように、ビット抜出部203から入力した4ビットの値を暗号キーの最上位ビットから順に並べ、所定ビット数N(=64ビット)に到達したか否かを判定する(ステップS405)。N<64であれば(ステップS405;NO)、制御回路107はN=64に到達するまで暗号生成用メモリセルを順次選択しながら、上記ステップS401−S404を繰り返す。所定長N=64に到達すると(ステップS405;YES)、ビット蓄積部204はNビット暗号キーKを制御回路107へ出力し、制御回路107は暗号キーKをメモリセルアレイ101の所定位置に書き込む(ステップS406)。なお、暗号キーKを格納する記憶領域をメモリセルアレイ101とは別個に設けることもできる。この場合、メモリセルアレイ101の内容がすべてコピーされたとしても、暗号キーKはコピーされないのでセキュリティを更に強化できる。

【0040】

具体例として図6および図7を参照すると、Block0/Page0の先頭から16ビット分のメモリセルを使用して64ビット長の暗号キーを生成する。まず、Page0の先頭1ビット目のメモリセルのしきい値電圧を読出し、その8ビットAD変換値が「01101001b」(bは二進数であることを示す)であるとする。ビット抜出部203は、8ビットAD変換値が「01101001b」からbit3〜6の値「1101b」を抜き出し、ビット蓄積部204は抜き出された「1101b」を暗号キーの先頭部分に配置する。

【0041】

続いて、2ビット目のメモリセルを使用して8ビットAD変換値「11010010b」が得られたものとすれば、そこからbit3〜6の値「1010b」を抜き出して、すでに生成した暗号キー「1101b」の下位側に続けて配置する。以上のビット蓄積動作を所定の64ビット長となるまで繰返すことで、暗号キーKを得ることができる。

【0042】

3.3)効果

以上説明した本実施例による暗号キー生成方法は次の効果を奏する。

【0043】

第1の効果としては、フラッシュメモリのしきい値電圧のばらつきを用いてメモリカードの暗号キーを生成しているので、離散性が高く、またフラッシュメモリごとに固有な暗号キーを生成できる。

【0044】

第2の効果としては、メモリカードの内部回路に基づいて暗号キーを生成しているので、ユーザの手に渡った後でも暗号キーを新たに生成でき、必要に応じて暗号キーを生成する際のビット選択方法や暗号キーのキー長を変更することも可能であるから、秘匿性の高い暗号キーを得ることができる。

【0045】

第3の効果としては、本実施例を実現するには抵抗器201およびADC202を追加するだけよいので低いコストで実現が可能である。

【0046】

4.第2実施例

上記第1実施例では、NAND型フラッシュメモリのしきい値電圧をAD変換で数値化したが、しきい値電圧をAD変換器ではなくNAND型フラッシュメモリで一般的に行なわれるデータ読み出し方法により数値化することも可能である。本発明の第2実施例による暗号キー生成方法を図8を参照しながら説明する。

【0047】

図8に示すように、2値型NANDフラッシュメモリのメモリセルが、データ「1」を表わすしきい値電圧の分布Cと、データ「0」を表わすしきい値電圧の分布Dを有するものとする。暗号キーの生成に用いるメモリセルがプログラム状態でデータ「0」だとすれば、このメモリセルのしきい値電圧は電圧V0と電圧V4との間にある。そこで電圧V0とV4との間を4つの区間に分け、しきい値電圧が属している区間により2ビットの判定値を割り当てる。たとえばV0〜V1に属しているときは「00b」、V1〜V2のときは「01b」、V2〜V3のときは「10b」、V3〜V4のときは「11b」とし、その値を暗号キーの最上位ビット側から順に配置して暗号キーを生成することができる。

【0048】

ただし、この方式では1つのメモリセルから2ビット分の値しか生成できないため、64ビット長の暗号キー生成には32個のメモリセルを用いる必要がある。本実施例ではADCを使用しないため回路規模を小さくできるという利点がある。

【0049】

図9は本発明の第2実施例による暗号キー生成方法を用いたメモリカードの機能構成を示す。ただし、図3に示す第1実施例と同じ機能を有するブロックには同一参照番号を付して説明は省略する。

【0050】

図9において、本実施例による暗号キー生成部111は、書き換え/読み出し回路104の出力からデータを判定する判定部301を検出部として有し、暗号キー生成用の判定値を蓄積するビット蓄積部302を生成部として有する。電源制御回路106は、制御回路107の制御に従って、データ読み出し判定用の基準電圧Vsと暗号キー生成用の基準電圧V0−V4とを判定部301に切り替え可能に供給する。

【0051】

判定部301は、データ読み出し時には基準電圧Vsを用いて書き換え/読み出し回路104の出力から選択セルのデータを判定し読み出しデータを出力する。さらに判定部301は、暗号キー生成時には基準電圧V0−V4を用いて書き換え/読み出し回路104の出力から上述した2ビット判定値を生成し、判定値がビット蓄積部302で蓄積されて所定長の暗号キーが生成される。

【0052】

なお、本実施例における暗号キー生成部111の判定部301およびビット蓄積部302は、制御回路107と共に、プログラム制御プロセッサ上でプログラムを実行することにより同等の機能を実現することができる。したがって、本実施例によれば、上述した第1実施例のように抵抗器201やADC202を用いることなく、暗号キーを生成することができる。

【0053】

5.暗号キーの使用例

以下、メモリカード100に対してデータを記録/読み出しする場合の著作権保護方法の1例を図10を参照して簡単に説明する。

【0054】

図10(A)に示すように、ホスト機器400からメモリカード100へ暗号化コンテンツを書き込む場合には、メモリカード100をホスト機器400と接続すると(ステップS501)、ホスト機器400がメモリカード100に暗号キーが存在するか否かを判定し、暗号キーがない場合には暗号キー生成要求を行う(ステップS502)。この要求を受けて、メモリカード100は、上述したように内部のメモリセルアレイの所定セルを使用して暗号キーを生成して保存すると共に(ステップS503)、生成された暗号キーKをホスト機器400へ送信する(ステップS504)。ホスト機器400は、記録すべきコンテンツデータを暗号キーKで暗号化してメモリカード100へ送信し(ステップS506)、暗号化コンテンツデータがメモリカード100に書き込まれる(ステップS507)。

【0055】

こうして記録された暗号化コンテンツデータを読み出す場合は、図10(B)に示すように、ホスト機器400に接続すると(ステップS601)、メモリカード100はホスト機器400からの要求により暗号キーKと暗号化コンテンツデータを送信する(ステップS602、S603)。こうしてホスト機器400は暗号キーKを用いて暗号化コンテンツデータを復号することができる(ステップS604)。こうして復号されたコンテンツデータはホスト機器400の記憶領域(図示せず)に格納される。

【0056】

上述したように、メモリカード100が保持する暗号キーKはメモリカードごとに異なる数値であり、その値はホスト機器400がメモリカード100へアクセスする前に定まっている。また暗号キーKは暗号化コンテンツデータの格納場所以外の領域に存在しているため、通常外部から値を書き込むことは不可能である。

【0057】

よって、メモリカード100に記録した暗号化コンテンツデータが他のメモリカードや記憶媒体にコピーされたとしても、暗号キーKがない限り暗号化コンテンツデータの復号は不可能であり、不正コピーを防ぐことができる。

【0058】

なお、上記各実施例ではNAND型メモリフラッシュを用いたが、NOR型メモリフラッシュでも同様にメモリセルのしきい値電圧のばらつきがあるので、本発明はNOR型メモリフラッシュにも適用できる。また上記実施例ではBlock0/Page0の先頭16ビットデータを記憶するメモリセルのしきい値電圧を使用したが、他の任意のメモリセルを用いて暗号キーを生成してもよい。また、コンテンツデータは音楽データや映像データなどの著作物データであるが、これに限定されるものではなく、ユーザ指示により不正コピーを防止すべきデータ一般を含む。

【0059】

4.付記

上述した実施形態の一部あるいは全部は、以下の付記のようにも記載されうるが、これらに限定されるものではない。

【0060】

(付記1)

(付記1)

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置であって、

前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出手段と、

前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する暗号キー生成手段と、

を有することを特徴とする不揮発性メモリ装置。

【0061】

(付記2)

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする付記1に記載の不揮発性メモリ装置。

【0062】

(付記3)

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする付記1または2に記載の不揮発性メモリ装置。

【0063】

(付記4)

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする付記3に記載の不揮発性メモリ装置。

【0064】

(付記5)

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする付記1−4のいずれか1項に記載の不揮発性メモリ装置。

【0065】

(付記6)

前記暗号キー生成手段により生成された前記暗号キーを保存する保存手段を更に有し、前記メモリセルアレイに書き込まれるべきデータを暗号化または復号するために読み出されることを特徴とする付記1−5のいずれか1項に記載の不揮発性メモリ装置。

【0066】

(付記7)

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置における暗号キー生成方法であって、

検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出し、

暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する、

ことを特徴とする暗号キー生成方法。

【0067】

(付記8)

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする付記7に記載の暗号キー生成方法。

【0068】

(付記9)

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする付記7または8に記載の暗号キー生成方法。

【0069】

(付記10)

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする付記9に記載の暗号キー生成方法。

【0070】

(付記11)

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする付記7−10のいずれか1項に記載の暗号キー生成方法。

【0071】

(付記12)

前記暗号キー生成手段により生成された前記暗号キーを保存手段に保存し、前記メモリセルアレイに書き込まれるべきデータを暗号化または復号するために読み出されることを特徴とする付記7−11のいずれか1項に記載の暗号キー生成方法。

【0072】

(付記13)

付記1−6のいずれか1項に記載の不揮発性メモリ装置を含むメモリカードと、

前記メモリカードへ書き込むデータを前記暗号キーを用いて暗号化し、または前記メモリカードから読み出された暗号化データを前記暗号キーを用いて復号するホスト機器と、

からなることを特徴とするメモリシステム。

【0073】

(付記14)

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置におけるプログラム制御プロセッサを暗号キー生成装置として機能させるプログラムであって、

検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する機能と、

暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する機能と、

を前記プログラム制御プロセッサに実現することを特徴とするプログラム。

【産業上の利用可能性】

【0074】

本発明はNANDフラッシュメモリ等のメモリカードに適用可能である。

【符号の説明】

【0075】

100 メモリカード

101 メモリセルアレイ

102 ロウデコーダ

103 カラムデコーダ

104 書き換え/読み出し回路

105 アドレスレジスタ

106 電圧制御回路

107 制御回路

108 ロジックコントローラ

109 入出力バッファ

110 コマンドレジスタ

111 暗号キー生成部

201 抵抗器

202 アナログ−デジタル変換器

203 ビット抜出部

204 ビット蓄積部

301 判定部

302 ビット蓄積部

【技術分野】

【0001】

本発明は電気的に書き換え可能な不揮発性の半導体メモリを搭載したメモリ装置に係り、特に記録する情報の暗号化に用いる暗号キーの生成方法に関する。

【背景技術】

【0002】

記憶媒体に格納されたデータの不正コピーを防止する方法が種々提案されている。たとえば特許文献1に開示されたメモリシステムは、NANDフラッシュメモリの先頭ブロックに記録されたCIS識別情報(通常は外部から書き換えできない)とファイル中の識別子とを読み出して比較し、不一致であれば不正コピーされたものと判断して以降の処理を中止する。

【0003】

また特許文献2に開示された記録方法では、コンテンツデータを鍵情報を用いて暗号化し、その鍵情報を含む管理情報と共に記録媒体に記録する。これにより、コンテンツをコピーしても鍵情報がないとコンテンツを復号できない。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−112824号公報

【特許文献2】国際公開第WO2005/122165号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記特許文献1に開示されたCIS識別情報は、工場生産時に書き込まれる記憶装置ごとに異なる固定値であり、出荷後に変更することができない。また特許文献2も不正使用を防止するために暗号鍵を導入しており、この鍵情報を書き換えることは想定されていない。

【0006】

しかしながら、一般にパスワードや暗号鍵などの秘密情報は、ある程度の時間が経過すれば更新する方が安全である。特に、パスワードや暗号鍵を別の英数字に更新するだけでなく、セキュリティレベルを上げるために暗号鍵のビット長を長くすることも有効である。上記特許文献に開示された方法では、不正使用を防止する目的で設けられた識別情報や鍵情報などが既に与えられたものであって、安全に変更する手段がないために、十分に高いセキュリティを得ることができないという課題があった。

【0007】

そこで、本発明の目的は、メモリ側の情報を用いて暗号キーを安全に生成することができる暗号キー生成方法およびそれを用いた不揮発性メモリ装置を提供することにある。

【課題を解決するための手段】

【0008】

本発明による不揮発性メモリ装置は、電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置であって、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出手段と、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する暗号キー生成手段と、を有することを特徴とする。

【0009】

本発明による暗号キー生成方法は、電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置における暗号キー生成方法であって、検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出し、暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する、ことを特徴とする。

【発明の効果】

【0010】

本発明により、メモリ側の情報を用いて暗号キーを安全に生成することができる。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の一実施形態による不揮発性メモリ装置におけるメモリセルのしきい値電圧のばらつき分布を模式的に示すグラフである。

【図2】図2は、本発明の一実施形態による不揮発性メモリ装置であるメモリカードの内部回路の機能構成を示すブロック図である。

【図3】図3は、本発明の第1実施例による不揮発性メモリ装置における暗号キー生成部の機能構成および動作を説明するためにメモリカードの関連回路部分だけを示すブロック図である。

【図4】図4は、本実施例による暗号キー生成方法におけるセル選択方法の一例を示すメモリセルアレイの模式図である。

【図5】図5は、本実施例による暗号キー生成方法を示すフローチャートである。

【図6】図6は、図4に示すセル選択方法により選択されたセルのしきい値から抜き出されるビットの一例を示す模式図である。

【図7】図7は、図6に示す抜出ビットの値を用いた暗号キー生成の一例を示す模式図である。

【図8】図8は、本発明の第2実施例におけるメモリセルのしきい値電圧のばらつき分布と暗号キー生成方法の一例を模式的に示すグラフである。

【図9】図9は、本発明の第2実施例による不揮発性メモリ装置における暗号キー生成部の機能構成および動作を説明するためにメモリカードの関連回路部分だけを示すブロック図である。

【図10】図10(A)は本発明によるメモリカードのコンテンツ書き込み時の使用例、図10(B)は読み出し時の使用例をそれぞれ示すシーケンス図である。

【発明を実施するための形態】

【0012】

本発明の一実施形態によるメモリカードは電気的に書き換え可能な不揮発性メモリを有し、メモリセルのしきい値電圧がセルごとにばらついていることを利用して暗号キーを生成する。以下、本発明の一実施形態について詳細に説明するが、本発明はこの実施形態に限定されるものではなく、測定可能な電気的性質にばらつきがある不揮発性メモリを用いたメモリ装置であれば適用可能である。

【0013】

1.不揮発性メモリ

一般に、フローティングゲートに電荷を蓄積する絶縁ゲート型の不揮発性メモリでは、ソース・ドレイン間電流が流れ始めるしきい値電圧にばらつきがある。たとえば、同一シリコン基板上のメモリチップであっても、書き込み時の条件(温度、電圧)や製造時のゲート酸化膜の厚さ、加工精度のばらつき、書き込み・消去に伴なうゲート酸化膜の劣化等により、蓄積される電荷量はメモリセルごとに異なっている。このために、書き込まれているデータが同じであってもメモリセルが取り得るしきい値電圧はある分布を持ってばらついている。

【0014】

1つのメモリセルに2値データを記憶する2値型NANDフラッシュメモリを例にとると、図1に示すように、記憶データごとに、メモリセルのしきい値電圧がある範囲で分布している。ここで、図1のグラフの横軸はメモリセルのしきい値電圧、縦軸はセル数である。2値型のNANDフラッシュメモリにおけるメモリセルのしきい値電圧の分布は、消去状態とされるデータ「1」を表わすしきい値電圧の分布Aと、プログラム状態とされるデータ「0」を表わすしきい値電圧の分布Bがある。このような分布を有するフラッシュメモリであれば、分布Bを十分に超えるゲート電圧Vreadを印加することで、当該メモリセルを導通状態にすることができる。また分布Aと分布Bとの間のゲート電圧Vcheckを印加した場合、当該メモリセルの書き込みデータが「1」であれば導通状態、書き込みデータが「0」であれば非導通状態となり、当該メモリセルのソース・ドレイン電流を検出することで書き込みデータの判定が可能である。4値型NANDフラッシュメモリであれば、それぞれのデータ00/01/10/11に対応して4つのしきい値電圧の分布があり、分布間のゲート電圧を印加することで書き込まれたデータを同様に判定可能である。

【0015】

このような不揮発性メモリにおいて、消去・書き込み時に外部からの操作でしきい値電圧をある一意の値にすることは困難である。そこで、個々のセルのしきい値電圧を測定できれば、その測定値のばらつきを利用して暗号キーの離散性・固有性を高めることができる。

【0016】

2.メモリカード

図2を参照すると、本発明の一実施形態によるメモリカード100には、電気的書き換え可能な不揮発性半導体メモリを配列したメモリセルアレイ101が設けられている。メモリセルアレイ101にはNAND型フラッシュメモリが用いられ、各メモリセルはフローティングゲートに電荷を蓄積する絶縁ゲート型の半導体メモリデバイスからなる。より詳しくは、メモリセルアレイ100は複数のスタックド・ゲート構造の電気的書き換え可能な不揮発性メモリセルから構成され、各メモリセルのフローティングゲートに蓄積されている電荷量でデータの記憶を行なう。メモリセルは、図1に示すような2値型であってもよいし、多値型(たとえば、上述した4値型)であってもよい。

【0017】

メモリセルアレイ100は、ロウデコーダ102、カラムデコーダ103および書き換え/読み出し回路104により、個々のセルの選択および情報の書込/読み出しが行われる。後述するように、ロウデコーダ102は、ページ単位でセルのゲート電極に接続されたワード線を選択し、カラムデコーダ103はビット線を選択する。メモリセルアレイ101では、ページ単位でデータ書き込みおよび読み出しが実行されるので、書き換え/読み出し回路104にはビット線ごとにセンスアンプ回路およびラッチ回路が設けられている(以下、ページバッファと呼ぶ)。

【0018】

アドレスレジスタ105は、ロウデコーダ102およびカラムデコーダ103へ指定されたアドレスを出力し、ロウデコーダ102およびカラムデコーダ103は当該アドレスをデコードして対応するワード線およびビット線を選択する。

【0019】

電圧制御回路106は制御回路107により制御され、データ書き換え、消去、読み出し時に用いられる高電圧や中間電圧を発生し、メモリアレイ101やロウデコーダ102などへ供給する。ロウデコーダ102は、選択されたワード線の電圧をデータ読出、書込あるいは消去の動作に応じて変化させる。後述するように、制御回路107はデータ書き込み、消去および読み出しのシーケンス制御を行なう。

【0020】

ロジックコントロール回路108は、外部からチップイネーブル信号CEB、コマンドラッチイネーブル信号CLE、アドレスラッチイネーブル信号ALE、書き込みイネーブル信号WEB、読み出しイネーブル信号REB、ライトプロテクト信号WPBなどの外部制御信号を取り込み、動作モードに応じて内部制御信号を発生して制御回路107へ出力する。

【0021】

入出力バッファ109は、外部回路との間でデータの入出力およびアドレス信号の入力を行うために用いられる。すなわち、入出力バッファ109を通して入出力端子I/O0〜7と書き換え/読み出し回路104との間でデータが転送され、入出力端子I/O0〜7から入力されるアドレス信号はアドレスレジスタ105に蓄積され、動作制御コマンドはデコードされてコマンドレジスタ110に蓄積される。制御回路107は、コマンドレジスタ110の内容に従ってメモリカードの制御を行なう。内部制御信号は入出力バッファ109でのデータラッチ、転送などの制御に用いられ、またロジックコントロール回路108から生成された内部制御信号は制御回路107に送られ、それに従って制御回路107は動作制御を行う。

【0022】

さらに、本実施形態によるメモリカード100は暗号キー生成部111を有する。暗号キー生成部111は、後述するように、書き換え/読み出し回路104により読み出された複数の選択セルからの出力信号から暗号キーを生成し、制御回路107へ出力する。制御回路107は書き換え/読み出し回路104を通して暗号キーをメモリセルアレイ101に書き込む。暗号キー生成部111の構成及び動作については後述する。

【0023】

なお、制御回路107および暗号キー生成部111は機能的に分かれていればよく、別々のハードウエア回路で実現することもできる。また、それぞれの機能プログラムを図示しないメモリに格納しておき、これらのプログラムをCPU(中央処理装置)等のプログラム制御プロセッサ上で実行することで、制御回路107および暗号キー生成部111と同等の機能を実現することも可能である。

【0024】

3.第1実施例

本発明の第1実施例によれば、読み出されたメモリセルのしきい値電圧を所定解像度のアナログ−デジタル変換器(ADC)を用いてデジタル化し、そのビットデータを用いて暗号キーを生成する。以下、図3〜図7を参照しながら本発明の第1実施例を詳細に説明する。

【0025】

3.1)構成

図3において、NAND型フラッシュメモリのメモリセルアレイ101には複数のメモリセルMCがワード線WL0−WL15およびビット線BL0−BLmに沿って配列されているものとする。具体的には、所定数m個のメモリセルMCの制御電極(ゲート電極)がワード線WL0−WL15の各々に接続され、ワード線WL0−WL15にはロウデコーダ102によりそれぞれ選択された電圧(Vread、Vcheck、または0)が印加される。

【0026】

さらに、所定数m個の選択トランジスタTsgdのゲート電極は選択線SGaに接続され、各選択トランジスタTsgdのドレイン電極は対応するビット線に接続されている。また所定数m個の選択トランジスタTsgsのゲート電極は選択線SGbに、ソース電極は共通ソース線SLにそれぞれ接続されている。選択線SGaおよびSGbには、ロウデコーダ102によりそれぞれ選択された電圧(Vreadあるいは0)が印加される。

【0027】

また、各ビット線方向の選択トランジスタTsgdと選択トランジスタTsgsとの間には16個のメモリセルMCが直列接続されている。したがって、各ビット線と共通ソース線SLとは、対応する選択トランジスタTsgd、16個のメモリセルMCおよび選択トランジスタTsgsからなる直接回路を通して接続されている。上述したように、ワート線および選択線に電圧Vreadが印加されると、対応する選択トランジスタおよびメモリセルは導通状態となる。したがって、ビット線方向の16個のメモリセルのうち、チェック電圧Vcheckが印加されたメモリセルの蓄積電荷量に対応した電流が当該ビット線に流れることとなり、選択されたメモリセルのデータ読み出しあるいはしきい値電圧測定が可能となる。

【0028】

ビット線BL0−BLmは書き換え/読み出し回路104のセンスアンプSA0−SAmにそれぞれ接続されている。カラムデコーダ103で選択されたビット線を流れる電流は、対応するセンスアンプSAにより増幅され、後段のデータ判定あるいは暗号キー生成が実行される。

【0029】

暗号キー生成部111は、抵抗器201およびADC202からなる検出部と、ビット抜出部203およびビット蓄積部204からなる生成部とを含み、制御回路107の制御下で暗号キーの生成プロセスを実行する。まず、書き換え/読み出し回路104から出力された選択セルのチェック出力電流により抵抗器201の両端に電圧が発生し、それをADC202が所定ビット数でデジタル変換する。ADC202の分解能は任意である。ADC202のデジタル出力は、ビット抜出部203により所定の抜出位置Lの所定数nのビットが抜き出され、ビット蓄積部204により所定キー長Nになるまで蓄積されることで所定長の暗号キーが生成される。

【0030】

なお、抵抗器201およびADC202以外のビット抜出部203およびビット蓄積部204は、プログラム制御プロセッサ上でプログラムを実行することにより実現可能である。また、ビットの抜出位置L、抜き出しビット数nおよびキー長Nの設定は、工場出荷時に決定されてもよいが、ホストコンピュータから暗号キーを要求された時あるいはユーザ指定で任意に決定することも可能である。

【0031】

3.2)動作

以下、図4〜図7を参照しながら、暗号キー生成方法について詳細に説明する。

【0032】

先ず、図4に示すように、制御回路107には、暗号キーを作成するために使用するメモリセルが予め決められている。一例として、16個のメモリセルを用いる場合には、ブロックBlock0におけるページPage0の先頭16ビットを構成する16個のメモリセルMCを先頭から順に使うようにしておけばよい。あるいは、すでに値が書き込まれているページの任意のメモリセル16個を選択して使用することもできる。

【0033】

また、暗号キー長さ(N)は任意であるが、以下の説明ではN=64ビット長の暗号キーを作成するものとし、ADC202の分解能は8ビットであるものとする。また、後述するように、ビット抜出部203によるビット抜出位置Lおよび抜き出されるビット数nは、MSBを除く上位4ビット分であるものとする。したがって、1つのメモリセルから4ビット分の値が生成されるので、64ビットの暗号キーを生成するために全部で16個のメモリセルが使用される。

【0034】

制御回路107は、外部機器から制御信号(CEB/CLE/ALE/WEB/REB/WPB)および入出力端子I/O0〜7により暗号キー生成要求を受信すると、暗号キー生成プロセスを開始する。この暗号キー生成要求は外部機器が著作権保護したいデータを書き込む場合、具体的には工場での生産時、メモリカード100の初期化を行う時、あるいはメモリセルアレイ101に暗号キーが存在しない時などである。

【0035】

図5において、暗号キー生成プロセスが開始されると、制御回路107はロウデコーダ102およびカラムデコーダ103を制御して所定の暗号生成用メモリセルを選択する(ステップS401)。たとえば、図3に示すようにメモリセルMC15が選択されたとすれば、ロウデコーダ102はそのワード線WL15にチェック用電圧Vcheckを出力すると共に、それ以外のワード線WL0〜WL14、選択線SGDおよびSDSには導通ゲート電圧Vreadを出力して導通状態にする。チェック用電圧Vcheckは、図1に示すように分布Aと分布Bの間にあるので、データ「0」のメモリセルでは非導通であるが、データ「1」のメモリセルではそのしきい値電圧と電圧Vcheckとの電位差に応じたソース・ドレイン電流を得ることができる。

【0036】

チェック用電圧Vcheckがワード線WL15に印加されると、ワード線WL15に接続されたメモリセルMCのうちデータ「1」を記憶したメモリセルにおいてしきい値電圧に応じたソース・ドレイン電流が流れる状態となる。図3に例示するようにカラムデコーダ103によってビットラインBL0のみが選択されると、センスアンプSA0から出力される電流にはメモリセルMC15のフローティングゲートに蓄積される電荷量が反映されている。図1に示すように、メモリセルMC15のしきい値電圧が分布Aのなかで比較的高い場合には、チェック用電圧Vcheckとの電位差が小さいので検出されるビット線の電流量は小さく、逆にしきい値電圧が比較的低い場合には電流量は大きくなる。

【0037】

こうしてメモリセルMC15の蓄積電荷量に対応した電流が書き換え/読み出し回路104のセンスアンプSA0から読み出されると(ステップS402)、ADC202は抵抗器201の両端の電圧を8ビットのデジタルデータに変換し(ステップS403)、ビット抜出部203へ出力する。

【0038】

ビット抜出部203は、予め設定されたビット抜出位置Lおよび抜出ビット数nに従って、8ビットデータから4ビット分を抜き出しビット蓄積部204へ出力する(ステップS404)。ここでは、図6に示すように、ADC202が出力する8ビットのAD変換値から最上位ビット(MSB)のbit7と下位3ビット(bit0〜2)を削除したbit3〜6を抜き出し、ビット蓄積部204に蓄積する。

【0039】

ビット蓄積部204は、図7に示すように、ビット抜出部203から入力した4ビットの値を暗号キーの最上位ビットから順に並べ、所定ビット数N(=64ビット)に到達したか否かを判定する(ステップS405)。N<64であれば(ステップS405;NO)、制御回路107はN=64に到達するまで暗号生成用メモリセルを順次選択しながら、上記ステップS401−S404を繰り返す。所定長N=64に到達すると(ステップS405;YES)、ビット蓄積部204はNビット暗号キーKを制御回路107へ出力し、制御回路107は暗号キーKをメモリセルアレイ101の所定位置に書き込む(ステップS406)。なお、暗号キーKを格納する記憶領域をメモリセルアレイ101とは別個に設けることもできる。この場合、メモリセルアレイ101の内容がすべてコピーされたとしても、暗号キーKはコピーされないのでセキュリティを更に強化できる。

【0040】

具体例として図6および図7を参照すると、Block0/Page0の先頭から16ビット分のメモリセルを使用して64ビット長の暗号キーを生成する。まず、Page0の先頭1ビット目のメモリセルのしきい値電圧を読出し、その8ビットAD変換値が「01101001b」(bは二進数であることを示す)であるとする。ビット抜出部203は、8ビットAD変換値が「01101001b」からbit3〜6の値「1101b」を抜き出し、ビット蓄積部204は抜き出された「1101b」を暗号キーの先頭部分に配置する。

【0041】

続いて、2ビット目のメモリセルを使用して8ビットAD変換値「11010010b」が得られたものとすれば、そこからbit3〜6の値「1010b」を抜き出して、すでに生成した暗号キー「1101b」の下位側に続けて配置する。以上のビット蓄積動作を所定の64ビット長となるまで繰返すことで、暗号キーKを得ることができる。

【0042】

3.3)効果

以上説明した本実施例による暗号キー生成方法は次の効果を奏する。

【0043】

第1の効果としては、フラッシュメモリのしきい値電圧のばらつきを用いてメモリカードの暗号キーを生成しているので、離散性が高く、またフラッシュメモリごとに固有な暗号キーを生成できる。

【0044】

第2の効果としては、メモリカードの内部回路に基づいて暗号キーを生成しているので、ユーザの手に渡った後でも暗号キーを新たに生成でき、必要に応じて暗号キーを生成する際のビット選択方法や暗号キーのキー長を変更することも可能であるから、秘匿性の高い暗号キーを得ることができる。

【0045】

第3の効果としては、本実施例を実現するには抵抗器201およびADC202を追加するだけよいので低いコストで実現が可能である。

【0046】

4.第2実施例

上記第1実施例では、NAND型フラッシュメモリのしきい値電圧をAD変換で数値化したが、しきい値電圧をAD変換器ではなくNAND型フラッシュメモリで一般的に行なわれるデータ読み出し方法により数値化することも可能である。本発明の第2実施例による暗号キー生成方法を図8を参照しながら説明する。

【0047】

図8に示すように、2値型NANDフラッシュメモリのメモリセルが、データ「1」を表わすしきい値電圧の分布Cと、データ「0」を表わすしきい値電圧の分布Dを有するものとする。暗号キーの生成に用いるメモリセルがプログラム状態でデータ「0」だとすれば、このメモリセルのしきい値電圧は電圧V0と電圧V4との間にある。そこで電圧V0とV4との間を4つの区間に分け、しきい値電圧が属している区間により2ビットの判定値を割り当てる。たとえばV0〜V1に属しているときは「00b」、V1〜V2のときは「01b」、V2〜V3のときは「10b」、V3〜V4のときは「11b」とし、その値を暗号キーの最上位ビット側から順に配置して暗号キーを生成することができる。

【0048】

ただし、この方式では1つのメモリセルから2ビット分の値しか生成できないため、64ビット長の暗号キー生成には32個のメモリセルを用いる必要がある。本実施例ではADCを使用しないため回路規模を小さくできるという利点がある。

【0049】

図9は本発明の第2実施例による暗号キー生成方法を用いたメモリカードの機能構成を示す。ただし、図3に示す第1実施例と同じ機能を有するブロックには同一参照番号を付して説明は省略する。

【0050】

図9において、本実施例による暗号キー生成部111は、書き換え/読み出し回路104の出力からデータを判定する判定部301を検出部として有し、暗号キー生成用の判定値を蓄積するビット蓄積部302を生成部として有する。電源制御回路106は、制御回路107の制御に従って、データ読み出し判定用の基準電圧Vsと暗号キー生成用の基準電圧V0−V4とを判定部301に切り替え可能に供給する。

【0051】

判定部301は、データ読み出し時には基準電圧Vsを用いて書き換え/読み出し回路104の出力から選択セルのデータを判定し読み出しデータを出力する。さらに判定部301は、暗号キー生成時には基準電圧V0−V4を用いて書き換え/読み出し回路104の出力から上述した2ビット判定値を生成し、判定値がビット蓄積部302で蓄積されて所定長の暗号キーが生成される。

【0052】

なお、本実施例における暗号キー生成部111の判定部301およびビット蓄積部302は、制御回路107と共に、プログラム制御プロセッサ上でプログラムを実行することにより同等の機能を実現することができる。したがって、本実施例によれば、上述した第1実施例のように抵抗器201やADC202を用いることなく、暗号キーを生成することができる。

【0053】

5.暗号キーの使用例

以下、メモリカード100に対してデータを記録/読み出しする場合の著作権保護方法の1例を図10を参照して簡単に説明する。

【0054】

図10(A)に示すように、ホスト機器400からメモリカード100へ暗号化コンテンツを書き込む場合には、メモリカード100をホスト機器400と接続すると(ステップS501)、ホスト機器400がメモリカード100に暗号キーが存在するか否かを判定し、暗号キーがない場合には暗号キー生成要求を行う(ステップS502)。この要求を受けて、メモリカード100は、上述したように内部のメモリセルアレイの所定セルを使用して暗号キーを生成して保存すると共に(ステップS503)、生成された暗号キーKをホスト機器400へ送信する(ステップS504)。ホスト機器400は、記録すべきコンテンツデータを暗号キーKで暗号化してメモリカード100へ送信し(ステップS506)、暗号化コンテンツデータがメモリカード100に書き込まれる(ステップS507)。

【0055】

こうして記録された暗号化コンテンツデータを読み出す場合は、図10(B)に示すように、ホスト機器400に接続すると(ステップS601)、メモリカード100はホスト機器400からの要求により暗号キーKと暗号化コンテンツデータを送信する(ステップS602、S603)。こうしてホスト機器400は暗号キーKを用いて暗号化コンテンツデータを復号することができる(ステップS604)。こうして復号されたコンテンツデータはホスト機器400の記憶領域(図示せず)に格納される。

【0056】

上述したように、メモリカード100が保持する暗号キーKはメモリカードごとに異なる数値であり、その値はホスト機器400がメモリカード100へアクセスする前に定まっている。また暗号キーKは暗号化コンテンツデータの格納場所以外の領域に存在しているため、通常外部から値を書き込むことは不可能である。

【0057】

よって、メモリカード100に記録した暗号化コンテンツデータが他のメモリカードや記憶媒体にコピーされたとしても、暗号キーKがない限り暗号化コンテンツデータの復号は不可能であり、不正コピーを防ぐことができる。

【0058】

なお、上記各実施例ではNAND型メモリフラッシュを用いたが、NOR型メモリフラッシュでも同様にメモリセルのしきい値電圧のばらつきがあるので、本発明はNOR型メモリフラッシュにも適用できる。また上記実施例ではBlock0/Page0の先頭16ビットデータを記憶するメモリセルのしきい値電圧を使用したが、他の任意のメモリセルを用いて暗号キーを生成してもよい。また、コンテンツデータは音楽データや映像データなどの著作物データであるが、これに限定されるものではなく、ユーザ指示により不正コピーを防止すべきデータ一般を含む。

【0059】

4.付記

上述した実施形態の一部あるいは全部は、以下の付記のようにも記載されうるが、これらに限定されるものではない。

【0060】

(付記1)

(付記1)

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置であって、

前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出手段と、

前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する暗号キー生成手段と、

を有することを特徴とする不揮発性メモリ装置。

【0061】

(付記2)

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする付記1に記載の不揮発性メモリ装置。

【0062】

(付記3)

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする付記1または2に記載の不揮発性メモリ装置。

【0063】

(付記4)

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする付記3に記載の不揮発性メモリ装置。

【0064】

(付記5)

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする付記1−4のいずれか1項に記載の不揮発性メモリ装置。

【0065】

(付記6)

前記暗号キー生成手段により生成された前記暗号キーを保存する保存手段を更に有し、前記メモリセルアレイに書き込まれるべきデータを暗号化または復号するために読み出されることを特徴とする付記1−5のいずれか1項に記載の不揮発性メモリ装置。

【0066】

(付記7)

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置における暗号キー生成方法であって、

検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出し、

暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する、

ことを特徴とする暗号キー生成方法。

【0067】

(付記8)

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする付記7に記載の暗号キー生成方法。

【0068】

(付記9)

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする付記7または8に記載の暗号キー生成方法。

【0069】

(付記10)

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする付記9に記載の暗号キー生成方法。

【0070】

(付記11)

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする付記7−10のいずれか1項に記載の暗号キー生成方法。

【0071】

(付記12)

前記暗号キー生成手段により生成された前記暗号キーを保存手段に保存し、前記メモリセルアレイに書き込まれるべきデータを暗号化または復号するために読み出されることを特徴とする付記7−11のいずれか1項に記載の暗号キー生成方法。

【0072】

(付記13)

付記1−6のいずれか1項に記載の不揮発性メモリ装置を含むメモリカードと、

前記メモリカードへ書き込むデータを前記暗号キーを用いて暗号化し、または前記メモリカードから読み出された暗号化データを前記暗号キーを用いて復号するホスト機器と、

からなることを特徴とするメモリシステム。

【0073】

(付記14)

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置におけるプログラム制御プロセッサを暗号キー生成装置として機能させるプログラムであって、

検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する機能と、

暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する機能と、

を前記プログラム制御プロセッサに実現することを特徴とするプログラム。

【産業上の利用可能性】

【0074】

本発明はNANDフラッシュメモリ等のメモリカードに適用可能である。

【符号の説明】

【0075】

100 メモリカード

101 メモリセルアレイ

102 ロウデコーダ

103 カラムデコーダ

104 書き換え/読み出し回路

105 アドレスレジスタ

106 電圧制御回路

107 制御回路

108 ロジックコントローラ

109 入出力バッファ

110 コマンドレジスタ

111 暗号キー生成部

201 抵抗器

202 アナログ−デジタル変換器

203 ビット抜出部

204 ビット蓄積部

301 判定部

302 ビット蓄積部

【特許請求の範囲】

【請求項1】

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置であって、

前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出手段と、

前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する暗号キー生成手段と、

を有することを特徴とする不揮発性メモリ装置。

【請求項2】

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする請求項1に記載の不揮発性メモリ装置。

【請求項3】

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする請求項1または2に記載の不揮発性メモリ装置。

【請求項4】

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする請求項3に記載の不揮発性メモリ装置。

【請求項5】

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする請求項1−4のいずれか1項に記載の不揮発性メモリ装置。

【請求項6】

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置における暗号キー生成方法であって、

検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出し、

暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する、

ことを特徴とする暗号キー生成方法。

【請求項7】

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする請求項6に記載の暗号キー生成方法。

【請求項8】

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする請求項6または7に記載の暗号キー生成方法。

【請求項9】

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする請求項8に記載の暗号キー生成方法。

【請求項10】

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする請求項6−9のいずれか1項に記載の暗号キー生成方法。

【請求項1】

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置であって、

前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出する検出手段と、

前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する暗号キー生成手段と、

を有することを特徴とする不揮発性メモリ装置。

【請求項2】

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする請求項1に記載の不揮発性メモリ装置。

【請求項3】

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする請求項1または2に記載の不揮発性メモリ装置。

【請求項4】

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする請求項3に記載の不揮発性メモリ装置。

【請求項5】

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする請求項1−4のいずれか1項に記載の不揮発性メモリ装置。

【請求項6】

電気的に書き換え可能なメモリセルアレイを有する不揮発性メモリ装置における暗号キー生成方法であって、

検出手段が、前記メモリセルアレイの予め定められた複数のメモリセルから、各メモリセルのしきい値電圧を示す電気量を複数ビットのデジタル値で検出し、

暗号キー生成手段が、前記複数のメモリセルの各々の前記複数ビットのデジタル値に基づいて暗号キーを生成する、

ことを特徴とする暗号キー生成方法。

【請求項7】

前記複数のメモリセルおよびその個数が変更可能であることを特徴とする請求項6に記載の暗号キー生成方法。

【請求項8】

前記暗号キー生成手段は、前記複数ビットのデジタル値の一部のビットを抜き出すビット抜出手段を有することを特徴とする請求項6または7に記載の暗号キー生成方法。

【請求項9】

前記ビット抜出手段は前記複数ビットのデジタル値の抜出部分の位置およびビット数を変更可能であることを特徴とする請求項8に記載の暗号キー生成方法。

【請求項10】

前記暗号キー生成手段は複数ビットのデジタル値の少なくとも一部分を所定ビット数になるまで蓄積するビット蓄積手段を有することを特徴とする請求項6−9のいずれか1項に記載の暗号キー生成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−34268(P2012−34268A)

【公開日】平成24年2月16日(2012.2.16)

【国際特許分類】

【出願番号】特願2010−173483(P2010−173483)

【出願日】平成22年8月2日(2010.8.2)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成24年2月16日(2012.2.16)

【国際特許分類】

【出願日】平成22年8月2日(2010.8.2)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]