不揮発性メモリ装置及びLSI装置

【課題】不正コピーを阻止しつつ、長寿命化を図る。

【解決手段】入力されたセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とが一致した場合、CPU1から入力された論理アドレス○○○○とアドレスメモリ21内の物理先頭アドレス****とに基づいて、正しい物理アドレス※※※※(=****+○○○○)を算出し、この正しい物理アドレス※※※※及び入力された読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△をフラッシュメモリ部10から読出/書込みする。このように、セキュリティコードが一致した場合にアドレスメモリ21から物理先頭アドレスを読み出すので、不正コピーを阻止できる。また、入力される論理アドレスと、メモリ部10の物理アドレスとが異なるため、メモリ部全体の書き換え頻度を均等にでき、長寿命化を図り得る。

【解決手段】入力されたセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とが一致した場合、CPU1から入力された論理アドレス○○○○とアドレスメモリ21内の物理先頭アドレス****とに基づいて、正しい物理アドレス※※※※(=****+○○○○)を算出し、この正しい物理アドレス※※※※及び入力された読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△をフラッシュメモリ部10から読出/書込みする。このように、セキュリティコードが一致した場合にアドレスメモリ21から物理先頭アドレスを読み出すので、不正コピーを阻止できる。また、入力される論理アドレスと、メモリ部10の物理アドレスとが異なるため、メモリ部全体の書き換え頻度を均等にでき、長寿命化を図り得る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体メモリ全般に適用可能な不揮発性メモリ及びLSI(large-scale integrated circuit)装置に係り、例えば、不正コピーを阻止しつつ、長寿命化を図り得る不揮発性メモリ装置及びLSI装置に関する。

【背景技術】

【0002】

フラッシュメモリを始めとする不揮発性メモリは、書換え可能機能を特徴とする反面、書き換え回数に制限があることや、セキュリティ上、ぜい弱な部分があるといった不都合な点がある。ここで、セキュリティ上のぜい弱な部分としては、例えば、メモリ内のデータを容易に不正コピーし得ることが挙げられる。

【0003】

この種の不正コピーは、従来のシステムではメモリ周辺機能にセキュリティ機能をもたせる方式が多く、メモリ自体にセキュリティ機能をもたせる方式が無かったため、メモリ自体からデータをコピーすることが容易であることに起因すると考えられる。

【0004】

これに対し、メモリ内のデータの不正コピーを阻止する観点から、例えば特許文献1,2に記載の技術が提案されている。特許文献1に記載の技術は、暗号化データをメモリ領域に保持しておき、不正な読出処理の際には、復号を行わずに、メモリ領域内の暗号化データを出力するものである。特許文献2に記載の技術は、データをコピーする際に禁止アドレスをアクセスすると所定サイクル後に誤データが出力されるものである。

【特許文献1】特開2002−268947号公報

【特許文献2】特願平7−243335号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1,2に記載の技術は、本発明者の検討によれば、不正コピーを阻止する技術ではあるが、書き換え回数の制限については未だ改善の余地があると考えられる。なお、一般的なメモリ構造では、書換え空間がシステム上、同じ空間を利用するため、書き換え頻度の高い空間のみメモリ寿命が短くなる。

【0006】

従って、不揮発性メモリにおいては、前述したような不正コピーを阻止しつつ、さらに、長寿命化を図る必要があると考えられる。

【0007】

本発明は上記実情を考慮してなされたもので、不正コピーを阻止しつつ、長寿命化を図り得る不揮発性メモリ装置及びLSI装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の第1の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、物理先頭アドレスを記憶するためのアドレス記憶手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、前記セキュリティコード記憶手段内のセキュリティコードに基づいて前記物理先頭アドレスを決定し、当該決定した物理先頭アドレスを前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力された論理アドレスと前記アドレス記憶手段内の物理先頭アドレスとに基づいて、物理アドレスを算出する手段と、この算出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置である。

【0009】

本発明の第2の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、物理先頭アドレスの各部分が置換されてなる被置換物理先頭アドレスを記憶するためのアドレス記憶手段と、システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された物理先頭アドレスの各部分が前記切替部により置換されてなる被置換物理先頭アドレスを前記アドレス記憶手段に伝送するための配線手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、システムコードが入力されると、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスを、前記切替信号が入力された配線手段を介して前記被置換物理先頭アドレスとして前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記切替信号が入力された配線手段を介して前記アドレス記憶手段内の被置換物理先頭アドレスを物理先頭アドレスとして読み出す第1の物理アドレス読出手段と、前記第1の物理アドレス読出手段により読み出された物理アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第1の物理アドレス算出手段と、前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記配線手段を介して前記アドレス記憶手段から被置換物理先頭アドレスを読み出す第2の物理アドレス読出手段と、前記第2の物理アドレス読出手段により読み出された被置換物理先頭アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第2の物理アドレス算出手段と、前記第1又は第2の物理アドレス算出手段により算出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置である。

【0010】

本発明の第3の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、論理アドレスに関連付けて物理アドレスを記憶するためのアドレス記憶手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを当該物理アドレスとは異なる値の論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力された論理アドレスを前記アドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す手段と、この読み出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置。

【0011】

本発明の第4の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、論理アドレスの各部分が置換されてなる被置換論理アドレスに物理アドレスを関連付けて記憶するためのアドレス記憶手段と、システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された論理アドレスの各部分が前記切替部により置換されてなる被置換論理アドレスを前記アドレス記憶手段に伝送するための配線手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを被置換論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記入力された論理アドレスを、前記切替信号が入力された配線手段を介して被置換論理アドレスとしてアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第1の物理アドレス読出手段と、前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記入力された論理アドレスを前記配線手段からアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第2の物理アドレス読出手段と、前記第1又は第2の物理アドレス読出手段により読み出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置である。

【0012】

なお、第1〜第4の各局面の不揮発性メモリ装置はLSI装置に設けてもよい。ここでいう「LSI装置」の用語は、半導体集積回路の総称として用いており、集積度によるLSIの通常の定義(1000個以上で10万個未満の素子を搭載した半導体集積回路)には限定されず、例えば、IC、SSI、MSI、LSI(通常の定義)、VLSI、ULSI又はMPUなどの上位概念として使用されている。

【0013】

(作用)

第1〜第4の局面によれば、セキュリティコードが一致した場合にアドレス記憶手段から物理先頭アドレス又は物理アドレスを読み出した後に、得られた正しい物理アドレスでメモリ部にアクセスする構成により、不正コピーを阻止することができる。

【0014】

また、第1〜第4の局面によれば、入力される論理アドレスと、メモリ部内の物理アドレスとが異なるため、メモリ部全体の書き換え頻度を均等にでき、長寿命化を図ることができる。

【発明の効果】

【0015】

以上説明したように本発明によれば、不正コピーを阻止しつつ、長寿命化を図ることができる。

【発明を実施するための最良の形態】

【0016】

以下、本発明の各実施形態について図面を用いて説明する。

(第1の実施形態)

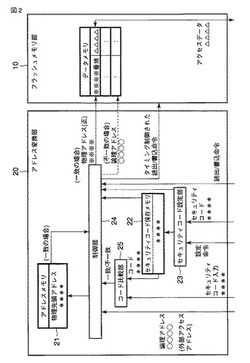

図1は本発明の第1の実施形態に係るLSI装置の構成を示す模式図であり、図2はこのLSI装置が有する不揮発性メモリ装置の構成を示す模式図である。このLSI装置は、CPU1がアドレスバス2、データバス3及びコントロールバス4を個別に介して不揮発性メモリ装置100に接続されており、各バス2〜4を介して不揮発性メモリ装置100にデータを読出/書込する機能と、通常のプログラム処理機能とをもっている。

【0017】

不揮発性メモリ装置100は、フラッシュメモリ部10及びアドレス変換部20を備えている。

【0018】

ここで、フラッシュメモリ部10は、物理アドレスに対応してデータを保持する読出/書込可能な不揮発性のメモリ部であり、アドレス変換部20からアクセス可能となっている。なお、保持データは任意であるが、例えば、通常のファイル等の他、LSI装置の機能を実現させるための基本データ(例、制御値、制御プログラム等)がある。この種の基本データは、LSI装置の動作性能を左右するものであり、システム開発者の独自の技術的知識(ノウハウ)により記述されるから、模倣・盗用を防ぐ観点からもCPU1のみが利用可能とし、外部から不正コピーされないことが望ましい。また、フラッシュメモリ部10としては、不揮発性メモリの一例としてフラッシュメモリを用いているが、これに限らず、例えば読出専用のROM等のように、フラッシュメモリ以外の不揮発性メモリを用いてもよい。

【0019】

アドレス変換部20は、アドレスメモリ21、セキュリティコード保存メモリ22、セキュリティコード設定部23、制御部24及びコード比較部25を備えている。

【0020】

ここで、アドレスメモリ21は、制御部24から読出/書込可能であり、物理先頭アドレスを記憶するためのメモリである。

【0021】

セキュリティコード保存メモリ22は、セキュリティコード設定部23から読出/書込可能であり、コード比較部25から読出可能であって、セキュリティコードを記憶するためのメモリである。

【0022】

セキュリティコード設定部23は、CPU1からバス4,3を介してコード設定命令及びセキュリティコードが入力されると、当該セキュリティコードをセキュリティコード保存メモリ22に書き込む機能をもっている。

【0023】

制御部24は、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスをアドレスメモリ21に書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける機能と、入力されたセキュリティコードをコード比較部25に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、当該入力された論理アドレスとアドレスメモリ21内の物理先頭アドレスとに基づいて、物理アドレスを算出する機能と、この算出した物理アドレス及び入力された読出/書込命令をフラッシュメモリ部10に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、当該入力された論理アドレス又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する機能とをもっている。

【0024】

なお、論理アドレスと物理先頭アドレスとに基づいて、物理アドレスを算出する機能としては、例えば、論理アドレスと物理先頭アドレスとを互いに加算する機能、又は論理アドレス及び物理先頭アドレスのうちの一方から他方を減算する機能といった任意の演算機能が使用可能となっている。また、論理アドレスと物理先頭アドレスとに基づいて物理アドレスを算出する機能として任意の演算機能を使用可能なことは、他の実施形態でも同様である。

【0025】

コード比較部25は、制御部24から受けた(CPU1からデータバス3を介して入力された)セキュリティコードとセキュリティコード保存メモリ22内のセキュリティコードとを比較する機能と、この比較結果を制御部24に送出する機能とをもっている。

【0026】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図3及び図4のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0027】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0028】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST1)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24に通知する。

【0029】

制御部24は、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理先頭アドレス****を決定し、当該決定した物理先頭アドレス****をアドレスメモリ21に書き込む(ST2)。

【0030】

これにより、初期化時の動作が完了する。

【0031】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST14に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。

【0032】

不揮発性メモリ装置100においては、制御部24が、この入力されたセキュリティコード****、論理アドレス○○○○及び読出/書込命令を受け付けると(ST11)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0033】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST12)、比較結果を制御部24に送出する。

【0034】

制御部24は、コード比較部25による比較の結果、両セキュリティコードが一致した場合、CPU1から入力された論理アドレス○○○○とアドレスメモリ21内の物理先頭アドレス****とに基づいて、正しい物理アドレス※※※※(=****+○○○○)を算出し(ST13)、この正しい物理アドレス※※※※及び入力された読出/書込命令をフラッシュメモリ部10に送出する(ST14)。

【0035】

フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0036】

一方、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、制御部24は、CPU1から入力された論理アドレス○○○○又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する(ST15)。

【0037】

フラッシュメモリ部10では、読出/書込命令に基づいて、論理アドレス○○○○又は偽のアドレスに対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0038】

上述したように本実施形態によれば、セキュリティコードが一致した場合にアドレスメモリ21内の物理先頭アドレスに基づき、算出した正しい物理アドレスでフラッシュメモリ部10にアクセスする構成により、不正コピーを阻止することができる。また、セキュリティコードが不一致の場合、アドレスメモリ21にアクセスせずにフラッシュメモリ部10からデータを読み出すので、本来、意図したデータとは異なるデータが読み出される。

【0039】

さらに、本実施形態によれば、入力される論理アドレスと、メモリ部内の物理アドレスとが異なるため、フラッシュメモリ部10全体の書き換え頻度を均等にでき、長寿命化を図ることができる。

【0040】

例えば、従来技術では、図5に示すように、CPUから入力される論理アドレスと、フラッシュメモリ内の物理アドレスとが同一のため、物理先頭アドレス付近のメモリ領域の書き換え頻度が高いことから、メモリ寿命が短くなる。

【0041】

これに対し、本実施形態は、セキュリティコードで決定される物理先頭アドレスの分だけ、図6に示すように、アドレス変換部20に入力される論理アドレスと、フラッシュメモリ部10内の物理アドレスとが異なるため、フラッシュメモリ部10全体に書き換え頻度が分散して均等化されることから、長寿命化を図ることができる。この場合、フラッシュメモリ部10においては、物理アドレス順にデータが配列されず、外見上、ランダムにデータが配列される。このような書き換え頻度の均等化は、例えばデータ毎に異なるセキュリティコードを設定することにより、より一層の向上を図ることができる。

【0042】

(第2の実施形態)

図7は本発明の第2の実施形態に係るLSI装置の構成を示す模式図であり、図8はこのLSI装置が有する不揮発性メモリ装置の構成を示す模式図であって、前述した図面とほぼ同一部分には同一符号を付してその詳しい説明を省略し、ここでは異なる部分について主に述べる。なお、以下の各実施形態も同様にして重複した説明を省略する。

【0043】

すなわち、第2の実施形態は、第1の実施形態の変形例であり、システムコードに応じて攪拌した物理先頭アドレスをアドレスメモリ21aに保持する形態となっている。

【0044】

これに伴い、アドレス変換部20aは、前述したアドレス変換部20に比べ、アドレスメモリ21及び制御部24に代えて、アドレスメモリ21a、制御部24a、コード対応配線パターンメモリ26及び配線部27を備えた構成となっている。

【0045】

ここで、アドレスメモリ21aは、制御部24aから配線部27を介して読出/書込可能であり、物理先頭アドレスの各部分が置換されてなる被置換物理先頭アドレスを記憶するためのメモリである。

【0046】

コード対応配線パターンメモリ26は、制御部24aから読出/書込可能であり、システムコード毎に、配線部27の配線パターン情報が記憶されたメモリである。

【0047】

ここで、配線パターン情報とは、制御部24a側のアドレス線と、アドレスメモリ21a側のアドレス線とが互いに異なる配線パターンを指定する情報である。図8に示す例では、制御部24a側のアドレス線をA0とし、アドレスメモリ21a側のアドレス線をA15とした配線パターンを指定している。但し、これに限らず、配線パターン情報は、制御部24a側のアドレス線とアドレスメモリ21a側のアドレス線とが互いに異なる配線パターンであれば、任意の配線パターンを指定可能となっている。このような配線パターン情報は、他の実施形態でも同様である。

【0048】

配線部27は、制御部24aとアドレスメモリ21aとの間のアドレス線の配線パターンと、制御部24aから入力される切替信号に基づいて当該配線パターンを切替可能な切替部とを有し、制御部24aから配線パターン上に送出された物理先頭アドレスの各部分が切替部により置換されてなる被置換物理先頭アドレスをアドレスメモリ21aに伝送するためのものである。ここで、切替部としては、例えばマルチプレクサが使用可能となっている。

【0049】

制御部24aは、CPU1から専用線5を介してシステムコードが入力されると、この入力されたシステムコードに基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスを、切替信号が入力された配線部27を介して被置換物理先頭アドレスとしてアドレスメモリ21aに書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令とCPU1から専用線5を介して入力されたシステムコードとを受け付ける機能と、入力されたセキュリティコードをコード比較部25に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、入力されたシステムコードに基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に、切替信号が入力された配線部27を介してアドレスメモリ21a内の被置換物理先頭アドレスを物理先頭アドレスとして読み出す第1の物理アドレス読出機能と、第1の物理アドレス読出機能により読み出された物理アドレスとCPU1から入力された論理アドレスとに基づいて、物理アドレスを算出する第1の物理アドレス算出機能と、コード比較部25による比較の結果、両者が不一致の場合、切替信号を入力せずに、配線部27を介してアドレスメモリ21aから被置換物理先頭アドレスを読み出す第2の物理アドレス読出機能と、第2の物理アドレス読出機能により読み出された被置換物理先頭アドレスとCPU1から入力された論理アドレスとに基づいて、物理アドレスを算出する第2の物理アドレス算出機能と、第1又は第2の物理アドレス算出機能により算出された物理アドレス及びCPU1から入力された読出/書込命令をフラッシュメモリ部10に送出する機能とをもっている。

【0050】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図9及び図10のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0051】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0052】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST21)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24aに通知する。

【0053】

制御部24aは、CPU1から専用線5を介してシステムコード####が入力されると、この入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に(ST22)、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理先頭アドレス****を決定し、当該決定した物理先頭アドレス****を、切替信号が入力された配線部27を介して被置換物理先頭アドレス□□□□としてアドレスメモリ21aに書き込む(ST23)。

【0054】

これにより、初期化時の動作が完了する。

【0055】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST37に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。また、CPU1は、専用線5を介してシステムコード####を不揮発性メモリ装置100に入力する。

【0056】

不揮発性メモリ装置100においては、制御部24aが、この入力されたセキュリティコード****、システムコード####、論理アドレス○○○○及び読出/書込命令を受け付けると(ST31)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0057】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST32)、比較結果を制御部24aに送出する。

【0058】

制御部24aは、コード比較部25による比較の結果、両セキュリティコードが一致した場合、CPU1から入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に、切替信号が入力された配線部27を介してアドレスメモリ21a内の被置換物理先頭アドレス□□□□を物理先頭アドレス****として読み出す(ST33)。

【0059】

また、制御部24aは、ステップST33で読み出された物理先頭アドレス****とCPU1から入力された論理アドレス○○○○とに基づいて、正しい物理アドレス※※※※(=****+○○○○)を算出する(ST34)。

【0060】

一方、制御部24aは、ステップST32における比較の結果、両者が不一致の場合、切替信号を入力せずに、配線部27を介してアドレスメモリ21aから被置換物理先頭アドレス□□□□を読み出す(ST35)。

【0061】

また、制御部24aは、ステップST35で読み出された被置換物理先頭アドレス□□□□とCPU1から入力された論理アドレス○○○○とに基づいて、偽の物理アドレス××××(=□□□□+○○○○)を算出する(ST36)。

【0062】

しかる後、制御部24aは、ステップST34で算出した正しい物理アドレス※※※※又はステップST36で算出した偽の物理アドレス××××と、入力された読出/書込命令とをフラッシュメモリ部10に送出する(ST37)。

【0063】

正しい物理アドレス※※※※が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0064】

一方、偽の物理アドレス××××が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、偽の物理アドレス××××に対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0065】

上述したように本実施形態によれば、第1の実施形態と同様に、不正コピーを阻止しつつ、長寿命化を図ることができる。

【0066】

また、正しいセキュリティコードの入力に加え、CPU1が正しいシステムコードを入力しないと、制御部24aが正しい物理アドレスを算出できないので、第1の実施形態に比べ、より確実に、不正コピーを阻止することができる。

【0067】

(第3の実施形態)

図11は本発明の第3の実施形態に係る不揮発性メモリ装置の構成を示す模式図であり、この不揮発性メモリ装置は図1に示したようにLSI装置に設けられている。

【0068】

第3の実施形態は、第1の実施形態の変形例であり、論理アドレスに対応した物理アドレスをアドレスメモリ21bに保持する形態となっている。

【0069】

これに伴い、アドレス変換部20bは、前述したアドレス変換部20に比べ、アドレスメモリ21及び制御部24に代えて、アドレスメモリ21b及び制御部24bを備えた構成となっている。

【0070】

ここで、アドレスメモリ21bは、制御部24bから読出/書込可能であり、論理アドレスに関連付けて物理アドレスを記憶するためのメモリである。

【0071】

制御部24bは、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを当該物理アドレスとは異なる値の論理アドレスに関連付けるようにアドレスメモリ21bに書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、当該入力された論理アドレスをアドレスメモリ21bに送出して当該アドレスメモリ21bから物理アドレスを読み出す機能と、この読み出した物理アドレス及び入力された読出/書込命令をフラッシュメモリ部10に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、当該入力された論理アドレス又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する機能とをもっている。

【0072】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図12及び図13のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0073】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0074】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST41)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24bに通知する。

【0075】

制御部24bは、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理アドレス※※※※を決定し、当該決定した物理アドレス※※※※をアドレスメモリ21bに書き込む(ST42)。

【0076】

これにより、初期化時の動作が完了する。

【0077】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST54又はST55に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。

【0078】

不揮発性メモリ装置100においては、制御部24bが、この入力されたセキュリティコード****、論理アドレス○○○○及び読出/書込命令を受け付けると(ST51)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0079】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST52)、比較結果を制御部24bに送出する。

【0080】

制御部24bは、コード比較部25による比較の結果、両セキュリティコードが一致した場合、当該入力された論理アドレス○○○○をアドレスメモリ21bに送出して当該アドレスメモリ21bから正しい物理アドレス※※※※を読み出す(ST53)。

【0081】

しかる後、制御部24bは、この正しい物理アドレス※※※※及び入力された読出/書込命令をフラッシュメモリ部10に送出する(ST54)。

【0082】

フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0083】

一方、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、制御部24bは、CPU1から入力された論理アドレス○○○○又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する(ST55)。

【0084】

フラッシュメモリ部10では、読出/書込命令に基づいて、論理アドレス○○○○又は偽のアドレスに対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0085】

上述したように本実施形態によれば、第1の実施形態と同様に、不正コピーを阻止しつつ、長寿命化を図ることができる。

【0086】

これに加え、入力される論理アドレスと、フラッシュメモリ部10内の物理アドレスとは、アドレスメモリ21b内の関連付けに応じて異ならせることができるので、この関連付けに応じて、フラッシュメモリ部10内のデータ配列のランダム性を向上できると共に、書き込み頻度を均等にすることができる。

【0087】

(第4の実施形態)

図14は本発明の第4の実施形態に係る不揮発性メモリ装置の構成を示す模式図であり、この不揮発性メモリ装置は図7に示したようにLSI装置に設けられている。

【0088】

第4の実施形態は、第2及び第3の実施形態の組合せ例であり、システムコードに応じて攪拌した論理アドレスをアドレスメモリ21cに保持し、且つ論理アドレスに対応した物理アドレスをアドレスメモリ21cに保持する形態となっている。

【0089】

これに伴い、アドレス変換部20cは、前述したアドレス変換部20aに比べ、アドレスメモリ21a及び制御部24aに代えて、アドレスメモリ21c及び制御部24cを備えており、且つこのアドレスメモリ21cに接続された配線部27cを備えている。

【0090】

ここで、アドレスメモリ21cは、制御部24cから配線部27cを介して読出/書込可能であり、論理アドレスの各部分が置換されてなる被置換論理アドレスに関連付けて物理アドレスを記憶するためのメモリである。

【0091】

配線部27cは、制御部24cとアドレスメモリ21cとの間のアドレス線の配線パターンと、制御部24cから入力される切替信号に基づいて当該配線パターンを切替可能な切替部とを有し、制御部24cから配線パターン上に送出された論理アドレスの各部分が切替部により置換されてなる被置換論理アドレスをアドレスメモリ21cに伝送するためのものである。ここで、切替部としては、例えばマルチプレクサが使用可能となっている。

【0092】

制御部24cは、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを被置換論理アドレスに関連付けるようにアドレスメモリ21cに書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令とCPU1から専用線5を介して入力されたシステムコードとを受け付ける機能と、入力されたセキュリティコードをコード比較部25に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、入力されたシステムコードに基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27cの切替部に入力すると共に、CPU1から入力された論理アドレスを、切替信号が入力された配線部27cを介して被置換論理アドレスとしてアドレスメモリ21cに送出して当該アドレスメモリ21cから物理アドレスを読み出す第1の物理アドレス読出機能と、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、切替信号を入力せずに、当該入力された論理アドレスを配線部27cからアドレスメモリ21cに送出して当該アドレスメモリ21cから物理アドレスを読み出す第2の物理アドレス読出機能と、第1又は第2の物理アドレス読出機能により読み出された物理アドレス及び入力された読出/書込命令をフラッシュメモリ部10に送出する機能とをもっている。

【0093】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図15及び図16のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0094】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0095】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST61)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24aに通知する。

【0096】

制御部24aは、CPU1から専用線5を介してシステムコード####が入力されると、この入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27cの切替部に入力すると共に(ST62)、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理アドレス※※※※を決定し、当該決定した物理アドレス※※※※を、切替信号が入力された配線部27cを介した被置換論理アドレス□□□□に関連付けてアドレスメモリ21cに書き込む(ST63)。

【0097】

これにより、初期化時の動作が完了する。

【0098】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST75に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。また、CPU1は、専用線5を介してシステムコード####を不揮発性メモリ装置100に入力する。

【0099】

不揮発性メモリ装置100においては、制御部24cが、この入力されたセキュリティコード****、システムコード####、論理アドレス○○○○及び読出/書込命令を受け付けると(ST71)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0100】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST72)、比較結果を制御部24cに送出する。

【0101】

制御部24cは、コード比較部25による比較の結果、両セキュリティコードが一致した場合、CPU1から入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27cの切替部に入力すると共に、CPU1から入力された論理アドレス○○○○を、切替信号が入力された配線部27cを介して被置換論理アドレス□□□□としてアドレスメモリ21cに送出して当該アドレスメモリ21cから正しい物理アドレス※※※※を読み出す(ST73)。

【0102】

一方、制御部24aは、ステップST72における比較の結果、両者が不一致の場合、切替信号を入力せずに、当該入力された論理アドレス○○○○を配線部27cからアドレスメモリ21cに送出して当該アドレスメモリ21cから偽の物理アドレス××××を読み出す(ST74)。

【0103】

しかる後、制御部24aは、ステップST73で読み出した正しい物理アドレス※※※※又はステップST74で読み出した偽の物理アドレス××××と、入力された読出/書込命令とをフラッシュメモリ部10に送出する(ST75)。

【0104】

正しい物理アドレス※※※※が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0105】

一方、偽の物理アドレス××××が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、偽の物理アドレス××××に対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0106】

上述したように本実施形態によれば、第2及び第3の実施形態と同様に、不正コピーをより確実に阻止しつつ、長寿命化を図ることができる。

【0107】

例えば、正しいセキュリティコードの入力に加え、CPU1が正しいシステムコードを入力しないと、制御部24cがメモリアドレス21cから正しい物理アドレスを読み出せないので、第3の実施形態に比べ、より確実に、不正コピーを阻止することができる。

【0108】

なお、上記実施形態に記載した手法は、コンピュータに実行させることのできるプログラムとして、磁気ディスク(フロッピー(登録商標)ディスク、ハードディスクなど)、光ディスク(CD−ROM、DVDなど)、光磁気ディスク(MO)、半導体メモリなどの記憶媒体に格納して頒布することもできる。

【0109】

また、本願発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組合せてもよい。

【図面の簡単な説明】

【0110】

【図1】本発明の第1の実施形態に係るLSI装置の構成を示す模式図である。

【図2】同実施形態における不揮発性メモリ装置の構成を示す模式図である。

【図3】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図4】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【図5】従来技術における論理空間と物理空間との関係を説明するための模式図である。

【図6】同実施形態における論理空間と物理空間との関係を説明するための模式図である。

【図7】本発明の第2の実施形態に係るLSI装置の構成を示す模式図である。

【図8】同実施形態における不揮発性メモリ装置の構成を示す模式図である。

【図9】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図10】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【図11】本発明の第3の実施形態に係る不揮発性メモリ装置の構成を示す模式図である。

【図12】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図13】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【図14】本発明の第4の実施形態に係る不揮発性メモリ装置の構成を示す模式図である。

【図15】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図16】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【符号の説明】

【0111】

1…CPU、2…アドレスバス、3…データバス、4…コントロールバス、5…専用線、10…フラッシュメモリ部、20,20a,20b,20c…アドレス変換部、21,21a,21b,21c…アドレスメモリ、22…セキュリティコード保存メモリ、23…セキュリティコード設定部、24,24a,24b,24c…制御部、25…コード比較部、26…コード対応配線パターンメモリ、27,27c…配線部、100…不揮発性メモリ装置。

【技術分野】

【0001】

本発明は、半導体メモリ全般に適用可能な不揮発性メモリ及びLSI(large-scale integrated circuit)装置に係り、例えば、不正コピーを阻止しつつ、長寿命化を図り得る不揮発性メモリ装置及びLSI装置に関する。

【背景技術】

【0002】

フラッシュメモリを始めとする不揮発性メモリは、書換え可能機能を特徴とする反面、書き換え回数に制限があることや、セキュリティ上、ぜい弱な部分があるといった不都合な点がある。ここで、セキュリティ上のぜい弱な部分としては、例えば、メモリ内のデータを容易に不正コピーし得ることが挙げられる。

【0003】

この種の不正コピーは、従来のシステムではメモリ周辺機能にセキュリティ機能をもたせる方式が多く、メモリ自体にセキュリティ機能をもたせる方式が無かったため、メモリ自体からデータをコピーすることが容易であることに起因すると考えられる。

【0004】

これに対し、メモリ内のデータの不正コピーを阻止する観点から、例えば特許文献1,2に記載の技術が提案されている。特許文献1に記載の技術は、暗号化データをメモリ領域に保持しておき、不正な読出処理の際には、復号を行わずに、メモリ領域内の暗号化データを出力するものである。特許文献2に記載の技術は、データをコピーする際に禁止アドレスをアクセスすると所定サイクル後に誤データが出力されるものである。

【特許文献1】特開2002−268947号公報

【特許文献2】特願平7−243335号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1,2に記載の技術は、本発明者の検討によれば、不正コピーを阻止する技術ではあるが、書き換え回数の制限については未だ改善の余地があると考えられる。なお、一般的なメモリ構造では、書換え空間がシステム上、同じ空間を利用するため、書き換え頻度の高い空間のみメモリ寿命が短くなる。

【0006】

従って、不揮発性メモリにおいては、前述したような不正コピーを阻止しつつ、さらに、長寿命化を図る必要があると考えられる。

【0007】

本発明は上記実情を考慮してなされたもので、不正コピーを阻止しつつ、長寿命化を図り得る不揮発性メモリ装置及びLSI装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の第1の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、物理先頭アドレスを記憶するためのアドレス記憶手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、前記セキュリティコード記憶手段内のセキュリティコードに基づいて前記物理先頭アドレスを決定し、当該決定した物理先頭アドレスを前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力された論理アドレスと前記アドレス記憶手段内の物理先頭アドレスとに基づいて、物理アドレスを算出する手段と、この算出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置である。

【0009】

本発明の第2の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、物理先頭アドレスの各部分が置換されてなる被置換物理先頭アドレスを記憶するためのアドレス記憶手段と、システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された物理先頭アドレスの各部分が前記切替部により置換されてなる被置換物理先頭アドレスを前記アドレス記憶手段に伝送するための配線手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、システムコードが入力されると、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスを、前記切替信号が入力された配線手段を介して前記被置換物理先頭アドレスとして前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記切替信号が入力された配線手段を介して前記アドレス記憶手段内の被置換物理先頭アドレスを物理先頭アドレスとして読み出す第1の物理アドレス読出手段と、前記第1の物理アドレス読出手段により読み出された物理アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第1の物理アドレス算出手段と、前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記配線手段を介して前記アドレス記憶手段から被置換物理先頭アドレスを読み出す第2の物理アドレス読出手段と、前記第2の物理アドレス読出手段により読み出された被置換物理先頭アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第2の物理アドレス算出手段と、前記第1又は第2の物理アドレス算出手段により算出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置である。

【0010】

本発明の第3の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、論理アドレスに関連付けて物理アドレスを記憶するためのアドレス記憶手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを当該物理アドレスとは異なる値の論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力された論理アドレスを前記アドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す手段と、この読み出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置。

【0011】

本発明の第4の局面は、物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、論理アドレスの各部分が置換されてなる被置換論理アドレスに物理アドレスを関連付けて記憶するためのアドレス記憶手段と、システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された論理アドレスの各部分が前記切替部により置換されてなる被置換論理アドレスを前記アドレス記憶手段に伝送するための配線手段と、セキュリティコードを記憶するためのセキュリティコード記憶手段と、コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを被置換論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記入力された論理アドレスを、前記切替信号が入力された配線手段を介して被置換論理アドレスとしてアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第1の物理アドレス読出手段と、前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記入力された論理アドレスを前記配線手段からアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第2の物理アドレス読出手段と、前記第1又は第2の物理アドレス読出手段により読み出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、を備えた不揮発性メモリ装置である。

【0012】

なお、第1〜第4の各局面の不揮発性メモリ装置はLSI装置に設けてもよい。ここでいう「LSI装置」の用語は、半導体集積回路の総称として用いており、集積度によるLSIの通常の定義(1000個以上で10万個未満の素子を搭載した半導体集積回路)には限定されず、例えば、IC、SSI、MSI、LSI(通常の定義)、VLSI、ULSI又はMPUなどの上位概念として使用されている。

【0013】

(作用)

第1〜第4の局面によれば、セキュリティコードが一致した場合にアドレス記憶手段から物理先頭アドレス又は物理アドレスを読み出した後に、得られた正しい物理アドレスでメモリ部にアクセスする構成により、不正コピーを阻止することができる。

【0014】

また、第1〜第4の局面によれば、入力される論理アドレスと、メモリ部内の物理アドレスとが異なるため、メモリ部全体の書き換え頻度を均等にでき、長寿命化を図ることができる。

【発明の効果】

【0015】

以上説明したように本発明によれば、不正コピーを阻止しつつ、長寿命化を図ることができる。

【発明を実施するための最良の形態】

【0016】

以下、本発明の各実施形態について図面を用いて説明する。

(第1の実施形態)

図1は本発明の第1の実施形態に係るLSI装置の構成を示す模式図であり、図2はこのLSI装置が有する不揮発性メモリ装置の構成を示す模式図である。このLSI装置は、CPU1がアドレスバス2、データバス3及びコントロールバス4を個別に介して不揮発性メモリ装置100に接続されており、各バス2〜4を介して不揮発性メモリ装置100にデータを読出/書込する機能と、通常のプログラム処理機能とをもっている。

【0017】

不揮発性メモリ装置100は、フラッシュメモリ部10及びアドレス変換部20を備えている。

【0018】

ここで、フラッシュメモリ部10は、物理アドレスに対応してデータを保持する読出/書込可能な不揮発性のメモリ部であり、アドレス変換部20からアクセス可能となっている。なお、保持データは任意であるが、例えば、通常のファイル等の他、LSI装置の機能を実現させるための基本データ(例、制御値、制御プログラム等)がある。この種の基本データは、LSI装置の動作性能を左右するものであり、システム開発者の独自の技術的知識(ノウハウ)により記述されるから、模倣・盗用を防ぐ観点からもCPU1のみが利用可能とし、外部から不正コピーされないことが望ましい。また、フラッシュメモリ部10としては、不揮発性メモリの一例としてフラッシュメモリを用いているが、これに限らず、例えば読出専用のROM等のように、フラッシュメモリ以外の不揮発性メモリを用いてもよい。

【0019】

アドレス変換部20は、アドレスメモリ21、セキュリティコード保存メモリ22、セキュリティコード設定部23、制御部24及びコード比較部25を備えている。

【0020】

ここで、アドレスメモリ21は、制御部24から読出/書込可能であり、物理先頭アドレスを記憶するためのメモリである。

【0021】

セキュリティコード保存メモリ22は、セキュリティコード設定部23から読出/書込可能であり、コード比較部25から読出可能であって、セキュリティコードを記憶するためのメモリである。

【0022】

セキュリティコード設定部23は、CPU1からバス4,3を介してコード設定命令及びセキュリティコードが入力されると、当該セキュリティコードをセキュリティコード保存メモリ22に書き込む機能をもっている。

【0023】

制御部24は、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスをアドレスメモリ21に書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける機能と、入力されたセキュリティコードをコード比較部25に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、当該入力された論理アドレスとアドレスメモリ21内の物理先頭アドレスとに基づいて、物理アドレスを算出する機能と、この算出した物理アドレス及び入力された読出/書込命令をフラッシュメモリ部10に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、当該入力された論理アドレス又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する機能とをもっている。

【0024】

なお、論理アドレスと物理先頭アドレスとに基づいて、物理アドレスを算出する機能としては、例えば、論理アドレスと物理先頭アドレスとを互いに加算する機能、又は論理アドレス及び物理先頭アドレスのうちの一方から他方を減算する機能といった任意の演算機能が使用可能となっている。また、論理アドレスと物理先頭アドレスとに基づいて物理アドレスを算出する機能として任意の演算機能を使用可能なことは、他の実施形態でも同様である。

【0025】

コード比較部25は、制御部24から受けた(CPU1からデータバス3を介して入力された)セキュリティコードとセキュリティコード保存メモリ22内のセキュリティコードとを比較する機能と、この比較結果を制御部24に送出する機能とをもっている。

【0026】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図3及び図4のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0027】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0028】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST1)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24に通知する。

【0029】

制御部24は、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理先頭アドレス****を決定し、当該決定した物理先頭アドレス****をアドレスメモリ21に書き込む(ST2)。

【0030】

これにより、初期化時の動作が完了する。

【0031】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST14に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。

【0032】

不揮発性メモリ装置100においては、制御部24が、この入力されたセキュリティコード****、論理アドレス○○○○及び読出/書込命令を受け付けると(ST11)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0033】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST12)、比較結果を制御部24に送出する。

【0034】

制御部24は、コード比較部25による比較の結果、両セキュリティコードが一致した場合、CPU1から入力された論理アドレス○○○○とアドレスメモリ21内の物理先頭アドレス****とに基づいて、正しい物理アドレス※※※※(=****+○○○○)を算出し(ST13)、この正しい物理アドレス※※※※及び入力された読出/書込命令をフラッシュメモリ部10に送出する(ST14)。

【0035】

フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0036】

一方、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、制御部24は、CPU1から入力された論理アドレス○○○○又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する(ST15)。

【0037】

フラッシュメモリ部10では、読出/書込命令に基づいて、論理アドレス○○○○又は偽のアドレスに対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0038】

上述したように本実施形態によれば、セキュリティコードが一致した場合にアドレスメモリ21内の物理先頭アドレスに基づき、算出した正しい物理アドレスでフラッシュメモリ部10にアクセスする構成により、不正コピーを阻止することができる。また、セキュリティコードが不一致の場合、アドレスメモリ21にアクセスせずにフラッシュメモリ部10からデータを読み出すので、本来、意図したデータとは異なるデータが読み出される。

【0039】

さらに、本実施形態によれば、入力される論理アドレスと、メモリ部内の物理アドレスとが異なるため、フラッシュメモリ部10全体の書き換え頻度を均等にでき、長寿命化を図ることができる。

【0040】

例えば、従来技術では、図5に示すように、CPUから入力される論理アドレスと、フラッシュメモリ内の物理アドレスとが同一のため、物理先頭アドレス付近のメモリ領域の書き換え頻度が高いことから、メモリ寿命が短くなる。

【0041】

これに対し、本実施形態は、セキュリティコードで決定される物理先頭アドレスの分だけ、図6に示すように、アドレス変換部20に入力される論理アドレスと、フラッシュメモリ部10内の物理アドレスとが異なるため、フラッシュメモリ部10全体に書き換え頻度が分散して均等化されることから、長寿命化を図ることができる。この場合、フラッシュメモリ部10においては、物理アドレス順にデータが配列されず、外見上、ランダムにデータが配列される。このような書き換え頻度の均等化は、例えばデータ毎に異なるセキュリティコードを設定することにより、より一層の向上を図ることができる。

【0042】

(第2の実施形態)

図7は本発明の第2の実施形態に係るLSI装置の構成を示す模式図であり、図8はこのLSI装置が有する不揮発性メモリ装置の構成を示す模式図であって、前述した図面とほぼ同一部分には同一符号を付してその詳しい説明を省略し、ここでは異なる部分について主に述べる。なお、以下の各実施形態も同様にして重複した説明を省略する。

【0043】

すなわち、第2の実施形態は、第1の実施形態の変形例であり、システムコードに応じて攪拌した物理先頭アドレスをアドレスメモリ21aに保持する形態となっている。

【0044】

これに伴い、アドレス変換部20aは、前述したアドレス変換部20に比べ、アドレスメモリ21及び制御部24に代えて、アドレスメモリ21a、制御部24a、コード対応配線パターンメモリ26及び配線部27を備えた構成となっている。

【0045】

ここで、アドレスメモリ21aは、制御部24aから配線部27を介して読出/書込可能であり、物理先頭アドレスの各部分が置換されてなる被置換物理先頭アドレスを記憶するためのメモリである。

【0046】

コード対応配線パターンメモリ26は、制御部24aから読出/書込可能であり、システムコード毎に、配線部27の配線パターン情報が記憶されたメモリである。

【0047】

ここで、配線パターン情報とは、制御部24a側のアドレス線と、アドレスメモリ21a側のアドレス線とが互いに異なる配線パターンを指定する情報である。図8に示す例では、制御部24a側のアドレス線をA0とし、アドレスメモリ21a側のアドレス線をA15とした配線パターンを指定している。但し、これに限らず、配線パターン情報は、制御部24a側のアドレス線とアドレスメモリ21a側のアドレス線とが互いに異なる配線パターンであれば、任意の配線パターンを指定可能となっている。このような配線パターン情報は、他の実施形態でも同様である。

【0048】

配線部27は、制御部24aとアドレスメモリ21aとの間のアドレス線の配線パターンと、制御部24aから入力される切替信号に基づいて当該配線パターンを切替可能な切替部とを有し、制御部24aから配線パターン上に送出された物理先頭アドレスの各部分が切替部により置換されてなる被置換物理先頭アドレスをアドレスメモリ21aに伝送するためのものである。ここで、切替部としては、例えばマルチプレクサが使用可能となっている。

【0049】

制御部24aは、CPU1から専用線5を介してシステムコードが入力されると、この入力されたシステムコードに基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスを、切替信号が入力された配線部27を介して被置換物理先頭アドレスとしてアドレスメモリ21aに書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令とCPU1から専用線5を介して入力されたシステムコードとを受け付ける機能と、入力されたセキュリティコードをコード比較部25に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、入力されたシステムコードに基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に、切替信号が入力された配線部27を介してアドレスメモリ21a内の被置換物理先頭アドレスを物理先頭アドレスとして読み出す第1の物理アドレス読出機能と、第1の物理アドレス読出機能により読み出された物理アドレスとCPU1から入力された論理アドレスとに基づいて、物理アドレスを算出する第1の物理アドレス算出機能と、コード比較部25による比較の結果、両者が不一致の場合、切替信号を入力せずに、配線部27を介してアドレスメモリ21aから被置換物理先頭アドレスを読み出す第2の物理アドレス読出機能と、第2の物理アドレス読出機能により読み出された被置換物理先頭アドレスとCPU1から入力された論理アドレスとに基づいて、物理アドレスを算出する第2の物理アドレス算出機能と、第1又は第2の物理アドレス算出機能により算出された物理アドレス及びCPU1から入力された読出/書込命令をフラッシュメモリ部10に送出する機能とをもっている。

【0050】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図9及び図10のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0051】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0052】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST21)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24aに通知する。

【0053】

制御部24aは、CPU1から専用線5を介してシステムコード####が入力されると、この入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に(ST22)、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理先頭アドレス****を決定し、当該決定した物理先頭アドレス****を、切替信号が入力された配線部27を介して被置換物理先頭アドレス□□□□としてアドレスメモリ21aに書き込む(ST23)。

【0054】

これにより、初期化時の動作が完了する。

【0055】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST37に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。また、CPU1は、専用線5を介してシステムコード####を不揮発性メモリ装置100に入力する。

【0056】

不揮発性メモリ装置100においては、制御部24aが、この入力されたセキュリティコード****、システムコード####、論理アドレス○○○○及び読出/書込命令を受け付けると(ST31)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0057】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST32)、比較結果を制御部24aに送出する。

【0058】

制御部24aは、コード比較部25による比較の結果、両セキュリティコードが一致した場合、CPU1から入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27の切替部に入力すると共に、切替信号が入力された配線部27を介してアドレスメモリ21a内の被置換物理先頭アドレス□□□□を物理先頭アドレス****として読み出す(ST33)。

【0059】

また、制御部24aは、ステップST33で読み出された物理先頭アドレス****とCPU1から入力された論理アドレス○○○○とに基づいて、正しい物理アドレス※※※※(=****+○○○○)を算出する(ST34)。

【0060】

一方、制御部24aは、ステップST32における比較の結果、両者が不一致の場合、切替信号を入力せずに、配線部27を介してアドレスメモリ21aから被置換物理先頭アドレス□□□□を読み出す(ST35)。

【0061】

また、制御部24aは、ステップST35で読み出された被置換物理先頭アドレス□□□□とCPU1から入力された論理アドレス○○○○とに基づいて、偽の物理アドレス××××(=□□□□+○○○○)を算出する(ST36)。

【0062】

しかる後、制御部24aは、ステップST34で算出した正しい物理アドレス※※※※又はステップST36で算出した偽の物理アドレス××××と、入力された読出/書込命令とをフラッシュメモリ部10に送出する(ST37)。

【0063】

正しい物理アドレス※※※※が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0064】

一方、偽の物理アドレス××××が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、偽の物理アドレス××××に対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0065】

上述したように本実施形態によれば、第1の実施形態と同様に、不正コピーを阻止しつつ、長寿命化を図ることができる。

【0066】

また、正しいセキュリティコードの入力に加え、CPU1が正しいシステムコードを入力しないと、制御部24aが正しい物理アドレスを算出できないので、第1の実施形態に比べ、より確実に、不正コピーを阻止することができる。

【0067】

(第3の実施形態)

図11は本発明の第3の実施形態に係る不揮発性メモリ装置の構成を示す模式図であり、この不揮発性メモリ装置は図1に示したようにLSI装置に設けられている。

【0068】

第3の実施形態は、第1の実施形態の変形例であり、論理アドレスに対応した物理アドレスをアドレスメモリ21bに保持する形態となっている。

【0069】

これに伴い、アドレス変換部20bは、前述したアドレス変換部20に比べ、アドレスメモリ21及び制御部24に代えて、アドレスメモリ21b及び制御部24bを備えた構成となっている。

【0070】

ここで、アドレスメモリ21bは、制御部24bから読出/書込可能であり、論理アドレスに関連付けて物理アドレスを記憶するためのメモリである。

【0071】

制御部24bは、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを当該物理アドレスとは異なる値の論理アドレスに関連付けるようにアドレスメモリ21bに書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、当該入力された論理アドレスをアドレスメモリ21bに送出して当該アドレスメモリ21bから物理アドレスを読み出す機能と、この読み出した物理アドレス及び入力された読出/書込命令をフラッシュメモリ部10に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、当該入力された論理アドレス又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する機能とをもっている。

【0072】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図12及び図13のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0073】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0074】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST41)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24bに通知する。

【0075】

制御部24bは、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理アドレス※※※※を決定し、当該決定した物理アドレス※※※※をアドレスメモリ21bに書き込む(ST42)。

【0076】

これにより、初期化時の動作が完了する。

【0077】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST54又はST55に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。

【0078】

不揮発性メモリ装置100においては、制御部24bが、この入力されたセキュリティコード****、論理アドレス○○○○及び読出/書込命令を受け付けると(ST51)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0079】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST52)、比較結果を制御部24bに送出する。

【0080】

制御部24bは、コード比較部25による比較の結果、両セキュリティコードが一致した場合、当該入力された論理アドレス○○○○をアドレスメモリ21bに送出して当該アドレスメモリ21bから正しい物理アドレス※※※※を読み出す(ST53)。

【0081】

しかる後、制御部24bは、この正しい物理アドレス※※※※及び入力された読出/書込命令をフラッシュメモリ部10に送出する(ST54)。

【0082】

フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0083】

一方、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、制御部24bは、CPU1から入力された論理アドレス○○○○又は偽のアドレスと、読出/書込命令とをフラッシュメモリ部10に送出する(ST55)。

【0084】

フラッシュメモリ部10では、読出/書込命令に基づいて、論理アドレス○○○○又は偽のアドレスに対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0085】

上述したように本実施形態によれば、第1の実施形態と同様に、不正コピーを阻止しつつ、長寿命化を図ることができる。

【0086】

これに加え、入力される論理アドレスと、フラッシュメモリ部10内の物理アドレスとは、アドレスメモリ21b内の関連付けに応じて異ならせることができるので、この関連付けに応じて、フラッシュメモリ部10内のデータ配列のランダム性を向上できると共に、書き込み頻度を均等にすることができる。

【0087】

(第4の実施形態)

図14は本発明の第4の実施形態に係る不揮発性メモリ装置の構成を示す模式図であり、この不揮発性メモリ装置は図7に示したようにLSI装置に設けられている。

【0088】

第4の実施形態は、第2及び第3の実施形態の組合せ例であり、システムコードに応じて攪拌した論理アドレスをアドレスメモリ21cに保持し、且つ論理アドレスに対応した物理アドレスをアドレスメモリ21cに保持する形態となっている。

【0089】

これに伴い、アドレス変換部20cは、前述したアドレス変換部20aに比べ、アドレスメモリ21a及び制御部24aに代えて、アドレスメモリ21c及び制御部24cを備えており、且つこのアドレスメモリ21cに接続された配線部27cを備えている。

【0090】

ここで、アドレスメモリ21cは、制御部24cから配線部27cを介して読出/書込可能であり、論理アドレスの各部分が置換されてなる被置換論理アドレスに関連付けて物理アドレスを記憶するためのメモリである。

【0091】

配線部27cは、制御部24cとアドレスメモリ21cとの間のアドレス線の配線パターンと、制御部24cから入力される切替信号に基づいて当該配線パターンを切替可能な切替部とを有し、制御部24cから配線パターン上に送出された論理アドレスの各部分が切替部により置換されてなる被置換論理アドレスをアドレスメモリ21cに伝送するためのものである。ここで、切替部としては、例えばマルチプレクサが使用可能となっている。

【0092】

制御部24cは、セキュリティコード保存メモリ22内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを被置換論理アドレスに関連付けるようにアドレスメモリ21cに書き込む機能と、CPU1からバス3,2,4を介して入力されたセキュリティコード、論理アドレス及び読出/書込命令とCPU1から専用線5を介して入力されたシステムコードとを受け付ける機能と、入力されたセキュリティコードをコード比較部25に送出する機能と、コード比較部25による比較の結果、両セキュリティコードが一致した場合、入力されたシステムコードに基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27cの切替部に入力すると共に、CPU1から入力された論理アドレスを、切替信号が入力された配線部27cを介して被置換論理アドレスとしてアドレスメモリ21cに送出して当該アドレスメモリ21cから物理アドレスを読み出す第1の物理アドレス読出機能と、コード比較部25による比較の結果、両セキュリティコードが不一致の場合、切替信号を入力せずに、当該入力された論理アドレスを配線部27cからアドレスメモリ21cに送出して当該アドレスメモリ21cから物理アドレスを読み出す第2の物理アドレス読出機能と、第1又は第2の物理アドレス読出機能により読み出された物理アドレス及び入力された読出/書込命令をフラッシュメモリ部10に送出する機能とをもっている。

【0093】

次に、以上のように構成された不揮発性メモリ装置を備えたLSI装置の動作を図15及び図16のフローチャートを用いて初期化時及び読出/書込時の順に説明する。

【0094】

(初期化時)

CPU1は、バス4,3を介してコード設定命令及びセキュリティコードを不揮発性メモリ装置100に入力する。

【0095】

不揮発性メモリ装置100においては、セキュリティコード設定部23が、この入力されたコード設定命令及びセキュリティコード****に基づいて、当該セキュリティコード****をセキュリティコード保存メモリ22に書き込むことにより、セキュリティコードを設定する(ST61)。また、セキュリティコード設定部23は、セキュリティコードの書込完了を制御部24aに通知する。

【0096】

制御部24aは、CPU1から専用線5を介してシステムコード####が入力されると、この入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27cの切替部に入力すると共に(ST62)、セキュリティコード保存メモリ22内のセキュリティコード****に基づいて物理アドレス※※※※を決定し、当該決定した物理アドレス※※※※を、切替信号が入力された配線部27cを介した被置換論理アドレス□□□□に関連付けてアドレスメモリ21cに書き込む(ST63)。

【0097】

これにより、初期化時の動作が完了する。

【0098】

(読出/書込時)

CPU1は、バス3,2,4を介してセキュリティコード****、論理アドレス○○○○及び読出/書込命令を不揮発性メモリ装置100に入力する。なお、読出命令又は書込命令のうち、書込命令の場合には、この後、後述するステップST75に合わせたタイミングでCPU1は書込みデータをデータバス3に送出する。また、CPU1は、専用線5を介してシステムコード####を不揮発性メモリ装置100に入力する。

【0099】

不揮発性メモリ装置100においては、制御部24cが、この入力されたセキュリティコード****、システムコード####、論理アドレス○○○○及び読出/書込命令を受け付けると(ST71)、当該入力されたセキュリティコード****をコード比較部25に送出する。

【0100】

コード比較部25は、このセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とを比較し(ST72)、比較結果を制御部24cに送出する。

【0101】

制御部24cは、コード比較部25による比較の結果、両セキュリティコードが一致した場合、CPU1から入力されたシステムコード####に基づいて、コード対応配線パターンメモリ26から読み出した配線パターン情報に対応する切替信号を配線部27cの切替部に入力すると共に、CPU1から入力された論理アドレス○○○○を、切替信号が入力された配線部27cを介して被置換論理アドレス□□□□としてアドレスメモリ21cに送出して当該アドレスメモリ21cから正しい物理アドレス※※※※を読み出す(ST73)。

【0102】

一方、制御部24aは、ステップST72における比較の結果、両者が不一致の場合、切替信号を入力せずに、当該入力された論理アドレス○○○○を配線部27cからアドレスメモリ21cに送出して当該アドレスメモリ21cから偽の物理アドレス××××を読み出す(ST74)。

【0103】

しかる後、制御部24aは、ステップST73で読み出した正しい物理アドレス※※※※又はステップST74で読み出した偽の物理アドレス××××と、入力された読出/書込命令とをフラッシュメモリ部10に送出する(ST75)。

【0104】

正しい物理アドレス※※※※が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△が読出/書込される。

【0105】

一方、偽の物理アドレス××××が送出された場合、フラッシュメモリ部10では、読出/書込命令に基づいて、偽の物理アドレス××××に対応するデータ(正しい物理アドレス※※※※に対応しないデータ)が読出/書込される。

【0106】

上述したように本実施形態によれば、第2及び第3の実施形態と同様に、不正コピーをより確実に阻止しつつ、長寿命化を図ることができる。

【0107】

例えば、正しいセキュリティコードの入力に加え、CPU1が正しいシステムコードを入力しないと、制御部24cがメモリアドレス21cから正しい物理アドレスを読み出せないので、第3の実施形態に比べ、より確実に、不正コピーを阻止することができる。

【0108】

なお、上記実施形態に記載した手法は、コンピュータに実行させることのできるプログラムとして、磁気ディスク(フロッピー(登録商標)ディスク、ハードディスクなど)、光ディスク(CD−ROM、DVDなど)、光磁気ディスク(MO)、半導体メモリなどの記憶媒体に格納して頒布することもできる。

【0109】

また、本願発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組合せてもよい。

【図面の簡単な説明】

【0110】

【図1】本発明の第1の実施形態に係るLSI装置の構成を示す模式図である。

【図2】同実施形態における不揮発性メモリ装置の構成を示す模式図である。

【図3】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図4】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【図5】従来技術における論理空間と物理空間との関係を説明するための模式図である。

【図6】同実施形態における論理空間と物理空間との関係を説明するための模式図である。

【図7】本発明の第2の実施形態に係るLSI装置の構成を示す模式図である。

【図8】同実施形態における不揮発性メモリ装置の構成を示す模式図である。

【図9】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図10】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【図11】本発明の第3の実施形態に係る不揮発性メモリ装置の構成を示す模式図である。

【図12】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図13】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【図14】本発明の第4の実施形態に係る不揮発性メモリ装置の構成を示す模式図である。

【図15】同実施形態における初期化時の動作を説明するためのフローチャートである。

【図16】同実施形態における読出/書込時の動作を説明するためのフローチャートである。

【符号の説明】

【0111】

1…CPU、2…アドレスバス、3…データバス、4…コントロールバス、5…専用線、10…フラッシュメモリ部、20,20a,20b,20c…アドレス変換部、21,21a,21b,21c…アドレスメモリ、22…セキュリティコード保存メモリ、23…セキュリティコード設定部、24,24a,24b,24c…制御部、25…コード比較部、26…コード対応配線パターンメモリ、27,27c…配線部、100…不揮発性メモリ装置。

【特許請求の範囲】

【請求項1】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

物理先頭アドレスを記憶するためのアドレス記憶手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

前記セキュリティコード記憶手段内のセキュリティコードに基づいて前記物理先頭アドレスを決定し、当該決定した物理先頭アドレスを前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力された論理アドレスと前記アドレス記憶手段内の物理先頭アドレスとに基づいて、物理アドレスを算出する手段と、

この算出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項2】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

物理先頭アドレスの各部分が置換されてなる被置換物理先頭アドレスを記憶するためのアドレス記憶手段と、

システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、

入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された物理先頭アドレスの各部分が前記切替部により置換されてなる被置換物理先頭アドレスを前記アドレス記憶手段に伝送するための配線手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

システムコードが入力されると、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスを、前記切替信号が入力された配線手段を介して前記被置換物理先頭アドレスとして前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記切替信号が入力された配線手段を介して前記アドレス記憶手段内の被置換物理先頭アドレスを物理先頭アドレスとして読み出す第1の物理アドレス読出手段と、

前記第1の物理アドレス読出手段により読み出された物理アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第1の物理アドレス算出手段と、

前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記配線手段を介して前記アドレス記憶手段から被置換物理先頭アドレスを読み出す第2の物理アドレス読出手段と、

前記第2の物理アドレス読出手段により読み出された被置換物理先頭アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第2の物理アドレス算出手段と、

前記第1又は第2の物理アドレス算出手段により算出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項3】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

論理アドレスに関連付けて物理アドレスを記憶するためのアドレス記憶手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを当該物理アドレスとは異なる値の論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力された論理アドレスを前記アドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す手段と、

この読み出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項4】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

論理アドレスの各部分が置換されてなる被置換論理アドレスに物理アドレスを関連付けて記憶するためのアドレス記憶手段と、

システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、

入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された論理アドレスの各部分が前記切替部により置換されてなる被置換論理アドレスを前記アドレス記憶手段に伝送するための配線手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを被置換論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記入力された論理アドレスを、前記切替信号が入力された配線手段を介して被置換論理アドレスとしてアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第1の物理アドレス読出手段と、

前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記入力された論理アドレスを前記配線手段からアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第2の物理アドレス読出手段と、

前記第1又は第2の物理アドレス読出手段により読み出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項5】

請求項1乃至請求項4のいずれか1項に記載の不揮発性メモリ装置を備えたことを特徴とするLSI装置。

【請求項1】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

物理先頭アドレスを記憶するためのアドレス記憶手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

前記セキュリティコード記憶手段内のセキュリティコードに基づいて前記物理先頭アドレスを決定し、当該決定した物理先頭アドレスを前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力された論理アドレスと前記アドレス記憶手段内の物理先頭アドレスとに基づいて、物理アドレスを算出する手段と、

この算出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項2】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

物理先頭アドレスの各部分が置換されてなる被置換物理先頭アドレスを記憶するためのアドレス記憶手段と、

システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、

入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された物理先頭アドレスの各部分が前記切替部により置換されてなる被置換物理先頭アドレスを前記アドレス記憶手段に伝送するための配線手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

システムコードが入力されると、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理先頭アドレスを決定し、当該決定した物理先頭アドレスを、前記切替信号が入力された配線手段を介して前記被置換物理先頭アドレスとして前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記切替信号が入力された配線手段を介して前記アドレス記憶手段内の被置換物理先頭アドレスを物理先頭アドレスとして読み出す第1の物理アドレス読出手段と、

前記第1の物理アドレス読出手段により読み出された物理アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第1の物理アドレス算出手段と、

前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記配線手段を介して前記アドレス記憶手段から被置換物理先頭アドレスを読み出す第2の物理アドレス読出手段と、

前記第2の物理アドレス読出手段により読み出された被置換物理先頭アドレスと前記入力された論理アドレスとに基づいて、物理アドレスを算出する第2の物理アドレス算出手段と、

前記第1又は第2の物理アドレス算出手段により算出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項3】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

論理アドレスに関連付けて物理アドレスを記憶するためのアドレス記憶手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを当該物理アドレスとは異なる値の論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力された論理アドレスを前記アドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す手段と、

この読み出した物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

前記比較の結果、両者が不一致の場合、前記入力された論理アドレス又は偽のアドレスと、前記読出/書込命令とを前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項4】

物理アドレスに対応してデータを保持する読出/書込可能なメモリ部を備えた不揮発性メモリ装置であって、

論理アドレスの各部分が置換されてなる被置換論理アドレスに物理アドレスを関連付けて記憶するためのアドレス記憶手段と、

システムコード毎に、配線パターン情報が記憶された配線パターン記憶手段と、

入力される切替信号に基づいて配線パターンを切替可能な切替部を有し、当該配線パターン上に送出された論理アドレスの各部分が前記切替部により置換されてなる被置換論理アドレスを前記アドレス記憶手段に伝送するための配線手段と、

セキュリティコードを記憶するためのセキュリティコード記憶手段と、

コード設定命令及びセキュリティコードが入力されると、当該セキュリティコードを前記セキュリティコード記憶手段に書き込む手段と、

前記セキュリティコード記憶手段内のセキュリティコードに基づいて物理アドレスを決定し、当該決定した物理アドレスを被置換論理アドレスに関連付けるように前記アドレス記憶手段に書き込む手段と、

入力されたセキュリティコード、システムコード、論理アドレス及び読出/書込命令を受け付ける手段と、

前記入力されたセキュリティコードと前記セキュリティコード記憶手段内のセキュリティコードとを比較する手段と、

この比較の結果、両者が一致した場合、前記入力されたシステムコードに基づいて、前記配線パターン記憶手段から読み出した配線パターン情報に対応する切替信号を前記切替部に入力すると共に、前記入力された論理アドレスを、前記切替信号が入力された配線手段を介して被置換論理アドレスとしてアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第1の物理アドレス読出手段と、

前記比較の結果、両者が不一致の場合、前記切替信号を入力せずに、前記入力された論理アドレスを前記配線手段からアドレス記憶手段に送出して当該アドレス記憶手段から物理アドレスを読み出す第2の物理アドレス読出手段と、

前記第1又は第2の物理アドレス読出手段により読み出された物理アドレス及び前記入力された読出/書込命令を前記メモリ部に送出する手段と、

を備えたことを特徴とする不揮発性メモリ装置。

【請求項5】

請求項1乃至請求項4のいずれか1項に記載の不揮発性メモリ装置を備えたことを特徴とするLSI装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2009−258992(P2009−258992A)

【公開日】平成21年11月5日(2009.11.5)

【国際特許分類】

【出願番号】特願2008−107205(P2008−107205)

【出願日】平成20年4月16日(2008.4.16)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

【公開日】平成21年11月5日(2009.11.5)

【国際特許分類】

【出願日】平成20年4月16日(2008.4.16)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

[ Back to top ]