不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】制御ゲート電極および浮遊ゲート電極を備えた構成において、制御ゲート電極を構成する多結晶シリコンの空乏化を抑制できるようにした不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、複数の浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成されたワード線と、を備える。ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ複数の浮遊ゲート電極間に一部が位置する分断層を介在して形成され、ワード線は、その下層の高さが上層の高さよりも低い。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、複数の浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成されたワード線と、を備える。ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ複数の浮遊ゲート電極間に一部が位置する分断層を介在して形成され、ワード線は、その下層の高さが上層の高さよりも低い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置に関する。

【背景技術】

【0002】

例えばNAND型のフラッシュメモリ装置のような不揮発性半導体記憶装置は、制御ゲート電極と半導体基板の間に浮遊ゲート電極を設け、制御ゲート電極に所定電圧を印加することで浮遊ゲート電極に電荷を蓄積する。これにより浮遊ゲート電極に情報を保持する。浮遊ゲート電極は、層間絶縁膜を介して隣接する他の浮遊ゲート電極と対向しており、浮遊ゲート電極と半導体基板の間にはトンネル酸化膜となるシリコン熱酸化膜が設けられている。

【0003】

これらの制御ゲート電極および浮遊ゲート電極は、その材料としてリン(P)などの不純物を含む多結晶シリコンが用いられる。このような不揮発性半導体記憶装置は、素子の微細化の要求に伴い、制御ゲート電極および浮遊ゲート電極の幅寸法を細くすることが望まれており、対向する浮遊ゲート間の距離も狭くすることが望まれている。

【0004】

このような微細化の要求に伴い、多結晶シリコンの空乏化の影響が大きくなってきている。この空乏化の原因は、制御ゲート電極および浮遊ゲート電極のアスペクト比の増加に伴い、多結晶シリコンの体積に対するゲート電極の表面積の割合が増加することが一因として挙げられる。

【0005】

ゲート電極の表面積が増加すると、多結晶シリコンに添加されたリン(P)などの不純物の放出度が増加し、当該多結晶シリコン中の自由キャリア数が減少し、空乏化が生じると考えられる。このような空乏化の影響が大きくなると、書込時に浮遊ゲート電極にかかる電圧が減少してしまい、書込不良を生じる虞がある。このような空乏化問題に対処するため、多結晶シリコンの不純物活性化率を保持する技術が提供されている。しかしながら、微細化の要求を考慮すれば、空乏化対策として十分とは言えない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−244108号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

そこで、制御ゲート電極および浮遊ゲート電極を備えた構成において、制御ゲート電極を構成する多結晶シリコンの空乏化を抑制できるようにした不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置を提供する。

【課題を解決するための手段】

【0008】

一実施形態に係る不揮発性半導体記憶装置の製造方法は以下を含む。半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に複数の浮遊ゲート電極を形成する。複数の浮遊ゲート電極上に電極間絶縁膜を形成する。不純物がドープされた多結晶シリコンを含むワード線を電極間絶縁膜上に形成するときに、ワード線の下層と上層の間を分断し且つ複数の浮遊ゲート電極間に一部が存在するよう酸素または窒素を含有した分断層を形成する。

【0009】

このワード線を堆積するときには、ワード線の下層をその一部の上面が複数の浮遊ゲート電極間に位置するように堆積する。分断層について酸素を含有して形成するときにはシリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換して形成する。分断層について窒素を含有して形成するときにはシリコンを堆積する途中に雰囲気を窒素(N2)雰囲気に置換して形成する。そして分断層上にワード線の下層の高さよりも高くワード線の上層を形成する。

【0010】

一実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、複数の浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成されたワード線と、を備える。ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ複数の浮遊ゲート電極間に一部が存在する分断層を介在して形成されている。ワード線は、その下層の高さが上層の高さよりも低い。

【図面の簡単な説明】

【0011】

【図1】一実施形態について不揮発性半導体記憶装置の電気的構成の一部を示す等価回路図

【図2】不揮発性半導体記憶装置のレイアウト構成の一部を示す平面図

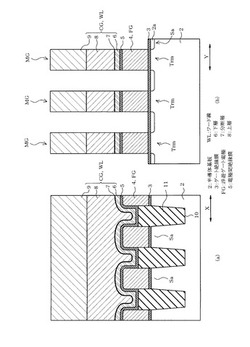

【図3】(a)図2の3A−3A線に沿って模式的に示す縦断面図、(b)図2の3B−3B線に沿って模式的に示す縦断面図

【図4】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その1)

【図5】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その2)

【図6】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その3)

【図7】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その4)

【図8】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その5)

【図9】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その6)

【図10】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その7)

【図11】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その8)

【図12】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その9)

【発明を実施するための形態】

【0012】

以下、半導体記憶装置をNAND型のフラッシュメモリ装置に適用した場合の一実施形態について図1ないし図12を参照して説明する。尚、各実施形態において、実質的に同一の構成部位には同一の符号を付して説明を省略する。但し、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なる。説明の都合上、当該実施するための形態の説明における上下左右や高低、深浅などの方向は、後述する半導体基板の裏面側を基準とした相対的な位置関係を示している。従って、重力方向を基準とした方向に対し、位置関係が異なる場合がある。

【0013】

まず、本実施形態のNAND型のフラッシュメモリ装置の構造について説明する。図1は、NAND型フラッシュメモリ装置(不揮発性半導体記憶装置に相当)1のメモリセル領域におけるメモリセルアレイの一部の等価回路図を示している。

【0014】

NAND型フラッシュメモリ装置1は、そのメモリセルアレイ内に、2個の選択ゲートトランジスタTrs1、Trs2と、当該選択ゲートトランジスタTrs1、Trs2間に直列接続された複数個(例えば64個)のメモリセルトランジスタTrmとを有するNANDセルユニットSUが行列状に配置されることにより構成されている。NANDセルユニットSU内では、複数個のメモリセルトランジスタTrmは隣接するもの同士でソース/ドレイン領域を共用している。

【0015】

図1中のX方向(ワード線方向)に配列されたメモリセルトランジスタTrmは、ワード線WLにより共通接続されている。また、図1中のX方向に配列された選択ゲートトランジスタTrs1は選択ゲート線SGL1で共通接続され、選択ゲートトランジスタTrs2は選択ゲート線SGL2で共通接続されている。選択ゲートトランジスタTrs1のドレイン領域にはビット線コンタクトCBが接続されている。このビット線コンタクトCBは、図1中X方向に直交するY方向(ビット線方向)に延びるビット線BLに接続されている。また、選択ゲートトランジスタTrs2は、ソース領域を介して図1中X方向に延びるソース線SLに接続されている。

【0016】

図2は、メモリセル領域の一部のレイアウトパターンを平面図により示している。この図2に示すように、STI(shallow trench isolation)構造の素子分離領域Sbが図2中Y方向に沿って延伸して形成される。これらの素子分離領域Sbは、図2中、X方向に所定間隔で複数形成されている。これにより、素子領域Saが図2中のY方向に沿って延伸形成されることになり、複数の素子領域SaがX方向に分離して形成されている。

【0017】

ワード線WLは、素子領域Saと直交して交差する方向(図2中X方向)に沿って延伸形成される。ワード線WLは、図2中Y方向に所定間隔で複数本形成されている。ワード線WLと交差する素子領域Sa上方には、メモリセルトランジスタTrmのメモリセルゲート電極MG(図3参照)が形成されている。

【0018】

図1に示すように、Y方向に隣接した複数のメモリセルトランジスタTrmはNAND列(メモリセルストリング)を構成する。選択ゲートトランジスタTrs1、Trs2は、NAND列の端部メモリセルのY方向両外側に隣接してそれぞれ構成されている。

【0019】

選択ゲートトランジスタTrs1はX方向に複数設けられており、複数の選択ゲートトランジスタTrs1の選択ゲート電極SG(図2参照)は選択ゲート線SGL1により電気的に接続されている。なお選択ゲート線SGL1と交差する素子領域Saに、選択ゲートトランジスタTrs1の選択ゲート電極SGが構成されている。

【0020】

また、図1に示すように、選択ゲートトランジスタTrs2はX方向に複数設けられており、複数の選択ゲートトランジスタTrs2の選択ゲート電極(図2および図3には図示せず)は選択ゲート線SGL2によって電気的に接続されている。

【0021】

図1に示すように、Y方向に隣接するNANDセルユニットSU−SUの選択ゲートトランジスタTrs1−Trs1間にはビット線コンタクトCBが構成されている。複数のビット線コンタクトCBは複数の素子領域Sa上にそれぞれ構成されている。

【0022】

図3(a)は、図2の3A−3A線に沿う縦断面構造を模式的に示し、図3(b)は図2の3B−3B線に沿う縦断面構造を模式的に示している。これらの図3(a)および図3(b)は、メモリセルトランジスタTrmの縦断面構造を示している。図3(a)に示すように、半導体基板(例えばp型のシリコン基板)2上にはゲート絶縁膜3が形成されている。このゲート絶縁膜3は例えばシリコン酸化膜を含んで構成され、メモリセルトランジスタTrmの形成領域において半導体基板2の上面上に沿って形成される。

【0023】

メモリセルトランジスタTrmは、当該ゲート絶縁膜3上に形成されたメモリセルゲート電極MGと、当該メモリセルゲート電極MGの両脇に半導体基板2の表層に形成されたソース/ドレイン領域2aとを含む。

【0024】

メモリセルゲート電極MGは、ゲート絶縁膜3上にリン(P)などのn型不純物がドープされた多結晶シリコン層4を用いた浮遊ゲート電極(電荷蓄積層)FG、電極間絶縁膜5、ワード線WLとなる制御ゲート電極CGが順に積層されている。

【0025】

電極間絶縁膜5は、浮遊ゲート電極FGと制御ゲート電極CGとの間に位置した絶縁膜であり、多結晶シリコン層を挟んで構成されたインターポリ絶縁膜、ゲート間絶縁膜となる。この電極間絶縁膜5としては、例えば酸化膜/窒化膜/酸化膜の積層構造(所謂ONO膜)を用いて構成できるが、当該膜の成膜前後に窒化膜を成膜した所謂NONON膜としても良いし、酸化アルミニウム(アルミナ)または酸化ハフニウムを含む高誘電率膜を中間の窒化膜の代わりに形成しても良い。

【0026】

ワード線WLとなる制御ゲート電極CGは、リン(P)によるn型の不純物がドープされた多結晶シリコンの下層6と、この多結晶シリコンの下層6上にシリコン酸化(SiO)層を用いて形成された分断層7と、この分断層7の上に形成された多結晶シリコンの上層8と、この上層8をシリサイド化したシリサイド層9とを含む。シリコンの上層8もまたリン(P)によるn型の不純物がドープされている。ここで、下層6、上層8は、不純物がドープされたアモルファスシリコンが多結晶化した層である。

【0027】

分断層7は、多結晶シリコン層の下層6を堆積した後、酸素(O2)雰囲気中に僅かに曝露して形成された非常に薄い(数Å(オングストローム)程度:例えば5Å)酸化層を用いて形成されている。

【0028】

シリサイド層9は、シリコンの上層8の上部を低抵抗化金属によりシリサイド化された層である。ここで、低抵抗化金属としては、ニッケル(Ni)、チタン(Ti)、コバルト(Co)、白金(Pt)、パラジウム(Pd)、タンタル(Ta)、モリブデン(Mo)などの遷移金属を適用できる。シリサイド層9の厚さは、シリサイド化金属材料に応じて適宜変更しても良く、適切な金属材料を選定することでシリコンの上層8の上部の全部、または上層8および下層6の全部をシリサイド層9として構成しても良い。図3(b)に示すように、メモリセルトランジスタTrmは、Y方向に複数隣接して設けられている。

【0029】

なお、断面構造の図示を省略しているが、選択ゲートトランジスタTrs1およびTrs2の選択ゲート電極は、メモリセルトランジスタTrmのメモリセルゲート電極MGとほぼ同様の構造であり、多結晶シリコン層4、電極間絶縁膜5、シリコンの下層6、分断層7、シリコンの上層8、シリサイド層9を積層した構造となっているが、電極間絶縁膜5のほぼ中央に位置して貫通孔が形成されており、シリコンの下層6および多結晶シリコン層4間を接触させることで電極間絶縁膜5としての機能を無効化している。

【0030】

図3(b)は、図2の3B−3B線に沿う縦断面図を示している。メモリセルトランジスタTrmの素子領域Saは、素子分離溝10に埋め込まれたSTI(Shallow Trench Isolation)構造の素子分離絶縁膜11によって素子分離されている。

【0031】

素子分離絶縁膜11は、浮遊ゲート電極FGの側面に沿って自己整合的に形成されており、その上面が浮遊ゲート電極FGの下面より上方で且つ浮遊ゲート電極FGの上面より下方に位置している。素子分離絶縁膜11はシリコン酸化膜を主として構成されている。図3(a)に示すように、電極間絶縁膜5は素子分離絶縁膜11の上面上に沿うと共に浮遊ゲート電極FGの上部側面に沿って形成されている。

【0032】

そして、シリコンの下層6が、隣接する浮遊ゲート電極FG−FG間に挟まれた窪部に埋込まれており、これによりワード線WLと浮遊ゲート電極FGとの間の対向面積を拡大してカップリング比を向上している。シリコンの下層6上には分断層7を介在してシリコンの上層8が堆積されている。このシリコンの下層6の高さはシリコンの上層8の高さの例えば10分の1ほどの高さに低く形成されている。これにより、多結晶シリコンの下層6は、その結晶粒径平均値が多結晶シリコンの上層8の結晶粒径の平均値に比較して小さくなる。これは、グレインバウンダリ(結晶粒界)が分断層7で非連続となるためであり、各メモリセルゲート電極MGのシリコンの下層6の高さがシリコンの上層8の高さに比較して低くなるためである。結晶粒径の平均値は下層6が上層8に比較して小さい。

【0033】

前記した構成の製造方法の一例について説明する。本実施形態の説明では特徴部分を中心に説明するが、一般的な工程であれば各工程間に他の工程を追加しても良いし、必要なければ高低を削除しても良い。また、各工程は実用的に可能であれば必要に応じて入れ替えても良い。前述した膜、層と同一機能を有する被加工膜については同一または類似の符号を付して説明を行う。

【0034】

図4(a)〜図12(a)のうち「a」を付した図面は、図3(a)に対応した部分について一製造段階の縦断面を模式的に示すものであり、図4(b)〜図12(b)の「b」を付した図面は、図3(b)に対応した部分について一製造段階の縦断面を模式的に示している。

【0035】

図4(a)および図4(b)に示すように、半導体基板2上にゲート絶縁膜3を形成する。本実施形態では、半導体基板2をp型のシリコン基板によって形成しているため、シリコン基板の上面を熱酸化処理することでシリコン酸化膜をゲート絶縁膜3として形成する。次に、浮遊ゲート電極FG膜となる多結晶シリコン層4をLP−CVD(化学気相成長)法により堆積する。このとき添加する不純物としてはn型不純物であるリン(P)を用いる。

【0036】

次に、図5(a)および図5(b)に示すように、この多結晶シリコン層4の上にLP−CVD法によって窒化膜12を適切な膜厚だけ堆積し、続いて、この窒化膜12上に化学気相成長法によって酸化膜13を適切な膜厚だけ堆積する。次に、酸化膜13上にレジスト14を塗布し、露光してから現像してレジスト14をパターニングする。このとき、レジスト14をパターニングして所定間隔のラインアンドスペースパターンに形成する。

【0037】

次に、図6(a)および図6(b)に示すように、パターニングされたレジスト14をマスクとして酸化膜13をRIE法によりエッチングする。エッチング後にフォトレジスト14を除去し、酸化膜13をマスクとして窒化膜12をエッチングし、続いて、多結晶シリコン層4、ゲート絶縁膜3、半導体基板2の上部を所定間隔でエッチングすることで素子分離溝10を形成する。

【0038】

次に、図7(a)および図7(b)に示すように、素子分離溝10内に堆積技術、塗布技術などを用いて酸化膜などによって素子分離絶縁膜11を埋込み、素子分離絶縁膜11を窒化膜12の上面が露出するまでCMP(Chemical Mechanical Polishing)法により平坦化し、その後、素子分離絶縁膜11の上面を選択的にエッチングすることで、素子分離絶縁膜11の上部を多結晶シリコン層4の上面より下方でゲート絶縁膜3の上面より上方の位置までエッチング処理して落とし込む。この後、多結晶シリコン層4上に残留する窒化膜12を例えばウェットエッチングで選択的にエッチング除去する。

【0039】

次に、図8(a)および図8(b)に示すように、多結晶シリコン層4の上面、上部側面、素子分離絶縁膜11の上面に沿って電極間絶縁膜5を形成する。この電極間絶縁膜5は、酸化膜/窒化膜/酸化膜(所謂ONO)の積層構造を周知のプロセスにより形成するものである。電極間絶縁膜5としてONO膜の成膜前後にラジカル窒化処理することでNONON膜としても良いし、酸化アルミニウム(アルミナ)または酸化ハフニウムを含む高誘電率膜を中間の窒化膜の代わりに形成しても良い。

【0040】

次に、図9(a)および図9(b)に示すように、ワード線WL、制御ゲート電極CGの一部を構成するシリコンをLP−CVD法により下層6として堆積する。このとき用いる成膜条件は、リン(P)ドープ用のフォスフィン(PH3)ガスとモノシラン(SiH4)を反応炉内に供給すると共に当該反応炉内を所定の減圧状態に維持しシリコンを堆積する。成膜パラメータとしては、例えば、温度を525℃、圧力53Pa、モノシラン流量500cc、フォスフィン流量47.2ccとする。

【0041】

目的厚さの下層6を堆積した後この成膜を停止し、チャンパー内の雰囲気を酸素(O2)に置換し、酸素(O2)パージを2分行う。すると、図10(a)および図10(b)に示すように、下層6上に酸素(O)含有層による分断層7を形成できる。分断層7の膜厚は5Å(数Å程度)としており、その他の機能膜(例えばシリコンの下層6、上層8、電極間絶縁膜5など)に比較して極薄の膜としている。酸素(O2)パージの後、成膜条件を戻して、図11(a)および図11(b)に示すように、目的厚さまで上層8の成膜を行う。上層8の成膜条件は下層6の成膜条件と同様の成膜条件とする。本実施の形態では、この上層8の膜厚は下層6の厚さに比較して10倍程度の膜厚にしている。

【0042】

酸素(O2)パージの前後には、チャンバー内の真空引きを合計5分ほど行うが、本実施形態の成膜条件を用いることで下層6、分断層7、上層8を同一チャンバー内で連続して成膜できる。前記した温度条件で成膜されたシリコンの下層6、上層8は、堆積直後においてアモルファス状態であるものの、後の熱工程で多結晶シリコンに変成する。

【0043】

本実施形態では、下層6の膜厚が薄く、分断層7の下方から上方にかけて結晶が成長しにくくなる。分断層7を設けることでシリコンの下層6および上層8間に結晶粒界(Grain Boundary)を設けることができ、この結果、特に多結晶シリコンの下層6の結晶粒径の平均値を小さくできる。これにより、特に下層6の空乏化を抑制できる。多結晶シリコンの単位体積中の粒界の割合が増加し、リン(P)などの不純物が多結晶シリコンの下層6中に留まりやすくなりキャリアの割合が増加する。

【0044】

次に、シリコンの上層8の上にレジストを塗布してマスクパターン(図示せず)を形成し、図12(a)および図12(b)に示すように、上層8、分断層7、下層6、電極間絶縁膜5、多結晶シリコン層4、必要に応じてゲート絶縁膜3を異方性エッチングすることによって分断し、マスクパターンを除去する。次に、分断した積層膜4〜8間の半導体基板2の表層にn型不純物をイオン注入する。このイオン注入された不純物は後に活性化され、この領域がソース/ドレイン領域2aとして形成される。

【0045】

その後、分断された積層膜4〜8間に層間絶縁膜を埋込み(図示せず)、その後、図3(a)および図3(b)に示すように、シリコンの上層8の上部を金属でシリサイド化することでシリサイド層9を形成する。シリサイド層9はそのシリサイド化金属材料に応じて、シリコンの上層8全体のみに留まらずシリコンの下層6をシリサイド化しても良いし、シリコンの上層8のシリサイド化を分断層7でストップしても良い。

【0046】

その後の製造工程は、本実施形態の特徴に関係しないため詳細説明を省略するが、ビット線コンタクトCBなどのコンタクト、多層配線構造などを構成する。その後の製造工程は発明の特徴部分に特に関係しないため説明を省略する。これにより、NAND型のフラッシュメモリ装置1を形成できる。

【0047】

以上説明したように、本実施形態によれば、シリコンの下層6上に酸素を含有する分断層7を形成するときには、シリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換することで分断層7を形成している。すると、分断層7の下方から上方にかけてシリコンの結晶が成長しにくくなり、分断層7を設けることでシリコンの下層6および上層8間に結晶粒界を設けることができる。

【0048】

この結果、特に多結晶シリコンの下層6の結晶粒径の平均値を小さくでき、多結晶シリコンの単位体積中の粒界の割合が増加する。リン(P)などの不純物は多結晶シリコンの粒界を伝達し当該多結晶シリコン中に滞留しやすい傾向がある。したがって、リン(P)などの不純物が多結晶シリコンの下層6中に留まりやすくなり、有効キャリアの割合が増加する。これにより下層6の電気的な空乏化を抑制できる。

【0049】

分断層7は、隣接した浮遊ゲート電極FG−FG間に位置しているため、浮遊ゲート電極FG−FG間に位置する分断層7と電極間絶縁膜5とのスペースが小さくなり、下層6を構成するシリコンが結晶化したとしてもその平均粒径はより小さくなる。

【0050】

(その他の実施形態)

前述実施形態の説明では、酸素(O2)雰囲気中に曝して酸素(O2)パージし酸素含有層を分断層7として構成したが、これに限定されるものではなく、窒素(N2)雰囲気中に曝して窒素(N2)パージした窒素含有層を分断層7に代えて構成しても良い。窒素(N2)パージを行う場合、約900℃−1000℃の温度条件を用いると良い。

【0051】

また、上層8の膜厚は下層6の厚さに比較して10倍程度の膜厚としたが、これに限定されるものではなく、上層8の膜厚が下層6の厚さより厚ければ、下層6の方が多結晶シリコンの粒径を小さくすることができる。

【0052】

シリコンの下層6、上層8を堆積するときに、カーボンなどの成分をドープすることにより多結晶シリコンの粒径を小さくするようにしても良い。制御ゲート電極CGを構成するシリサイド層9は設けても設けなくても良い。

【0053】

NAND型のフラッシュメモリ装置1に適用したが、NOR型のフラッシュメモリ装置、EEPROM等の半導体記憶装置にも適用できる。

本発明のいくつかの実施形態を説明したが、各実施形態に示した構成、各種条件に限定されることはなく、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0054】

図面中、1はフラッシュメモリ装置(不揮発性半導体記憶装置)、2は半導体基板、3はゲート絶縁膜、5は電極間絶縁膜、6は下層、7は分断層、8は上層、FGは浮遊ゲート電極、WLはワード線を示す。

【技術分野】

【0001】

本発明の実施形態は、不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置に関する。

【背景技術】

【0002】

例えばNAND型のフラッシュメモリ装置のような不揮発性半導体記憶装置は、制御ゲート電極と半導体基板の間に浮遊ゲート電極を設け、制御ゲート電極に所定電圧を印加することで浮遊ゲート電極に電荷を蓄積する。これにより浮遊ゲート電極に情報を保持する。浮遊ゲート電極は、層間絶縁膜を介して隣接する他の浮遊ゲート電極と対向しており、浮遊ゲート電極と半導体基板の間にはトンネル酸化膜となるシリコン熱酸化膜が設けられている。

【0003】

これらの制御ゲート電極および浮遊ゲート電極は、その材料としてリン(P)などの不純物を含む多結晶シリコンが用いられる。このような不揮発性半導体記憶装置は、素子の微細化の要求に伴い、制御ゲート電極および浮遊ゲート電極の幅寸法を細くすることが望まれており、対向する浮遊ゲート間の距離も狭くすることが望まれている。

【0004】

このような微細化の要求に伴い、多結晶シリコンの空乏化の影響が大きくなってきている。この空乏化の原因は、制御ゲート電極および浮遊ゲート電極のアスペクト比の増加に伴い、多結晶シリコンの体積に対するゲート電極の表面積の割合が増加することが一因として挙げられる。

【0005】

ゲート電極の表面積が増加すると、多結晶シリコンに添加されたリン(P)などの不純物の放出度が増加し、当該多結晶シリコン中の自由キャリア数が減少し、空乏化が生じると考えられる。このような空乏化の影響が大きくなると、書込時に浮遊ゲート電極にかかる電圧が減少してしまい、書込不良を生じる虞がある。このような空乏化問題に対処するため、多結晶シリコンの不純物活性化率を保持する技術が提供されている。しかしながら、微細化の要求を考慮すれば、空乏化対策として十分とは言えない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−244108号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

そこで、制御ゲート電極および浮遊ゲート電極を備えた構成において、制御ゲート電極を構成する多結晶シリコンの空乏化を抑制できるようにした不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置を提供する。

【課題を解決するための手段】

【0008】

一実施形態に係る不揮発性半導体記憶装置の製造方法は以下を含む。半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に複数の浮遊ゲート電極を形成する。複数の浮遊ゲート電極上に電極間絶縁膜を形成する。不純物がドープされた多結晶シリコンを含むワード線を電極間絶縁膜上に形成するときに、ワード線の下層と上層の間を分断し且つ複数の浮遊ゲート電極間に一部が存在するよう酸素または窒素を含有した分断層を形成する。

【0009】

このワード線を堆積するときには、ワード線の下層をその一部の上面が複数の浮遊ゲート電極間に位置するように堆積する。分断層について酸素を含有して形成するときにはシリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換して形成する。分断層について窒素を含有して形成するときにはシリコンを堆積する途中に雰囲気を窒素(N2)雰囲気に置換して形成する。そして分断層上にワード線の下層の高さよりも高くワード線の上層を形成する。

【0010】

一実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、複数の浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成されたワード線と、を備える。ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ複数の浮遊ゲート電極間に一部が存在する分断層を介在して形成されている。ワード線は、その下層の高さが上層の高さよりも低い。

【図面の簡単な説明】

【0011】

【図1】一実施形態について不揮発性半導体記憶装置の電気的構成の一部を示す等価回路図

【図2】不揮発性半導体記憶装置のレイアウト構成の一部を示す平面図

【図3】(a)図2の3A−3A線に沿って模式的に示す縦断面図、(b)図2の3B−3B線に沿って模式的に示す縦断面図

【図4】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その1)

【図5】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その2)

【図6】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その3)

【図7】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その4)

【図8】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その5)

【図9】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その6)

【図10】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その7)

【図11】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その8)

【図12】(a)図2の3A−3A線に沿って示す製造工程の一段階における模式的な縦断面図、(b)図2の3B−3B線に沿って示す製造工程の一段階における模式的な縦断面図(その9)

【発明を実施するための形態】

【0012】

以下、半導体記憶装置をNAND型のフラッシュメモリ装置に適用した場合の一実施形態について図1ないし図12を参照して説明する。尚、各実施形態において、実質的に同一の構成部位には同一の符号を付して説明を省略する。但し、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なる。説明の都合上、当該実施するための形態の説明における上下左右や高低、深浅などの方向は、後述する半導体基板の裏面側を基準とした相対的な位置関係を示している。従って、重力方向を基準とした方向に対し、位置関係が異なる場合がある。

【0013】

まず、本実施形態のNAND型のフラッシュメモリ装置の構造について説明する。図1は、NAND型フラッシュメモリ装置(不揮発性半導体記憶装置に相当)1のメモリセル領域におけるメモリセルアレイの一部の等価回路図を示している。

【0014】

NAND型フラッシュメモリ装置1は、そのメモリセルアレイ内に、2個の選択ゲートトランジスタTrs1、Trs2と、当該選択ゲートトランジスタTrs1、Trs2間に直列接続された複数個(例えば64個)のメモリセルトランジスタTrmとを有するNANDセルユニットSUが行列状に配置されることにより構成されている。NANDセルユニットSU内では、複数個のメモリセルトランジスタTrmは隣接するもの同士でソース/ドレイン領域を共用している。

【0015】

図1中のX方向(ワード線方向)に配列されたメモリセルトランジスタTrmは、ワード線WLにより共通接続されている。また、図1中のX方向に配列された選択ゲートトランジスタTrs1は選択ゲート線SGL1で共通接続され、選択ゲートトランジスタTrs2は選択ゲート線SGL2で共通接続されている。選択ゲートトランジスタTrs1のドレイン領域にはビット線コンタクトCBが接続されている。このビット線コンタクトCBは、図1中X方向に直交するY方向(ビット線方向)に延びるビット線BLに接続されている。また、選択ゲートトランジスタTrs2は、ソース領域を介して図1中X方向に延びるソース線SLに接続されている。

【0016】

図2は、メモリセル領域の一部のレイアウトパターンを平面図により示している。この図2に示すように、STI(shallow trench isolation)構造の素子分離領域Sbが図2中Y方向に沿って延伸して形成される。これらの素子分離領域Sbは、図2中、X方向に所定間隔で複数形成されている。これにより、素子領域Saが図2中のY方向に沿って延伸形成されることになり、複数の素子領域SaがX方向に分離して形成されている。

【0017】

ワード線WLは、素子領域Saと直交して交差する方向(図2中X方向)に沿って延伸形成される。ワード線WLは、図2中Y方向に所定間隔で複数本形成されている。ワード線WLと交差する素子領域Sa上方には、メモリセルトランジスタTrmのメモリセルゲート電極MG(図3参照)が形成されている。

【0018】

図1に示すように、Y方向に隣接した複数のメモリセルトランジスタTrmはNAND列(メモリセルストリング)を構成する。選択ゲートトランジスタTrs1、Trs2は、NAND列の端部メモリセルのY方向両外側に隣接してそれぞれ構成されている。

【0019】

選択ゲートトランジスタTrs1はX方向に複数設けられており、複数の選択ゲートトランジスタTrs1の選択ゲート電極SG(図2参照)は選択ゲート線SGL1により電気的に接続されている。なお選択ゲート線SGL1と交差する素子領域Saに、選択ゲートトランジスタTrs1の選択ゲート電極SGが構成されている。

【0020】

また、図1に示すように、選択ゲートトランジスタTrs2はX方向に複数設けられており、複数の選択ゲートトランジスタTrs2の選択ゲート電極(図2および図3には図示せず)は選択ゲート線SGL2によって電気的に接続されている。

【0021】

図1に示すように、Y方向に隣接するNANDセルユニットSU−SUの選択ゲートトランジスタTrs1−Trs1間にはビット線コンタクトCBが構成されている。複数のビット線コンタクトCBは複数の素子領域Sa上にそれぞれ構成されている。

【0022】

図3(a)は、図2の3A−3A線に沿う縦断面構造を模式的に示し、図3(b)は図2の3B−3B線に沿う縦断面構造を模式的に示している。これらの図3(a)および図3(b)は、メモリセルトランジスタTrmの縦断面構造を示している。図3(a)に示すように、半導体基板(例えばp型のシリコン基板)2上にはゲート絶縁膜3が形成されている。このゲート絶縁膜3は例えばシリコン酸化膜を含んで構成され、メモリセルトランジスタTrmの形成領域において半導体基板2の上面上に沿って形成される。

【0023】

メモリセルトランジスタTrmは、当該ゲート絶縁膜3上に形成されたメモリセルゲート電極MGと、当該メモリセルゲート電極MGの両脇に半導体基板2の表層に形成されたソース/ドレイン領域2aとを含む。

【0024】

メモリセルゲート電極MGは、ゲート絶縁膜3上にリン(P)などのn型不純物がドープされた多結晶シリコン層4を用いた浮遊ゲート電極(電荷蓄積層)FG、電極間絶縁膜5、ワード線WLとなる制御ゲート電極CGが順に積層されている。

【0025】

電極間絶縁膜5は、浮遊ゲート電極FGと制御ゲート電極CGとの間に位置した絶縁膜であり、多結晶シリコン層を挟んで構成されたインターポリ絶縁膜、ゲート間絶縁膜となる。この電極間絶縁膜5としては、例えば酸化膜/窒化膜/酸化膜の積層構造(所謂ONO膜)を用いて構成できるが、当該膜の成膜前後に窒化膜を成膜した所謂NONON膜としても良いし、酸化アルミニウム(アルミナ)または酸化ハフニウムを含む高誘電率膜を中間の窒化膜の代わりに形成しても良い。

【0026】

ワード線WLとなる制御ゲート電極CGは、リン(P)によるn型の不純物がドープされた多結晶シリコンの下層6と、この多結晶シリコンの下層6上にシリコン酸化(SiO)層を用いて形成された分断層7と、この分断層7の上に形成された多結晶シリコンの上層8と、この上層8をシリサイド化したシリサイド層9とを含む。シリコンの上層8もまたリン(P)によるn型の不純物がドープされている。ここで、下層6、上層8は、不純物がドープされたアモルファスシリコンが多結晶化した層である。

【0027】

分断層7は、多結晶シリコン層の下層6を堆積した後、酸素(O2)雰囲気中に僅かに曝露して形成された非常に薄い(数Å(オングストローム)程度:例えば5Å)酸化層を用いて形成されている。

【0028】

シリサイド層9は、シリコンの上層8の上部を低抵抗化金属によりシリサイド化された層である。ここで、低抵抗化金属としては、ニッケル(Ni)、チタン(Ti)、コバルト(Co)、白金(Pt)、パラジウム(Pd)、タンタル(Ta)、モリブデン(Mo)などの遷移金属を適用できる。シリサイド層9の厚さは、シリサイド化金属材料に応じて適宜変更しても良く、適切な金属材料を選定することでシリコンの上層8の上部の全部、または上層8および下層6の全部をシリサイド層9として構成しても良い。図3(b)に示すように、メモリセルトランジスタTrmは、Y方向に複数隣接して設けられている。

【0029】

なお、断面構造の図示を省略しているが、選択ゲートトランジスタTrs1およびTrs2の選択ゲート電極は、メモリセルトランジスタTrmのメモリセルゲート電極MGとほぼ同様の構造であり、多結晶シリコン層4、電極間絶縁膜5、シリコンの下層6、分断層7、シリコンの上層8、シリサイド層9を積層した構造となっているが、電極間絶縁膜5のほぼ中央に位置して貫通孔が形成されており、シリコンの下層6および多結晶シリコン層4間を接触させることで電極間絶縁膜5としての機能を無効化している。

【0030】

図3(b)は、図2の3B−3B線に沿う縦断面図を示している。メモリセルトランジスタTrmの素子領域Saは、素子分離溝10に埋め込まれたSTI(Shallow Trench Isolation)構造の素子分離絶縁膜11によって素子分離されている。

【0031】

素子分離絶縁膜11は、浮遊ゲート電極FGの側面に沿って自己整合的に形成されており、その上面が浮遊ゲート電極FGの下面より上方で且つ浮遊ゲート電極FGの上面より下方に位置している。素子分離絶縁膜11はシリコン酸化膜を主として構成されている。図3(a)に示すように、電極間絶縁膜5は素子分離絶縁膜11の上面上に沿うと共に浮遊ゲート電極FGの上部側面に沿って形成されている。

【0032】

そして、シリコンの下層6が、隣接する浮遊ゲート電極FG−FG間に挟まれた窪部に埋込まれており、これによりワード線WLと浮遊ゲート電極FGとの間の対向面積を拡大してカップリング比を向上している。シリコンの下層6上には分断層7を介在してシリコンの上層8が堆積されている。このシリコンの下層6の高さはシリコンの上層8の高さの例えば10分の1ほどの高さに低く形成されている。これにより、多結晶シリコンの下層6は、その結晶粒径平均値が多結晶シリコンの上層8の結晶粒径の平均値に比較して小さくなる。これは、グレインバウンダリ(結晶粒界)が分断層7で非連続となるためであり、各メモリセルゲート電極MGのシリコンの下層6の高さがシリコンの上層8の高さに比較して低くなるためである。結晶粒径の平均値は下層6が上層8に比較して小さい。

【0033】

前記した構成の製造方法の一例について説明する。本実施形態の説明では特徴部分を中心に説明するが、一般的な工程であれば各工程間に他の工程を追加しても良いし、必要なければ高低を削除しても良い。また、各工程は実用的に可能であれば必要に応じて入れ替えても良い。前述した膜、層と同一機能を有する被加工膜については同一または類似の符号を付して説明を行う。

【0034】

図4(a)〜図12(a)のうち「a」を付した図面は、図3(a)に対応した部分について一製造段階の縦断面を模式的に示すものであり、図4(b)〜図12(b)の「b」を付した図面は、図3(b)に対応した部分について一製造段階の縦断面を模式的に示している。

【0035】

図4(a)および図4(b)に示すように、半導体基板2上にゲート絶縁膜3を形成する。本実施形態では、半導体基板2をp型のシリコン基板によって形成しているため、シリコン基板の上面を熱酸化処理することでシリコン酸化膜をゲート絶縁膜3として形成する。次に、浮遊ゲート電極FG膜となる多結晶シリコン層4をLP−CVD(化学気相成長)法により堆積する。このとき添加する不純物としてはn型不純物であるリン(P)を用いる。

【0036】

次に、図5(a)および図5(b)に示すように、この多結晶シリコン層4の上にLP−CVD法によって窒化膜12を適切な膜厚だけ堆積し、続いて、この窒化膜12上に化学気相成長法によって酸化膜13を適切な膜厚だけ堆積する。次に、酸化膜13上にレジスト14を塗布し、露光してから現像してレジスト14をパターニングする。このとき、レジスト14をパターニングして所定間隔のラインアンドスペースパターンに形成する。

【0037】

次に、図6(a)および図6(b)に示すように、パターニングされたレジスト14をマスクとして酸化膜13をRIE法によりエッチングする。エッチング後にフォトレジスト14を除去し、酸化膜13をマスクとして窒化膜12をエッチングし、続いて、多結晶シリコン層4、ゲート絶縁膜3、半導体基板2の上部を所定間隔でエッチングすることで素子分離溝10を形成する。

【0038】

次に、図7(a)および図7(b)に示すように、素子分離溝10内に堆積技術、塗布技術などを用いて酸化膜などによって素子分離絶縁膜11を埋込み、素子分離絶縁膜11を窒化膜12の上面が露出するまでCMP(Chemical Mechanical Polishing)法により平坦化し、その後、素子分離絶縁膜11の上面を選択的にエッチングすることで、素子分離絶縁膜11の上部を多結晶シリコン層4の上面より下方でゲート絶縁膜3の上面より上方の位置までエッチング処理して落とし込む。この後、多結晶シリコン層4上に残留する窒化膜12を例えばウェットエッチングで選択的にエッチング除去する。

【0039】

次に、図8(a)および図8(b)に示すように、多結晶シリコン層4の上面、上部側面、素子分離絶縁膜11の上面に沿って電極間絶縁膜5を形成する。この電極間絶縁膜5は、酸化膜/窒化膜/酸化膜(所謂ONO)の積層構造を周知のプロセスにより形成するものである。電極間絶縁膜5としてONO膜の成膜前後にラジカル窒化処理することでNONON膜としても良いし、酸化アルミニウム(アルミナ)または酸化ハフニウムを含む高誘電率膜を中間の窒化膜の代わりに形成しても良い。

【0040】

次に、図9(a)および図9(b)に示すように、ワード線WL、制御ゲート電極CGの一部を構成するシリコンをLP−CVD法により下層6として堆積する。このとき用いる成膜条件は、リン(P)ドープ用のフォスフィン(PH3)ガスとモノシラン(SiH4)を反応炉内に供給すると共に当該反応炉内を所定の減圧状態に維持しシリコンを堆積する。成膜パラメータとしては、例えば、温度を525℃、圧力53Pa、モノシラン流量500cc、フォスフィン流量47.2ccとする。

【0041】

目的厚さの下層6を堆積した後この成膜を停止し、チャンパー内の雰囲気を酸素(O2)に置換し、酸素(O2)パージを2分行う。すると、図10(a)および図10(b)に示すように、下層6上に酸素(O)含有層による分断層7を形成できる。分断層7の膜厚は5Å(数Å程度)としており、その他の機能膜(例えばシリコンの下層6、上層8、電極間絶縁膜5など)に比較して極薄の膜としている。酸素(O2)パージの後、成膜条件を戻して、図11(a)および図11(b)に示すように、目的厚さまで上層8の成膜を行う。上層8の成膜条件は下層6の成膜条件と同様の成膜条件とする。本実施の形態では、この上層8の膜厚は下層6の厚さに比較して10倍程度の膜厚にしている。

【0042】

酸素(O2)パージの前後には、チャンバー内の真空引きを合計5分ほど行うが、本実施形態の成膜条件を用いることで下層6、分断層7、上層8を同一チャンバー内で連続して成膜できる。前記した温度条件で成膜されたシリコンの下層6、上層8は、堆積直後においてアモルファス状態であるものの、後の熱工程で多結晶シリコンに変成する。

【0043】

本実施形態では、下層6の膜厚が薄く、分断層7の下方から上方にかけて結晶が成長しにくくなる。分断層7を設けることでシリコンの下層6および上層8間に結晶粒界(Grain Boundary)を設けることができ、この結果、特に多結晶シリコンの下層6の結晶粒径の平均値を小さくできる。これにより、特に下層6の空乏化を抑制できる。多結晶シリコンの単位体積中の粒界の割合が増加し、リン(P)などの不純物が多結晶シリコンの下層6中に留まりやすくなりキャリアの割合が増加する。

【0044】

次に、シリコンの上層8の上にレジストを塗布してマスクパターン(図示せず)を形成し、図12(a)および図12(b)に示すように、上層8、分断層7、下層6、電極間絶縁膜5、多結晶シリコン層4、必要に応じてゲート絶縁膜3を異方性エッチングすることによって分断し、マスクパターンを除去する。次に、分断した積層膜4〜8間の半導体基板2の表層にn型不純物をイオン注入する。このイオン注入された不純物は後に活性化され、この領域がソース/ドレイン領域2aとして形成される。

【0045】

その後、分断された積層膜4〜8間に層間絶縁膜を埋込み(図示せず)、その後、図3(a)および図3(b)に示すように、シリコンの上層8の上部を金属でシリサイド化することでシリサイド層9を形成する。シリサイド層9はそのシリサイド化金属材料に応じて、シリコンの上層8全体のみに留まらずシリコンの下層6をシリサイド化しても良いし、シリコンの上層8のシリサイド化を分断層7でストップしても良い。

【0046】

その後の製造工程は、本実施形態の特徴に関係しないため詳細説明を省略するが、ビット線コンタクトCBなどのコンタクト、多層配線構造などを構成する。その後の製造工程は発明の特徴部分に特に関係しないため説明を省略する。これにより、NAND型のフラッシュメモリ装置1を形成できる。

【0047】

以上説明したように、本実施形態によれば、シリコンの下層6上に酸素を含有する分断層7を形成するときには、シリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換することで分断層7を形成している。すると、分断層7の下方から上方にかけてシリコンの結晶が成長しにくくなり、分断層7を設けることでシリコンの下層6および上層8間に結晶粒界を設けることができる。

【0048】

この結果、特に多結晶シリコンの下層6の結晶粒径の平均値を小さくでき、多結晶シリコンの単位体積中の粒界の割合が増加する。リン(P)などの不純物は多結晶シリコンの粒界を伝達し当該多結晶シリコン中に滞留しやすい傾向がある。したがって、リン(P)などの不純物が多結晶シリコンの下層6中に留まりやすくなり、有効キャリアの割合が増加する。これにより下層6の電気的な空乏化を抑制できる。

【0049】

分断層7は、隣接した浮遊ゲート電極FG−FG間に位置しているため、浮遊ゲート電極FG−FG間に位置する分断層7と電極間絶縁膜5とのスペースが小さくなり、下層6を構成するシリコンが結晶化したとしてもその平均粒径はより小さくなる。

【0050】

(その他の実施形態)

前述実施形態の説明では、酸素(O2)雰囲気中に曝して酸素(O2)パージし酸素含有層を分断層7として構成したが、これに限定されるものではなく、窒素(N2)雰囲気中に曝して窒素(N2)パージした窒素含有層を分断層7に代えて構成しても良い。窒素(N2)パージを行う場合、約900℃−1000℃の温度条件を用いると良い。

【0051】

また、上層8の膜厚は下層6の厚さに比較して10倍程度の膜厚としたが、これに限定されるものではなく、上層8の膜厚が下層6の厚さより厚ければ、下層6の方が多結晶シリコンの粒径を小さくすることができる。

【0052】

シリコンの下層6、上層8を堆積するときに、カーボンなどの成分をドープすることにより多結晶シリコンの粒径を小さくするようにしても良い。制御ゲート電極CGを構成するシリサイド層9は設けても設けなくても良い。

【0053】

NAND型のフラッシュメモリ装置1に適用したが、NOR型のフラッシュメモリ装置、EEPROM等の半導体記憶装置にも適用できる。

本発明のいくつかの実施形態を説明したが、各実施形態に示した構成、各種条件に限定されることはなく、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0054】

図面中、1はフラッシュメモリ装置(不揮発性半導体記憶装置)、2は半導体基板、3はゲート絶縁膜、5は電極間絶縁膜、6は下層、7は分断層、8は上層、FGは浮遊ゲート電極、WLはワード線を示す。

【特許請求の範囲】

【請求項1】

半導体基板上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に複数の浮遊ゲート電極を形成し、

前記複数の浮遊ゲート電極上に電極間絶縁膜を形成し、

不純物がドープされた多結晶シリコンを含むワード線を前記電極間絶縁膜上に形成するときに、前記ワード線の下層と上層を分断し且つ前記複数の浮遊ゲート電極間に一部が位置するよう酸素または窒素を含有した分断層を形成する工程であって、

前記ワード線の下層をその一部の上面が前記複数の浮遊ゲート電極間に位置するように堆積し、

前記分断層について、前記酸素を含有して形成するときにはシリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換して形成し、前記窒素を含有して形成するときにはシリコンを堆積する途中に雰囲気を窒素(N2)雰囲気に置換して形成し、

前記分断層上に前記ワード線の下層の高さよりも高く前記ワード線の上層を形成することを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項2】

半導体基板と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、

前記複数の浮遊ゲート電極上に形成された電極間絶縁膜と、

前記電極間絶縁膜上に形成されたワード線と、を備え、

前記ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ前記複数の浮遊ゲート電極間に一部が位置する分断層を介在して形成され、

前記ワード線は、その下層の高さが上層の高さよりも低いことを特徴とする不揮発性半導体記憶装置。

【請求項3】

前記分断層は、シリコン酸化(SiO)層を含むことを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項4】

前記分断層は、前記ワード線の下層を構成するシリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換することで形成されていることを特徴とする請求項3記載の不揮発性半導体記憶装置。

【請求項5】

前記分断層は、シリコン窒化(SiN)層を含むことを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項6】

前記分断層は、前記ワード線の下層を構成するシリコンを堆積する途中に雰囲気を窒素(N2)雰囲気に置換することにより形成されていることを特徴とする請求項5記載の不揮発性半導体記憶装置。

【請求項1】

半導体基板上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に複数の浮遊ゲート電極を形成し、

前記複数の浮遊ゲート電極上に電極間絶縁膜を形成し、

不純物がドープされた多結晶シリコンを含むワード線を前記電極間絶縁膜上に形成するときに、前記ワード線の下層と上層を分断し且つ前記複数の浮遊ゲート電極間に一部が位置するよう酸素または窒素を含有した分断層を形成する工程であって、

前記ワード線の下層をその一部の上面が前記複数の浮遊ゲート電極間に位置するように堆積し、

前記分断層について、前記酸素を含有して形成するときにはシリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換して形成し、前記窒素を含有して形成するときにはシリコンを堆積する途中に雰囲気を窒素(N2)雰囲気に置換して形成し、

前記分断層上に前記ワード線の下層の高さよりも高く前記ワード線の上層を形成することを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項2】

半導体基板と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、

前記複数の浮遊ゲート電極上に形成された電極間絶縁膜と、

前記電極間絶縁膜上に形成されたワード線と、を備え、

前記ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ前記複数の浮遊ゲート電極間に一部が位置する分断層を介在して形成され、

前記ワード線は、その下層の高さが上層の高さよりも低いことを特徴とする不揮発性半導体記憶装置。

【請求項3】

前記分断層は、シリコン酸化(SiO)層を含むことを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項4】

前記分断層は、前記ワード線の下層を構成するシリコンを堆積する途中に雰囲気を酸素(O2)雰囲気に置換することで形成されていることを特徴とする請求項3記載の不揮発性半導体記憶装置。

【請求項5】

前記分断層は、シリコン窒化(SiN)層を含むことを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項6】

前記分断層は、前記ワード線の下層を構成するシリコンを堆積する途中に雰囲気を窒素(N2)雰囲気に置換することにより形成されていることを特徴とする請求項5記載の不揮発性半導体記憶装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−69947(P2013−69947A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−208366(P2011−208366)

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]