不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

【発明の詳細な説明】

【技術分野】

【0001】

実施形態は、不揮発性半導体記憶装置及びその製造方法に関する。

【背景技術】

【0002】

不揮発性半導体メモリの高集積化、大容量化を進めるためには、デザインルールを縮小することが必要となる。このデザインルールを縮小するためには、配線パターン等の更なる微細加工が必要となる。しかし、そのためには、非常に高度な加工技術が要求されるため、結果としてデザインルールの縮小化が困難になってきている。

【0003】

そこで、近年、メモリセルの集積度を高めるために、3次元構造を有する不揮発性半導体メモリが提案されている。

【0004】

このようなメモリの一つとして、半導体基板上に積み重ねられる複数の半導体層を、直列接続される複数のメモリセル(セルトランジスタ)を備えるメモリストリングのチャネルとして用い、かつ、各メモリセルが、データを記憶するための電荷蓄積層を備える垂直ゲート型3次元積層のVLB (Vertical gate ladder-Bit cost scalable memory)と呼ばれる不揮発性半導体メモリが知られている。

【0005】

また、VLBは、電荷蓄積層が電気的にフローティング状態の導電層(フローティングゲート)であるVG-FG型 (Vertical gate-Floating gate type)と、電荷蓄積層が電荷をトラップする絶縁層であるVG-SONOS型 (Vertical gate-Si/Oxide/Nitride/Oxide/Si type)とに分類される。

【0006】

VG-FG型では、フローティングゲートに一定の厚さが必要であるため、メモリストリングのシュリンクに限界がある。これに対し、VG-SONOS型では、電荷蓄積層を薄膜化できるため、理論的には、VG-FG型に比べて、メモリストリングのシュリンクを推し進めることができる。

【0007】

しかし、VG-SONOS型においても、VG-FG型と同様に、1つのメモリセルの電荷蓄積層内の電荷がそれに隣接する他のメモリセルの電荷蓄積層内へ移動することを防止するため、メモリセルごとに電荷蓄積層を分断する必要がある。

【0008】

この電荷蓄積層の分断は、メモリストリングのシュリンクの進行や、メモリストリングの積層数の増加などにより困難になる。特に、1つのメモリストリング内の直列接続される複数のメモリセルの電荷蓄積層は、複数の半導体層が積み重ねられる方向に延びるコントロールゲートを加工するときに同時に分断されるが、この時に電荷蓄積層の分断不良が発生し易い。

【0009】

そして、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が互いに結合してしまうと、その電荷蓄積層内で電荷が移動することによりメモリ特性が悪化する。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】A. Hubert, et al, IEDM, pp.637-640, 2009

【非特許文献2】S-J Whang et al., IEDM, pp.668-670, 2010

【発明の概要】

【発明が解決しようとする課題】

【0011】

実施形態は、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が分断されていなくても、各メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制可能な技術を提案する。

【課題を解決するための手段】

【0012】

実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板の表面に垂直な第1の方向に積み重ねられ、前記半導体基板の表面に平行な第2の方向に延び、互いに絶縁される第1乃至第nの半導体層(nは2以上の自然数)と、前記第1乃至第nの半導体層をチャネルとする第1乃至第nのメモリストリングとを備え、前記第1乃至第nのメモリストリングの各々は、前記第2の方向に直列接続される複数のメモリセルを備え、前記第iのメモリストリング(iは1〜nのうちの1つ)は、前記第iの半導体層の前記第1及び第2の方向に垂直な第3の方向にある表面上に、前記複数のメモリセルに対応する、複数の電荷蓄積層及び複数のコントロールゲートを備え、前記第iのメモリストリング内において、少なくとも前記第2の方向に隣接する2つのメモリセルの電荷蓄積層が互いに結合され、前記複数のコントロールゲート間に添加され、前記複数の電荷蓄積層のバンドオフセットを上昇させる金属元素をさらに備える。

【図面の簡単な説明】

【0013】

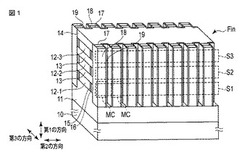

【図1】不揮発性半導体記憶装置を示す斜視図。

【図2】不揮発性半導体記憶装置を示す平面図。

【図3】メモリセルを示す断面図。

【図4】メモリセルを示す断面図。

【図5】メモリセルを示す断面図。

【図6】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図7】不揮発性半導体記憶装置の製造方法を示す断面図。

【図8】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図9】不揮発性半導体記憶装置の製造方法を示す断面図。

【図10】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図11】不揮発性半導体記憶装置の製造方法を示す断面図。

【図12】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図13】不揮発性半導体記憶装置の製造方法を示す断面図。

【図14】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図15】不揮発性半導体記憶装置の製造方法を示す断面図。

【図16】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図17】不揮発性半導体記憶装置の製造方法を示す断面図。

【図18】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図19】不揮発性半導体記憶装置の製造方法を示す断面図。

【図20】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図21】不揮発性半導体記憶装置の製造方法を示す断面図。

【図22】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図23】図22のXXIII−XXIII線に沿う断面図。

【図24】図22のXXIV−XXIV線に沿う断面図。

【図25】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図26】図25のXXVI−XXVI線に沿う断面図。

【図27】図25のXXVII−XXVII線に沿う断面図。

【図28】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図29】図28のXXIX−XXIX線に沿う断面図。

【図30】図28のXXX−XXX線に沿う断面図。

【図31】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図32】図31のXXXII−XXXII線に沿う断面図。

【図33】図31のXXXIII−XXXIII線に沿う断面図。

【図34】適用例としてのVLBを示す斜視図。

【図35】図34のXXXV−XXXV線に沿う断面図。

【図36】適用例としてのVLBを示す平面図。

【図37】適用例としてのVLBを示す平面図。

【図38】適用例としてのVLBを示す平面図。

【図39】適用例としてのVLBを示す平面図。

【発明を実施するための形態】

【0014】

以下、図面を参照しながら実施形態を説明する。尚、実施形態を通して共通の構成には同一の符号を付すものとし、重複する説明は省略する。また、各図は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置と異なる個所があるが、これらは以下の説明と公知の技術を参酌して適宜、設計変更することができる。

【0015】

以下の実施形態は、半導体基板上に積み重ねられる複数の半導体層を、直列接続される複数のメモリセル(セルトランジスタ)を備えるメモリストリングのチャネルとして用い、かつ、各メモリセルが、データを記憶するための電荷蓄積層を備える不揮発性半導体メモリにおいて、1つのメモリストリング内の複数のメモリセル間(複数のコントロールゲート間)に、電荷蓄積層のバンドオフセットを上昇させる金属元素を添加した点に特徴を有する。

【0016】

このような3次元不揮発性半導体メモリでは、1つのメモリストリング内の1つのメモリセルの電荷蓄積層内の電荷がそれに隣接する他のメモリセルの電荷蓄積層内へ移動することを防止するため、メモリセルごとに電荷蓄積層を分断する必要がある。しかし、メモリストリングのシュリンクの進行や、メモリストリングの積層数の増加などにより、この分断が困難になってきている。

【0017】

そこで、以下の実施形態では、1つのメモリストリング内の複数のメモリセル間(複数のコントロールゲート間)に、複数のメモリセルの電荷蓄積層側が負又は正に帯電するようなダイポールを形成する金属元素を添加する。これにより、その金属元素が接触する電荷蓄積層のバンドオフセットを上昇させることができるため、各メモリセルの電荷蓄積層内での電荷の移動を抑制することができる。

【0018】

例えば、電荷蓄積層側が負に帯電するようなダイポールを形成すれば、各メモリセルの電荷蓄積層内での電子の移動を抑制することができる。

【0019】

従って、メモリ特性の向上による高信頼性を実現できる。

【0020】

このように、実施形態によれば、各メモリセルの電荷蓄積層内での電荷の移動を抑制する、即ち、電荷の横方向(メモリストリングが延びる方向)の移動を防止できるため、例えば、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が分断されていなくても、所望のメモリ特性を得ることができる。

【0021】

尚、この効果は、特に、消去特性の改善のために、電荷蓄積層として、More-Si-Rich Nitride (MSRN)、即ち、Siの組成比がNの組成比よりも多いSixNy(x>y)を用いた場合に顕著に現われる。

【0022】

また、実施形態は、複数のメモリセルの電荷蓄積層を分断することを前提にしたときの分断不良の対策に有効であるが、電荷蓄積層の分断不良が発生していない、即ち、複数のメモリセルの電荷蓄積層が完全に分断されている場合に、上述の金属元素が添加されていても何ら問題ない。

【0023】

さらに、実施形態によれば、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が互いに結合されていても問題ないため、複数のメモリセルの電荷蓄積層を分断することを前提としなくても、所望のメモリ特性を得ることができる。

【0024】

本実施形態は、電荷蓄積層が電気的にフローティング状態の導電層(フローティングゲート)であるVG-FG型、及び、電荷蓄積層が電荷をトラップする絶縁層であるVG-SONOS型の双方に適用可能である。但し、スケーリングや加工精度などを考慮すると、本実施形態をVG-SONOS型に適用した不揮発性半導体メモリのほうが実用化に適している。

【0025】

[構造]

図1及び図2は、実施形態に係わる不揮発性半導体記憶装置を示している。

【0026】

半導体基板10は、例えば、シリコン基板である。絶縁層11は、例えば、BOX (Buried oxide)と呼ばれる酸化シリコン層であり、素子分離絶縁層として用いられる。

【0027】

絶縁層11上には、半導体基板10の表面に垂直な第1の方向に積み重ねられ、半導体基板10の表面に平行な第2の方向に延び、互いに絶縁される第1、第2及び第3の半導体層12−1,12−2,12−3が配置される。

【0028】

本例では、3つの半導体層が積層された構造を示すが、これに限定されるものではなく、2つ以上の半導体層が積み重ねられていればよい。また、積み重ねられる半導体層の数が多いほど、半導体メモリとしてのメモリ容量が大きくなるため、望ましい。

【0029】

第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層(例えば、酸化シリコン層)13により互いに絶縁される。但し、第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13以外の他の手段(例えば、キャビティ)により絶縁されていてもよい。

【0030】

最上層の第3の半導体層12−3上には、絶縁層(例えば、酸化シリコン層、窒化シリコン層又はこれらの積層)14が配置される。

【0031】

第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14は、フィン型積層構造Finを構成する。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶状態であるのが望ましいが、多結晶状態、アモルファス状態であっても構わない。

【0032】

第1、第2及び第3のメモリストリングS1,S2,S3は、それぞれ、第1、第2及び第3の半導体層12−1,12−2,12−3をチャネルとする。第1、第2及び第3のメモリストリングS1,S2,S3の各々は、第2の方向に直列接続される複数のメモリセルMCを備える。

【0033】

第1、第2及び第3のメモリストリングS1,S2,S3は、それぞれ、第1、第2及び第3の半導体層12−1,12−2,12−3の第1及び第2の方向に垂直な第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。

【0034】

第1、第2及び第3の半導体層12−1,12−2,12−3と複数の電荷蓄積層16との間には、トンネル絶縁層(ゲート絶縁層)15が配置され、複数の電荷蓄積層16と複数のコントロールゲート18との間には、書き込み/消去時のリーク電流を防止するブロック絶縁層17が配置される。

【0035】

複数のコントロールゲート18は、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面に沿って、第1の方向に延びる。

【0036】

本例では、3つの半導体層に対応して3つのメモリストリングが積層された構造を示すが、これに限定されるものではなく、2つ以上の半導体層に対応して2つ以上のメモリストリングが積み重ねられていればよい。

【0037】

そして、複数のコントロールゲート18間、具体的には、少なくとも、コントロールゲートの加工後の複数のメモリセルMCの電荷蓄積層16の剥き出しになった表面と層間絶縁層20との界面には、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。この金属元素19は、例えば、複数のメモリセルMCの電荷蓄積層16側が負に帯電するようなダイポールを形成する。

【0038】

金属元素19は、例えば、Ge, Y, Sr, ランタノイド(La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu)のグループから選択される1つの元素を含む。

【0039】

また、金属元素19は、1つの層を構成していてもよいし、1つの層を構成しない状態(例えば、金属元素がドット状又は部分的に添加されているような状態)でもよい。

【0040】

金属元素19が1つの層を構成する場合、その1つの層は、金属元素19を含む酸化物、窒化物又は酸窒化物を備える。例えば、複数のメモリセルMCの電荷蓄積層16が窒化シリコン層を備えるときは、金属元素19は、La2O3を含む材料のLaとすることにより、電荷蓄積層16側が負に帯電するようなダイポールを形成することができる。

【0041】

これにより、複数のメモリセルMCの電荷蓄積層16内での電荷の横方向(第1、第2及び第3のメモリストリングS1,S2,S3が延びる方向)の電荷の移動を抑制することができる。この効果は、複数のコントロールゲート18間において、金属元素19を含む1つの層の第3の方向の厚さ(図3のt1に相当)が1 nm以下である場合に顕著である。また、この場合、金属元素19が高誘電率を持ついわゆるHigh-k材料であるときに、それによるセル間干渉の影響を最小限に抑えるという効果も奏する。

【0042】

以上のような構造によれば、第1、第2及び第3のメモリストリングS1,S2,S3の各々において、複数のメモリセルMCの電荷蓄積層16が互いに結合され、第2の方向に延びる1つの層を構成していても、電荷の横方向の移動を抑制できる。

【0043】

例えば、図3は、図2の領域Xを示している。この図は、複数のメモリセルMCの電荷蓄積層16を分断することを前提にしたときに、電荷蓄積層16の分断不良が発生した状況を示している。この場合、電荷蓄積層16としての1つの層は、複数のコントロールゲート18間の第3の方向の厚さt1が、それ以外の第3の方向の厚さt2よりも薄くなるのが一般的である。

【0044】

但し、図4に示すように、複数のメモリセルMCの電荷蓄積層16を分断することを前提にしたときに、電荷蓄積層16の分断不良が発生していない、即ち、複数のメモリセルMCの電荷蓄積層16が完全に分断されている場合に、上述の金属元素19が添加されていても何ら問題ない。

【0045】

さらに、図5に示すように、1つのメモリストリング内の複数のメモリセルMCの電荷蓄積層16が互いに結合されていても問題ないため、複数のメモリセルMCの電荷蓄積層16を分断することを前提としなくてもよい。この場合、電荷蓄積層16としての1つの層の第3の方向の厚さは、概ね均一になる。

【0046】

上述の不揮発性半導体記憶装置の各要素を構成する材料については、半導体メモリの各世代に応じた最適な材料を適宜選択することができるが、以下では、最もよく使用される材料例を説明する。

【0047】

半導体基板10は、例えば、単結晶シリコン基板である。また、絶縁層11,13は、例えば、酸化シリコン層である。

【0048】

第1、第2及び第3の半導体層12−1,12−2,12−3は、それぞれ、例えば、シリコン(Si)層である。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶であるのが望ましいが、アモルファス又は多結晶であっても構わない。

【0049】

フィン型積層構造Finを構成する最上層の絶縁層14は、例えば、酸化シリコン(SiO2)、窒化シリコン(SiN)、又は、それらが積み重ねられた構造を有する。

【0050】

メモリセルMCを構成するトンネル絶縁層(ゲート絶縁層)15は、例えば、酸化シリコン層である。トンネル絶縁層15は、酸窒化シリコン、酸化シリコンと窒化シリコンとの積層構造などであってもよい。また、トンネル絶縁層15は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。

【0051】

メモリセルMCを構成する電荷蓄積層16が、例えば、窒化シリコン層であり、複数のコントロールゲート18間を満たす層間絶縁層がTEOS(TetraEthOxySilane)であるとき、電荷蓄積層19側のバンドオフセットを高くするための金属元素19を含む1つの材料としては、La2O3層を用いることができる。La2O3層は、1 nm以下の厚さとするのが望ましい。これを超える厚さにすると、セル間干渉が大きくなる懸念が発生するからである。

【0052】

複数のコントロールゲート18間を満たす層間絶縁層としては、比誘電率3.9を有する酸化シリコン層と同程度の誘電率を有する材料とするのが望ましい。ここでは、層間絶縁層の例としてTEOSを掲げたが、例えば、熱処理によりポリシラザン系溶剤を焼成することにより形成される酸化シリコン層でもよい。

【0053】

また、電荷蓄積層16が窒化シリコン層でない場合や、層間絶縁層が酸化シリコン層でない場合などにおいても、既に説明した金属元素19の例のなかから適切な材料を選択することにより、金属元素19が接触する電荷蓄積層16のバンドオフセットを上昇させ、電荷蓄積層16内の電荷の横方向の移動を抑制することが可能である。

【0054】

尚、メモリセルMCを構成する電荷蓄積層16は、例えば、シリコンリッチSiN、シリコンと窒素の組成比x、yが任意であるSixNy、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)及びランタン・アルミネート(LaAlO3)のグループから選択することができる。

【0055】

また、電荷蓄積層16は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。電荷蓄積層16は、不純物が添加されたポリシリコン、メタルなどの導電体を備えることにより、フローティングゲートとして機能させてもよい。

【0056】

メモリセルMCを構成するブロック絶縁層17は、例えば、書き込み/消去時のリーク電流を防止する機能を有する。ブロック絶縁層17は、例えば、酸化シリコン(SiO2)、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)、ランタン・アルミネート(LaAlO3)及びランタンアルミシリケート(LaAlSiO)のグループから選択することができる。

【0057】

メモリセルMCを構成するコントロールゲート18は、例えば、導電性ポリシリコン層及び珪化ニッケル(NiSi)などの金属シリサイド層のうちの1つを備える。

【0058】

コントロールゲート18は、例えば、タンタルナイトライド(TaN)、タンタルカーバイト(TaC)、チタンナイトライド(TiN)などの金属化合物、又は、金属的な電気伝導特性を示す、Ni、V、Cr、Mn、Y、Mo、Ru、Rh、Hf、Ta、W,Ir、Co、Ti、Er、Pt、Pd、Zr、Gd、Dy、Ho、Er、及び、これらのシリサイドであってもよい。

【0059】

[製造方法]

図6乃至図33は、図1及び図2の半導体装置の製造方法を示している。

【0060】

まず、図6及び図7に示すように、半導体基板10として、例えば、面方位(100)、比抵抗10〜20Ωcmのp型又はn型のシリコン基板を用意する。この半導体基板10上に、絶縁層11,13,14としての酸化シリコン層と、第1、第2及び第3の半導体層12−1,12−2,12−3としての多結晶シリコン層とを、交互に形成する。続けて、絶縁層14上にマスク層(例えば、窒化シリコン層)21を形成する。

【0061】

また、PEP(Photo Engraving Process)により、マスク層21上にレジストパターンを形成する。そして、レジストパターンをマスクにして、RIE(Reactive Ion Etching)により、マスク層21、絶縁層14、第3の半導体層12−3、絶縁層13、第2の半導体層12−2、絶縁層13及び第1の半導体層12−1を、順次、エッチングする。

【0062】

これにより、フィン型積層構造Finが形成される。この後、レジストパターンは除去される。

【0063】

次に、図8及び図9に示すように、例えば、コリンを用いるウェットエッチング、CDE(Chemical Dry Etching)、又は、塩素ガスを用いるドライエッチングにより、フィン型積層構造Finを構成する第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面をリセスエッチングする。その結果、フィン型積層構造Finの第3の方向にある表面に凹部が形成される。

【0064】

次に、図10及び図11に示すように、例えば、SPA(Slot Plane Antenna)プラズマ生成技術により、フィン型積層構造Finの第3の方向にある凹部内、即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面上に、トンネル絶縁層(例えば、酸化シリコン層)15を形成する。

【0065】

次に、図12及び図13に示すように、例えば、CVDにより、フィン型積層構造Finの表面の全体を覆う電荷蓄積層(例えば、窒化シリコン層)16を形成する。

【0066】

次に、図14及び図15に示すように、例えば、RIEにより、フィン型積層構造Finの第3の方向にある凹部内に存在する電荷蓄積層16を除き、他の部分に存在する電荷蓄積層16を除去する。その結果、電荷蓄積層16は、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面上のトンネル絶縁層15上のみに残存する。

【0067】

また、この時、電荷蓄積層16は、第1の方向に複数の部分に分断され、各部分は、メモリストリングのチャネルとして機能する1つの半導体層12−i(iは1〜3のうちの1つ)に沿って第2の方向に延びる1つの層を構成する。

【0068】

次に、図16及び図17に示すように、例えば、等方性エッチングにより、マスク層21をエッチングし、マスク層21の第3の方向の幅をシュリンクする。

【0069】

この工程は、後述するコントロールゲートのパターニング時に、1つのメモリストリング内の電荷蓄積層(第2の方向に延びる1つの層)を、メモリセル毎に互いに分断することを目的に実行される。

【0070】

従って、1つのメモリストリング内の電荷蓄積層をメモリセル毎に互いに分断しないことを前提とする場合には、この工程は省略できる。

【0071】

この工程によるマスク層21のシュリンク量dとしては、コントロールゲートのパターニング時に、1つのメモリストリング内の電荷蓄積層がメモリセル毎に互いに分断されるに十分な量(理論値)とする。

【0072】

具体的には、シュリンク後のマスク層21の第3の方向の端部は、第1、第2及び第3の半導体層12−1,12−2,12−3とトンネル絶縁層15の界面より外側に配置する。より望ましくは、シュリンク後のマスク層21の第3の方向の端部は、第1、第2及び第3の半導体層12−1,12−2,12−3とトンネル絶縁層15の界面より外側かつトンネル絶縁膜15と電荷蓄積層16の界面よりも内側に配置するのが良い。

【0073】

ここで、マスク層21のシュリンク量dのばらつきが、1つのメモリストリング内の電荷蓄積層の分断不良の一因となる。

【0074】

次に、図18及び図19に示すように、例えば、CVDにより、フィン型積層構造Finの表面の全体を覆うブロック絶縁層(例えば、Al2O3層)17を形成する。

【0075】

次に、図20及び図21に示すように、フィン型積層構造Finを覆い、かつ、フィン型積層構造Fin間のスペースを完全に満たすコントロールゲート(例えば、ポリシリコン層)18を形成する。

【0076】

次に、図22乃至図24に示すように、PEPにより、コントロールゲート18上にレジストパターンを形成し、このレジストパターンをマスクにして、RIEにより、コントロールゲート18をパターニングする。

【0077】

ここで、コントロールゲート18は、パターニング前に、CMP(Chemical Mechanical Polishing)により、その上面(第1の方向の表面)を平坦化してもよい。この場合、コントロールゲート18上に酸化シリコン層などの絶縁層を形成した後に、CMPを実行するのが望ましい。

【0078】

また、レジストパターンは、コントロールゲート18の上面において、第3の方向に延びるライン&スペースパターンを有する。

【0079】

レジストパターンにより覆われていない部分に存在するコントロールゲート18及びブロック絶縁層17は、完全に除去される。同時に、レジストパターンにより覆われていない部分に存在する電荷蓄積層16も、除去される。

【0080】

このRIEでは、レジストパターンとシュリンクされたマスク層21とにより覆われていない部分が積極的に除去されるため、理論的には、レジストパターンにより覆われていない部分に存在する電荷蓄積層16も、除去される。

【0081】

しかし、既に述べたように、マスク層21のシュリンク量のばらつき等により、電荷蓄積層16の分断不良が発生する場合がある。

【0082】

そこで、電荷蓄積層16の分断不良が発生している例を、図25乃至図27に示す。この例によれば、1つのメモリストリング内の電荷蓄積層16が、メモリセル毎に完全に分断されずに、第2の方向に延びる1つの層として残存している。

【0083】

このパターニングにより、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面に沿って第1の方向に延びるライン&スペースパターンの複数のコントロールゲート18が形成される。

【0084】

また、フィン型積層構造Finを第1の方向から見たときは、複数のコントロールゲート18は、レジストパターンと同様に、全体として、第3の方向に延びる。

【0085】

このパターニング後、レジストパターンは除去される。

【0086】

次に、図28乃至図30に示すように、複数のコントロールゲート18間、具体的には、複数のコントロールゲート18の加工後の複数の電荷蓄積層16の剥き出しになった表面上、及び、複数のコントロールゲート18の表面上に、それぞれ、金属元素19又はその金属元素19を含む化合物(酸化物、窒化物又は酸窒化物)を添加する。

【0087】

ここで、金属元素19単体を添加するときは、イオン注入法を用い、金属元素19を含む化合物を添加するときは、LPCVD法やALD法などのコンフォーマルな堆積プロセスを用いればよい。

【0088】

尚、金属元素19又はその化合物は、1つの層を構成する必要はないが、金属元素19又はその化合物が1つの層を構成するときは、その厚さは、1 nm以下に設定するのが望ましい。

【0089】

また、金属元素19又はその化合物は、電荷蓄積層16と、後述する層間絶縁層との界面に添加されることにより、電荷蓄積層16のバンドオフセットを上昇させる。

【0090】

最後に、図31乃至図33に示すように、複数のコントロールゲート18間に、層間絶縁層(例えば、SiO2)20を満たす。層間絶縁層20は、フィン型積層構造Finの間のスペースも完全に満たす。

【0091】

以上の工程により、図1及び図2の不揮発性半導体記憶装置を形成できる。

【0092】

尚、この装置を、VLBなどの3次元不揮発性半導体メモリとして使用する場合には、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択するための選択機能が必要になるが、その選択機能については、階段構造や、レイヤー選択トランジスタなどが既に提案済みであるので、ここでの説明を省略する。

【0093】

[適用例]

実施形態に係わる不揮発性半導体記憶装置の適用例を説明する。

【0094】

尚、以下の適用例においては、上述の図1乃至図2の不揮発性半導体記憶装置と同じ要素に同じ符号を付すことによりその詳細な説明を省略する。

【0095】

図34は、第1の適用例としてのVLBを示している。図35は、図34のXXXV−XXXV線に沿う断面図を示している。

【0096】

この適用例は、半導体基板10上に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3の選択を、階段形状により行う場合を示している。

【0097】

第1、第2及び第3の半導体層12−1,12−2,12−3を備えるフィン型積層構造Finの第2の方向の両端は、それぞれ、梁22に接続される。梁22は、第3の方向に延びることにより、フィン型積層構造Finの倒壊を防止する機能を発揮する。

【0098】

梁22は、フィン型積層構造Finと同様に、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層11,13,14を備える。梁22の第3の方向の一端は、階段形状を有する。この階段形状により、コンタクトプラグ23は、それぞれ独立に、第1、第2及び第3の半導体層12−1,12−2,12−3に接続可能である。

【0099】

梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅と同じであっても、異なっていてもよい。但し、梁22における配線抵抗を下げる目的及びフィン型積層構造Finの倒壊を防止する目的から、梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅よりも広いのが望ましい。

【0100】

尚、コンタクトプラグ23は、例えば、W、Alなどの金属材料を備える。コンタクトプラグ23には、ビット線又はソース線が接続される。

【0101】

図36は、第iの半導体層(iは1〜3のうちの1つ)12−iを、半導体基板10の表面に平行な面で切り取った図である。また、図37は、絶縁層13,14を、半導体基板10の表面に平行な面で切り取った図である。

【0102】

これらの図によれば、複数のフィン型積層構造Finを並べる場合、複数のコントロールゲート18のパターニング後において、複数のコントロールゲート18間には、トレンチが形成されることが分かる。この場合、金属元素19又はその化合物は、そのトレンチの内面に添加される。また、金属元素19又はその化合物を添加した後、トレンチは、層間絶縁層20により満たされる。

【0103】

即ち、金属元素19及びその化合物は、複数のコントロールゲート18間に存在する電荷蓄積層16の第3の方向の表面上、及び、複数のコントロールゲート18の第2の方向の表面上に、それぞれ添加される。

【0104】

図38は、フィン型積層構造Finを第1の方向から見たときの複数のコントロールゲート18のパターンを示している。

【0105】

複数のコントロールゲート18は、ライン&スペースパターンを有し、全体として、第3の方向に延びる。但し、フィン型積層構造Fin間においては、複数のコントロールゲート18は、フィン型積層構造Finの第3の方向にある表面に沿って第1の方向(紙面に垂直な方向)に延びる。

【0106】

図39は、第2の適用例としてのVLBを示している。

【0107】

この適用例は、半導体基板10上に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3の選択を、第1、第2及び第3のレイヤー選択トランジスタにより行う場合を示している。

【0108】

第1、第2及び第3の半導体層12−1,12−2,12−3を備えるフィン型積層構造Finの第2の方向の両端は、それぞれ、梁22に接続される。梁22は、第3の方向に延びることにより、フィン型積層構造Finの倒壊を防止する機能を発揮する。

【0109】

梁22は、フィン型積層構造Finと同様に、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層11,13,14を備える。梁22の第3の方向の一端には、第1、第2及び第3のレイヤー選択トランジスタLSTが配置される。

【0110】

第1、第2及び第3のレイヤー選択トランジスタLSTは、例えば、FET (Field Effect Transistor)であり、第1、第2及び第3の半導体層12−1,12−2,12−3をチャネルとし、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する。

【0111】

第1、第2及び第3のレイヤー選択トランジスタLSTは、第3の方向に並んで配置され、かつ、コンタクトプラグ(共通電極)23側から順番に、一定ピッチPで配置される第1、第2及び第3のゲート電極24−1,24−2,24−3を有する。第1、第2及び第3のゲート電極24−1,24−2,24−3は、例えば、導電性ポリシリコン層、ニッケルシリサイド層などの金属シリサイド層、又は、これらの積層を備える。

【0112】

第1、第2及び第3のゲート電極24−1,24−2,24−3は、少なくとも、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面に沿って第1の方向に延びる。

【0113】

本例では、第1、第2及び第3のゲート電極24−1,24−2,24−3は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面を覆う。即ち、レイヤー選択トランジスタLSTは、ダブルゲート構造を有する。

【0114】

また、第1のゲート電極24−1を備える第1のレイヤー選択トランジスタLSTは、第1の半導体層12−1内にノーマリーオンチャネルを有する。即ち、第1のゲート電極24−1を備える第1のレイヤー選択トランジスタLSTは、第1の半導体層12−1内でノーマリーオン、第2及び第3の半導体層12−2,12−3内でオン/オフ制御可能である。

【0115】

第2のゲート電極24−2を備える第2のレイヤー選択トランジスタLSTは、第2の半導体層12−2内にノーマリーオンチャネルを有する。即ち、第2のゲート電極24−2を備える第2のレイヤー選択トランジスタLSTは、第2の半導体層12−2内でノーマリーオン、第1及び第3の半導体層12−1,12−3内でオン/オフ制御可能である。

【0116】

第3のゲート電極24−3を備える第3のレイヤー選択トランジスタLSTは、第3の半導体層12−3内にノーマリーオンチャネルを有する。即ち、第3のゲート電極24−3を備える第3のレイヤー選択トランジスタLSTは、第3の半導体層12−3内でノーマリーオン、第1及び第2の半導体層12−1,12−2内でオン/オフ制御可能である。

【0117】

一般化すると、第1乃至第nの半導体層(nは、2以上の自然数)12−1〜12−nをチャネルとする第1乃至第nのレイヤー選択トランジスタLSTのうち、第iのレイヤー選択トランジスタ(iは1〜nのうちの1つ)は、第iの半導体層においてノーマリーオン、それ以外の半導体層においてオン/オフ制御可能である。

【0118】

尚、第1、第2及び第3の半導体層12−1,12−2,12−3内のノーマリーオンチャネルは、n型不純物(砒素、リンなどの5価元素)、p型不純物(硼素、インジウムなどの3価元素)、又は、それらの両方を含む不純物領域により形成可能である。

【0119】

以上の第1、第2及び第3のレイヤー選択トランジスタLSTにより、コンタクトプラグ23を、第1、第2及び第3の半導体層12−1,12−2,12−3に共通の共通電極とすることが可能である。即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の各々に対して、個別にコンタクトプラグを設ける必要がないため、コンタクト領域のサイズを縮小可能である。

【0120】

尚、梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅と同じであっても、異なっていてもよい。但し、梁22における配線抵抗を下げる目的及びフィン型積層構造Finの倒壊を防止する目的から、梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅よりも広いのが望ましい。

【0121】

また、コンタクトプラグ(共通電極)23は、例えば、W、Alなどの金属材料を備える。コンタクトプラグ23には、ビット線又はソース線が接続される。

【0122】

[その他]

本実施形態は、電荷蓄積層が電気的にフローティング状態の導電層(フローティングゲート)であるVG-FG型にも適用可能である。

【0123】

例えば、電荷蓄積層としてのフローティングゲートの加工面が加工中に形成された自然酸化膜(SiO2)により覆われているときは、電荷蓄積層側を負に帯電させ、電荷蓄積層側のバンドオフセットを上昇させ、電荷蓄積層内の電子の動きを抑制するダイポールを形成可能な金属元素又はその化合物を十分な厚さで形成すればよい。

【0124】

また、電荷蓄積層としてのフローティングゲートの加工面が剥き出しになっているときは、電荷蓄積層側を負に帯電させ、電荷蓄積層側のバンドオフセットを上昇させ、電荷蓄積層内の電子の動きを抑制するダイポールを形成可能な金属元素又はその化合物を 1 nm以下の非常に薄い厚さで形成すればよい。

【0125】

この場合においても、金属元素は、例えば、Ge, Y, Sr, ランタノイド(La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu)のグループから選択可能である。

【0126】

[むすび]

実施形態によれば、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が分断されていなくても、各メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制できる。

【0127】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0128】

10: 半導体基板、 11,13,14: 絶縁層、 12−1,12−2,12−3: 半導体層、 15: トンネル絶縁層(ゲート絶縁層)、 16: 電荷蓄積層、 17: ブロック絶縁層、 18: コントロールゲート、 19: 金属元素、 20: 層間絶縁層、 21: マスク層、 22: 梁、 23: コンタクトプラグ、 24−1,24−2,24−3: ゲート電極、 S1,S2,S3: メモリストリング、 MC: メモリセル、 LST: レイヤー選択トランジスタ。

【技術分野】

【0001】

実施形態は、不揮発性半導体記憶装置及びその製造方法に関する。

【背景技術】

【0002】

不揮発性半導体メモリの高集積化、大容量化を進めるためには、デザインルールを縮小することが必要となる。このデザインルールを縮小するためには、配線パターン等の更なる微細加工が必要となる。しかし、そのためには、非常に高度な加工技術が要求されるため、結果としてデザインルールの縮小化が困難になってきている。

【0003】

そこで、近年、メモリセルの集積度を高めるために、3次元構造を有する不揮発性半導体メモリが提案されている。

【0004】

このようなメモリの一つとして、半導体基板上に積み重ねられる複数の半導体層を、直列接続される複数のメモリセル(セルトランジスタ)を備えるメモリストリングのチャネルとして用い、かつ、各メモリセルが、データを記憶するための電荷蓄積層を備える垂直ゲート型3次元積層のVLB (Vertical gate ladder-Bit cost scalable memory)と呼ばれる不揮発性半導体メモリが知られている。

【0005】

また、VLBは、電荷蓄積層が電気的にフローティング状態の導電層(フローティングゲート)であるVG-FG型 (Vertical gate-Floating gate type)と、電荷蓄積層が電荷をトラップする絶縁層であるVG-SONOS型 (Vertical gate-Si/Oxide/Nitride/Oxide/Si type)とに分類される。

【0006】

VG-FG型では、フローティングゲートに一定の厚さが必要であるため、メモリストリングのシュリンクに限界がある。これに対し、VG-SONOS型では、電荷蓄積層を薄膜化できるため、理論的には、VG-FG型に比べて、メモリストリングのシュリンクを推し進めることができる。

【0007】

しかし、VG-SONOS型においても、VG-FG型と同様に、1つのメモリセルの電荷蓄積層内の電荷がそれに隣接する他のメモリセルの電荷蓄積層内へ移動することを防止するため、メモリセルごとに電荷蓄積層を分断する必要がある。

【0008】

この電荷蓄積層の分断は、メモリストリングのシュリンクの進行や、メモリストリングの積層数の増加などにより困難になる。特に、1つのメモリストリング内の直列接続される複数のメモリセルの電荷蓄積層は、複数の半導体層が積み重ねられる方向に延びるコントロールゲートを加工するときに同時に分断されるが、この時に電荷蓄積層の分断不良が発生し易い。

【0009】

そして、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が互いに結合してしまうと、その電荷蓄積層内で電荷が移動することによりメモリ特性が悪化する。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】A. Hubert, et al, IEDM, pp.637-640, 2009

【非特許文献2】S-J Whang et al., IEDM, pp.668-670, 2010

【発明の概要】

【発明が解決しようとする課題】

【0011】

実施形態は、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が分断されていなくても、各メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制可能な技術を提案する。

【課題を解決するための手段】

【0012】

実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板の表面に垂直な第1の方向に積み重ねられ、前記半導体基板の表面に平行な第2の方向に延び、互いに絶縁される第1乃至第nの半導体層(nは2以上の自然数)と、前記第1乃至第nの半導体層をチャネルとする第1乃至第nのメモリストリングとを備え、前記第1乃至第nのメモリストリングの各々は、前記第2の方向に直列接続される複数のメモリセルを備え、前記第iのメモリストリング(iは1〜nのうちの1つ)は、前記第iの半導体層の前記第1及び第2の方向に垂直な第3の方向にある表面上に、前記複数のメモリセルに対応する、複数の電荷蓄積層及び複数のコントロールゲートを備え、前記第iのメモリストリング内において、少なくとも前記第2の方向に隣接する2つのメモリセルの電荷蓄積層が互いに結合され、前記複数のコントロールゲート間に添加され、前記複数の電荷蓄積層のバンドオフセットを上昇させる金属元素をさらに備える。

【図面の簡単な説明】

【0013】

【図1】不揮発性半導体記憶装置を示す斜視図。

【図2】不揮発性半導体記憶装置を示す平面図。

【図3】メモリセルを示す断面図。

【図4】メモリセルを示す断面図。

【図5】メモリセルを示す断面図。

【図6】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図7】不揮発性半導体記憶装置の製造方法を示す断面図。

【図8】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図9】不揮発性半導体記憶装置の製造方法を示す断面図。

【図10】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図11】不揮発性半導体記憶装置の製造方法を示す断面図。

【図12】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図13】不揮発性半導体記憶装置の製造方法を示す断面図。

【図14】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図15】不揮発性半導体記憶装置の製造方法を示す断面図。

【図16】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図17】不揮発性半導体記憶装置の製造方法を示す断面図。

【図18】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図19】不揮発性半導体記憶装置の製造方法を示す断面図。

【図20】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図21】不揮発性半導体記憶装置の製造方法を示す断面図。

【図22】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図23】図22のXXIII−XXIII線に沿う断面図。

【図24】図22のXXIV−XXIV線に沿う断面図。

【図25】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図26】図25のXXVI−XXVI線に沿う断面図。

【図27】図25のXXVII−XXVII線に沿う断面図。

【図28】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図29】図28のXXIX−XXIX線に沿う断面図。

【図30】図28のXXX−XXX線に沿う断面図。

【図31】不揮発性半導体記憶装置の製造方法を示す斜視図。

【図32】図31のXXXII−XXXII線に沿う断面図。

【図33】図31のXXXIII−XXXIII線に沿う断面図。

【図34】適用例としてのVLBを示す斜視図。

【図35】図34のXXXV−XXXV線に沿う断面図。

【図36】適用例としてのVLBを示す平面図。

【図37】適用例としてのVLBを示す平面図。

【図38】適用例としてのVLBを示す平面図。

【図39】適用例としてのVLBを示す平面図。

【発明を実施するための形態】

【0014】

以下、図面を参照しながら実施形態を説明する。尚、実施形態を通して共通の構成には同一の符号を付すものとし、重複する説明は省略する。また、各図は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置と異なる個所があるが、これらは以下の説明と公知の技術を参酌して適宜、設計変更することができる。

【0015】

以下の実施形態は、半導体基板上に積み重ねられる複数の半導体層を、直列接続される複数のメモリセル(セルトランジスタ)を備えるメモリストリングのチャネルとして用い、かつ、各メモリセルが、データを記憶するための電荷蓄積層を備える不揮発性半導体メモリにおいて、1つのメモリストリング内の複数のメモリセル間(複数のコントロールゲート間)に、電荷蓄積層のバンドオフセットを上昇させる金属元素を添加した点に特徴を有する。

【0016】

このような3次元不揮発性半導体メモリでは、1つのメモリストリング内の1つのメモリセルの電荷蓄積層内の電荷がそれに隣接する他のメモリセルの電荷蓄積層内へ移動することを防止するため、メモリセルごとに電荷蓄積層を分断する必要がある。しかし、メモリストリングのシュリンクの進行や、メモリストリングの積層数の増加などにより、この分断が困難になってきている。

【0017】

そこで、以下の実施形態では、1つのメモリストリング内の複数のメモリセル間(複数のコントロールゲート間)に、複数のメモリセルの電荷蓄積層側が負又は正に帯電するようなダイポールを形成する金属元素を添加する。これにより、その金属元素が接触する電荷蓄積層のバンドオフセットを上昇させることができるため、各メモリセルの電荷蓄積層内での電荷の移動を抑制することができる。

【0018】

例えば、電荷蓄積層側が負に帯電するようなダイポールを形成すれば、各メモリセルの電荷蓄積層内での電子の移動を抑制することができる。

【0019】

従って、メモリ特性の向上による高信頼性を実現できる。

【0020】

このように、実施形態によれば、各メモリセルの電荷蓄積層内での電荷の移動を抑制する、即ち、電荷の横方向(メモリストリングが延びる方向)の移動を防止できるため、例えば、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が分断されていなくても、所望のメモリ特性を得ることができる。

【0021】

尚、この効果は、特に、消去特性の改善のために、電荷蓄積層として、More-Si-Rich Nitride (MSRN)、即ち、Siの組成比がNの組成比よりも多いSixNy(x>y)を用いた場合に顕著に現われる。

【0022】

また、実施形態は、複数のメモリセルの電荷蓄積層を分断することを前提にしたときの分断不良の対策に有効であるが、電荷蓄積層の分断不良が発生していない、即ち、複数のメモリセルの電荷蓄積層が完全に分断されている場合に、上述の金属元素が添加されていても何ら問題ない。

【0023】

さらに、実施形態によれば、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が互いに結合されていても問題ないため、複数のメモリセルの電荷蓄積層を分断することを前提としなくても、所望のメモリ特性を得ることができる。

【0024】

本実施形態は、電荷蓄積層が電気的にフローティング状態の導電層(フローティングゲート)であるVG-FG型、及び、電荷蓄積層が電荷をトラップする絶縁層であるVG-SONOS型の双方に適用可能である。但し、スケーリングや加工精度などを考慮すると、本実施形態をVG-SONOS型に適用した不揮発性半導体メモリのほうが実用化に適している。

【0025】

[構造]

図1及び図2は、実施形態に係わる不揮発性半導体記憶装置を示している。

【0026】

半導体基板10は、例えば、シリコン基板である。絶縁層11は、例えば、BOX (Buried oxide)と呼ばれる酸化シリコン層であり、素子分離絶縁層として用いられる。

【0027】

絶縁層11上には、半導体基板10の表面に垂直な第1の方向に積み重ねられ、半導体基板10の表面に平行な第2の方向に延び、互いに絶縁される第1、第2及び第3の半導体層12−1,12−2,12−3が配置される。

【0028】

本例では、3つの半導体層が積層された構造を示すが、これに限定されるものではなく、2つ以上の半導体層が積み重ねられていればよい。また、積み重ねられる半導体層の数が多いほど、半導体メモリとしてのメモリ容量が大きくなるため、望ましい。

【0029】

第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層(例えば、酸化シリコン層)13により互いに絶縁される。但し、第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13以外の他の手段(例えば、キャビティ)により絶縁されていてもよい。

【0030】

最上層の第3の半導体層12−3上には、絶縁層(例えば、酸化シリコン層、窒化シリコン層又はこれらの積層)14が配置される。

【0031】

第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14は、フィン型積層構造Finを構成する。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶状態であるのが望ましいが、多結晶状態、アモルファス状態であっても構わない。

【0032】

第1、第2及び第3のメモリストリングS1,S2,S3は、それぞれ、第1、第2及び第3の半導体層12−1,12−2,12−3をチャネルとする。第1、第2及び第3のメモリストリングS1,S2,S3の各々は、第2の方向に直列接続される複数のメモリセルMCを備える。

【0033】

第1、第2及び第3のメモリストリングS1,S2,S3は、それぞれ、第1、第2及び第3の半導体層12−1,12−2,12−3の第1及び第2の方向に垂直な第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。

【0034】

第1、第2及び第3の半導体層12−1,12−2,12−3と複数の電荷蓄積層16との間には、トンネル絶縁層(ゲート絶縁層)15が配置され、複数の電荷蓄積層16と複数のコントロールゲート18との間には、書き込み/消去時のリーク電流を防止するブロック絶縁層17が配置される。

【0035】

複数のコントロールゲート18は、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面に沿って、第1の方向に延びる。

【0036】

本例では、3つの半導体層に対応して3つのメモリストリングが積層された構造を示すが、これに限定されるものではなく、2つ以上の半導体層に対応して2つ以上のメモリストリングが積み重ねられていればよい。

【0037】

そして、複数のコントロールゲート18間、具体的には、少なくとも、コントロールゲートの加工後の複数のメモリセルMCの電荷蓄積層16の剥き出しになった表面と層間絶縁層20との界面には、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。この金属元素19は、例えば、複数のメモリセルMCの電荷蓄積層16側が負に帯電するようなダイポールを形成する。

【0038】

金属元素19は、例えば、Ge, Y, Sr, ランタノイド(La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu)のグループから選択される1つの元素を含む。

【0039】

また、金属元素19は、1つの層を構成していてもよいし、1つの層を構成しない状態(例えば、金属元素がドット状又は部分的に添加されているような状態)でもよい。

【0040】

金属元素19が1つの層を構成する場合、その1つの層は、金属元素19を含む酸化物、窒化物又は酸窒化物を備える。例えば、複数のメモリセルMCの電荷蓄積層16が窒化シリコン層を備えるときは、金属元素19は、La2O3を含む材料のLaとすることにより、電荷蓄積層16側が負に帯電するようなダイポールを形成することができる。

【0041】

これにより、複数のメモリセルMCの電荷蓄積層16内での電荷の横方向(第1、第2及び第3のメモリストリングS1,S2,S3が延びる方向)の電荷の移動を抑制することができる。この効果は、複数のコントロールゲート18間において、金属元素19を含む1つの層の第3の方向の厚さ(図3のt1に相当)が1 nm以下である場合に顕著である。また、この場合、金属元素19が高誘電率を持ついわゆるHigh-k材料であるときに、それによるセル間干渉の影響を最小限に抑えるという効果も奏する。

【0042】

以上のような構造によれば、第1、第2及び第3のメモリストリングS1,S2,S3の各々において、複数のメモリセルMCの電荷蓄積層16が互いに結合され、第2の方向に延びる1つの層を構成していても、電荷の横方向の移動を抑制できる。

【0043】

例えば、図3は、図2の領域Xを示している。この図は、複数のメモリセルMCの電荷蓄積層16を分断することを前提にしたときに、電荷蓄積層16の分断不良が発生した状況を示している。この場合、電荷蓄積層16としての1つの層は、複数のコントロールゲート18間の第3の方向の厚さt1が、それ以外の第3の方向の厚さt2よりも薄くなるのが一般的である。

【0044】

但し、図4に示すように、複数のメモリセルMCの電荷蓄積層16を分断することを前提にしたときに、電荷蓄積層16の分断不良が発生していない、即ち、複数のメモリセルMCの電荷蓄積層16が完全に分断されている場合に、上述の金属元素19が添加されていても何ら問題ない。

【0045】

さらに、図5に示すように、1つのメモリストリング内の複数のメモリセルMCの電荷蓄積層16が互いに結合されていても問題ないため、複数のメモリセルMCの電荷蓄積層16を分断することを前提としなくてもよい。この場合、電荷蓄積層16としての1つの層の第3の方向の厚さは、概ね均一になる。

【0046】

上述の不揮発性半導体記憶装置の各要素を構成する材料については、半導体メモリの各世代に応じた最適な材料を適宜選択することができるが、以下では、最もよく使用される材料例を説明する。

【0047】

半導体基板10は、例えば、単結晶シリコン基板である。また、絶縁層11,13は、例えば、酸化シリコン層である。

【0048】

第1、第2及び第3の半導体層12−1,12−2,12−3は、それぞれ、例えば、シリコン(Si)層である。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶であるのが望ましいが、アモルファス又は多結晶であっても構わない。

【0049】

フィン型積層構造Finを構成する最上層の絶縁層14は、例えば、酸化シリコン(SiO2)、窒化シリコン(SiN)、又は、それらが積み重ねられた構造を有する。

【0050】

メモリセルMCを構成するトンネル絶縁層(ゲート絶縁層)15は、例えば、酸化シリコン層である。トンネル絶縁層15は、酸窒化シリコン、酸化シリコンと窒化シリコンとの積層構造などであってもよい。また、トンネル絶縁層15は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。

【0051】

メモリセルMCを構成する電荷蓄積層16が、例えば、窒化シリコン層であり、複数のコントロールゲート18間を満たす層間絶縁層がTEOS(TetraEthOxySilane)であるとき、電荷蓄積層19側のバンドオフセットを高くするための金属元素19を含む1つの材料としては、La2O3層を用いることができる。La2O3層は、1 nm以下の厚さとするのが望ましい。これを超える厚さにすると、セル間干渉が大きくなる懸念が発生するからである。

【0052】

複数のコントロールゲート18間を満たす層間絶縁層としては、比誘電率3.9を有する酸化シリコン層と同程度の誘電率を有する材料とするのが望ましい。ここでは、層間絶縁層の例としてTEOSを掲げたが、例えば、熱処理によりポリシラザン系溶剤を焼成することにより形成される酸化シリコン層でもよい。

【0053】

また、電荷蓄積層16が窒化シリコン層でない場合や、層間絶縁層が酸化シリコン層でない場合などにおいても、既に説明した金属元素19の例のなかから適切な材料を選択することにより、金属元素19が接触する電荷蓄積層16のバンドオフセットを上昇させ、電荷蓄積層16内の電荷の横方向の移動を抑制することが可能である。

【0054】

尚、メモリセルMCを構成する電荷蓄積層16は、例えば、シリコンリッチSiN、シリコンと窒素の組成比x、yが任意であるSixNy、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)及びランタン・アルミネート(LaAlO3)のグループから選択することができる。

【0055】

また、電荷蓄積層16は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。電荷蓄積層16は、不純物が添加されたポリシリコン、メタルなどの導電体を備えることにより、フローティングゲートとして機能させてもよい。

【0056】

メモリセルMCを構成するブロック絶縁層17は、例えば、書き込み/消去時のリーク電流を防止する機能を有する。ブロック絶縁層17は、例えば、酸化シリコン(SiO2)、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)、ランタン・アルミネート(LaAlO3)及びランタンアルミシリケート(LaAlSiO)のグループから選択することができる。

【0057】

メモリセルMCを構成するコントロールゲート18は、例えば、導電性ポリシリコン層及び珪化ニッケル(NiSi)などの金属シリサイド層のうちの1つを備える。

【0058】

コントロールゲート18は、例えば、タンタルナイトライド(TaN)、タンタルカーバイト(TaC)、チタンナイトライド(TiN)などの金属化合物、又は、金属的な電気伝導特性を示す、Ni、V、Cr、Mn、Y、Mo、Ru、Rh、Hf、Ta、W,Ir、Co、Ti、Er、Pt、Pd、Zr、Gd、Dy、Ho、Er、及び、これらのシリサイドであってもよい。

【0059】

[製造方法]

図6乃至図33は、図1及び図2の半導体装置の製造方法を示している。

【0060】

まず、図6及び図7に示すように、半導体基板10として、例えば、面方位(100)、比抵抗10〜20Ωcmのp型又はn型のシリコン基板を用意する。この半導体基板10上に、絶縁層11,13,14としての酸化シリコン層と、第1、第2及び第3の半導体層12−1,12−2,12−3としての多結晶シリコン層とを、交互に形成する。続けて、絶縁層14上にマスク層(例えば、窒化シリコン層)21を形成する。

【0061】

また、PEP(Photo Engraving Process)により、マスク層21上にレジストパターンを形成する。そして、レジストパターンをマスクにして、RIE(Reactive Ion Etching)により、マスク層21、絶縁層14、第3の半導体層12−3、絶縁層13、第2の半導体層12−2、絶縁層13及び第1の半導体層12−1を、順次、エッチングする。

【0062】

これにより、フィン型積層構造Finが形成される。この後、レジストパターンは除去される。

【0063】

次に、図8及び図9に示すように、例えば、コリンを用いるウェットエッチング、CDE(Chemical Dry Etching)、又は、塩素ガスを用いるドライエッチングにより、フィン型積層構造Finを構成する第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面をリセスエッチングする。その結果、フィン型積層構造Finの第3の方向にある表面に凹部が形成される。

【0064】

次に、図10及び図11に示すように、例えば、SPA(Slot Plane Antenna)プラズマ生成技術により、フィン型積層構造Finの第3の方向にある凹部内、即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面上に、トンネル絶縁層(例えば、酸化シリコン層)15を形成する。

【0065】

次に、図12及び図13に示すように、例えば、CVDにより、フィン型積層構造Finの表面の全体を覆う電荷蓄積層(例えば、窒化シリコン層)16を形成する。

【0066】

次に、図14及び図15に示すように、例えば、RIEにより、フィン型積層構造Finの第3の方向にある凹部内に存在する電荷蓄積層16を除き、他の部分に存在する電荷蓄積層16を除去する。その結果、電荷蓄積層16は、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面上のトンネル絶縁層15上のみに残存する。

【0067】

また、この時、電荷蓄積層16は、第1の方向に複数の部分に分断され、各部分は、メモリストリングのチャネルとして機能する1つの半導体層12−i(iは1〜3のうちの1つ)に沿って第2の方向に延びる1つの層を構成する。

【0068】

次に、図16及び図17に示すように、例えば、等方性エッチングにより、マスク層21をエッチングし、マスク層21の第3の方向の幅をシュリンクする。

【0069】

この工程は、後述するコントロールゲートのパターニング時に、1つのメモリストリング内の電荷蓄積層(第2の方向に延びる1つの層)を、メモリセル毎に互いに分断することを目的に実行される。

【0070】

従って、1つのメモリストリング内の電荷蓄積層をメモリセル毎に互いに分断しないことを前提とする場合には、この工程は省略できる。

【0071】

この工程によるマスク層21のシュリンク量dとしては、コントロールゲートのパターニング時に、1つのメモリストリング内の電荷蓄積層がメモリセル毎に互いに分断されるに十分な量(理論値)とする。

【0072】

具体的には、シュリンク後のマスク層21の第3の方向の端部は、第1、第2及び第3の半導体層12−1,12−2,12−3とトンネル絶縁層15の界面より外側に配置する。より望ましくは、シュリンク後のマスク層21の第3の方向の端部は、第1、第2及び第3の半導体層12−1,12−2,12−3とトンネル絶縁層15の界面より外側かつトンネル絶縁膜15と電荷蓄積層16の界面よりも内側に配置するのが良い。

【0073】

ここで、マスク層21のシュリンク量dのばらつきが、1つのメモリストリング内の電荷蓄積層の分断不良の一因となる。

【0074】

次に、図18及び図19に示すように、例えば、CVDにより、フィン型積層構造Finの表面の全体を覆うブロック絶縁層(例えば、Al2O3層)17を形成する。

【0075】

次に、図20及び図21に示すように、フィン型積層構造Finを覆い、かつ、フィン型積層構造Fin間のスペースを完全に満たすコントロールゲート(例えば、ポリシリコン層)18を形成する。

【0076】

次に、図22乃至図24に示すように、PEPにより、コントロールゲート18上にレジストパターンを形成し、このレジストパターンをマスクにして、RIEにより、コントロールゲート18をパターニングする。

【0077】

ここで、コントロールゲート18は、パターニング前に、CMP(Chemical Mechanical Polishing)により、その上面(第1の方向の表面)を平坦化してもよい。この場合、コントロールゲート18上に酸化シリコン層などの絶縁層を形成した後に、CMPを実行するのが望ましい。

【0078】

また、レジストパターンは、コントロールゲート18の上面において、第3の方向に延びるライン&スペースパターンを有する。

【0079】

レジストパターンにより覆われていない部分に存在するコントロールゲート18及びブロック絶縁層17は、完全に除去される。同時に、レジストパターンにより覆われていない部分に存在する電荷蓄積層16も、除去される。

【0080】

このRIEでは、レジストパターンとシュリンクされたマスク層21とにより覆われていない部分が積極的に除去されるため、理論的には、レジストパターンにより覆われていない部分に存在する電荷蓄積層16も、除去される。

【0081】

しかし、既に述べたように、マスク層21のシュリンク量のばらつき等により、電荷蓄積層16の分断不良が発生する場合がある。

【0082】

そこで、電荷蓄積層16の分断不良が発生している例を、図25乃至図27に示す。この例によれば、1つのメモリストリング内の電荷蓄積層16が、メモリセル毎に完全に分断されずに、第2の方向に延びる1つの層として残存している。

【0083】

このパターニングにより、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある表面に沿って第1の方向に延びるライン&スペースパターンの複数のコントロールゲート18が形成される。

【0084】

また、フィン型積層構造Finを第1の方向から見たときは、複数のコントロールゲート18は、レジストパターンと同様に、全体として、第3の方向に延びる。

【0085】

このパターニング後、レジストパターンは除去される。

【0086】

次に、図28乃至図30に示すように、複数のコントロールゲート18間、具体的には、複数のコントロールゲート18の加工後の複数の電荷蓄積層16の剥き出しになった表面上、及び、複数のコントロールゲート18の表面上に、それぞれ、金属元素19又はその金属元素19を含む化合物(酸化物、窒化物又は酸窒化物)を添加する。

【0087】

ここで、金属元素19単体を添加するときは、イオン注入法を用い、金属元素19を含む化合物を添加するときは、LPCVD法やALD法などのコンフォーマルな堆積プロセスを用いればよい。

【0088】

尚、金属元素19又はその化合物は、1つの層を構成する必要はないが、金属元素19又はその化合物が1つの層を構成するときは、その厚さは、1 nm以下に設定するのが望ましい。

【0089】

また、金属元素19又はその化合物は、電荷蓄積層16と、後述する層間絶縁層との界面に添加されることにより、電荷蓄積層16のバンドオフセットを上昇させる。

【0090】

最後に、図31乃至図33に示すように、複数のコントロールゲート18間に、層間絶縁層(例えば、SiO2)20を満たす。層間絶縁層20は、フィン型積層構造Finの間のスペースも完全に満たす。

【0091】

以上の工程により、図1及び図2の不揮発性半導体記憶装置を形成できる。

【0092】

尚、この装置を、VLBなどの3次元不揮発性半導体メモリとして使用する場合には、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択するための選択機能が必要になるが、その選択機能については、階段構造や、レイヤー選択トランジスタなどが既に提案済みであるので、ここでの説明を省略する。

【0093】

[適用例]

実施形態に係わる不揮発性半導体記憶装置の適用例を説明する。

【0094】

尚、以下の適用例においては、上述の図1乃至図2の不揮発性半導体記憶装置と同じ要素に同じ符号を付すことによりその詳細な説明を省略する。

【0095】

図34は、第1の適用例としてのVLBを示している。図35は、図34のXXXV−XXXV線に沿う断面図を示している。

【0096】

この適用例は、半導体基板10上に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3の選択を、階段形状により行う場合を示している。

【0097】

第1、第2及び第3の半導体層12−1,12−2,12−3を備えるフィン型積層構造Finの第2の方向の両端は、それぞれ、梁22に接続される。梁22は、第3の方向に延びることにより、フィン型積層構造Finの倒壊を防止する機能を発揮する。

【0098】

梁22は、フィン型積層構造Finと同様に、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層11,13,14を備える。梁22の第3の方向の一端は、階段形状を有する。この階段形状により、コンタクトプラグ23は、それぞれ独立に、第1、第2及び第3の半導体層12−1,12−2,12−3に接続可能である。

【0099】

梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅と同じであっても、異なっていてもよい。但し、梁22における配線抵抗を下げる目的及びフィン型積層構造Finの倒壊を防止する目的から、梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅よりも広いのが望ましい。

【0100】

尚、コンタクトプラグ23は、例えば、W、Alなどの金属材料を備える。コンタクトプラグ23には、ビット線又はソース線が接続される。

【0101】

図36は、第iの半導体層(iは1〜3のうちの1つ)12−iを、半導体基板10の表面に平行な面で切り取った図である。また、図37は、絶縁層13,14を、半導体基板10の表面に平行な面で切り取った図である。

【0102】

これらの図によれば、複数のフィン型積層構造Finを並べる場合、複数のコントロールゲート18のパターニング後において、複数のコントロールゲート18間には、トレンチが形成されることが分かる。この場合、金属元素19又はその化合物は、そのトレンチの内面に添加される。また、金属元素19又はその化合物を添加した後、トレンチは、層間絶縁層20により満たされる。

【0103】

即ち、金属元素19及びその化合物は、複数のコントロールゲート18間に存在する電荷蓄積層16の第3の方向の表面上、及び、複数のコントロールゲート18の第2の方向の表面上に、それぞれ添加される。

【0104】

図38は、フィン型積層構造Finを第1の方向から見たときの複数のコントロールゲート18のパターンを示している。

【0105】

複数のコントロールゲート18は、ライン&スペースパターンを有し、全体として、第3の方向に延びる。但し、フィン型積層構造Fin間においては、複数のコントロールゲート18は、フィン型積層構造Finの第3の方向にある表面に沿って第1の方向(紙面に垂直な方向)に延びる。

【0106】

図39は、第2の適用例としてのVLBを示している。

【0107】

この適用例は、半導体基板10上に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3の選択を、第1、第2及び第3のレイヤー選択トランジスタにより行う場合を示している。

【0108】

第1、第2及び第3の半導体層12−1,12−2,12−3を備えるフィン型積層構造Finの第2の方向の両端は、それぞれ、梁22に接続される。梁22は、第3の方向に延びることにより、フィン型積層構造Finの倒壊を防止する機能を発揮する。

【0109】

梁22は、フィン型積層構造Finと同様に、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層11,13,14を備える。梁22の第3の方向の一端には、第1、第2及び第3のレイヤー選択トランジスタLSTが配置される。

【0110】

第1、第2及び第3のレイヤー選択トランジスタLSTは、例えば、FET (Field Effect Transistor)であり、第1、第2及び第3の半導体層12−1,12−2,12−3をチャネルとし、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する。

【0111】

第1、第2及び第3のレイヤー選択トランジスタLSTは、第3の方向に並んで配置され、かつ、コンタクトプラグ(共通電極)23側から順番に、一定ピッチPで配置される第1、第2及び第3のゲート電極24−1,24−2,24−3を有する。第1、第2及び第3のゲート電極24−1,24−2,24−3は、例えば、導電性ポリシリコン層、ニッケルシリサイド層などの金属シリサイド層、又は、これらの積層を備える。

【0112】

第1、第2及び第3のゲート電極24−1,24−2,24−3は、少なくとも、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面に沿って第1の方向に延びる。

【0113】

本例では、第1、第2及び第3のゲート電極24−1,24−2,24−3は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面を覆う。即ち、レイヤー選択トランジスタLSTは、ダブルゲート構造を有する。

【0114】

また、第1のゲート電極24−1を備える第1のレイヤー選択トランジスタLSTは、第1の半導体層12−1内にノーマリーオンチャネルを有する。即ち、第1のゲート電極24−1を備える第1のレイヤー選択トランジスタLSTは、第1の半導体層12−1内でノーマリーオン、第2及び第3の半導体層12−2,12−3内でオン/オフ制御可能である。

【0115】

第2のゲート電極24−2を備える第2のレイヤー選択トランジスタLSTは、第2の半導体層12−2内にノーマリーオンチャネルを有する。即ち、第2のゲート電極24−2を備える第2のレイヤー選択トランジスタLSTは、第2の半導体層12−2内でノーマリーオン、第1及び第3の半導体層12−1,12−3内でオン/オフ制御可能である。

【0116】

第3のゲート電極24−3を備える第3のレイヤー選択トランジスタLSTは、第3の半導体層12−3内にノーマリーオンチャネルを有する。即ち、第3のゲート電極24−3を備える第3のレイヤー選択トランジスタLSTは、第3の半導体層12−3内でノーマリーオン、第1及び第2の半導体層12−1,12−2内でオン/オフ制御可能である。

【0117】

一般化すると、第1乃至第nの半導体層(nは、2以上の自然数)12−1〜12−nをチャネルとする第1乃至第nのレイヤー選択トランジスタLSTのうち、第iのレイヤー選択トランジスタ(iは1〜nのうちの1つ)は、第iの半導体層においてノーマリーオン、それ以外の半導体層においてオン/オフ制御可能である。

【0118】

尚、第1、第2及び第3の半導体層12−1,12−2,12−3内のノーマリーオンチャネルは、n型不純物(砒素、リンなどの5価元素)、p型不純物(硼素、インジウムなどの3価元素)、又は、それらの両方を含む不純物領域により形成可能である。

【0119】

以上の第1、第2及び第3のレイヤー選択トランジスタLSTにより、コンタクトプラグ23を、第1、第2及び第3の半導体層12−1,12−2,12−3に共通の共通電極とすることが可能である。即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の各々に対して、個別にコンタクトプラグを設ける必要がないため、コンタクト領域のサイズを縮小可能である。

【0120】

尚、梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅と同じであっても、異なっていてもよい。但し、梁22における配線抵抗を下げる目的及びフィン型積層構造Finの倒壊を防止する目的から、梁22の第2の方向の幅は、フィン型積層構造Finの第3の方向の幅よりも広いのが望ましい。

【0121】

また、コンタクトプラグ(共通電極)23は、例えば、W、Alなどの金属材料を備える。コンタクトプラグ23には、ビット線又はソース線が接続される。

【0122】

[その他]

本実施形態は、電荷蓄積層が電気的にフローティング状態の導電層(フローティングゲート)であるVG-FG型にも適用可能である。

【0123】

例えば、電荷蓄積層としてのフローティングゲートの加工面が加工中に形成された自然酸化膜(SiO2)により覆われているときは、電荷蓄積層側を負に帯電させ、電荷蓄積層側のバンドオフセットを上昇させ、電荷蓄積層内の電子の動きを抑制するダイポールを形成可能な金属元素又はその化合物を十分な厚さで形成すればよい。

【0124】

また、電荷蓄積層としてのフローティングゲートの加工面が剥き出しになっているときは、電荷蓄積層側を負に帯電させ、電荷蓄積層側のバンドオフセットを上昇させ、電荷蓄積層内の電子の動きを抑制するダイポールを形成可能な金属元素又はその化合物を 1 nm以下の非常に薄い厚さで形成すればよい。

【0125】

この場合においても、金属元素は、例えば、Ge, Y, Sr, ランタノイド(La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu)のグループから選択可能である。

【0126】

[むすび]

実施形態によれば、1つのメモリストリング内の複数のメモリセルの電荷蓄積層が分断されていなくても、各メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制できる。

【0127】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0128】

10: 半導体基板、 11,13,14: 絶縁層、 12−1,12−2,12−3: 半導体層、 15: トンネル絶縁層(ゲート絶縁層)、 16: 電荷蓄積層、 17: ブロック絶縁層、 18: コントロールゲート、 19: 金属元素、 20: 層間絶縁層、 21: マスク層、 22: 梁、 23: コンタクトプラグ、 24−1,24−2,24−3: ゲート電極、 S1,S2,S3: メモリストリング、 MC: メモリセル、 LST: レイヤー選択トランジスタ。

【特許請求の範囲】

【請求項1】

半導体基板と、前記半導体基板の表面に垂直な第1の方向に積み重ねられ、前記半導体基板の表面に平行な第2の方向に延び、互いに絶縁される第1乃至第nの半導体層(nは2以上の自然数)と、前記第1乃至第nの半導体層をチャネルとする第1乃至第nのメモリストリングとを具備し、

前記第1乃至第nのメモリストリングの各々は、前記第2の方向に直列接続される複数のメモリセルを備え、

前記第iのメモリストリング(iは1〜nのうちの1つ)は、前記第iの半導体層の前記第1及び第2の方向に垂直な第3の方向にある表面上に、前記複数のメモリセルに対応する、複数の電荷蓄積層及び複数のコントロールゲートを備え、

前記第iのメモリストリング内において、少なくとも前記第2の方向に隣接する2つのメモリセルの電荷蓄積層が互いに結合され、

前記複数のコントロールゲート間に添加され、前記複数の電荷蓄積層のバンドオフセットを上昇させる金属元素をさらに備える

不揮発性半導体記憶装置。

【請求項2】

前記第iのメモリストリング内において、前記複数の電荷蓄積層は、互いに結合されることにより前記第2の方向に延びる1つの層を構成し、

前記金属元素は、前記複数のコントロールゲート間に存在する前記1つの層の前記第3の方向にある表面上に添加される

請求項1に記載の不揮発性半導体記憶装置。

【請求項3】

前記1つの層は、前記複数のコントロールゲート間の前記第3の方向の厚さが、それ以外の前記第3の方向の厚さよりも薄い請求項2に記載の不揮発性半導体記憶装置。

【請求項4】

前記金属元素は、Ge, Y, Sr, ランタノイド(La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu)から選択される少なくとも1つの元素を含む請求項1に記載の不揮発性半導体記憶装置。

【請求項5】

前記複数のコントロールゲート間に金属化合物層をさらに備え、前記金属化合物層は、前記金属元素を含む請求項1に記載の不揮発性半導体記憶装置。

【請求項6】

前記金属化合物層は、前記金属元素を含む酸化物、窒化物又は酸窒化物を備える請求項5に記載の不揮発性半導体記憶装置。

【請求項7】

前記金属化合物層の前記第3の方向の厚さは、1 nm以下である請求項5に記載の不揮発性半導体記憶装置。

【請求項8】

前記複数の電荷蓄積層は、窒化シリコン層を備え、前記金属化合物層は、La2O3を備える請求項5に記載の不揮発性半導体記憶装置。

【請求項9】

前記第1乃至第nの半導体層の前記第2の方向の一端は、階段形状を有する請求項1に記載の不揮発性半導体記憶装置。

【請求項10】

前記第1乃至第nの半導体層をチャネルとする第1乃至第nのレイヤー選択トランジスタをさらに備え、前記第iのレイヤー選択トランジスタ(iは1〜nのうちの1つ)は、第iの半導体層においてノーマリーオンである請求項1に記載の不揮発性半導体記憶装置。

【請求項11】

請求項1に記載の不揮発性半導体記憶装置の製造方法において、

前記第1乃至第nの半導体層を形成する工程と、

前記第iの半導体層の前記第3の方向にある表面上に、前記複数のメモリセルに対応する、前記複数の電荷蓄積層及び前記複数のコントロールゲートを形成する工程と、

前記複数のコントロールゲート間に前記金属元素を添加する工程と

を具備する不揮発性半導体記憶装置の製造方法。

【請求項12】

前記金属元素の添加は、前記複数のコントロールゲート間に、前記金属元素を含む酸化物、窒化物又は酸窒化物を形成することにより行う請求項11に記載の不揮発性半導体記憶装置の製造方法。

【請求項1】

半導体基板と、前記半導体基板の表面に垂直な第1の方向に積み重ねられ、前記半導体基板の表面に平行な第2の方向に延び、互いに絶縁される第1乃至第nの半導体層(nは2以上の自然数)と、前記第1乃至第nの半導体層をチャネルとする第1乃至第nのメモリストリングとを具備し、

前記第1乃至第nのメモリストリングの各々は、前記第2の方向に直列接続される複数のメモリセルを備え、

前記第iのメモリストリング(iは1〜nのうちの1つ)は、前記第iの半導体層の前記第1及び第2の方向に垂直な第3の方向にある表面上に、前記複数のメモリセルに対応する、複数の電荷蓄積層及び複数のコントロールゲートを備え、

前記第iのメモリストリング内において、少なくとも前記第2の方向に隣接する2つのメモリセルの電荷蓄積層が互いに結合され、

前記複数のコントロールゲート間に添加され、前記複数の電荷蓄積層のバンドオフセットを上昇させる金属元素をさらに備える

不揮発性半導体記憶装置。

【請求項2】

前記第iのメモリストリング内において、前記複数の電荷蓄積層は、互いに結合されることにより前記第2の方向に延びる1つの層を構成し、

前記金属元素は、前記複数のコントロールゲート間に存在する前記1つの層の前記第3の方向にある表面上に添加される

請求項1に記載の不揮発性半導体記憶装置。

【請求項3】

前記1つの層は、前記複数のコントロールゲート間の前記第3の方向の厚さが、それ以外の前記第3の方向の厚さよりも薄い請求項2に記載の不揮発性半導体記憶装置。

【請求項4】

前記金属元素は、Ge, Y, Sr, ランタノイド(La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, Lu)から選択される少なくとも1つの元素を含む請求項1に記載の不揮発性半導体記憶装置。

【請求項5】

前記複数のコントロールゲート間に金属化合物層をさらに備え、前記金属化合物層は、前記金属元素を含む請求項1に記載の不揮発性半導体記憶装置。

【請求項6】

前記金属化合物層は、前記金属元素を含む酸化物、窒化物又は酸窒化物を備える請求項5に記載の不揮発性半導体記憶装置。

【請求項7】

前記金属化合物層の前記第3の方向の厚さは、1 nm以下である請求項5に記載の不揮発性半導体記憶装置。

【請求項8】

前記複数の電荷蓄積層は、窒化シリコン層を備え、前記金属化合物層は、La2O3を備える請求項5に記載の不揮発性半導体記憶装置。

【請求項9】

前記第1乃至第nの半導体層の前記第2の方向の一端は、階段形状を有する請求項1に記載の不揮発性半導体記憶装置。

【請求項10】

前記第1乃至第nの半導体層をチャネルとする第1乃至第nのレイヤー選択トランジスタをさらに備え、前記第iのレイヤー選択トランジスタ(iは1〜nのうちの1つ)は、第iの半導体層においてノーマリーオンである請求項1に記載の不揮発性半導体記憶装置。

【請求項11】

請求項1に記載の不揮発性半導体記憶装置の製造方法において、

前記第1乃至第nの半導体層を形成する工程と、

前記第iの半導体層の前記第3の方向にある表面上に、前記複数のメモリセルに対応する、前記複数の電荷蓄積層及び前記複数のコントロールゲートを形成する工程と、

前記複数のコントロールゲート間に前記金属元素を添加する工程と

を具備する不揮発性半導体記憶装置の製造方法。

【請求項12】

前記金属元素の添加は、前記複数のコントロールゲート間に、前記金属元素を含む酸化物、窒化物又は酸窒化物を形成することにより行う請求項11に記載の不揮発性半導体記憶装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【公開番号】特開2013−110193(P2013−110193A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−252444(P2011−252444)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]